### Beyond ADPLLs for RF and mm-Wave Frequency Synthesis Watching out for new techniques: oversampling-reference and charge-sharing locking

Siriburanon, Teerachot; Staszewski, Robert Bogdan

10.1109/MSSC.2024.3496612

**Publication date**

**Document Version** Final published version

Published in

IEEE Solid-State Circuits Magazine

Citation (APA)

Siriburanon, T., & Staszewski, R. B. (2025). Beyond ADPLLs for RF and mm-Wave Frequency Synthesis: Watching out for new techniques: oversampling-reference and charge-sharing locking. *IEEE Solid-State Circuits Magazine*, 17(1), 69-85. https://doi.org/10.1109/MSSC.2024.3496612

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

### Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# Beyond ADPLLs for RF and mm-Wave Frequency Synthesis

Watching out for new techniques: oversampling-reference and charge-sharing locking

Frequency command word

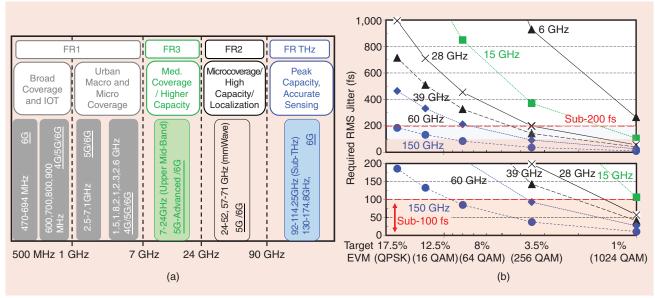

o address the relentless increase in data rates in wireless communication systems employing advanced modulation schemes, such as 5G frequency range (FR) 2 [see Fig-

Digital Object Identifier 10.1109/MSSC.2024.3496612 Date of current version: 22 January 2025 ure 1(a)], generating mm-wave signals with minimal integrated phase noise (PN) or RMS jitter is of paramount concern [1]. Figure 1(b) specifies the required jitter to achieve the targeted EVM performance. For instance, for an EVM of less than 3.5%, as needed by a 256-QAM 28-GHz carrier, the RMS jitter contributed by the LO must be below 200 fs. As the

carrier frequency or the symbol constellation density increases, the required RMS jitter becomes even more stringent. For example, 1024 QAM at 39 GHz demands an RMS jitter of <50 fs [2], [3], [4].

To reach such good performance, two major noise sources, i.e., the oscillator PN and noise associated with the phase detection mechanism in a PLL, should be carefully considered. Under the optimal loop bandwidth, the overall jitter should be equally contributed by the oscillator and PD. Note that the in-band (IB) PN of a PLL is typically dominated by its PD and the preceding reference path, i.e., the XO and its low-noise reference buffer [5], [6].

In this article, architectures of low-jitter RF and mm-wave PLLs, with special emphasis on ADPLLs, are reviewed. Finally, PLL benchmarking and the future outlook will be discussed.

#### **PLL Architectures**

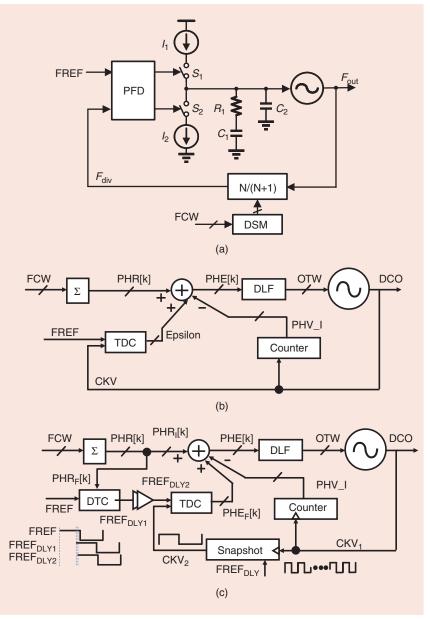

To address the stringent jitter requirements of 5G systems, various techniques have been proposed in the past decade. Traditional analog charge pump (CP)-based PLLs targeting low jitter mainly rely on the precise design of high-current CP circuitry with accurate up/down current matching  $[I_1 \text{ and } I_2 \text{ in Figure 2(a)}]$ and large analog loop filter components ( $C_1$ ,  $C_2$ , and  $R_1$ ). Moreover, these issues become increasingly challenging in advanced CMOS nodes (e.g., below 28 nm) [7], [8], [9]. Additionally, in a fractional-N operation, the nonlinearity in the CP as well as in the PFD, exacerbated by the associated delta-sigma modulator (DSM), will result in a worse IBPN [10]. To overcome these difficulties, ADPLLs are often utilized, as they are more compatible with CMOS scaling [11], [12]. Additionally, digital calibration and compensation techniques can be easily employed to maintain performance across PVT variations [13]. However, the conventional ADPLL approaches often encounter RMS jitter constraints resulting from the resolution and linearity limitations of the inverter-delay-based TDC, which in turn leads to a less competitive IBPN and IB fractional spurs in 5G applications [14], [15].

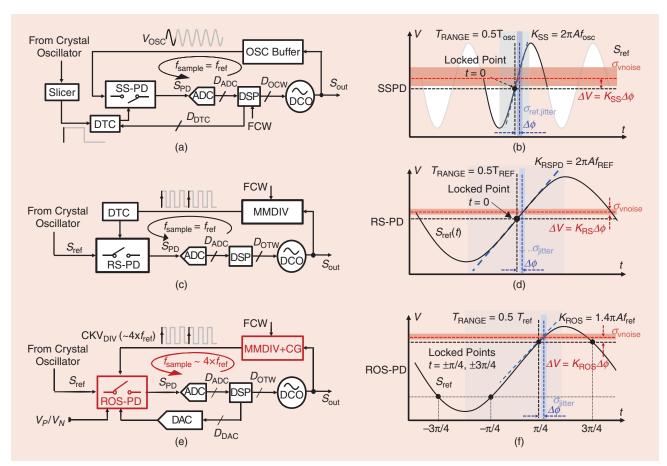

In response, more complex phase detection methods, such as using a digital-to-time converter (DTC) to prealign the reference and variable clocks for the ultimate high-resolution (but short-range) detection, have been proposed [16], [17], [18], [19]. As another example, a subsampling (SS) PD leverages the high slew rate of the oscillator feedback signal by sampling it with sharp edges of the reference frequency ( $f_{ref}$ ) clock [20], [21], [22]. This yields a high PD gain with extremely high resolution. However, due to the limited linearity of the oscillator waveform, the PLL may lose lock in the presence of oscillator perturbations [23], necessitating an additional frequency-locked loop (FLL) to ensure reliable locking [24]. Alternatively, a reference sampling (RS) PLL utilizes a frequency-divided signal from the oscillator feedback path to directly sample the reference sinusoidal XO waveform [25]. The wide linear range and limited slew rate of a typical low-cost XO (below 50 MHz) provide excellent locking robustness over a broad locking range. However, this introduces challenges related to resolving the issue of the low gain of the time-to-voltage conversion [26].

Due to the practical limitations in the PN performance of oscillators at mm-wave frequencies, a fairly large PLL bandwidth is necessary to achieve jitter below 100 fs. However, there is a tradeoff between the achievable PLL bandwidth and  $f_{ref}$ , and therefore, the authors of [27], [28], [29], and [30] take advantage of using rather "exotic" XOs with an extremely high reference frequency (e.g., >250 MHz). To keep the use of an inexpensive XO with ≤50 MHz, various reference multiplication techniques have been introduced. Unfortunately, these methods typically require an additional delay chain and calibration for the proper phase relationship, leading to increased power consumption and area [31], [32], [33]. Recently, a more efficient solution

FIGURE 1: (a) 5G/6G communication standards at various FRs [FR1–FR3 and FR terahertz (THz)] and (b) the target RMS jitter for various types of complex modulation schemes and carrier frequencies.

points to the oversampling of the frequency reference waveform source, which can enhance the PD rate beyond FREF. This is achieved by not only locking at the zero-crossing points of the sinusoidal reference waveform but also by distributing the locking points across the entire reference period [34], [35], [36], [37], [38].

In the following section, we review the counter-based and DTC-assisted ADPLL architectures before discussing the evolution leading to the oversampling-based ADPLLs. We then conclude with implementation examples.

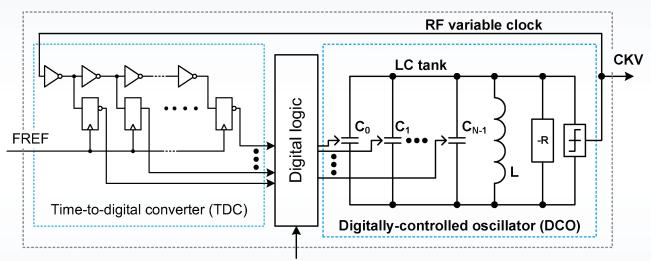

#### ADPLL

Figure 2(b) is a block diagram of the natively fractional-N ADPLLbased frequency synthesizer, which operates in a digitally synchronous fixed-point phase domain [39].1 The variable phase signal PHV[i] is generated by counting the rising edges of the DCO's clock through a digital counter. For fine phase detection, a TDC measures and digitizes the phase difference ( $\epsilon$ ) between the reference clock (FREF) and the oscillator feedback signal (CKV). Meanwhile, the reference phase signal PHR[k]is derived by accumulating the frequency command word (FCW)2 at each rising edge of the retimed FREF clock. The synchronous arithmetic PD computes the difference between the sampled variable phase and the reference phase to determine the phase error (PHE) PHE[k]. This can be mathematically modeled as  $PHE[k] = PHR[k] - PHV[k] + \epsilon$ . The digital PHE is processed by a simple digital loop filter and then normalized by the DCO gain  $(K_{DCO})$  to produce the oscillator tuning word (OTW). This approach ensures that the extensive digital logic is clocked after the quiet phase of the PHE detection by the TDC.

<sup>1</sup>Note that it is also common for digital PLL architectures to utilize a multimodulus divider (MMD) with a DSM in the feedback path to achieve the fractional-*N* operation [17], [18]. For a more detailed comparison between the two approaches, see [40].

<sup>2</sup>Historically, this is referred to as "*N*."

Figure 3 provides more details on how the reference phase PHR[*k*] (shown in green) aligns with the variable phase (shown in red) when the latter is perfectly locked, lagging, or leading against the former. For the sake of illustration, the FCW, which denotes the expected frequency multiplication ratio, is 3.2. Since the oscillation time period is an inverse of the oscillating frequency, there will be 3.2 clock cycles of CKV per single cycle of FREF. Also, we assume that the

initial phase is zero (i.e., the FREF and CKV rising edges are aligned at time zero).

It can be observed that in the fractional-N operation, the fractional relation between the reference phase and the variable phase changes across one oscillator period. Therefore, this sets the required range for the fractional phase measurement via a TDC, which is the key component to ensure low quantization noise. The

FIGURE 2: Simplified PLL block diagrams: the (a) conventional PFD/CP PLL, (b) counter-based ADPLL, and (c) ADPLL with digital-to-time converter (DTC) assistance to ease the TDC range. FCW: frequency command word; OTW: oscillator tuning word; PHE: phase error; DLF: digital loop filter.

IBPN due to the TDC quantization can be modeled as

$$\mathcal{L} = \frac{(2\pi)^2}{12} \left(\frac{\Delta t_{\rm res}}{T_V}\right)^2 \frac{1}{f_R} \tag{1}$$

where  $\mathcal{L}$  is the PN contributed by the TDC resolution  $\Delta t_{\rm res}$  and  $T_V$  is the period of the DCO signal fed back into the TDC.

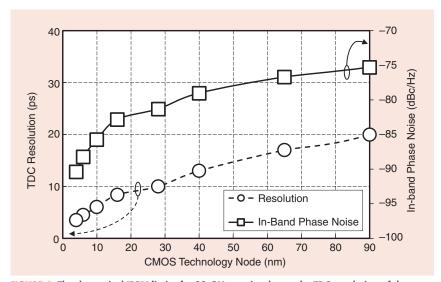

As shown in Figure 4, as the CMOS technology scales down from the 90-nm node to 28 nm, the typical resolution of a delay line-based TDC [39], [41] is reduced from 20 to 10 ps but can further go down to 2–3 ps in

advanced FinFETs (and GAA nodes) [42]. This results in a reduction of the IBPN from -75 to -81 dBc/Hz when considering a 30-GHz carrier. However, to further lower the total RMS jitter below this limit, alternative techniques must be considered. In the past two decades, there have been various techniques proposed to lower  $\Delta t_{\rm res}$ , e.g., Vernier delay lines, time amplifiers, and so on. The downside of such high resolution is the need to cover the whole oscillator period, resulting in either high power consumption or poor nonlinearity causing high fractional spurs.

FIGURE 3: A conceptual block diagram of a phase-domain ADPLL with the evolution of phase signals.

FIGURE 4: The theoretical IBPN limit of a 30-GHz carrier due to the TDC resolution of the corresponding CMOS technology nodes.

As a means to alleviate the above issue, Figure 2(c) illustrates a DTCassisted ADPLL architecture. The DTC can be controlled by the fractional part of the accumulated reference phase  $(PHR_F[k])$  to delay the edge of the reference clock (FREF<sub>D</sub>. LY2) in order to align it with the oscillator feedback signal (CKV). Note that due to the much higher rate of the oscillator feedback signal clock, a snapshot circuit is introduced to allow only the important edges of the feedback signal (i.e., CKV<sub>2</sub>) to proceed to the TDC. This approach greatly reduces the required range of the TDC. However, achieving a high-resolution DTC with excellent linearity now becomes crucial [43], [44], [45]. Consequently, several new techniques, such as oversampling-based TDCs, have been developed.

### Evolution of Phase Detection: From Sub-Sampling and Sampling to Oversampling

To achieve excellent jitter with high power efficiency, leading to a high FOM of a PLL, SS/bang-bang (BB) PDs have been promoted [24], [30], [46]. They exploit the intrinsically high time-to-voltage gain provided by the high slope of the oscillator waveform and sharp edges of the reference clock in order to reduce the PD noise, but at the expense of a narrow locking range [see Figure 5(a) and (b)]. As the sampling clock of the comparator input, the reference signal from the XO needs to translate its "gentle" sinusoidal waveform into sharp edges through an LNB, but that consumes significant power.

Alternatively, the XO waveform can be used directly as an input without requiring a buffer, while the sampling edge is generated from the divided oscillator output via a feedback clock generator (CG). This approach, known as the *RS-PD* [25], is examined in Figure 5(c) and (d). Although the PD gain from the input slope ( $K_{RSPD}$ ) is lower, the phase detection range is significantly wider, allowing it to detect various disturbances

and enhance robustness against PVT variations. Additionally, compared to the SS approach, the slew rate requirement of the sampling clock is more relaxed.

To reduce the PD's noise contribution to the output, a higher reference frequency ( $f_{\rm ref}$ ) is typically employed, as it gives a lower N [6]. However, the 100–500-MHz XOs used for this purpose are rather expensive and consume excessive power. Another approach to boost the effective reference frequency with a standard-

frequency XO calls for an additional reference multiplier (doubler/quadrupler/octrupler) [31], [32], [33] or cascaded PLLs [47]. This requires a duty cycle calibration (DCC) and/or additional circuits, which increase the overall power and area. Arguably, the best approach would be to extract the information contained in the reference sinusoidal XO waveform,  $S_{ref}$ , by sampling it by the oscillator clock edges [26]. This allows the possibility of increasing the PD rate, and consequently,  $N_s$ , by, for example,  $4\times$  overs-

ampling, as in Figure 5(e) and (f) [34], [35], [37], [38], [48].

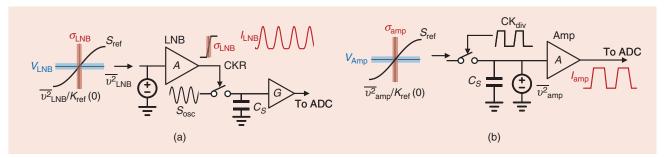

Figure 6 presents a detailed analysis of PN considerations associated with the SSPD and RS-PD when using a standard XO providing a sinusoidal waveform as the reference [2], [26], [49]. With an ideal clock edge of the sliced reference (CKR), the PD noise in the SSPD can be minimized to a negligible level [20]. This is achieved because the sampled thermal voltage noise and input-referred noise (IRN) of the gain stage *G* are converted

FIGURE 5: Simplified diagrams of digital PLL architectures using the (a) SSPD, (c) RS-PD, and (e) reference oversampling (ROS) PD, together with their corresponding PD characteristics of the (b) SSPD, (d) RS-PD, and (f) ROS-PD. CG: clock generator.

FIGURE 6: A comparison of PN contributions in the (a) SSPD and (b) RS-PD.

to time jitter via a steep slope of  $2\pi A_{\rm osc} f_{\rm osc}$ , where  $A_{\rm osc}$  and  $f_{\rm osc}$  represent the oscillator's amplitude and frequency, respectively. Note that the LNB plays an important role in translating the relatively slow sinusoidal input waveform into "super"-sharp clock edges for sampling, but considerations of the on-chip LNB are usually neglected in the literature. The IRN of the LNB ( $\overline{v^2}_{LNB}$ ) can actually dominate the SSPD jitter, due to the gentle slope of  $2\pi A_{\text{ref}} f_{\text{ref}}$ , where  $A_{\text{ref}}$ is the reference waveform amplitude. The variance of timing uncertainty in the SSPD can be derived as

$$\sigma_{\text{SSPD}}^2 = \frac{\overline{v^2}_{\text{LNB}}}{(2\pi A_{\text{ref}} f_{\text{ref}})^2} + \frac{KT/C_S + \overline{v^2}_{\text{IRN-}G}}{(2\pi A_{\text{osc}} f_{\text{osc}})^2}.$$

(2)

In contrast, in the RS-PD [Figure 6(b)], the sampling clock is obtained from an MMD in the oscillator feedback path ( $CK_{\rm div}$ ), which naturally features sharp edges. The reference sinusoidal waveform is now directly sampled on the sampling capacitor  $C_S$  without any buffer but at the expense of a slow slope of  $2\pi A_{\rm ref} f_{\rm ref}$  of the incoming  $S_{\rm ref}$ . To address this, an isolation buffer is employed with amplification A to help with the quantization noise downstream. The variance of timing uncertainty in the RS-PD can be derived as

$$\sigma_{RSPD}^2 = \frac{\overline{v^2}_{amp} + KT/C_S}{(2\pi A_{ref} f_{ref})^2}$$

(3)

where  $\overline{v^2}_{amp}$  is the amplifier's IRN. When using a sufficiently large capacitor  $C_S$  (in picofarads), its thermal noise can be neglected compared to the IRN of the LNB or amplifier.

The PN in radians ( $\sigma_{\phi \rm SSPD}^2$  and  $\sigma_{\phi \rm RSPD}^2$ ) can be obtained by normalizing with an oscillator period and multiplying by  $2\pi$ . Further, the magnitude of PN spectra at the AD-PLL RF output can be calculated by normalizing  $\sigma_{\phi \rm SSPD}^2$  and  $\sigma_{\phi \rm RSPD}^2$  by the phase detection rate  $f_{\rm PD}$ , which is equal to the reference clock  $f_{\rm ref}$  for the RS-PD. The output PN contributed by the SSPD and RS-PD can be derived as

$$\begin{cases} \mathcal{L}_{\text{SSPD}} \approx \frac{\overline{V^2}_{\text{LNB}}}{f_{\text{ref}}} \cdot \frac{f_{\text{out}}^2}{A_{\text{ref}}^2 f_{\text{ref}}^2} \\ \mathcal{L}_{\text{RSPD}} \approx \frac{\overline{V^2}_{\text{amp}}}{f_{\text{PD}}} \cdot \frac{f_{\text{out}}^2}{A_{\text{ref}}^2 f_{\text{ref}}^2}. \end{cases} \tag{4}$$

It can be observed that the jitter in both the SSPD and RS-PD can be dominated by the LNB and amplifier, respectively. For the output PN contributed by the RS-PD, the IRN of an inverter-based amplifier ( $\bar{\nu}_{amp}$ ) adopted in [37] is 34.75  $\mu$ V<sub>RMS</sub> while consuming 122  $\mu$ W. Considering an  $A_{ref}$  of 0.5 V,  $f_{ref}$  of 50 MHz, and  $f_{out}$  of 9.6 GHz, the theoretical IBPN can be estimated by (4), yielding

-114.48 dBc/Hz. On the other hand. an inverter can operate as an LNB that converts a reference waveform into the RS edges used in the SSPD. Considering an  $f_{ref}$  of 50 MHz and an input swing of  $\sim 1 V_{pp}$ , the simulated PN shows a reference floor of around -160 dBc/Hz when consuming a similar power of 120  $\mu$ W. Note that this level of PN at 50 MHz is equivalent to -114 dBc/Hz when it refers to an output frequency of 9.6 GHz. Therefore, it can be concluded that the jitter performance limited by either an LNB or amplifier in the SSPD and RS-PD is quite similar under the constraint of similar power consumption.

The RS-PD architecture has recently been gaining interest thanks to its natural capability of beneficially increasing the phase detection rate  $f_{\rm PD}$  in (4) beyond  $f_{\rm ref}$  [35], [36]. With an example of 4× oversampling, four points are chosen at  $\pm \pi/4, \pm 3\pi/4$  positions on  $S_{\rm ref}$ , which keep the PD gain (i.e., sampling slope) at  $(1/\sqrt{2})A_{\rm ref}f_{\rm ref}$ . Taking advantage of the 4× PD rate, the output PN contributed by the reference oversampling (ROS) PD is

$$\mathcal{L}_{\text{ROSPD}} \approx \frac{\overline{V^2_{\text{amp}}}}{4f_{\text{ref}}} \cdot \frac{2f_{\text{out}}^2}{A_{\text{ref}}^2f_{\text{ref}}^2}.$$

(5)

The net result is a 2× improvement in jitter power compared to a singlesampling RS-PD. Table 1 summarizes the theoretical jitter and power consumption numbers in 1x sampling and 4× oversampling PLLs. Under the 4× ROS, the amplifier consumes 4× higher power. The amplifier amplifies the sampled voltage and charges the ADC's capacitor. This operation can be gated off outside of the tracking phase, thereby allowing power saving by a factor  $\gamma$ (e.g., 0.5). Comparing the FOM<sub>iitter</sub> in Table 1, which is defined as  $10\log_{10}(\sigma_t^2) + 10\log_{10}(P_{dc})$  [20], the first jitter term in the ROS-PD is lowered by a factor of 1/4 (1.25 dB), while the second power term is increased by  $10\log_{10}(1+3\beta)$ , where  $\beta = P_{PD}/P_{dc}$  represents the fraction of the full PD path power to the total. For example, in [50],  $P_{PD} \approx 0.22 \,\text{mW}$  (PD,

TABLE 1. THE PERFORMANCE OF THE RS-PD (SINGLE SAMPLING) VERSUS THE ROS-PD (4× SAMPLING).

| PARAMETER                 | SINGLE SAMPLING                                              |                            | 4× OVERSAMPLING                                             |                                |

|---------------------------|--------------------------------------------------------------|----------------------------|-------------------------------------------------------------|--------------------------------|

|                           | EQUATION                                                     | VALUE                      | EQUATION                                                    | VALUE                          |

| $I_{D,RMS}$               | $\gamma I_{D, \text{RMS}}$                                   | <i>I</i> <sub>1</sub>      | $4\gamma I_{D,RMS}$                                         | 4/1                            |

| $\sigma_{ m amp}$         | $rac{ar{V_{ m amp}}}{2\pi A f_{ m ref}}$                    | $\sigma_{	ext{amp1}}$      | $\frac{\bar{v}_{amp}}{2\pi A f_{ref} \sin \frac{\pi}{4}} *$ | $\sqrt{2\sigma_{\text{amp1}}}$ |

| $\sigma_{\phi-	ext{amp}}$ | $rac{ar{v}_{amp}f_{out}}{Af_{ref}}$                         | $\sigma_{\phi-	ext{amp1}}$ | $\sqrt{2}rac{ar{v}_{ m amp}f_{ m out}}{Af_{ m ref}}$       | $\sqrt{2\sigma_{\phi-amp1}}$   |

| $P_{\rm PD}$              | $\gamma V_{DD}I_{D,\mathrm{RMS}}$                            | $P_{\rm PD1}$              | $4\gamma V_{DD}I_{D,RMS}$                                   | $4P_{\rm PD1}$                 |

| $\sigma_t^{2\dagger}$     | $\sigma_{	ext{PD}}^{	ext{2}} + \sigma_{	ext{OSC}}^{	ext{2}}$ | $\sigma_{t1}^2$            | $\frac{1}{2}\sigma_{PD}^2 + \sigma_{OSC}^2$                 | $\frac{3}{4}\sigma_{t1}^2$     |

| $P_{\rm dc}$              | $P_{\rm PD} + P_{\rm HS}$                                    | $P_{dc1}$                  | $4P_{\rm PD} + P_{\rm HS}$                                  | $P_{\rm dc1} + 3 P_{\rm PD}$   |

<sup>\*</sup>The 4× oversampling PD samples the slope at four  $\pm \pi/4$  positions.

<sup>&</sup>lt;sup>†</sup>Under optimum bandwidth, the jitter contributed by the PD and oscillator are equal.

ADC, digital) of the 1× sampling, and  $P_{dc} \approx 12$  mW. As a result, the FOM<sub>jitter</sub> improvement of 4× ROS can be 1.25 –  $10 log_{10}(1+30.22/12) = 1.01$  dB.

### **Selected PLL Examples**

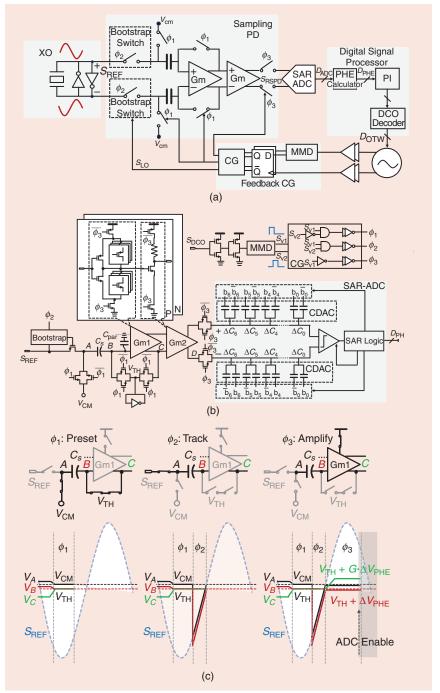

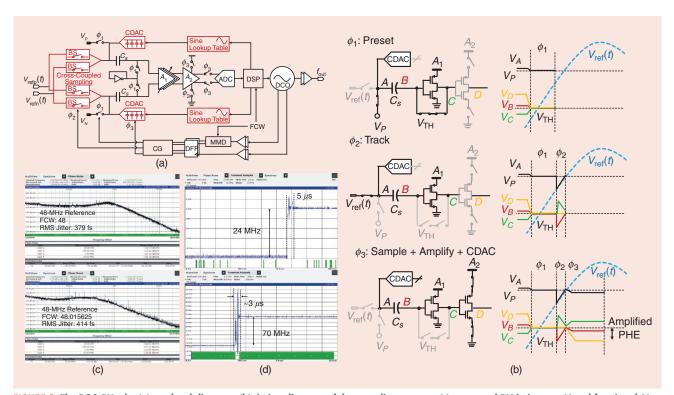

### RS-PLL

A system diagram of the featured RS-PLL appears in Figure 7(a). The outputs from the DCO are buffered to generate digital clock signals. One of them is divided by the MMD, whose phases are then resampled by standard-cell D flip-flops to eliminate the MMD noise. The CG produces  $S_{LO}$ and the three phases for the RS-PD switches. The  $S_{LO}$  signal carries the oscillator's phase information, decimated to a rate close to the reference frequency, and directly samples the reference XO's waveform through the bottom plate sampling capacitor. The sampled signal is then converted into voltage, representing the PHE, and amplified by the twostage amplifier. A compact SAR-ADC digitizes the amplified signal,  $S_{RSPD}$ , into an 8-b digital output,  $D_{ADC}$ . In the DSP block, the PHE calculator converts  $D_{ADC}$  into  $D_{PHE}$ , applying dc offset compensation. The digital loop filter, implemented with proportional-integral (PI) control, uses adjustable  $\alpha$  and  $\rho$  factors for optimization. The digital nature of the loop allows easy programming and optimization of the loop bandwidth and stability, which are crucial for minimizing the integrated jitter by fine-tuning the  $\alpha$  and  $\rho$  parameters. The DCO decoder manages the DCO gain ( $K_{DCO}$ ) and generates the OTW for the switched-capacitor banks, helping to minimize the DCO PN.

The circuit implementation of the RS-PD is depicted in Figure 7(b). The reference sinusoidal waveform ( $S_{REF}$ ) from the XO is directly sampled by the high-speed bootstrap switch, triggered by the divided oscillator edges from the CG block. The left and right plates of the bottom-plate sampling capacitor  $C_S = 2$  pF are preset to the common-mode voltage ( $V_{cm}$ ) and threshold voltage ( $V_{th}$ ), respectively,

both of which are automatically generated by a self-bias inverter with a minimum transistor width and the same length as used in the  $G_{m1}$  stage. The preset switches are implemented using CMOS transmission gates to ensure low on-resistance.

As mentioned earlier, the sampled signal must be amplified prior to digitization to compensate for the low time-

to-voltage gain ( $K_{RSPD}$ ), which is due to the slow slope of the reference signal. This amplification is handled by the two-stage amplifier ( $G_{m1}$  and  $G_{m2}$ ). For an accurate voltage transfer during the bottom plate sampling, the input parasitic capacitance of  $G_{m1}$  must be kept small, limiting the gain of the first stage. Additionally, input node B of  $G_{m1}$  carries voltage information

FIGURE 7: An RS ADPLL: the (a) top-level diagram, (b) schematic of the RS phase digitization, and (c) timing diagram of the sampling phases.

# Generating mm-wave signals with minimal integrated phase noise or RMS jitter is of paramount concern.

derived from  $S_{DCO}$ , which has a low transfer gain due to the slope of  $S_{REF}$ . This imposes a strict noise constraint, necessitating a low IRN for  $G_{m1}$ . An inverter-based structure is employed for  $G_{m1}$ , with the transistor length optimized to 120 nm to minimize the flicker noise and achieve a low IRN. Eight parallel PMOS and NMOS units are used to control both the gain (~6) and the output common-mode voltage. Additionally, power saving functionality is integrated through gated PMOS and NMOS transistors controlled by  $\bar{\phi}_3$ and  $\phi_3$ . With this gated design,  $G_{m1}$ consumes less than 60 µW while maintaining a low IRN of 122  $\mu V_{RMS}$  when integrated up to 160 MHz, corresponding to an IBPN limit of -122 dBc/Hz. The second stage,  $G_{m2}$ , is a commonsource amplifier that provides higher gain and improved driving capability to charge the CDAC in the subsequent SAR-ADC stage. Since  $G_{m1}$  dominates the overall IRN,  $G_{m2}$  is designed with a minimum transistor length of 30 nm to enhance the settling speed. It delivers a gain of 10 when driving a 120-fF CDAC load, with a settling time of under 5 ns. In addition,  $G_{m2}$  incorporates gated PMOS and NMOS switches at the top and bottom to reduce the power consumption. Once the amplified signal has fully settled on the bottom plates of the CDAC, two CMOS switches between  $G_{m2}$  and the 8-b SAR-ADC open, initiating the ADC's conversion process. It is worth noting that even in the presence of significant frequency perturbations, the sampled voltage remains within a large monotonic range centered around the locking point. Even at the saturation point, the loop will maintain the proper negative feedback for accurate phase and frequency tracking, unlike in the prior art, such as [2] and [20].

The Reference Sampling process consists of three operational phases, as depicted in Figure 7(c). When op-

erating at an  $f_{\rm ref}$  of 80 MHz,  $\phi_1$  provides a ~4-ns window to preset the voltages on the top and bottom plates of  $C_s$ . During this phase,  $V_A$  is set by the common-mode voltage  $V_{\rm CM}$ , and  $V_B$  is set by  $V_C$ , which is self-biased at the threshold voltage ( $V_{\rm th}$ ) of  $G_{\rm ml}$ . This configuration helps to eliminate any offset caused by mismatches between the common-mode voltage of  $S_{\rm ref}$  and the threshold voltage of  $G_{\rm ml}$ .

The second phase  $(\phi_2)$  is for tracking, during which there is a 2-ns window that allows  $V_A$  to follow the input waveform  $S_{\rm ref}$  The bottom plate sampling operation ensures that  $V_B$  tracks the changes in  $V_A$ . Once  $\phi_2$  is complete, the sampled voltage held at  $V_B$  (on the ground capacitance of the bottom plate of  $C_S$  at node B) represents the voltage  $V_{\rm th} + \Delta V_{\rm PHE}$ , where  $\Delta V_{\rm PHE}$  contains the PHE information translated from the time-to-voltage conversion at the sampling instant  $0 + \Delta \phi$

In the final phase,  $\phi_3$ ,  $V_C$  is amplified and settles at  $V_{\rm th} + G_1 \cdot \Delta V_{\rm PHE}$ . MM] The second-stage amplifier  $G_{m2}$ further amplifies this signal with an additional gain  $G_2$  at node D before charging the CDAC capacitors in the SAR-ADC. The ADC enable signal, triggered by  $\phi_1$ , initiates the ADC conversion process. It is critical to ensure that the end of  $\phi_2$ , which marks the time-to-voltage conversion, is not interrupted by any other phase. To prevent any such interference, a small delay is introduced at the rising edge of  $\phi_3$ . Additionally, the CMOS switches preceding the SAR-ADC must open before the shutdown of  $G_{m2}$  during phase  $\phi_3$ .

The proof-of-concept RS-PLL was fabricated in Taiwan Semiconductor Manufacturing Company (TSMC) 28-nm LP CMOS. A standard external 80-MHz XO was employed as the reference. The output PN at 2.4 GHz, corresponding to a frequency multiplica-

tion factor of N = 30, shows that the optimal bandwidth is around 2 MHz, and the IBPN reaches -115 dBc/Hz. The integrated jitter, measured from 10 kHz to 30 MHz, is 355 fs. Additionally, the main reference spur measures -60 dBc. The total power consumption is 1.1 mW. The passive sampling switches and gated operation in the  $G_m$  stages consumes a low power consumption of 120  $\mu$ W. The compact-sized SAR-ADC consumes  $60 \,\mu\text{W}$  while operating at 80 MHz. The RS-PLL remains locked even under a DCO supply modulation ranging from the original 0.2 up to 0.6 V, demonstrating the architectural robustness, without requiring any additional FLL.

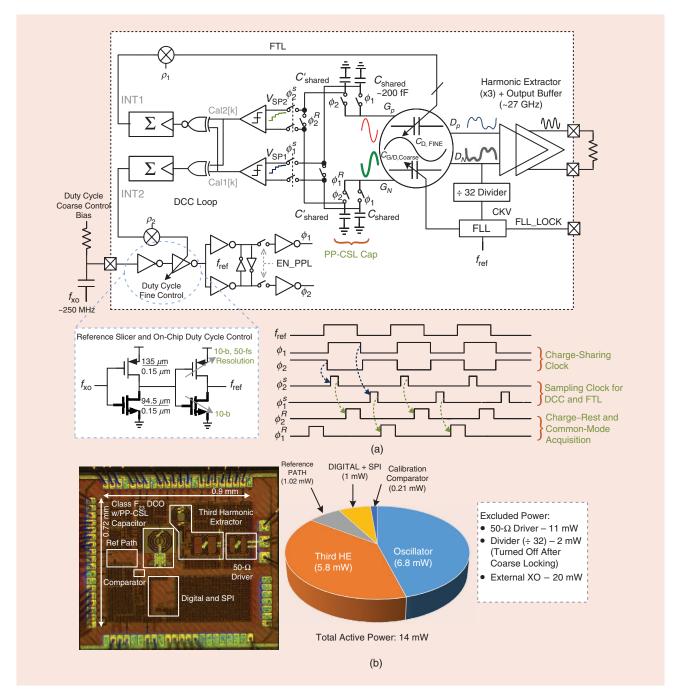

### **ROS-PLL**

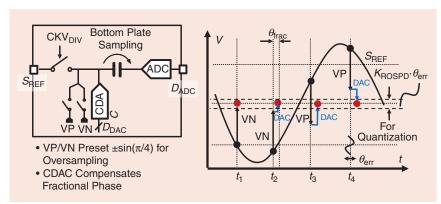

By sampling more points along the accurate sinusoidal waveform  $S_{REE}$ of the XO, we can increase the PLL's phase correction rate beyond the reference frequency,  $f_{ref}$  A higher oversampling ratio  $(M = f_{\text{sample}}/f_{\text{ref}})$  can expand the loop bandwidth, accelerating the locking process and reducing the IBPN contributed by the PD. An oversampling ratio of M = 4 [see Figure 5(f)] is a balance between the direct sampling [M = 1 in Figure 5(c)]used in [26] and other conventional PLLs/ADPLLs and an excessively high M, which could lead to 1) variations in the oversampling PD gain  $(K_{ROS})$ across the reference waveform, with the gain peaking at zero crossings and dipping near peaks/troughs; 2) a reduced monotonic PD range; and 3) increased power consumption.

The 4× ROS-PD results in four locking points with a phase increment of  $2\pi/4$  in an integer-N operation. In a fractional-N mode, the sampled voltage tracks the entire extent of  $S_{\text{REF}}$ . Consequently, the next-stage quantizer would normally need to handle the full-scale ~1-V input range, necessitating an extremely high-resolution ADC to achieve a low IBPN. Such a high-resolution ADC would require significant power, especially at conversion speeds in the hundreds of megahertz.

To avoid the above issue, a bottom plate sampling circuit (similar to the

one used in the RS-PD) is now assisted by a voltage zero-forcing technique, as in Figure 8. This technique relaxes the required range by removing the dc offset, i.e.,  $\pm A\sin(\pi/4)$ , at each locking point by means of  $V_P$  and  $V_N$ . Additionally, a fine-resolution/small-range CDAC, placed at the top plate, can be programmed to further compensate for any fractional voltage residues. The net result is that the voltage on the top plate (right side) of  $C_S$  represents the ideally bias-free PHE, proportional to  $K_{ROS} \cdot \Delta \phi$ . Since

the required input range is much smaller, the requirements on subsequent circuits can be relaxed to achieve low noise while maintaining low power.

The operation of the ROS-PD, which is at the heart of the ROS-PLL in Figure 9(a), occurs in three distinct phases, as demonstrated in Figure 9(b). In the first phase,  $\phi_1$ , having a clock pulsewidth of 1.3 ns, presets node A to the expected  $S_{\text{REF}}$  of 0.85 V (i.e.,  $V_p$ ) and node B to a  $V_{\text{TH}}$  of 0.5 V. At the end of this presetting

phase, the voltage across the top and bottom plates of  $C_S$  is 0.35 V. In the second phase,  $\phi_2$ , a brief pulse of approximately 0.7 ns allows the bottom sampling (BS) circuit to track the incoming  $S_{REF}$ . This action charges the capacitance at node A, which primarily comprises the CDAC input. While the charge on  $C_S$  remains conserved, the voltage at node B tracks the  $S_{REF}$ trajectory with the previously established offset of 0.35 V. Simultaneously,  $A_1$  amplifies the voltage at node B with a gain of 15. The third phase,  $\phi_3$ , halts the input tracking to establish the sampling point. To adjust for a fractional-N operation, the DSP alters the CDAC code to modify the load capacitance at node A, allowing the voltage at nodes A and B to be programmed to eliminate any voltage residue. At the same time, the second-stage amplifier,  $A_2$ , drives the 6-b SAR-ADC and amplifies the sampled voltage from the input CDAC of the SAR-ADC. This phase is allocated a duration of 3 ns.

The showcased 4× ROS-ADPLL was realized in TSMC 28-nm LP CMOS. The

FIGURE 8: Reference waveform oversampling using bottom plate (over) sampling with zero forcing [26], [37], [38].

FIGURE 9: The ROS-PLL: the (a) top-level diagram, (b) timing diagram of the sampling process, (c) measured PN in integer-N and fractional-N operation at 2.2 GHz, and (d) measured transient locking.

oscillator accounts for the majority of the ADPLL's active area, occupying 0.16 mm<sup>2</sup> out of the total 0.24 mm<sup>2</sup>. Due to the large bandwidth provided by the 4× oversampling of  $f_{ref}$ , the PN requirement of the DCO is less stringent, allowing for power savings. Specifically, the DCO and its buffer consume only 380  $\mu$ W. The MMD and clock generation circuits use 200  $\mu$ W while operating at a  $CKV_{DIV}$  rate of 200 MHz. The ROS-PD, which includes bootstrapped switches, low-noise amplifiers  $A_1$ and  $A_2$ , CDAC buffers, and other passive switches, consumes  $300 \,\mu\text{W}$  at 200 MHz. Overall, the total power consumption of the ADPLL is just 1.15 mW. In an integer-N operation, this  $4\times$ ROS-ADPLL was tested with a 48-MHz reference frequency and FCW, of 48. Figure 9(c) presents the PN plot at 2.304 GHz. The IBPN is as low as -113 dBc/Hz, with an integrated RMS jitter of 379 fs over the 10 kHz to 30 MHz range. For a fractional-N operation, the

PN at a carrier frequency of 2.30475 GHz, with an FCW of 48.015625, is also shown in Figure 9(c). With optimal bandwidth settings, the integrated RMS jitter is 414 fs. With a power budget of ~1 mW, this results in one of the best FOMs for jitter, FOM<sub>jitter</sub>, of 247 dB among fractional-N ADPLLs consuming less than 5 mW. The wide monotonic PD range of this architecture eliminates the need for an FLL, which is typically required in SS-PLLs for locking robustness and fast settling. This is validated by the transient measurement results in Figure 9(d). Under a 1-MHz loop bandwidth, the ADPLL settles to a new frequency 24 MHz away within  $5 \mu s$ . Increasing the loop bandwidth to approximately 5 MHz reduces the settling time to 3  $\mu$ s for a 70-MHz frequency step. The measured relocking behavior aligns well with simulation results, demonstrating the robustness of the system. Consequently, this

architecture's inherent phase and frequency tracking can effectively counter various environmental perturbations, such as supply and temperature variations or interference from strong power amplifiers.

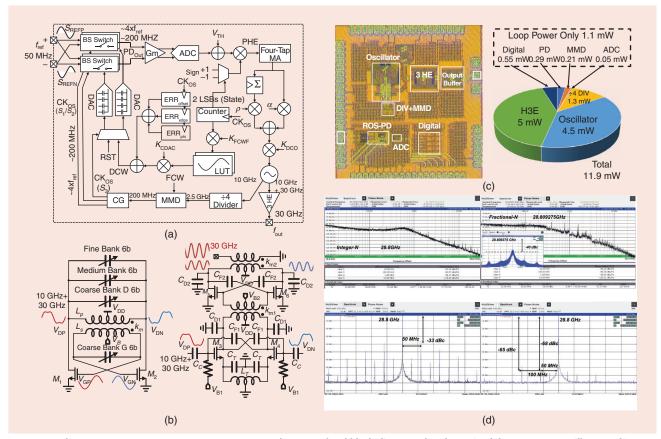

### mm-Wave ROS-PLL

The presented architecture has been adapted to support mm-wave frequencies, as described in Figure 10(a). The reference waveform ( $S_{REF}$ ) is likewise directly oversampled by the divided oscillator clock (the outputs of CG) using cross-coupled bottom plate sampling switches. A programmable PI controller functions as a loop filter and tunes the 30-GHz class  $F_{23}$ DCO with a third-harmonic extractor (H3E). The DCO provides a fundamental 10-GHz component to the ÷4 frequency divider, MMD, and CG, which produces the clocks for the ROS-PD and digital blocks. A schematic of the class  $F_{23}$  oscillator

FIGURE 10: The mm-wave ROS-ADPLL (mm-wave ROS-PLL): the (a) top-level block diagram, (b) schematic of the mm-wave oscillator and its harmonic extractor, (c) chip microphotograph and breakdown of the measured power consumption, and (d) measured PN and spectrum. MA: moving average; RST: resit; DCW: digital-control word.

is presented in Figure 10(b), which includes the H3E and a second-stage output buffer designed to drive a  $50-\Omega$  load [52], [53]. The source inductor  $L_T$  in the H3E is tuned to resonate at 10 GHz, effectively filtering out the fundamental harmonic current. The 10-GHz signal from the oscillator gate node is divided by two  $\div 2$  dividers to produce a 2.5-GHz signal with high reliability.

The mm-wave ROS-ADPLL is also implemented in 28-nm CMOS, covering an active area of 0.3 mm<sup>2</sup> and consuming just 11.9 mW, with 80% of this power allocated to the DCO and H3E [see Figure 10(c)]. The measured PN and spectral plots are given in Figure 10(d). With a 50-MHz reference input, the system achieves an RMS jitter of 199 fs in the integer-N mode and 237 fs in the fractional-N mode when synthesizing a 28.8-GHz carrier. By enabling the digital calibration loop, reference spurs and their harmonics can be reduced by 32 dB, bringing them down to -65 dBc [38]. In the fractional-*N* mode, the typical fractional spur is -40 dBc. The AD-PLL's wide PD range allows it to settle within 15  $\mu$ s after a 62-MHz frequency jump, demonstrating the robustness of the design. This system achieves exceptionally low jitter and power consumption for ADPLLs operating above 10 GHz, using a standard 50-MHz reference—the lowest among recent state-of-the-art PLLs/ ADPLLs. Without relying on high reference frequencies or additional cascading PLLs, this ADPLL delivers an FOM of -241.7 dB and a record FOM<sub>jitter-N</sub> [54] of -269.3 dB for mmwave ADPLLs.

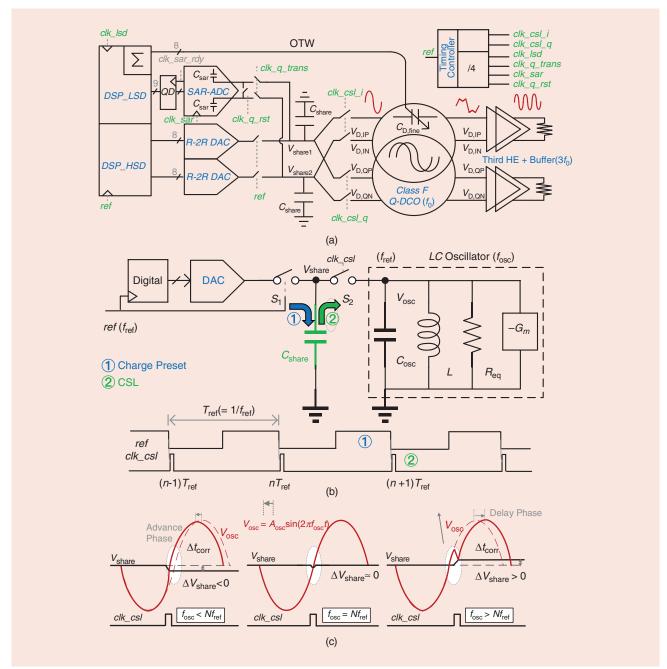

### **Charge-Sharing Locking PLLs**

An entirely different technique of exploiting a digitally friendly approach to simultaneously achieve ultralow jitter, low power consumption, and robustness is revealed in Figure 11(a). A new technique of charge-sharing locking (CSL) with an implicit digital frequency tracking loop (FTL) exploits a minimalistic SAR-ADC (0.1 mW). In contrast to the conven-

## As the carrier frequency or the symbol constellation density increases, the required RMS jitter becomes even more stringent.

tional subharmonic injection locking (IL), in which the switch is used to preset the oscillator waveform to the ac ground, a sharing capacitor  $C_{\text{share}}$ (1 pF) with a DAC-controlled preset voltage is employed for charge sharing with the resonant LC tank (realizing a phase-correcting proportional path), while the resulting charge residue on  $C_{\text{share}}$  (which mainly represents the frequency error after the charge sharing) is then sampled and processed by the digital FTL (including a SAR-ADC, an IIR filter, and an integrator) for frequency tracking (integral path). The CSL technique offers the following advantages: 1) thanks to the  $C_{\text{share}}$  recording of how much charge was used to correct the PHE caused by the frequency error and intrinsic DCO PN, the timingrace problem can be effectively mitigated; 2) the SAR-ADC-based digital FTL consumes ultralow power and occupies a tiny area; and 3) the fine switched-capacitor tuning bank in the DCO is used only for frequency tracking rather than phase correction in the ADPLL or digital SS-PLL, thus relieving the tough requirements on the resolution, usually requiring a high-speed DSM, and the linearity of the switched capacitor. The timing diagram is in Figure 11(b). First,  $C_{\rm share}$  is preset by the DAC (when the reference pulse is high and  $S_1$  is on). After that,  $S_1$  is off, and  $S_2$  is on. This results in a charge injection into the oscillator (when the clock signal-CSL is high). Figure 11(c) shows the effect of charge-sharing injection on the oscillator's phase when there is a frequency mismatch. The leftover

<sup>3</sup>Since traditional IL requires an ac ground (either single ended or differential) to inject the adjusting signal, it can natively support only an integer-*N* operation (unless assisted by an additional DTC). On the other hand, CSL can allow an injection at any point along the voltage waveform, and thus, it can inherently support the fractional-*N* operation.

charge on  $C_{\rm share}$  is fed back to the SAR-ADC to ensure that the intrinsic frequency of the oscillator ( $f_{\rm osc}$ ) is equal to  $N \times f_{\rm ref}$ . Thus, a robust locking operation can be ensured. The prototype in [55] achieves a low RMS jitter of 75 fs at 26.25 GHz, while the reference spur is –45 dBc at a 250-MHz offset. The total power consumption of the whole system is 16.5 mW.

Despite the low RMS jitter achieved, the realized prototype in [55] still requires manual calibration of the pulsewidth ( $\tau_{\text{pulse}}$ ), due to its sensitivity to PVT variations. A narrow pulse may reduce the injection time, leading to a lower bandwidth, while a wider pulse increases the time that the LC tank is loaded by  $C_{\rm shared}$ , complicating the performance optimization at mm-wave frequencies. To address these challenges, a ping-pong (PP) CSL technique was introduced in [56] and is illustrated in Figure 12(a). Instead of relying on the narrowest achievable  $\tau_{\text{pulse}}$ , this technique uses a 50% duty cycle reference clock  $(\phi_1)$  and its complement  $(\phi_2)$  in a ping-pong manner. During each clock phase, either  $C_{\rm shared}$  or  $C'_{\rm shared}$  connects to the LCtank, thereby minimizing loading variation. The extended duration of the charge-sharing operation, due to a longer  $\tau_{\text{pulse}}$ , improves the injection efficiency independent of the RC time constant of  $C_{\text{shared}}$ , resulting in a wider achievable bandwidth. The charge residues on the disconnected capacitor can be read out during  $\phi_1^s$  (or  $\phi_2^s$ ) to gather the oscillator state information. This information can then be used for the DCC and FTL. The PP operation inherently provides a 2× reference multiplication without the need for explicit multiplier circuitry operating directly at  $2 \times f_{REF}$ , thus reducing the IBPN of the PLL. Additionally, the common-mode

precharging DAC found in prior designs is replaced by simply connecting the complementary phases of the PP operation during  $\phi_1^R$  (or  $\phi_2^R$ ), which enables automatic commonmode acquisition. A detailed timing diagram and corresponding phase relationships are shown at the bottom of Figure 12(a).

Figure 12(b) presents a chip micrograph of this PLL fabricated in TSMC

28-nm HPC+ CMOS, with an active area of 0.21 mm<sup>2</sup>. The measured PN demonstrates a lower RMS jitter of 42 fs (integrated from 10 kHz to 30 MHz) using a 250-MHz reference. The measured spur is -60 dBc at an offset of  $f_{\rm ref}$  around the 27-GHz carrier, highlighting the effectiveness of the employed FTL and DCC calibration when compared to the spur level of -29 dBc without any calibration. The PLL con-

sumes only 14 mW, with 90% of this power allocated to the DCO and H3E. The low-noise reference path and calibration loop, including the FTL, consume only 1 and 1.2 mW, respectively. This results in an FOM $_{\rm litter}$  of -256.3 dB.

### **PLL Benchmark and Future Outlook**

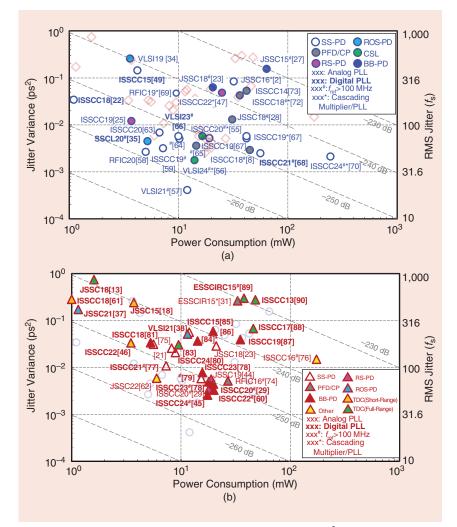

To fairly benchmark the performance of low-jitter PLLs, the work in [6] has proposed a PLL FOM defined

FIGURE 11: A charge-sharing locking (CSL) PLL [55]: the (a) top-level diagram, (b) timing diagram of the CSL operation, and (c) oscillator waveform after the CSL injection applied. LSD: low-speed digital; HSD: high-speed digital; HE: harmonic extractor.

as  $20(\log_{10}(\sigma_t/1s)) + 10(P_{dc}/1mW)$ , where  $\sigma_t$  and  $P_{dc}$  are the integrated PN or RMS jitter and power consumption, respectively. Figure 13(a) surveys the jitter variance versus the power consumption of integer-N PLL/ADPLLs. In the past two decades, various techniques have been proposed to push the PLL FOM performance. It can be observed that integer-N PLLs adopting the

SSPD with the higher slew rate of the PD input signal, either from the reference clock or oscillator feedback path, can achieve a high PD gain with low intrinsic noise, which leads to an exceptional FOM of below –250 dBc/Hz [57], [58], [59]. Alternatively, CSL PLLs also show competitive FOM performance due to the improved injection efficiency and low latency [55], [56]. Recently,

approaches using ROS techniques [34], [36], [37] have gained interest and offer plenty of room to push the FOM limit while maintaining the reference frequency below 100 MHz.

For fractional-*N* PLLs [see Figure 13(b)], it can be observed that most of the high-performance AD-PLLs adopt the DTC-assisted architecture with the BB-PD but with the reference above 200 MHz [33], [45]

FIGURE 12: A PP CSL-PLL (PP-CSL) [56]: the (a) top-level diagram and its clocking scheme and (b) chip photo and measured power breakdown.

FIGURE 13: PLL/ADPLL benchmarking in terms of the jitter variance  $(\sigma^2)$  versus the power consumption in (a) integer-N and (b) fractional-N operation. VLSI: Symposium on VLSI Technology and Circuits; *JSSC*: *IEEE Journal of Solid-State Circuits*; *ISSCC*: *IEEE International Solid-State Circuits* Conference; RFIC: *IEEE Symposium on Radio Frequency Integrated Circuits; SSC-L: IEEE Solid-State Circuits Letters*; ESSCIRC: European Conference on Solid-State Circuits.

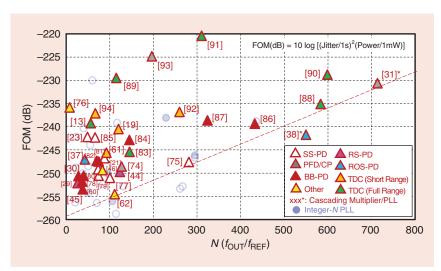

FIGURE 14: Fractional-N PLL/ADPLL benchmarking considering the FOM versus the  $N(f_{out}/f_{ref})$  ratio.

or use other short-range high-resolution TDCs [18], [46], [61]. Alternative methods using harmonic mixing phase locking can achieve excellent performance [62]. Figure 14 conveys the PLL FOM performance for different N ratios. It can be observed that, when the effect of the output frequency and reference frequency is taken into account, techniques using the reference multiplier [31] or oversampling PDs [38] together with the output frequency multiplier can break the trend line. From the above PLL surveys, it can be observed that there is still room to further push the PLL FOM while maintaining a low reference clock, i.e., lower than 100 MHz.

### References

- [1] A. Verma et al., "A 16-channel, 28/39GHz dual-polarized 5G FR2 phased-array TRX with a quad-stream IF TRX supporting non-contiguous carrier aggregation up to 1.6 GHz BW," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2022, pp. 1–3, doi: 10.1109/ISSCC42614.2022. 9731664.

- [2] T. Siriburanon et al., "A low-power low-noise mm-wave subsampling PLL using dual-step-mixing ILFD and tail-coupling quadrature injection-locked oscillator for IEEE 802.11ad," *IEEE J. Solid-State Circuits*, vol. 51, no. 5, pp. 1246–1260, May 2016, doi: 10.1109/JSSC.2016.2529004.

[3] Y. Hu et al., "A charge-sharing locking

- [3] Y. Hu et al., "A charge-sharing locking technique with a general phase noise theory of injection locking," *IEEE J. Solid-State Circuits*, vol. 57, no. 2, pp. 518–534, Feb. 2022, doi: 10.1109/JSSC.2021.3106237.

- [4] N. Markulic, P. T. Renukaswamy, E. Martens, B. van Liempd, P. Wambacq, and J. Craninckx, "A 5.5-GHz background-calibrated subsampling polar transmitter with –41.3-dB EVM at 1024 QAM in 28-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 54, no. 4, pp. 1059–1073, Apr. 2019, doi: 10.1109/JSSC.2018.2886324.

- [5] B. Razavi, "Jitter-power trade-offs in PLLs," *IEEE Trans. Circuits Syst. I, Reg. Pa*pers, vol. 68, no. 4, pp. 1381–1387, Apr. 2021, doi: 10.1109/TCSI.2021.3057580.

- [6] X. Gao, E. A. M. Klumperink, P. F. J. Geraedts, and B. Nauta, "Jitter analysis and a benchmarking figure-of-merit for phase-locked loops," *IEEE Trans. Circuits Syst., II, Exp. Briefs*, vol. 56, no. 2, pp. 117–121, Feb. 2009, doi: 10.1109/TCSII.2008.2010189.

- [7] W. Rhee, B.-S. Song, and A. Ali, "A 1.1-GHz CMOS fractional-N frequency synthesizer with a 3-b third-order ΔΣ modulator," *IEEE J. Solid-State Circuits*, vol. 35, no. 10, pp. 1453-1460, Oct. 2000, doi: 10.1109/4.871322.

- [8] D. Turker et al., "A 7.4-to-14GHz PLL with 54fs<sub>rms</sub> jitter in 16 nm FinFET for integrated RF-data-converter SoCs," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2018, pp. 378–380, doi: 10.1109/ISSCC.2018.8310342.

- [9] Y. Zhao, M. Forghani, and B. Razavi, "A 20-GHz PLL with 20.9-fs random jitter,"

- *IEEE J. Solid-State Circuits*, vol. 58, no. 6, pp. 1597–1609, Jun. 2023, doi: 10.1109/JSSC.2022.3225105.

- [10] V. Mazzaro and M. P. Kennedy, "Folded noise prediction in nonlinear fractional-N frequency synthesizers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 68, no. 10, pp. 4038–4048, Oct. 2021, doi: 10.1109/ TCSI.2021.3104275.

- [11] R. B. Staszewski, K. Waheed, F. Dulger, and O. E. Eliezer, "Spur-free multirate alldigital PLL for mobile phones in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 46, no. 12, pp. 2904–2919, Dec. 2011, doi: 10.1109/JSSC.2011.2162769.

- [12] C. Venerus and I. Galton, "A TDC-free mostly-digital FDC-PLL frequency synthesizer with a 2.8-3.5 GHz DCO," *IEEE J. Solid-State Circuits*, vol. 50, no. 2, pp. 450-463, Feb. 2015, doi: 10.1109/ JSSC.2014.2361523.

- [13] N. Pourmousavian, F.-W. Kuo, T. Siriburanon, M. Babaie, and R. B. Staszewski, "A 0.5-V 1.6-mW 2.4-GHz fractional-N all-digital PLL for bluetooth LE with PVT-insensitive TDC using switched-capacitor doubler in 28-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 53, no. 9, pp. 2572–2583, Sep. 2018, doi: 10.1109/JSSC.2018.2843337.

- [14] M. Lee and A. A. Abidi, "A 9 b, 1.25 ps resolution coarse-fine time-to-digital converter in 90 nm CMOS that amplifies a time residue," *IEEE J. Solid-State Circuits*, vol. 43, no. 4, pp. 769-777, Apr. 2008, doi: 10.1109/JSSC.2008.917405.

- [15] J. Yu, F. F. Dai, and R. C. Jaeger, "A 12-bit vernier ring time-to-digital converter in 0.13 μm CMOS technology," *IEEE J. Solid-State Circuits*, vol. 45, no. 4, pp. 830–842, Apr. 2010, doi: 10.1109/JSSC.2010.2040306.

- [16] D. Tasca, M. Zanuso, G. Marzin, S. Levantino, C. Samori, and A. L. Lacaita, "A 2.9-4.0-GHz fractional-N digital PLL with bang-bang phase detector and 560-fs<sub>rms</sub> integrated jitter at 4.5-mW power," *IEEE J. Solid-State Circuits*, vol. 46, no. 12, pp. 2745-2758, Dec. 2011, doi: 10.1109/ISSC.2011.2162917.

- [17] S. Levantino, G. Marzin, and C. Samori, "An adaptive pre-distortion technique to mitigate the DTC nonlinearity in digital PLLs," *IEEE J. Solid-State Circuits*, vol. 49, no. 8, pp. 1762–1772, Aug. 2014, doi: 10.1109/JSSC.2014.2314436.

- [18] A. Elkholy, T. Anand, W.-S. Choi, A. Elshazly, and P. K. Hanumolu, "A 3.7 mW lownoise wide-bandwidth 4.5 GHz digital fractional-N PLL using time amplifier-based TDC," *IEEE J. Solid-State Circuits*, vol. 50, no. 4, pp. 867–881, Apr. 2015, doi: 10.1109/JSSC.2014.2385753.

- [19] V. K. Chillara et al., "9.8 an 860μw 2.1-to-2.7 GHz all-digital PLL-based frequency modulator with a DTC-assisted snapshot TDC for WPAN (bluetooth smart and zigbee) applications," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2014, pp. 172– 173, doi: 10.1109/ISSCC.2014.6757387.

- [20] X. Gao, E. A. M. Klumperink, M. Bohsali, and B. Nauta, "A low noise sub-sampling PLL in which divider noise is eliminated and PD/CP noise is not multiplied by N<sup>2</sup>," *IEEE J. Solid-State Circuits*, vol. 44, no. 12, pp. 3253–3263, Dec. 2009, doi: 10.1109/JSSC.2009.2032723.

- [21] X. Gao et al., "9.6 A 2.7-to-4.3GHz, 0.16psrms-jitter, -246.8dB-FOM, digital fractional-N sampling PLL in 28nm CMOS," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2016, pp. 174-175, doi: 10.1109/ISSCC.2016.7417963.

- [22] A. Sharkia, S. Mirabbasi, and S. Shekhar, "A type-I sub-sampling PLL with a 100  $\times$  100  $\mu$ m<sup>2</sup> footprint and -255-dB FoM,"

- *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3553–3564, Dec. 2018, doi: 10.1109/JSSC.2018.2874013.

- [23] D. Liao, F. F. Dai, B. Nauta, and E. A. M. Klumperink, "A 2.4-GHz 16-phase subsampling fractional-N PLL with robust soft loop switching," *IEEE J. Solid-State Circuits*, vol. 53, no. 3, pp. 715–727, Mar. 2018, doi: 10.1109/JSSC.2018.2791486.

- [24] T. Siriburanon et al., "A 2.2 GHz –242 dB-FOM 4.2 mW ADC-PLL using digital sub-sampling architecture," *IEEE J. Solid-State Circuits*, vol. 51, no. 6, pp. 1385–1397, Jun. 2016, doi: 10.1109/JSSC.2016.2546304.

- [25] J. Sharma and H. Krishnaswamy, "A 2.4-GHz reference-sampling phase-locked loop that simultaneously achieves lownoise and low-spur performance," *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1407–1424, May 2019, doi: 10.1109/JSSC.2018.2889690.

- [26] J. Du, T. Siriburanon, Y. Hu, V. Govindaraj, and R. B. Staszewski, "A 2.02-2.87-GHz -249-dB FoM 1.1-mW digital PLL exploiting reference-sampling phase detector," *IEEE Solid-State Circuits Lett.*, vol. 3, pp. 158-161, Jul. 2020, doi: 10.1109/ LSSC.2020.3008298.

- [27] M. Hekmat, F. Aryanfar, J. Wei, V. Gadde, and R. Navid, "A 25 GHz fast-lock digital LC PLL with multiphase output using a magnetically-coupled loop of oscillators," *IEEE J. Solid-State Circuits*, vol. 50, no. 2, pp. 490–502, Feb. 2015, doi: 10.1109/JSSC.2014.2361351.

- [28] S. Ek et al., "A 28-nm FD-SOI 115-fs jitter PLL-based LO system for 24–30-GHz sliding-IF 5G transceivers," *IEEE J. Solid-State Circuits*, vol. 53, no. 7, pp. 1988–2000, Jul. 2018, doi: 10.1109/JSSC.2018.2820149.

[29] M. Mercandelli et al., "17.5 A 12.5 GHz

- [29] M. Mercandelli et al., "17.5 A 12.5 GHz fractional-N type-I sampling PLL achieving 58fs integrated jitter," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2020, pp. 274-276, doi: 10.1109/ISS-CC19947.2020.9063135.

- [30] A. Santiccioli et al., "A 66-fs-rms jitter 12.8-to-15.2-GHz fractional-N bang-bang PLL with digital frequency-error recovery for fast locking," *IEEE J. Solid-State Circuits*, vol. 55, no. 12, pp. 3349–3361, Dec. 2020, doi: 10.1109/JSSC.2020.3019344.

- [31] T. Siriburanon et al., "A 28-GHz fractional-N frequency synthesizer with reference and frequency doublers for 5G cellular," in *Proc. ESSCIRC Conf. 41st Eur. Solid-State Circuits Conf. (ESSCIRC*), 2015, pp. 76–79, doi: 10.1109/ESSCIRC.2015.7313832.

- [32] K. M. Megawer, A. Elkholy, M. Gamal Ahmed, A. Elmallah, and P. Kumar Hanumolu, "Design of crystal-oscillator frequency quadrupler for low-jitter clock multipliers," *IEEE J. Solid-State Circuits*, vol. 54, no. 1, pp. 65–74, Jan. 2019, doi: 10.1109/JSSC.2018.2872539.

- [33] H. Kim, H.-S. Oh, W. Jung, Y. Song, J. Oh, and D.-K. Jeong, "A 100 MHz-reference, 8 GHz/16 GHz, 177fs<sub>rms</sub>/223fs<sub>rms</sub> RO-based IL-ADPLL incorporating reference octupler with probability-based fast phase-error calibration," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2022, pp. 1–3, doi: 10.1109/ISSCC42614.2022.9731714.

- [34] J.-H. Seol, D. Sylvester, D. Blaauw, and T. Jang, "A reference oversampling digital phase-locked loop with -240 dB FOM and -80 dBc reference spur," in *Proc. Symp. VLSI Circuits*, 2019, pp. C160-C161, doi: 10.23919/VLSIC.2019.8778010.

- [35] J.-H. Seol, K. Choo, D. Blaauw, D. Sylvester, and T. Jang, "A 67-fs<sub>rms</sub> jitter, -130 dBc/Hz in-band phase noise, -256-dB FoM reference oversampling digital PLL with proportional path timing control," *IEEE Solid*-

- State Circuits Letters, vol. 3, pp. 430–433, 2020, doi: 10.1109/LSSC.2020.3025142.

- [36] J. Qiu et al., "A 32-kHz-reference 2.4-GHz fractional-N oversampling PLL with 200-kHz loop bandwidth," *IEEE J. Solid-State Circuits*, vol. 56, no. 12, pp. 3741–3755, Dec. 2021, doi: 10.1109/JSSC.2021.3106514.

- [37] J. Du, T. Siriburanon, Y. Hu, V. Govindaraj, and R. B. Staszewski, "A reference-waveform oversampling technique in a fractional-NADPLL," *IEEE J. Solid-State Circuits*, vol. 56, no. 11, pp. 3445–3457, Nov. 2021, doi: 10.1109/JSSC.2021.3101046.

- [38] J. Du et al., "A 24-31 GHz reference oversampling ADPLL achieving FoMjitter-N of -269.3dB," in *Proc. Symp. VLSI Circuits* (VLSI-Circuits), 2021, pp. 1-2.

- [39] R. B. Staszewski and P. Balsara, All-Digital Frequency Synthesizer in Deep-Submicron CMOS. Hoboken, NJ, USA: John Wiley & Sons, Inc., 2006.

- [40] T. Tokairin, M. Okada, M. Kitsunezuka, T. Maeda, and M. Fukaishi, "A 2.1-to-2.8-GHz low-phase-noise all-digital frequency synthesizer with a time-windowed time-to-digital converter," *IEEE J. Solid-State Circuits*, vol. 45, no. 12, pp. 2582–2590, Dec. 2010, doi: 10.1109/JSSC.2010.2076591.

- [41] R. Staszewski and P. Balsara, "Phase-domain all-digital phase-locked loop," *IEEE Trans. Circuits Syst., II, Exp. Briefs*, vol. 52, no. 3, pp. 159–163, Mar. 2005, doi: 10.1109/TCSII.2004.842067.

- [42] T.-H. Tsai, R.-B. Sheen, S.-Y. Hsu, C.-H. Chang, and R. B. Staszewski, "A 55.9-fs integrated jitter (100 kHz-100 MHz) hybrid LC-tank PLL in 5-nm FinFET using programmable phase realignment and dynamic coarse tuning," *IEEE Solid-State Circuits Letters*, vol. 4, pp. 230-233, 2021, doi: 10.1109/LSSC.2021.3130575.

- [43] P. Chen, F. Zhang, Z. Zong, S. Hu, T. Siriburanon, and R. B. Staszewski, "A 31-µW, 148-fs step, 9-bit capacitor-DAC-based constant-slope digital-to-time converter in 28-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 54, no. 11, pp. 3075–3085, Nov. 2019, doi: 10.1109/JSSC.2019.2939663.

- [44] W. Wu et al., "A 28-nm 75-fs<sub>rms</sub> analog fractional-N sampling PLL with a highly linear DTC incorporating background DTC gain calibration and reference clock duty cycle correction," *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1254–1265, May 2019, doi: 10.1109/JSSC.2019.2899726.

[45] M. Rossoni et al., "10.1 an 8.75 GHz

- [45] M. Rossoni et al., "10.1 an 8.75 GHz fractional-N digital PLL with a reverse-concavity variable-slope DTC achieving 57.3fs<sub>rms</sub> integrated jitter and -252.4 dB FoM," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2024, pp. 188-190, doi: 10.1109/ISSCC49657.2024.10454388.

- [46] Z. Gao et al., "A 2.6-to-4.1 GHz fractional-N digital PLL based on a time-mode arithmetic unit achieving –249.4 dB FoM and –59 dBc fractional spurs," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2022, pp. 380–382, doi: 10.1109/iss-cc42614.2022.9731561.

- [47] T.-H. Tsai, R.-B. Sheen, S.-Y. Hsu, Y.-T. Chang, C.-H. Chang, and R. B. Staszewski, "A cascaded PLL (LC-PLL + RO-PLL) with a programmable double realignment achieving 204fs integrated jitter (100 kHz to 100 MHz) and -72 dB reference spur," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2022, pp. 1-3, doi: 10.1109/ISS-CC42614.2022.9731676.

- [48] J. Qiu et al., "A 32 kHz-reference 2.4 GHz fractional-N nonuniform oversampling PLL with gain-boosted PD and loop-gain calibration," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2023, pp. 80–82, doi: 10.1109/ISSCC42615.2023.10067516.

- [49] T. Siriburanon et al., "25.2 A 2.2 GHz -242 dB-FOM 4.2 mW ADC-PLL using digital sub-sampling architecture," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2015, pp. 1–3, doi: 10.1109/ISSCC.2015.7063115.

- [50] J. Du et al., "A millimeter-wave ADPLL with reference oversampling and thirdharmonic extraction featuring high FoMjitter-N," IEEE Solid-State Circuits Lett., vol. 4, pp. 214–217, 2021, doi: 10.1109/ LSSC.2021.3124130.

- [51] A. T. Ramkaj, M. Strackx, M. S. J. Steyaert, and F. Tavernier, "A 1.25-GS/s 7-b SAR ADC with 36.4-dB SNDR at 5 GHz using switch-bootstrapping, USPC DAC and triple-tail comparator in 28-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 53, no. 7, pp. 1889–1901, Jul. 2018, doi: 10.1109/ISSC.2018.2822823.

- [52] Y. Hu, T. Siriburanon, and R. B. Staszewski, "A low-flicker-noise 30-GHz class-F23 oscillator in 28-nm CMOS using implicit resonance and explicit common-mode return path," *IEEE J. Solid-State Circuits*, vol. 53, no. 7, pp. 1977-1987, Jul. 2018, doi: 10.1109/JSSC.2018.2818681.

- [53] X. Chen, Y. Hu, T. Siriburanon, J. Du, R. B. Staszewski, and A. Zhu, "A 30-GHz class-F quadrature DCO using phase shifts between drain-gate-source for low flicker phase noise and I/Q exactness," *IEEE J. Solid-State Circuits*, vol. 58, no. 7, pp. 1945–1958, Jul. 2023, doi: 10.1109/ISSC.2023.3237788.

- JSSC.2023.3237788.

[54]"," H. Zhang et al., "0.2 mW 70 fs<sub>rms</sub>-jitter injection-locked PLL using de-sensitized SSPD-based injecting-time self-alignment achieving –270 dB FoM and –66 dBc reference spur," in *Proc. Symp. VLSI Circuits*, 2019, pp. C38–c39, doi: 10.23919/VL-SIC.2019.8778059.

- [55] Y. Hu et al., "17.6 A 21.7-to-26.5 GHz charge-sharing locking quadrature PLL with implicit digital frequency-tracking loop achieving 75fs jitter and -250 dB FoM," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2020, pp. 276-278, doi: 10.1109/ISSCC19947.2020.9063024.

- [56] S. Kumar, P. Sawakewang, T. Siriburanon, and R. B. Staszewski, "A 25.4-27.5 GHz ping-pong charge-sharing locking PLL achieving 42 fs jitter with implicit reference frequency doubling," in Proc. IEEE Symp. VLSI Technol. Circuits (VLSI Technol. Circuits), 2024, pp. 1-2, doi: 10.1109/VLSITechnologyandCir46783. 2024.10631558.

- [57] Y. Zhao and B. Razavi, "A 19-GHz PLL with 20.3-fs jitter," in *Proc. Symp. VLSI Circuits*, 2021, pp. 1–2, doi: 10.23919/VLSICircuits52068.2021.9492419.

- [58] J. Gong, F. Sebastiano, E. Charbon, and M. Babaie, "A 10-to-12 GHz 5 mW chargesampling PLL achieving 50 fsec RMS jitter, -258.9 dB FOM and -65 dBc reference spur," in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), 2020, pp. 15-18, doi: 10.1109/RFIC49505.2020.9218380.

- [59] Z. Zhang, G. Zhu, and C. P. Yue, "30.8 A 0.65V 12-to-16 GHz sub-sampling PLL with 56.4fs<sub>rms</sub> integrated jitter and -256.4 dB FoM," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2019, pp. 488-490, doi: 10.1109/JSSC.2020.2967562.

[60] S. M. Dartizio et al., "A 68.6fs<sub>rms</sub>-total-

- [60] S. M. Dartizio et al., "A 68.6fs<sub>rms</sub>-total-integrated-jitter and 1.56 μs-locking-time fractional-N bang-bang PLL based on type-II gear shifting and adaptive frequency switching," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2022, pp. 1–3, doi: 10.1109/ISSCC42614.2022.9731683.

- [61] H. Liu et al., "A 0.98 mW fractional-N AD-PLL using 10b isolated constant-slope DTC with FOM of –246dB for IoT applications in

- 65nm CMOS," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2018, pp. 246–248, doi: 10.1109/ISSCC.2018.8310276.

- [62] D. Yang et al., "A harmonic-mixing PLL architecture for millimeter-wave application," *IEEE J. Solid-State Circuits*, vol. 57, no. 12, pp. 3552–3566, Dec. 2022, doi: 10.1109/JSSC.2022.3209614.

- [63] Y. Lim et al., "17.8 A 170 MHz-lock-in-range and –253 dB-FoMjitter 12-to-14.5 GHz subsampling PLL with a 150 μW frequencydisturbance-correcting loop using a lowpower unevenly spaced edge generator," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2020, pp. 280–282, doi: 10.1109/ ISSCC19947.2020.9062921.

- [64] Z. Yang, Y. Chen, S. Yang, P. Mak, and R. P. Martins, "16.8 A 25.4-to-29.5 GHz 10.2 mW isolated sub-sampling PLL achieving –252.9 dB jitter-power FoM and –63dBc reference spur," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2019, pp. 270–272, doi: 10.1109/ISSCC.2019.8662364.

- [65] X. Geng, Y. Tian, Y. Xiao, Z. Ye, Q. Xie, and Z. Wang, "A 25.8 GHz integer-N PLL with time-amplifying phase-frequency detector achieving 60fs<sub>rms</sub> jitter, -252.8 dB FoMJ, and robust lock acquisition performance," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2022, pp. 388-390, doi: 10.1109/ISSCC42614.2022.9731578.

- [66] W. Tao, W. Zhao, R. B. Staszewski, F. Lin, and Y. Hu, "An 18.8-to-23.3 GHz ADPLL based on charge-steering-sampling technique achieving 75.9 fs RMS jitter and -252 dB FoM," in Proc. IEEE Symp. VLSI Technol. Circuits (VLSI Technol. Circuits), 2023, pp. 1-2, doi: 10.23919/VLSITechnologyandCir57934.2023.10185415.

- [67] J. Kim et al., "16.2 A 76fs<sub>rms</sub> jitter and -40 dBc integrated-phase-noise 28-to-31 GHz frequency synthesizer based on digital sub-sampling PLL using optimally spaced voltage comparators and background loop-gain optimization," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2019, pp. 258–260, doi: 10.1109/ ISSCC.2019.8662532.

- [68] E. Thaller et al., "32.6 A K-Band 12.1-to-16.6 GHz subsampling ADPLL with 47.3fs<sub>rms</sub> jitter based on a stochastic flash TDC and coupled dual-core DCO in 16 nm FinFET CMOS," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2021, pp. 451–453, doi: 10.1109/ISSCC42613.2021.9365775.

- [69] H. Wang and O. Momeni, "A 9.6 mW lownoise millimeter-wave sub-sampling PLL with a divider-less sub-sampling lock detector in 65 nm CMOS," in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), 2019, pp. 171–174, doi: 10.1109/RFIC.2019.8701766.

- [70] B.-T. Moon, H.-C. Park, and S.-G. Lee, "10.8 A 281 GHz, -1.5 dBm output-power CMOS signal source adopting a 46fs<sub>rms</sub> jitter D-band cascaded subharmonically injection-locked sub-sampling PLL with a 274 MHz reference," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2024, pp. 202-204, doi: 10.1109/ISS-CC49657.2024.10454484.

- [71] D. Liao, Y. Zhang, F. F. Dai, Z. Chen, and Y. Wang, "An mm-wave synthesizer with robust locking reference-sampling PLL and wide-range injection-locked VCO," *IEEE J. Solid-State Circuits*, vol. 55, no. 3, pp. 536–546, Mar. 2020, doi: 10.1109/ JSSC.2019.2959513.

- [72] H. Yoon et al., "A -31dBc integrated-phase-noise 29 GHz fractional-N frequency synthesizer supporting multiple frequency bands for backward-compatible 5G using a frequency doubler and injection-locked frequency multipliers," in Proc. IEEE Int. Solid-State Circuits Conf.

- (ISSCC), 2018, pp. 366–368, doi: 10.1109/ISSCC.2018.8310336.

- [73] V. Szortyka, Q. Shi, K. Raczkowski, B. Parvais, M. Kuijk, and P. Wambacq, "21.4 A 42 mW 230fs-jitter sub-sampling 60 GHz PLL in 40nm CMOS," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2014, pp. 366–367, doi: 10.1109/ISS-CC.2014.6757472.

- [74] W. El-Halwagy, A. Nag, P. Hisayasu, F. Aryanfar, P. Mousavi, and M. Hossain, "A 28 GHz quadrature fractional-N synthesizer for 5G mobile communication with less than 100fs jitter in 65 nm CMOS," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, 2016, pp. 118–121, doi: 10.1109/RFIC.2016.7508265.

[75] N. Markulic et al., "9.7 a self-calibrated

- [75] N. Markulic et al., "9.7 a self-calibrated 10Mb/s phase modulator with -37.4 db EVM based on a 10.1-to-12.4 Ghz, -246.6 dB-FOM, fractional-N subsampling PLL," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2016, pp. 176-177, doi: 10.1109/ISSCC.2016.7417964.

- [76] A. Agrawal and A. Natarajan, "2.2 a scalable 28 GHz coupled-PLL in 65 nm CMOS with single-wire synchronization for large-scale 5G mm-wave arrays," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2016, pp. 38–39, doi: 10.1109/ISSCC.2016.7417895.

- [77] J. Kim et al., "32.4 a 104fs<sub>rms</sub>-jitter and -61dBc-fractional spur 15 GHz fractional-N subsampling PLL using a voltagedomain quantization-error cancelation technique," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2021, pp. 448–450, doi: 10.1109/ISSCC42613.2021.9365815

- doi: 10.1109/ISSCC42613.2021.9365815.

[78] G. Castoro et al., "4.5 A 9.25 GHz digital PLL with fractional-spur cancellation based on a multi-DTC topology," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2023, pp. 82-84, doi: 10.1109/ISSCC42615.2023.10067351.

- [79] Y. Shin, J. Lee, J. Kim, Y. Jo, and J. Choi, "10.5 A 76 fs<sub>rms</sub> jitter and -65 dBc-fractional-spur fractional-N sampling PLL using a nonlinearity-replication technique," in *Proc. IEEE Int. Solid-State Circuits Conf.* (ISSCC), 2024, pp. 196-198, doi: 10.1109/ ISSCC49657.2024.10454557.

- [80] S. Jang, M. Chae, H. Park, C. Hwang, and J. Choi, "10.2 A 5.5 μs-calibration-time, low-jitter, and compact-area fractional-N digital PLL using the recursive-leastsquares (RLS) algorithm," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2024, pp. 190–192, doi: 10.1109/ISS-CC49657.2024.10454495.

- [81] L. Bertulessi, L. Grimaldi, D. Cherniak, C. Samori, and S. Levantino, "A lowphase-noise digital bang-bang PLL with fast lock over a wide lock range," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2018, pp. 252–254, doi: 10.1109/ ISSCC.2018.8310279.

- [82] D. Xu et al., "10.3 A 7 GHz digital PLL with cascaded fractional divider and pseudodifferential DTC achieving -62.1 dBc fractional spur and 143.7 fs integrated jitter," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2024, pp. 192-194, doi: 10.1109/ ISSCC49657.2024.10454284.

- [83] X. Gao et al., "9.4 A 28 nm CMOS digital fractional-N PLL with -245.5 dB FOM and a frequency tripler for 802.11abgn/ac radio," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2015, pp. 1-3, doi: 10.1109/ ISSCC.2015.7062978.

- [84] D. Xu et al., "A 6.5-to-8 GHz cascaded dual-fractional-N digital PLL achieving -63.7 dBc fractional spurs with 50 MHz reference," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, 2023, pp. 1-2, doi: 10.1109/CICC57935.2023.10121180.

- [85] Z.-Z. Chen et al., "14.9 sub-sampling all-digital fractional-N frequency synthesizer with -111dBc/Hz in-band phase noise and an FOM of -242 dB," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2015, pp. 1-3, doi: 10.1109/ISSCC.2015.7063029.

- [86] D. Cherniak, L. Grimaldi, L. Bertulessi, R. Nonis, C. Samori, and S. Levantino, "A 23-GHz low-phase-noise digital bang-bang PLL for fast triangular and sawtooth chirp modulation," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3565–3575, Dec. 2018, doi: 10.1109/JSSC.2018.2869097.

- [87] L. Grimaldi et al., "16.7 A 30 GHz digital sub-sampling fractional-N PLL with 198fs<sub>rms</sub> jitter in 65 nm LP CMOS," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2019, pp. 268–270, doi: 10.1109/ISSCC.2019.8662411.

- [88] A. Hussein, S. Vasadi, M. Soliman, and J. Paramesh, "19.3 A 50-to-66 GHz 65 nm CMOS all-digital fractional-N PLL with 220fs<sub>rms</sub> jitter," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2017, pp. 326–327, doi: 10.1109/ISSCC.2017.7870393.

- [89] M. B. Dayanik, N. Collins, and M. P. Flynn, "A 28.5-33.5 GHz fractional-N PLL using a 3rd order noise shaping time-to-digital converter with 176fs resolution," in Proc. ESSCIRC Conf. 41st Eur. Solid-State Circuits Conf. (ESSCIRC), 2015, pp. 376-379, doi: 10.1109/ESSCIRC.2015.7313906.

- [90] W. Wu, X. Bai, R. B. Staszewski, and J. R. Long, "A 56.4-to-63.4 GHz spurious-free all-digital fractional-N PLL in 65nm CMOS," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2013, pp. 352–353, doi: 10.1109/ISSCC.2013.6487766.

- [91] D. Weyer, M. B. Dayanik, S. Jang, and M. P. Flynn, "A 36.3-to-38.2 GHz -216 dBc/Hz2 40 nm CMOS fractional-N FMCW chirp synthesizer PLL with a continuous-time bandpass delta-sigma time-to-digital converter," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2018, pp. 250-252, doi: 10.1109/ISSCC.2018.8310278.

- [92] H. Liu et al., "16.1 a 265 µW fractional-N digital PLL with seamless automatic switching subsampling/sampling feedback path and duty-cycled frequency-locked loop in 65nm CMOS," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), 2019, pp. 256–258, doi: 10.1109/ISSCC.2019.8662374.

- [93] M. Ferriss, B. Sadhu, A. Rylyakov, H. Ainspan, and D. Friedman, "10.9 A 13.1-to-28 GHz fractional-N PLL in 32 nm SOI CMOS with a  $\Delta\Sigma$  noise-cancellation scheme," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2015, pp. 1–3, doi: 10.1109/ISSCC.2015.7062991.

### **About the Authors**

**Teerachot Siriburanon** (teerachot. siriburanon@ucd.ie) received his B.E. degree in telecommunications engineering from the Sirindhorn International Institute of Technology, Thammasat University, Pathumthani, Thailand, in 2010 and his M.E. and Ph.D. degrees in physical electronics from the Tokyo Institute of Tech-

nology, Tokyo, Japan, in 2012 and 2016, respectively. In 2016, he joined University College Dublin (UCD), Dublin D04, Ireland, as a postdoctoral researcher through the Marie Skłodowska-Curie Individual Fellowship Program. Since 2019, he has been an assistant professor with UCD. His research interests include CMOS wireless transceiver systems and clock/frequency generations for wireless and wireline communications. He was a recipient of the Japanese Government (MEXT) Scholarship, the Thailand-Japan Microwave Young Researcher Best Presentation Award in 2013, the Asia and South Pacific Design Automation Conference Best Design Award in 2014 and 2015, the IEEE Solid-State Circuits Society (SSCS) Student Travel Grant Award in 2014, the SSCS Predoctoral Achievement Award in 2016, the Tejima Research Award in 2016, and the Science Foundation Ireland Frontiers for the Future Award in 2021. He is a member of the technical program committee of the IEEE Radio Frequency Integrated Circuits Symposium. He has been a guest editor of IEEE Transactions on Circuits and Systems I (TCAS-I) in 2019-2020, an associate editor of TCAS-I in 2023, and an associate editor of IEEE Access since 2020. He is an active reviewer for various IEEE journals. He was recognized as one of the best TCAS-I reviewers of 2022, and he received one of the inaugural SSCS best reviewer awards in 2023. He is a Senior Member of IEEE.

Robert Bogdan Staszewski (robert. staszewski@ucd.ie) was born in Białystok, Poland. He received his B.Sc. (summa cum laude), M.Sc., and Ph.D. degrees in electrical engineering from the University of Texas at Dallas, Richardson, TX, USA, in 1991, 1992, and 2002, respectively. From 1991 to 1995, he was with Alcatel Network Systems, Richardson, in-

volved in SONET cross-connect systems for fiber-optic communications. He joined Texas Instruments, Dallas, in 1995, where he was elected a distinguished member of the technical staff (a recognition limited to 2% of the technical staff). From 1995 to 1999, he was engaged in advanced CMOS read channel development for hard disk drives. In 1999, he cofounded the Digital RF Processor (DRP) group within Texas Instruments, with a mission to invent new digitally intensive approaches to traditional RF functions for integrated radios in deeply scaled CMOS technology. He was appointed as a chief technology officer of the DRP group from 2007 to 2009. In 2009, he joined the Delft University of Technology, Delft, The Netherlands, where he holds a guest appointment of full professor (Antoni van Leeuwenhoek full professor). Since 2014, he has been a full professor with University College Dublin (UCD), Dublin D04, Ireland. He is also a cofounder of a start-up company, Equal1 Labs, with design centers located in Silicon Valley and Dublin, aiming to produce singlechip CMOS quantum computers. He has authored or coauthored seven books, eight book chapters, and 160 journal and 220 conference publications, and he holds 220 issued U.S. patents. His research interests include nanoscale CMOS architectures and circuits for frequency synthesizers, transmitters, and receivers as well as quantum computers. He was a technical program committee chair of the 2019 European Solid-State Electronics Research Conference, in Kraków, Poland. He also serves on the technical program committee of the Symposium on VLSI Technology and Circuits. He was a recipient of the 2012 IEEE Circuits and Systems Industrial Pioneer Award. He is a Fellow of IEEE.

SSC