# Design of Balancing Converter for Bipolar DC Grids Using Series Connected MOSFET Switches Pooja Sinha

# Design of Balancing Converter for Bipolar DC Grids Using Series Connected MOSFET Switches

by

# Pooja Sinha

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Friday December 16, 2022 at 09:00 AM.

Student number: 5351448

Project duration: January, 2022 – December, 2022

Thesis committee: Dr. Ir. Zian Qin , TU Delft (Supervisor)

Prof. Dr. Ir. Pavol Bauer, TU Delft

Dr. Ir. Rudi Santbergen, TU Delft

Ir. Sachin Yadav, TU Delft

An electronic version of this thesis is available at http://repository.tudelft.nl/.

# Acknowledgement

As I write this, I am filled with bittersweet emotions with the realisation that the MSc journey is finally coming to an end. The past 2 years at TU Delft have been life-changing for me in more ways than I can imagine. I was tested to the limit of my resilience, and the fact that I am still standing strong here at the cusp of this long challenging voyage is only going to make my resolve to learn and explore even stronger. It would not have been possible to complete this journey without the love and support of the people around me and I would like to express my gratitude to all of you with the words of Albert Schweitzer.

#### Each of us has cause to think with deep gratitude of those who have lighted the flame within us

First and foremost, I would like to thank the faculty and staff members at EEMCS and DCE&S for giving me the opportunity to explore the field of power electronics in the most welcoming and warm environment of the EWI building. I could only access the department in my  $2^{nd}$  year due to COVID restrictions, however for the past 1 year  $10^{th}$  floor of the EWI building was like a  $2^{nd}$  home to me and I will always look back at the time spent here with utmost happiness and joy.

I would like to thank Dr. Zian Qin for being my supervisor for this thesis and guiding me through the journey. I am also thankful to Dr. Pavol Bauer for agreeing to be my thesis chair and especially for being supportive when I needed it the most. I would also like to thank Dr. Rudi Santbergen for agreeing to be on my committee and taking the time to go through my work.

It would have been impossible to finish my work had it not been for the constant support and guidance of my PhD supervisor Sachin Yadav. Anything I say about the impact you have had on my thesis and the quality of knowledge I will take away from my work will be an understatement. It is because of your knowledge, guidance, and patience that enabled me to complete this work. Thanks for being an amazing mentor and a guide and having faith in me even at moments I lacked belief.

I would like to use this opportunity to thank my academic counselor, Paula Leenders Bresser for all your help and support. You held my hand and guided me to the right path when all seemed lost to me and showed me the right path amidst all the chaos I was in. I also want to thank Mijntje Boon for listening to my issues patiently and guiding me to see the light when all seemed lost.

I also want to thank Dr. Domenico Lahaye for your support and guidance. You reached out to me, listened to my problems, and continued to guide me by going out of your way. I will always be thankful for your support. I also want to thank all my friends and seniors at TU Delft; you all made my stay at Delft a lot more enjoyable.

I would like to thank my parents and my sisters for all their love and support throughout. Finally, I would like to thank Kunal- my partner in the master's journey, and my partner in life. You are my biggest blessing. Words fall short when I think of writing anything about you. To wrap it in a sentence- "Tu hai toh I'll be alright".

Pooja Sinha Delft, December 2022

# **Abstract**

Global electricity usage has been increasing exponentially over the last 40 years and with the current pace of population and economic growth, the same trend will continue in the coming years. However, the current electricity generation is predominantly fossil fuels based, which makes the overall process unsustainable and polluting, and is contributing directly to the menace of global warming. The need of the hour is to transition to renewable and sustainable sources of electricity generation such as solar, wind, etc.

However, the major bottleneck in the large-scale implementation of renewable energy sources (RESs) is the intermittent availability and their integration into existing AC grids as the RESs are predominantly DC sources. In order to tackle the issue of intermittency various energy storage solutions are being developed. Further, as a solution to the issue of integrating RESs into the current electricity distribution system, DC distribution grids are being developed.

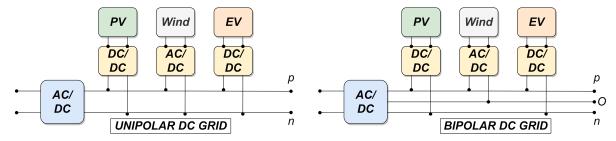

The DC distribution architecture is of two types, Unipolar and Bipolar distribution systems characterized by the number of wires used for power transmission; 2 wires for unipolar and 3 wires for Bipolar. Out of the two, Bipolar systems have inherent advantages of flexibility, stability, and efficiency over unipolar systems.

Current thesis focuses on series connected switch configuration of voltage balancing converter for bipolar DC power distribution systems.

For this thesis, various topologies of voltage balancers for bipolar dc distribution systems were studied and a buck-boost based series connected switch voltage balancer topology was chosen for the final design. For this topology, using MATLAB, the parameterization and optimization of magnetic components of the converter were performed. The optimized configuration was then modeled and simulated using LTSpice.

Post this, a comparison between different methods adopted to account for the unbalanced voltage sharing across the series connected switch configuration of the balancing converter owing to the non-linearities present in the circuit was done. Based on this study, the most prominent of the methods is then integrated into the LTSpice model.

# Contents

| PI | relace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •                                                                                   |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Ak | bstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | iii                                                                                 |

| No | omenclature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | xiii                                                                                |

| 1  | Introduction  1.1 Electricity: Need for sustainability  1.2 Issues with the Renewable sources of Energy  1.3 Mitigation of bottlenecks  1.4 DC Distribution Architecture  1.5 Research Objectives  1.6 Research Questions  1.7 Structure of the thesis                                                                                                                                                                                                                                                                                                                                                    | 1<br>1<br>2<br>3<br>4<br>6<br>6                                                     |

| 2  | Background  2.1 Bipolar DC Distribution System  2.2 Bipolar DC Grids: Challenges 2.2.1 Voltage Imbalance: Bipolar DC Grid  2.3 Voltage Balancer:  2.4 Existing topologies 2.4.1 Buck-Boost Topology 2.4.2 Dual-Buck Half Bridge Voltage Balancer Topology: 2.4.3 Super SEPIC type Voltage Balancer Topology 2.4.4 Super-ZETA Voltage Balancer Topology: 2.4.5 Cuk Type Voltage Balancer Topology: 2.4.6 Three-level converter Topology: 2.5.1 SiC MOSFET 2.5.2 Operation of synchronous buck-boost converter 2.5.3 Losses in synchronous buck-boost converter 2.6 Series Connected Switches  2.7 Summary: | 8<br>9<br>9<br>10<br>11<br>11<br>12<br>13<br>14<br>15<br>15<br>17<br>17<br>19<br>20 |

| 3  | Design and Optimisation 3.1 MOSFET Selection: 3.1.1 MOSFET selection parameters: 3.1.2 Single switch vs Series connected switch configuration: 3.1.3 MOSFET Loss Calculation: 3.2 Inductor design: Parameterisation and Optimisation of magnetic circuit 3.2.1 Core Material Selection: 3.2.2 Core Selection: 3.3 Magnetic design results: 3.3.1 Converter loss calculation:                                                                                                                                                                                                                              | 21<br>21<br>22<br>22<br>24<br>24<br>25<br>32                                        |

| 4  | LTSpice Simulation:  4.1 Series Connected Voltage Balancer:  4.2 Voltage Balancer without non-linearity:  4.3 Series Connected Voltage Balancer with Non-Linearity  4.3.1 $R_{on}$ = 2.5 $\Omega$ with $\pm$ 5% tolerance  4.3.2 Parasitic Capacitance: 20pF  4.3.3 Parasitic Capacitance: 100pF                                                                                                                                                                                                                                                                                                          | 37<br>38<br>41<br>41<br>44<br>47                                                    |

Contents

|    |                         | 4.3.4                                                                                     | Gate Delay in Switch2: 10ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50                                                                                |

|----|-------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 5  | <b>Volt</b> 5.1 5.2 5.3 | age Ba<br>Voltag<br>Techni<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>RC Sr<br>5.3.1<br>5.3.2 | Gate Delay in Switch2: 10ns  lancing: e sharing of series-connected SiC MOSFETS: iques for voltage balancing across series connected MOSFET: Active Gate Driver: Active Clamp circuit: RC Snubber circuit: Summary: Dubber: Gate Delay in Switch2: 10ns with Snubber Simulation Results: ical calculation: Optimization of the RC snubber design for series connection For estimating voltage difference across the switches with different snubber resistance and capacitance values For estimating the possibility of ZVS | 50<br><b>54</b><br>54<br>54<br>55<br>58<br>60<br>63<br>65<br>65<br>77<br>77<br>82 |

|    |                         | 5.4.3                                                                                     | For estimating power loss in snubber                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 83                                                                                |

| 6  | 6.1                     | Conclu<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5                                       | n and Recommendations usion  Voltage Balancer Topology:  Switch Selection: Inductor Design:  Voltage balancer simulation: Analytical calculation model: nmendations:                                                                                                                                                                                                                                                                                                                                                        | 85<br>85<br>85<br>86<br>87<br>88<br>89                                            |

| Re | fere                    | nces                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 90                                                                                |

| Α  | A.1<br>A.2              | MOSF<br>Perfor<br>Comp                                                                    | ET On Resistance vs Drain-Source Current ET Switching Loss vs Drain-Source Current mance Factor plot for Ferrite core materials: arison of compatible MOSFETs for series connected configuration arison of compatible MOSFETs for single connected configuration                                                                                                                                                                                                                                                            | 94<br>94<br>95<br>96<br>97<br>98                                                  |

| В  |                         | <b>nulas</b><br>Condu                                                                     | uction Loss of MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>99</b><br>99                                                                   |

| С  |                         |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>100</b><br>100                                                                 |

|    |                         |                                                                                           | figuration of bipolar DC voltage balancer using MOSFET: C2M0045170P MATLAB script to calculate total converter loss of series connected switch con-                                                                                                                                                                                                                                                                                                                                                                         | 100                                                                               |

|    |                         |                                                                                           | figuration of bipolar DC voltage balancer using MOSFET: C3M0030090K                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 101                                                                               |

# List of Figures

| 1.1        | Global Electricity generation sources (2019) [2]                                               | 1  |

|------------|------------------------------------------------------------------------------------------------|----|

| 1.2        | The rise in global temperature is directly linked to the increase in $CO_2$ level in the atmo- |    |

|            | sphere due to the increased burning of fossil fuels[3]                                         | 1  |

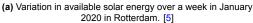

| 1.3        | Daily and Monthly variation in availability of Solar energy                                    | 2  |

| 1.4        | Conversion stages of an AC and DC distribution system                                          | 4  |

| 1.5        | A Unipolar and Bipolar DC distribution grid                                                    | 5  |

| 2.1        | Grid connected DC distribution system                                                          | 8  |

| 2.2        | Islanded mode DC distribution system                                                           | 9  |

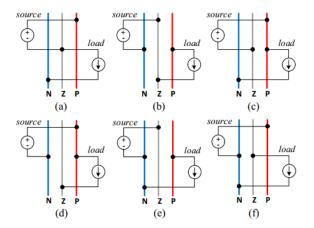

| 2.3        | Voltage imbalance in Bipolar DC grids can arise due to 6 different types of asymmetric         | 9  |

| 2.4        | operation/connection. Image taken from the works of Pires et al.[25]                           | 10 |

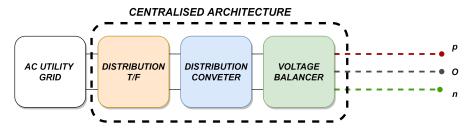

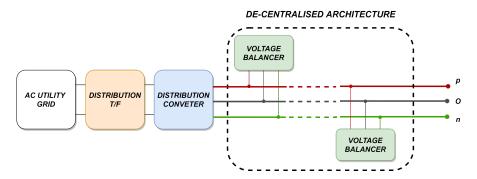

| 2.4<br>2.5 | De-centralised architecture of DC distribution system                                          | 10 |

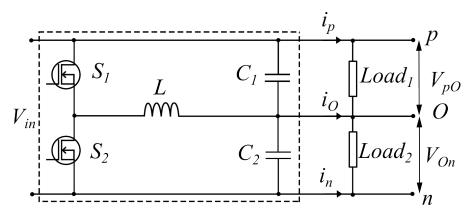

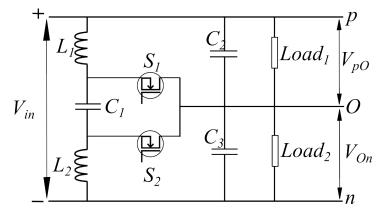

| 2.6        | Buck-Boost voltage balancer topology                                                           | 11 |

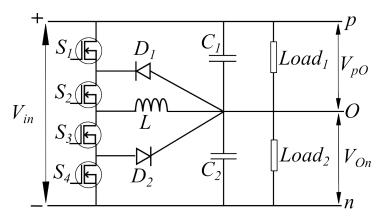

| 2.7        | Dual-Buck Half Bridge voltage balancer topology                                                | 12 |

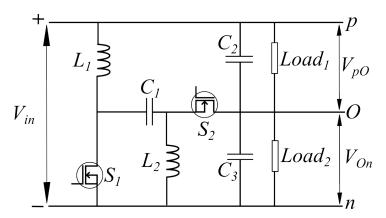

| 2.8        | Super SEPIC type voltage balancer topology                                                     | 12 |

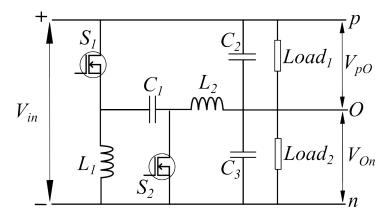

| 2.9        | Super ZETA type voltage balancer topology                                                      | 13 |

|            | Cuk Type voltage balancer topology                                                             | 14 |

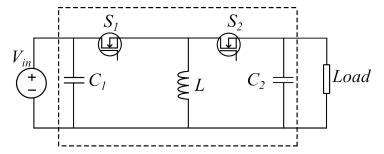

| 2.10       | Three-level voltage balancer topology                                                          | 14 |

| 2.11       | Synchronous Buck-Boost Converter                                                               | 15 |

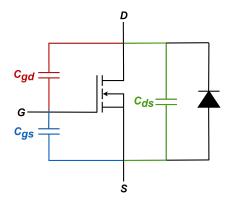

|            | Device model of SiC MOSFET. D, G, and S are Drain, Gate, and Source terminals re-              |    |

|            | spectively                                                                                     | 16 |

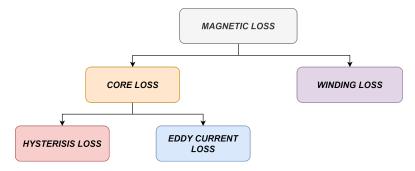

| 2.14       | Magnetic loss is primarily of two types, Core and Winding loss. Core loss can be further       |    |

| 0.45       | subdivided into Hysteresis and Eddy current loss                                               | 18 |

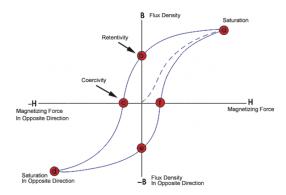

| 2.15       | Hysteresis curve for a magnetic material. The magnetic field density does not increase or      |    |

|            | decrease at the same rate when the magnetic field strength across it changes direction.        | 40 |

| 0.46       | (Image taken from [32])                                                                        | 18 |

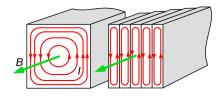

| 2.16       | Eddy current losses in solid and laminated cores. (Image taken from [33])                      | 19 |

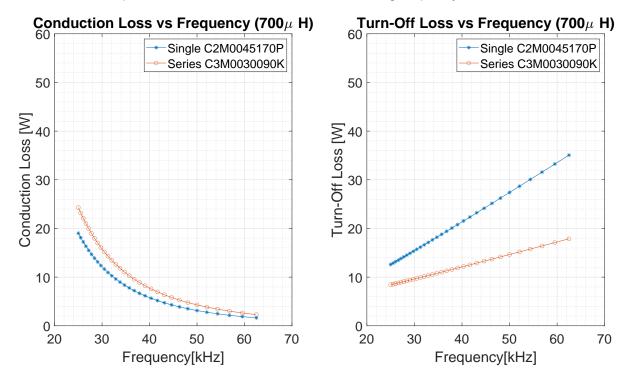

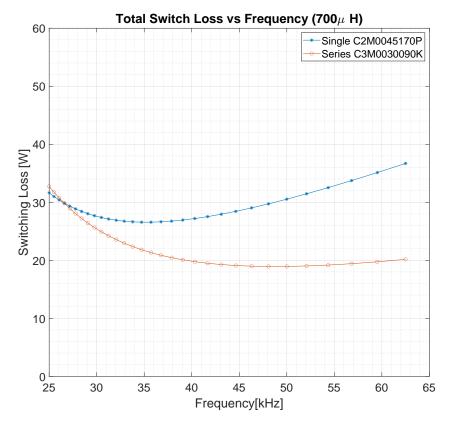

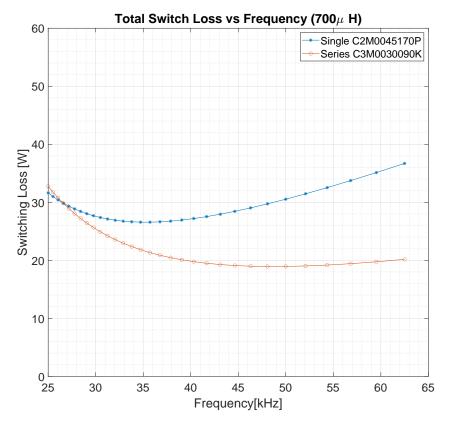

| 3.1        | Conduction and Turn-off loss vs Frequency for single and series connected MOSFET for           |    |

|            | 700 $\mu$ H inductance value. The conduction loss for series connected MOSFET is higher        |    |

|            | than for single MOSFET. However, Turn-off loss for single MOSFET is much higher than           |    |

|            |                                                                                                | 23 |

| 3.2        | Total switch loss vs Frequency for single and series connected MOSFET for 700 $\mu H$          |    |

|            | inductance value. The total switching loss (sum of Conduction and Turnoff loss) for            |    |

|            | single connected MOSFET is much higher than for series connected MOSFET                        | 24 |

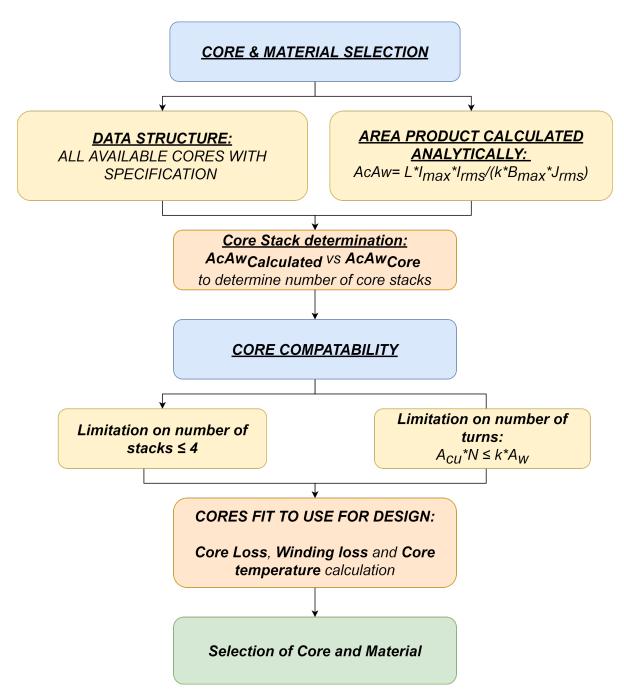

| 3.3        | Magnetic circuit design procedure used for parameterization and Optimisation of the design     | 26 |

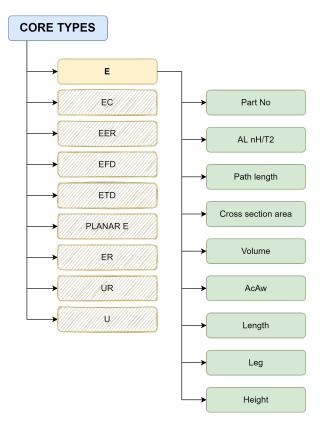

| 3.4        | Schematic representation of the data matrix showing the core specification and data            | ~= |

| ۰.         | collated for 'E' core type to be used for finalising core type for the magnetic circuit design | 27 |

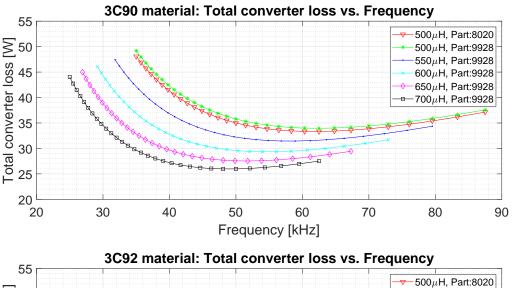

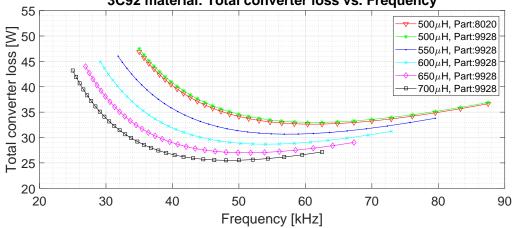

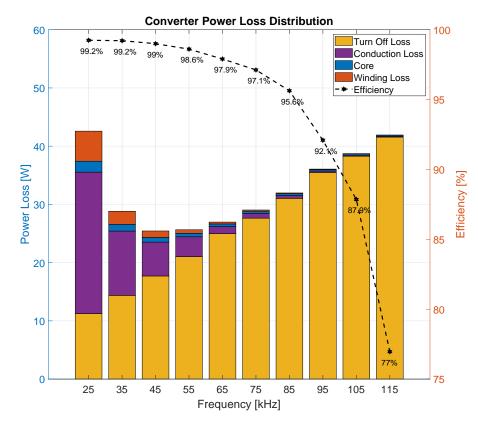

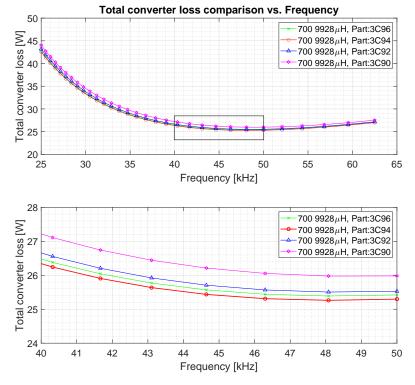

| 3.5        | Total Converter Loss vs Frequency for 3C90 and 3C92 material for EE core. It can be            |    |

|            | observed that for both materials 3C90 and 3C92, total converter loss initially decreases       |    |

|            | with an increase in frequency, reaches a minimum value, and then again starts increasing.      |    |

|            | Further, the minimum power loss is observed for the highest inductance value of $700\mu$ H     | ~~ |

| 2.0        | and part number 9928 for both 3C90 and 3C92 material                                           | 32 |

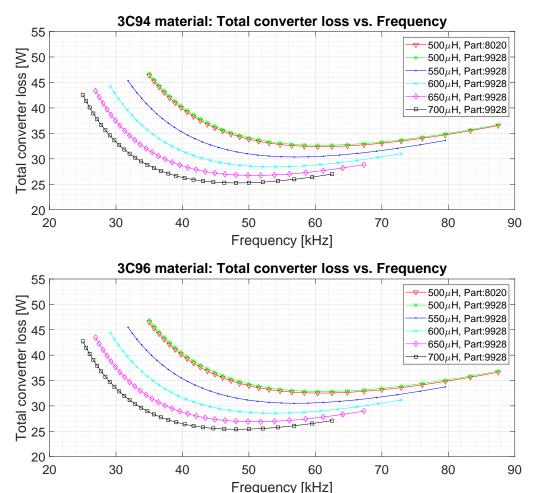

| 3.6        | Total Converter Loss vs Frequency for 3C94 and 3C96 material for EE core. It can be            |    |

|            | observed that for both materials 3C94 and 3C96, total converter loss initially decreases       |    |

|            | with an increase in frequency, reaches a minimum value, and then again starts increasing.      |    |

|            | Further, the minimum power loss is observed for the highest inductance value of $700\mu$ H     | 20 |

|            | and part number 9928 for both 3C94 and 3C96 material                                           | 33 |

List of Figures viii

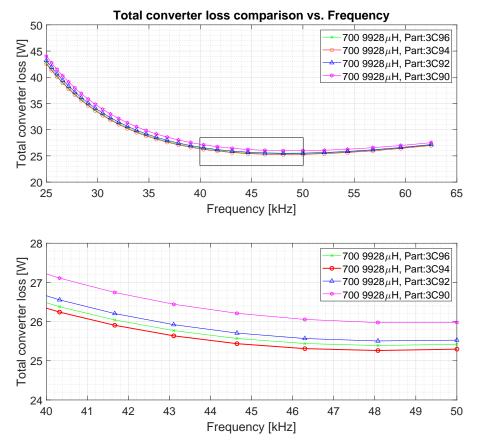

| 3.7         | Total Converter loss vs Frequency for $700\mu$ H and part no 9928 for 3C90,3C92,3C94 and 3C96 material. The minimum converter loss obtained for each material, as seen in Figure[3.5] and Figure[3.6 are compared and it can be seen that for 3C94 material the                                                                                                             |          |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

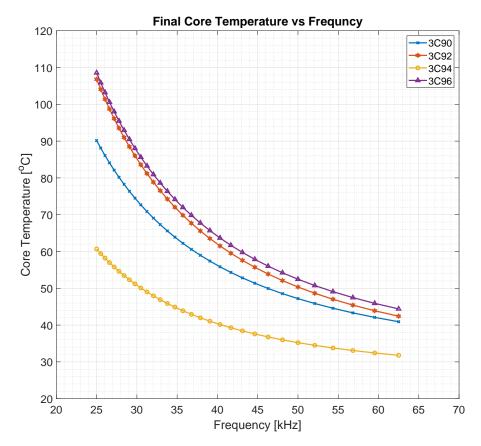

| 3.8         | total converter loss is observed to be the minimum at all operating frequencies Final core temperature for all core materials                                                                                                                                                                                                                                               | 34<br>35 |

| 3.9         | Converter loss distribution and Efficiency (displayed at the top of each bar) for different operating frequencies                                                                                                                                                                                                                                                           | 36       |

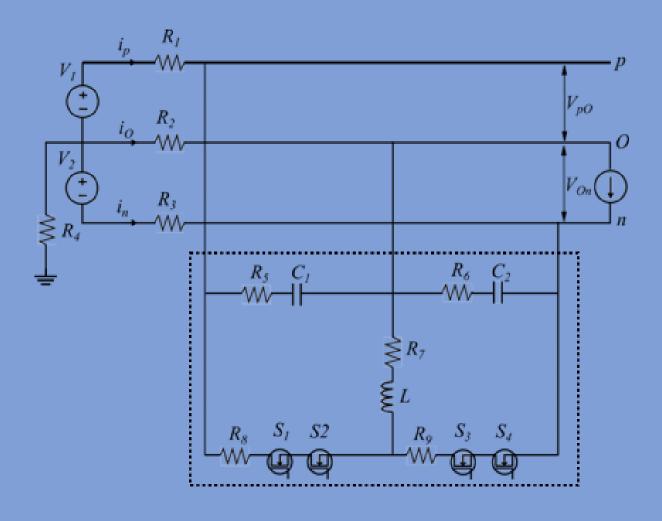

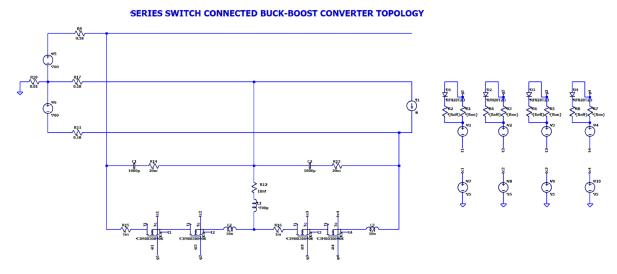

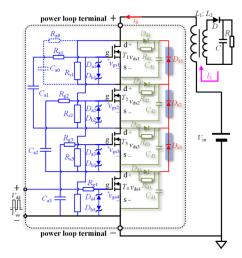

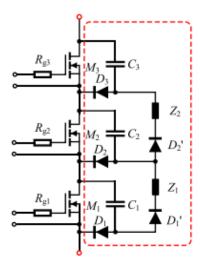

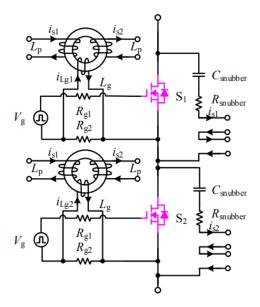

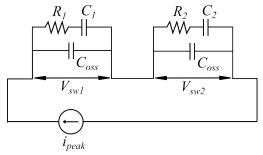

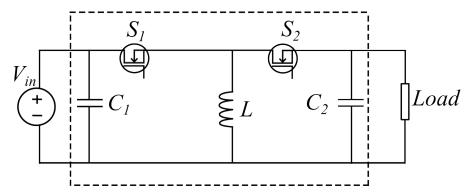

| 4.1         | Equivalent circuit of the series connected synchronous voltage balancer topology                                                                                                                                                                                                                                                                                            | 37       |

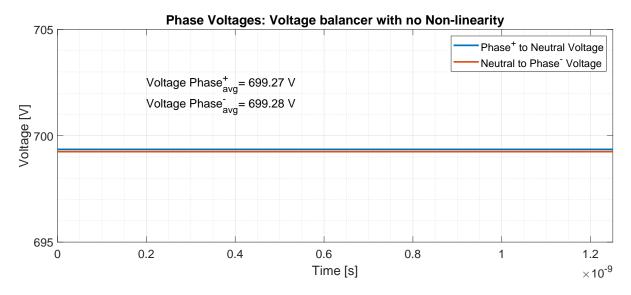

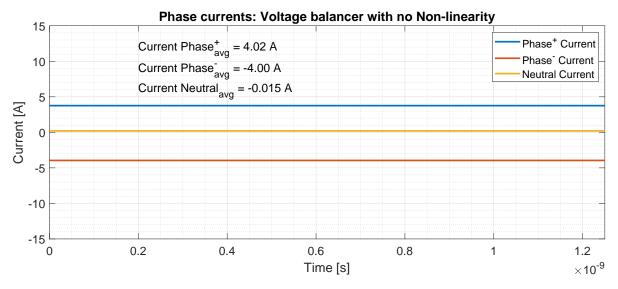

| 4.2         | Phase voltage and current in series connected voltage balancer without non-Linearity. It can be seen that the average Phase voltage for positive to neutral and neutral to negative lines are in balance. Further, the neutral line current is practically zero                                                                                                             | 38       |

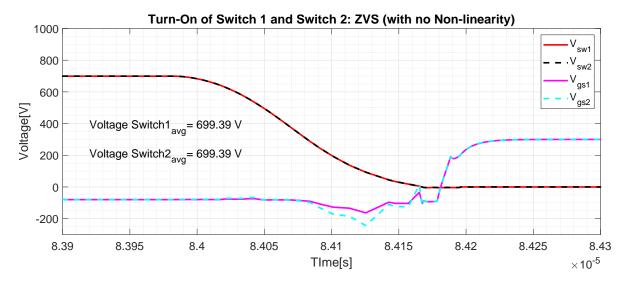

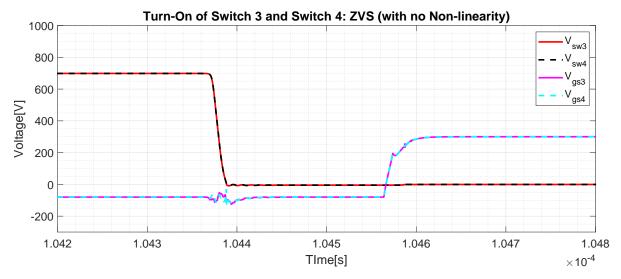

| 4.3         | ZVS Turn-On of Switch 1-2 and Switch 3-4 in series connected voltage balancer without non-Linearity. It can be observed that for both Switches 1-2 and Switches 3-4, ZVS at Turn-on is being achieved. Further, the average voltage over Switch 1 and Switch 2 is                                                                                                           |          |

| 4.4         | the same, indicating that voltage is equally distributed between the switches                                                                                                                                                                                                                                                                                               | 39       |

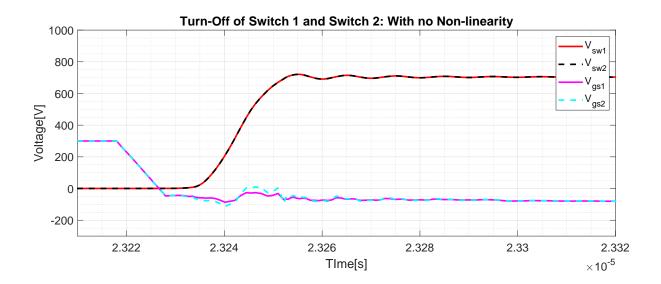

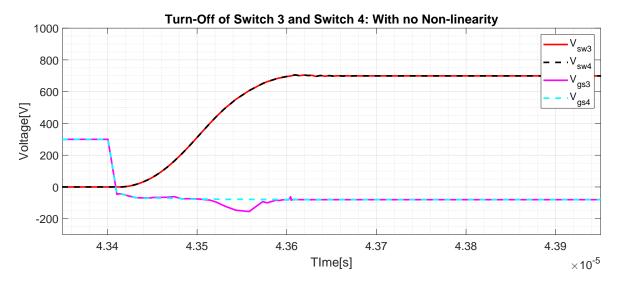

|             | without Non-linearity                                                                                                                                                                                                                                                                                                                                                       | 40       |

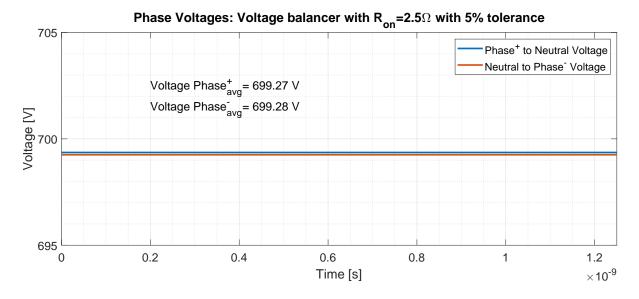

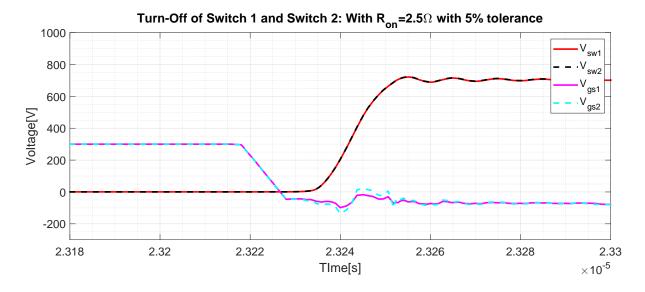

|             | 2.5 $\Omega$ with $\pm$ 5% tolerance. It can be seen that the average Phase voltage for positive to neutral and neutral to negative lines are in balance. Further, the neutral line current is practically zero.                                                                                                                                                            | 41       |

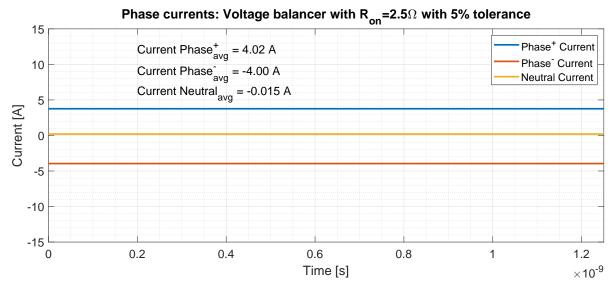

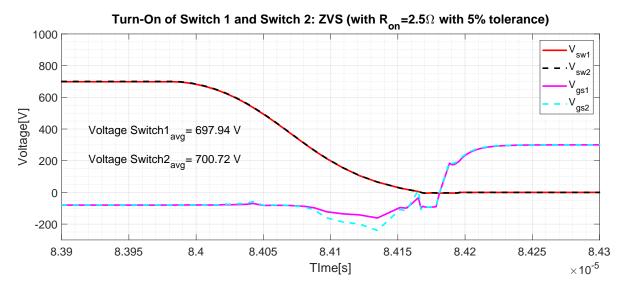

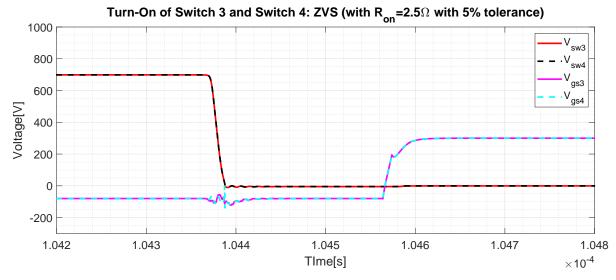

| 4.6         | ZVS Turn-On of Switch 1-2 and Switch 3-4 in series connected voltage balancer with non-Linearity: $R_{on}$ =2.5 $\Omega$ . It can be observed that for both Switches 1-2 and Switch 3-4, ZVS at Turn-on is being achieved. Further, the average voltage over Switch 1 and Switch 2 is the same for 1 time period indicating that voltage is equally distributed between the |          |

| 4.7         | switches                                                                                                                                                                                                                                                                                                                                                                    | 42       |

| 4.7         | with non-linearity $R_{on}$ =2.5 $\Omega$                                                                                                                                                                                                                                                                                                                                   | 43       |

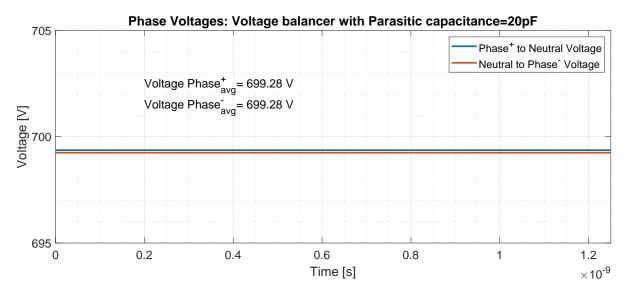

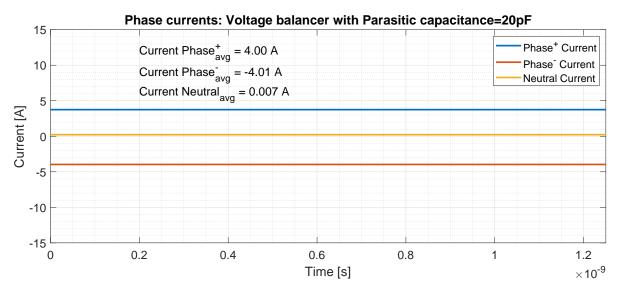

| 4.8         | Phase voltage and current in series connected voltage balancer with non-Linearity: Parasitic Capacitance:20pF. It can be seen that the average Phase voltage for positive to neutral and neutral to negative lines are in balance. Further, the neutral line current is practically zero.                                                                                   | 44       |

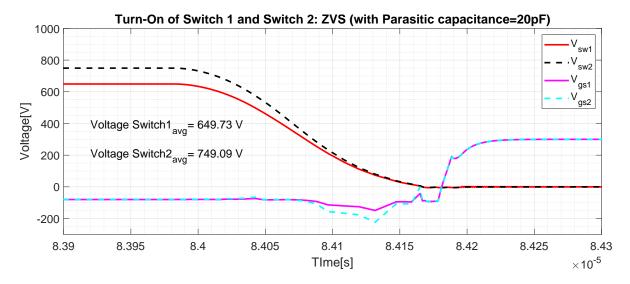

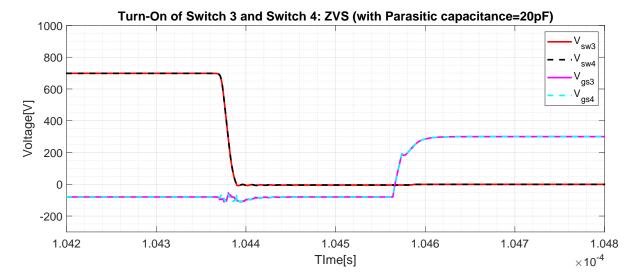

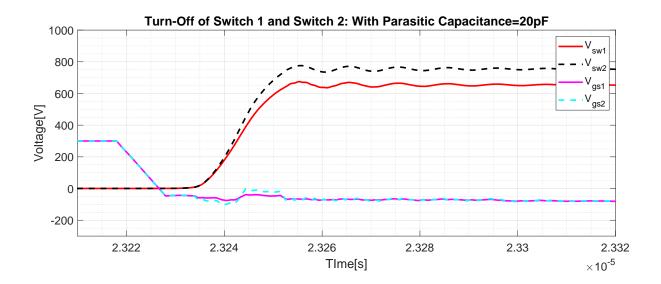

| 4.9         | ZVS Turn-On of Switch 1-2 and Switch 3-4 in series connected voltage balancer with non-Linearity: Parasitic Capacitance:20pF. It can be observed that for both Switches 1-2 and Switch 3-4, ZVS at Turn-on is being achieved. However, the average voltage over                                                                                                             |          |

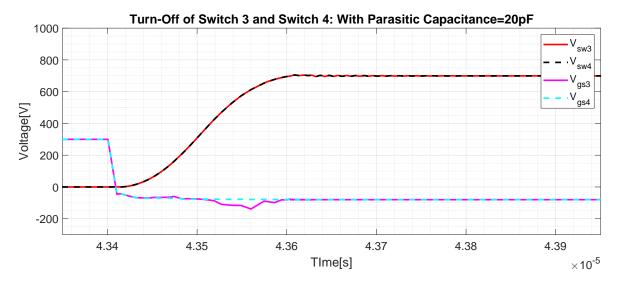

| <i>1</i> 10 | Switch 1 and Switch 2 is different.  Turn-off behaviour in Switch 1-2 and Switch 3-4 in series connected voltage balancer                                                                                                                                                                                                                                                   | 45       |

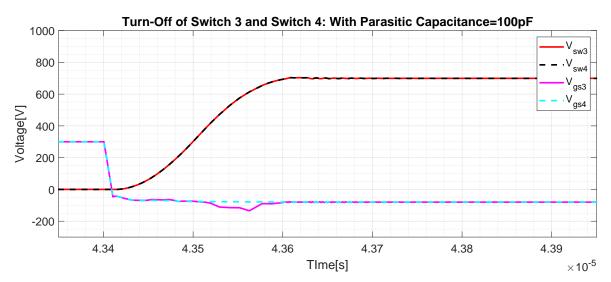

|             | with non-linearity Parasitic capacitance 20pF  Phase voltage and current in series connected voltage balancer with non-Linearity: Para-                                                                                                                                                                                                                                     | 46       |

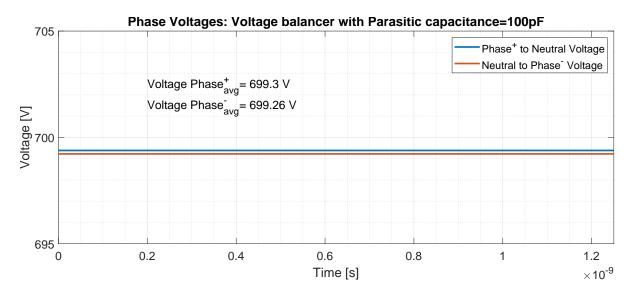

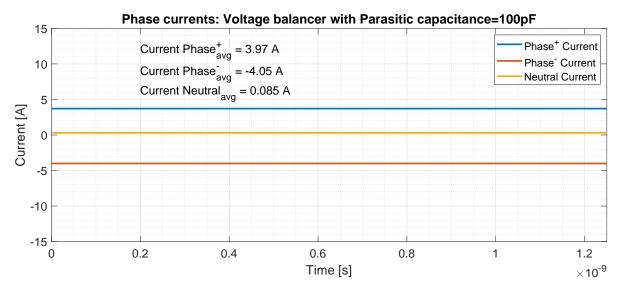

| 7.11        | sitic Capacitance:100pF, shown for 1 time period. It can be seen that the average Phase voltage for positive to neutral and neutral to negative lines are in balance. Further, the                                                                                                                                                                                          |          |

| 4.12        | neutral line current is practically zero.  ZVS Turn-On of Switch 1-2 and Switch 3-4 in series connected voltage balancer with non-Linearity: Parasitic Capacitance:100pF. It can be observed that for both Switches                                                                                                                                                         | 47       |

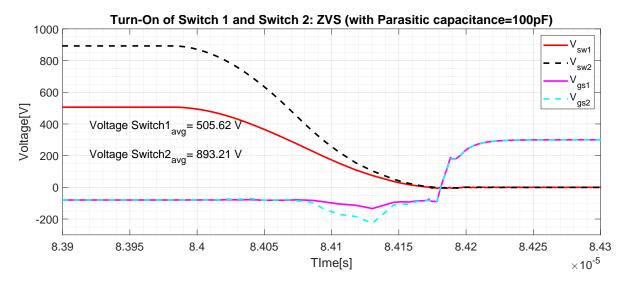

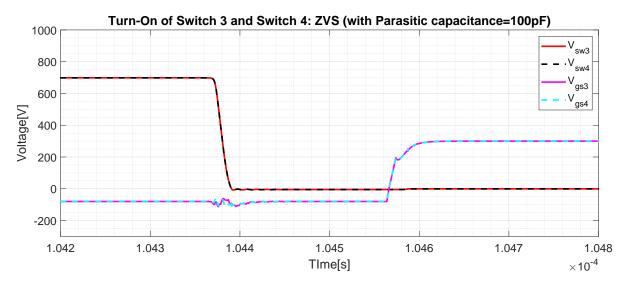

|             | 1-2 and Switch 3-4, ZVS at Turn-on is being achieved. However, the average voltage over Switch 1 and Switch 2 is different.                                                                                                                                                                                                                                                 | 48       |

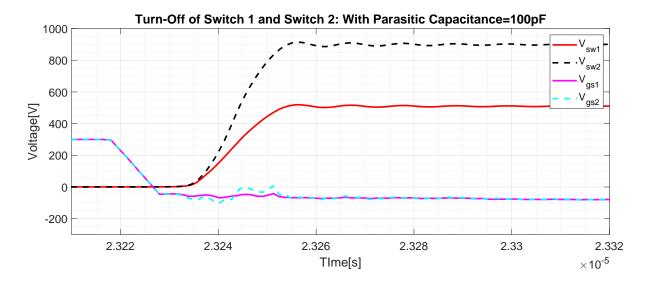

| 4.13        | Turn-off behaviour in Switch 1-2 and Switch 3-4 in series connected voltage balancer with non-linearity Parasitic capacitance 100pF                                                                                                                                                                                                                                         | 49       |

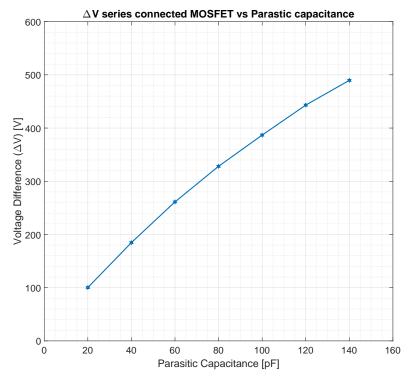

| 4.14        | LTSpice simulation results depicting how the voltage difference across the series con-                                                                                                                                                                                                                                                                                      |          |

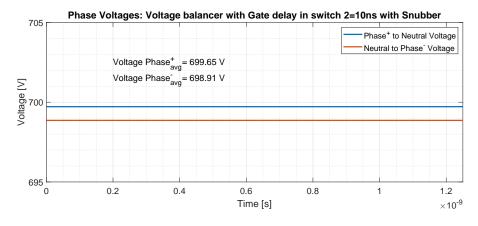

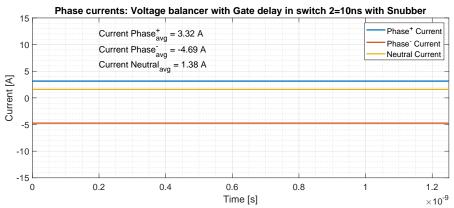

| 4.15        | nected MOSFET increases with an increase in parasitic capacitance across switch1 Phase voltage and current in series connected voltage balancer with non-Linearity: Gate delay in switch2: 10ns, shown for 1 time period. It can be seen that the average Phase voltage for positive to pourtal and pourtal to positive linear are in balance. Further, the                 | 50       |

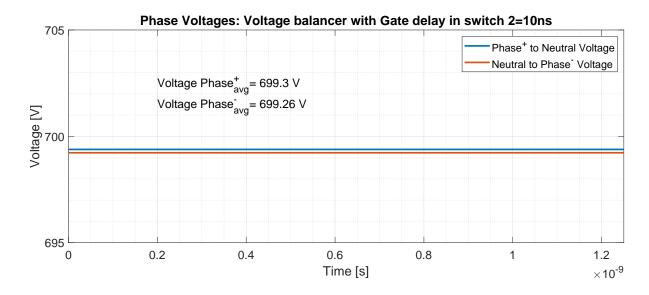

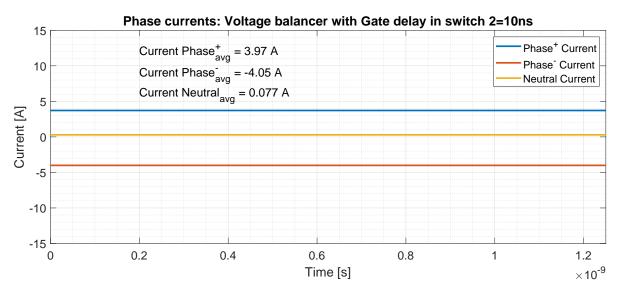

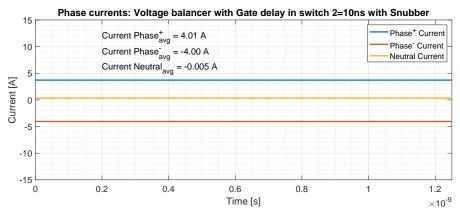

|             | voltage for positive to neutral and neutral to negative lines are in balance. Further, the neutral line current is practically zero.                                                                                                                                                                                                                                        | 51       |

List of Figures ix

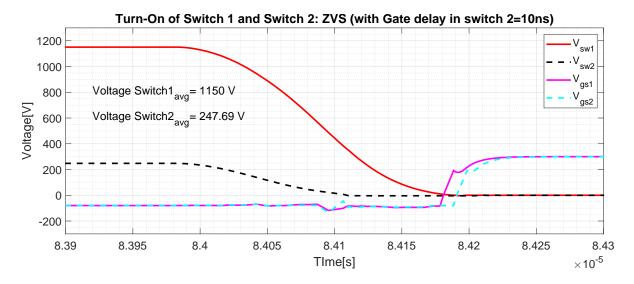

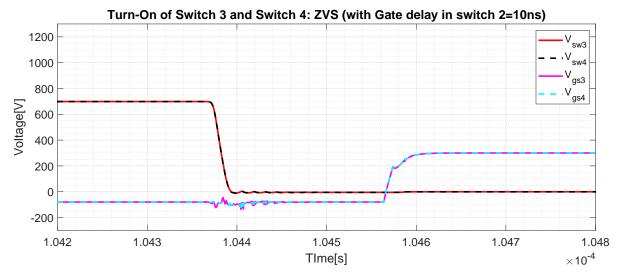

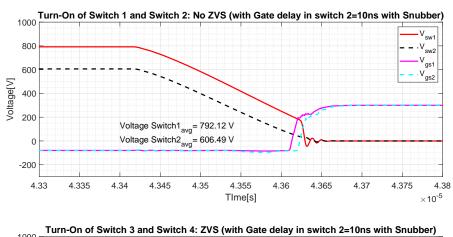

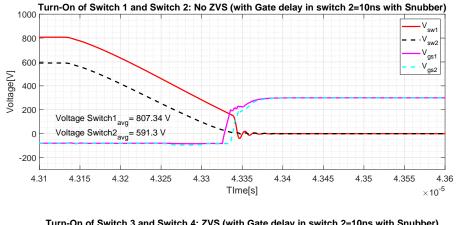

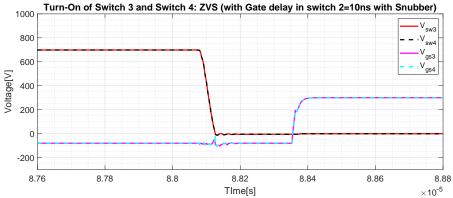

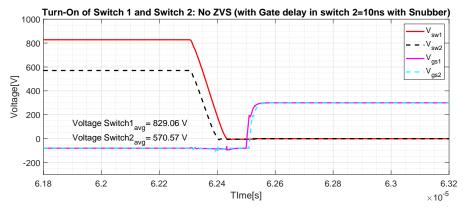

| 4.16       | 2VS Turn-On of Switch 1-2 and Switch 3-4 in series connected voltage balancer with non-Linearity: Gate delay in switch 2. It can be observed that for both Switches 1-2 and Switch 3-4, ZVS at Turn-on is being achieved. However, the average voltage over                                                                                                      |    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

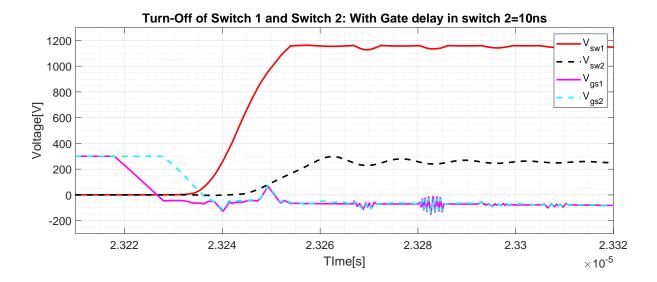

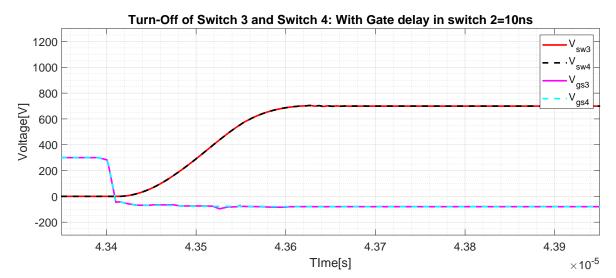

| 4.17       | Switch 1 and Switch 2 is different                                                                                                                                                                                                                                                                                                                               | 52 |

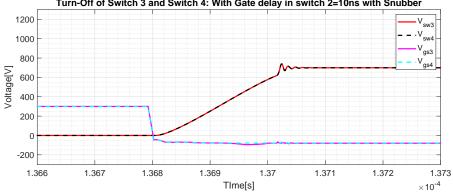

|            | with non-linearity Gate delay in switch 2=10ns                                                                                                                                                                                                                                                                                                                   | 53 |

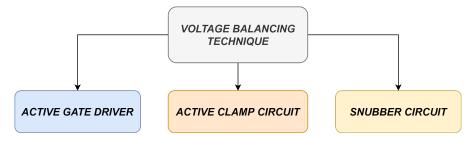

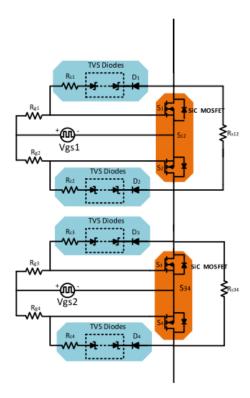

| 5.1<br>5.2 | Different techniques used for voltage balancing [35]                                                                                                                                                                                                                                                                                                             | 55 |

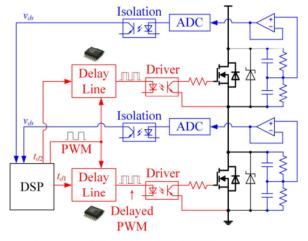

| 5.3        | and ensure that both switches get activated at the same time                                                                                                                                                                                                                                                                                                     | 55 |

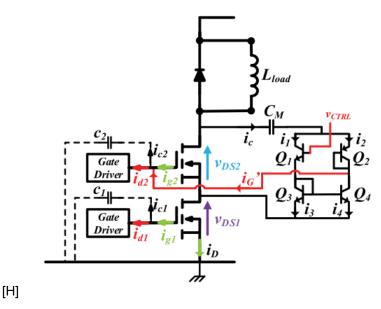

| 5.4        | in order to control the voltage slew rate $\frac{dv}{dt}$ of the MOSFET                                                                                                                                                                                                                                                                                          | 56 |

| 5.5        | pensation current to the gate driver with delay                                                                                                                                                                                                                                                                                                                  | 57 |

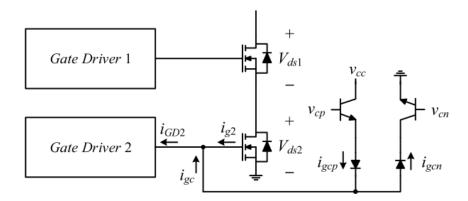

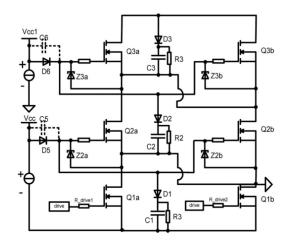

| 5.6        | vices as proposed by Wang et al [48]                                                                                                                                                                                                                                                                                                                             | 58 |

|            | proposed by Rahman et al [49]                                                                                                                                                                                                                                                                                                                                    | 59 |

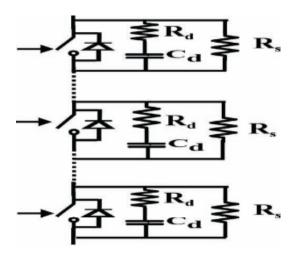

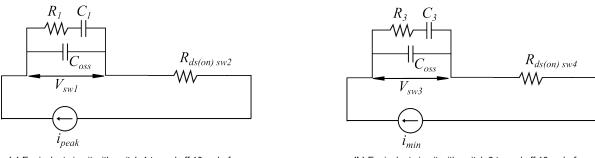

|            | the voltage balance across series connected MOSFET devices                                                                                                                                                                                                                                                                                                       | 60 |

|            | Equivalent circuit of the proposed RC snubber circuit for voltage balance across series connected MOSFET devices[52]                                                                                                                                                                                                                                             | 61 |

| 5.9        | Energy recovery snubber circuit proposed as a solution for unequal voltage sharing across series connected MOSFET by Zhang et al [46]                                                                                                                                                                                                                            | 62 |

| 5.10       | Modified RC snubber with a coupled inductor for voltage sharing across series connected MOSFET devices as proposed by Li et al [53],[55]                                                                                                                                                                                                                         | 63 |

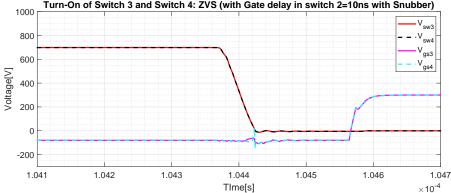

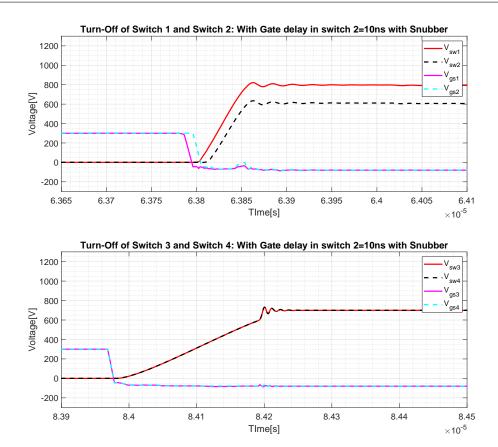

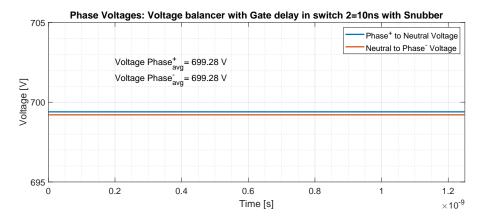

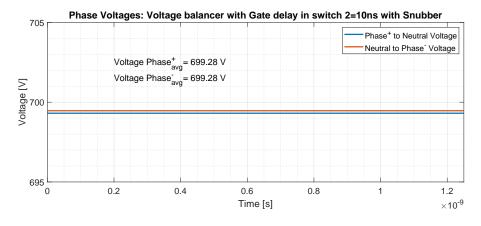

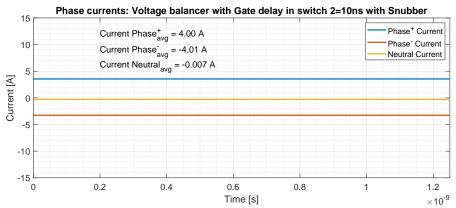

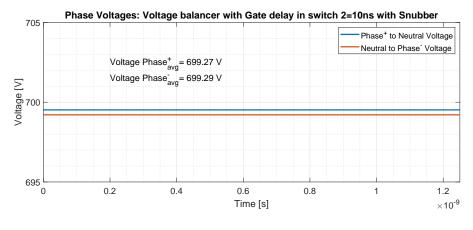

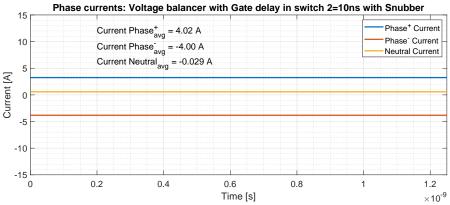

| 5.11       | Phase voltage and current in series connected voltage balancer with non-Linearity: Gate delay in switch2: 10ns with snubber circuit, shown for 1 time period. It can be seen that the average Phase voltage for positive to neutral and neutral to negative lines are not                                                                                        |    |

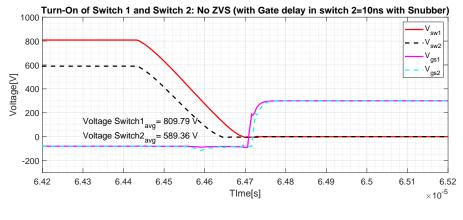

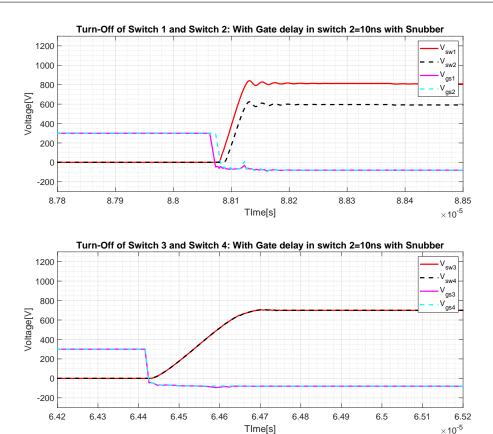

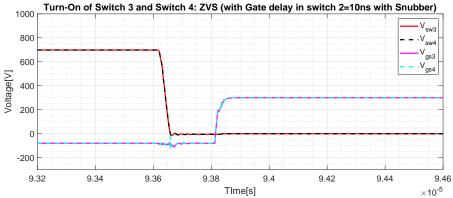

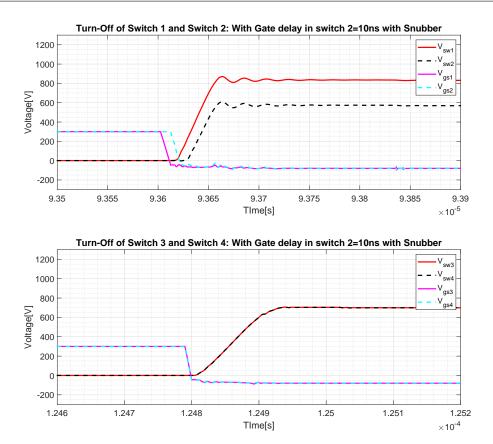

| 5.12       | balanced. Further, the neutral line current is also high                                                                                                                                                                                                                                                                                                         | 66 |

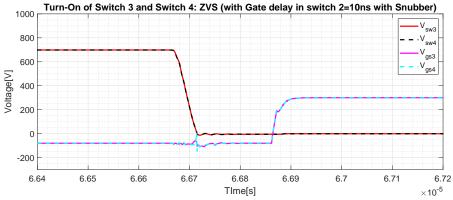

| 5 13       | achieved for Switch 1-2. For Switches 3-4 ZVS at turn-on is being achieved Turn-off behaviour in Switch 1-2 and Switch 3-4 in series connected voltage balancer                                                                                                                                                                                                  | 67 |

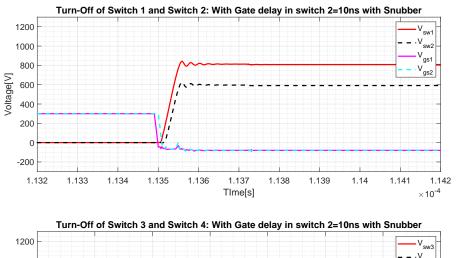

|            | with non-linearity gate delay in switch 2=10ns with snubber circuit                                                                                                                                                                                                                                                                                              | 68 |

| 5.14       | Phase voltage and current in series connected voltage balancer with non-Linearity: Gate delay in switch2: 10ns with snubber circuit with frequency changed to 21.35 kHz shown for 1 time period. It can be seen that the average Phase voltage for positive to neutral and neutral to negative lines are now balanced. Further, the neutral line current is also |    |

| - 4-       | balanced ( $\leq$ 0.03A)                                                                                                                                                                                                                                                                                                                                         | 69 |

| 5.15       | ZVS Turn-On of Switch 1-2 and Switch 3-4 in series connected voltage balancer with non-Linearity: Gate delay in switch 2 with snubber circuit with frequency changed to 21.35kHz. It can be observed with the snubber circuit, the voltage across switch 1 and switch 2 is unbalanced.                                                                           | 70 |

| 5.16       | switch 2 is unbalanced  Turn-off behaviour in Switch 1-2 and Switch 3-4 in series connected voltage balancer with non-linearity gate delay in switch 2=10ns with snubber circuit with frequency changed to                                                                                                                                                       | 70 |

| 5.17       | 21.35kHz  Phase voltage and current in series connected voltage balancer with non-Linearity: Gate delay in switch2: 10ns with snubber circuit with dead time 300ns, shown for 1 time period. It can be seen that the average Phase voltage for positive to neutral and neutral to                                                                                | 71 |

|            | negative lines and the neutral line current are all balanced                                                                                                                                                                                                                                                                                                     | 72 |

List of Figures x

| 5.18       | ZVS Turn-On of Switch 1-2 and Switch 3-4 in series connected voltage balancer with non-Linearity: Gate delay in switch 2 with snubber circuit with dead time 300ns. It can be seen that with this configuration ZVS at turn-on is being achieved for both the series switches                                                                                                                                      | 73       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.19       | Turn-off behaviour in Switch 1-2 and Switch 3-4 in series connected voltage balancer with non-linearity gate delay in switch 2=10ns with snubber circuit and dead time 300ns                                                                                                                                                                                                                                       | 74       |

| 5.20       | Phase voltage and current in series connected voltage balancer with non-Linearity: Gate delay in switch2: 10ns with snubber circuit with frequency 16kHz and Duty cycle 0.501, shown for 1 time period. It can be seen that voltage across positive to neutral, neutral to negative and neutral line current are all balanced.                                                                                     | 75       |

| 5.21       | ZVS Turn-On of Switch 1-2 and Switch 3-4 in series connected voltage balancer with non-Linearity: Gate delay in switch 2 with snubber circuit with frequency 16kHz and Duty cycle 0.501. It can be seen that with current operating condition, ZVS at turn-on in both switch is getting achieved.                                                                                                                  | 76       |

| 5.22       | Turn-off behaviour in Switch 1-2 and Switch 3-4 in series connected voltage balancer with non-linearity gate delay in switch 2=10ns with snubber circuit with frequency 16kHz                                                                                                                                                                                                                                      |          |

|            | and Duty cycle 0.501                                                                                                                                                                                                                                                                                                                                                                                               | 77       |

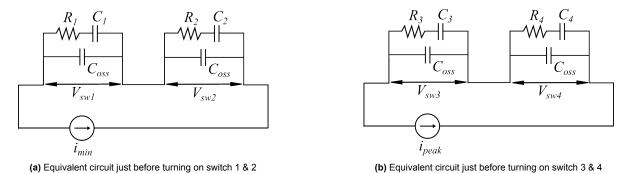

|            | Equivalent circuit with gate delay in switch 2 (10ns) at turn-off                                                                                                                                                                                                                                                                                                                                                  | 78       |

|            | Equivalent circuit with gate delay in switch 2 (10ns) turn-off after time: 10ns                                                                                                                                                                                                                                                                                                                                    | 79<br>81 |

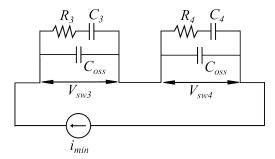

|            | Analytically calculated voltage across switch 1 at turn off vs LTspice simulation results . Analytically calculated voltage across switch 2 at turn off vs LTspice simulation results .                                                                                                                                                                                                                            | 81       |

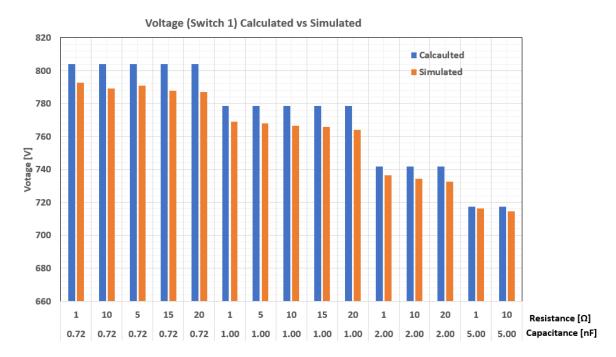

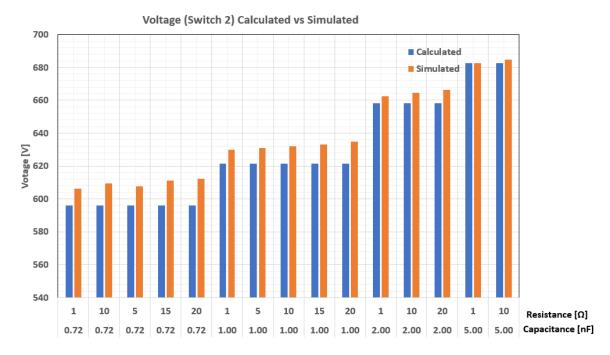

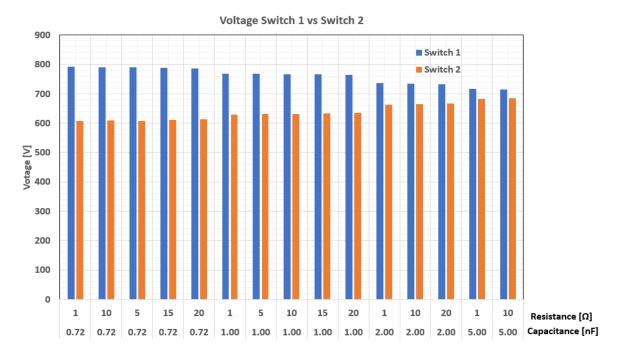

|            | Voltage across switches 1 and 2 at the turn-off. It can be seen that voltage difference across switches reduces with an increase in capacitance values. However, with higher capacitance, the discharge time of the capacitor increases which negates the possibility of ZVS at turn-on                                                                                                                            | 82       |

| 5.28       | Equivalent circuit before turning-on                                                                                                                                                                                                                                                                                                                                                                               | 82       |

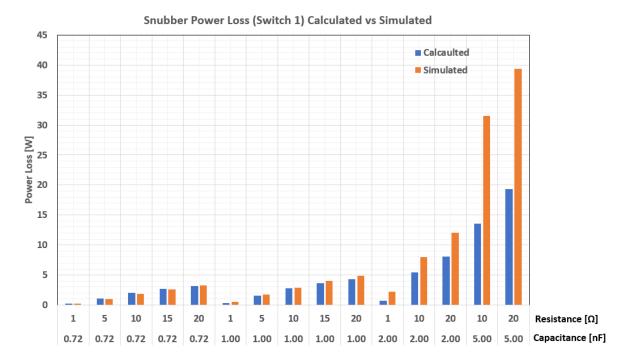

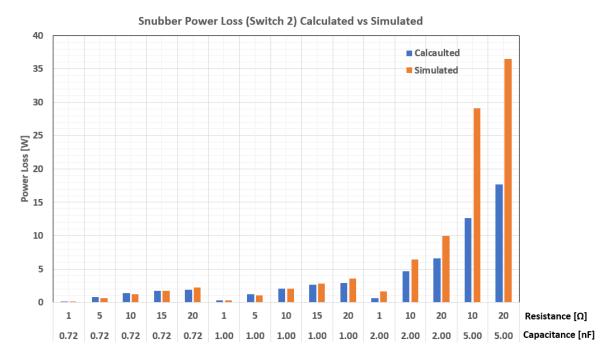

| 5.29       | Analytically calculated snubber losses vs LTspice simulation results for Switch 1 Analytically calculated snubber losses vs LTspice simulation results for Switch 2                                                                                                                                                                                                                                                | 84<br>84 |

| 6.1<br>6.2 | Synchronous Buck-Boost voltage balancer Topology                                                                                                                                                                                                                                                                                                                                                                   | 85       |

| 6.3        | than for series connected MOSFET for all switching frequency Total Converter loss vs Frequency for $700\mu\text{H}$ and part no 9928 for 3C90,3C92,3C94 and 3C96 material. The minimum converter loss obtained for each material, as seen in Figure[3.5] and Figure[3.6 are compared and it can be seen that for 3C94 material the total converter loss is observed to be the minimum at all operating frequencies | 86<br>87 |

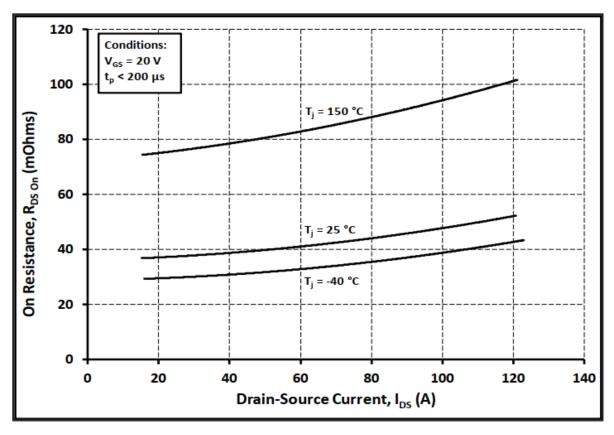

| Λ 4        | D vol for MOCEET COMONAEATOD for different to reconstitute                                                                                                                                                                                                                                                                                                                                                         | 0.4      |

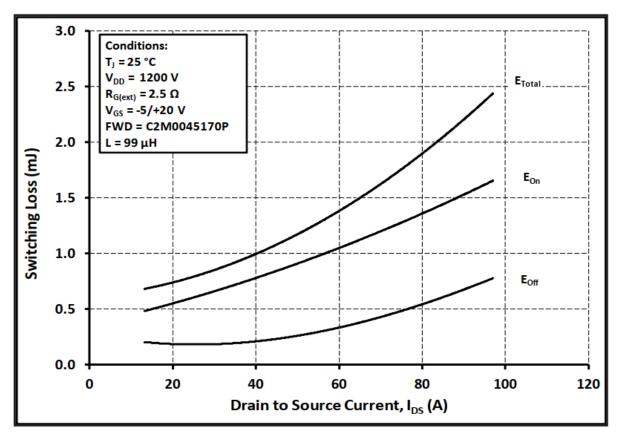

| A.1<br>A.2 | $R_{(DS)on}$ vs $I_{DS}$ for MOSFET C2M0045170P for different temperatures Switching loss vs drain-source current for MOSFET C2M0045170P                                                                                                                                                                                                                                                                           | 94<br>95 |

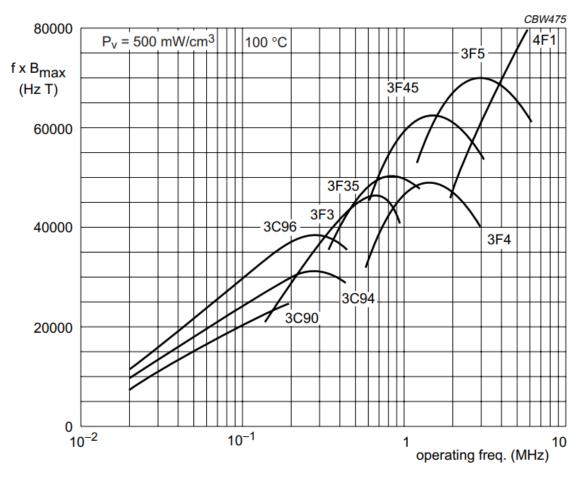

| A.2<br>A.3 | Performance factor plot for different ferrite materials for the specific power loss of 500                                                                                                                                                                                                                                                                                                                         | 90       |

| 73.0       | mWcm <sup>-3</sup> [40]                                                                                                                                                                                                                                                                                                                                                                                            | 96       |

# List of Tables

| 1.1        | Voltage Balancer Design Specification                                                                                                                                                  | 6  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1        | Description of MOSFET Capacitance                                                                                                                                                      | 16 |

| 3.16       | Final Inductor design parameters                                                                                                                                                       | 35 |

| 4.1<br>4.2 | Operating parameters for the LTspice simulation:                                                                                                                                       | 37 |

|            | balancer without non-linearity                                                                                                                                                         | 39 |

| 4.3        | LTSpice simulation results of ZVS at turn-on of switch 1-2 and switch 3-4 for series connected voltage balancer without non-linearity                                                  | 40 |

| 4.4        | LTSpice simulation results for series connected voltage balancer with non-linearity: $R_{on}$ = 2.5 $\Omega$ with $\pm$ 5% tolerance                                                   | 42 |

| 4.5        | LTSpice simulation results of ZVS at turn-on of switch 1-2 and switch 3-4 for series connected voltage balancer with non-linearity: $R_{on}$ = 2.5 $\Omega$ with $\pm$ 5% tolerance    | 43 |

| 4.6        | LTSpice simulation results for series connected voltage balancer with non-linearity: Parasitic capacitance=20pF                                                                        | 45 |

| 4.7        | LTSpice simulation results of ZVS at turn-on of switch 1-2 and switch 3-4 for series con-                                                                                              |    |

| 4.8        | nected voltage balancer with non-linearity: Parasitic capacitance=20pF LTSpice simulation results for series connected voltage balancer with non-linearity: Parasitic capacitance=20pF | 46 |

| 4.9        | asitic capacitance=100pF                                                                                                                                                               | 47 |

| 4.10       | nected voltage balancer with non-linearity: Parasitic capacitance=100pF LTSpice simulation results for series connected voltage balancer with non-linearity: Gate                      | 48 |

| 4.11       | delay of 10ns in switch 2                                                                                                                                                              | 51 |

|            | nected voltage balancer with non-linearity: Gate delay of 10ns in switch 2                                                                                                             | 52 |

| 5.1        | Summary of different methods used for voltage balancing across series connected MOS-FET devices                                                                                        | 64 |

| 5.2        | LTSpice simulation results for series connected voltage balancer with non-linearity: Gate delay of 10ns in switch 2 with RC snubber                                                    | 66 |

| 5.3        | LTSpice simulation results of ZVS at turn-on of switch 1-2 and switch 3-4 for series con-                                                                                              |    |

| 5.4        | nected voltage balancer with non-linearity: Gate delay of 10ns in switch 2 with RC snubber LTSpice simulation results for series connected voltage balancer with non-linearity: Gate   |    |

| 5.5        | delay of 10ns in switch 2 with RC snubber with frequency changed to 21.35kHz LTSpice simulation results of ZVS at turn-on of switch 1-2 and switch 3-4 for series con-                 | 69 |

| 5.6        | nected voltage balancer with non-linearity: Gate delay of 10ns in switch 2 with RC snubber LTSpice simulation results for series connected voltage balancer with non-linearity: Gate   | 70 |

| 5.7        |                                                                                                                                                                                        | 72 |

|            | nected voltage balancer with non-linearity: Gate delay of 10ns in switch 2 with RC snubber                                                                                             | 73 |

| 5.8        | LTSpice simulation results for series connected voltage balancer with non-linearity: Gate delay of 10ns in switch 2 with RC snubber                                                    | 75 |

| 5.9        | LTSpice simulation results of ZVS at turn-on of switch 1-2 and switch 3-4 for series connected voltage balancer with non-linearity: Gate delay of 10ns in switch 2 with RC snub-       |    |

|            |                                                                                                                                                                                        | 76 |

| 6.1        | Final Inductor design parameters                                                                                                                                                       | 87 |

| * ' · · C = 11 |     |

|----------------|-----|

| List of Tables | Xll |

| LIST OF TADICS | All |

| A.1        | Comparison of compatible MOSFETs for series connected configuration | 97 |

|------------|---------------------------------------------------------------------|----|

| <b>A.2</b> | Comparison of compatible MOSFETs for single connected configuration | 98 |

# Nomenclature

# Abbreviations

| Abbreviation | Definition                                        |

|--------------|---------------------------------------------------|

| AC           | Alternating Current                               |

| ADC          | Analog to Digital Converter                       |

| $CO_2$       | Carbon Dioxide                                    |

| DC           | Direct Current                                    |

| DSP          | Digital Signal Processing                         |

| EV           | Electric Vehicles                                 |

| LED          | Light Emitting Diode                              |

| $NO_x$       | Nitrogen oxides                                   |

| RES          | Renewable Energy Source                           |

| $SO_x$       | Sulphur Oxides                                    |

| MOSFET       | Metal-Oxide-Semiconductor Field-Effect Transistor |

| RC           | Resistive-Capacitive                              |

| SEPIC        | Single-Ended Primary Inductance Converter         |

| SiC          | Silicon Carbide                                   |

| ZVS          | Zero Voltage Switching                            |

# Introduction

In this chapter, the issue of global warming and bottlenecks with renewable energy sources (RES) is briefly presented followed by the introduction of DC distribution grids for facilitating RES implementation. Lastly, the research objectives and research questions are presented.

# 1.1. Electricity: Need for sustainability

Electricity today is an integral part of our daily life, with electrical appliances becoming ubiquitous and indispensable in carrying out our daily activities. Further, with the current pace of economic growth and the advent of the digital economy, the global electricity demand is expected to rise exponentially.[1].

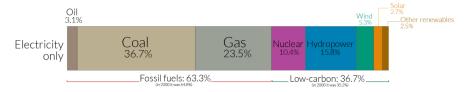

Electricity in itself is a clean source of energy; however, the current methods of its production are primarily fossil fuel-based, mainly coal and gas which accounts for more than 60% of global electricity production [2] as shown in Figure 1.1. The major issues with using carbon-intensive fossil fuels, as a source of electricity generation are mentioned below:

Figure 1.1: Global Electricity generation sources (2019) [2]

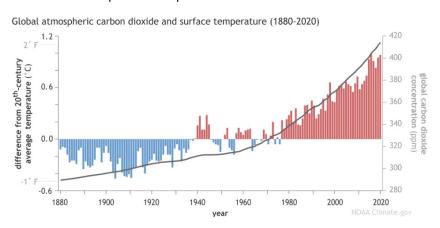

• **Global Warming:** Burning of fossil fuels leads to the emission of greenhouse gases such as  $CO_2$ ,  $SO_x$ , and  $NO_x$  among others. The rise in  $CO_2$  levels in the atmosphere is directly linked to the unprecedented warming up of the atmosphere, land, and oceans[3]. The same is shown in Figure 1.2 below. This is adversely affecting all life forms on earth, and if this continues unabated, then it will lead to catastrophic consequences for the earth's climate.

Figure 1.2: The rise in global temperature is directly linked to the increase in  $CO_2$  level in the atmosphere due to the increased burning of fossil fuels[3]

• **Unsustainable:** Fossil fuel reserves are limited in their supply and hence, it is not sustainable to depend on fossil fuels as the main energy source. Thus, it is imperative that a transition be made to renewable/sustainable sources of energy.

Therefore, the decarbonization of the electricity sector is the central element of current global climate policies. As per IPCC report 2021[4], limiting global temperature rise to 1.5°C would require rapid and far-reaching transitions in terms of energy generation and improvement in the efficiency of current electricity sources. Thus, a rapid transition towards RES is imperative in resolving the climate crisis.

Although RES have been around for quite some time, their contribution towards electricity supply is still restricted to  $\approx$  11% even in 2019 (see Figure 1.1). This is mainly because RES have certain limitations which restrict their integration in the current electricity infrastructure. The same is discussed in the next section.

# 1.2. Issues with the Renewable sources of Energy

The major hindrances in the large-scale implementation of RES are as below:

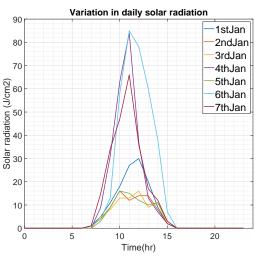

Availability: One of the major drawbacks of renewable sources of energy is the availability of energy. Wind, Solar energy, etc., suffer from the issue of intermittent availability. This intermittency can vary on a short time hourly variation to the long time scale of seasonal variation. Figure 1.3a and 1.3b below show the daily and monthly variation in available solar energy over Rotterdam [5]. Furthermore, there is also often a mismatch between energy availability and demand which further hinders their usage.

(b) Variation in available solar energy over the year 2020 in Rotterdam. [5]

Figure 1.3: Daily and Monthly variation in availability of Solar energy

• Integration into existing grids: AC distribution system is inextricably woven into our power system. However, to accommodate RES and other distributed generation resources to the existing power system, the incorporation of power electronic interfaces is needed as many renewable power sources are inherently DC supplies. Wind energy too can be better optimized if at least part of the wind generator's capacity is coupled through power electronic conversion that includes a DC bus [6]. However, these distributed generation sources when integrated into the present AC utility grid can cause voltage rise and protection issues which then challenge the security, reliability, stability, and quality of the utility grid. Along with this, their integration will require multiple conversion stages making the system more complicated and prone to additional conversion power losses thus making it less efficient.

# 1.3. Mitigation of bottlenecks

In order to mitigate the bottlenecks discussed in previous sections, various solutions are being developed.

- Availability: To tackle the issue of intermittent availability of renewable sources, various energy storage systems are being developed. These systems can help overcome the issue of intermittency and can help offset the demand-supply mismatch. Some of the prominent energy storage systems which are being used are mentioned below:

- Battery: Advancement in Lithium-ion and Redox flow batteries has been a major achievement in battery technology and has resulted in their large-scale deployment, especially with the global push for electric vehicles. However, in order to be economically viable for large-scale energy storage, more development in terms of energy capacity improvement and cost reduction is required [7].

- Hydrogen: Using renewable electricity to generate hydrogen via electrolysis and then using this hydrogen in a fuel cell to get back electricity as per demand is another strategy that is being deployed to tackle the issue of demand-supply mismatch. However, in the current state of technology, the cost of generation of hydrogen using renewable energy sources is much higher as compared to fossil-based sources [8]. Further, the overall system efficiency with hydrogen is still not very high for such systems.

- Super-capacitors: Super-capacitors are also being developed to store energy. These capacitors can release the stored energy in a very short time and hence can be very useful. However, the low energy density and high cost of super-capacitors are limiting its large-scale implementation [9].

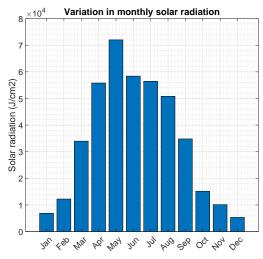

- DC Distribution system: To mitigate the issues of integration of renewable sources into the AC grid, a DC active grid at the distribution level is being adopted. There are varied applications of DC distribution system including, datacenters, electric vehicle charging infrastructure, commercial buildings, shipboard microgrids, etc. Along with the benefit of integration, there are multiple advantages of switching from AC to DC distribution grids as mentioned below:

- In the DC distribution grid, RES can be fully utilised because of their compatibility with the DC-based system. RES and power electronic loads can be supplied more effectively and efficiently by choosing a suitable voltage level that will in turn reduce the number of conversion stages [10]. DC distribution system has simplified power conversion stages which require less number of components and complexity. For instance, integrating a DC load to a DC bus via a DC-DC converter is simpler and more efficient than integrating the same to an AC line via inverters [11], [12].

- Less conductor material is required to transfer the same amount of power in the DC distribution system as compared to AC which controls the total conduction losses of the DC line [13].

- The increased penetration of DC sinks such as computers, laptops, LEDs, battery chargers, etc., which represents 50 % of electronic loads in many commercial and residential buildings [14], makes using DC distribution systems more appealing. Therefore, considerable attention has been given to the DC distribution system which converts and delivers DC power directly to the DC loads. This enhances energy efficiency by reducing conversion and power losses from 15-40% to 10-15% [15].

- Figure 1.4a and 1.4b below compares the number of conversion stages involved in an AC and DC microgrid respectively [16].

(a) Conversion stages of a AC distribution system [16]

(b) Conversion stages of a DC distribution system [16]

Figure 1.4: Conversion stages of an AC and DC distribution system

- Present AC systems have virtually no storage thus making them susceptible to interruptions

in power supply. These limitations are taken care of in the DC distribution system by introducing various energy storage systems (ESS). ESS can also come in handy during peak

shaving, load leveling, absorbing regenerative power, etc.

- DC distribution systems are also suitable for AC supply RES. Integration of wind turbines

with the AC grid requires back-to-back power conversion from AC to DC and back to AC to

synchronize and adjust the voltage and output frequency level. It is easier to adopt a DC-DC

converter than an AC-DC inverter.

- To maintain the power stability in an AC utility grid, both voltage and frequency are required to be monitored and controlled whereas, in DC distribution lines, only voltage needs to be monitored. Along with this, DC distribution lines are free of reactive power issues, AC losses, and skin effects and thus have lower control complexity and smaller footprints (fewer filters) [17].

- There is a possibility of potential health concerns from human exposure to 60 Hz distribution lines and thus switching to DC grids will have long-term benefits on the health of human beings as well as animals.[18]

#### 1.4. DC Distribution Architecture

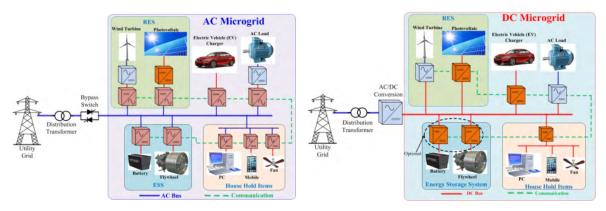

In order to integrate new technologies such as RES, modifications in the existing DC architectures are required to further enhance their flexibility and controllability. Electric power in a DC distribution system can be transmitted either over a two-wire or three-wire system configuration.

According to the number of buses, the existing DC distribution network system can be categorized into two types of DC bus frames: Unipolar and Bipolar DC bus configuration [19].

- **Unipolar**: A unipolar (also known as monopolar) DC distribution system comprises two DC wires providing a single DC voltage level between the two conductors. The majority of DC installations adopt this configuration. Though this architecture is easier to control and is less complex, it lacks the reliability and resilience of a three-wire Bipolar DC distribution.

- **Bipolar**: A Bipolar DC distribution system is a three-wire system that provides two voltage levels across those three wires [20] and thus provides more flexibility and reliability than unipolar systems.

Figure 1.5 below shows a schematic representation of a unipolar and bipolar DC distribution grid.

Figure 1.5: A Unipolar and Bipolar DC distribution grid

The advantages of using a bipolar DC distribution system over a unipolar system are as follows:

- The bipolar architecture of the DC distribution system provides two voltage levels to choose from

with fewer buses. Therefore, a device can be connected between pole-to-neutral or pole-to-pole

depending on its end-use application. More voltage levels make the system more connectionfriendly between DC sources and DC loads.

- RES, EV charging stations, and green buildings can be flexibly integrated to efficiently utilize the DC power supply system, reducing the conversion stages even further. Fewer buses for transfer mean lower transmission losses [13].

- With the presence of three DC lines, system stability, reliability, flexibility, and efficiency can be improved. Independent operation of the DC buses protects the system against failure. In case of operational failure in one DC line, the power continuity can be ensured by using the other two lines of the bipolar grid, thus ensuring the system's reliability.

- Short circuit faults and grounding issues are some of the major challenges associated with DC systems. The presence of a neutral conductor in Bipolar DC configuration provides an easier and faster method for clearing these faults ([21], [22]), and thus makes Bipolar DC configuration more suitable than unipolar DC grids.

- Bipolar architecture allows a reduction in the distribution voltage with respect to the ground, thereby improving safety [23].

Despite the various advantages of the Bipolar DC distribution system, it has its own share of limitations:

- Asymmetrical operation due to the unbalanced power distribution is caused by drawing or injecting different power levels in the two poles. For instance, unbalanced load distribution and/or integration of ESS leads to an unbalanced neutral line current. This further leads to voltage imbalance between the phases leading to deterioration of power quality and increase voltage stress of semiconductor devices [20].

- The power losses in the system are increased due to unbalanced voltages. Further, the lifetime of the devices is also adversely affected due to these unbalanced voltages [24].

Due to the tremendous potential that bipolar DC grids hold for the development of DC distribution systems, it is essential to regulate the unbalanced voltage in the bipolar DC distribution network by adopting a voltage balancer circuit. Voltage balancer improves the quality and flexibility of the power supply in a bipolar DC distribution system by balancing the bus voltage and current to ensure that the system operates safely within the rated range.

This thesis pertains to the development of a voltage balancer for a DC Distribution system focusing on the Bipolar DC Distribution system. The specification for the same is provided in Table 1.1 below:

ParameterDescriptionValueUnit $V_{Grid}$ Grid Voltage1400V $P_{Out}$ Output Power5kW

Table 1.1: Voltage Balancer Design Specification

Further, through this research, the application of a series connected switch configuration will also be explored and its performance will be evaluated over a single switch configuration.

# 1.5. Research Objectives

The main objective of the thesis is to design a balancing converter that can be used to keep the phase voltages of a bipolar DC grid balanced and the neutral line current to zero to account for the unbalances in the system.

The research objectives can be summarised below:

- Identifying a suitable topology for balancing converter through literature research

- Modelling and simulation of the balancing converter for the single switch and series connected switches configuration using MATLAB and LTSpice.

- Comparison of various methods for driving series connected MOSFET switches and implementation of the most suitable method in the LTSpice simulation model.

## 1.6. Research Questions

To achieve the research objectives, the following are the research questions this thesis aims to answer:

- 1. What are the promising topologies that have been developed for voltage balancing of a Bipolar DC distribution system?

- 2. What is the optimum design for the chosen topology of the voltage balancer?

- 3. What is the impact of series switch configuration in the optimized design of voltage balancer?

- 4. What are the available methods to account for voltage imbalance in series connected switch configuration?

## 1.7. Structure of the thesis

The thesis addresses each of the research questions in separate chapters. The chapters are arranged as follows:

• Chapter 2: It provides an overview of the literature research into the working of Bipolar DC distribution systems, existing topology for voltage balancer of DC distribution system, and the design considerations for the chosen voltage balancer topology for this thesis. This chapter also delves into the possibility of using series-connected switches to enable the balancer converter model for high-voltage applications.

- Chapter 3: This chapter elaborates on the modeling of the voltage balancing converter design using MATLAB. This encapsulates the switch selection for single and series-connected configurations of voltage balancer topology, comparison of the two configurations based on their losses, parameterization of the components of the configuration chosen, optimization of the magnetic design, and calculation of total converter loss.

- Chapter 4: This chapter discusses the LTSpice simulation model of the optimized series connected switch configuration of the voltage balancing converter for bipolar DC grid operation. Further, non-linearities are introduced in the configuration to address the issue with the seriesconnected switch configuration of the voltage balancer. LTSpice simulation results of the same are also discussed.

- Chapter 5: It covers the comparison between different methods adopted to account for the unbalanced voltage sharing across the series-connected switch configuration of the balancing converter owing to the non-linearities introduced in the previous chapter. The most prominent of the methods is then employed in the LTSpice model. An analytical derivation to interpret the degree of voltage unbalance is also provided for the employed method.

- **Chapter 6:** In the final chapter the conclusions from this thesis and the recommendations for further research are presented.

In this chapter the background information required to achieve the research objectives of the thesis is presented. At first, the Bipolar DC distribution system and its working are explained in detail, followed by an overview of the existing voltage balancer topologies used for Bipolar systems. After this, the chosen topology, i.e., the Buck-Boost system is explained. Lastly, the series switch configuration of buck-boost topology as a voltage balancer is presented.

## 2.1. Bipolar DC Distribution System

The expansion of RESs, ESS, and the large-scale implementation of electronics in most appliances have resulted in the development and implementation of DC distribution systems [25]. Within the DC power grids, Bipolar DC distribution systems are more favorable than unipolar grids (established in Section 1.4).

The Bipolar DC grids, based on their connection with the utility grid, can further be sub-divided into the following categories:

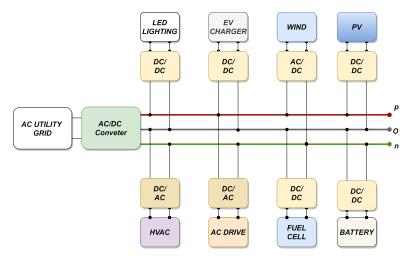

• **Grid Connected:** In this configuration, the AC utility voltage is converted to DC with the use of distribution transformer and an active rectifier. At the DC level, the system adopts a three-wire structure composed of a positive conductor (p), a negative conductor (n), and a neutral conductor (O). Although the three-wired structure looks complex, it provides a clear advantage over the two-wired unipolar structure. The two voltage levels of a bipolar configuration allow penetration of a wide set of distributed generators, energy storage systems, and loads with different voltage levels and power rating combinations in a single DC network. A schematic of this configuration is shown in Figure 2.1 below:

Figure 2.1: Grid connected DC distribution system

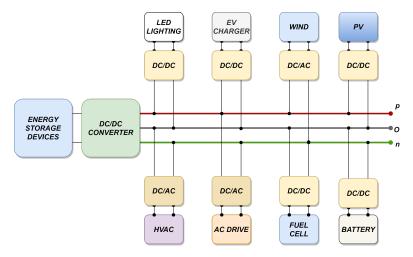

• Islanded Mode: In this configuration, the DC grid is connected to a DC power system which can be a DC Energy storage system or RES which directly generates DC power through a DC-DC

converter stage. At the DC level, the connection is similar to as shown for grid connected DC grid in Figure 2.1. A schematic of this configuration is shown in Figure 2.2 below.

Figure 2.2: Islanded mode DC distribution system

# 2.2. Bipolar DC Grids: Challenges