# Mixed signal pcb design and Analog Readout Circuitry for a Pixelated Capacitive Sensor Enose array

# **BSc Thesis**

# Mixed signal pcb design and Analog Readout Circuitry for a Pixelated Capacitive Sensor E-nose array

# **BSc Thesis**

by

P. Olyslaegers Y. Machtane

to obtain the degree of Bachelor of Science at the Delft University of Technology,

Student: P. Olyslaegers 5667127 Y. Machtane 5709628

Project duration: April 21, 2025 – June 27, 2025

Supervisors: Prof. dr. ir. F. P. Widdershoven, TU Delft, NXP Semiconductors

MSc. T. Shen TU Delft

Thesis committee: Prof. dr. ir. F. P. Widdershoven, TU Delft, NXP Semiconductors

MSc. T. Shen TU Delft

Dr.ir. C. J. M. Verhoeven TU Delft

An electronic version of this thesis is available at http://repository.tudelft.nl/.

# **Abstract**

This thesis addresses the development of a supporting electronics platform for a CMOS Pixelated Capacitive Sensor (PCS) array intended for high-sensitivity applications. The work focuses on enabling accurate extraction of capacitance changes at the sensor interface and translating them into signals suitable for digital processing. The design process emphasizes functional integration and signal integrity.

A custom analog front-end was developed, featuring a transimpedance amplifier (TIA) optimized for low input-referred noise and sufficient bandwidth to preserve pixel-level signal integrity. The complete analog signal path supports capacitive measurements with attofarad-level resolution and readout frequencies ranging from 1 MHz to 100 MHz.

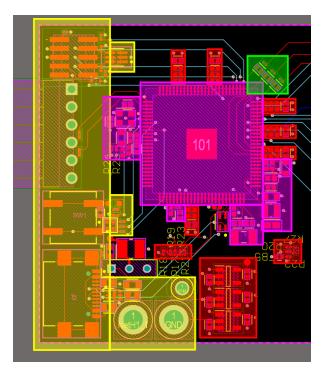

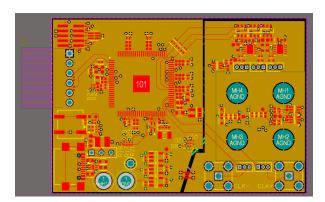

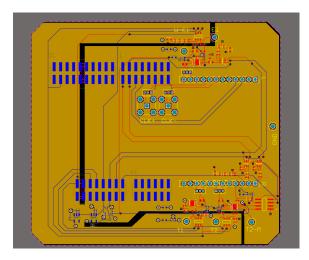

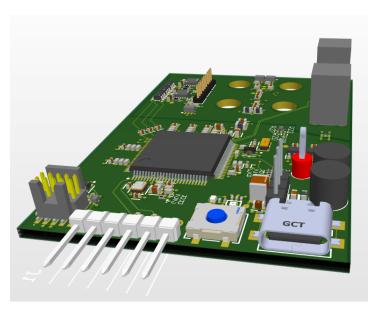

The main PCB integrates the readout circuitry with a central microcontroller (MCXN947), DAC-controlled programmable power supplies, and a variety of user interface connectors, all within a compact six-layer mixed-signal stackup. Particular attention was given to minimizing electromagnetic interference (EMI) and power supply noise through careful grounding, power segmentation, and layout strategies. Although the PCB theoretically satisfies most mandatory and trade-off requirements, including spatial and interface constraints, final verification of the noise performance remains pending due to fabrication lead times.

# **Preface**

Every chip requires a reliable interface, and every sensor must be properly read to deliver meaningful data. The goal of this project was to provide the e-nose sensor with the necessary supporting infrastructure and readout circuits, while maintaining an efficient and compact PCB footprint.

We would like to express our sincere gratitude to our daily supervisor, Tao Shen, and our supervisor, Prof. Dr. Ir. Frans Widdershoven, for their invaluable guidance and advice throughout this project. We also warmly thank Dr. Ir. Chris Verhoeven for his insightful discussions and for serving as an inspiring sounding board for our ideas.

Furthermore, we extend our heartfelt thanks to our team members, Chantal Chen, Feifei Lin, Kevin Pang, and Wilson Rong, for their dedication, enthusiasm, and friendship over the past few months.

P. Olyslaegers Y. Machtane Delft, June 2025

# Contents

| Αk | stra              | :t                                                                                                                         |                                                                              |                       |              |          |             |         |     |     |      |   |                                                          | İ                                              |

|----|-------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------|--------------|----------|-------------|---------|-----|-----|------|---|----------------------------------------------------------|------------------------------------------------|

| 1  | Intro             | duction                                                                                                                    |                                                                              |                       |              |          |             |         |     |     |      |   | 1                                                        | 1                                              |

| 2  | Prog              | ramme of                                                                                                                   | Requirements                                                                 | 5                     |              |          |             |         |     |     |      |   | 3                                                        | 3                                              |

| 3  |                   | gn Proces System Ov Backgroun 3.2.1 SLI Sensor rea 3.3.1 PC 3.3.2 Ser 3.3.3 Qua 3.3.4 Bas 3.3.5 T-n                        | -                                                                            | onsiderati            | <br>         |          |             | <br>    |     |     | <br> |   | <br>. 6<br>. 6<br>. 7<br>. 10<br>. 12<br>. 14            | 5<br>5<br>5<br>6<br>7<br>7<br>7<br>7<br>7<br>8 |

|    | 3.4               | Power 3.4.1 MC 3.4.2 PC 3.4.3 Rea                                                                                          | iable gain<br><br>U PWR<br>S chip PWR .<br>adout circuit P\<br>nplete system | <br><br><br>WR        | <br><br><br> | <br><br> | · · · · · · | <br>    |     |     | <br> |   | <br>. 21<br>. 21<br>. 23                                 | 1<br>1<br>3                                    |

|    | 3.5<br>3.6<br>3.7 | Grounding<br>Connector<br>3.6.1 SW<br>3.6.2 UA<br>3.6.3 US<br>3.6.4 UA<br>3.6.5 Res<br>3.6.6 Ext<br>MCU Integ<br>3.7.1 Dat | s & UI                                                                       | TAG ove               | <br>         |          |             |         |     |     |      |   | <br>. 24<br>. 25<br>. 25<br>. 26<br>. 26<br>. 27<br>. 27 | 4555677                                        |

| 4  |                   | em Implen Full PCB 4.1.1 Sta 4.1.2 Ele 4.1.3 Me 4.1.4 Ser 4.1.5 Lay                                                        | •                                                                            | rations.<br>derations | <br>         |          |             | <br>    |     |     | <br> |   | <br>29<br>. 29<br>. 30<br>. 30<br>. 30                   | 9 9 0 0 1                                      |

| 5  |                   | 4.2.2 Lay<br>ussion<br>Full PCB                                                                                            | ditional comporout                                                           |                       | <br>         | <br>     |             | <br>    |     |     | <br> |   | <br>. 34<br>. 35                                         | 4<br>5<br>5                                    |

| 6  | ·                 | clusion                                                                                                                    | a readout Of                                                                 | ouit                  | <br>• •      | <br>     | • •         | <br>• • | • • | • • | <br> | • | <br>. 37                                                 |                                                |

| Α | Simulation results A.0.1 Differential | <b>39</b><br>43 |

|---|---------------------------------------|-----------------|

| В | TIA T network                         | 45              |

| С | Schematics                            | 47              |

| D | PCS Chip Pinout and Functionality     | 54              |

1

# Introduction

In large-scale greenhouse cultivation, effective disease control is essential for both crop yield and economic sustainability. For example, in 2020 the average pesticide usage for roses in the Netherlands reached  $40.1\,\frac{\mathrm{kg}}{\mathrm{ha}}\,$  [1]. In a 4-hectare greenhouse, this corresponds to  $\mathrm{\leqslant}4,010\mathrm{-}\mathrm{\leqslant}16,040$  per treatment, based on current pesticide pricing, excluding labor and application overhead. Reducing unnecessary pesticide use not only minimizes environmental impact but also presents significant cost-saving opportunities.

Electronic nose (e-nose) systems provide a promising route for precision agriculture by enabling early detection and localization of plant diseases. These systems detect Volatile Organic Compounds (VOCs) emitted by infected plants, allowing targeted treatment at the individual plant level. The e-nose architecture employed in this project uses a CMOS Pixelated Capacitive Sensor (PCS) array functionalized with VOC-sensitive inks. These inks exhibit changes in dielectric constant upon exposure to specific gaseous compounds, leading to a corresponding change in capacitance that can be measured electronically.

While the sensing mechanism is conceptually straightforward, its practical implementation involves significant technical challenges. Capacitance variations induced by VOC interactions are extremely small, typically in the attofarad  $(10^{-18}F)$  range, necessitating low-noise, high-resolution analog front-ends for accurate signal acquisition. In addition, the mixed-signal nature of the system imposes stringent requirements on power distribution, electromagnetic compatibility, and grounding strategies. These constraints become particularly demanding in embedded platforms where size, power, and integration density are limited.

## State of the Art

Early e-nose systems were based on large-scale lab instrumentation such as gas chromatography and mass spectrometry, which offered high selectivity and sensitivity but lacked portability and affordability. More recent approaches have leveraged miniaturized sensor arrays, often based on metal-oxide semiconductors, conductive polymers, or capacitive sensing—to provide compact and application-specific alternatives.

Capacitive e-noses based on CMOS technology, such as PCS arrays, offer several advantages: scalability, low power consumption, and compatibility with post-processing steps such as inkjet printing for functionalization. However, their practical deployment depends on the ability to read out the capacitive signals with high fidelity. As sensor dimensions decrease, parasitic effects and noise become dominant, requiring robust circuit design techniques such as differential readout, shielding, and correlated sampling.

An effective analog front-end design requires a careful balance between gain, resolution, and noise to maintain sensitivity while preserving signal integrity. Additionally, the integration of these analog systems with modern microcontrollers, such as the NXP MCXN947, provides a platform for building fully embedded e-nose solutions. However, few existing systems document the challenges and design decisions involved in building such a tightly integrated, high-precision capacitive readout platform.

#### Thesis Overview

This thesis addresses these challenges through the design of a custom mixed-signal PCB that interfaces a CMOS PCS array with a high-performance microcontroller. The work involves the development of an analog readout chain tailored to small-signal detection, integration of a multi-rail programmable power subsystem, and layout of a compact, interference-resilient board architecture.

The remainder of this thesis is organized as follows:

- Chapter 2 outlines the Program of Requirements for the system and details design constraints.

- Chapter 3 describes the design methodology and analog circuitry, including amplification stages and readout considerations.

- · Chapter 4 covers full system implementation, stackup considerations, and mechanical layout.

- Chapter 5 presents performance evaluations and discusses limitations and observations.

- · Chapter 6 summarizes the work and provides recommendations for future development.

# Programme of Requirements

In order to evaluate the success and objectives of the project, a **Programme of Requirements** was created. This is divided into two parts for each task. For every task, the structure consists of:

- Mandatory Requirements (MR): These must be fulfilled for the project to be considered successful.

- Trade-Off Requirements (ToR): These are desirable goals that can be compromised if necessary.

## **Readout Circuit**

#### **Mandatory Requirements (MR.1)**

- [MR.1.1] The pixel capacitance shall be measured with sufficient resolution to allow detection of changes induced by the presence of VOCs.

- [MR.1.2] The measured capacitance values shall be converted into a digital format readable by the MCXN947 microcontroller

- [MR.1.3] The analog noise present at the output of the readout circuit shall not exceed the equivalent of four quantization steps of the ADC.

#### Trade-Off Requirements (ToR.1)

- **[ToR.1.1]** The system should support pixel readout using a variable switching frequency in the range of 1 MHz to 100 MHz.

- **[ToR.1.2]** Only the capacitance variation resulting from interactions with VOCs should be measured, while the intrinsic pixel capacitance should be excluded. This requirement builds upon **[MR.1.1]** to further enhance measurement accuracy.

- **[ToR.1.3]** The analog noise at the output of the readout circuit should not exceed two quantization steps of the ADC when measuring VOC-induced capacitance changes.

#### Main PCB

#### Mandatory Requirements (MR.2)

- [MR.2.1] The PCB shall support UART for serial communication.

- [MR.2.2] The PCB shall support SWD/JTAG for debugging and programming.

- [MR.2.3] The PCB shall support USB-C for power and data connectivity.

- [MR.2.4] The PCB shall employ the MCXN947 microcontroller as the central unit for control and sensor data processing.

- **[MR.2.5]** The PCB shall have a physical footprint smaller than  $84.5 \, \text{mm} \times 49 \, \text{mm}$ , which corresponds to the dimensions of the previous board revision.

- [MR.2.6] The PCB shall regulate the 5 V input voltage to 3.3 V and distribute it to all components requiring a 3.3 V supply.

- [MR.2.7] The PCB shall be able to deliver the necessary power to all onboard components, taking into account an estimated total current consumption of approximately 100 mA based on the previous board implementation.

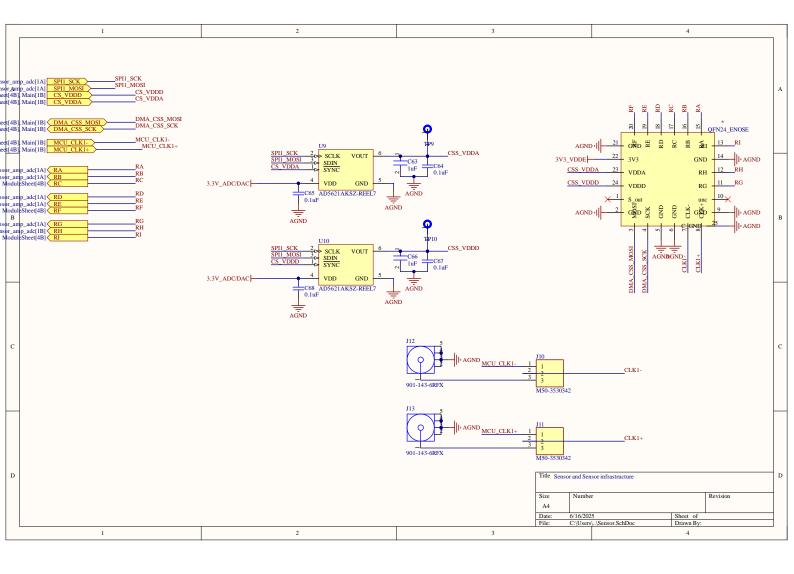

- [MR.2.8] The PCS array chip shall be supplied with the required power, control and differential clock signals.

- [MR.2.9] The PCS chips VDDA and VDDD inputs shall have a variable power source to allow for further testing the optimal voltage level.

- **[MR.2.10]** The output signals from the PCS array chip shall be acquired, processed, and transferred to the MCU for further handling.

- [MR.2.11] The noise at the outputs of the chip caused by the combination of crosstalk from the VDDA, VDDE, and VDDD supplies shall not exceed 4 quantization steps of the ADC.

#### **Trade-Off Requirements (ToR.2)**

- **[ToR.2.1]** All external connectors and interface ports should be located on a single side of the PCB to simplify cable routing during testing and deployment.

- [ToR.2.2] The PCB should provide an option to connect an external lab power supply.

- **[ToR.2.3]** The noise at the outputs of the chip caused by the combination of crosstalk from the VDDA, VDDE, and VDDD supplies should not exceed 2 quantization steps of the ADC.

# **Design Process**

## 3.1. System Overview

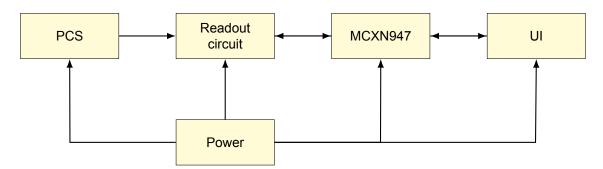

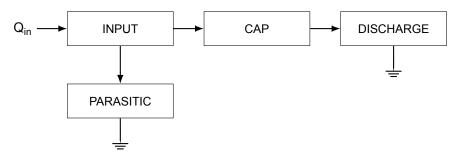

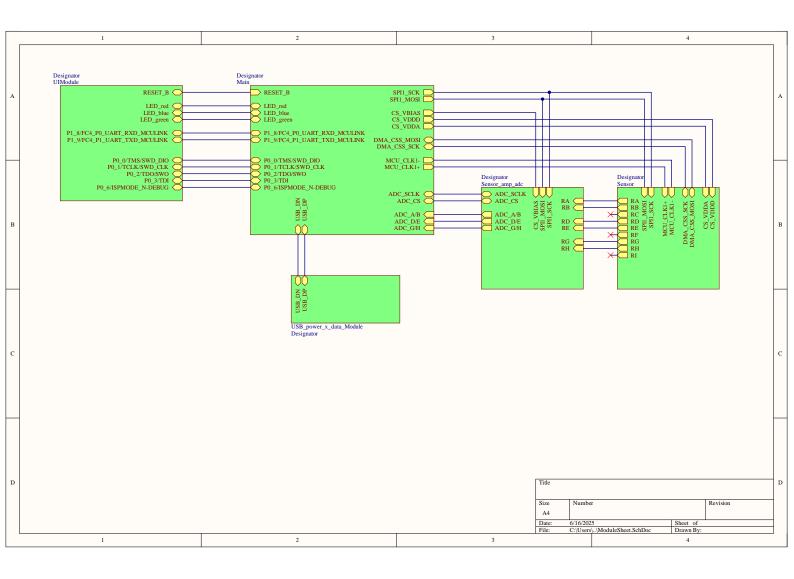

The system consists of five main components, as illustrated in Figure 3.1.

- **PCS**: The Pixelated Capacitive Sensor (PCS) array serves as the core sensing element. Each pixel detects changes in capacitance caused by interactions between sensing inks and Volatile Organic Compounds (VOCs).

- **Readout circuit**: This block converts the capacitance variations from the PCS into voltage signals using low-noise analog circuitry, including a transimpedance amplifier and differential gain stages. The processed signal is then digitized for interpretation by the MCU.

- MCXN947: The microcontroller coordinates the operation of the system. It receives data from the readout circuit, processes it, and communicates with the user interface. It also controls various peripherals, including programmable DACs.

- UI: The user interface (UI) comprises the physical connectors and indicators that enable interaction with the system. This includes SWD/JTAG, UART, and USB-C ports for communication, as well as status LEDs and a reset button for basic user control and feedback.

- Power: The power subsystem generates and distributes the required supply rails (e.g., 3.3 V) to all components. It includes low-dropout regulators and decoupling strategies to ensure signal integrity and reduce noise.

Figure 3.1: Overview of the components in the system

## 3.2. Background information

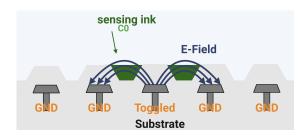

As introduced in Chapter 1, the e-nose system developed in this thesis employs a CMOS-based electrode array in which mutual capacitances are formed between adjacent electrodes. Each sense electrode in the array can be individually toggled, while the surrounding electrodes are held at ground potential to create localized capacitance measurements.

As illustrated in Figure 3.2, a sensing ink is deposited between the electrodes onto a self-assembled monolayer (SAM), which serves to improve the fluidic properties of the printed ink droplets prior to the drying or curing process. This structure defines the functional sensing region. The sensing ink, located between the electrode pins, functions as the dielectric medium and thereby determines the relative permittivity during capacitance measurements.

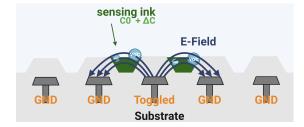

Figure 3.3 depicts the scenario in which Volatile Organic Compounds (VOCs) interact with the sensing ink. The absorption of VOC molecules alters the ink's relative permittivity  $\epsilon_r$ , which in turn changes the measured capacitance between the electrodes.

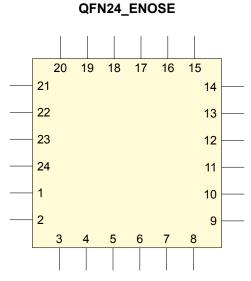

A detailed overview of the PCS chip pinout and corresponding functionality of each pin is provided in Appendix D.

Figure 3.2: The electrodes and sensing ink in the PCS array

Figure 3.3: The electrodes and sensing ink with VOCs in the PCS array

#### 3.2.1. SLICAP

In this report, circuit noise and transfer function analyses are primarily performed using **SLiCAP**, while circuit verification is conducted with LTspice. SLiCAP is a Python-based symbolic analysis tool that expresses circuit behavior such as transfer functions and noise contributions in terms of symbolic variables, rather than relying solely on fixed numerical values. This symbolic approach offers deeper insight into the circuit's parametric dependencies and relationships, enabling a more comprehensive understanding of its behavior. [2]

### 3.3. Sensor readout

In this chapter, the expected output characteristics of the PCS array are presented. Various circuit configurations for sensor readout are examined, with an emphasis on accurately detecting the dielectric changes in the sensing ink of the PCS array. Furthermore, the quantization requirements are discussed to ensure that these changes are captured with sufficient fidelity

#### 3.3.1. PCS output

To understand the design of the readout circuit, it is important to first clarify what type of signal is expected from the PCS array. This section outlines the assumptions made regarding the sensor's behavior and the resulting electrical characteristics of its output. These include the nature of the capacitive changes in the sensing ink of the PCS array and how these changes appear as measurable current at the readout interface.

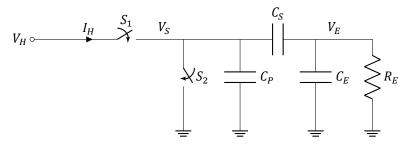

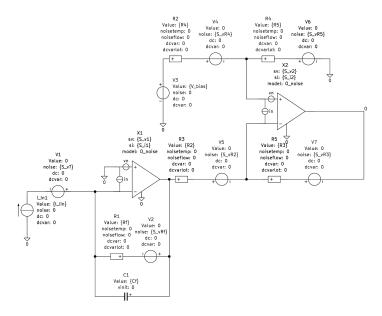

Figure 3.4: Equivalent circuit of a capacitive sensor pixel.

From previous research [3], it is known that a single pixel can be modeled by the equivalent circuit shown in Figure 3.4. Here,  $C_P$  is the parasitic capacitance, and  $C_S$  is the surface capacitance of a self-assembled monolayer (SAM) on the microectrode surface. The elements  $C_E$  and  $R_E$  represent the material in the passivation layer valleys, which can be either sensing ink or air. In the case of air,  $R_E = \infty$ . [4]

The value of  $C_E$  is influenced by the presence of specific VOCs, as absorption of these compounds changes the relative permittivity  $\varepsilon_r$  of the sensing ink, thus altering  $C_E$ .[5]

The switches  $S_1$  and  $S_2$  alternately toggle the sensing node voltage  $V_S$  between the input voltage  $V_H$  and ground, operating at a switching frequency  $f_S$ . When  $S_1$  is closed, the pixel connects to  $V_H$ , causing a charge build up and when  $S_2$  is closed, the pixel is grounded, and the accumulated charge is discharged.

Figure 3.5: Simplified equivalent circuit of a capacitive sensor pixel.

For  $f_s \gg \frac{1}{2C_E R_E}$ , the current through  $R_E$  becomes negligible [4]. Under this condition,  $C_S$  and  $C_E$  can be considered effectively in series and approximated by a single equivalent capacitance.

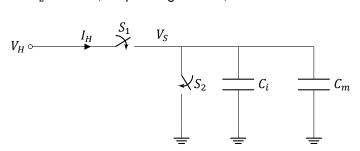

From this point onward, the baseline (VOC-independent) of the equivalent capacitance is grouped with the parasitic capacitance  $\mathcal{C}_P$  and denoted as  $\mathcal{C}_i$ , representing the intrinsic capacitance of the pixel. The VOC-dependent component is referred to as the measurement capacitance  $\mathcal{C}_m$ . The total capacitance  $\mathcal{C}_{\text{pixel}}$  at the sensing node is then defined as the sum of these two contributions. This simplified representation, as illustrated in Figure 3.5, will be used in the subsequent analysis of the pixel's electrical behavior.

Although a sensor pixel model has been established, many elements of the surrounding circuitry remain unspecified. At first glance, this may appear to be a significant limitation. However, upon closer analysis, it becomes evident that much of this complexity can be abstracted away under some assumptions.

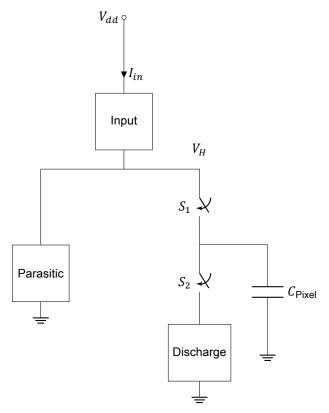

Figure 3.6: Capacitive sensor pixel with surrounding abstracted blocks for input, discharge, and parasitic network.

Assuming the pixel behaves purely as a capacitive load  $C_{\text{Pixel}}$ , and that the surrounding network can be abstracted by three simplified functional blocks: an input, a discharge, and a parasitic network, as illustrated in Figure 3.6. Despite these element blocks not being known at the circuit level, their influence on the behavior can be inferred by analyzing the charge balance of the system.

Figure 3.7: Charge flow representation .

From a charge flow perspective, the system can be represented as shown in Figure 3.7. All incoming charge must pass through the input network. Subsequently, part of this charge is dissipated through the parasitic path, while the remainder flows into the capacitor and discharge network.

Assuming that charge loss through the parasitic network is negligible, nearly all of the transferred charge is eventually accumulated in the capacitor  $C_{\text{Pixel}}$ . In this idealized case, the system behaves like a sequential pipeline, all charge stored in the capacitor must have passed through the input network and will subsequently pass through the discharge network. This unidirectional flow implies that analyzing any one stage provides insight into the charge behavior across the entire system within the same cycle.

If the capacitor is completely discharged during the discharge phase, then the total transferred charge is given by:

$$Q = C \cdot V_{\text{discharge}} \tag{3.1}$$

Where  $V_{\text{discharge}}$  corresponds to the capacitor  $C_{\text{Pixel}}$  voltage  $V_S$  immediately before switch  $S_2$  is toggled.

Since the charge flow of the capacitor is effectively in series with the rest of the functional blocks, this same amount of charge must pass through the preceding input network during that cycle. Resulting in that, under steady-state operation at a switching frequency  $f_s$ , the average input current can be expressed as:

$$I_{\text{avg}} = C_{\text{pixel}} \cdot V_{\text{discharge}} \cdot f_{s} \tag{3.2}$$

The input network includes an additional current mirror that amplifies this current, producing an output current with a gain factor  $G_{\text{current mirror}}$ . Therefore, for an enabled PCS array operating in steady state under a fixed differential clock, the average output current is assumed to be:

$$I_{\text{output}} = G_{\text{current mirror}} \cdot C_{\text{pixel}} \cdot V_{\text{discharge}} \cdot f_{\text{s}}$$

(3.3)

This relationship establishes the expected output characteristics of the pixilated capacitive sensor array and forms the basis for the design of the sensor readout circuitry.

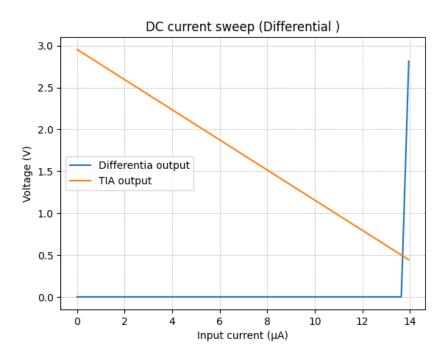

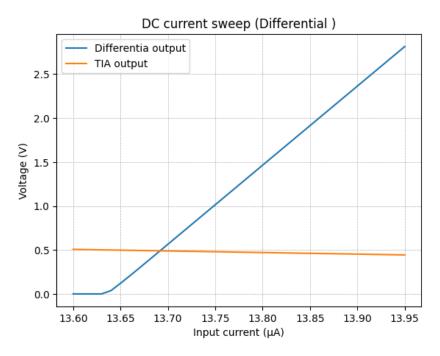

For the PCS array used, the current mirror has a gain factor  $G_{\text{current mirror}}$  of 100, the discharge voltage  $V_{\text{discharge}}$  is approximately 0.9 V, and the intrinsic pixel capacitance is  $C_i = 3.8$  fF [5]. The added measurement capacitance  $C_m$  varies in the range of 3.2 aF to 64 aF [5]. To ensure robustness in the readout design, a margin is applied, extending the effective upper bound of  $C_m$  to 75 aF.

Applying the derived equation 3.3 with these parameter values, the expected output current can be estimated for the intrinsic, minimal and maximum measurement current based on the frequency used. Table 3.1 summarizes the resulting output currents for the operating frequencies  $f_s$ : 40 MHz (matching the preceding board), 1 MHz, and 100 MHz.

| Frequency (MHz) | Pixel capacitance      | Output Current (A)       |

|-----------------|------------------------|--------------------------|

| 40              | $C_i = 3.8 \text{ fF}$ | $13.67 \times 10^{-6}$   |

| 40              | $C_i + 3.2 \text{ aF}$ | $13.69 \times 10^{-6}$   |

| 40              | $C_i + 75 \text{ aF}$  | $13.95 \times 10^{-6}$   |

| 1               | $C_i$                  | $3.42 \times 10^{-7}$    |

| 1               | $C_i + 3.2 \text{ aF}$ | $3.42288 \times 10^{-7}$ |

| 1               | $C_i + 75 \text{ aF}$  | $3.4875 \times 10^{-7}$  |

| 100             | $C_i$                  | $3.42 \times 10^{-5}$    |

| 100             | $C_i + 3.2 \text{ aF}$ | $3.42288 \times 10^{-5}$ |

| 100             | $C_i + 75 \text{ aF}$  | $3.4875 \times 10^{-5}$  |

Table 3.1: Estimated output current across frequency and capacitance ranges

#### 3.3.2. Sensor readout considerations

Building on the expected sensor output previously defined, this section examines the design considerations for the readout circuitry. This involves proper signal conversion and amplification before the sampling stage.

A critical consideration is that the ADC selection range for voltage signals is significantly wider than for current, therefore it is advantageous to convert current into voltage prior to sampling. This conversion can be described using the transformation matrix T1 notation [6], with two practical implementations:

A Current Integrator:

$$\begin{bmatrix} V_i \\ I_i \end{bmatrix} = \begin{bmatrix} 0 & 0 \\ \frac{S}{G_{\text{integrator}}} & 0 \end{bmatrix} \cdot \begin{bmatrix} V_o \\ I_o \end{bmatrix}$$

(3.4)

Configuration A corresponds to an integrator that accumulates input current over each sampling period and is then reset at the end of the cycle. The integration period is not limited to a clock cycle; it can span multiple clock cycles. This due to the fact that each pixel will be enabled for more than one clock cycle to reach a steady-state current [5]. Once the integrated charge is obtained, the microcontroller (MCU) can divide it by the integration period to determine the average current during that period.

**B** Transimpedance Amplifier:

$$\begin{bmatrix} V_i \\ I_i \end{bmatrix} = \begin{bmatrix} 0 & 0 \\ \frac{1}{G_{\text{TIA}}} & 0 \end{bmatrix} \cdot \begin{bmatrix} V_o \\ I_o \end{bmatrix}$$

(3.5)

While the integrator facilitates the measurement of total accumulated charge, configuration B - based on a standard transimpedance amplifier (TIA), may be sufficient when the input current remains relatively constant during the sampling interval. Furthermore, implementing an integrator presents certain practical challenges. Specifically, below its cutoff frequency, the integrator begins to behave as a highgain TIA due to the large value of the feedback resistor. As a result, for low-frequency input signals, the integrator output will quickly clip.

It is observed that the output signal operates closer to a near-DC signal [5], which makes Configuration B, the simple transimpedance amplifier, the more suitable choice. The transimpedance gain  $G_{TIA}$  is selected to convert the expected input current range into a voltage that maximally utilizes the allowable output swing of the readout circuit, thereby maximizing the usable input range for the ADC.

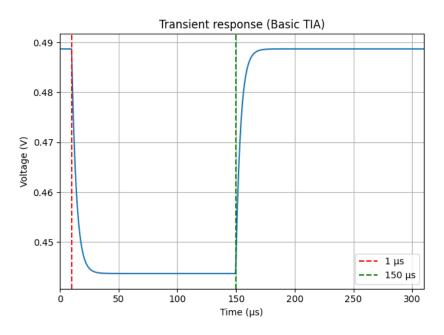

Since the array sequentially switches between pixels during readout, each pixel remains active for a fixed duration before advancing to the next one. During this interval, the signal output is effectively constant, producing a piecewise-constant waveform that exhibits jumps at fixed time intervals. Although each segment exhibits near-DC behavior while a pixel is active, the transitions between pixels introduce higher-frequency components into the overall waveform.

To preserve the integrity of each pixel's response, the transimpedance amplifier (TIA) must have sufficient bandwidth to accurately reproduce this stepwise behavior. Specifically, the TIA bandwidth is chosen to be:

$$f_{\rm BW} = \frac{N}{T_{\rm pixel}} \tag{3.6}$$

Where  $T_{\rm pixel}$  is the duration each pixel is active, and N is the number of harmonics to retain. In this case N=5, which is sufficient to preserve the first 3 harmonics of the signal, assuming a square wave. This choice strikes a balance between capturing sharp transitions and limiting noise amplification.

The pixel activation duration  $T_{\rm pixel}=150\,\mu{\rm s}$  is inherited from the preceding board design and is assumed fixed throughout the analysis. Based on this timing and the harmonic requirement, the corresponding minimum bandwidth requirement for the TIA is determined. Table 3.2 summarizes these design considerations, which form the basis for the specification of the read out circuit.

Table 3.2: Readout Circuit considerations

|                    | Description                                         |           |

|--------------------|-----------------------------------------------------|-----------|

| Readout Circuit    | Final readout architecture selected based on signal | TIA       |

|                    | behavior                                            |           |

| T <sub>pixel</sub> | Pixel activation duration (sampling period)         | 150 μs    |

| N                  | Number of harmonics retained                        | 5         |

| $f_{BW}$           | Minimum required bandwidth for TIA                  | 33.33 kHz |

### 3.3.3. Quantization and noise budget

While it may initially appear premature to address quantization before completing the sensor readout circuitry, this section focuses on defining the quantization specifications. These specifications will also establish the corresponding noise budget, which will subsequently be back-propagated to inform the design of the readout circuit.

#### Quantization

To define the ADC requirements for the system, two measurement strategies are evaluated: one that considers the full pixel capacitance, and another that isolates the dynamic component. These approaches determine both the minimum number of bits required for quantization and the associated noise constraints imposed on the sensor readout circuit.

The two strategies are defined as follows:

- Full-range measurement: accounts for the total capacitance observed at the pixel, comprising the intrinsic pixel capacitance  $C_i$  and the variable measurement capacitance  $C_m$ .

- **Differential measurement**: isolates only the variable component  $C_m$ , assuming the intrinsic part  $C_i$  can be suppressed through techniques such as biasing or subtraction. Signal amplification may be applied afterward to restore usable dynamic range.

What makes the differential approach particularly compelling in this context is that the intrinsic capacitance causes a current three orders of magnitude larger than that caused by the measurement variation. As a result, when measuring the full range, a significant portion of the ADC resolution is consumed in representing a known quantity, effectively reducing the sensitivity to changes in  $C_m$ . For both strategies the target resolution is set to 1 aF, corresponding to the change in  $C_i$  being in the aF range.

To determine the number of ADC bits required to achieve this resolution, the same methodological procedure is applied to both measurement strategies. The voltage range of the ADC is translated into an equivalent measurable capacitance range, from which the bit depth needed to meet the resolution criterion can be calculated.

The measurable voltage range is first derived from the available ADC input range. Both the readout circuit and the ADC are supplied by a 3.3 V source. However, due to practical limitations, the output of the readout circuit and the ADC input range is limited by the supply voltage. In particular, the readout output voltage is expected to clip below the ADC's maximum input, resulting in a region of unused ADC range.

This unexploited headroom is expressed as:

$$V_{\text{unused}} = V_{\text{ADC.max}} - V_{\text{readout.max}}$$

(3.7)

This unused margin reduces the effective signal swing at the ADC input. To express this in terms of measurable capacitance, an equivalent capacitance  $\mathcal{C}_{\text{headroom}}$  is computed based on the inverse of the expected output current of the PCS array 3.3 and the overall gain of the TIA:

$$C_{\text{headroom}} = \frac{V_{\text{unused}}}{G_{\text{TIA}} \cdot G_{\text{mirror}} \cdot V_{\text{discharge}} \cdot f_s}$$

(3.8)

Accordingly, the measurable capacitance range for each strategy is defined as:

$$C_{\mathrm{full}} = C_i + C_{m,\mathrm{max}} + C_{\mathrm{headroom}}$$

$$C_{\mathrm{diff}} = C_{m,\mathrm{max}} + C_{\mathrm{headroom}}$$

The number of ADC bits required to meet the resolution target of 1 aF is then calculated as:

$$Bits_{ADC} = \left[ log_2 \left( \frac{C_{range}}{1 \text{ aF}} \right) \right]$$

(3.9)

#### Noise budget

Once the quantization resolution has been determined, it indirectly translates this into a noise budget for the sensor readout circuit. Additional noise introduced by the ADC itself is not included but would further tighten the noise budget in a practical implementation. The guiding principle for defining the noise budget is that the signal-to-noise ratio (SNR) must exceed the quantization noise floor; otherwise, the additional resolution provided by the ADC is effectively lost. Consequently, a minimum SNR must be maintained at the output of the readout circuit that exceeds the SNR caused by quantization.

The corresponding signal-to-noise ratio (SNR) resulting from quantization is then determined by:

$$SNR_{quant} = 6.02 \cdot Bits_{ADC}$$

(3.10)

To ensure a sufficient noise margin, an additional 3 dB is added:

$$SNR_{in} = SNR_{quant} + 3 dB (3.11)$$

Since SNR is a dimensionless ratio, it must be expressed as a physical RMS voltage in order to define a more concrete noise constraints for the readout circuit. This requires establishing the expected signal power at the output. As the output signal is originally defined as a DC current, it is converted to a voltage through a transimpedance gain  $G_{\text{TIA}}$ . Based on the signal voltage and the required input SNR, the corresponding maximum permissible RMS noise voltage at the readout output is:

$$V_{\text{noise,rms}} = \frac{G_{\text{TIA}} \cdot I_{\text{signal}}}{10^{\text{SNR}_{\text{in}}/20}}$$

(3.12)

Assuming that the ADC input range extends close to its supply voltage of 3.3 V, and that the sensor readout circuit clips approximately 0.3 V below this limit, and the resulting headroom. Using the previously established current level at 40 MHz, the corresponding noise budget results are calculated and summarized in table 3.3 .

| Table 3.3: ADC noise and re | esolution specifications |

|-----------------------------|--------------------------|

|-----------------------------|--------------------------|

|                           | Description                                             | Value                           |

|---------------------------|---------------------------------------------------------|---------------------------------|

| $Resolution_{C}$          | Desired resolution                                      | 1 aF                            |

| $Bits_{diff\_C}$          | Required ADC resolution if only the differential $C$ is | 9 bits                          |

|                           | measured                                                |                                 |

| $Bits_{full\_C}$          | Required ADC resolution if full range of C is mea-      | 13 bits                         |

|                           | sured                                                   |                                 |

| $SNR_{Quant\_diff}$       | Quantization SNR for differential C                     | 54.18 dB                        |

| SNR <sub>Quant full</sub> | Quantization SNR for full C                             | 78.25 dB                        |

| $SNR_{In\_diff}$          | Required input SNR for differential $\mathcal C$        | 57.18 dB                        |

| $SNR_{In\ full}$          | Required input SNR for full C                           | 81.25 dB                        |

| $V_{rms\_diff}$           | Max RMS noise voltage at output for differential C      | $1 \cdot 10^{-2} \text{ V}$     |

| $V_{rms\_full}$           | Max RMS noise voltage at output for full C              | $630.5 \cdot 10^{-6} \text{ V}$ |

Having defined the current ranges, bandwidth requirements and established noise constraints, the design of the transimpedance amplifier can now proceed based on these specifications and design budgets. To ensure that the resulting design meets all performance targets, validation will be performed primarily using SLiCAP [2].

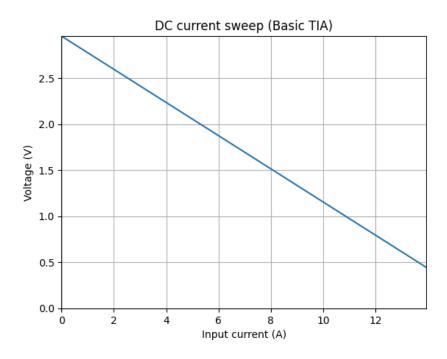

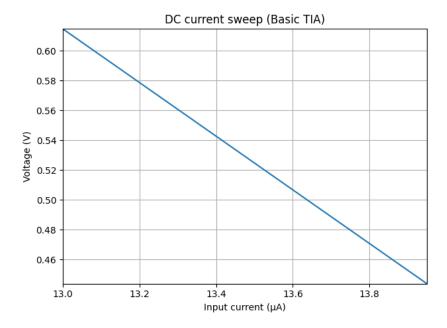

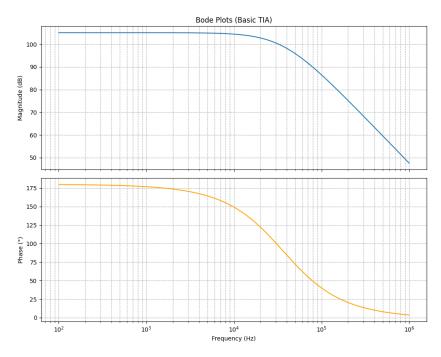

#### 3.3.4. Basic Tia

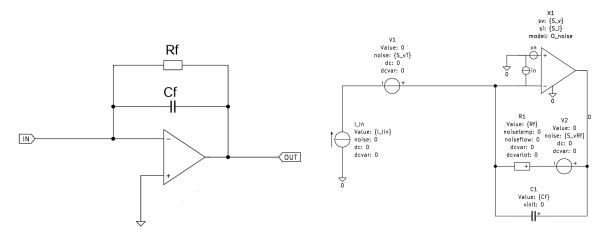

Figure 3.8: Basic Tia schematic

Figure 3.9: Basic Tia noise model

When implementing a basic transimpedance amplifier (TIA), as illustrated in Figure 3.8, the feedback network consists of a resistor  $R_f$  in parallel with a capacitor  $C_f$ . The transfer function describing the conversion from input current to output voltage is given by:

$$H(f) = \frac{-R_f}{1 + j\omega R_f C_f} \tag{3.13}$$

Given the target transimpedance gain  $G_{\mathsf{TIA}}$ , the feedback resistor  $R_f$  is selected to match this gain. The feedback capacitor  $C_f$  is then chosen such that the  $-3\,\mathrm{dB}$  point of the transfer function aligns with the defined bandwidth :

$$C_f = \frac{1}{2\pi R_f f_{\text{bw}}} \tag{3.14}$$

Since the TIA provides a negative gain and the readout circuit operates from a single  $3.3\,\mathrm{V}$  supply without a negative rail, the operational amplifier must be properly biased. Given that only positive input currents are expected and full-range utilization is desired, the amplifier is biased near the upper rail. Letting  $V_{\mathrm{bias}}$  denote the non-inverting input bias voltage, chosen with sufficient headroom below the supply voltage to prevent clipping, the amplifier is biased accordingly. For input currents within the bandwidth of the TIA, the corresponding output voltage is given by:

$$V_{\text{out}} = V_{\text{bias}} - R_f \cdot I_{\text{in}} \tag{3.15}$$

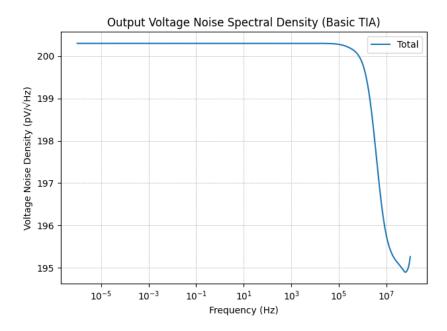

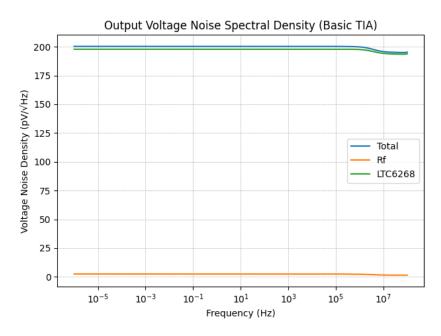

To evaluate the noise performance of this configuration, a symbolic noise model as shown in Figure 3.9 is constructed and analyzed. The model captures the individual contributions of each circuit component to the total output noise voltage. Using the calculated values for  $R_f$  and  $C_f$ , the total output-referred noise is expressed as:

$$V_{\text{oNoise}} = 3.132 \cdot 10^7 \left( S_i + 3.399 \cdot 10^{-11} S_v + 2.669 \cdot 10^{-11} S_{vR_f} + S_{vT} \right)^{0.5}$$

(3.16)

By selectively enabling individual noise sources within the model, their isolated contributions to the total output noise can be independently evaluated. Comparing each of these with the specified noise constraint  $V_{\rm rms\_full}$  allows the determination of upper limits for each source. The bounds represent the threshold at which a single noise contributor alone would cause the output noise to exceed the permissible limit.

For the input-referred noise at the output, the equivalent noise bandwidth  $B_{\rm eq}$  of the TIA is computed:

$$B_{\text{eq}} = \frac{\int_0^\infty |H(f)|^2 df}{|H(0)|^2}$$

(3.17)

Based on the voltage noise constraint  $V_{\rm rms\ full}$ , the input noise limit is calculated as:

$$S_{i,\text{max}} = \frac{V_{\text{rms\_full}^2}}{B_{\text{eq}}}$$

(3.18)

To select a suitable operational amplifier, noise specifications alone are insufficient, specifications such as the minimum slew rate and gain-bandwidth product (GBW) are considered. For the slew rate, the maximum expected voltage change at the TIA output corresponds to the difference between the peak input current and the intrinsic baseline current, scaled by the transimpedance gain.

The voltage transition resulting from a measurement must settle quickly enough to ensure accurate readout. However, since the TIA acts as a low-pass filter, its response is inherently delayed. It is therefore not meaningful to require a transition faster than the circuit's natural response. A practical settling time is approximated as  $5\tau$ , where  $\tau=R_f\cdot C_f$ . Within this time frame, the output should transition from maximum to minimum voltage. Accordingly, the minimum required slew rate  $SR_{min}$  is defined as:

$$SR_{min} > \frac{G_{TIA} \cdot (I_{max} - I_{intrinsic})}{5 \cdot R_f \cdot C_f}$$

(3.19)

To estimate the minimum required gain-bandwidth product (GBW) for the transimpedance amplifier, the following expression is used [7]:

$$GBW > \frac{C_i + C_f}{2\pi \cdot R_1 \cdot C_f^2} \tag{3.20}$$

where  $C_i = C_S + C_d + C_{cm}$ , with:

- C<sub>S</sub>: Input source capacitance

- C<sub>d</sub>: Differential input capacitance of the op-amp

- $C_{cm}$ : Common-mode input capacitance of the inverting input

Since the op-amp has not yet been selected, and the input source capacitance is unspecified, the exact value of  $C_i$  cannot be determined at this stage. To ensure sufficient design margin, a **conservative** estimate of  $C_i = 100 \, \text{pF}$  is assumed.

Given that the measurement currents in the TIA are in the microampere range, the input bias current of the operational amplifier is a critical design consideration. Excessive bias current can significantly distort the measured signal, making accurate readout infeasible. To ensure measurement accuracy, the input bias current is chosen to be at least three orders of magnitude smaller than the input current, i.e., less than  $10^{-3} \cdot I_{\text{in}}$ .

Using the previously defined specifications, the necessary component values and corresponding noise limits have been derived. These results provide a basis for further implementation and validation. A summary of the selected parameters and their permissible noise contributions for fs=40Mhz is presented in Table 3.4

| Symbol            | Description                             | Value                  | Units              |

|-------------------|-----------------------------------------|------------------------|--------------------|

| $C_f$             | Feedback capacitor                      | $24.66 \cdot 10^{-12}$ | F                  |

| $R_f$             | Feedback resistor                       | $193.5 \cdot 10^3$     | Ω                  |

| $f_{-3dB}$        | TIA bandwidth (-3 dB point)             | $33.33 \cdot 10^3$     | Hz                 |

| SR <sub>min</sub> | Minimal slew rate of the op-amp         | $2.253 \cdot 10^{-3}$  | V/μs               |

| GBW               | Minimal GBW rate of the op-amp          | 168.6                  | kHz                |

| $I_{Bias}$        | Minimal bias current of the op-amp      | $13.67 \times 10^{-9}$ | Α                  |

| $S_{i\max}$       | Maximum current noise opamp input       | $7.593 \cdot 10^{-12}$ | $A^2/Hz$           |

| $S_{vT\max}$      | Maximum voltage noise opamp input       | $18.91 \cdot 10^{-9}$  | V <sup>2</sup> /Hz |

| $S_{iT\max}$      | Maximum input current noise             | $12.04 \cdot 10^{-9}$  | $A^2/Hz$           |

| $S_{vR_f}$ max    | Maximum feedback resistor voltage noise | $24.08 \cdot 10^{-9}$  | V <sup>2</sup> /Hz |

| $S_{v\max}$       | Maximum input voltage noise             | $642.9 \cdot 10^{-21}$ | V <sup>2</sup> /Hz |

Table 3.4: Final TIA Design Specifications

#### 3.3.5. T-network

The feedback network of a transimpedance amplifier is not limited to the conventional parallel resistor-capacitor configuration discussed previously in section 3.3.4. An alternative implementation, based on a T-network topology, has been extensively considered and is recommended in application literature by Texas Instruments [8]. This topology is suggested to offer improved noise performance. Given that noise minimization is a critical design criterion for the TIA, the potential benefits of the T-network approach merit detailed consideration.

Figure 3.10: Tia implemented with a T-network circuit schematic

The premise of the T-network is that the amplifier's output is attenuated through a voltage divider before being applied to the original feedback path of a basic TIA, as can be seen in Figure 3.10. This configuration is intended to achieve the same gain using smaller resistors values, thereby reducing thermal noise. However, during evaluation, this premise didn't hold in practice. As a result, the T-network configuration was not selected for the final design. Thus only a brief overview is presented here, while a more detailed analysis, including a possible reason for this lack of improvement is provided in Appendix B.

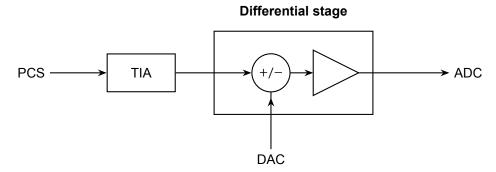

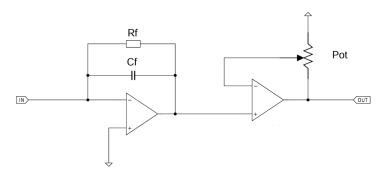

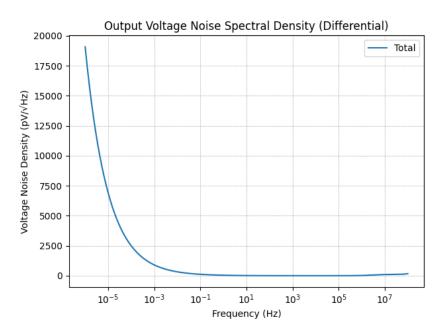

#### 3.3.6. Differential

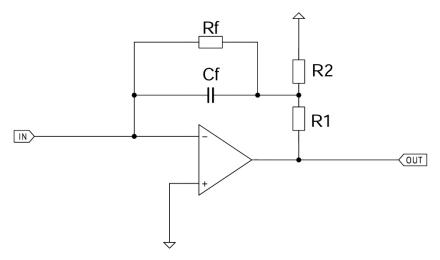

Focusing exclusively on measuring the change in capacitance induced by the presence of VOCs, presents multiple advantages for PCS array readout, which are discussed in detail in Section 3.3.3. Most notably, it eliminates the need to digitize the intrinsic, known baseline capacitance, thereby reducing the required resolution of the output ADC and increasing the permissible noise margin at its input. To realize this measurement approach, a differential stage is required, as illustrated in Figure 3.11.

Figure 3.11: Block diagram of differential stage implementation

The TIA stage remains unchanged; however, it's important to recall that it has a negative gain and is positively biased. As a result, the output voltage corresponding to the intrinsic current is higher than the voltage produced by a VOC-induced change. To isolate only the variation caused by VOCs, the TIA output is **subtracted** from a baseline voltage. This baseline is simply the output voltage of the TIA at intrinsic current conditions and is generated by a DAC to allow for fine-tuning. Approximately, the baseline voltage should be equal to:

$$V_{\text{DAC}} = -G_{\text{TIA}} \cdot (I_{\text{intrinsic}} - I_{\text{max}}) \tag{3.21}$$

However, this subtraction step alone does not improve the signal resolution. It merely inverts the signal around the baseline, without expanding the voltage range. Since the differential stage operates on a single supply, it cannot represent negative values. Current inputs below the intrinsic level create a TIA output voltage that is higher than the baseline voltage, therefore the differential output is clipped to zero. Conversely, when the current rises above the intrinsic level, the differential output increases, but will not exceed the original baseline voltage of the TIA. As a result, the measurable current variation remains constrained to the same limited portion of the ADC's range. Therefore, to enhance resolution, the output of the differential stage must be amplified so that the VOC-induced current variation spans a broader portion of the ADC's input range.

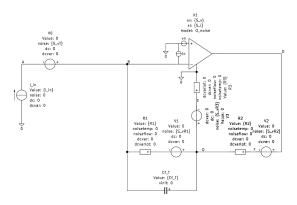

To implement the differential stage, a simple differential amplifier is added at the output of the TIA, as shown in Figure 3.12.

Figure 3.12: Basic TIA with differential stage schematic

With the inclusion of the differential stage, the output voltage is expressed as:

$$V_{\text{out}} = \frac{R_2}{R_1} \left( V_{\text{DAC}} - V_{\text{TIA}} \right)$$

(3.22)

Here, the ratio  $\frac{R_2}{R_1}$  defines the gain of the differential amplifier. To ensure that the full range of VOC-induced current variation is observed at the ADC, the differential stage required gain,  $g_{\text{diff}}$ , is determined as the ratio of the unused voltage range to the baseline voltage. This is expressed as

$$g_{\text{diff}} = \frac{V_{\text{readout,max}} - V_{\text{DAC}}}{V_{\text{DAC}}}$$

(3.23)

The selection of resistor values  $R_1$  and  $R_2$  requires careful consideration to balance loading effects and noise performance. If the resistance is too low, it may excessively load the amplifiers and the DAC. Conversely, excessively high resistance increases thermal noise.

The current drawn from the DAC can be approximated as  $I_{\rm DAC} = V_{\rm DAC}/(R_1 + R_2)$ . For the amplifiers, the worst-case loading scenario occurs when the TIA output is near 0 V. In this condition, the differential amplifier must source at least :

$$I_{\text{differential}} = \frac{V_{\text{DAC}} \cdot R2}{(R1 + R2)} \cdot \frac{1}{R1}$$

(3.24)

This arises because  $R_1$  and  $R_2$  form a voltage divider with  $V_{\rm DAC}$  applied to the non-inverting terminal of the amplifier. Since the op-amp maintains equal voltages at both terminals, its similar at the inverting terminal, which is connected to the near 0 V output of the TIA through  $R_1$ . For the op-amp in the TIA, it must sink this current in addition to the measurement current.

To minimize loading and limit thermal noise contributions, resistor values in the kilo-ohm range were selected. These values reflect practical trade-offs rather than detailed optimization. Specifically,  $R_1$  was chosen to be  $5~\mathrm{k}\Omega$ , and  $R_2$  was set to  $250~\mathrm{k}\Omega$ , which achieves the required gain for the differential stage.

The op-amp specifications for the TIA stage remain unchanged in this context. However, for the differential amplifier stage, the op-amp must be reconsidered. Since the voltage difference will now span the full output range, the minimum required slew rate is given by:

$$SR_{min} > \frac{V_{readout,max}}{5 \cdot R_f \cdot C_f}$$

(3.25)

To ensure stable operation across the intended bandwidth, the minimum required GBW of the op-amp in the differential stage is estimated by using the desired gain  $g_{\text{diff}}$  and the bandwidth  $f_{\text{BW}}$ :

$$GBW > g_{diff} \cdot f_{BW} \tag{3.26}$$

Figure 3.13: Basic TIA with differential stage schematic noise model

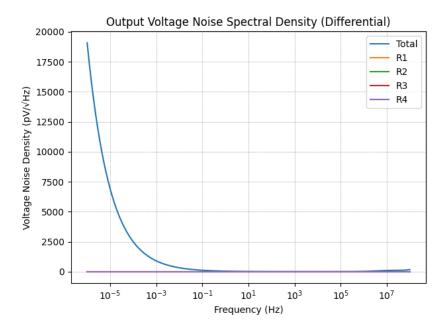

Following the same methodology outlined in Subsection 3.3.4, a corresponding noise model is made, as shown in Figure 3.13. In this case, the noise constraint is based on  $V_{\rm rms\_diff}$  rather than  $V_{\rm rms\_full}$  The resulting noise limits for each contributing source and parameters are summarized in table 3.5.

| Table 3.5: TIA with differential stages specifications | Table 3.5: | TIA with | differential | stages | specifications |

|--------------------------------------------------------|------------|----------|--------------|--------|----------------|

|--------------------------------------------------------|------------|----------|--------------|--------|----------------|

| Symbol              | Description                                    | Value                  | Units              |

|---------------------|------------------------------------------------|------------------------|--------------------|

| $C_f$               | Feedback capacitor                             | $24.66 \cdot 10^{-12}$ | F                  |

| $R_f$               | Feedback resistor                              | $193.5 \cdot 10^3$     | Ω                  |

| $R_1$               | R1                                             | $5\cdot 10^3$          | Ω                  |

| $R_2$               | R2                                             | $258.3 \cdot 10^3$     | Ω                  |

| $R_3$               | R3                                             | $5\cdot 10^3$          | Ω                  |

| $R_4$               | R4                                             | $258.3 \cdot 10^3$     | Ω                  |

| SR <sub>diff</sub>  | Minimal slew rate of the op-amp (differential) | 0.12                   | V/μs               |

| GBW <sub>diff</sub> | Minimal GBW rate of the op-amp (differential)  | 1.70                   | MHz                |

| SR <sub>TIA</sub>   | Minimal slew rate of the op-amp (TIA)          | $2.253 \cdot 10^{-3}$  | V/μs               |

| GBW <sub>TIA</sub>  | Minimal GBW rate of the op-amp (TIA)           | 168.6                  | kHz                |

| $I_{Bias}$          | Minimal bias current of the op-amp (TIA)       | $13.67 \times 10^{-9}$ | A                  |

| $S_{i1max}$         | Maximum current noise opamp 1                  | $107.7 \cdot 10^{-21}$ | $A^2/Hz$           |

| $S_{i2max}$         | Maximum current noise opamp 2                  | $44.04 \cdot 10^{-21}$ | $A^2/Hz$           |

| $S_{v1max}$         | Maximum voltage noise opamp 1                  | $3.171 \cdot 10^{-9}$  | $V^2/Hz$           |

| $S_{v2max}$         | Maximum voltage noise opamp 2                  | $1.100 \cdot 10^{-12}$ | $V^2/Hz$           |

| $S_{vR2max}$        | Maximum noise of R2                            | $3.171 \cdot 10^{-9}$  | $V^2/Hz$           |

| $S_{vR3max}$        | Maximum noise of R3                            | $8.465 \cdot 10^{-6}$  | $V^2/Hz$           |

| $S_{vR4max}$        | Maximum noise of R4                            | $1.143 \cdot 10^{-12}$ | $V^2/Hz$           |

| $S_{vR5max}$        | Maximum noise of R5                            | $3.051 \cdot 10^{-9}$  | $V^2/Hz$           |

| $S_{vR_f \max}$     | Maximum feedback resistor noise                | $4.037 \cdot 10^{-9}$  | V <sup>2</sup> /Hz |

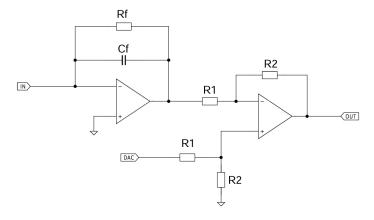

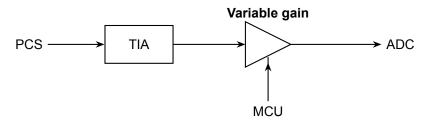

#### 3.3.7. Variable gain

As outlined in requirement **[ToR.1.1]**, it is desirable to develop a readout circuit capable of operating across a range of clock frequencies, specifically from 1 MHz to 100 MHz, rather than being limited to a fixed frequency. To accommodate this variability, a configurable gain is required. As shown in section 3.3, the average output current is linearly dependent on the clock frequency. Consequently, operating across this frequency span implies a change in output current by a factor of up to 100.

To address this, the proposed architecture consists of a TIA followed by a variable-gain amplification stage which is controlled by the MCU, as illustrated in Figure 3.14.

Figure 3.14: Block diagram of variable gain implementation

The implemented circuit consists of a TIA , with  $R_f$  and  $\mathcal{C}_f$  selected to an input current corresponding to a  $f_s$  of 100 MHz, following the same design methodology outlined in Section 3.3.4. The output of the TIA is connected to a non-inverting amplifier stage, where the gain is set by a feedback network incorporating a potentiometer, as shown in Figure 3.15. To enable gain control by the MCU, a digital potentiometer is employed instead of a conventional one.

Figure 3.15: Basic TIA with variable stage schematic

Because a digital potentiometer is more complex than a simple resistor pair with a center tap, modeling it in this way would be an oversimplification. As a result, simulation was deemed impractical, and the selection focused instead on digital pots whose datasheet specifies low output noise voltage and adequate bandwidth.

3.4. Power 21

### 3.4. Power

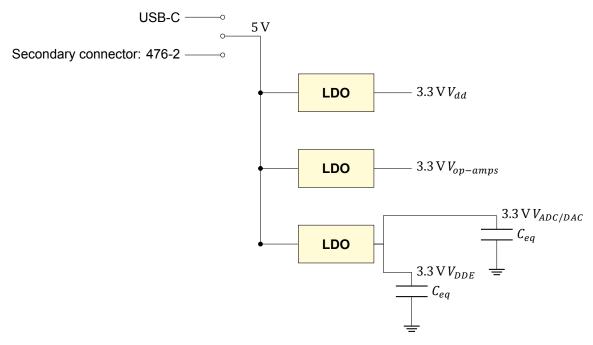

To enable full-system functionality, a consistent power distribution approach was implemented for the Main PCB. Unlike the previous revision, which employed multiple supply rails, this design uses a single voltage level of  $3.3\,\mathrm{V}$  across the entire board. This decision was made to simplify the design and layout, and because the MCXN947 microcontroller **[MR.2.4]** operates natively at  $3.3\,\mathrm{V}$ . Consequently, all other components were selected to be compatible with this voltage.

The following subsections detail the power requirements for each major circuit block, beginning with the MCU, and followed by the PCS chip and the readout circuit. The user interface (UI) components are excluded from this discussion, as they operate directly from the 3.3 V rail without any special requirements.

To ensure stable and noise-free power delivery, each component is equipped with dedicated decoupling capacitors. These capacitors serve to suppress electromagnetic interference (EMI) from the surrounding environment and to buffer against transient voltage drops caused by dynamic load changes. For the components discussed in the sections below, the specific values and placement strategies of their associated decoupling capacitors will also be addressed. In addition to the use of decoupling capacitors, ferrite beads were employed to suppress high-frequency noise above 25 kHz. Without such filtering, this noise could propagate through the power distribution network and potentially interfere with sensitive components, such as the reference sources of ADCs, thereby degrading their performance [9].

The value of decoupling capacitors was, where feasible, estimated using the guideline provided in [10, Ch. 6.1, p. 244]:

$$C = I_{\text{peak}} \cdot \frac{t}{V_{\text{droop\_max}}} \tag{3.27}$$

where  $I_{\rm peak}$  is the estimated peak current, t is the duration of the transient, and  $V_{\rm droop\_max}$  is the maximum allowable voltage droop. However, as noted in [10, Ch. 6.1], this formula serves only as a rough approximation, since the involved parameters are often imprecisely known and rather vague the capacitor value is therefore not highly critical.

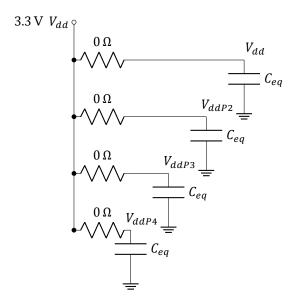

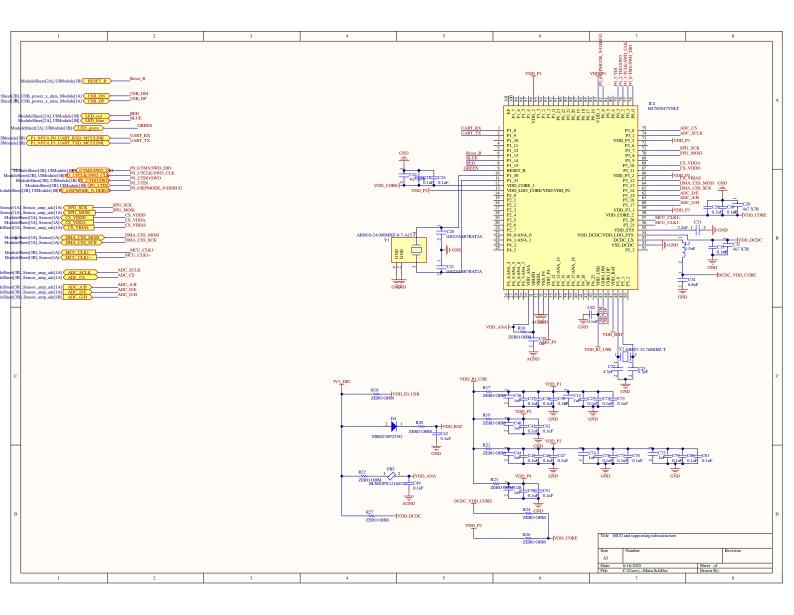

#### 3.4.1. MCU PWR

The microcontroller unit (MCU) is a digitally intensive component that features multiple independent voltage domains, including a system domain ( $V_{dd\_SYS}$ ), a core domain ( $V_{dd\_CORE}$ ), and per-port I/O domains ( $V_{dd}$ ,  $V_{dd\_P2}$ – $V_{dd\_P4}$ , corresponding to Port 1, Port 2 - Port 4). To simplify the power distribution the the port domains while maintaining flexibility, the design uses a single regulated 3.3 V rail that is split into the required voltage domains through removable 0  $\Omega$  resistors as can be seen in Fig.3.16. This approach allows for easy rerouting or isolation of power domains during testing or debugging. On the current version of the PCB, most GPIO pins have been routed to the Port 3 domain. Therefore (this will be discussed later in 3.7),  $V_{dd\_P3}$  must be powered.

Per the datasheet [11], the  $V_{dd\_SYS}$  domain must always be supplied as it powers essential subsystems such as internal regulators and the power-on-reset circuitry.  $V_{dd\_CORE}$  is typically powered via an on-chip LDO or DCDC converter derived from  $V_{dd\_SYS}$ . Additionally, there are  $V_{bat}$  and  $V_{dd\_ANA}$  pins, which have been connected to the power rail according to the datasheet [11].

To ensure signal integrity and suppress transient noise on the digital power domains, each supply pin is locally decoupled with ceramic capacitors. Proper placement of these decoupling capacitors is critical to minimize power distribution network (PDN). As discussed in [12], the effectiveness of decoupling relies not only on the capacitor value but also on the via placement and the return current path in multilayer PCBs. The implemented layout adheres to these guidelines by placing capacitors as close as possible to the supply pins and using short traces to ground. The decoupling capacitor are also added to the Power distribution network of the MCU in Fig.3.16. Please note that  $C_{eq}$  represents multiple capacitors. In the final design, three  $0.1\,\mu\text{F}$  and a single  $1\,\mu\text{F}$  caps were used as per the schematic of the FRDM-MCXN947 development board [13].

#### 3.4.2. PCS chip PWR

The PCS chip features three distinct power supply inputs: VDDE, VDDD, and VDDA. The analog domains VDDD and VDDA operate nominally at 1.1 V. To enable crosstalk characterization, VDDA and VDDD are

3.4. Power 22

Figure 3.16: Power distribution MCU

supplied by adjustable power sources, permitting fine voltage adjustments (e.g.,  $\pm 25\,\mathrm{mV}$ ) around the nominal  $1.1\,\mathrm{V}$  level. This allows for the evaluation of crosstalk effects from VDDA to the output current, as well as for tuning VDDD to mitigate timing issues, albeit at the expense of accelerated degradation. In contrast, VDDE operates at a nominal voltage of  $3.3\,\mathrm{V}$  and is directly powered by a low-noise Linear Dropout Regulator (LDO) with additional decoupling capacitors.

As previously discussed, the PCS chip is a highly sensitive analog component and particularly susceptible to power supply noise. As noted by F. Widdershoven, "variations on VDDA are expected to transfer almost 1:1 to the sensor's cell voltage and, therefore, to the sense current" (F. Widdershoven, personal communication, June 3, 2025). According to Requirement [MR.2.11], the noise originating from the readout circuit must not exceed four quantization steps of the ADC. Since the noise is limited to 4 bits, dithering techniques can be applied to recover the signal.

Using Python in combination with SLICAP (Symbolic Linear Circuit Analysis Program), the noise corresponding to these four quantization steps was back-propagated to the output of the PCS chip. This analysis yielded a maximum total noise power spectral density of  $7.104 \times 10^{-19}~V^2~Hz^{-1}$  at the output of the current mirror. Taking the square root of this value results in a noise voltage spectral density of  $0.843~\text{nV}/\sqrt{\text{Hz}}$ . Since the intrinsic noise contribution of the chip itself is unknown, the voltage variations at the input should remain well below this threshold. It should be noted, however, that this analysis does not include possible 1/f noise contributions of the PCS chip or surrounding circuitry. Given the potentially significant impact of low-frequency noise on high-resolution measurements, incorporating 1/f noise into the noise budget analysis would be a valuable extension for future work.

To support software-controlled regulation of the VDDA and VDDD supplies, Digital-to-Analog Converters (DACs) are employed. However, identifying DACs with sufficiently low noise proved challenging. In scenarios where cost and board area are less restrictive, the AD5791, a 20-bit DAC, offers a promising (but not complete) solution, with a noise spectral density of  $7.5\,\mathrm{nV}/\mathrm{\overline{Hz}}$  [14]. However, given that this project serves as a prototyping platform for academic research and must remain low-cost to allow for free distribution to external collaborators, the use of such a high-end DAC is not feasible.

More affordable DACs typically exhibit noise spectral densities in the range of  $100-200~\rm nV/\sqrt{\rm Hz}$ . To minimize design risk and ensure consistency, the DAC previously used in the board designed by T. Shen was reused. This DAC has a typical noise spectral density of approximately  $120~\rm nV/\sqrt{\rm Hz}$  [15], exceeding the calculated noise budget by a factor of roughly 150.

To mitigate this, several noise-reduction techniques can be applied:

• Low-frequency and 1/f noise: On the software side, correlated double sampling can be used.

3.4. Power 23

This technique leverages the slowly varying nature of low-frequency noise. By acquiring two measurements, one from the target pixel and one from a reference pixel, and subtracting them in post-processing, the common-mode noise component is effectively canceled, preserving only the differential signal.

• **High-frequency noise:** A dedicated RC low-pass filter is included in the final PCB design to suppress high-frequency noise components in hardware. The exact cutoff frequency of this filter is still to be determined but can be chosen relatively low, as crosstalk measurements between VDDA and the sense current will not be conducted at high frequencies.

For the VDDE supply, where little is known about the propagation of noise into the readout circuit, an LDO was selected as a precautionary measure. Although LDOs are generally less energy efficient than switching regulators, they offer superior noise performance [16].

For instance, while typical peak-to-peak noise levels for buck converters can reach  $20\,\mathrm{mV}$  [17], the ADPL4050 LDO selected for the final PCB exhibits an output noise of only  $20\,\mu\mathrm{V}_{\mathrm{rms}}.$  This corresponds to approximately  $132\,\mu\mathrm{V}$  peak-to-peak at a 99.9% confidence level, based on the statistical scaling of Gaussian noise described in Chapter 7 of [18]. To further reduce noise, additional decoupling capacitors are included at the input of the PCS chip.

## 3.4.3. Readout circuit PWR

The readout circuit is designed such that the operational amplifiers operate at 3.3 V and do not require rail-to-rail voltage. This design choice significantly simplifies the power supply architecture. In addition to the amplifiers, the only other active components in the analog signal path are the three ADCs corresponding to the three sensor arrays.

Given that these components operate on sensitive analog signals, a clean and stable reference or supply voltage is critical. As noted in [19], "any noise greater than 1/2 Least Significant Bit (LSB) in amplitude has some effect upon the converter noise performance. This effect is proportional to the input voltage level." Since  $1\,\mathrm{LSB} = 403\,\mu\mathrm{V}$ , the maximum permissible RMS noise on the ADC power supply is  $201.5\,\mu\mathrm{V}$ .

Consequently, switch-mode power supplies are unsuitable due to their typically higher noise levels [16]. A low dropout regulator (LDO) is therefore required. The ADPL40502 was selected for this purpose, as it provides an RMS output noise of only 20 µV [20], well below the specified limit.

A separate DAC of the same type as that used for the PCS power rails is employed to generate the bias voltage for the operational amplifiers.

To further reduce potential interference between analog subsystems, the final design employs two separate LDOs: one dedicated to the ADCs and DACs, and another exclusively for the operational amplifiers.

#### 3.4.4. Complete system

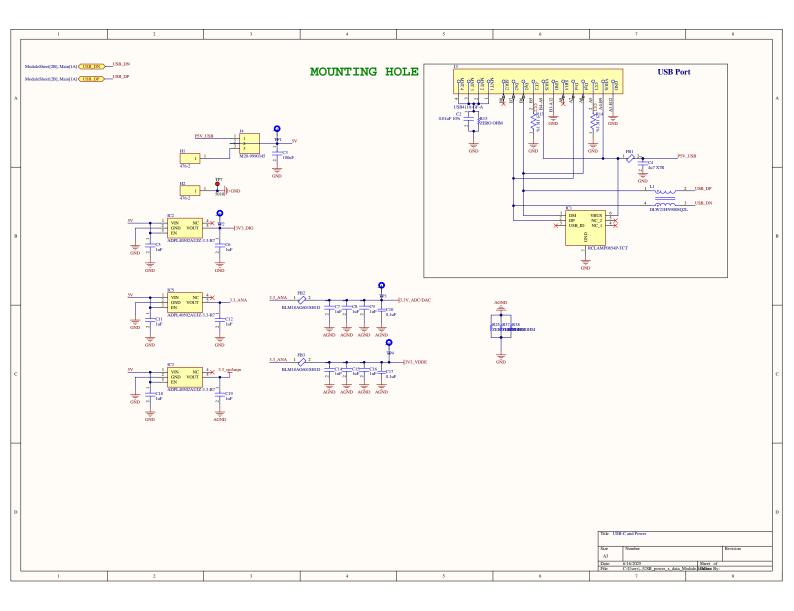

As specified in Requirement **[ToR.2.2]**, a second power input was added alongside a USB-C connector. The user can select the active 5 V power source by configuring a header jumper.

The secondary power connector is intended to be a commonly used type with a minimal footprint to conserve board space. Currently, a Keystone 476-2 connector has been selected. However, alternative connectors with smaller footprints are under consideration to further optimize the layout.

A complete overview of the power delivery system is provided in Fig. 3.17. It should be noted that the symbols  $C_{eq}$  represent the combined decoupling capacitor network at each supply node.

3.5. Grounding

Figure 3.17: Power system overview

# 3.5. Grounding

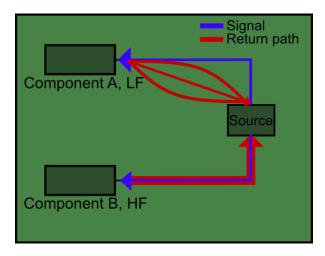

With all components now powered, it is essential to establish well-defined return current paths. Following the recommendation by Park [21], the grounding system is divided into two distinct domains: Analog Ground (AGND) and Digital Ground (DGND). This separation helps to isolate digital switching noise from sensitive analog circuitry, thereby enhancing overall signal integrity. Components are assigned to one of the two domains based on guidance provided in their respective datasheets.

For components that feature both AGND and DGND pins (e.g., the PCS chip), Zumbahlen [18], in Chapter 12, recommends connecting these pins externally and routing both to the analog ground (AGND) plane. This approach minimizes the risk of ground loops and supports the maintenance of a low-noise environment.

The practical implementation of these ground planes is described in more detail in Subsection 4.1.1.

3.6. Connectors & UI 25

### 3.6. Connectors & UI

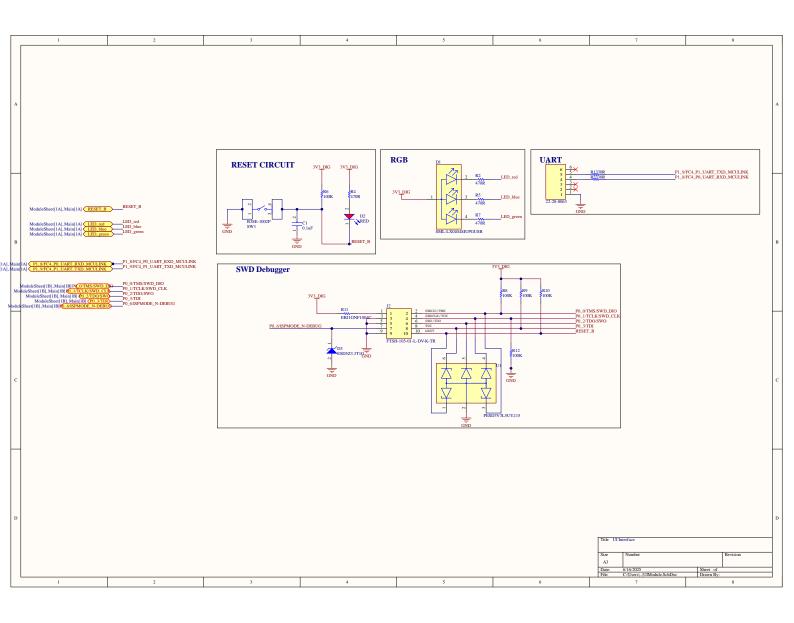

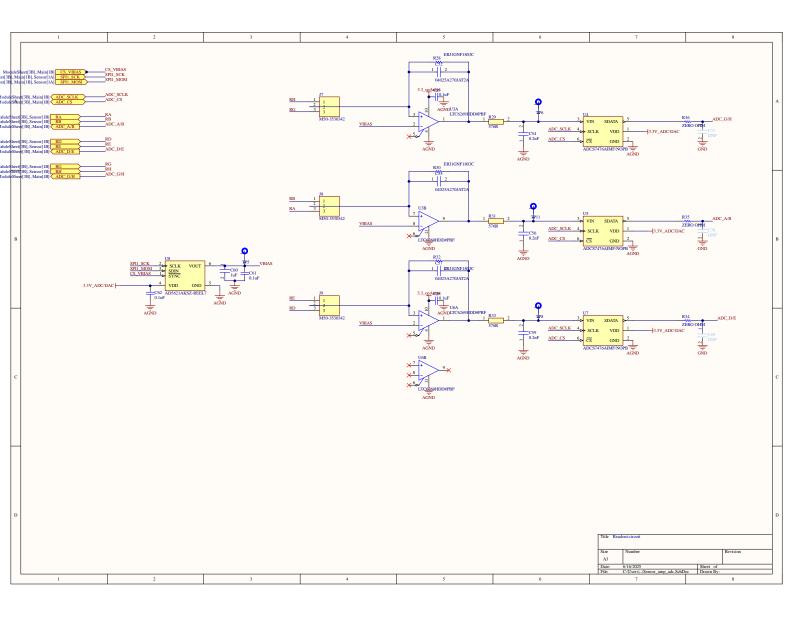

This section will focus on Mandatory Requirements **[MR.2.1]**, **[MR.2.2]** and **[MR.2.3]**. The section first covers the design choices for the connectors as well as a quick view on possible future improvements, lastly, it will cover the reset circuitry and status LED. All schematics can be found in more detail in appendix C.

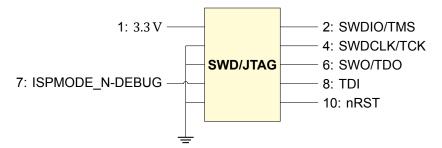

#### 3.6.1. SWD/JTAG

The SWD/JTAG port serves as an interface for programming and debugging microcontrollers. It connects directly to a PC or external debugger via dedicated cables. The pinout of the SWD/JTAG interface is as shown in Fig.3.18.

Figure 3.18: SWD/JTAG connector

The cables mentioned above are susceptible to Electrostatic Discharge (ESD) events during connection and disconnection of the debugger. These discharges can pose a risk to the MCU and other connected components. To mitigate this risk, the PESD3V3L5UY was added. This component is a five-channel Transient Voltage Suppression (TVS) diode array and is connected to pins 2, 4, 6, 8, and 10 of the connector. For pin 7, which is not covered by the array, a separate TVS diode (ESD5Z3.3T1G) was used.

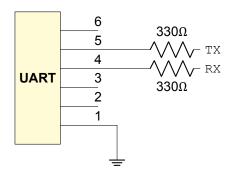

#### 3.6.2. UART

The UART port facilitates serial communication with the PC and utilizes a six-pin connector. In this design, only three of the pins are active: TX, RX, and GND as shown in Fig.3.19. The remaining pins are left unconnected.

Although the UART port is fully exposed making it theoretically susceptible to ESD events, dedicated TVS diodes were not included. Instead, according to the FRDM-MCXN947 schematic [13], two  $330\,\Omega$  resistors are placed in series between the connector and the microcontroller on the TX and RX lines. These resistors serve to limit surge currents in the event of accidental misconnections and provide partial attenuation of ESD transients, while preserving signal integrity.

In contrast, the SWD/JTAG interface, which connects directly to critical debug circuitry within the MCU, employs dedicated TVS diodes to ensure robust ESD protection.

Figure 3.19: UART circuit

3.6. Connectors & UI 26

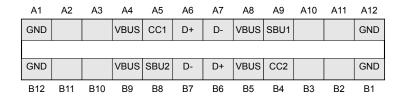

#### 3.6.3. USB-C

To comply with modern interface standards, the Micro-USB connector used in the previous version of the board has been replaced by a more versatile USB Type-C port. This connector serves two primary functions: delivering power to the system and enabling data communication between the microcontroller and a host PC.

According to the USB Type-C specification [22], USB 2.0 devices are limited to a default current of  $500\,\mathrm{mA}$ , although additional circuitry can allow for negotiated currents up to  $3\,\mathrm{A}$ . In this design, such negotiation is unnecessary. As stated in requirement [MR.2.7], the previous board consumed approximately  $100\,\mathrm{mA}$ . Given the removal of the power-intensive dual supply operational amplifiers in the new design, the total current draw is expected to remain at or below this value. Thus, the default USB 2.0 configuration provides sufficient power for the board.

Figure 3.20: USB Type-C receptacle pinout.

Power is delivered through the multiple VBUS pins, which are duplicated in the connector to support cable reversibility, as shown in Fig. 3.20. These pins are shorted together on the PCB and filtered using a ferrite bead and decoupling capacitor to generate a stable 5 V supply for the Main PCB.

Similarly, data communication is handled through the D+ and D- lines, which are also duplicated for orientation independence. These lines are shorted accordingly to form a single differential pair. To protect the data interface from ESD and transient events, the RCLAMP0854P-TCT TVS diode is employed. This component is specifically designed to safeguard high-speed differential data lines while maintaining signal integrity.

The CC1 and CC2 pins serve to indicate the orientation of the USB-C cable and to establish the role of the connected device. Three roles are defined by the USB-C specification: Upstream Facing Port (UFP), which corresponds to a peripheral or "slave" device; Downstream Facing Port (DFP), which acts as a host or "master" device; and Dual-Role Power (DRP), which can dynamically alternate between UFP and DFP functionalities. As specified in [22], for a UFP configuration, the CC1 and CC2 pins must be pulled down to ground through  $5.1\,\mathrm{k}\Omega$  resistors.

The SBU1 and SBU2 pins are designated for low-speed signaling and alternate modes not inherent to the standard USB-C protocol. Since these functionalities are not relevant to the Main PCB, the SBU lines are left unconnected (floating).

#### 3.6.4. UART and SWD/JTAG over USB-C

One of the advantages of USB-C is its support for a dedicated debug mode known as Debug Accessory Mode (DAM). Several developers, including J. Whittington [23], have demonstrated systems that utilize the USB-C DAM protocol to integrate SWD/JTAG and UART functionality into a single USB-C port, alongside the standard USB features. This approach has the potential to significantly reduce PCB footprint by eliminating the need for separate, bulky connectors for UART and SWD/JTAG. However, due to time constraints, the implementation of the additional circuitry required for DAM support could not be completed within the scope of this project.

#### 3.6.5. Reset circuitry & Status LED

A simple reset button and status LED were added to the schematics. To address the issue of contact bounce in mechanical switches, a debounce circuit was implemented, as recommended in [24]. This circuit consists of a  $0.1\,\mu\mathrm{F}$  capacitor in combination with a  $100\,\mathrm{k}\Omega$  resistor, resulting in a time constant of  $10\,\mathrm{ms}$ . This duration is sufficient to filter out the  $5\,\mathrm{ms}$  bounce time specified for the switch in [25], thereby preventing false triggers during operation.

3.7. MCU Integration 27

Two LEDs were included in the design. One is directly connected between the 3.3 V power rail and ground, serving as a power indicator for correct board operation. The second is an RGB LED connected to the microcontroller, which can be configured for status indication or user-defined signaling.

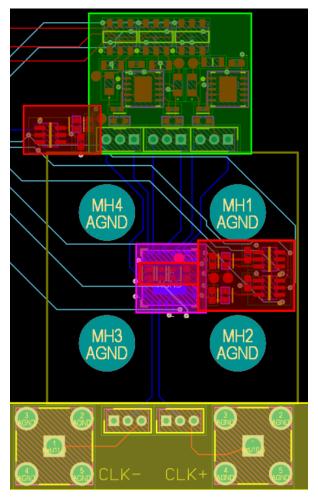

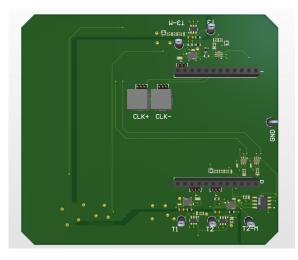

#### 3.6.6. External Clock ports

During the project, several issues and uncertainties arose on the software side related to generating a reliable differential clock. To mitigate the risk of failing to provide a clean clock signal to the PCS chip, two RF connectors were added to allow connection to an external high-quality clock generator. To maintain flexibility and enable testing of the MCU-generated clock, two jumper wires were included, allowing the user to switch between the internal and external clock sources.

# 3.7. MCU Integration

With all major subsystems defined in the preceding chapters, they must now be interconnected to form a coherent and functional system. This involves routing data lines from the debugger, USB-C interface, UART, and ADC outputs to their corresponding pins on the microcontroller (MCU). In addition, the ADCs, DACs, and the chip itself require dedicated control signals originating from the MCU.

Accordingly, the following subsections are organized into two categories: data lines and control signals.

#### 3.7.1. Data Pins

This subsection addresses all signal lines responsible for transferring data to and from the MCU.

The MCU has designated pins for SWD/JTAG signals, UART RX/TX, and USB D+ and D-, which have been connected in accordance with the manufacturer's datasheet.

As described in Subsection 3.4.1, the MCU's I/O structure is organized into four primary ports, each associated with a distinct GPIO speed class: Port 1 provides medium-speed GPIOs, Ports 2 and 3 support fast GPIOs, and Port 4 consists of slow GPIOs.

- ADC outputs: For the ADC output signals, signal integrity is of critical importance. To optimize

performance, layout support was added for optional RC impedance matching circuits at each

output. Although these components will not be populated by default, their corresponding pads

have been included to allow for post-assembly modification if necessary.

- The ADC outputs from the readout circuit are not assigned to fixed microcontroller pins. Since a large number of Fast GPIO pins are available, the design aimed to route all ADC outputs to either Port 2 or 3 to ensure redundancy and enable robust signal acquisition. Consequently, the signals were mapped to Fast GPIO pins that provided the most efficient routing paths during the PCB layout phase.

- Differential clock: The differential clock for the PCS chip operates at high frequency and thus

also requires Fast GPIO support. To accommodate this, two adjacent pins in either Port 2 or 3

were reserved for the CLK+ and CLK- signals. This approach mirrors the rationale used for the

ADC outputs, namely to mitigate risk and ensure timing-critical signals are handled appropriately.

- **RGB LED:** Due to the simplicity of the RGB LED, there were no specific requirements regarding port speed, nor was it necessary to assign it to a Fast GPIO. During the layout phase, the pins were selected based on routing convenience and ease of implementation.

#### 3.7.2. Control Signals