# **High-Performance Operational and Instrumentation Amplifiers**

# High-Performance Operational and Instrumentation Amplifiers

Proefschrift

ter verkrijging van de graad van doctor

aan de Technische Universiteit Delft,

op gezag van de Rector Magnificus prof. ir. K.C.A.M. Luyben,

voorzitter van het College voor Promoties,

in het openbaar te verdedigen op

vrijdag, 16 oktober, 2015 om 15:00 uur

door

### **Behzad SHAHI**

Master of Science in Electrical Engineering Santa Clara University – Santa Clara, California USA

Geboren in Masjedsoleiman, Iran

This dissertation has been approved by the

promotor: Prof.dr.ir. G.C.M. Meijer

Composition of the doctoral committee:

Rector Magnificus, chairperson Prof.dr.ir. G.C.M. Meijer promotor

Independent members:

Prof. dr. P.J. French, TU Delft Prof. dr.R.B. Staszewski TU Delft

Prof Dr. Ir. L J. Breems, TU Eindhoven Prof. dr.ir. A.J.M. van Tuijl Universiteit Twente

Dr. ir. R.G.H. Eschauzier Mellanox

Other member of the doctoral committee:

Em. prof. dr.ir. J.H. Huijsing, TU Delft

Em. prof. dr.ir. J.H. Huijsing has, as former promotor, contributed significantly to the preparation of this dissertation.

Printed by Ipskamp Drukkers, Rotterdam

ISBN / EAN: 978-94-6259-856-0

Copyright: © 2015 by B. Shahi

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system without written permission of the author.

Printed in the Netherlands

| To the Loving Memory of My Late Father, Seyed Mohammad Hasan Shahi (Apr. 1, 1924 – Oct. 11, 2011)                                                                                                                                                                                                             |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                                                                                                                                                                                                                                                                                               |  |  |  |

| The schematic on the cover page represents a simplified block diagram of a patented design for Maxim Integrated Products, Sunnyvale, California. MAX4208 / MAX4209 were awarded "The Product of the Year" in 2008 by EN-Genius NETWORK under the category of "The Most Innovative Instrumentation Amplifier". |  |  |  |

## **Table of Contents**

| Summary                                                                                                 | 9       |

|---------------------------------------------------------------------------------------------------------|---------|

| Chapter 1: Introduction                                                                                 | 9       |

| Chapter 2: Review of Major Error Sources in Op-Amps and Inst-Amps                                       | 9       |

| Chapter 3: Techniques to Reduce Offset Error                                                            | 10      |

| Chapter 4: Dynamic Offset-Cancellation Techniques; Auto-Zeroing: a sampling Techniques                  | nique10 |

| Chapter 5: Dynamic Offset-Cancellation Techniques; Chopping: a Modulation-Based Approach                | 10      |

| Chapter 6: Realization                                                                                  | 10      |

| Samenvatting                                                                                            | 12      |

| 1. Introduction                                                                                         | 15      |

| 1.1 Motivation                                                                                          | 15      |

| 1.1.1 The Need for Amplifiers in Electronic Sensing and Control                                         | 16      |

| 1.1.2 Major Requirements of Precision Gain Blocks for Sensors                                           | 20      |

| 1.2 Challenges with the Three Op-Amp Instrumentation Amplifier as a Conventional Gain Block for Sensors | 20      |

| 1.2.1 Summary of the Disadvantages Associated with the Three Op-Amp Structure                           | 24      |

| 1.3 A Review of Conventional Current Feedback Instrumentation Amplifiers (Conventional CFIAs)           | 25      |

| 1.3.1 Performance Limitations of Conventional CFIA Topology                                             | 28      |

| 1.4 Challenges with Designing Precision Amplifiers in CMOS Technology, and Aim of this Thesis           |         |

| 1.5 Organization of this Thesis                                                                         | 30      |

| 2. Review of Major Error Sources in Op-Amps and Inst-Amps                                               | 32      |

| 2.1 Background                                                                                          | 32      |

| 2.2 Major Error Sources in Op-Amps and Inst-Amps                                                        | 32      |

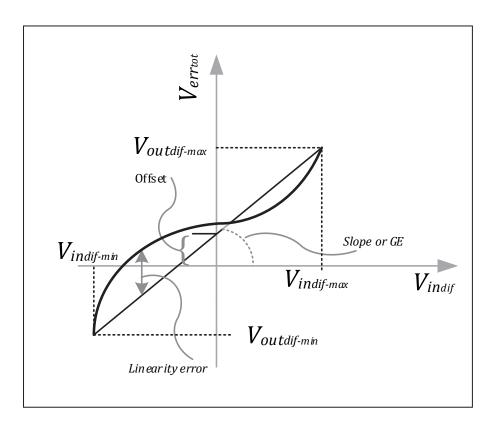

| 2.2.1         | Definition of Offset Error                                                                                            | 34 |

|---------------|-----------------------------------------------------------------------------------------------------------------------|----|

| 2.3 T         | The Origin of the Offset Error in CMOS Op-Amps and Inst-Amps                                                          | 35 |

| 2.3.1         | The Effect of Random Process Variations on Offset                                                                     | 36 |

| 2.3.2         | Drain Current Mismatch and the Consequent Offset Error                                                                | 39 |

| 3. Tech       | nniques to Reduce Offset Error                                                                                        | 42 |

| 3.1           | Conventional Approaches to Reduce Offset                                                                              | 42 |

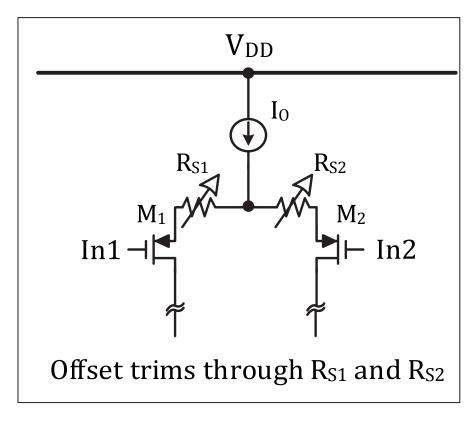

| 3.1.1         | Offset Trimming at Source Degeneration Resistors of the Input Differential Pa                                         |    |

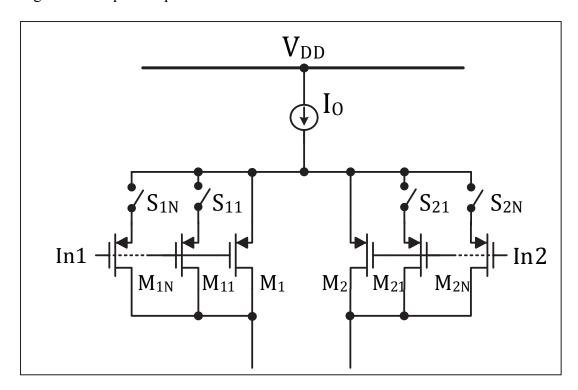

| 3.1.2         | Offset Trimming by Size Adjustments $\Delta W/L$ of the Input Differential Pair Transistors                           | 44 |

| 3.1.3         | Offset Trimming at Source Degeneration Resistors of Current Mirror Load or Folded Cascode                             | 45 |

| 3.1.4         | Offset Trimming by Changing the Load Current Sources at the Drain/Source of Input Differential Pair Transistors       |    |

| 3.1.5         | Offset Trimming by Addition of a Trimmable Current to One Side of the Load a Differential Pair Transistors            |    |

| 3.2 T         | rimming Step within the Production Flow                                                                               | 47 |

| 3.2.1<br>3.2. | Wafer-Sort Trimming (WST) and Associated Techniques  1.1 Advantages and Disadvantages of WST                          |    |

| 3.2.2<br>3.2. | Post-Package Trimming (PPT) and Associated Techniques                                                                 |    |

| 3.3 D         | Oynamic Offset Cancellation (Real Time Offset Removal)                                                                | 53 |

| 3.3.1         | General Advantages of Dynamic Offset Cancellation (DOC) Techniques                                                    | 53 |

| 3.4 A         | Short Review of Accuracy Errors in Inst-Amps                                                                          | 54 |

|               | A Practical Note on Over-Temperature Performance Assurance and Misinterpretation of Performance Guaranteeing Term GBD | 58 |

| •             | amic Offset-Cancellation (DOC) Techniques: Auto-Zeroing, A pling Based Approach                                       | 61 |

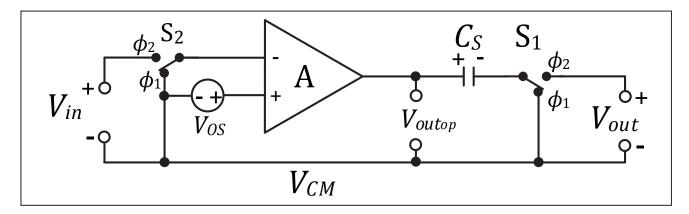

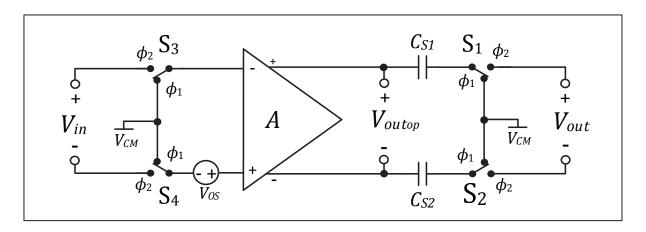

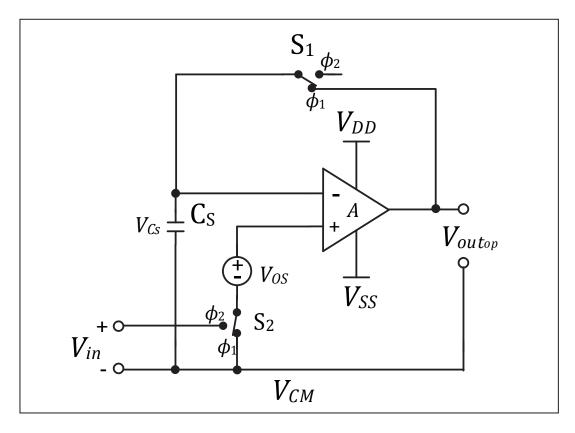

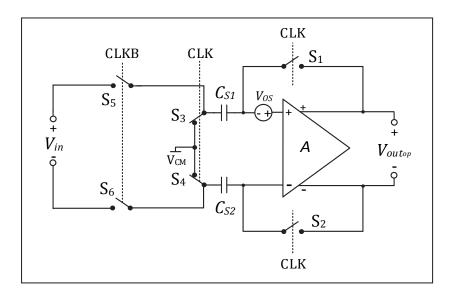

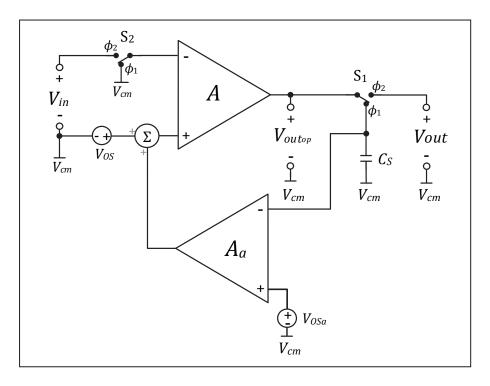

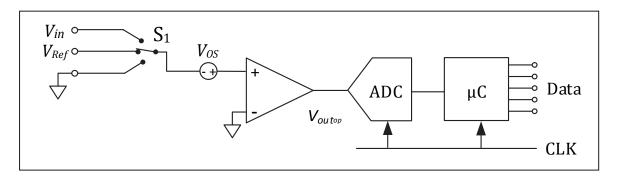

| 4.1 A         | Auto-Zeroing: A Sampling and Storage Based Technique                                                                  | 61 |

|    | 4.1.1<br>4.1.1 | Output Offset Storage (OOS)                                                                                                              |      |

|----|----------------|------------------------------------------------------------------------------------------------------------------------------------------|------|

|    |                | Input Offset Storage (IOS)                                                                                                               |      |

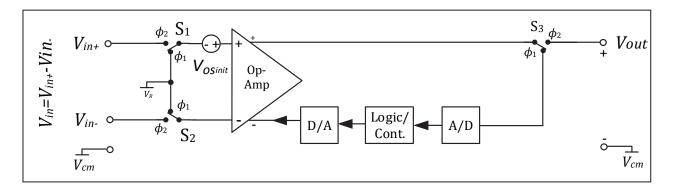

|    |                | Using an Auxiliary Amplifier in a Closed Loop Configuration                                                                              |      |

|    | 4.1.4<br>4.1.4 | Ping-Pong Configuration                                                                                                                  |      |

|    |                | Self-Calibration or Digital Offset Storage and Control Technique                                                                         |      |

|    | 4.1.6<br>4.1.6 | Auto Calibration (Digital Signal Processing Approach)  Advantages and Disadvantages of the Digital Signal Processing Approach            |      |

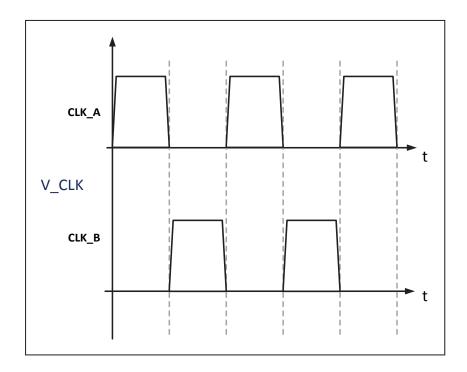

| 5. |                | mic Offset Cancellation Techniques: Chopping, A Modulation                                                                               | 78   |

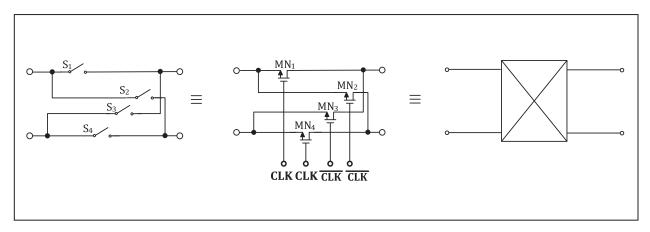

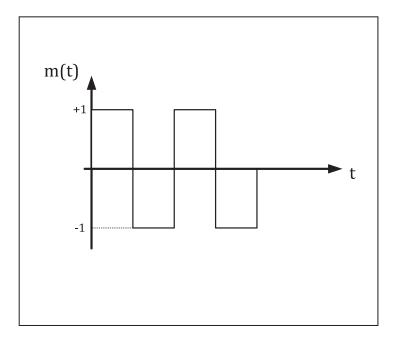

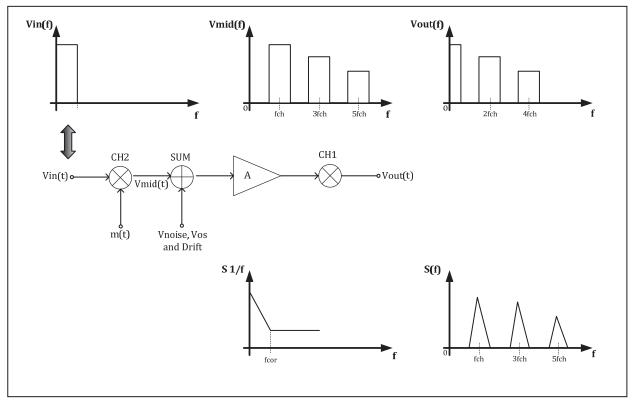

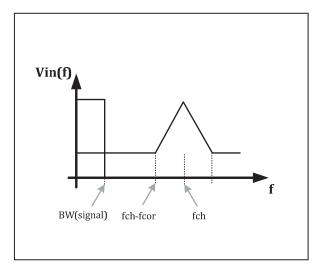

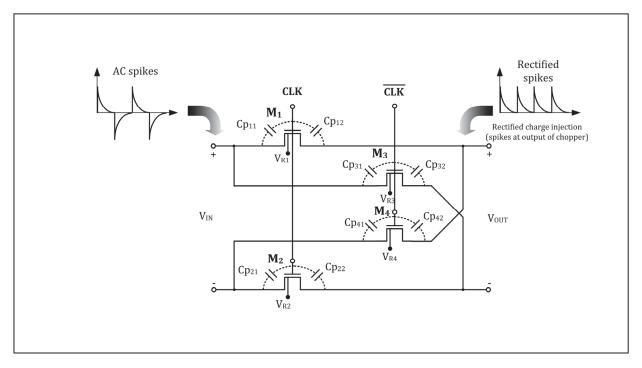

| 5  | .1 Ba          | sic Chopper Operation                                                                                                                    | . 79 |

| 5  | .2 Ch          | opper Techniques                                                                                                                         | . 82 |

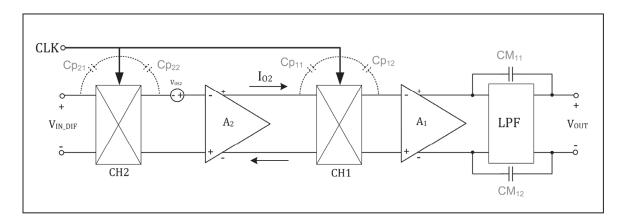

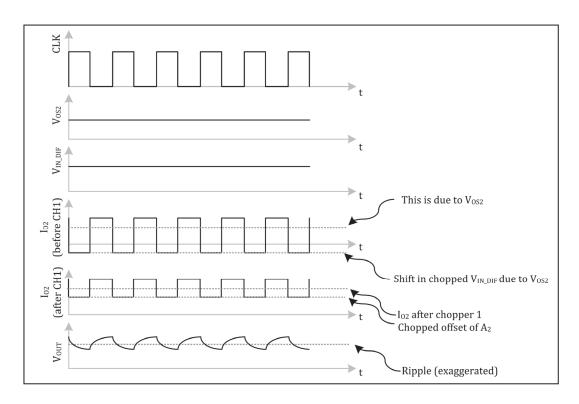

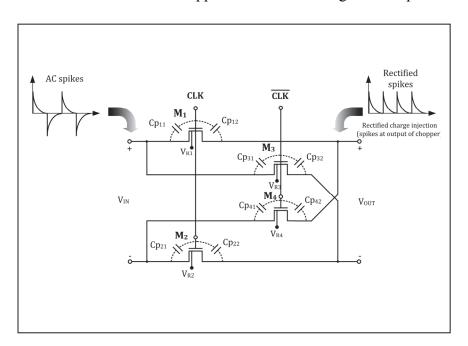

|    | 5.2.1<br>5.2.1 | Conventional Chopper Techniques                                                                                                          | 82   |

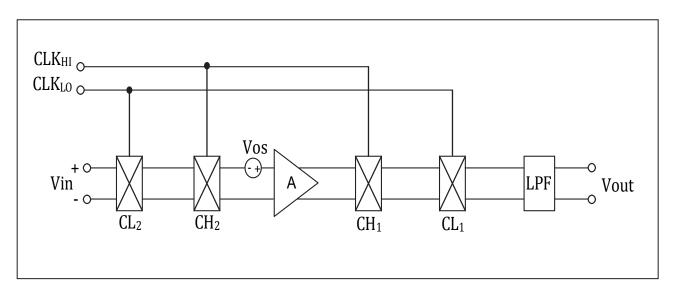

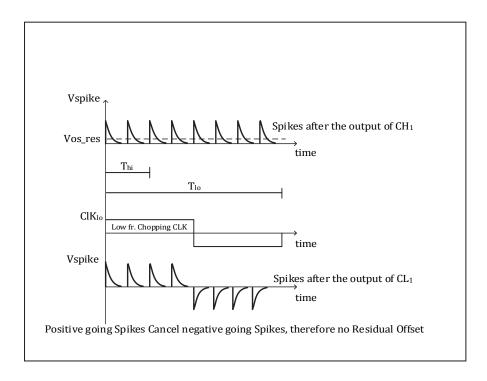

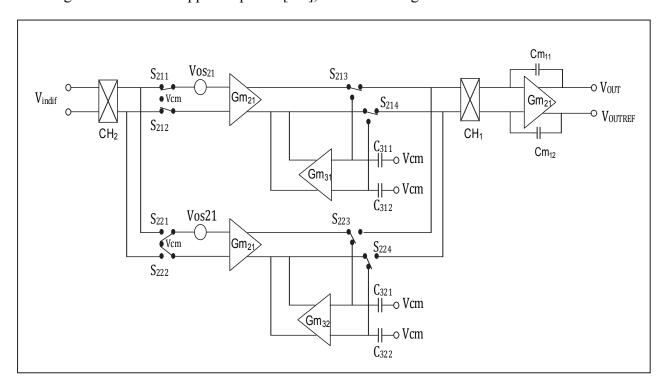

|    | 5.2.2<br>5.2.2 | Nested Chopper Techniques                                                                                                                |      |

|    | 5.2.3          | Chopper Techniques with Auto-Zeroing                                                                                                     | 89   |

|    | 5.2.4<br>5.2.4 |                                                                                                                                          |      |

|    | 5.2.5          | Design                                                                                                                                   |      |

|    | 5.2.6          | Chopper Stabilized Auto-Zeroed Chopper Techniques                                                                                        | 94   |

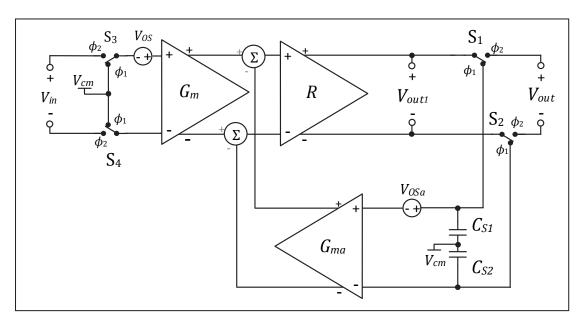

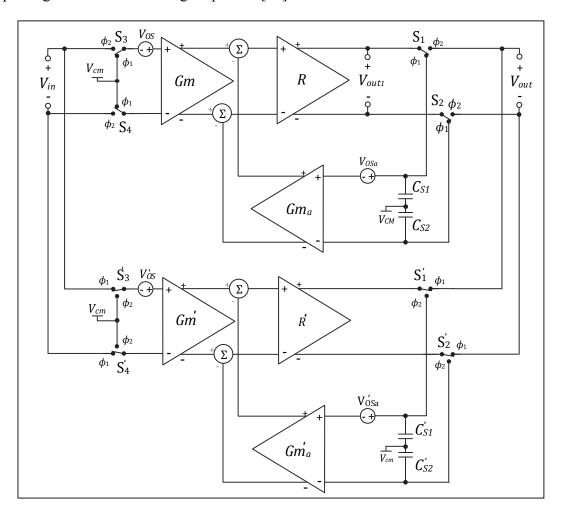

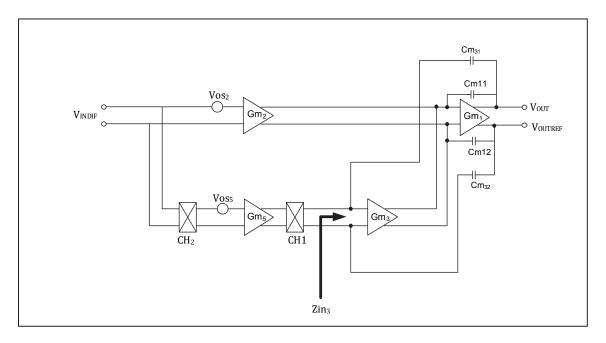

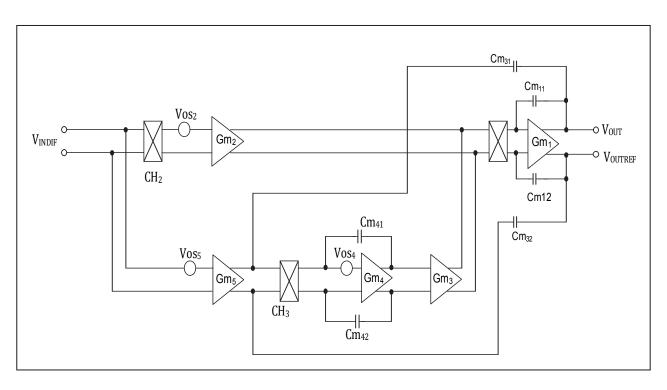

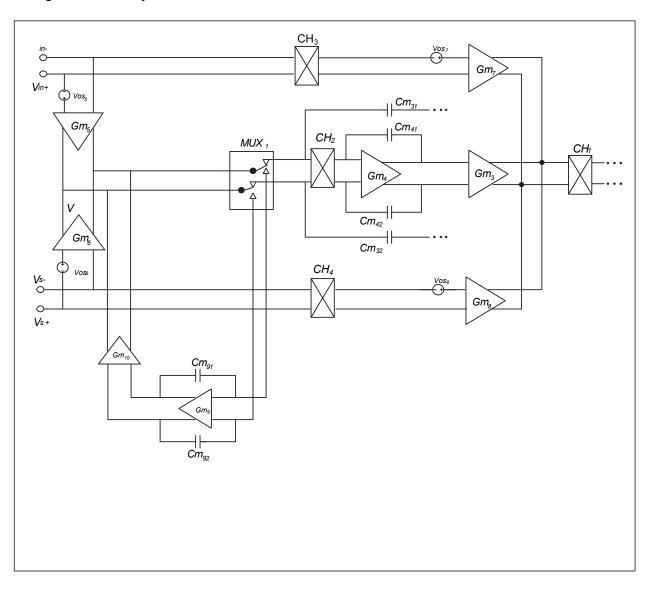

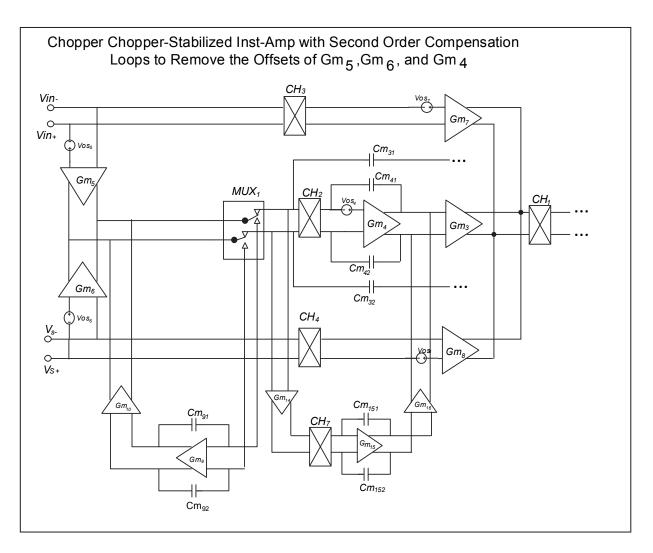

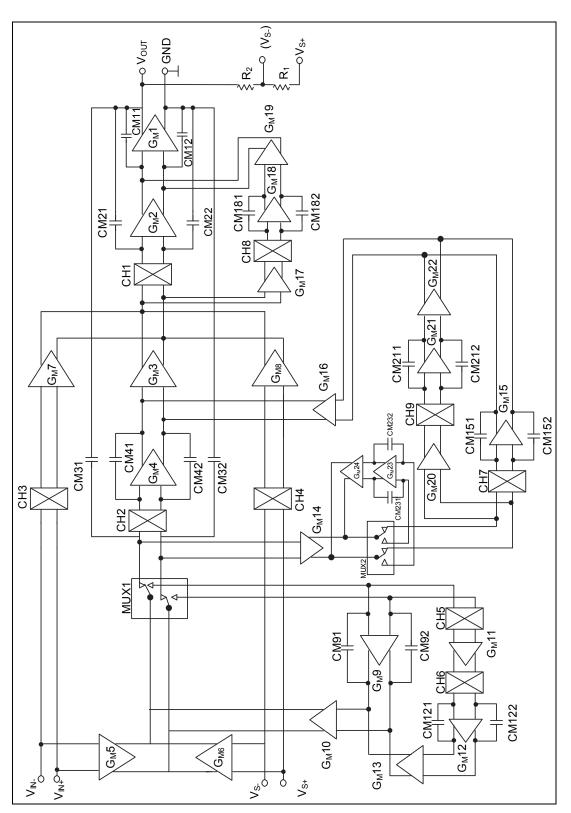

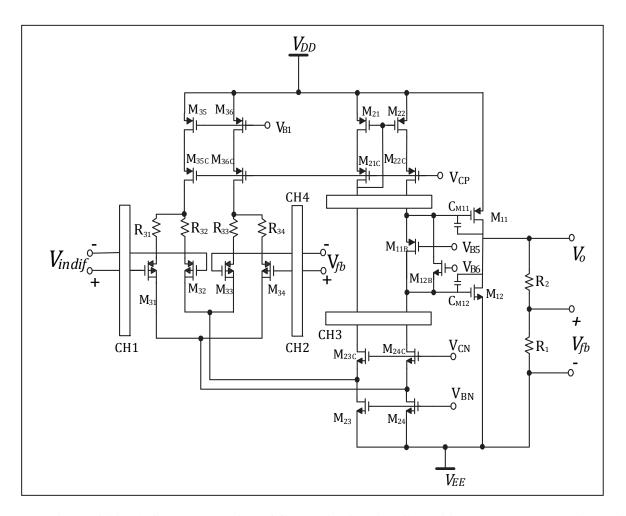

| 5  |                | opper-Stabilized Chopper Inst-Amps Utilizing Indirect Current Feedback pology                                                            | 94   |

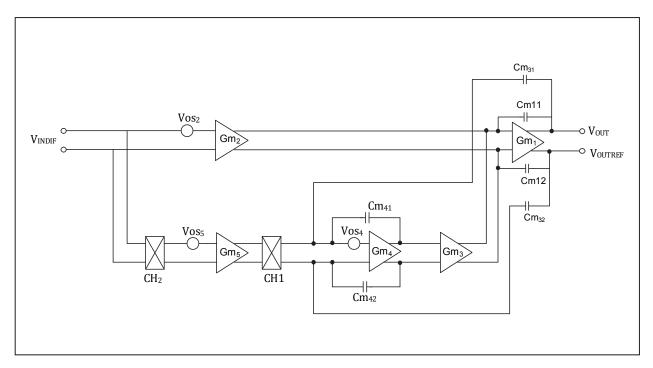

| 5  | .4 Ch          | opper-Stabilized Auto-Zeroed Chopper CFIA Development                                                                                    | . 94 |

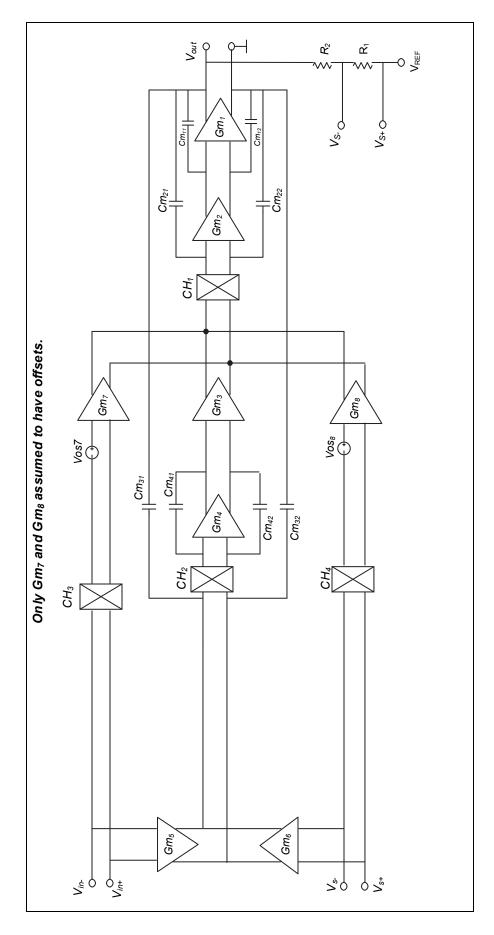

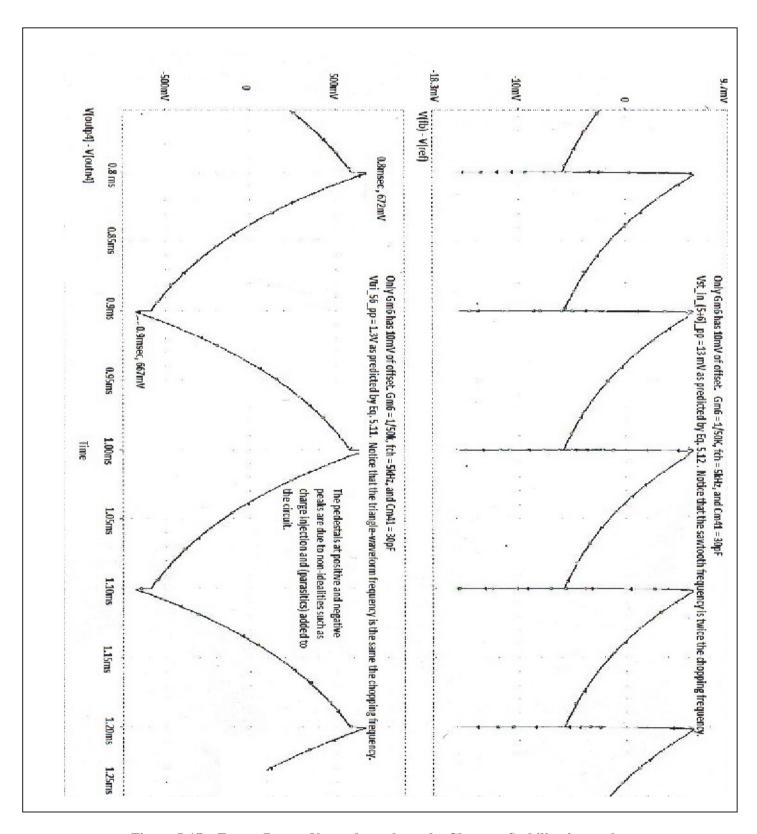

|    | 5.4.1          | Removal of the Input-Referred offset due to the Offset of the Input Transconductances of the High-Frequency path $(G_{m7}$ and $G_{m8})$ | 97   |

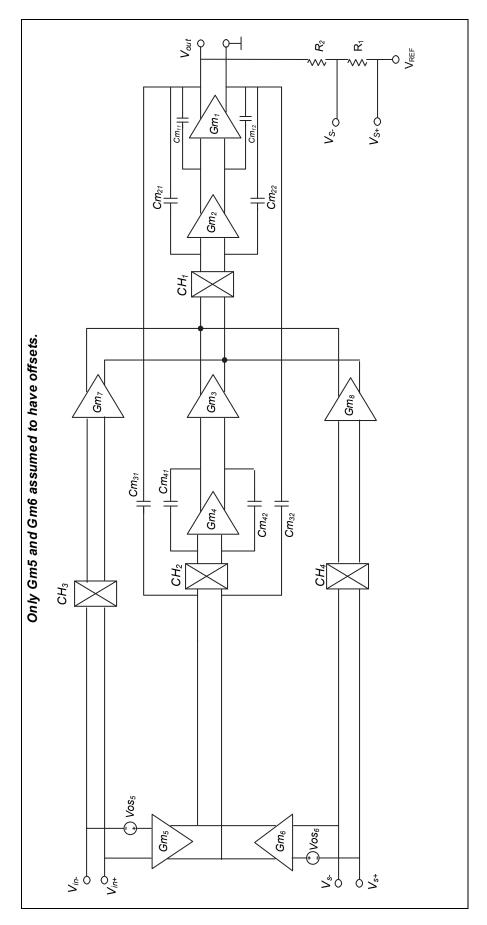

|   | 5.4.2          | Input-Referred offset due to the offset of the Input Transconductances of the Frequency Path ( $Gm_5$ and $Gm_6$ )    |           |

|---|----------------|-----------------------------------------------------------------------------------------------------------------------|-----------|

|   | 5.4.2          | 1 2                                                                                                                   | ey Path   |

|   | 5.4.3<br>5.4.3 | Input-Referred Offset due to the offset of the Integrator Block $(G_{m4})$                                            |           |

|   | 5.4.4          | Input-Referred Offset due to the Weak transconductance $(G_{m3})$                                                     | 106       |

|   | 5.4.5<br>5.4.5 | Input-Referred offsets due to the offset of the Integrator $Gm_9$                                                     |           |

|   | 5.4.6<br>5.4.6 | Input-Referred offset due to the offset of the Sense Amplifier $G_{m14}$                                              |           |

|   | 5.4.7<br>5.4.7 | Input-Referred offset due to the offset of the Integrator $G_{m15}$                                                   |           |

|   | 5.4.8<br>5.4.8 | Effects of the offset of the Transimpedance $G_{m2}$ on $V_{out}$ Spikes                                              |           |

|   | 5.4.9          | Summary of the Effects of Different Transconductance Native Offsets, aloother parameters on the Input-Referred Offset |           |

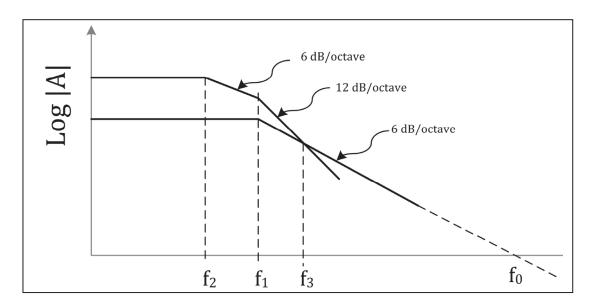

|   | 5.4.10         | Overcoming Frequency Compensation Issues Caused by the Existence of a Path Amplification                              |           |

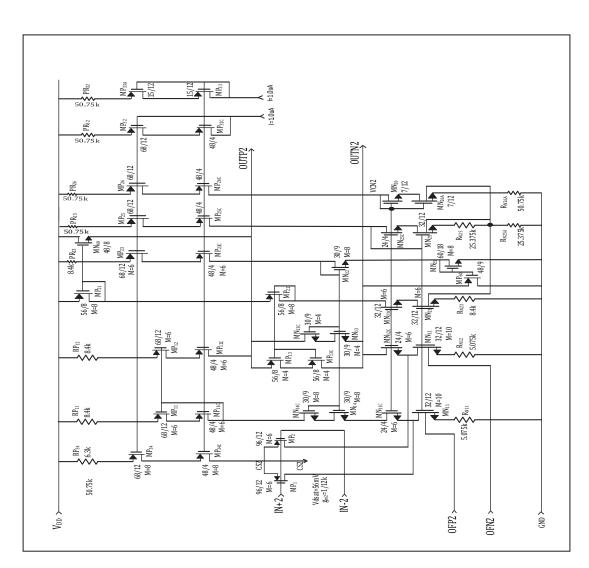

| 6 | . Realiz       | zation                                                                                                                | 118       |

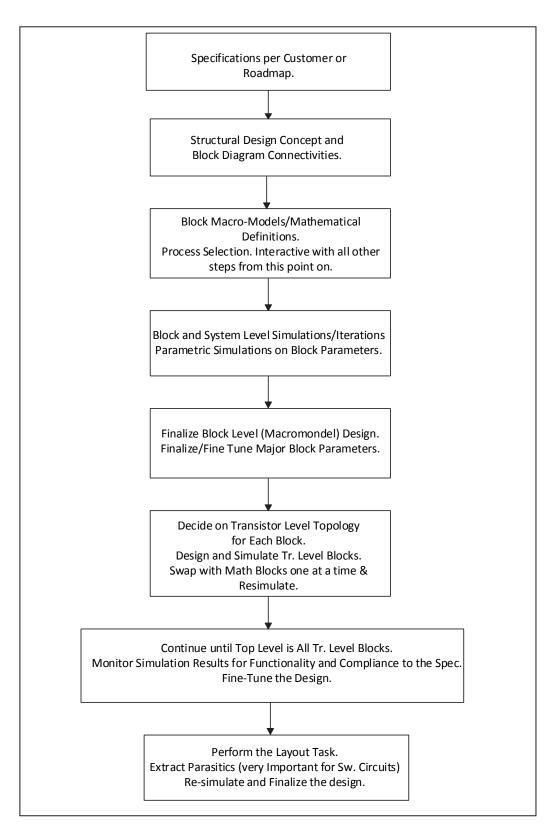

|   | 6.1 To         | p-Down versus Bottom-Up Design Approaches                                                                             | 118       |

|   | 6.2 To         | p-Down Design Steps and considerations                                                                                | 120       |

|   | 6.3 Pro        | ocess Technology Considerations                                                                                       | 123       |

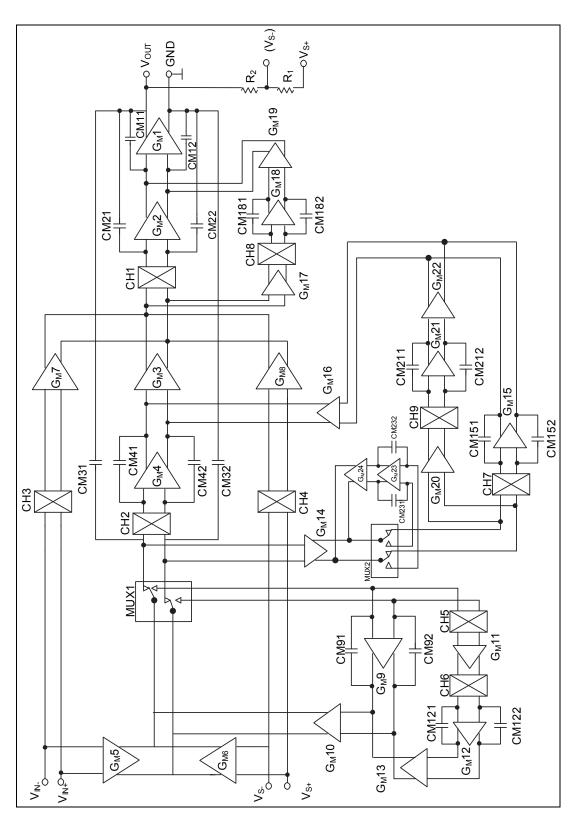

|   |                | p-Down Model-Based Design of the Chopper-Stabilized Auto-Zeroecopper Instrumentation Amplifier                        |           |

|   | 6.4.1          | General Specifications of the CFIA design                                                                             | 128       |

|   | 6.4.2          | Model-Based Design of the Output Stage and Frequency Compensation N                                                   | etwork129 |

|   | 6.4.3          | Model-Based Design of the Input Stage Transconductances, and their First Offset Cancellation loop                     |           |

|   | 6.4.4          | Model-Based Design of Higher-Level Offset Cancellation Loops                                                          | 134       |

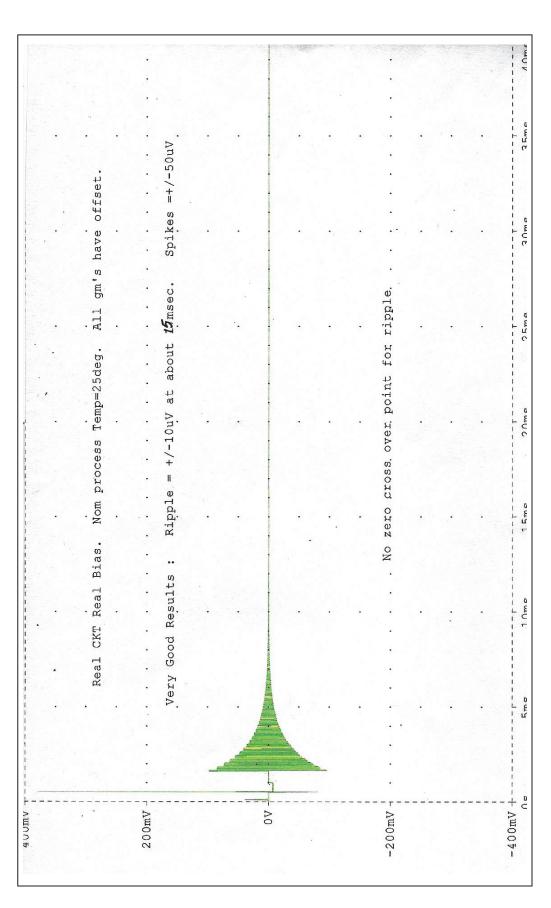

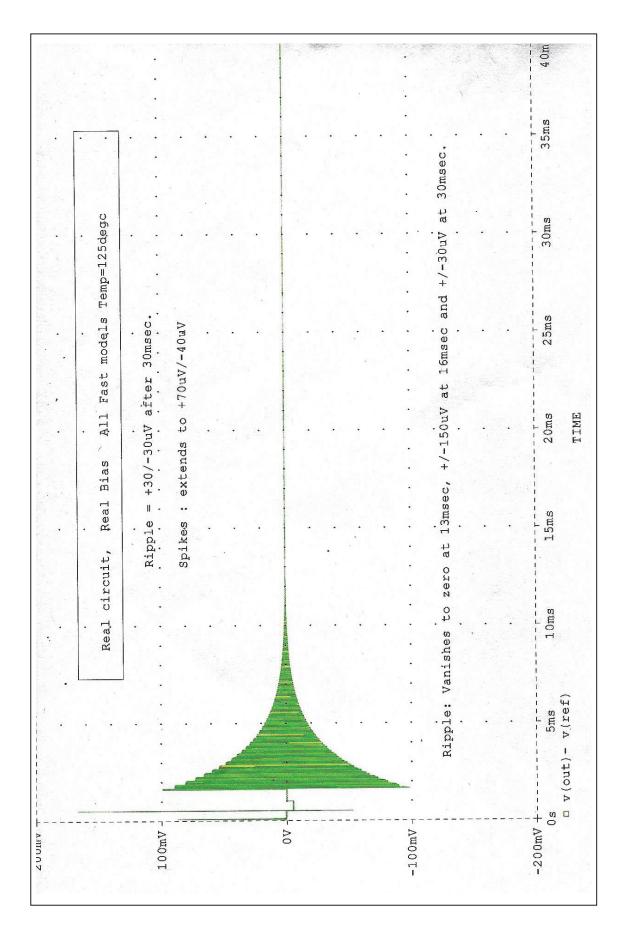

| 6   | .4.5           | Sim   | ulation Results for the Model-Based Design of CFIA                                                                   | .138 |

|-----|----------------|-------|----------------------------------------------------------------------------------------------------------------------|------|

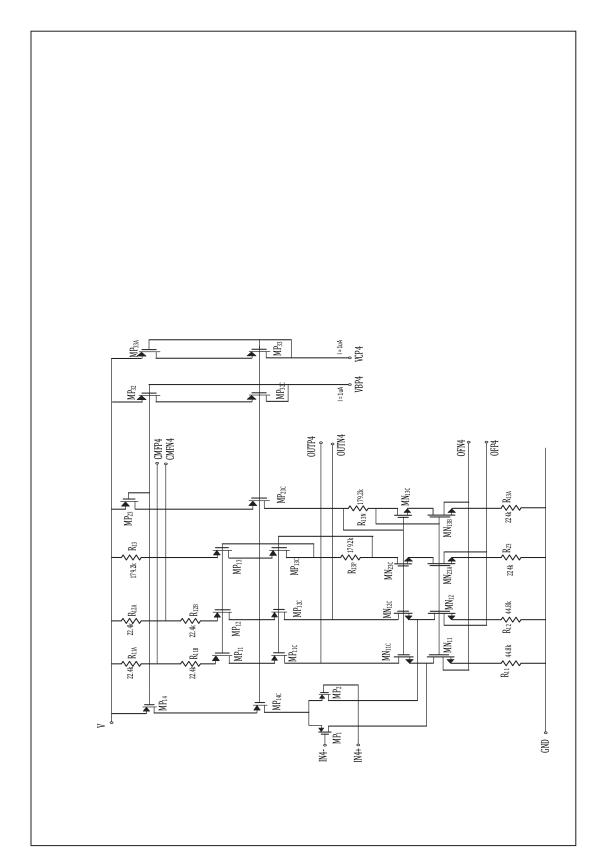

| 6.5 | Tra            | ansis | tor-Level Design of the CFIA in CMOS Technology                                                                      | 142  |

| 6   | .5.1           | Basi  | c Process Parametric Specifications                                                                                  | .142 |

| 6   | .5.2           |       | nsistor-Level Design of Output stage $G_{ml}$ and the Frequency Compensation work in CMOS Technology                 |      |

| 6   | .5.3           |       | nsistor-Level Design of the Driver Stage $G_{m2}$ and the Push-Pull Translinear                                      | .145 |

|     | 6.5.3.         |       | Transistor-Level Design of the Output Over-Current Protection Circuitry within $G_{m2}$ block                        |      |

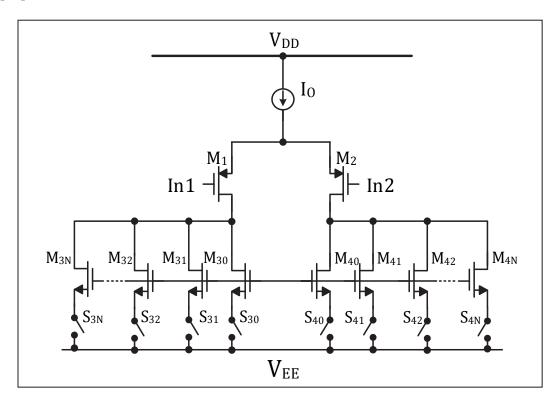

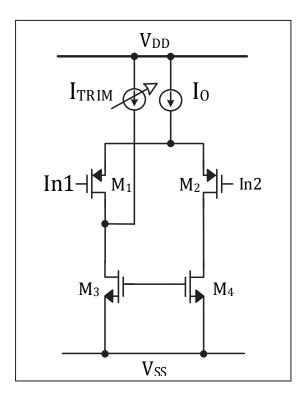

| 6   | .5.4<br>6.5.4. |       | Introduction to the Design of Accurate High-Gain Transconductance Blocks V-I Converters and prior Arts [ 35]         |      |

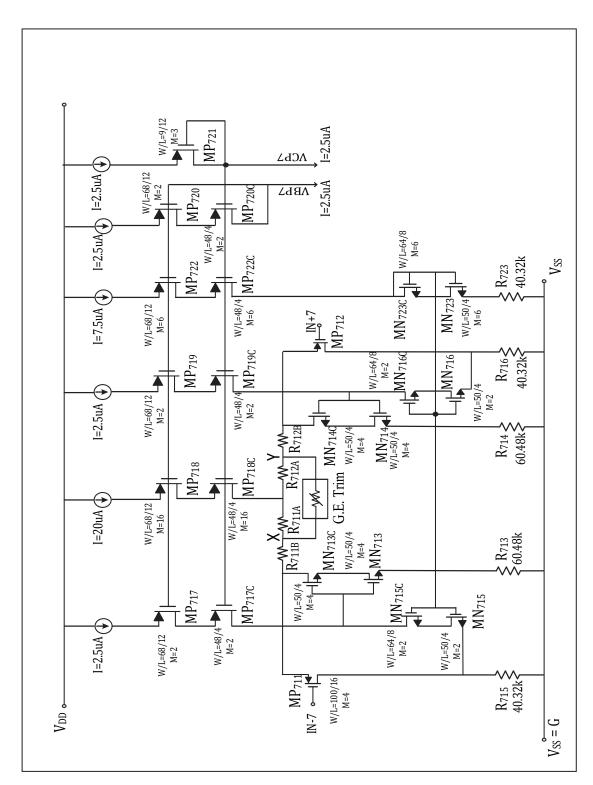

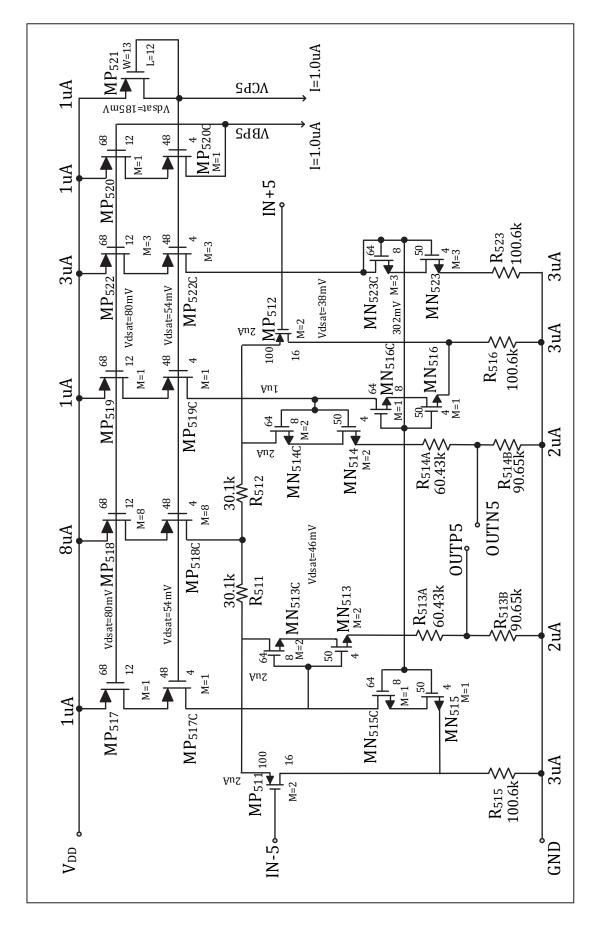

| 6   | .5.5           |       | nsistor-Level Design of High-Gain, Accurate Input and Feedback asconductance blocks $G_{m7}$ and $G_{m8}$            | 155  |

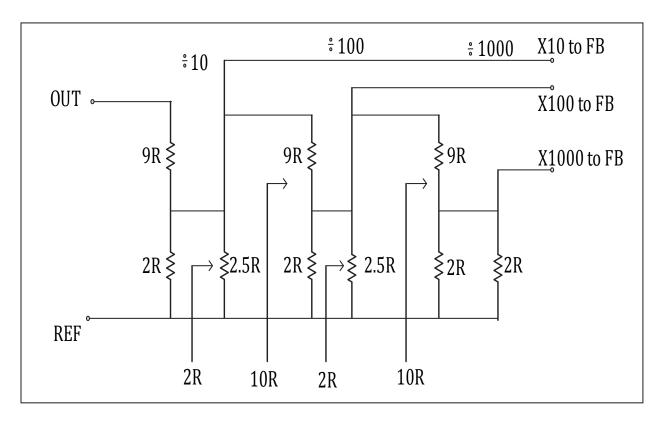

|     | 6.5.5.         |       | Gain Setting Options in CFIA Design                                                                                  |      |

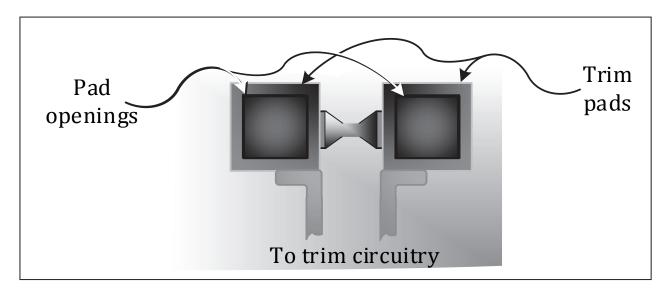

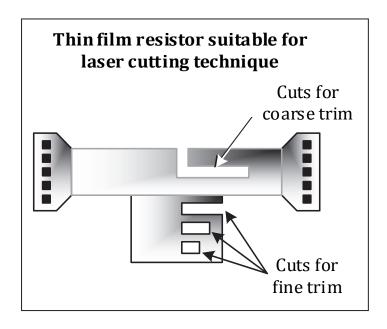

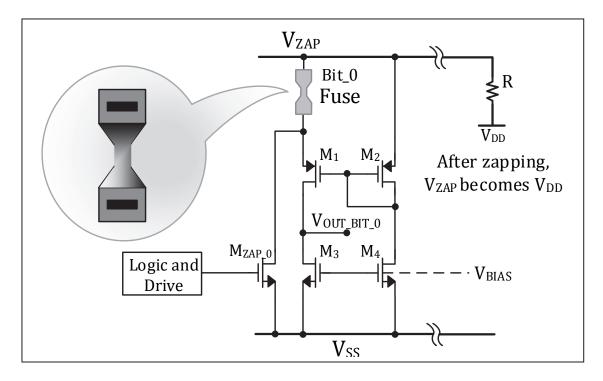

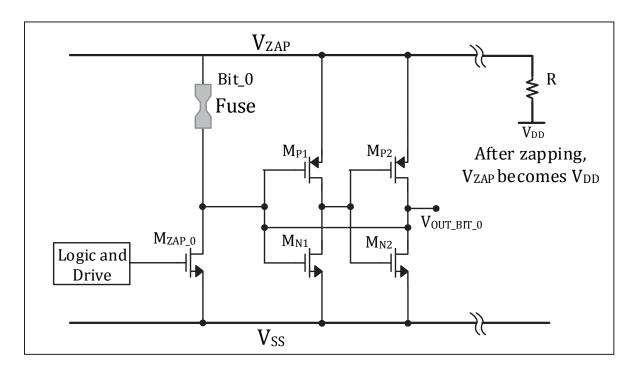

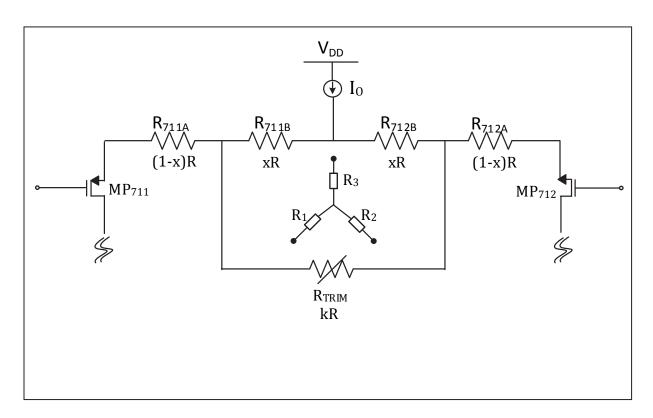

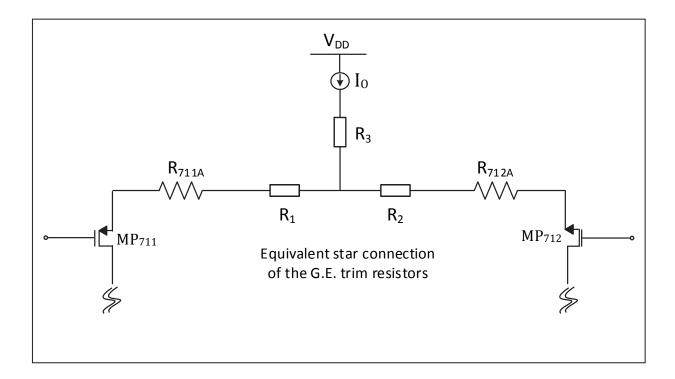

|     | 6.5.5.         |       | General Trim Considerations in Precision Analog Design                                                               |      |

|     | 6.5.5.         | .3    | Sources of Errors Contributing to Gain Error in CFIA Designs                                                         |      |

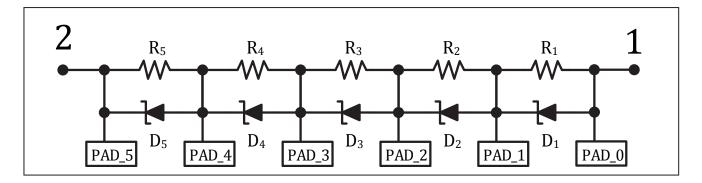

|     | 6.5.5.         | .4    | Gain-Error Trim Range and Resolution for the CFIA Design of this Thesis                                              | 161  |

|     | 6.5.5.         | .5    | Gain-Error Trim Implementation for the CFIA Design of this Thesis                                                    |      |

|     | 6.5.5          |       | Estimation of Trim-Links Branch-Off Points at Degeneration Resistors                                                 |      |

| 6   | .5.6           | Trar  | nsistor-Level Design of the Integrator $G_{m4}$                                                                      | .166 |

|     | 6.5.6.         |       | Transistor-Level Designs of the Integrators $G_{m9}$ , $G_{m12}$ , $G_{m15}$ , $G_{m18}$ , $G_{m21}$ , and $G_{m23}$ | d    |

| 6   | .5.7           | Trar  | nsistor-Level Design of $G_{m5}$ and $G_{m6}$ Sense Amplifiers                                                       | .167 |

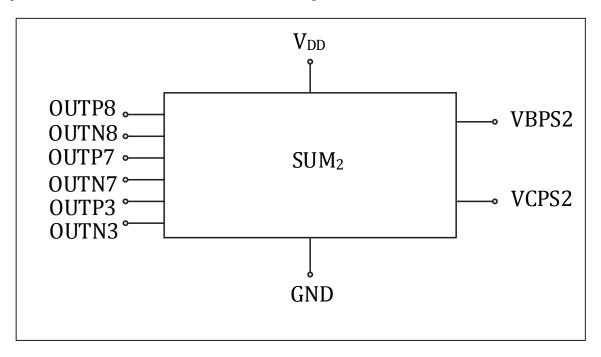

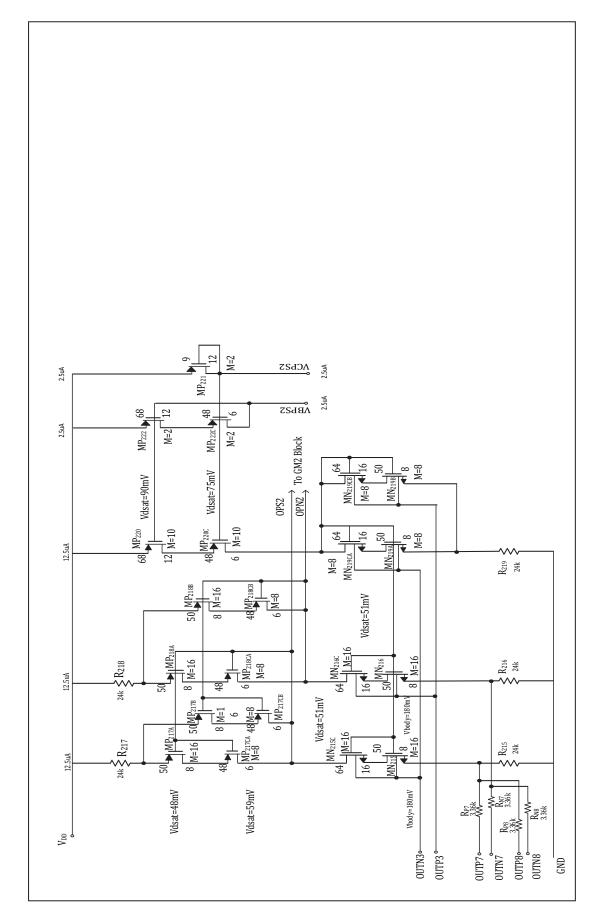

| 6   | .5.8           | Trar  | nsistor-Level Design of the Summing Circuits SUM <sub>2</sub> and SUM <sub>4</sub>                                   | .171 |

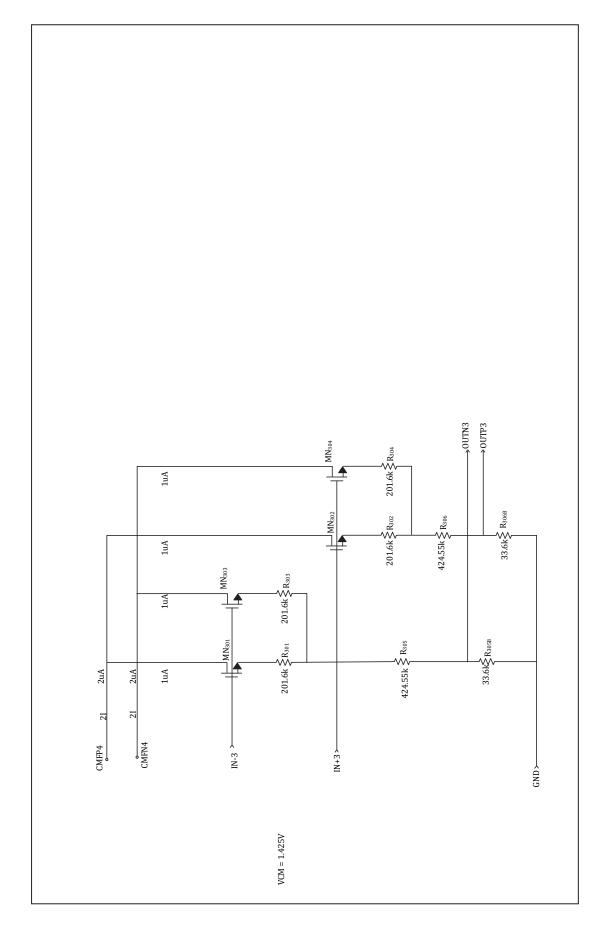

| 6   | .5.9           | Trar  | nsistor-Level Design of the Weak Transconductance $G_{m3}$                                                           | .172 |

| 6   | .5.10          | Trar  | nsistor-Level Design of $G_{m10}$ , $G_{m13}$ , $G_{m19}$ , $G_{m22}$ , and $G_{m24}$ ,                              | .172 |

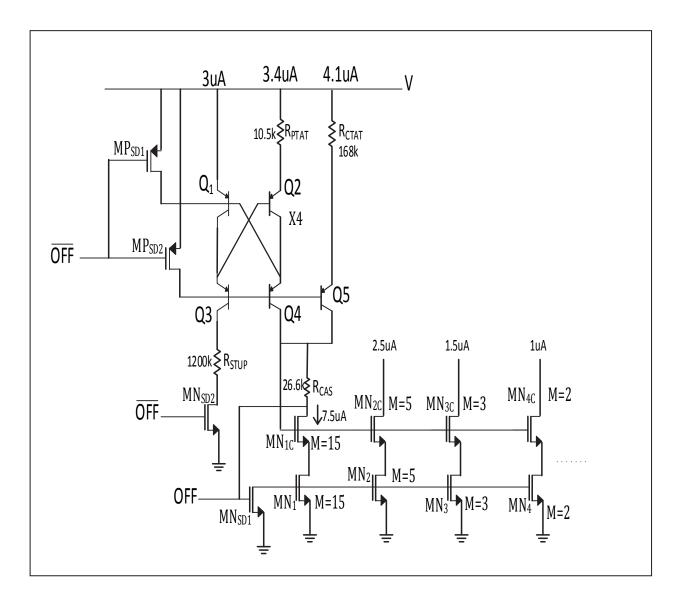

| 6   | .5.11          | Trar  | nsistor-Level Design of the Bias Circuitry (Simplified)                                                              | .175 |

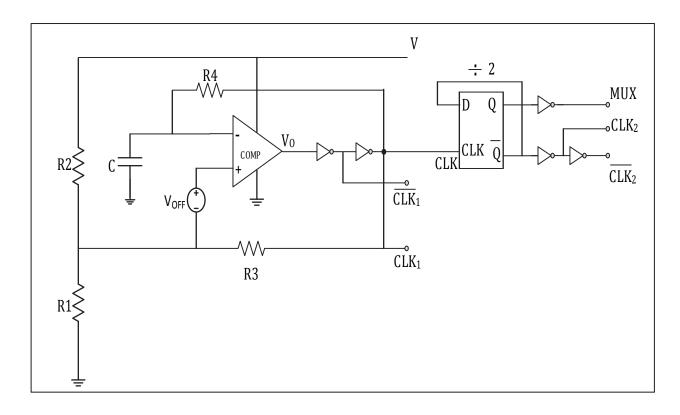

| 6   | .5.12          | Trar  | nsistor-Level Design of the Oscillator Circuit (Simplified)                                                          | .177 |

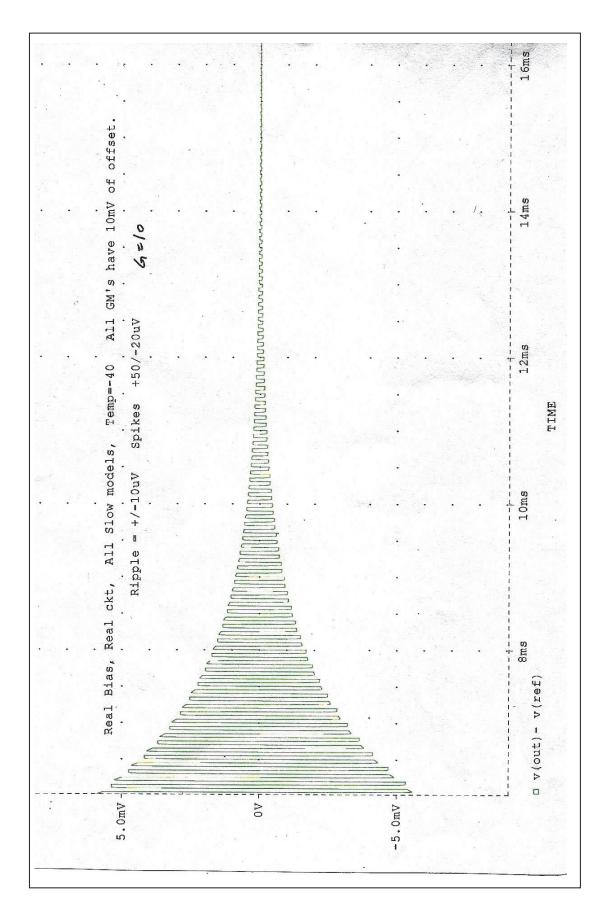

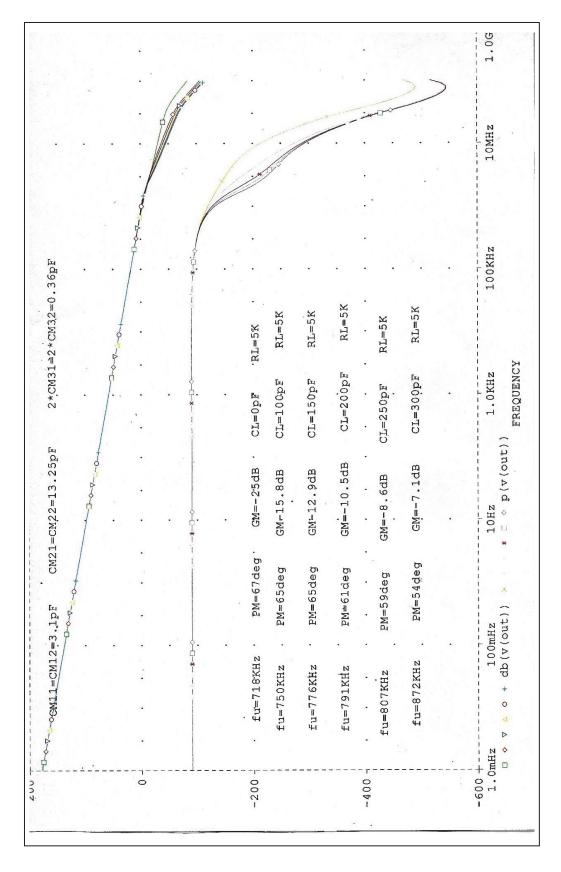

| 6   | 6.5.13         |       | ulation Results for the Transistor-Level Design of CFIA                                                              | nd   |

| 6.6 | Me             | eacur | ement Results                                                                                                        | 184  |

|              | nput-Referred offset for Model-Based Simulations, Transistor-Level |                |

|--------------|--------------------------------------------------------------------|----------------|

| 8            | and Silicon Measurements                                           | 184            |

| 6.6.2 I      | Bench Measurements of the Accuracy, DC, and AC Parameters          | 184            |

| 6.6.2.1      |                                                                    |                |

| 6.6.2.2      | DC Parameters                                                      | 185            |

| 6.6.2.3      | AC Parameters                                                      | 186            |

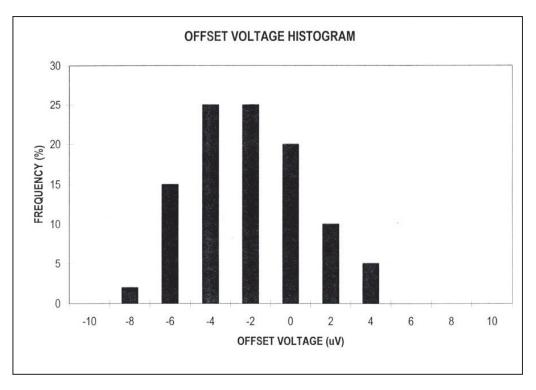

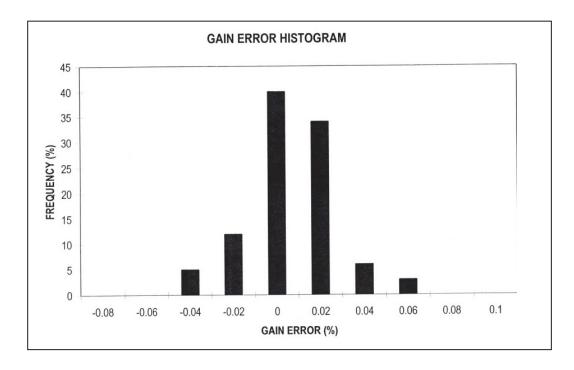

| 6.6.3 I      | Histograms of Accuracy Parameters                                  | 186            |

| 6.6.3.1      | Input-Referred Offset Voltage Histogram                            | 186            |

| 6.6.3.2      | Gain Error Histogram                                               | 187            |

|              | Bench Measurement Results Showing Typical Operating Curves (TOC    |                |

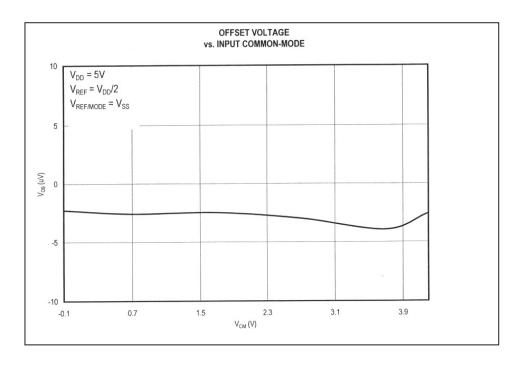

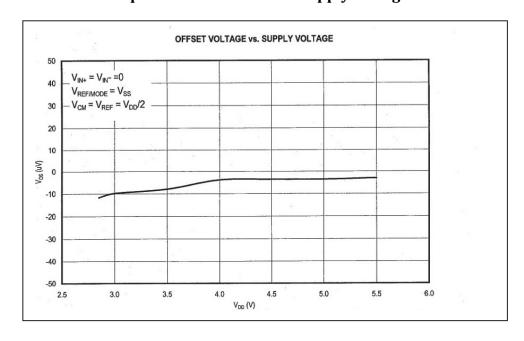

|              | Offset vs. Input Common-Mode and Supply Voltages                   |                |

| 6.6.4.1      | r r r r g                                                          |                |

| 6.6.4.2      | Input-Referred Offset vs. Supply Voltage                           | 188            |

| Conclu       | sions and Improvements                                             | 189            |

| .1 Con       | clusions                                                           | 189            |

| 7.1.1 I      | mprovements Offered by the Chopper-Stabilized Auto-Zeroed Chopp    | er Inst-Amps19 |

| List of Pate | ents                                                               | 192            |

| List of Earl | y Publications                                                     | 192            |

| wards        |                                                                    | 192            |

| About the A  | Author                                                             | 193            |

| Acknowled    | gements                                                            | 194            |

| st of Refe   | rences                                                             | 197            |

| st of Figu   | res                                                                | 200            |

| st of Tabl   | P\$                                                                | 205            |

### **Summary**

This subsection describes a summary of the materials presented in each chapter. Chapters one to four are presented as a foundation, as well as a description of the prior arts and techniques for the patented work of this thesis. These chapters are not part of the work of this thesis. They are presented to provide an overview of the history of the prior art, and to help understand the need for improvements. Advantages and disadvantages of such techniques are presented, with the latter leading to the development of the work of this thesis.

Chapters five and six are entirely devoted to the work of this thesis. Throughout these chapters, the reader is frequently referred to the background chapters to either show a drawback in the existing prior art, or to conduct a comparative evaluation to prove an advantage of the new technique over the previous methods.

A more detailed description of the contents and purposes of each chapter are presented below.

#### **Chapter 1: Introduction**

In this chapter we discuss the need for amplifiers in sensing and control electronics. The major requirements of such precision gain blocks are brought forward. Challenges with the older gain enhancement techniques such as the "Three Op-Amp Instrumentation Amplifier", along with its benefits and drawbacks are discussed.

Conventional "Current-Feedback Instrumentation Amplifiers" (CFIAs) are mentioned as the most popular configurations to construct Instrumentation Amplifiers (Inst-Amps). The performance limitations of this widely-used conventional technique are also reviewed throughout this chapter.

Challenges of designing precision amplifiers in CMOS technology are discussed next.

### **Chapter 2: Review of Major Error Sources in Op-Amps and Inst-Amps**

This chapter deals with the major error sources in Op-Amps and Inst-Amps. The voltage offset error and its origin in CMOS based Op-Amps and Inst-Amps are discussed. Fabrication variables such as the effects of random process-parameter variations, as well as the drain-current mismatches and their consequential offset errors are highlighted.

#### **Chapter 3: Techniques to Reduce Offset Error**

Conventional techniques to reduce offset errors such as trimming and their associated techniques are discussed in this chapter. Major trim techniques at different steps of chip development such as Wafer-Sort Trimming (WST) and variety of different Post-Package Trimming (PPT) options are presented in this chapter. The advantage and disadvantages of all such techniques are discussed to better understand the issues in-hand.

Some industry-accepted terminology and standards relevant to the subject are covered here.

# Chapter 4: Dynamic Offset-Cancellation Techniques; Auto-Zeroing: a sampling Technique

This chapter is concerned with "Auto-Zeroing" as a special class of dynamic offset cancellation, which is based on sampling techniques. A variety of different circuits with their major benefits and drawbacks is discussed in this chapter. Later on and in the following chapters it is shown that the "Auto-Zeroing" technique is partly employed in the design associated with the work of this thesis.

# Chapter 5: Dynamic Offset-Cancellation Techniques; Chopping: a Modulation-Based Approach

Techniques discussed here belong to a second category of real-time offset-cancellation methods, that is, chopping. It is about techniques which are based on modulation as opposed to sampling to remove the offset dynamically, or in real time.

In this chapter the approach presented by the work of this thesis is gradually but thoroughly described from a system-level perspective. This is done by developing and improving on the prior art. To better explain the concept, and when required, some mathematical formulas are presented.

### **Chapter 6: Realization**

This chapter covers the realization of the work of this thesis, that is, a design based on the approach presented in chapter five. First the foundation of good design practice is discussed through an introduction to the systematic model-based top-down design approach vs. the older technique of bottom-up design.

The model-based design, from a system-level point of view, is employed to design the entire system with follow-up simulations, for which the results are provided. The simulation results prove the validity of the new architecture from a system-level simulation stand-point. This is the first but critical step for such designs.

The transistor-level design is presented next in this chapter. The important simulation results are provided, and compared with the model-based design for functionality and major characteristics of the design i.e. the input-referred offset voltage. Practical issues with designing precision amplifiers in CMOS technologies are also covered in this chapter.

Accurate V-I converters and the patented approach are given here. Techniques to reduce offset and improve the gain accuracy are presented in addition to actual circuit design examples of gain-trim accuracy. Other blocks such as band-gap and oscillator circuits are briefly discussed for the sake of completeness.

Simulation results are judged by a comparison to the performance of the real silicon. The results in all cases are very similar and consistent across the board as depicted in Table 6-9.

The results show that the input-referred offset has an extremely low value in the range of  $0.3\mu V$  to  $6\mu V$ . Furthermore, the CMRR measured about 130dB. Other accuracy specifications such as gain-error and linearity-error were measured as low as 0.01%.

### **Samenvatting**

De hoofdstukken één tot en met vier presenteren de grondbeginselen en een beschrijving van het werk dat voorafging aan het gepatenteerde werk dat de kern vormt van dit proefschrift. Als zodanig vormen deze inleidende hoofdstukken geen onderdeel van het kernmateriaal. Zij verschaffen echter een overzicht van de geschiedenis van hetgeen aan het onderzoekwerk voorafging en helpen om de noodzaak te begrijpen van verbeteringen. Voor- en nadelen van de verschillende technieken worden aangeduid. Dit verschaft het inzicht dat heeft geleid tot de ontwikkelingen die verderop in het proefschrift zijn beschreven.

Hoofdstuk vijf en zes zijn geheel gewijd aan het kernmateriaal van dit proefschrift. Overal in deze hoofdstukken worden de lezers veelvuldig verwezen naar het achtergrondmateriaal, teneinde de nadelen van bestaande technieken te laten zien, ofwel om middels een evaluatie de voordelen van de nieuwe methoden te laten zien in vergelijking met voorgaande methoden. Nu volgt een gedetailleerde beschrijving van de inhoud en doelstellingen van elk hoofdstuk.

#### **Hoofdstuk 1: Inleiding**

In dit hoofdstuk bespreken we nut en noodzaak van versterkers in sensor- en regelelektronica. De belangrijkste eigenschappen van deze precisie versterkereenheden wordt naar voren gebracht. Uitdagingen die zich voordoen met oudere versterkervormen, zoals de "Drie-Opamp Instrumentatieversterkers" worden besproken tezamen met voor-en nadelen.

De conventionele "Current-Feedback Instrumentation Amplifiers" (CFIAs) worden genoemd als de meest populaire configuraties voor de constructie van Instrumentatieversterkers (Inst-Amps). De beperkingen van deze wijdverbreide conventionele configuratie worden overal in dit hoofdstuk naar voren gebracht.

Vervolgens worden de uitdagingen besproken voor het ontwerpen van precisieversterkers uitgevoerd in CMOS technologie.

# Hoofdstuk 2: Bespreking van de belangrijkste foutbronnen in Op-Amps en Inst-Amps

Dit hoofdstuk behandelt de belangrijkste foutbronnen in Op-Amps en Inst-Amps. De herkomst van offsetspanningen in CMOS Op-Amps en Inst-Amps, alsmede de fouten die hierdoor worden veroorzaakt worden besproken. Fabricagevariabelen, zoals de effecten van willekeurige variaties van procesparameters, en mismatches van drainstromen en de gevolgen daarvan voor de "offsetfouten" worden belicht.

#### Hoofdstuk 3: Technieken om offsetfouten te reduceren

Conventionele technieken om offsetfouten te reduceren, zoals trimming en daarmee verwante technieken, worden in dit hoofdstuk besproken. Belangrijke trimtechnieken voor verschillende stadia van chip-ontwikkeling, zoals "Wafer-Sort Trimming" (WST) en verschillende "Post-Package Trimming" (PPT) opties worden in dit hoofdstuk behandeld. De voor- en nadelen van al deze technieken worden besproken, teneinde beschikbare mogelijkheden beter te kunnen begrijpen.

Terminologie en standaarden die relevant zijn voor dit onderwerp komen hier ter sprake.

# Hoofdstuk 4: Dynamic Offset Cancellation Techniques; Auto-Zeroing: een bemonsteringstechniek

Dit hoofdstuk behandelt "Auto-Zeroing" als een speciale klasse van "dynamic offset-cancellation" die gebaseerd is op bemonsteringstechniek. Een verscheidenheid aan circuits met hun specifieke voor- en nadelen wordt in dit hoofdstuk besproken. In latere hoofdstukken wordt aangetoond dat een deel van de "Auto-Zeroing" techniek wordt gebruikt bij de ontwerpen die het kernmateriaal vormen van dit proefschrift.

# Hoofdstuk 5: Dynamic Offset-Cancellation Techniques; Chopping: een benadering gebaseerd op modulatie

Technieken die hier worden bediscussieerd behoren tot een tweede categorie van "real-time offset-cancellation" methoden, te weten "chopping". Het verschil met de voorgaande benadering om offset real-time en dynamisch te verwijderen is dat het hier een techniek betreft die gebaseerd is op modulatie in plaats van bemonstering.

In dit hoofdstuk wordt de werkwijze die is toegepast bij de ontwerpen die de kern vormen van dit proefschrift stap-voor-stap belicht vanuit systeemperspectief. Dit wordt gedaan met het oog op verdere ontwikkeling en verbetering van bestaande ontwerpen. Voor een beter begrip van het concept, worden zo nodig wiskundige formules gebruikt.

#### **Hoofdstuk 6: Realisatie**

Dit hoofdstuk behandelt de realisatie van de ontwikkelde concepten voor versterkers, zoals die zijn gepresenteerd in hoofdstuk vijf. De basis voor een goede ontwerpmethode wordt gevormd door een systematische modelgebaseerde top-down benadering in plaats van de oudere benadering van bottom-up ontwerp.

Vanuit systeemoogpunt wordt het modelgebaseerde ontwerp gebruikt om het gehele systeem te ontwerpen middels simulaties. Simulatieresultaten laten de waarde zien van de nieuwe architectuur vanuit systeemperspectief. Deze ontwerpstap vormt een eerste maar belangrijke stap voor het uiteindelijke ontwerp.

Vervolgens wordt in dit hoofdstuk het ontwerp gepresenteerd op transistorniveau. Belangrijke simulatieresultaten worden verschaft en vergeleken met de resultaten ven het modelgebaseerde ontwerp, voor wat betreft de functionaliteit en de belangrijkste ontwerpkarakteristieken en met name de offsetspanning. Praktische ontwerpoverwegingen voor precisieversterkers uitgevoerd met CMOS technologie komen ook in dit hoofdstuk aan de orde.

Nauwkeurige spanning-stroomomzetters en de gepatenteerde benadering worden hier gepresenteerd. Technieken om offset te verminderen en om de nauwkeurigheid van de versterkingsfactor te verbeteren worden gepresenteerd tezamen met actuele voorbeelden van circuitontwerpen met nauwkeurige versterkingsafregeling. Voor de volledigheid worden ook andere circuitblokken, zoals bandgap-spanningsreferenties en oscillatorcircuits, kort behandeld. Simulatieresultaten van het ontwerp zijn vergeleken met de meetresultaten voor de echte chips en tonen een hoge mate van overeenkomst, zoals weergegeven in Tabel 6-9.

De resultaten laten zien dat de ingangsoffsetspanning een extreem lage waarde kan bereiken in de orde van  $0.3\mu V$  tot  $6\mu V$ . Verder bedraagt de gemeten CMRR meer dan 130 dB. Andere nauwkeurigheidsspecificaties, zoals versterkings- en lineariteitsfouten, blijken niet hoger te zijn dan 0.01%.

### 1. Introduction

This thesis describes techniques to reduce the offset error in precision instrumentation and operational amplifiers. The offset along with some other major accuracy errors such as gain, linearity and Common-Mode errors, if not properly compensated for, degrade the performance of the precision gain blocks to the extent that severely affects their effectiveness in accurate amplification of sensor signals. The offset error which is considered a major error source associated with gain blocks, together with other errors are reviewed in more details within chapters 2 and 3 of this thesis. Conventional and newer approaches will be discussed, with a focus on "Chopper-Stabilized Auto-Zeroed Chopper Instrumentation Amplifiers". In addition, major advantages and disadvantages of these techniques are described.

#### 1.1 Motivation

Electronic instrumentation and control has long been established as indispensable means to reliably set, monitor, and control physical quantities of interest. Examples of such physical quantities are temperature, torque, and speed, which are encountered in many real-world system applications.

Electronic control has pervaded every aspect of our day-to-day lives, finding itself in things such as home appliances, power tools, and toys, as well as cars, airplanes, ships, and industrial machinery. These control systems comprise basic components that include sensors, amplifiers, data converters, digital processors, and mechanical actuators.

Systems need to sense or measure a physical quantity through a sensor and the associated circuitries. Next is to process the response, make a decision, and perform an appropriate change on a parameter in some part of the system under control to tame the overall response and ensure that the system remains under control.

There are a vast variety of different sensors serving as the front line components to convert the physical quantity of interest to an electrical signal. These sensors are of many types, shapes, and constructions. The choice of particular sensor depends on the measured parameter, expected range of operation, operating characteristics of the system under consideration, and intended overall cost of the system.

A sensor's electrical response to a change in a physical quantity may or may not be a linear function of the physical quantity itself. They are often approximated as linear functions in small regions using piece-wise linear approximation. Another approach is to mathematically model the transfer function in its entire range of operation through embedded digital processors within the system of interest.

Examples of such sensors are thermistors, thermocouples, piezoelectric sensors, light sensors, bridges, Hall sensors, and more. The subject of different types of sensors, their characteristics, and theories of operation is beyond the scope of this thesis.

While the aforementioned sensors are different in shapes, sizes, constructions, or even physical principles behind their operation, they have one characteristic shared by almost all of them. No matter if the response or output signal of a sensor is a voltage or current, its magnitude is generally much too small to be dealt with directly, especially when used in a noisy environment.

#### 1.1.1 The Need for Amplifiers in Electronic Sensing and Control

The low voltage (few mV), or current (fraction of mA) output signal of a sensor is by no means large enough to be processed without amplification. Accurate gain blocks such as Precision Operational Amplifiers (Op-Amps), or Instrumentation Amplifiers (Inst-Amps) are needed to bring the signal levels to values sufficient for their intended applications.

Such gain blocks should be able to deal with very small input signals and amplify the electrical signal without any noticeable alteration in parameters other than amplitude. Moreover, the noise performance of such gain blocks should be superior to assure reliable amplification of the small input signal; otherwise the tiny signal is convoluted with or buried under the noise generated within the system itself.

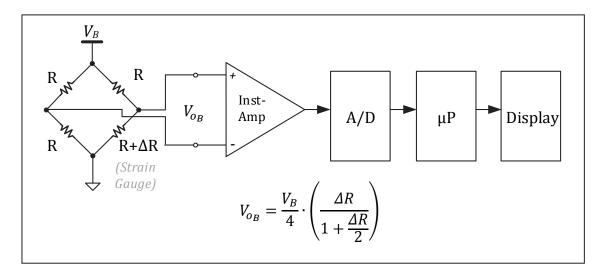

Figure 1-1 – Instrumentation Amplifier in a Sensor Bridge and Display Chain

Amplification is performed prior to drive actuators, or more often prior to digitizing the information by an analog to digital convertor (A/D) for the subsequent digital processing. The processed digital data is going to some display or readout in measuring instrument systems.

In a closed-loop control system, the data may be converted back to an analog signal by a digital to analog converter (D/A) prior to drive an actuator, or being injected at a summing node in the system under control. Not all closed-loop systems employing Inst-Amps are digitally controlled.

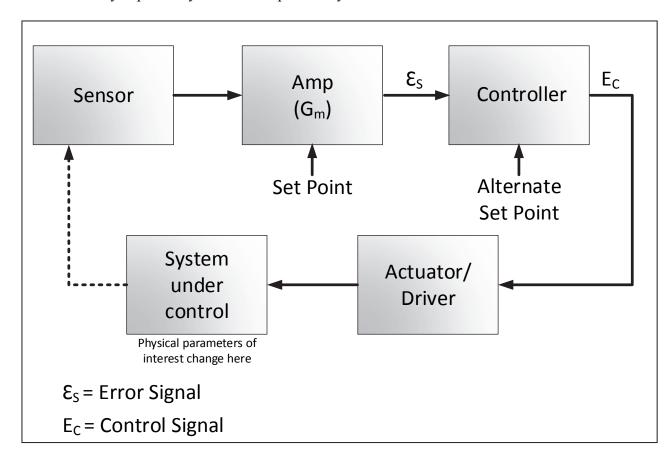

Figure 1-2 shows a top-level view of a simple general Analog Closed-Loop Control System. As seen, the system under control has a Sensor to convert a physical parameter of interest -whose controllability is desired, to an electrical signal. The signal is amplified by a precision gain block and passed on to an Analog-Controller / Signal-Conditioning stage. The output of the Analog-Controller block eventually drives an Actuator within the system under control through a Driver or Power-Amplifier. Some Control and Set-Point Signals are added in an analog fashion to either the amplification block, or the controller itself. The above control method is relatively old, therefore today is primarily used in inexpensive systems or those without a microcontroller.

Figure 1-2 – Gain Block (Amp) in a typical Analog Controlled Closed-Loop System

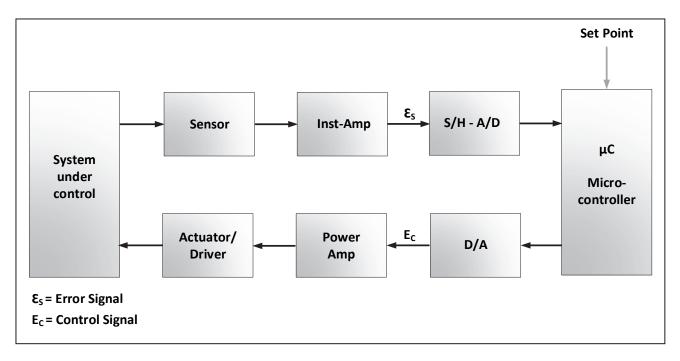

The more adapted systems are the ones using Digital Closed-Loop Control System as depicted in figure 1-3. Here again the system under control has a Sensor together with a Gain-Block (often Inst-Amps) to sense and amplify the physical parameter of interest (voltage, current, charge, temperature, speed, torque, etc...). The output of the amplifier feeds the A/D whose output is driving the Microcontroller's Data Bus through its I/O port. There, the "to be controlled" physical parameter is digitally processed and compared with a Set-Point data.

Finally, a microcontroller provides the necessary output to a D/A convertor for amplification and eventual drive of an Actuator within the system under control to tame the physical parameter.

As can be seen, Precision Gain-Blocks are integral components of both Open-Loop, and Closed-Loop systems. The open-loop systems are mainly for Monitory and Read-Out purposes, whereas the closed-loop systems are not only monitoring, but also controlling a physical parameter of interest to stay at, or within certain desired boundaries through Set-Point inputs.

Figure 1-3 – Instrumentation Amplifier in a Typical Digital Controlled Closed-Loop System

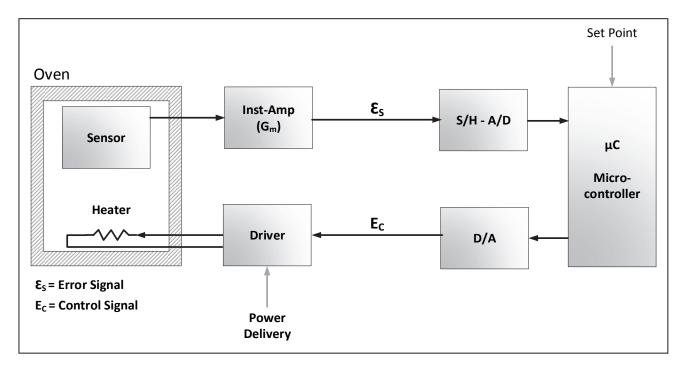

Figure 1-4 – Instrumentation Amplifier used in a common Microcontroller-Based Oven Temperature Control

As the last example, a high level block diagram of an oven temperature control common to many other practical applications such as the temperature control of building's heating systems is shown in figure 1-4.

Notice that in systems based on the diagram presented in figure 1-4 the heating control process is often simply performed by turning the heating element ON and OFF as required so that the system can reach the target Set-Point (desired temperature). However for cooling, one has to rely on heat losses in the system unless provisions for reducing the temperature (such as fans or other cooling techniques) are incorporated and controlled within the system.

Ovens to Bench-Test Integrated Circuits (ICs) are for sure of the second type, that is for those ovens with requirements for cold temperature testing, provisions for reducing the temperature to values below -55°C is certainly included.

#### 1.1.2 Major Requirements of Precision Gain Blocks for Sensors

As the output voltage of a sensor is in the millivolt (mV) range, the input offset voltage ( $V_{off-in}$ ; to be described in section 2.2) of the gain block following the sensor, must be at least one or two orders of magnitude smaller than the sensor's output signal itself. This requires an amplifier with an offset voltage specification in the order of few  $\mu V$  to few tens of  $\mu V$ .

Although both Operational Amplifiers (Op-Amps), and Instrumentation Amplifiers (Inst-Amps) can be used as gain blocks following a sensor, the latter are preferred for their capability to directly handle differential signals and reject unwanted common-mode signals.

Instrumentation Amplifiers are generally closed-loop differential amplifiers, with fixed or adjustable gains. Operational Amplifiers, on the other hand, are offered as open-loop gain blocks, with a need for a feedback loop from output to input to set the closed-loop gain.

Since Inst-Amps are differential type amplifiers, they are ideally capable of selectively amplifying only the differential input signal (the output from the sensor), and be insensitive to the undesired common-mode signal. The insensitivity of an amplifier to common-mode signals is demonstrated through a parameter called the Common-Mode Rejection Ratio (CMRR), which is defined as the ratio of Differential Mode to Common Mode Amplifications and often presented in the unit of dB. Inst-Amps generally have excellent CMRR, typically at or in the excess of 120dB.

Another often-required characteristic of the gain blocks following sensors is the ability of the amplifier's input stage to work at or slightly (some few hundreds of mV) beyond the supply rails. This requirement is of prime interest in measuring the supply currents at High-Side ( $V_{DD}$ ) or Low-Side ( $V_{SS}$  or GND) through a Sense-Resistor in the path of current. This Current-Sensing application is very common, especially in Power Management Electronics.

The requirement of sensing at or slightly beyond both rails for an Inst-Amp or Op-Amp simultaneously mandates the use of complementary devices at the input stages. This makes the design more complex compared to sensing at only one rail.

# 1.2 Challenges with the Three Op-Amp Instrumentation Amplifier as a Conventional Gain Block for Sensors

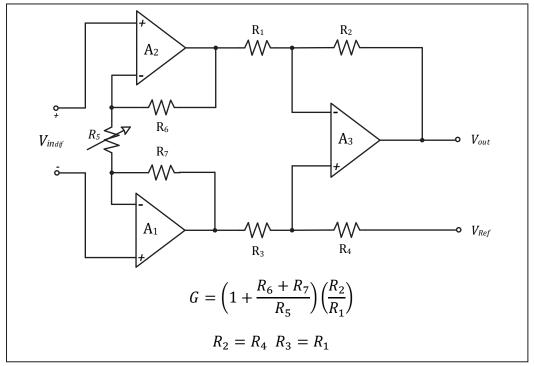

One of the well-known Inst-Amps topologies historically used for amplification is the "Three Op-Amp Instrumentation Amplifier" shown in figure 1-5.

Due to its circuit simplicity, the topology is a popular one for gain blocks in a variety of different sensor applications. Although the architecture is straightforward, it suffers from several disadvantages.

The Three Op-Amp Instrumentation Amplifier is incapable of sensing any of the two supply rails because otherwise the output of one of the two input Op-Amps in the structure collapses to that

rail. This means that the output device becomes saturated for a BJT output transistor or enters the linear (Ohmic) region for a MOS device.

If there is a need to amplify a differential input voltage near or slightly beyond the rails using a Three Op-Amp Instrumentation Amplifier, the only option would be to use level shifters at the inputs. As an example, if  $V_{in_{cm}}$  (see figure 1-5) is set to GND, the negative feedback loops around  $A_1$  and  $A_2$  will force the voltage across resistor R5 to be equal to  $V_{in_{dif}}$ , which sets a zero potential at the output of  $A_2$  and  $A_1$  for a zero differential input, or will demand a negative swing below the GND at the output of  $A_1$  for a positive differential input.

The *CMRR* of a Three Op-Amp structure is very much dependent on the resistors R<sub>1</sub> to R<sub>4</sub> around the Op-Amp in the second stage as seen below. More or less similar expressions for the worst case *CMRR* of this Ins-Amp structure (assuming a well matched input Op-Amp pairs A1 / A2) are given by [19, 20, 21].

If we use letter "H" to denote the CMRR, then:

$$\frac{1}{H_{Inst-Amp}} = \left[\frac{1}{A_v + 1}\right] \cdot \left[\frac{1}{H_{res}} + \frac{1}{H_{Op-Amp}}\right] \tag{1.1}$$

where  $A_{\nu}$  is the voltage gain given by:

$$\begin{split} A_v &= \frac{V_{out}}{V_{in-dif}} = -\left(\frac{R_2}{R_1}\right) \left(\frac{R_6 + R_5 + R_7}{R_5}\right) \\ &= -\left(\frac{R_2}{R_1}\right) \left(1 + \frac{R_6 + R_7}{R_5}\right); \text{ Where } R_1 = R_3 \text{ and } R_2 = R_4 \end{split} \tag{1.2}$$

and:

$$H_{res} = \frac{1 + \frac{R2}{R1}}{4 \cdot \frac{\Delta R}{R}}$$

; and  $\frac{\Delta R}{R} = \text{Resistor's Relative Tolerance}$  (1.3)

Figure 1-5 – The Three Op-Amp Topology

So, the common-mode error is partly coming from the mismatch of the resistor pairs  $R_1$ ,  $R_2$  and  $R_3$ ,  $R_4$ ; each having a mismatch of  $\Delta = \frac{\Delta R}{R}$ , in such a way and direction that together, the mismatches make a worst-case imbalance. The  $H_{Op\text{-}Amp}$  appearing in the second term of the equation is simply the CMRR of Op-Amp A3 in the second stage. Note that if the amplifiers  $A_1$  and  $A_2$  are well matched, the structure is virtually insensitive to the CMRR of these input devices.

Here one simply notices that if the Op-Amp A3 has a CMRR of 100 dB, the bridge resistors are matched within %0.1, the Instrumentation is used in a gain of 30 configuration, with an equal resistor values of R5 through R7, and a well matched input Op-Amps A1 and A2, the CMRR of the structure, is hardly 70 dB without any trim.

This is due to the strong dependence of the *CMRR* of the circuit on the bridge resistor mismatches, something which is hard to prevent and costly to trim. The difficulty of achieving a high *CMRR* without trimming is considered one of the major drawbacks of this topology.

However, if the cost of the trim is acceptable, it is possible to achieve high values of CMRR in the excess of 100dB. This is possible, in particular, when one error source (bridge mismatch), is purposefully compensated with the other one (Op-Amp common mode error), but in any case, the performance of the Chopper-Stabilized Inst-Amps are far superior in this regard.

The Three Op-Amp Instrumentation often consumes more area or power compared to newer techniques, and provides less optimal performance in many accuracy specifications compared to its rival counterparts. These counterparts comprise the category of amplifiers employing Dynamic Offset Cancellations (DOC) techniques, as will be explained in the following chapters.

In order to achieve a good performance, all the Op-Amps in the Three Op-Amp structure must be of high quality in terms of the accuracy specifications. Often this requirement manifests itself in a demand for higher chip area, increased power consumption, or complex trims.

If the Three-Op-Amp Instrumentation IC is used in a variable-gain configuration, the temperature tracking of the external gain setting resistor R5 compared with those internal ones in the bridge and feedback network could be troublesome.

This issue is not limited to the Three Op-Amp design, but holds true for all structures with a single gain setting resistor outside the chip.

# 1.2.1 Summary of the Disadvantages Associated with the Three Op-Amp Structure

In summary, the disadvantages of the Three Op-Amp Instrumentation Amplifiers are as follows:

- 1) Since the structure has Three Op-Amps that all need to have good characteristics to deliver an overall high-quality precision specification, it is usually considered costly and taking a large area, with a likely higher overall current consumption.

- 2) The CMRR is affected not only by the Op-Amps used, but also by the mismatches of the resistor bridge around the difference amplifier at the second stage, hence the need for complex trimming of the Op-Amp and the bridge for optimal performance

- 3) In order to get to very low offset values, both of the input Op-Amps need trimming.

- 4) The Three Op-Amp Instrumentation Amplifier is incapable of sensing at or slightly beyond the supply rails, unless level shifters are used at the inputs. This disadvantage is a major drawback in applications requiring a precise measurement at or slightly beyond the supply voltage rails. Common application examples requiring this feature are high and low side current sensing at VDD, GND, or VSS supply lines in single or dual power supply systems as mentioned before.

- 5) For adjustable gains with an external resistor (here R5 in figure 1-5), the temperature mismatch between the external and internal gain setting resistors degrades the performance of the Inst-Amp over temperatures. However, this drawback is not limited to Three Op-Amp structure, but for all structures that have their gain setting resistor outside the chip.

In chapter five and six, when the new approaches involving the chopper techniques, in particular the work of this thesis "Chopper-Stabilized Auto-Zeroed Chopper Techniques" are discussed, we will revisit the subject again for a comparison of the old versus new approach.

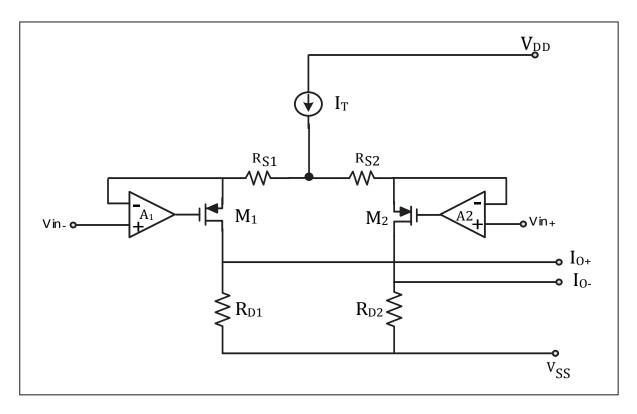

# 1.3 A Review of Conventional Current Feedback Instrumentation Amplifiers (Conventional CFIAs)

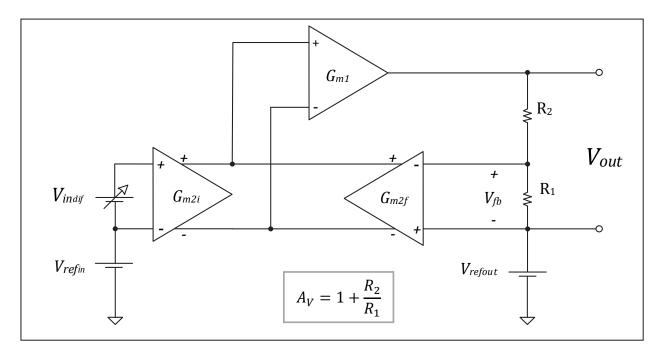

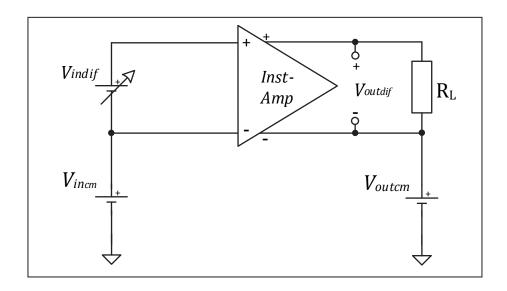

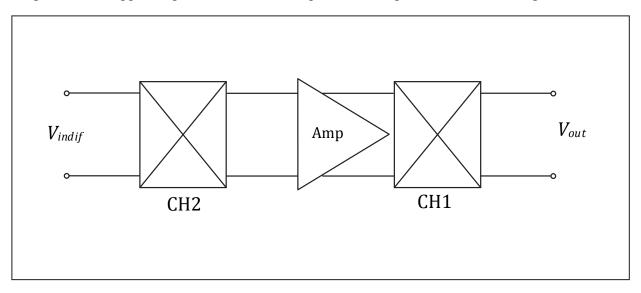

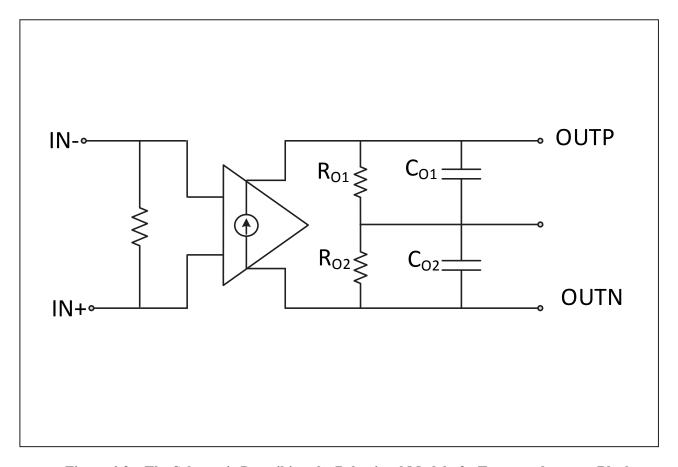

Another Gain Block commonly used as an instrumentation amplifier is the so called Current Feedback Instrumentation Amplifier (CFIA), also known as the Indirect Current Feedback Instrumentation Amplifier (ICFIA) topology. The simple, yet frequently used architecture, as shown in figure 1-6 consists of two identical transconductance amplifiers  $G_{\rm m2i}$ , and  $G_{\rm m2f}$ , an output stage  $G_{\rm m1}$ , along with the gain setting resistors  $R_2$ , and  $R_1$ , which constitute the feedback network as well.

Figure 1-6 – Block View of Current Feedback Instrumentation Amplifier (CFIA)

The input transconductance amplifier  $G_{m2i}$  converts the differential input voltage  $V_{indif}$  to a differential current, while the second voltage to current converter  $G_{m2f}$  (the feedback transconductance), converts a fraction of the output voltage, that is the feedback voltage  $V_{fb}$ , to a second differential current.

The two differential currents at the outputs of  $G_{m2i}$  and  $G_{m2f}$ , which are complementary, are summed up at the input of the output amplifier  $G_{m1}$ ; ideally leaving zero current entering the output amplifier  $G_{m1}$ .

Equating the output currents of  $G_{\rm m2i}$  and  $G_{\rm m2f}$ , with the assumption that they are free of offset errors, and an infinite open loop gain for  $G_{\rm m1}$  stage, reveals the voltage gain of the ideal Inst-Amp.

$$A_V = \left(\frac{G_{m2i}}{G_{m2f}}\right) \cdot \left(1 + \frac{R_2}{R_1}\right) \tag{1.4}$$

In order to make errors associated with different  $G_{m2i}$  and  $G_{2mf}$  insignificant, it is customary to make them equal. This simplifies the gain equation to:

$$A_{\rm v} = 1 + \frac{R_2}{R_1}$$

; For  $G_{m2i} = G_{m2f}$  (1.5)

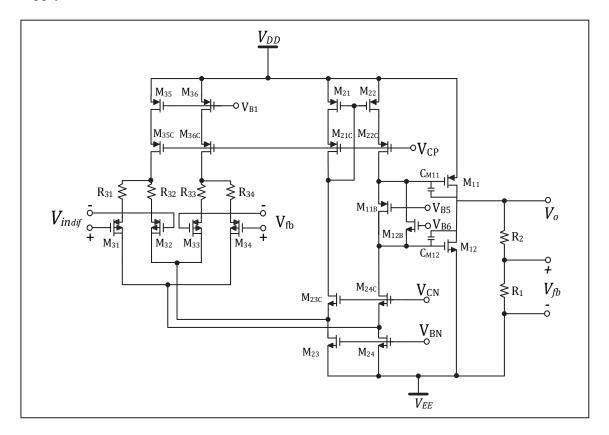

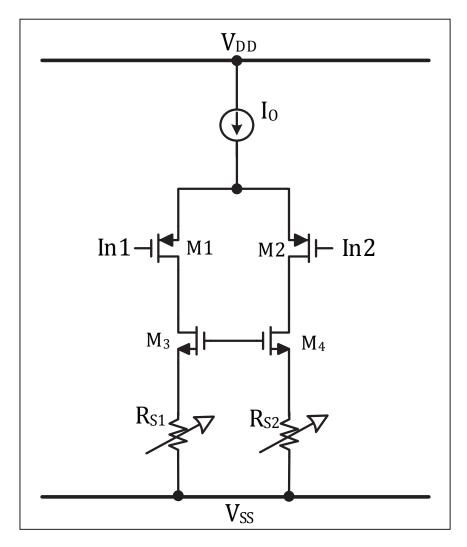

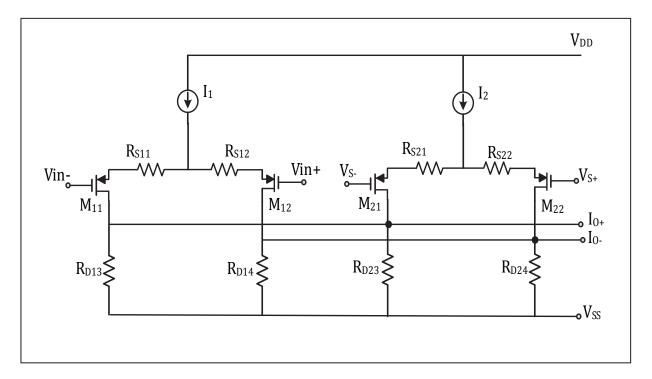

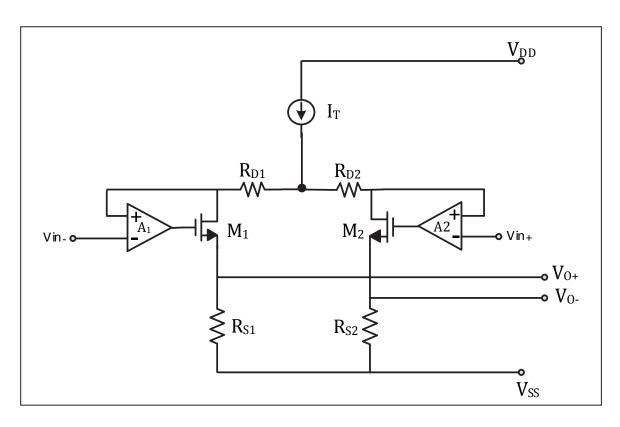

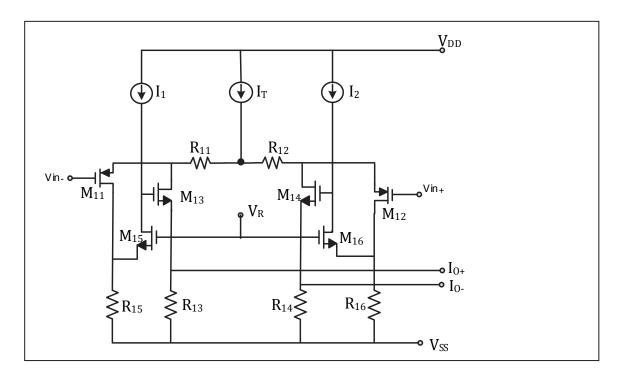

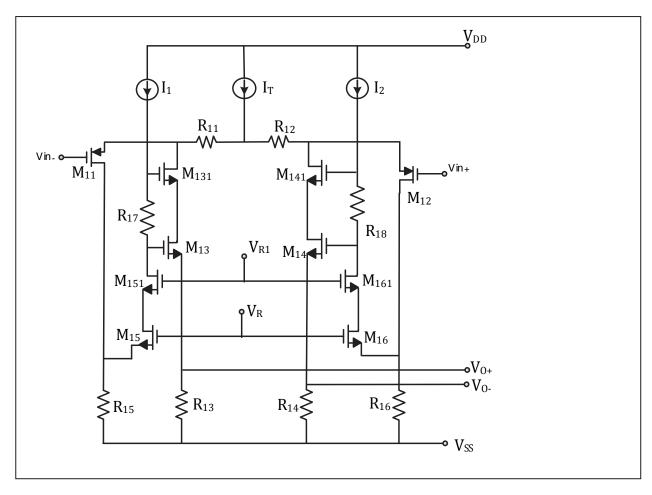

Figure 1-7 shows a basic schematic for a current feedback Inst-Amp in CMOS technology, capable of sensing the negative supply rail due to the fact that the input devices are PMOS transistors. An NMOS device at the input, with a flipped folded cascade configuration and summing node compared to the schematic of figure 1-7, would obviously sense the positive supply rail.

Figure 1-7 – Basic Schematic of a CMOS Current Feedback Instrumentation Amplifier (CFIA)

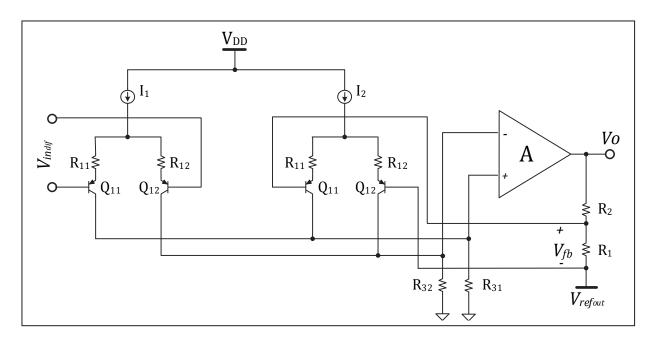

A simple pioneer bipolar version of this topology is shown in figure 1-8 [ 3 ].

Figure 1-8 – Basic Schematic of a BJT Current Feedback Instrumentation Amplifier (CFIA)

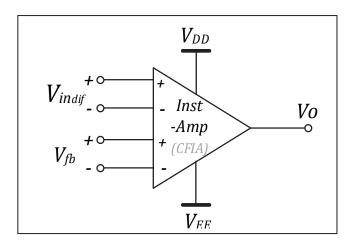

The general symbol for the CFIA is shown in figure 1-9.

Figure 1-9 – General Symbol for Current Feedback Instrumentation Amplifier (CFIA)

#### 1.3.1 Performance Limitations of Conventional CFIA Topology

Although the Current Feedback Instrumentation Amplifiers (CFIA) is a simple yet efficient topology (it could simply be just a two stage amplifier), the approach generally suffers from the same limitations common among many similar configurations that do not employ Dynamic Element Matching (DEM) or Dynamic Offset Cancellation (DOC) techniques. This is true particularly when CMOS technology is employed as the process of the choice, which more than often has been the case for long.

As will be seen in the next sections, MOS devices suffer significantly from their native mismatches when used in differential pairs at the input stages of amplifiers. This choice will certainly show a far larger input referred offset as compared to designs using their BJT counter parts. Even with BJT devices, without any sort of trim, the performance in terms of input referred offset, and noise (particularly flicker noise), is nowhere sufficient to categorize the amplifier in the class of Precision Inst-Amps or OP-Amps.

An order-of-magnitude improvement for input-referred offset can be assumed when conventional trims are employed to take care of mismatches of the input transistors of the differential pair in addition to the load devices mismatches at this stage. No matter what type of conventional trim (Wafer-Level or Post-Package trim) is used, the trim is done at only one temperature, which is almost always the room temperature. This means that the matching improvement resulting from the trim may not hold true as temperature is changed, resulting in degradation of accuracy specifications, most importantly input-referred offset.

On the other hand, the Dynamic Offset Cancellation techniques, as will be shown, not only work at room with far better accuracy, but are in effect at over temperatures as well. An improvement of two to three orders of magnitudes is common.

Table 1-1 gives a relative measure of the input referred offset specification of a general CFIA, using MOS devices, but with different offset removal techniques.

| MOS Dif. Pair Native<br>Input Ref. Offset | With Conventional Techniques | With DOC Techniques         |

|-------------------------------------------|------------------------------|-----------------------------|

| 15mV ~ 20mV                               | $0.25$ mV $\sim 1.5$ mV      | $0.2 \mu V  \sim  20 \mu V$ |

Table 1-1 – Typical Input Referred Offset Specifications for a CFIA in CMOS Technology using Different Trim Techniques

# 1.4 Challenges with Designing Precision Amplifiers in CMOS Technology, and the Aim of this Thesis

Complementary Metal Oxide Semiconductor (CMOS) Technology has been the process of choice for a few decades now, dominating the analog, mixed signal and power domains. This is due primarily to the size, cost, and ease of integration with digital portions in many mixed signal Integrated Circuit (IC) designs.

Despite the overall advantages of CMOS technology, the Metal Oxide Semiconductor (MOS) transistors are inherently inferior compared to their bipolar counterparts when used in precision analog designs.

First and foremost, the input referred offset error of a CMOS amplifier is often more than an order of magnitude worse than that of its bipolar counterpart. As a relative measure of comparison, the 1-sigma of  $\Delta Vbe$  of Bipolar Junction Transistors (BJTs) at the input differential pair is typically around  $100\mu V$  to  $150\mu V$ , whereas the 1-sigma of  $\Delta V_T$  for the MOS devices of a MOS differential pair is around 2mV to 5mV. While the 3-sigma input referred offset of a MOS input stage is around 5mV to 20mV, the same input referred offset for a BJT input stage is normally around 0.5mV to 1mV. If CMOS devices are to be used, offset reduction techniques are required to overcome this issue. The reduction, depending on the technology and technique, is often around one or two orders of magnitude. The work of this thesis "Chopper-Stabilized Auto-Zeroed Chopper Techniques" is serving this purpose.

There are other disadvantages inherent to MOS transistors. MOSFET devices, unless used in Subthreshold Region, have lower transconductance per unit drain current when compared to BJTs. This is evident from the relationship of the transconductance  $g_m$  with drain current in each device. The transconductance of MOS devices operating in strong inversion is proportional to the square root of the drain current, whereas in BJT devices the relationship is linear. The transconductance factor is a critical design parameter which sets the gain, and together with the load or feedback capacitors, determines the bandwidth of the amplifier.

Fortunately, many applications of precision amplifiers are either relatively at low frequencies (below few MHz) or DC, so the application of MOS devices in subthreshold region is not only justified but preferred. This is primarily due to the fact that Transconductance per unit Drain-Current ( $g_m/I_D$ ) is higher in Weak Inversion (WI) operation than in Strong Inversion (SI) as will be discussed in section 2.3.2, together with a discussion of the parameters affecting the Drain-Current Mismatches in MOS devices. There we conclude that for any application not requiring higher drive capability, speed, or bandwidth, the subthreshold region is considered to be the preferred region of operation for MOS devices.

MOS transistors operating below a corner frequency exhibit the famous Flicker Noise, also called (1/f) noise, which is the dominant noise source at low frequencies for such devices. Among all active semiconductors the MOS-FETs have the highest 1/f noise due to their surface conduction mechanism [2].

Although the flicker noise is heavily process dependent, factors such as geometry area WL (with inverse proportionality), gate oxide capacitance  $C_{ox}$  (with inverse proportionality), and the saturation voltage  $V_{GS} - V_T$  (with direct proportionality), can be utilized to reduced its effect.

For example, in a differential amplifier with a known tail current, increasing the aspect ratio W/L (practically increasing W) will not only help reduce the flicker noise and native offset of the devices, but also will likely push the operating region of the MOS transistors to the subthreshold region. This maximizes the transconductance per unit drain current, but care must be taken into consideration that no need for high speed operation, or bandwidth are in the way.

Since the low frequency noise is often indistinguishable from the offset itself, any attempt to reduce the offset will improve the low frequency (1/f) noise performance as well.

The work described in this Thesis aims to reduce the offset and low frequency noise in precision instrumentation amplifiers by introducing a new technique: "Chopper-Stabilized Auto-Zeroed Chopper Techniques". The approach can be used in both BJT and CMOS technologies. However due to the inherent large offset and device mismatches in CMOS technology, amplifiers made in this process are the primarily beneficiaries of the technique.

### 1.5 Organization of this Thesis

This thesis is presented in six chapters. However, chapters one to four are not the contributions of this author, but are presented just as a foundation, and to provide a history of prior arts. Advantages and disadvantages of these techniques are brought forward, with the latter being a motivation to seek for more advanced techniques to overcome the issues with the prior arts. Chapter five and six are about new and patented techniques in designing high performance operational and instrumentation amplifiers. Chapter 7 presents the conclusion and summary.

Chapter one briefly touches the dominant effect of sensing and control electronics in our daily lives. The need for accurate Gain Blocks to amplify the Sensor's weak output signal within the system is also discussed. The major requirements for such Gain Blocks along with the limitations of the flagship of the conventional approaches, the Three Op-Amp instrumentation amplifier, are described. Next the Current Feedback Instrumentation Amplifier, one of the most commonly used Inst-Amps is reviewed. A section is devoted to the major challenges of designing Precision Amplifiers in CMOS Technologies. Finally, the need for the newer techniques and the aim of this thesis is disclosed.

**Chapter two** reviews the major error sources in amplifiers, revealing the offset error as the dominant source for sensor applications. The origin of the offset error in CMOS amplifiers and the effect of random process variations are presented. Finally, the drain current mismatch and the resultant error at the input of an amplifier are discussed.

Chapter three covers techniques to reduce offset error. Several conventional methods of offset trimmings at Wafer-Level or at Post-Package are presented in short, along with general advantages of Dynamic Offset Cancellation (DOC) techniques.

**Chapter Four** deals with Dynamic Offset Cancellation techniques, emphasizing the Auto-Zeroing concept as one of the supplementary techniques used in the work of this thesis. Several methods and calibration techniques along with their advantages and disadvantages are presented.

Chapter Five covers Chopper Techniques with heavy emphasis on the work done for this thesis, primarily from a system-level perspective. The idea, the design, and their validity through descriptive mathematical modeling and formulas, or simulation support wherever needed are presented. Care is taken to limit the formulas to a manageable size and format. Complex mathematical modeling, which is impractical to be utilized in design, is generally avoided in this discussion.

#### Chapter 6

The chapter demonstrates the Realization of the "Chopper Stabilized Auto-zeroed Chopper Instrumentation Amplifiers" using CFIA topology, and presents the results.

Top-down model-Based design approach is discussed against bottom-up design in this chapter. The new patented techniques already described in chapter 5 are validated in this chapter through the model-based, as well as transistor-level designs. Finally both designs are compared against each other for harmony, and later with silicon measurements for validation.

The results of the model-based design were in agreement with the transistor-level design, and both in agreement with silicon measurement results.

## 2. Review of Major Error Sources in Op-Amps and Inst-Amps

### 2.1 Background

Real-world operational and instrumentation amplifiers contain error sources that cause their performance to differ from that predicted by the ideal models that are used to simplify the analysis of circuits involving such gain blocks.

Operational amplifiers (Op-Amps) are generally considered to be open-loop gain blocks. However, when they are used in a closed-loop configuration with negative feedback, the voltages at their inverting and non-inverting terminals are separated only by the amount of their total input-referred error, which is usually in the low mV range.

Instrumentation amplifiers, on the other hand, are generally classified as closed-loop gain blocks capable of handling a differential input voltage of a few hundred mV at their inputs, but they suffer from the same error sources as their Op-Amp counterparts.

These error sources cover a range of DC to low-frequency origins such as offset voltage and current, finite DC open-loop gain, linearity, closed loop gain, DC common mode, DC supply rejection, and flicker noise errors. A variety of AC limitations such as finite bandwidth and finite slew rate also contribute to total overall error.

The existence of such errors in both Op-Amps and Inst-Amps limit the performance of these gain blocks in precision analog circuitry, particularly when the small signals often associated with sensor's outputs must accurately be amplified and processed.

### 2.2 Major Error Sources in Op-Amps and Inst-Amps

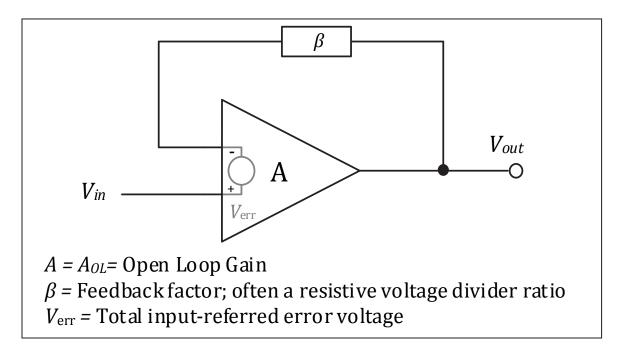

It is common to model the major error sources of the amplifiers in a closed loop circuit, in particular the DC errors, as voltage or current sources presented at the input of the amplifier as shown in figure 2-1.

Figure 2-1 shows an Op-Amp in a closed-loop negative feedback configuration with its equivalent total error source shown as  $V_{err}$ . This error source is given by [6]:

$$V_{err} = V_{os} + \frac{V_{out}}{A_{ol}} + v_{noise} + \frac{\delta V_{cm}}{H} + \frac{\delta V_{sup}}{Y} + (I_{B_{-}})(R_{S_{-}}) + (I_{B_{+}})(R_{S_{+}})$$

(2.1)

In Eq. (2.1)  $V_{os}$  is the input-referred offset voltage,  $A_{ol}$  is the open-loop gain of the Op-Amp,  $v_{noise}$  is total equivalent noise voltage at the input,  $\delta V_{CM}$ ,  $\delta V_{Sup}$ , are the changes in the common mode and supply voltages, and finally H, and Y are the common-mode rejection ratio, and power supply rejection ratios of the Op-Amp, respectively.

Figure 2-1 – Op-Amp in a Closed Loop Configuration with Errors Modeled as an Input Referred Source

$I_{B-}$ ,  $I_{B+}$ ,  $R_{s-}$ , and  $R_{s+}$  are the input bias currents to inverting and non-inverting inputs, along with the source resistances of the signal sources connected to these terminals.

Although Eq. (2.1) models the majority of the major error sources of the Op-Amp; the expression falls short of listing other important errors such as distortion, bandwidth, slew rate, linearity, etc., which are also considered as key performance characteristic parameters of amplifiers. Despite this, the equation still fairly depicts a good picture of the most important DC parameters of an Op-Amp, in particular the offset and offset-related parameters.

The errors associated with the input bias currents (the voltage drop across the source resistances of the signal sources at the input terminals of the Op-Amp) are mostly encountered in Op-Amps with bipolar junction transistors (BJT's) at the input stage.

MOS transistors do not have a DC bias current at their inputs, since they are voltage-controlled devices with capacitive elements at the input. Therefore the sixth and seventh terms of Eq. (2.1) are removed in a DC analysis if MOS devices are used for the input differential pair of the Op-Amp. Throughout this thesis, and in designing of low offset amplifiers via a new technique called "Dynamic Offset Cancellation", the focusing will be on using MOS devices as the primary choice of device.

When offset reduction is realized with a method that affects all the offset errors, the *DC CMRR* can be defined as the ratio of the change in the offset voltage due to a change in common mode voltage. It is then clear that offset performance affects the *CMRR* parameter. The same is also true for *DC PSRR*, which is then defined as the change in offset voltage due to a change in supply voltage. The above are represented by the fourth and the fifth terms of Eq. (2.1).

The noise term at low frequencies is called flicker noise, also known as 1/f noise. This error is often summed up or treated as part of the DC offset error, as it is frequently indistinguishable from the offset error itself.

The second term of Eq. (2.1) represents the input-referred error due to the finite DC open-loop gain of the Op-Amp. As this DC gain is normally very high, the effect of the error in a closed-loop circuit of low or moderate gains is usually negligible; especially when compared to the offset error itself. As will be shown, the offset error, the first error term in Eq. (2.1) is noticeably the most important one.

As an example to see the relative weight of different error terms in Eq. (2.1), we consider a rail-to-rail Op-Amp with a MOS differential pair at the input stage, with an input referred offset error of 10mV, CMRR of 80dB, PSRR of 60dB, and DC open loop gain of 10,000. If the amplifier is used in system with a  $5(1 \pm 10\%)$  V power supply, the error terms associated with Common mode change, supply change, and finite gain are 0.5mV, 1mV, 0.5mV respectively. The largest error source is still an order of magnitude less than the offset alone. This example shows that the offset error by far dominates the other error sources in MOS amplifier design.

In the following sections, we will formally define the offset and its effects on circuit performances, the origin of the error, and ways to compensate or reduce it in CMOS amplifier design.

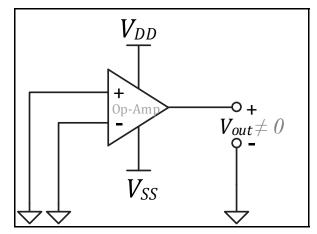

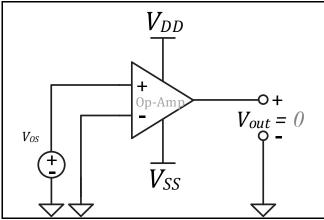

#### 2.2.1 Definition of Offset Error

If the inputs of any real world Op-Amp or Inst-Amp are shorted together at some common-mode voltage, for example ground as shown in figure 2-2 for an Op-Amp, the output will not be at zero voltage as expected. A small voltage  $V_{os}$ , called input referred offset, is needed to bring the output voltage to zero, as shown in figure 2-3.

Figure 2-2 – Real Op-Amp with a Non-Zero Output Voltage for a Zero Input Voltage

Figure 2-3 – Real Op-Amp with Offset Compensation Bringing  $V_{out}$  to Zero (Definition of Offset Error Voltage)

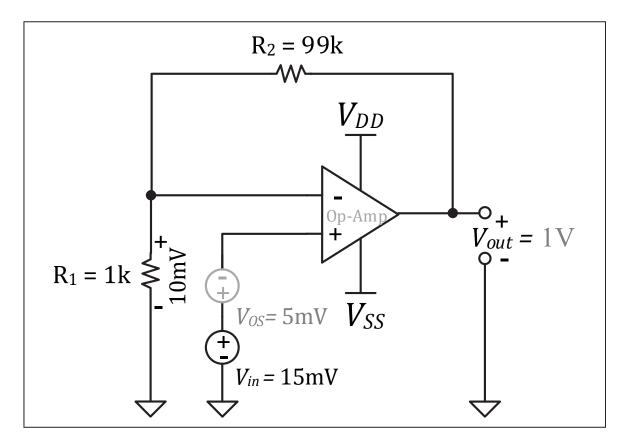

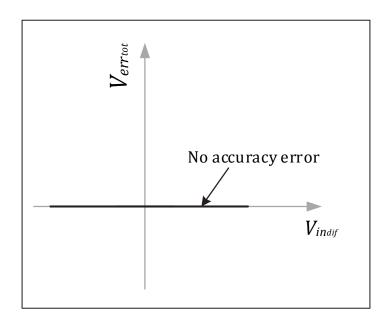

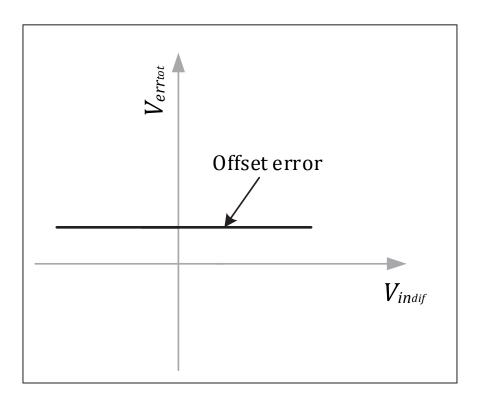

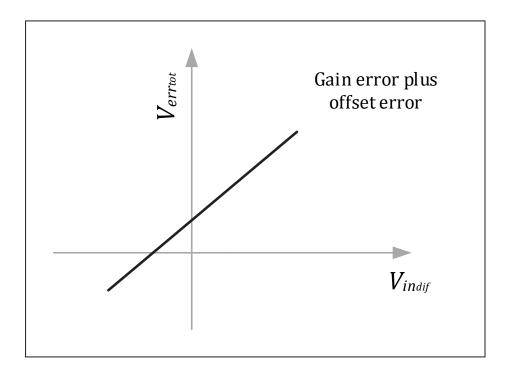

This  $V_{os}$  error can be troublesome when the task is to accurately amplify small signals. An example is shown here in which a 15mV signal is to be amplified to a gain of 100 by an Op-Amp with a 5mV offset error, used in a conventional non-inverting configuration as shown in figure 2-4. It is obvious that the 5mV offset is indistinguishable from the small DC signal itself. The resultant 10mV at the junction of the gain setting resistors generates a 1V output voltage instead of the expected 1.5V, which could be wrongly misinterpreted as if the gain was set to two-thirds of its intended value. In reality the Gain-Error (GE) is a multiplicative or slope (rotational) error, and can never be compensated by an offset error which is on the contrary an additive (or vertical shift) error within the transfer function of the gain block ( $V_{out}$  vs.,  $V_{in}$ , or alternatively the graph of the Total-Error vs. the input voltage). The concept is presented in section 3.4 with more details.

Figure 2-4 – Offset Voltage of the Op-Amp Causes a Total Error in the Output Voltage as if There Exists a Gain Error in the Circuit

## 2.3 The Origin of the Offset Error in CMOS Op-Amps and Inst-Amps

In order to know how to compensate the offset error in Op-Amps and Inst-Amps, a review of the origin of this error and the dominant contributing factors leading to offset error in CMOS amplifier design is presented. As a first step, an overview of random distribution of MOSFET parameters and their spreads is presented.

MOSFET devices have their drain currents determined by process factors such as  $\mu$ ,  $C_{ox}$ ,  $V_T$ ,  $\lambda$ , the geometry factors W and L, and the overdrive or bias condition  $(V_{GS} - V_T)$ . When a MOS device is used in the Strong Inversion (SI) region, the drain-to-source current is often given by the simple square law model as shown below.

$$I_D = \frac{\mu C_{ox}}{2} \left( \frac{W}{L} \right) (V_{GS} - V_T)^2 (1 + \lambda V_{DS}) \approx \frac{\mu C_{ox}}{2} \left( \frac{W}{L} \right) (V_{GS} - V_T)^2 = \beta (V_{GS} - V_T)^2$$

(2.2)

Here  $I_D$  is the drain (or source) current,  $\mu$  is the mobility factor,  $C_{ox}$  is the gate oxide capacitance per unit area, W, and L are width and length of the device,  $V_{GS}$  is the gate source bias voltage,  $V_T$  is threshold voltage of the MOS transistor, and finally  $\lambda$  is the channel length modulation factor, which is an indicative of small signal output resistance of the MOS device when used in saturation region. Often, the term  $(1 + \lambda V_{DS})$  is dropped, and the process and geometry factors  $\frac{\mu C_{OX} W}{2L}$  are combined, and shown as the transconductance factor  $\beta$  given in Eq. (2.2)

If the MOS device is used in Weak-Inversion (WI), which is also called sub-threshold, or exponential region, the dependence of the drain current on its  $V_{GS}$ , is more or less similar to a BJT device that is, showing an exponential relationship [7], [8], [9].

$$I_{D} = I_{D0}e^{\left(\frac{V_{GS-V_{T}}}{nk_{q}^{T}}\right)} \qquad ; \qquad I_{D0} = 2n\mu C_{ox}\frac{W}{L}V_{th}^{2} = 4n\beta V_{th}^{2}$$

(2.3)

Here  $I_D$  is the drain current,  $I_{D\theta}$  is the specific current which is a function of process and geometry of the device,  $V_{GS}$  is the gate source voltage,  $V_T$  is the MOS threshold voltage, n is the sub-threshold slope factor, k is the Boltzmann's constant (1.38 x  $10^{-23}$  J/K), T is the absolute temperature, and q is the electron charge (1.6 x  $10^{-19}$  C). The term  $V_{th} = kT/q$  is the well-known thermal voltage, which is 26mV at room (27°C or 300K).

#### 2.3.1 The Effect of Random Process Variations on Offset

Process variations in parameters affecting MOSFET drain current such as  $V_T$ , and  $\mu$ , or lithographic errors in the fine geometries of today's MOSFETs transistors create device mismatches. This is critical for devices used at the input of the differential pair, or current mirrors. These mismatches are either directly seen as the input referred offset (such as  $V_T$  mismatches), or translated to an offset voltage through the transconductance  $(g_m)$  parameter of the first stage. The tighter the control on the process (the smaller the  $\sigma$ ), the less is the input-referred offset.

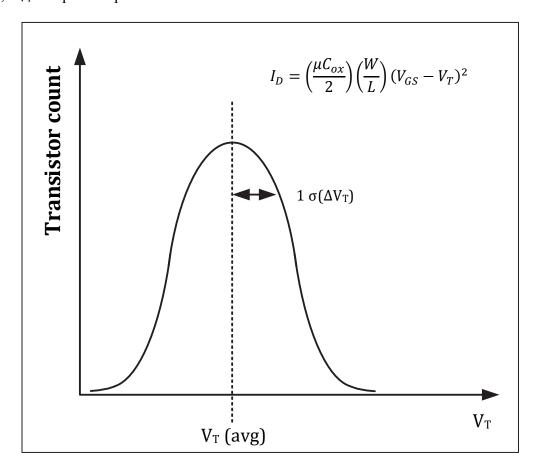

Consider a MOS Transistor biased in Strong Inversion (SI), obeying the square law of Eq. (2.2). Suppose that thousands of such devices which were laid out equally are evaluated to extract the MOSFET parameters  $V_T$ ,  $\beta$ , etc. If the number of transistors having a particular  $V_T$  for example, are graphed on a vertical axis with  $V_T$  being the horizontal axis, a Gaussian distribution is obtained with a mean value of  $V_{T(avg)}$ , and a standard deviation  $\sigma$  as a measure of spread of the parameter as shown in figure 2-5.

For a Gaussian distribution, only 0.5% of population has a  $V_T$  more than 3-sigma away from the average  $V_T$ . Experimental investigations have shown that sigma is inversely proportional to the square root of the area (WL) of the transistor [10], according to the equation:

$$\sigma(\Delta V_T) = \frac{A_{VT}}{\sqrt{WL}} \tag{2.4}$$

Where,  $A_{\rm VT}$  is a process parameter.

Figure 2-5 – Normal Distribution of Random V<sub>T</sub> Mismatch Leading to Offset Error in Applications