# Multi-port DC hub based on the Modular Multilevel Converter for Multi-terminal HVDC grids

Michalis Poikilidis

# Multi-port DC Hub based on the Modular Multilevel Converter for Multi-terminal HVDC grids

Ву

#### Michalis Poikilidis

in partial fulfilment of the requirements for the degree of

#### **Master of Science**

in Electrical Engineering

at the Delft University of Technology, to be defended publicly on Friday September 15, 2017 at 09:00 AM.

Supervisor: Prof. P. Bauer, Faculty EEMCS, TU Delft

Daily Advisor: E. Kontos, MSc., Faculty EEMCS, TU Delft

Thesis committee: Prof. P. Bauer, Faculty EEMCS, TU Delft

Dr. Ir. M. Cvetkovic, Faculty EEMCS, TU Delft

Dr. Ir. Z. Qin, Faculty EEMCS, TU Delft

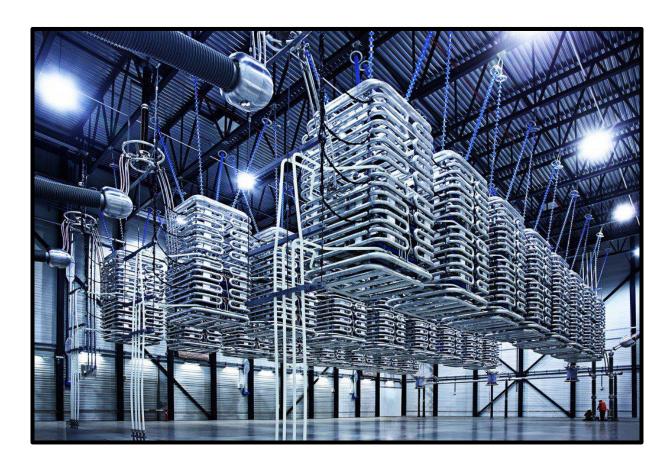

This thesis is confidential and cannot be made public until September 15, 2017. An electronic version of this thesis is available at <a href="http://repository.tudelft.nl/">http://repository.tudelft.nl/</a>. Cover picture URL: http://www.abb.com/cawp/seitp202/3c9756832c3a881cc1257f710048e9bc.aspx

${\it To the memory of my beloved grandmother,}$

Despoina

# Contents

| Abstract                                                                                  | 1    |

|-------------------------------------------------------------------------------------------|------|

| Acknowledgements                                                                          | 3    |

| 1.Introduction                                                                            | 5    |

| 1.1 Motivation                                                                            | 5    |

| 1.2 Research questions                                                                    | 6    |

| 1.3 Contributions                                                                         | 7    |

| 1.4 Thesis Outline                                                                        | 7    |

| 2.DC Hub and DC-DC Converter Topologies                                                   | 9    |

| 2.1 DC Hub Concept                                                                        | 9    |

| 2.2 DC-DC Converters for HVDC applications                                                | . 10 |

| 2.3 DC Hub Design                                                                         | . 17 |

| 3.Introduction to MMC                                                                     | 21   |

| 3.1 Introduction to Multilevel Converters                                                 |      |

| 3.2 Mathematical Model of the MMC                                                         | 26   |

| 3.3 Control Strategy of the MMC                                                           |      |

| 3.4 Modulation Techniques                                                                 | 32   |

| 4.Modeling of the MMC converter                                                           | 37   |

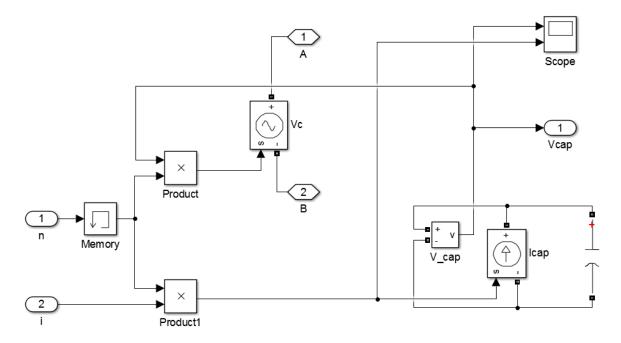

| 4.1 Averaged model of the MMC                                                             |      |

| 4.2 Calculation of the MMC parameters                                                     |      |

| 4.3 MMC control strategies                                                                |      |

| 4.4 Phase Locked Loop (PLL)                                                               |      |

| 4.5 Active/Reactive power and DC voltage controllers                                      | . 40 |

| 4.6 Inner Current Controller                                                              | 42   |

| 4.7 Circulating current controller                                                        | 43   |

| 4.8 AC Voltage controller                                                                 |      |

| 5.Case Study 1:Design of the inner AC circuit of the DC Hub                               | 47   |

| 5.1 Interconnection of HVDC lines using transformers                                      |      |

| 5.2 Power transfer capability of the MMC converter                                        | . 56 |

| 5.3 Direct interconnection of HVDC lines                                                  |      |

| 5.4 Interconnection of HVDC lines using LCL filters                                       | . 62 |

| 5.5 Conclusion.                                                                           | . 66 |

| 6.Case Study 2: Connection/Disconnection of ports and AC faults within the DC Hub         | . 67 |

| 6.1 Methodology for the connection/disconnection of ports                                 |      |

| 6.2 Methodology for clearing AC faults within the DC Hub                                  |      |

| 6.3 Methodology for clearing AC faults at the port controlling the voltage of the AC link | : 79 |

| 6.4 Expandability of the DC Hub.                                                          |      |

| 6.5 Conclusion.                                                                           | . 86 |

| 7. Case Study 3: Connection of a load or a wind farm to the AC side of the DC Hub         | . 87 |

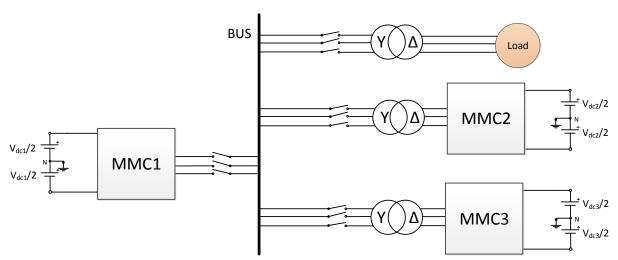

| 7.1 Load connected to the AC side of the DC hub                                           | . 87 |

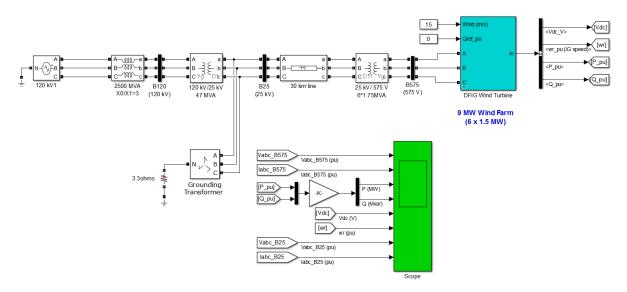

| 7.2 Wind farm connected to the AC side of the DC hub                                      | . 89 |

| 7.3 Conclusion.                                                                           | . 92 |

| 8.Conclusion-Future work                                                                  |      |

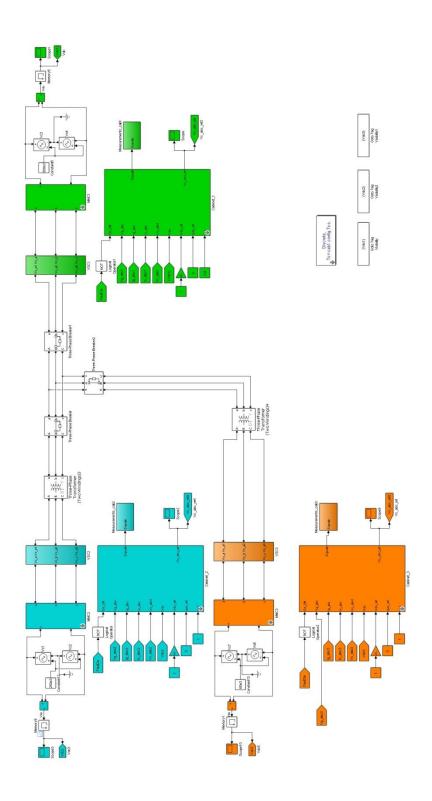

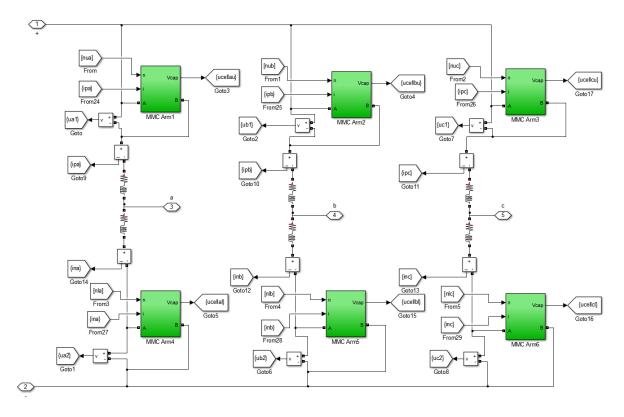

| Appendix A: Simulink model                                                                |      |

| Bibliography                                                                              |      |

### **Abstract**

It is expected that DC grids will evolve into large meshed networks, which will have multiple DC voltage levels. Two DC grids operating at different voltage levels could be interconnected using a DC-DC converter. The role of the DC-DC converter in meshed DC networks is similar to the role of a transformer in traditional AC systems. The DC-DC converter could take a range of functions in DC grids. The DC-DC converter should prevent the propagation of DC faults and should also have the ability to isolate DC faults. Because of its high cost, the DC-DC converter cannot be used as DC breaker in meshed DC grids, but it can be strategically placed in the DC grid to provide protection zone separation. In case multiple HVDC (High Voltage Direct Current) lines need to be interconnected, a multiport DC-DC converter should be used. The DC hub is a multiport DC/DC converter which consists of an inner AC circuit and AC/DC converters interfacing each HVDC line. The main goal of the DC hub is the interconnection of multiple HVDC lines operating at different voltage levels and with different DC grid configurations.

In this thesis, the operation of a DC hub based on the MMC (Modular Multilevel Converter) converter was investigated. A three-port MMC-based DC hub was simulated using *Matlab/Simulink*. An important contribution of this thesis is a comparison of different DC hub topologies which could be used for the interconnection of multiple HVDC lines. Several designs for the inner AC circuit are suggested and the advantages and disadvantages of each recommended design are described in detail. Furthermore, a methodology is presented for the clearing of AC faults within the DC hub and the protection of the system during the fault. An AC fault within the DC hub should be cleared by opening the AC circuit breaker of the faulted port. A methodology is also presented for the safe connection or disconnection of additional ports from the DC hub. Any port should be easily connected or disconnected from the DC hub without affecting the operation of the other ports. The DC hub should also offer connection points to allow the interconnection of more ports. Finally, the operation of the DC hub is investigated when generation or consumption units are connected to its inner AC circuit. In case the DC hub is used for the interconnection of multiple offshore HVDC cables, the loads of the offshore platform or a nearby offshore wind farm could be directly connected to its inner AC circuit.

With the concepts analysed in this thesis, HVDC network system designers will be able to select the most suitable DC hub topology for the interconnection of multiple HVDC lines, use a methodology for the clearing of AC faults within the DC hub, use a methodology for the safe connection or disconnection of ports and understand the design limitations of the DC hub when generation or consumption units are connected to its AC side.

# Acknowledgements

Firstly, I would like to thank my responsible professor, Prof. Pavol Bauer, for giving me the opportunity to work on this project, accepting to guide my research and trusting in me. I would also like to express my sincere gratitude to my daily supervisor, Epameinondas (Minos) Kontos for his valuable suggestions, guidance and support during this project. I hope that in the future we will have the opportunity to collaborate again.

I am also grateful to my university colleagues and friends, Charis, Thekla, Yunhe, Wenrui and Natali for their support, encouragement and all the fun, yet valuable conversations. Moreover, I would like to thank my friends Alexandros and Giannis, for their interest, constant encouragement and valuable advice. I would also like to thank all the friends I have made in Delft and Arnhem during the last two years. Every single one of you has contributed to the successful completion of this thesis, in one way or another.

A special thanks goes to my girlfriend, Anna, for believing in me, encouraging me in difficult times, making me feel special and always being by my side.

Above all, I would like to thank my parents, Giorgos and Katerina and my brothers Alexandros and Konstantinos for their love and constant encouragement. Without your help and support, nothing would have been possible for me. I thank you from the bottom of my heart.

Michalis Poikilidis

Delft, The Netherlands

September 5, 2017

### 1.Introduction

#### 1.1 Motivation

It is expected that DC grids will evolve into large meshed networks, which will have multiple DC voltage levels. For this reason, a DC/DC converter will be needed in order to interconnect two DC grids operating at different voltage levels. One possible DC/DC application could be the interconnection of DC cables (which have DC voltage up to 600 kV) with overhead lines (which may have higher DC voltage levels). Given that the existing HVDC (High Voltage Direct Current) links have wide range of highly optimized DC voltage levels, their integration into the DC grid will require DC/DC converters. It is also expected that medium-voltage DC grids (like those with offshore wind farms) will need to be integrated into the DC grid and their connection with the DC grid will require high-stepping ratio DC/DC converters. The role of the DC-DC converter in DC grids is similar to the role of the transformer in traditional AC systems [54].

A DC/DC converter is a versatile device, which can take a range of functions in DC grids. The DC/DC converter should prevent the propagation of DC faults and should also have the ability to isolate DC faults. Because of its cost, the DC-DC converter cannot be used as DC circuit breaker but it can be strategically placed in the DC grid to provide protection zone separation [54].

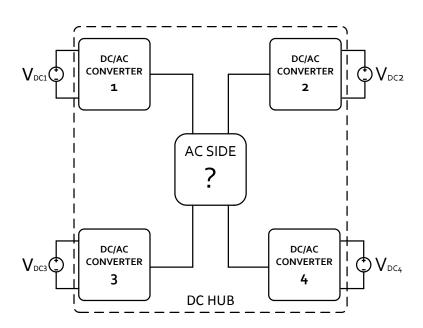

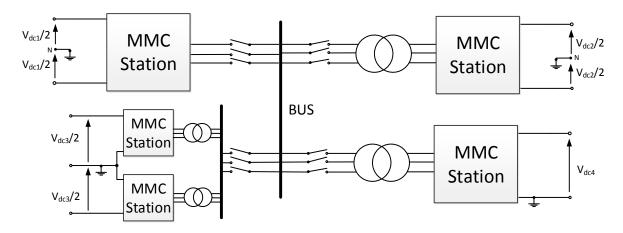

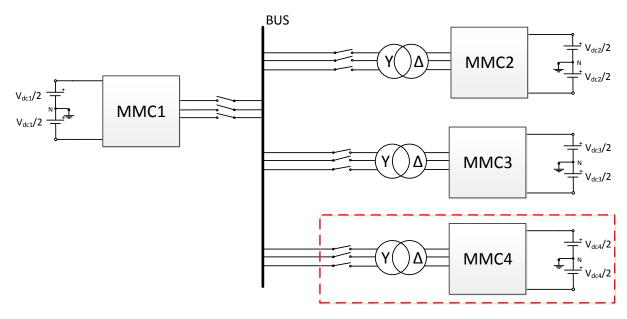

Figure 1.1 Four-port DC hub topology.

The DC hub is a multiport DC/DC converter, which consists of an inner AC circuit and AC/DC converters interfacing each DC line. Figure 1.1 shows the topology of a four-port DC hub. The inner AC circuit of the DC hub may contain transformers, LCL filters and AC circuit breakers for port isolation. The inner AC circuit should operate at high frequencies. In this way, the size of its components (filters, transformers etc) and the footprint of the system would be smaller. A multiphase topology would increase the power transfer capability of the DC hub. It would also increase its reliability and redundancy, given that a faulted phase could be replaced by a standby

phase. The inner control systems of the DC hub will be complex and they should manage the power flow and stability of the isolated inner AC circuit. The interconnected DC lines could have different voltage levels and different DC link configurations. In case a DC fault occurs at any port of the DC hub, the fault can be easily isolated by opening the mechanical AC circuit breaker of the faulted port [54].

The DC hub could be viewed as a DC transformer in DC grids, which has the following functions:

- Voltage stepping between two interconnected DC lines

- Power flow control on each DC line

- DC fault isolation on each line

- Connection points for expansion. Any number of additional DC lines can be connected to the DC hub

Multiple DC hubs will be required for large, geographically dispersed grids, but the exact number of DC hubs will be determined using complex optimization while considering technical performance, reliability, power security, costs and losses [54].

#### 1.2 Research questions

The key research questions this thesis addresses are:

- Which is the most appropriate design for the inner AC circuit of the DC hub?

- How does the connection/disconnection of a port affect the normal operation and stability of the system?

- How do AC faults within the DC hub affect the normal operation and stability of the system?

- How could the DC hub be expanded to allow the interconnection of multiple ports?

- Could generation or consumption units be connected to the inner AC circuit of the DC hub?

As mentioned in section 1.1, the main goal of the DC hub is the interconnection of multiple HVDC lines operating at different voltage levels and with different DC grid configurations. In case the voltage levels of the DC lines are different, the use of transformers may be necessary. Otherwise, in case the voltage levels of the DC lines are similar, the lines could be interconnected directly or using LCL filters. Several designs for the inner AC circuit of the DC hub will be suggested and the advantages and disadvantages of each recommended design will be described in detail. Any port should easily connect and disconnect from the DC hub without affecting the operation of the other ports. For this reason, a methodology will be presented for the safe connection or disconnection of ports. Moreover, the DC hub should offer connection points to allow the interconnection of more lines. The connection of additional ports may affect the operation of the other ports and several design limitations should be taken into account. A methodology will be presented for the connection of additional ports and the effect on the operation of the other ports will also be discussed.

Furthermore, any AC faults within the DC hub should be cleared by opening the mechanical AC circuit breaker of the faulted port. A methodology will be presented for the clearing of AC faults within the DC hub and for the protection of the system during the fault. Finally, the operation of the DC hub will be investigated when generation or consumption units are connected to its inner AC circuit. One possible application of the DC hub is the interconnection of multiple offshore HVDC cables. In this case, the loads of the offshore platform could be directly supplied by the inner AC circuit of the DC hub. Thus, the use of additional generation units for the supply of the loads of the offshore platform would not be needed. Moreover, a nearby offshore wind farm could also be connected to the AC side of the DC hub. In this manner, the use of additional offshore cables for the connection of the wind farm to the onshore grid would not be necessary and the installation cost of the wind farm would be significantly lower.

#### 1.3 Contributions

The original contributions of the thesis are listed below:

- A comparison of different DC hub topologies which could be used for the interconnection of multiple DC lines;

- A methodology for the clearing of AC faults within the DC hub;

- A methodology for the connection or disconnection of additional ports from the DC hub;

- Investigation of the operation of the DC hub when generation or consumption units are connected to its AC side.

#### 1.4 Thesis Outline

To answer the research questions and meet the objectives, the thesis is structured as follows:

Chapter 2 presents the DC hub concept and the candidate DC-DC converter topologies which could be used as the building block of the DC hub. Several DC hub topologies are suggested and the most suitable one for high power applications is indicated. Chapter 3 presents the different types of multilevel converters. This analysis is succeeded by the presentation of the mathematical model of the Modular Multilevel Converter (MMC). The chapter concludes with the presentation of the control strategy and the modulation techniques of the MMC converter. Chapter 4 presents the averaged model of the MMC converter and the different control structures which were implemented in *Matlab/Simulink*. The averaged model of the MMC is subsequently used for all the simulations in this thesis. Chapter 5 presents the different possible DC hub topologies which could be used for the interconnection of multiple DC lines operating at different voltage levels. The DC lines could be interconnected using transformers, LCL filters or directly. The advantages and disadvantages of each topology are discussed and the most suitable topology for the interconnection of DC lines operating at different voltage levels is selected. The selected topology is subsequently used for all the simulations in this thesis. In Chapter 6, a methodology is presented for the connection or

disconnection of additional ports. Moreover, a methodology is suggested for the clearing of AC faults within the DC hub and the protection of the system during the fault. The expandability of the DC hub is also investigated and the necessary actions that should be taken before and after the connection of an additional port are also analysed. In Chapter 7, the operation of the DC hub is investigated when a load or a wind farm is connected to its AC side. Chapter 8 concludes the thesis by answering the research questions which were presented in section 1.2, based on the conducted research. Finally, recommendations for future work are also given in Chapter 8.

# 2.DC Hub and DC-DC Converter Topologies

#### 2.1 DC Hub Concept

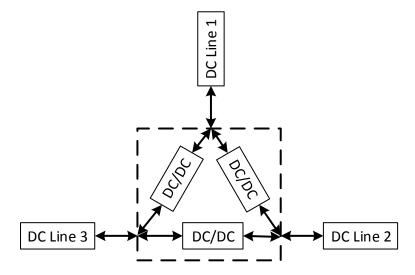

Two topologies are recommended for the interconnection of multiple HVDC lines operating at different voltage levels and with different DC grid configurations. The first alternative is to use DC-DC converters for the interconnection of each pair of lines. As can be seen in Figure 2.1, in case 3 HVDC lines must be interconnected, three DC-DC converters should be used. In this case, the power flow between the lines must be controlled by a reliable communication system. Furthermore, in case an extra HVDC line need to be connected to the DC hub, three additional DC-DC converters should be used, one for the connection of the new HVDC line to each of the existing three. Thus, the cost of this solution would be high and a complex protection mechanism would be required. As a consequence, this alternative is not reliable and has limited design modularity [35].

Figure 2.1 Multiple DC-DC converters to interconnect DC lines [35].

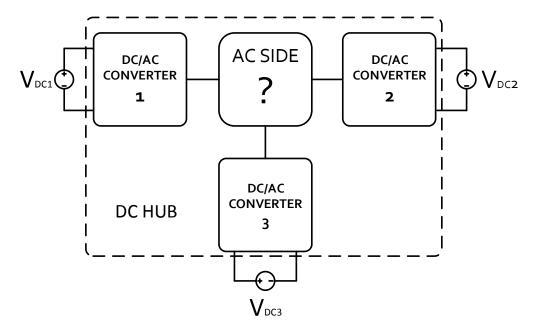

A more promising topology which assists the direct connection of all the HVDC lines on a common node can be seen in Figure 2.2. The DC hub is a multi-port DC-DC converter which is used for the interconnection of multiple ports. This topology has many advantages such as reliability and expansion capability. It can be placed in any point of the DC grid and it offers DC voltage transformation, fault ride-through ability through the common AC node and more control options. The DC hub can be used as DC transformer in DC grids, similar to the conventional AC transformer in AC grids. The main objectives of the DC hub are [35]:

- It enables the interconnection of multiple HVDC lines operating at different voltage levels and with different DC grid configurations

- Any HVDC line can controllably exchange power with any other HVDC line which is connected to the DC hub

- Any DC fault can be easily cleared by using the AC breakers of the faulted port

- Any HVDC line can be connected or disconnected from the DC hub without affecting the operation of the DC grid

Figure 2.2 DC Hub topology [35].

#### 2.2 DC-DC Converters for HVDC applications

With the increasing energy production from renewable energy resources and the development of voltage source converters, there has been an increasing interest in using multi-terminal HVDC networks and DC grids. Nowadays, DC grids are usually built by interconnecting multiple HVDC lines using DC circuit breakers. However, this topology is not suitable for large DC grids, since a DC fault at any point of the DC grid would cause voltage collapse of the entire system. DC breakers could be used for the isolation of the fault and the protection of the system, but their technology is still at an early stage and they cannot be used in high power, high voltage applications.

DC-DC converters could be used for the interconnection of multiple HVDC transmission lines operating at different voltage levels. In this manner, the propagation of DC faults within the DC grid would be prevented and the reliability of the entire system would be higher.

The DC-DC converter topology which could be used as the building block of the DC hub should have the following characteristics:

- **High power transfer capability**: the DC-DC converter should have high power rating and should be able to withstand high voltage and current stresses.

- **High transformation ratio**: the DC-DC converter should be able to interconnect HVDC lines operating at different voltage levels.

- Bidirectional power transfer capability: the DC-DC converter should be able to transfer power in both directions, since the interconnected HVDC lines exchange power and any HVDC line could either export or import power from the interconnected system.

• **Modularity**: The topology of the multiport DC-DC converter should offer connection points to allow the interconnection of more lines.

The DC-DC converters can be categorized as:

- Two-stage (or front-to-front) converters

- One-stage converters

In the two-stage converter topology, the DC lines are interconnected through an intermediate AC link and two DC/AC converters are used. In the one-stage topology, there is no distinct AC link. The main advantage of the one-stage topology is that only one converter is used. As a consequence, the number of semiconductor devices is lower, resulting in lower weight, cost and volume. However, the one-stage converters do not have modular structure and thus, cannot be used as the building block of the DC Hub. For this reason, only two-stage converters will be studied.

Several DC-DC converter topologies which could be used in high power applications are recommended in the literature. Some of the these topologies are the following:

- Hard switched full bridge converter [5]

- Phase-shift full bridge converter [5]

- Series load resonant converter [5]

- Parallel load resonant converter [5]

- Dual active bridge converter [5]

- Thyristor based resonant converter [5]

- HVDC-DC auto transformer (HVDC-AT) [6]

- Push-pull M2DC [7]

- Three-phase dual-active bridge converter [7]

However, these DC-DC converter topologies do not meet all the aforementioned criteria and thus, they cannot be used as the building block of the DC hub. The most promising DC-DC converters which could be used as the building block of the DC hub are presented in the following part of this section.

#### High power IGBT-based DC/DC converter

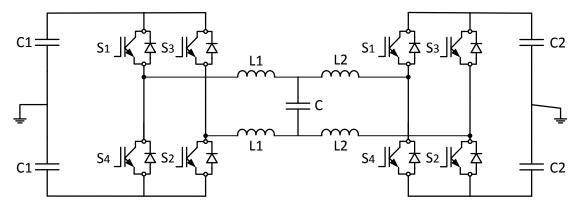

A bidirectional DC-DC converter with an LCL filter in the intermediate AC link was introduced in [34]. Although it is a promising topology, it uses thyristors. As a result, its efficiency is low, its controllability is limited and the system cannot be easily expanded to interconnect multiple DC lines. For this reason, as shown in Figure 2.3, the thyristors were replaced by IGBTs to increase the efficiency of the system [72].

Figure 2.3 High power IGBT-based DC/DC converter [35].

With the appropriate design of the LCL filter, the cost of the L,C components can be kept low and the converter has the ability to keep control even under the worst-case faults. Furthermore, the voltage stresses on the switching devices is low and comparable to the converter topologies using transformers. The ripple of the DC current and the maximum power transfer capability of the converter depend on the number of phases [72]. One drawback of this topology is that it steps the DC voltage symmetrically around the mid-point and thus, it cannot be used with asymmetric monopolar HVDC configuration. Finally, another drawback is that it exhibits low efficiency in small transformation ratios compared to the topologies using transformers.

This converter type has high and bidirectional power transfer capability. It also supports the interconnection of multiple HVDC lines and an additional HVDC line can be easily connected to the intermediate AC link though a dedicated AC/DC converter. However, it exhibits low efficiencies in small transformation ratios and thus, it cannot be used as the building block of the DC Hub.

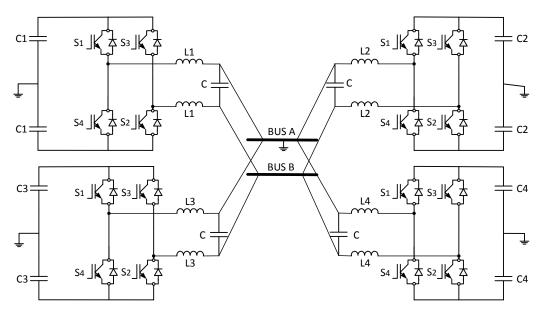

#### **High Power, low Ratio DC-DC Converter**

The topology of the high power, low ratio DC-DC converter can be seen in Figure 2.4. This converter type consists of two 3-phase DC-AC converters. The AC sides of the converters are directly connected without using transformer. Due to the absence of transformer, the cost of this topology is low. As can be seen in Figure 2.4, each phase leg of the DC-AC converter consists of two arms. Each arm consists of series connected full bridge submodules (red elements), a Director Switch (blue elements) and an inductor. The full-bridge submodules are rated for the maximum DC voltage of the system whereas the Director Switch is rated for the maximum DC voltage of the system plus an offset voltage that could result from a DC fault in the system. As a consequence, even without galvanic isolation, a DC fault cannot propagate from one DC side of the system to the other [8].

Each DC-AC converter comprises three phases. In case high power has to be transferred, a multiphase connection could be utilized. The frequency of the AC link should not necessarily be 50 Hz. Higher frequencies, such as 350 Hz, could be used in order to minimize the components size (eg. submodule capacitance). Moreover, given that no load is connected to the intermediate AC link, the waveform of the AC voltage should not necessarily be sinusoidal. Other waveshapes, such as trapezoidal or square-wave could be used. In this manner, both converter losses and components ratings could be optimized [8].

Figure 2.4 High Power, low Ratio DC-DC Converter [8].

In case the voltage levels of the DC lines are much different, a circulating DC current will flow between the two DC systems through the AC link, increasing this way the losses of the system. For this reason, this topology is only suitable for the interconnection of DC lines operating at similar voltage levels.

To summarize, this converter type has bidirectional and high power transfer capability. Due to the absence of transformer, the cost of the system is low. This topology is also suitable for the interconnection of multiple HVDC lines since an additional HVDC line can be easily connected to the AC link through a dedicated DC-AC converter. However, this topology cannot be used when the voltage levels of the DC lines are much different and it is only suitable for low transformation ratio applications. Thus, it could be used as the building block of the DC hub only in case the voltage levels of the DC lines are similar. Otherwise, the efficiency of the system would be significantly reduced.

#### LCC/VSC DC-DC Converter

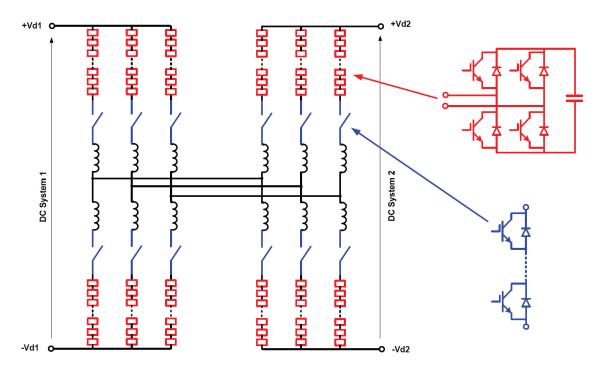

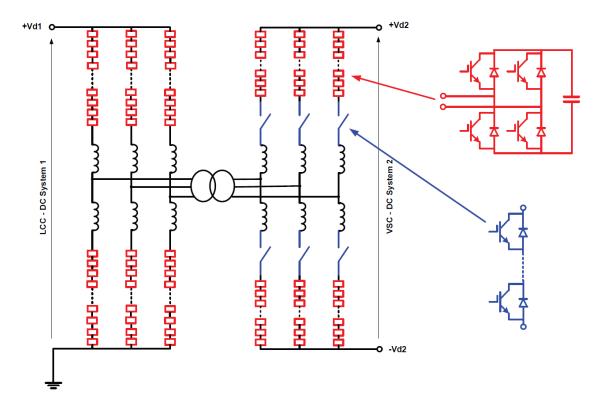

The circuit diagram of the LCC/VSC DC-DC converter can be seen in Figure 2.5. This DC-DC converter type consists of an LCC DC-AC converter and a VSC DC-AC converter. The AC sides of the converters are connected through a three phase transformer. In case high power has to be transferred, a multiphase AC connection could be utilized. On the other hand, single phase connection could be used for medium power transfer levels.

The VSC converter always keeps the same voltage polarity whilst the power transfer can be reversed by changing the direction of the DC current. On the other hand, in the LLC scheme, the direction of the power transfer can be reversed by changing the polarity of the DC voltage [8].

As can be seen in Figure 2.5, each phase leg of the VSC converter consists of two arms. Each arm consists of series connected full-bridge submodules (red elements), a Director Switch (blue element) and an inductor. The Director Switch is rated for the DC voltage  $V_{d2}$ . On the other hand, as shown in the same figure, each arm of the LCC converter consists of series connected full-bridge submodules and an inductor. Given that each full bridge submodule can provide both positive and negative DC voltage, energy can be transferred from the DC side of the LCC to the AC link irrespective of the polarity of the DC voltage  $V_{d1}$  [8].

Figure 2.5 LCC/VSC DC-DC Converter [8].

The frequency of the AC voltage should not necessarily be 50 Hz. Higher frequencies, such as 350 Hz, could be used. In this way, the size of the transformer and the submodule capacitors could be reduced. However, the selection of a high operating frequency would increase the losses of the converter and thus, its efficiency would be reduced. As a result, the selection of the operating frequency of the intermediate AC link will be a trade-off between the footprint of the system and the efficiency of the converter.

This converter type has high and bidirectional power transfer capability. It also has high transformation ratio and thus, it enables the interconnection of multiple HVDC lines operating at different voltage levels. For this reason, it could be used as the building block of the DC hub. However, the VSC technology is usually preferred over the LCC. Finally, this converter type could not be used in applications in which all the interconnected DC lines have firm voltages.

#### **MMC-based LCL DC-DC Converter**

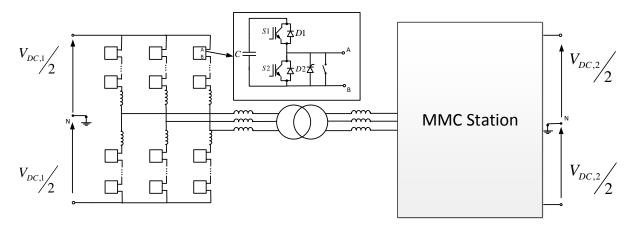

The Modular Multilevel Converter (MMC) offers higher reliability, better power transfer quality and higher efficiency. Having modular structure, it aids the DC-DC converter to have high efficiency for all transformation ratios. An MMC-based LCL converter was presented in [74] with unity transformation ratio, high efficiency and fault ride-through capability. The topology of the MMC-based LCL DC-DC converter can be seen in Figure 2.6.

Figure 2.6 MMC-based LCL DC-DC converter [35].

This converter type has high and bidirectional power transfer capability. It is also suitable for the interconnection of multiple HVDC lines. However, it exhibits low efficiency in high transformation ratios, as will be explained in detail in Chapter 5. For this reason, it can be used as the building block of a DC hub which interconnects multiple HVDC lines operating at similar voltage levels.

#### Isolated modular DC-DC converter

The MMC-based DC-DC converter topology using transformer can be seen in Figure 2.7. The main advantages of this topology over the two level DAB topology are the lower switching losses and the lower voltage stresses on the isolation transformer. Moreover, at black start and during DC faults, the full modulation index is available for the control of the voltage of the AC link. The use of the isolation transformer minimizes the circulating reactive power in the AC link and offers better switching utilization. The main drawback of the suggested topology is the larger footprint due to the use of the transformer. Different AC frequency levels and AC voltage waveforms could be used. The selection of the operating frequency will be a compromise between the footprint of the converter and its efficiency (recommended range 300-500 Hz). The selection of the AC voltage level will also be a trade-off between the volume and the efficiency of the converter. The higher the AC voltage level, the higher the number of series-connected power devices will be (cell capacitors, IGBTs, diodes). On the other hand, low AC voltage values lead to high AC current values, and thus, to lower efficiency (considering constant power transfer level). The AC voltage waveform could be different than sinusoidal, such as triangular or trapezoidal, since no loads are connected to the AC link and the quality of the AC voltage is not very important. The main advantage of using trapezoidal voltage waveform is the lower submodule capacitor energy requirements, and thus, the smaller footprint of the system [75].

Figure 2.7 Isolated modular DC-DC converter [35].

The suggested DC-DC converter topology has high and bidirectional power transfer capability. Due to the use of transformer, it can be used for the interconnection of multiple HVDC lines operating at different voltage levels. Therefore, this DC-DC converter topology could be used as the building block of the DC Hub.

#### **Alternate Arm MMC**

The alternate arm converter could replace the traditional MMC converter in one at least of the ports of the DC-DC converter topology. The recommended topology is presented in Figure 2.8 [15]. The design of this topology leads to more efficient devices utilization because there is no path for circulating currents. Furthermore, the voltage rating of the converter is lower due to the fact that the voltage is shared between the switches and the wave shaping circuit. In contrast to the traditional MMC, the alternate arm MMC has DC fault blocking capability and smaller footprint. However, its efficiency is lower due to the larger number of switches in the conduction path.

This DC-DC converter topology has high and bidirectional power transfer capability. It is also suitable for the interconnection of multiple HVDC lines operating at different voltage levels and thus, it could be used as the building block of the DC hub.

Overall, the review of the DC-DC converter topologies showed that a few designs could be used as the building block of the DC hub. The most promising design is the MMC-based DC-DC converter. In case there is need for galvanic isolation and the voltage levels of the interconnected DC lines are different, a transformer could be placed in the intermediate AC link. The use of transformer offers better switching devices utilization and minimizes the circulating reactive power in the AC link, especially in case the DC voltage levels of the interconnected DC lines are much different. On the downside, the use of transformer increases the volume, weight and cost of the system.

Figure 2.8 DC-DC converter using alternate arm MMC [35].

#### 2.3 DC Hub Design

Several topologies have been proposed in the literature for the realization of the DC Hub. A DC Hub topology based on the IGBT-based DC-DC converter can be seen in Figure 2.9 [13]. As shown in Figure 2.9, this topology comprises LCL filters and mechanical AC breakers. The active and reactive power at each port can be independently controlled by controlling the dq components of the AC current of each converter. With the appropriate design of the LCL filter, the reactive power at each port can be maintained at zero. In this way, the power transfer capability of each port becomes maximal. The operating frequency of the intermediate AC link must be chosen further away from the resonance frequency in order to avoid undesired oscillations. Moreover, the selection of the L,C parameters of the filter is based on the voltage and power of each port. It implies that any HVDC line can be easily connected or disconnected from the common AC link without affecting the operation of the others. Finally, the suggested topology has fault ride-through capability and can be easily expanded to allow the interconnection of multiple ports. Due to the fact that transformers are not used, the footprint and cost of the system are low. On the downside, no galvanic isolation is present and the switching devices utilization is not the best possible.

Figure 2.9 Four-port DC Hub using 2-level VSC converters and LCL filters [35].

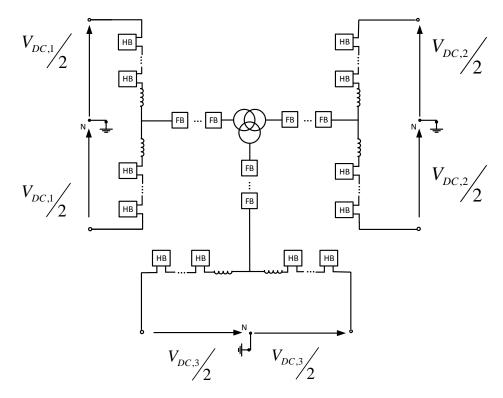

Another possible DC hub topology is presented in Figure 2.10 [76]. Three hybrid MMC converters are interconnected through a three-winding transformer which is placed in the intermediate AC link. A chain-link of full-bridge submodules is connected on each phase of each half-bridge MMC converter. Therefore, each MMC converter has the ability to ride-through DC faults. Regarding the control structure, one converter should be responsible for the control of the voltage of the intermediate AC link, while the other two converters could operate either in DC voltage or in active power control mode. In case a fault occurs at any of the ports, only the faulted port should be disconnected from the DC hub, while the other ports could continue their operation without interruption. Finally, the design of the three-winding transformer is demanding and increases the footprint of the system, while the modularity is compromised because only one transformer is used. In case a fourth port need to be connected to the DC Hub, a fourth winding should be added to the central transformer, making the design and the expansion of the system complicated.

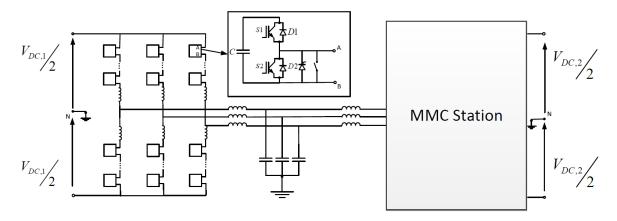

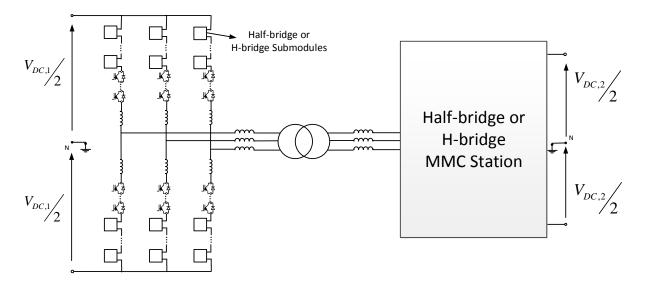

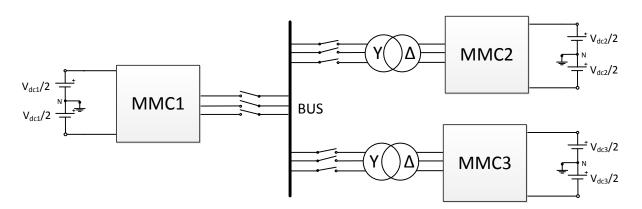

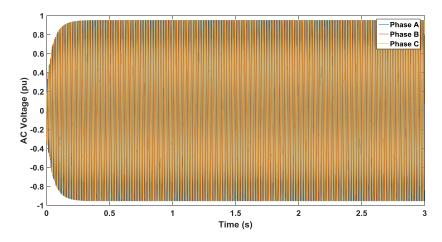

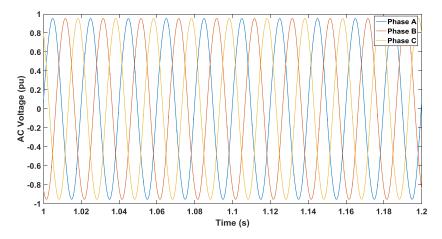

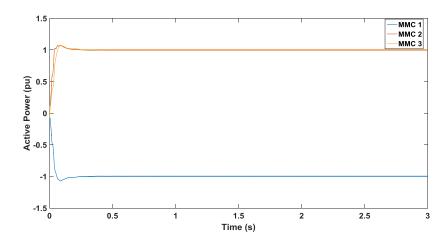

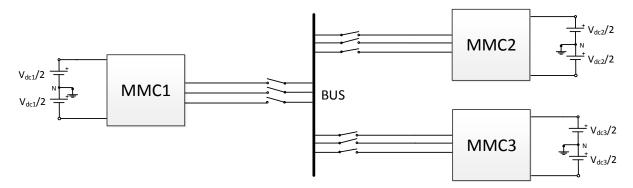

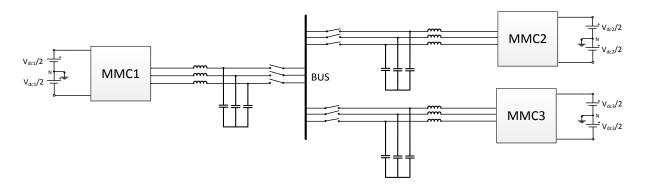

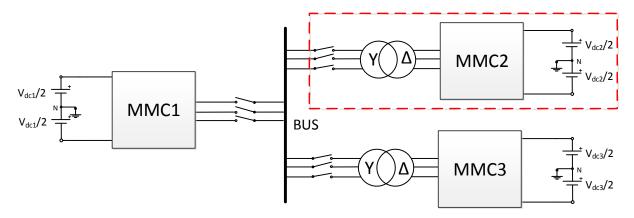

The most promising DC hub topology is shown in Figure 2.11 [52]. This topology is based on the multiport front-to-front type DC-DC converter. In this four-port DC Hub topology, each HVDC line is connected to the common AC bus through a dedicated MMC converter. Each port may also have a transformer if needed and a mechanical AC circuit breaker. As shown in Figure 2.11, the suggested topology can be used for the interconnection of ports with different DC line configurations. Concerning the control structure, one port should be responsible for the control of the voltage of the common AC bus, while the other ports could operate either in DC voltage or in active power control mode. The reference angle for the rotating dq frame is provided by a global voltage-controlled oscillator. The system is able to ride-through DC faults due to the use of self-blocking submodules at 50% of the converters and half-bridge submodules at the other 50%. However, the semiconductor needs of an MMC using self-blocking submodules are 25% higher compared to an MMC using half-bridge submodules. Finally, the system can be easily expanded to include additional ports. However, as the number of ports increases, the footprint of the system also increases due to the use of additional transformers. As a consequence, the use of this DC hub topology is not recommended for offshore applications.

Figure 2.10 Three-port DC Hub using hybrid MMC and three-winding transformer [35].

Figure 2.11 Four-port MMC-based DC Hub interconnecting different DC link configurations [35].

## 3.Introduction to MMC

This chapter starts with the description of the two-level voltage source converters (VSC). Then, the main advantages of the multilevel converters over the two-level converters are analysed. Finally, the mathematical model, the control strategy and the modulation techniques of the MMC converter are described in detail.

#### 3.1 Introduction to Multilevel Converters

#### **Two-level VSC converter**

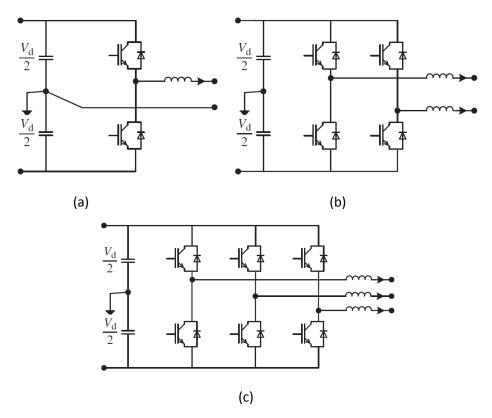

The different topologies of two-level VSC converters only differing in terms of the number of phase legs are shown in Figure 3.1.

Figure 3.1 Two-level VSC converters with different number of phase legs [1].

As shown in Figure 3.1, all the VSC topologies are equipped with a DC capacitor which maintains the DC voltage of the converter constant. The terminals of this capacitor form the DC terminals of the converter. A number of phase legs are connected in parallel to these terminals. Each phase leg is equipped with two semiconductor valves connected in series. Each semiconductor valve consists of a unidirectional controllable switch (IGBT) and an anti-parallel diode. In this manner, the semiconductor valve is able to conduct current in both directions and block voltage in one direction by controlling the gate signal of the switch. The AC terminals of the converter are formed between the midpoints of the phase legs. An inductance is usually connected in series with the AC terminals of the converter to filter out the AC currents and to keep them fairly constant in the short time interval between the commutation of the phase legs [1].

As can be seen in Figure 3.1, the AC terminal of the converter can be connected to either the positive or the negative DC terminal. When the upper semiconductor switch of the phase leg is conducting, the AC terminal is connected to the positive DC terminal and thus, the output voltage is positive  $(+V_d/2)$ . On the other hand, when the lower semiconductor switch of the phase leg is conducting, the AC terminal is connected to the negative DC terminal and thus, the output voltage is negative  $(-V_d/2)$ . It should be mentioned that the upper and lower semiconductor valves of each phase leg cannot conduct simultaneously, as it would cause a short-circuit across the DC capacitor and it would be detrimental for the converter.

By using the switching sequence described above, the potential at the AC terminal can be switched from one of the DC terminals to the other at any desired instant and thus, the converter can behave as a controllable voltage source. Using appropriate repetitive switching, a desired AC side voltage can be achieved. This methodology is known as *pulse-width modulation* (PWM) [1]. Due to the PWM modulation technique, the AC voltage and thus, the AC current will contain a significant amount of higher-order harmonics. As mentioned before, the inductor which is connected in series with the AC terminal will filter out these harmonic components and will maintain the output current fairly constant in the short time interval between the commutation of the phase legs.

#### **Benefits of Multilevel Converters**

The two-level VSC converters have a simple structure with low number of components and are suitable for low power and voltage applications. Thus, they cannot be used in high power and voltage applications because of the following drawbacks [1]:

- The AC side voltage of the VSC converter will contain a significant amount of harmonic components around multiples of the switching frequency. The selection of a high switching frequency could offer a solution to this problem, since only high-order harmonics would appear in the spectrum. In this case, smaller AC filters could be used. However, the selection of a high switching frequency would increase the switching losses. For this reason, the selection of the switching frequency is a trade-off between the harmonic distortion of the output AC voltage (size of the AC filters) and the switching losses (efficiency of the converter).

- The maximum blocking voltage of the available power semiconductors used in VSC converters is a couple of kilovolts. In case a two-level VSC converter must be used in high voltage applications, a high number of power semiconductors should be connected in series. However, there are not available technical solutions to achieve such series connection.

- In two-level VSC converters, the AC phase voltage is always switched between the DC terminals. In order to keep the switching losses to relatively low levels, the switching operation should be very fast. In high voltage applications, the voltage slope will be high and thus, the stress on the insulation of the equipment connected to the AC side will also be high.

A transition to multilevel converters could offer many advantages. At first, multilevel converters have more than one DC link capacitors. Thus, the blocking capability requirements of each semiconductor valve depend on the individual capacitor voltages and not on the full DC link voltage. Thus, the power

rating of the converter can be increased without direct series connection of semiconductor elements. At second, the output AC voltage has more than two levels. Therefore, the harmonic distortion of the AC voltage is lower and the amplitude of the harmonics is significantly reduced. Moreover, the frequency at which the output voltage is changed can be increased without increasing the value of the switching frequency. As a result, the harmonics in the spectrum will appear at higher frequencies where they can be easily filtered out by smaller AC filters [1].

#### **Multilevel Converter Topologies**

Some of the most popular multilevel converter topologies are:

- Neutral-Point Clamped (NPC) converter [3]

- Flying Capacitor (FC) converter [3]

- Cascaded H-Bridge (CHB) converter [3]

- Modular Multilevel Converter (MMC)

#### **Modular Multilevel Converter**

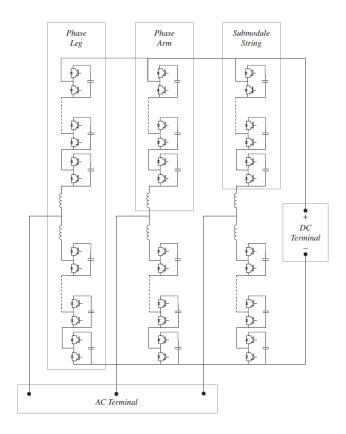

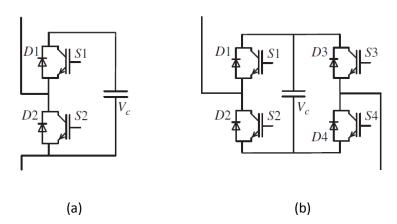

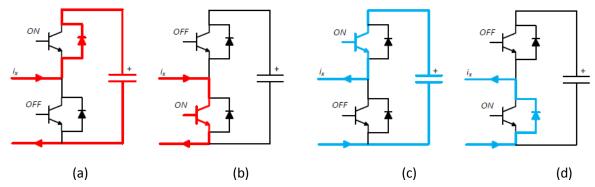

The topology of the Modular Multilevel Converter (MMC) is shown in Figure 3.2. As can be seen in Figure 3.2, the fundamental building block of the MMC is the submodule. The most commonly used types of submodules are the half-bridge and the full-bridge submodules. The circuit diagram of each type of submodule is presented in Figure 3.3. The half-bridge submodule topology is the most commonly used in bidirectional power flow applications. As shown in Figure 3.3, the half-bridge submodule consists of one two-level phase leg which is connected in parallel with a DC capacitor. The external terminals of the submodule are formed by the phase leg midpoint on the one hand and one of the DC capacitor terminals on the other hand [1].

The series connection of submodules in one phase forms the leg of the converter, as shown in Figure 3.2. Each leg consists of the upper and lower arms, and the number of submodules per arm is the same. The common point connection between the upper and lower arms constitutes the AC terminal of the MMC converter. Given that the total DC voltage is equally divided among the submodule capacitors of each phase leg, there is no need for bulky DC link capacitors. Finally, an inductor is placed in each arm of the phase leg to limit the circulating current and the arm overcurrents in case of fault [3].

Figure 3.2 Three-phase Modular Multilevel Converter [1].

Figure 3.3 Converter submodules: half bridge (a) and full-bridge (b) [1].

For the purpose of this study, the term submodule refers to the half-bridge topology. The submodule capacitor acts as DC voltage source, the switches are responsible for the insertion of the submodule capacitors into the arm and the anti-parallel diodes ensure uninterruptable flow of the current [3].

Each submodule has two states depending on the conduction state of the switches. As can be seen in Figure 3.3, when switch S1 is ON and switch S2 is OFF, the submodule is inserted into the arm and the voltage across the submodule is equal to the voltage of the inner capacitor. On the other hand, when switch S1 is OFF and switch S2 is ON, the submodule is bypassed and the voltage across the submodule is zero. It should be mentioned that switches S1 and S2 cannot be ON simultaneously, as it would cause a short circuit across the submodule capacitor. The different switching states of a half bridge submodule can be seen in Figure 3.4. By controlling the number of the inserted submodules, a staircase output voltage waveform can be generated at the AC terminals of the converter.

Figure 3.4 Different switching states of half-bridge submodule [3].

The direction of the arm current affects the state of charge of the submodule capacitors. As can be seen in Figure 3.4, in case the submodule capacitor is inserted into the arm, a positive current will charge the capacitor whereas a negative current will discharge the capacitor. In case the submodule capacitor is by-passed, its voltage will remain constant [3].

The switching states of the submodule are shown in Table 3.1. When both switches S1 and S2 are OFF, the submodule consists of two diodes and a submodule capacitor. In this case, if the arm current is positive, it will flow through the upper diode, charging this way the capacitor. This state of operation can be used for the initial charging of the submodule capacitors [3].

| State of S1 | State of S2 | Submodule terminal voltage | Polarity of arm current | Status of the capacitor |

|-------------|-------------|----------------------------|-------------------------|-------------------------|

| ON          | OFF         | V <sub>C</sub>             | +                       | Charging                |

| OFF         | ON          | 0                          | +                       | By-passed               |

| ON          | OFF         | V <sub>C</sub>             | -                       | Discharging             |

| OFF         | ON          | 0                          | -                       | By-passed               |

| ON          | ON          | Capacitor Shorted          |                         |                         |

| OFF         | OFF         | Open Circuit               |                         |                         |

**Table 3.1** Switching states of the submodule [3].

The main advantages of the MMC converter are [3]:

- Modularity. The series connection of multiple submodules in each arm of the converter decreases the power and voltage ratings of the semiconductor devices (diodes, switches) and submodule capacitors. In other words, the converter can be easily scaled to high power and voltage levels.

- Better AC voltage quality. The output voltage has more than two levels. As a result, the harmonic distortion of the output voltage is lower and the amplitude of the harmonics is significantly reduced.

- Redundancy. Redundant submodules can be used in case of submodule failures.

- Higher efficiency. The frequency at which the output voltage is changed can be increased without increasing the switching frequency. Thus, the low switching frequency of each submodule results in increased efficiency of the converter.

- Reduced footprint. Smaller filters can be used, because the harmonic distortion of the output AC voltage is lower. Moreover, there is no need for bulky DC link capacitors.

Due to the aforementioned advantages, the MMC topology is the most commonly used in HVDC applications.

#### 3.2 Mathematical Model of the MMC

The simplified topology of an MMC converter can be seen in Figure 3.2 [2]. Three levels can be observed:

- a) The submodules (Level I)

- b) The arm (Level II)

- c) The phase leg (Level III)

In order to fully understand the operation of the MMC, a continuous model should be derived based on its voltage-current equations. Using the continuous model of the MMC, a method could be developed for the control of the upper and lower arm voltages of the converter [2].

Considering that each arm consists of N submodules, each arm can be controlled by an insertion index n(t). When n(t)=1, all the submodules are inserted into the arm. When n(t)=0, all the submodules are bypassed.

The ideal capacitance of the arm is given by:

$$C^{arm} = \frac{C}{N} \tag{3.1}$$

where C is the submodule capacitance.

The effective capacitance of the arm depends on the insertion index and can be expressed as:

$$C^m = \frac{C^{arm}}{n(t)} \tag{3.2}$$

where the index m corresponds to the number of the arm (in a three-phase converter m=1,2,...,6).

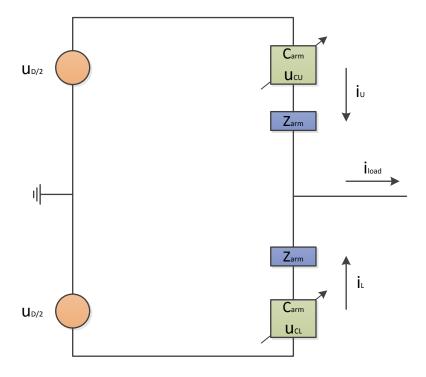

The development of the control schemes of the MMC could be based on its full representation, including the operation of each submodule. However, this approach would be complicated. Instead, the continuous model could be used as a base for the development of the control structure of the MMC. A simplified circuit which represents the overall operation of the MMC can be seen in Figure 3.5.

Figure 3.5 Simplified circuit of the MMC converter.

As mentioned before, the index m represents the number of the arm, n(t) is the insertion index and  $u_c^{\Sigma}(t)$  is the sum of all the submodule capacitor voltages in the m arm.

$$u_C^m = n(t) u_C^{\Sigma}(t) \tag{3.3}$$

$$\frac{du_C^{\Sigma}(t)}{dt} = \frac{i(t)}{C^m} \tag{3.4}$$

As shown in Figure 3.5,  $i_U$  is the upper arm current and  $i_L$  is the lower arm current. The output current  $i_{load}$  is equal to the sum of the upper and lower arm currents. The current  $i_{diff}$  represents the circulating current that flows between the phase leg and the DC link or between two phase legs. The aforementioned relations can be written as

$$i_U = \frac{i_{load}}{2} + i_{diff} \tag{3.5}$$

$$i_L = \frac{i_{load}}{2} - i_{diff} \tag{3.6}$$

$$i_{load} = i_U + i_L \tag{3.7}$$

$$i_{diff} = \frac{i_U - i_L}{2} \tag{3.8}$$

In the ideal condition, the contributions of the arm currents  $i_U$  and  $i_L$  to the output current  $i_{load}$  should be equal and the difference current  $i_{diff}$  should be zero. In case the equivalent capacitances of the upper and lower arms of a phase leg are not equally charged, the difference current  $i_{diff}$  will be different than zero. In this case, the appropriate control of the difference current  $i_{diff}$  can lead to equal distribution of the total charge among the submodule capacitors of each phase leg. For the purpose of this analysis, it is assumed that the sum of the submodule capacitor voltages of each arm is equal to the DC link voltage  $u_D$ .

Equation (3.4) can now be rewritten as

$$\frac{du_{CU}^{\Sigma}(t)}{dt} = \frac{n_U i_U}{C^{arm}} \tag{3.9}$$

$$\frac{du_{CL}^{\Sigma}(t)}{dt} = -\frac{n_L i_L}{C^{arm}} \tag{3.10}$$

By applying the Kirchhoff voltage equations in the simplified circuit of the MMC shown in Figure 3.5, the following equations can be derived

$$\frac{u_D}{2} - Ri_U - L\frac{di_U}{dt} - n_U u_{CU}^{\Sigma} = u_{load}$$

(3.11)

$$-\frac{u_D}{2} - Ri_L - L\frac{di_L}{dt} + n_L u_{CL}^{\Sigma} = u_{load}$$

(3.12)

The expression for the calculation of the difference current  $i_{diff}$  can be re-written as

$$i_U - i_L = 2i_{diff} \tag{3.13}$$

The derivative of Equation (3.13) yields

$$\frac{di_U}{dt} - \frac{di_L}{dt} = 2\frac{di_{diff}}{dt} \tag{3.14}$$

Using Equations (3.11) and (3.12), Equation (3.14) can be re-written as:

$$\frac{di_{diff}}{dt} = \frac{u_D}{2L} - \frac{R}{L}i_{diff} - \frac{n_U}{2L}u_{CU}^{\Sigma} - \frac{n_L}{2L}u_{CL}^{\Sigma}$$

(3.15)

From Equations (3.5)-(3.10), the following dynamic equations for the upper and lower arm voltages can be derived:

$$\frac{du_{CU}^{\Sigma}}{dt} = \frac{n_U}{C^{arm}} i_{diff} + \frac{n_U}{2C^{arm}} i_{load}$$

(3.16)

$$\frac{du_{CL}^{\Sigma}}{dt} = \frac{n_L}{C^{arm}} i_{diff} - \frac{n_L}{2C^{arm}} i_{load}$$

(3.17)

As can be seen from Equations (3.16) and (3.17), when the difference current  $i_{diff}$  is equal to zero, the load current  $i_{load}$  is proportional to the time derivative of the upper and lower arm voltages. In other words, the load current causes the unbalance in the arm voltages. In steady state operation, the output current  $i_{load}$ , having sinusoidal waveform, fluctuates between positive and negative values. As a consequence, the time derivative of the upper and lower arm voltages also changes. Ideally, the arm voltage oscillates around a constant average value. However, the operation of the converter is not ideal. Power losses and other factors may lead to instability. As a result, the presence of the difference current is necessary for the safe operation of the converter [2].

Using Equations (3.15), (3.16) and (3.17), a dynamic and continuous model for the MMC converter can be derived:

$$\frac{d}{dt} \begin{bmatrix} i_{diff} \\ u_{CU}^{\Sigma} \\ u_{CL}^{\Sigma} \end{bmatrix} = \begin{bmatrix} -\frac{R}{L} & -\frac{n_{U}}{2L} & -\frac{n_{L}}{2L} \\ \frac{n_{U}}{C^{arm}} & 0 & 0 \\ \frac{n_{L}}{C^{arm}} & 0 & 0 \end{bmatrix} \begin{bmatrix} i_{diff} \\ u_{CU}^{\Sigma} \\ u_{CL}^{\Sigma} \end{bmatrix} + \begin{bmatrix} \frac{u_{D}}{2} \\ \frac{n_{U}i_{load}}{2C^{arm}} \\ -\frac{n_{L}i_{load}}{2C^{arm}} \end{bmatrix}$$

(3.18)

Given that the desired output voltage should be sinusoidal, the reference signal for modulation should also be sinusoidal and can be given by

$$m(t) = \widehat{m}\cos(\omega_N t) \tag{3.19}$$

The desired output voltage can be given by

$$u_{load}(t) = \frac{u_D}{2} m(t) \tag{3.20}$$

Assuming that the load current  $i_{load}$  is also sinusoidal, it can be expressed as

$$i_{load}(t) = \hat{i}_{load}\cos(\omega_N t + \theta) \tag{3.21}$$

where  $\theta$  is the phase difference between the output voltage and the output current.

The modulation indices for the upper and lower arms can be written as

$$n_U(t) = \frac{1 - m(t)}{2} \tag{3.22}$$

$$n_L(t) = \frac{1 + m(t)}{2} \tag{3.23}$$

As can be seen from Equations (3.22) and (3.23), the sum of the modulation indices  $n_U(t)$  and  $n_L(t)$  is always equal to one. It implies that the sum of the upper and lower arm voltages should always be equal to the DC link voltage  $u_D$ , assuming that the capacitor voltages of the upper and lower arms are equal to the reference value.

In reality, the capacitor voltages of the upper and lower arms will not be exactly equal to the reference value. There will always be a difference between the DC link voltage and the sum of the

upper and lower arm voltages. Due to this difference voltage, a difference current will circulate between the DC link and the phase leg of the converter. The appropriate control of this difference current is crucial for achieving equal sharing of the DC link voltage among the submodule capacitors of each phase leg of the converter.

In order to create the difference voltage  $u_{diff}$ , and thus the difference current  $i_{diff}$ , an offset voltage should be added to the upper and lower arm voltages. The addition of the offset voltage does not affect the output voltage of the converter since the output voltage depends on the difference between the upper and lower arm voltages. However, it will affect the difference current  $i_{diff}$ .

#### 3.3 Control Strategy of the MMC

From Equations (3.11) and (3.12), the following equations can be derived

$$u_{load} = \frac{u_{CU} - u_{CL}}{2} - \frac{R}{2}i_{load} - \frac{L}{2}\frac{di_{load}}{dt}$$

(3.24)

$$L\frac{di_{diff}}{dt} + Ri_{diff} = \frac{u_D}{2} - \frac{u_{CL} + u_{CU}}{2}$$

(3.25)

From Equations (3.24) and (3.25), the following conclusions can be drawn:

- The output voltage  $u_{load}$  depends only on the output current  $i_{load}$  and the difference between the upper and lower arm voltages  $u_{CU} u_{CL}$ .

- The term  $\frac{u_D}{2} \frac{u_{CL} + u_{CU}}{2}$  acts as an alternating voltage source, R and L as a passive impedance for the alternating current  $i_{diff}$ .

- The difference current  $i_{diff}$  depends only on the DC link voltage  $u_D$  and the sum of the upper and lower arm voltages  $u_{CL} + u_{CU}$ .

As mentioned in section 3.2, the addition of an offset voltage to the upper and lower arm voltages will not affect the output voltage  $u_{load}$ . However, it will influence the difference current  $i_{diff}$ .

From Equations (3.5) and (3.11), the following equation can be derived

$$\frac{u_D}{2} - \frac{R}{2}i_{load} - Ri_{diff} - \frac{L}{2}\frac{di_{load}}{dt} - L\frac{di_{diff}}{dt} - u_{CU} = u_{load}$$

(3.26)

Equation (3.26) can be rewritten as

$$u_{CU} = \frac{u_D}{2} - u_{load} - \frac{R}{2}i_{load} - \frac{L}{2}\frac{di_{load}}{dt} - Ri_{diff} - L\frac{di_{diff}}{dt}$$

(3.27)

Equation (3.24) can be rewritten as

$$u_{load} + \frac{R}{2}i_{load} + \frac{L}{2}\frac{di_{load}}{dt} = \frac{u_{CL} - u_{CU}}{2} = e_{load}$$

(3.28)

Using Equation (3.28), Equation (3.27) can be rewritten as

$$u_{CU} = \frac{u_D}{2} - e_{load} - u_{diff} \tag{3.29}$$

By following exactly the same procedure,  $u_{CL}$  can be expressed as

$$u_{CL} = \frac{u_D}{2} + e_{load} - u_{diff} \tag{3.30}$$

where  $u_{diff}$  can be given by

$$u_{diff} = Ri_{diff} + L\frac{di_{diff}}{dt} \tag{3.31}$$

The influence of the difference voltage ( $u_{diff}$ ) on the upper and lower arm voltages ( $u_{CU}$  and  $u_{CL}$ ) can be expressed by Equations (3.29) and (3.30).

The quantity  $e_{load}$  is equal to the output voltage  $u_{load}$  and is defined as

$$e_{load} = \frac{u_{CL} - u_{CU}}{2} \tag{3.32}$$

In order to derive a suitable control strategy for determining the value of the difference voltage  $u_{diff}$ , the energy stored in the equivalent upper and lower arm capacitances should be introduced.

Considering that the energy stored in each arm is equally shared between the submodule capacitors, the energy of the upper and lower arms of each phase leg can be given by

$$W_{CU}^{\Sigma} = N \left[ \frac{C}{2} \left( \frac{u_{CU}^{\Sigma}}{N} \right)^{2} \right] = \frac{C}{2N} (u_{CU}^{\Sigma})^{2} = \frac{C^{arm}}{2} (u_{CU}^{\Sigma})^{2}$$

(3.33)

$$W_{CL}^{\Sigma} = N \left[ \frac{C}{2} \left( \frac{u_{CL}^{\Sigma}}{N} \right)^{2} \right] = \frac{C}{2N} (u_{CL}^{\Sigma})^{2} = \frac{C^{arm}}{2} (u_{CL}^{\Sigma})^{2}$$

(3.34)

The power is the time derivative of the energy. Therefore, the power of the upper and lower arms can be expressed as

$$\frac{dW_{CU}^{\Sigma}}{dt} = i_U u_{CU} = \left(\frac{i_{load}}{2} + i_{diff}\right) \left(\frac{u_D}{2} - e_{load} - u_{diff}\right)$$

(3.35)

$$\frac{dW_{CL}^{\Sigma}}{dt} = -i_L u_{CL} = \left(-\frac{i_{load}}{2} + i_{diff}\right) \left(\frac{u_D}{2} + e_{load} - u_{diff}\right) \tag{3.36}$$

The total energy stored in a phase leg is

$$W_C^{\Sigma} = W_{CU}^{\Sigma} + W_{CL}^{\Sigma} \tag{3.37}$$

The difference between the energy stored in the upper and lower arms is

$$W_c^{\Delta} = W_{CU}^{\Sigma} - W_{CL}^{\Sigma} \tag{3.38}$$

Differentiating Equations (3.37) and (3.38) and using Equations (3.35) and (3.36), the power of the upper and lower arms can be written as

$$\frac{dW_C^{\Sigma}}{dt} = (u_D - 2u_{diff})i_{diff} - e_{load}i_{load}$$

(3.39)

$$\frac{dW_C^{\Delta}}{dt} = \left(\frac{u_D}{2} - u_{diff}\right)i_{load} - 2e_{load}i_{diff} \tag{3.40}$$

Supposing that the difference current  $i_{diff}$  has only a DC component, the quantity  $u_D i_{diff}$  represents the power which is delivered to the AC side (load and submodule capacitors). The quantity  $u_{diff}i_{diff}$  represents the power losses on the arm resistance R and the variation of the magnetic energy in the arm inductance L. The quantity  $e_{load}i_{load}$  represents the power which is delivered to the load. As can be seen from Equation (3.40), the DC component of the difference current  $i_{diff}$  does not affect the difference between the energy which is stored in the upper and lower arms of the converter, since the output voltage  $e_{load}$  has no DC components. For this reason, the DC component of the difference current  $i_{diff}$  can be used for the control of the total energy which is stored in each phase leg of the converter [2]. Moreover, the AC component of the difference current  $i_{diff}$ , having the same fundamental frequency with the output current  $i_{load}$ , could be used to control the distribution of the capacitor energy between the upper and lower arms of each phase leg. In fact, the quantity  $e_{load}$   $i_{diff}$  has a DC component which can be used to force the energy difference between the upper and lower arms to change.

## 3.4 Modulation Techniques

There are two different types of modulation techniques:

- PWM with carrier wave Level and Phase Shifted

- Nearest Level Control

#### PWM methods with carrier wave – Level and Phase Shifted

The carrier-based PWM methods are based on the comparison of a reference signal with a high frequency triangular signal (carrier waveform). The carrier waveform can be either bipolar or unipolar. The switching instants are determined by the intersections of the reference signal and the carrier waveform [3].

In case of the MMC, each carrier is assigned to a particular submodule of the phase leg of the converter. This technique allows independent submodule control and modulation.

There are two types of carrier-based modulation methods:

- I. The Level Shifted Carrier (LSC)-PWM

- II. The Phase Shifted Carrier (PSC)-PWM

In the Level Shifted Carrier (LSC)-PWM method, the amplitude of the carriers is divided with N and an offset is added to each carrier. The number of carrier signals is N-1, and all the carriers have the same amplitude and frequency. Several ways of phase shifting the level-shifted carriers with respect to each other have been proposed in the literature.

The most commonly used methods are:

- Phase disposition (PD): carriers have the same phase angle and only differ in terms of a level offset [1].

- Phase opposition disposition (POD): carriers above zero level are  $\pi$  rad phase shifted with respect to those below zero [1].

- Alternative phase opposition disposition (APOD): alternating phase shifts of zero and  $\pi$  rad are used so that adjacent carriers will be in anti-phase [1].

In the Phase Shifted Carrier (PSC)-PWM method, the amplitude of the carriers is identical, while each carrier has a different phase. An advantage of this method is that each submodule is switched with the same frequency. As a consequence, the switching losses are better distributed among the submodules of the converter [4]. This method has N-1 carrier signals with the same amplitude and frequency. A staircase multilevel output waveform can be obtained by applying the following phase shift between the carriers:

$$\theta = \frac{360^o}{N - 1} \tag{3.41}$$

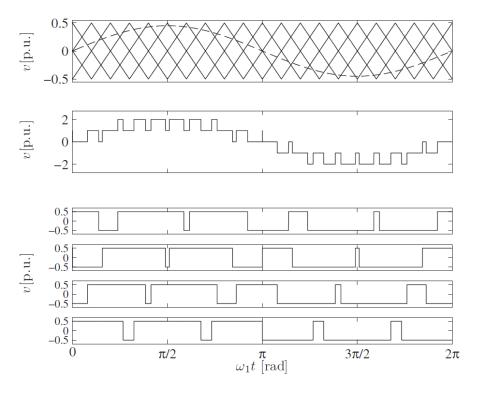

The waveforms of the carrier signals, the reference signal and the multilevel output signal can be seen in Figure 3.6. As mentioned before, this method provides equal duty and power allocation among the submodule capacitors. Thus, capacitor voltage balancing can be achieved by selecting the appropriate carrier frequency [3]. For this reason, the Phase Shifted Carrier - PWM method is usually preferred over the Level Shifted Carrier – PWM method.

**Figure 3.6** Phase Shifted Carrier (PSC)-PWM method. First diagram (upper): carriers and reference waveform, Second diagram: modulated output voltage waveform, Third diagram (lower): two-level modulated waveforms [1].

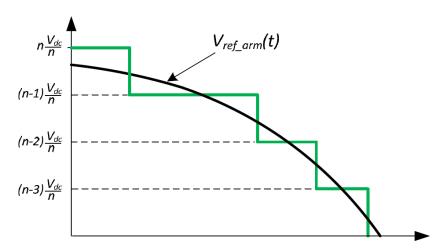

#### **Nearest Level Control (NLC)**

The main idea behind NLC is to sample the reference signal at high frequency and to approximate it with the nearest available level. Supposing that the submodule capacitor voltages are constant and equal to  $V_C = u_D/N$ , the converter arms can produce the following N+1 voltage levels:  $0, u_D/N, ..., u_D$ . The number of submodule capacitors which should be inserted and bypassed can be given by the following formulas [3]

$$n_{on,u} = round \left[ N \left( \frac{1}{2} - \frac{u_{ref}(t)}{u_D} \right) \right]$$

(3.42)

$$n_{off,u} = N - n_{on,u} \tag{3.43}$$

$$n_{on,l} = round \left[ N \left( \frac{1}{2} + \frac{u_{ref}(t)}{u_D} \right) \right]$$

(3.44)

$$n_{off,l} = N - n_{on,l} \tag{3.45}$$

The function round(x) is defined as [1]

$$round(x) = \begin{cases} floor(x) & x < floor(x) + 0.5\\ ceil(x) & x \ge floor(x) + 0.5 \end{cases}$$

(3.46)

where floor(x) is the largest integer lower than x and ceil(x) is the lowest integer higher than x. As a result, the output voltage waveform becomes a staircase. The insertion and bypassing of submodules generates an output AC voltage which is very close to the reference waveform. This technique is recommended for the control of MMC converters with high number of submodules due to the low switching frequency and the small voltage steps [3]. The waveforms of the output staircase voltage and the reference voltage can be seen in Figure 3.7.

Figure 3.7 Nearest Level Modulation (NLC), output voltage waveform-reference waveform [3].

To summarize, the PWM method is a widely used technique to control power electronic converters. In case of the MMC, the most commonly used techniques to control the switching operation of the submodules are the Carrier-less and the Carrier-Based methods. In the Carrier-less methods (NLC), the reference is approximated by the nearest level resulting in a staircase output which determines directly the number of submodules which should be inserted. In the Carrier-Based methods (LSC-PWM, PSC-PWM), a high frequency carrier is assigned to each submodule. In Level-Shifted PWM, an offset is added to each carrier, whereas in Phase-Shifted PWM, the phase of the carriers is shifted [4].

According to [4], when the number of submodules per arm is above 12, the use of the NLC method is recommended due to the lower switching frequency. However, in case the number of submodules per arm is below 12, the Carrier-based methods are preferable because they generate output voltage of better quality.

# 4. Modeling of the MMC converter

#### 4.1 Averaged model of the MMC

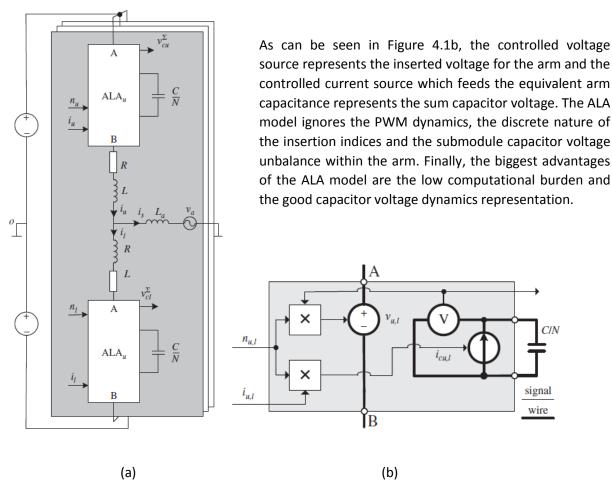

The MMC converters which are used in HVDC applications usually include hundreds of submodules per arm. In case the detailed model of the MMC is used for the modelling of the system, the computational effort will be enormous. For this reason, averaged models of MMCs are used, which provide satisfactory dynamic properties (as the detailed models). In this project, the Arm-Level Averaged (ALA) Model of the MMC converter was used. In this model, each converter arm is represented by an aggregated ideal voltage source averaged over the switching period. The inputs of the ALA model are the insertion indices and the arm currents of the converter. The insertion indices are assumed continuous in the range [0,1]. The equivalent electrical circuit of the converter leg and the ALA arm model can be seen in Figures 4.1a and 4.1b [1].

Figure 4.1 ALA model (a) Electrical circuit (b) ALA arm model [1].

#### 4.2 Calculation of the MMC parameters

The input parameters of the MMC model which was implemented in Simulink are:

- the number of phases (M)

- the DC voltage  $(V_d)$

- the amplitude of the line-to-neutral AC voltage  $(V_{SMax})$

- the rated power of the converter ( $S_{rated}$ )

- the amplitude of the output current  $(I_{sMax} = (2 \cdot S_{rated})/(M \cdot V_{sMax}))$

- the operating frequency  $(f_{qrid})$

The MMC parameters which were calculated based on the input parameters are:

- the grid angular frequency (rad/s):  $\omega_1 = 2 \cdot \pi \cdot f_{grid}$

- the rated energy storage capability of the converter:  $W_{rated} = 30 \cdot 10^{-3} J/VA$

- the arm inductance (8% of base impedance-[H]):  $L = (0.16 \cdot V_{sMax})/(\omega_1 \cdot I_{sMax})$

- the arm resistance (10% of X-[ $\Omega$ ]):  $R = 0.1 \cdot L \cdot \omega_1$

- the submodule capacitance (F):  $C = (N \cdot 2 \cdot W_{rated} \cdot S_{rated})/6/{V_d}^2$

- the equivalent arm capacitance for ALA type model (F):  $C_{arm} = C/N$

- the average voltage of each submodule (V):  $V_{sm} = V_d/N$

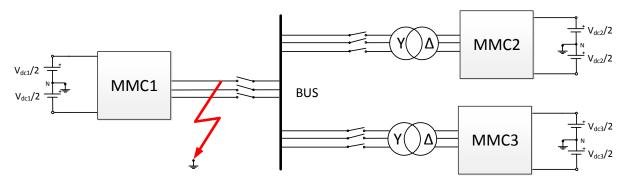

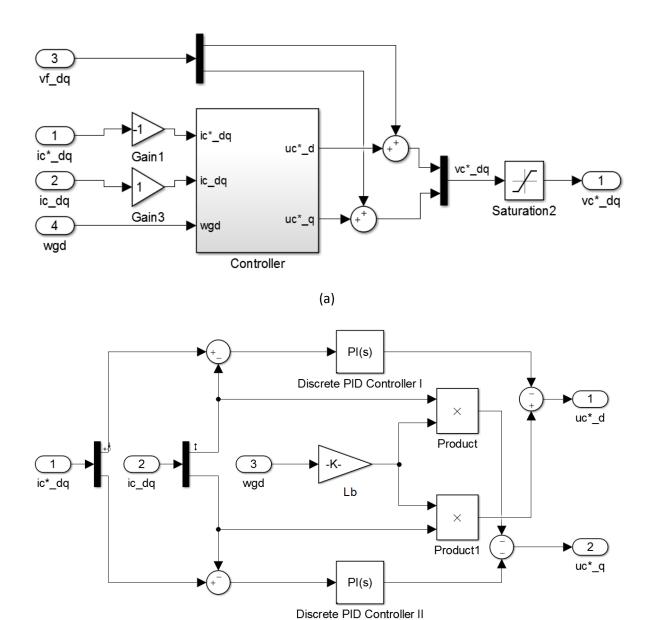

#### 4.3 MMC control strategies

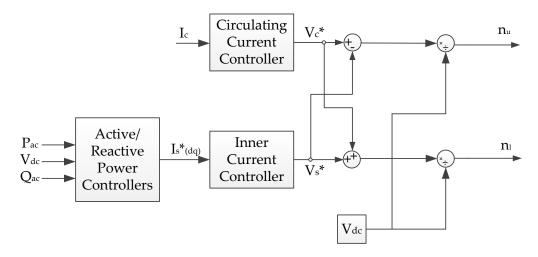

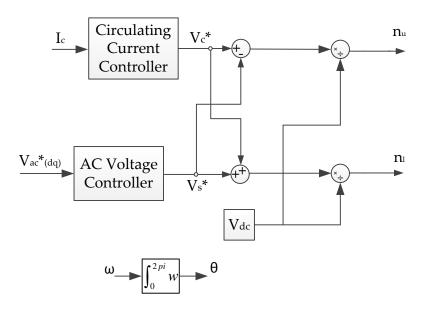

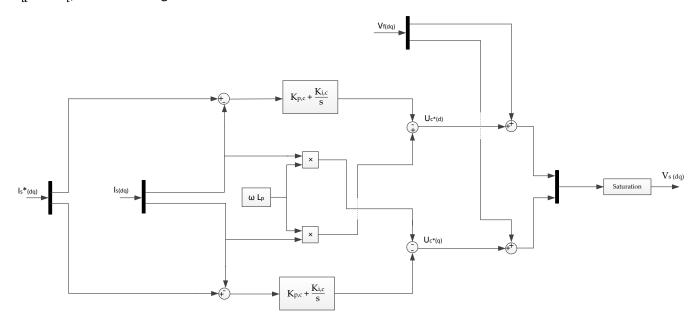

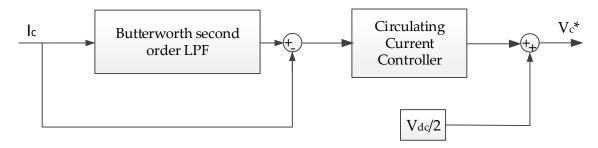

In this section, the main control structures of the MMC which were implemented in Matlab/Simulink will be presented. As mentioned in Chapter 2, in a three-port DC Hub topology, one MMC should be responsible for controlling the voltage of the intermediate AC link, while the other two MMCs should operate in active power or in DC voltage control mode. The control system of an MMC operating in active power  $(P_{ac})$  or in DC voltage  $(V_{dc})$  control mode can be seen in Figure 4.2, while the control system of an MMC operating in AC voltage  $(V_{ac})$  control mode can be seen in Figure 4.3. The insertion indices  $n_u$  and  $n_l$  of the MMC are defined as

$$n_u = \frac{V_c^* - V_s^*}{V_{dc}} \tag{4.1}$$

$$n_l = \frac{V_c^* + V_s^*}{V_{dc}} \tag{4.2}$$

where  $V_s^*$  is the voltage which drives the output current,  $V_c^*$  is the voltage which drives the circulating current and  $V_{dc}$  is the voltage on the DC side of the converter.

It is assumed that the insertion indices are continuous in the range [0,1]. Irrespective of the control mode in which the MMC operates, its control can be achieved by controlling the values of the insertions indices. In this manner, the number of submodule capacitors which are inserted into each arm of the converter can be controlled at all times.

In the following, the control structure of the MMC and the tuning process of each individual controller will be described in detail.

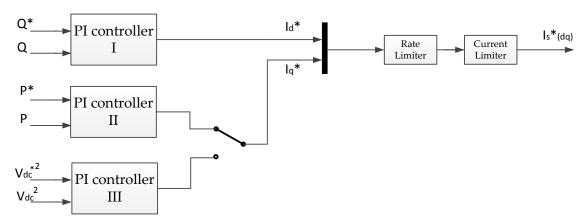

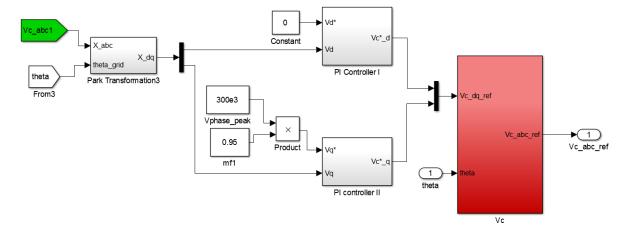

Figure 4.2 Control system of an MMC working in active power or in DC voltage control mode.

Figure 4.3 Control system of an MMC working in AC voltage control mode.

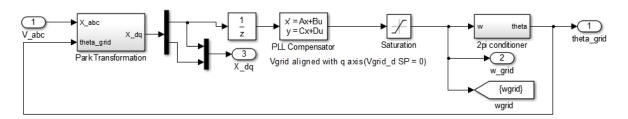

# 4.4 Phase Locked Loop (PLL)

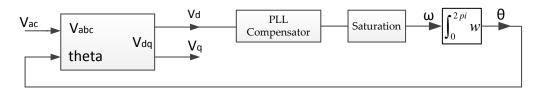

PLLs are commonly found in radio-frequency electronic systems where they are used for synchronization purposes. The PLL in a converter control system is also used for performing synchronization. More specifically, the output AC voltage of the MMC is measured and it is transformed into the dq system (Park transformation). Then, the d component of the voltage is controlled at zero. In this way, the rotating vector of the AC voltage of the MMC can be aligned with the q axis. This synchronization makes the control of the active power and DC voltage of the converter simpler as will be explained in the following sections of this chapter. The block diagram of the PLL which was implemented in Matlab/Simulink can be seen in Figure 4.4.

**Figure 4.4** Phase Locked Loop (PLL)-Synchronization with the q axis of the AC voltage.

It should be mentioned that the use of a PLL is necessary only in case the MMC converter operates in active power or in DC voltage control mode. In case the MMC works in AC voltage control mode, the value of the rotating angle *theta* of the output AC voltage can be manually set by selecting the desired value of the angular frequency  $\omega$ , as shown in Figure 4.3.

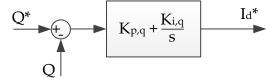

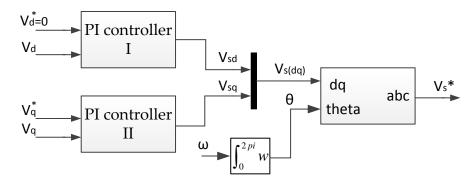

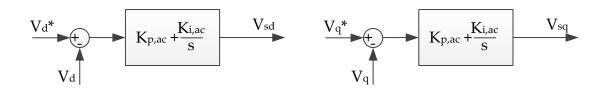

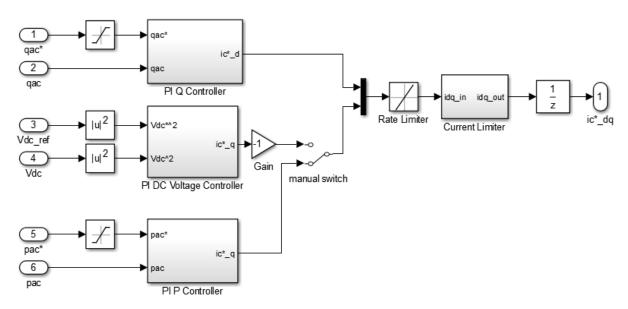

#### 4.5 Active/Reactive power and DC voltage controllers

In this section, the active/reactive power and DC voltage controllers will be analysed. These controllers receive as input the reference of the active/reactive power or DC voltage of the MMC and give as output the d and q components of the output current. The diagram of this controller can be seen in Figure 4.5.

Figure 4.5 Active/reactive power and DC voltage controller.

As described in the previous section, the PLL is responsible for aligning the rotating vector of the AC voltage of the MMC with the q axis of the rotating dq frame. As a consequence, the d component of the AC voltage will be zero ( $V_d$ =0). The active and reactive power from a periodic set of three-phase voltages and currents expressed in the dq0 reference frame can be expressed as:

$$P = \frac{3}{2} (V_d I_d + V_q I_q) \tag{4.3}$$

$$Q = \frac{3}{2} (V_q I_d - V_d I_q) \tag{4.4}$$

Given that  $V_d = 0$ , Equations (4.3) and (4.4) can be rewritten as

$$P = \frac{3}{2}V_q I_q \tag{4.5}$$

$$Q = \frac{3}{2} V_q I_d \tag{4.6}$$

Equations (4.5) and (4.6) indicate that the active and reactive power of the MMC converter can be independently controlled by controlling the q and d components of the current. The q and d components of the current need to be saturated before fed to the Inner Current Controller. For this reason, a current limiter is used to keep the current references within the acceptable limits.

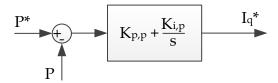

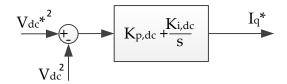

As shown in Figure 4.5, the MMC converter could operate either in active power or in DC voltage control mode. If the converter works in active power control mode, the q reference of the current is given by the active power controller (PI controller II). Otherwise, if the converter works in DC voltage control mode, the q reference of the current is given by the DC voltage controller (PI controller III).

The DC voltage controller aims to keep the DC voltage of the converter at a certain level. The controller could be operating on the error of the DC voltage. In this case, the closed-loops dynamics would depend on the operating point, because the DC current  $(I_{dc})$  is inversely proportional to the DC voltage  $(V_{dc})$ . To avoid non-linearity problems, the control should be based on the square of the DC voltage  $(V_{dc}^2)$ .

The equivalent diagram of the active power controller (PI controller II) is shown in Figure 4.6.

Figure 4.6 Active power controller.

The tuning of the active power controller was performed according to the following formulas:

$$K_{p,p} = \frac{bw \cdot 12 \cdot \pi \cdot f_s \cdot \frac{C_m}{N} \cdot V_{dc}^2}{\sqrt{3} \cdot S_b \cdot V_b}$$

(4.7)

$$K_{i,p} = \frac{(bw \cdot 2 \cdot \pi \cdot f_s)^2 \cdot 6 \cdot \frac{C_m}{N} \cdot V_{dc}^2}{\sqrt{3} \cdot S_b \cdot U_b}$$

(4.8)

where  $b_w$  is the selected bandwidth ( $b_w$ =0.01),  $f_s$  is the switching frequency ( $f_s$  = 600 Hz),  $C_m$  is the submodule capacitance (F), N is the number of submodules per arm,  $V_{dc}$  is the voltage on the DC side of the converter,  $S_b$  is the power base of the converter and  $U_b$  is the AC voltage base of the converter.

The equivalent diagram of the reactive power controller (PI controller I) is shown in Figure 4.7.

Figure 4.7 Reactive power controller.

The tuning of the reactive power controller was based on the same formulas and the gains are exactly the same as in the previous case.

$$K_{p,q} = K_{p,p} \tag{4.9}$$

$$K_{i,q} = K_{i,p} (4.10)$$

The equivalent diagram of the DC voltage controller (PI Controller III) is shown in Figure 4.8.

Figure 4.8 DC voltage controller.

The tuning of the DC voltage controller was performed according to the following formulas:

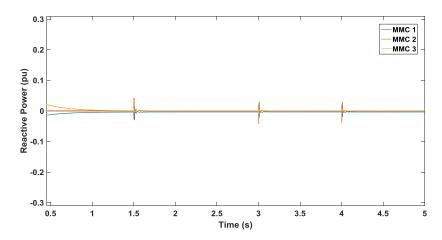

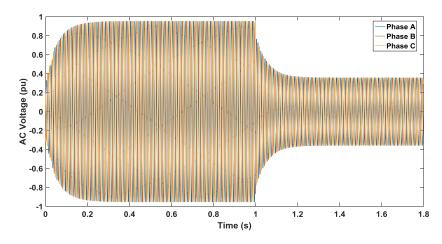

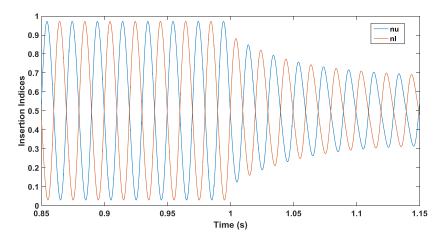

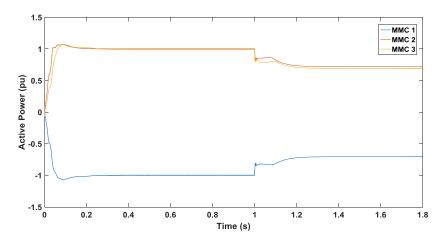

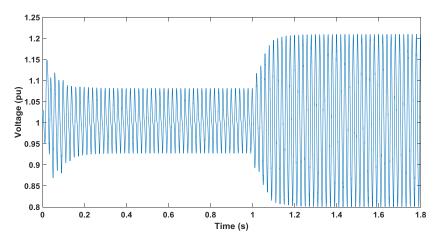

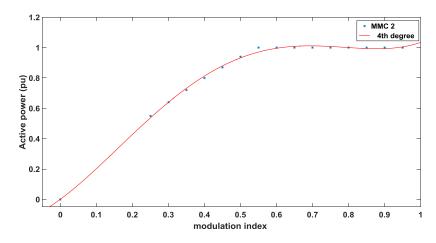

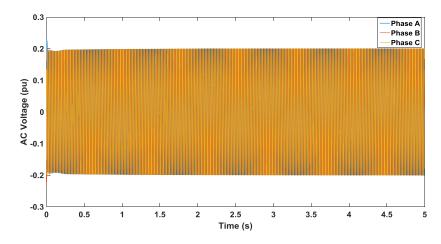

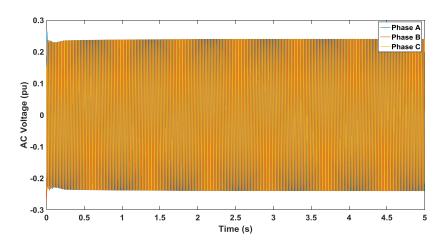

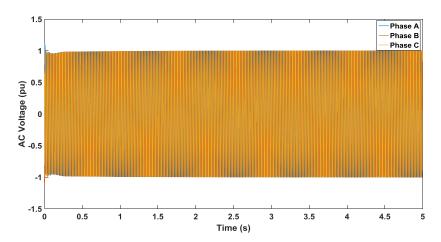

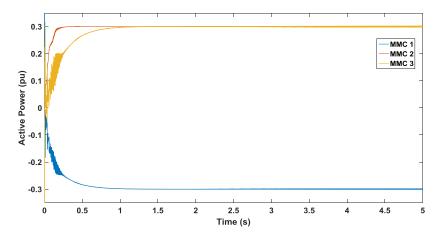

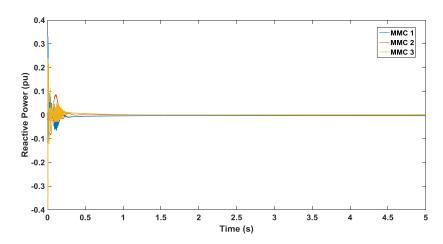

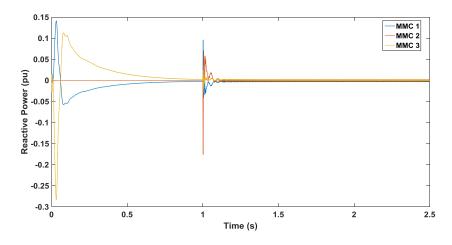

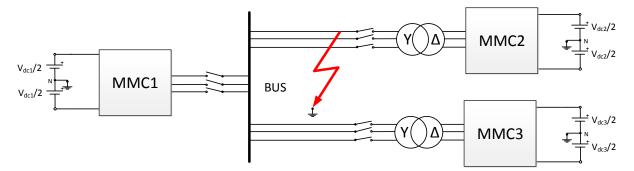

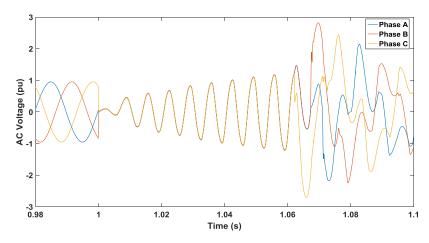

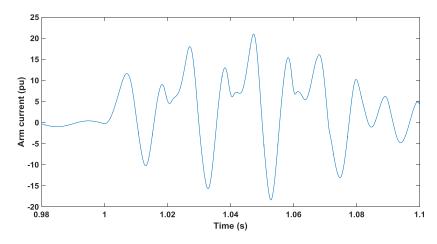

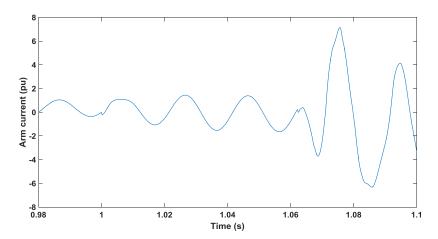

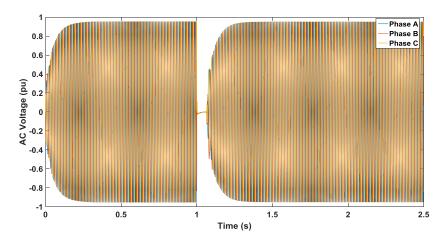

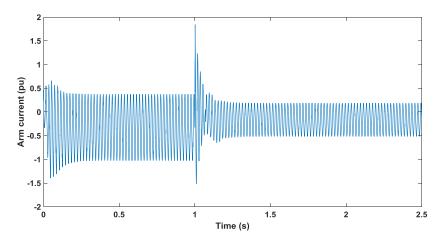

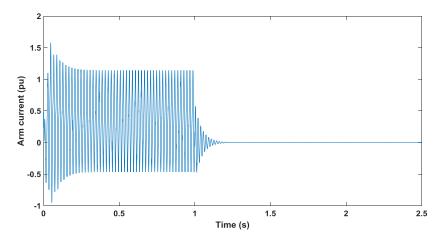

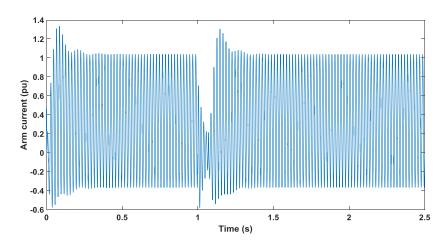

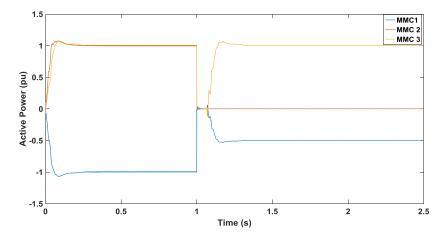

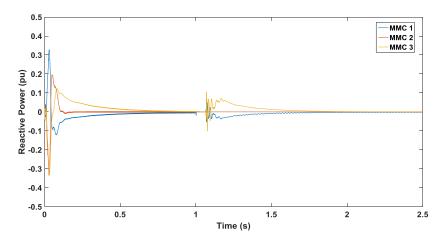

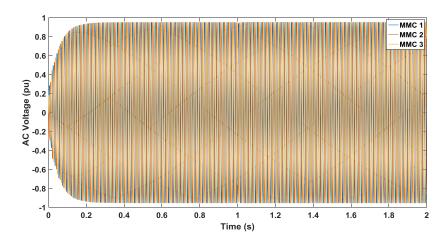

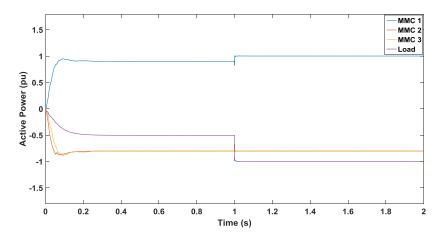

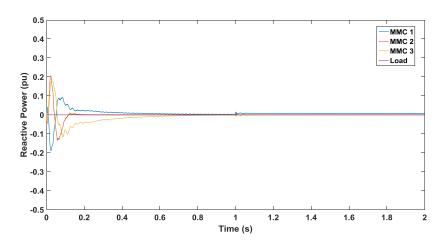

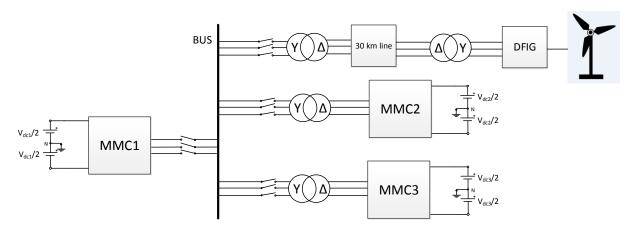

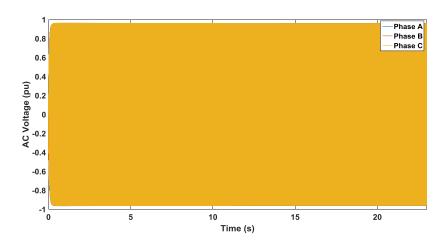

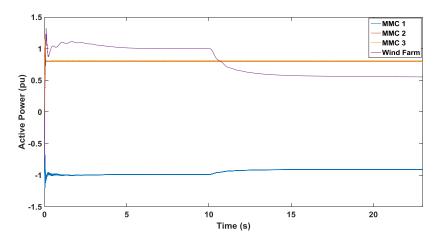

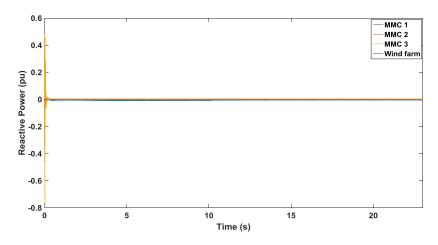

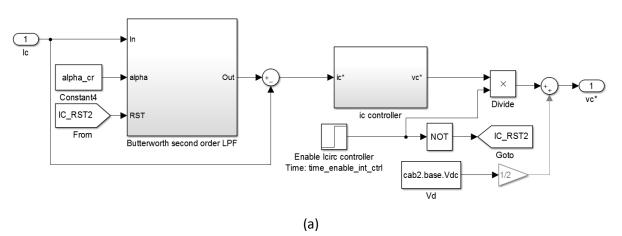

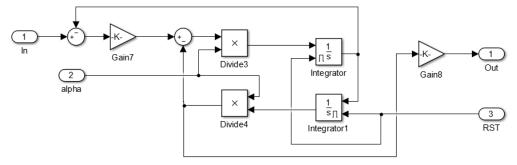

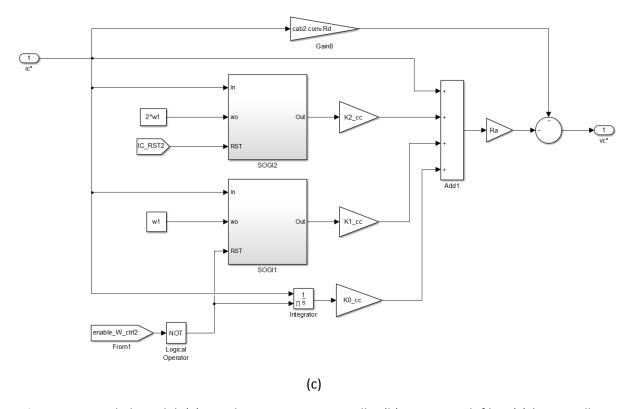

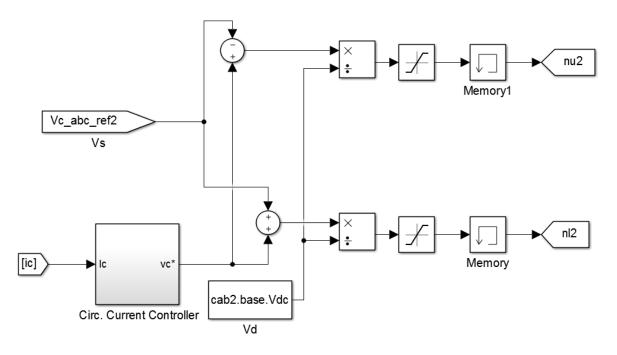

$$K_{p.dc} = \frac{bw \cdot 12 \cdot \pi \cdot f_s \cdot \frac{C_m}{N}}{\sqrt{3} \cdot U_h} \tag{4.11}$$