#### Low-cost temperature sensors in CMOS technology

Yousefzadeh, B.

10.4233/uuid:389f6a1c-f86b-48bd-a53c-f66bea5a3db8

**Publication date**

**Document Version** Final published version

Citation (APA)

Yousefzadeh, B. (2024). Low-cost temperature sensors in CMOS technology. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:389f6a1c-f86b-48bd-a53c-f66bea5a3db8

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

# Low-cost Temperature Sensors in CMOS TECHNOLOGY

# Low-cost Temperature Sensors in CMOS Technology

#### Dissertation

for the purpose of obtaining the degree of doctor at Delft University of Technology by the authority of the Rector Magnificus Prof. dr. ir. T. H. J. J. van der Hagen chair of the Board for Doctorates to be defended publicly on Thursday 30 May 2024 at 15:00

by

## **Bahman YOUSEFZADEH**

Master of Science in Electrical Engineering, Sharif University of Technology, Iran born in Shoshtar, Iran

This dissertation has been approved by the promotor.

#### Composition of the doctoral committee:

Rector Magnificus chairperson

Prof. dr. K.A.A. Makinwa Delft University of Technology, promotor

#### Independent members:

Prof. dr. ir. F. P. Widdershoven Delft University of Technology Prof. dr. Y. Chae Yonsei University, South Korea Dr. ir. M. A. P. Pertijs Delft University of Technology Dr. F. Sebastiano Delft University of Technology Dr. I. Shor Bar-Ilan University, Israël Prof. dr. ir. A. J. P. Theuwissen Delft University of Technology

Keywords: CMOS, BJT, Accurate, Low-cost, Calibration, Heater-assisted, On-chip

heater, Multi-function sensor, ADC

*Printed by:* ProefschriftMaken

Copyright © 2024 by Bahman Yousefzadeh

ISBN 978-94-6384-590-8

An electronic version of this dissertation is available at http://repository.tudelft.nl/

To Joëlle and my parents

# Contents

| 1        | Intr                   | oducti  | ion                                            | 1  |

|----------|------------------------|---------|------------------------------------------------|----|

|          | 1.1                    | Backg   | round                                          | 1  |

|          | 1.2                    | Produ   | action cost of a temperature sensor            | 2  |

|          | 1.3                    | Motiva  | ation and objectives                           | 3  |

|          | 1.4                    | Metho   | od                                             | 3  |

|          | 1.5                    | Organ   | ization of this thesis                         | 4  |

|          | Bibl                   | iograph | y                                              | 6  |

| <b>2</b> | $\mathbf{C}\mathbf{M}$ | OS te   | mperature-to-digital converters                | 9  |

|          | 2.1                    | Resist  | or-based TDCs                                  | 9  |

|          |                        | 2.1.1   | Resistors in CMOS technology                   | 9  |

|          |                        | 2.1.2   | Readout circuits                               | 12 |

|          |                        | 2.1.3   | Temperature-sensing inaccuracy and calibration | 15 |

|          | 2.2                    | Therm   | nal diffusivity (TD) based TDCs                | 18 |

|          |                        | 2.2.1   | Principle of operation                         | 18 |

|          |                        | 2.2.2   | Readout circuits                               | 18 |

|          |                        | 2.2.3   | Temperature-sensing inaccuracy and calibration | 20 |

|          | 2.3                    | MOSF    | FET-based TDCs                                 | 22 |

|          |                        | 2.3.1   | Principle of operation                         | 22 |

|          |                        | 2.3.2   | Readout circuits                               | 23 |

|          |                        | 2.3.3   | Temperature-sensing inaccuracy and calibration | 26 |

viii Contents

|   | 2.4  | BJT-b   | ased TDCs                                      | 27 |

|---|------|---------|------------------------------------------------|----|

|   |      | 2.4.1   | BJTs in CMOS Technology                        | 27 |

|   |      | 2.4.2   | Principle of operation                         | 29 |

|   |      | 2.4.3   | Readout circuits                               | 31 |

|   |      | 2.4.4   | Temperature-sensing inaccuracy and calibration | 32 |

|   | 2.5  | Conclu  | ision                                          | 33 |

|   | Bibl | iograph | у                                              | 34 |

| 3 | Bip  | olar ju | nction transistors in CMOS technology          | 43 |

|   | 3.1  | Ideal I | $I_C - V_{BE}$ characteristic                  | 43 |

|   | 3.2  | Satura  | ation current $(I_S)$                          | 44 |

|   |      | 3.2.1   | Temperature dependence of $I_S$                | 44 |

|   |      | 3.2.2   | Spread of $I_S$                                | 44 |

|   |      | 3.2.3   | $I_S$ compensation                             | 45 |

|   | 3.3  | Curren  | nt gains $\alpha_F$ and $\beta$                | 46 |

|   |      | 3.3.1   | Temperature dependence of $\beta$              | 46 |

|   |      | 3.3.2   | Spread of $\beta$                              | 47 |

|   |      | 3.3.3   | $\beta$ compensation                           | 48 |

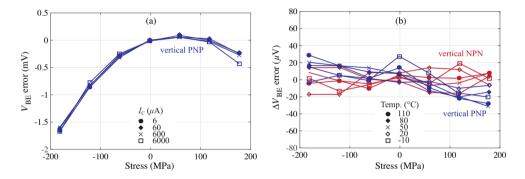

|   | 3.4  | Series  | resistances $(R_S)$                            | 49 |

|   |      | 3.4.1   | Base resistance $(R_B)$                        | 50 |

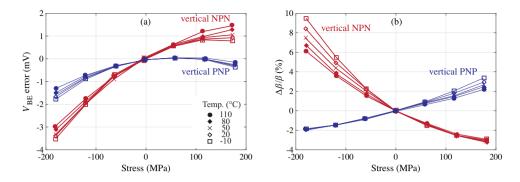

|   | 3.5  | Effect  | of mechanical stress on BJTs                   | 50 |

|   |      | 3.5.1   | Stress due to packaging                        | 51 |

|   |      | 3.5.2   | Piezo-junction effect                          | 52 |

|   | 3.6  | Conclu  | ısion                                          | 54 |

|   | Bibl | iograph | y                                              | 55 |

| 4 | An   | accura  | te and process-insensitive BJT-based TDC       | 59 |

|   | 4.1  | Opera   | ting principle                                 | 60 |

|   | 4.2  | Accura  | acv limits of the bipolar core                 | 60 |

Contents

|   |      | 4.2.1   | Uncompensated $\beta$ and $R_S$                   | 61  |

|---|------|---------|---------------------------------------------------|-----|

|   |      | 4.2.2   | Compensated $\beta$ and uncompensated $R_S$       | 62  |

|   |      | 4.2.3   | Compensated $\beta$ and $R_S$                     | 63  |

|   | 4.3  | Inaccu  | racy sources in the bias circuit                  | 65  |

|   | 4.4  | Sensin  | g front-end                                       | 69  |

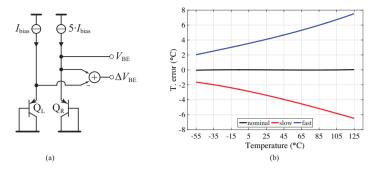

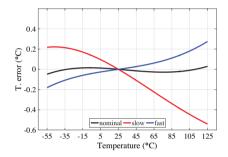

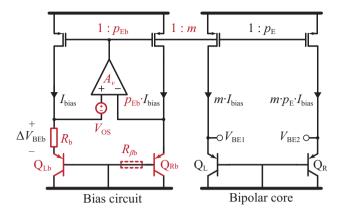

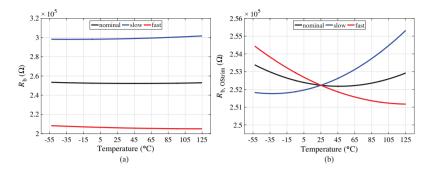

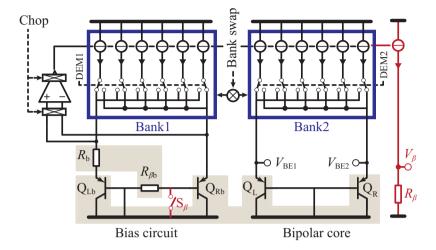

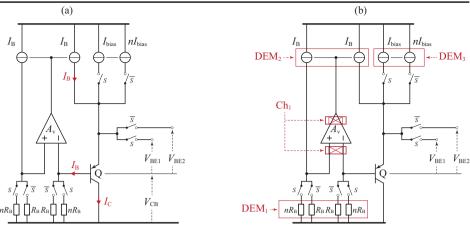

|   |      | 4.4.1   | Bias circuit                                      | 70  |

|   |      | 4.4.2   | $\beta$ detection                                 | 71  |

|   | 4.5  | Reado   | ut circuit                                        | 71  |

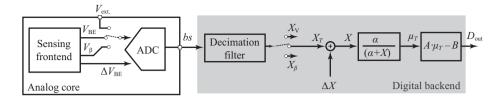

|   |      | 4.5.1   | Zoom-ADC                                          | 72  |

|   |      | 4.5.2   | Switch leakage                                    | 74  |

|   | 4.6  | Experi  | imental results                                   | 75  |

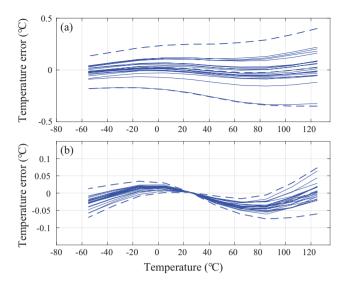

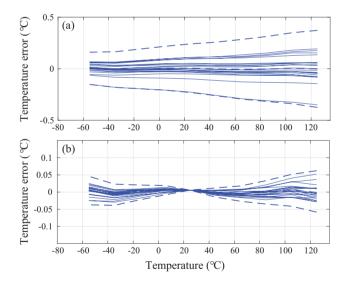

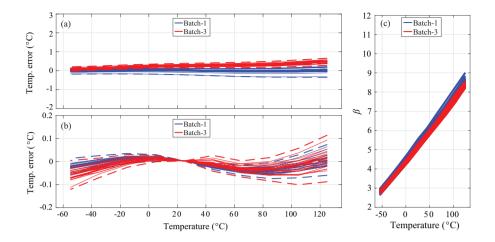

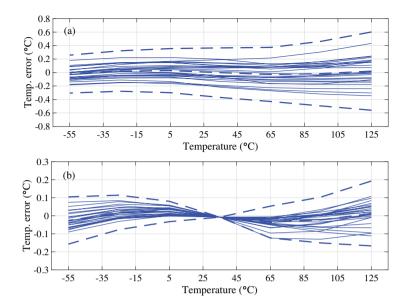

|   |      | 4.6.1   | Batch-calibrated accuracy                         | 77  |

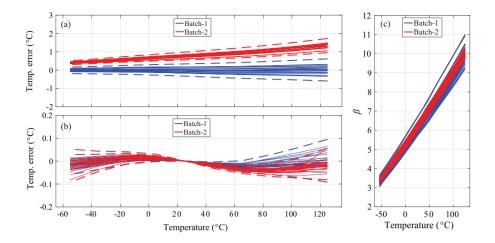

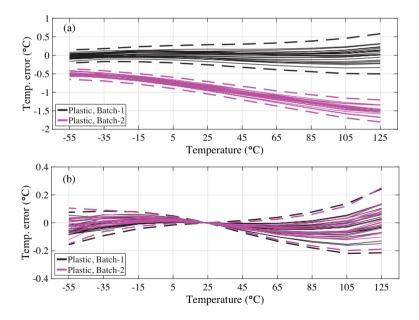

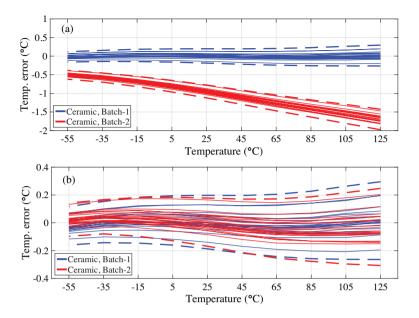

|   |      | 4.6.2   | Batch-to-batch variation                          | 80  |

|   |      | 4.6.3   | Switch leakage                                    | 81  |

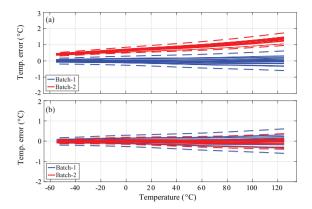

|   |      | 4.6.4   | Voltage calibration (VCAL)                        | 82  |

|   |      | 4.6.5   | Batch trimming                                    | 84  |

|   | 4.7  | Conclu  | ısion                                             | 85  |

|   | Bibl | iograph | у                                                 | 86  |

| 5 | Hea  | ter-ass | sisted calibration and trimming of BJT-based TDCs | 89  |

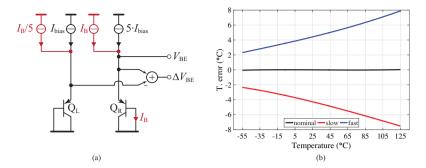

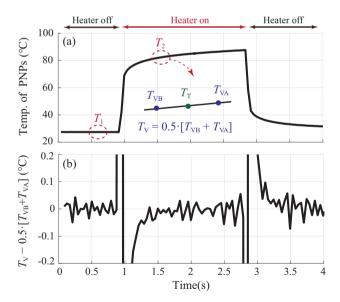

|   | 5.1  |         | r-assisted voltage calibration (HA-VCAL)          | 90  |

|   |      | 5.1.1   | Operating principle                               | 90  |

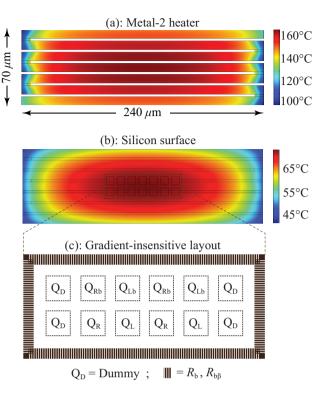

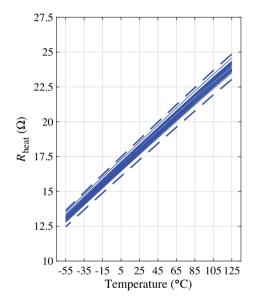

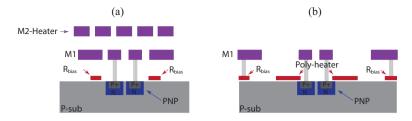

|   |      | 5.1.2   | On-chip heater                                    | 90  |

|   |      | 5.1.3   | Sources of error                                  | 92  |

|   | 5.2  | Heater  | r-assisted bandgap trimming (HA-BT)               | 95  |

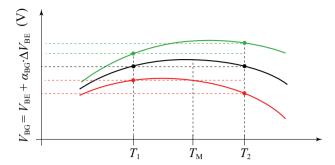

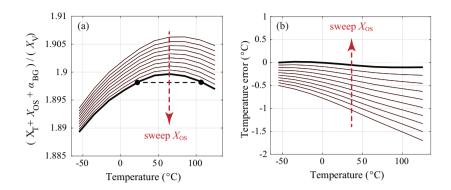

|   |      | 5.2.1   | Operating principle                               | 96  |

|   |      | 5.2.2   | Sources of error                                  | 98  |

|   | 5.3  | Low-le  | eakage readout circuit                            | 100 |

|   |      | 5.3.1   | Switch leakage                                    | 100 |

|   |      |         |                                                   |     |

Contents

|   |                 | 5.3.2     | Charge-balancing scheme in the low-leakage ADC                      | 101          |

|---|-----------------|-----------|---------------------------------------------------------------------|--------------|

|   |                 | 5.3.3     | Sampling scheme in the low-leakage ADC $\ \ldots \ \ldots \ \ldots$ | 102          |

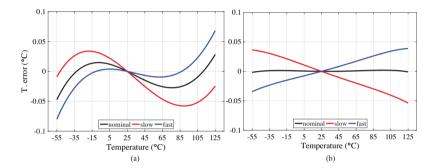

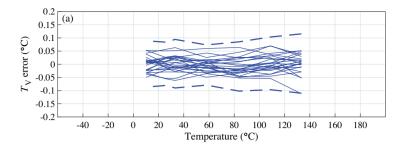

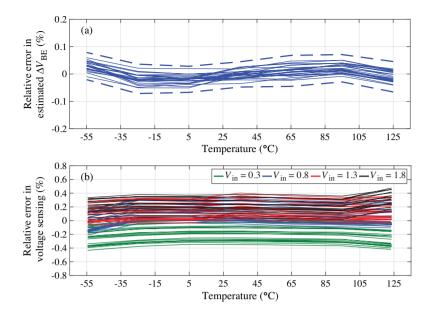

|   | 5.4             | Experi    | imental results                                                     | 104          |

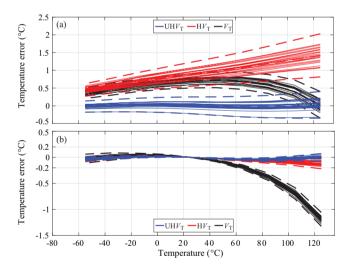

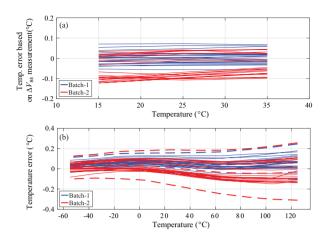

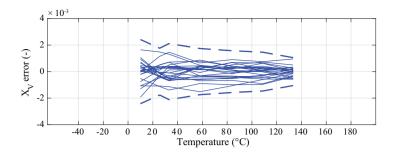

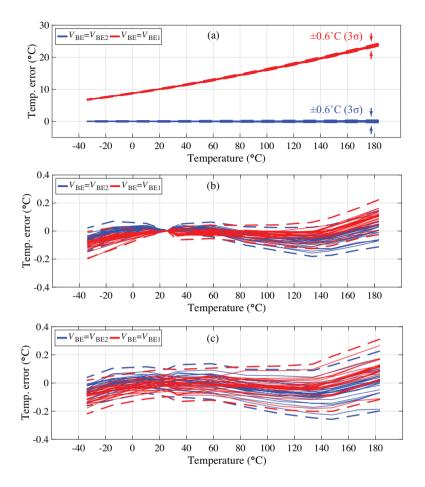

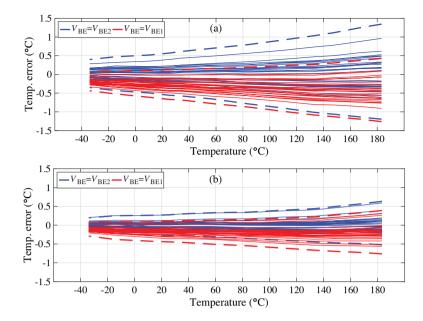

|   |                 | 5.4.1     | Errors due to plastic packaging stress                              | 106          |

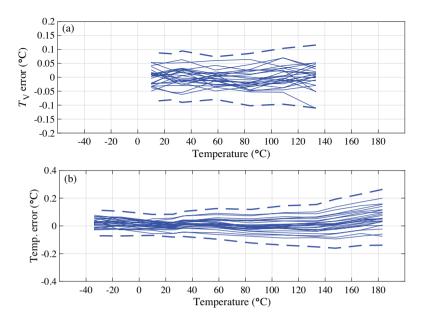

|   |                 | 5.4.2     | Wafer-level trimming and package-specific calibration $\dots$ .     | 107          |

|   |                 | 5.4.3     | On-chip temperature gradients                                       | 109          |

|   |                 | 5.4.4     | Local heating versus uniform heating                                | 111          |

|   |                 | 5.4.5     | Conventional VCAL versus HA-VCAL                                    | 111          |

|   |                 | 5.4.6     | Post-packaging HA-VCAL                                              | 114          |

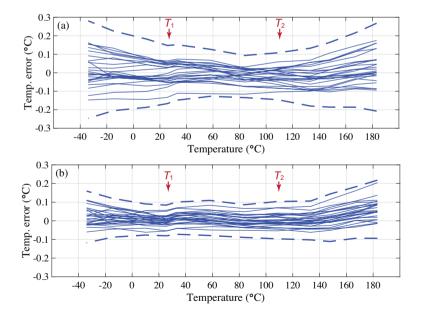

|   |                 | 5.4.7     | Heater-assisted bandgap trimming (HA-BT)                            | 114          |

|   | 5.5             | Conclu    | usion                                                               | 118          |

|   | Bibl            | iograph   | y                                                                   | 120          |

| 6 | ΑN              | ∕Iulti-fı | unction sensor with temperature, voltage, and capacitanc            | ·e           |

| U |                 | sing m    |                                                                     | 123          |

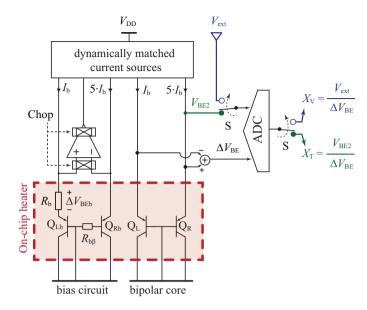

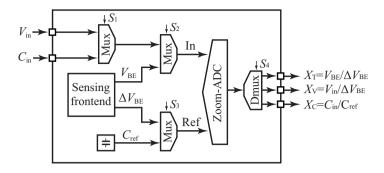

|   | 6.1             | Overv     | iew of the multi-function sensor                                    | 123          |

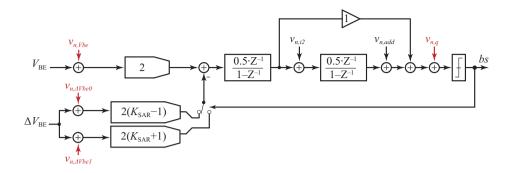

|   | 6.2             | Tempe     | erature-to-digital conversion                                       | 124          |

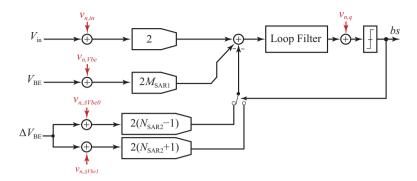

|   | 6.3             | Voltag    | ge-to-digital conversion                                            | 126          |

|   |                 | 6.3.1     | Principle of operation                                              | 126          |

|   |                 | 6.3.2     | Accuracy of the voltage sensing mode                                | 128          |

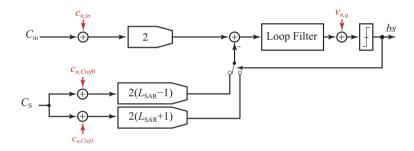

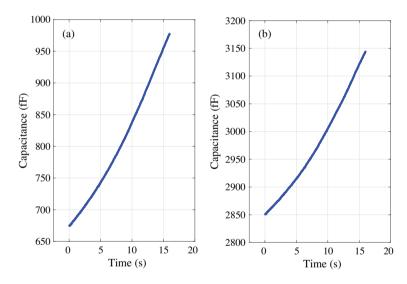

|   | 6.4             | Capac     | citance-to-digital conversion                                       | 129          |

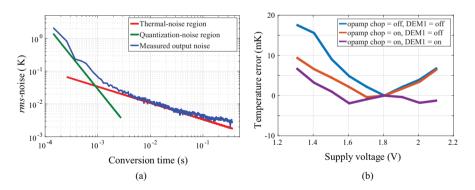

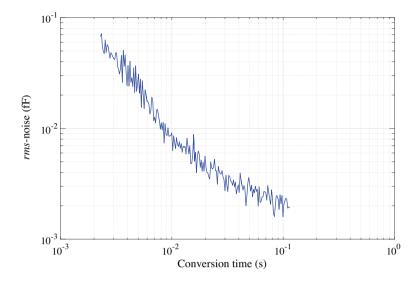

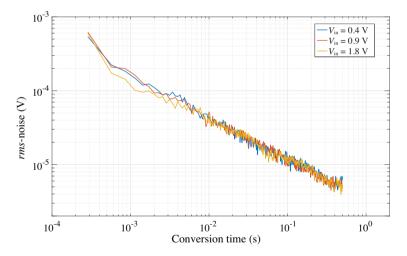

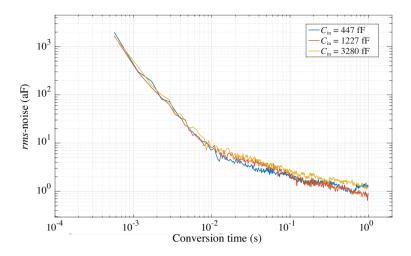

|   | 6.5             | Noise     | analysis                                                            | 131          |

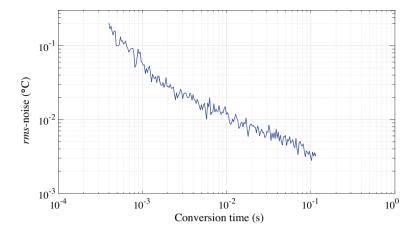

|   |                 | 6.5.1     | Noise in the temperature sensing mode                               | 131          |

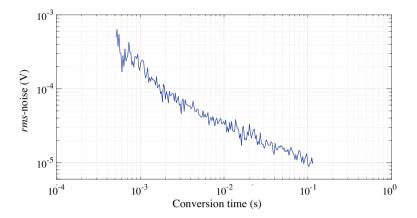

|   |                 | 6.5.2     | Noise in the voltage sensing mode                                   | 134          |

|   |                 | 6.5.3     | Noise in the capacitance sensing mode                               | 135          |

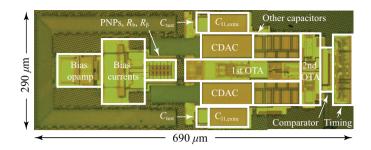

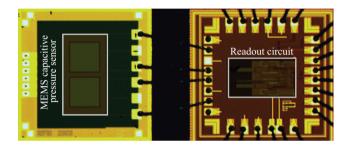

|   | 6.6             | Experi    | imental results                                                     | 137          |

|   | 6.7             | Conclu    | usion                                                               | 141          |

|   | Bibl            | iograph   | y                                                                   | 143          |

| 7 | Con             | clusio    | n                                                                   | 145          |

| • | $\sim$ $\sigma$ |           | **                                                                  | <b>T T O</b> |

Contents xi

|              | 7.1   | Main f    | indings                                        | . 145 |

|--------------|-------|-----------|------------------------------------------------|-------|

|              | 7.2   | Future    | work                                           | . 146 |

|              |       | 7.2.1     | $\beta\text{-compensation for BJT-based TDCs}$ | . 146 |

|              |       | 7.2.2     | Efficient on-chip heaters                      | . 148 |

|              | Bibli | ograph    | y                                              | . 149 |

| Ap           | pene  | dices     |                                                | 150   |

| $\mathbf{A}$ | вјт   | theor     | у                                              | 151   |

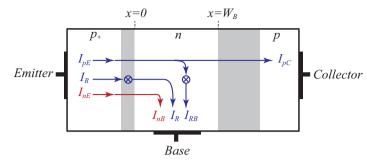

|              | A.1   | Ideal $I$ | $I_C - V_{BE}$ characteristic                  | . 151 |

|              | A.2   | Non-id    | eal current components                         | . 153 |

|              | A.3   | Tempe     | rature dependence of $I_S$                     | . 156 |

|              | A.4   | Non-id    | ealities of the $I_C - V_{BE}$ characteristic  | . 159 |

|              |       | A.4.1     | High-level injection                           | . 159 |

|              |       | A.4.2     | Base-width modulation                          | . 159 |

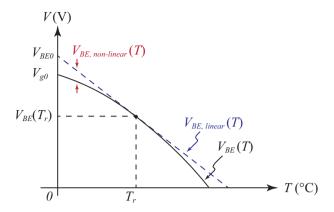

|              | A.5   | Non-lin   | nearity of the $V_{BE}(T)$ curve               | . 162 |

|              | A.6   | Noise i   | in the BJTs                                    | . 165 |

|              | Bibli | ograph    | y                                              | . 167 |

| Su           | mma   | ary       |                                                | 169   |

| Sa           | men   | vatting   | ;                                              | 171   |

| Ac           | knov  | vledge    | ments                                          | 173   |

| Lis          | st of | public    | ations                                         | 175   |

| Ał           | out   | the au    | thor                                           | 177   |

# Chapter 1

#### Introduction

Temperature greatly affects the performance of integrated circuits (ICs), and so temperature sensors are often necessary to ensure reliable operation and stable performance. For instance, they can be used to detect hot-spots in large system-on-chips (SoCs) to prevent them from premature failure and increase their performance. They are also used to compensate for the temperature dependence of other sensors and references and thus increase their accuracy. Depending on the application, the required sensing range varies: from small (e.g.,  $\pm 10$  °C around body temperature) in biomedical sensors [1.1], to large (e.g., -40 °C to +150 °C) in automotive electronics [1.2]. The required inaccuracy also varies with application: from  $\pm 1$  °C for the thermal management of SoCs [1.3], to less than  $\pm 0.1$  °C in precision sensors [1.4],[1.5], and references [1.6].

Temperature can be determined by measuring an electrical parameter of an onchip element with a known temperature dependency. To make an accurate temperature sensor, the variation in this parameter due to the fabrication process and the mechanical stress of packaging must be corrected by calibration or by design. In principle, parameter variation can be sufficiently suppressed by using multiple calibration points. However, this will proportionally increase production costs.

# 1.1 Background

The temperature behavior of Bipolar Junction Transistors (BJTs) has been well studied [1.7]–[1.9], and shown to be stable over long periods of time [1.10]. Furthermore, the effect of process spread in BJTs can be corrected by a single calibration. As a

result, BJTs are often used in integrated temperature sensors.

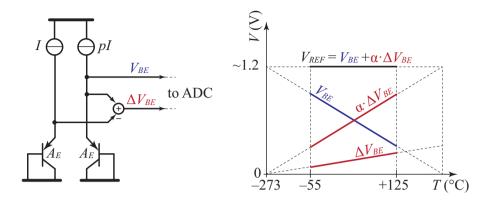

In early bipolar technologies, the difference between the Base-Emitter voltages of two BJTs with different current densities ( $\Delta V_{BE}$ ) was used to generate stable bias currents [1.11]. Later, temperature sensors based on this principle were introduced. These typically had outputs in the form of voltages [1.12], currents [1.13],[1.14], or frequencies [1.15]. Analog-to-digital converters (ADCs) were subsequently added to realize temperature-to-digital converters (TDCs) [1.16], whose digital outputs were more robust and could be easily connected to microprocessors.

TDCs then evolved by shifting from bipolar technologies to CMOS, mainly to be compatible with the mainstream digital circuits. Fortunately, BJTs can still be realized in CMOS technologies as lateral [1.17], or vertical [1.18] devices. MOSFETs also exhibit bipolar-like behavior when biased in the weak inversion region [1.19].

# 1.2 Production cost of a temperature sensor

The cost of producing a temperature sensor can be divided into three parts: design, fabrication, and testing. Design accounts for the smallest fraction of the total costs, as it is a fixed amount that will be spread over a large number of samples. Fabrication costs are higher, as they consist of a one-time cost for the production of masks and then the repeated cost of fabricating each batch of wafers, which contain thousands of samples. The third and highest costs are due to testing, which may need to be carried out on each sample. Delivering a faulty sample can cause a larger system to fail, leading to even higher costs.

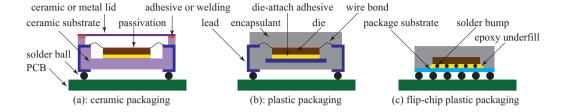

Temperature sensors can be tested at wafer-level, package-level, or both. During wafer-level testing, non-functional samples are marked and then excluded from the packaging. A performance assessment is also carried out, which is then used to sort samples into different bins with different performance ranges. When required, calibration and trimming are carried out during wafer-level testing. During package-level testing, errors that might arise from either erroneous wire-bonding, or the high pressure used during the encapsulation process, will also be detected.

The cost of wafer-level testing is usually lower than that of package-level testing, because thousands of samples can be tested at the same time. A test probe then scans the wafer, makes connections to each sample, and performs an electrical test. For temperature calibration, the wafer is placed on a temperature-controlled chuck. In a minute-long process, the wafer and the chuck reach a thermal equilibrium after which the electrical measurements can start. Due to its higher costs and infrastructure

requirements, package-level testing is usually limited to simple functionality tests.

### 1.3 Motivation and objectives

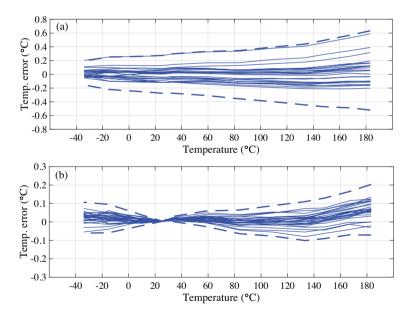

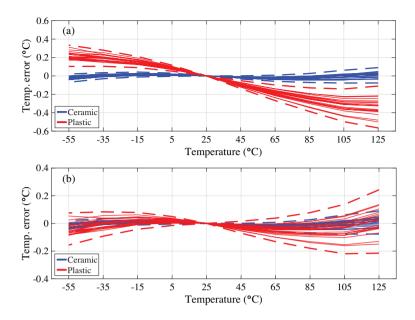

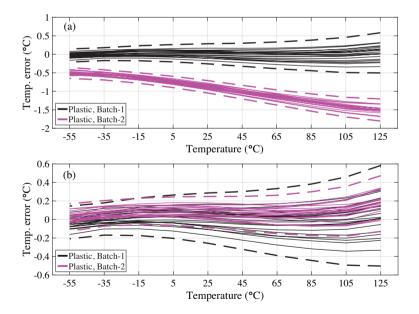

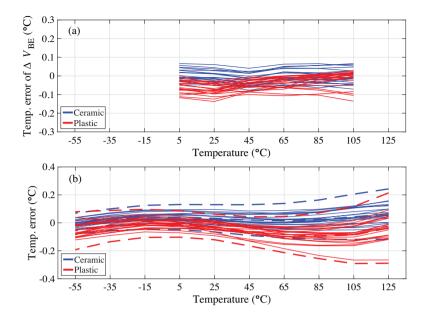

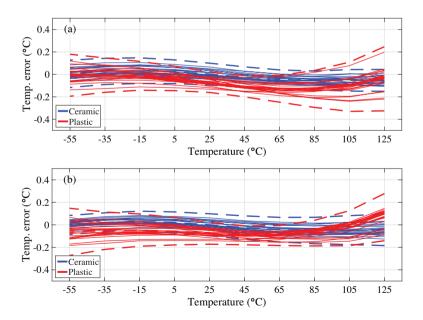

At the start of this work, a state-of-the-art temperature sensor in the target CMOS technology (0.16- $\mu$ m) could obtain  $3\sigma$ -inaccuracies of  $\pm 0.15$  °C from -55 °C to 125 °C [1.20]. However, this shifted somewhat over two production batches, and could only be corrected at the expense of more calibration. In earlier 0.7- $\mu$ m CMOS technology, by contrast, this shift was negligible [1.10]. Table 1.1 summarizes the results of [1.20] for two different production batches, and in both ceramic and plastic packaging. To correct the shift between the two batches, a batch-specific set of calibration parameters (A, B,  $\alpha$ ) had to be determined. The same procedure had to be repeated when the sensor was packaged in plastic. The need to re-calibrate separate batches and differently packaged samples made it impractical to use the sensor in [1.20] as a low-cost precision product.

The goal of the work described in this thesis is the realization of a temperature sensor that does not require batch-calibration. To this end, the first challenge is to determine the root cause behind the batch-to-batch shift observed in [1.20]. From the reported performance of this sensor (see Table 1.1), it could not be conclusively determined whether this shift was due to the available BJTs and resistors, or due to an architectural limitation. The second challenge is to develop low-cost methods to correct the sensor's shift in different packages.

#### 1.4 Method

To address the first challenge, an accurate and process-insensitive sensor was designed, which unlike [1.20] does not require individual batch-calibration, and thus, can be produced with lower costs. This was achieved by adding circuit techniques to the sensor's front-end to mitigate its sources of error. The accuracy of the sensor was then verified by measuring samples from three different batches. This approach enabled the experimental characterization of the main sources of spread, thus capturing physical effects not included in the device models.

To address the second challenge, low-cost calibration methods were developed to help reduce test costs. These calibration methods involved measurements at two different temperatures. Room temperature was used as one temperature point, while

|                                  | Batch-1       | Batch-2       | Batch-2       |

|----------------------------------|---------------|---------------|---------------|

| CMOS technology $(\mu m)$        | 0.16          | 0.16          | 0.16          |

| Packaging type                   | Ceramic       | Ceramic       | Plastic       |

| Temperature range (°C)           | -55  to  +125 | -55  to  +125 | -55  to  +125 |

| Untrimmed inaccuracy $(3\sigma)$ | ±0.6 °C       | ±0.6 °C       | ±0.8 °C       |

| Trimmed inaccuracy $(3\sigma)$   | ±0.15 °C      | ±0.25 °C      | ±0.25 °C      |

| $\alpha$                         | 15.44         | 15.45         | 15.47         |

| A                                | 613.31        | 610.74        | 611.59        |

| В                                | 283.70        | 282.93        | 283.94        |

Table 1.1: Performance summary of the state-of-the-art CMOS BJT-based temprature sensor [1.21].  $\alpha$ , A, and B are average calibration parameters.

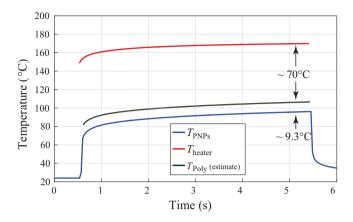

an on-chip heater was used to elevate die temperature and create a second temperature point. The effectiveness of these heater-assisted calibration methods was then evaluated on sensors from different production batches and in different packages.

In the final step, additional functionality was added to the sensor by re-configuring its front-end circuitry, and so, making more cost-effective use of its area. The result is a multi-function sensor that can digitize external voltages and capacitances as well as temperature.

# 1.5 Organization of this thesis

Chapter 2 discusses four different methods for realizing a TDC in CMOS technology based on resistors, MOSFETs, thermal-diffusivity (TD), and BJTs. For each method, the sensing principle is explained, and then examples of typical readout circuits and the resulting inaccuracy are provided. This gives an overview of the expected inaccuracy of different TDCs and their calibration requirements.

Chapter 3 focuses on BJT devices. It starts with a discussion of the equations that govern the operation of ideal BJTs. Non-ideal effects that cause temperature inaccuracy, such as finite current gain and non-zero series resistances, are explained in detail. Lastly, the effect of mechanical stress on the BJTs is discussed.

Chapter 4 discusses the first TDC implementation in this thesis, which was intended to reduce the batch-to-batch shift observed in [1.20]. It starts with an analysis of the error sources in the sensor's front-end and then describes ways of suppressing them. Compared to the state-of-the-art, the sensor achieved  $2\times$  better accuracy, which also eliminated the need for batch calibration. Voltage calibration as a low-

cost alternative to temperature calibration was also verified for this sensor.

Chapter 5 describes the second TDC implementation in this thesis. It includes the realization of two TDCs that were equipped with on-chip heaters. These TDCs were used to investigate two different heater-assisted calibration methods. The effect of the mechanical stress of plastic packaging on the TDC, and low-cost methods to correct for this are also discussed in this chapter.

Chapter 6 describes the third TDC implementation in this thesis, which expanded the sensor's functionality. It describes how the circuitry of the TDC in Chapter 4 can be re-used to also digitize external voltages and capacitances.

Chapter 7 summarizes the main findings in this thesis and provides some suggestions for future work.

6 Bibliography

# **Bibliography**

[1.1] A. Vaz, A. Ubarretxena, I. Zalbide, D. Pardo, H. Solar, A. Garcia-Alonso, and R. Berenguer, "Full passive UHF tag with a temperature sensor suitable for human body temperature monitoring," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 57, no. 2, pp. 95–99, 2010.

- [1.2] R. W. Johnson, J. L. Evans, P. Jacobsen, J. R. Thompson, and M. Christopher, "The changing automotive environment: high-temperature electronics," *IEEE Transactions on Electronics Packaging Manufacturing*, vol. 27, no. 3, pp. 164–176, 2004.

- [1.3] U. Sönmez, F. Sebastiano, and K. A. A. Makinwa, "Compact thermal-diffusivity-based temperature sensors in 40-nm CMOS for SoC thermal monitoring," *IEEE Journal of Solid-State Circuits*, vol. 52, no. 3, pp. 834–843, 2017.

- [1.4] M. H. Perrott, J. C. Salvia, F. S. Lee, A. Partridge, S. Mukherjee, C. Arft, J. Kim, N. Arumugam, P. Gupta, S. Tabatabaei, S. Pamarti, H. Lee, and F. Assaderaghi, "A temperature-to-digital converter for a MEMS-based programmable oscillator with < ±0.5-ppm frequency stability and < 1-ps integrated jitter," *IEEE Journal of Solid-State Circuits*, vol. 48, no. 1, pp. 276–291, 2013.

- [1.5] S. Heidary Shalmany, D. Draxelmayr, and K. A. A. Makinwa, "A  $\pm 36$ - $\mu$ A integrated current-sensing system with a 0.3% gain error and a 400- $\mu$ A offset from -55 °C to +85 °C," *IEEE Journal of Solid-State Circuits*, vol. 52, no. 4, pp. 1034–1043, 2017.

- [1.6] S. M. Kashmiri, M. A. P. Pertijs, and K. A. A. Makinwa, "A thermal-diffusivity-based frequency reference in standard CMOS with an absolute inaccuracy of ±0.1% from -55 °C to 125 °C," *IEEE Journal of Solid-State Circuits*, vol. 45, no. 12, pp. 2510–2520, 2010.

- [1.7] Y. P. Tsividis, "Accurate analysis of temperature effects in  $I_C V_{BE}$  characteristics with application to bandgap reference sources," *IEEE Journal of Solid-State Circuits*, vol. 15, no. 6, pp. 1076–1084, 1980.

- [1.8] G. C. M. Meijer and K. Vingerling, "Measurement of the temperature dependence of the  $I_C V_{BE}$  characteristics of integrated bipolar transistors," *IEEE Journal of Solid-State Circuits*, vol. 15, no. 2, pp. 237–240, 1980.

- [1.9] G. Wang and G. C. Meijer, "The temperature characteristics of bipolar transistors fabricated in CMOS technology," *Sensors and Actuators A: Physical*, vol. 87, no. 1, pp. 81 89, 2000.

- [1.10] G. Wang, A. Heidari, K. A. A. Makinwa, and G. C. M. Meijer, "An accurate BJT-based CMOS temperature sensor with duty-cycle-modulated output," IEEE Transactions on Industrial Electronics, vol. 64, no. 2, pp. 1572–1580, Feb. 2017.

Bibliography 7

[1.11] R. Widlar, "Some circuit design techniques for linear integrated circuits," *IEEE Transactions on Circuit Theory*, vol. 12, no. 4, pp. 586–590, 1965.

- [1.12] R. Dobkin, "Monolithic temperature transducer," in *IEEE International Solid-State Circuits Conference (ISSCC)*. Dig. of Tech. Papers, vol. XVII, 1974, pp. 126–127.

- [1.13] M. P. Timko, "A two-terminal IC temperature transducer," *IEEE Journal of Solid-State Circuits*, vol. 11, no. 6, pp. 784–788, 1976.

- [1.14] G. C. M. Meijer, "An IC temperature transducer with an intrinsic reference," *IEEE Journal of Solid-State Circuits*, vol. 15, no. 3, pp. 370–373, 1980.

- [1.15] D. Van Maaren, J. Klijn, and G. C. M. Meijer, "An integrated micropower low-voltage temperature-controlled oscillator," *IEEE Journal of Solid-State Circuits*, vol. 17, no. 6, pp. 1197–1201, 1982.

- [1.16] G. C. M. Meijer, A. J. M. Boomkamp, and R. J. Duguesnoy, "An accurate biomedical temperature transducer with on-chip microcomputer interfacing," *IEEE Journal of Solid-State Circuits*, vol. 23, no. 6, pp. 1405–1410, 1988.

- [1.17] P. Krummenacher and H. Oguey, "Smart temperature sensor in CMOS technology," Sensors and Actuators A: Physical, vol. 22, no. 1, pp. 636 638, 1990.

- [1.18] A. Bakker and J. H. Huijsing, "Micropower CMOS temperature sensor with digital output," *IEEE Journal of Solid-State Circuits*, vol. 31, no. 7, pp. 933– 937, Jul 1996.

- [1.19] E. A. Vittoz and O. Neyroud, "A low-voltage CMOS bandgap reference," *IEEE Journal of Solid-State Circuits*, vol. 14, no. 3, pp. 573–579, 1979.

- [1.20] K. Souri, Y. Chae, and K. A. A. Makinwa, "A CMOS temperature sensor with a voltage-calibrated inaccuracy of  $\pm 0.15^{\circ}$ C ( $3\sigma$ ) from  $-55^{\circ}$ C to  $125^{\circ}$ C," *IEEE Journal of Solid-State Circuits*, vol. 48, no. 1, pp. 292–301, Jan. 2013.

# Chapter 2

# CMOS temperature-to-digital converters

This chapter gives an overview of various types of CMOS temperature-to-digital converters (TDCs). For each TDC type, its operating principle and some typical readout circuitry will be discussed. Based on the available literature, the achievable temperature inaccuracy, calibration requirements, and limitations will also be discussed, which then allows the TDCs to be compared. This chapter consists of five sections. The first four sections discuss TDCs based on resistors, thermal diffusivity (TD), MOSFETs, and BJTs, respectively. Section 5 concludes this chapter.

#### 2.1 Resistor-based TDCs

### 2.1.1 Resistors in CMOS technology

When the behavior of a resistor with respect to temperature is known, its value can be digitized and used as a measure of temperature. The available resistors in standard CMOS technology are shown in Table 2.1, tohether with their associated parameters such as Sheet Resistance  $R_{sh}$ , Temperature Coefficient (TC), Voltage Coefficient (VC), and also a qualitative description of their flicker noise.

Metal resistors are made with the same material used to realize the interconnects in a chip. Initially, Aluminium (Al) or an alloy of Al with Silicon (Si) or Copper (Cu) was used as the interconnecting material in CMOS technology. Later, Cu was chosen for its lower resistivity compared to Al, its higher resistance to electro-migration, and also its better reliability. Metal resistors have a very low sheet resistance which, depending on the thickness of the metal layer used, ranges from  $\sim 0.02$  to  $\sim 0.08 \ \Omega/\Box$ .

| Resistor type         | $R_{sh} ^{a}(\Omega/\Box)$ | $TC^{b}(\%/^{\circ}C)$ | $VC^{c}(ppm/V)$        | 1/f noise  |

|-----------------------|----------------------------|------------------------|------------------------|------------|

| Metal                 | 0.02 to 0.08               | +0.3  to  +0.4         | Negligible             | Negligible |

| N-well                | 1 k to 10 k                | +0.3                   | ~10 k                  | Very low   |

| Diffusion $(p+/n+)$   | 50 to 200                  | +0.08  to  +0.15       | 100 to 500             | Very low   |

| Silicided diffusion   | 5 to 10                    | +0.25  to  +0.4        | Lower than diffusion   | Low        |

| Polysilicon $(p+/n+)$ | $50 \text{ to } 350^{-d}$  | -0.15  to  +0.01       | ~100                   | High       |

| Silicided polysilicon | 5 to 10                    | +0.25  to  +0.4        | Lower than polysilicon | Low        |

<sup>&</sup>lt;sup>a</sup> Sheet resistance

Table 2.1: Overview of resistor characteristics in CMOS technologies.

They have a large TC of  $\sim 0.3\%/^{\circ}$ C and little to no flicker noise. Metal resistors also show a very low dependence on applied voltages. This is mainly because, unlike diffusion or n-well resistors, their geometry hardly changes in response to applied voltages. Due to their large TC, decent linearity, and negligible low-frequency noise, metal resistors are very suitable candidates for realizing a TDC. However, due to their relatively low sheet resistance, these advantages come at the expense of area.

In standard single-well CMOS technology, N-well resistors are made with lowdoped (n-type) silicon in a p-type substrate. In twin-well technologies, it is also possible to realize p-well resistors. Well resistors typically have a high  $R_{sh}$ , which can range from  $\sim 1$  to  $\sim 10 \text{ k}\Omega/\Box$ . They exhibit a large TC of  $\sim +0.3\%/^{\circ}\text{C}$ , and also very low flicker noise [2.1]. However, well resistors are known for their poor non-linearity or equivalently large voltage dependence. The resistance of an n-well resistor is modulated by the potential difference between the well and the underlying p-substrate. This is because the width of the depletion region formed in the reversebiased junction between the p-substrate and the n-well varies with the voltage across the resistor. As a result, the effective geometry of the well-resistor varies and cause resistance variation [2.2]. The resistance of an n-well increases with an increase in the applied voltage, since a higher voltage extends the depletion region into the resistor region and reduces its effective thickness. Due to the relatively low doping concentration of the n-well, the depletion region predominantly extends inside the n-well rather than the p-substrate, which accounts for their relatively higher VC compared to diffusion resistors. Unless it is necessary to realize very large resistors in a small area, this makes them unsuitable for use in most analog circuits. Besides their high VC, they are also vulnerable to substrate noise, which can couple to the resistor via the well to substrate junction capacitance, and they are very sensitive to mechanical stress.

<sup>&</sup>lt;sup>b</sup> Temperature coefficient

<sup>&</sup>lt;sup>c</sup> Voltage coefficient

<sup>&</sup>lt;sup>d</sup>  $R_{sh}$  of high-resistive poly (undoped) is  $\sim 1 \ k\Omega/\Box$

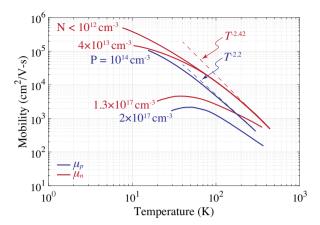

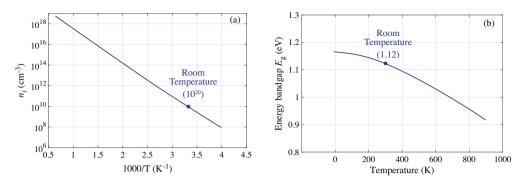

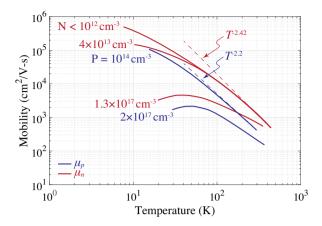

Figure 2.1: Temperature dependence of mobility in doped silicon for different doping concentrations.

Diffusion resistors are made from the n+ or p+ regions which form the source and drain of MOSFETs. These regions are usually silicided to provide a robust connection to the metal interconnect. Using unsilicided diffusion, a decent  $R_{sh}$  can be obtained, which depending on the doping concentration can range from  $\sim 50$  to  $\sim 200~\Omega/\Box$ . The TC of diffusion resistors depends on the doping concentration and ranges from  $\sim +0.08\%/^{\circ}$ C to  $\sim +0.15\%/^{\circ}$ C. As shown in Fig. 2.1, a higher doping level results in a lower TC since the dependence of mobility on temperature becomes weaker at higher doping levels. The TC of diffusion resistors is positive at all doping levels since the charge carrier mobility is mainly determined by phonon scattering [2.3]. Similar to n-well resistors, diffusion resistors have low-levels of flicker noise and suffer from a relatively large VC. The VC of diffusion resistors, however, is lower than that of well resistors [2.4]. This is due to their relatively higher doping concentration, which results in a thinner depletion region.

Poly resistors are made from the polysilicon material used to realize the gate of MOSFETs. Polysilicon consists of amorphous silicon, i.e., grains of silicon with different crystal orientations. As a result, the behavior of polysilicon resistors differs from that of resistors made from mono-crystalline silicon such as n-well or diffusion resistors. They exhibit the largest flicker noise compared to other resistors [2.5]. Poly resistors depend less on the applied voltage and are very linear since they are placed on top of an insulating layer of oxide. This prevents direct junctions between the resistor and the substrate. However, the bottom part of this resistor can still be depleted by the field across the oxide [2.6], which accounts for a small VC. Typical values for the VC of polysilicon resistors are  $\sim 100$  ppm/V. It is known that the average size

of the grains in the polysilicon plays a key role in determining their  $R_{sh}$  and TC [2.7]. As a result, the  $R_{sh}$  and TC of poly resistors are functions of the parameters that determine the size of these grains, such as the chosen time and temperature used to grow and, subsequently, anneal the polysilicon film [2.7]. Polysilicon resistors are often doped with p or n impurities, which can then cause their  $R_{sh}$  and TC to vary depending on the type and dose of the impurity used. It is also known that the dimension of the doped polysilicon resistors is a determining factor of their TC [2.3]. Being dependent on several parameters, the  $R_{sh}$  of poly resistors can range between  $\sim 50$  to  $\sim 350 \ \Omega/\Box$ , while their TC can vary from negative values, e.g.,  $\sim -0.15 \ \%/^{\circ}$ C to positive values, e.g.,  $\sim +0.01 \ \%/^{\circ}$ C [2.7]. As a result, they can be used as temperature-sensing elements in TDCs, in which a high TC is desirable, and also in precision analog circuits, where a near-zero TC is preferred.

There are two other types of resistors available in standard CMOS which are essentially variants of the ones already described: silicided poly and silicided diffusion resistors. Silicide is conventionally used to form a low-resistive interface to the terminals of circuit elements such as the source and drain of MOSFETs or the terminals of resistors. It is formed by the reaction of a metal (usually Titanium) with silicon, which provides a low-resistance, thermally stable, and CMOS-compatible solution for realizing contacts. Silicide, in combination with polysilicon (or diffusion), can make resistors which are highly conductive and, as shown in Table 2.1, exhibit behavior that lies between that of poly (or diffusion) and metal. Silicided poly (or diffusion) resistors have a very low  $R_{sh}$  of  $\sim 5$  to 10  $\Omega/\Box$ , which is considerably higher than that of metal resistors. Their VC is lower than that of unsilicided resistors since their resistance is mainly determined by the silicide layer [2.8], [2.9]. Silicided p+ poly resistors exhibit a very low flicker noise [2.9],[2.10] and also a high TC of  $\sim 0.3 \%/^{\circ}$ C, both similar to that of metal resistors. Their relatively high  $R_{sh}$  compared to metal resistors makes them a suitable choice for realizing TDCs. In some modern Fin-Fet technologies, silicided resistors are not part of the standard fabrication process. Therefore, metal resistors can be employed as an alternative [2.11].

#### 2.1.2 Readout circuits

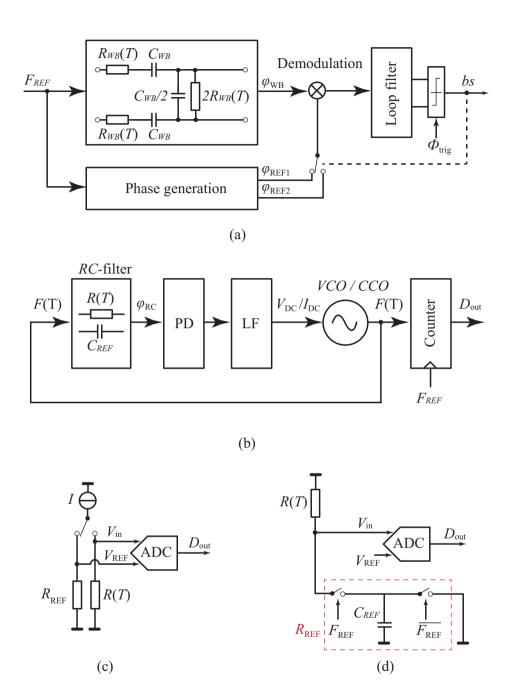

Fig. 2.2 (a) shows one method for digitizing a resistor's value that is used in a variety of resistor-based TDCs [2.9],[2.12],[2.13]. This involves digitizing the phase shift of a Wien Bridge (WB)  $\phi_{WB}$  with respect to a reference phase  $\phi_{REF}$ . When driven by a sine-wave signal, the output of the WB exhibits a phase-shift  $\phi_{WB}$  with respect to the input sine-wave. This output signal is then demodulated by multiplying it by a

sine-wave with the same frequency but a different phase  $\phi_{DEM}$ . This yields a DC term, which is a function of  $\phi_{WB} - \phi_{DEM}$ , along with a higher-frequency term that can be disregarded when sufficiently filtered. In practical implementations, generating a sine-wave reference signal with a precise phase reference and employing an analog multiplier is often not feasible. Instead, a square wave signal and a square-wave mltiplier, i.e., chopper switches, are utilized. It can be demonstrated that this approach only minimally reduces the DC term generated in the demodulation process. To digitize  $\phi_{WB}$ , a phase-domain  $\Sigma\Delta$  ADC can then be used to balance  $\phi_{WB}$  with respect to two demodulation signals with phases  $\phi_{REF1}$  and  $\phi_{REF2}$ . When the modulator is stable, its decimated bitstream bs is a function of  $\phi_{WB}$  and the two phase references  $\phi_{REF1}$  and  $\phi_{REF2}$ .

Over temperature,  $\phi_{WB}(T)$  is a function of the bridge resistance  $R_{WB}(T)$ , the bridge capacitance  $C_{WB}(T)$  and the driving frequency  $F_{REF}(T)$ . To be able to extract  $R_{WB}(T)$  from the digitized  $\phi_{WB}(T)$ , it is essential that  $F_{REF}(T)$  and  $C_{WB}(T)$  are independent of temperature, or at least that their temperature dependence is known. On-chip Metal-Insulator-Metal (MIM) capacitors have an extremely low TC ( $\sim 15$  ppm/°C), resulting in a nearly constant  $C_{WB}$ , while a fixed  $F_{REF}(T)$  can be provided externally. As a result,  $\phi_{WB}(T)$  can be mainly defined by  $R_{WB}(T)$ . One main drawback of this method is the need for an accurate external  $F_{REF}$ , which also needs to have very low jitter (e.g., 1  $ps_{rms}$  used in [2.9]) to avoid adding extra phase error to  $\phi_{REF1}$  and  $\phi_{REF2}$ .

Another method for digitizing a resistor's value is to integrate it in a Frequency-Locked-Loop (FLL) as demonstrated in [2.14],[2.15]. Fig. 2.2 (b) illustrates a simplified diagram for such a readout circuit. The FLL comprises an RC filter, a Phase-Detector (PD), a Loop Filter (LP), and either a Voltage-Controlled Oscillator (VCO) or a Current-Controlled Oscillator (CCO). The RC filter introduces a phase-shift,  $\phi_{RC}$ , at the driving frequency, F(T). This phase shift is detected and then converted into a DC voltage or current by using a PD and the LF, respectively. The VCO or the CCO then outputs F(T). At steady-state, the loop enforces a zero at the output of the PD, thereby keeping the value of  $\phi_{RC}$  fixed. This, in turn, requires F(T) to become a function of the RC components, R(T) and  $C_{REF}$ . The value of F(T) can then be digitized using a counter that is sampled at a much higher frequency,  $F_{REF}$ . Similar to the previously discussed readout method, when both  $F_{REF}$  and  $C_{REF}$  are held constant, the digitized value of F(T) is determined by the value of F(T).

An alternative method of digitizing a resistor's value R(T) is to use a reference resistor  $R_{REF}$  and then digitize their ratio using an ADC. Fig. 2.2 (c) shows an example of a readout circuit using an external  $R_{REF}$  in which an arbitrary bias current

Figure 2.2: Different methods for digitizing a resistor's value: (a) using a phase-domain  $\Sigma\Delta$  modulator, (b) using an FLL, (c) using an external  $R_{REF}$  and a voltage-domain ADC, and (d) replacing  $R_{REF}$  with its switched capacitor equivalent.

excites both R(T) and  $R_{REF}$ . The ratio of output voltages can then be digitized by a voltage-domain ADC [2.16]. The requirement for an external component, however, rules out this method in many applications. Instead, an equivalent on-chip  $R_{REF}$  can be realized, albeit at the cost of less accuracy. As shown in Fig. 2.2 (d),  $R_{REF}$  can also be replaced by its switched-capacitor equivalent using an external reference frequency  $F_{REF}$  and an on-chip capacitor [2.17]. This results in a reference resistor equal to  $1/(C_{REF} \cdot F_{REF})$ , where  $C_{REF}$  is the value of the on-chip capacitor. Similar to the phase-domain readout circuit shown in Fig. 2.2 (a), this method also requires an accurate and low-jitter frequency reference [2.17].

The main drawback of the aforementioned readout circuits is that they require external references or components, which may not be readily available in many applications. However, when such limitations are not a concern, FLL-based TDCs have been shown to be a suitable option for achieving low area consumption [2.14],[2.15]. Moreover, they have exhibited decent accuracy after a single-point trim across a wide temperature range from -40°C to +180°C [2.18].

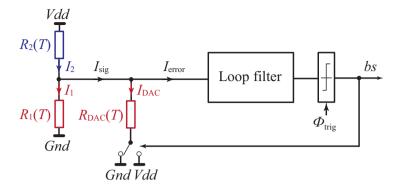

Ratio-metric readout circuits composed of two temperature-dependent resistors can also be used to digitized temperature. Such stand-alone resistor-based TDCs digitize a ratio of two resistor values which can then be mapped to temperature. One example of such a readout circuit, shown in Fig. 2.3, is used in [2.10] and [2.19]. For simplicity, the single-ended realization is shown in this figure. Two types of resistors are configured as a Wheatstone bridge (WhB), which provides a temperature-dependent current  $I_{sig}$ . This current is then balanced against a reference current  $I_{DAC}$  using a  $\Sigma\Delta$  loop that eventually reduces the error signal  $I_{error} = I_{sig} - I_{error}$  to zero.  $I_{DAC}$  is made from one of the resistor types, and the same supply voltage is used to generate the currents. As a result, the output of the TDC becomes a ratio which only depends on the value of the two resistors. Due to the combined temperature dependence of the two resistor types in this ratio, these sensors are the most energy efficient type of on-chip TDCs [2.20].

### 2.1.3 Temperature-sensing inaccuracy and calibration

Neglecting its voltage dependence, the value of a resistor as a function of temperature can be expressed as:

$$R(T) = R(T_r) \left( 1 + TC_1 \cdot (T - T_r) + TC_2 \cdot (T - T_r)^2 \right), \tag{2.1}$$

Figure 2.3: Stand-alone resistor-based readout circuit using two temperature-dependent resistors, and a  $\Sigma\Delta$  modulator to digitize their ratio.

where  $R(T_r)$  is its absolute value at a reference temperature  $T_r$ , and  $TC_1$  and  $TC_2$  are the first- and second-order temperature coefficients (TCs). The resistor's higher-order TCs are neglected in (2.1), which is a reasonable assumption for most temperaturesensing applications. The inaccuracy and the required calibration for resistor-based TDCs thus depend on the variations in  $R(T_r)$ ,  $TC_1$  and  $TC_2$  due to processing spread and the mechanical stress caused by packaging. Unlike BJT-based TDCs, which only have to deal with one major source of spread (see Sec. 2.4), resistor-based TDCs must cope with variations of multiple parameters and thus usually require multiple calibration points ( $\geq 2$ ) to achieve comparable accuracies [2.9]. This is the main disadvantage of resistor-based TDCs, which, in turn, limits their use in lowcost applications. In highly accurate MEMS frequency references, however, multiplepoint calibration is often required and so resistor-based TDCs have been used to compensate for their temperature dependence [2.17]. Furthermore, resistor-based TDCs are capable of obtaining the  $\mu$ K-level resolution required to avoid increasing their phase noise [2.9],[2.13]. Lastly, resistors can be co-integrated with the MEMS, which can then provide good thermal tracking and thus robust compensation.

The sensitivity of a resistor's parameters to mechanical stress can also cause its accuracy to degrade after packaging. This stress sensitivity originates from either the piezo-resistive effect or from dimensional changes in the resistor due to strain. For metal resistors, this change is dominated by the dimensional variation [2.21], while for semiconductor resistors, it is dominated by the piezo-resistive effect [2.22]. Piezo-resistive coefficients, i.e., the variation of resistivity as a function of the applied stress are often empirically found [2.23],[2.24].

The piezo-resistive coefficient of a semiconductor material is a function of tem-

perature, carrier mobility and doping concentration [2.25]. It is known that lower doping concentrations result in a higher piezo-resistive coefficient [2.25]. Therefore, the stress sensitivity of n-well resistors is much higher than that of heavily doped diffusion resistors. Poly resistors are also stress-sensitive, but less than n-well or diffusion resistors [2.26]. Finally, metal resistors have the lowest stress sensitivity. Temperature also affects the piezo-resistive coefficient. It has been shown that at  $-75^{\circ}$ C, the piezo-resistive coefficient can be  $2 \times$  higher than at  $+175^{\circ}$ C [2.25].

For a single-crystalline p-type resistor, the stress of 150 MPa creates a relative error  $\Delta R/R$  of  $\sim 7\%$  [2.22]. For this p-type resistor, piezo-resistive coefficients have opposite signs for different orientations of the resistor. As a result, a series combination of two resistors that are perpendicular to each other could greatly reduce the effect of stress [2.23]. For an n-type resistor, however, such cancellation found to be not perfect [2.24]. Semiconductor resistors are generally more sensitive to stress ( $\sim 15 \times$  to  $40 \times$ ) than vertical BJTs [2.27]. Even with *L-shaped* layout, they are at least 2-3× more stress-sensitive. The higher sensitivity of the resistors to mechanical stress imposes the need for post-packaging multi-point calibration and also introduces long-term reliability issues. The latter is because packaging stress can change over time due to variations in the encapsulation material used [2.28]–[2.30].

In [2.12], the accuracy of TDCs based on four different types of resistors (n-well, unsilicided n+ poly, unsilicided n+ and p+ diffusion resistors) implemented in a 0.18- $\mu$ m CMOS technology is compared. The results show that the n+ poly resistor is the most accurate, resulting in 0.24% relative temperature-sensing inaccuracy  $(\pm 3\sigma)$  after a three-point calibration. Similar results are shown in [2.13] using an n+ poly resistor which achieves 0.2% relative inaccuracy. However, silicided poly resistors achieve better accuracy than unsilicided ones. In [2.9], use of a silicided p+ poly resistor in the same  $0.18-\mu m$  CMOS technology resulted in 0.05% relative inaccuracy after a two-point trim. In the same work, while using the same readout circuit, an unsilicided n+ poly resistor achieved 0.48% relative inaccuracy after a two-point trim, which is about 10× worse. The flicker noise corner of the silicided p+ poly resistor has also been measured to be about  $10 \times$  lower than that of the unsilicided n+ poly resistor: 1 Hz versus 10 Hz. The silicided p+ poly resistor also shows less stress sensitivity than the n+ poly. When the TDCs are packaged in plastic, the silicided p+ poly sensor shows a shift of about  $\sim 0.2$  °C, while this is about  $\sim 1.4$  °C and  $\sim 2.5$  °C for n+ poly and highly resistive poly (undoped polysilicon) resistors. TDCs based on silicided p+ poly and n+ poly in a 65-nm technology achieve relative inaccuracies of 0.19% and 0.34\% after a two-point trim [2.31]. Using a one-point trim, the inaccuracy achieved is about  $20 \times$  worse: 4% and 7.2%.

Stand-alone TDCs using two types of resistors are expected to have worse accuracy and stress sensitivity than those that use only one type. This is due to the combined effect of spread and stress on the two types of resistors, which is unlikely to be correlated or canceled out. In [2.19], the combination of an n+ poly and a p+ diffusion is used, resulting in a relative inaccuracy of 1.1% (Max-Min) after a one-point trim. This then drops to 0.23% after a two-point trim. A better result is obtained by combining a silicided p+ poly and an n+ poly resistor, as done in [2.10]. Although the TDC shows a large untrimmed inaccuracy of 8.3%, using a one-point trim can reduce this to 1.1% ( $3\sigma$ ), and using a two-point trim can reduce it even further to 0.13%. Slightly better accuracy has been demonstrated in [2.20] using a silicided diffusion resistor combined with an n+ poly resistor.

# 2.2 Thermal diffusivity (TD) based TDCs

#### 2.2.1 Principle of operation

Another method for realizing a CMOS TDC is to measure the temperature-dependent rate at which heat diffuses through silicon [2.32],[2.33]. The thermal diffusivity of silicon  $D_{si}$ , is a measure of the speed at which heat diffuses through silicon.  $D_{si} = k_{si}/(\rho_{si} \cdot C_{si})$ , where  $k_{si}$  is the heat conductivity,  $\rho_{si}$  is the density of silicon and  $C_{si}$  is its thermal capacity.

In standard CMOS, the substrate is made from lightly doped silicon, and so its thermal characteristics are close to that of pure silicon. As a result,  $D_{sub}$  is similar to  $D_{si}$ , and it is reasonably process-independent.  $D_{si}$  is also a strong function of absolute temperature [2.32]. Over the industrial temperature range,  $D_{si}$  can be approximated to within a few percentage points with a power law, i.e.,  $D_{si} \propto T^{-n}$ , where the n of pure silicon is  $\sim 1.8$  [2.34]. Measurements show that  $D_{si}$  varies from 2  $cm^2s^{-1}$  at 200 K to 0.53  $cm^2s^{-1}$  at 400 K [2.34].

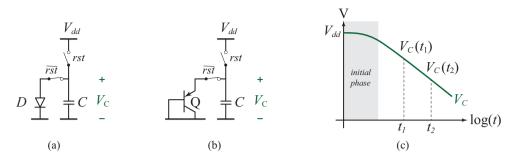

#### 2.2.2 Readout circuits

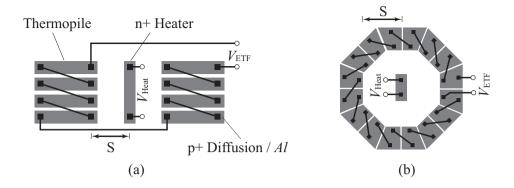

In order to measure  $D_{sub}$ , thermal-diffusivity (TD) sensors based on electro-thermal filters (ETFs) are used. An ETF consists of a heater and a relative temperature sensor placed in close proximity (see Fig. 2.4). An ETF behaves like a low pass filter in thermal domain, exhibiting a phase shift between the output of the temperature sensors and the applied heat [2.35]. This phase shift is not only a function of the frequency of the applied heat but also of the geometry of the ETF and  $D_{sub}$  [2.33].

Figure 2.4: Electro-thermal filters (ETF) realized in CMOS. (a) A bar-type ETF, taken from [2.33]. (b) optimized ETF by placing a thermopile in a fixed phase shift contour around the heater, taken from [2.38].

The geometry is defined by lithography, which can be considered very accurate for relatively large ETF dimensions. The phase shift of the ETF at a known frequency will thus be mainly determined by  $D_{sub}$ .

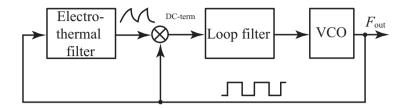

The objective of the readout circuit of a TD sensor is to digitize the phase shift of the ETF. This can be done by incorporating it in a Frequency-Locked Loop (FLL), which generates a temperature-dependent output frequency, as shown in Fig. 2.5 [2.32],[2.33]. The output frequency can be digitized using a higher frequency reference provided externally [2.33],[2.36]. Alternatively, the phase shift of an ETF driven by a known frequency,  $F_{REF}$ , can be digitized with a phase-domain  $\Sigma\Delta$  modulator similar to that used in the resistor-based TDCs shown in Fig. 2.2 (a), except that the ETF replaces the WB [2.36],[2.37].

As shown in Fig. 2.4 (a), the heater of the ETF is realized with n+ diffusion, while the temperature sensor consists of thermocouple junctions of p+ diffusion and Al that are placed at a distance s from the heater's centroid. To further maximize the sensitivity, a number of thermocouples are daisy-chained around the heater to form a thermopile. The thermopile is a relative temperature sensor which creates an output voltage proportional to the Seebeck coefficient of the junction and the temperature difference between the hot and cold junctions at each side of the thermocouple arm. Taking the temperature gradient of the heat pulses into account, reducing s causes a larger signal between the hot and cold junctions, but also means that the distance s will become comparable to the ETF's geometry, resulting in lower accuracy [2.33]. This results in a trade-off between accuracy and resolution in TD-based sensors.

One main consideration in designing TD-based sensors is the mitigation of additive

Figure 2.5: Thermal-diffusivity based sensor using a frequency-locked-loop (FLL) readout circuit. The output frequency is proportional to the phase shift of the ETF.

phase shift errors. These, for instance, can originate from the electrical filtering caused by the resistance of the p+ arms of the thermocouple with the capacitance formed between them and the n-well. Similarly, an additional phase shift can be caused by any readout circuitry that is directly connected to the ETF's output, for instance, an amplifier. Although increasing the arm length of the ETF increases the hot-cold difference and results in a higher signal, it also increases the resistance, electrical phase shift, and thermal noise. When it is not calibrated, the large spread of thermocouple resistance can contribute substantially to the temperature-sensing errors [28]. Since these resistances are also temperature-dependent, they can create a temperature-dependent error that cannot be removed with a one-time calibration. Therefore phase calibration might be required, as suggested in [2.38]. Another major drawback of TD-based sensors is their relatively large power consumption (a few mW) most of which (> 80%) is consumed by the heater to create a sufficiently large electrical signal at the output of the thermopile ( $\sim 1-5$  mV). Compared to other types of TDCs, TD-sensors consume the most power.

#### 2.2.3 Temperature-sensing inaccuracy and calibration

Without trimming, TD-based sensors in 0.7- $\mu$ m CMOS technology achieve relative temperature-sensing inaccuracies of 0.69% (3 $\sigma$ ) and 1.38% (3 $\sigma$ ), respectively, for thermopiles with s=20 and 10  $\mu$ m [2.36]. By optimizing the layout of the ETF in the same technology, the inaccuracy achieved could be improved by  $2 \times [2.37]$ . Compared to the parallel placement of thermocouple arms on each side of the bar-type heater in [2.36], in the optimized ETF in [2.37], the arms are placed in a fixed phase-shift

contour around a central heater. Fig. 2.4 (b) shows an example of an optimized ETF in which the resistance of the thermopile is also reduced [2.38]. The improved inaccuracy in [2.37] is mainly due to the large choice of s (= 24  $\mu$ m) compared to the ETF's geometry, which reduced the SNR. This, in turn, means that a relatively long conversion time of  $\sim 6.25$  s is required to obtain a 30 mK<sub>rms</sub> [2.37]. Using the same ETF dimensions of [2.37], but realized in a 0.18- $\mu$ m technology, results in an improved inaccuracy due to the higher accuracy of the lithography, with a 0.22% inaccuracy [2.39].

TD-based sensors can also be made very small, occupying for instance 0.0017 mm<sup>2</sup> in a 40-nm standard CMOS technology [2.38], which is one of the smallest temperature sensors reported to date. This level of area consumption is mainly achieved due to better lithographic accuracy allowing both s to be reduced, and the use of mostlydigital phase-domain readout circuitry [2.38]. The distance  $s = 2 \mu m$  chosen in this TD sensor is  $\sim 10 \times$  lower than the previously mentioned TD sensors. The sensor is also realized in an octagonal thermopile shape (see Fig. 2.4 (b)), which increases it's SNR. After a batch-calibration to extract the average parameters of a fifth-order master curve, the TD sensor in [2.38] achieves inaccuracies of 1.7% (3 $\sigma$ ) and 2.79%  $(3\sigma)$  for ETFs with  $s=3.3~\mu\mathrm{m}$  and  $s=2~\mu\mathrm{m}$ , respectively. Compared to [2.37] and [2.39], the TD-based sensor in [2.38] also achieves a substantially larger bandwidth of 500 Hz, which is an improvement of more than  $\sim 1000\times$ . Increasing the driving frequency, however, imposes an additional electrical phase shift on both the ETF and the readout circuit, resulting in the need for a background phase calibration to remove them from the phase shift of interest. After a continuous phase calibration, the inaccuracy of the two TD-based sensors drops to 0.6% ( $3\sigma$ ) and 1% ( $3\sigma$ ), respectively.

Based on the implemented TD-based sensors in standard CMOS technology nodes from 0.7- $\mu$ m to 40-nm CMOS, it can be concluded that TD sensors can be very accurate when the ETF is realized with a relatively large s ( $\sim 10~\mu$ m): untrimmed inaccuracies of  $\sim \pm 0.2^{\circ}$ C ( $\sigma$ ) from  $-55^{\circ}$ C to  $+125^{\circ}$ C [2.40]. The ability to achieve such decent accuracy without trimming is the main advantage of TD sensors. In [2.41], this specific characteristic of TD sensors is exploited to self-calibrate a low-power and energy-efficient resistor-based sensor. Since both sensor types can be read out by a phase-domain ADC, the area overhead is minimal. Ultimately, the TD sensor, achieving a  $3\sigma$ -inaccuracy of  $\sim 0.2^{\circ}$ C, is employed to self-calibrate the resistive sensor at two temperatures, significantly reducing its  $3\sigma$ -inaccuracy from  $\sim 10^{\circ}$ C to  $\sim 0.25^{\circ}$ C.

In [2.40], however, TD sensors exhibited a batch-to-batch shift of about 2°C. Although this could be corrected by a single-point trim, this removes most of the accuracy advantages of TD sensors. One hypothesis is that this shift is caused by the

spread of the doping in the substrate and the spread of thickness in epi-layer [2.40], which changes the thermal properties of ETF. In line with this, sensors fabricated in an SOI process exhibited  $10 \times$  less batch-to-batch shift [2.40]. The effect of packaging on TD-based sensors has been reported in [2.38], [2.39] and [2.40], which show an increase in the sample-to-sample spread with plastic packaging compared to that with relatively stress-free ceramic packaging. This is due to either the sensitivity of  $D_{si}$  to mechanical stress [2.42], or to the extra self-heating in the plastic packaging [2.40]. However, the shift is only about  $\pm 0.1^{\circ}$ C [2.40], which eliminates the need for post-package trimming for TD sensors.

#### 2.3 MOSFET-based TDCs

#### 2.3.1 Principle of operation

The temperature-dependent characteristic of MOSFETs can also be used to realize TDCs. The key advantage of MOSFET-based TDCs is their ability to operate with low supply voltages (e.g., 0.5 V), dissipating very little power (e.g., tens of nanowatts), or ocuppying a very small area (e.g., 0.001 mm²) [2.43]–[2.45]. However, they achieve poor accuracies due to the several process dependent parameters that determine MOSFET behavior, and they are sensitive to packaging stress. As a result, MOSFET-based TDCs require a multi-point (post-packaging) calibration to obtain accuracies comparable to those of BJT-based TDCs. When the operating temperature range is limited, for instance in health applications, or when ultra-low power consumption is required, for instance in IoT sensing nodes, MOSFET-based TDCs are suitable candidates [2.43],[2.46].

MOSFETs can be biased in different operating regions. When the Gate-Source voltage  $V_{GS}$  surpasses the threshold voltage  $V_T$ , the channel under the gate is inverted, i.e., the concentration of mobile carriers at the surface (with opposite polarity) exceeds the dopant density in the bulk. In this inversion region, depending on the Drain-Source voltage  $V_{DS}$ , the MOSFET operates in either the triode or saturation region. The drain current then becomes a function of  $V_{GS}$ ,  $V_{DS}$ , mobility  $\mu$ , and  $V_T$ .

When  $V_{GS}$  is below  $V_T$ , the channel under the gate of a MOSFET is not inverted. Nevertheless, the number of mobile carriers at the surface exhibits an exponential dependence on  $V_{GS}$ . In this so-called sub-threshold region, applying a  $V_{DS}$  that is larger than the drain saturation voltage  $V_{DSAT}$  results in a current that can be approximated as:

$$I_{D,sth} = (m-1) \mu C_{ox} \frac{W}{L} \left(\frac{kT}{q}\right) exp\left(\frac{q \cdot (V_{GS} - V_T)}{mkT}\right) \cdot \nu_{sat}, \qquad (2.2)$$

where m is the subthreshold factor defined as  $m = 1 + C_D/C_{ox}$  that can range from 1.1 to 1.4,  $C_D$  and  $C_{ox}$  are the depletion and oxide capacitances, and  $\nu_{sat}$  is the saturated velocity. This exponential  $I_D - V_{GS}$  relationship resembles the  $I_C - V_{BE}$  characteristics of BJT, albeit with additional parameters involved.

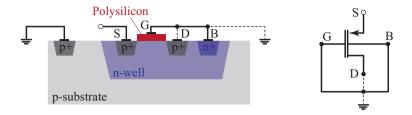

A MOSFET can also be used as a dynamic threshold device: DTMOST [2.47]–[2.49]. In this configuration, the gate and the well of a MOSFET are tied together as shown in Fig. 2.6. This prevent the formation of a strong channel under the gate, and thus, the device exhibits behavior similar to a subthreshold MOSFET. A DTMOST can also be viewed as a lateral PNP device with an extra polysilicon gate placed on top of the base region resulting in a lower apparent bandgap voltage [2.47]. This is due to a built-in voltage appearing between the polysilicon gate and the silicon well that will then be divided between the  $C_{ox}$  and  $C_{D}$  of the MOSFET. In a 0.35- $\mu$ m technology, this is  $\sim 0.6$  V, which is about half of the silicon bandgap voltage.

The temperature dependence of MOSFETs relies on that of the parameters involved in their model. Among the most critical parameters are  $\mu$  and  $V_T$ , whose temperature dependence is often described by simple empirical model. As discussed in A.3,  $\mu(T) = (T_r)(T/T_r)^m$ , where m is a process-dependent constant, and  $\mu(T_r)$  is the value of  $\mu$  at a reference temperature  $T_r$ . Similarly, the threshold voltage is given by  $V_T(T) = V_T(T_r) - \alpha_{V_T}(T - T_r)$ , where  $\alpha_{V_T}$  is a process-dependent constant ranging from 1 to 4  $mV/^{\circ}C$ , and  $V_T(T_r)$  is the value of  $V_T$  at a reference temperature  $T_r$ . To understand the variations of the parameters m and  $\alpha$  due to process or stress, a thorough understanding of the physical dependence of  $\mu$  and  $V_T$  is necessary. For instance,  $V_T$  relies on several physical parameters, including intrinsic carrier concentration, dopant density, oxide capacitance per unit area, permittivity of silicon, metal-semiconductor work function difference, and fixed charges in the oxide layer.

#### 2.3.2 Readout circuits

MOSFET-based TDCs have been realized with different readout circuits. These circuits can best be classified in three main categories, which operate based on the digitization of the (1) temperature-dependent propagation delay of a delay cell, (2) temperature-dependent frequency of an oscillator or a ring oscillator, and (3) temperature-dependent ratios of voltages or currents derived from MOSFET charac-

Figure 2.6: P-type dynamic threshold MOS transistor (DTMOST) realized in a CMOS technology.

teristics.

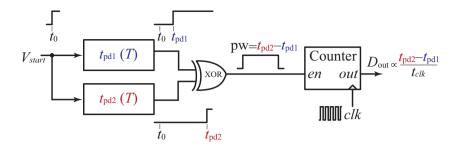

In the first category, the readout circuit is based on digitizing the width of a pulse, which is determined by the propagation delay  $(t_{pd})$  of some delay cells [2.43],[2.50]. The pulse-width is controlled by controlling its rising edge, falling edge, or both. This pulse-width is then digitized by using a counter clocked by a higher frequency reference. In [2.50], the pulse-width is determined by the propagation delay of CMOS inverters that control only one edge of the pulse.  $t_{pd}$  is thus related to dimensions,  $V_T$  and  $\mu$  of the MOSFETs in the inverter and also the supply voltage. In [2.43], the pulse-width is defined by the  $t_{pd}$  of two delay cells, which independently determine the rising and falling edges of a pulse, as shown in Fig. 2.7. Unlike using an inverter as the delay determining element, the delay of these two cells is controlled by two temperature-dependent currents derived from MOSFETs in the subthreshold region.  $V_{GS}$  and  $V_{DS}$  of the MOSFETs are converted into current using V-I converters. Several other examples have been shown in the literature for the digitization of temperature-dependent delays, for instance in [2.51] and [2.52]. One drawback of these delay-based readout circuits is the dependency of  $t_{pd}$  to supply variations, which can be as high as  $1 \,^{\circ}\text{C/mV}$  [2.53]. The challenge is, then, to provide a regulated supply voltage for the delay cells which is also temperature-independent.

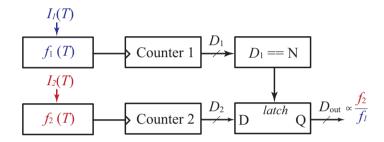

The second category of readout circuits is based on the digitization of the temperature dependent frequency of an oscillator (or two oscillators). This process is very similar to that of delay-based readout circuits, as the frequency of oscillation is also defined by some propagation delays. Fig. 2.8 illustrates one example, in which  $I_1$  and  $I_2$  are derived from the temperature-dependent characteristics of MOSFETs that determine the frequencies of two ring oscillators. The ratio of these frequencies is then obtained by using an asynchronous counter as shown in Fig. 2.8 [2.54],[2.55]. A temperature-dependent frequency can also be obtained by using temperature-dependent delay cells inside the ring oscillator as used in [2.56]–[2.58]. This category of MOSFET-based

Figure 2.7: Readout circuit using temperature-dependent propagation delays.

Figure 2.8: Readout circuit using temperature-dependent frequencies.

TDCs has also showed a high level of supply dependence. Mitigating this sensitivity thus remains an ongoing challenge, with efforts focused on employing circuit techniques and implementing effective supply regulation strategies [2.56],[2.57],[2.59].

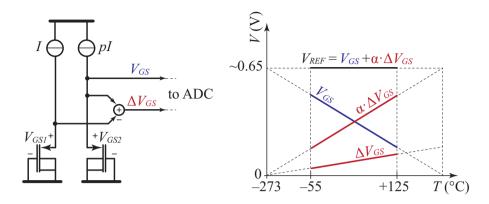

In the third category of readout circuits, a voltage-domain ADC is used to digitize the ratio of two temperature-dependent voltages derived from MOSFETs. Similarly, this can be done by obtaining temperature-dependent currents or charges and then digitizing their ratio with the corresponding current or charge domain ADCs. In [2.48],[2.49], temperature-dependent signals are derived from two DTMOSTs that are biased at a fixed current ratio as illustrated in Fig. 2.9. The  $V_{GS}$  ( $V_{GS2}$ ) of a DTMOST has a CTAT characteristic, while the difference between the two  $V_{GS}$ , i.e.,  $\Delta V_{GS} (= V_{GS2} - V_{GS1})$ , has a PTAT characteristic. The combination of  $V_{GS}$  and  $\Delta V_{GS}$  can result in a flat reference voltage  $V_{REF}$  (=  $V_{GS} + \alpha \cdot \Delta V_{GS}$ ), where  $\alpha$  is a gain factor. A voltage-domain ADC can then digitize the ratio  $\alpha \cdot \Delta V_{GS}/V_{REF}$  as an indication of temperature. Combining  $V_{GS}$  and  $\Delta V_{GS}$  has also been used to realize low-voltage ( $\sim$ 0.6 V) bandgap voltage references [2.47].

Figure 2.9: Operation principle of DTMOST-based temperature sensors, taken from [2.48].

#### 2.3.3 Temperature-sensing inaccuracy and calibration

Based on the reported results in the literature [2.60], MOSFETs in the saturation and triode regions are usually less accurate than MOSFETs in either the subthreshold region or configured as a DTMOST. As an example, in [2.61] a current is derived from a MOSFET in its triode region, which is then used to obtain temperature-dependent delay. Realized in a 0.18-µm CMOS technology, and using a time-domain readout circuit, the TDC achieves a relative inaccuracy of 2% (Max-Min) after a two-point calibration. The TDC in [2.53] is another example in which delay cells of a ring-oscillator are determined by MOSFETs in their saturation region. Realized in 65-nm CMOS technology, this TDC achieved inaccuracies of 2.73% (Max-Min) using one-point calibration.

In the subthreshold region, MOSFET-based TDCs seem to be more accurate. The TDC in [2.54], which is realized in a 0.18- $\mu$ m CMOS technology, uses two MOSFETs in the subthreshold region to generate two temperature-dependent currents. These MOSFETs have the same dimensions and  $V_{GS}$  but different  $V_{DS}$ . The ratio of the two currents is then digitized to generate a function of temperature, achieving temperature-sensing inaccuracies of 2% (Max-Min) after a two-point calibration. Similar results have been obtained in 65-nm CMOS technology by using two MOSFETs in the subthreshold region [2.51],[2.55]. Unlike [2.54] and [2.55], the MOSFETs in [2.51] have the same  $V_{DS}$  but different  $V_{GS}$  for generating the temperature-dependent currents. It then achieves an inaccuracy of 3% (Max-Min) after a two-point calibration. Better results have been reported in [2.56], in which MOSFETs in the subthreshold

2.4 BJT-based TDCs 27

region are used as the delay cell of a ring oscillator obtaining 0.42% relative inaccuracy after a two-point calibration. It is worth mentioning that the TDCs in [2.51], [2.54] and [2.56] all consume less than 1  $\mu$ W, while [2.51] and [2.54] could also operate below 0.8 V supply voltages.

MOSFETs configured as DTMOSTs have shown the best in class temperaturesensing inaccuracies and supply sensitivity. In a 0.16- $\mu$ m CMOS technology, DTMOSTbased TDCs achieve inaccuracies of 0.48% (3 $\sigma$ ) after a one-point calibration [2.48],[2.49]. In 28nm CMOS, a sensor achieves inaccuracy of 1.8% (3 $\sigma$ ) after a one-point calibration [2.62], while obtaining the lowest supply sensitivity among MOSFET-based TDCs.

One drawback of MOSFET-based TDCs is the higher sensitivity of MOSFETs to mechanical stress compared to BJTs. This not only results in costly post package calibration but may also cause long-term stability issues. It is known that mobility increases with the applied stress, e.g., 200 MPa stress causes  $\sim 10\%$  variation in mobility [2.63]. The threshold voltage of long channel MOSFETs, on the other hand, is at least  $\sim 10\times$  less sensitive to stress than mobility [2.64], and can therefore be ignored. In short-channel MOSFETs, the drain saturation voltage  $V_{dsat}$  is affected by the velocity saturation, making  $V_{dsat}$  more sensitive to stress than the  $V_T$  of long channel devices. The  $V_{dsat}$  of an NMOSFET varies by  $\sim -1.5\%$  and  $\sim -3.5\%$ , for  $\sim 140$  MPa tensile and compressive stress, respectively [2.64].

#### 2.4 BJT-based TDCs

### 2.4.1 BJTs in CMOS Technology

The most common method for realizing a TDC is to use Bipolar Junction Transistors (BJTs). In standard CMOS processes, two types of BJTs can be realized: vertical and lateral.

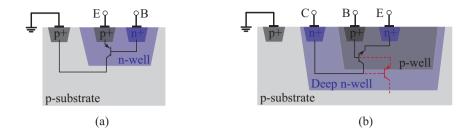

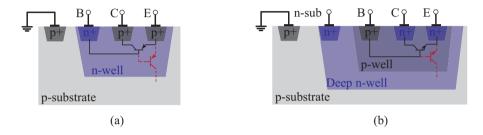

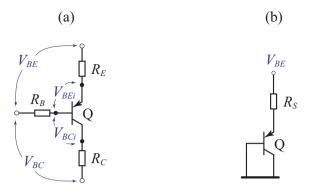

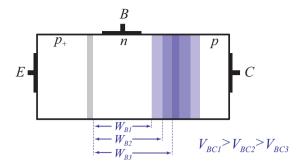

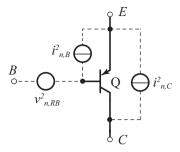

In vertical BJTs, the direction of current flow is perpendicular to the silicon surface. In the case of vertical PNPs, a p+ diffusion functions as the emitter, the n-well is the base and the p-substrate is the collector (see Fig. 2.10 (a)). A vertical PNP can be realized in any CMOS technology, since realizing an n-well is always possible. A vertical NPN, on the other hand, can only be realized in twin-well CMOS technologies, which allow the realization of a deep n-well (see Fig. 2.10 (b)). The key disadvantage of vertical PNPs is that their collector has a low-resistive path to the p-substrate and thus inevitably has the same (ground) potential. As a result, the only accessible terminals are the emitter and the base, which can then be used to

Figure 2.10: Vertical BJTs in CMOS technologies: (a) Vertical PNP and (b) vertical NPN. Red shows the parasitic vertical PNP associated with the vertical NPN.

Figure 2.11: Lateral BJTs available in CMOS technologies. (a) Lateral PNP and (b) lateral NPN. Red shows the parasitic vertical devices.

bias the device. This is not the case for vertical NPNs, as the p-well potential can be freely chosen. Vertical NPNs, however, come with a parasitic vertical PNP with a grounded collector, as shown in Fig. 2.10 (b). This causes the  $V_{BC}$  of the main NPN to appear as the  $V_{BE}$  of the PNP device, whose emitter current will be added to the base current of the NPN. One way to avoid this current is to use the vertical NPN in a diode-connected configuration (i.e., its  $V_{BC}=0$ ), in which the PNP has zero potential across its  $V_{BE}$ .

Lateral BJTs are made using doped regions near the surface that are usually used to form the drain and source of MOSFETs. In the case of a lateral PNP, p+ regions can form the collector and emitter terminals while an n-well forms the base. Unlike the vertical PNP, a lateral PNP has a free collector that can be set at arbitrary voltages. Although this is a potential advantage, this device is used less frequently compared to the vertical PNP. One reason is that there is an extra vertical device (see Fig. 2.11 (a)) that adds to its emitter current. In conventional bipolar technology, a buried n+ region prevents the formation of this vertical PNP. Similarly, in twin-well CMOS technologies, the deep n-well can be used to prevent currents from flowing through the vertical emitter (see Fig. 2.11 (b)). In standard CMOS technology, this layer does not

2.4 BJT-based TDCs 29

exist, and therefore lateral PNPs are inevitably associated with the vertical device. To reduce the effect of the parasitic device, the ratio  $I_{CL}/I_{CV}$  must be maximized, where  $I_{CL}$  is the lateral collector current, and  $I_{CV}$  is the vertical collector current. This can be achieved by minimizing the emitter area and the lateral base width, and by having the collector surround the emitter [2.65]. Experimental results show that the ratio  $I_{CL}/I_{CV}$  can be 1.5 to 4, which means that the lateral bipolar contributes 60% to 80% of the total current [2.65],[2.66].

#### 2.4.2 Principle of operation

Ideally, BJTs have an exponential  $I_C - V_{BE}$  characteristic that can be expressed as:

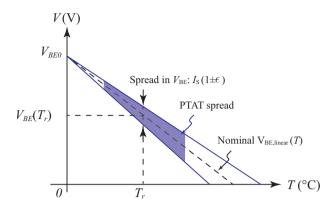

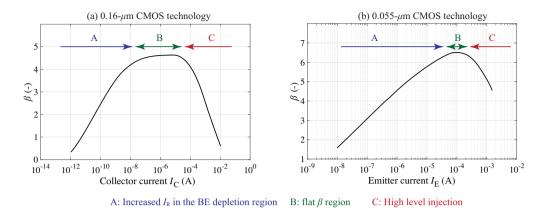

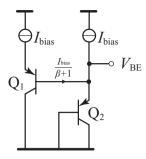

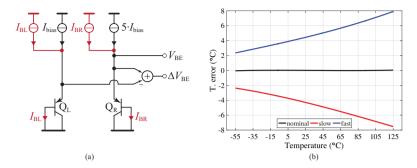

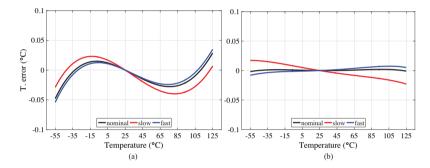

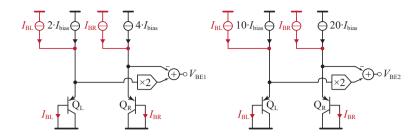

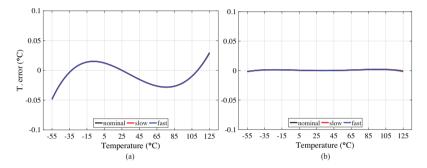

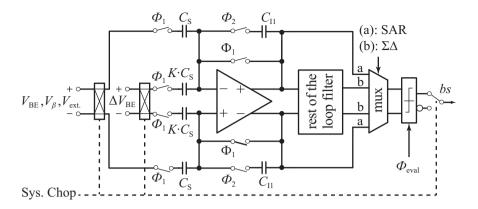

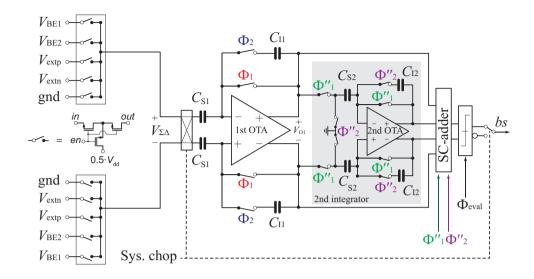

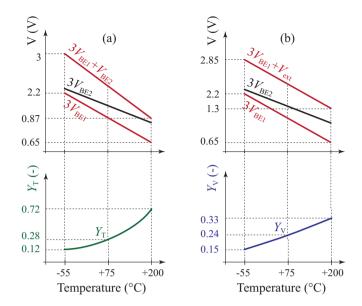

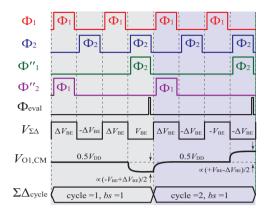

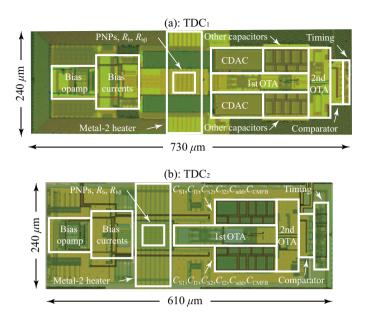

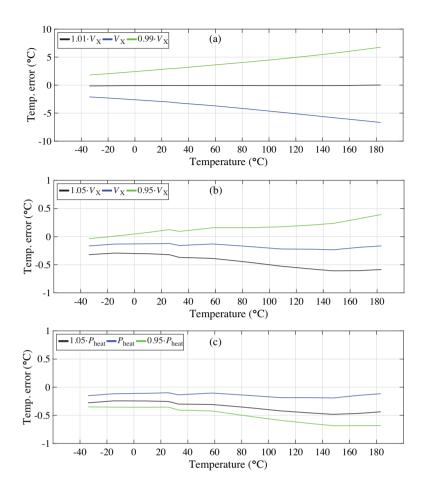

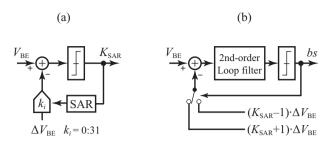

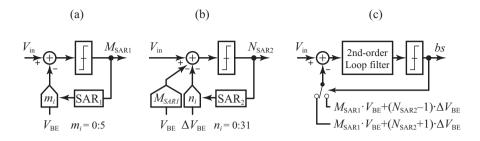

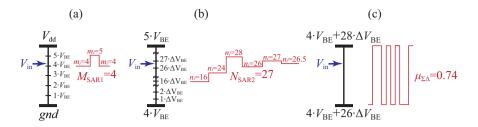

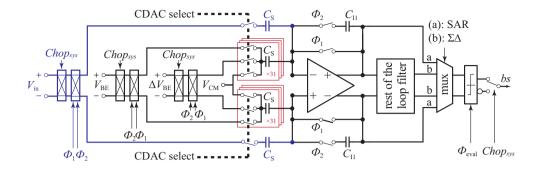

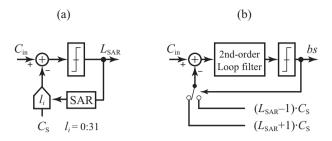

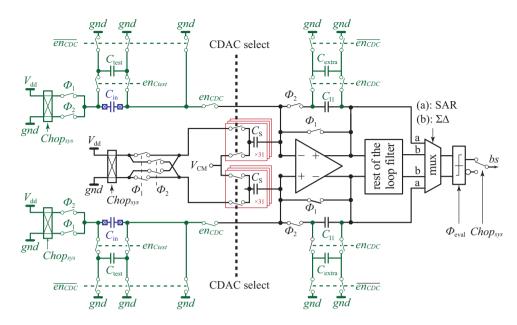

$$V_{BE} = n_F \frac{kT}{q} ln \left( \frac{I_C}{I_S} + 1 \right) , \qquad (2.3)$$