# Achieving Optimal Power Performance with Advanced FinFET Technology for NAND Memory Applications up to 8Gb/s I/O Bandwidth

**Master Thesis**

Arvis Jomerts

St. nr. 4840917

University Supervisors: Prof. Dr. ir. S. Hamdiuoi, Prof. Dr. ir. G. Gaydadjiev

Imec Supervisor: Dr. A. Spessot

Imec Advisors: Dr. I. G. Guerra, Dr. N. Pantano

Faculty: Faculty of Electrical Engineering, Delft

Image: vecteezy.com/Timplaru Emil

Style: TU Delft Report Style, with modifications by Daan Zwaneveld

This page was intentionally left blank

## Acknowledgements

After 9 months of sheer dedication to this project, I present this letter of appreciation with great pleasure. First of all, I would like to express sincere gratitude to my Imec Project Manager Alessio Spessot for giving me a chance to obtain valuable experience in the industry environment, as well as continuous support and guidance throughout the project. I am extremely grateful to my daily Imec Supervisors Nicolas Pantano and Ivick Guerra Gomez for providing me with a continuous feedback loop, technical and practical advice, which helped me to elevate the quality of this thesis to a higher level. Their availability for Q&A sessions is highly appreciated, as without them, several doubts would be hard to straighten out.

I am also thankful to Delft University of Technology and its staff members for the quality of education they provide on a daily basis. Special thanks to Said Hamdioui and Georgi Gaydadjiev for accepting me under their supervision for this master thesis, and their inputs on the project during progress update meetings.

Lastly, I would like to mention Elma Lūcija Ulmane, who provided me with useful recommendations on thesis layout and figure visual representation. I would be remiss in not mentioning Kavitha Soundrapandiyan, with whom we had constructive discussion sessions on technical aspects of the project and on practical day-to-day matters.

Arvis Jomerts Delft, October 2023

## Abstract

3D NAND memory devices are intrinsically very cost sensitive, implying that their size, and hence logic area must be limited in order to acquire a chip which is able to conquer the competitive market price. Market forecasts of upcoming NAND products predict Input/Output (I/O) speed increase well beyond 2 Gb/s that is the current industry standard. I/O bandwidth strongly correlates with the device technology used for logic and the current state-of-the-art planar devices are predicted to reach their maximum capabilities in the near future. Use of FinFET transistor is expected to substantially enhance I/O area-performance of 3D NAND memory logic, alleviating area restriction severity and providing a foundation for future periphery generations to come.

In this thesis, a 3D NAND compatible I/O able to achieve 8 Gb/s throughput has been developed using simulation of thermally stable Imec in-house developed 14 nm FinFET technology equivalent. To validate throughput quality, industry defined eye diagram standards are used. To determine area savings provided by utilizing FinFET devices, FinFET active transmitter area is benchmarked against 45 nm planar device setup achieving the same 8 Gb/s data rate performance. To ensure an unbiased comparison, two signaling topologies are used - single ended signaling (SES) and differential signaling (DS). To extend analysis, sensitivity of the design against various parameters such as data rate, voltage and temperature is explored.

It is concluded, that active area of FinFET driver is several times lower than that of similar planar transmitter (same power and throughput) for both SES and DS. Additionally, suitable use cases of DS and SES have been evaluated depending on environmental conditions investigated during sensitivity analysis. All in all, this research provides a baseline for planar-to-FinFET scaling in I/O system and guidelines in choosing signaling topology appropriately, depending on system constraints.

# Contents

| Αc  | knov  | vledgements                                            | ii             |

|-----|-------|--------------------------------------------------------|----------------|

| Ak  | strac | et                                                     | iii            |

| Lis | st of | Figures                                                | νi             |

| No  | men   | clature                                                | ix             |

| 1   | Intro | oduction                                               | 1              |

|     | 1.1   | Motivation                                             | 1              |

|     | 1.2   | Contributions                                          | 1              |

|     | 1.3   | Thesis Outline                                         | 2              |

| 2   | 3D N  | NAND I/O Interface and Topology Overview               | 3              |

|     | 2.1   | 3D NAND I/O General Considerations                     | 3              |

|     | 2.2   | I/O Interconnect Topologies                            | 4              |

|     |       | 2.2.1 Single Ended Signalling Topologies               | 5              |

|     |       | 2.2.2 Differential Signalling Topologies               | 12             |

|     | 2.3   | Receiver Options                                       | 16             |

|     |       | 2.3.1 Static Receivers                                 | 17             |

|     |       |                                                        | 21             |

|     | 2.4   |                                                        | 23             |

|     |       | ·                                                      | 23             |

|     | ۰.    | 11                                                     | 24             |

|     | 2.5   |                                                        | 29             |

|     |       | 1 1 5                                                  | 29<br>32       |

|     | 2.6   |                                                        | 34             |

|     | 2.0   |                                                        | 3 <del>4</del> |

|     |       |                                                        | 36             |

|     | 2.7   |                                                        | 38             |

|     |       | ,                                                      | 38             |

|     |       |                                                        | 39             |

|     |       |                                                        | 39             |

|     |       |                                                        | 40             |

|     |       |                                                        | 41             |

|     |       | 2.7.6 Variation of Process and its Impact              | 42             |

|     |       |                                                        | 42             |

|     |       | 2.7.8 Variation of Jitter and its Impact               | 43             |

| 3   | Sele  | ection of Topology and Design Case Simulations         | 44             |

| _   | 3.1   | 1 0)                                                   | 44             |

|     | 3.2   |                                                        | 45             |

|     |       | 3.2.1 Quality Requirements                             | 45             |

|     |       | 3.2.2 Signal Limitations and Non-idealities            | 46             |

|     | 3.3   |                                                        | 53             |

|     |       | ,                                                      | 54             |

|     |       |                                                        | 56             |

|     |       |                                                        | 57             |

|     |       |                                                        | 57             |

|     |       | ,                                                      | 58             |

|     |       | , ,                                                    | 60             |

|     | 0.4   | 0 0 1 07                                               | 60             |

|     | 3.4   | ,                                                      | 60             |

|     | 3.5   |                                                        | 61<br>61       |

|     |       | , , ,                                                  | 61<br>64       |

|     |       |                                                        | 65             |

|     |       | 5.5.5 Tommation Elimitations and Design Considerations | J              |

<u>Contents</u> v

|    | 3.6<br>3.7                         | Discussion on Device Type Selection and Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 67<br>68                                                                               |

|----|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 4  | <b>Sen</b> 4.1 4.2 4.3 4.4 4.5 4.6 | Sensitivity Analysis Strategy: Reference Case and Basis of Evaluation  Design Sensitivity to Data Rate Variation  Design Sensitivity to Transmission Line Parameter Variation  4.3.1 Transmission Line Length Variation  4.3.2 Guard Line Spacing Variation  Design Sensitivity to $V_{th}$ Variation  Design Sensitivity to Jitter Variation  Design Sensitivity to Voltage Variation  4.6.1 Skewing of Pre-input Voltage  4.6.2 Skewing of Driver Power Supply  4.6.3 Equivalent Technology Scaling  Design Sensitivity to Process Variation  Design Sensitivity to Temperature Variation  Critical Corner Determination and Analysis | 72<br>72<br>72<br>77<br>77<br>79<br>79<br>80<br>81<br>81<br>83<br>85<br>86<br>87<br>88 |

| 5  |                                    | clusions and Future Directions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 89                                                                                     |

| Re | ferer                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 93                                                                                     |

| Α  | Opti<br>ogy                        | imum Power Design of an 8 Gb/s NAND I/O Interconnect in 14 nm FinFET Technol-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 99                                                                                     |

# List of Figures

| 2.1   | An example of an I/O interconnect for differential (top) and single ended (bottom) signalling            | 4  |

|-------|----------------------------------------------------------------------------------------------------------|----|

| 2.2   | Schematic of CTT topology                                                                                | 5  |

| 2.3   | Slew rate non-uniformity at RX input voltage in single edge transition of CTT topology                   |    |

|       | with following simulation conditions: Imec low $V_{th}$ FinFET 14 nm tech. RMG, $V_{in}$ = $V_{dd}$      |    |

|       | = 1 V, $TL_{len}$ = 4 cm, line spacing = 135 um, corner:TT, temp = 25°C, DR = 8Gb/s, input               |    |

|       | jitter = 16%                                                                                             | 6  |

| 2.4   | Equivalent CTT circuit model in terms of resistances, when only NFET is operational                      | 8  |

| 2.5   | Schematic of Saturated FET Driver                                                                        | 9  |

| 2.6   | Schematic of Saturated FET Driver operation principle                                                    | 9  |

| 2.7   | Schematic of Saturated FET Driver with a current source at its tail                                      | 10 |

| 2.8   | Small signal model of SFD with tail current source                                                       | 10 |

| 2.9   | Example of HSTL topology                                                                                 | 11 |

| -     | Scalable Low Voltage Signalling Schematic                                                                | 13 |

|       | Low-Voltage Differential Signalling schematic                                                            | 14 |

|       |                                                                                                          | 15 |

|       | Current mode logic signalling schematic                                                                  | 13 |

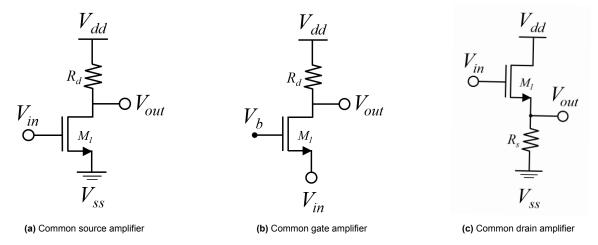

| 2.13  | Simple amplifier topologies configured in a) common source b) common gate c) common                      | 47 |

| 0 4 4 | drain                                                                                                    | 17 |

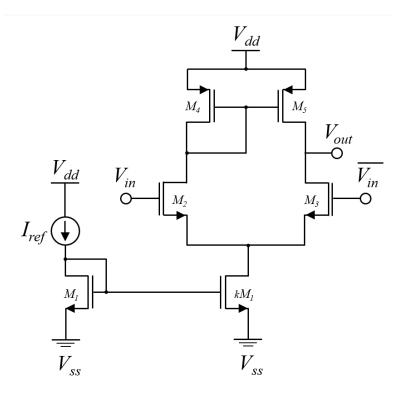

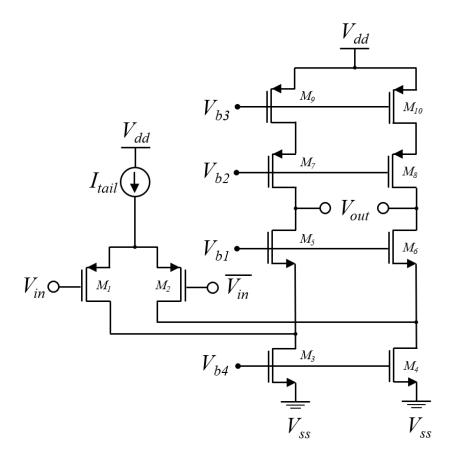

|       | Five transistor OTA with NFET differential pair and PFET loading                                         | 19 |

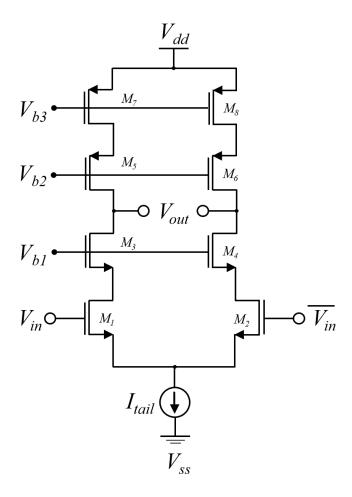

|       | Two level telescopic amplifier                                                                           | 20 |

|       | Two level folded cascode amplifier with PFET differential pair                                           | 21 |

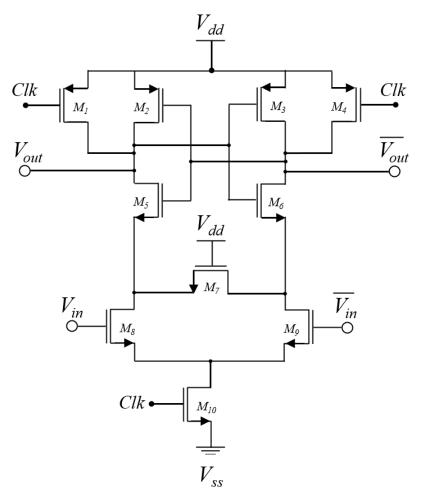

|       | Conventional sense amplifier topology                                                                    | 22 |

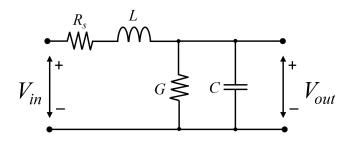

|       | Distributed transmission line model                                                                      | 24 |

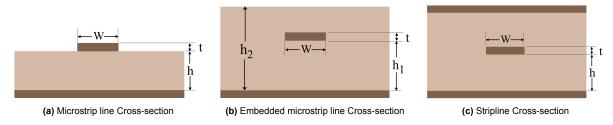

|       | PCB trace type known as a) microstrip b) embedded microstrip c) stripline [46]                           | 25 |

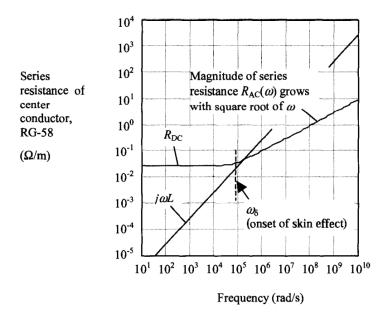

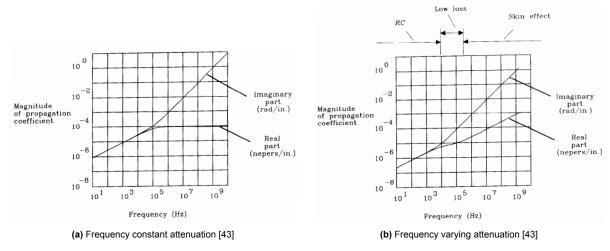

|       | Resistance variation with frequency [44]                                                                 | 27 |

| 2.21  | Attenuation constant and wave number accounting for resistance with a) no skin effect                    |    |

|       | b) skin effect [43]                                                                                      | 27 |

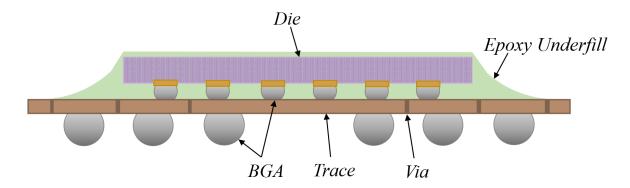

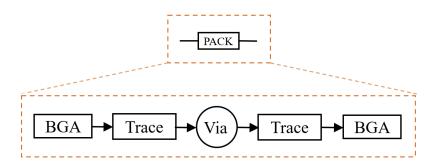

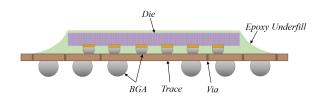

|       | Flip-chip packaging model                                                                                | 30 |

| 2.23  | Simplified flip-chip package                                                                             | 30 |

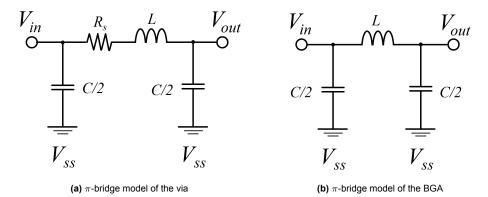

| 2.24  | Lumped element model of a $\pi$ -bridge for a) via b) BGA                                                | 31 |

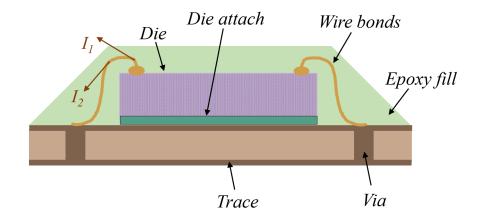

| 2.25  | Chip-on-board package cross-section view                                                                 | 33 |

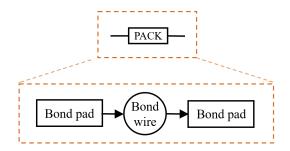

| 2.26  | Simplified chip-on-board package                                                                         | 33 |

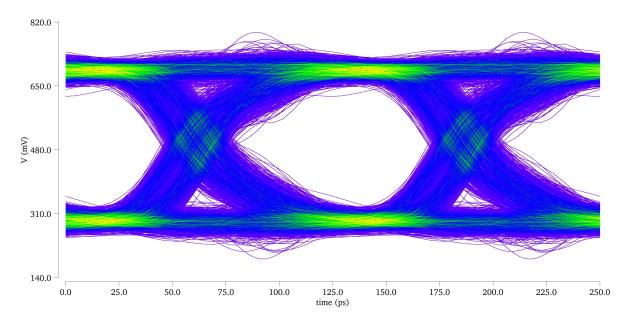

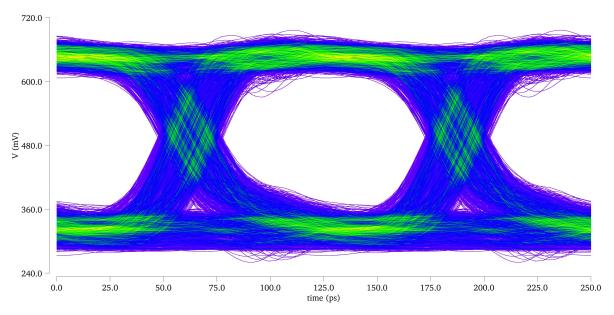

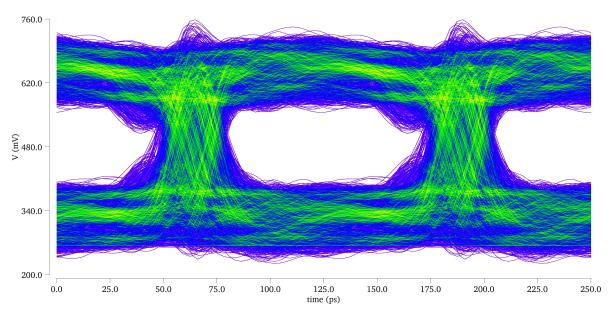

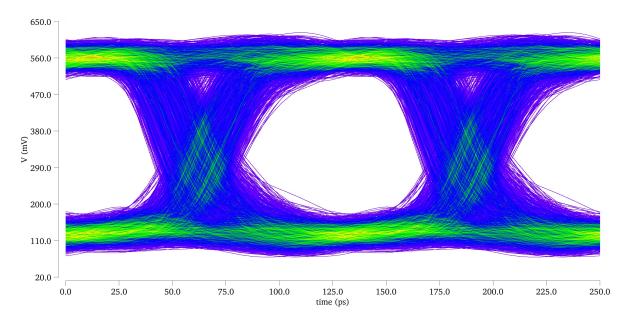

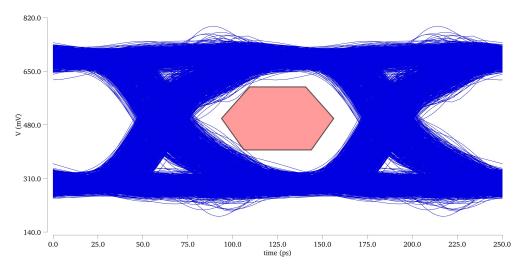

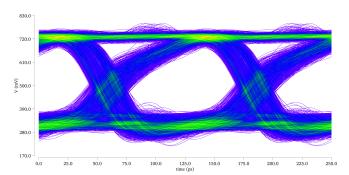

| 2.27  | Example of transient signal eye when termination is located outside of the chip. Simu-                   |    |

|       | lation conditions (refer to Section 4.1): CTT topology, Imec low $V_{th}$ FinFET 14 nm tech.             |    |

|       | RMG, $V_{in}$ = $V_{dd}$ = 1 V, $TL_{len}$ = 4 cm, line spacing = 135 um, corner:TT, temp = 25°C,        |    |

|       | DR = 8Gb/s, input jitter = 16%                                                                           | 35 |

| 2.28  | Example of transient signal eye when termination is located on-chip. Simulation condi-                   |    |

|       | tions (refer to Section 4.1): CTT topology, Imec low $V_{th}$ FinFET 14 nm tech. RMG, $V_{in}$           |    |

|       | = $V_{dd}$ = 1 V, $TL_{len}$ = 4 cm, line spacing = 135 um, corner:TT, temp = 25°C, DR = 8Gb/s,          |    |

|       | input jitter = 16%                                                                                       | 35 |

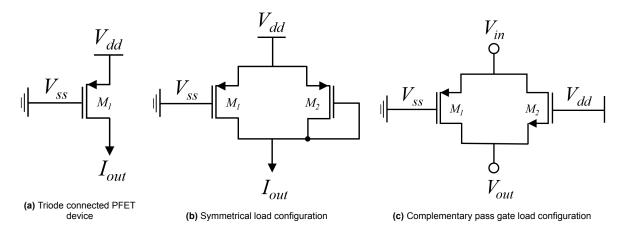

| 2.29  | Active load device in a) triode configuration b) symmetric configuration c) complementary                |    |

|       | pass gate configuration                                                                                  | 36 |

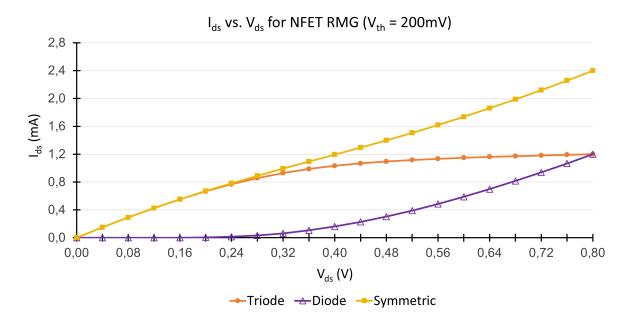

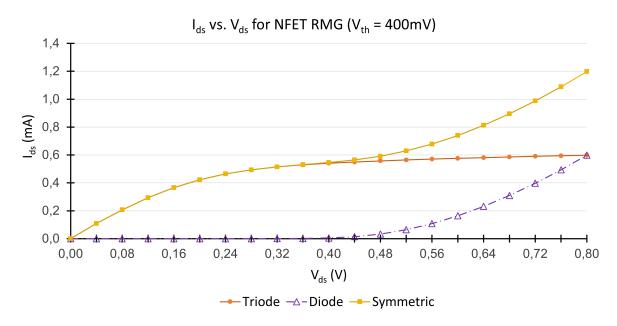

| 2.30  | $Ids$ vs. $V_{ds}$ characteristic for symmetric load configuration. Simulations performed with           |    |

|       | Imec FinFET 14 nm tech. RMG and $V_{th}$ value of 400 mV                                                 | 37 |

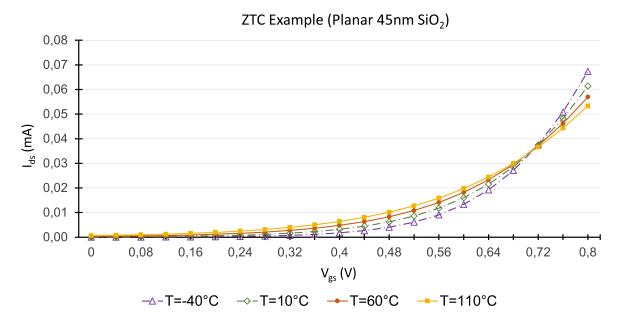

| 2 31  | $I_D$ vs. applied gate voltage for various system temperatures generating a ZTC. Simula-                 | •  |

|       | tions performed for isolated planar NFET using Imec planar Silicon gate oxide technology                 | 42 |

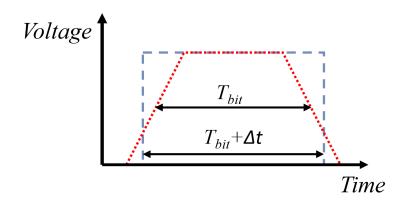

| 2 32  | Bit width changes due to immensely high gain stage                                                       | 43 |

| 2.02  | bit width changes due to infinionolly high gain stage                                                    | 70 |

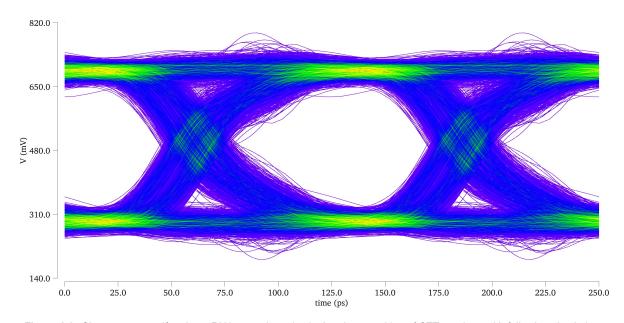

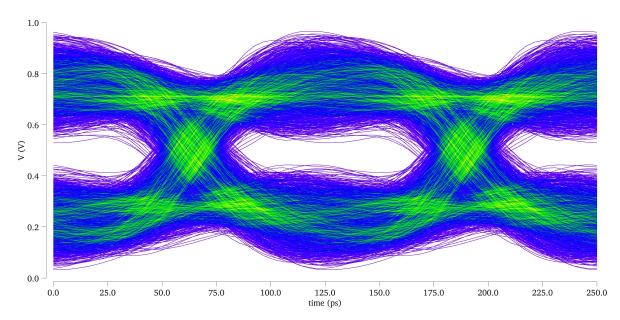

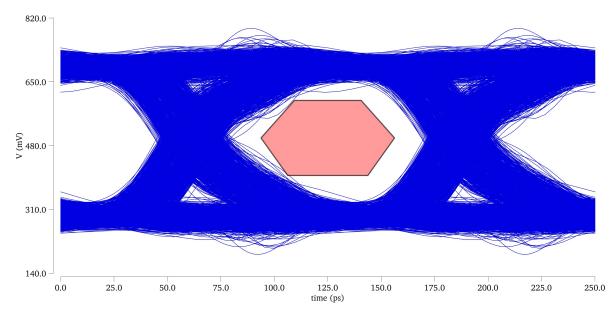

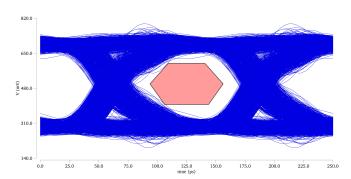

| 3.1   | An eye diagram including compatibility eye mask for CTT topology with following simula-                  |    |

|       | tion conditions: Imec low $V_{th}$ FinFET 14 nm tech. RMG, $V_{in}$ = $V_{dd}$ = 1 V, $TL_{len}$ = 4 cm, |    |

|       | line spacing = 135 um, corner:TT, temp = 25°C, DR = 8Gb/s, input jitter = 16%                            | 45 |

| 3.2   | Jitter effect on an ideal square wave signal                                                             | 47 |

| 3.3   | Varying slew rate implementation using VerilogA                                                          | 47 |

| 3.4   | Difference in signal eye at inverter output with (red) and without (yellow) jitter                       | 48 |

| 3.5   | The quasi-ideal signal at the output of the inverter chain                                               | 48 |

| 3.6   | Quasi-ideal signal with the addition of noise                                                            | 49 |

|       |                                                                                                          |    |

List of Figures vii

| 3.7<br>3.8<br>3.9 | Non-ideal voltage source simplified schematic                                                                                                                                                                                                                                                 | 51<br>53 |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.10              | 135 um, corner:TT, temp = 25°C, DR = 8Gb/s, input jitter = 16% SLVS RX input eye for non-matched termination of 135 $\Omega$ . Simulation conditions used: Imec low $V_{th}$ FinFET 14 nm tech. RMG, $V_{in}$ = $V_{dd}$ = 1 V, $TL_{len}$ = 4 cm, line spacing =                             | 59       |

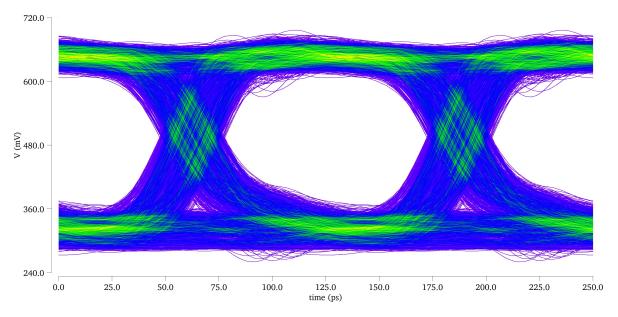

| 3.11              | 135 um, corner:TT, temp = 25°C, DR = 8Gb/s, input jitter = 16% Signal eye of RX input for CTT topology when TL is of microstrip configuration. Simulation conditions used: Imec low $V_{th}$ FinFET 14 nm tech. RMG, $V_{in} = V_{dd} = 1$ V, $TL_{len} = 1$                                  | 59       |

| 3.12              | 4 cm, line spacing = 135 um, corner:TT, temp = 25°C, DR = 8Gb/s, input jitter = 16% Signal eye of RX input for CTT topology when TL is of stripline configuration. Simulation conditions used: Imec low $V_{th}$ FinFET 14 nm tech. RMG, $V_{in}$ = $V_{dd}$ = 1 V, $TL_{len}$ = 4 cm,        | 63       |

| 3.13              | line spacing = 135 um, corner:TT, temp = 25°C, DR = 8Gb/s, input jitter = 16%, Example of transient signal eye when termination is located outside of chip. Simulation conditions (refer to Section 4.1): SLVS topology, Imec low $V_{th}$ FinFET 14 nm tech. RMG,                            | 63       |

| 3.14              | $V_{in}$ = $V_{dd}$ = 1 V, $TL_{len}$ = 4 cm, line spacing = 135 um, corner:TT, temp = 25°C, DR = 8Gb/s, input jitter = 16%                                                                                                                                                                   | 65       |

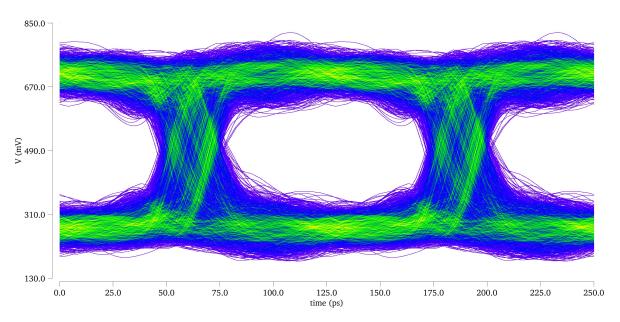

| 3 15              | = $V_{dd}$ = 1 V, $TL_{len}$ = 4 cm, line spacing = 135 um, corner:TT, temp = 25°C, DR = 8Gb/s, input jitter = 16%                                                                                                                                                                            | 66<br>66 |

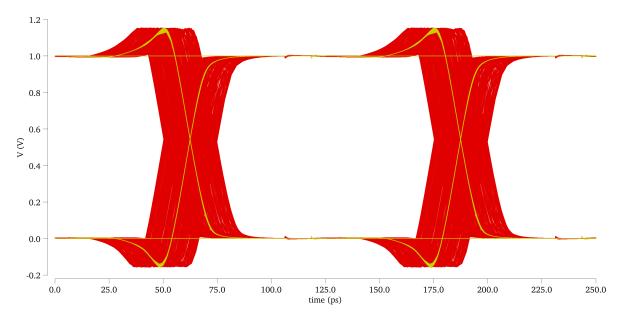

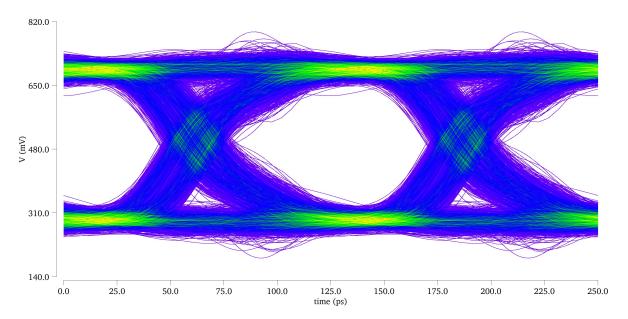

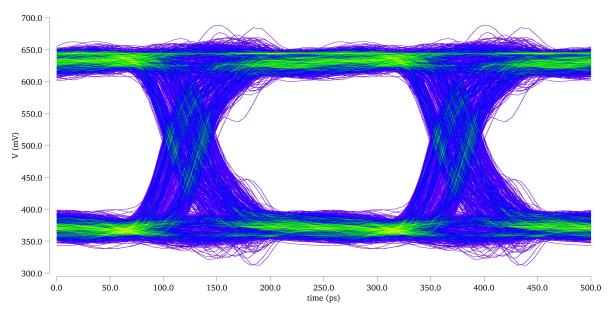

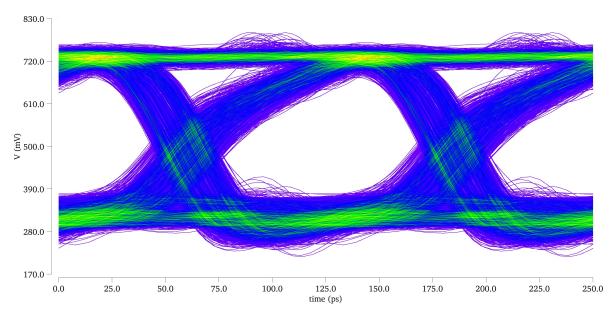

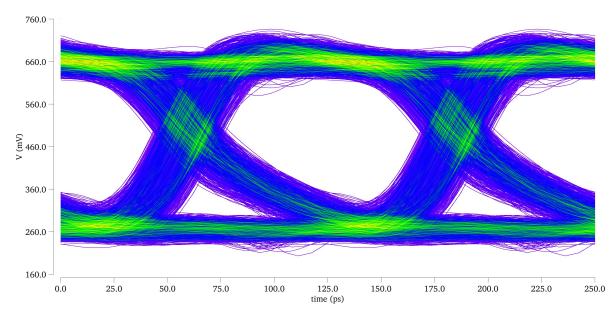

| 3.16              | Total current of symmetric TERM for lines in-house 14nm FinFET technology, $V_{th}$ = 400 mV CTT example of signal eye at driver output. Simulation conditions (refer to Section 4.1): Imec low $V_{th}$ FinFET 14 nm tech. RMG, $V_{in}$ = $V_{dd}$ = 1 V, $TL_{len}$ = 4 cm, line spacing = |          |

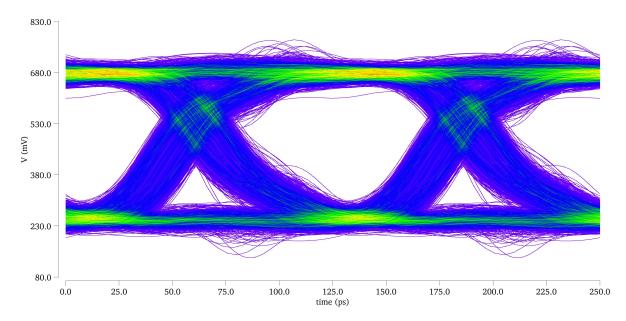

| 3.18              | 135 um, corner:TT, temp = 25°C, DR = 8Gb/s, input jitter = 16% SLVS example of signal eye at driver output. Simulation conditions (refer to Section 4.1):                                                                                                                                     | 70       |

|                   | Imec low $V_{th}$ FinFET 14 nm tech. RMG, $V_{in}$ = $V_{dd}$ =1 V, $TL_{len}$ = 4 cm, line spacing = 135 um, corner:TT, temp = 25°C, DR = 8Gb/s, input jitter = 16%                                                                                                                          | 70       |

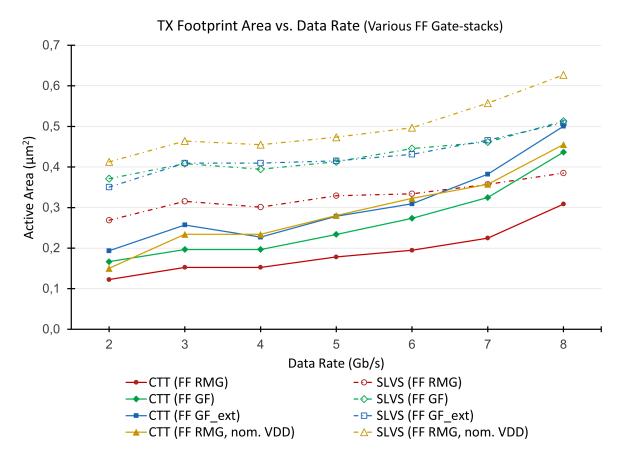

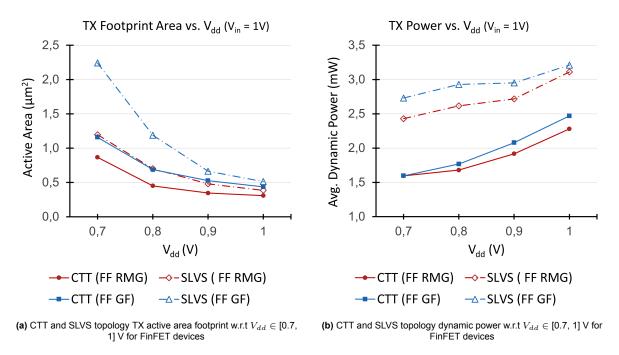

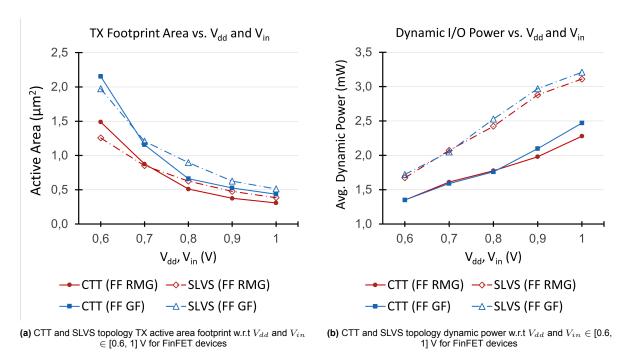

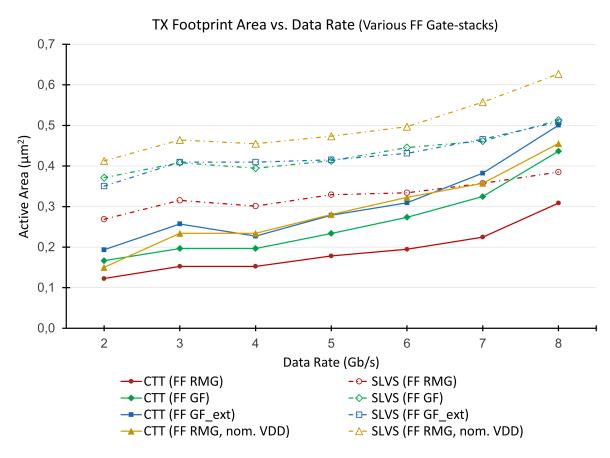

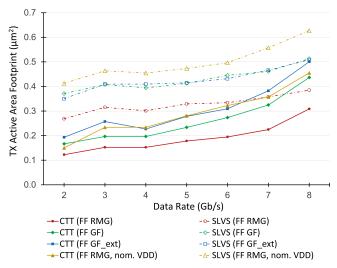

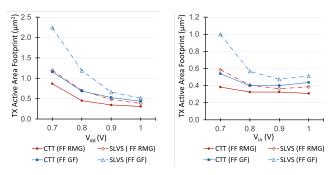

|                   | CTT and SLVS topology TX active area footprint w.r.t DR $\in$ [2, 8] Gb/s for various FinFET devices                                                                                                                                                                                          | 73       |

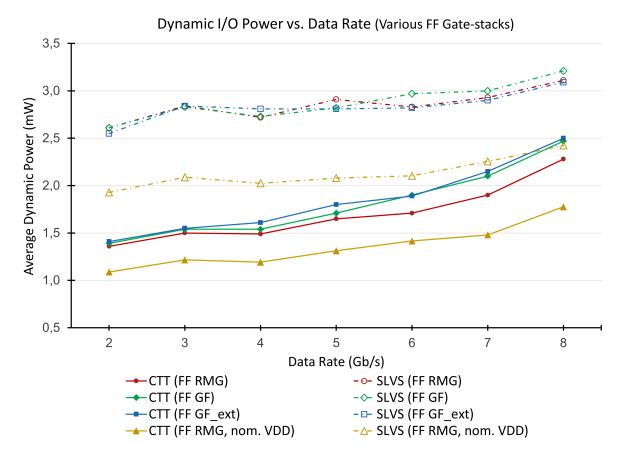

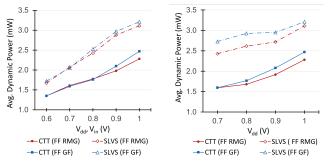

|                   | CTT and SLVS topology TX dynamic power w.r.t DR $\in$ [2, 8] Gb/s for various FinFET devices                                                                                                                                                                                                  | 74       |

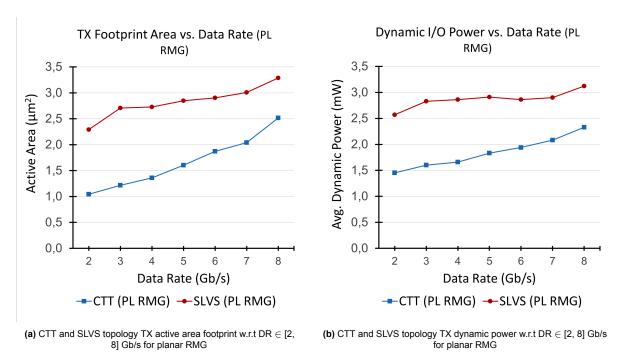

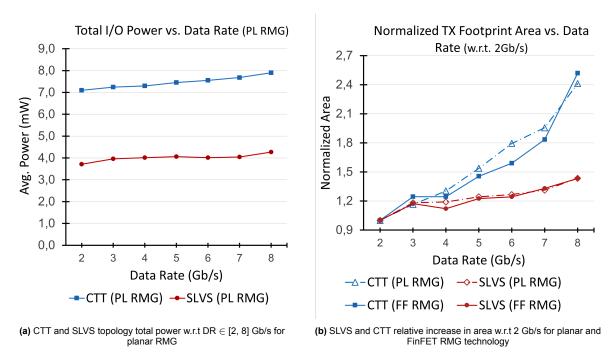

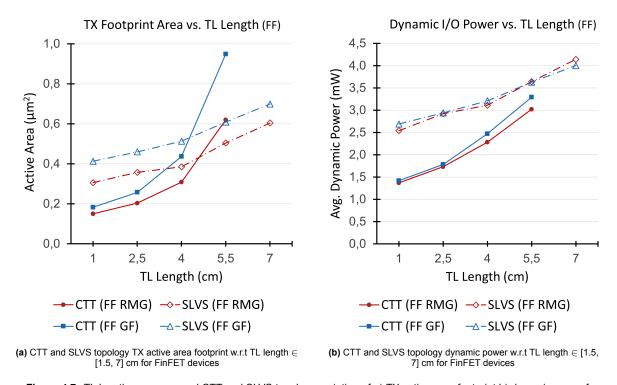

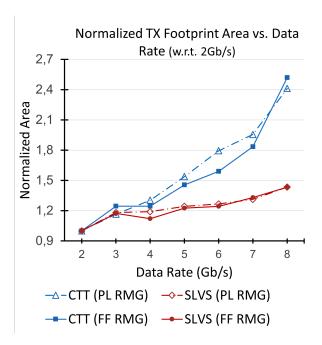

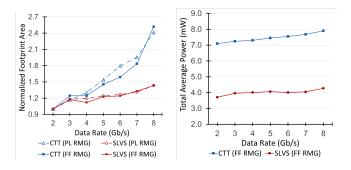

|                   | Graph indicating SLVS and CTT planar RMG configuration's a) TX active area footprint b) dynamic power for DR $\in$ [2, 8] Gb/s                                                                                                                                                                | 75       |

|                   | Graph indicating SLVS and CTT a) planar RMG configuration's total power b) relative area w.r.t 2 Gb/s for RMG devices                                                                                                                                                                         | 76       |

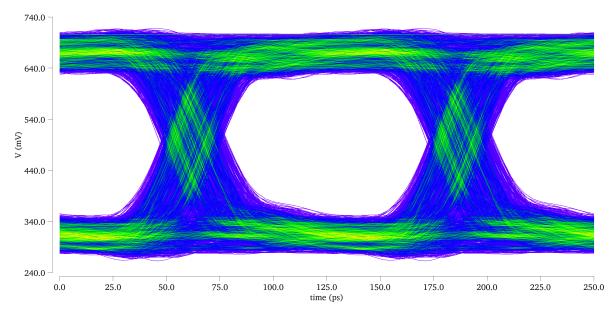

| 4.5               | CTT topology signal eye at RX input for 4 Gb/s, FinFET RMG. Simulation conditions (refer to Section 4.1): Imec low $V_{th}$ FinFET 14 nm tech. RMG, $V_{in}$ = $V_{dd}$ = 1 V, $TL_{len}$ = 4 cm, line spacing = 135 um, corner:TT, temp = 25°C, DR = 4Gb/s, input jitter = 16%               | 76       |

| 4.6               | CTT topology signal eye at RX input for 8 Gb/s, FinFET RMG. Simulation conditions (refer to Section 4.1): Imec low $V_{th}$ FinFET 14 nm tech. RMG, $V_{in} = V_{dd} = 1$ V, $TL_{len} = 1$                                                                                                   | 77       |

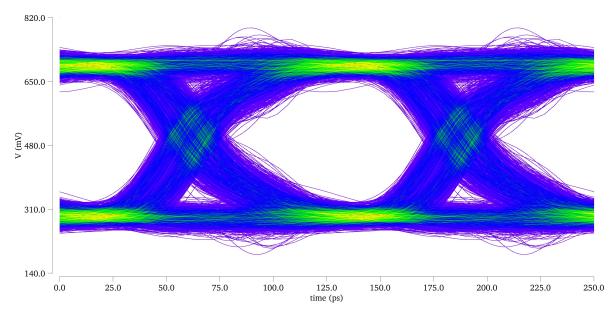

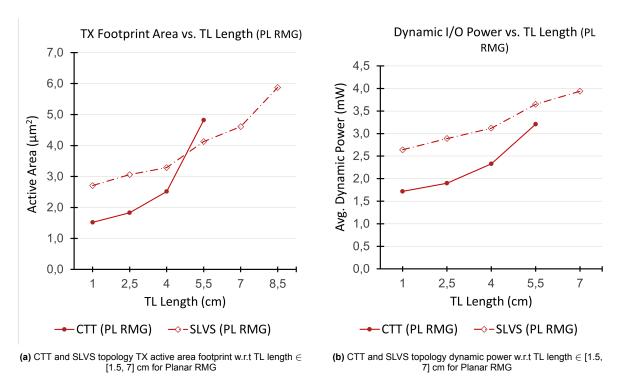

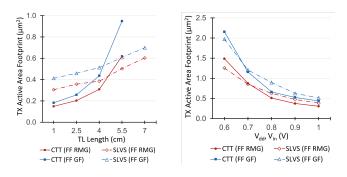

| 4.7               | 4 cm, line spacing = 135 um, corner:TT, temp = 25°C, DR = 8Gb/s, input jitter = 16% TL length sweep caused CTT and SLVS topology variation of a) TX active area footprint                                                                                                                     | 77       |

| 4.8               | b) dynamic power for FinFET devices                                                                                                                                                                                                                                                           | 78       |

| 4.9               | b) dynamic power for planar devices                                                                                                                                                                                                                                                           | 78       |

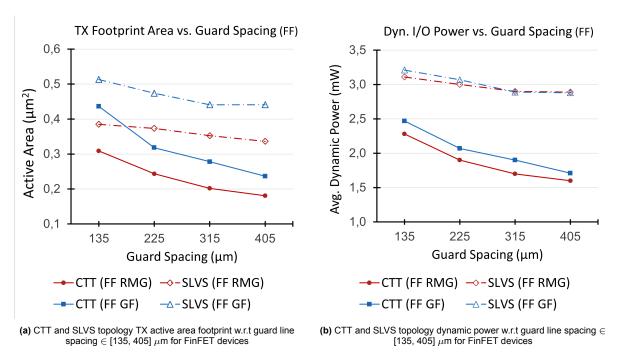

| 4.10              | area footprint b) dynamic power for FinFET devices                                                                                                                                                                                                                                            | 79       |

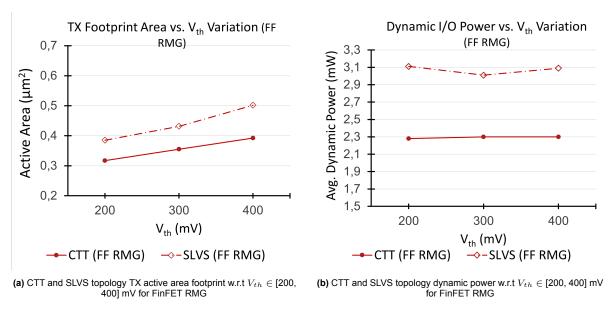

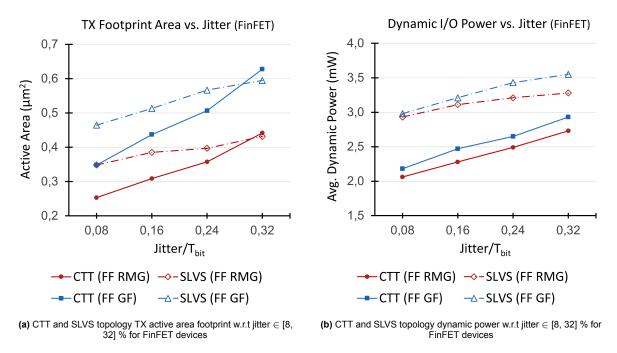

| 4.11              | dynamic power for FinFET RMG                                                                                                                                                                                                                                                                  | 80<br>81 |

List of Figures viii

| 4.12       | SLVS example of signal eye skewness for reduced $V_{in}$ . Simulation conditions (refer to             |    |

|------------|--------------------------------------------------------------------------------------------------------|----|

|            | Section 4.1): Imec low $V_{th}$ FinFET 14 nm tech. RMG, $V_{in}$ = 0.7 V, $V_{dd}$ = 1 V, $TL_{len}$ = |    |

|            | 4 cm, line spacing = 135 um, corner:TT, temp = 25°C, DR = 8Gb/s, input jitter = 16%                    | 82 |

| 4.13       | CTT example of signal eye skewness for reduced $V_{in}$ . Simulation conditions (refer to              |    |

|            | Section 4.1): Imec low $V_{th}$ FinFET 14 nm tech. RMG, $V_{in}$ = 0.7 V, $V_{dd}$ = 1 V, $TL_{len}$ = |    |

|            | 4 cm, line spacing = 135 um, corner:TT, temp = 25°C, DR = 8Gb/s, input jitter = 16%                    | 82 |

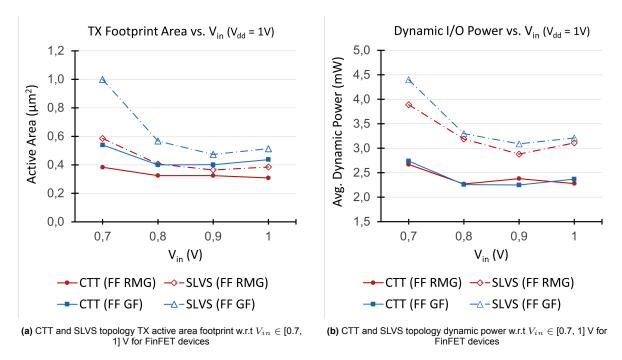

| 4.14       | $V_{in}$ fluctuation caused CTT and SLVS topology variation of a) TX active area footprint b)          |    |

|            | dynamic power for FinFET devices                                                                       | 83 |

| 4.15       | SLVS example of signal eye skewness for reduced $V_{dd}$ . Simulation conditions (refer to             |    |

|            | Section 4.1): Imec low $V_{th}$ FinFET 14 nm tech. RMG, $V_{in}$ = 1 V, $V_{dd}$ = 0.7 V, $TL_{len}$ = |    |

|            | 4 cm, line spacing = 135 um, corner:TT, temp = 25°C, DR = 8Gb/s, input jitter = 16%                    | 84 |

| 4.16       | CTT example of signal eye skewness for reduced $V_{dd}$ . Simulation conditions (refer to              |    |

|            | Section 4.1): Imec low $V_{th}$ FinFET 14 nm tech. RMG, $V_{in}$ = 1 V, $V_{dd}$ = 0.7 V, $TL_{len}$ = |    |

|            | 4 cm, line spacing = 135 um, corner:TT, temp = 25°C, DR = 8Gb/s, input jitter = 16%                    | 84 |

| 4.17       | $V_{dd}$ fluctuation caused CTT and SLVS topology variation of a) TX active area footprint b)          |    |

|            | dynamic power for FinFET devices                                                                       | 85 |

| 4.18       | $V_{dd}$ fluctuation caused CTT and SLVS topology variation of a) TX active area footprint b)          |    |

|            | dynamic power for FinFET devices                                                                       | 86 |

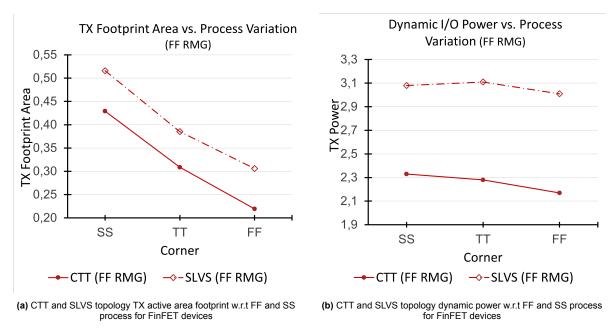

| 4.19       | Process variation caused CTT and SLVS topology variation of a) TX active area footprint                |    |

|            | b) dynamic power for FinFET devices                                                                    | 86 |

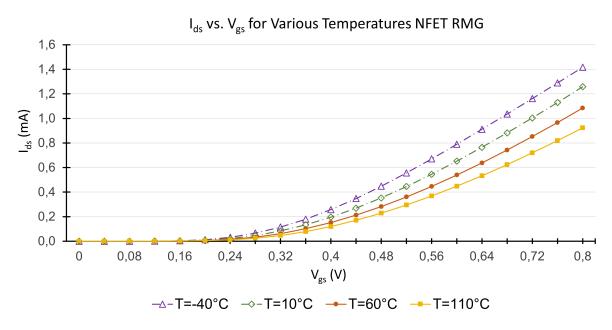

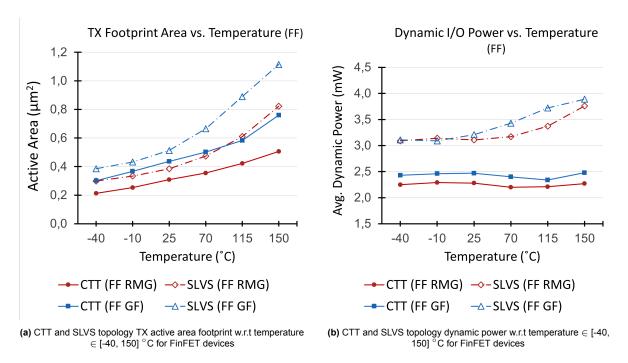

| 4.20       | Imec 14 nm NFET drain current vs. applied gate voltage for various system temperatures                 | 87 |

| 4.21       | Temperature variation caused CTT and SLVS topology variation of a) TX active area                      |    |

|            | footprint b) dynamic power for FinFET devices                                                          | 88 |

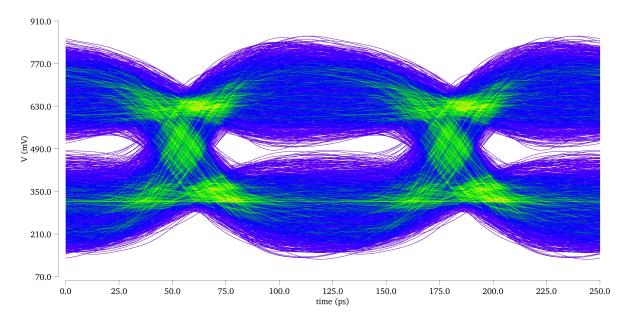

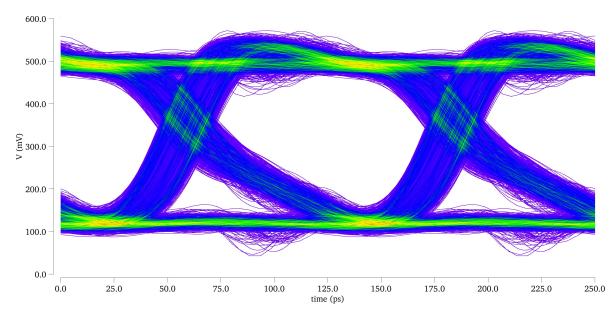

| 4.22       | Signal eye of RX input for SLVS for 150°C temperature. Simulation conditions used:                     |    |

|            | Imec low $V_{th}$ FinFET 14 nm tech. RMG, $V_{in}$ = $V_{dd}$ = 1 V, $TL_{len}$ = 4 cm, line spacing = |    |

|            | 135 um, corner:TT, temp = 150°C, DR = 8Gb/s, input jitter = 16%                                        | 88 |

| E 1        | Depiction of a) CTT b) SLVS signalling topology used in simulations                                    | 89 |

| 5.1<br>5.2 | An eye diagram including compatibility eye mask for CTT topology with following simula-                | 09 |

| 5.2        | tion conditions: Imec low $V_{th}$ FinFET 14 nm tech. RMG, $V_{in} = V_{dd} = 1$ V, $TL_{len} = 4$ cm, |    |

|            | line spacing = 135 um, corner:TT, temp = 25°C, DR = 8Gb/s, input jitter = 16%                          | 89 |

| 5.3        | CTT and SLVS topology TX active area footprint w.r.t DR $\in$ [2, 8] Gb/s for various FinFET           | 03 |

| 0.0        | devices                                                                                                | 91 |

| 5.4        | SLVS and CTT relative increase in area w.r.t 2 Gb/s for planar and FinFET RMG technology               | -  |

| J.¬        | CET G and CTT Total To more doc in a real will E CET of the plantar and thin ET TWO technology         | ے  |

# Nomenclature

### Abbreviations

| Abbreviation | Definition                              |

|--------------|-----------------------------------------|

| AC           | Alternating Current                     |

| BER          | Bit Error Rate                          |

| BGA          | Ball Grid Array                         |

| BJT          | Bipolar Junction Transistor             |

| BW           | Bandwidth                               |

| CD           | Common Drain                            |

| CEM          | Compatibility Eye Mask                  |

| CG           | Common Gate                             |

| CM           | Current Mode                            |

| CML          | Current Mode Logic                      |

| CMs          | Current Mirrors                         |

| CMRR         | Common Mode Rejection Ratio             |

| CMOS         | Complementary Metal-oxide Semiconductor |

| CoB          | Chip-on-board                           |

| CS           | Common Source                           |

| CTT          | Centre Tapped Termination               |

| CuA          | CMOS under Array                        |

| DC           | Direct Current                          |

| DCS          | Differential Current Steering           |

| DDR          | Double Data Rate                        |

| DP           | Differential Pair                       |

| DR           | Data Rate                               |

| DS           | Differential Signaling                  |

| ECL          | Emitter-coupled Logic                   |

| EM           | Elect-magnetic                          |

| EMI          | Electro-magnetic interference           |

| EMS          | Embedded Microstrip                     |

| EOT          | Equivalent Oxide Thickness              |

| ESD          | Electrostatic Discharge                 |

| FC           | Flip Chip                               |

| FEM          | Finite Element Method                   |

| FET          | Field-effect Transistor                 |

| FF           | Fast-fast                               |

| GBWP         | Gain Bandwidth Product                  |

| GF           | Gate First                              |

| GND          | Ground                                  |

| HDD          | Hard Disk Drive                         |

| HK/MG        | High $\kappa$ Metal Gate                |

| HSTL         | High Speed Transceiver Logic            |

| IC           | Integrated Circuit                      |

| ISI          | Inter-symbol Interference               |

| I/O          | Input/Output                            |

| LTT          | Lower Tapped Termination                |

| LVDS         | Low-voltage Differential Signaling      |

| MS           | Microstrip                              |

| NGS          | Near Ground Signaling                   |

| ODT          | On-die Termination                      |

| ONFI         | Open NAND Flash Interface               |

| OTA          | Operational Transconductance Amplifier  |

| PACK         | Package                                 |

| PCB          | Printed Circuit Board                   |

| . 00         | Triffica Official Double                |

List of Figures x

| Abbreviation | Definition                     |

|--------------|--------------------------------|

| PDS          | Pseudo-differential Signaling  |

| PDN          | Pull-down Network              |

| PODL         | Pseudo-open Drain Logic        |

| PSRR         | Power Supply Rejection Ratio   |

| PU           | Processing Unit                |

| PUN          | Pull-up Network                |

| PVT          | Process, Voltage, Temperature  |

| QFN          | Quad Flat No-lead              |

| QFP          | Quad Flat Package              |

| RC           | Resistance-capacitance         |

| RMG          | Replacement Metal Gate         |

| RX           | Receiver                       |

| SA           | Sensitivity Analysis           |

| SFD          | Saturated FET Driver           |

| SES          | Single Ended Signaling         |

| SL           | Stripline                      |

| SLVS         | Scalable low-voltage Signaling |

| SNR          | Signal-to-noise Ratio          |

| SOI          | Silicon on Insulator           |

| SS           | Slow-slow                      |

| SSD          | Solid State Drive              |

| TERM         | Termination                    |

| TL           | Transmission Line              |

| TSV          | Through-silicon Via            |

| TT           | Typical-typical                |

| TX           | Transmitter                    |

| UI           | Unit Interval                  |

| VM           | Voltage Mode                   |

| ZTC          | Zero Temperature Coefficient   |

## Symbols

| Symbol         | Definition                                  | Unit              |

|----------------|---------------------------------------------|-------------------|

| $\overline{A}$ | Area                                        | [m <sup>2</sup> ] |

| C              | Capacitance                                 | [F]               |

| $C_{ds}$       | Drain-to-source Capacitance of Transistor   | [F]               |

| $C_{gd}$       | Gate-to-drain Capacitance of Transistor     | [F]               |

| $C_{gs}$       | Gate-to-source Capacitance of Transistor    | [F]               |

| $C_{in}$       | Input Capacitance                           | [F]               |

| $C_L$          | Load Capacitance                            | [F]               |

| $C_{mut}$      | Mutual Capacitance                          | [F]               |

| $C_{out}$      | Output Capacitance                          | [F]               |

| $C_{ox}$       | Transistor Gate Oxide Capacitance           | $[F\;m^{-1}]$     |

| $C_{vb}$       | Via Body Capacitance                        | [F]               |

| $C_{vp}$       | Via Pad Capacitance                         | [F]               |

| c              | Speed of Light in Vacuum                    | $[ms^{-1}]$       |

| d              | Separation Between Two Adjacent Wires/Lines | [m]               |

| f              | Signal Frequency                            | [Hz]              |

| G              | Conductance                                 | [S]               |

| $g_m$          | Transistor Transconductance                 | [S]               |

| h              | Dielectric Height of PCB                    | [m]               |

| $h_{via}$      | Via Height                                  | [m]               |

| I              | Current                                     | [A]               |

List of Figures xi

| Symbol                   | Definition                                         | Unit       |

|--------------------------|----------------------------------------------------|------------|

| $\overline{I_D}$         | Drain Current                                      | [A]        |

| $I_{OL}$                 | Current Flow Through Pull-down Transistor          | [V]        |

| $I_{sink}$               | Current Sunk by SFD                                | [A]        |

| $J_0$                    | Bessel's Function of First Kind of Order Zero      | [-]        |

| $k_a$                    | Correction Factor for Return Path Resistance       | [-]        |

| $k_p$                    | Correction Factor for Proximity Effect             | [-]        |

| $k_r$                    | Correction Factor for Copper Roughness             | [-]        |

| $\stackrel{\kappa_r}{L}$ | Transistor Length                                  | [m]        |

| $\stackrel{L}{L}$        | Inductance                                         | [H]        |

| $L_{mut}$                | Mutual Inductance                                  | [H]        |

|                          | Self Inductance of a Component                     | [H]        |

| $L_{slef}$               | Bondwire Length                                    | [m]        |

| $l_b w$                  | Distance Signal has Propagated during Rise/Fall    |            |

| $l_{prop}$               | Time                                               | [s]        |

| 1                        | Transmission Line Distributed Instance Length      | [m]        |

| $l_{TL}$                 |                                                    | [m]        |

| m                        | Number of Capa Returner Signal and Cuard Lines     | [-]        |

| m                        | Number of Javanter Chain Stores                    | [-]        |

| N                        | Number of Inverter Chain Stages                    | [-]        |

| $N_0$                    | Neumann's Function of Order Zero or Bessel's Func- |            |

|                          | tion of Second Kind of First Order.                | r 1        |

| n                        | Number of Signal and Guard Lines                   | [-]        |

| $P_{dynamic}$            | Dynamic Power Consumption                          | [W]        |

| $P_{static}$             | Static Power Dissipation                           | [W]        |

| $P_{tot}$                | Total Power Consumption                            | [W]        |

| p                        | Perimeter of Cross-section                         | [m]        |

| Q                        | Charge                                             | [C]        |

| R                        | Resistance                                         | $[\Omega]$ |

| $R_{AC}$                 | Alternating Current Resistance                     | $[\Omega]$ |

| $R_{avg}$                | Average Surface Roughness                          | [ $\mu$ m] |

| $R_{bot}$                | Bottom Termination Resistance                      | $[\Omega]$ |

| $R_d$                    | Drain Termination Resistance                       | $[\Omega]$ |

| $R_{DC}$                 | Direct Current Resistance                          | $[\Omega]$ |

| $R_{PD}$                 | Pull-down Resistance                               | $[\Omega]$ |

| $R_{top}$                | Top Termination Resistance                         | $[\Omega]$ |

| $r_{ap}$                 | Via Anti-pad Radius                                | [m]        |

| $R_p$                    | Via Pad Radius                                     | [m]        |

| $r_{bw}$                 | Bondwire Radius                                    | [m]        |

| $r_o$                    | Transistor Output Resistance                       | $[\Omega]$ |

| $r_{via}$                | Via Radius                                         | [m]        |

| $T_{bit}$                | Bit Width                                          | [s]        |

| t                        | Time                                               | [s]        |

| t                        | Trace/Copper Layer Thickness                       | [m]        |

| $t_r$                    | Rise Time                                          | [s]        |

| $V_{cm}$                 | Common Mode Voltage                                | [V]        |

| $V_{dd}$                 | Power Supply Voltage                               | [V]        |

| $V_{ds}$                 | Drain-to-source Voltage of Transistor              | [V]        |

| $V_g$                    | Transistor's Gate Voltage                          | [V]        |

| $V_{gs}^{g}$             | Gate-to-source Voltage of Transistor               | [V]        |

| $V_{in}^{gs}$            | Input Voltage                                      | [V]        |

| $V_{OH}$                 | Threshold Voltage of High State                    | [V]        |

| $V_{OL}$                 | Threshold Voltage of Low State                     | [V]        |

| $V_{out}$                | Output Voltage                                     | [V]        |

| $V_s$                    | Source Voltage                                     | [V]        |

| $V_{th}$                 | Transistor's Threshold Voltage                     | [V]        |

| 010                      | <b>J</b> -                                         |            |

List of Figures xii

| Symbol               | Definition                                      | Unit              |

|----------------------|-------------------------------------------------|-------------------|

| $\overline{V_{Z_0}}$ | Voltage drop across termination resistance      | [V]               |

| $V_{+}$              | Voltage of RX Positive Terminal                 | [V]               |

| v                    | Propagation Velocity of Signal                  | $[ms^{-1}]$       |

| W                    | Transistor Width                                | [m]               |

| W                    | Trace Width                                     | [m]               |

| $Z_0$                | TL Characteristic Impedance                     | $[\Omega]$        |

| $\alpha$             | Scaling Factor Between Two Consecutive Inverter | [-]               |

|                      | Chain Stages                                    |                   |

| $\Delta$             | Variation/Deviation                             | [-]               |

| $\delta$             | Skin Depth                                      | [m]               |

| $	an \delta$         | Loss Tangent of Dielectric Material             | [-]               |

| $\epsilon_{eff}$     | Effective Dielectric Constant                   | [-]               |

| $\epsilon_r$         | Relative Dielectric Constant                    | [-]               |

| $\eta$               | Input-to-Output Capacitance ratio               | [-]               |

| $\kappa$             | dielectric constant                             | [-]               |

| $\lambda$            | Channel Length Modulation Parameter             | $[V^{-1}]$        |

| $\mu$                | Mobility of Majority Charge Carriers            | $[m^2V^{-1}s^-1]$ |

| $\mu$                | Material Permeability                           | $[Hm^{-1}]$       |

| $\mu_0$              | Permeability of Free Space                      | $[Hm^{-1}]$       |

| $\mu_r$              | Relative Permeability                           | $[Hm^{-1}]$       |

| ho                   | Resistivity                                     | $[\Omega m]$      |

| au                   | RC Constant                                     | [s]               |

| $\chi_{01}$          | First Root of Via Pad Determination Chain       | [-]               |

| $\omega$             | Angular Frequency                               | [rad $s^{-1}$ ]   |

## Introduction

This chapter introduces the subject covered in the thesis. The motivation to investigate the topic is discussed first and can be found in Section 1.1. Brief overview of the state-of-the-art NAND I/O performance can be found at the end of Section 1.1. The main thesis objective together with contributions can be found in Section 1.2.

#### 1.1. Motivation

Unrelenting thirst for higher capacity data storage with faster transfer capabilities has been ceaselessly driven by continuous generation of data in large quantities (Big Data [1]) that has to be processed and retained in the system [2]. With processing speeds developing rapidly and memory bandwidth (BW) lagging behind, data transfer bottleneck has grown immensely in conventional processor-centric architectures, causing designers to use multi-level cache memory to hide transmission latency [3]. Several solutions exist which can resolve the lack of data rate (DR) compatibility between memory and processor - one of the most straightforward fixes is increasing input/output (I/O) speed performance [4].

A promising candidate for Big Data applications is solid state drive (SSD) based on 3D NAND flash memory, as it provides high memory density ought to further increase [5] and relatively high I/O data rates in comparison to hard disk drives (HDD) [6]. With SSD niche being portable devices as smartphones and laptops, further improvement in NAND I/O speed opens possibilities for high performance, light-weight and small-size device manufacturing [7].

Conventional 3D NAND I/O logic is commonly located under memory die stacks (defined as complementary metal-oxide semiconductor (CMOS) under array (CuA)) making periphery area strongly size restricted [8]. Thereafter, using a lower technology node able to provide higher drive strength at iso-area conditions and meeting thermal stability requirement imposed by 3D NAND manufacturing technique, is a prominent solution to I/O BW limitation [4]. Area-demanding transistor devices have already been shown to be the culprit in I/O speed limitation [9].

Current state-of-the-art 3D NAND I/O achieves DR as high as 2.4 Gb/s for CuA configuration [10], while recently, staggering 3.2 Gb/s I/O transfer has been presented for memory-logic wafer-to-wafer bonded structure <sup>1 2</sup>. However, as I/O speed is expected to roughly double every 3 consequent years [11], investigation of next generation I/O for 3D NAND is crucial. With current trends leaning towards CuA system integration [12], one can guess that closest descendants of latest commercial products will employ alike topology. Thereby, it is particularly interesting to investigate CuA compatible high-performance, thermally stable devices with mature manufacturing flow.

#### 1.2. Contributions

With all the aforementioned in mind, this thesis aims to develop and analyse 8 Gb/s 3D NAND compatible I/O employing thermally stable Imec in-house developed Fin field-effect transistor (FinFET) 14 nm technology equivalent. Such configuration achieves  $\approx$ 3 times higher BW, implying that it corresponds to  $2^{nd}$  generation of current I/O standards. The main contributions of this thesis are:

- A journal submission on optimal performance NAND I/O platform for future generations: This thesis provides a design methodology and analysis for FinFET based NAND I/O able to reach 8 Gb/s. Industry defined signal quality requirements [13] were used to validate system throughput, ensuring that common signalling protocols are not violated. With this, a systematic approach to develop 8 Gb/s interconnect is developed, which can be repeated for any FET technology. The paper has been submitted to IEEE Journal of Solid-State Circuits (JSSC), see Appendix A.

- Benchmarking of FinFET based I/O against planar alternatives: In this thesis it was concluded that transmitter active area footprint can be reduced multiple times if switch from planar 45 nm tech. to 14 nm FinFET node is performed. Iso-performance conditions and shared power supply voltage were applied. Determination of exact area savings attained allows to evaluate whether shift towards using lower, more costly, technology pays-off.

- Exploration of high-speed I/O system sensitivities against environmental conditions and system parameters: In this thesis I/O analysis is broadened by exploring I/O design sensitivity to

<sup>&</sup>lt;sup>1</sup>URL https://www.anandtech.com/show/18799/kioxia-and-western-digital-debut-218layer-3d-nand-1tb-tlc-with-32-gts-io-speed[cited on 5th of May 2023]

<sup>&</sup>lt;sup>2</sup>URL https://www.tomshardware.com/news/kioxia-and-western-digital-unveil-worlds-fastest-3d-nand?utm\_medium=social&utm\_source=twitter.com&utm\_campaign=socialflow [cited on 5th of May 2023]

1.3. Thesis Outline 2

various parameters, such as DR, voltage, temperature and so forth. Sensitivity analysis provided indication of which system parameters require higher amounts of focus, to ensure proper operations in case environmental condition or system parameter variations are expected. Sensitivity is evaluated in terms of how much area has to be increased/relaxed to compensate performance degradation/enhancement to keep iso-performance conditions.

• Use of advanced FinFET technology in strictly area limited and temperature sensitive system: In this thesis CuA structured 3D NAND I/O was explored, inferring a low periphery size and thermal stability requirements. It is worth noting that equivalent technology was used. Equivalent technology implies that characteristics of NAND thermal annealing compatible logic devices would match those of current 14 nm FinFET Dynamic random access memory (DRAM) annealing process tolerant transistors, when manufacturing flow for required NAND devices would be established. At the moment, development of NAND thermally stable logic devices is under way, thereafter, best provided alternative is used in this project assuming that almost exactly the same characteristics will be obtained for the product yet to come.

#### 1.3. Thesis Outline

This thesis is structured in the following manner. Chapter 2 discusses state-of-the-art I/O topologies, covers sensitivity analysis scope, and defines theory related to transmission line, termination and packaging. In Chapter 3, design limitations, constraints and requirements are defined, choice of design topology made and target case simulations provided and discussed. Sensitivity analysis of various parameters is performed in Chapter 4, which is accompanied with discussion on observed outcomes. The thesis is concluded in Chapter 5, which is supplemented with recommendations for future research.

# 2. 3D NAND I/O Interface and Topology Overview

This chapter discusses theory related with I/O system and provides both qualitative and quantitative analysis of I/O underlying components. In Section 2.1 various 3D NAND system specifics are covered. Section 2.2 provides an overview of commonly used I/O topologies, including both benefits and drawbacks. Options for receiver amplifier are given in Section 2.3. Theoretical analysis of the transmission line can be found in Section 2.4, while high-speed applicable packaging characteristics are given in Section 2.5. Further, discussion on termination is provided in Section 2.6. Lastly, the setup of sensitivity analysis is provided in Section 2.7.

#### 2.1. 3D NAND I/O General Considerations

Conventional memory to processing unit (PU) interconnect architecture consists of three main components - memory, PU (including memory controller) and external link in combination with its supporting data transfer enabling logic. The key elements of the logic are the driver and receiver located at I/O pins, which characterise *Data* signal strength and quality upon transmission and reception. Other supporting signals as *Data Strobe*, *Address Line Enable*, *Chip Enable*, etc. are required to ensure that data is properly sampled, written/read in/from the right place in memory, and all of that is done at the right time [14]. Even though all the aforementioned signals have different electrical requirements [13], the same interconnection topology can be used for their transmission from one integrated circuit (IC) to the other.

Note, NAND I/O topology has a generic design, meaning that the design could be shared with other purpose I/O interconnects. Nevertheless, the key difference for state-of-the art NAND devices is the compatibility with technology node used. Commonly 3D NAND memory periphery (e.g. I/O logic) is produced on the same wafer as memory array, with the memory being located on top - the structure is more frequently referred to as CuA [8]. The former imposes several limitations on the logic circuitry - first, area available for periphery is restricted by chip size and required memory density [15]. Thereafter, further scaling of NAND chips to smaller sizes to satisfy industry's growing demand for miniaturization requires rapid scaling of periphery logic.

Second, CuA requires manufacturing of logic circuitry first - it has to withstand not only temperature annealing of itself, but also the memory. The former implies that the logic devices have to be thermally stable, since memory and logic subjection to temperature is different, with memory temperature being higher. Thereafter any conventional device technology cannot be directly transferred to stacked system applications. [16]

Temperature stability also allows to fix system BW and settling response to a constant value more accurately, as resistance-capacitance (RC) contributions of on-chip components are more process, voltage, temperature (PVT) resilient [15]. The bandwidth is further enhanced by stacked memory-logic placement, as trace length reduction is enabled relatively to 2D NAND memory, lowering overall interconnect trace resistivity [8].

Current CuA state-of-the-art NAND I/O employs planar technology, reaching 2 Gb/s I/O speed [17], however, as transmission speed is expected to follow Moore's law, it is inevitable that other more performing solutions will be required. It is crucial to investigate such means timely to determine how much device performance is going to be increased when advancing to a smaller technology node. Thereafter, the novelty of this thesis lies in investigating CuA NAND I/O attained area when FinFET devices are used and benchmarking this result with planar device size for iso-performance conditions. Two wafer bonded chips using through-silicon vias (TSV) is left as future research as it provides relaxed temperature and area requirements.

When considering CuA with regards to FinFET devices, thermally stable, and as mature as possible, technology manufacturing flow has to be selected. Bear in mind, FinFET devices have switched from using  $SiO_2$  as gate insulating material and doped poly-silicon gate conductor to thin high dielectric ( $\kappa$ ) metal gate structure (HK/MG), which tends to be more susceptible to degradation upon thermal anneal [18]. However, without HK/MG, further down-scaling of transistors and their oxide thickness would be impossible due to immense  $SiO_2$  device leakage current [19].

There are two HK/MG compatible manufacturing techniques: gate-first (GF) and gate last or replacement metal gate (RMG). As the name implies, in GF the HK/MG is implemented before full device

is formed, while in RMG first a dummy gate is made, which is removed after thermal annealing and later replaced with actual HK/MG. From the above, one can derive that GF structure is significantly more temperature resistant, as it has to survive its own annealing while RMG bypasses temperature processing associated challenges almost entirely. The former makes GF a more compatible technology with CuA type NAND memory, however, GF gate dielectric material choice is severely limited as device has to tolerate high temperature exposure. [20]

With all the above in mind, both RMG and GF can be viable options for 3D NAND I/O if manufacturing and device tolerance modifications are achieved. For the given moment, as technology development cannot be precisely predicted, design investigation is performed using current thermally stable Imec 14 nm FinFET technology equivalent with both RMG and GF stack-ups. In this chapter various state-of-the-art I/O interconnects suitable for 3D NAND memory I/O interface are covered, while discussion on devices is continued in Section 3.6.

#### 2.2. I/O Interconnect Topologies

Signal propagation in the system can happen over two different configurations - point-to-point or multipoint interface. In point-to-point interconnect, the signal is sent from one IC directly to the other, while in multipoint configuration, signal created by one IC can be simultaneously used by a multitude of other components. To simplify the analysis, only point-to-point interface is analysed further in this chapter, as multipoint topology can be generated using point-to-point elements as the most basic building blocks. Performance degradation due to reflections from idle component interface would be observed in multipoint configuration - investigation of this effect is left as recommendation for future research. Moreover, only a unidirectional interface is considered, assuming that bidirectional signalling mode would not cause significant system performance loss with well designed clocking network [21].

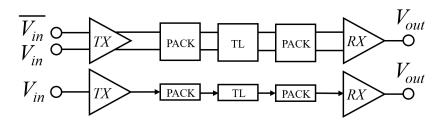

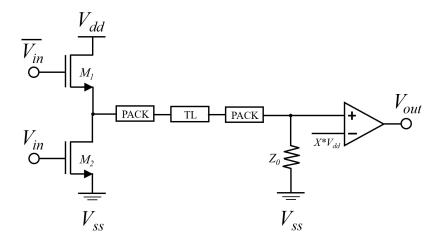

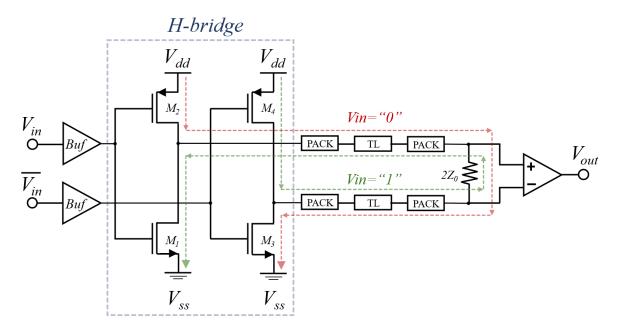

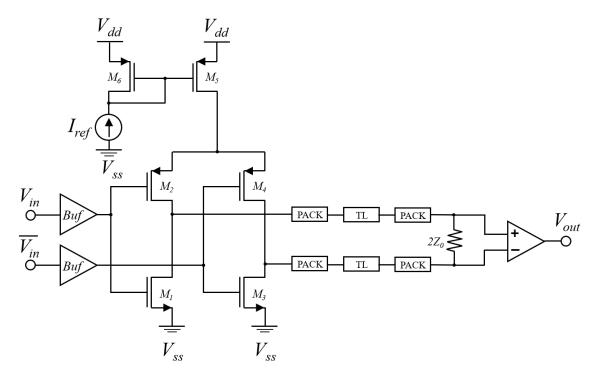

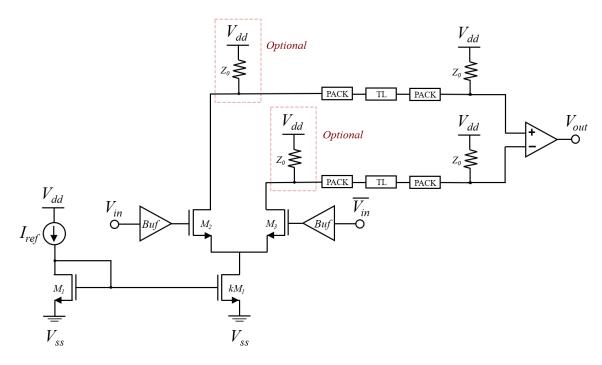

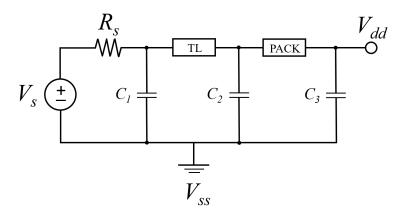

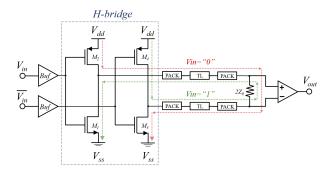

Conventional point-to-point signalling interface is composed of 4 main components: transmitter (TX), receiver (RX), termination (TERM) and transmission line (TL). Nevertheless, to make a clear distinction between TX and RX on-die and external components, packaging is introduced as an additional element. Note, the packaging of RX is assumed to be a mirrored version of TX package as now the signal is coming in the IC rather than going out of it. With this, an example of the overall point-to-point system for differential and single ended signalling look as depicted in Figure 2.1 (TERM is not depicted as it differs per choice of signalling topology, e.g series/parallel)

Figure 2.1: An example of an I/O interconnect for differential (top) and single ended (bottom) signalling

Electrical data transfer between two I/O pins can be split into two main classes - voltage mode (VM) and current mode (CM) signalling. The former scheme propagates information in the form of nodal voltages, while the latter performs the information processing via branch currents. The system's termination serves as the main indication of the class - VM signalling uses series or no termination, with signal propagation relying only on the charging and discharging of systems intrinsic capacitances. CM signalling on the other hand mostly uses parallel termination, with a possibility of combined seriesparallel termination, thus, directly utilizing the voltage rails to source/sink current. [22]

The structural differences of the signalling classes lead to a variation in circuit's attainable speed performance, with the current driven circuits being superior. The CM signalling outperforms voltage mode with its increased noise and power supply variation rejection, higher data transfer bandwidth and improved impedance matching. Nevertheless, the drawbacks of using a CM signalling is relatively high static power dissipation and increased area, if weak saturation current sources are used. [14]

Note, exploration of VM circuits is omitted in this thesis as the required data rate of 8 Gb/s for a single I/O pin renders VM signalling practically infeasible [22]. Thereafter, for complete theoretical coverage

only a mention of basic voltage mode circuit operation mechanism is deemed sufficient.

CM circuits can be further divided in single ended (SES) and differential signalling (DS) modes. Each of the data transfer modes can be realized with a variety of topologies providing different advantages. First, the SES topologies are discussed in Subsection 2.2.1, which is followed by Subsection 2.2.2 where DS topologies are covered. Observe, this chapter discusses sizing of the devices only qualitatively. Also, as the objective of the thesis stands as designing an I/O able to achieve continuous 8 Gb/s transmission speed, only the driver of the TX is going to be analysed. It is assumed that prior circuitry performs all the required actions to ready the signal for transmission. Thus, potential pre-circuitry components are neglected in this thesis, implying that full system integration is required to verify the findings obtained in this work. Note, only input drive strength limiting elements are included to ensure that TX is not under-designed.

#### 2.2.1. Single Ended Signalling Topologies

Single ended signalling is the current standard for communication between NAND memory and a PU due to its compact size and integration simplicity [13] [10]. Nonetheless, it has to be kept in mind, that state-of-the-art bonded NAND I/O interface can achieve up to 3.2 Gb/s transfer per line <sup>1 2</sup> utilizing planar technology, while CuA reaches only 2 Gb/s margin [17]. Hence design choices have to be critically reevaluated when investigating DR of up to 8 Gb/s due to more than doubling/quadrupling in frequency.

For instance, the crosstalk and reflection caused signal degradation becomes more severe with increase in signalling speed [23] and intrinsic device gain and thus also stage gain reduces with higher switching frequency. Reduced gain in combination with lowered power supply voltage of smaller device technology node (14 nm FinFET vs. Planar 45 nm) leads to more susceptibility to both amplitude and time noise, causing higher likelihood of signal errors to arise [24]. Nevertheless, it is assumed that SES topologies can reach the target speed, therefore they are considered as potential candidates for the 8 Gb/s interconnect.

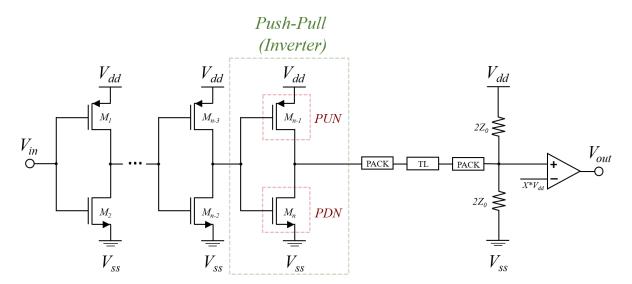

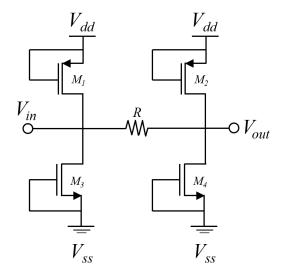

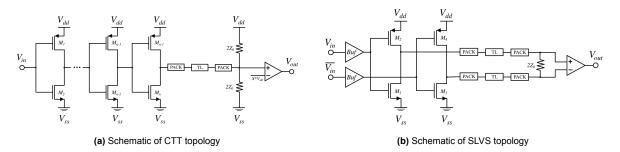

#### **Center-Tapped Termination**

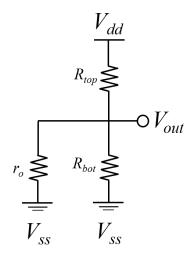

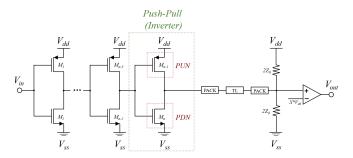

Center-tapped termination (CTT) is one of the most common transmission standards used in small chip applications, where area is crucial and can come with the sacrifice of power dissipation [22]. A schematic of CTT interconnect can be seen in Figure 2.2. The TX is composed of a push-pull circuitry, the TERM is in Thevenin configuration (parallel to both rails) and the RX is differential-to-single ended with the negative terminal being applied to the reference voltage. Since RX can be common for various topologies, it is not going to be covered in the individual subsections - a discussion on several receiver options can be found in Section 2.3. Note, the value X at negative RX terminal is the ratio between reference voltage (here, the common mode voltage ( $V_{cm}$ )) and power supply voltage ( $V_{dd}$ ).

Figure 2.2: Schematic of CTT topology

Commonly push-pull circuitry consists of a pull-up network (PUN) which is responsible for sourcing current from the power supply and pull-down network (PDN) which sinks the current into the ground <sup>3</sup>. For CTT, PUN is composed only by a single p-FET (PFET) and PDN by a single n-FET (NFET). Such configuration allows to interchangeably charge or discharge next stage depending on the input received, making the circuit fully transparent.

The push-pull circuitry of the driver can be designed in various ways - both using complementary and only single type (NFET or PFET) devices. The use of single type devices corresponds to high speed transceiver logic (HSTL) interface which is covered later in this section. Using a chain of inverters (complementary push-pull) as driver ensures that a full rail-to-rail swing is utilized, which allows to provide maximum drive strength to the output, meaning that large loads can be driven. Nevertheless, complementary circuitry has several drawbacks especially if planar technology is used. For instance, mobility differences in PFET and NFET transistors causes an approximate effective current ratio of 2 between PUN and PDN devices. Thereafter, either the speed and thus one of the signal transitions is compromised or PFET has to be made double the size of NFET to compensate for lack of mobility [24]. Luckily, strength deviation is practically absent in FinFET devices, hence most of PFET and NFET device characteristics are indistinguishable [25]. However, small deviations in effective current and output resistance accumulate in large area designs, causing the necessity to slightly differentiate sizing of PUN and PDN.

The most characteristic property of CTT is the symmetric termination, which sets the  $V_{cm}$  on the line to be half the termination voltage. Nevertheless, Thevenin configuration generates a direct current path between the power rails, consequently causing static power dissipation at all times. By increasing TERM resistance value the power dissipation can be reduced, however, it comes at a cost of increased signal reflections due to poor matching and charging delay at RX input due higher RC constant.

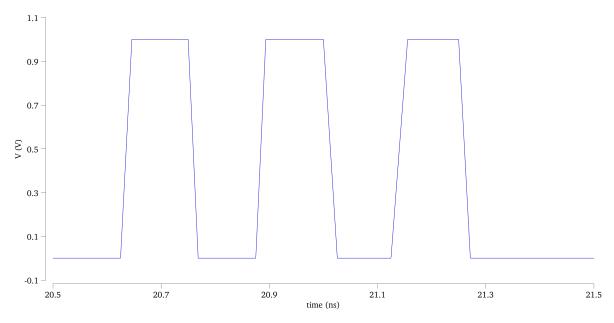

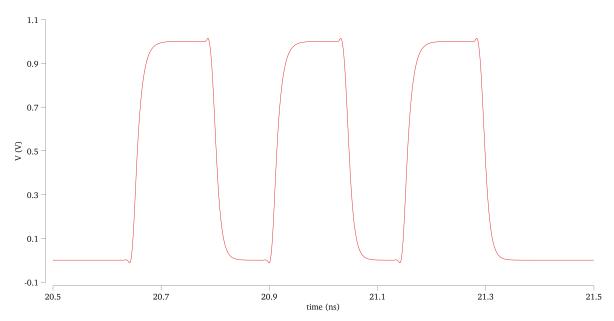

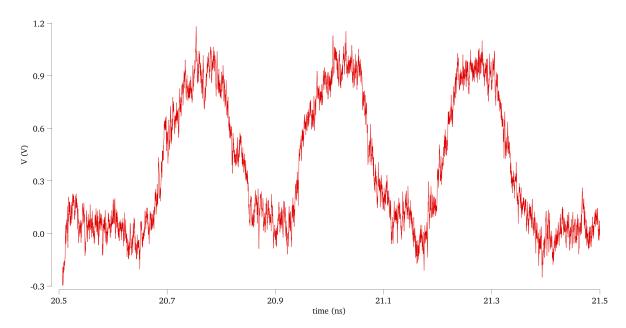

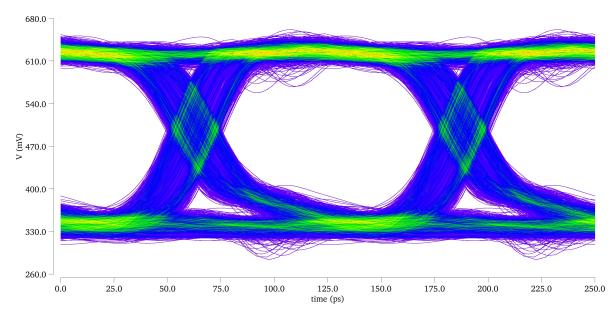

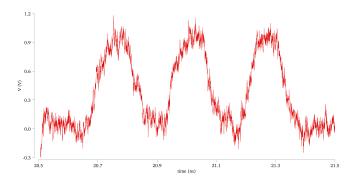

A particularly interesting characteristic caused by TERM upon signal switching from high-to-low or vice versa is non-constant slew rate on a single transition edge. This phenomenon is depicted in Figure 2.3. The split happens at half supply voltage due to termination first helping to bring the voltage up/down to the common mode level and later fighting the signal, trying to bring it back down/up.

Figure 2.3: Slew rate non-uniformity at RX input voltage in single edge transition of CTT topology with following simulation conditions: Imec low  $V_{th}$  FinFET 14 nm tech. RMG,  $V_{in}$  =  $V_{dd}$  = 1 V,  $TL_{len}$  = 4 cm, line spacing = 135 um, corner:TT, temp = 25°C, DR = 8Gb/s, input jitter = 16%

TERM can also be used for shifting  $V_{cm}$ . As TERM resistors act as a simple potential divider, using different resistor values for top and bottom leads to a change in center voltage. The shift might be required to compensate for common mode skew due to variation in PUN vs. PDN strength. It is

<sup>&</sup>lt;sup>3</sup>URL https://www.analog.com/en/design-center/glossary/push-pull.html [cited on 10th of June 2023]

important to set  $V_{cm}$  to half power supply voltage in order to obtain symmetric signal properties for '0' and '1', especially if other skew correction methods are absent.

Alternatively, differences in PFET and NFET strength can be counteracted by using asymmetric inverters, however, it is far from the optimal strategy as the whole chain of inverters would have to be ideally skewed. The latter is infeasible for large, multi-stage designs since PVT influence on the system would demolish the meta-stability achieved in ideal conditions. Upon PVT variations, fluctuation of  $V_{cm}$  would be amplified with each subsequent stage and further enhanced by attenuation and reflections on the TL.

With all the CTT components defined, power consumption has to be determined. Observe, CTT power can be estimated in terms of TERM and voltage supply voltage value. The total power consists of two components: static and dynamic power. Static power is consumed continuously, when power supply has been activated, even if no input data is provided. In case no input is applied, the static power dissipation can be estimated by Equation 2.1, where  $V_{dd}$  represents the power supply voltage value. Otherwise, the computations are slightly more tedious and are shown after determination of dynamic power.

$$P_{static} = \frac{V_{dd}^2}{R_{top} + R_{bot}} \tag{2.1}$$

The dynamic power can be estimated to the first degree with taking certain assumptions. First, it is assumed that only the last stage of the inverter chain has a significant contribution to power dissipation. The assumption holds true as long as TL and PACK intrinsic capacitances are significantly larger than gate capacitance of last inverter. In such a case the current to charge the external circuitry has to be multiple times higher than self-loading current. Second, the output resistances of NFET and PFET transistors are assumed to be equal, implying that input voltage  $(V_{in})$  equal to '0' or '1' provides equivalent loading case. The only difference is whether current gets sourced or sunk. Lastly, the transistor output resistances are assumed to be invariant, which can only be the case if ideal, zero rise time signals are present.

Ideally the dynamic power is negligible, which is the case when output resistance of active stage is infinite. This partially holds for low speed designs where TX area is small and transition of the signals happens rarely. However, as higher data rate requires more current to be provided by the transmitter to charge the load in shorter time period, the inverter area has to be increased. As a result, the internal resistance of the transistors is reduced. Taking a time instance where only NFET transistor is operational, the equivalent circuit model in terms of resistances can be seen in Figure 2.4. It can be noticed, that the NFET output resistance is effectively in parallel to pull-down termination resistance, thus reducing the overall rail-to-rail resistance. For calculations in this thesis, dynamic power is assumed to be of comparable magnitude to static power and thus has to be accounted.

With the former assumptions in place, the total power dissipation of CTT can be approximately determined as shown in Equation 2.2, where  $r_o$  corresponds to the output resistance of NFET. The dynamic power is approximated as  $I_{OL}^2 r_o$ , where  $I_{OL}$  represents the current value through the PDN transistor. Bear in mind, the power in the equation is given for case of turned-on NFET and turned-off PFET. Due to the aforementioned assumptions power in reverse operating case would be exactly the same, thus opposite scenario computations are omitted here.

$$P_{tot} = \frac{V_{dd}^2}{R_{top} + \left(\frac{1}{R_{bot}} + \frac{1}{r_o}\right)^{-1}}$$

(2.2)

Figure 2.4: Equivalent CTT circuit model in terms of resistances, when only NFET is operational

To determine the individual components (static and dynamic) slightly more sophisticated computations have to be performed. For simplicity, only the dynamic power is determined as shown in Equation 2.3, from which static power can be expressed as  $P_{static} = P_{tot} - P_{dynamic}$ .  $V_{OL}$  is defined as threshold voltage of system's low state.

$$P_{dynamic} = r_o \left( \frac{V_{dd}}{R_{top} + \left(\frac{1}{R_{bot}} + \frac{1}{r_o}\right)^{-1}} \cdot \frac{\left(\frac{1}{R_{bot}} + \frac{1}{r_o}\right)^{-1}}{r_o} \right)^2 = \frac{V_{OL}^2}{r_o}$$

(2.3)

The inverter has a fully transparent signal propagation characteristic for an ideal input signal - either of driver's transistor is going to be 'on' if there is a  $V_{in}$  applied. Thereby, the total power given in Equation 2.2 represents the average power in time. In case of realistic signals, both the transistors could be operational simultaneously during  $V_{in}$  transition leading to higher dynamic power dissipation due to alternate (w.r.t TERM) current path to ground. Dynamic energy wise, each of the transistors would constitute for only a half of total dynamic energy as their duty cycles (on time compared to period) are 'on' average 50% long.

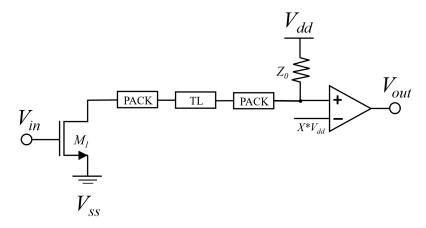

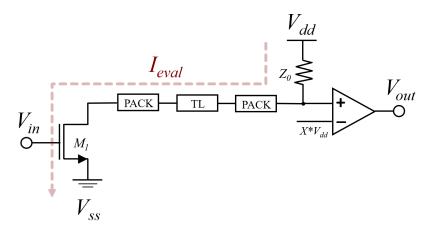

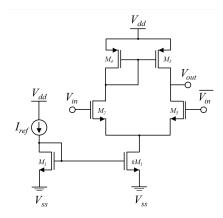

#### Saturated FET Driver

Saturated FET driver (SFD) is one of the earliest and simplest transmitter designs used in I/O systems [21] [26]. An example schematic of SFD topology can be seen in Figure 2.5. The simplest form of SFD includes only a single transistor operating in saturation region and one parallelly terminated load resistor. Saturation conditions for an NFET correspond to  $V_{ds} > V_{gs} - V_{th}$ , where  $V_{ds}$  is drain-to-source voltage,  $V_{th}$  is threshold voltage and  $V_{gs}$  is gate-to-source voltage [27]. To improve the drive strength and signal quality on the line another parallely terminated resistance can be added to the source side. However, adding source side termination would come at the cost of nearly doubling the dynamic power consumption due to both terminations seen to be effectively in parallel - halving overall resistance.

Figure 2.5: Schematic of Saturated FET Driver

The transmitter operates by being only partially transparent - the inverse of the signal is transmitted only when input is high, else, the line is pre-charged to termination voltage. During the evaluation phase, the NFET has to sink the current on the line to obtain the desired voltage drop across the termination resistor (see Figure 2.6). However, as termination is continuously going to resist the voltage drop, it can be concluded that the falling edge of signal seen at the input of RX is going to be significantly less steep than the rising edge. The lagging discharge could potentially cause bit errors, if long streams of 1 bits are transferred as interconnect's intrinsic capacitors would become fully charged and thus tought ot discharge. The errors can be prevented by increasing transistor's area, and as a consequence, enhancing the current sinking abilities and reducing TX output resistance.

Figure 2.6: Schematic of Saturated FET Driver operation principle

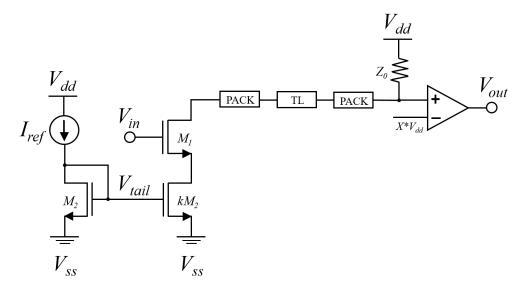

Moreover, a single transistor configuration can lead to performance degradation of up to two times due to PVT variation. To stabilize the current sinking, a set of parallelly connected digitally controllable saturated current mirrors (CMs) can be added on the source side of the driver as shown in Figure 2.7. By switching various current mirrors 'on' and 'off' it is possible to set the current to a desired value - a reference has to be compared to the current in the circuit. Nevertheless, the extra circuitry leads to an immense increase in area as both finite state machine (FSM) for controls and idle CMs are required to ensure that correct current is provided. The PVT offset can also be partially rectified by having significantly larger output swing by directly increasing the saturated NFET size, if maximum swing is not utilized from the start. Note, however, direct increase of SFD main transistor could corrupt the signal if too much miss-match between TERM and *M1* output resistance arises upon sizing. [21]

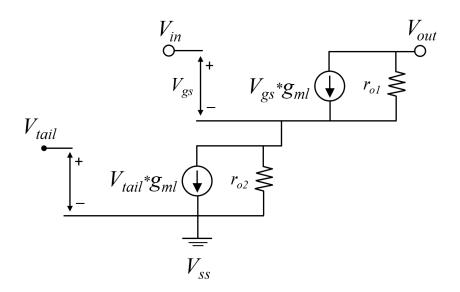

Figure 2.7: Schematic of Saturated FET Driver with a current source at its tail