### Back-end Power Electronics Modules for DC-type EV Charging Wide Voltage Range DC/DC Converters

Lyu, D.

10.4233/uuid:3d81ea50-4bd3-434f-aa32-eb837af0cfaa

**Publication date**

**Document Version**

Final published version

Citation (APA) Lyu, D. (2024). Back-end Power Electronics Modules for DC-type EV Charging: Wide Voltage Range DC/DC Converters. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:3d81ea50-4bd3-434f-aa32-eb837af0cfaa

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# BACK-END POWER ELECTRONICS MODULES FOR DC-TYPE EV CHARGING

WIDE VOLTAGE RANGE DC/DC CONVERTERS

## BACK-END POWER ELECTRONICS MODULES FOR DC-TYPE EV CHARGING

WIDE VOLTAGE RANGE DC/DC CONVERTERS

#### Dissertation

for the purpose of obtaining the degree of doctor at Delft University of Technology by the authority of the Rector Magnificus prof. dr. ir. T. H. J. J. van der Hagen chair of the Board for Doctorates to be defended publicly on Thursday 12<sup>th</sup>, September 2024 at 10:00 o'clock

by

### Dingsihao Lyu

Master of Science in Electrical Engineering, Delft University of Technology, The Netherlands, Born in Meishan, Sichuan, China. This dissertation has been approved by the promotor(s).

#### Composition of the doctoral committee:

Rector Magnificus, Chairperson

Prof.dr.ir. P. Bauer, Delft University of Technology, promotor

Dr. Zian Qin, Delft University of Technology, copromotor

Independent members:

Prof.dr. G. Papafotiou Eindhoven University of Technology

Prof.dr. D. F. Lascu Politehnica University Timisoara

Prof.dr.ir. A. H. M. Smets Delft University of Technology

Prof.dr.ir. M. Popov Delft University of Technology

Other members:

Prof.dr. T. B. Soeiro University of Twente

Printed by: Riddleprint Cover design: Haonan Yan

Copyright © 2024 by Dingsihao Lyu

An electronic version of this dissertation is available at <a href="http://repository.tudelft.nl/">http://repository.tudelft.nl/</a>.

## **CONTENTS**

| Su | ımma  | ary            |                                                                                   | ΧÌ     |

|----|-------|----------------|-----------------------------------------------------------------------------------|--------|

| Sa | men   | vatting        | ş                                                                                 | xiii   |

| 1  | Intr  | oducti         | on                                                                                | 1      |

|    | 1.1   | 1.1.1<br>1.1.2 | round                                                                             | 1<br>3 |

|    | 1.2   |                | rch Objective                                                                     |        |

|    | 1.3   |                | rch Questions and Methodologies                                                   |        |

|    | 1.4   |                | e of the thesis                                                                   |        |

|    | 1.5   | The D          | esign Requirements                                                                | 7      |

| Bi | bliog | raphy          |                                                                                   | 9      |

| 2  | Rec   | onfigu         | rable Phase Shift Full Bridge Converter                                           | 11     |

|    | 2.1   | Introd         | luction                                                                           | 12     |

|    | 2.2   | The o          | perational principle and analytical modeling                                      | 16     |

|    |       | 2.2.1          | Re-configuration by the Auxiliary Switches                                        | 16     |

|    |       | 2.2.2          | Comparison between the two structures of the r-PSFB converter $$ . $$ .           | 17     |

|    |       | 2.2.3          | Operating Principle                                                               | 18     |

|    |       | 2.2.4          | Steady State Analytical Modeling of the r-PSFB Converter                          |        |

|    | 2.3   |                | n Requirements of the Power Module                                                |        |

|    | 2.4   | Design         | n of the 11kW r-PSFB converter                                                    | 24     |

|    |       | 2.4.1          | Boundary Voltage Value of Reconfiguration $V_{\rm re}$ and the Auxiliary Switches |        |

|    |       | 2.4.2          | Transformer Turns Ratio $n$                                                       | 24     |

|    |       | 2.4.3          | Output Inductance Value $L_{\text{out}}$                                          |        |

|    |       | 2.4.4          | Output Capacitor $C_{\text{out}}$                                                 |        |

|    |       | 2.4.5          | Semiconductor Choices                                                             |        |

|    |       | 2.4.6          | Magnetic Components Design                                                        |        |

|    |       | 2.4.7          | Auxiliary Switches                                                                |        |

|    |       | 2.4.8          | RCD snubber circuitry                                                             |        |

|    | 2.5   |                | imental Results of the r-PSFB Prototype                                           |        |

|    | 2.6   | Concl          | usion                                                                             | 36     |

| Bi | bliog | raphy          |                                                                                   | 39     |

| 3  |       | _              | rable Resonant Converter                                                          | 43     |

|    |       |                | luction                                                                           |        |

|    | 3.2   | Opera          | ting principle of the two-stage converter                                         | 48     |

viii Contents

|    | 3.3      | Steady State Analytical Modelling of the LLC converter                      |

|----|----------|-----------------------------------------------------------------------------|

|    |          | 3.3.1 Soft Switching                                                        |

|    | 3.4      | Steady State Analytical Modelling of the Interleaved TCM buck converter . 5 |

|    |          | 3.4.1 Deadtime Analysis                                                     |

|    | 3.5      | Converter Design                                                            |

|    |          | 3.5.1 Design Requirements                                                   |

|    |          | 3.5.2 Semiconductor Selection                                               |

|    |          | 3.5.3 Resonant Capacitors                                                   |

|    |          | 3.5.4 Transformer Design                                                    |

|    |          | 3.5.5 Inductor Design                                                       |

|    |          | 3.5.6 Design Summary                                                        |

|    | 3.6      | Results of the Analytical Comparison                                        |

|    |          | 3.6.1 LLC converter                                                         |

|    |          | 3.6.2 Interleaved TCM buck converter                                        |

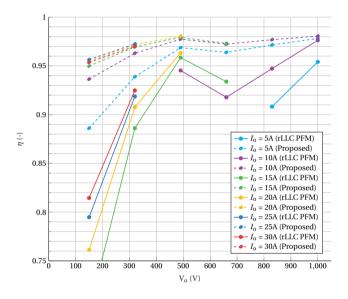

|    | 3.7      | Comparison to conventional frequency-modulated LLC 60                       |

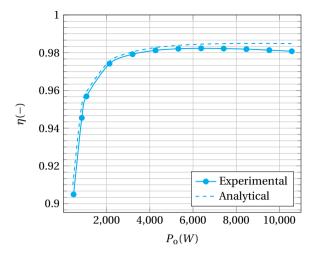

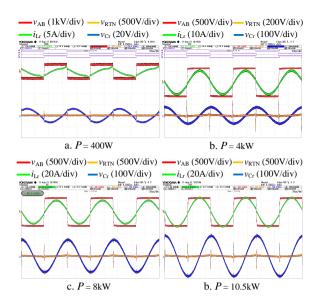

|    | 3.8      | Experimental Results                                                        |

|    |          | 3.8.1 LLC converter                                                         |

|    |          | 3.8.2 Interleaved TCM buck converter                                        |

|    |          | 3.8.3 Two-stage converter efficiency                                        |

|    | 3.9      | Conclusion                                                                  |

| Bi | bliog    | raphy 67                                                                    |

| 1  | Wid      | e Voltage Range Design of Dual Active Bridge Converter 79                   |

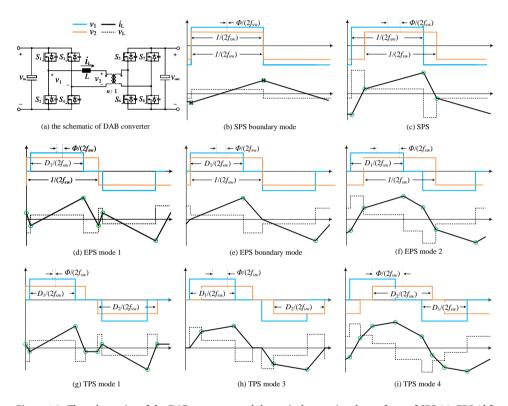

| 7  |          | Introduction                                                                |

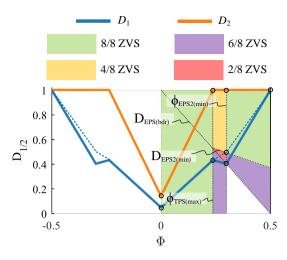

|    |          | Analytical expressions of the TPS mode 1 and 4                              |

|    | 1.2      | 4.2.1 full ZVS boundary conditions for TPS mode 1                           |

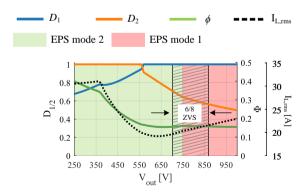

|    |          | 4.2.2 full ZVS boundary conditions for EPS mode 2                           |

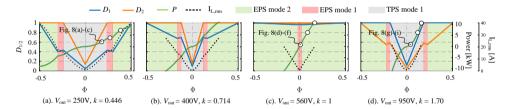

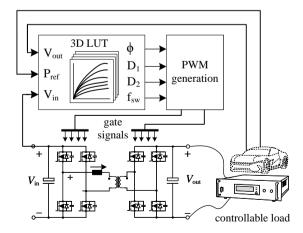

|    | 4.3      | The ZVS-Optimized Constant Frequency Modulation Scheme                      |

|    |          | 4.3.1 Construction of the modulation scheme                                 |

|    |          | 4.3.2 Loss of ZVS During Transition                                         |

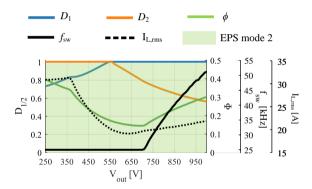

|    | 4.4      | The Variable Frequency Modulation Scheme for Full Power Operation 90        |

|    |          | 4.4.1 Working Principle                                                     |

|    |          | 4.4.2 Construction of the modulation scheme for full power operation 90     |

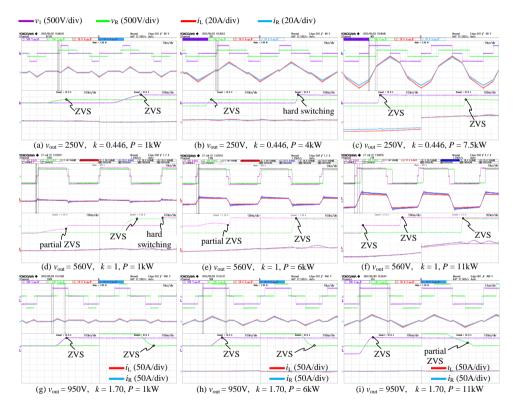

|    | 4.5      | Experimental Verification                                                   |

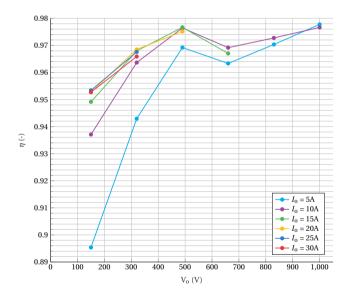

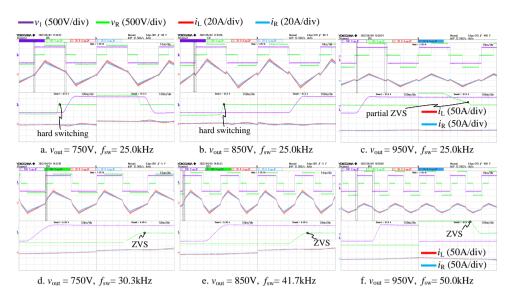

|    |          | 4.5.1 Results of constant frequency modulation scheme 94                    |

|    |          | 4.5.2 Results of variable frequency modulation scheme 99                    |

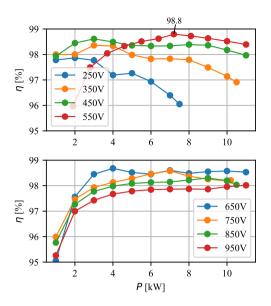

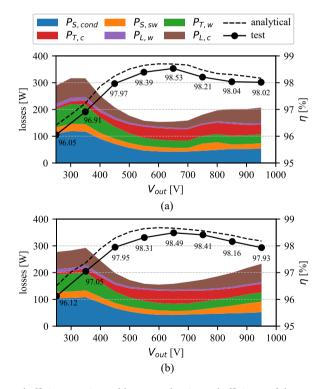

|    |          | 4.5.3 Efficiency performance                                                |

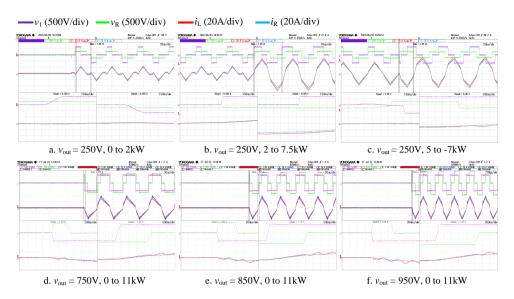

|    |          | 4.5.4 Transient Behaviours                                                  |

|    | 4.6      | Conclusion                                                                  |

| Bi | bliog    | raphy 10:                                                                   |

| 5  | Mul      | ti-Objective Design of the DC/DC Converters 10                              |

| •  |          | Introduction                                                                |

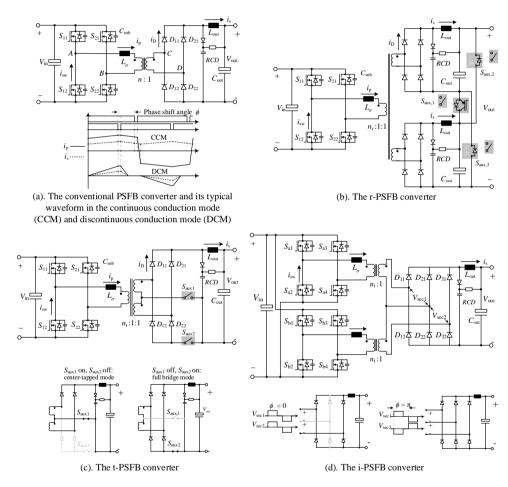

|    |          | Operation Principles of the Re-configurable PSFB Converters                 |

|    | <b>-</b> | 5.2.1 The Conventional PSFB Converter                                       |

|    |          |                                                                             |

CONTENTS ix

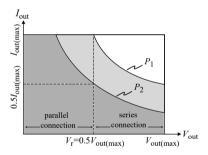

|    |        | 5.2.2  | The r-PSFB Converter with Re-configurable Secondary Side                  | 112        |

|----|--------|--------|---------------------------------------------------------------------------|------------|

|    |        | 5.2.3  | The t-PSFB Converter with Re-configurable Secondary Side                  | 112        |

|    |        | 5.2.4  | The i-PSFB Converter with Hybrid Diode Rectifiers                         | 112        |

|    | 5.3    |        | it Level Comparison Among Conventional PSFB, r-PSFB, t-PSFB and           |            |

|    |        |        | B Converters                                                              |            |

|    |        | 5.3.1  | Transformer Turns Ratios $n$                                              | 113        |

|    |        | 5.3.2  | Output Filter $L_{\text{out}}$ and $C_{\text{out}}$                       | 114        |

|    |        | 5.3.3  | Voltage Stress of $C_{\text{out}}$ and Current Stress of $L_{\text{out}}$ | 115        |

|    |        | 5.3.4  | Voltage Stress of the RCD Snubber Circuitry                               | 115        |

|    |        | 5.3.5  | Voltage and Current Stresses of the Rectifier Diodes and Transistors .    | 116        |

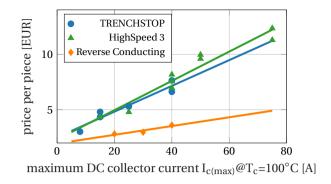

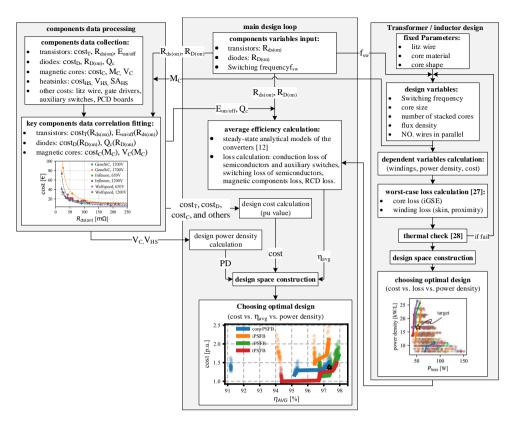

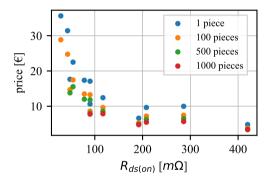

|    | 5.4    | Key C  | omponents Data collection and processing                                  | 117        |

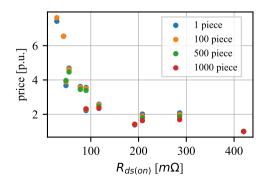

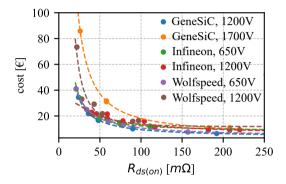

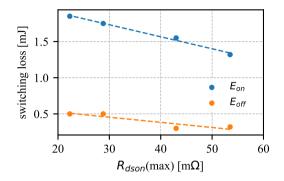

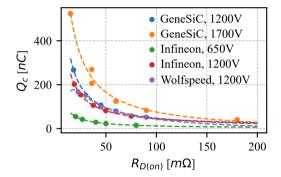

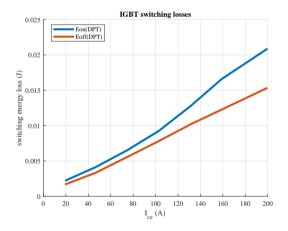

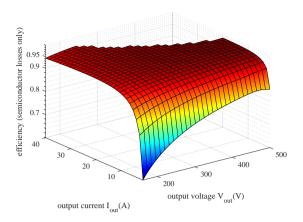

|    |        | 5.4.1  | Active Semiconductors                                                     |            |

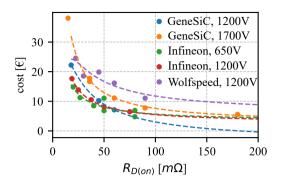

|    |        | 5.4.2  | SiC rectifier diodes                                                      | 122        |

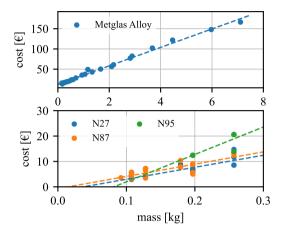

|    |        | 5.4.3  | Magnetic core material and Litz Wire                                      | 122        |

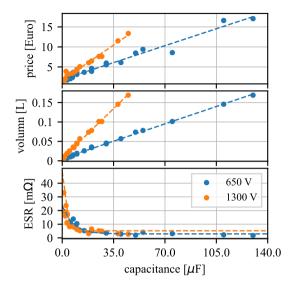

|    |        | 5.4.4  | Film capacitors                                                           | 124        |

|    |        | 5.4.5  | Heatsink                                                                  | 126        |

|    |        |        | Gate driver, relay and PCB                                                |            |

|    | 5.5    |        | -objective Design of The Converters                                       |            |

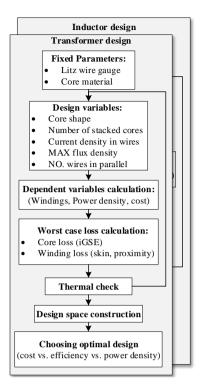

|    |        |        | Magnetic Components Designs                                               |            |

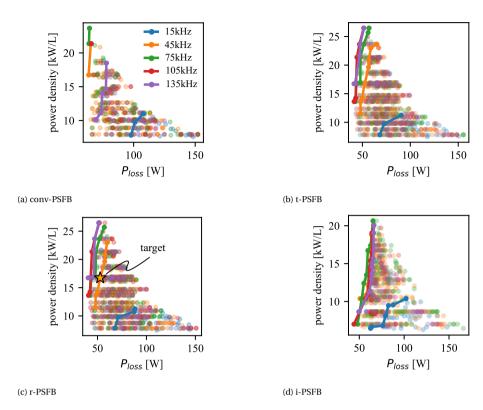

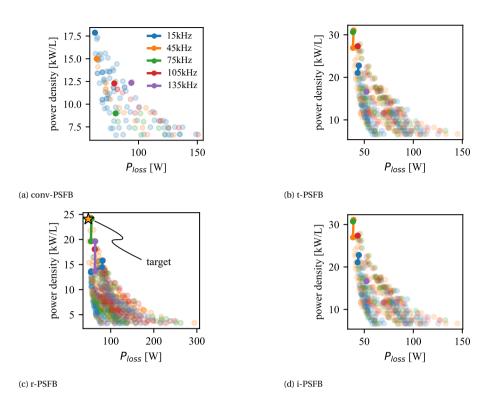

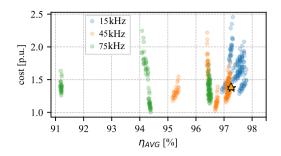

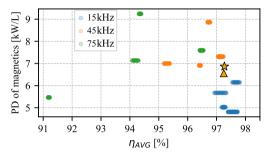

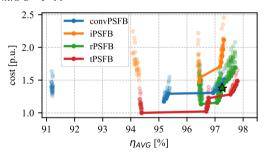

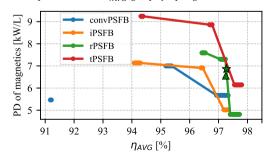

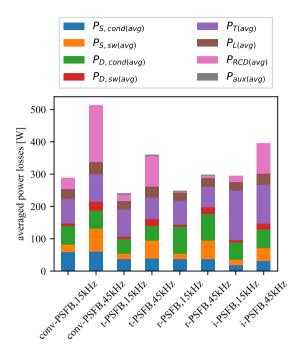

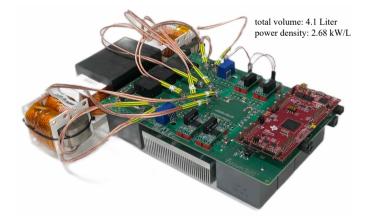

|    |        |        | Multi-Objective Design Results                                            |            |

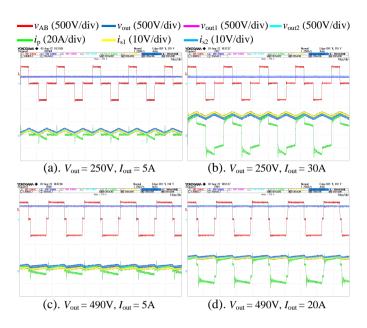

|    |        |        | imental Verification                                                      |            |

|    | 5.7    | Concl  | usion                                                                     | 135        |

| Bi | ibliog | raphy  |                                                                           | 141        |

| 6  | Bey    | ond Co | onverter: Battery Charging Strategies and Charging System                 | 145        |

|    | 6.1    | Introd | luction                                                                   | 146        |

|    | 6.2    | Revie  | w of Battery Charging Strategies                                          | 147        |

|    |        |        | Constant Current-Constant Voltage (CC-CV)                                 |            |

|    |        |        | Multi-Step Constant Current                                               |            |

|    |        |        | Boost Charging                                                            |            |

|    |        | 6.2.4  | Pulse Charging (PC)                                                       |            |

|    |        | 6.2.5  | Summary                                                                   |            |

|    | 6.3    | _      | cts of Charging Strategies on the performance of a PSFB Converter         |            |

|    |        |        | PSFB Analytical Modeling                                                  |            |

|    |        |        | PSFB Semiconductor Loss Model                                             |            |

|    |        |        | Charging Profile Simulation                                               |            |

|    | 6.4    | Bench  | nmarking Results                                                          |            |

|    |        | 6.4.1  | Comparison I: 1C current rate                                             |            |

|    |        | 6.4.2  | Comparison II: 2C current rate                                            |            |

|    | 6.5    |        | usion                                                                     |            |

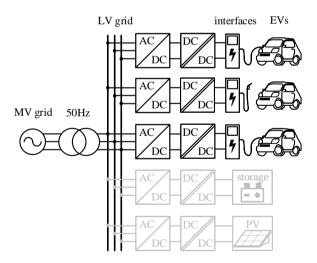

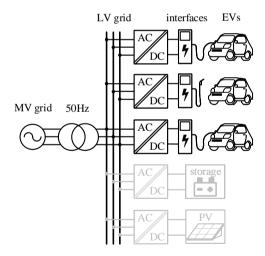

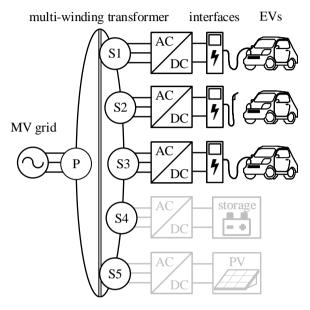

|    | 6.6    |        | w of the System Structures of Multi-ports EV Charging Station $\dots$     |            |

|    |        |        |                                                                           |            |

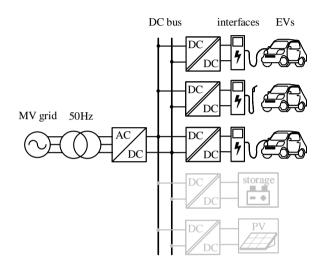

|    |        | 6.6.1  | Two-Stage Low Voltage AC Grid Coupled Structure                           |            |

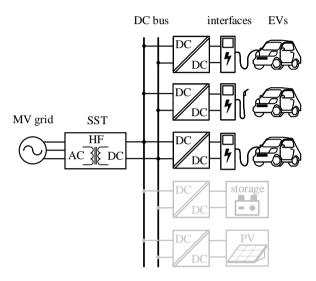

|    |        | 6.6.2  | Single-Stage LV AC Grid Coupled Structure                                 | 160        |

|    |        |        |                                                                           | 160<br>161 |

X CONTENTS

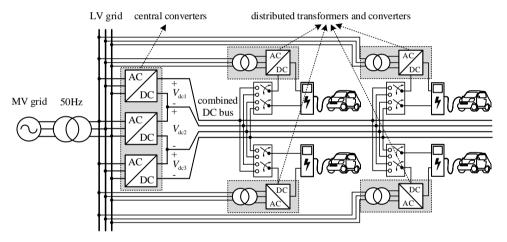

| 6.7     | 6.6.5 Combined DC Bus Coupled Structure | . 163 |

|---------|-----------------------------------------|-------|

| Biblio  | graphy                                  | 167   |

| 7 Cor   | nclusion and Future Research            | 171   |

| 7.1     | Addressing Research Questions           | . 171 |

| 7.2     | Future Research Recommendation          | . 173 |

| Ackno   | wledgements                             | 175   |

| List of | Publications                            | 177   |

## **SUMMARY**

In the last decade, the market for Electric Vehicles (EV) has expanded at an unprecedented rate. Concurrently, there has been a surge in the demand for public Direct Current (DC) EV charging stations. To accommodate a diverse array of EVs, these charging stations are required to support a broad operational voltage and power spectrum. However, this necessity introduces a trade-off between the operational range and the efficiency and utilization of the installed power within the charging infrastructure. The core of the issue lies in the fact that the charging stations, designed to cater to a wide range of operational conditions, often do not operate at their peak efficiency outside their designated optimal performance region.

To address this challenge, this thesis investigates the advantageous DC/DC power electronics solutions that can maintain high efficiency across a wider operational range while optimizing the utilization of installed power. The research topics include the suitable DC/DC converters for the back-end power modules of the charging system, the multi-objective design process of the power modules, and the advanced operation of the power modules.

#### SUITABLE DC/DC POWER MODULES

The back-end DC/DC power modules are required to operate with extremely wide battery voltage ranges due to the introduction of EV models with high battery pack voltage. However, conventional power electronic converters yield poor efficiency performance when they are operated in such a wide voltage range.

In this thesis, novel power electronic solutions for the back-end power modules within EV charging systems are introduced. These solutions are characterized by their reconfigurable topologies and the application of advanced modulation techniques. Through experimental validation, it is demonstrated that these innovative solutions significantly broaden the operational voltage spectrum while maintaining high efficiency across the entire range of operations. Consequently, these proposed power electronics building blocks represent a significant advancement for DC-type EV charging infrastructure, offering an efficient solution to meet the dynamic demands of electric vehicle charging.

#### MULTI-OBJECTIVE DESIGN OF POWER MODULES

The multi-objective design and benchmark of power electronic converters in terms of cost, power density, and efficiency performance is challenging, primarily due to the poor availability of the components' data. Component cost models depending on physical component properties are typically applied in the literature, but they are not so straightforward to implement. Moreover, a large database acquired from manufacturers is needed for a better fitting, which is not easily accessible.

xii Summary

This thesis proposes a multi-objective power electronic converter design and benchmark process in terms of the normalized cost, power density of the magnetic components and heatsinks, and the average efficiency performance. This process utilizes well-accessible data provided by the components' re-distributors to establish the correlations between the cost and loss performance of the components. Using this multi-objective design process, three re-configurable structure PSFB converters are analyzed and benchmarked for the wide voltage range public EV charging application. The research results prove the feasibility of the proposed multi-objective design and benchmark process, and identify the t-PSFB and r-PSFB converters to be the outstanding solutions in the wide voltage range public EV charging application.

#### ADVANCED OPERATION OF POWER MODULES

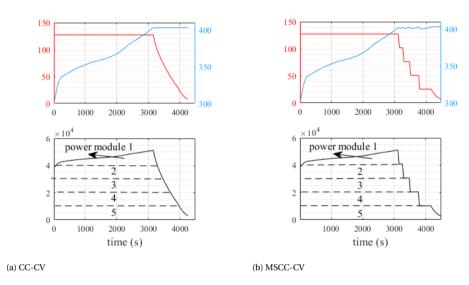

The charging strategies, which define how the electric energy is transferred from the charger to the EV battery, significantly impact the system's performance metrics. On the one hand, the charging strategy, especially the injected current, determines how fast the battery is being charged, affecting the cells' efficiency and aging. On the other hand, it determines how and in what range the power electronics converter of the EV charger will operate, thus affecting the efficiency and utilization rate of the circuit components.

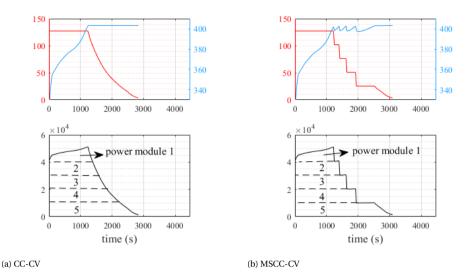

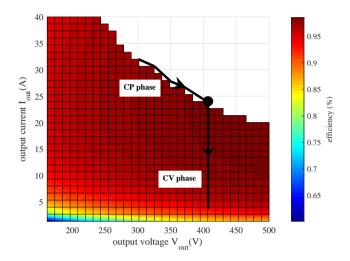

This thesis conducts a simulation case study to investigate how different charging strategies affect the performance of a modular EV charger. It is found that, firstly, the alternative charging strategies together with the modular structure of the charger can narrow the operation range of the power modules compared to the conventional CC-CV charging strategy. Combined with a tailored power module design, higher charging cycle efficiency can be achieved using alternative charging strategies. Secondly, alternative charging strategies can improve the utilization rates of installed power if combined with a flexible parallel modular multiple outputs structure.

### **SAMENVATTING**

In het afgelopen decennium is de markt voor elektrische voertuigen (EV) in ongekend tempo gegroeid. Tegelijkertijd is er een toename in de vraag naar openbare gelijkstroom (DC) EV-laadstations. Om een breed scala aan EV's te kunnen huisvesten, moeten deze laadstations een breed operationeel spannings- en vermogensspectrum ondersteunen. Deze noodzaak brengt echter een afweging met zich mee tussen het operationele bereik en de efficiëntie en het gebruik van het geïnstalleerde vermogen binnen de laadinfrastructuur. De kern van het probleem ligt in het feit dat de laadstations, die zijn ontworpen om te voldoen aan een breed scala aan operationele omstandigheden, vaak niet op hun maximale efficiëntie werken buiten hun aangewezen optimale prestatiegebied.

Om deze uitdaging aan te pakken, onderzoekt dit proefschrift de voordelige DC/DC-vermogenselektronica-oplossingen die een hoge efficiëntie kunnen behouden over een breder operationeel bereik en tegelijkertijd het gebruik van het geïnstalleerde vermogen kunnen optimaliseren. De onderzoeksonderwerpen omvatten de geschikte DC/DC-converters voor de back-end-vermogensmodules van het laadsysteem, het multiobjectieve ontwerpproces van de vermogensmodules en de geavanceerde werking van de vermogensmodules.

#### GESCHIKTE DC/DC-VERMOGENSMODULES

De back-end DC/DC-vermogensmodules moeten werken met extreem brede batterijspanningsbereiken vanwege de introductie van EV-modellen met een hoge batterijspanning. Conventionele vermogenselektronische converters leveren echter slechte efficiëntieprestaties wanneer ze worden gebruikt in zo'n breed spanningsbereik.

In dit proefschrift worden nieuwe vermogenselektronische oplossingen voor de backend-vermogensmodules binnen EV-laadsystemen geïntroduceerd. Deze oplossingen worden gekenmerkt door hun herconfigureerbare topologieën en de toepassing van geavanceerde modulatietechnieken. Door experimentele validatie wordt aangetoond dat

deze innovatieve oplossingen het operationele spanningsspectrum aanzienlijk verbreden, terwijl een hoge efficiëntie over het gehele bereik van de werking wordt gehandhaafd. Bijgevolg vertegenwoordigen deze voorgestelde vermogenselektronicabouwstenen een aanzienlijke vooruitgang voor DC-type EV-laadinfrastructuur en bieden ze een

efficiënte oplossing om te voldoen aan de dynamische eisen van het opladen van elektrische voertuigen.

#### MULTI-OBJECTIEF ONTWERP VAN VERMOGENSMODULES

Het multi-objectieve ontwerp en de benchmark van vermogenselektronische omvormers in termen van kosten, vermogensdichtheid en efficiëntieprestaties is een uitdaging, voornamelijk vanwege de slechte beschikbaarheid van de componentgegevens. Componentkostenmodellen die afhankelijk zijn van fysieke componenteigenschappen worden

xiv Samenvatting

doorgaans toegepast in de literatuur, maar ze zijn niet zo eenvoudig te implementeren. Bovendien is een grote database van fabrikanten nodig voor een betere aanpassing, die niet gemakkelijk toegankelijk is.

Dit proefschrift stelt een multi-objectief ontwerp en benchmarkproces voor vermogenselektronische omvormers voor in termen van de genormaliseerde kosten, vermogensdichtheid van de magnetische componenten en koellichamen en de gemiddelde efficiëntieprestaties. Dit proces maakt gebruik van goed toegankelijke gegevens die door de herdistributeurs van de componenten worden verstrekt om de correlaties tussen de kosten en verliesprestaties van de componenten vast te stellen. Met behulp van dit multiobjectieve ontwerpproces worden drie herconfigureerbare structuur PSFB omvormers geanalyseerd en gebenchmarkt voor de brede spanningsbereik openbare EV laadtoepassing. De onderzoeksresultaten bewijzen de haalbaarheid van het voorgestelde multi-objectieve ontwerp en benchmarkproces en identificeren de t-PSFB- en r-PSFB-converters als de uitstekende oplossingen in de brede spanningsbereik openbare EV-laadtoepassing.

#### GEAVANCEERDE WERKING VAN VERMOGENSMODULES

De laadstrategieën, die definiëren hoe de elektrische energie van de lader naar de EV-batterij wordt overgebracht, hebben een aanzienlijke impact op de prestatiemetingen van het systeem. Enerzijds bepaalt de laadstrategie, met name de geïnjecteerde stroom, hoe snel de batterij wordt opgeladen, wat de efficiëntie en veroudering van de cellen beïnvloedt. Anderzijds bepaalt het hoe en in welk bereik de omvormer van de EV-lader zal werken, wat de efficiëntie en benuttingsgraad van de circuitcomponenten beïnvloedt.

Dit proefschrift voert een simulatiecasestudy uit om te onderzoeken hoe verschillende laadstrategieën de prestaties van een modulaire EV-lader beïnvloeden. Ten eerste is gebleken dat de alternatieve laadstrategieën samen met de modulaire structuur van de lader het werkingsbereik van de vermogensmodules kunnen verkleinen in vergelijking met de conventionele CC-CV-laadstrategie. Gecombineerd met een op maat gemaakt powermoduleontwerp kan een hogere laadcyclusefficiëntie worden bereikt met behulp van alternatieve laadstrategieën. Ten tweede kunnen alternatieve laadstrategieën de benuttingspercentages van geïnstalleerd vermogen verbeteren als ze worden gecombineerd met een flexibele parallelle modulaire structuur met meerdere uitgangen.

1

### Introduction

#### 1.1. BACKGROUND

The climate change is extremely likely to be caused by the increased anthropogenic greenhouse gas (GHG) emission driven by economic and population growth [1]. To adapt and mitigate the risks of climate change, intergovernmental actions have been taken and several treaties have been made, such as the Kyoto Protocol and Paris Agreement, with the focus on reducing the risks and impacts of climate change by controlling emissions of the main anthropogenic GHGs [2] [3].

Governments around the world have developed tailored climate strategies and targets within the framework of international agreements. European Union as a leader in tackling climate change, has made the 2020, 2030, and 2050 climate strategies and targets [4]. The key targets of these strategies are summarized in the table 1.1 below. The Netherlands has committed itself to various international agreements and has developed a climate agreement aiming to emit 49% less  $CO_2$  by 2030 compared to 1990, and by 2050, GHG emissions must have fallen by 95% [5].

#### 1.1.1. EV ADOPTION

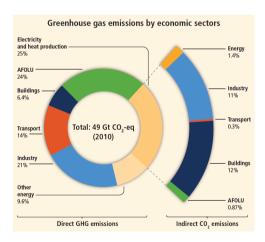

Transportation being one of the largest sources of GHG emission needs to be addressed with priority. The anthropogenic GHG emissions mainly come from electricity and heat production, industry, transport, buildings, agriculture, forestry and other land use (AFOLU), and other energy. Figure 1.1 shows the total anthropogenic GHG emissions from economic sectors in 2010 [1], where the circle shows the shares of direct GHG emissions (in % of total anthropogenic GHG emissions) from five economic sectors in 2010. The pull-out shows how shares of indirect  $CO_2$  emissions (in % of total anthropogenic GHG emissions) from electricity and heat production are attributed to sectors of final energy use. It can been seen that the GHG emissions from the transport sector account for around 14% globally. In the Netherlands, the transport sector is responsible for a quarter of all Dutch energy-related  $CO_2$  emissions and 20% of the total Dutch GHG emissions. Target has been set by the EU government to reduce  $CO_2$  emissions of the transport sector

#### **EU Climate Targets**

| by 2020 | 20% cut in greenhouse gas emissions (from 1990 levels) 20% of EU energy from renewables 20% improvement in energy efficiency                             |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| by 2030 | At least 40% cuts in greenhouse gas emissions (from 1990 levels) At least 32% share for renewable energy At least 32.5% improvement in energy efficiency |

| by 2050 | climate neutrality – an economy with net-zero GHG emissions                                                                                              |

Table 1.1: Key targets of climate strategies of EU

by 60% in comparison with 1990 [6]. The Netherlands made agreements on sustainable growth of the transport sector that,  $CO_2$  emissions caused by the transport sector must be reduced by 17% to at most 25 megatonnes (in comparison with 1990) in 2030, and to at most 12 megatonnes by 2050. Especially, one long-term perspective set out in the Agreement on Energy for Sustainable Growth is that all new passenger cars must be capable of driving without producing any  $CO_2$  emissions by 2035, and this will be applied to all passenger cars by 2050. [7].

Figure 1.1: Total anthropogenic GHG emissions from economic sectors in 2010. [1]

Road transport accounts for the predominant part of the total emissions of the trans-

port sector. The statistics from [8] show the  $CO_2$  emissions on Dutch territory by mobile sources in million kg. It can be concluded that around 73% of the total  $CO_2$  emissions come from road traffic. In a more specific measure, more than 50% of  $CO_2$  emissions are caused by passenger transport by road, and above 25% are produced by freight transport. Inland shipping, fisheries, and maritime shipping in Dutch territorial waters are responsible for nearly 20% of the  $CO_2$  emissions caused by the Dutch transport sector [7].

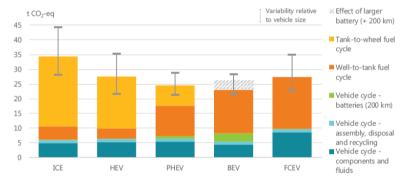

The electrification of transportation is a significant contribution to reduce  $CO_2$  emissions, and to which Electric Vehicle (EV) is the key. Figure 1.2 shows the comparative lifecycle GHG emissions of a global average mid-size car by powertrain [9]. It can be seen that the life-cycle emissions of BEVs and PHEVs is less than ICE vehicles. Together with the efforts to decarbonize electricity generation, which effectively reduce the emission of well-to-tank fuel cycle, the mitigation of emissions from the transport sector could be maximized.

Figure 1.2: Comparative life-cycle GHG emissions of a global average mid-size car by powertrain, 2018 [9]

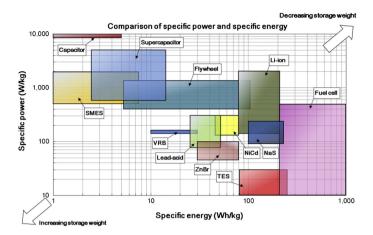

Among the different energy storage systems for EV, Lithium-Ion battery is the preferred choice due to its high specific energy, high specific power, long cycling times, wide range of operation temperature, low memory effect, low maintenance requirement, fast response time, small self-discharge rate and potential lower cost [10]. Figure 1.3 shows the mapping of different energy storage systems in terms of specific energy and specific power. It can been seen that Lithium Ion battery is able to provide relatively high power density and energy density at the same time, which are crucial to EV application. Moreover, the price of Lithium Ion battery is showing a trend of dropping [11]. Hydrogen fuel cells, on the other hand, is still limited by its cost, durability, and low energy density of the on-board hydrogen storage [12]. Moreover, The hydrogen refueling infrastructure is far from mature. There are only 381 refueling stations worldwide by the end of 2018 [9]. In this thesis, the term EV refers to Lithium-Ion battery EV.

#### 1.1.2. DC-TYPE EV CHARGER

With the policy incentives and the development of new technologies, the EV market is growing rapidly, and so is the need for DC-type EV chargers which are cost-efficient, fast, accessible, and with high efficiency.

Figure 1.3: Comparison of specific power and specific energy [10]

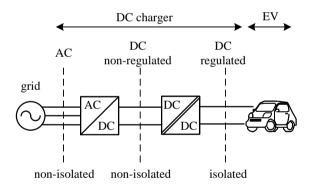

The typical diagram of an isolated DC-type EV charger is shown in Figure 1.4. It converts the electric energy from the grid and supplies the vehicle battery with a DC charging current or voltage per the vehicle's request.

Figure 1.4: The typical diagram of an isolated DC-type EV charger [13]

In order to be able to provide public charging service to various EVs, the charger needs to have wide output voltage and power range. Table 1.2 shows the battery and charging specification of three different EV models as examples. It could be seen that the battery voltage of EVs would not only changes in a large range during charging process, but also varies among different models. Moreover, the maximum allowed charging power differs drastically with different models.

Having these wide voltage and power ranges may lead to lowered efficiency and poor utilization of the installed power of the charging system. Since the chargers would only have optimal performance in certain operation region, lowered efficiency could happen when the operation condition is out of the design region, such as operating at very low

| Car Model                    | Nissan Leaf (40kW) | Tesla model 3 (long range) | Porche taycan (turbo) |

|------------------------------|--------------------|----------------------------|-----------------------|

| end-of-discharge votlage (V) | 240                | 240                        | 495                   |

| end-of-charge voltage (V)    | 403                | 403                        | 830                   |

| maximum charging power (kW)  | 50                 | 250                        | 270                   |

Table 1.2: Battery and charging specifications for different EV models

voltage and/or low power. On the other hand, poor utilization of the installed power could happen when operating the charger at low power, leaving the rest of the installed power capability idle. An example is using a charger with 300kW power rating which could been used to charging a Porche Taycan, to charge a Nissan Leaf. Since the maximum charging power is limited by the EV, the exceeding 250kW installed power is left idle. Last but not least, the time that an EV is connected to a charger is much longer than the actual charging time. A study on the public charge infrastructure in the city of Amsterdam [14] finds out that only 12 to 18% of the average connection time is actually used for charging.

#### 1.2. RESEARCH OBJECTIVE

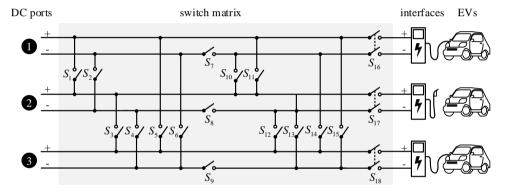

To address the challenges of the EV charging application, a cost-efficient, fast, and flexible DC-type Electric Vehicle (EV) charger which features multiple output charging spots through the implementation of multiplexing techniques is proposed as a possible solution.

In order to successfully develop such a charging system, both the physical layer and the virtual layer need to be designed. The physical layer is the whole hardware of the power-delivering system constructed by the power modules. It includes not only the individual power modules but also the system structure. The virtual layer determines how the hardware operates. It consists of several elements: the modulation method to control the power module, the charging strategy which determines how the power is regulated during the charging process, and the multiplexing method to control the power flow from the output ports of the charger.

The research objective of this thesis focuses on the physical layer, and it is as follows: To research the design and operation of the advantageous isolated back-end (DC/DC) power electronic converters which can be used as Power Electronic Building Blocks (PEBBs) for a flexible Electric Vehicle (EV) DC-type charger that features wide voltage range operation.

#### 1.3. RESEARCH QUESTIONS AND METHODOLOGIES

To achieve the research objective, three main research questions need to be answered. The first and foremost research question is:

1. What are the suitable DC-DC converters for the back-end power modules?

To answer this first question, the following methodology is used:

Define the design specifications for the isolated DC-DC converters.

1

- Conduct literature reviews on possible isolated DC-DC converter design solutions and identify the advantageous converter topologies and modulation methods.

- Propose 2-3 candidates, conduct further analytical modeling, simulation, and design

- Verify the designs by prototyping and experimental tests.

Once the suitable DC/DC converters are identified, the question becomes: how to better design them? Thus, the second research question and the methodology used are as follows:

- 2. How to conduct a multi-objective design for an optimal power module design?

- Define the most critical design objectives for the power modules.

- Propose a multi-objective design procedure that yields the optimal converter designs based on the design objectives.

- Form the multi-objective design space using analytical modeling and simulation.

- Choose an optimal point of design, and verify the design method with the experimental prototype.

Last but not least, when the power modules can be selected and designed, the third research question is:

3. How to operate the power modules in the charging system to achieve higher efficiency and utilization?

The methodology to tackle this research question is as follows:

- Conduct literature reviews on possible lithium-ion battery charging strategies.

- Investigate the influence of charging strategy on power converters among the evaluation criteria.

- Simulate and compare the performance of the power modules with different charging strategies. The evaluation criteria is the efficiency of the power converter over the whole charging cycle, and the utilization rate of the installed power.

- Study the multiplexing method, and investigate how to achieve flexible power distribution by multiplexing method.

- Verify the feasibility of multiplexing by a scaled-down prototype consisting of at least 2 power modules.

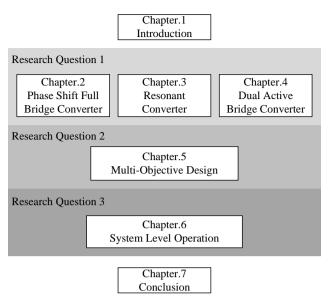

Figure 1.5: The outline of this thesis

#### 1.4. OUTLINE OF THE THESIS

This thesis tries to answer the research questions and present the research outcomes. Figure 1.5 shows the outline of this thesis.

Chapters 2, 3, and 4 address research question 1 by presenting the design and evaluation of advantageous DC/DC converters that can be used for the wide voltage range EV charging application. More specifically, chapter 2 introduces the reconfigurable phase shift full bridge converter design, chapter 3 the reconfigurable resonant converter design, and Chapter 4 the dual active bridge converter design with a novel modulation method. The research question 2 is addressed in Chapter 5, where a multi-objective power electronic converter design process is proposed to optimize the efficiency performance, power density, and cost. Chapter 6 tackles research question 3 by investigating the impacts of the lithium-ion battery charging strategies and conducting a survey on the charging system structure. Finally, the conclusion is summarized in Chapter 7, and some future works are discussed.

#### **1.5.** THE DESIGN REQUIREMENTS

The design restrictions of the isolated back-end DC/DC converter of the EV chargers are obtained by studying the EV charger standards, including the CHADEMO and IEC 61851 standards of electric vehicle conductive charging system, Part 23: DC electric vehicle charging station [13].

Isolation requirements: the secondary circuit(output side) of the DC supply shall be designed as an IT (isolated terra) system, and protection measures in accordance with 411 of IEC 60364-4-41:2005 shall be applied. In addition, if the DCEV

- charging station has multiple DC outputs designed for simultaneous operation, each output circuit shall be isolated from each other by basic insulation or reinforced insulation.

- 2. The minimum input voltage  $V_{in(min)} = 540V$ . This is the result of the 600V output of a conventional three-phase rectifier considering the 10% mains dip.

- 3. The maximum input voltage  $V_{in(max)} = 900V$ . By limiting the maximum input voltage, the 1200V semiconductor device could be better utilized. otherwise higher voltage rating devices should be considered.

- 4. The minimum output voltage  $V_{out(min)} = 150 \, V$ . This is the minimum output voltage stated in the chademo standard. In the IEC61851 standard, the minimum output voltage is 50V, but from a fast charging point of view, with a 50V output voltage, the charging power is fairly low. Moreover, considering the trend of the increasing battery capacity, and higher demand of fast charging, the higher 150V is chosen as the minimum output voltage.

- 5. The maximum output voltage  $V_{out(max)} = 1000V$ . This is the maximum output voltage stated in IEC61851.

- 6. The maximum current ripple during CC phase (peak2peak)  $I_{out,ripple(max)} = 9A$ , as in IEC61851.

- 7. The maximum voltage ripple during CV phase (peak2peak)  $V_{out,ripple(max)} = 10V$ , as in IEC61851.

- 8. The minimum switching frequency  $f_{sw(min)} = 15kHz$ , to avoid the audible frequency band.

- 9. The maximum switching frequency  $f_{sw(max)} = 150kHz$ , to have easier EMC requirements.

- 10. The EV charger should be able to operate under ambient temperatures from -5 to 40 degrees celsius.

- 11. The maximum output current allowed is 125A for a 50kW charger, and 25A for a 10kW charger. This is because of the limitation of charging cable (non-liquid cooling)

## **BIBLIOGRAPHY**

- [1] R.K. Pachauri Core Writing Team and L.A. Meyer (eds.). Climate change 2014 synthesis report. Report, IPCC, 2015.

- [2] United Nations. Kyoto protocol to the united nations framework convention on climate change. agreement, 1998.

- [3] United Nations. Paris agreement. agreement, 2015.

- [4] Eu climate strategies and targets. https://ec.europa.eu/clima/policies/strategies\_en.

- [5] Dutch climate agreement. https://www.rijksoverheid.nl/onderwerpen/ klimaatakkoord/documenten/rapporten/2019/06/28/klimaatakkoord, 2019.

- [6] White paper on transport. https://ec.europa.eu/transport/sites/transport/files/themes/strategies/doc/2011\_white\_paper/white-paper-illustrated-brochure\_en.pdf, 2011.

- [7] Ministry of Economic Affairs of the Netherlands. Energy report: transition to sustainable energy. report, 2015.

- [8] Air emissions on dutch territory; mobile resources. https://opendata.cbs.nl/ statline/#/CBS/nl/dataset/7062/line?ts=1572883076640, 2019.

- [9] IEA. Global ev outlook 2019. Report, IEA, 2019.

- [10] Xing Luo, Jihong Wang, Mark Dooner, and Jonathan Clarke. Overview of current development in electrical energy storage technologies and the application potential in power system operation. <u>Applied Energy</u>, 137:511–536, 2015.

- [11] Tarvydas D. Lebedeva N. Tsiropoulos, I. Li-ion batteries for mobility and stationary storage applications scenarios for costs and market growth. Report, Publications Office of the European Union, 2018.

- [12] S. M. Lukic, J. Cao, R. C. Bansal, F. Rodriguez, and A. Emadi. Energy storage systems for automotive applications. <u>IEEE Transactions on Industrial Electronics</u>, 55(6):2258–2267, 2008.

- [13] IEC. European standard iec 61851-23: 2014. electric vehicle conductive charging system—part 23: Dc electric vehicle charging station, 2014.

- [14] R. Van den Hoed, J.R. Helmus, R. De Vries, and D. Bardok. Data analysis on the public charge infrastructure in the city of amsterdam. World Electric Vehicle Journal, 6(4):829–838, 2013.

## RECONFIGURABLE PHASE SHIFT FULL BRIDGE CONVERTER

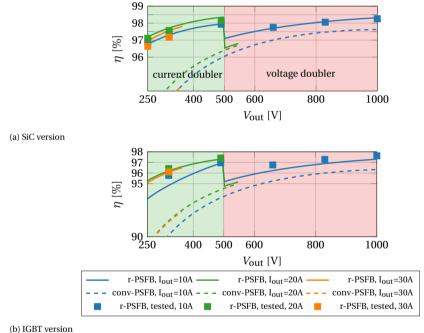

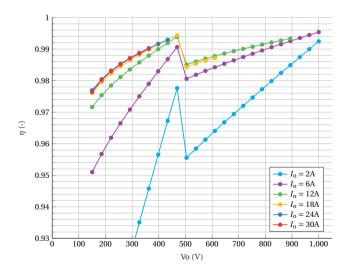

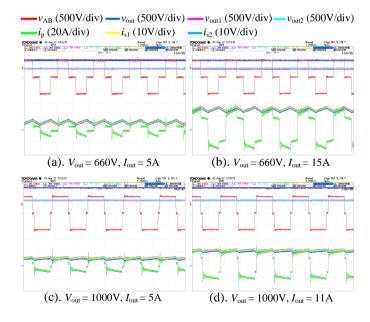

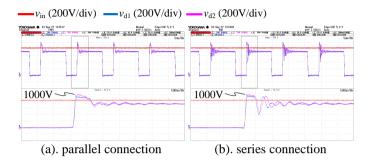

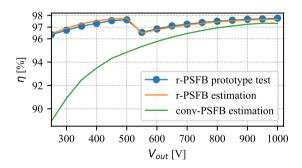

This chapter analyzes, designs, and tests a re-configurable phase-shift full-bridge (r-PSFB) isolated DC/DC converter well suited for a wide voltage operating range. By controlling the auxiliary switches, a series or parallel connection can be realized on the secondary side of the converter. As a result, the r-PSFB converter can operate in an extremely wide voltage range without compromising the system efficiency. In this chapter, the characteristics of the r-PSFB converter and its design considerations are discussed in detail. An 11kW r-PSFB converter prototype with 640-840V input voltage and 250-1000V output voltage ranges is developed and tested to validate the analysis and efficiency of the designed converter. A comparative study against a conventional PSFB converter is conducted for benchmark purposes to prove the advantages of the studied r-PSFB converter.

<sup>&</sup>lt;sup>1</sup>This Chapter is based on:

D. Lyu, T. B. Soeiro and P. Bauer, "Design and Implementation of a Reconfigurable Phase Shift Full-Bridge Converter for Wide Voltage Range EV Charging Application," in IEEE Transactions on Transportation Electrification, vol. 9, no. 1, pp. 1200-1214, March 2023, doi: 10.1109/TTE.2022.3176826.

#### 2.1. Introduction

The Electric Vehicle (EV) market has been expanding with an unprecedented speed in the last decade. The EV cars stock market nearly doubled from 2018 to 2020, as shown in [1]. Along with this trend, rises the demand for public EV charging stations. While the most common EV battery voltage architecture is 400V, adopted by many manufacturers, namely, Tesla, Nissan, etc., new high-end EV models with 800V battery voltage architectures are introduced to the market. Examples are Porsche Taycan [2], Hyundai IONIQ 5 [3], Rapide E from Aston Martin [4], and Lucid Air from Lucid Motors [5]. Therefore, the challenge for the EV chargers is clear: to provide charging services to different cars, which will demand the power electronic circuits to operate with extremely wide battery voltage ranges.

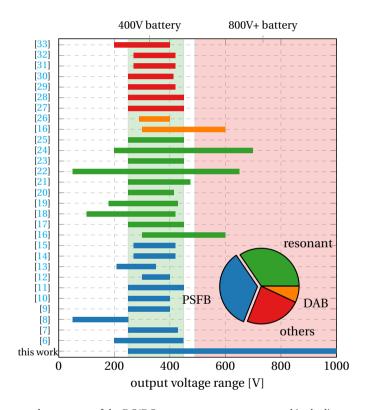

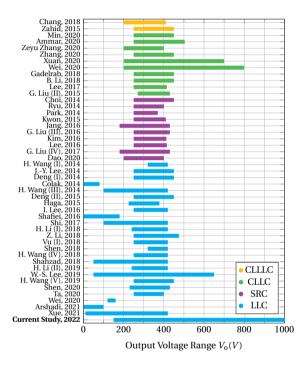

Figure 2.1: Output voltage ranges of the DC/DC converter prototypes reported in the literature from 2011 to 2021. (only the studies with prototype design and testing are included.)

However, according to the knowledge of the authors, there is no study in the literature that has provided experimentally verified isolated DC/DC converters for battery charging that is able to charge both the 400V and 800V EVs [6–33]. Figure 2.1 shows the output voltage ranges of the available literature of DC/DC converters researched for the EV charging application from the year of 2011 up to 2021. It is shown that, while most of the designs are focused on the 400V EV charging, none can charge both the 400V and

#### 800V EVs.

The problem lies in the poor efficiency performance when these converters are made to operate in such a wide voltage range. As can be seen from Figure 2.1, the most popular isolated DC/DC converter topologies used in EV charging are the phase-shift full-bridge (PSFB) converter and the series resonant circuits.

PSFB converters are widely used in EV charging application [6–15]. For the PSFB type converter, the highest efficiency is obtained at the smallest phase shift, or in other words, the highest operating output voltage. And the efficiency will drop as the phase shift increases or the output voltage decreases. The work developed [7] proposes a hybrid-switching PSFB converter that provides a wide ZVS range for the leading leg and ZCS for the lagging leg. Interestingly, the freewheeling circulating losses can also be avoided, and the undesirable voltage overshoots can be clamped well. However, additional passive components (two diodes, a capacitor, and an inductor) are needed, and the complexity of the converter increases. The work in [8] proposes a secondary-side PSFB converter that extends the soft-switching operation and eliminates the circulating current, but it comes with the cost of two additional switches and more complex control. In [13] a ZVS full-bridge DC/DC converter is proposed, which incorporates a diode clamping circuitry on the primary side for the voltage ringing clamping, and uses an asymmetrical PWM modulation together with an additional auxiliary inductor to reduce circulating losses.

Due to its simple structure and ability of soft-switching, resonant converters are also widely used for EV charging [16-25]. The resonant converter is typically controlled by frequency modulation. The highest efficiency is typically achieved when the switching frequency is close to the resonant frequency in the inductive region of the resonant tank, i.e., when the converter voltage gain is mostly given by the transformer turns ratio, and the H-bridge inverter operates with Zero-Voltage-Switching (ZVS) turn-on. The efficiency of the resonant converter will drop when the voltage regulation is necessary, particularly at low voltage values where the circuit has to operate deeply in the inductive equivalent impedance of the resonant tank. In order to improve the ZVS performance and efficiency of the resonant converter in the wide output voltage range EV charging application, the work in [18] proposes to connect the LLC converter to a SEPIC converter. The SEPIC converter can follow the EV battery voltage and provide a wide DC link voltage range so that the LLC converter can always operate in proximity of the resonant frequency. The work in [19] proposes to reduce the switching frequency range of the LLC converter by adding delay-time control on the secondary side rectifier switches, which unavoidably increases the cost and complexity of the converter. The authors of [22] suggest the addition of a BUCK converter to the LLC converter so that the LLC converter operates with a fixed switching frequency, and the BUCK converter is responsible for the voltage regulation. However, the BUCK converter still suffers from an efficiency drop when operated at a low duty cycle. In [24] a three-level CLLC resonant converter is presented whereby combining the working modes of the three-level full-bridges, the voltage regulation range is extended while the controllable switching frequency is kept within a reasonable range. The work in [25] introduces an asymmetric parameters methodology for designing the CLLC converter for EV charging application so that the switching frequency range can be reduced for the bi-direction EV charging application.

Unfortunately, none of these researches have investigated the charging of 800V EVs,

and no experimental results have shown high-efficiency performance in the operation range of 400V and 800V EV charging, which is crucial for the current and future EV charging application. Moreover, when the charging voltage up to 1000V has to be considered, the usage of rectifier diodes with 1700V voltage rating becomes necessary if the aforementioned topologies are used, which are more commercially limited and less compatible compared to the 650V and 1200V ones, which have a broad application range in several other markets.

In order to extend the output voltage conversion range of a PSFB converter without compromising the system efficiency performance in the whole operational range, Sun et al. (2011) [34] proposed the idea of a re-configurable structure PSFB converter, which can be re-configurable by connecting its two isolated outputs in series for high voltage operation and in parallel for high current operation. This idea is further extended in [35-38], where a wide input voltage range of 100-400V and output voltage range of 15-96V is realized with more re-configurable steps on the secondary side, and one more switching leg on the primary side to enable the series and parallel re-configuration in the primary side. Since this idea of re-configurable structure also enables the utilization of lower current and voltage rating devices on the secondary sides and does not bring extra complexity to the control stage, it seems well suited for the wide output voltage EV charging application. The paper from Sun et al., [34] focuses on the design of a constant peak power protection control scheme for the circuit, a nonlinear smooth transition control method for the two configurations and the stability analysis of the re-configurable structure. The works presented in [35–38] describe more in detail the circuit operation principle, and design considerations including the separate transformer design for better thermal management, ZVS performance and loss calculation for the re-configurable PSFB converter. However, the steady-state analytical model for calculating the current stresses of the circuit's components, which requires adjustments to that of the conventional PSFB converter, is not elaborated. The voltage ringing issue on the secondary side, which is inherent for the PSFB type converter, is not addressed in these works. Whereas in the EV charging application, where the output voltage is up to 1000V, the voltage ringing needs to be well-clamped to ensure the safe operation of the rectifier diodes. Moreover, the aforementioned works have not considered different output filter structures, which require different numbers and voltage/current ratings of the filter components. This trade-off has to be examined in the EV charging application. Last but not least, no actual benchmark comparison between the re-configurable PSFB converter and the conventional PSFB converter has been carried out for the wide voltage range necessary for the EV charging application.

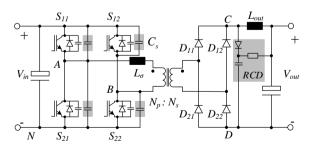

This chapter designs and implements a re-configurable phase-shift full-bridge (r-PSFB) converter based on the idea of the wide output range and constant peak power (RS-WOCP) converter from Sun et al. [34] for the wide output voltage EV charging application. Compared to a traditional PSFB converter, the operational phase shift angle of the converter during the charging of the low voltage battery is reduced, resulting in high efficiency in a larger operational output voltage range. In the series connection mode, the output voltage of the converter is twice that of a single secondary side, allowing the converter to charge up to 1000V without the necessity of employing higher voltage rating devices (e.g., 1700V Shottky diodes). While in the parallel connection mode, the con-

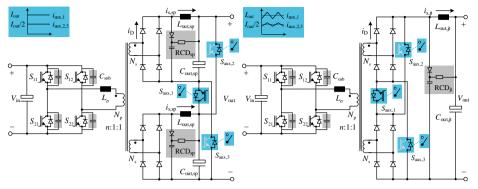

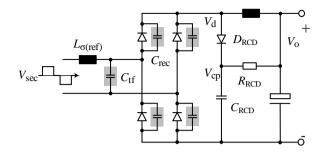

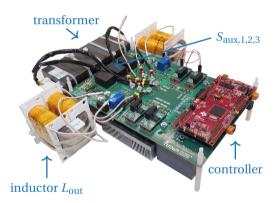

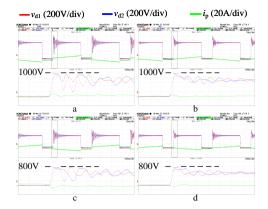

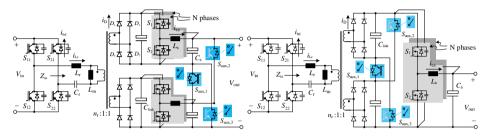

(a) separate output filter and RCD snubber (selected topol- (b) joint output filter and RCD snubber ogy)

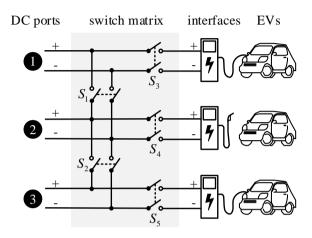

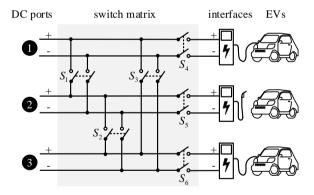

Figure 2.2: r-PSFB converter with separate or joint output filter and RCD snubber, with  $i_{aux,1,2,3}$  illustrated. Note that  $S_{aux,1,2,3}$  can be either mechanical switches or semiconductor transistors. The separate output filter structure is chosen in this work for further analysis and design.

verter can charge the 400V EVs more efficiently due to the reduced current stresses on the components. Another important point to highlight is that most of the conventional EVs designed for the lower cost mass-market will employ the conventional 400V battery. Therefore, an EV charger may be mostly used for this voltage class. Based on this, it is wise to implement circuits where high power efficiency is found within the 400V battery charging profile, even if the output voltage range covers the 800V battery charging. Unfortunately, the conventional PSFB and most resonant converters used for EV charging would feature a BUCK-type regulation, and naturally, the peak efficiency range would be found at the highest voltage range, i.e., the 800V EV battery class. This technical feature highlights the suitability of the r-PSFB converter for the application of EV charging.

The contribution of this chapter is as follows:

- 1. Extended analysis and comparison of the two possible output filter and snubber circuitry structures of the r-PSFB converter.

- The detailed steady-state model of the r-PSFB converter is presented and verified, while the modification to the conventional PSFB converter is explained thoroughly.

- 3. The complete design guideline of the r-PSFB converter is elaborated, including the essential snubber circuitry design.

- 4. The benchmark design of an 11kW r-PSFB converter and conventional PSFB converter for the wide output voltage range (250-1000V) EV charging application is presented, which was not yet elaborated in the literature. This is particularly important because it identifies the r-PSFB converter as an outstanding solution for the future EV market.

- 5. The experimental results show excellent charging cycle efficiency for both 400V and 800V EV battery charging, and a peak efficiency of 98.3% using SiC switches,

which is among the highest reported in the available literature analyzing the PSFB converter in the EV charging application with proven prototype experimental results.

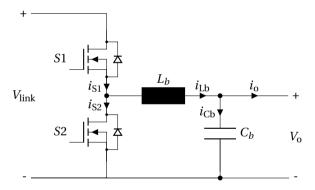

# **2.2.** THE OPERATIONAL PRINCIPLE AND ANALYTICAL MODELING

There are two possible structures that can be implemented for the r-PSFB converter, namely the separate output filter structure, and the joint output filter structure. Figure 2.2 shows the circuit schematics of these two possible r-PSFB converters. Threewinding transformer is used, which has one primary and two secondary windings, with the turns ratio n:1:1. The primary side is fed by the DC input voltage  $V_{in}$  and a fullbridge inverter. An equivalent leakage inductance  $L_{\sigma}$  is present in the primary side, which is utilized for the ZVS turn-on of the transistors. Each of the secondary sides is connected to a diode bridge rectifier. For the separate output filter structure as shown in Figure 2.2a, each diode-bridge rectifier is connected to an output filter,  $L_{\text{out}}$  and  $C_{\text{out}}$ , and a RCD snubber circuitry. Three auxiliary switches, Saux,1,2,3, connect the two secondary sides and enable two different configurations according to their switching states. For the joint output filter structure as shown in Figure 2.2b, the two diode-bridge rectifiers are firstly connected to  $S_{\text{aux},1,2,3}$ , and they share a common output filter and RCD snubber. The RCD snubber circuitry is used for mitigating the voltage spikes on the secondary side diodes [39]. The lossless turn-off snubber  $C_{\rm snb}$  for the H-bridge is also shown in the primary side of the transformer. The auxiliary switches can be implemented by either mechanical switches or semiconductor transistors, as shown in Figure 2.2.

#### **2.2.1.** RE-CONFIGURATION BY THE AUXILIARY SWITCHES

In an EV charging session, before the actual energy transfer happens, there is a communication period. During this period, the EV will inform the charger about the required charging voltage and current value [40]. By comparing the voltage value to a preset boundary voltage value  $V_{\rm re}$ , the r-PSFB converter can be configured into a parallel connection configuration if the required charging voltage value is lower or as a series connection if the value is higher, by setting the states of the auxiliary switches  $S_{\text{aux},1,2,3}$ . It is important to mention that the r-PSFB converter does not need to change the configuration during operation in the EV charging application. This is because the voltage range of the 400V EVs does not overlap with the 800V EVs [41]. Therefore, the boundary voltage value  $V_{\rm re}$  can be set to be higher than the maximum charging voltage of the 400V EV batteries and lower than the minimum charging voltage of the 800V ones, such as 500V. As a result, the converter operates only in series connection when charging 400V EVs and operates only in parallel connection when charging 800V EVs. With this mechanism, the use of mechanical switches as the auxiliary switches for the re-configuration, such as relays, is possible, which has less cost and lower equivalent conduction resistance. The detailed explanation is as follows.

#### SERIES CONNECTION

When  $S_{\mathrm{aux},1}$  is kept on while  $S_{\mathrm{aux},2,3}$  are maintained off, the negative rail of the upper rectifier is connected with the positive rail of the lower rectifier, making the two secondary side circuits connected in series. This configuration, in principle, enables the converter to supply high output voltage with the utilization of diodes and capacitors with halved voltage rating compared to those of the conventional approach.

#### PARALLEL CONNECTION

When  $S_{\text{aux},1}$  is kept off while  $S_{\text{aux},2,3}$  are maintained on, the positive and negative rails of the two rectifiers are connected in parallel. The parallel connection configuration enables the converter to operate in the low output voltage range with lower current stresses on the components.

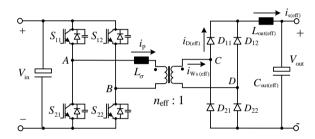

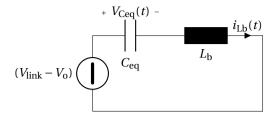

Figure 2.3: The equivalent circuit of Figure 2.2a without the RCD snubber circuits

## **2.2.2.** Comparison between the two structures of the R-PSFB converter

While the primary side H-bridge, transformer, and secondary side rectifier diode bridges are identical, the two different structures shown in Figure 2.2 have differences regarding the output LC filter, the RCD clamping snubber circuitry, and the auxiliary switches.

From the perspective of the component counts, the separate output filter structure has double component counts for the RCD snubber circuitry and LC filter.

However, the separate output filter structure enables the usage of low voltage rating diodes and capacitors for  $D_{\rm RCD}$ ,  $C_{\rm RCD}$  and  $C_{\rm out}$ , whose voltage rating is half compared to that of the joint output filter structure. This is particularly interesting in the EV charging application where the voltage is up to 1000V, as it enables the usage of 1200V or even lower voltage rating diodes for the RCD circuitry, which is much more commercially available and compatible compared to the 1700V diodes that have to be used in the joint output filter structure. From the perspective of cost, components with lower voltage ratings usually have lower costs. Thus the usage of halved voltage rating components counters the double components count.

Additionally, the separate output filter structure has slightly lower current and voltage stress on  $S_{\text{aux},1,2,3}$ . Placing before  $L_{\text{out}}$ ,  $S_{\text{aux},1,2,3}$  in the joint structure need to block the rectifier diode bridge voltage, and the current passing through has the current ripple that is determined by  $L_{\text{out}}$ . In comparison, in the separate structure,  $S_{\text{aux},1,2,3}$  need to block the output voltage, and the current through  $S_{\text{aux},1,2,3}$  in the separate structure

equals the average of that of the joint structure, but without the current ripple. As a result, the separate structure enables the usage of slightly lower current/voltage rating switches for  $S_{\rm aux,1,2,3}$ , or has less conduction loss compared to the joint structure when the same switches are used. The comparison of the current and voltage stresses between the separate and joint structure is summarized in Table 2.1.  $V_{\rm cp}$  represents the clamping voltage determined by the RCD clamping snubber circuitry, which will be further explained in Section V.

|                                           | separate structure | joint structure  |

|-------------------------------------------|--------------------|------------------|

| $V_{\text{stress}}$ of $D_{\text{RCD}}$   | $V_{ m cp}$        | $2V_{\rm cp}$    |

| $V_{\text{stress}}$ of $C_{\text{RCD}}$   | $V_{ m cp}$        | $2V_{ m cp}$     |

| $V_{\text{stress}}$ of $C_{\text{out}}$   | $V_{ m out}/2$     | $V_{ m out}$     |

| $V_{\text{stress}}$ of $S_{\text{aux},1}$ | $V_{ m out}$       | $2V_{ m cp}$     |

| $V_{\rm stress}$ of $S_{\rm aux,2,3}$     | $V_{ m out}/2$     | $V_{ m cp}$      |

| $I_{\rm stress}$ of $S_{\rm aux,1}$       | $I_{ m out}$       | $i_{ m s,jt}$    |

| $I_{\rm stress}$ of $S_{\rm aux,2,3}$     | $I_{ m out}/2$     | $i_{\rm s,jt}/2$ |

Moreover, the separate output filter structure has a better performance clamping the diode voltage on the two secondary sides because the two separate output capacitors help share the output current evenly on the two secondary sides. On the other hand, in the joint filter structure, the diode voltage on the two secondary sides is prone to uneven sharing due to the mismatch of the diode resistance between the two sides. As a result, the joint output filter structure has a higher risk of over-voltage on the diodes.

Last but not least, the separate output filter structure facilitates thermal distribution, as the losses are divided into two parts instead of concentrating on one spot.

In conclusion, in the EV charging application, the halved voltage stress, less current stress, better voltage clamping, and thermal distribution of the separate structure shown in Figure 2.2a prevails over the higher component counts compared to the joint structure shown in Figure 2.2b. The joint structure can be a better candidate in the low power/voltage application, where the usage of the common 650/1200V diodes is possible, and the inductor does not have a severe thermal issue. The r-PSFB converter with the separate output filter and RCD snubber will be further analyzed and designed in this work.

#### 2.2.3. OPERATING PRINCIPLE

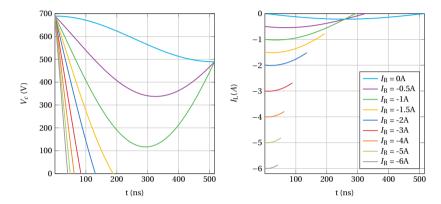

Being either the series or parallel connection configuration, the r-PSFB converter shown in Figure 2.2a can be seen as equivalent to a conventional PSFB with a turns ratio of  $n_{\rm eff}$ : 1, an output inductor  $L_{\rm out(eff)}$ , and an output capacitor  $C_{\rm out(eff)}$ , whose values change for the two configurations. Figure 2.3 shows the schematics of the equivalent conventional PSFB converter of the r-PSFB converter, and Table 2.2 lists the equivalent circuit

parameters for the series and parallel configurations.

| Table 2.2: The circuit | parameters in the equi | ivalent PSFB shown in Figure 2.3 |

|------------------------|------------------------|----------------------------------|

|                        |                        |                                  |

|                         | series connection | parallel connection |

|-------------------------|-------------------|---------------------|

| $S_{\text{aux},1,2,3}$  | 1,0,0             | 0,1,1               |

| $n_{ m eff}$            | n/2               | n                   |

| $L_{out(eff)}$          | $2L_{ m out,sp}$  | $L_{\rm out,sp}/2$  |

| $C_{\mathrm{out(eff)}}$ | $C_{ m out,sp}/2$ | $2C_{ m out,sp}$    |

| $i_{\mathrm{Ws(eff)}}$  | $i_{ m Ws}$       | $2i_{ m Ws}$        |

| $i_{ m D(eff)}$         | $i_{ m D}$        | $2i_{ m D}$         |

| $i_{ m s(eff)}$         | $i_{ m s,sp}$     | $2i_{ m s,sp}$      |

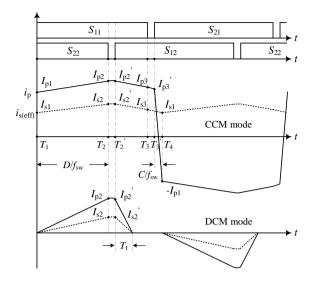

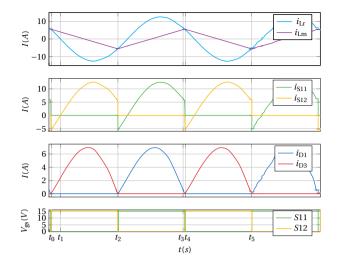

Like the conventional PSFB converter, the r-PSFB converter is typically controlled with fixed switching frequency by phase-shift modulation where the two half-bridge legs are operated with 50% duty cycle. The phase-shift refers to the asynchronization between the operation of the two half-bridge legs. When the phase shift is null, the diagonal pair of transistors ( $S_{11}$  &  $S_{22}$ , or  $S_{12}$  &  $S_{21}$ ) turn on and off synchronously, making the primary side voltage  $v_{AB}$  alternate between  $+V_{in}$  and  $-V_{in}$ , which is equivalent to a bipolar modulation of the H-bridge inverter. When the phase shift is non-null, the synchronization is broken, and the parallel pair of transistors ( $S_{11}$  &  $S_{12}$ ,  $S_{21}$  &  $S_{22}$ ) are able to be kept turned on at the same time, creating a third circuit state that is  $v_{AB} = 0V$ , leading to a controllable unipolor modulation action. Due to the impressed  $i_p$  caused by  $L_\sigma$  and inverter bridge capacitance the switching transition in each half-bridge leg creates a lowered  $di_p/dt$  and  $dv_{AB}/dt$  on the primary side, making the ZVS turn-on possible and lowering the turn-off losses of the transistors. Figure 2.4 shows the typical switching signals and current waveform of the PSFB converter in continuous conduction mode (CCM) and discontinuous conduction mode (DCM).

The operation can be divided into 5 phases: the active phase where the diagonal transistors conduct  $(T_1-T_2)$ ; the reactive phase where the parallel transistors conduct  $(T_2'-T_3)$ ; the commutation phase where the secondary side current commutes among the rectifier diodes  $(T_3'-T_4)$ ; and two transition phases during the dead-time of each bridge  $(T_2-T_2')$  and  $(T_3-T_3')$ . A complete description of the operation of a PSFB converter can be found in [42]. The r-PSFB converter can be modeled in the same way as an equivalent PSFB converter with the relation shown in Table 2.2.

#### 2.2.4. Steady State Analytical Modeling of the R-PSFB Converter

The steady state analytical model of the r-PSFB in CCM and DCM is introduced and verified by simulation in this section. For the simplicity of the circuit analysis, the following assumption is made:

•

$$T_2 = T_2'$$

,  $I_{p2} = I_{p2}'$ ,  $I_{s2} = I_{s2}'$

Figure 2.4: The typical switching signals and current waveform of the PSFB converter in CCM and DCM

•

$$T_3 = T_3'$$

,  $I_{p3} = I_{p3}'$

This is because the transition phases are very short (tens or several hundred nanoseconds) compared to the other three phases. The influence of them on the overall current waveform is therefore negligible.

Firstly, the initial inductor current  $I_{s1}$  can be calculated according to Equation (2.1):

$$I_{\rm s1} = I_{\rm out} - \frac{V_{\rm out}(V_{\rm in(ref)} - V_{\rm out})}{4f_{\rm sw}L_{\rm total(ref)}V_{\rm in(ref)}}$$

(2.1)

Where  $V_{\text{in(ref)}}$  and  $L_{\text{total(ref)}}$  are the reflected input voltage and the total inductance value seen from the secondary side, respectively, and they are calculated by:

$$V_{\rm in(ref)} = V_{\rm in}/n_{\rm eff} \tag{2.2}$$

$$L_{\text{total(ref)}} = L_{\sigma(\text{ref})} + L_{\text{out(eff)}} = L_{\sigma} / n_{\text{eff}}^2 + L_{\text{out(eff)}}$$

(2.3)

If  $I_{s1} \ge 0$ , the converter operates in CCM, otherwise, it works in DCM. In CCM, the duty cycle D is calculated as in  $\ref{eq:commutation}$ , and the commutation cycle C is calculated according to  $\ref{eq:commutation}$ . In DCM, the current starts from zero, thus,  $I_{s1} = 0$ . The duty cycle D in DCM is calculated differently, as Equation (2.8).

With  $I_{\rm s1}$ , D and C calculated,  $I_{\rm s2,3}$  and  $I_{\rm p1,2,3}$  can be determined based on the voltage-second balance on the inductor.  $I_{\rm s2}$  can be calculated by Equation (2.4) for both CCM and DCM operation.

$$I_{s2} = I_{s1} + \frac{D(V_{\text{in(ref)}} - V_{\text{out}})}{2f_{\text{sw}}L_{\text{total(ref)}}}$$

(2.4)

2

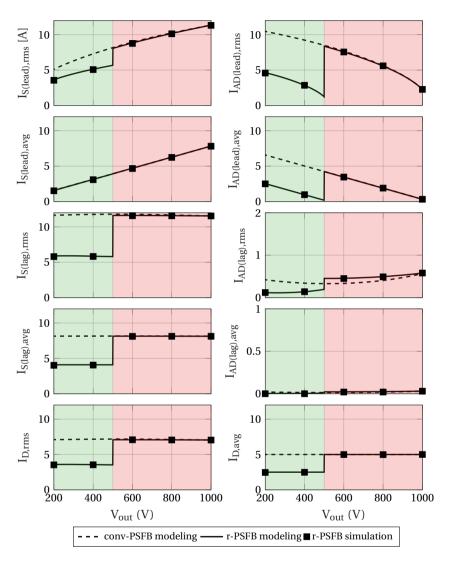

Table 2.3: The closed-form steady state analytical model of the current stresses on the transistors of the r-PSFB converter. Herein, it is assumed that the body diodes of the MOSFETs do not conduct and thus the MOSFET channels process the whole impressed current.

|     |                             | IGBT                                                                                                                   | MOSFET                                                                                                                                 |

|-----|-----------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| CCM | $I_{S(lead),rms}$           | $\sqrt{((I_{\rm s1}^2 + I_{\rm s1}I_{\rm s2} + I_{\rm s2}^2)D + 2I_{\rm s1}^2T_{\rm 02n}f_{\rm sw})/(6n_{\rm eff}^2)}$ | $\sqrt{(-(I_{\rm s2}+I_{\rm s3})(I_{\rm s2}+I_{\rm s1}-I_{\rm s3})C+I_{\rm s1}^2+I_{\rm s2}I_{\rm s1}+I_{\rm s2}^2)/(6n_{\rm eff}^2)}$ |

|     | $I_{\rm S(lead),avg}$       | $((I_{\rm s1}+I_{\rm s2})D+2I_{\rm s1}T_{\rm 02n}f_{\rm sw})/(4n_{\rm eff})$                                           | $((2C+2D-1)I_{s1}+(C+2D-1)I_{s2}-CI_{s3})/(4n_{eff})$                                                                                  |

|     | $I_{\mathrm{AD(lead),rms}}$ | $\sqrt{((1-D-C)(I_{\rm s1}^2+I_{\rm s2}^2+I_{\rm s1}I_{\rm s2})+2f_{\rm sw}I_{\rm s3}^2T_{\rm p20})/(6n_{\rm eff}^2)}$ | 0                                                                                                                                      |

|     | $I_{\mathrm{AD(lead),avg}}$ | $((1-D-C)(I_{\rm s1}+I_{\rm s2})+2f_{\rm sw}I_{\rm s3}T_{\rm p20})/(4n_{\rm eff})$                                     | 0                                                                                                                                      |

|     | $I_{\rm S(lagg),rms}$       | $\sqrt{((2f_{\rm sw}T_{\rm 02n}-1C+1)I_{\rm sl}^2-I_{\rm sl}(C-1)I_{\rm s2}-I_{\rm s2}^2(C-1))/(6n_{\rm eff}^2)}$      | $\sqrt{(-(I_{\rm s2}+I_{\rm s3})(I_{\rm s2}+I_{\rm s1}-I_{\rm s3})C+I_{\rm s1}^2+I_{\rm s2}I_{\rm s1}+I_{\rm s2}^2)/(6n_{\rm eff}^2)}$ |

|     | $I_{\rm S(lagg),avg}$       | $((2f_{\text{sw}}T_{02n}-C+1)I_{\text{s1}}-I_{\text{s2}}(C-1))/(4n_{\text{eff}})$                                      | $(-CI_{\rm s2}-CI_{\rm s3}+I_{\rm s1}+I_{\rm s2})/(4n_{\rm eff})$                                                                      |

|     | $I_{\mathrm{AD(lagg),rms}}$ | $\sqrt{f_{ m sw}I_{ m s3}^2T_{ m p20}/(3n_{ m eff}^2)}$                                                                | 0                                                                                                                                      |

|     | $I_{\rm AD(lagg),avg}$      | $f_{\rm sw}I_{\rm s3}T_{ m p20}/(2n_{ m eff})$                                                                         | 0                                                                                                                                      |

| DCM | $I_{S(lead),rms}$           | $\sqrt{I_{ m s2}^2D/(6n_{ m eff}^2)}$                                                                                  | $\sqrt{I_{\rm s2}^2(2f_{\rm sw}T_{\rm f}+D)/(6n_{ m eff}^2)}$                                                                          |

|     | $I_{\rm S(lead),avg}$       | $I_{\rm s2}D/(4n_{ m eff})$                                                                                            | $I_{\rm s2}(-2f_{\rm sw}T_{\rm f}+D)/(4n_{\rm eff})$                                                                                   |

|     | $I_{\mathrm{AD(lead),rms}}$ | $\sqrt{f_{ m sw}} I_{ m s2}^2 T_{ m f}/(3n_{ m eff}^2)$                                                                | 0                                                                                                                                      |

|     | $I_{\mathrm{AD(lead),avg}}$ | $f_{\rm sw}I_{ m s2}T_{ m f}/(2n_{ m eff})$                                                                            | 0                                                                                                                                      |

|     | $I_{\rm S(lagg),rms}$       | $\sqrt{I_{\rm s2}^2(2f_{\rm sw}T_{\rm f}+D)/(6n_{\rm eff}^2)}$                                                         | $\sqrt{I_{\rm s2}^2(2f_{\rm sw}T_{\rm f}+D)/(6n_{ m eff}^2)}$                                                                          |

|     | $I_{\rm S(lagg),avg}$       | $I_{\rm s2}(2f_{\rm sw}T_{\rm f}+D)/(4n_{\rm eff})$                                                                    | $I_{\rm s2}(2f_{\rm sw}T_{\rm f}+D)/(4n_{\rm eff})$                                                                                    |

|     | $I_{\mathrm{AD(lagg),rms}}$ | 0                                                                                                                      | 0                                                                                                                                      |

|     | $I_{\mathrm{AD(lagg),avg}}$ | 0                                                                                                                      | 0                                                                                                                                      |

$$D^{\text{DCM}} = 2\sqrt{\frac{I_{\text{out}}V_{\text{out}}f_{\text{sw}}L_{\text{total(ref)}}}{V_{\text{in(ref)}}(V_{\text{out}} - V_{\text{in(ref)}})}}$$

(2.8)

$$T_{\rm p20,02n} = I_{\rm p3,p1} \cdot L_{\sigma} / V_{\rm in}$$

(2.9)

$$T_{\rm f} = I_{\rm s2} \cdot L_{\rm total(ref)} / V_{\rm out} \tag{2.10}$$

The effective rms and average current stress on the secondary side diodes  $I_{D,rms/avg(eff)}$  can be calculated by Equations (2.11) to (2.13). Depending on the configuration, the actual diode current stress can be calculated from the effective value based on Table 2.2.

$$I_{\text{D,rms(eff)}}^{\text{CCM}} = \sqrt{(1-C)(I_{\text{s2}}^2 + I_{\text{s1}}I_{\text{s2}}) + CI_{\text{s3}}^2 + I_{\text{s1}}^2/6}$$

(2.11)

$$I_{\text{D,rms(eff)}}^{\text{DCM}} = \sqrt{I_{\text{s2}}^2 (2f_{\text{sw}}T_{\text{f}} + D^{\text{DCM}})/6}$$

(2.12)

$$I_{\text{D,avg(eff)}} = I_{\text{out}}/2 \tag{2.13}$$

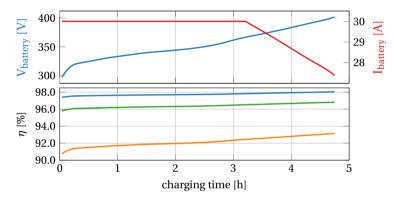

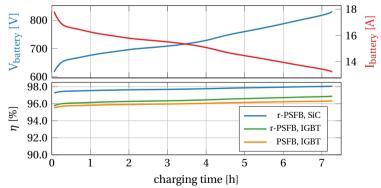

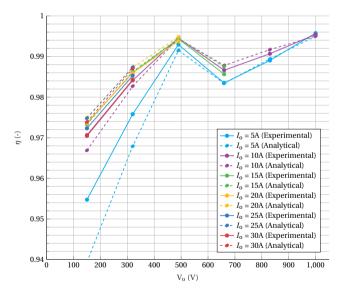

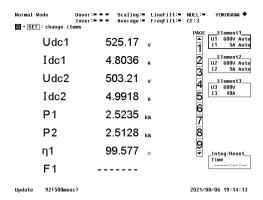

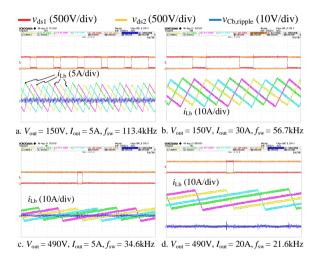

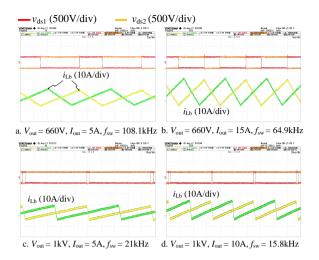

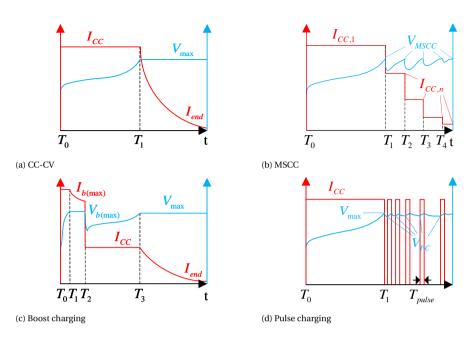

The rms current stress on the primary winding of the transformer,  $I_{Wp,rms}$ , can be calculated based on Equations (2.14) and (2.15) in CCM and DCM operation respectively.