# Low cost precision Vds current sensing

Arthur Admiraal

# Low cost precision Vds current sensing

Author: Arthur Admiraal

Project duration: October 1, 2022 - December 9, 2024

Supervisor: Prof. Dr. Ir. Qinwen Fan

Thesis committee: Prof. Dr. Ir. Qinwen Fan

Prof. Dr. Ir. Aditya Shekhar

Ir. Anton Montagne

In partial fulfilment of the requirements for the degree of

**Master of Science**

in Electrical Engineering

at the Delft University of Technology.

An electronic copy of this thesis is available at <https://repository.tudelft.nl/>.

# Contents

|                                                                                                        |            |

|--------------------------------------------------------------------------------------------------------|------------|

| <b>Abstract</b>                                                                                        | <b>ii</b>  |

| <b>Acknowledgements</b>                                                                                | <b>iii</b> |

| <b>1 Introduction</b>                                                                                  | <b>1</b>   |

| 1.1 Background . . . . .                                                                               | 1          |

| 1.2 This work . . . . .                                                                                | 5          |

| <b>2 Errors in Vds sensing</b>                                                                         | <b>7</b>   |

| 2.1 Error model . . . . .                                                                              | 7          |

| 2.2 Sources of error . . . . .                                                                         | 8          |

| 2.3 Conclusion . . . . .                                                                               | 14         |

| <b>3 Architecture design</b>                                                                           | <b>15</b>  |

| 3.1 Choice of error suppression method . . . . .                                                       | 15         |

| 3.2 Choice of detector . . . . .                                                                       | 18         |

| 3.3 Injected current signal shape . . . . .                                                            | 20         |

| 3.4 Current injection method . . . . .                                                                 | 27         |

| 3.5 Topology . . . . .                                                                                 | 30         |

| 3.6 Dimensioning . . . . .                                                                             | 31         |

| 3.7 Operation . . . . .                                                                                | 32         |

| <b>4 Verification</b>                                                                                  | <b>34</b>  |

| 4.1 Methods . . . . .                                                                                  | 34         |

| 4.2 Experimental results . . . . .                                                                     | 35         |

| <b>5 Conclusion</b>                                                                                    | <b>39</b>  |

| <b>Bibliography</b>                                                                                    | <b>40</b>  |

| <b>A Selected derivations</b>                                                                          | <b>44</b>  |

| A.1 Small-signal source resistance acts as drain resistance in triode region . . . . .                 | 44         |

| A.2 The error due to temperature ramps has an upper bound . . . . .                                    | 44         |

| A.3 The variation in the resistance is slow compared to the measurement period . . . . .               | 45         |

| A.4 It is always possible to construct a signal orthogonal to any polynomial of a given order. . . . . | 45         |

| A.5 Resistive current injection does not significantly degrade interference robustness . . . . .       | 46         |

# Abstract

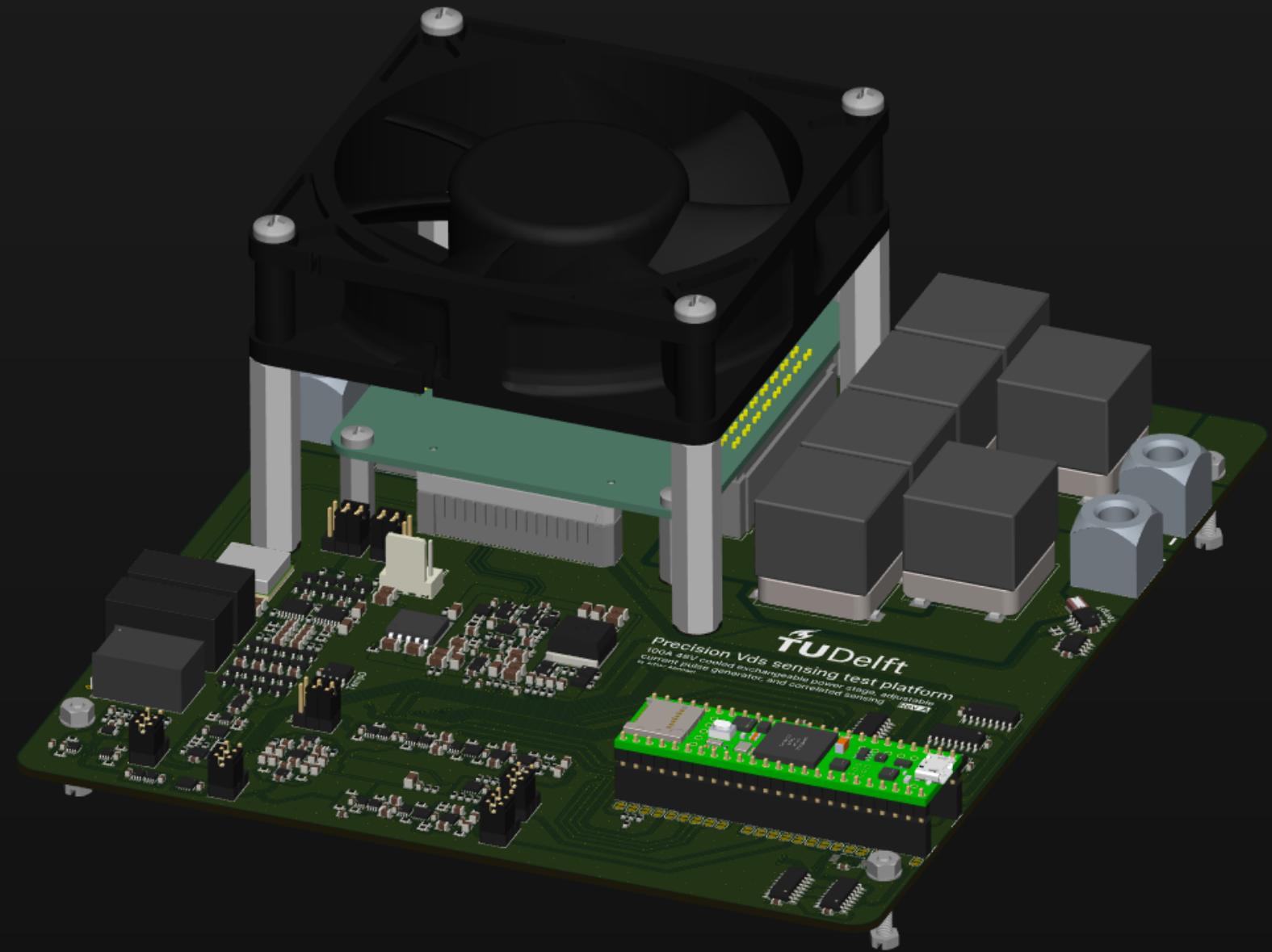

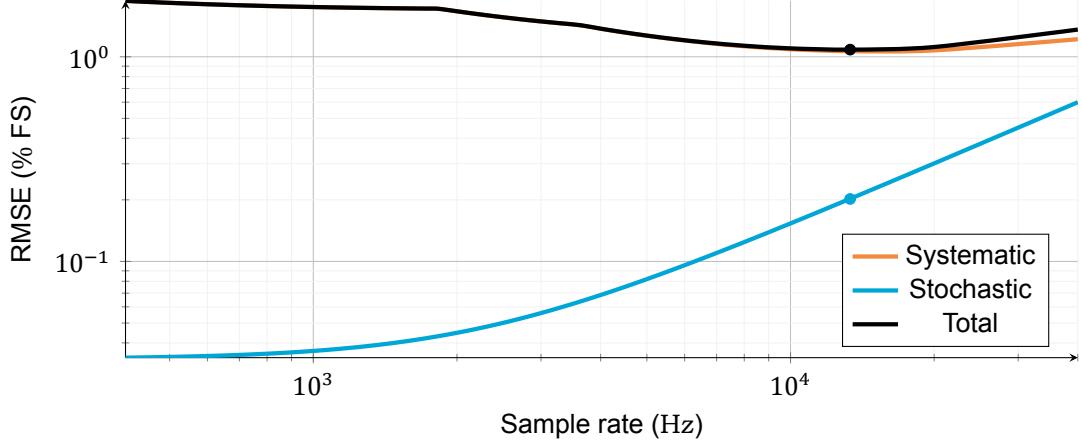

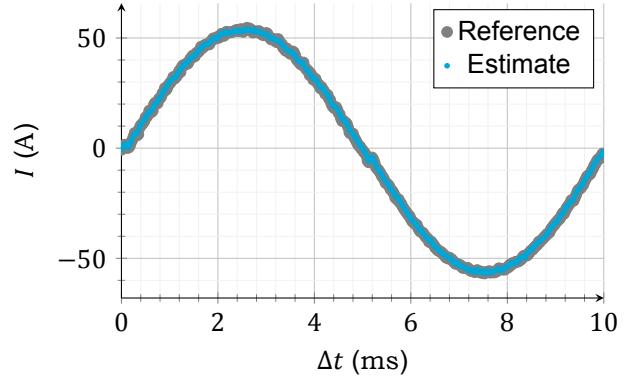

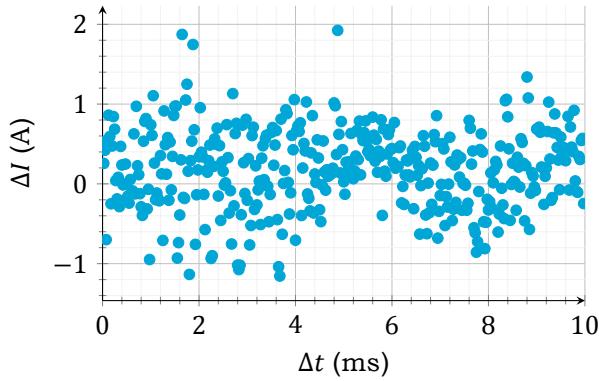

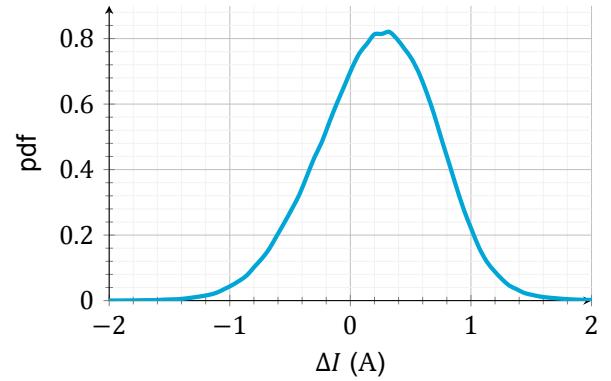

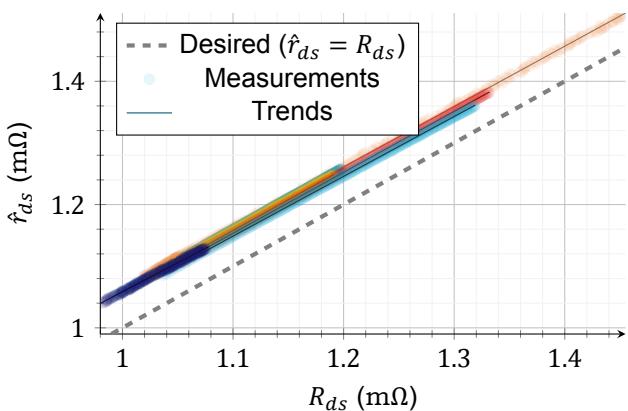

$V_{ds}$  current sensing has the potential to improve power density, efficiency, and cost compared to conventional current sensing methods by removing the need for a dedicated (quasi-)lossy sensing device. However, achieving high precision requires a temperature compensation method that has traditionally come at the expense of flexibility, test cost, or power density. This work proposes an online calibration method based on small signal resistance measurement through the periodic injection of small submicrosecond current pulses that are orthogonal to the load current. This provides an estimate of the large signal resistance that is insensitive to manufacturing tolerance and device type. Furthermore, junction temperature can be simultaneously estimated from the resistance variation. With 129 mW injection power, the method achieves 0.54 A RMS single point calibrated current error over a  $\pm 54$  A range on a 48 V single phase experimental platform. Since all circuitry is connected parallel to the power stage, the method is suited to integration into a smart gate driver IC.

# Acknowledgements

In October 2022, I started on the final leg of my journey to completing my Master's degree. Little did I know that it would take over two years to arrive at my destination, during which time I would meet a partner, see my company turn from a scrappy student team to a professional organisation, and deal with a fire that nearly burnt it all down. Hence, I am indebted to a great many people for their support and encouragement that helped complete this work.

First of, I would like to express my deepest gratitude to my supervisor Prof. Dr. Ir. Qinwen Fan, whose guidance motivated me to push beyond what I thought possible and whose flexibility helped me keep advancing towards my goals, even in challenging and unforeseen circumstances. Beyond her academic support, I will also cherish the discovery of Rotterdam's best hot-pot restaurant on a team trip she led—a delicious bonus to my research journey.

Second, I am grateful to the members of the defense committee, who were not only kind of enough to offer their time, but were also gracious enough to offer access to their lab equipment (in the case of Prof Dr. Ir. Aditya Shekhar) and give detailed feedback on my work, pushing me to be more creative (in the case of Ir. Anton Montagne).

I would also like to extend my sincere thanks to Prof. Dr. Ir. Kofi Makinwa for his encouragement in pursuing this work when I first had the idea, to my colleagues at Lobster for their kind understanding and less kind but effective ideas to motivate me, and to the ever-suffering technicians, system administrators, and workshop supervisors for their patience with my requests, in particular the kind people of DEMO for turning a cheese storage box into a sophisticated high voltage protection enclosure.

Finally, I want to acknowledge those who are closest to me. My heartfelt thanks go to my parents for their patience and support, and to my girlfriend who was always there for me.

Thank you all, I could not have done it without you.

Arthur Admiraal

Delft, Netherlands

December 2024

# Introduction

## 1.1. Background

### 1.1.1. Driving small electric motors

The compactness, controllability, and low cost of small electric motors have enabled diverse applications, from cordless power tools and Light Electric Vehicles (LEVs) (e.g., e-bikes) to Unmanned Aerial Vehicles (UAVs) and lightweight robotics. Their low weight and size reduce strain in handheld uses and improve performance in mobile applications, where battery power is common. Smaller, lighter components further compound these advantages.

Industry has focussed on Brushless DC (BLDC) motors [1, 2], a type of Permanent Magnet Synchronous Motor (PMSM), due to their high torque density, efficiency, and reliability at a low cost [3, 4]. These motors rely on three-phase currents in stator windings, producing a rotating magnetic field that guides rotor magnets. This field, shaped by magnetic materials, creates a significant winding inductance of generally  $10 \mu\text{H}$  to  $1 \text{mH}$ . Although nonlinear and rotor-dependent, this inductance largely limits the motor's electrical dynamics, while the rotor motion induces a back-EMF voltage in the windings.

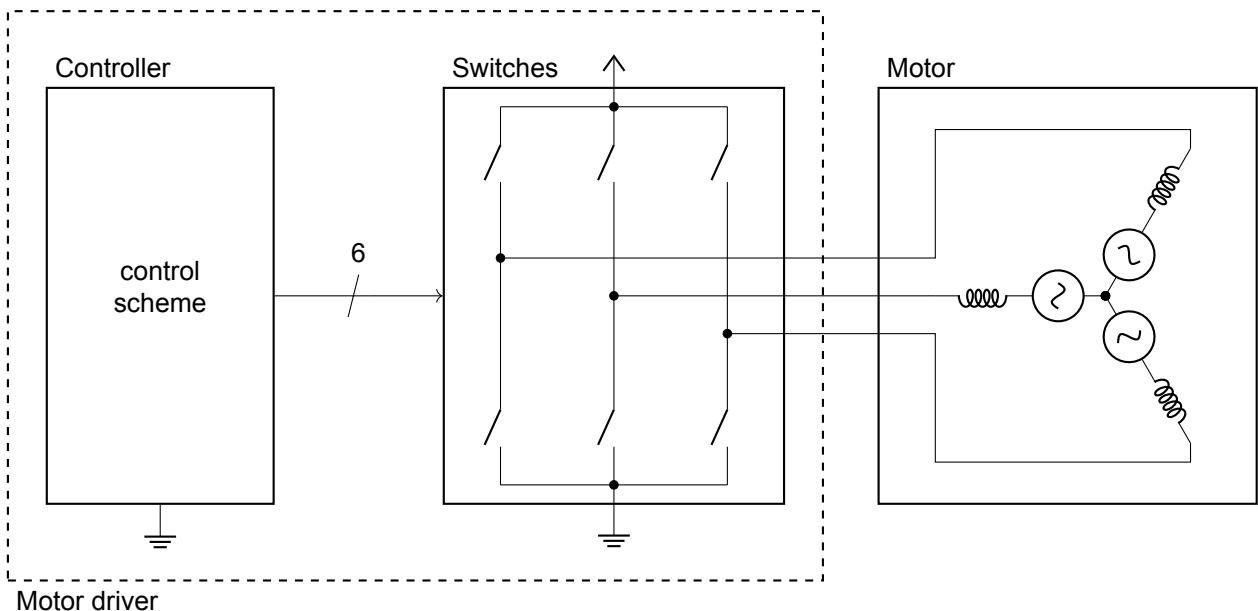

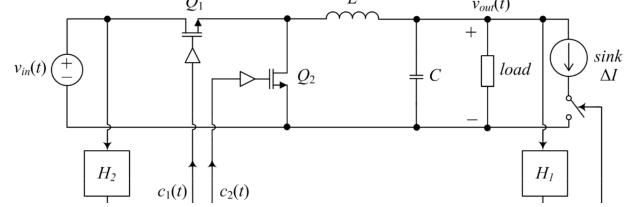

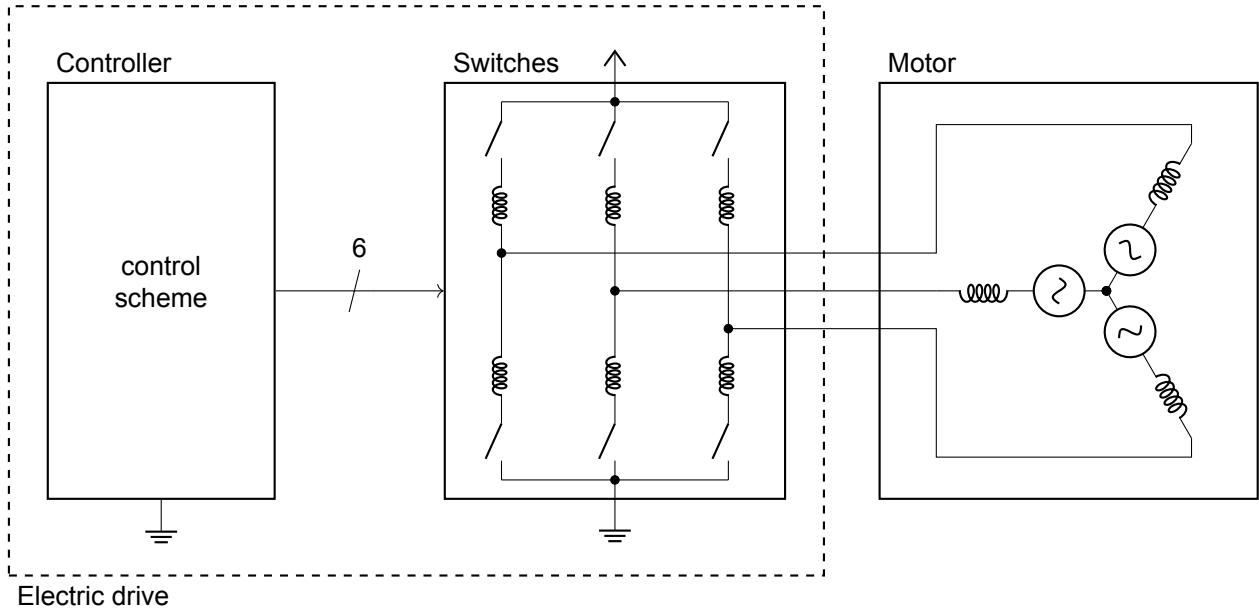

BLDC motors require current at variable frequencies (usually up to  $2 \text{ kHz}$ ) and thus depend on motor drivers to manage power flow from a DC bus (mainly up to  $50 \text{ V}$ ). High power density and a low price are common goals [1] as is high efficiency, which extends battery life and reduces the need for bulky cooling systems [5, 6]. Typically, they comprise three inverters feeding the motor phases and a control system that manages switching, as shown in figure 1.1. Though many motor drivers are filterless, having a direct connection from the inverters to the motor, an additional output filter may be used to reduce the ripple current flowing into the motor.

Figure 1.1: Typical motor driver system

Current sensing is essential for motor control and protection. It provides real-time feedback on the motor's operating state, allowing precise adjustment of torque and speed. By continuously monitoring and correcting the current, the control scheme can achieve precise motion control. This requires a low error, with typical Root Mean Squared

Errors (RMSEs) of at most 2 % of full scale. Current sensing is also used to detect faults such as short circuits, which protects both the motor and its driver from potential damage.

### 1.1.2. Discrete current sensing

Many approaches to current sensing have been developed [7, 8, 9], though some are more commonly applied than others. Traditionally, dedicated discrete components play a key role.

Shunt resistors are widely used. They are based on Ohm's law: the current is passed through a known shunt resistance, creating a voltage that is proportional to the current. To limit power loss, the shunt resistance is kept very low - typically in the  $\text{m}\Omega$  range. This results in low signal swings that are scaled up for further processing, often by so-called current sense amplifiers.

Usually, the shunt resistors are not put inline with the output phases and there are fewer shunt resistors than phases. Instead, the shunt resistors are placed at some of the lower legs of the inverters. This saves cost by decreasing the amount of components and reducing the common mode swing requirements on the current sense amplifiers [10, 11]. Since the motor has three connections, one phase current can be fully reconstructed using measurements of two other phases. With slight modifications of the modulation, phase currents may also be reconstructed through sequential measurements of a single bus return current measurement [12].

Another approach to current sensing relies on measuring the magnetic field that forms around currents. In current transformers, the field induces a voltage in a secondary winding wrapped around a high magnetic permeability core that is placed around the current-carrying wire. Since only dynamic fields induce voltages, this technique does not pick up DC currents. Alternatively, strategically placed Hall effect sensors can be used to directly measure the fields and distinguish both DC and AC current. These magnetic field-based methods avoid the inherent power loss of shunt resistors, making them effectively "lossless" while also naturally rejecting common-mode voltage swings. The galvanic isolation is also often noted as an advantage, but is not relevant to low voltage systems. Though more complex and costly than shunt resistors, they offer a viable alternative in certain applications.

Table 1.1: For a 50 A peak 48 V power stage based on the DRV8302, traditional current sensing methods come with significant cost factors.

| Device                | Hall sensor [13]                       | Current transformer [14]                   | Leg shunt resistor [15]                  |

|-----------------------|----------------------------------------|--------------------------------------------|------------------------------------------|

| Price at 1k quantity  | €1.74                                  | €2.14                                      | €0.20                                    |

| Size                  | $6 \times 4.9 \times 1.6 \text{ mm}^3$ | $12.8 \times 20.5 \times 7.5 \text{ mm}^3$ | $1.5 \times 3.1 \times 0.5 \text{ mm}^3$ |

| Power loss            | 625 mW                                 | 625 mW                                     | 469 mW                                   |

| Total error (typical) | $\pm 1.0 \text{ A}$                    | Unspecified                                | $\pm 1.5 \text{ A}$                      |

As tabulated in table 1.1 each of these current sensing methods come with a cost in terms of power dissipation, area, capital, and complexity. First, there are the direct costs. Each discrete component comes with procurement and assembly costs. The inherent losses of shunt resistors come with a significant area requirement for adequate power dissipation. Furthermore, structures with the required electromagnetic coupling for magnetic current sensing tend to be bulky. Yet, the indirect costs may be more significant. Though the magnetic sensors are not inherently lossy, they do require the diversion of the flow of current through a structure with the appropriate electromagnetic properties. This indirectly forces additional power consumption in the parasitic resistance of the added wire length and thus makes these methods only quasi-lossless. Similarly, as devices move towards higher frequency operation the parasitic inductance of shunt resistors can require the adoption of more complex driving circuitry that is robust to the associated ground bounce [16]. In a practical sense, all of these methods are invasive, having to be accommodated by additional routing in-line with the current.

### 1.1.3. The desire for integration and its limits

Significant advances have been made in the efficiency, power density, and cost-effectiveness of motor drivers. Though much of this improvement has been driven by advances in switching devices, integration has also been recognised as a powerful tool to achieve these goals [17].

Yet, this integration has not always been realised. At high currents, switching devices are often not integrated. They tend to be manufactured using specialised processes that are not compatible with monolithic integration. Furthermore, the flexibility in the selection of the switching device is used to make an appropriate tradeoff of efficiency, size, and cost for the target application.

Instead, there has been a trend to integrating everything but the switching devices. Some commercial products integrate high and low side gate drivers, adjustable dead-time, overcurrent protection, precision current sense amplifiers, and a low-voltage supply for digital control circuitry [18]. Recent developments in smart-gate drivers have seen further integration of slew rate control circuitry, dead-time optimisation, and intelligent protection features that optimise efficiency and enable the removal of external damping components [19, 20].

Despite this trend, current sensing has usually been integrated to a limited extent. At high current levels, parasitics of common packages and process nodes form a barrier to the efficient conduction of the load current. The added parasitics of routing these currents from the power stage to gate drivers poses an additional challenge. Hence, though current sense amplifiers and inprecise overcurrent protection have long been a part of many gate drivers, invasive external components have traditionally been required to achieve a fidelity that is suitable for closed-loop motor control.

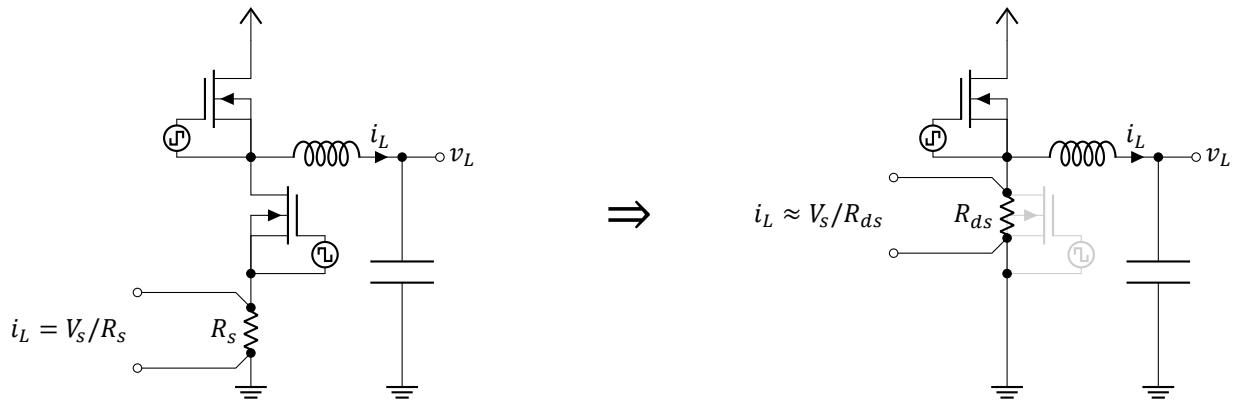

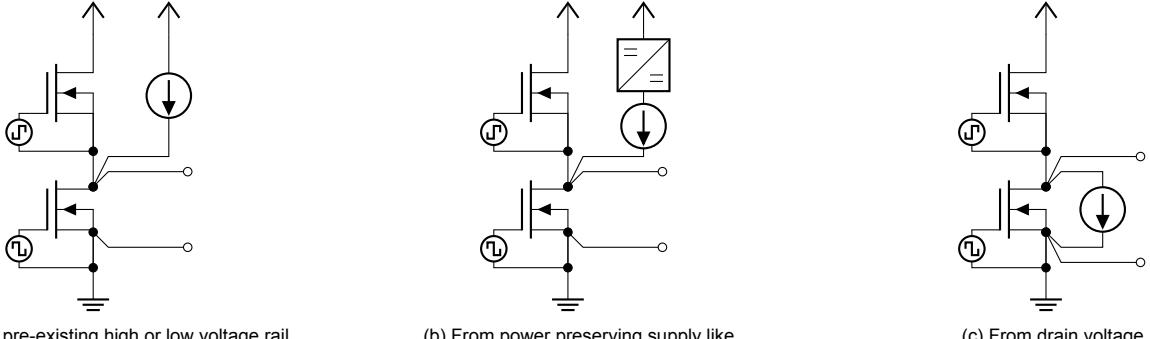

#### 1.1.4. The potential and challenge of $V_{ds}$ sensing

$V_{ds}$ -based current sensing is a promising technique for enabling tighter integration of current sensing within smart gate drivers. As illustrated in figure 1.2, it involves using the parasitic resistance of the switching device as a shunt resistor so that the drain source voltage  $V_{ds}$  is taken to be proportional to the current. Since the sensing circuitry is in parallel to the power path and thus does not need to conduct the load current, integration into standard processes becomes viable. There is also the advantage of a higher signal swing, since a greater portion of the power budget is usually dedicated to losses in the switching device. Though this method shares the disadvantage of leg shunts that the current measurement must be performed in a limited window, three sensors are sufficient to fully reconstruct the phase currents, even at full modulation.

Figure 1.2:  $V_{ds}$  sensing uses the parasitic on-state resistance to estimate output current.

$V_{ds}$  sensing comes with several challenges. One challenge is that the sensing circuitry must tolerate the large voltage swings at the switching node [21], which may overshoot the rails by up to 30 % of the bus voltage. However, the more fundamental challenge is that the parasitic resistance depends strongly on temperature and, to a lesser extent, on other environmental conditions. This has given  $V_{ds}$  sensing a reputation of low accuracy [9, 8]. Several solutions can be considered, which will now be discussed.

#### Compensation-based techniques

Compensation-based techniques are based on the subtraction of an estimate of the error, thus correcting for the known component of the error. The advantage of these methods is that the error estimate can be derived from readily available or easily measurable information. However, their effectiveness is limited by the accuracy of the underlying model; unmodeled effects can significantly exacerbate errors. Notably, most of the approaches considered here fail to account for the degradation of the switching device, which can reach up to 20 % according to [21]. This omission raises concerns about the robustness of these methods.

**Replica sensing** Perhaps the most complete model of a switching device is a copy of it. In replica current sensing, this idea is exploited by measuring the current through a scaled-down copy of the switching device with equal terminal voltages and in close proximity to the switching device. Since the devices are in close proximity, their temperatures are matched. As the replica copies all aspects of the device, it also compensates for other errors such as production tolerance and nonlinearity.

This idea has been widely applied in integrated circuits, where the voltage over the power and sensing devices are usually equalised using feedback at the drain [22, 23, 24, 25]. With discrete switches in higher power applications, accuracy is often traded for simplicity by sensing the voltage over a shunt resistor at the source, though feedback at the source has also been described [26, 27].

The accuracy of this method is limited by matching, at  $\approx \pm 3\%$  in power semiconductors [26, 28, 29]. An advantage is that the method is in principle robust to degradation, which affects both the main switching device and replica.

Adoption is hampered by the increased cost and restriction of design freedom to a limited set of specialised devices [8].

**Using a separate structure** Co-integrated and thus closely thermally coupled temperature sensors have been used to implement linear temperature compensation. Total errors of 3% [30] and 5% [29] have been reported. Like replica sensing, these structures are only found in specialised devices, limit flexibility and come with inherent costs.

**Case temperature compensation** Measurements of the case temperature may be combined with  $V_{DS}$  measurements and models of the switch behaviour to estimate the device temperature. In [31], models of the temperature dependence of the channel resistance, the thermal resistance of the case, and power losses of the switch are iteratively applied to find the junction temperature, resulting in a  $3\sigma$  error of 1.5% in steady state for static loads and case temperature rises of 15 °C.

The advantage of this method is that no specialised devices are required. Though a temperature sensor must be included, this is already found on many motor drivers for temperature monitoring. A disadvantage is that extensive testing must be performed to find the 6 model coefficients. Given that production tolerances may mean these coefficients are substantially different between devices, slow and thus expensive factory thermal characterisation may be needed. Initially gathering these coefficients will also increase development time. Given that dynamics were not modelled, this issue will become more severe if the method is adapted to dynamic loads, such as those found in motor drivers.

**Using Temperature Sensitive Electrical Parameters** The large body of work on estimating the junction temperature from electrical parameters of switching devices could provide another path towards die temperature compensation in ordinary devices, though no applications to  $V_{DS}$  sensing are known to the author. Apart from on-resistance, commonly investigated Temperature Sensitive Electrical Parameters (TSEPs) include gate leakage current, gate resistance, threshold voltage, and switching delay times [32, 33]. A potential problem is that the available well-behaved TSEPs vary by device type. Furthermore, measuring the die temperature is only half the battle. The connection of the die to the circuit board has been shown to be a major contributor to the resistance of Insulated-Gate Bipolar Transistors (IGBTs) devices whilst not closely tracking the die temperature [34]. It may be possible to predict this temperature using a thermal model, though this would increase the calibration requirements for the system.

### Feedback-based techniques

Feedback-based techniques are based on the subtraction of the measured error. The advantage of these approaches is that it can correct errors that are not easily predicted. However, the downside is that it requires a measurement of the error, which may not be straightforward. Case in point, the resistance is not in itself an electrical signal, and can thus only be measured from its response to a signal. This could be the current resulting from an applied voltage or the voltage resulting from an applied current. Applying a voltage requires a lower impedance source than the parasitic resistance of the switch, but this is usually not practical in a power stage, which requires a low parasitic resistance to reduce losses. Applying a current requires a higher impedance source than the parasitic resistance, and is thus a good fit.

Several approaches for measurements based on injecting such a test current will now be discussed.

**Through an alternate measurement of the load current** One option is to turn the load current in a known test current through a separate measurement of it. The resistance may then be calculated using Ohm's law. The main proponents of this technique make the measurement by diverting the current through an alternate path that has a current sensing resistor [35], as illustrated in figure 1.3a. Since the calibration measurement is made very infrequently, this enables the measurement circuitry to be optimised for small size and cost.

Since an alternate path is used for the measurement, the current and voltage measurements do not occur at the same instant. This introduces an error, especially since the change in resistance due to the measurement path will cause a disturbance in the current. [35] introduces a scheme that suppresses this error to below 1 % but depends on the stability of the load over several cycles. Better transient performance may be attainable when the alternate path is only enabled for a part of the switching cycle, as in [36].

The advantage of this method is the large signal swing provided by the use of the load current. The downside is that even for low duty cycles, an alternate path still comes at a significant cost in high-current systems.

(a) The load current that normally flows through Q2 can be measured while flowing through the alternate path through Q3 [35].

(b) A small test current can be injected at the output [37].

Figure 1.3: Resistance measurement options

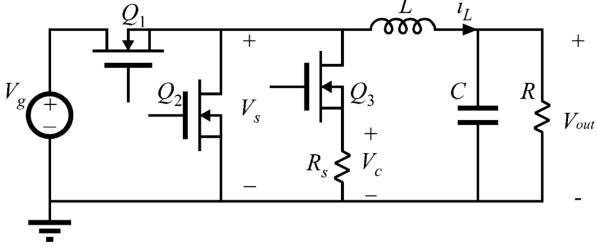

**Through a known feature of the current** If some feature of the load current signal is known, this could serve as the test current. For example, though the bulk current may be unknown, a high-frequency component may have known characteristics. Though this approach has not yet been explored in the context of Vds sensing, the idea has often been applied in Voltage Regulator Modules (VRMs) [38, 39]. Alternatively, though the instantaneous values may not be known, the statistical behaviour of the signal may be known. In motor drivers, such a feature may exist in the ripple current, given by:

$$\frac{\partial i}{\partial t} = \frac{V_{\text{applied}} - V_{\text{bemf}}}{L} \Rightarrow \Delta \frac{\partial i}{\partial t} = \frac{V_s - V_{\text{bemf}}}{L} - \frac{0 - V_{\text{bemf}}}{L} = \frac{V_s}{L}$$

Though the rising and falling ramp rate of the current depends on the back-emf, the difference between them depends only on the supply voltage and inductance. If the inductance is known, this may be used to predict this ramp rate, which may then serve as a test signal to find the current.

The advantages of this method are that it does not require circuitry to divert current from the switch whilst still providing a sizeable signal swing. The downside is that the accuracy is low, as the inductance has significant manufacturing tolerance and may vary due to the nonlinearity of the magnetics.

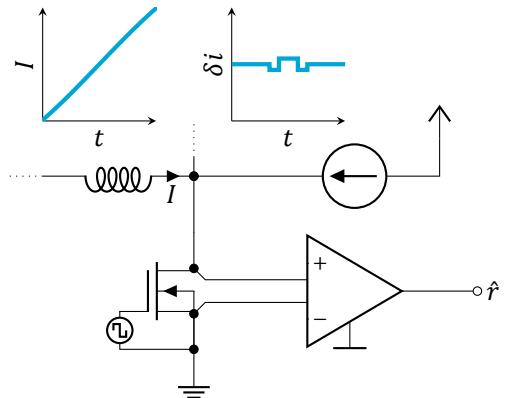

**Through an injected reference feature** If the load current does not contain a known feature, such a feature can be purposefully added by the injection of a current. This current should be small to prevent high power dissipation and significant heating of the switching device. It should also have a high enough frequency not to be shorted by the inductance but a low enough frequency not to be shorted by the parasitic capacitance. Furthermore, it should be possible to distinguish the current from the bulk current.

The advantage of this method is that the measurement process can be tightly controlled, but the disadvantage is that the signal swing is dependent on the size of the current feature that can be generated.

The test current could be injected before or after the output filter. Injection after the filter has been discussed [37, 40], as illustrated in figure 1.3b. An advantage of this method is the low voltage swing, easing requirements on the current source. The disadvantage is that the filter also affects the measurement, giving a low update rate. This technique is not applicable to filterless motor drivers.

Another design option that merits further investigation is the injection of a small current at the switching node, directly into the channel resistance. Compared to injection after the filter, this offers a higher update rate but comes at the expense of higher requirements on the current source. It also offers compatibility with filterless motor drivers. Though it has not been applied in the context of Vds sensing, injection directly into shunt resistors has been explored in accuracy monitoring of energy meters [41], where 0.1 % performance was achieved through measuring the response to an out-of-band pilot tone. Similarly to Vds sensing, the measurement was performed while the load flowed through the shunt resistor. Dissimilarly, the dynamics were significantly slower and the shunt resistor was continually connected, enabling long integration periods. Recently, a similar idea was used for self-calibration of trace shunt resistors [42], which achieved 0.2 % gain error but did so with the load unconnected for long integration times. Though there are big differences between these applications and Vds sensing, they show the potential of this method.

## Conclusion

Compensation-based methods have not yet shown sufficient fidelity for use in motor drivers. Even if the error could be reduced, they inherently come with limited flexibility, expensive integration, or a large characterisation effort. Feedback-based approaches show promising performance, but existing injection methods have been costly, inaccurate, or too slow for Vds sensing. Yet, this is not a fundamental limitation. The rapid injection of current pulses at the switching node has not yet been explored and has the potential to reduce the cost of feedback-based Vds sensing.

## 1.2. This work

So far, Vds sensing has not delivered on its promise of precision current sensing at a low cost, preventing integration into smart gate drivers. Existing methods do not achieve the required performance, or rely on the addition of costly

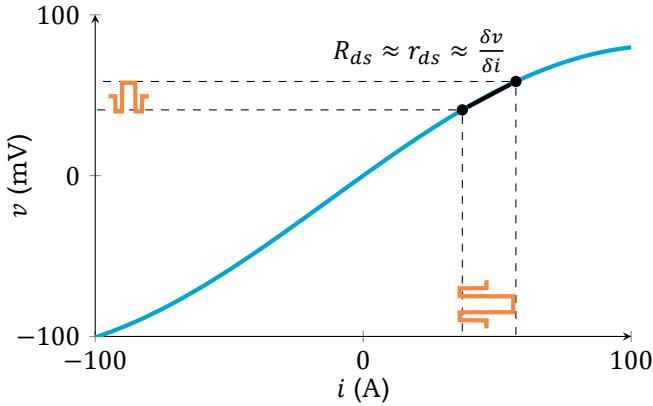

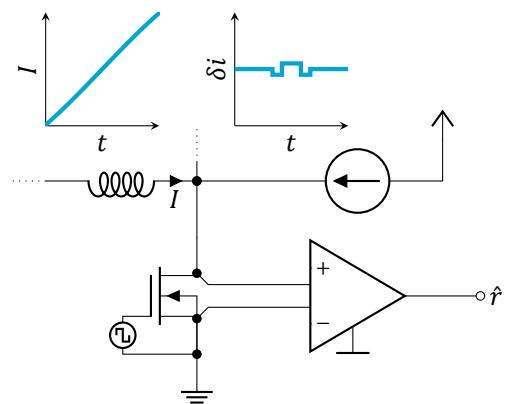

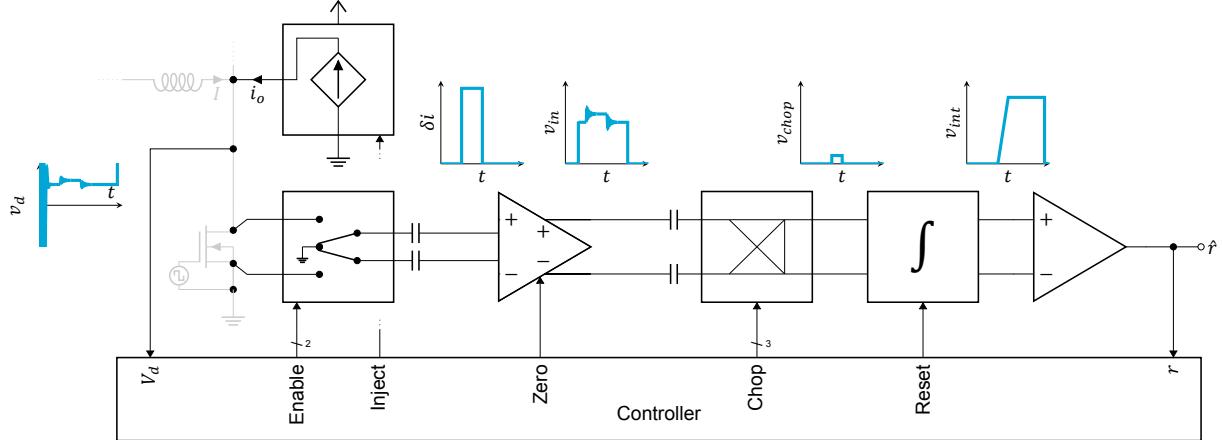

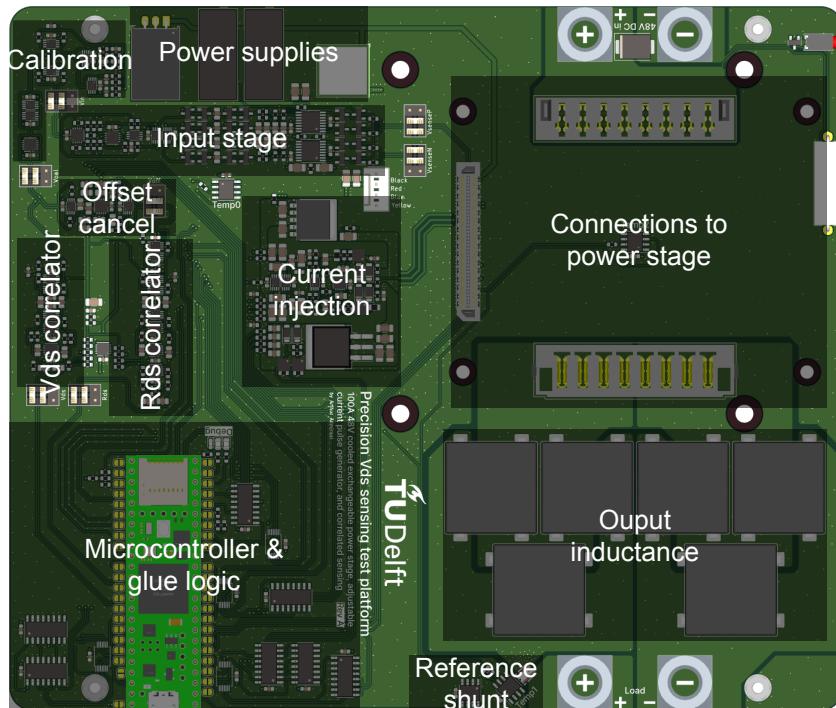

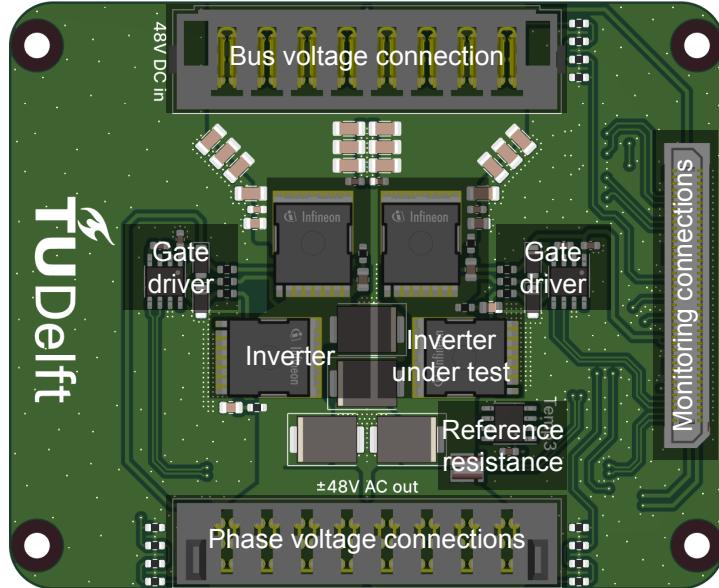

production processes and/or components. The goal of this thesis is to assess to what extent the cost to performance ratio of  $V_{ds}$  sensing may be improved with measurement of the small-signal resistance through the injection of small currents at the switching node, as illustrated in figure 1.4.

(a)  $R_{ds}$  is estimated from  $r_{ds}$  measurement through a small injected current  $\delta i$ .

(b) The measurement path is in parallel to the power path.

Figure 1.4: The big idea is to estimate the current  $I$  from the drain-source voltage  $V$  through online measurement of the small-signal resistance.

First, chapter 2 provides an error analysis that informs what errors need suppression. Then, chapter 3 will build upon this to motivate that linear online calibration is sufficient to achieve 2 % error, provided that a sufficient update rate is chosen. It will also argue that an architecture based on correlation processing and the injection of down-up-up-down pulses by a linear current source achieves a precision within 6 dB of the optimum while minimising cost factors. Furthermore, it will show that the architecture is insensitive to the most significant nonidealities through modelling their error. Chapter 4 describes a test platform in PCBA technology that achieves a 1 % RMSE while experiencing a 20 % shift in channel resistance in under 30 s. Finally, chapter 5 concludes this thesis.

# 2

## Errors in Vds sensing

V<sub>ds</sub> sensing is based on the assumption that channel resistances of switching devices behave as ohmic resistors, such that  $I = V_{ds}/R_{ds}$ . In reality switching devices deviate from this assumption, exhibiting several effects that become sources of error when not addressed. Hence, achieving high fidelity requires suppressing the impact of some of these effects. However, this suppression comes with costs. Hence, the highest performance to cost ratio achieved when the suppression is limited to effects that reduce performance below the desired level.

Here these effects are identified by quantifying the impact of several potential sources of error based on electrothermal simulation models of a representative silicon MOSFET (IPT010N08NM5) and GaN HEMT (EPC2031).

### 2.1. Error model

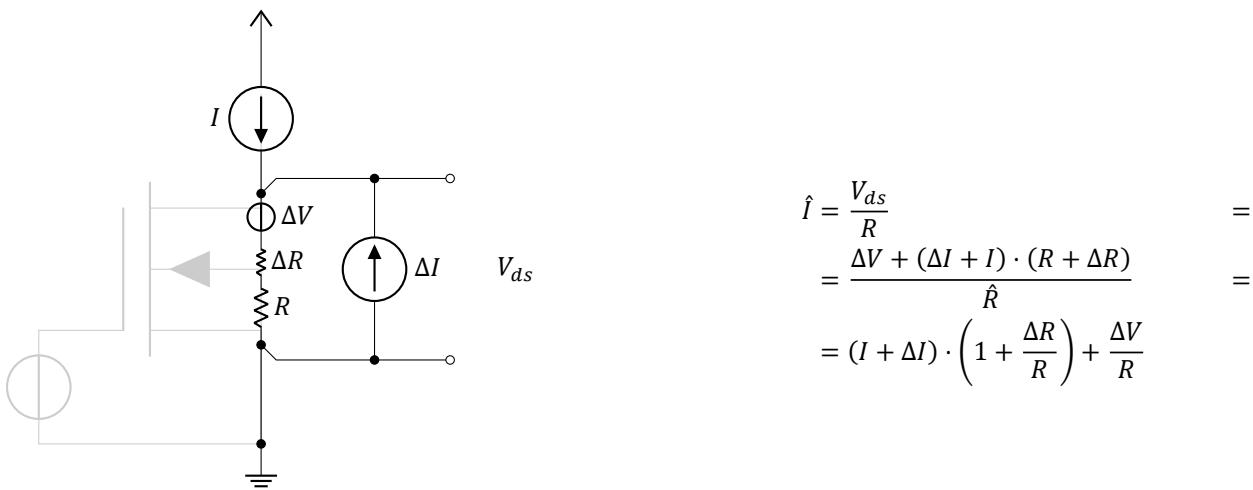

The errors can be divided in three categories: current errors, voltage errors, and resistance errors. Each affects the estimated current in a different way, as illustrated in figure 2.1. Under a small fluctuation assumption, resistance errors cause gain errors of  $\Delta G_r = \Delta R/R$ , voltage errors cause offsets of  $\Delta I_{off} = \Delta V/R$ , and current errors cause offsets of  $\Delta I$  that are subject to the gain errors.

Figure 2.1: Voltage, current, and resistance errors each affect the estimated current in a unique way.

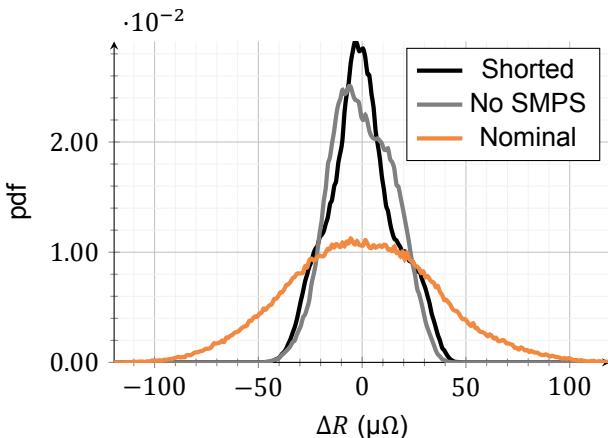

In general, the instantaneous error is not meaningful, as it may be current-dependent and stochastic. Rather, an average quantity gives more insight. The Root Mean Square (RMS) error is a natural fit due to the widespread familiarity with RMS measures. Under a small fluctuation approximation and for the  $T$ -periodic signals found in motor drivers, the total RMS error is:

$$\Delta \hat{I}_{rms} = \sqrt{\frac{1}{T} \int_0^T \Delta \hat{i}(t)^2 dt} \approx \sqrt{\frac{1}{T} \int_0^T \left( i(t) \cdot \frac{\Delta r(t)}{R} + \Delta i(t) + \frac{\Delta v(t)}{R} \right)^2 dt}$$

The contribution of individual RMS errors to the total depends on their mutual correlation. The contribution to the total error is highest when the errors are fully correlated, in which case the RMS errors add. Hence, the RMS error evaluated for individual error sources can be seen as a pessimistic estimate for their contribution to the total error.

Errors may also depend on factors specific to a unit or the environment. In a Bayesian approach, the average would be taken over a statistical model of such factors, so that the error metric emphasizes circumstances that are most likely to occur. However, many applications will have poorer performance than this average. Hence, a classical approach will be adopted here, with no statistical assumptions on these factors. Instead, worst case analysis will be applied to find the worst case RMS error. This ensures the error metric can be interpreted as the minimum performance in any application.

## 2.2. Sources of error

### 2.2.1. Temperature dependence

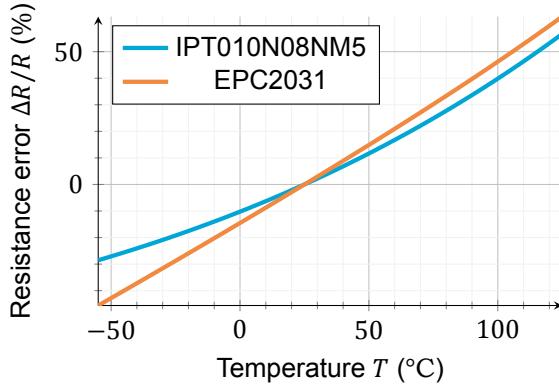

The temperature dependence of switching resistances is commonly cited as a major source of error [31, 8, 9, 43, 35, 29]. It can be modelled as a resistance error on top of a nominal resistance. Figure 2.2 shows the simulated small-signal resistance at no load current over temperature. A significant variation can be observed. Figure 2.2b shows that the associated temperature coefficient is roughly  $0.5\% \text{ }^{\circ}\text{C}^{-1}$ .

(a) The resistance varies with a factor of  $\approx 2 \times$  over temperature.

(b) The temperature coefficient of the resistance exceeds  $0.5\%$ .

Figure 2.2: The temperature dependency of the switching resistance gives a considerable error.

Taking the room temperature resistance as the nominal resistance and assuming full-scale sinusoidal currents, the worst-case RMS error due to temperature dependence occurs at the maximum temperature of  $125\text{ }^{\circ}\text{C}$ :

$$\hat{\Delta I}_{temp,rms} = \frac{I_{FS}}{\sqrt{2}} \cdot \frac{|\Delta R|_{max}}{R} \quad \Rightarrow \quad \frac{\hat{\Delta I}_{temp,rms}}{I_{FS}} = \frac{1}{\sqrt{2}} \cdot \frac{|\Delta R|_{max}}{R} = \frac{1}{\sqrt{2}} \cdot 63\% = 45\% \quad (2.1)$$

### 2.2.2. Production tolerance

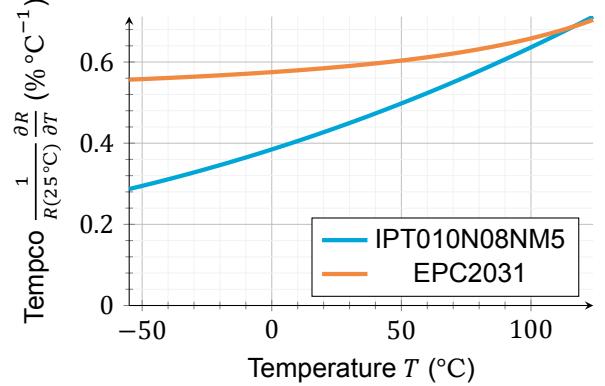

Another widely recognised source of error is uncertainty about the value of the parasitic resistance due to production tolerance [9, 43, 35, 29] or lack of manufacturer documentation [8]. This can be modelled as a resistance error. Switching device datasheets do not typically list the minimum resistance value, only the typical and maximum value [44, 45]. This gives an indication of the positive tolerance, which is illustrated in figure 2.3, along with an estimate for both the positive and negative tolerance from Motorola application note [26], a switching device manufacturer.

Figure 2.3: Various sources indicate a production tolerance of about 30% worst-case.

There is a reasonable agreement between the sources, though the IPT010N08NM5 exhibits a significantly better

tolerance. This may be attributable to its low channel resistance, which makes the resistance of relatively precise metal bonding elements a larger contributor, as shown in section 2.2.3. The worst-case RMS error due to production tolerance then is:

$$\frac{\Delta \hat{I}_{tol,rms}}{I_{FS}} = \frac{1}{\sqrt{2}} \cdot \frac{|\Delta R|_{max}}{R} = \frac{1}{\sqrt{2}} \cdot 30\% = 21\% \quad (2.2)$$

### 2.2.3. Gate voltage dependency

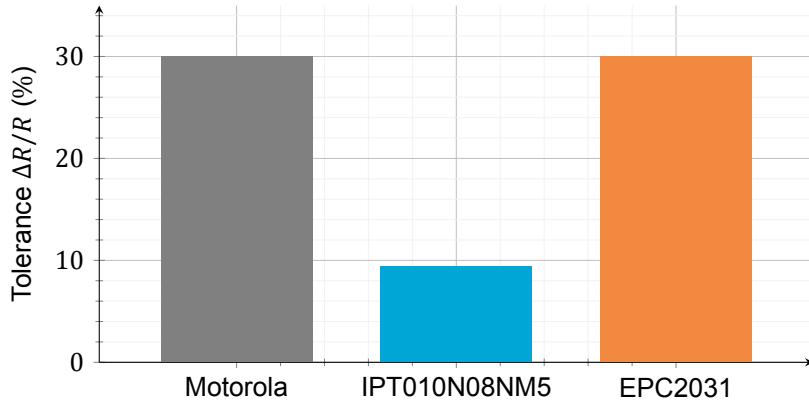

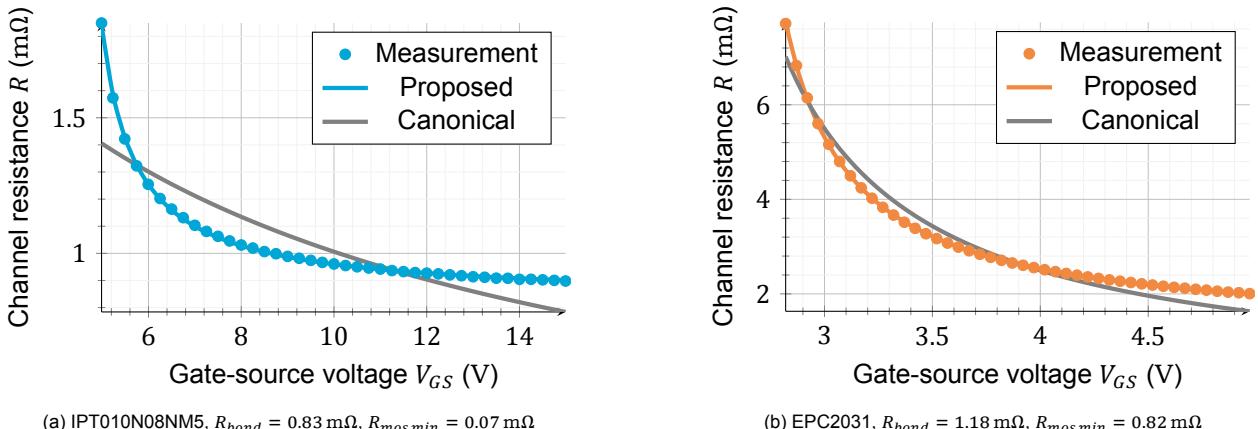

The dependency of the resistance on gate voltage is often noted [31, 8, 9, 43, 29], though not explicitly associated with a source of error. This can be modelled as a resistance error. For the square law model of a mosfet in triode region, the resistance can be found through a derivative:

$$I_D = \frac{W}{L} \cdot \mu C_{ox} \cdot \left( (V_{gs} - V_{th}) \cdot V_{ds} - \frac{V_{ds}^2}{2} \right) \Rightarrow R = \frac{\partial V_{ds}}{\partial I_D} = \frac{L}{W \cdot \mu C_{ox} \cdot (V_{gs} - V_{th})} \quad (2.3)$$

And this formula is frequently stated [9, 8, 43, 43]. Yet, it is not a good fit to the resistance to gate voltage dependency curves in datasheets, as illustrated in figure 2.4. This is because it does not take into account the linear parasitic resistances at the source and drain of the device, which become significant for high currents. The effect can be modelled using a single linear bonding resistance  $R_{bond}$ , as derived in appendix A.1:

$$R = \frac{\partial V_{ds}}{\partial I_D} = \frac{L}{W \cdot \mu C_{ox} \cdot (V_{gs} - V_{th})} + R_{bond} \quad (2.4)$$

As illustrated in figure 2.4, this model achieves a close fit to datasheet curves. Note that at the maximum gate voltage the bonding resistance is a significant fraction of the resistance for both devices, even dominating the resistance of the IPT010N08NM5.

Figure 2.4: The square-law model fits poorly to datasheet measurements, but the discrepancy is resolved when modelling bonding resistance.

Using equation 2.4, the sensitivity of the relative on-resistance error to gate voltage errors can be found:

$$\frac{1}{R} \cdot \frac{\partial R}{\partial V_{gs}} = -\frac{1}{(V_{gs} - V_{th}) \cdot \left(1 + \frac{R_{bond}}{R_{mos}}\right)} \Rightarrow \frac{\Delta R}{R} \approx -\frac{1}{1 - \frac{V_{th}}{V_{gs}}} \cdot \frac{1}{1 + \frac{R_{bond}}{R_{mos}}} \cdot \frac{\Delta V_{gs}}{V_{gs}} \quad (2.5)$$

In which  $R_{mos}$  is the square law resistance of the mos device, as given in equation (2.3). Equation (2.5) shows that the relative error in the on-resistance is directly related to the relative error in gate voltage, scaled up or down depending on the ratio of the gate voltage to threshold voltage and the bonding resistance to mosfet resistance.

It is difficult to determine the relative error in the gate voltage, since it strongly depends on the specific gate driver implementation. However, an educated guess can be made for a typical system based on a traditional bootstrap capacitor driven by a controlled power supply through a diode. The power supply is typically tightly controlled, to within 1%. Hence, the voltage over the diode when the high-side switch is activated is the dominant source of error.

After the switching node voltage goes low, the diode becomes strongly forward biased and thus has a low small-signal resistance. As a result, the bootstrap capacitor quickly charges. However, as the bootstrap capacitor gets charged, the forward bias over the diode grows weaker, decreasing the impedance and exponentially slowing the charging. Because of this, the voltage on the bootstrap capacitor at a given sufficiently late moment is relatively insensitive to the starting voltage or charging time but very sensitive to the low-current forward voltage of the diode. This voltage is heavily temperature dependent. As an example, it varies between 0.35 V and 0.7 V for the UCC27282-Q1 gate driver IC used in the test setup described in chapter 4. For the lowest gate-voltage EPC2031 device, this corresponds to a  $\pm 4\%$  error compared to nominal voltage.

Then the worst-case RMS error due to gate voltage dependency occurs at the maximum gate voltage deviation and for the EPC2031:

$$\frac{\Delta \hat{I}_{v_{gate,rms}}}{I_{FS}} = \frac{1}{\sqrt{2}} \cdot \frac{1}{1 - \frac{V_{th}}{V_{gs}}} \cdot \frac{1}{1 + \frac{R_{bond}}{R_{mos}}} \cdot \frac{\Delta V_{gs}}{V_{gs}} = \frac{1}{\sqrt{2}} \cdot \frac{1}{1 - \frac{2.51\text{V}}{5\text{V}}} \cdot \frac{1}{1 + \frac{1.18\text{m}\Omega}{0.82\text{m}\Omega}} \cdot 4\% = 2\% \quad (2.6)$$

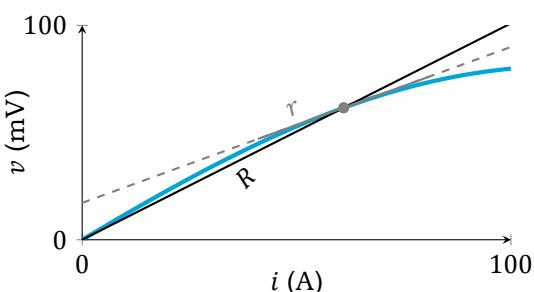

## 2.2.4. Nonlinearity

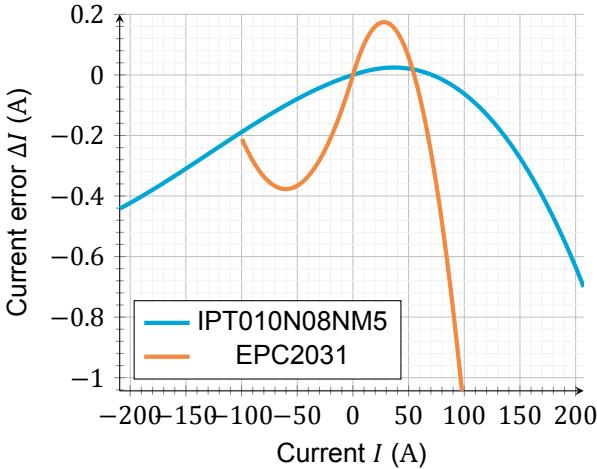

The parasitic resistance of the switching device is not perfectly linear, which some have named among dominant sources of error [9]. Assuming that nonlinearities scale with resistance changes such that  $i = i(v) \cdot R_{nom}/R$ , they are best modelled as current errors. Figure 2.5a shows the simulated error compared to a least squares zero-offset linear fit for drain voltages between  $-200\text{ mV}$  and  $200\text{ mV}$  at a junction and case temperature of  $25\text{ }^\circ\text{C}$ . The voltage was limited to  $\pm 200\text{ mV}$  because higher voltages correspond to power dissipation that would be too high for typical applications.

(a) The nonlinearity remains below 1% over a large current range.

(b) As the maximum current is reduced, the linearity increases.

Figure 2.5: A linear model gives a good approximation of the resistance of the switching devices.

It can be seen that the error remains lower than 1% over a large current range range. As the range of currents is reduced, the i,v characteristics of the switching devices become better approximated by an Ohmic resistance, giving a lower error compared to the full-scale current. This tradeoff is shown in figure 2.5b. For very low current ranges, the simulation model of the EPC2031 exhibits an offset that gives an increased error. Whether this does or does not correspond to reality could be settled by experiment but is not relevant to the current ranges considered in this work.

The usable RMS current range of the devices is about 50 A for the EPC2031 and 100 A for the IPT010N08NM5 due to the thermal constraints facing most applications. In this range, the worst-case RMS error due to nonlinearity occurs at 50 A for the EPC2031 and is given by:

$$\frac{\Delta \hat{I}_{linear,rms}}{I_{FS}} = 0.5\% \quad (2.7)$$

## 2.2.5. Limited access

When the switching devices are disabled, the current starts flowing through a different leg of the inverter and the  $V_{ds}$  sensing method can not be applied. Because of this, the current information is masked for large parts of the switching cycle. Though this makes it impossible to recover the full current waveform in the general case, it is fully compatible with the sampling strategy used to extract low-frequency current information that is used in many motor drivers.

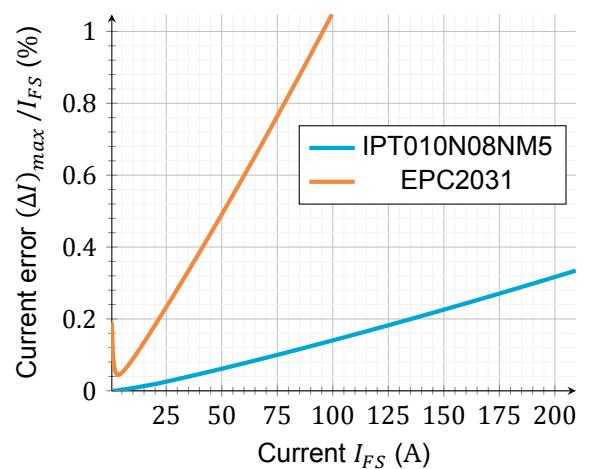

(a) The modulation is symmetric around a midpoint.

(b) The ripple is zero at the midpoint.

Figure 2.6: Midpoint sampling nullifies coupling from ripple to current samples.

Generally motor drivers employ midpoint sampling, where the switching moments are centred around the sampling moment. As illustrated in figure 2.6, this aims to ensure no ripple current is present at sampling moment, so that only the 'average' low-frequency current is sampled. In this scheme, the current information is only accessed when  $V_{ds}$  sensing is possible, so that the limited access poses only a synchronisation problem [31].

The idea that the instantaneous current at the midpoint corresponds to the average current is based on the assumption that the current varies linearly. In practice, nonlinearities in the current waveform introduce errors [46]. However, these errors are not commonly considered and are not unique to  $V_{ds}$  sensing. Hence, they should thus not be considered as part of this analysis.

As such, the worst-case added RMS error due to limited access is insignificant:

$$\frac{\hat{I}_{access,rms}}{I_{FS}} < 0.01 \% \quad (2.8)$$

## 2.2.6. Ringing

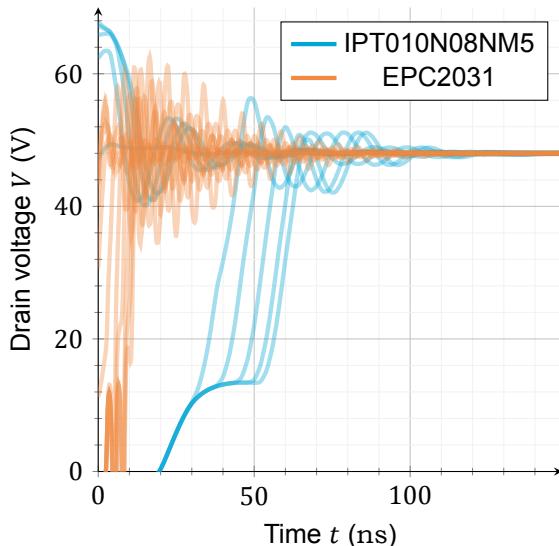

Unmodelled dynamics give rise to ringing following switching transitions. These can be modelled as voltage errors. Figure 2.7 shows the decay of simulated transients during the rising edges in half bridge output stages of simulated switching devices carrying one period of a 1 kHz 100 A (IPT010N08NM5) and 50 A (EPC2031) sine wave.

(a) The ringing dies down rapidly.

(b) The ringing is below millivolt level within 250 ns.

Figure 2.7: Though large transients are created by switching, they die down rapidly.

Figure 2.7a gives an overview of the transients. The difference between hard and soft switching can clearly be seen. Meanwhile, the decay can be reviewed more precisely in figure 2.7b, where the difference with the final value has been plotted on a logarithmic scale. Due to uncertainty in the final value, the error saturates around 0.1 mV. Hence, some trend lines are drawn, which illustrate the expected amplitude of the ringing.

Assuming a settling time of at least 400 ns, the worst-case RMS error due to ringing occurs at 400 ns for the EPC2031 and is insignificant:

$$\frac{\hat{I}_{ringing,rms}}{I_{FS}} = \frac{\Delta V}{R \cdot I_{FS}} = \frac{1 \mu V}{2.0 \text{ m}\Omega \cdot 50 \text{ A}} < 0.01 \% \quad (2.9)$$

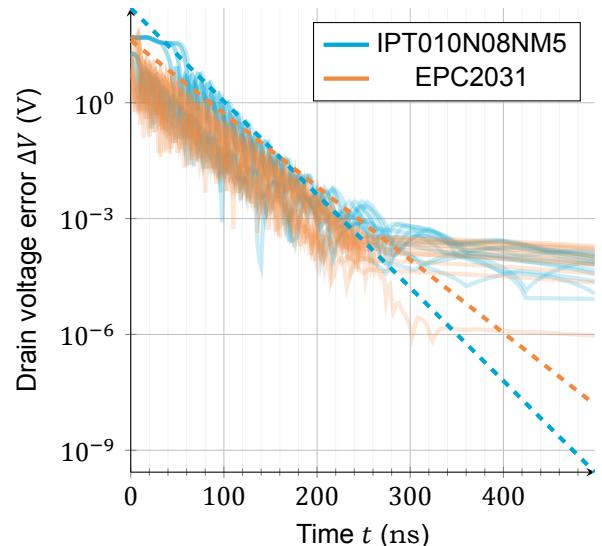

## 2.2.7. Leakage current

When the switches enter the off-state, they pass a leakage current. This leakage current adds as a current error to the sensed phase current. Figure 2.8 shows the simulated leakage current over temperature for a 48 V bus voltage.

Figure 2.8: The leakage current is low, even as it increases with temperature.

The worst-case RMS error due to leakage occurs at 125 °C for the EPC2031 and is insignificant:

$$\frac{\Delta \hat{I}_{leakage,rms}}{I_{FS}} = \frac{\Delta I}{I_{FS}} = \frac{30 \mu\text{A}}{50 \text{ A}} < 0.01 \% \quad (2.10)$$

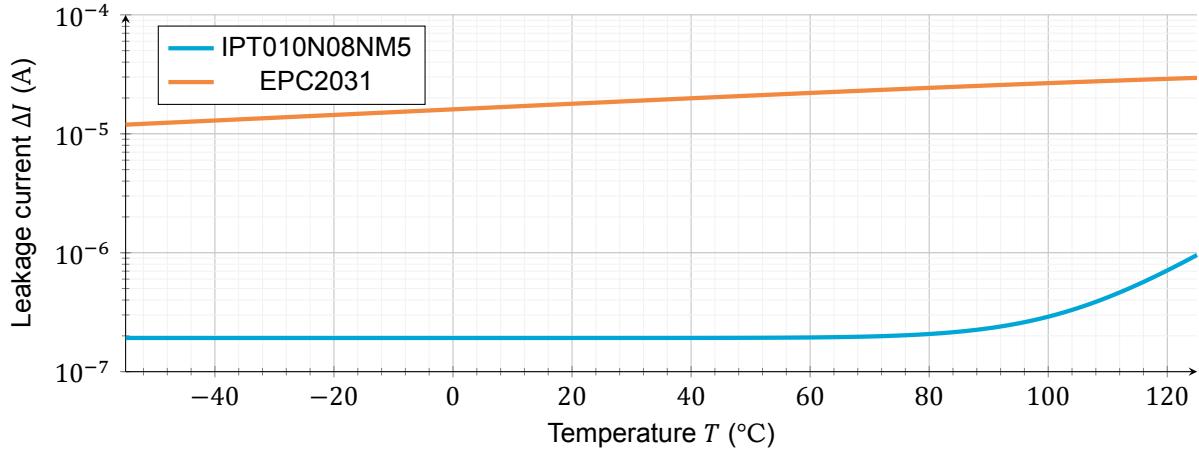

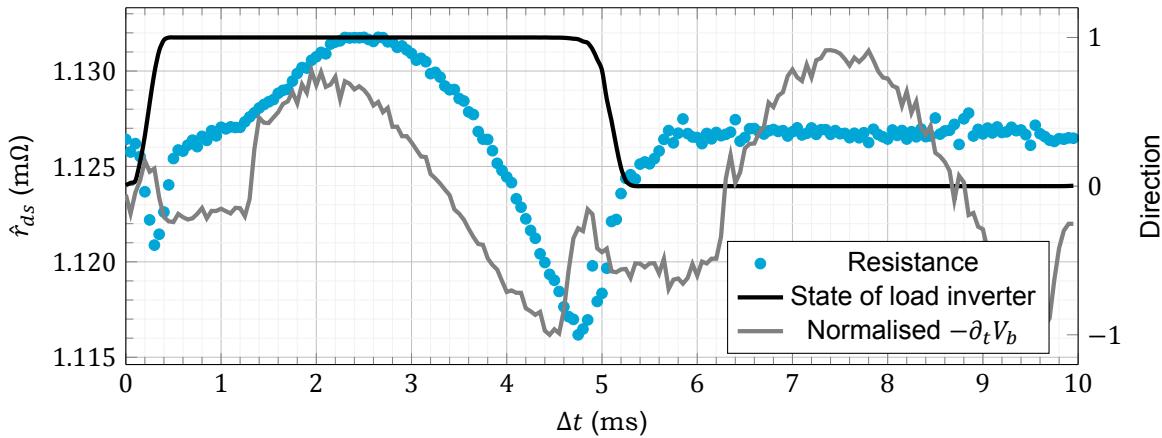

## 2.2.8. Dynamic changes in resistance

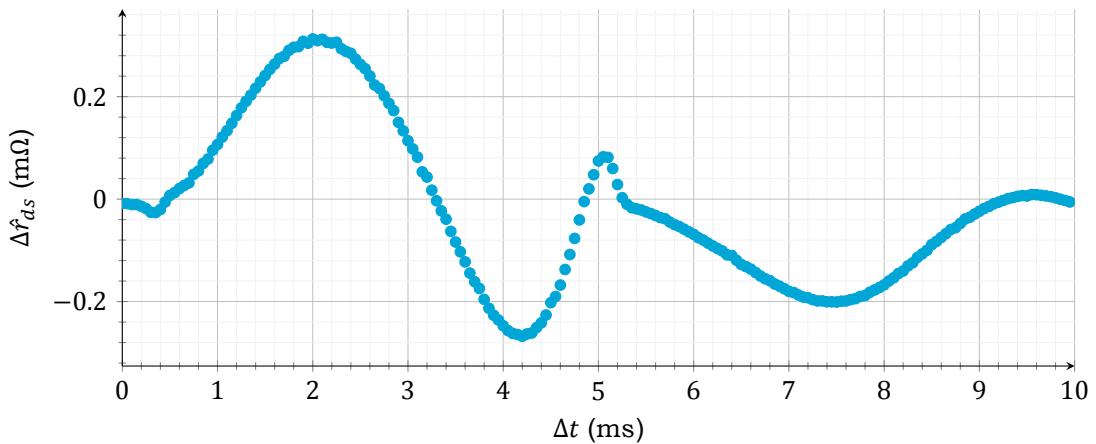

Changes of the on-resistance with time have been reported for Gallium Nitride (GaN) switching devices [47], with dynamics at the switching frequency. These are best modelled as resistance errors. Though these changes are not incorporated in the simulation models, measurements for the EPC2045 device have been reported [47] and are shown in figure 2.9.

Figure 2.9: The dynamic Ron effect is well approximated by a linear slope for short periods. Adapted from the EPC2045 measurements in [47].

It can be seen that the resistance may grow by over 54% compared to DC conditions. Within a 9 μs period the resistance is relatively stable, but still changes by 6 %. As illustrated, the variation is linear over time to within an error of roughly 0.1% for time periods smaller than 8 μs. Since the key reason the industry is moving towards GaN switches is to achieve a higher switching frequency, this condition should always be satisfied.

Assuming that the nominal resistance includes dynamic on-resistance effects, the error is given by the changes in on-resistance over changes in operating conditions. There is an effort to characterise the size of such changes for the purpose of efficiency modelling. It has revealed dependencies on pulse length and operating voltage [47]. Extrapolating from figure 2.9a, there may be a change of up to  $0.66 \% \mu\text{s}^{-1} \cdot 12.5 \mu\text{s} = 8 \% \text{ for off-times between } 0 \mu\text{s and } 25 \mu\text{s}$  (and midpoint sampling at half the off-time). Furthermore, for a 2:1 input voltage range, the dynamic

resistance may change by up to 20 %. Assuming a nominal resistance in the middle of these changes, the uncertainty is  $(8\% + 20\%) / 2 = 14\%$

Then the worst-case RMS error due to dynamic changes in resistance can be approximated by:

$$\frac{\Delta \hat{I}_{rdynamic,rms}}{I_{FS}} = \frac{1}{\sqrt{2}} \cdot \frac{|\Delta R|_{max}}{R} = \frac{1}{\sqrt{2}} \cdot 14\% = 10\% \quad (2.11)$$

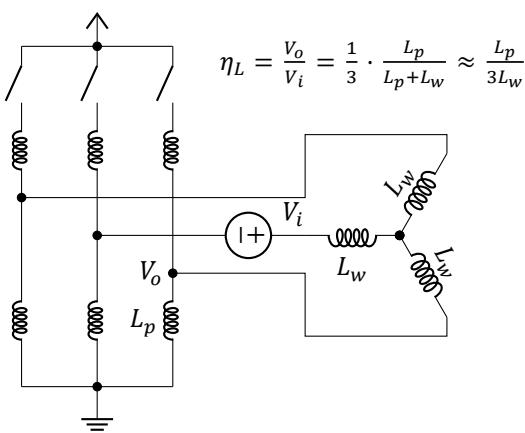

## 2.2.9. Lead inductance

The switching devices contain lead inductance, over which current ramps induce voltages that can be modelled as voltage errors. Figure 2.10 gives a simplified circuit model.

Figure 2.10: Both the back-EMF of the motors and the other inverters create offsets on the lead inductances.

Since the current ramps originate from voltages over the motor inductances, the error voltages can be modelled as the output of voltage dividers formed by the motor and lead inductances. Two voltage sources induce offsets: the back-EMF of the motor and the output voltages of the other inverters. In the worst case, the back-EMF of the motor is equal to the bus voltage, and both other inverters are in the opposite state of the inverter that is being sensed. In that case:

$$\Delta V_L \approx V_{bus} \cdot \frac{2L_p}{3L_w} \quad (2.12)$$

So that the worst-case RMS error due to lead inductance occurs for the IPT010N08NM5 at the minimum motor inductance of  $10\ \mu\text{H}$  and the maximum bus voltage of  $48\ \text{V}$ :

$$\frac{\Delta \hat{I}_{inductance,rms}}{I_{FS}} = \frac{\Delta V}{R \cdot I_{FS}} \approx \frac{V_{bus}}{R \cdot I_{FS}} \cdot \frac{2L_p}{3L_w} = \frac{48\ \text{V}}{0.90\ \text{m}\Omega \cdot 100\ \text{A}} \cdot \frac{2 \cdot 3\ \text{nH}}{3 \cdot 10\ \mu\text{H}} = 11\% \quad (2.13)$$

## 2.2.10. Noise

Noise poses a fundamental limit to the information that can be extracted from any system. The noise can be modelled as a current error due to thermal noise:

$$\Delta \bar{I}^2 = \frac{4kT}{R} \cdot B \quad (2.14)$$

In which  $B$  is the noise bandwidth of the measurement, which is limited by the parasitic dynamics of the inverter, which form a RLC filter. The bandwidth can be estimated as:

$$B_{IPT} \approx \frac{1}{2\pi \cdot \sqrt{LC}} = \frac{1}{2\pi \cdot \sqrt{3\ \text{nH} \cdot 3\ \text{pF}}} = 1.7\ \text{GHz} \quad B_{EPC} \approx \frac{1}{2\pi \cdot \sqrt{LC}} = \frac{1}{2\pi \cdot \sqrt{0.5\ \text{nH} \cdot 0.5\ \text{pF}}} = 10\ \text{GHz}$$

Where the small contribution above the cutoff frequency was ignored for a first approximation.

Then the worst-case RMS error due to noise occurs for the EPC2031 at  $125\ ^\circ\text{C}$  and is insignificant:

$$\frac{\Delta \hat{I}_{noise,rms}}{I_{FS}} \approx \frac{1}{I_{FS}} \cdot \sqrt{\frac{4kT}{R} \cdot B} = \frac{1}{50\ \text{A}} \cdot \sqrt{\frac{4 \cdot 1.38 \cdot 10^{-23}\ \text{J K}^{-1} \cdot 400\ \text{K}}{2\ \text{m}\Omega} \cdot 10\ \text{GHz}} < 0.01\% \quad (2.15)$$

## 2.3. Conclusion

Table 2.1 summarises the worst-case error contribution of various effects. Gate voltage dependency and nonlinearity have often been named as sources of error, but even in the worst case are not limiting in practice. Similarly, though lead inductance and dynamic changes in resistance have not traditionally been considered major sources of error, in some cases they may be among dominant error sources. Nevertheless, it should be noted that they may not be for many devices and in many operating conditions because they represent the worst-case. However, for the large range of devices and operating conditions encountered in the application of motor drivers, the worst case is likely to be encountered.

Table 2.1: Impact of potential error sources (arranged in descending order of importance).

| Effect                        | Worst-case MSE (% FS) | Notes                                     |

|-------------------------------|-----------------------|-------------------------------------------|

| Temperature dependence        | 45                    |                                           |

| Production tolerance          | 21                    |                                           |

| Lead inductance               | 11                    |                                           |

| Dynamic changes in resistance | 10                    | Only occurs in GaN devices                |

| Gate voltage dependency       | 2                     |                                           |

| Nonlinearity                  | 0.5                   |                                           |

| Ringing                       | < 0.01                | Provided the settling time exceeds 400 ns |

| Leakage current               | < 0.01                |                                           |

| Limited access                | < 0.01                |                                           |

| Noise                         | < 0.01                |                                           |

# 3

## Architecture design

### 3.1. Choice of error suppression method

Several approaches could be considered to suppress the errors found in chapter 2.

In single-point calibration, errors are measured at fabrication time and subsequently compensated. This compensates for the fixed production tolerance, but not dynamic errors. Ideally, the production tolerance is fully suppressed. In reality, the suppression will be limited by degradation.

In temperature compensation, the temperature dependency is corrected with an estimate of the error based on a temperature measurement or estimate. Ideally, this method fully suppresses the temperature dependency error. In reality, the suppression is limited by errors in the temperature estimate and the model of the temperature dependency.

Linear feedback of the resistance error can be used to suppress all linear resistive errors. Lead inductance effects are not suppressed since they do not originate from the resistance. Nonlinear effects also cannot be compensated due to the linear nature of the feedback. Ideally, all resistive errors are fully suppressed. In reality, the suppression is limited by the bandwidth of the feedback and errors in the resistance measurement.

With lead inductance compensation, the voltage over the lead inductance could be corrected with an estimate based on an uncorrected output current estimate, the measured bus voltage, the known state of the inverters, and a model of the load behaviour. Ideally, the error due to lead inductance is fully suppressed. In reality, the suppression is limited by the errors in the model of the load behaviour.

Table 3.1: Even with ideal performance, no single error suppression method achieves the desired suppression of the worst-case RMSE in % FS.

| Effect ↓ method →             | Unsuppressed | Single-point calibration | Temperature compensation | Linear feedback | Lead compensation |

|-------------------------------|--------------|--------------------------|--------------------------|-----------------|-------------------|

| Temperature dependence        | 45           | 45                       | 0                        | 0               | 45                |

| Production tolerance          | 21           | 0                        | 21                       | 0               | 21                |

| Lead inductance               | 11           | 11                       | 11                       | 11              | 0                 |

| Dynamic changes in resistance | 10           | 10                       | 10                       | 0               | 10                |

| Gate voltage dependency       | 2            | 2                        | 2                        | 0               | 2                 |

| Nonlinearity                  | 0.5          | 0.5                      | 0.5                      | 0.5             | 0.5               |

| <i>Total</i>                  | 89.5         | 68.5                     | 44.5                     | 11.5            | 78.5              |

As tabulated in table 3.1, even with ideal behaviour no single method can achieve the desired performance. In silicon devices, a combination of single-point calibration and compensation methods may achieve the desired performance. However, the suppression would not be robust to degradation and the method is not applicable to GaN devices. In contrast, a method based on the combination of linear feedback and lead inductance would not only achieve the desired performance, but be applicable to GaN devices and have robustness to degradation. Hence, it will be adopted here.

The adopted methods will now be considered more closely.

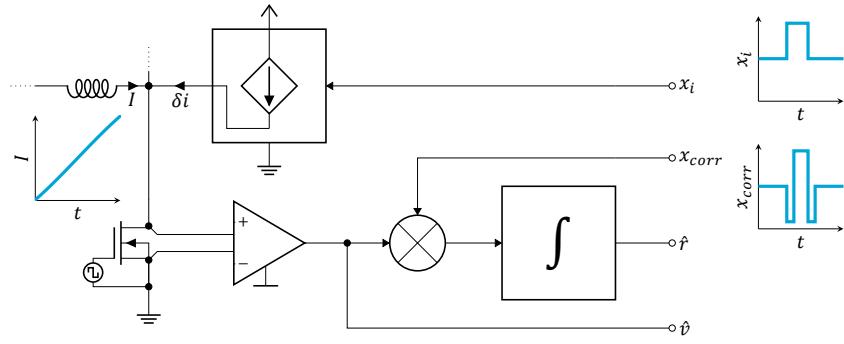

### 3.1.1. Linear resistance feedback

(a)  $R_{ds}$  is estimated from  $r_{ds}$  through an injected current  $\delta i$ .

(b) The measurement requires current injection and voltage sensing.

Figure 3.1: The big idea is to estimate the current  $I$  from the drain source voltage  $V$  through on-line measurement of the small-signal resistance.

Linear resistance feedback depends on a measurement of the resistance. However, resistance is not a quantity that can be directly observed. It is only meaningful as the response to some excitation. Hence, measuring the resistance requires observing the response to some test signal applied to the channel resistance of the switching device.

There are several methods that could be used to generate this test signal. As motivated in section 1.1.4, current injection at the switching node is the most promising method in terms of accuracy, stability, and bandwidth.

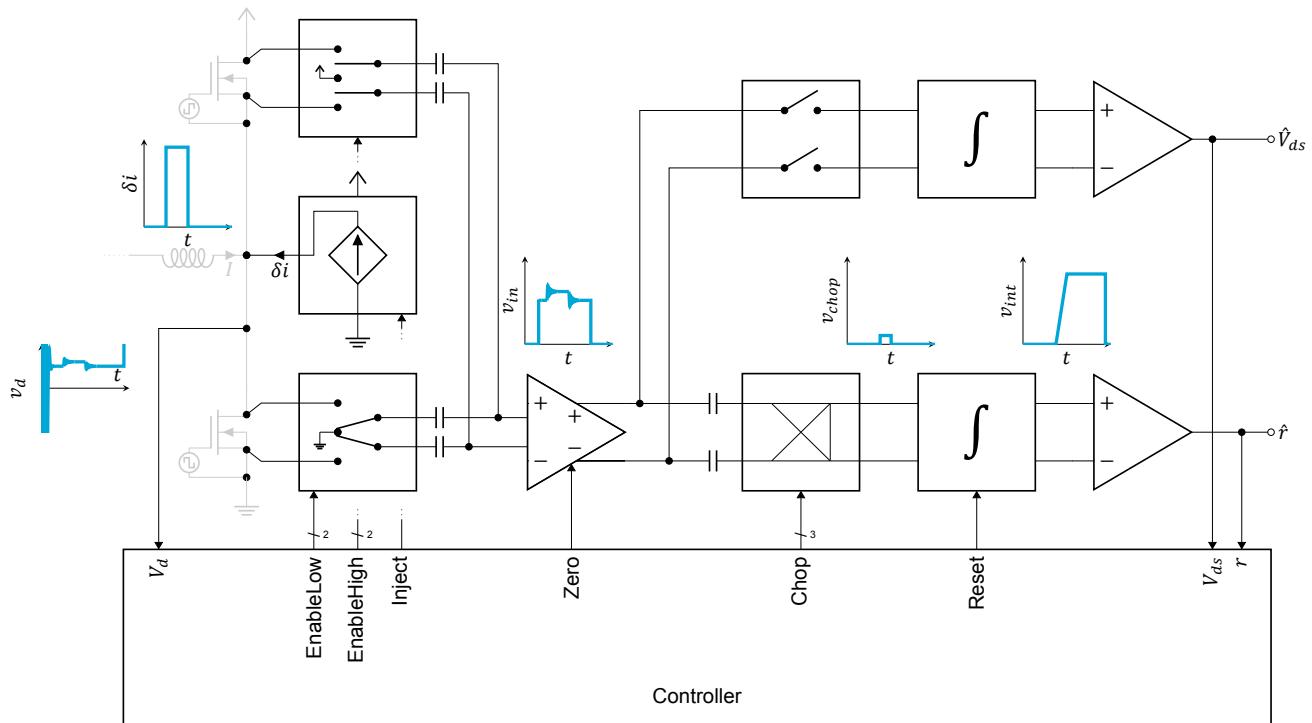

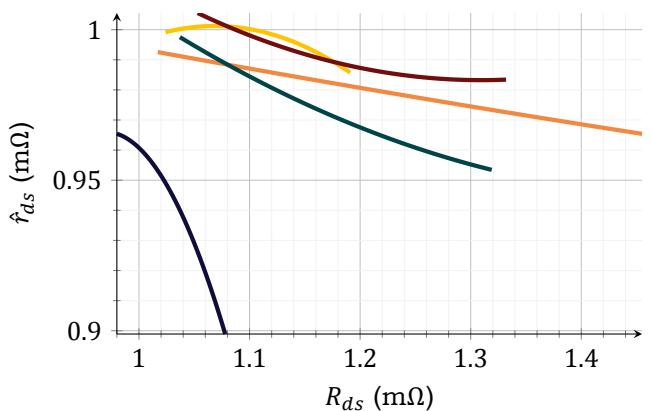

The key idea is to use continual measurements of the small-signal resistance  $r_{ds}$  of the switching device as an estimate of the large signal resistance  $R_{ds}$ .  $r_{ds}$  is measured through finding the amplitude of the small voltage pulse  $\delta v$  in response to a known small injected current pulse  $\delta i$ , as illustrated in figure 3.1a. This requires current injection and voltage sensing, as illustrated in figure 3.1b.

This method inherently comes with several errors. These will now be considered in more detail.

#### Linearity assumption

The method is based on the idea that the small-signal drain-source resistance  $r_{ds}$  is a good approximation of the large signal resistance  $R_{ds}$ . This is true for linear resistors. However, this assumption is only true to within a certain accuracy for practical switching devices. This will create a resistance error, as illustrated in figure 3.2a.

(a) The large signal and small signal resistances differ due to nonlinearity, giving rise to an error.

(b) As the maximum current is reduced, the linearity increases.

Figure 3.2: The linearity assumption comes with an inherent error, but it is manageable.

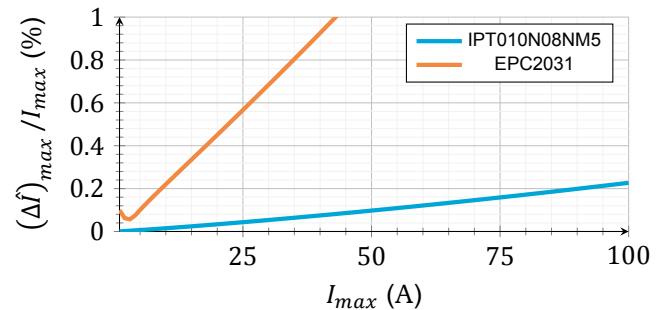

The error can be quantified in terms of the maximum deviation with respect to the full scale current:

$$\Delta \hat{I}_{linear} < I_{max} \cdot \frac{(r - R)_{max}}{R} \Rightarrow \frac{\Delta \hat{I}_{max}}{I_{max}} = \frac{(r - R)_{max}}{R} \quad (3.1)$$

Thanks to the roughly linear behaviour of the resistance, the small signal resistance is a good estimate of the large signal resistance.

#### Insufficient tracking of thermal ramps

During operation, the switching devices dissipate power causing temperature variations. Due to the temperature dependency of the switch resistance, this in turn causes the resistance to fluctuate. Depending on the interval between resistance measurements, a significant error may be accumulated compared to the last estimate.

Quantifying the error requires quantifying the temperature fluctuations. This can be accomplished with a thermal model of the switching device. Though modelling the exact behaviour for a dynamic power flow creates an unwieldy result, an upper bound can be found. As shown in appendix A.2 the resistance error is:

$$\Delta\hat{R}_{thermal} < \left(\frac{\partial R}{\partial T}\right)_{max} \cdot \min_i P_{max} \cdot \left( \frac{1}{\Delta t_{sample,R} \cdot \sum_{k=0}^i C_k} + \sum_{k=0}^i R_k \right) \quad (3.2)$$

### Voltage offsets & low-frequency noise

Voltage errors due to offset and low frequency noise in the voltage measurement path directly translate to current offsets and low-frequency noise. The resulting current error is given by:

$$(\Delta\hat{I})_{offset} = \hat{I} \cdot \frac{\Delta\hat{V}}{\hat{V}} = \frac{v_{off}(t)}{R} \quad (3.3)$$

In which  $v_{off}$  is the offset voltage, including low-frequency noise, in V.

### Gain mismatch between voltage and resistance estimation paths

Fabrication tolerances will inevitably cause gain mismatches between the voltage and resistance measurements. This combination of voltage and resistance errors will create gain errors in the estimated current, which can be estimated from the error model:

$$\Delta\hat{I}_{mismatch} = \hat{I} \cdot \left( \frac{\hat{V} \cdot \Delta G_v}{\hat{V}} - \frac{\hat{r} \cdot \Delta G_r}{\hat{r}} \right) = \hat{I} \cdot (\Delta G_v - \Delta G_r) \quad (3.4)$$

#### 3.1.2. Lead inductance compensation

The voltage errors over the lead inductances can be compensated using post-processing. This requires a rough estimate of the motor to lead inductance voltage division ratio, defined as the ratio of voltage offset over one of the connected lead inductances to a voltage source in series with either of the other phases, as illustrated in figure 3.3. Note that this ratio is independent of the inverter output states. It can be measured during design time.

Figure 3.3:  $\eta_L$  is the ratio of voltage offset over the connected lead inductance to a voltage source in series with either of the other phases.

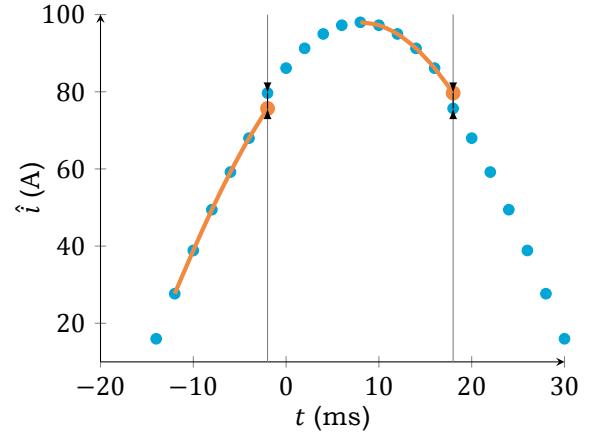

Figure 3.4: The inductance voltage division ratio can be measured from the jump in estimated current around an inverter state transition.

The compensation also requires knowledge of the back-EMF. Its estimation is already part of many motor control algorithms. If an estimate is not already available, it is also possible to estimate the back-EMF from the derivative of current estimate, duty cycle history, and a rough estimate of the motor inductance.

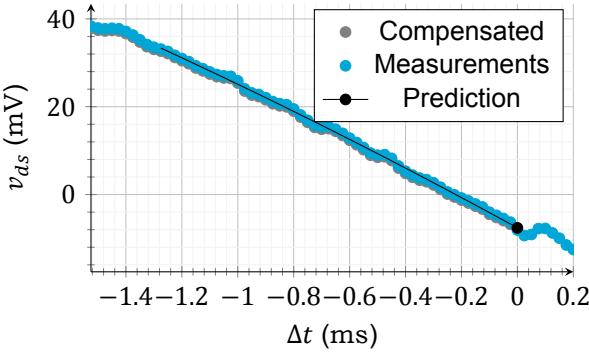

The offset contributions due to inverter outputs and the back-EMF are calculated using the voltage division ratio, estimated back-EMF and a measurement of the bus voltage. They are then subtracted from the raw measurements, compensating for the errors over the lead inductances of the switching devices. The motor inductance will in general be different than estimated due to unit-to-unit mismatch, core saturation effects, the rotation of the motor, and temperature dependency. However, a large certainty is not needed. Even if the estimate is off by  $\pm 10\%$ , the lead inductance errors can be suppressed by an order of magnitude. Nevertheless, some computation power can be used to refine the estimate through measurements of the division ratio from jumps in the estimated current compared to the quadratic trend before an inverter output transition, as illustrated in figure 3.4. Alternatively, a single point calibration can be performed at fabrication time to cancel unit-to-unit mismatch.

## Residual offset over the lead inductance

The lead inductance voltage offset compensation is never perfect, so that a residual offset exists. This manifests as a voltage error as modelled in section 2.1. Since the compensation voltage scales with the inductor ratio, the voltage error can be expressed in the inductor ratio error:

$$|\Delta \hat{I}|_{lead} = \hat{I} \cdot \frac{\Delta \hat{V}}{\hat{V}} < \left| \hat{I} \cdot \frac{2 \cdot V_{bus} \cdot (\eta_L - \hat{\eta}_L)}{\hat{V}} \right| = \frac{2 \cdot V_{bus}}{R} \cdot |\Delta \hat{\eta}_L| \quad (3.5)$$

## 3.2. Choice of detector

Two measurements are made to implement Vds sensing. One is of the Vds voltage, the other of the resistance. The resistance measurement is the most constraining, since it involves measuring the voltage created by an injected current that is only a fraction of the load current that causes the Vds voltage. The voltage measurement can be a simplified version of the resistance measurement. Hence, the focus will be on the resistance measurement.

Injecting the resistance test signal requires power. Since this power is wasted, it is desirable to keep it to a minimum. This increases the total power efficiency of the system and also decreases the power handling requirements of the injection source. In contrast, observation will come with noise. Since a lower noise will - all other things being equal - require more resources such as power and size, it is desirable to be able tolerate the maximum amount of noise.

These are contradictory requirements: larger test signals can be spotted in larger amounts of noise, whereas strict noise tolerances enable the detection of small test signals. Hence, it is important to make efficient use of the injected signal by optimising the signal chain. This starts at the detector.

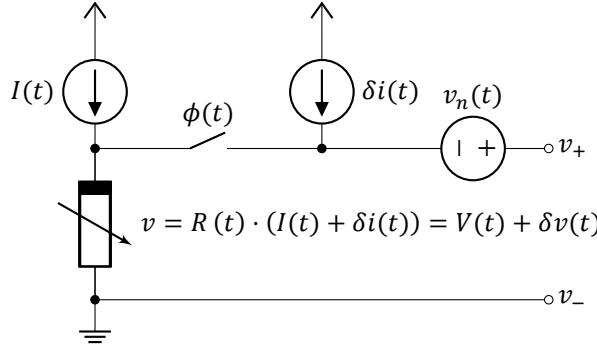

Since the electrical dynamics of the switching device must be quicker than the switching dynamics, the voltage over the switching element in the blocking phase is not meaningfully related to the current, and the behaviour of the closed switch is nearly linear, the switching device can be modelled as a variable linear resistor with intermittent access.

Figure 3.5: Model of the detection problem.

The detection problem can be modelled as shown in figure 3.5, where the size of the response  $\delta v$  of the unknown time-dependent resistance  $R(t)$  to a small known current  $\delta i(t)$  must be determined in the presence of an additive white Gaussian input noise voltage  $v_n(t)$  and an unknown bulk current  $I(t)$ . Ideally, the signal to noise ratio for a given injected power is maximised.

A near-optimal detector for this problem can be found through a perturbation argument. Say that  $\phi(t) = 1$ ,  $I(t) = 0$ , and  $R(t) = R$  is constant, then the optimal detector is given by the matched filter [48], with a time-domain description of:

$$\hat{R} = \frac{\int_{-T}^T \delta i(t) \cdot v(t) dt}{\int_{-T}^T \delta i(t)^2 dt}$$

In which  $[-T, T]$  is the support of the injected current. The Signal to Noise Ratio (SNR) is independent of the shape of  $\delta i$  and is given by:

$$\text{SNR} = \frac{2E}{N_0} = \frac{2R^2 E_i}{N_0}$$

In which  $E$  is the normalised voltage energy of the applied signal,  $E_i$  is the normalised current energy of the applied signal  $\delta i$ , and  $N_0$  is the single-sided input voltage noise density. The distribution of the associated resistance estimation error can be found from the SNR:

$$\Delta \hat{R} \sim \mathcal{N} \left( 0, \frac{R^2}{\text{SNR}} \right) = \mathcal{N} \left( 0, \frac{N_0}{2E_i} \right) \quad (3.6)$$

### 3.2.1. Effect of intermittent access

In reality  $\phi(t)$  changes with time, so that the access to the resistor is intermittent. When the switch is open, no information can be gained about the resistance. If  $\Delta i \neq 0$  when  $\phi = 0$ , this breaks one of the preconditions for the matched filter, and the detector is not optimal. However, if  $\Delta i = 0$  when  $\phi = 0$ , the detector is essentially blind to what happens when the switch is open, so that the output is unaffected. Since the performance is independent of pulse shape, this still gives optimal performance. Hence, a proper choice of injected signal the matched filter is an optimal detector.

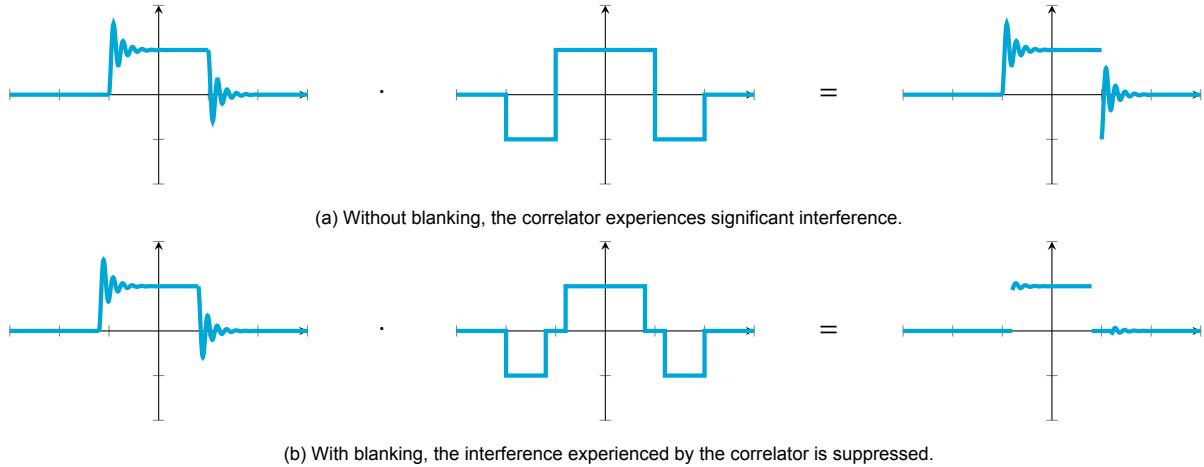

### 3.2.2. Effect of bulk current

In reality,  $I(t) \neq 0$ , which creates interference with the detector. The magnitude of this interference can be found from the time-domain description of the matched filter:

$$\Delta \hat{R} = \frac{\int_{-T}^T \delta i(t) \cdot R \cdot I(t) dt}{\int_{-T}^T \delta i(t)^2 dt} = \frac{R}{\int_{-T}^T \delta i(t)^2 dt} \cdot \int_{-T}^T \delta i(t) \cdot I(t) dt$$

For the zero interference condition  $\Delta \hat{R} = 0$ , the injected current must be orthogonal to the bulk current  $\int_{-T}^T \delta i(t) \cdot I(t) dt = 0$ . Hence, for a proper choice of injected signal, the matched filter is an optimal detector.

### 3.2.3. Effect of resistance changes

In reality,  $R(t) \neq R$ . Changes in temperature and dynamic changes in on-resistance will cause changes in resistance with dynamics near harmonics of the modulated signal frequency, so that  $R(t) = R(0) + \delta R(t)$ . This interferes with the detector. There are two effects, which will now be considered.

First, the changes in resistance will create changes in voltage, giving an error of:

$$\Delta \hat{R} = \frac{\int_{-T}^T \delta i(t) \cdot \delta R(t) \cdot I dt}{\int_{-T}^T \delta i(t)^2 dt} = \frac{I}{\int_{-T}^T \delta i(t)^2 dt} \cdot \int_{-T}^T \delta i(t) \cdot \delta R(t) dt$$

Like with the bulk current, for the zero interference condition  $\Delta \hat{R} = 0$ , the injected current must be orthogonal to the bulk current  $\int_{-T}^T \delta i(t) \cdot \delta R(t) dt = 0$ . Hence, for a proper choice of injected signal, the matched filter is an optimal detector. The same argument holds for mixing effects with the bulk current.

Second, the resistance becomes a moving target, so that the measurement may not accurately reflect a single sample. The associated error in resistance is given by:

$$\Delta \hat{R} = \frac{\int_{-T}^T \delta i(t) \cdot \delta i(t) \cdot R(t) dt}{\int_{-T}^T \delta i(t)^2 dt} - R(0) = \int_{-T}^T \frac{\delta i(t)^2}{\int_{-T}^T \delta i(t)^2 dt} \cdot R(t) dt - R(0) = \int_{-T}^T \frac{1}{\int_{-T}^T \delta i(t)^2 dt} \cdot \delta i(t)^2 \cdot \delta R(t) dt$$

Which is the difference between the instantaneous value and the weighted average of the resistance. For the zero error condition  $\Delta \hat{R} = 0$ , the square of the injected current must be orthogonal to the changes in resistance  $\int_{-T}^T \delta i(t)^2 \cdot \delta R(t) dt = 0$ . Hence, for a proper choice of injected signal, the matched filter is an optimal detector.

### 3.2.4. Constraints due to unmodelled effects

**Dynamics** In reality, various dynamic elements surround the switching device, which will cause ringing that is not modelled, as discussed in section 2.2.6. These effects can be blocked by setting the injected current to 0 in the detector while in reality already applying the current, giving a settling time. This is no longer an optimal detector, as there is inefficiency since fraction of power needed to injected current during the settling time is wasted according to  $\eta_{settle} = 1 - T_{settle}/T_{measurement}$ . However, the performance remains near-optimal for a sufficiently small settling time. As discussed in section 2.2.6, such  $T_{dead} \approx 400$  ns dead band times are achievable. As shown in section 3.4.2, the system-level performance is optimised for  $\eta_{settle} = 0.5$ , so that the performance of the detector is reduced by no more than a factor of 2x compared to the optimum

**Lead inductance** Changes in bulk current will create voltages over the lead inductance, which can interfere with the detector. The argument about interference due to bulk current over the resistance holds for these contributions.

**Pink noise**  $1/f$  noise was ignored in the derivation of this detector, but could introduce additional error. However, the zero interference conditions imply that the detector is insensitive to DC offsets, and thus low frequencies. Hence, the pink noise can be expected to not significantly affect the output of the detector and ignoring it is justified.

### 3.2.5. Enhancement by filtering

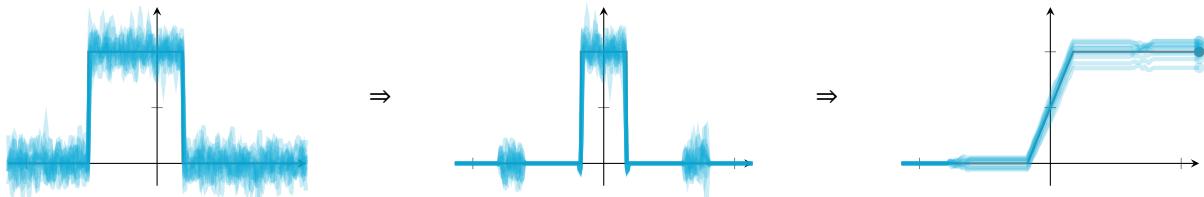

Though the matched detector gives near-optimal instantaneous measurement of a single injected pulse, the combination of these measurements may not be an optimal representation of the signal. For example, for a constant signal the average of the measurements is a much better representation of the signal than the time sequence of instantaneous measurements. Similarly, for a bandwidth-limited signal a filtered sequence more closely matched the underlying signal. Assuming sampling above the Nyquist rate and perfect reconstruction, the signal-to-noise Power Spectral Density (PSD) ratio of a uniformly sampled sequence of measurements at a sampling frequency  $f_s$  is:

$$\frac{P_s}{\partial P_n / \partial f} = \frac{f_s}{2} \cdot \frac{2R^2 E_i}{N_0}$$

So that for filtered version of the signal the SNR is:

$$\text{SNR} = \frac{f_s \eta_f}{2B} \cdot \frac{2R^2 E_i}{N_0} = \eta_f \cdot \frac{R^2 P_i}{N_0 B}$$

In which  $\eta_f = B/B_{\text{noise}}$  is an optimality factor of the filter, with  $\eta_f \leq 1$ , and  $\eta_f = 2/\pi$  for a first order time-continuous filter. It can be seen that the SNR is dependent on the normalised injected current power  $P_i$  rather than the pulse energy. This shows that the amount of pulses is not important to the SNR, only the rate of energy delivered. Hence, a system based on a matched detector achieves the same performance as a continuous-time system with equivalent bandwidth.

### 3.2.6. Conclusion

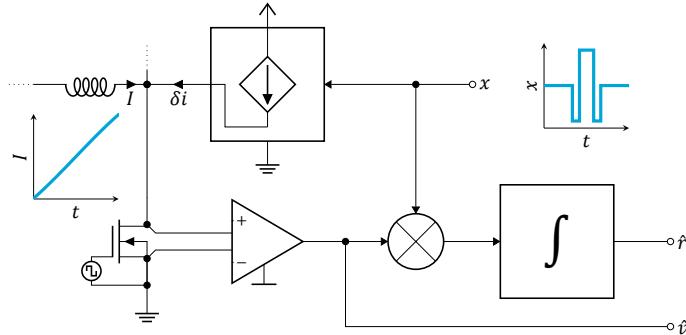

All in all, the matched filter is not an optimal solution to the intermittent resistance detection problem. Settling of unmodelled dynamics limits the amount of signal captured and more noise is captured due to the presence of pink noise. However, despite these adverse effects, under reasonable orthogonality constraints on the injected current there is no significant room for improvement over the matched filter. Furthermore, efficient implementation exist, such as using a multiplier and integrator, as shown in figure 3.6. Hence, it is adopted here.

Figure 3.6: A correlator is used to find the amplitude of the small signal voltage pulse  $\delta\bar{v}$ .

This has several implications for the design.

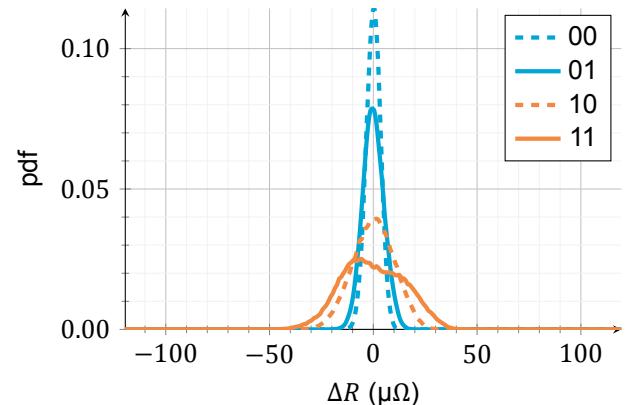

First of, the performance of the system is independent of the shape of the injected current, only its power. Second, this shape must adhere to several orthogonality constraints:

$$\int_{-T}^T |\delta i(t)| \cdot \bar{\phi}(t) dt = 0 \quad \int_{-T}^T \delta i(t) \cdot I(t) dt = 0 \quad \int_{-T}^T \delta i(t) \cdot \delta R(t) dt = 0 \quad \int_{-T}^T \delta i(t)^2 \cdot \delta R(t) dt = 0 \quad (3.7)$$

In addition, a settling time  $T_{\text{settle}} > 400 \text{ ns}$  must be observed.

## 3.3. Injected current signal shape

### 3.3.1. Signal class

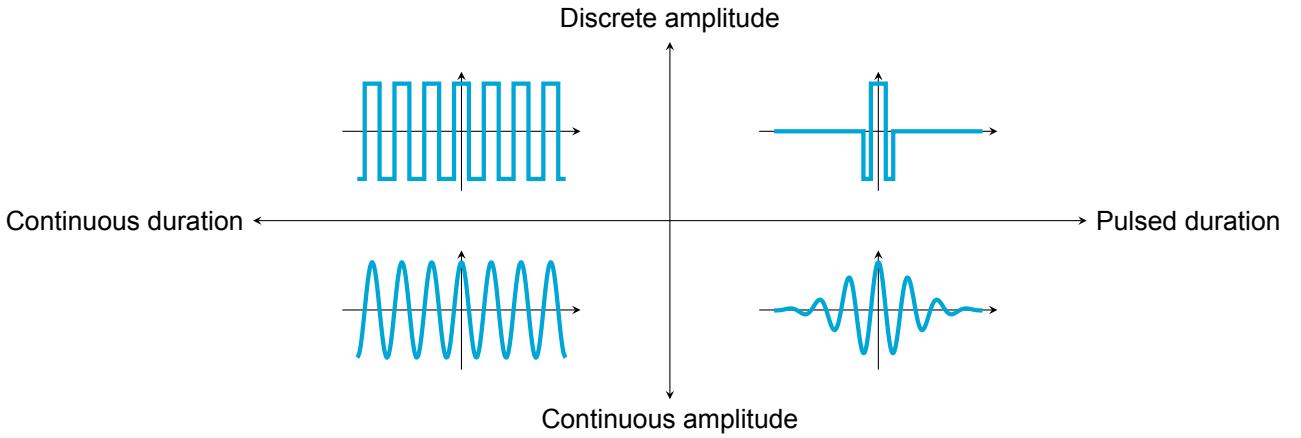

For a constant injected power, the shape of the injected signal does not influence the SNR of the measurement. However, the shape can influence the performance to cost ratio of the system. In particular, signal shapes may be grouped in four classes, depending on the continuous or pulsed operation and continuous or discrete amplitude. Representatives of these classes are illustrated in figure 3.7.

Figure 3.7: Signal shapes may be grouped depending on continuous or pulsed duration and continuous or discrete amplitude.

Since resistance information is only available in one of the switching phases, continuous signals introduce a mixing behaviour with the duty cycle. This introduces an unnecessary problem, and is thus best avoided. Furthermore, there are several reasons to prefer discrete amplitudes over continuous amplitudes. First, the generation and detection can be efficiently implemented using switches and chopped integrators. Second, the power delivery capability of the injection power stage can be fully used. Hence, discrete amplitude pulsed signals are adopted here.

### 3.3.2. Satisfying constraints

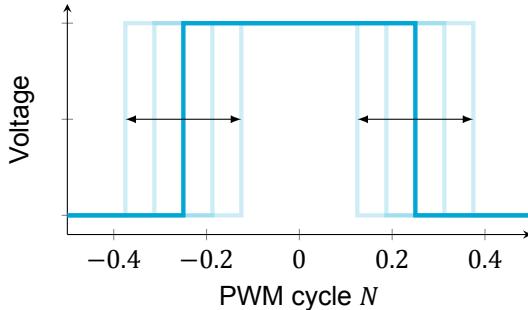

#### Orthogonality to inverter output

The shape of the injected signal must be orthogonal to several signals. First, its absolute value must be orthogonal to the output of the inverter  $\bar{\phi}(t)$ . This is a center-aligned Pulse Width Modulation (PWM) signal with a varying duty cycle. Orthogonality requires the injected pulse length to fit inside of the low period of this PWM signal.

There is a tradeoff between the length of this measurement window and the duty cycle range over which resistance measurements can be performed. For a given maximum current amplitude, longer injection lengths impart more energy giving a better SNR. However, a longer injection length also gives a smaller maximum duty cycle. As discussed in section 3.4.2, the optimum measurement time is roughly as long as the settling time of the system. Hence, good performance can be attained for a small decrease in modulation range. Furthermore, a full modulation range can be maintained when the 'blind' current is estimated using the current measurement from two other phases, such as used to avoid blind spots in leg shunt current measurements [12]. Finally, note that the measurement window need not be contiguous and constrained to a single cycle. A the injected signal could be spread over pulses in multiple fixed duty cycle PWM cycles to allow more measurement time. This is particularly relevant to the high switching frequencies the industry is moving towards.

There is also the option to adapt the length of the measurement signal to the available time. This improves the SNR for lower duty cycles, at the cost of added complexity. Yet, this method has the same worst case RMSE as a constant-time approach. Hence, the constant time approach is adopted here for its simplicity.

#### Orthogonality to bulk current and resistance errors

The injected signal is required to be orthogonal to the bulk current  $I(t)$  and resistance error  $\delta R(t)$ . In general, these signals consist of a complex combination of time-varying distorted sinusoids and sawtooth waves. However, any signal becomes well approximated by its  $N$ th order Taylor polynomial for sufficiently short timespans. Hence, any signal that is orthogonal to polynomials of sufficiently high orders will have the required orthogonality properties.

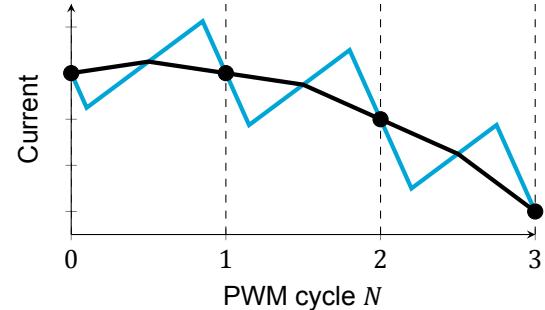

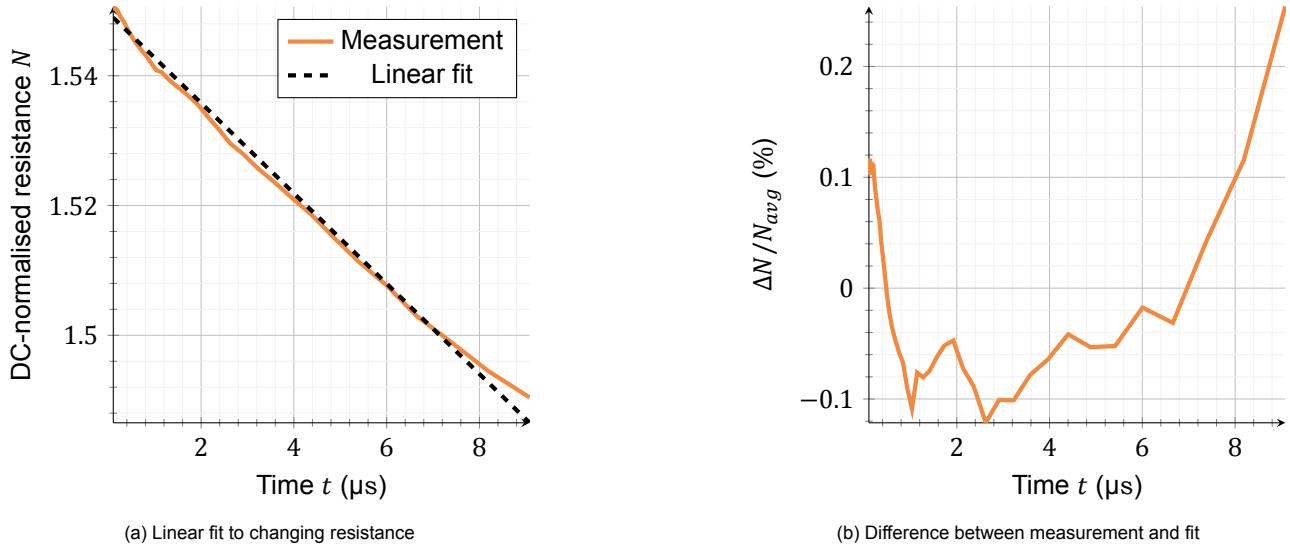

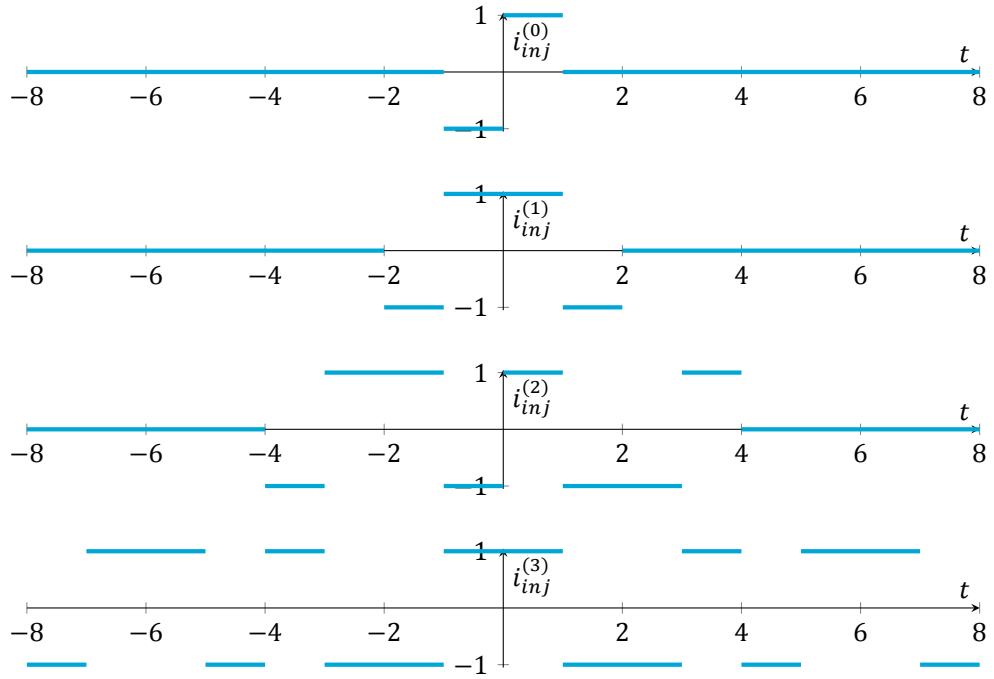

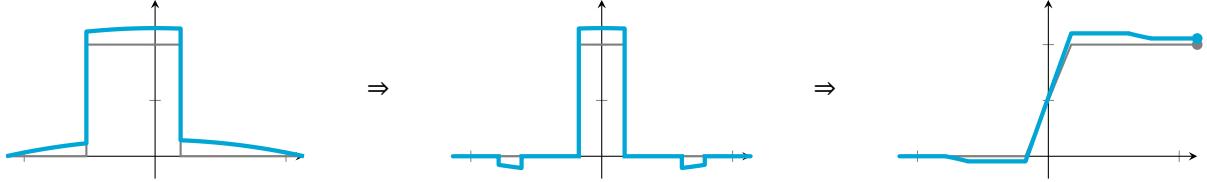

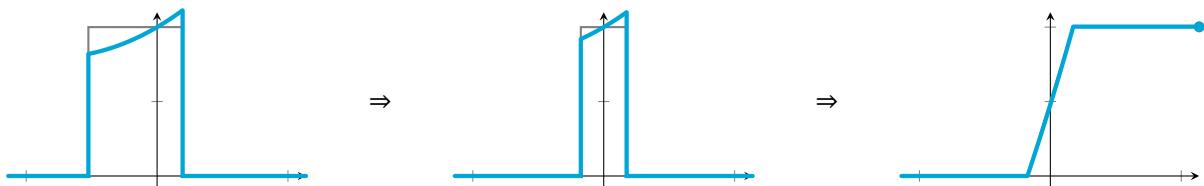

As confirmed by the outline of a proof in appendix A.4, such signals can be found for any base pulse shape and any polynomial order  $N$  by repeated application of shifting, mirroring and rotating. The procedure starts with a base pulse shape. To make it orthogonal to 0th order polynomials (constant values), the start of the signal is right-aligned with the zero axis. Then, a  $180^\circ$  rotated version is added to it. To make it orthogonal to 1st order polynomials (offset ramps), the resulting signal is again right-aligned with the zero axis and its mirror image along that axis is added. For orthogonality with higher order polynomials, rotation is applied for odd orders and mirroring for even orders. The resulting signals for a unit pulse base shape are shown in figure 3.8.

Figure 3.8: Signals orthogonal to first 4 orders of polynomials can be constructed from unit pulses.

Since every edge comes with ringing and thus additional time and power overhead incurred due to dead time, the amount of edges should be minimised. For a given order  $N$ , the use of the unit gate pulse as the base pulse shape achieves this goal, as it has the minimal amount of edges of any discrete base pulse shape. To further minimise the edges, the order  $N$  should be minimised.

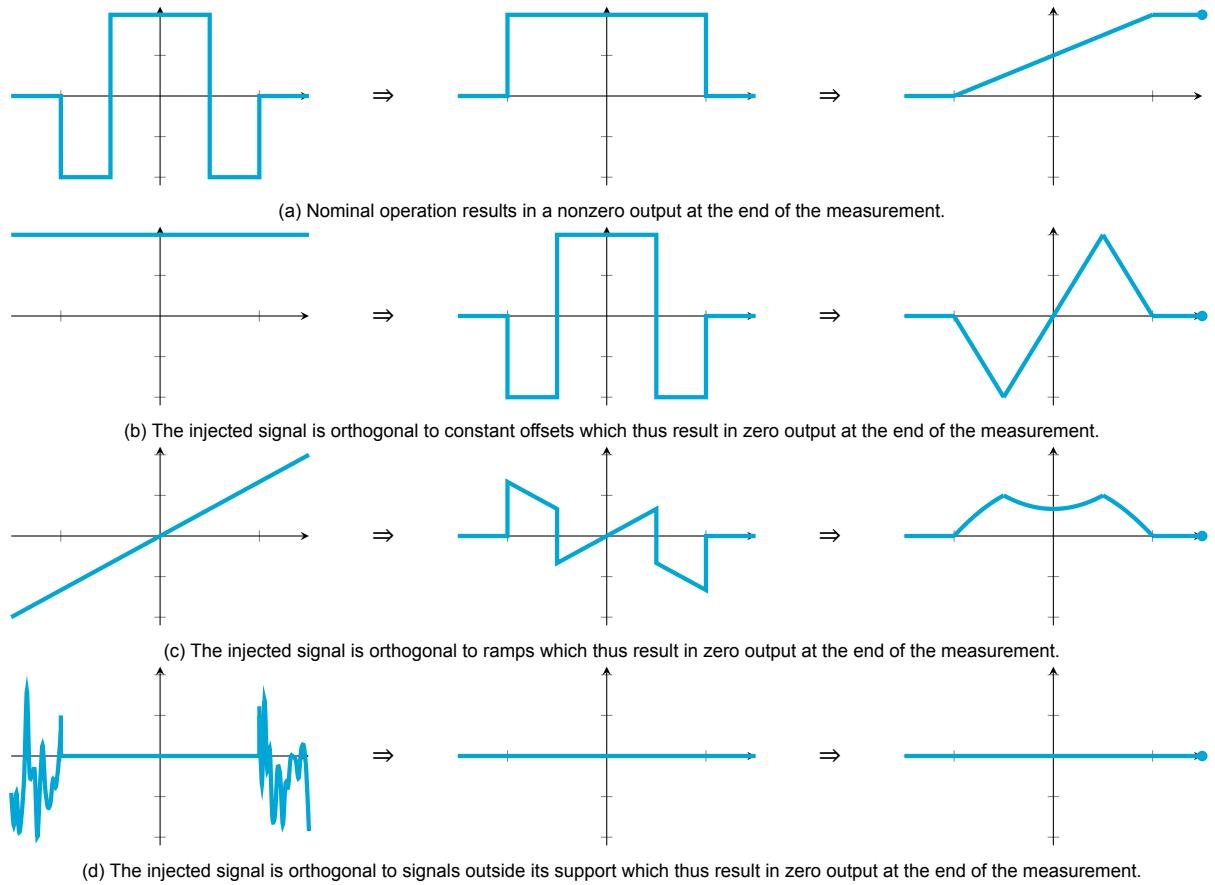

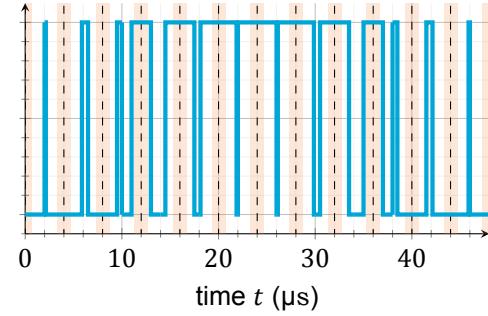

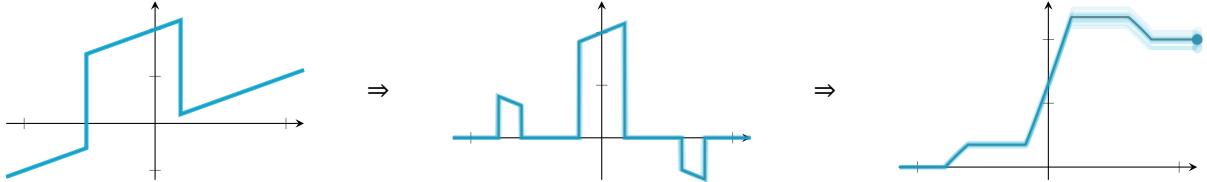

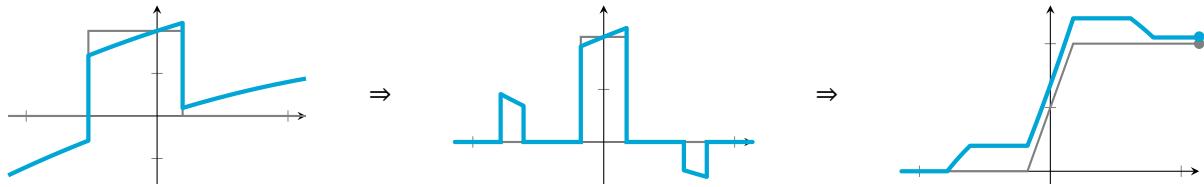

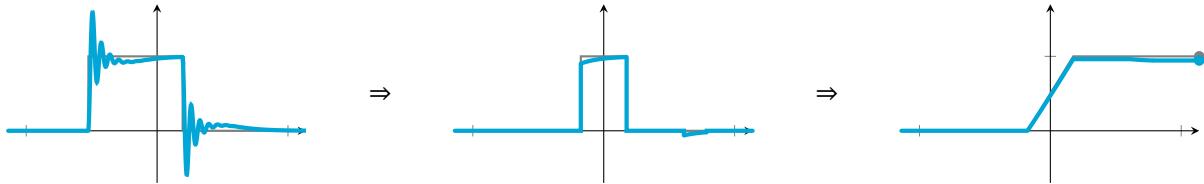

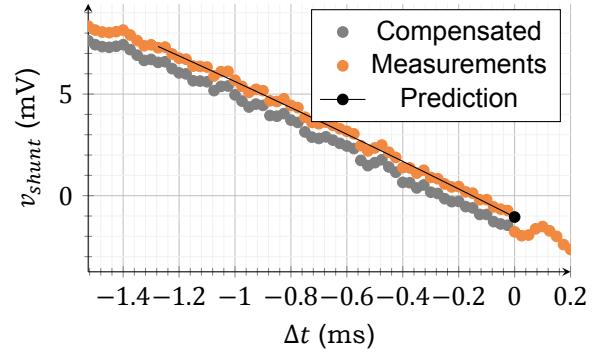

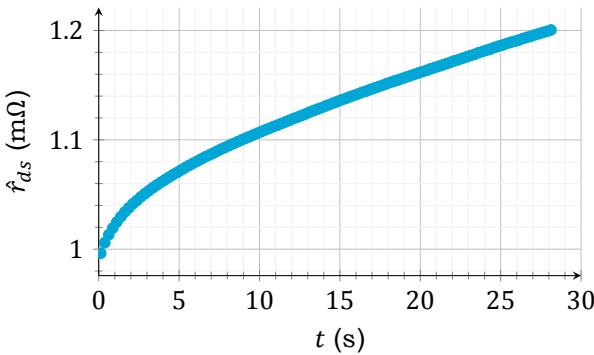

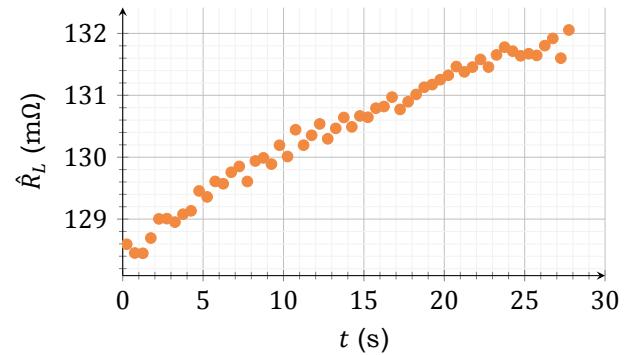

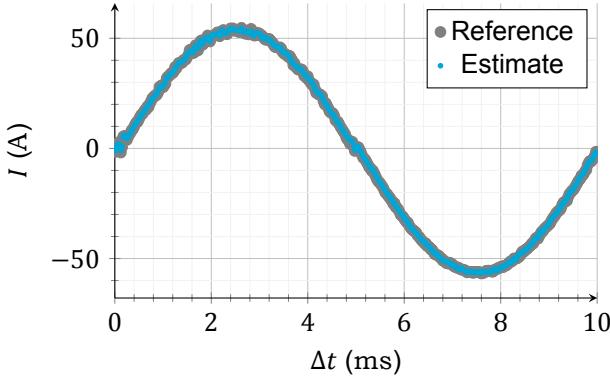

Figure 3.9: The down-up-up-down pulse is orthogonal to offset linear interference. On the left, various input signals are shown. In the middle, the product with the down-up-up-down pulse is shown. On the right, the running integral of the signals is shown. The sampling moment is indicated with a dot, with the vertical deflection corresponding to the result of the measurement.