# **Modelling of Modular Multilevel Converters for Fast and Accurate** Simulation of Electromagnetic **Transient Phenomena in HVDC Applications**

## By Salman Saeed Khan

in partial fulfilment of the requirements for the degrees of

Master of Science. Electrical Engineering, Delft University of Technology.

Master of Science. Technology-Wind Energy, Norwegian University of Science and Technology.

European Wind Energy Master

Erasmus Mundus MSc programme

# Modelling of Modular Multilevel Converters for Fast and Accurate Simulation of Electromagnetic Transient Phenomena in HVDC Applications

#### Salman Saeed Khan 4407830

Supervisors : Prof. Pavol Bauer (TU Delft)

Prof. Elisabetta Tedeschi (NTNU)

Thesis Defense on Monday, August 15th, 2016.

Prof. Pavol Bauer (TU Delft)

Thesis Committee: Prof. Elisabetta Tedeschi (NTNU)

Dr. Henk Polinder (TU Delft)

## **Abstract**

Modular multilevel converters (MMC) are gradually becoming the technology of choice in high-voltage direct current (HVDC) power transmission for grid integration of large-scale offshore wind farms and multi-terminal HVDC transmission schemes. Each phase of an MMC HVDC terminal consists of several hundreds of identical submodules that switch a module capacitor in and out of the circuit to synthesize near perfect sinusoidal ac voltages. This operation requires sophisticated control and modulation techniques. Furthermore, the design of converter, validation of control system and operational planning requires robust simulation models. To precisely model the switching operation in the converters electromagnetic transient solvers are employed. These solvers utilize numerical integration methods and nodal analysis to resolve the system in time domain.

However, the design of MMC poses a computational challenge to the classical electromagnetic transient simulations techniques. Independent operation of submodules necessitates explicit their modeling, which leads to hundreds of nodes and semiconductor devices in the equivalent models. This time-varying topology with hundreds of nodes leads to the excessive computational load on the electromagnetic transient solvers. To address this, existing literature proposes numerous efficient equivalent models for MMC based on submodule/arm's Thevenin's equivalence, switching function or average representations. The desired equivalent models for EMT studies are expected to reproduce internal and external dynamics of the converter in stationary and transient conditions. However, many of the existing models in literature lack the capability to capture the *blocked* state of operation of submodules, which finds application in the dc fault operation of the converter. Furthermore, with an extensive collection of proposed models, existing literature lacks an independent collective objective comparison of proposed models, which enable suitable selection of model based on the simulation needs.

In light of these requirements, this thesis presents a comprehensive review and enhances models from the existing literature. Moreover, using PSCAD/EMTDC simulations the proposed models are evaluated against the detailed model of the converter regarding accuracy and computational load. The simulations confirm the ability of enhanced models to capture the dynamics of converter under stationary and severe transient conditions. Furthermore, based on the simulation methods and results, the thesis addresses limitations of the proposed models and presents recommendations for their simulation applications.

In addition to the specific focus on electromagnetic transient simulation models, the thesis further aims to serve as a tutorial for the MMCs technology. Therefore the thesis presents a detailed account of MMC operation, and its associated control and modulation system.

*Index Terms* — High-voltage direct current (HVDC), Modular multilevel converters (MMC), Thevenin's equivalent model, Switching function models, Average value models, Electromagnetic transients.

# Acknowledgment

First and foremost, I would like to express my profound gratitude to my supervisors, Prof. Elisabetta Tedeschi, NTNU Trondheim and Prof. Pavol Bauer, TU Delft. Their expertise and continuous guidance made this work possible.

Furthermore, I am grateful to Dr. Jon Are Suul, co-supervisor, for his valuable insight on the topic. In addition, I would like to acknowledge the valuable suggestions from Dr. Raymundo Torres (NTNU), Dr. Muhammad Jafar (DNV GL) and Minos Kontos (TU Delft).

I would also like to express my sincere gratitude to Dr. ir. Henk Polinder, Prof. Olav B. Fosso, and Linda Gaffel for the administrative support throughout the masters. Specials thanks are due to the Erasmus EWEM program for the financial support of my masters. Moreover, I would especially thank all of my friends in Delft and Trondheim for making the last two years memorable.

Above all, I would like to thank my parents, Saeed Khan and Shahida Khan, for their relentless support in every step of my life.

Salman Saeed Khan

# Contents

| Li | st of | Figures                                                                                                                                                                                                          | 1                          |

|----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Li | st of | Tables                                                                                                                                                                                                           | 7                          |

| Li | st of | Acronyms                                                                                                                                                                                                         | 9                          |

| Li | st of | Symbols                                                                                                                                                                                                          | 13                         |

| 1  | 1.1   | Motivation and Past Work                                                                                                                                                                                         | 15<br>15<br>18             |

|    | 1.4   | 1.2.1 Specific Objective.  Main Contributions  Report outline.  Publication                                                                                                                                      | 18<br>18<br>19<br>19       |

| 2  |       | Modes of Transmission                                                                                                                                                                                            | 21<br>21<br>21<br>25       |

|    | 2.2   | 2.1.3 HVDC vs. HVAC                                                                                                                                                                                              | 27<br>28<br>29<br>30       |

| 3  | Mod   | dular Multi-Level Converter                                                                                                                                                                                      | 33                         |

|    |       | Design                                                                                                                                                                                                           | 36<br>38<br>40             |

|    |       | 3.2.1 Sub-Module Operation                                                                                                                                                                                       | 40<br>41                   |

|    | 3.3   | Currents and Voltages in System  3.3.1 Assumptions for analytical modeling of MMC  3.3.2 Arm voltages and currents  3.3.3 Average Power Balance  3.3.4 Equivalent Model of a MMC  3.3.5 Instantaneous Power flow | 43<br>44<br>49<br>51<br>53 |

|    | 3.4   | 3.3.6 Voltage Ripple and Circulating Current                                                                                                                                                                     | 55<br>57                   |

| 4  |       | nponent Selection  Number of Sub-modules                                                                                                                                                                         | <b>59</b>                  |

xii Contents

|   |            | Sub-module capacitance                                                                                                                             | 60<br>62                    |

|---|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 5 |            | trol Scheme           Upper level control                                                                                                          | <b>63</b><br>64<br>64<br>65 |

|   | 5.2        | Voltage Balancing control                                                                                                                          | 70<br>71                    |

|   | 5.3        | <ul><li>5.2.2 Capacitor voltage balancing loop.</li><li>Circulating Current Control</li><li>5.3.1 Synchronous reference frame controller</li></ul> | 71<br>72<br>72              |

|   | 5.4<br>5.5 |                                                                                                                                                    | 74<br>74                    |

| 6 | Mod        | dulation                                                                                                                                           | 75                          |

|   | 6.1        | Arm Level Modulation                                                                                                                               | 76                          |

|   |            | 6.1.1 Direct modulation                                                                                                                            | 76                          |

|   |            | 6.1.2 Uncompensated Modulation                                                                                                                     | 77                          |

|   | 6.2        | 6.1.3 Compensated Modulations                                                                                                                      | 77<br>79                    |

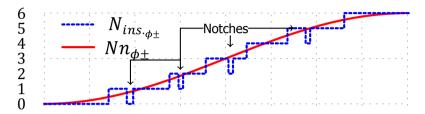

|   | 0.2        | 6.2.1 Nearest Level Control                                                                                                                        | 79<br>80                    |

|   |            | 6.2.2 Nearest Level Modulation                                                                                                                     | 81                          |

|   |            | 6.2.3 Multi-carrier PWM techniques                                                                                                                 | 82                          |

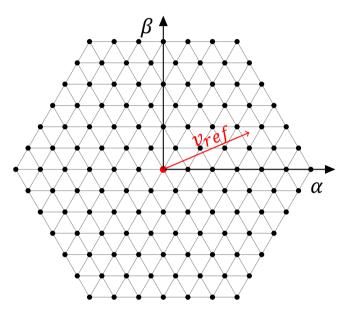

|   |            | 6.2.4 Space-vector domain                                                                                                                          | 86                          |

|   |            | 6.2.5 Selective harmonic elimination                                                                                                               | 87                          |

|   | 6.3        | Conclusion                                                                                                                                         | 87                          |

| 7 | AC         | & DC Fault Ride through Capability                                                                                                                 | 89                          |

|   |            | AC disturbances                                                                                                                                    | 90                          |

|   |            | DC disturbances                                                                                                                                    | 91                          |

|   | 7.3        | Conclusion                                                                                                                                         | 91                          |

| 8 | EM'        | T Modeling                                                                                                                                         | 93                          |

|   | 8.1        | Electromagnetic Transients                                                                                                                         | 95                          |

|   |            | 8.1.1 Simulation Program                                                                                                                           | 95                          |

|   | 8.2        |                                                                                                                                                    | 96                          |

|   |            | 8.2.1 Lumped Circuit elements                                                                                                                      | 96                          |

|   | 0.0        | 8.2.2 Distributed Circuit elements                                                                                                                 | 97                          |

|   | 8.3        | Power electronics in power system                                                                                                                  | 100<br>101                  |

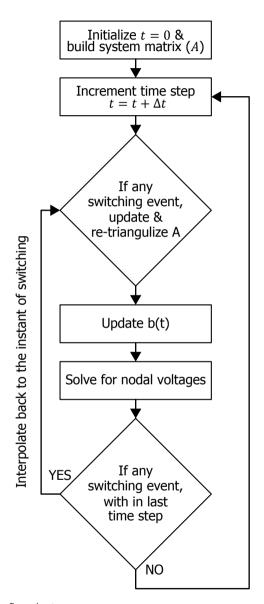

|   |            | 8.3.2 Flow Chart of EMT solver                                                                                                                     | 101                         |

|   | 8.4        |                                                                                                                                                    | 100                         |

|   |            |                                                                                                                                                    | 111                         |

|   | 8.6        | Detailed Models                                                                                                                                    | 112                         |

|   |            | 8.6.1 T-I Full Physics based models                                                                                                                | 112                         |

|   |            | 8.6.2 T-II Detailed IGBT models                                                                                                                    | 112                         |

Contents xiii

|    | 8.7<br>8.8<br>8.9 | Behavioral mode simulations.  8.7.1 Bi-value resistor Model  8.7.2 T-VI Switching Function Models  8.7.3 T-VII Average value model  Time step for simulation  Conclusion | 113<br>113<br>125<br>129<br>131<br>132 |

|----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 9  |                   | ulation                                                                                                                                                                  | 133                                    |

|    |                   | Arm & Module Level Modulations                                                                                                                                           | 133<br>135<br>139<br>143<br>144<br>157 |

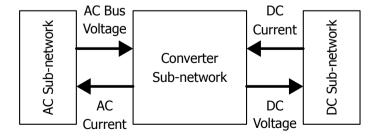

|    | 9.3               | 9.2.3 Conclusion  Application of Models                                                                                                                                  | 157<br>158<br>158                      |

| 10 |                   | <b>cussion and Conclusion</b><br>I Future work                                                                                                                           | <b>171</b><br>174                      |

| Aŗ | pen               | dices                                                                                                                                                                    | 177                                    |

| A  | A.1               | monics in circulating current Capacitor Voltage                                                                                                                          | 1 <b>79</b><br>179<br>181              |

| В  |                   | T Solution Method Compensation Method                                                                                                                                    | <b>186</b><br>186                      |

| C  |                   | Comparison of EMT Models                                                                                                                                                 | <b>187</b><br>187<br>187               |

| D  | D.1<br>D.2<br>D.3 | tel Source Codes  Equivalent ideal Model                                                                                                                                 | 195<br>195<br>198<br>201<br>204        |

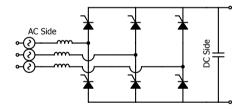

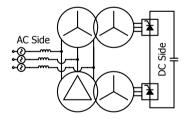

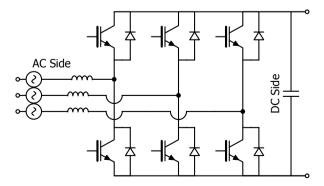

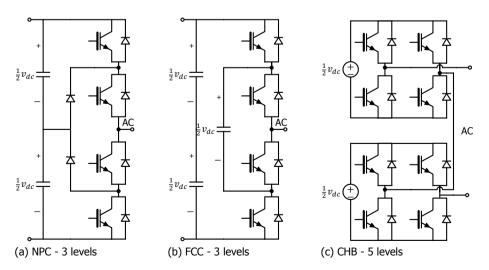

| <ul><li>2.1</li><li>2.2</li><li>2.3</li><li>2.4</li><li>2.5</li><li>2.6</li></ul>           | Representation of segment of a transmission line / cable  Maximum transmission capability of transmission line/cable  AC vs. DC Transmission Cost over distance  Six Pulse bridge converter  Twelve Pulse converter  Two level Voltage Source Converter                                                                                                                                                                                                         | 22<br>23<br>28<br>29<br>29<br>31                               |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

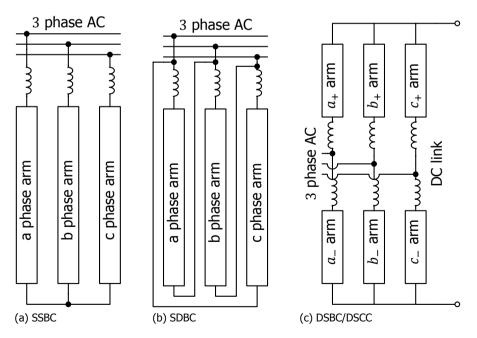

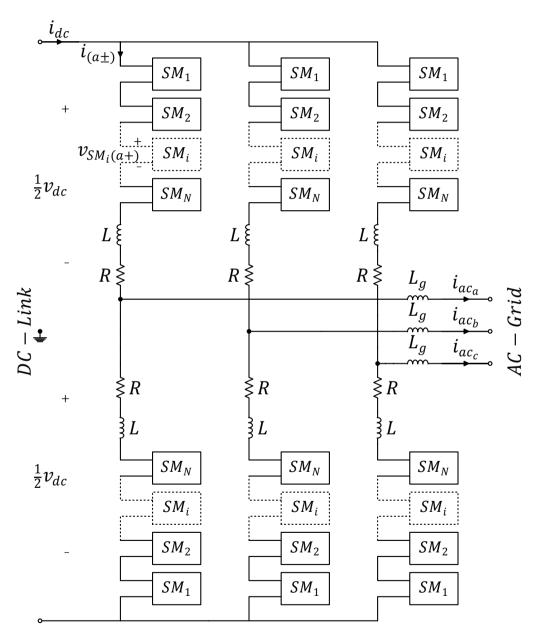

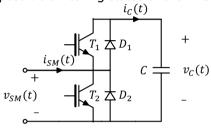

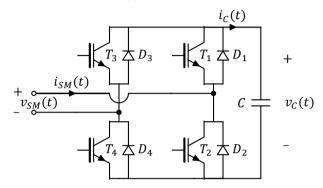

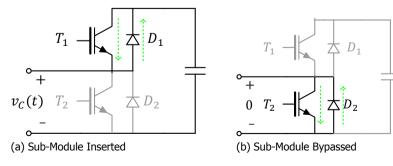

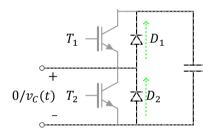

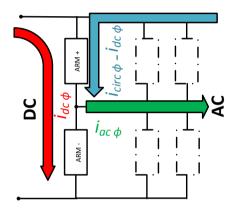

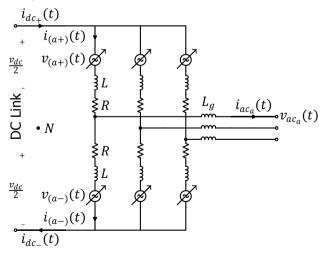

| 2.7 3.1 3.2 3.3 3.4 3.5 3.6 3.7 3.8 3.9 3.10 3.11                                           | Classical Multilevel Topologies  MMC - Classification  Double-star-configured MMC  Sub-Module Half Bridge  Sub-Module Full Bridge  SM - Nominal Operation  Sub-Module Blocked  Current flow in an arm  MMC - currents and voltages  MMC Representation  State Space Model  State Space Model                                                                                                                                                                    | 32<br>36<br>37<br>38<br>39<br>40<br>41<br>44<br>47<br>52<br>52 |

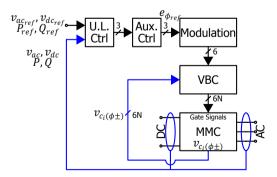

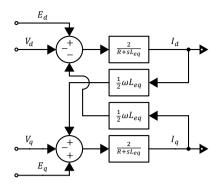

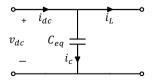

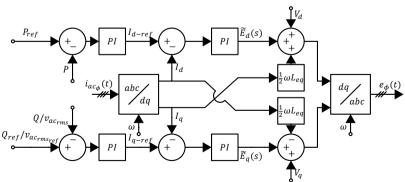

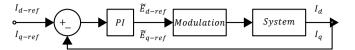

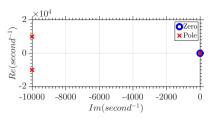

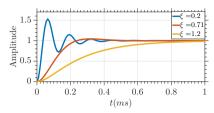

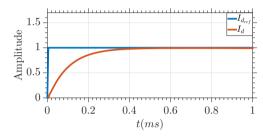

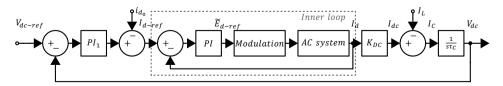

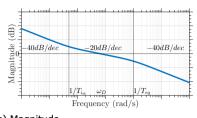

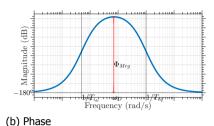

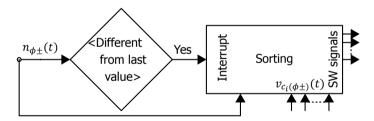

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13 | Control Schematic for a grid-connected MMC Direct control strategy D-Q Axis representation of AC side of MMC DC side representation of MMC D-Q control: Inverter end Inner current loop tuning Modulus optimum tuning Repsonse of step cheange in $I_d$ in detailed model DC voltage control system: Rectifier end Bode plot Interrupt mode: Capacitor voltage ranking Based VBC D-Q Axis representation of circulating current Circulating Current Suppression | 63<br>64<br>66<br>67<br>68<br>69<br>69<br>70<br>71<br>73<br>74 |

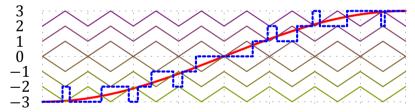

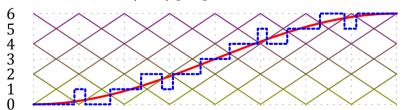

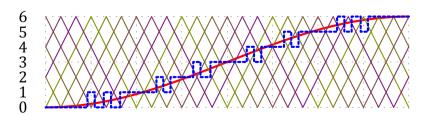

| 6.1<br>6.2<br>6.3<br>6.4                                                                    | Nearest Level Control - 7 Levels  Nearest level modulation - 7 Levels  Carrier wave-forms for phase disposition PWM - 7 levels  Carrier wave-forms for phase opposition disposition PWM - 7 levels                                                                                                                                                                                                                                                              | 80<br>81<br>83                                                 |

| 6.5  | Carrier wave-forms for alternative phase opposition disposition PWM - 7 levels | 83  |

|------|--------------------------------------------------------------------------------|-----|

| 6.6  | Carrier wave-forms for phase-shift PWM - 7 levels                              | 84  |

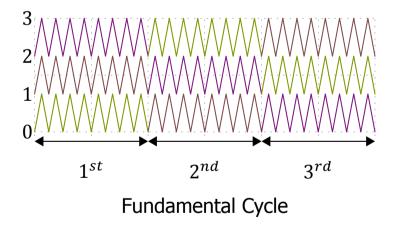

| 6.7  | Carrier wave-form rotation for phase disposition PWM - 3 levels                | 85  |

| 6.8  | Space Vector/ Nearest Vector - 7 levels                                        | 86  |

| 6.9  | Selective harmonic elimination - 7 levels                                      | 87  |

| 0.9  | Selective Harmonic elimination - 7 levels                                      | 0/  |

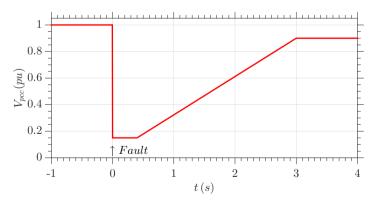

| 7.1  | Typical LVRT requirements                                                      | 90  |

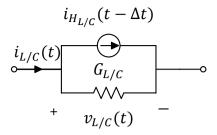

| 8.1  | EMT Equivalent Representation of lumped elements                               | 97  |

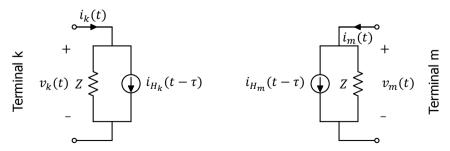

| 8.2  | Transmission line                                                              | 97  |

| 8.3  | Transmission line equivalent representation                                    | 98  |

| 8.4  | Network Splitting                                                              | 103 |

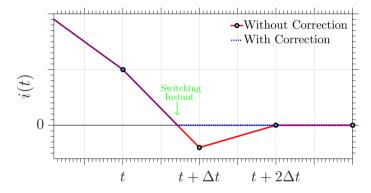

| 8.5  | Out of step switching (diode)                                                  | 104 |

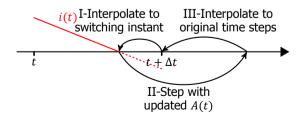

| 8.6  | Out of step switching: Interpolation method                                    | 104 |

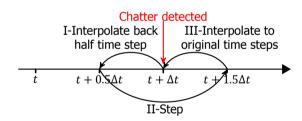

| 8.7  | Chatter: Interpolation method                                                  | 105 |

| 8.8  | EMT solution flow chart                                                        | 106 |

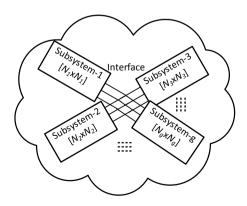

| 8.9  | System Partitioning                                                            | 108 |

| 8.10 | IGBT full Physics model                                                        | 112 |

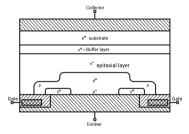

| 8.11 | Detailed IGBT model                                                            | 112 |

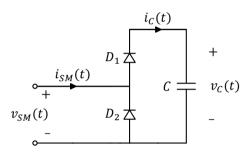

| 8.12 | IGBT and Diode                                                                 | 113 |

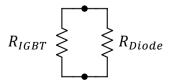

| 8.13 | Bi-value resistor model                                                        | 113 |

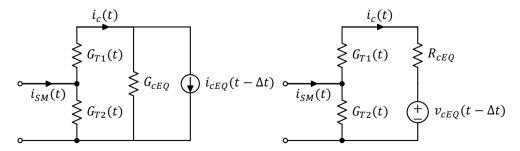

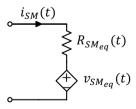

| 8.14 | SM's Equivalent representation                                                 | 114 |

| 8.15 | SM's Equivalent representation                                                 | 114 |

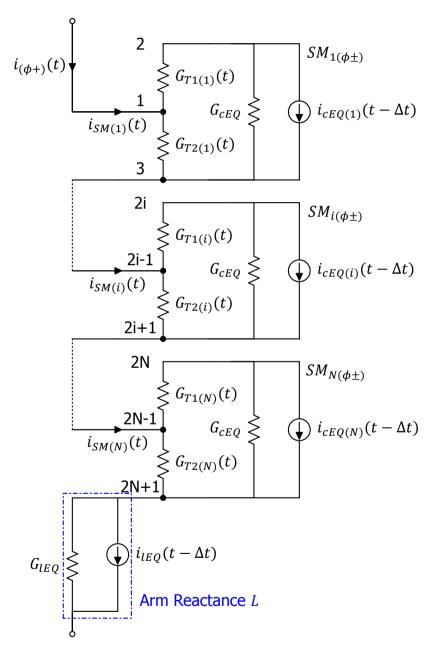

| 8.16 | Equivalent Representation for an arm                                           | 115 |

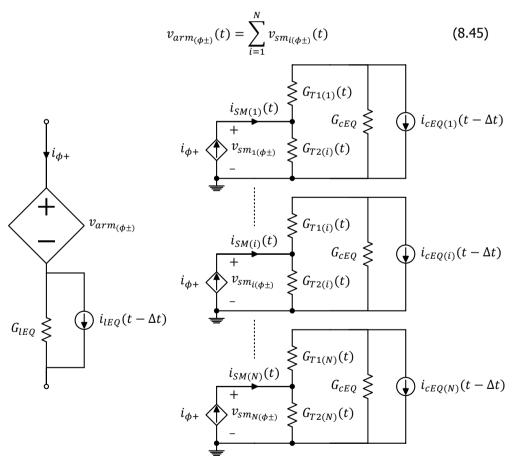

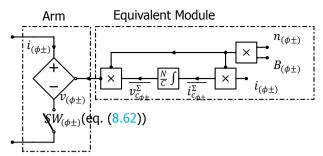

| 8.17 | ISM - Equivalent Representation for an arm                                     | 118 |

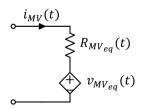

| 8.18 | Sub-module's Thevenin equivalent representation                                | 120 |

| 8.19 | Cascaded Chain of N sub-modules                                                | 121 |

| 8.20 | Arm's Thevenin equivalent representation                                       | 121 |

| 8.21 | Blocked state representation of a SM                                           | 122 |

| 8.22 | TEM with blocked state modeling                                                | 123 |

| 8.23 | SM state after first block                                                     | 126 |

| 8.24 | Sub-module's switching function representation                                 | 126 |

| 8.25 | Arm's switching function representation                                        | 127 |

| 8.26 | Arm's average value representation                                             | 130 |

| 9.1  | PSCAD Model Schematic                                                          | 134 |

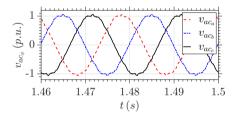

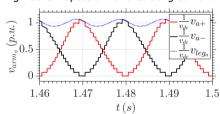

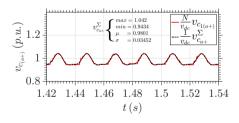

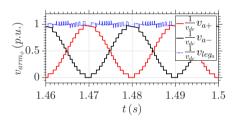

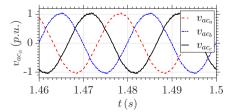

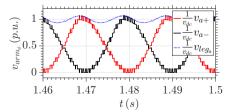

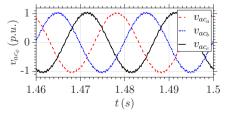

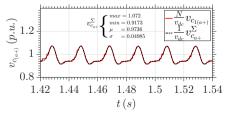

| 9.2  | Three Phase AC voltage at PCC                                                  | 135 |

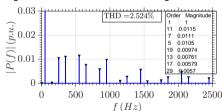

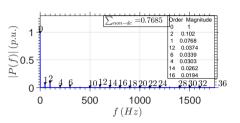

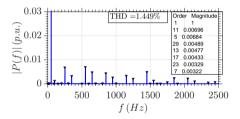

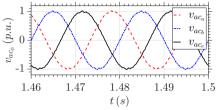

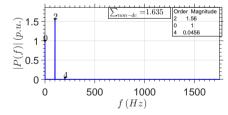

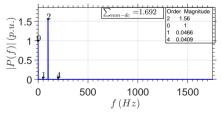

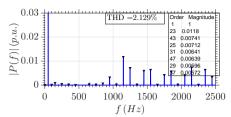

| 9.3  | Harmonic distortion in line-line ac voltage $v_{ab}$                           | 135 |

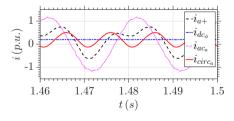

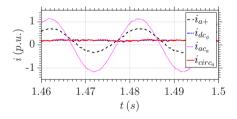

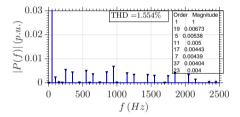

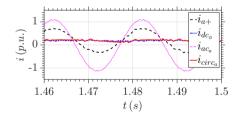

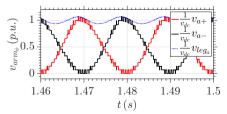

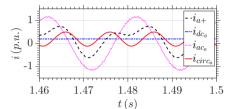

| 9.4  | Currents in MMC                                                                | 135 |

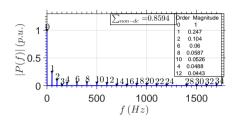

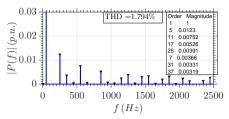

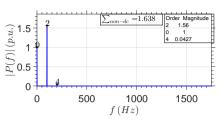

| 9.5  | Spectrum of Circulating Current                                                | 135 |

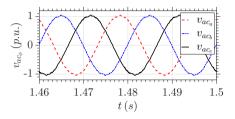

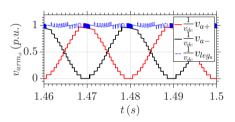

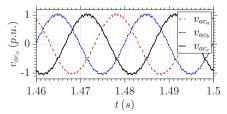

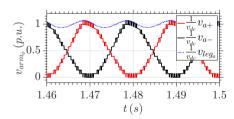

| 9.6  | Arm voltages and cumulative inserted voltage in a leg                          | 135 |

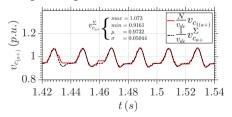

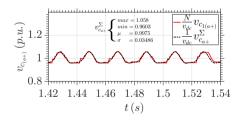

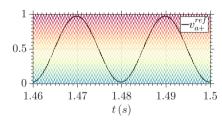

| 9.7  | Capacitor Voltage                                                              | 135 |

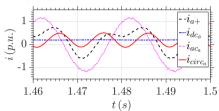

| 9.8  | Three Phase AC voltage at PCC                                                  | 136 |

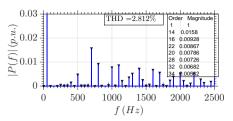

| 9.9  | Harmonic distortion in line-line ac voltage $v_{ab}$                           | 136 |

| 9.10 | Spectrum of Circulating Current                                                | 136 |

| 5.10 | Spectrum of Circulating Current                                                | 100 |

| 9.11 | Arm voltages and cumulative inserted voltage in a leg | 136 |

|------|-------------------------------------------------------|-----|

| 9.12 | Currents in MMC                                       | 136 |

| 9.13 | Capacitor Voltage                                     | 136 |

| 9.14 | Three Phase AC voltage at PCC                         | 137 |

| 9.15 | Harmonic distortion in line-line ac voltage $v_{ab}$  | 137 |

| 9.16 | Spectrum of Circulating Current                       | 137 |

| 9.17 | Arm voltages and cumulative inserted voltage in a leg | 137 |

| 9.18 | Currents in MMC                                       | 137 |

| 9.19 | Capacitor Voltage                                     | 137 |

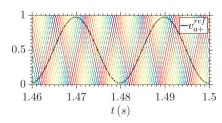

| 9.20 | PD-PWM Carrier waves                                  | 139 |

| 9.21 | Three Phase AC voltage at PCC                         | 139 |

| 9.22 | Spectrum of Circulating Current                       | 139 |

| 9.23 | Arm voltages and cumulative inserted voltage in a leg | 139 |

| 9.24 | Harmonic distortion in line-line ac voltage $v_{ab}$  | 140 |

| 9.25 | Currents in MMC                                       | 140 |

| 9.26 | Capacitor Voltage                                     | 140 |

| 9.27 | APOD-PWM Carrier waves                                | 140 |

| 9.28 | Three Phase AC voltage at PCC                         | 140 |

| 9.29 | Spectrum of Circulating Current                       | 140 |

| 9.30 | Arm voltages and cumulative inserted voltage in a leg | 140 |

| 9.31 | Harmonic distortion in line-line ac voltage $v_{ab}$  | 141 |

| 9.32 | Currents in MMC                                       | 141 |

| 9.33 | Capacitor Voltage                                     | 141 |

| 9.34 | PS-PWM Carrier waves                                  | 141 |

| 9.35 | Three Phase AC voltage at PCC                         | 141 |

| 9.36 | Arm voltages and cumulative inserted voltage in a leg | 141 |

| 9.37 | Capacitor Voltage                                     | 141 |

| 9.38 | Harmonic distortion in line-line ac voltage $v_{ab}$  | 142 |

| 9.39 | Currents in MMC                                       | 142 |

| 9.40 | Spectrum of Circulating Current                       | 142 |

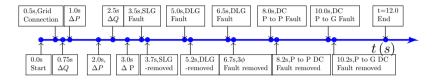

| 9.41 | Time-line of events in simulation                     | 143 |

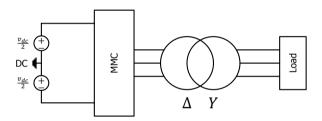

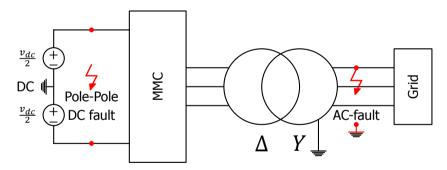

| 9.42 | PSCAD Model Schematic                                 | 143 |

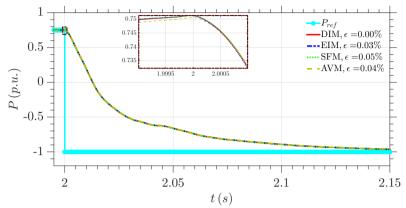

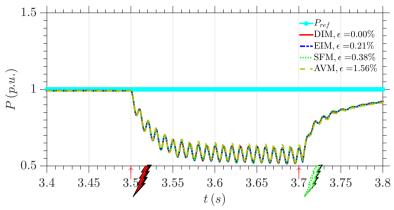

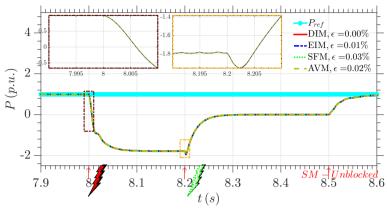

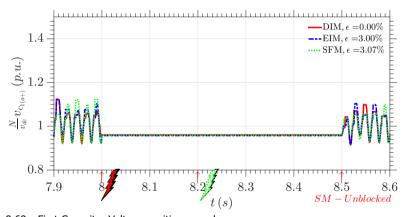

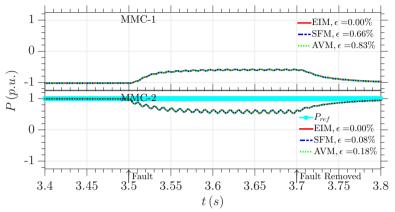

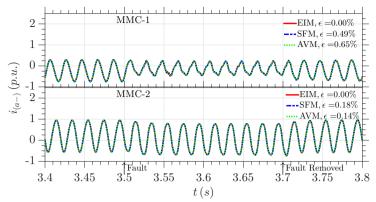

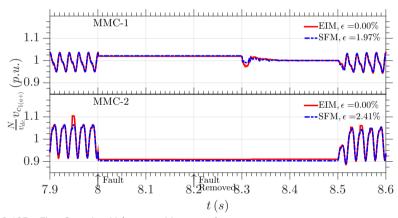

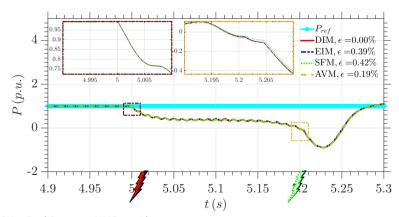

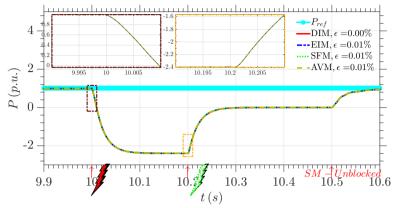

| 9.43 | Real Power at MMC ac-side                             | 145 |

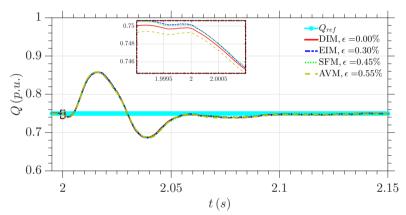

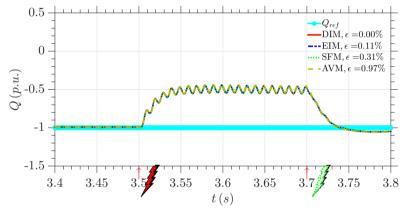

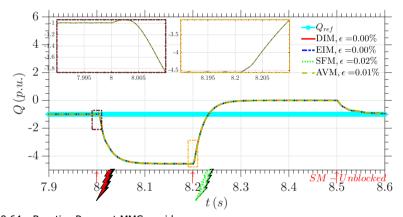

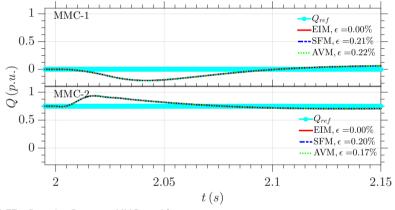

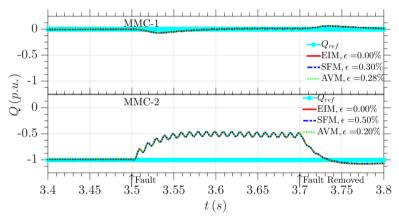

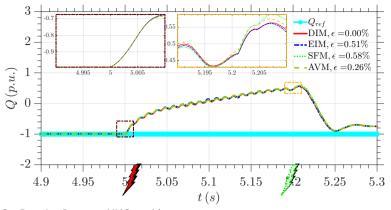

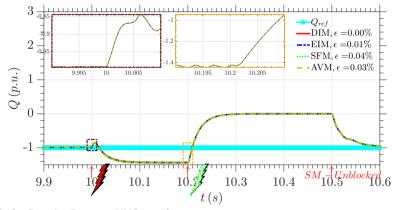

| 9.44 | Reactive Power at MMC ac-side                         | 145 |

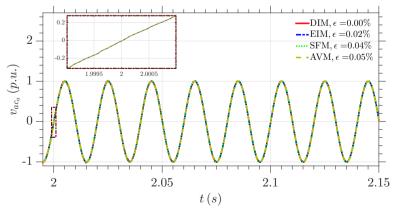

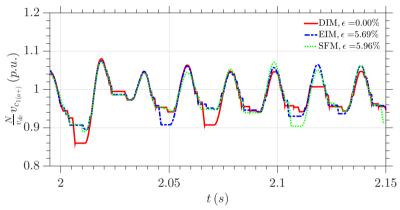

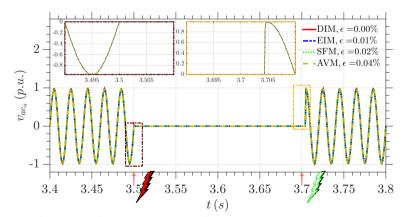

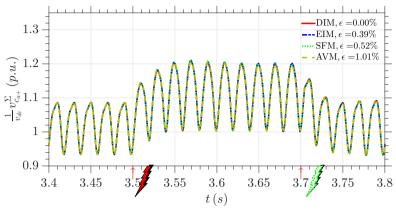

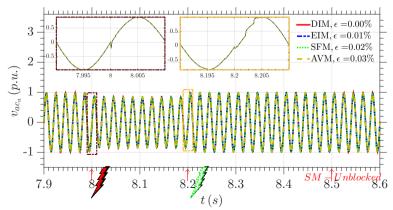

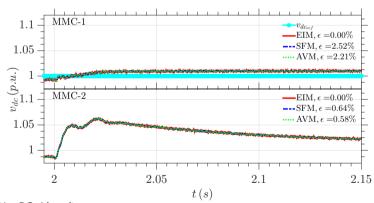

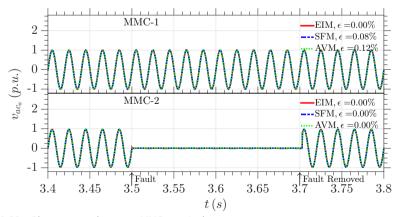

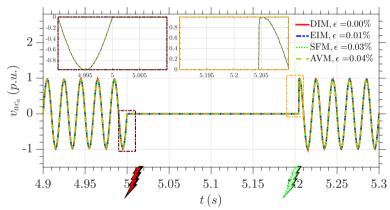

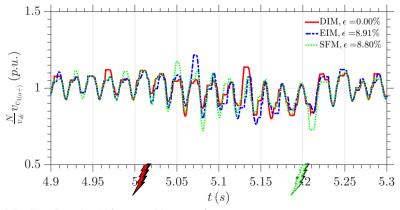

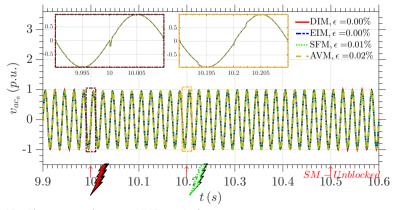

| 9.45 | Phase a ac voltages at MMC terminals                  | 145 |

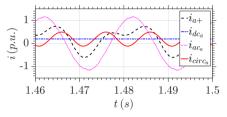

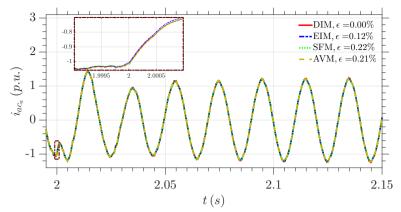

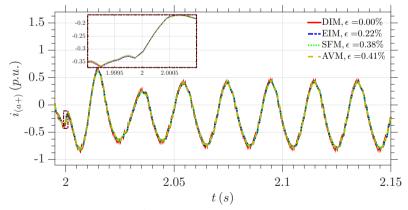

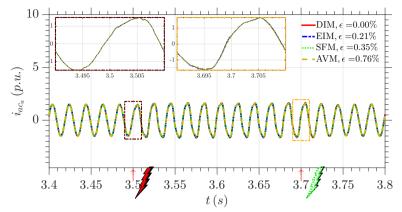

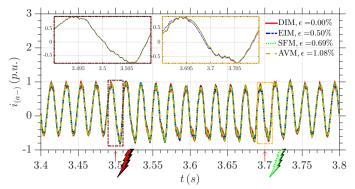

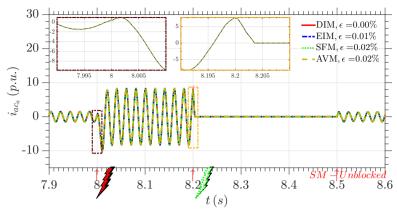

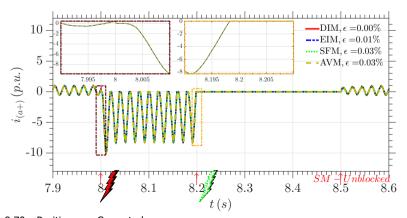

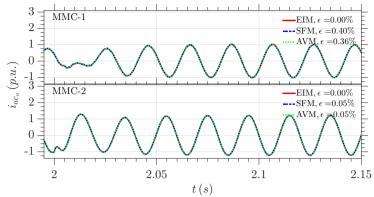

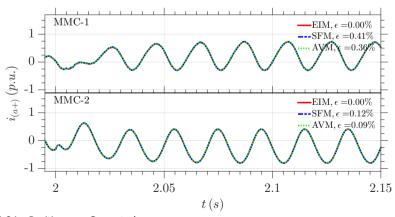

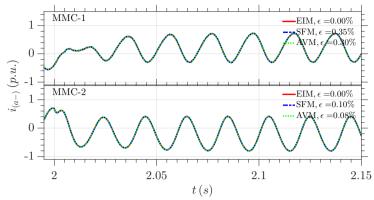

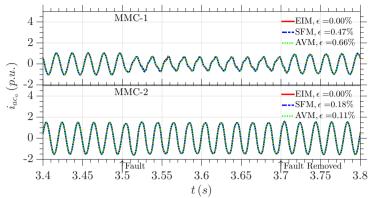

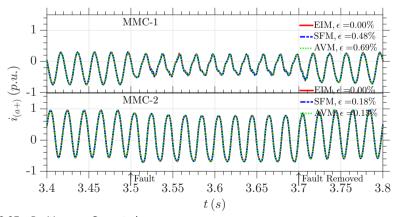

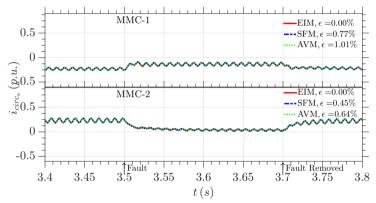

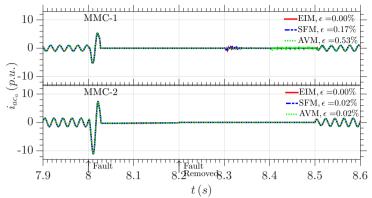

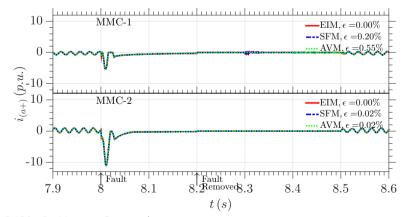

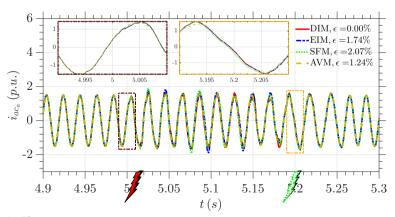

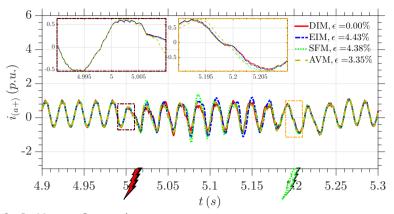

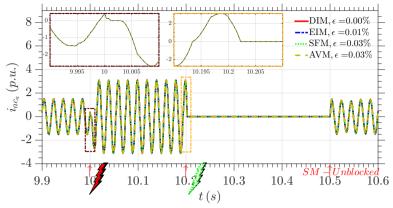

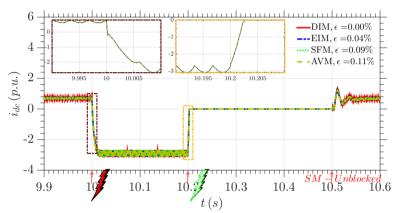

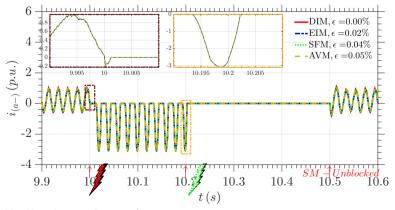

| 9.46 | Phase a ac currents                                   | 146 |

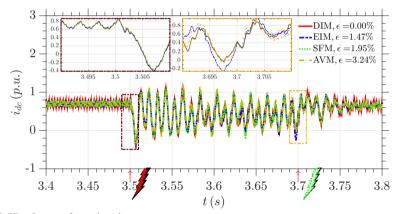

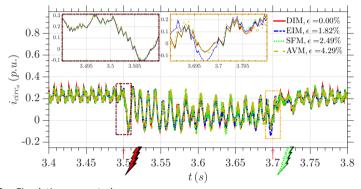

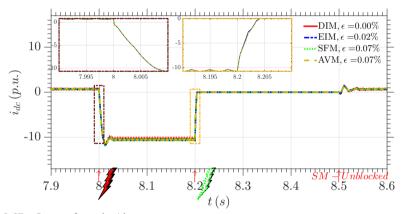

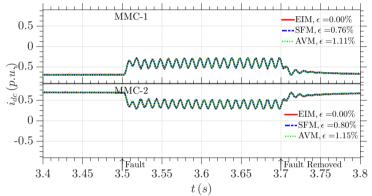

| 9.47 | Current from dc side                                  | 146 |

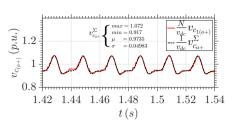

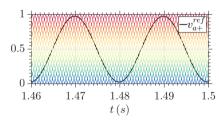

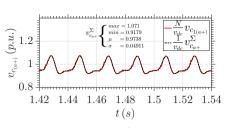

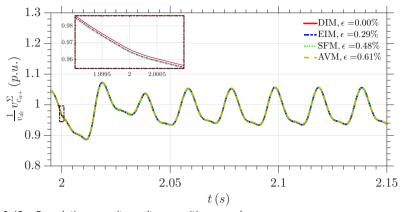

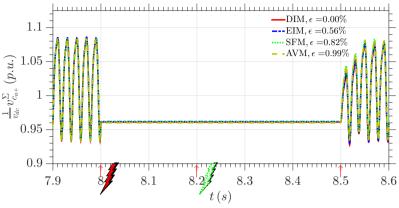

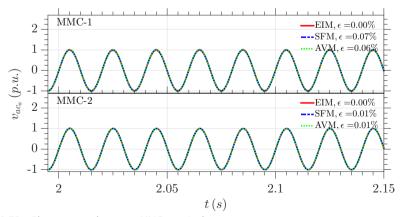

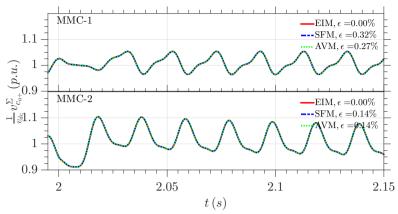

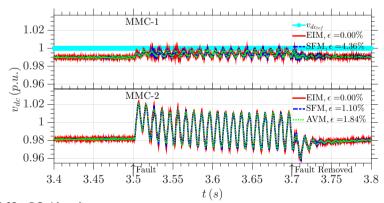

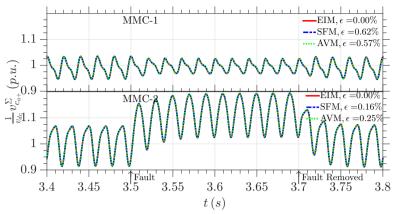

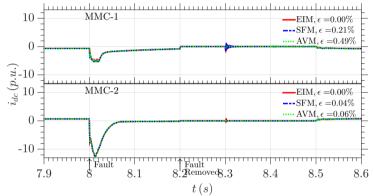

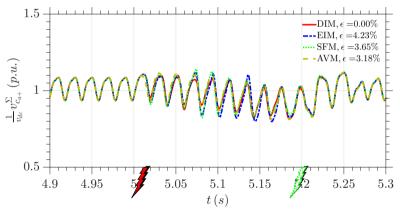

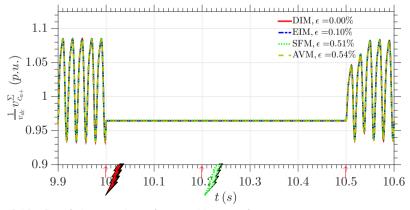

| 9.48 | Cumulative capacitor voltage positive arm phase-a     | 147 |

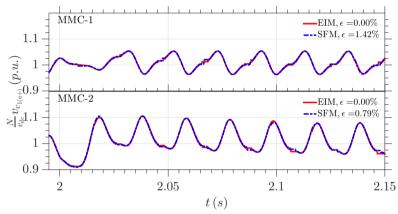

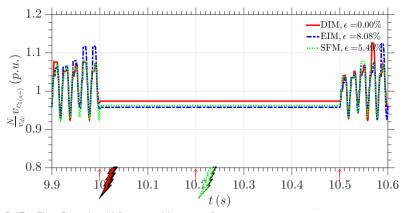

| 9.49 | First Capacitor Voltage positive arm phase-a          | 147 |

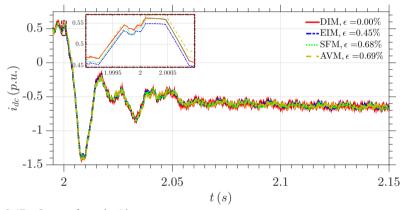

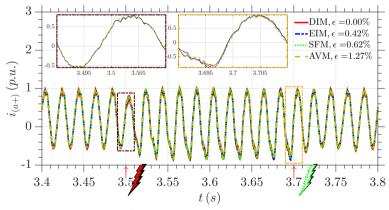

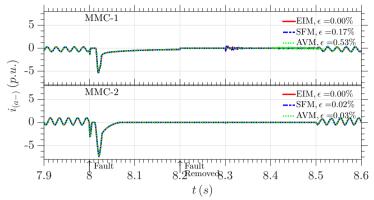

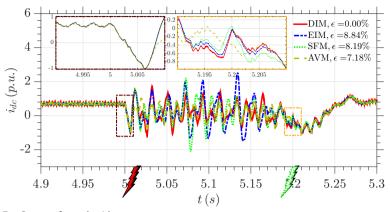

| 9.50 | Positive arm Current phase-a                          | 147 |

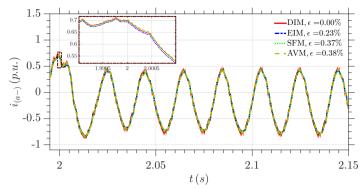

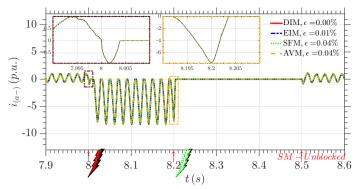

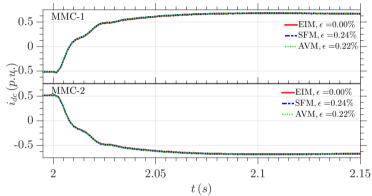

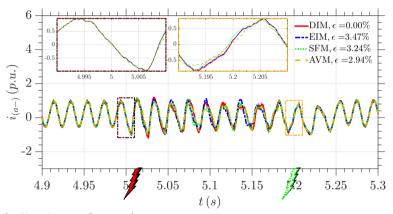

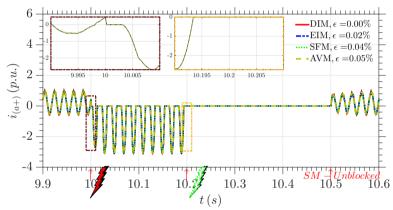

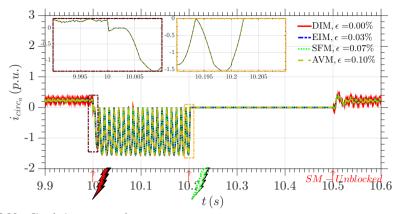

| 9.51 | Negative arm Current phase-a                          | 148 |

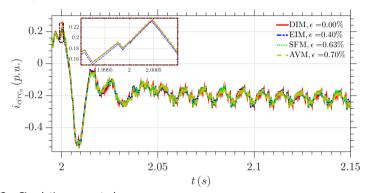

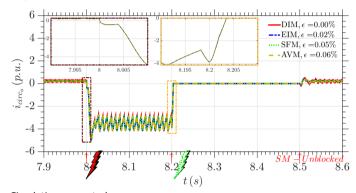

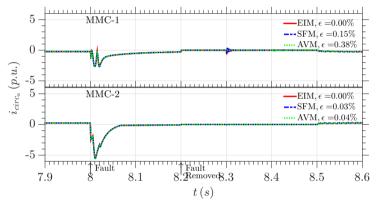

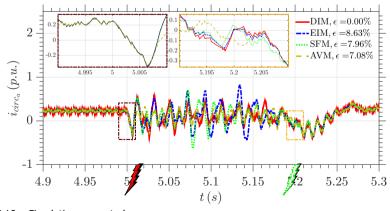

| 9.52 | Circulating current phase-a                           | 148 |

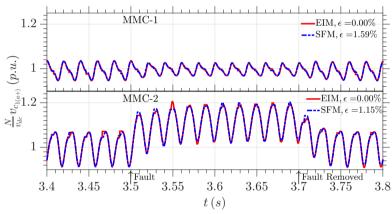

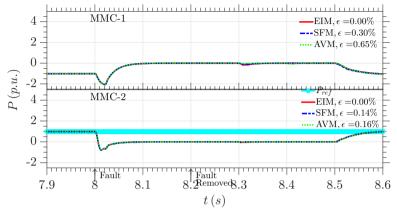

| 9.53 | Real Power at MMC ac-side                             | 149 |

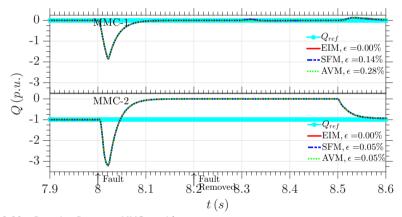

| 9.54 | Reactive Power at MMC ac-side                         | 149 |

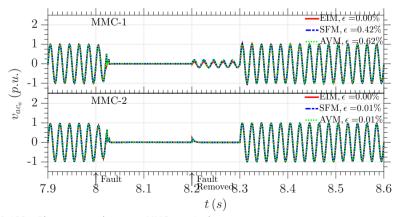

| 9.55 | Phase a ac voltages at MMC terminals                  | 149 |

| 9.56  | Phase a ac currents                               | 150 |

|-------|---------------------------------------------------|-----|

| 9.57  | Current from dc side                              | 150 |

| 9.58  | Cumulative capacitor voltage positive arm phase-a | 151 |

| 9.59  | First Capacitor Voltage positive arm phase-a      | 151 |

| 9.60  | Positive arm Current phase-a                      | 151 |

| 9.61  | Negative arm Current phase-a                      | 152 |

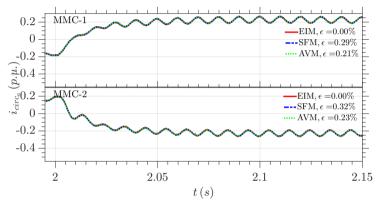

| 9.62  | Circulating current phase-a                       | 152 |

| 9.63  | Real Power at MMC ac-side                         | 153 |

| 9.64  | Reactive Power at MMC ac-side                     | 153 |

| 9.65  | Phase a ac voltages at MMC terminals              | 153 |

| 9.66  | Phase a ac currents                               | 154 |

| 9.67  | Current from dc side                              | 154 |

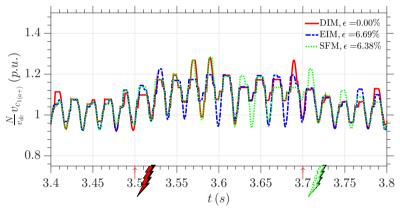

| 9.68  | Cumulative capacitor voltage positive arm phase-a | 155 |

| 9.69  | First Capacitor Voltage positive arm phase-a      | 155 |

| 9.70  | Positive arm Current phase-a                      | 155 |

| 9.71  | Negative arm Current phase-a                      | 156 |

| 9.72  | Circulating current phase-a                       | 156 |

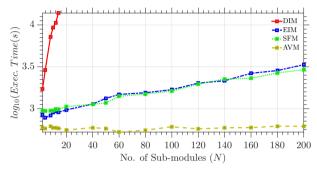

| 9.73  | Computational burden of MMC models                | 157 |

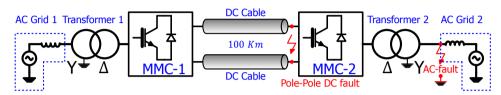

| 9.74  | Symmetric monopole HVDC transmission - schematic  | 158 |

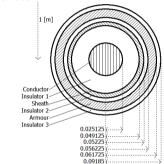

| 9.75  | HVDC cable cross-section                          | 158 |

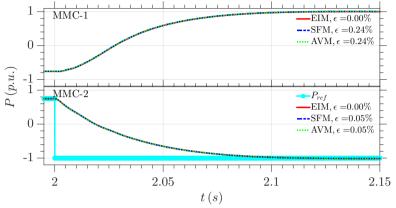

| 9.76  | Real Power at MMC ac-side                         | 159 |

| 9.77  | Reactive Power at MMC ac-side                     | 159 |

| 9.78  | Phase a ac voltages at MMC terminals              | 159 |

| 9.79  | Phase a ac currents                               | 160 |

| 9.80  | Current from dc side                              | 160 |

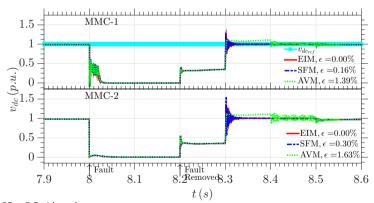

| 9.81  | DC side voltage                                   | 160 |

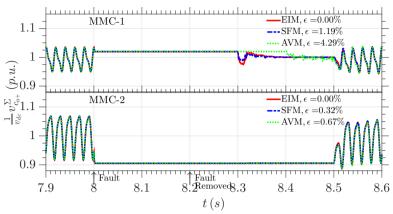

| 9.82  | Cumulative capacitor voltage positive arm phase-a | 161 |

| 9.83  | First Capacitor Voltage positive arm phase-a      | 161 |

| 9.84  | Positive arm Current phase-a                      | 161 |

| 9.85  | Negative arm Current phase-a                      | 162 |

| 9.86  | Circulating current phase-a                       | 162 |

| 9.87  | Real Power at MMC ac-side                         | 163 |

| 9.88  | Reactive Power at MMC ac-side                     | 163 |

| 9.89  | Phase a ac voltages at MMC terminals              | 163 |

| 9.90  | Phase a ac currents                               | 164 |

| 9.91  | Current from dc side                              | 164 |

| 9.92  | DC side voltage                                   | 164 |

| 9.93  | Cumulative capacitor voltage positive arm phase-a | 165 |

| 9.94  | First Capacitor Voltage positive arm phase-a      | 165 |

| 9.95  | Positive arm Current phase-a                      | 165 |

| 9.96  | Negative arm Current phase-a                      | 166 |

| 9.97  | Circulating current phase-a                       | 166 |

| 9.98  | Real Power at MMC ac-side                         | 167 |

| 9.99  | Reactive Power at MMC ac-side                     | 167 |

| 9.100 |                                                   | 167 |

| J.100 | Thase a de voltages at mine terminais             | 10/ |

|       | Phase a ac currents                               | 168 |

|-------|---------------------------------------------------|-----|

|       | Current from dc side                              | 168 |

|       | DC side voltage                                   | 168 |

|       | Cumulative capacitor voltage positive arm phase-a | 169 |

|       | First Capacitor Voltage positive arm phase-a      | 169 |

|       | Positive arm Current phase-a                      | 169 |

| 9.107 | Negative arm Current phase-a                      | 170 |

| 9.108 | Circulating current phase-a                       | 170 |

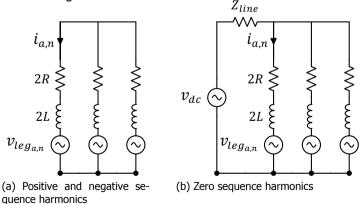

| A.1   | Circuit for circulating current                   | 183 |

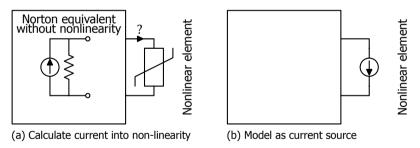

| B.1   | Compensation Method                               | 186 |

| C.1   | Real Power at MMC ac-side                         | 187 |

| C.2   | Reactive Power at MMC ac-side                     | 188 |

| C.3   | Phase a ac voltages at MMC terminals              | 188 |

| C.4   | Phase a ac currents                               | 188 |

| C.5   | Current from dc side                              | 189 |

| C.6   | Cumulative capacitor voltage positive arm phase-a | 189 |

| C.7   | First Capacitor Voltage positive arm phase-a      | 189 |

| C.8   | Positive arm Current phase-a                      | 190 |

| C.9   | Negative arm Current phase-a                      | 190 |

| C.10  | Circulating current phase-a                       | 190 |

| C.11  | Real Power at MMC ac-side                         | 191 |

| C.12  | Reactive Power at MMC ac-side                     | 191 |

| C.13  | Phase a ac voltages at MMC terminals              | 191 |

| C.14  | Phase a ac currents                               | 192 |

| C.15  | Current from dc side                              | 192 |

| C.16  | Cumulative capacitor voltage positive arm phase-a | 192 |

| C.17  | First Capacitor Voltage positive arm phase-a      | 193 |

| C.18  | Positive arm Current phase-a                      | 193 |

| C.19  | Negative arm Current phase-a                      | 193 |

| C 20  | Circulating current phase-a                       | 194 |

# List of Tables

| 1.1                                                          | Climate Change: International Treaties and Targets                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15                                                                                                    |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| 2.1                                                          | Parameters of Cable/Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23                                                                                                    |

| 3.1<br>3.2<br>3.3                                            | MMCs vs. Classical VSCs Operation of Half Bridge Sub-Module Operation of Full Bridge Sub-Module                                                                                                                                                                                                                                                                                                                                                                                                      | 35<br>38<br>39                                                                                        |

| 8.1<br>8.2<br>8.3                                            | Truth table for Switching functions  EMT Models for MMC: Summary  EMT Models for MMC: Requirements                                                                                                                                                                                                                                                                                                                                                                                                   | 126<br>132<br>132                                                                                     |

| 9.11<br>9.12<br>9.13<br>9.14<br>9.15<br>9.16<br>9.17<br>9.18 | MMC <sub>14</sub> - Parameters Case I: Details for system Case I: Switching Details Case II: Switching Details Case III: Switching Details Arm Level Modulation: Findings Arm Level Modulation: Conclusion Case I: Details for system Case IV: Switching Details Case V: Switching Details Case VI: Switching Details Module Level Modulation: Findings Module Level Modulation: Findings MMC <sub>14</sub> - Parameters EMT Simulation accuracy EMT Model Use System Parameters DC Cable parameters | 134<br>135<br>136<br>137<br>138<br>138<br>139<br>140<br>141<br>142<br>142<br>143<br>157<br>158<br>158 |

|                                                              | Relative Computational Load                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 170<br>173                                                                                            |

# List of Acronyms

AC Alternating Current.

APOD-PWM Alternative Phase Opposition Disposition PWM.

AVM Average Value Model.

C-PWM Multi-carrier PWM methods.

CCC Capacitor Commutated Converter.

CCSC Circulating current suppression control.

CHB Cascaded H-bridge Converter.

CIGRE Conseil International des Grands Reseaux Elec-

triques.

CSC Current Source Converter.

CTL Cascaded Two-Level Converter.

DC Direct Current.

DIM Detailed Ideal Model.

DLG Double Line to Ground.

DQ Direct-Quadrant.

DSBC Double Star Bridge Cell.

DSCC Double Star Chopper Cell.

EIM Equivalent Ideal Model.

EMC ElectroMagnetic Compatibility.

EMF ElectroMotive Force.

EMT ElectroMagnetic Transients.

EMTDC ElectroMagnetic Transients for DC. EMTP ElectroMagnetic Transients Program.

FACTS Flexible AC transmission system.

FBSM Full Bridge Sub Module.

FCC Flying Capacitor Converter.

FFT Fast Fourier Transform.

HBSM Half Bridge Sub Module.

HVAC High Voltage Alternating Current. HVDC High Voltage Direct Current.

IGBT Insulated-gate bipolar transistor. ISM Isolated sub-module model.

KCI Kirchhoff's current law. KVL Kirchhoff's voltage law.

LCC Line Commutated Converter.

LTI Linear time invariant.

LU Lower Upper.

**LVRT** Low Voltage Ride Through.

MMC Modular Multilevel converter.

MO Modulus Optimum.

NI C Nearest Level Control. NLM Nearest Level Modulation.

**NPC** Neutral Point Clamped converter.

NVC Nearest Vector Control.

OHL Over Head Lines.

PCC Point of Common Coupling. PD-PWM Phase Disposition PWM. **PGDC** Pole to Ground DC. PΙ Proportional Integral. PLL Phase-Locked Loop.

Phase Opposition Disposition PWM. POD-PWM

PPDC Pole to Pole DC.

**PSCAD** Power System Computer Aided Design.

рu per unit.

PWM Pulse Width Modulation.

**RMS** Root Mean Square.

SCR Short Circuit Ratio.

SDBC Single Delta configured Bridge Cell.

SFM Switching Function Model. SHE Selective Harmonic Elimination. SIL Surge Impedance Loading.

SLG Single Line to Ground.

SM Sub Module.

SO Symmetric Optimum.

SPICE Simulation Program with Integrated Circuit Em-

Single Star configured Bridge Cell. **SSBC**

SSSL Steady-State Stability Limit.

STATCOM Static compensator. Space Vector Modulation. SVM

List of Acronyms 11

| THD        | Total Harmonic Distortion.                              |

|------------|---------------------------------------------------------|

| VBC<br>VSC | Voltage Balancing Control.<br>Voltage Source Converter. |

| ZVRT       | Zero Voltage Ride Through.                              |

# List of Symbols

$\eta_{SM_i(\phi\pm)}[t] \& \beta_{SM_i(\phi\pm)}[t]$  Switching functions for SM operation.

$\overline{P_{ac_{\phi}}}$  Average power on ac side.

$\overline{P_{dc_{th}}}$  Average power on dc side.

$B_{(\phi^+)}[t]$  Block Index.

C Sub-module's Capacitance.

C' Line/Cable per unit length shunt capacitance.

D1 HBSM upper diode.

D2 HBSM lower diode.

$E_{MMC}$  Nominal stored energy in MMC.

G' Line/Cable per unit length shunt conductance.

L Arm reactance.

L' Line/Cable per unit length inductance.

$L_q$  Converter transformer reactance.

N Number of sub-modules in an arm..

$P_{\phi}^{\Delta}(t)$  Difference of instantaneous power flow in positive and negative arms.

$P_{\phi}^{\Sigma}(t)$  Sum of instantaneous power flow in positive and negative arms.

$P_{\pm_{\phi}}(t)$  Instantaneous power flow in an arm.

R Arm resistance.

R' Line/Cable per unit length resistance.

T1 HBSM upper IGBT.

T2 HBSM lower IGBT.

$\hat{k}_{\phi}$  Current modulation index.

$\hat{m}_{\phi}$  Voltage modulation index.

$\boldsymbol{\phi}\$  subscript indicates the phase leg of converter.

$\pm\,$  subscript addresses the arms of a phase leg.

$e_{\phi}(t)$  Internal emf.

i subscript refers the position of sub-module in an arm.

$i_{Harm._{\phi}}^{\Sigma}(t)$  Harmonics in circulating current.

$i_{(\phi+)}$  Arm current.

$i_{SM}/i_{SM_i(\phi\pm)}$  Current in sub-module.

$i_{ac_{\phi}}(t)$  AC Current.

$i_{circ_{\phi}}$  Circulating current.

$i_c/i_{c_i(\phi\pm)}$  Current in sub-module's capacitor.

$i_{dc_{\phi}}$  DC component in arm current.

$i_{dc}$  DC current.

$i_{diff_{\phi}}$  AC current component in an arm.

$n_{(\phi\pm)}(t)$  Insertion Index.

$v_{c_{\phi+}}^{\Sigma}$  Cumulative capacitor voltage in an arm.

$v_c/v_{c_i(\phi\pm)}$  Sub-module capacitor voltage.

$v_{(\phi^+)}$  Voltage inserted in an arm.

$v_{SM}/v_{SM_i(\phi\pm)}$  Voltage inserted by sub-module.

$v_{ac_{\phi}}(t)$  AC Voltage.

$v_{circ_{\phi}}$  Arm voltage due to circulating current.

$v_{dc}\,$  Voltage across dc terminals.

$v_{leg_{\phi}}$  Voltage inserted in a phase leg.

$i^0_{\ ac}(t)$  Zero-sequence component in ac current.

# Introduction

This introductory chapter serves to state the background, the motivation behind the work, primary objectives and defines the layout of the Thesis.

#### **1.1.** Motivation and Past Work

Changing climate conditions, limited fossil fuel resources and ever increasing global thirst for energy, demand for major transformations in the energy landscape. In the last century, electric power has gradually evolved as the primary medium of energy for household and commercial consumption. With electricity sector accounting for around 24.6% of global greenhouse gas emissions [3], international treaties [1, 2, 4], summarized in table 1.1, are pushing for reduced dependency on fossil fuels and deployment of renewable energy sources. An eco-friendly electrical generation with renewable resources, e.g. hydro, the wind and solar, offers a clean and sustainable solution to the energy demand. However, integration of these resources into the traditional AC power grid poses various challenges. In most cases, renewable assets are concentrated in remote areas. In particular, for off-shore

Table 1.1: Climate Change: International Treaties and Targets

| Treaty         | Targets                                                                                                                                |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Kyoto Protocol | "Stabilization of greenhouse gas concentrations in the atmosphere"[1]                                                                  |

| EU 20-20-20    | 20% cut in greenhouse emissions, 20% energy from renewables and 20% increase in energy efficiency ( <i>Targets for the year 2020</i> ) |

| COP-21         | "Holding the increase in the global average temperature to well below $2^{\circ}\mathcal{C}''[2]$                                      |

wind farms, long distance submarine power cables are required for water crossings. Transmission of bulk power over long distances especially via underground and sub-sea cables turns out to be a challenging task for high-voltage alternating current (HVAC) transmission, where the innate reactance of overhead lines or cables tend to limit power transmission capability. In addition to this, integration of intermittent renewable assets, such as wind energy, with weak AC links presents additional problems.

An alternative for HVAC is high-voltage direct current (HVDC) transmission which unaffected by reactive elements of line, has theoretically no limit on transmission distance and provides a controllable mode of transmission. However, HVDC requires converters at both ends to convert from AC to DC and vice versa. Historically absence of reliable and efficient converters has been the bottleneck in the development of HVDC. Nevertheless, the recent invention of DC/AC cascaded modular multilevel converters by Lesnicar and Marquardt [5–8], offers an efficient and economically viable solution for grid integration of remote resources and bulk power transfer. This converter topology with its inherent modular and scalable configuration promises to mitigate the limitations of existing dc-ac converter technologies and is gradually becoming the choice for HVDC converters.

Modular multilevel converters (MMC) are becoming the technology of choice in HVDC power transmission for grid integration of large-scale offshore wind farms and multi-terminal HVDC transmission schemes. Each phase of an MMC HVDC terminal can consist of several hundreds of identical sub-modules that switch a module capacitor in and out of the circuit at different times to synthesize the reguired ac-side voltage waveform. This operation requires sophisticated control and modulation techniques. Besides this, the application-specific design of converter system presents a need for its accurate modeling and computer simulation together with the associated power system, which is essential for efficient design, validation of complex control systems, and operational planning. In power electronic systems, switching operation is integral and the prime source of transients in the system. Therefore for MMCs, Electromagnetic transients (EMT)-type solvers are utilized for the simulations. These solvers employ the solution method proposed by Dommel [9] that uses the trapezoidal rule of integration and Bergeron's method [10] for representation of lumped and distributed circuit elements in the form of time-varying current sources and conductances respectively. With this equivalent representation, step by step time domain solution of the system is obtained using nodal analysis. However, due to the non-linear characteristics of semiconductor devices and subsequent time-dependent topology, power electronic systems tend to be computationally intensive with this solution method [11, 12].

In conventional thyristor and IGBT based converters, individual valves are composed of series-connected semiconductor devices which operate simultaneously and for purposes of EMT modeling behave as a single component. To the contrast, MMCs for HVDC applications employ hundreds of sub-modules with an independent operation. Therefore, MMC simulation with explicit modeling for each semiconductor device has an enormous computational load.

To address the need for efficient MMC models existing literature presents several levels of equivalent representation. Fast and accurate simulations of EMT phenomena require models that capture all of the operating modes of the converter and allow for the natural development of its dynamics.

Such efficient models from the existing literature include:

- A simplified average model for the steady-state and dynamic behavior of MMC was investigated first by Teeuwsen [13]; however the article provides little detail on the model itself.

- Based on the nested fast and simultaneous method [14], Gnanarathna et al. [15] proposed an equivalent detailed model for MMC where all sub-modules in an arm are modeled with their Thevenin's equivalence. This model offers superior computational speed while retaining information for each sub-module. However, this representation does not inherently capture blocked state of operation of sub-modules. References [16–24] validate and present enhanced versions of this detailed equivalent model. Similar to this, Xu et al. [25] proposed an accelerated model, which partitions sub-modules from the rest of the system and mimics the interconnection with dependent sources. Reference [23, 26] validate and present enhanced versions of this model.

Both of these representations split the computation associated with individual sub-module/arm and rest of the system. Thus, they exploit the computational efficiency of solving numerous small matrices or a set of algebraic equations instead of one large matrix and drastically increase the computational speed.

- Switching functions models for MMC are presented in [27–31]. Articles [28–30] utilize state-space formulation which is computationally intensive and not suitable for fault studies in an HVDC system. While articles Adam et al. [31] proposes a generalized switching function model that uses binary functions to model the individual operation of sub-modules with high computational efficiency.

- To address the need for very fast modeling representation, various simplified average models for MMC have been proposed in the literature [18, 32–47]. Articles [18, 32–34] extend the classical average modeling technique for 2/3-level converters [48] to MMC and represent its terminal dynamics using controlled sources; articles [35, 36] presents enhanced versions of this model, capable of simulating blocked state of operation. References [37, 38] reduce MMC to an equivalent buck-boost circuit. These representations do not inherently model internal dynamics of the converter and lack natural development of its internal and external dynamics, which are governed by arm currents, and sub-module capacitors, and therefore are only suitable for the stationary operation of the converter.

Furthermore, articles [39, 40] present continuous models of converter based on state-space formulation and differential equation respectively; articles [41, 42] extends the latter model for the modeling capability of the *blocked* state.

These existing models provide a faithful representation of the terminal behavior of

18 1. Introduction

1

converter. However, these models do not inherently capture all operating states of converter but instead, utilize fictitious diodes and switches to mimic *blocked* state of operation. Furthermore, the literature lacks an independent collective comparison of the equivalent models.

Therefore, this thesis aims to enhance and develop MMC equivalent representations that model all states of operation and provide a thorough review and objective comparison, regarding relative accuracy and computational efficiency, of the models that are suitable for EMT studies.

## 1.2. Objective

This thesis is aimed towards gaining insight in of modular multilevel converters for high-voltage direct current applications. The prime objective is to develop computationally efficient models for modular multilevel converters for simulation of electromagnetic transients.

#### 1.2.1. Specific Objective

- Develop the understanding of operating principles of MMC.

- Investigate various control and modulation techniques for MMC.

- Investigate and develop different levels of simplified equivalent models for MMC.

- Validate proposed models of the converter regarding accuracy and computational speed against a detailed representation.

## 1.3. Main Contributions

The main contributions of this thesis are:

- Theoretical analysis of MMC: The thesis presents a detail mathematical formulation of internal and external dynamics of converter and optimization of the size of converter components. Furthermore, building on this mathematical formulation the thesis presents an overview of control and modulation techniques.

- Enhancement equivalent models: The primary contribution of this thesis is an

independent study of existing equivalent models of MMC and enhancement in

these models that enable inherent modeling all operating states of the converter

and allow for the natural development of all of its internal and external dynamics

under stationary and transient conditions.

- Comprehensive comparison of equivalent models: The thesis presents a detailed comparison regarding accuracy and computation speed of the equivalent models under various operating conditions.

## **1.4.** Report outline

The report is structured as follows:

- Chapter 2 gives an overview of the need for HVDC systems against HVAC and presents a brief account of power converter technologies besides modular multilevel converters.

- Chapter 3 introduces the basic structure of MMC converter, its operating principle and develops a continuous analytical model. Furthermore, circulating currents and capacitor voltage ripple associated with converter arms are analyzed here.

- Chapter 4 provides brief mathematical derivations for optimum sizing of MMC components for given ratings and constraints.

- Chapter 5 provides a brief description of the control techniques for grid-connected converters including voltage balancing and circulating current suppression control methods for MMCs. Furthermore, a linear time-invariant model of MMC is derived and subsequently utilized in optimal tuning of MMC's dc voltage and ac-power flow side controllers.

- Chapter 6 gives a review of modulation techniques for the MMCs.

- Chapter 7 presents a very short account of the operation of MMC under AC and DC fault scenarios.

- Chapter 8 delves into the solution methods for electromagnetic transient simulations. Different levels of EMT models for MMCs from existing literature are derived and enhanced in this chapter.

- Chapter 9 presents and compares PSCAD/EMTDC simulation results for various equivalent models of MMCs under various transient conditions.

- Finally, Chapter 10 completes the thesis with discussion and drawn conclusions.

## **1.5.** Publication

The list of publications from this thesis is as follows:

Conference Presentation: **S. Khan**, J. A. Suul, E. Tedeschi and M. Jafar, "Blocking capability for Switching Function and Average Models of Modular Multilevel Converters", *Environment and Electrical Engineering (EEEIC)*, 2016 16th International Conference on, Florence, Italy, 7-10 June, 2016.

# 2

# Background

AC and DC mode of transmission are individually viable for different applications. With generation and consumption in AC, power converters are essential for HVDC transmission. This chapter serves to give a brief account and comparison of HVAC and HVDC transmission. A short overview of the two most frequently used types of power converters is also presented here.

#### 2.1. Modes of Transmission

Power transmission forms the critical link of connecting consumers to generation. Distributed generation and an emphasis to tap into renewable resources are pushing conventional methods of transmission to its limits. This section presents a brief account of the two modes of transmission.

## **2.1.1.** High Voltage Alternating Current Transmission

Conventional high-voltage alternating current (HVAC) transmission systems form the backbone of electric power system. In AC systems, transformers are utilized to step up/down voltages and transfer of energy is achieved by overhead transmission lines or underground/submarine cables. Easy transformation capability, together with generation and consumption of electricity in AC has been the driving forces behind widespread use of AC systems.

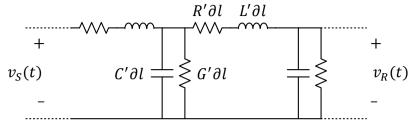

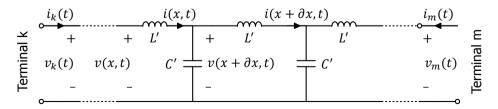

For AC, the transmission line is modeled by four parameters i.e. series resistance R', inductance L', shunt capacitance C' and shunt conductance G' which are distributed along the line as illustrated in fig. 2.1. Resistance R' is dependent on conductor's resistivity and dimensions. The skin effect associated with AC tends to make R'

Figure 2.1: Representation of segment of a transmission line / cable

higher than that for a DC system. Series inductance L' in line is attributed to the internal and external magnetic fields. Mutual and ground coupling of conductors results in the parasitic shunt capacitance C'. Insulating medium, dimension and relative position of conductors determine these reactive parameters of line. Shunt capacitance is further affected by the conductor's proximity to the ground. Furthermore, leakage currents between conductors or between conductors and ground give rise to the shunt conductance G'.

Similar to the overhead lines (OHL) parasitic elements are present in underground and submarine cables. However, different structure, arrangement and insulation materials in cables imply a significant difference in values [49]. In comparison to OHL, conductors in cables are relatively closer to each other and the ground. Moreover, cables employ solid or a combination of solid/ liquid dielectrics which have higher permittivity, unlike OHL where the air is the dielectric medium. These conditions subsequently lead to higher shunt capacitance and lower series inductance in cables as compared to OHL.

These parameters characterize the transmission line/cable and define the power transmission capability. For an AC transmission line/cable power carrying capacity is limited by [50]:

- 1. Steady-state stability.

- 2. Thermal limits.

- 3. Voltage limits.

#### Steady-state stability

The steady-state stability limit (SSSL) is defined as "... maximum power at the receiving end of the circuit that can be transmitted without loss of synchronism if the load is increased in very small steps and if the field currents are changed after each increment of load so as to restore the normal operating conditions (usually constant terminal voltages) [51]". This limit is even applicable to lossless lines. If a system exceeds this power limit, associated machines in the system will lose synchronism.

Table 2.1: Parameters of Cable/Line

|                      | OHL <sup>1</sup> | Submarine Cable <sup>2</sup> |

|----------------------|------------------|------------------------------|

| Voltage level (KV)   | 500              | 500                          |

| $R'(\Omega/Km)$      | 0.024            | 0.026                        |

| L'(mH/Km)            | 0.87535          | 0.17507                      |

| C'(nF/Km)            | 12.992           | 286.9                        |

| $G'(\Omega^{-1}/Km)$ | 0                | 0                            |

The steady state stability limit in an AC transmission lines is given by [50]:

$$P_{max} = \frac{V_R V_S}{Z'} - \frac{A V_R^2}{Z'} \cos(\theta_Z - \theta_A) \tag{2.1}$$

$$\begin{cases} \text{Voltage at sending end} &= V_S \angle \delta \\ \text{Voltage at receiving end} &= V_R \angle 0 \\ \gamma &= \sqrt{(R' + j\omega L')(G' + j\omega C')} \\ Z' \angle \theta_Z &= Z_c \sinh(\gamma l) \\ Z_c &= \sqrt{\frac{R' + j\omega L'}{G' + j\omega C'}} \\ A \angle \theta_A &= \cosh(\gamma l) \\ \text{SSS } P_{max} \text{ corresponds to } \delta = \theta_Z \end{cases}$$

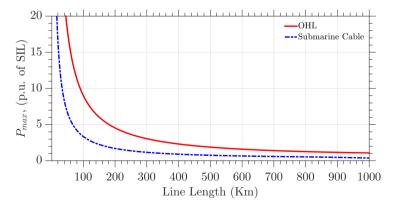

Figure 2.2 illustrates the impact of line length on SSSL, where  $P_{max}$  vs. transmission distance(eq. (2.1)) is plotted for typical values of an OHL and submarine cable table 2.1 with assumption  $V_R = V_S$ . The plot reveals that power transmission capability of a transmission line decrease with increasing length of the conductor, where cables tend to suffer more drastically with increasing distance.

Figure 2.2: Maximum transmission capability of transmission line/cable

<sup>&</sup>lt;sup>1</sup>Table 7.1 [49]

<sup>&</sup>lt;sup>2</sup>Table 7.2 [49]

#### Thermal limits

Losses in the conductor impose thermal limits, to restrict the temperature rise and the subsequent sag in the overhead lines. The resistance of line contributes these losses; which tend to elevate in ac systems, due to the increased magnitude of the current because of the flow of reactive power.

Alternating current implies changing flux in the parasitic inductance, and this leads to consumption of reactive power by the line. Similarly, alternating voltage implies continuous charging and discharging of the parasitic capacitance which leads to the generation of reactive power. The associated reactive power produced by shunt capacitance and consumed by series reactance is given by:

$$Q_c \approx j\omega(C'l)V^2$$

$Q_l \approx j\omega(L'l)I^2$  (2.2)

At a resistive load equal to surge impedance loading (SIL) ( $\sqrt{\frac{L'}{C'}}$  for a lossless line) the reactive power consumed by parasitic inductance balances reactive power supplied by parasitic capacitance. However, with higher loads line consumes reactive power; similarly, for lower loads, there is net reactive power generation. This flow of reactive power increases the magnitude of current in lines/cables which in turn increases losses and reduces its power carrying capability as imposed by the thermal limits.

#### Voltage limits

In the transmission system, the voltage drop along the line is also kept within limits and this, in turn, restricts the power carrying capacity. Besides voltage drop across line resistance, reactive power flow tends to disturb the voltage profile along the line. At SIL net reactive power in line equate to zero and the voltage profile along a lossless line is flat. However, for cases when a line is lightly loaded or unloaded the effect of shunt capacitors dominate. Shunt capacitors imply flow of "charging currents" even in absence of load which are given by:

$$I_{charging} \approx j\omega(C'l)V$$

(2.3)

Under these conditions, there is a net production of reactive power from the transmission line; this results in a higher magnitude of the voltage at receiving end than the transmitting end. This occurs, as capacitive "charging currents" through line inductance produce a voltage in phase with the voltage at transmitting end; resulting in an increase in voltage along the line. Here both inductance and shunt capacitance contribute to voltage rise, and this voltage rise is shown to be proportional to the square of line length. This effect is known as *Ferranti's effect* after its discoverer Sebastian de Ferranti [52]. To the contrast, when the line is overloaded, parasitic series inductance dominates, and there is a voltage drop along the line.

These over-voltage and under-voltage problem at the receiving end of the line becomes more significant as the line length increases and leads to voltage control problems.

In general, power carrying capacity of short transmission lines (< 80Km) are restricted by thermal limits; while loadability of medium length lines (80-100Km) are determined by voltage limits and *steady state stability limit* defines the loadability for the long transmission lines (> 300Km) [50].

In conclusion, HVAC transmission is plagued by higher line losses, lower power transmission capacity, and voltage control problems. Moreover underground/submarine cables with higher shunt capacitance tend to suffer from excessive reactive power in lines adding to losses, voltage regulation problems and have lower SSSL rendering limited application for long distance transmission. To address these limitations of HVAC reactive compensation in the form of shunt reactors/capacitors is required along the line at regular distances. Furthermore, in ac power flow is dictated by line parameters and network topology and is not controllable. Additional flexible alternating current transmission system (FACTS) devices are required to make power-flow controllable. These supplementary devices add to the cost of the system and are not always feasible for the submarine cables.

## 2.1.2. High Voltage Direct Current Transmission

HVDC transmission, as the name states use high voltage DC current to transmit power. Direct current implies that transmission capability is unaffected by parasitic reactive elements associated with lines and is, therefore, independent of the length of cable/line. However conversion from ac to dc and dc to ac at transmitting and receiving ends, respectively, requires additional power converters in the system.

Flow of dc current and presence of converters offers various advantages over HVAC transmission as enumerated below [53–56]:

- In DC, two conductors are required for transmission, whereas three phase AC systems utilize at least three conductors. This implies that

- HVDC offers more power transmission capability over the same network as HVAC. For similar insulation level and cross-sectional area for conductors, DC system provides 40% more power carrying capacity than that of an AC system.

- HVDC offers a smaller footprint, reducing cost and environmental impact.

- DC systems as stated earlier are unaffected by parasitic inductive and capacitive elements of cable/line. This implies that [54]:

- There is theoretically no limit on transmission distance.

- No voltage control problems due to Ferranti's effect.

- No requirement for reactive compensation along the line.

- Presence of converters on both ends of transmission line implies:

- High-speed controllability on the power flow.

- Limits on short-circuit currents, unlike AC where interconnection elevates fault level in the system

- No restriction of synchronism (frequency or phase angle) on the two AC sides.

- Lower transmission losses with HVDC due to the absence of skin, proximity effect and lower corona losses.

- HVDC links act as "firewall" to propagating and expanding faults in a network [56]. In a conventional system in case of a widespread outage or a "black-out" standby generators are required to bring power plants to operating conditions i.e. "black-start". HVDC due to its ability to isolate cascading faults restrict the extent of black-out. In addition to this, the ability of some HVDC converter technologies to operate in the absence of AC grid give them a potential as "black- starters" i.e. to restore AC network in case of a black-out.

Even with of all of the advantages of DC, historically AC has been the main driving force for transmission of energy. The proliferation of AC over DC is attributed to the ease with voltages can be stepped up or down in AC systems. AC employ transformers to convert voltages to desired levels, whereas such a simple equivalent device is absent for DC systems, which has been the core reasons for the dominance of AC transmission. In the past, solutions available for HVDC converters, either as an interface between AC and DC system or between different level DC-DC systems, have been inefficient, expensive, unreliable and had a much larger footprint. The disadvantages of HVDC systems are mainly contributed to the limitation of power converter technology.

The presence of converters poses:

- Additional losses and costs at the terminals of the HVDC system.

- An additional requirement of filters at terminals to mitigate harmonics from converters. Nevertheless, multi-level converter topological allow filter-less configuration.

- An additional requirement of reactive power compensation at terminals for some power converter technologies.

The absence of reliable and efficient converters has been the bottleneck in the development of HVDC. In addition to this, lack of DC breakers is still a constraint in multi-terminal and network operation for HVDC. This has restricted the use of HVDC in the power system. Nevertheless, due to its unique characteristics, HVDC transmission finds specialized application in [53]:

- 1. Long distance bulk power transmission.

- 2. Interconnection of asynchronous systems.

- 3. Submarine/offshore applications.

- 4. DC links in AC grid for control of the power flow.

Long distance bulk power transmission is mainly used for connection of remote hydro or solar generation e.g. the 3.0 GW 940-km long HVDC link between *three gorges* and *guangdong* in China [57]. Interconnection of asynchronous systems is meant for back to back connection of two or more independent systems especially links between countries operating at different frequencies. Submarine cables have application in connecting offshore wind farms and in some cases connection of offshore oil/gas platform to shore power. HVDC links in AC grid are primarily used to strengthen the existing grid; the high-speed control offered by HVDC link aids in the stability of an AC system.

#### 2.1.3. HVDC vs. HVAC

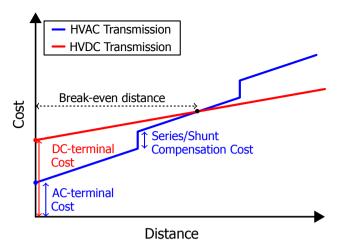

As discussed earlier "frequency" associated with AC systems tends to make long distance transmission far more involved than DC. On the other hand, the high cost of converters limits the feasibility of use of HVDC. Therefore, for any long distance transmission, economic analysis is necessary to determine the suitable mode of transmission. Based on this economic evaluation, the term "break-even distance" is introduced, which refers to the transmission distance at which both HVDC and HVAC have equal economic feasibility. For HVDC at break-even distance, lower line costs and lower capitalized cost of losses counterbalance the higher terminal costs, making HVDC as economically viable as HVAC [58].

To determine feasibility of HVDC vs. HVAC for a particular transmission system economic analyses is performed based on the following factors [59]:

#### 1. Terminal Cost.

The cost of power converters and filters to mitigate harmonics introduced by converter implies higher station cost in HVDC compared to HVAC.

#### 2. Cable/Line Cost.

The cost of line/cable per unit distance is lower in HVDC compared to HVAC. For similar power transmission capability, HVAC is required to have the higher rating as it suffers from the flow of reactive power and higher losses. Moreover, HVDC requires fewer conductors than HVAC and since DC peak voltage is  $\frac{1}{\sqrt{2}}$  times that of AC voltage a lower insulation class is required for the HVDC lines or cables.

#### 3. The value of losses.

An additional requirement of compensator along the line as distances increasing also adds to the cost of HVAC system. Figure 2.3 illustrates cost vs. transmission distance for typical HVAC and HVDC systems.

Technical and economic analyses presented in [60, 61] for offshore wind farms shows that economic break-even distance between HVAC and HVDC is around 35-90 Km. Similarly, for the case of overhead lines break even distance is around 500-800 Km [55].

Figure 2.3: AC vs. DC Transmission Cost over distance

## 2.2. HVDC Converters

With generation and consumer supply at AC voltages, converters are essential for HVDC transmission. HVDC converters date back to late 19th century when rotatory converters i.e. electrical machines were used as mechanical rectifier and inverters. With the invention of mercury arc valve in early 20th century these expensive, inefficient and high maintenance rotary converters were gradually replaced by mercury arc line commutated converters (LCC). Mercury arc valves converters for commercial HVDC transmission were first employed in 1954 for the HVDC link connecting Swedish mainland and the island of Gotland [62]. Development of solid state devices led to the replacement of mercury arc valve by solid state thyristor. Solid state thyristor valves offer various advantages over mercury valves; they are free of poisonous mercury, offers fewer losses and are less susceptible to re-strikes during transient fault events. The first thyristor valves only commercial converter was employed in 1972 by Canadian General Electric and NB Power at Eel River for HVDC transmission [63]. Further research in high power electronics gave way to insulated-gate bipolar transistors which unlike thyristors has the additional ability of controlled turn-off of current. This development led to voltage source converters (VSC), the first HVDC transmission with VSC converters commercial installed in 1997 power between Hellsjön and Grängesberg in Sweden [64].

At present both LCC and VSC are commercially used for HVDC converters, LCC with high power capability is the preferred choice for overhead lines whereas VSC with a smaller footprint and "black-start" capability is preferred for offshore wind farms. For now, HVDC converters are expensive, and the added cost of converters at the transmitting and receiving ends need to be offset by the energy saved due to lower losses, making HVDC financially unviable for short distances.

# 2.2.1. Current-source/Line-Commutated Converters

Line-commutated means that commutation process is dependent on the line voltage of the associated AC system. Line-commutated converters employ mercury valve or thyristor as the commutation device. The thyristor is a semi-controllable semiconductor device, i.e. a forward biased thyristor can be turned on at desired instant with the gate signal. However, the gate signal offers no control over the turn-off instant, which naturally occurs if the current through thyristor drops below the "holding current".

A six pulse bridge converter illustrated in fig. 2.4 forms the building block for LCC converter. It comprises of two thyristors per phase leg that allow or inhibit the flow of current in synchronized manner to get the desired operation. The term "six" refers to six commutations in converter per cycle, resulting in a pulsed voltage waveform [56]. The waveform on the dc side is made up of line-line voltage pulses and at any instant in time exactly one of the two thyristors in each leg is conducting. Each thyristor conducts for an angle of  $\frac{2\pi}{3}$  radians. For HVDC transmission, the inverter end sets the dc voltage whereas rectifier end controls the dc current by regulating the voltage difference. Delay/firing angle  $(\alpha)$ , i.e. delay of gate pulse from the instant when the thyristor is forward biased, provides control for the thyristor and consequently operation of the converter. For  $0 \le \alpha \le \frac{\pi}{2}$  converter has rectifier operation and for  $\frac{\pi}{2} \le \alpha \le \pi - \gamma_{min}$  it works as an inverter.

For HVDC systems mostly used configuration is the twelve pulse bridge arrangement fig. 2.5. This topology comprises of two six pulse bridges, phase shifted by 30°, connected in parallel on AC and series on the DC side. This configuration eliminates fifth and seventh harmonics [65, 66].

Figure 2.4: Six Pulse bridge converter

Figure 2.5: Twelve Pulse converter

The limitations of thyristor-based converters and their impact are as follows:

- For the operation of LCC synchronous voltage source is required. This implies

that LCC cannot operate in the absence of AC grid and hence doesn't have any

"black-start capabilities". Also due to this LCC does not perform well with weak

AC grid and requires short circuit ratio (SCR) ≥ 2 i.e. the short circuit capacity

from the AC grid ≥ two times the converter rating [56].

- LCC only operates at lagging currents. Therefore, the converter consumes reactive power. This reactive consumption varies with load hence switched reactive

compensation is required. This adds to the cost and footprint of the converters limiting its use in offshore transmission.

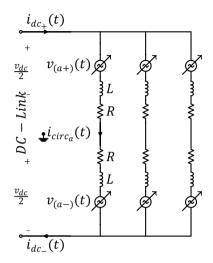

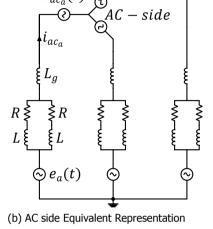

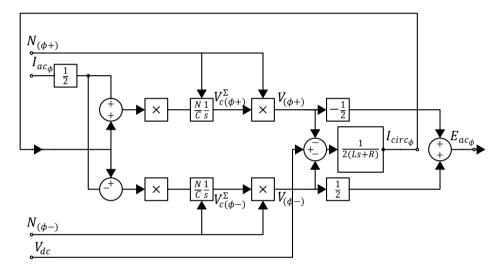

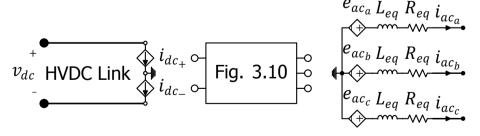

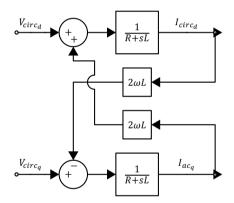

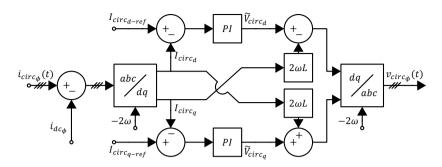

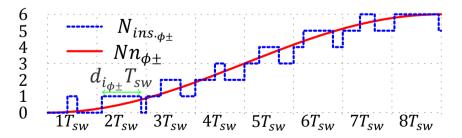

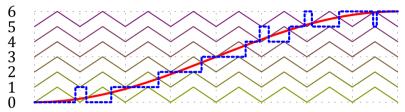

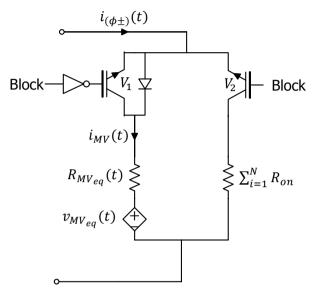

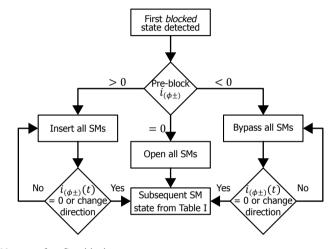

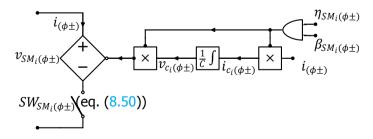

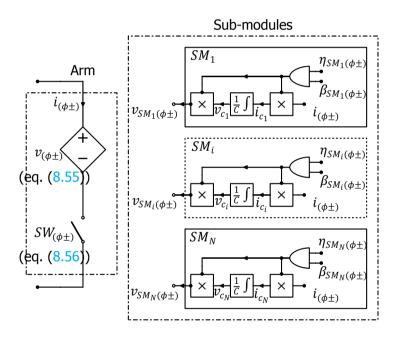

- LCC converters inject harmonics on the AC and DC side. Therefore, filters are required which again add to cost and footprint of converter restricting its use in offshore transmission.