# A Load Insensitive Doherty Power Amplifier with better than -39dBc ACLR on 2:1 VSWR Circle using a Constant 50 Ω Trained Pre-distorted Signal

Singh, Gagan Deep; Mul, Dieuwert; Nemati, Hossein Mashad; Alavi, Morteza S.; de Vreede, Leo C.N.

#### DOI

10.23919/EuMC54642.2022.9924452

Publication date

**Document Version** Final published version

Published in

Proceedings of the 52nd European Microwave Conference (EuMC)

Citation (APA)

Singh, G. D., Mul, D., Nemati, H. M., Alavi, M. S., & de Vreede, L. C. N. (2022). A Load Insensitive Doherty Power Amplifier with better than -39dBc ACLR on 2:1 VSWR Circle using a Constant 50 Ω Trained Predistorted Signal. In Proceedings of the 52nd European Microwave Conference (EuMC) (pp. 222-225). (2022 52nd European Microwave Conference, EuMC 2022). IEEE. https://doi.org/10.23919/EuMC54642.2022.9924452

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

**Takedown policy**Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# A Load Insensitive Doherty Power Amplifier with better than $-39\,\mathrm{dBc}$ ACLR on 2:1 VSWR Circle using a Constant $50\,\Omega$ Trained Pre-distorted Signal

Gagan Deep Singh<sup>1</sup>, Dieuwert Mul<sup>1</sup>, Hossein Mashad Nemati<sup>2</sup>, Morteza S. Alavi<sup>1</sup>, Leo C.N. de Vreede<sup>1</sup>

<sup>1</sup>ELCA, Delft University of Technology, The Netherlands

<sup>2</sup>Huawei Technologies, Sweden

Abstract - This paper presents a low-loss load-insensitive Doherty power amplifier (DPA) technique. The proposed DPA is insensitive to ohmic load variation by adjusting its supply voltages and input drive of the main and peaking stages in a mirrored approach. Moreover, a low-loss tunable matching network (TMN) is employed to cancel out any reactive part of the load. To validate this technique, a printed circuit board (PCB) based demonstrator consisting of the Doherty PA, a six-port reflectometer, and a tunable shunt resonator have been fabricated. When subjected to a  $50\,\Omega$  load, at the 1dB compression point, the DPA delivers an output power of  $32.3\,\mathrm{dBm}$  with a power gain and peak drain efficiency of 14.6 dB and 61 %, respectively. When the DPA is driven with a pre-distorted 64-QAM 4 MHz signal optimized for the  $50\,\Omega$  loading condition, it delivers  $24.4\,\mathrm{dBm}$  at  $41\,\%$ average drain efficiency, with EVM/ACLR  $-40.9\,\mathrm{dB}$  /  $-46.9\,\mathrm{dBc}$ . Subsequently, when subjected to a 2:1 VSWR over a 0°-360° mismatch trajectory, using the unaltered  $50\,\Omega$  DPD correction, it is capable of delivering an output power of  $24.4 \pm 0.1\,\mathrm{dBm}$  with a 34-39% drain efficiency while maintaining an EVM/ACLR better than  $-32.3 \, dB/-39.3 \, dBc$  for all load conditions.

Keywords — self-healing transmitter, VSWR, control circuit, Doherty, six-port reflectometers, and tunable matching networks.

#### I. INTRODUCTION

The ever-growing demand for higher data rates has led to the use of spectrally efficient complex modulated signals, which are characterized by a high peak-to-average power ratio (PAPR). To amplify these signals in an energy-efficient manner, envelope tracking (ET) and Doherty power amplifiers (DPA) are employed. ET-based transmitters utilize fast dynamic supply modulators, which can provide good performance for signals with a limited modulation bandwidth (< 40 MHz). Consequently, DPAs are typically preferred when operating with signals that have both high PAPR, and modulation bandwidth. However, DPAs are very sensitive to load impedance variation [1] and therefore are rarely found in handset or phased array applications. In a handset terminal, the changing antenna environment is the cause of PA load mismatch conditions [2]. While in phased-array systems, the (unwanted) mutual coupling between the antenna elements, in combination with the changing relative phases needed for the beam steering, cause loading variation [3]. A tunable matching network (TMN), in theory, can correct for these varying VSWR conditions [2]. However, correcting for arbitrary complex loads for a given

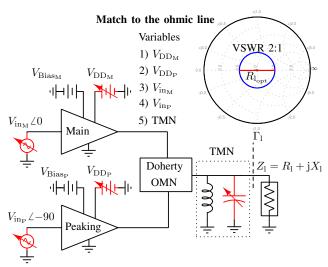

Fig. 1. The proposed low-loss load-insensitive Doherty PA consisting of a tunable input drive, supply voltage and tunable matching network.

VSWR range causes high insertion loss, defeating the potential benefits [2]. In contrast, this work exploits a combination of supply voltage and input drive adjustments to handle the ohmic load variation [4], [2], along with a low loss TMN/tunable shunt capacitor to compensate for the varying reactive part of the load [2], as such enabling truly load-insensitive DPA operation over a given VSWR area (see Fig. 1). The DC-DC supply modulators are considered not to be within the focus of this research. Since they only need to trace the slow varying VSWR conditions (they do not track the modulation envelope) and can be realized with very high efficiency (e.g., 98.4%) [4]. This work provides the following contributions. Firstly, compared to [4], for the first time on a DPA, 0°-360° VSWR detection and full correction are demonstrated. Secondly, it is theoretically shown the proposed technique applies to both symmetrical and asymmetrical DPAs. Thirdly, DPD correction no longer needs to be adjusted/updated for changing loading conditions in the proposed load-insensitive DPA approach. The latter statement is demonstrated by evaluating the DPA linearity over the full 2:1 VSWR circle while using a fixed DPD correction set pre-trained on a  $50\,\Omega$  load condition.

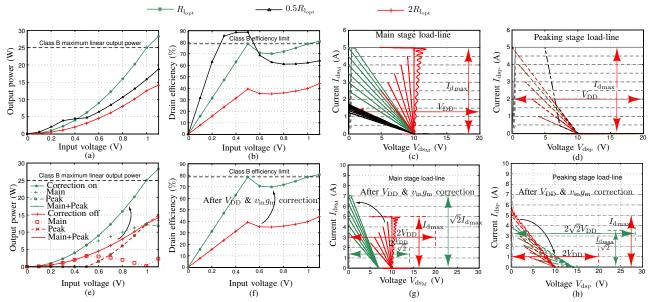

Fig. 2. DPA performance in terms of: (a) output power, (b) drain efficiency, (c) load-line of main output stage, and (d) load-line of peaking output stage, for  $R_1$ = $R_{l_{\rm opt}}$  (green),  $R_1$ = $2R_{l_{\rm opt}}$  (red), and  $R_1$ = $0.5R_{l_{\rm opt}}$  (black). DPA performance in terms of (e) output power, (f) efficiency, (g) main stage load-line, and (h) load-line of peaking output stage, when applying the mismatch condition ( $2R_{l_{\rm opt}}$ ) without (red) and with (green) the proposed correction-technique.

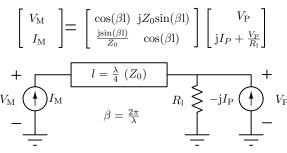

Fig. 3. An ideal Doherty PA

#### II. LOAD-INSENSITIVE DPA THEORY

Fig. 3 illustrates an ideal conventional (asymmetrical) two-way DPA using identical supply voltages  $(V_{\rm DD})$  and unequal currents for its main  $(I_{\rm M})$  and peaking device  $(I_{\rm P})$ . The impedance seen by the main device for a given power back-off point  $(\alpha)$  is given by,

$$Z_{\mathrm{M}(\mathrm{R}_{\mathrm{l}}=\mathrm{R}_{\mathrm{lopt}})} = \frac{R_{\mathrm{lopt}}^{2}}{\alpha^{2} R_{\mathrm{l}}} - \frac{R_{\mathrm{lopt}}}{\alpha} \frac{I_{\mathrm{P}}}{I_{\mathrm{M}}}$$

(1)

When an ohmic VSWR condition is applied the loading impedance  $R_{\rm l}$  will deviate from its optimum value  $R_{\rm l_{\rm opt}}.$  For a given VSWR value, the ohmic part of  $R_{\rm l}$  will vary from  $R_{\rm l_{\rm opt}}/VSWR$  to  $R_{\rm l_{\rm opt}}.VSWR.$  From (1), we can conclude that e.g. for a symmetric DPA  $(\alpha=0.5)$  and  $R_{\rm l}=2R_{\rm l_{\rm opt}}$  at  $v_{\rm in}=1$  (full power), the offered impedance to the main device becomes zero, as such entirely obstructing the desired Doherty operation. This highly sensitive feature of a Doherty amplifier for its provided load is also illustrated in Fig. 2, which relates to the symmetrical DPA  $(\alpha=0.5)$  case. In these simulations, the even harmonics are shorted by a  $\frac{\lambda}{4}$  transmission line, leaving the odd harmonics somewhat

uncontrolled. This arrangement represents the actual circuit implementation used in section III. Also note that, when  $R_{\rm l}$  = 0.5 $R_{\rm opt}$ , the main voltage clips much earlier than in the nominal case. Consequently,  $I_{\rm M}$  will not keep up with  $I_{\rm P}$  in a practical circuit, causing the peaking device impedance ( $Z_{\rm P}=V_{\rm P}/I_{\rm P}$ ) to move towards the short-circuited condition.

#### A. Solution

To alleviate the Doherty amplifier for ohmic mismatch due to  $R_{\rm l}$  deviations and restore its basic properties in terms of output power ( $P_{\rm out,max}$ ), and efficiency vs. power back-off, the following expressions are derived.

$$V_{\rm DD_M,R_l} = V_{\rm DD_M,R_{l_{\rm opt}}} \sqrt{\frac{R_{l_{\rm opt}}}{R_{\rm l}}}$$

(2)

$$I_{\rm M_{\rm max},R_l} = I_{\rm M_{\rm max},R_{l_{\rm opt}}} \sqrt{\frac{R_{\rm l}}{R_{\rm l_{\rm opt}}}}$$

(3)

Note that both the  $V_{\rm DD_M}$  and  $I_{\rm M_{max}}$  have been modified to handle the new  $R_{\rm l}$  and provide the same power for the main device in the power back-off point. Moreover, the new conditions for the supply voltage and required current of the peaking device are derived in the following equations.

$$I_{\rm P_{\rm max},R_{\rm l}} = I_{\rm P_{\rm max},R_{\rm l_{\rm opt}}} \sqrt{\frac{R_{\rm l_{\rm opt}}}{R_{\rm l}}} \tag{4}$$

Consequently, we find (5), which completes our solution for load-insensitive operation.

$$V_{\rm DD_P,R_l} = V_{\rm DD_P,R_{l_{\rm opt}}} \sqrt{\frac{R_{\rm l}}{R_{\rm l_{\rm opt}}}}$$

(5)

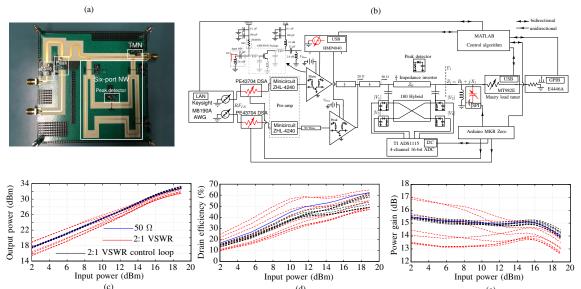

Fig. 4. a) The realized PCB of the prototype PA, (b) the detailed schematic of the Doherty PA, six-port reflectometer with RF peak detectors, and parallel resonator with tunable capacitor. The measurement instruments and the control loop implementation are also shown. DPA performance when the load is matched to the  $50\,\Omega$ , and on a 2:1 VSWR circle for a phase steps of  $45^\circ$  with and without the proposed control loop method. (c), (d), and (e) shows the DPA output power, power gain, and drain efficiency vs. input power.

As an example, simulation results of this recovery procedure when the DPA is subjected to a  $2R_{\rm lopt}$  load impedance, with (green color), and without (red color) adjusting the voltage and drive parameters for the main and peaking device are shown in Fig. 2e, 2f, 2g, and 2h.

#### III. DESIGN & MEASUREMENT

#### A. Design Details

A load-insensitive Doherty PA prototype ( $(R_{\rm l_{opt}} \approx 15\,\Omega)$ ) capable of delivering  $33\,\rm dBm$  at  $900\,\rm MHz$  is realized, using packaged LDMOS devices (AFIC901N)). In this context, an impedance matching control loop has been designed and implemented on a Rogers RO4350B substrate with  $0.508\,\rm mm$  thickness (see Fig. 4a).

## B. Measurement Results

The load-insensitive DPA with its measurement setup is shown in Fig. 4b. The main stage LDMOS device is biased in the desired class-AB mode with  $V_{\rm DD_M}$ =  $5.0\,\rm V$  yielding  $I_{\rm dq}$ =  $44\,\rm mA$ , respectively. While the peaking stage is biased in class-C mode with  $V_{\rm DD_P}=5.0\,\rm V$  yielding  $\approx 0\,\rm mA$ . It can be seen that the DPA (blue color) has a power gain of  $15.5\,\rm dB$  (see Fig. 4e) and delivers an output power of  $32.3\,\rm dBm$  (see Fig. 4c) at its  $1\,\rm dB$  compression point with a  $61\,\%$  (see Fig. 4d) drain efficiency when matched to its nominal  $50\,\Omega$  load.

#### 1) Control Loop Method

A MATLAB offline trained look-up table (LUT) based control algorithm was exploited in this work. The LUT takes the voltage ratios  $\frac{V_1}{V_2}$  and  $\frac{V_3}{V_4}$  as input, and returns the optimum setting for the switchable-capacitor bank, as well as, the input drive levels and supply voltages for the main and peak output stages.

- a) Single-tone: The single-tone measured DPA output power, power gain, and drain efficiency performance for the load trajectory on the 2:1 VSWR circle, with and without the actuation method, are shown in Fig. 4c, 4d, and 4e, respectively. The performance of the DPA when matched to a  $50\,\Omega$  load is added for comparison.

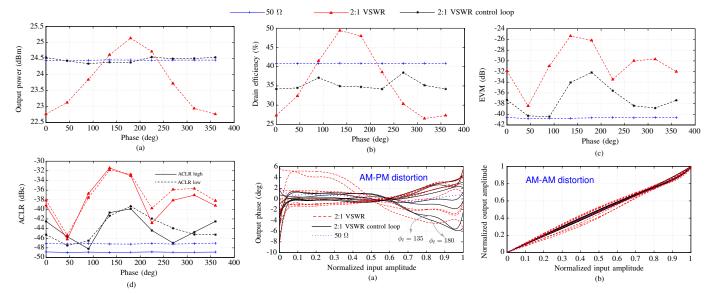

- b) Modulated signal: For a 64-QAM 4 MHz modulated signal, first a simple static AM-AM/AM-PM based DPD was trained for the DPA when connected to a  $50\,\Omega$  load, yielding a set of pre-distorted drive signals for the main and peaking devices, which remain unaltered in the following VSWR measurements. Fig. 5a, 5b, 5c, and 5d show the resulting DPA output power, drain efficiency, EVM in dB, and ACLR at 1 MHz offset for a 64-QAM 4 MHz signal using this unaltered ( $50\,\Omega$  case) DPD correction.

From the single-tone and modulated signal measurements, we can observe that the VSWR control loop, when activated recovers the DPA performance in terms of output power and gain with a variation of less than  $\pm~0.1\,\mathrm{dB}$  for a linear output power of 24.4 dBm. Furthermore, it can maintain close to constant efficiency and linearity performance, i.e., EVM/ACLR better than  $-32.3 \, dB/-39.3 \, dBc$  across the entire 2:1 VSWR circle. The limited degradation in linearity can be traced back to angles with increased changes in AM-PM distortion (see Fig. 5e). The latter can be explained by considering the impact of the non-linear output capacitance  $(C_{

m ds})$  of the main and peaking devices. Namely, it acts as a catalyst for the output phase distortion. In a practical DPA the output phase is a function of  $R_{\rm l},\,g_{\rm m},\,C_{\rm gs},$  and  $C_{\rm ds}$  (of which  $C_{\rm ds}$  has a dominant role) [5], [6]. Consequently, a change in  $C_{\rm ds}$  and  $R_{\rm l}$  (due to the changing load impedance) yields a change in the phase distortion.

In Table 1, a comparison with state-of-the-art load-insensitive

Fig. 5. The DPA performance on  $50\,\Omega$  load and 2:1 VSWR circle with and without activation of the VSWR control loop, while, using a  $50\,\Omega$  trained pre-distorted 64-QAM 4 MHz signal with an input power of 9 dBm (a) output power, (b) drain efficiency, (c) EVM, and (d) ACLR at 1 MHz offset. Also shown are the DPA (e) AM-PM distortion in degree and (f) AM-AM distortion.

Table 1. Comparison with the State of the Art Load Insensitive DPAs

| Comparison                   | This work           |                | [7] TMTT-2021 |              | [4] TMTT-2021              |            |

|------------------------------|---------------------|----------------|---------------|--------------|----------------------------|------------|

| Technique                    | Proposed            |                | QB-DPA ‡      |              | Supply + Input drive-DPA ‡ |            |

| Technology                   | LDMOS-PCB           |                | GaN-PCB       |              | GaN-PCB                    |            |

| Impedance detector           | yes                 |                | no            |              | yes                        |            |

| Freq GHz                     | 0.9                 |                | 3.5           |              | 3.6                        |            |

| $Z_{ m l}/{ m VSWR}$         | 50 Ω                | 2:1(0°-360°)   | 50 Ω          | 2:1(0°-360°) | 50 Ω                       | 25 Ω-100 Ω |

| CW signal                    | 1-tone CW           |                | 1-tone CW     |              | 1-tone CW                  |            |

| $P_{\mathrm{out_{1dB}}}$ dBm | 32.3                | 32.3[0.4,-0.2] | 40.7          | 38.8-40.4    | 43.5                       | 42.6-43.4  |

| DE/PAE %                     | 61/60               | 48-59/47-58    | 68.4/-        | 51-59/-      | 68.0/-                     | 54-64/-    |

| Modulated signal             | <b>64-QAM</b> 4 MHz |                | 64-QAM 20 MHz |              | LTE 5 MHz                  |            |

| DPD                          | static              |                | no            |              | no                         |            |

| PAPR                         | 7.3                 |                | NR            |              | 5.5                        |            |

| $P_{\mathrm{out}}$ dBm       | 24.4                | 24.4±0.1       | 35            | 33-34.2      | NR                         | NR         |

| $DE_{avg}/PAE_{avg}$ %       | 41/40               | 34-39/33-38    | 45            | 32.5-42.5/-  | 46.4/-                     | 40.2-43/-  |

| ACLR dBc                     | -46.9               | < -39.3        | -41.0         | NR           | -31.8                      | <-30.1     |

| $EVM \; \mathrm{dB}/\%$      | -40.9/              | < -32.3/       | -/1.48        | -/1.75-4     | NR                         | NR         |

$\ddagger$  results are estimated from plots; NR = Not Reported;  $\dagger$  Saturated performance;  $\dagger\dagger$  with PA  $50\,\Omega$  performance (VSWR 1:1) as the reference, the reflection loss for a 2:1 VSWR will be  $0.51\,\mathrm{dB};$

Doherty PAs is provided. It can be seen that the proposed technique achieves the best performance in terms of constant linear output power with a variation of only  $\pm~0.1\,\mathrm{dB},$  with an average drain efficiency of  $\approx~35~\%.$  The linearity performance i.e., EVM/ACLR is better than  $-32.3\,\mathrm{dB}/-39.3\,\mathrm{dBc}$  over the entire 2:1 VSWR circle.

## IV. CONCLUSION

This paper has demonstrated Doherty PA with built-in self-healing capability for handset or phased array applications. The realized DPA is insensitive to load variation by adjusting

its input drive levels and the supply voltages of the main and peaking devices in a mirrored approach, while an adjustable capacitor bank handles the reactive loads. The prototype DPA and LUT-based fully-automated control algorithm was able to recover from the load variations on a 2:1 VSWR circle and could reduce the gain and output power variation to less than  $\pm~0.1\,\mathrm{dB}$  when driven by a complex modulated signal. Furthermore, it was shown that the DPD correction is largely independent of load mismatch over a given VSWR range.

#### REFERENCES

- O. Hammi, J. Sirois, S. Boumaiza, and F. M. Ghannouchi, "Study of the Output Load Mismatch Effects on the Load Modulation of Doherty Power Amplifiers," in 2007 IEEE Radio and Wireless Symposium, 2007, pp. 393–394a.

- [2] G. D. Singh, H. M. Nemati, and L. C. N. de Vreede, "A Low-Loss Load Correction Technique for Self-Healing Power Amplifiers Using a Modified Two-Tap Six-Port Network," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 9, pp. 4069–4081, 2021.

- [3] A. Mohammadian, N. Martin, and D. Griffin, "A Theoretical and Experimental Study of Mutual Coupling in Microstrip Antenna Arrays," *IEEE Trans. Antennas Propag.*, vol. 37, no. 10, pp. 1217–1223, 1989.

- [4] C. F. Gonçalves, F. M. Barradas, L. C. Nunes, P. M. Cabral, and J. C. Pedro, "Quasi-Load Insensitive Doherty PA Using Supply Voltage and Input Excitation Adaptation," *IEEE Trans. Microw. Theory Techn.*, vol. 70, no. 1, pp. 779–789, 2022.

- [5] L. Piazzon, R. Giofrè, P. Colantonio, and F. Giannini, "Investigation of the AM/PM distortion in Doherty Power Amplifiers," in 2014 IEEE Topical Conference on Power Amplifiers for Wireless and Radio Applications (PAWR), 2014, pp. 7–9.

- [6] L. C. Nunes, P. M. Cabral, and J. C. Pedro, "AM/PM distortion physical origins in Si LDMOS Doherty power amplifiers," in 2016 IEEE MTT-S International Microwave Symposium (IMS), 2016, pp. 1–4.

- [7] H. Lyu, Y. Cao, and K. Chen, "Linearity-Enhanced Quasi-Balanced Doherty Power Amplifier With Mismatch Resilience Through Series/Parallel Reconfiguration for Massive MIMO," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 4, pp. 2319–2335, 2021.