# A Scalable Mextram Model for Advanced Bipolar Circuit Design

Hsien-Chang Wu

## A Scalable Mextram Model for Advanced Bipolar Circuit Design

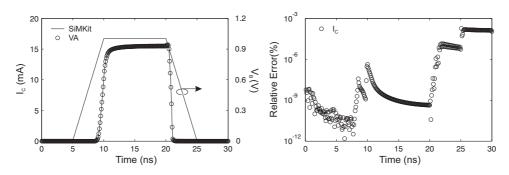

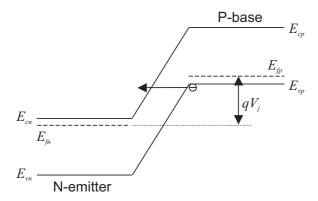

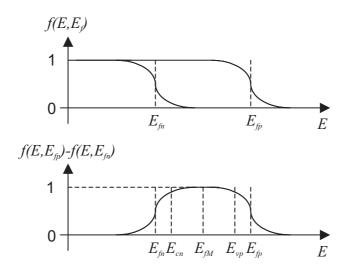

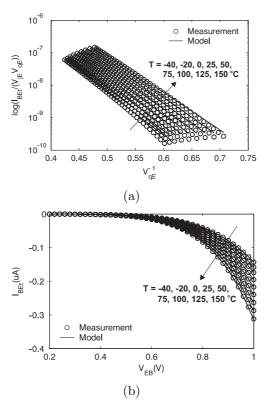

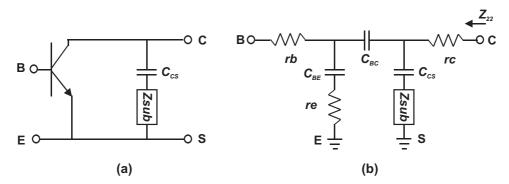

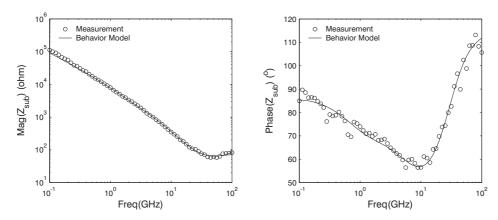

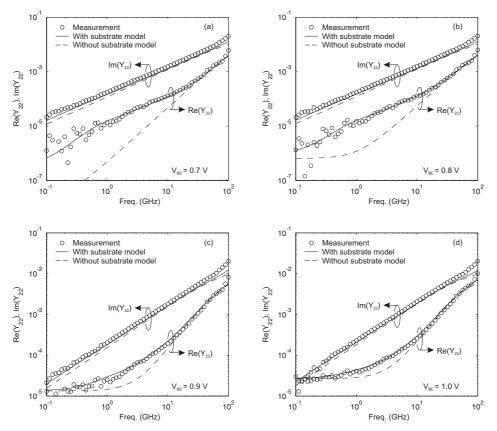

#### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus Prof. dr. ir. J. T. Fokkema, voorzitter van het College voor Promoties, in het openbaar te verdedigen

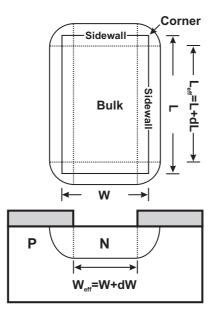

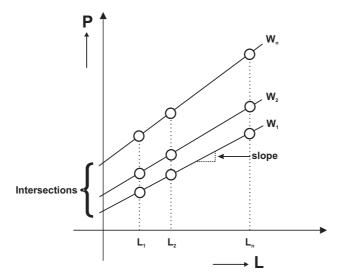

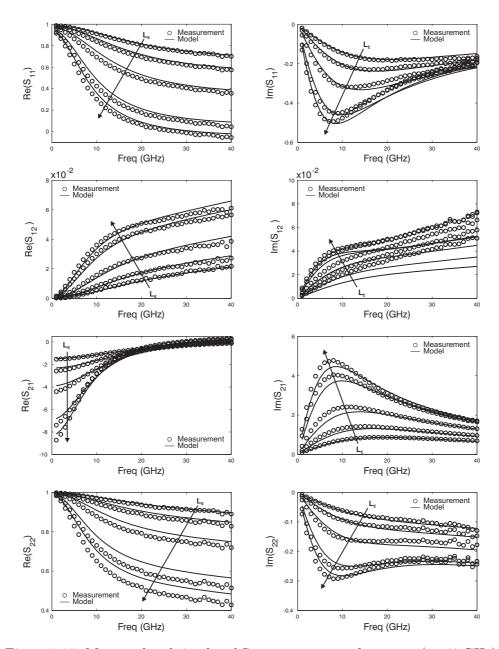

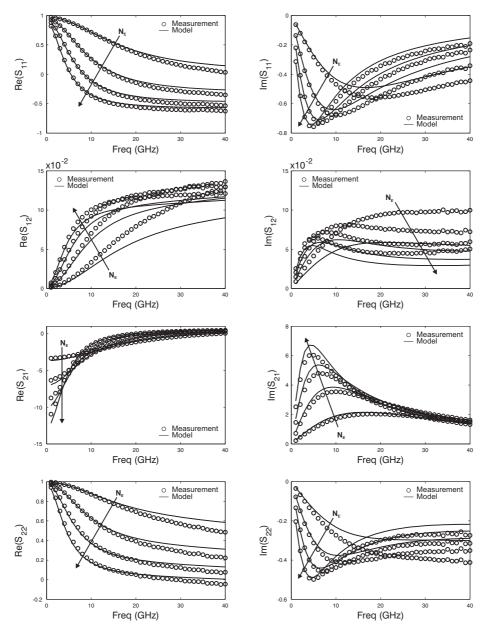

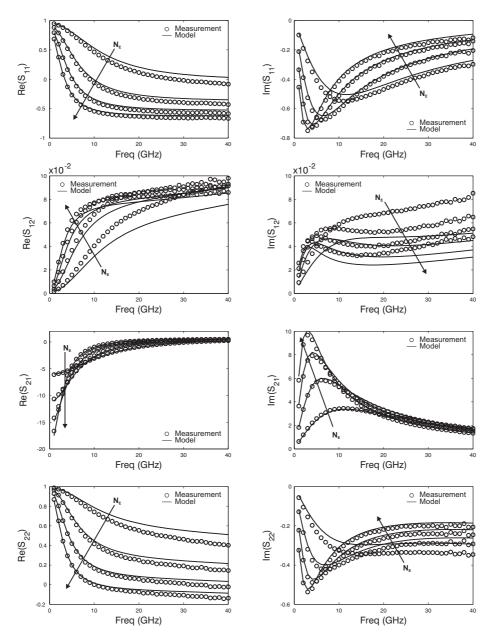

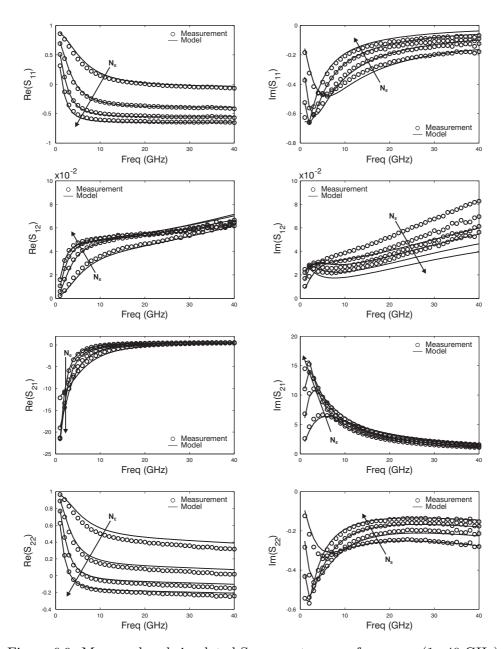

op maandag 24 september 2007 om 12:30 uur

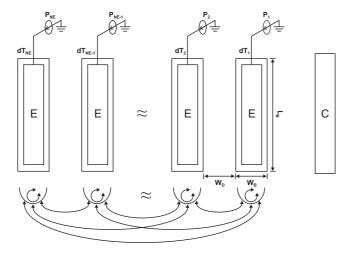

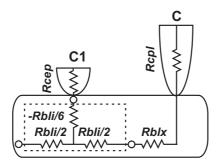

door

Hsien-Chang WU

Master of Science, National Taiwan University

Dit proefschrift is goedgekeurd door de promotor: Prof. Dr.-Ing. J. N. Burghartz

#### Samenstelling promotiecommissie:

Rector Magnificus, voorzitter

Prof. Dr. J. N. Burghartz, Technische Universiteit Delft, promotor

Prof. Dr. L. K. Nanver, Technische Universiteit Delft

Prof. Dr. J. W. Slotboom, Technische Universiteit Delft

Prof. Dr. P. J. French, Technische Universiteit Delft

Prof. Dr. T. Zimmer, University of Bordeaux I (France)

Dr. H. C. de Graaff, NXP Semiconductors

Dr. S. Mijalkovic, Silvaco Technology Center (United Kingdom)

The work in this thesis was supported by NXP Semiconductors.

Hsien-Chang Wu,

A Scalable Mextram Model for Advanced Bipolar Circuit Design, Ph.D. Thesis Delft University of Technology, with summary in Dutch.

Keywords: Mextram model, scalable model, SiGe HBT, bipolar device, parameter extraction.

ISBN: 978-90-8559-146-7

Copyright © 2007 by Hsien-Chang Wu

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the prior written permission of the copyright owner.

Printed by Optima Grafische Communicatie, Rotterdam, The Netherlands.

# Contents

| 1 | Intr         | roduction                                      | 1  |

|---|--------------|------------------------------------------------|----|

|   | 1.1          | Evolution of bipolar transistors               | 1  |

|   | 1.2          | Modeling bipolar transistors                   | 4  |

|   | 1.3          | Scope and outline                              | 8  |

| 2 | Phy          | vsics of the Mextram model                     | 11 |

|   | 2.1          | Introduction                                   | 11 |

|   | 2.2          | Transfer current                               | 13 |

|   |              | 2.2.1 Quasi-Neutral Base (QNB)                 | 14 |

|   |              | 2.2.2 Epilayer                                 | 17 |

|   | 2.3          | Recombination currents                         | 20 |

|   |              | 2.3.1 Intrinsic transistor region              | 20 |

|   |              | 2.3.2 Extrinsic quasi-neutral regions          | 22 |

|   |              | 2.3.3 Weak avalanche current                   | 23 |

|   | 2.4          | Substrate currents                             | 23 |

|   | 2.5          | Charges and capacitances                       | 24 |

|   |              | 2.5.1 Depletion capacitances                   | 24 |

|   |              | 2.5.2 Diffusion charges                        | 26 |

|   |              | 2.5.3 Distributed and non-quasi-static charges | 28 |

|   | 2.6          | Thermal phenomena                              | 29 |

|   | 2.7          | Noise                                          | 31 |

|   | 2.8          | Conclusion                                     | 34 |

| 3 | Mo           | del implementation and verification            | 35 |

| U | 3.1          | Introduction                                   | 35 |

|   | $3.1 \\ 3.2$ | Compact model implementation and               | 55 |

|   | IJ.∠ı        | testing of Mextram                             | 36 |

|   | 3.3          | Base-emitter tunneling current                 | 42 |

|   |              |                                                |    |

ii CONTENTS

|   | 3.4<br>3.5<br>3.6 | 3.3.1 Physical model       42         3.3.2 Temperature dependence       47         3.3.3 Model implementation       47         3.3.4 Tunneling current parameter extraction       49         Behavior modeling of substrate effect       50         Discussion       52         Conclusions       54 |

|---|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 | Dat               | a acquisition and model parameter extraction 55                                                                                                                                                                                                                                                       |

|   | 4.1               | Introduction                                                                                                                                                                                                                                                                                          |

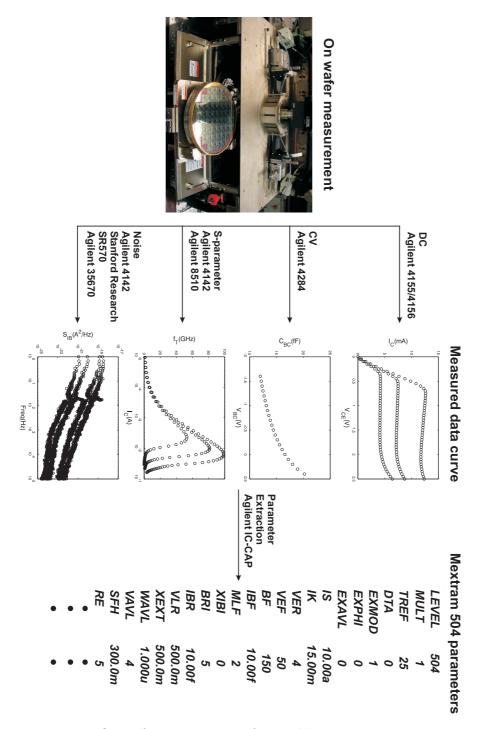

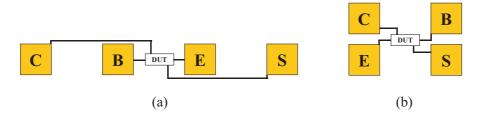

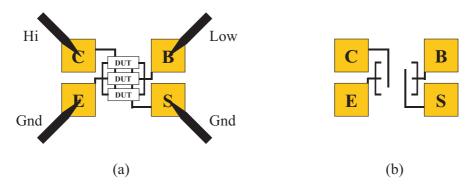

|   | 4.2               | On-wafer measurement for model parameter extraction 55                                                                                                                                                                                                                                                |

|   |                   | 4.2.1 DC measurement                                                                                                                                                                                                                                                                                  |

|   |                   | 4.2.2 Capacitance measurement                                                                                                                                                                                                                                                                         |

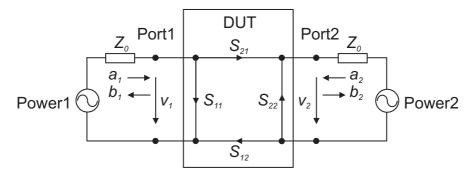

|   |                   | 4.2.3 S-parameters measurement                                                                                                                                                                                                                                                                        |

|   |                   | 4.2.4 Noise measurement                                                                                                                                                                                                                                                                               |

|   | 4.3               | Single model parameter extraction                                                                                                                                                                                                                                                                     |

|   |                   | 4.3.1 Layout and technology data                                                                                                                                                                                                                                                                      |

|   |                   | 4.3.2 Parameters extracted from measured data 71                                                                                                                                                                                                                                                      |

|   |                   | 4.3.3 Improved temperature scaling model for the reverse cur-                                                                                                                                                                                                                                         |

|   |                   | rent gain                                                                                                                                                                                                                                                                                             |

|   | 4.4               | Conclusion                                                                                                                                                                                                                                                                                            |

| 5 | Sca               | lable bipolar model approach and parameter extraction 83                                                                                                                                                                                                                                              |

| • | 5.1               | Introduction                                                                                                                                                                                                                                                                                          |

|   | 5.2               | Physics of geometry scaling                                                                                                                                                                                                                                                                           |

|   | J                 | 5.2.1 Geometry scaling rules of current and charge 85                                                                                                                                                                                                                                                 |

|   |                   | 5.2.2 Geometry scaling rules for ratio of current and charge . 88                                                                                                                                                                                                                                     |

|   |                   | 5.2.3 Geometry scaling rules for parasitic and thermal resistance 89                                                                                                                                                                                                                                  |

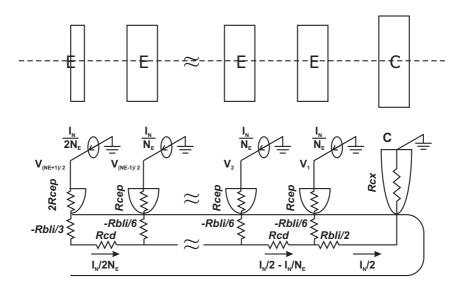

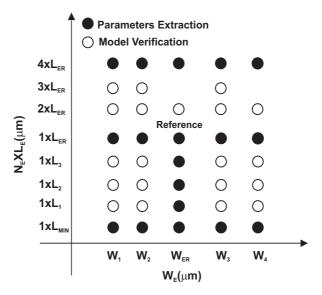

|   | 5.3               | Model implementation and parameter extraction 92                                                                                                                                                                                                                                                      |

|   | 5.4               | Conclusions                                                                                                                                                                                                                                                                                           |

| 6 | Me                | xtram modeling for high power application 105                                                                                                                                                                                                                                                         |

|   | 6.1               | Introduction                                                                                                                                                                                                                                                                                          |

|   | 6.2               | Derivation of scaling equations for                                                                                                                                                                                                                                                                   |

|   |                   | multi-emitter devices                                                                                                                                                                                                                                                                                 |

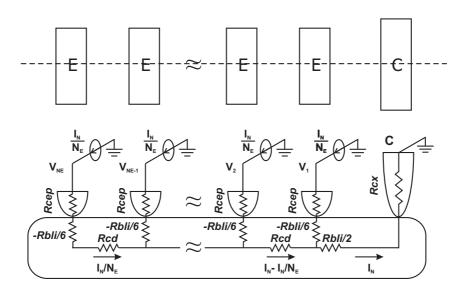

|   |                   | 6.2.1 Scaling of intrinsic transistor parameters 106                                                                                                                                                                                                                                                  |

|   |                   | 6.2.2 Thermal resistance scaling                                                                                                                                                                                                                                                                      |

|   |                   | 6.2.3 Collector resistance scaling                                                                                                                                                                                                                                                                    |

|   | 6.3               | Model implementation and parameter extraction in IC-CAP 113                                                                                                                                                                                                                                           |

|          | ••• |

|----------|-----|

| CONTENTS | 111 |

| CONTENIO | 111 |

|                    | 6.4                                                            | Conclusions                                      | 115 |  |  |

|--------------------|----------------------------------------------------------------|--------------------------------------------------|-----|--|--|

| 7                  | 7.1                                                            | Conclusions                                      |     |  |  |

|                    | 7.2                                                            | Recommendations for the future work              | 123 |  |  |

| $\mathbf{A}$       | List                                                           | of Mextram model parameters                      | 127 |  |  |

| В                  | Tur                                                            | neling current model implementation              | 131 |  |  |

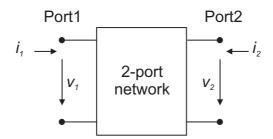

| $\mathbf{C}$       | C Definition of 2-port parameters and their transformation 133 |                                                  |     |  |  |

| D                  | Beł                                                            | navior substrate resistance model implementation | 135 |  |  |

| $\mathbf{E}$       | Geo                                                            | ometry scaling rules implementation              | 137 |  |  |

| Bi                 | bliog                                                          | graphy                                           | 141 |  |  |

| Su                 | Summary                                                        |                                                  |     |  |  |

| Samenvatting       |                                                                |                                                  | 153 |  |  |

| Lis                | st of                                                          | publication                                      | 157 |  |  |

| Acknowledgments 16 |                                                                |                                                  |     |  |  |

| Al                 | out                                                            | the author                                       | 165 |  |  |

iv CONTENTS

## Chapter 1

## Introduction

### 1.1 Evolution of bipolar transistors

The first transistor was the point contact transistor having two metal point contacts on a germanium substrate. It was invented in 1947 by W. Brattain, J. Bardeen and W. Shockley. Since then, bipolar junction transistors (BJTs) have been evolving rapidly. Nowadays, high-performance bipolar transistors are not only used in high-speed circuits for optical communication systems [1] but also to enhance the high-frequency performance of BiCMOS circuits building blocks [2] used in wireless communication systems.

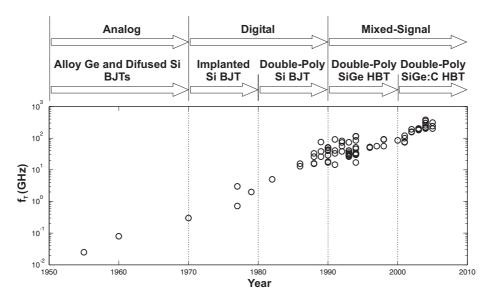

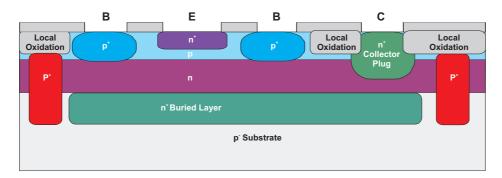

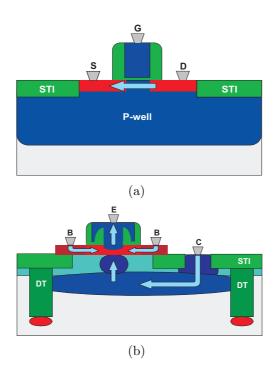

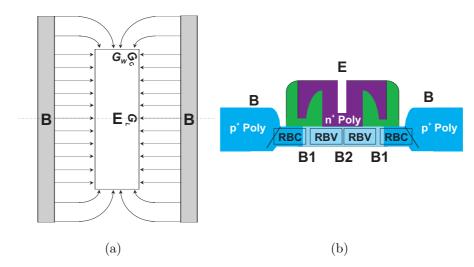

Fig. 1.1 shows the cut-off frequency  $(f_T)$ , the stages of technology development and the applications of bipolar transistors over time. Prior to 1970, the bipolar transistor was based on a diffused p-n junction structure, which was large in both lateral dimension and vertical doping profile. Due to large parasitic capacitance and high forward transit time  $(\tau_F)$  for the diffused transistor, its maximum  $f_T$  in this period of time was just around 1 GHz. The main applications in this period were analog amplifiers to replace the power hungry vacuum tubes and switches in telephone relays [4,5]. Later in the 70's, a bipolar transistor was formed by using ion-implantation, which has a steep vertical doping profile to reduce its  $\tau_F$ . As a result, its maximum  $f_T$  was increased to 5 GHz. Though  $f_T$  of the conventional bipolar transistor was still limited by its parasitic capacitance resulting from  $p^+$  junction isolation and extrinsic base-collector junction as shown in Fig. 1.2, it was believed that the bipolar transistors using a double polysilicon (poly-emitter and poly-base conbined).

2 Introduction

Figure 1.1: Cut-off frequency, the evolution of bipolar devices and applications vs. the year reported [3].

tacts) structure [6,7] were built to prevent from current-gain degradation from the self-aligned shallow emitter and to reduce the parasitic base-collector capacitance. Additional features such as an  $n^+$  local collector implant and deep trench isolation were also used to enhance quasi-saturation [8] immunity and to reduce collector-substrate capacitance. With the new double-poly self-aligned device structure, the  $f_T$  of the bipolar transistor was increased to 50 GHz and an ECL gate delay of 73 ps [9] had been reported. The bipolar transistors in the 70s and 80s were mainly used for high-speed digital applications, such as emitter-coupled logic (ECL) for main-framed computer and SRAM, transistor-transistor logic (TTL) for microprocessors.

In the late 80's, SiGe-base heterojunction bipolar transistors (HBTs) [10] were invented to further improve bipolar transistor performance. Using the "MBE" or "UHV/CVD" [11] epitaxy technique, an in-situ-doped SiGe-base becomes steeper than a boron ion-implant base. In addition to the narrower SiGe-base, the Ge-induced bandgap narrowing in the graded SiGe-base region leads to a reducing base transit time and a decreasing Gummel number [12] of a SiGe HBT as explained by Kroemer [13]. As a result of the smaller Gummel number, doping concentration in the thin SiGe-base can be increased to avoid punch-through from emitter to collector. Therefore, the current gain can be

Figure 1.2: Cross-section of a conventional bipolar transistor.

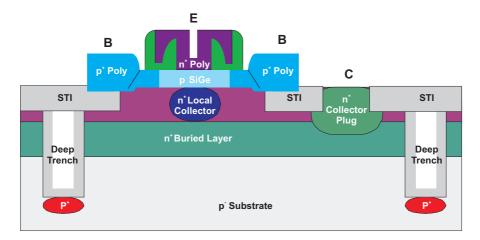

Figure 1.3: Cross-section of an advanced SiGe HBTs.

4 Introduction

maintained or be even higher in spite of the high doping density in the base. On the other hand, a high doping density in the base can also reduce the base resistance. In the mean time, the SiGe HBT inherits the device structure from the advanced Si bipolar transistor. As shown in Fig. 1.3, an advanced SiGe HBT has an  $n^+$  poly-emitter contact, a  $p^+$  poly-base contact, an  $n^+$  local collector implant, a buried  $n^+$  sub-collector and deep trench isolation. Therefore, the SiGe-base HBT has superior performance compared to its Sibase counter part. Later in the late 90's, carbon incorporated in the SiGe base to suppress boron out-diffusion [14] from thermal process or transient enhanced diffusion is introduced to form a steeper base doping profile to further improve the performance of a SiGe HBT. With all the advanced features mentioned above, the most advanced SiGe:C HBT has pushed the peak  $f_T$  up to 380 GHz and a ECL gate delay down to merely 3.2 ps [15].

For the sake of higher power consumption and lower integration density of pure bipolar circuits compared to the CMOS circuits, bipolar transistors started to retreat from digital applications in the 70's and 80's. From the 90's up to now, it is the BiCMOS technology, which combines high-speed bipolar devices for analog applications with low-standby power CMOS devices for digital applications, to dominate in mixed-signal applications. Especially with the superior RF performance [16] of SiGe HBTs for a given lithographic generation compared to that of CMOS devices, SiGe HBTs are widely used in wireless transceiver circuits such as low-noise amplifiers (LNAs), mixers, voltage-controlled oscillators (VCOs) and power amplifiers (PAs). With the booming market for the wireless mobile communication devices, the need for low-power and high-speed BiCMOS circuits are expect to continue to grow in the future.

### 1.2 Modeling bipolar transistors

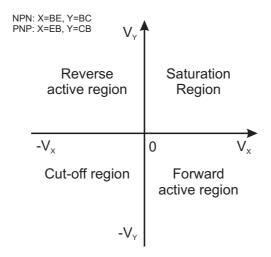

A compact semiconductor model is a mathematical description of the physical behavior of a semiconductor device. The first and simplest bipolar model is the Ebers-Moll (EM1) model, which considers two back-to-back PN diodes with only four model parameters to describe the large-signal behavior of a 3-terminal NPN/PNP bipolar transistor during transient analysis. This simple model was invented by J. J. Ebers and J. L. Moll [17] in 1954. The EM1 model is valid for 4 different regions of operation depending on the base-emitter and base-collector junction biases as shown in Fig. 1.4, where the reverse-active region is considered as the forward-active region of the common-

Figure 1.4: Regions of operation for a bipolar transistor.

collector configuration in the original EM1 model.

However, the bipolar circuit design was still a trial and error procedure on a breadboard with a lot of manual calculations for circuit analysis until the invention of the "simulation program with integrated circuit emphasis" (SPICE) [18, 19] in the 70's. The SPICE includes compact models for semiconductor devices and linear passive components (resistors, capacitors, inductors etc.) so that designers can perform circuit simulations in a computer aided design (CAD) environment. The original EM1 model is derived from a common-base configuration, which is later transformed to a common-emitter configuration with two base currents  $(I_{bf}, I_{br})$  and a collector to emitter transfer current  $(I_N)$  as shown in Fig. 1.5. This is because the common-emitter configuration is better suited for the description of a switch or an amplifier. With limited device physics and regions modeled, the EM1 model was later extended to have more physical effects, including: 1. Charge storage in the junction and base regions and 2. parasitic resistances. As a result, an extended EM1 model with three non-linear depletion capacitances to model depletion charges  $(Q_{tE}, Q_{tC})$  and  $Q_{tS}$ , two non-linear diffusion capacitances to model minority charge storage in the neutral base  $(Q_{BE} \text{ and } Q_{BC})$  and three parasitic resistances  $(R_E, R_B \text{ and } R_C)$  to model the bulk semiconductors in emitter, base and collector is shown in Fig. 1.5. The extended EM1 model is generally recognized as the second generation bipolar device model (EM2). Though the extrinsic region is larger than the intrinsic region in the conventional bipolar

6 Introduction

Figure 1.5: A simplified cross-section of a bipolar transistor with the Ebers-Moll model (in dashed box) and extended Ebers-Moll model (in the complete equivalent circuit).

Figure 1.6: A simplified cross-section of a bipolar transistor with the Gummel-Poon model (in dashed box) and the extended Gummel-Poon model (in the complete equivalent circuit).

transistor [20], only the intrinsic region is modeled by EM1 and EM2 as can be seen in Fig. 1.5.

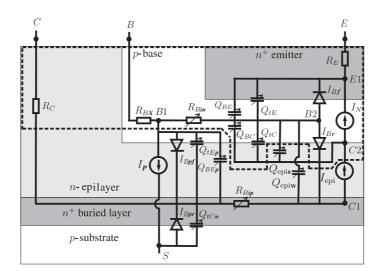

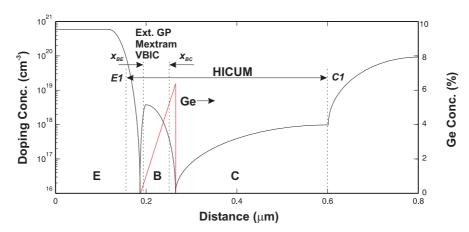

After the EM2 model, Getreu [21] classified a further extension of the EM model as a 3rd generation model (EM3) [22] and the Gummel-Poon (GP) model [23] from the 70's as a 4th generation model. The main difference between the EM3 and GP models is that there is an unified description of Early effect [24] and high-current injection in the base by a normalized base charge in the GP model. But both EM3 and GP models are still limited in modeling the intrinsic region of the device. The quasi-saturation effect is sill not addressed. With the advances of bipolar technology and higher integration density on a single chip in the 80's, intrinsic device delay from high current effects start to dominate the total delay time. Therefore, de Graaff [25] classifies the GP model as a 3rd generation bipolar model and Kull's extended GP (Ext. GP) model [26] as a 4th generation bipolar model. The Ext. GP model as shown in Fig 1.6 incorporates a bias dependent current source  $(I_{epi})$  and two injected epi-layer charges  $(Q_{epi0} \text{ and } Q_{epiw})$  to model the quasi-saturation effect in the epi-collector and a parasitic PNP model to model the extrinsic region. The Mextram model [27], which will be described in the next chapter, is viewed as 5th generation model. Moreover, HICUM [28] and VBIC [29] are also classified as 5th generation bipolar models [30]. All three 5th generation models include new physical effects such as avalanche breakdown, self-heating, non-linear bias dependent Early effect etc. to model advanced Si/SiGe bipolar transistors. The main difference among the three 5th generations models is the regions where the integral charge control relationship (ICCR) [23] for the transfer current is applied as shown in Fig. 1.7. Earlier versions of Mextram [27] tried to calculate the transfer current from the drift-diffusion current equation to incorporate a non-uniform base doping induced electric field at low injection. The integral base charge at both low and high injections is evaluated directly from the junction law at quasi-neutral base (QNB) boundaries ( $x_{BE}$  to  $x_{BC}$ ). In the later versions [31], it came back to the linear transfer current and charge relationship as used in Ext. GP and VBIC models. As a result, Ext. GP, Mextram and VBIC all applied ICCR from  $x_{BE}$  to  $x_{BC}$  and they also have a similar voltage-dependent current source  $I_{epi}$  to model the epi-collector region. However, HICUM integrates charge for ICCR from edge of emitterbase depletion region (E1) to the edge of epi-collector (C1). Since the epicollector is included in ICCR, no  $I_{epi}$  is needed for HICUM. The transfer current to integral charge relationship, however, becomes more complex to cover transistor operations from low injection to high injection.

8 Introduction

Figure 1.7: The 1-D SiGe HBT doping profile and integral charge control intervals employed in the evaluation of the transfer current [32].

After the development of the SiGe HBT technology in the early 90's, a Gummel number including the non-uniformed bandgap narrowing effect was later taken into account in HICUM [33] and Mextram [34] to model SiGe HBTs. When we look back to the bipolar model development history, we can conclude that compact modeling always lagged behind the device technology development. Therefore, numerical table-based models [35] or empirical models [36] are sometimes used to fill the gap between the compact modelling needs for the new technology generation and available compact device models.

### 1.3 Scope and outline

In this chapter, the evolution of bipolar transistor's technology and the main applications in each period of time since its invention has been described. Then, it is the discussion about how historically the compact model development has been driven by the technology progress. For the rest of the thesis, the outline is as follows.

In Chapter 2, the detailed equivalent circuit and physics of the Mextram model, on which the thesis is focused, is described.

In Chapter 3, a "short-cut" for compact model implementation with a high-level language VHDL Verilog-A to avoid time consuming C-code implementation and model verification after the implementation is discussed. Moreover, two additional features (tunneling current and behavioral substrate resistance)

for the Mextram model are implemented in Verilog-A to demonstrate that it is suitable for practicing new modeling ideas .

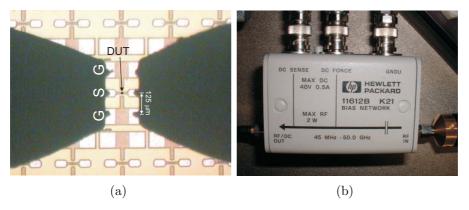

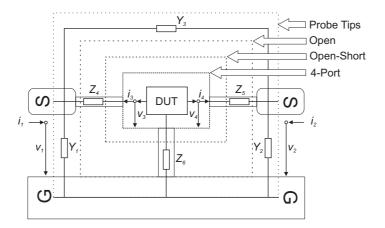

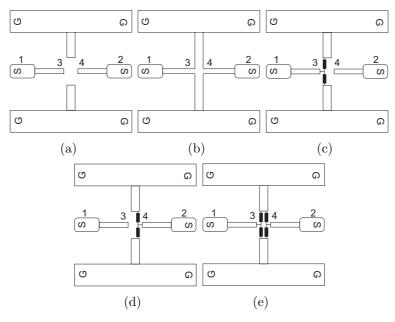

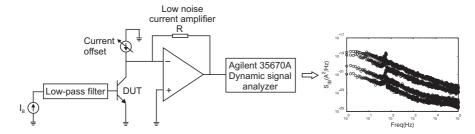

In Chapter 4, the bipolar transistor measurements (including DC, CV, S-parameters and 1/f noise), the test structures for use in device measurements and the pad parasitic de-embedding are discussed. Following the device measurements and test structure design, different measurement setups with their relevant Mextram model parameters are used to demonstrate parameter extraction from a SiGe HBT.

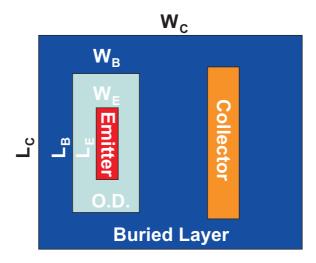

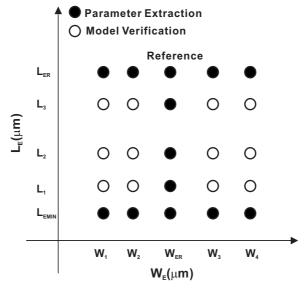

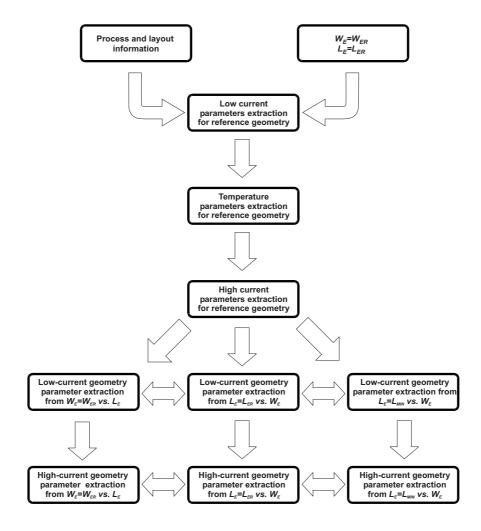

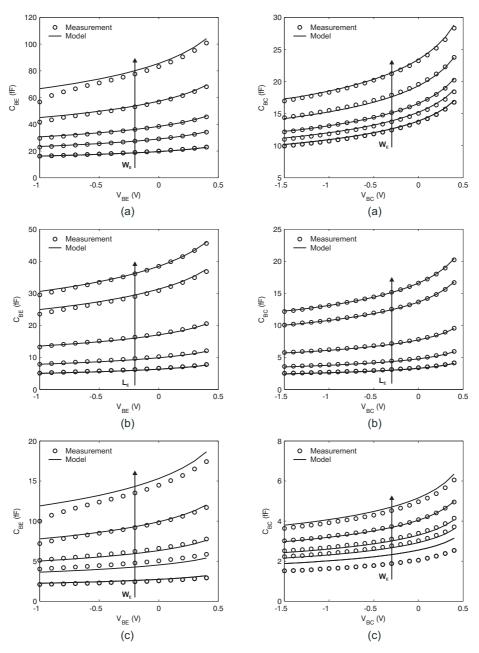

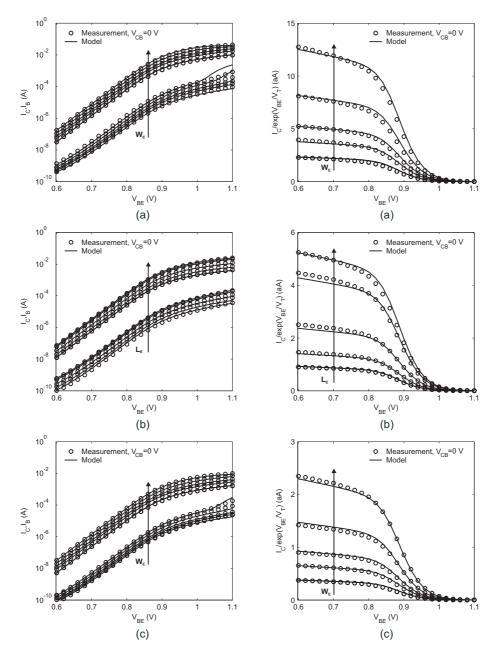

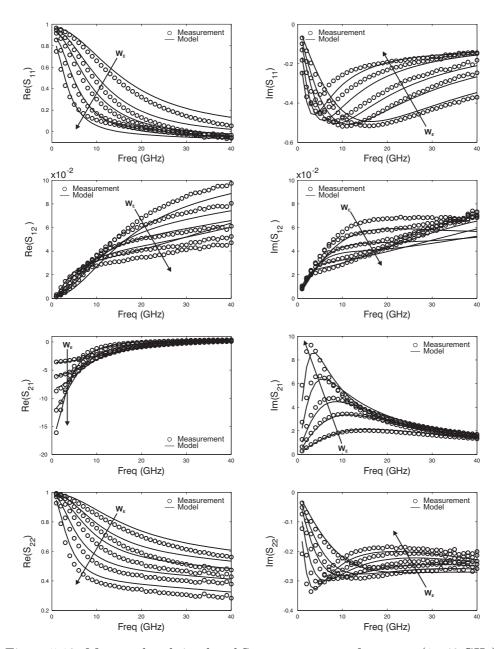

In Chapter 5, a reference based geometry scalable model and its parameter extraction procedure is proposed. The scaling rules for the scalable Mextram model are based on device physics and then re-formulated in terms of reference parameters, geometry parameters and drawn dimensions of the device layout for geometry scaling. As a result, the parameters can be systematically extracted from the measured data of devices with different geometries. The new approach is tested with SiGe HBTs within an IC-CAP model file, which is extended from the single device parameter extraction procedure.

In Chapter 6, the extension of the geometry scalable Mextram model to the configuration scalable model including different emitter numbers and collector contacts for high-power applications is described. The configuration scalable model uses almost the same set of model parameters as the geometry scalable model except additional geometry parameters representing the mutual heating effect and collector resistance between two adjacent fingers and additional instance parameters representing different layout configurations. The configuration model nicely predicts the  $f_T$ -degradation measured from SiGe HBTs due to an increase of the mutual heating and an increase the collector delay time with increasing emitter numbers.

Finally, Chapter 7 presents the conclusion and suggestions for the future directions in bipolar device compact modeling.

10 Introduction

## Chapter 2

## Physics of the Mextram model

#### 2.1 Introduction

The worldwide interest in SiGe heterojunction bipolar transistors (HBTs) as a commercial IC technology is growing rapidly [37]. The corresponding circuit design activities essentially depend on accurate compact models of SiGe HBTs in all relevant modes of the transistor operation. This chapter gives an overview of the vertical bipolar transistor compact model Mextram (the acronym of the "most exquisite transistor model") and its capabilities to meet SiGe HBT circuit design challenges. The Mextram has been introduced by De Graaff and Kloosterman at Royal Philips Electronics in 1985 [27]. The first Mextram release was introduced as Level 501 but the "real" 5th generation bipolar transistor model (after the previous four generation described in Chapter 1) is believed to be Level 502 in 1986 [38] with complete epi-layer model. Following the requirements of the continuous technology development, Mextram has appeared later in several update releases: Level 503 in 1994 [39] and Level 504 in 2000 [40].

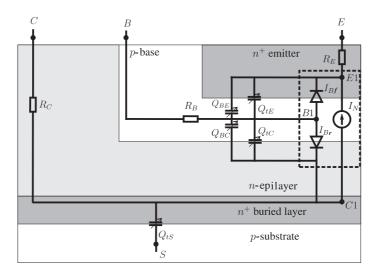

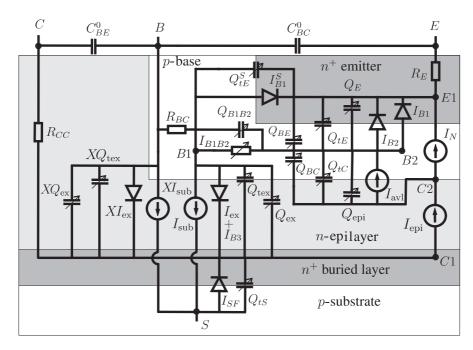

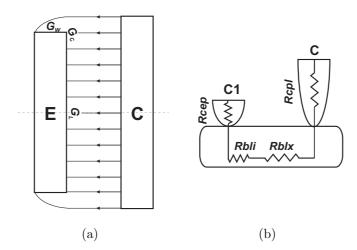

Fig. 2.1 shows the equivalent circuit of the Mextram model as it is specified in its latest release (Level 504). The branches representing model currents and charges are schematically associated with different physical regions of a bipolar transistor separated by the base-emitter (BE), base-collector (BC) and substrate-collector (SC) junctions. All current and charge branches in Mextram are given as explicit functions of external and internal nodal potentials and there are no implicit modeling variables that require internal iterations. The governing Mextram equations are formulated having in mind NPN tran-

Figure 2.1: The equivalent circuit of Mextram model.

sistors, but the model can be equally well used for PNP transistors with the same structure by simply change the current and charge polarities.

The main transfer current  $I_N$  in Mextram, as in the Gummel-Poon model, is evaluated in the quasi-neutral base (QNB) by the ICCR. However, the mathematical appearance of its equations governing the normalized QNB charge is slightly different in comparison to the Gummel-Poon model. The normalized QNB charge in Mextram is represented as a product of a normalized base charge without injection charges and a normalized base charge with injection charges. In the Gummel-Poon model, it is represented as a normalized sum of zero bias base charge, modulated depletion charges and injection charges. Moreover, the effects of graded Ge profile in QNB [41] are physically addressed in the transfer current description. A distinguished feature of the Mextram model is the description of the epilayer transfer current  $I_{\rm epi}$ . It is employed for intensive physical modelling of the quasi-saturation phenomena including base widening [8], hot-carrier behavior in the epilayer and advanced modeling of distortion effects [42].

The diode-like injection currents  $I_{B1}$ ,  $I_{B1}^S$ ,  $I_{B2}$ ,  $I_{B3}$ ,  $I_{ex}$  and  $XI_{ex}$  in the Mextram equivalent circuit describe various recombination currents in the

quasi-neutral and depletion transistor regions. The recombination in the modulated QNB, which is sometimes important for SiGe HBT applications [43], is also included. The effect of a distributed hole injection across the BE junction is described by an additional current branch  $I_{B1B2}$ . Mextram provides also a sophisticated model for the weak avalanche current in the branch  $I_{avl}$ . The contribution of the parasitic PNP transistor transfer current to the substrate current, represented by the current sources  $I_{sub}$  and  $XI_{sub}$ , is implemented by using a simplified Gummel-Poon integral charge control relationship.

The dynamic currents are accounted for by the depletion capacitances (charges)  $Q_{tE}$ ,  $Q_{tE}^S$ ,  $Q_{tC}$ ,  $Q_{tex}$ ,  $XQ_{tex}$  and  $Q_{tS}$  as well as diffusion charges (capacitances)  $Q_{BE}$ ,  $Q_{BC}$ ,  $Q_{E}$ ,  $Q_{epi}$ ,  $Q_{ex}$  and  $XQ_{ex}$  in the intrinsic and extrinsic transistor regions as shown in Fig. 2.1. The BC depletion capacitance is particularly equipped to account for the full depletion of the epilayer and modulation of the depletion charge by current in the BC depletion region. An additional charge branch  $Q_{B1B2}$  accounts for the distributed high frequency effects in the intrinsic transistor base.

The Mextram model is equipped with physical temperature scaling rules. Moreover, thermal phenomena are addressed in Mextram by a simple thermal impedance (thermal resistance and capacitance in parallel) and a power dissipation source but an elaborate thermal impedance network can be connected to the thermal node to model more complex self-heating and mutual heating effects. A set of temperature scaling parameters is extracted along with the corresponding electrical model parameters in a straightforward procedure [44]. The physical background of the Mextram parameters provides also an excellent framework for the geometrical [45] and configurational scaling [46].

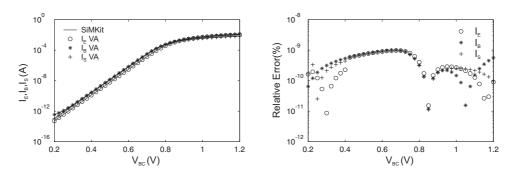

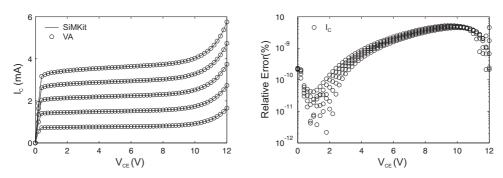

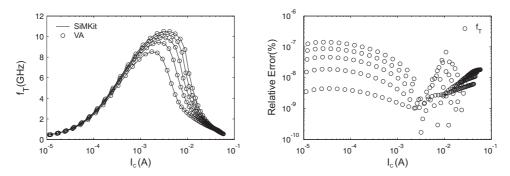

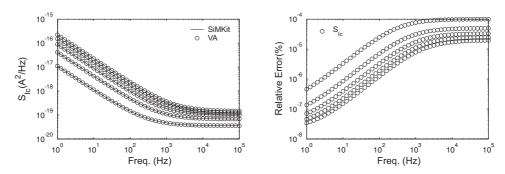

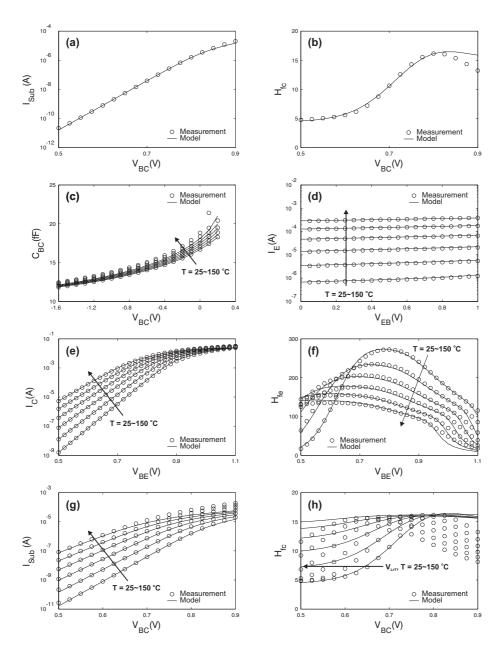

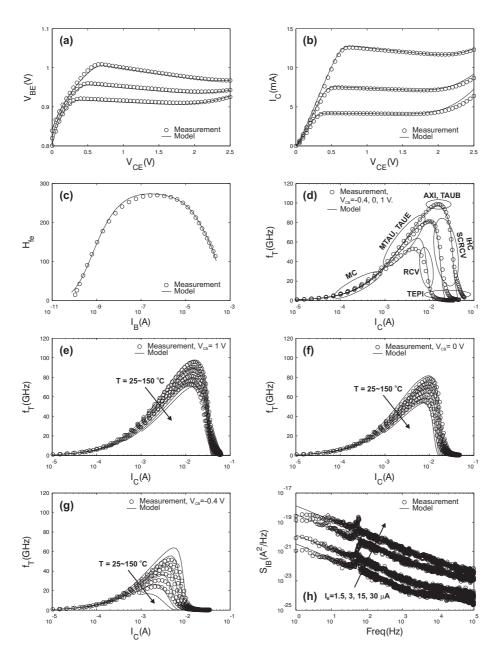

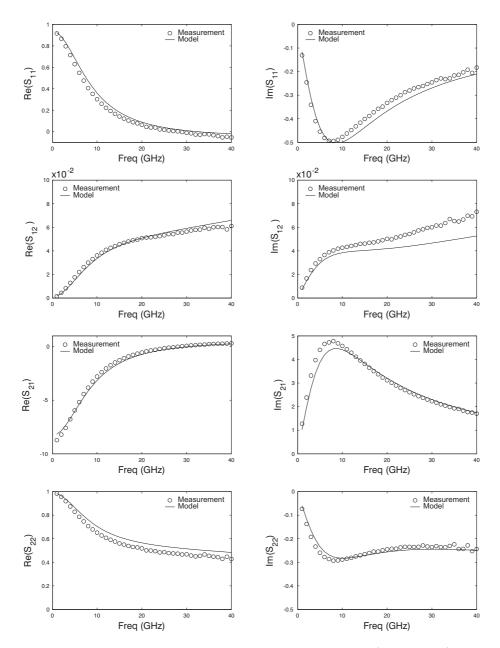

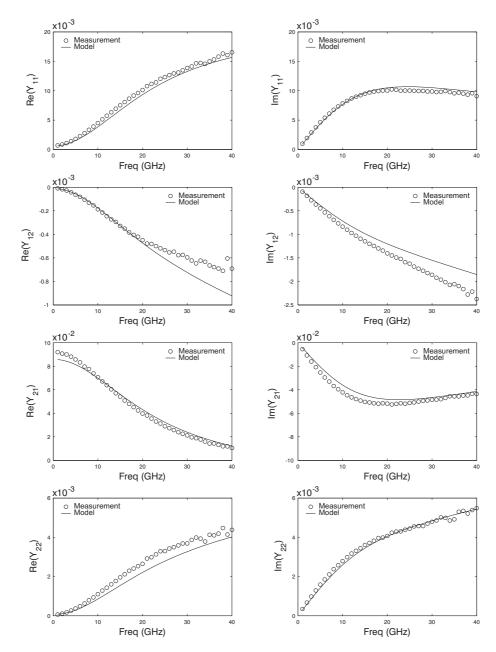

Mextram has been already used excessively in various SiGe HBTs applications including high performance SiGe HBT bipolar transistor integration [47], low noise amplifiers [48,49], power amplifiers [50,51] and SiGe HBT phototransistors [52]. As an additional illustration of Mextram capabilities, some results of the Mextram parameter extraction from an IBM SiGe HBT test sample device are demonstrated through the Compact Modeling Council's [30] bipolar model standardization procedure.

#### 2.2 Transfer current

The transfer current is maintained by the electron flow in vertical direction from the emitter contact to the collector buried layer and further up to the collector contact. The pure ohmic regions on that way are represented by the constant emitter resistance RE and collector resistance RCC. The electron current density  $J_n$  in QNB and epilayer is assumed to obey the one-dimensional drift-diffusion equation

$$J_n = -q\mu_n n(x) \frac{d\phi_n(x)}{dx} \tag{2.1}$$

where n is the electron concentration,  $\phi_n$  is the electron quasi-Fermi potential,  $\mu_n$  is the electron mobility, q is the elementary charge and the x-axis is directed from the emitter towards the epilayer region. Moreover, in the model derivation the electron and hole concentrations are related by the pn product

$$p(x)n(x) = n_{ie}^{2}(x) \exp\left(\frac{\phi_{pB} - \phi_{n}(x)}{V_{T}}\right)$$

(2.2)

where p is the hole concentration,  $n_{ie}$  is the position dependent effective intrinsic carrier concentration,  $\phi_{pB}$  is the constant hole quasi-Fermi level in the QNB, and  $V_T$  is the thermal voltage.

#### 2.2.1 Quasi-Neutral Base (QNB)

The electron current density (2.1), and transfer current  $I_N$ , can be expressed in QNB with the help of the pn product (2.2) as

$$J_n = -\frac{I_N}{A_E} = qV_T \mu_n(x) \frac{n_{ie}^2(x)}{p(x)} \cdot \frac{d}{dx} \exp\left(\frac{\phi_{pB} - \phi_n(x)}{V_T}\right), \qquad (2.3)$$

where  $A_E$  is the effective emitter area. Integrating (2.3) for constant  $J_n$  in the interval  $(x_{BE}, x_{BC})$ , where  $x_{BE}$  and  $x_{BC}$  denote the edges of the QNB,

$$I_{N} = \frac{qn_{i}^{2}A_{E}}{G\left(p; x_{BE}, x_{BC}\right)} \left[ \exp\left(\frac{\phi_{pB} - \phi_{n}(x_{BE})}{V_{T}}\right) - \exp\left(\frac{\phi_{pB} - \phi_{n}(x_{BC})}{V_{T}}\right) \right],$$

(2.4)

where  $n_i$  is the intrinsic carrier concentration and the functional

$$G(p; x_1, x_2) = \int_{x_1}^{x_2} \frac{p(x)}{\mu_n V_T} \left(\frac{n_i}{n_{ie}(x)}\right)^2 dx$$

(2.5)

is well known as the Gummel number [12]. The transfer current (2.4) is implemented in Mextram as

$$I_N = \frac{\text{IS}}{g_B} \left[ \exp\left(\frac{V_{B2} - V_{E1}}{V_T}\right) - \exp\left(\frac{V_{B2} - V_{C2}^*}{V_T}\right) \right],$$

(2.6)

where

$$g_B = \frac{G(p; x_{BE}, x_{BC})}{G(N_A; x_{BE}^0, x_{BC}^0)}$$

(2.7)

is the relative change of the Gummel number in QNB with BE and BC junction biases,  $x_{BE}^0$  and  $x_{BC}^0$  denote the edges of the QNB at zero bias,  $N_A$  is the acceptor doping concentration in the base and  $IS = qn_i^2A_E/G(N_A; x_{BE}^0, x_{BC}^0)$  is transfer saturation current. The quasi-Fermi potentials in (2.4) are replaced in (2.6) by the corresponding Mextram nodal biases. Note, that the value of the electron quasi-Fermi potential  $\phi_n(x_{BC})$  in (2.4) is not directly associated with the nodal bias  $V_{C2}$ . Instead an effective value  $V_{C2}^*$  is used in Mextram (Level 504) as provided by the epilayer model description.

The relative Gummel number  $g_B$  in (2.7) is further expressed in Mextram as a product  $g_B = g_{BW} \cdot g_{BH}$  where

$$g_{BW} = 1 + \frac{G(N_A; x_{BE}, x_{BE}^0)}{G(N_A; x_{BE}^0, x_{BC}^0)} + \frac{G(N_A; x_{BC}^0, x_{BC})}{G(N_A; x_{BE}^0, x_{BC}^0)}$$

(2.8)

and

$$g_{BH} = 1 + \frac{G(n; x_{BE}, x_{BC})}{G(N_A; x_{BE}, x_{BC})}.$$

(2.9)

The role of  $g_{BW}$  is to describe the relative change of the Gummel number in QNB with the modulation of BE and BC depletion widths (Early effect) at low injection. On the other hand, the term  $g_{BH}$  accounts for the relative change of the Gummel number in the QNB due to the minority electron concentration at high injection currents.

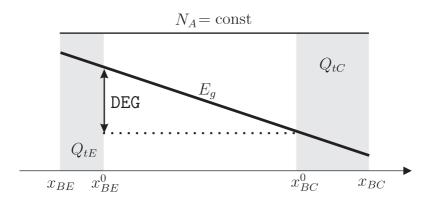

Assuming a linear graded Ge profile (and band-gap  $E_g$ ) in the QNB, as shown in Fig. 2.2, for the spatial dependence of  $(n_i/n_{ie})^2$  in (2.5) holds

$$\left(\frac{n_i}{n_{ie}}\right)^2 \propto \exp\left(-\frac{\text{DEG}}{qV_T \cdot w_{B0}} x\right),$$

(2.10)

where  $w_{B0} = x_{BC}^0 - x_{BE}^0$  is the width of the QNB and DEG =  $E_g(x_{BE}^0) - E_g(x_{BC}^0)$  is the band-gap difference over the base (in eV), both evaluated at zero bias. Integrating Gummel numbers in (2.8) for constant  $N_A$  and  $\mu_n$  using (2.10) the term  $g_{BW}$  becomes [34]

$$g_{BW} = 1 + \frac{\exp\left(\frac{\text{DEG}}{V_T} \frac{w_{BE}}{w_{B0}}\right) - 1}{1 - \exp\left(-\frac{\text{DEG}}{V_T}\right)} + \frac{\exp\left(-\frac{\text{DEG}}{V_T} \frac{w_{BC}}{w_{B0}}\right) - 1}{1 - \exp\left(\frac{\text{DEG}}{V_T}\right)}, \quad (2.11)$$

Figure 2.2: Doping and band-gap distribution in the QNB.

where  $w_{BE} = x_{BE}^0 - x_{BE}$  and  $w_{BC} = x_{BC} - x_{BC}^0$  define the modulation of BE and BC depletion regions. Notice that in the limiting case DEG = 0, the term  $g_{BW}$  is reduced to

$$g_{BW}^0 = 1 + \frac{w_{BE}}{w_{B0}} + \frac{w_{BC}}{w_{B0}} \tag{2.12}$$

representing the relative change of QNB width or the Early factor [21]. The relative variation of the depletion widths in (2.12) are implemented in Mextram in terms of the BE and BC depletion charges  $Q_{tE}$  and  $Q_{tC}$  as

$$\frac{w_{BE(C)}}{w_{B0}} = \frac{Q_{tE(C)}}{\text{VER(F)} \cdot \text{CJE(C)}}, \tag{2.13}$$

where CJE and CJC are zero-bias BE and BC depletion capacitances while VER and VEF are reverse and forward Early voltages. In that way,  $g_{BW}^0$  becomes identical to the Early factor proposed in [53] for silicon bipolar transistors. The model parameters VER and VEF may be interpreted for SiGe HBTs as the effective Early voltages that define the modulation rate of the QNB width instead of the Gummel number. For an alternative way to account for the Early effect in SiGe HBTs see [54].

The high injection term  $g_{BH}$  is implemented in Mextram in terms of minority electron concentration as

$$g_{BH} = 1 + \frac{1}{2} \left( \frac{n(x_{BE})}{N_A} + \frac{n(x_{BC})}{N_A} \right),$$

(2.14)

which for simplicity assumes uniform  $n_{ie}$  and linear distribution of n in QNB. The required normalized electron concentrations in (2.14) are evaluated solving the system of the electro-neutrality equation  $p = n + N_A$  and the pn product (2.2) at  $x_{BE}$  and  $x_{BC}$  as

$$\frac{n(x)}{N_A} = F\left(\frac{n_{ie}^2}{N_A^2} \exp\left(\frac{V_{B2} - \phi_n(x)}{V_T}\right)\right)$$

$$F(z) = \frac{2z}{1 + \sqrt{1 + 4z}}$$

(2.15)

where  $\phi_n(x_{BE}) = V_{E1}$  and  $\phi_n(x_{BC}) = V_{C2}^*$ . This is also the place where the forward knee current IK is introduced in Mextram using

$$\frac{n_{ie}^2}{N_A^2} = \frac{\text{IS}}{\text{IK}} \tag{2.16}$$

but in principle it has the same physical role in the description of the high current effects as the corresponding knee current parameter of the Gummel-Poon model [31].

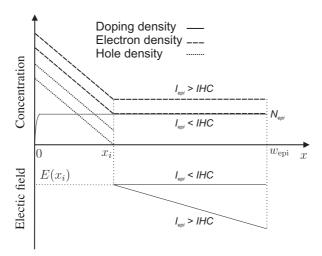

#### 2.2.2 Epilayer

The drop of the electron quasi-Fermi potential over epilayer is essential for the correct evaluation of  $\phi_n(x_{BC})$  and the transfer current  $I_N$  if the transistor is operating in quasi-saturation [55]. In that case, the epilayer region, between 0 and  $w_{\rm epi}$  having uniform donor doping concentration  $N_{\rm epi}$ , can be split into quasi-neutral injection region  $0 < x < x_i$  and drift region  $x_i < x < w_{\rm epi}$  as shown in Fig. 2.3.

From the pn product (2.2) we have

$$n(x)\frac{d\phi_n(x)}{dx} = -\frac{V_T}{p(x)}\frac{d\left(p(x)n(x)\right)}{dx} \tag{2.17}$$

which together with the quasi-neutrality condition  $n = N_{epi} + p$  allows to express the electron current density (2.1) in epilayer as [26]

$$J_n = -\frac{I_{\text{epi}}}{A_E} = q\mu_n N_{epi} \cdot V_T \left(\frac{2}{N_{epi}} + \frac{1}{p}\right) \frac{dp}{dx}.$$

(2.18)

Integrating (2.18) in the injection region for constant  $J_n$  and introducing the epilayer resistance  $RCV = w_{epi}/(q\mu_n N_{epi} A_E)$  we have

$$\frac{x_i}{w_{\text{epi}}} \text{RCV} \cdot I_{\text{epi}} = V_T \left( 2 \frac{p(0) - p(x_i)}{N_{epi}} + \ln \frac{p(0)}{p(x_i)} \right)$$

(2.19)

Figure 2.3: Distribution of the carrier concentrations and electric field in the epilayer when quasi-saturation occurs.

as an integral control relationship for the electron transport through the injection epilayer region. The normalized minority hole concentrations  $p(0)/N_{epi}$  and  $p(x_i)/N_{epi}$  in (2.19) are obtained similar to the electron normalized concentrations in (2.15) as

$$\frac{p(x)}{N_D} = F\left(\frac{n_{ie}^2}{N_{epi}^2} \exp\left(\frac{V_{B2} - \phi_n(x)}{V_T}\right)\right)$$

(2.20)

but this time the doping related term  $n_{ie}^2/N_{epi}^2$  is represented with the BC built-in voltage VDC as

$$\frac{n_{ie}^2}{N_{epi}^2} = \exp\left(-\frac{\mathtt{VDC}}{V_T}\right). \tag{2.21}$$

The drift epilayer region is neutral and has ohmic behavior as long as  $I_{\rm epi}$  is significantly smaller than the *critical current for velocity saturation* IHC =  $qA_EN_{epi}v_{\rm sat}$ , where  $v_{\rm sat}$  is the electron saturation velocity. Otherwise, the electron concentration becomes current dependent as  $n = N_{epi}I_{\rm epi}/{\rm IHC}$  and the electric field E(x) has slope defined by the Poisson equation

$$\frac{dE(x)}{dx} = \frac{qN_{epi}}{\epsilon} \left( 1 - \frac{I_{\rm epi}}{\rm IHC} \right), \tag{2.22}$$

where  $\epsilon$  is the permittivity of the epilayer. It should be emphasized that for the drift electron transport holds  $E(x) = -d\phi_n(x)/dx$  which allows to directly

evaluate the drop of  $\phi_n$  over the drift epilayer region integrating the Poisson equation (2.22) twice in the interval  $(x_i, w_{\text{epi}})$ . The result is

$$V_{C1} - \phi_n(x_i) = -E(x_i)w_{\text{epi}}d_R + \frac{qN_{epi}w_{\text{epi}}^2}{2\epsilon} \left(\frac{I_{\text{epi}}}{\text{IHC}} - 1\right)d_R^2, \qquad (2.23)$$

where  $d_R = 1 - x_i/w_{\text{epi}}$  is the relative depth of the drift epilayer region. Using the interface condition

$$E(x_i) = -\frac{v_s}{\mu_n} = -\frac{\text{IHC} \cdot \text{RCV}}{w_{\text{epi}}}$$

(2.24)

and introducing the epilayer space charge resistance SCRCV =  $qN_{\rm epi}w_{\rm epi}^2/(2\epsilon \cdot {\rm IHC})$ , (2.23) becomes

$$V_{C1} - \phi_n(x_i) = \text{IHC} \cdot \text{RCV} \cdot d_R + (I_{\text{epi}} - \text{IHC}) \cdot \text{SCRCV} \cdot d_R^2$$

(2.25)

and represents the governing equation for the electron transport through the drift epilayer region if  $I_{\rm epi}>$  IHC. The validity of (2.25) could be extended to the ohmic case after transformation

$$IHC \to \frac{IHC \cdot I_{\Omega}}{IHC + I_{\Omega}} \tag{2.26}$$

where

$$I_{\Omega} = \frac{V_{C1} - \phi_n(x_i)}{\text{RCV} \cdot d_R} \tag{2.27}$$

is the ohmic current in the drift epilayer region.

The integral relationships (2.19) and (2.25) for the injection and drift epilayer regions still require an additional condition to close the system of equations for unknown  $I_{\rm epi}$ ,  $x_i/w_{\rm epi}$  and  $\phi_n(x_i)$ . It may be the continuation of the electric field as proposed in [55]. In order to avoid implicit model variables and to improve smoothness of the modeling equations the present Mextram release (Level 504) implements the above epilayer physics in a qualitatively different way. Namely, the epilayer current  $I_{\rm epi}$ , as seen from the circuit simulator, is evaluated only from (2.19) applied to the whole epilayer. The governing equations (2.19) and (2.25) are then employed in the evaluation of the effective electron quasi-Fermi potential  $V_{C2}^* = \phi_n(x_{BC})$  that substitutes the nodal bias  $V_{C2}$  in all subsequent calculations. The detailed implementation procedure is given in [31,56].

#### 2.3 Recombination currents

The recombination currents in the intrinsic transistor region, due to the hole injection into quasi-neutral emitter (QNE) and BE space-charge region as well as recombination in QNB, actually serve to model the transistor forward base current. The ohmic part of the base region is represented by the *constant base resistance* RBC. The electron and hole injection across the BC junction, in the reverse transistor operation, are addressed in Mextram in the extrinsic transistor area. The carrier generation due to the weak avalanche effects is introduced separately as a controlled current source.

#### 2.3.1 Intrinsic transistor region

The carrier recombination in the intrinsic transistor region is indirectly evaluated in terms of the currents injected into quasi-neutral or space-charge regions. These currents are typically given in the form of a diode-like characteristics

$$I_D(V_j, I_0, m) = I_0 \left[ \exp\left(\frac{V_j}{mV_T}\right) - 1 \right],$$

(2.28)

where  $V_j$  is the junction voltage,  $I_0$  is the diode saturation current and m is the non-ideality factor.

The most important contribution to the static base current is the recombination (injection) into QNE. It is expressed in terms of the diode current (2.28) as

$$I_{BE} = I_D \left( V_{B2E1}, \frac{\mathtt{IS}}{\mathtt{BF}}, 1 \right), \tag{2.29}$$

where BF is the ideal forward current gain.

The recombination in the QNB may produce significant impact on the performance of SiGe HBTs [43]. It could be physically evaluated as an additional current component

$$I_{BB} = qA_E \int_{x_{BE}}^{x_{BC}} \frac{\Delta n}{\tau_n} dx, \qquad (2.30)$$

where  $\Delta n$  is the excess minority carrier concentration and  $\tau_n$  is the minority carrier lifetime in the QNB. Assuming that the excess minority concentrations

at the QNB boundaries are proportional to the injection currents as [57]

$$\Delta n(x_{BE}) \propto I_D\left(V_{B2E1}, \frac{\text{IS}}{\text{BF}}, 1\right)$$

and  $\Delta n(x_{BC}) \propto I_D\left(V_{B2C2}^*, \frac{\text{IS}}{\text{BF}}, 1\right)$ , (2.31)

the QNB recombination current (2.30) is implemented in Mextram as [34]

$$I_{BB} = \mathtt{XREC} \cdot \left[I_D\left(V_{B2E1}, \frac{\mathtt{IS}}{\mathtt{BF}}, 1\right) + I_D\left(V_{B2C2}^*, \frac{\mathtt{IS}}{\mathtt{BF}}, 1\right)\right] \left(1 + \frac{w_{BC}}{w_0}\right), \ (2.32)$$

where XREC is the *EB recombination current prefactor*. Note, that the width modulation of QNB, especially that due to the base-collector depletion capacitance, produces an Early-like effect in the forward base current.

The hole injection into QNE is essentially a two-dimensional phenomenon. Namely, a fraction of the holes is injected along the side walls of the BE junction. Moreover, the hole injection is laterally nonuniform along the intrinsic base below the emitter due to the variations of the internal base-emitter junction bias. The sidewall base current component is introduced by splitting the injection current into the area

$$I_{B1} = (1 - XIBI) [(1 - XREC) I_{BE} + I_{BB}]$$

(2.33)

and sidewall

$$I_{B1}^{S} = \text{XIBI} \cdot I_{D} \left( V_{B1E1}, \frac{\text{IS}}{\text{BF}}, 1 \right)$$

(2.34)

components by using the *diode partition factor* XIBI. The distributed injection along the pinched transistor base below the emitter is emulated using a nonlinear current branch [58,59]

$$I_{B1B2} = \frac{g_{BW}^0}{3 \cdot \text{RBV}} \left\{ V_{B1B2} + 2V_T \left[ \exp\left(\frac{V_{B1B2}}{V_T}\right) - 1 \right] \right\}, \tag{2.35}$$

where RBV is the resistance of the pinched base under the emitter at low injection. It may be approximated as

$$\mathrm{RBV} = \frac{\rho_\square W_E}{3L_E} \tag{2.36}$$

for the given pinched base sheet resistance  $\rho_{\square}$  as well as emitter width and length  $W_E$  and  $L_E$ , respectively.

The Shockley-Read-Hall (SRH) recombination [60,61] in the BE space-charge region is implemented in Mextram as a non-ideal diode current

$$I_{B2} = I_D (V_{B2E1}, IBF, MLF) + G_{\min} V_{B2E1},$$

(2.37)

where IBF is the saturation current and MLF is the emission coefficient of the BE leakage diode. A small conductance  $G_{\min} = 10^{-13} \,\Omega^{-1}$  in (2.37) is introduced for numerical stability.

#### 2.3.2 Extrinsic quasi-neutral regions

The current  $I_{\text{ex}}$  describes the recombination of carriers injected into the quasineutral regions of the extrinsic BC junction. It is evaluated by

$$I_{\text{ex}} = \frac{\text{IS}}{\text{BRI}} \frac{\exp\left(\frac{V_{B1C1}}{V_T}\right) - 1}{1 + \frac{1}{2} \frac{n(x_{BC}^{\text{ext}})}{N_A}},$$

(2.38)

where BRI is the ideal reverse current gain and

$$\frac{n(x_{BC}^{\text{ext}})}{N_A} = F\left(\frac{\text{IS}}{\text{IK}}\exp\left(\frac{V_{B1C1}}{V_T}\right)\right)$$

(2.39)

is the electron concentration at the edge of extrinsic QNB which is obtained in the same way as  $n(x_{BE})$  but for the bias  $V_{B1C1}$ . In principle  $I_{\rm ex}$  represents the ideal component of the reverse base current taking also high injection effects into account. An additional extrinsic current component  $XI_{\rm ex}$ , similar to (2.38) but evaluated for internal bias  $V_{BC1}$ , is introduced if the model flag EXMOD is set to 1.

It is also assumed that SRH recombination in the BC space-charge region considerably contributes to the extrinsic base current component. This current component is derived from maximum value of the net SRH recombination in the space charge region as [25]

$$I_{B3} = IBR \frac{\exp\left(\frac{V_{B1C1}}{V_T}\right) - 1}{\exp\left(\frac{V_{B1C1}}{V_T}\right) + \exp\left(\frac{VLR}{2V_T}\right)} + G_{\min}V_{B1C1}, \qquad (2.40)$$

where IBR is saturation current and VLR is the crossover voltage of the BC leakage diode.

#### 2.3.3 Weak avalanche current

The avalanche current  $I_{\text{avl}}$  is evaluated in Mextram as [62, 63]

$$I_{\text{avl}} = I_{\text{epi}} \int_{0}^{\text{WAVL}} \alpha_n \left( E(x) \right) \, dx, \tag{2.41}$$

where WAVL the effective width of the epilayer. The ionization rate  $\alpha_n$  is given by [64]

$$\alpha_n(E(x)) = A_n \exp\left(-\frac{B_n}{E(x)}\right) \tag{2.42}$$

and  $A_n$  and  $B_n$  are predefined model constants. Assuming the linear electric field distribution

$$E(x) = E_M \left( 1 - \frac{x}{\lambda_D} \right) \approx \frac{E_M}{1 + x/\lambda_D}$$

(2.43)

with the slope  $-1/\lambda_D$  around the maximum electric field value  $E_M$ , eqn.(2.41) may be integrated or express the weak avalanche current as

$$I_{\text{avl}} = I_{\text{epi}} \frac{A_n}{B_n} \lambda_D E_M \left[ \exp\left(-\frac{B_n}{E_M}\right) - \exp\left(-\frac{B_n}{E_M}\left(1 + \frac{\text{WAVL}}{\lambda_D}\right)\right) \right]. \quad (2.44)$$

The maximum electric field value  $E_M$  and  $\lambda_D$  are obtained from the Poisson equation (2.22) in the epilayer. To this end, it is rewritten as

$$\frac{dE(x)}{dx} = 2\frac{\text{VAVL}}{\text{WAVL}^2} \left( 1 - \frac{I_{\text{e}pi}}{\text{IHC}} \right), \tag{2.45}$$

where  $VAVL = qN_DWAVL^2/(2\epsilon)$  is the avalanche curvature voltage. If the model flag EXAVL is set to 1 the weak avalanche model handles also the electric field distribution in quasi-saturation due to the Kirk effect [31].

#### 2.4 Substrate currents

The substrate current is implemented in Mextram using a simplified Gummel-Poon integral charge control relationship for the parasitic PNP transistor:

$$I_{\text{sub}} = \frac{2 \cdot \text{ISS} \left[ \exp \left( \frac{V_{B1C1}}{V_T} \right) - 1 \right]}{1 + \sqrt{1 + 4 \frac{\text{IS}}{\text{IKS}}} \exp \left( \frac{V_{B1C1}}{V_T} \right)}, \tag{2.46}$$

where ISS is PNP transistor saturation current and IKS is the substrate knee current. Note, that the effects of the base width modulation by depletion capacitances is neglected and  $V_{SC1}=0$  is assumed. Moreover, the high-injection effects are expressed in terms of IS/IKS instead of ISS/IKS to simplify parameter extraction. An additional extrinsic substrate current component  $XI_{\rm sub}$ , similar to (2.46), but evaluated for an internal bias  $V_{BC1}$ , is introduced if the model flag EXMOD is set to 1. A diode-like current  $I_{SF}$  is added between the substrate and collector nodes, S and C1, to serve as an indicator of a falsely polarized SC junction.

It should be emphasized that the Mextram equivalent circuit is deliberately left without any circuit elements connecting the intrinsic substrate node S to the substrate contact. In that way, an external substrate network of arbitrary complexity could easily be attached to the intrinsic substrate node [65,66].

### 2.5 Charges and capacitances

The temporal variation of the electric field results in the displacement current components across the space charge regions. These dynamic current components are represented by the depletion capacitances (charges). On the other hand, the temporal variations of the compensated (diffusion) charges, produce an effective dynamic recombination current along the transistor transfer current flow which is implemented by the diffusion charges (capacitances). Mextram (Level 504) takes also into account the BE and BC parasitic overlap capacitances CBEO and CBCO as shown in Fig. 2.1.

#### 2.5.1 Depletion capacitances

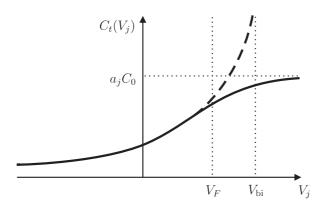

The bias dependence of the depletion capacitances is in Mextram generally considered as

$$C_t(V_j) = (1 - X_p) \frac{C_0 f_I}{\left(1 - \frac{V_j^{\text{eff}}(V_j)}{V_{\text{bi}}}\right)^P} + X_p C_0,$$

(2.47)

where  $C_0$  is the zero bias depletion capacitance,  $V_j$  is the internal P-N junction bias,  $V_{\text{bi}}$  is the junction built-in voltage and P is the grading coefficient. The expression (2.47) is inspired by the simple empirical description for depletion capacitance of abrupt (or linear) P-N junctions but also enhanced, with

quantities  $X_p$  and  $f_I$  as well as function  $V_j^{\text{eff}}(V_j)$ , to increase the physical and computational range of the model validity.

In order to avoid singular capacitance behavior at the forward bias, an effective junction bias  $V_j^{\text{eff}}(V_j)$  is employed in the denominator of (2.47). It is related to the real junction bias  $V_j$  as

$$V_j^{\text{eff}}(V_j) = V_j - V_{\text{ch}} \ln \left[ 1 + \exp\left(\frac{V_j - V_F}{V_{\text{ch}}}\right) \right], \qquad (2.48)$$

where the control voltage

$$V_F = V_{\rm bi} \cdot \left(1 - a_j^{-1/P}\right) \tag{2.49}$$

forces the capacitance to asymptotically approach the constant value  $a_jC_0$  for  $V_j > V_F$  (see Fig. 2.4). The smoothness of this transition is defined by  $V_{\rm ch}$ . The quantity  $X_p$  in (2.47) limits the decrease of the capacitance under the reverse bias. It is of particular importance for BC depletion capacitance having a fully depleted epilayer region. Finally, the term  $f_I$  accounts for the modulation of the BC depletion capacitance by the transfer epilayer current. It is defined as

$$f_I = \left(1 - \frac{I_{\text{epi}}}{I_{\text{epi}} + \text{IHC}}\right)^{\text{MC}} \tag{2.50}$$

where MC is the *current-modulation coefficient*. Table 2.1 provides the corresponding model parameters in Mextram for the BE, BC and SC junctions.

Figure 2.4: Implementation of the Mextram depletion capacitances.

| · · · · · · · · · · · · · · · · · · · | Carrie            | 101   | Dopi | 01011 | capaci |

|---------------------------------------|-------------------|-------|------|-------|--------|

|                                       | $V_{\mathrm{bi}}$ | $C_0$ | P    | $X_p$ | $f_I$  |

| $\overline{\mathrm{BE}}$              | VDE               | CJE   | PE   | -     | -      |

| BC                                    | VDC               | CJC   | PC   | XР    | MC     |

| SC                                    | VDS               | CJS   | PS   | -     | -      |

Table 2.1: Parameters for Depletion capacitances.

For compact modeling purposes, it is much better to consider corresponding depletion charges

$$Q_t(V_j) = \int_0^{V_j} C_t \left( V_j^{\text{eff}}(V_j) \right) dV, \qquad (2.51)$$

instead of the depletion capacitances. The Mextram depletion charges (see Fig. 2.1) are implemented as

$$Q_{tE}(V_{B2E1}) = (1 - XCJE) \cdot Q_t(V_{B2E1}), \qquad (2.52)$$

$$Q_{tE}^{S}(V_{B1E1}) = \mathtt{XCJE} \cdot Q_t(V_{B1E1}), \qquad (2.53)$$

$$Q_{tC}(V_{B2C2}) = XCJC \cdot Q_t (V_{jC}(V_{B2C2})), \qquad (2.54)$$

$$Q_{\text{tex}}(V_{B1C1}) = (1 - \text{XCJC}) (1 - \text{XEXT}) Q_t (V_{B1C1}), \qquad (2.55)$$

$$XQ_{\text{tex}}(V_{BC1}) = (1 - \texttt{XCJC}) \cdot \texttt{XEXT} \cdot Q_t(V_{BC1}), \qquad (2.56)$$

$$Q_{tS}(V_{SC1}) = Q_t(V_{SC1}), (2.57)$$

where XCJE, XCJC and XEXT are geometry partitioning factors splitting the depletion capacitances into area and sidewall components as well as between intrinsic and extrinsic parts of the transistor. Note, that the internal BC junction bias  $V_{jC}$  in (2.54) has to be evaluated implicitly as a function of the bias  $V_{B2C2}$  in order to correctly take into account the effects of quasi-saturation in the epilayer [31].

#### 2.5.2 Diffusion charges

The diffusion charges are evaluated in Mextram independently for the QNB, QNE and epilayer as well as for the extrinsic transistor region.

For the linear distribution of electrons in QNB, the total base diffusion charge is

$$Q_B = Q_{B0} \cdot g_{BW}^0 \cdot \frac{1}{2} \left( \frac{n(x_{BE})}{N_A} + \frac{n(x_{BC})}{N_A} \right), \tag{2.58}$$

where  $Q_{B0} = qA_EW_{B0}N_A$ . In the quasi-static approximation, the base diffusion charge (2.58) is split into BE and BC components  $Q_{BE}$  and  $Q_{BC}$  as

$$Q_{BE(C)} = \frac{1}{2} \cdot \text{TAUB} \cdot \text{IK} \cdot g_{BW}^0 \cdot \frac{n(x_{BE(C)})}{N_A}, \tag{2.59}$$

associated with Mextram nodes E1 and C2. The model parameter TAUB =  $Q_{B0}/\text{IK}$  is introduced as base transit time.

The diffusion charge in the QNE (including the compensated charge in the BE space-charge region is expressed as

$$Q_E = Q_{E0} \left[ \exp \left( \frac{V_{B2E1}}{\text{MTAU} \cdot V_T} \right) - 1 \right], \tag{2.60}$$

where MTAU is the *emitter diffusion charge coefficient*. The emitter transit time can approximately be expressed from (2.60) as

$$\tau_E(I_N) \approx \frac{Q_{E0}}{I_N} \left(\frac{I_N}{\text{IS}}\right)^{1/\text{MTAU}}.$$

(2.61)

Introducing an emitter transit time as TAUE =  $\tau_E(IK)$ , the prefactor  $Q_{E0}$  in (2.60) becomes

$$Q_{E0} = \text{TAUE} \cdot \text{IK} \left(\frac{\text{IS}}{\text{IK}}\right)^{1/\text{MTAU}}$$

(2.62)

as it is implemented in Mextram. The epilayer diffusion charge

$$Q_{\text{epi}} = qA_E \int_{0}^{x_i} p(x) dx \qquad (2.63)$$

actually represent the hole (minority carrier) charge in the injection epilayer region. This charge can be related to the epilayer current by the Gummel integral charge relationship

$$I_{\text{epi}} = \frac{q^2 n_i^2 A_E^2 D_n}{Q_{\text{epi}}} \left[ \exp\left(\frac{V_{B2C2}^*}{V_T}\right) - \exp\left(\frac{V_{B2} - \phi_n(x_i)}{V_T}\right) \right]. \tag{2.64}$$

Introducing the epilayer transit time TEPI =  $W_{\rm epi}^2/(4D_n)$  and with the help of pn product (2.2), the epilayer diffusion charge can be expressed also as

$$Q_{epi} = \frac{Q_{epi0}^2}{4 \cdot \text{TEPI} \cdot I_{epi}} \left[ \frac{p(0)}{N_D} \left( \frac{p(0)}{N_D} + 1 \right) - \frac{p(x_i)}{N_D} \left( \frac{p(x_i)}{N_D} + 1 \right) \right], \quad (2.65)$$

where

$$Q_{epi0} = qA_E W_{epi} N_D = \frac{4 \cdot \text{TEPI} \cdot V_T}{\text{RCV}}.$$

(2.66)

For practical implementation in Mextram, the expression for  $Q_{\text{epi}}$  is combined with the expression for the epilayer current  $I_{\text{epi}}$  and further simplified [31,67].

The extrinsic diffusion charge is evaluated combining the expression for the injection in QNB and the epilayer in the extrinsic part of the transistor:

$$Q_{\rm ex} = \frac{\mathtt{TAUR}}{\mathtt{TAUB} + \mathtt{TEPI}} \frac{1}{2} \left( Q_{B0} \frac{n(x_{BC}^{ext})}{N_A} + Q_{\rm epi} \frac{p(x_W^{\rm ex})}{N_D} \right), \tag{2.67}$$

where TAUR is the reverse base transit time,

$$\frac{p(x_W^{\text{ex}})}{N_D} = F\left(\exp\left(\frac{V_{B1C1} - \text{VDC}}{V_T}\right)\right),\tag{2.68}$$

while  $n(x_{BC}^{ext})/N_A$  is given in (2.39). Further partition of the extrinsic diffusion charge, similar to that of the extrinsic injection currents, is possible if the model flag EXMOD is set to 1. In that case, a similar expression to (2.67) is used to evaluate the extrinsic charge  $XQ_{\rm ext}$  in terms of junction bias  $V_{BC1}$ . The BC diode partition factor XEXT is used to split their contributions.

#### 2.5.3 Distributed and non-quasi-static charges

In high-frequency and high-speed applications the quasi-static assumption is no longer valid. Moreover, the effects of the distributed capacitances along the BE junction should be taken into account. The high-frequency currentcrowding effects are model by introducing an effective charge branch

$$Q_{B1B2} = \frac{1}{5} \frac{dQ_{B2E1}}{dV_{B2E1}} V_{B1B2}, \tag{2.69}$$

where  $Q_{B2E1} = Q_{tE} + Q_{BE} + Q_{E}$ .

The non-quasi-static effects in QNB base are accounted for in Mextram by introducing charge partitioning:

$$Q_{BC} \to \frac{1}{3}Q_{BE} + Q_{BC}$$

and  $Q_{BE} \to \frac{2}{3}Q_{BE}$ . (2.70)

Both modeling options require the flag EXPHI to be set to 1.

# 2.6 Thermal phenomena

The electrical characteristics of bipolar transistors are particularly susceptible to temperature variations due to the self-heating or thermal interaction with other devices. The electro-thermal effects are implemented in Mextram as a combination of the electrical model (current and charge branches), with temperature dependent parameters, and a thermal model that links the device average temperature to the dissipated electrical power. The temperature scaling parameters are based on strong physical background of the electrical parameters.

The default Mextram thermal model is a one-pole linear thermal impedance (parallel thermal resistance RTH and thermal capacitance CTH of the device surrounding) connected between the external thermal node dT and the zero bias (ambient) device temperature. If necessary, the default thermal impedance may be suspended and bypassed by a more advanced thermal network via the external thermal node. In order to correctly take into account the time delays of the internal biases, the total dissipated power in the device is calculated as a sum of the power dissipated in all nonreactive circuit elements.

Most of the Mextram current and charge modeling expressions have explicit temperature dependence. The actual device temperature is expressed as

$$T = T_A + DTA + V_{dT} + 273.15 K,$$

(2.71)

where  $T_A$  is the ambient (simulation) temperature, parameter DTA specifies a constant temperature shift to the ambient temperature and  $V_{dT}$  is the temperature at the thermal node dT. The electrical potential at the thermal node dT actually represents the excess device temperature in K. The temperature at which the electrical parameters are extracted is the reference temperature TREF in  $^0C$  or  $T_{\text{ref}} = \text{TREF} + 273.15 \ K$ .

The model parameters depend implicitly on temperature via the intrinsic carrier concentration and the carrier mobility temperature dependence. The temperature dependence of the intrinsic carrier concentration is

$$n_i^2 \propto t_N^3 \exp\left(-\frac{\text{VG*}}{V_{\Delta T}}\right),$$

(2.72)

where

$$t_N = \frac{T}{T_{\text{ref}}},\tag{2.73}$$

$$\frac{1}{V_{\Delta T}} = \frac{q}{k} \left( \frac{1}{T} - \frac{1}{T_{\text{ref}}} \right), \tag{2.74}$$

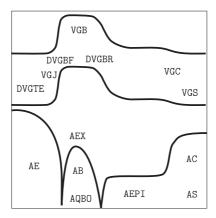

Figure 2.5: Temperature scaling parameters.

and k is the Boltzmann constant. The '\*' may be B, C, S and J for the band-gap in base, collector, substrate and BE depletion region, respectively. This approach is particularly suitable for HBTs with varying band-gap across the device. The carrier mobility is scaled with temperature as

$$\mu \propto t_N^{-A*},\tag{2.75}$$

where '\*' may be E, B, EX EPI, C and S for the emitter, base, extrinsic base, epilayer, collector and substrate region, respectively.

A few temperature scaling parameters, which could particularly be important for SiGe HBT applications, are introduced separately for certain electrical parameters. The forward and reverse current gain parameters BF and BRI depend on the difference of band-gaps at BE and BC junctions. Their temperature dependence is additionally expanded by

$$\mathrm{BF}(\mathrm{RI}) \propto \exp\left(-\frac{\mathrm{DVGBF}(\mathrm{R})}{V_{\Delta T}}\right), \tag{2.76}$$

where DVGBF and DVGBR are the *band-gap voltage differences*. An additional temperature parameter DAIS for fine tuning of temperature dependence of collector-emitter saturation current is given as

$${\rm IS} \propto t_N^{4-{\rm AB-AQBO+DAIS}} \exp\left(-\frac{{\rm VGB}}{V_{\Delta T}}\right). \tag{2.77}$$

It is well known that the compensated charge in the BE space-charge region could have significant effect on the dynamic performance of SiGe HBTs

2.7 Noise 31

[57]. This charge also has a different temperature dependence from the base diffusion charge. In Mextram it may easily be taken into account by the temperature dependence

TAUE

$$\propto \exp\left(-\frac{\text{DVGTE}}{V_{\Delta T}}\right)$$

, (2.78)

where DVGTE is the emitter transit time band-gap voltage difference. Finally, the base zero-bias charge  $Q_{B0}$  has a separate temperature scaling coefficient AQBO. Since it accounts also for the temperature dependence of  $w_{B0}$ , it is crucial for the temperature scaling of Early voltages VER and VEF but also for the Ge-related parameter DEG as

$$\mathrm{DEG} \propto t_N^{\mathrm{AQBO}}. \tag{2.79}$$

Fig. 2.5 shows the complete set of Mextram temperature scaling parameters associated with different band-gaps or doping areas along the transistor structure.

# 2.7 Noise

Noise is the statistical fluctuation of the terminal currents or voltages due to the quantization of charge, thermal motion of the carriers and generation or recombination process [68]. There are three different kinds of noise sources in the Mextram model, which are the thermal noise, shot noise and flicker noise. The thermal and shot noises are white noises, which are frequency independent, while the flicker noise is frequency dependent.

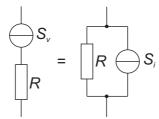

The thermal noise is generated from the random thermal motion of the carriers in a conducting material. As a result, a noise voltage source  $S_v$  in the unit of power spectral density (V<sup>2</sup>/Hz) in the frequency band of 1 Hz is in series with a noiseless constant resistance R during noise analysis, expressed as

$$S_v = 4kTR. (2.80)$$

The term  $S_v$  in series with R can be transformed to an equivalent noise current source  $S_i$   $(A^2/Hz)$  in parallel with R as shown in Fig. 2.6 by

$$S_i = \frac{S_v}{R^2},$$

$$= \frac{4kT}{R}.$$

(2.81)

Figure 2.6: thermal noise equivalent circuit for a resistor.

In Mextram, a noise current source  $S_i$  is added in parallel with the temperature scaled resistances  $\mathtt{RE}_{\mathtt{T}}$ ,  $\mathtt{RBC}_{\mathtt{T}}$  and  $\mathtt{RCC}_{\mathtt{T}}$ , but the thermal noise from the variable base resistance due to current crowding is described as [69]:

$$S_{iR_{BV}} = 4kT \frac{g_{BW}^0}{RBV_T} \frac{4e^{V_{B1B2}/V_T} + 5}{9}, \qquad (2.82)$$

which is added to the nonlinear current branch  $I_{B1B2}$ .

The shot noise that arises from the dc current I flowing through a PN junction is described as

$$S_i = 2q|I|. (2.83)$$

The shot noise source  $S_i$  is added in parallel with the branch current  $I_N$ ,  $I_{B1}$ ,  $I_{B2}$ ,  $I_{B1}^S$ ,  $I_{B3}$ ,  $I_{Sub}$ ,  $XI_{Sub}$  and  $I_{ex}$ . When EXMOD=1, the shot noise contribution from the sidewall base current  $(XI_{ex})$  of the parasitic PNP is also taken into account.

The flicker noise is a low frequency noise source due to the generation recombination process in the PN junction. It is empirically modeled as

$$S_i = \frac{\mathrm{KF}}{f} |I|^{\mathrm{AF}},\tag{2.84}$$

where f is the measured frequency. AF and KF are fitting parameters. The flicker noise of the branch current  $I_{B3}$  and  $I_{ex}$  is modeled by (2.84). As a result of splitting the base currents of the NPN and the parasitic PNP in the Mextram model, the flicker noise from the area contribution of  $I_{B1}$  is modeled as

$$S_i = \frac{\text{KF}}{f} (1 - \text{XIBI}) \left( \frac{|I_{B1}|}{1 - \text{XIBI}} \right)^{\text{AF}}, \qquad (2.85)$$

and the flicker noise from the sidewall contribution  $(I_{B1}^S)$  is modeled as

$$S_i = \frac{\text{KF}}{f} \text{XIBI} \left( \frac{|I_{B1}^S|}{\text{XIBI}} \right)^{\text{AF}}. \tag{2.86}$$

2.7 Noise 33

However, the flicker noise from  $I_{B2}$  [70] is slightly different from the ideal one. It is modeled as

$S_i = \frac{\text{KFN}}{f} |I_{B2}|^{2(\text{MLF}-1) + \text{AF}(2-\text{MLF})} \triangle f$  (2.87)

to take MLF into account. In addition, when extended modeling of reverse current gain (EXMOD=1) is considered, the flicker noise from  $I_{ex}$  and  $XI_{ex}$  are modeled as

$$S_i = \frac{\text{KF}}{f} (1 - \text{XEXT}) \left( \frac{|I_{ex}|}{1 - \text{XEXT}} \right)^{\text{AF}}, \qquad (2.88)$$

and

$$S_i = \frac{\text{KF}}{f} \text{XEXT} \left( \frac{|XI_{ex}|}{\text{XEXT}} \right)^{\text{AF}}. \tag{2.89}$$

There is also excess noise due to avalanche effect [71, 72] in the Mextram model. The extra noise sources resulting from the avalanche effect are split and added to  $I_{B1}$  and  $I_N$ . So, the noise currents in parallel with  $I_{B1}$  and  $I_N$  are increased and correlated. The  $I_N$  excess noise spectral density  $(S_{i_{Nex}})$ , the  $I_{B1}$  excess noise spectral density  $(S_{i_{B1ex}})$  and their correlated noise spectral density  $(S_{i_{B1ex}})$  are represented as [31]:

$$S_{i_{Nex}} = \text{KAVL} \cdot 2qI_{avl}(3 + 2G_{EM}), \qquad (2.90)$$

$$S_{i_{B1ex}} = \text{KAVL} \cdot 2qI_{avl}(1 + 2G_{EM}), \tag{2.91}$$

$$S_{i_{B1ex}i_{Nex}} = -\text{KAVL} \cdot 2qI_{avl}(2 + 2G_{EM}). \tag{2.92}$$

Where KAVL is the model parameter to switch on/off the excess noise,  $I_{avl}$  is the avalanche current and " $G_{EM}$ " is the multiplication factor minus one (M-1).

# 2.8 Conclusion

Mextram model covers all the important effects in modern bipolar devices including:

- 1. Bias-dependent Early effect;

- 2. Low-level non-ideal base currents;

- 3. High-injection effects;

- 4. Ohmic resistance of epilayer;

- 5. Velocity saturation effects on the resistance of the epilayer;

- 6. Hard and quasi-saturation (including non-ohmic quasi-saturation effect):

- 7. Weak avalanche (optionally including snap-back behavior);

- 8. Charge storage effects;

- 9. Split base-collector and base-emitter depletion capacitance;

- 10. Substrate effects and parasitic PNP;

- 11. Explicit modelling of inactive regions;

- 12. Current crowding and conductivity modulation of the base resistance;

- 13. First order approximation of the distributed high frequency effects in the intrinsic base (high-frequency current crowding and excess phase-shift);

- 14. Recombination in the base (meant for SiGe transistors);

- 15. Early effect in the case of graded bandgap (meant for SiGe transistors);

- 16. Temperature scaling;

- 17. Self-heating;

- 18. Thermal noise, shot noise and 1/f noise,

which meet various circuit design (ECL, mixer, VCO, LNA, PA... ) requirements.

In addition, it is elected by the members of the Compact Modelling Council as the bipolar standard model along with the HICUM model. The latest Mextram model level 504.6 parameters are listed in Appendix A.

# Chapter 3

# Model implementation and verification

## 3.1 Introduction

The path from compact model development to the implementation into a commercial circuit simulator is often time consuming. Moreover, it is not always straightforward how to implement behavioral models in SPICE-like simulators. In this chapter, the capability of the analog hardware description language (AHDL) Verilog-A [73] to handle a state-of-the-art compact bipolar transistor model mixed with a behavioral substrate coupling model is described. Verilog-A is a high-level language developed to describe the structure and behavior of analog systems and their components. It is an extension to the IEEE 1364 Verilog HDL specification for the digital design. The analog systems are described in Verilog-A in a modular way using hierarchy and different levels of model complexity. The motivation is to move into a higher level of abstraction in analog design and a combination with the digital design.

The basic programming unit for the structural and behavioral description of analog systems in Verilog-A is a **module**. The analog system structure is defined through the module's input and output signals and their connections. On the other hand, a sequence of mathematical equations is employed at the core of the module to describe its behavior. Here is an example of how a simple resistor is implemented in Verilog-A: