---

# Design of a 4-bit RISC Processor in Silicon Carbide Technology

---

*Master's Thesis*

Jianeng Xu

---

# Design of a 4-bit RISC Processor in Silicon Carbide Technology

---

THESIS

submitted in partial fulfillment of the

requirements for the degree of

MASTER OF SCIENCE

in

ELECTRICAL ENGINEERING

by

Jianeng Xu

born in Wuxi, China

The Electronic Components, Technology and Materials Group

Department of Electrical Engineering

Faculty EEMCS, Delft University of Technology

Delft, the Netherlands

[www.ewi.tudelft.nl](http://www.ewi.tudelft.nl)

---

# Design of a 4-bit RISC Processor in Silicon Carbide Technology

---

Author: Jianeng Xu

Student id: 5940311

## Abstract

Silicon carbide (SiC) is a wide-bandgap semiconductor with excellent thermal stability, high breakdown voltage, and robustness under harsh environments, making it well-suited for high-temperature digital logic applications. Compared with conventional silicon, SiC devices maintain reliable operation at significantly higher temperatures due to their strong electric field tolerance and reduced leakage characteristics. However, as an emerging technology, its integration level for digital circuits is still in a preliminary stage and requires validation through a full chip design and fabrication process.

This thesis presents the design and simulation of a fully functional 4-bit RISC processor in a  $2 \mu\text{m}$  SiC CMOS process developed by Fraunhofer IISB. The processor includes the implementation of the ALU, program counter, control unit, and memory blocks, together with validation of its functionality and performance through circuit-level simulations across a wide temperature range. Results demonstrate stable operation and robustness up to  $500^\circ\text{C}$ , as well as reliable logic performance at clock frequencies up to 750 kHz. The work further establishes a foundation for future digital systems based on the Fraunhofer IISB SiC CMOS process, paving the way toward more complex architectures such as 16-bit processors for real-world harsh-environment applications.

## Thesis Committee:

Chair: Dr. Ir. Sten Vollebregt, Faculty EEMCS, TU Delft

University supervisor: Dr. Ir. Sten Vollebregt, Faculty EEMCS, TU Delft

Committee Member: Dr. Chang Gao, Faculty EEMCS, TU Delft

---

# Contents

|                                                                                   |            |

|-----------------------------------------------------------------------------------|------------|

| <b>Contents</b>                                                                   | <b>iii</b> |

| <b>List of Figures</b>                                                            | <b>v</b>   |

| <b>1 Introduction</b>                                                             | <b>1</b>   |

| 1.1 Motivation . . . . .                                                          | 1          |

| 1.2 Research Objective . . . . .                                                  | 2          |

| 1.3 Thesis Outline . . . . .                                                      | 3          |

| <b>2 Literature Review</b>                                                        | <b>5</b>   |

| 2.1 Properties of SiC Devices for CMOS Integrated Circuits . . . . .              | 5          |

| 2.1.1 Fundamental Material Properties of 4H-SiC . . . . .                         | 5          |

| 2.1.2 The Fraunhofer IISB 4H-SiC CMOS Technology . . . . .                        | 8          |

| 2.2 Digital Circuit Design in SiC Technology . . . . .                            | 11         |

| 2.2.1 Pioneering Work in Early SiC Processes . . . . .                            | 12         |

| 2.2.2 Digital Circuits in IISB 4H-SiC CMOS Process . . . . .                      | 14         |

| 2.2.3 Design Characteristics and Considerations of SiC Digital Circuits . . . . . | 15         |

| 2.3 RISC Processor Design and Integration in SiC Technology . . . . .             | 18         |

| 2.3.1 Minimalist RISC Processors as Validation Vehicles . . . . .                 | 18         |

| 2.3.2 Existing SiC Processor Demonstrations and Integration Insights . . . . .    | 20         |

| 2.3.3 Summary and Outlook . . . . .                                               | 22         |

| <b>3 Processor Architecture Design</b>                                            | <b>23</b>  |

| 3.1 Design Philosophy . . . . .                                                   | 23         |

| 3.2 Instruction Set Architecture (ISA) . . . . .                                  | 24         |

| 3.3 Top-Level Architecture . . . . .                                              | 25         |

| 3.4 Control Unit (FSM) . . . . .                                                  | 28         |

| 3.5 Functional Implementation . . . . .                                           | 31         |

|                     |                                                         |           |

|---------------------|---------------------------------------------------------|-----------|

| 3.6                 | Summary of Architectural Design                         | 31        |

| <b>4</b>            | <b>Logical Design and Functional Verification</b>       | <b>33</b> |

| 4.1                 | Control Unit Logic Design and Verification              | 33        |

| 4.1.1               | FSM Hardware Architecture and State Transition Design   | 33        |

| 4.1.2               | RTL Design and Behavioral Simulation                    | 35        |

| 4.1.3               | Digital Synthesis Flow                                  | 36        |

| 4.1.4               | Control Unit Optimization                               | 38        |

| 4.2                 | Processor Logic Design and Verification                 | 40        |

| 4.2.1               | Input Module Modification and Timing Improvement        | 40        |

| 4.2.2               | Functional Verification of Processor Operation          | 42        |

| 4.2.3               | Schematic Synthesis of TOP-Level                        | 42        |

| 4.3                 | Summary of Logical Design                               | 43        |

| <b>5</b>            | <b>Circuit-Level Design and Simulation in SiC</b>       | <b>45</b> |

| 5.1                 | Logic Gate Design                                       | 45        |

| 5.1.1               | SiC CMOS Inverter Characteristics and Transistor Sizing | 45        |

| 5.1.2               | Derivation of Standard Logic Cells                      | 51        |

| 5.2                 | ALU Implementation                                      | 53        |

| 5.3                 | Memory Components Implementation                        | 56        |

| 5.3.1               | D flip-flops and Registers                              | 57        |

| 5.3.2               | Program Counter                                         | 59        |

| 5.3.3               | Input Latch                                             | 59        |

| 5.4                 | Control Unit Implementation                             | 62        |

| 5.5                 | Processor Implementation and Performance Analysis       | 63        |

| 5.5.1               | Processor Implementation                                | 63        |

| 5.5.2               | Processor Performance Analysis                          | 66        |

| 5.6                 | Summary of Circuit Design and Simulation                | 71        |

| <b>6</b>            | <b>Layout Design and Verification</b>                   | <b>73</b> |

| 6.1                 | Design of Digital Standard Cell                         | 73        |

| 6.2                 | Critical Module Layouts                                 | 76        |

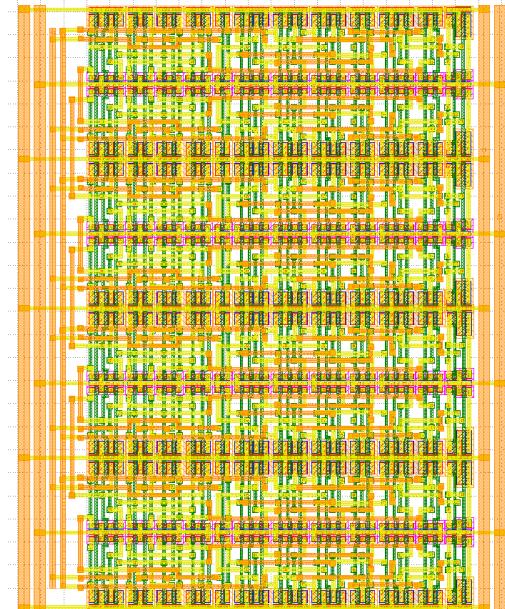

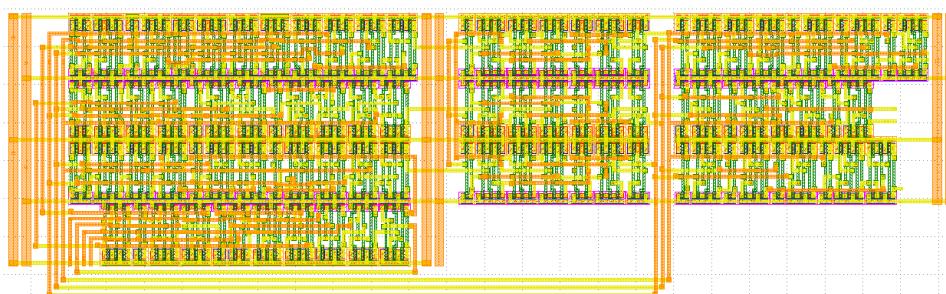

| 6.3                 | Top-Level Floorplan and Layout Implementation           | 76        |

| 6.4                 | Summary of Layout and Verification                      | 80        |

| <b>7</b>            | <b>Conclusions and Future Work</b>                      | <b>81</b> |

| 7.1                 | Summary of Contributions                                | 81        |

| 7.2                 | Future Work                                             | 82        |

| <b>Bibliography</b> |                                                         | <b>85</b> |

| <b>A</b>            | <b>Source Code</b>                                      | <b>89</b> |

| A.1                 | Control Unit Behavioral Implementation                  | 89        |

| A.2                 | Control Unit Structural Implementation                  | 92        |

| A.3                 | SiC 4-bit Processor Implementation                      | 95        |

---

# List of Figures

|     |                                                                                                                                                                                                                                                                                                                                                               |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

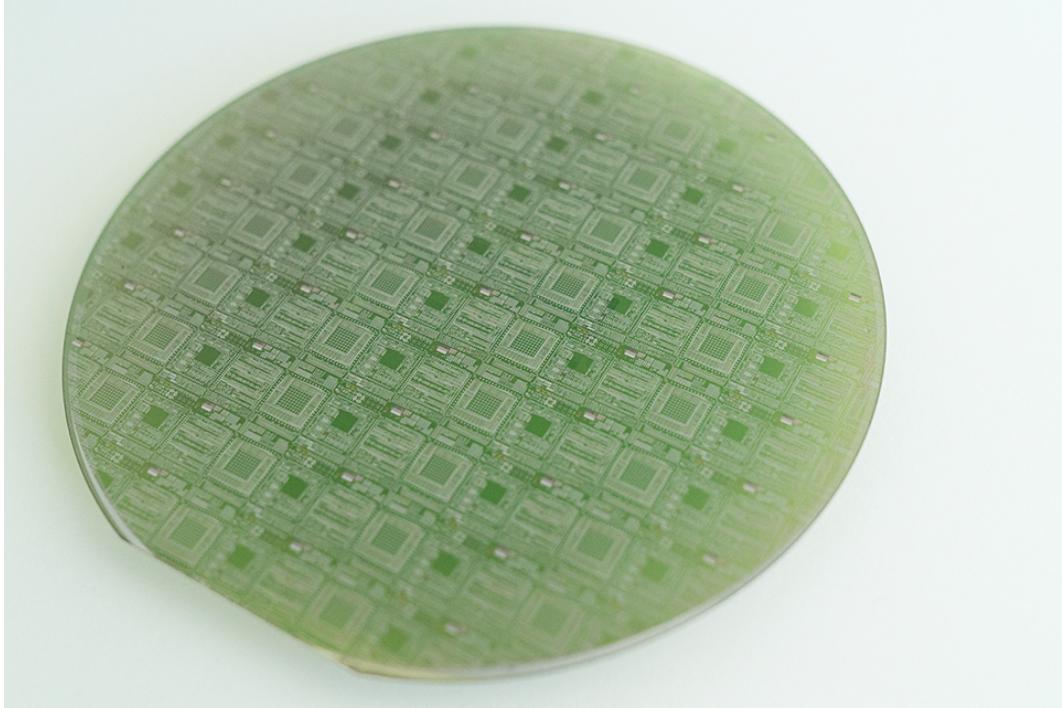

| 2.1 | 4H-SiC wafer with sensor arrays and integrated circuits in the Fraunhofer IISB technology [3] . . . . .                                                                                                                                                                                                                                                       | 6  |

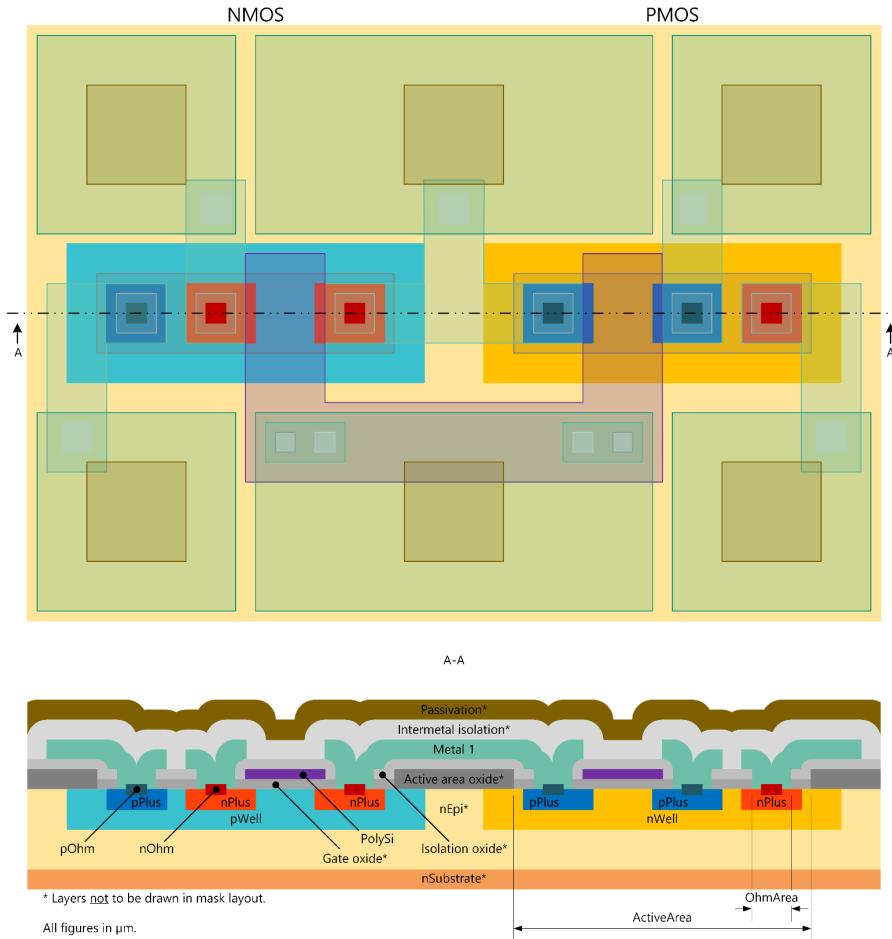

| 2.2 | Top view and cross section of the SiC MOSFET with metal layer in the Fraunhofer IISB 4H-SiC CMOS process [14]. . . . .                                                                                                                                                                                                                                        | 9  |

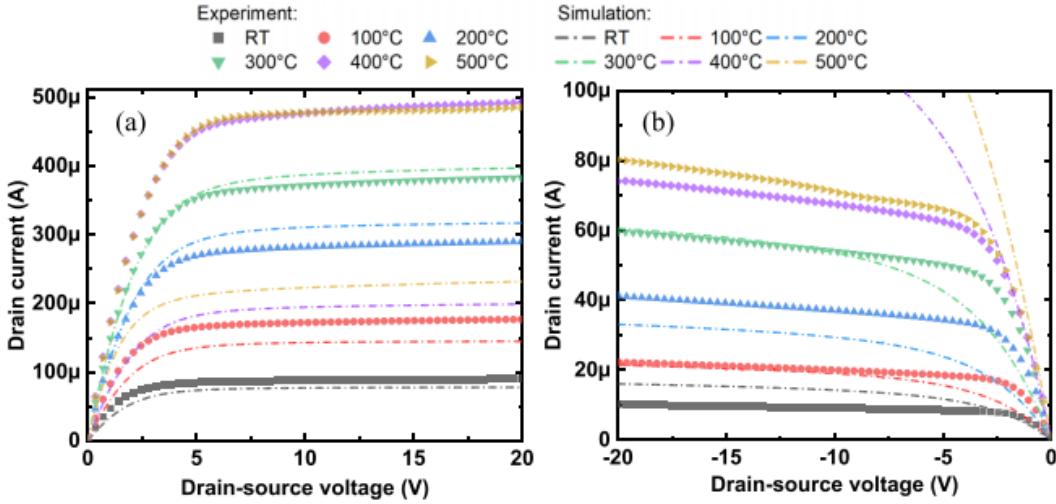

| 2.3 | Measured and simulated $I_{DS}$ - $V_{DS}$ characteristics of (a) NMOS and (b) PMOS transistors in the Fraunhofer IISB 4H-SiC CMOS process. The drain current increases notably with temperature, demonstrating enhanced carrier mobility and improved drive strength at elevated temperatures [15]. . . . .                                                  | 10 |

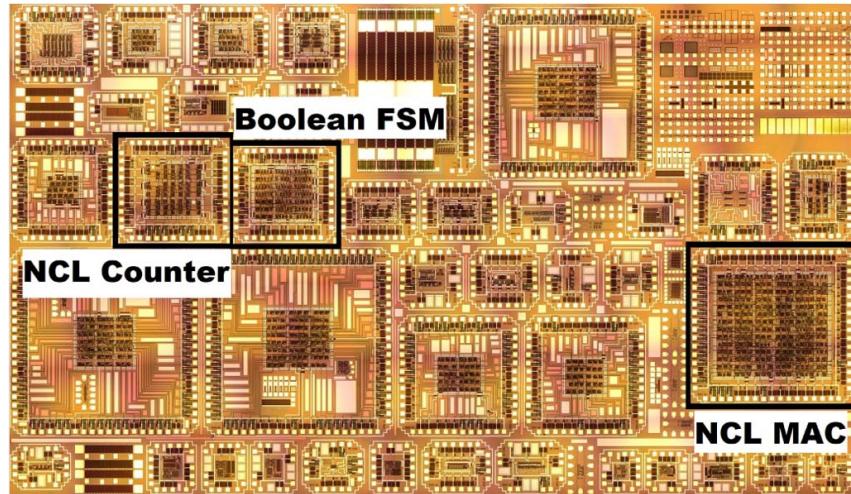

| 2.4 | Tapeout 1: Digital Circuits in HiTSiC® 4H-SiC CMOS [10] . . . . .                                                                                                                                                                                                                                                                                             | 13 |

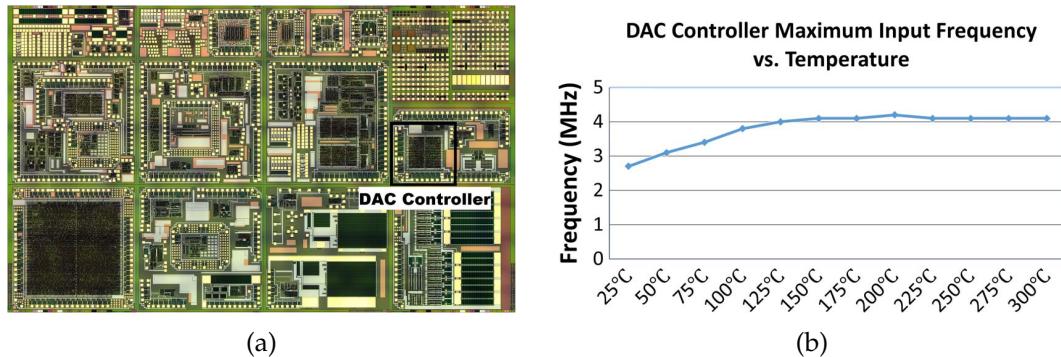

| 2.5 | (a) DAC controller layouts in HiTSiC® 4H-SiC CMOS and (b) corresponding graphical performance data of DAC controller [10]. . . . .                                                                                                                                                                                                                            | 13 |

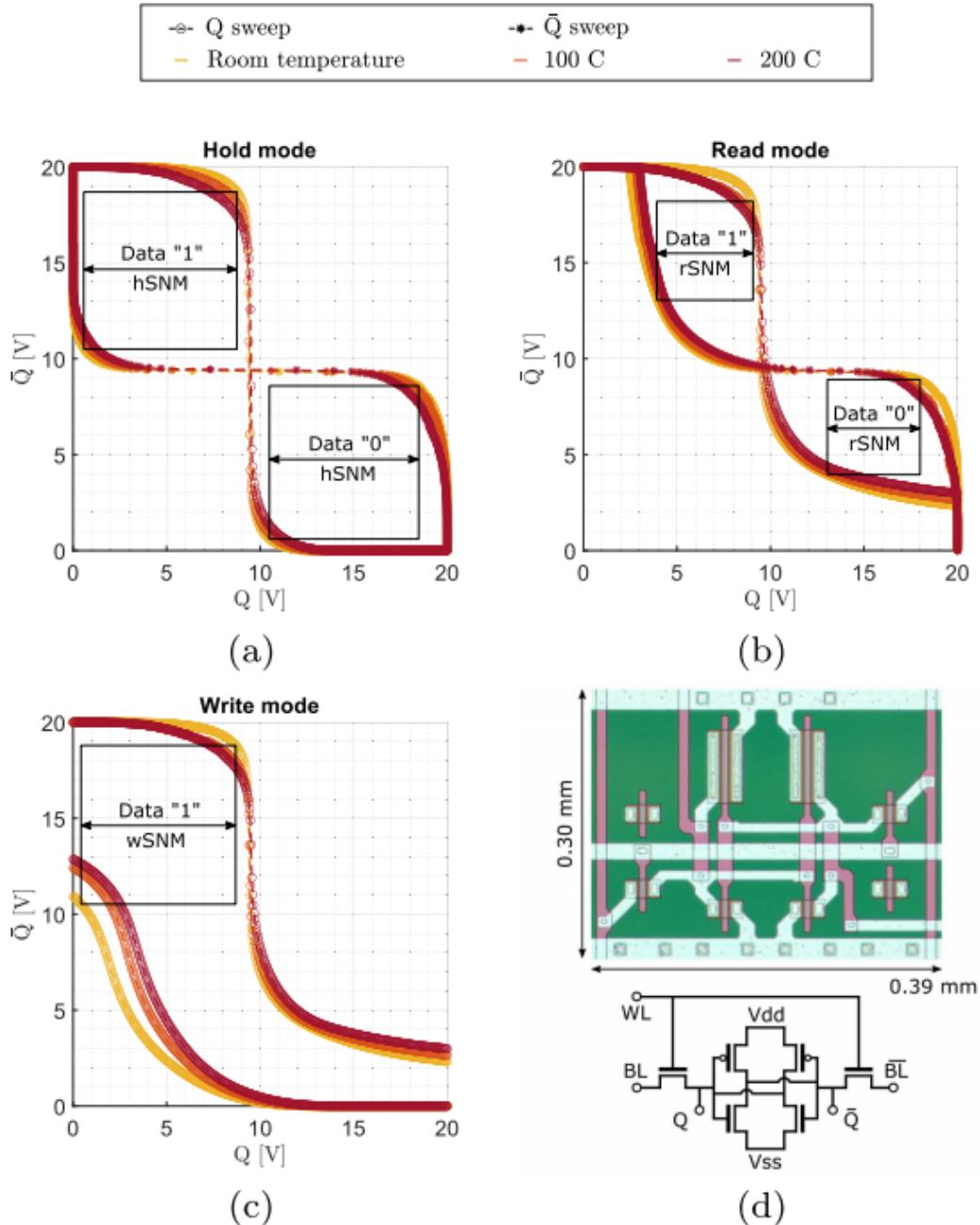

| 2.6 | Measured $Q/\bar{Q}$ SRAM cell butterfly curves for different temperature levels of (a) hold, (b) read, and (c) write mode including (d) circuit and micro-photograph on die (0, 2). A sweep of $Q/\bar{Q}$ and the maximum size squares are drawn for SNM derivation and a single sweep is depicted for the write mode in favor of readability [21]. . . . . | 16 |

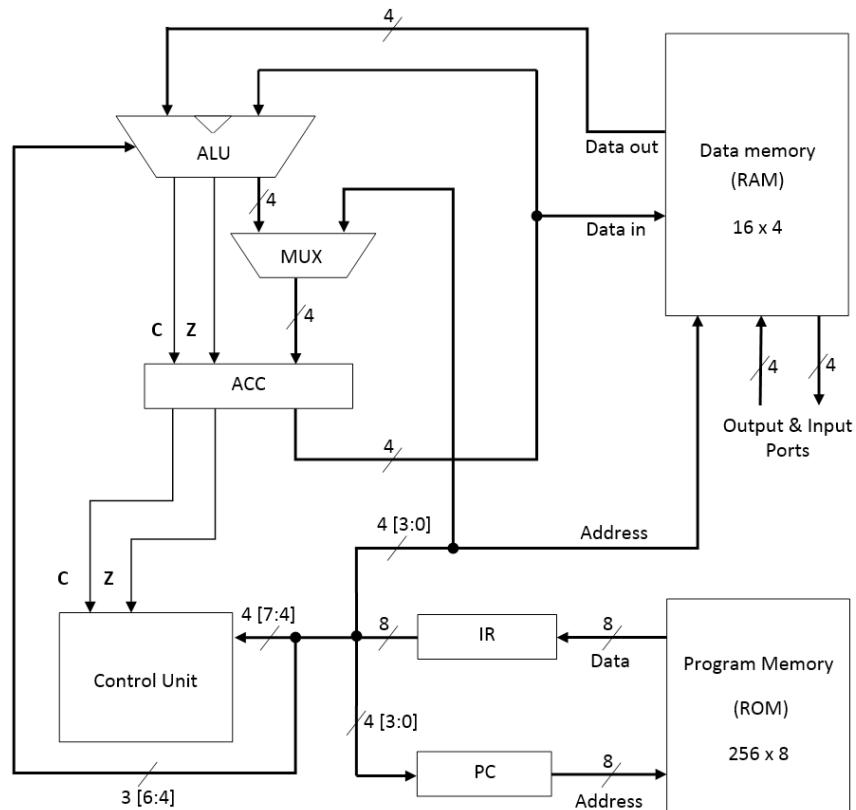

| 2.7 | The block diagram of a minimalist RISC processor showing the core modules and data flow between the ALU, ACC, control unit, ROM, and RAM [13]. . . . .                                                                                                                                                                                                        | 19 |

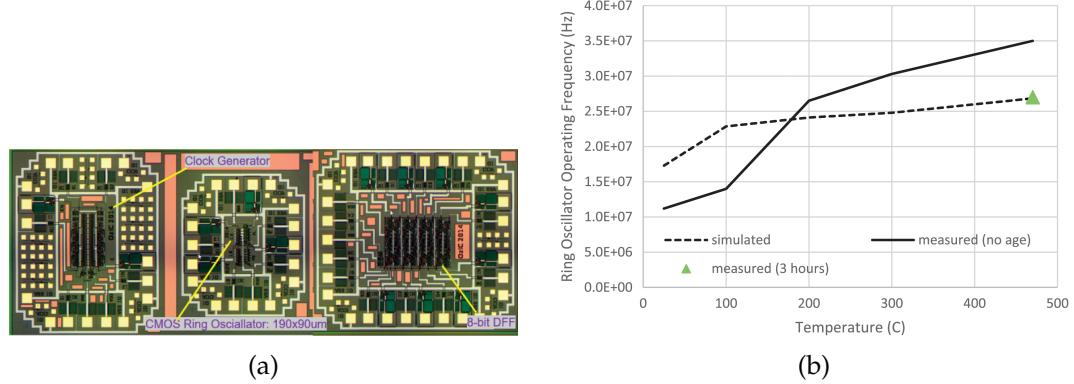

| 2.8 | (a) Die micrographs of CMOS clock generator, CMOS and NMOS ring oscillators, and D-type flip-flop and (b) Operation of ring oscillator using simulation models from room temperature to 470 °C [6]. . . . .                                                                                                                                                   | 21 |

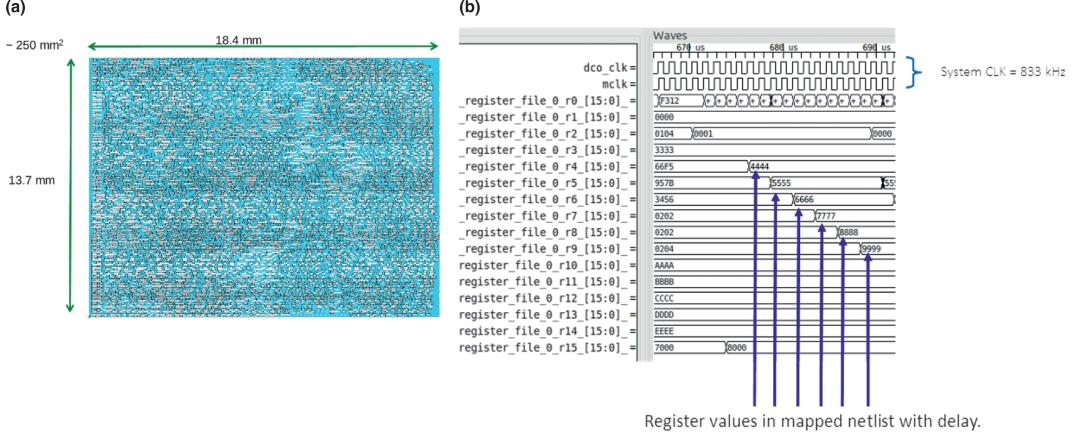

| 2.9 | (a) Layout of SiC-CMOS microcontroller core implemented with placed and routed SiC-CMOS digital standard cells and (b) digital simulation (ADD operation) using 470°C extracted timing models [6]. . . . .                                                                                                                                                    | 22 |

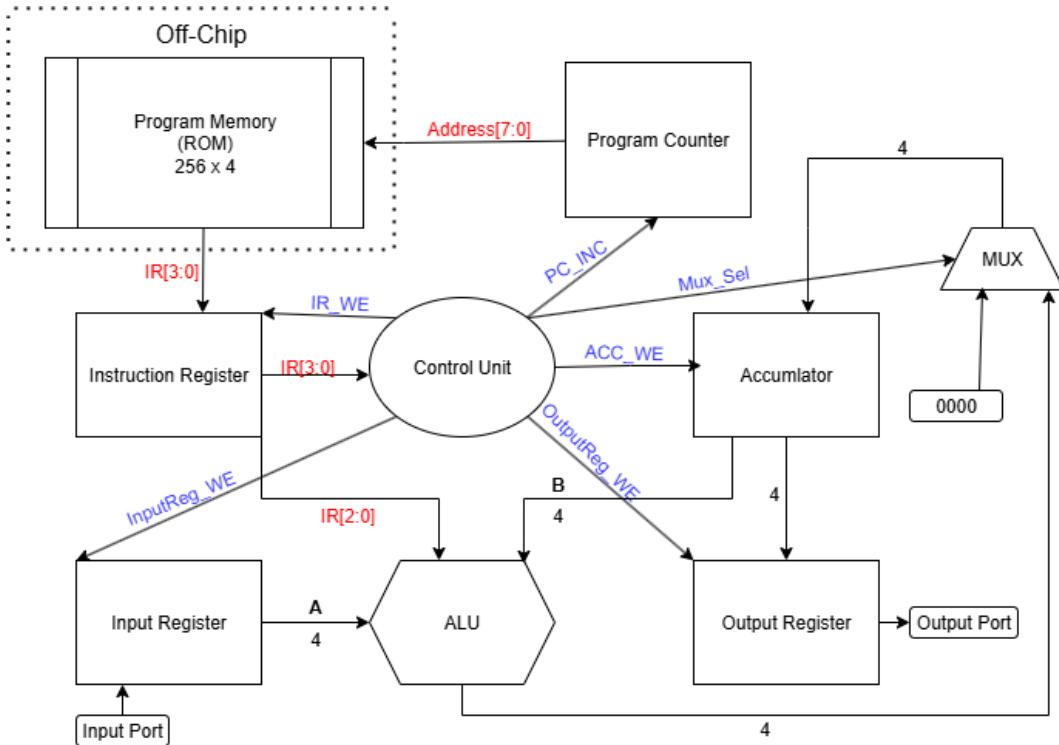

| 3.1 | Processor architecture block diagram . . . . .                                                                                                                                                                                                                                                                                                                | 26 |

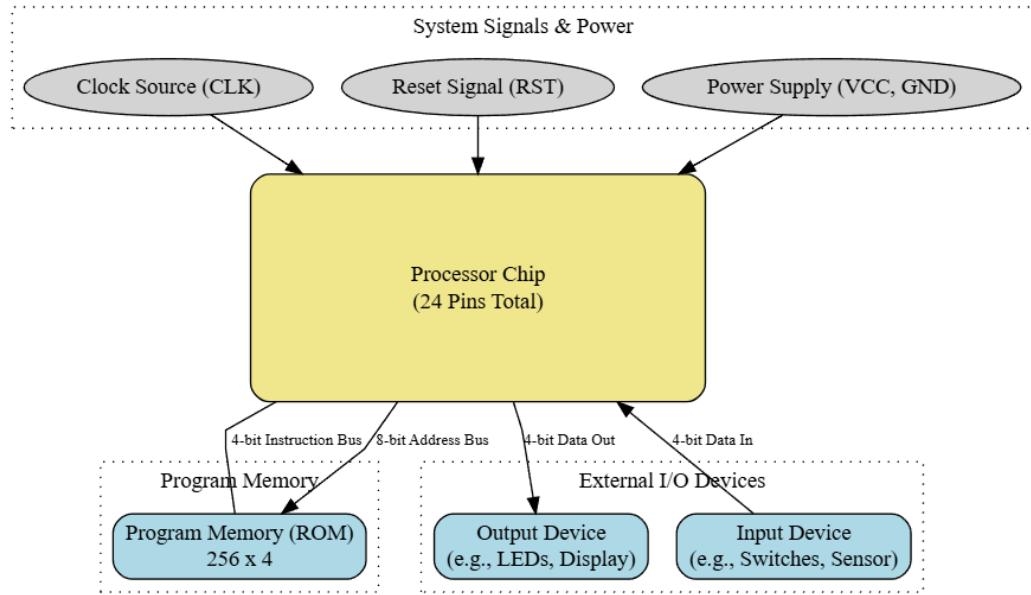

| 3.2 | Input and Output Ports of Processor . . . . .                                                                                                                                                                                                                                                                                                                 | 27 |

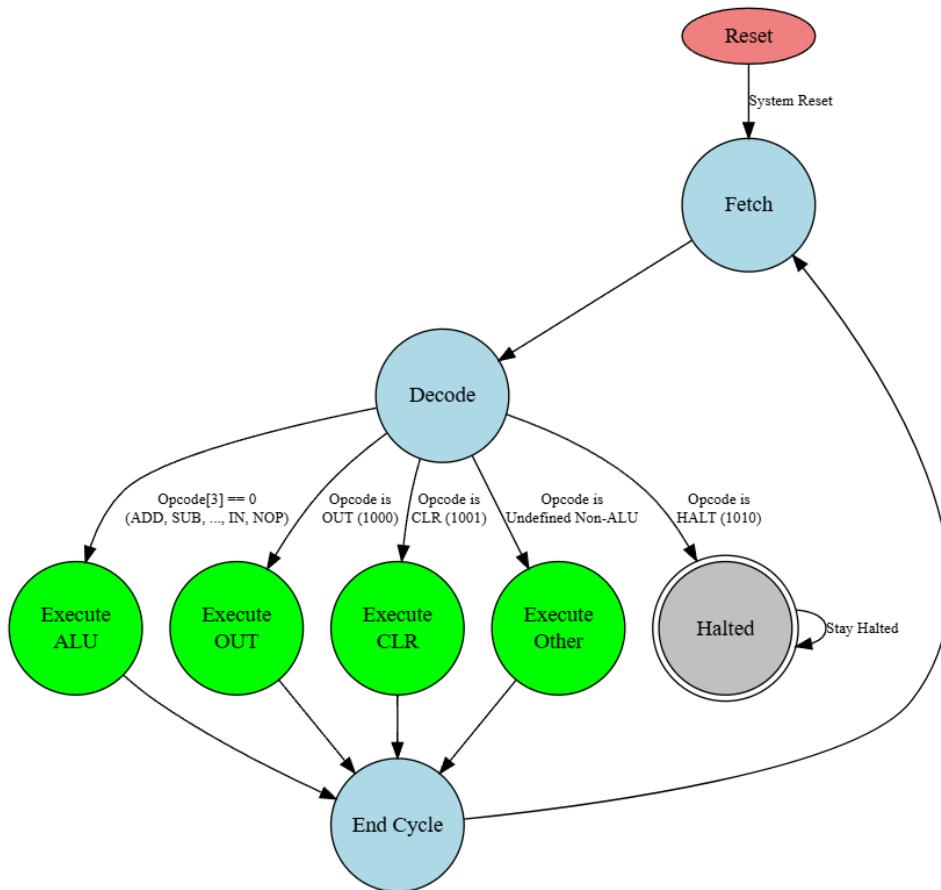

| 3.3 | Finite state machine of Control unit . . . . .                                                                                                                                                                                                                                                                                                                | 28 |

---

LIST OF FIGURES

|      |                                                                                                                                                                                                                                                                                |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

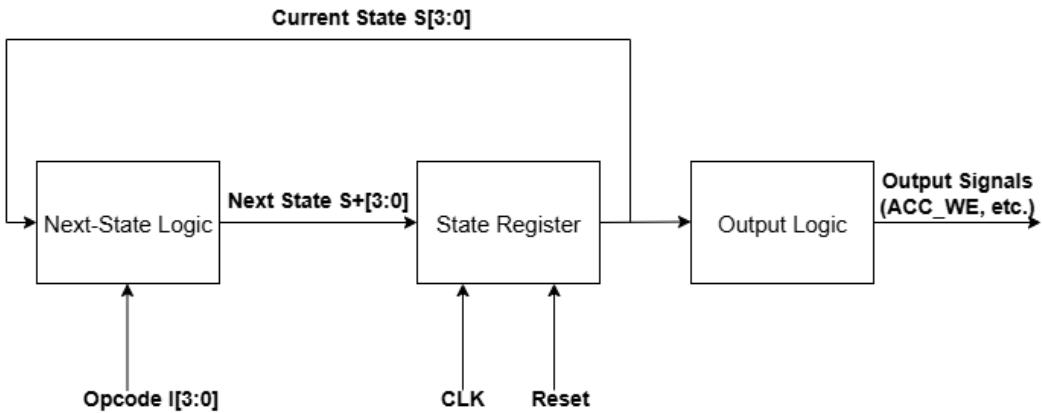

| 4.1  | Control Unit Block Diagram . . . . .                                                                                                                                                                                                                                           | 34 |

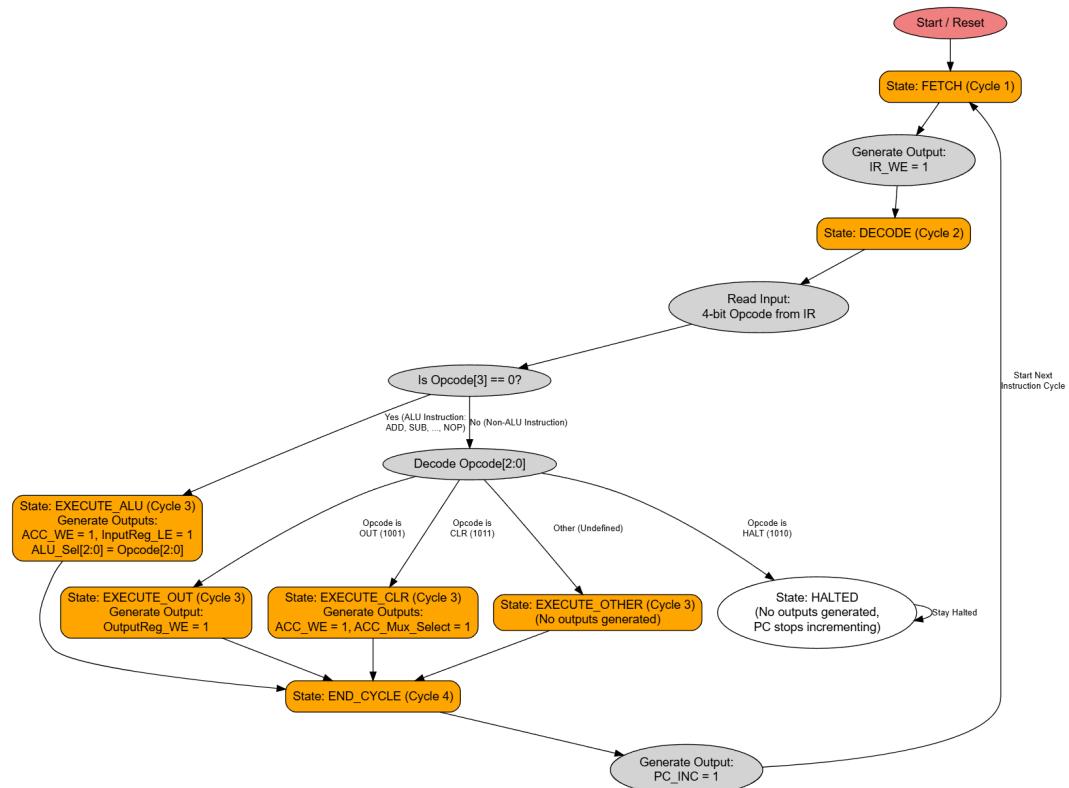

| 4.2  | FSM Flowchart with Control Signals and States . . . . .                                                                                                                                                                                                                        | 35 |

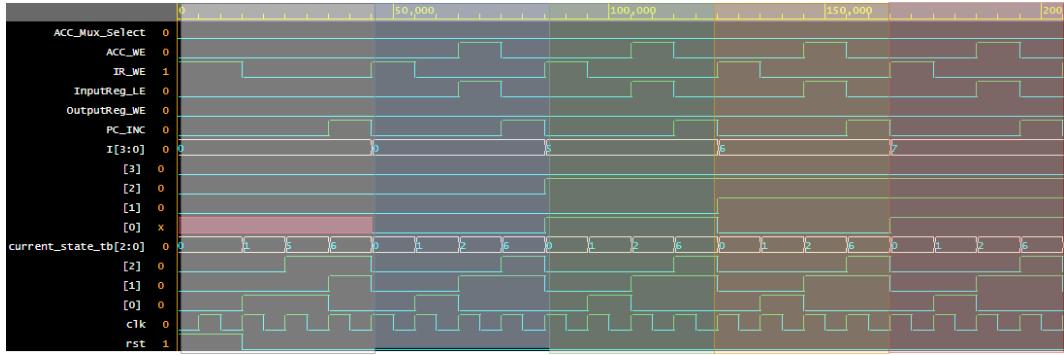

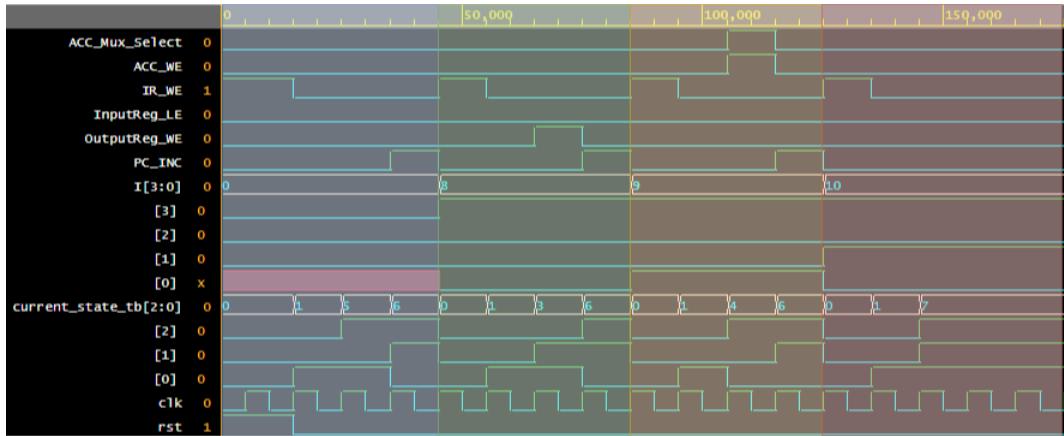

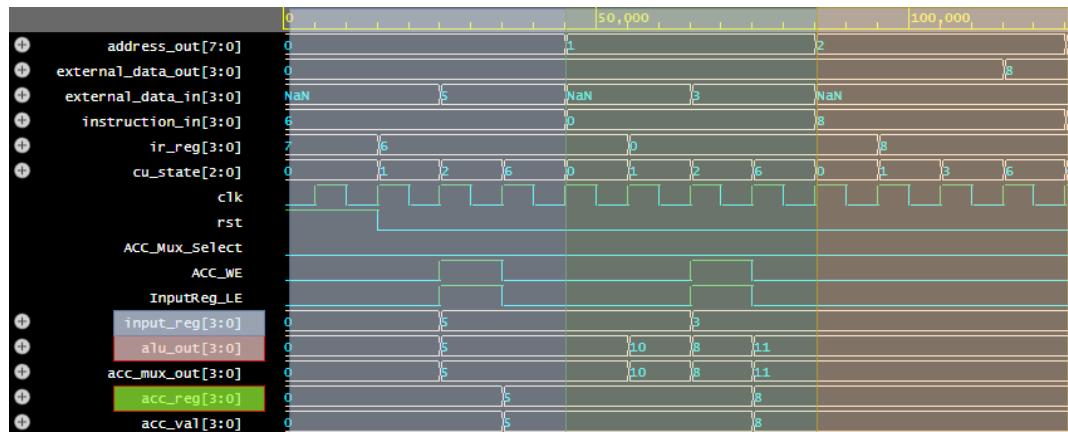

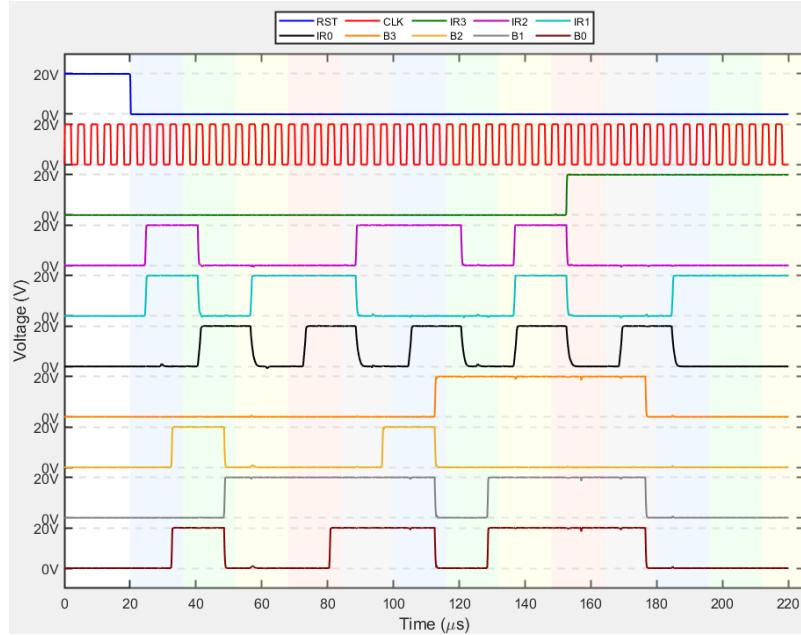

| 4.3  | Behavioral Simulation Waveform of ALU Execution. Color-coded intervals represent the execution periods of each instruction. . . . .                                                                                                                                            | 36 |

| 4.4  | Behavioral Simulation Waveform of Non-ALU Execution. Color-coded intervals represent the execution periods of each instruction. . . . .                                                                                                                                        | 36 |

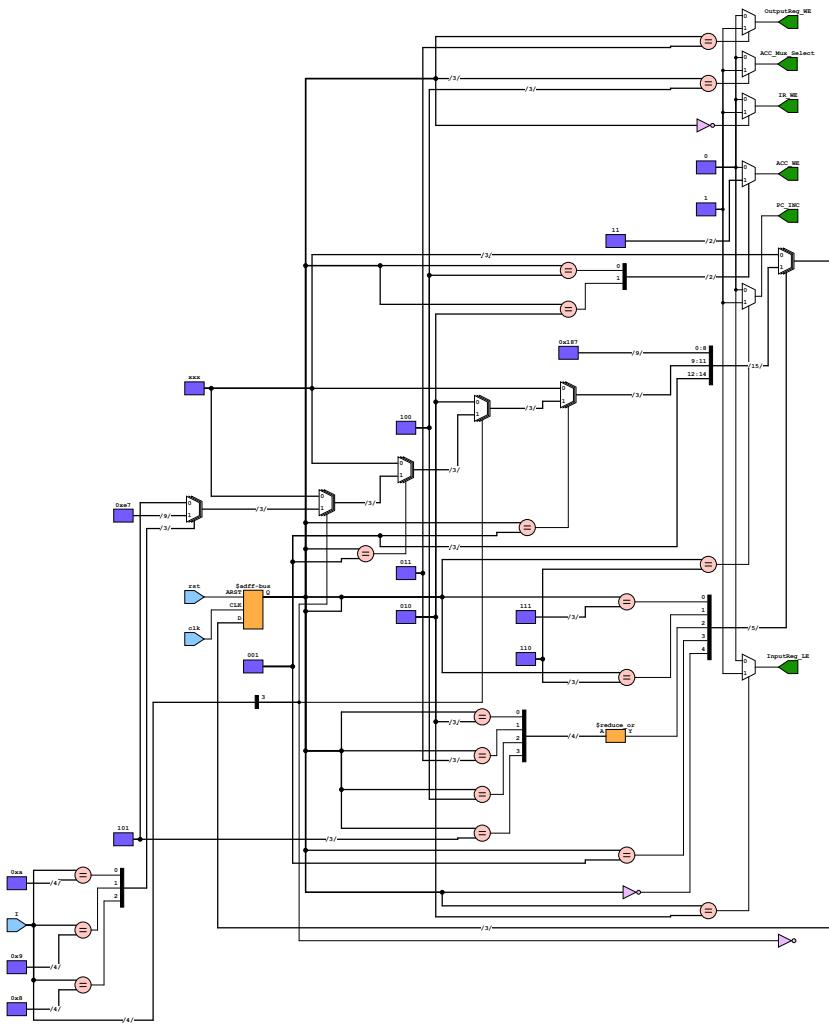

| 4.5  | Schematic of the Control Unit (Behavioral-level design). . . . .                                                                                                                                                                                                               | 37 |

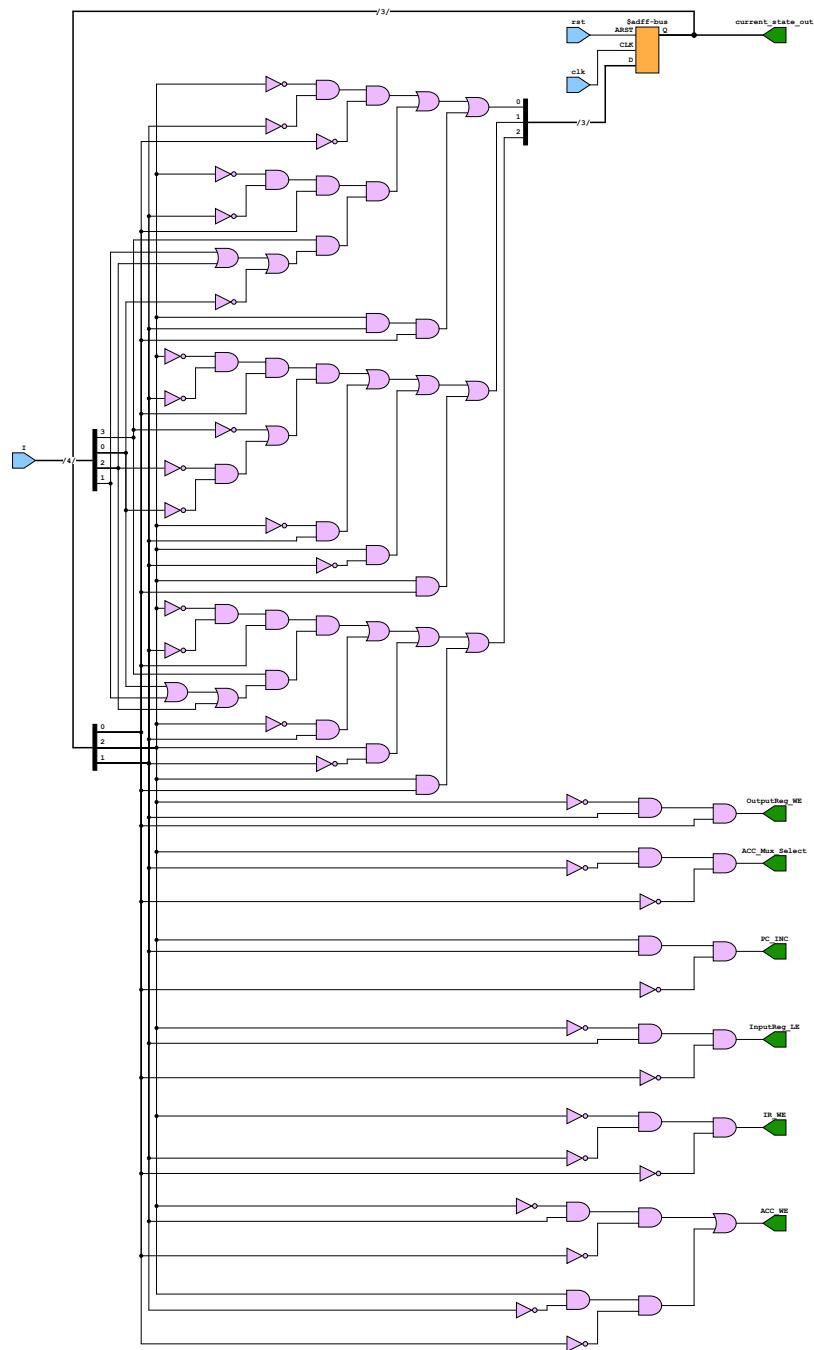

| 4.6  | Schematic of the Control Unit (Structural-level design). . . . .                                                                                                                                                                                                               | 39 |

| 4.7  | Behavioral simulation showing the one-cycle delay between ALU output and accumulator update caused by the edge-triggered input register. Different color-coded regions represent the execution intervals of each instruction. Signals in the key path are also marked. . . . . | 41 |

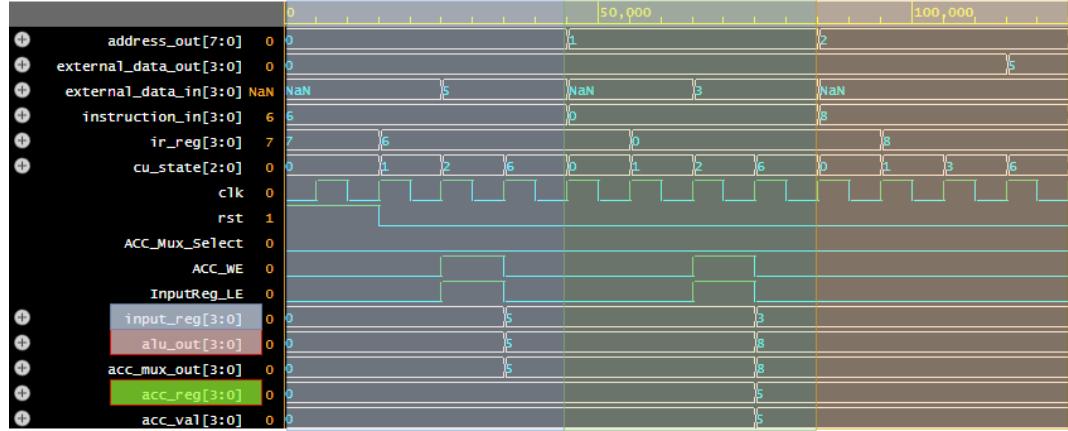

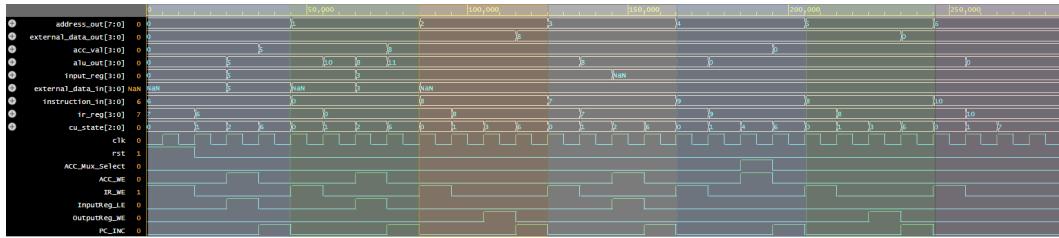

| 4.8  | Behavioral simulation result of the processor after input latch modification, showing correct four-cycle instruction execution. Different color-coded regions represent the execution intervals of each instruction. Signals in the key path are also marked. . . . .          | 41 |

| 4.9  | Behavioral Simulation Waveform of Processor. Different color-coded regions represent the execution intervals of each instruction. . . . .                                                                                                                                      | 42 |

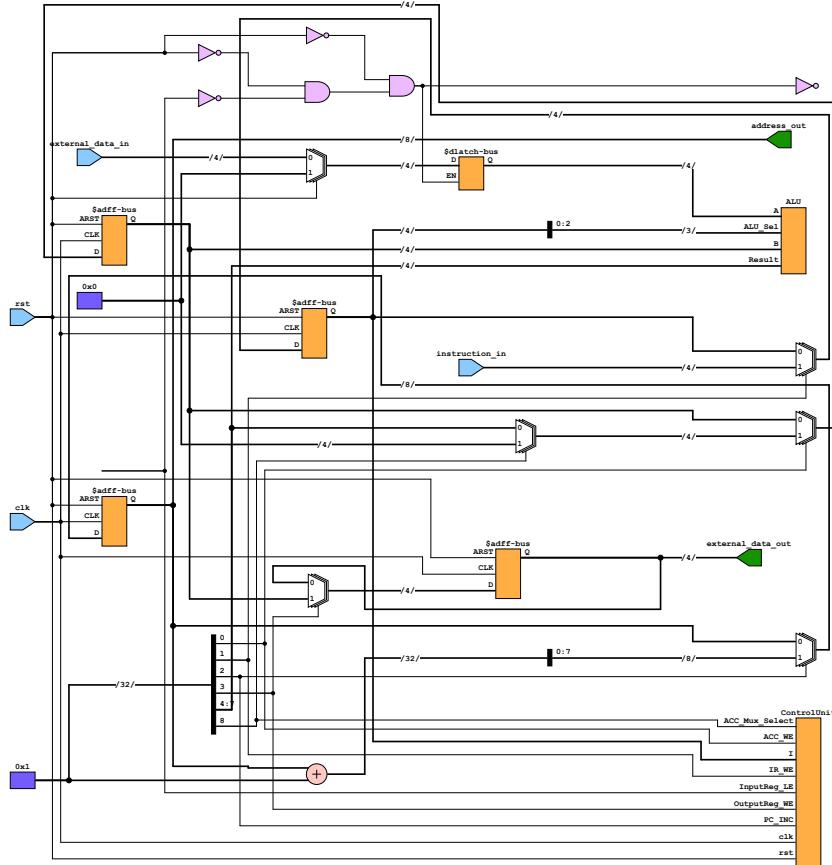

| 4.10 | TOP-level schematic of 4-bit RISC Processor synthesized by Yosys. . . . .                                                                                                                                                                                                      | 43 |

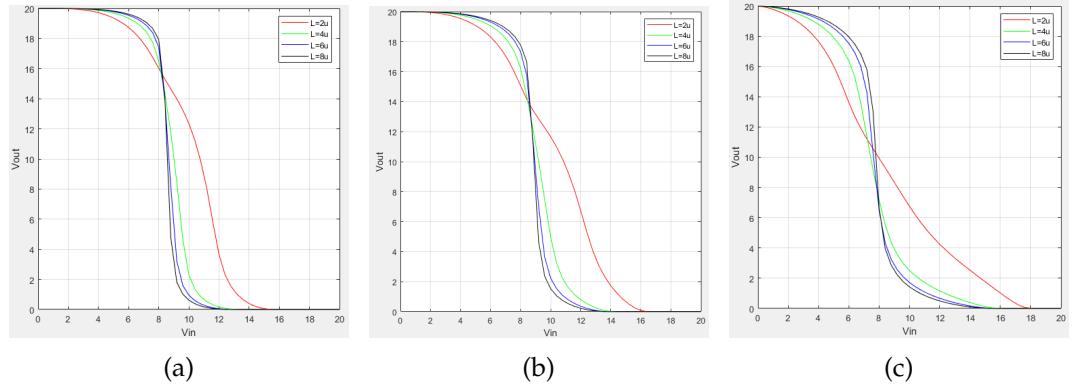

| 5.1  | DC transfer characteristics of inverters with different channel lengths ( $L = 2, 4, 6, 8 \mu\text{m}$ ) under 20 V supply: (a) 27 °C, (b) 200 °C, and (c) 500 °C. . . . .                                                                                                     | 47 |

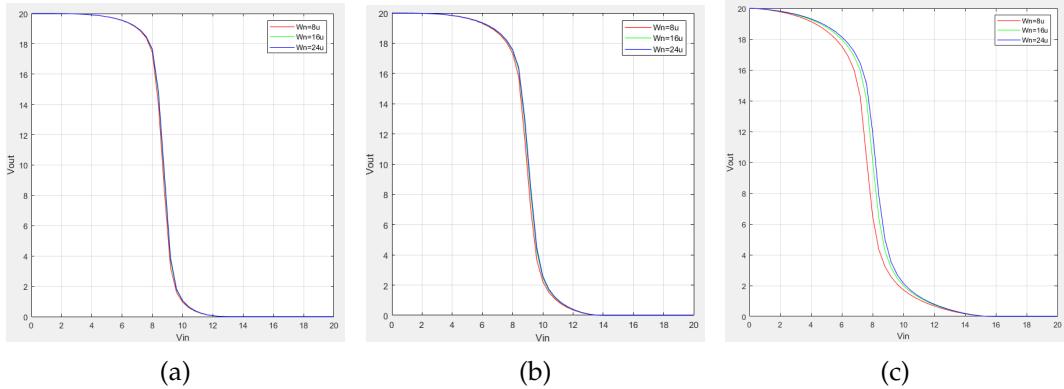

| 5.2  | DC transfer characteristics of inverters with different NMOS width ( $W_n = 8, 16, 24 \mu\text{m}$ ) under 20 V supply: (a) 27 °C, (b) 200 °C, and (c) 500 °C. . . . .                                                                                                         | 48 |

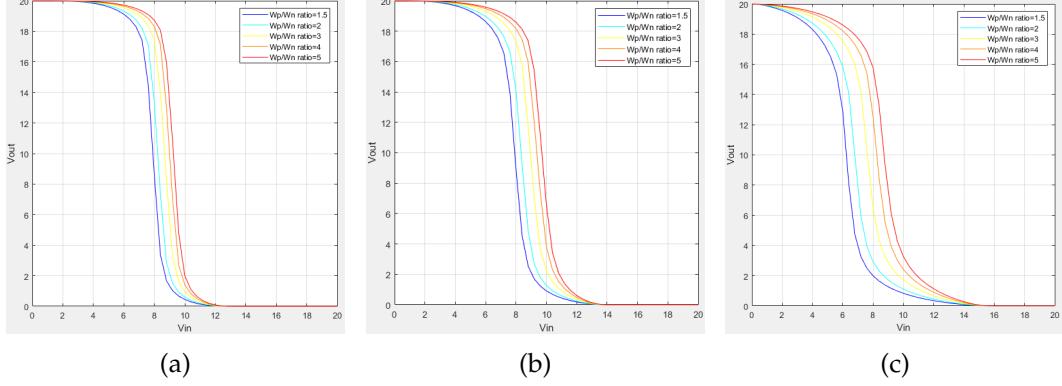

| 5.3  | DC transfer characteristics of inverters with different $W_p/W_n$ ratio (8, 16, 24 $\mu\text{m}$ ) under 20 V supply: (a) 27 °C, (b) 200 °C, and (c) 500 °C. . . . .                                                                                                           | 50 |

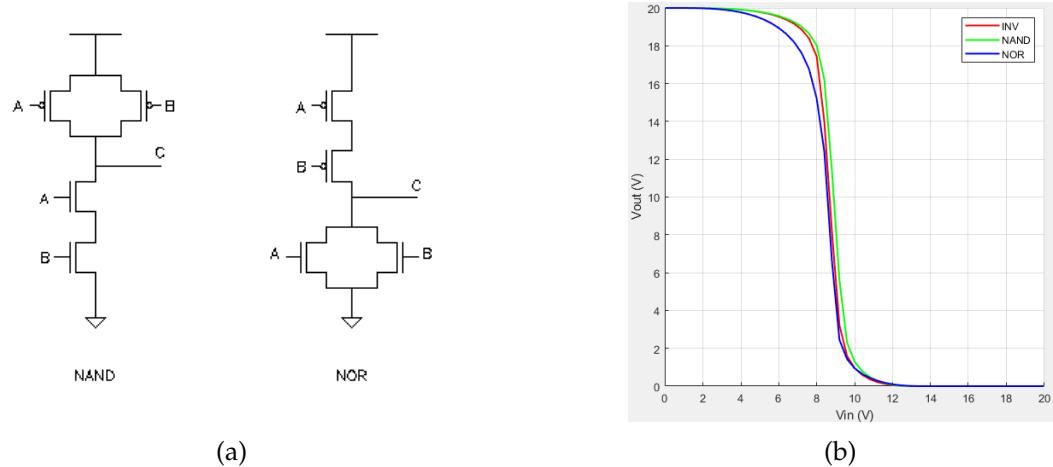

| 5.4  | (a) Standard logic gate implementation of NAND and NOR [9] (b) DC transfer characteristics of the 2-input NAND and NOR gates at room temperature (27 °C), overlaid with the baseline inverter. . . . .                                                                         | 51 |

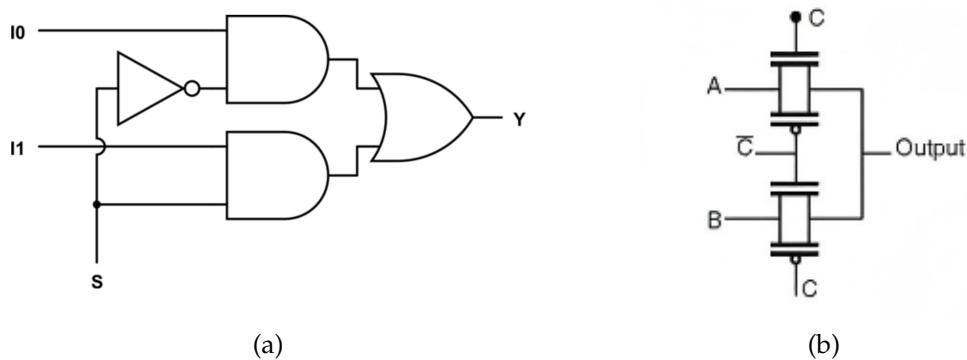

| 5.5  | Comparison of (a) standard logic gate implementation of a 2-to-1 MUX versus [27] (b) transmission gate implementation of a 2-to-1 MUX [2]. . . . .                                                                                                                             | 52 |

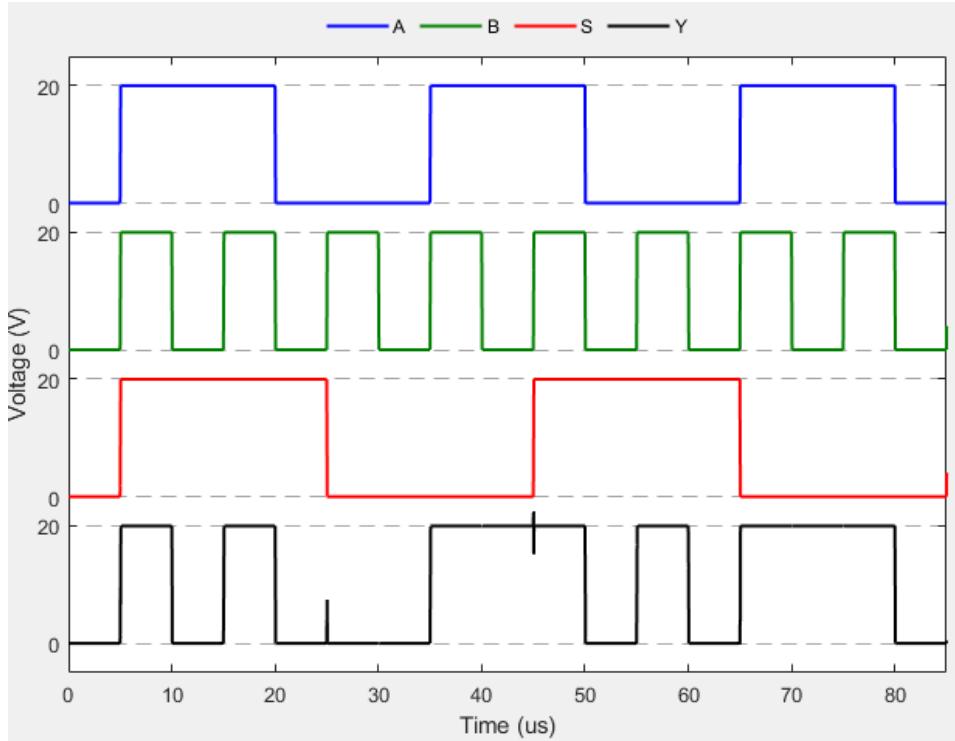

| 5.6  | Transient simulation of the transmission gate MUX at 500 °C. The output (Y) switches between inputs A and B based on the select signal (S). . . . .                                                                                                                            | 53 |

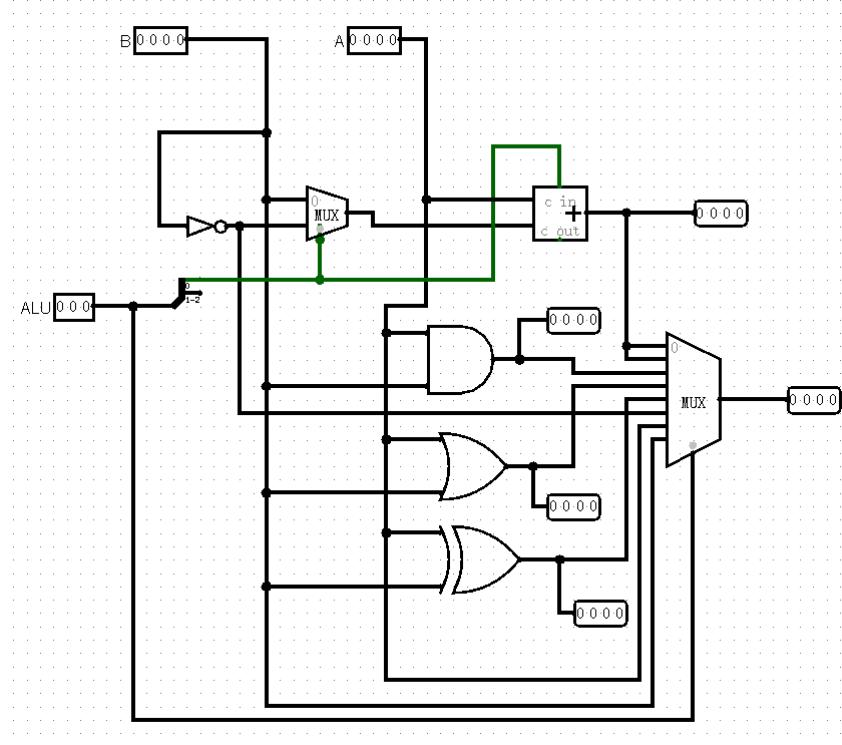

| 5.7  | Circuit schematic of a 4-bit ALU. . . . .                                                                                                                                                                                                                                      | 54 |

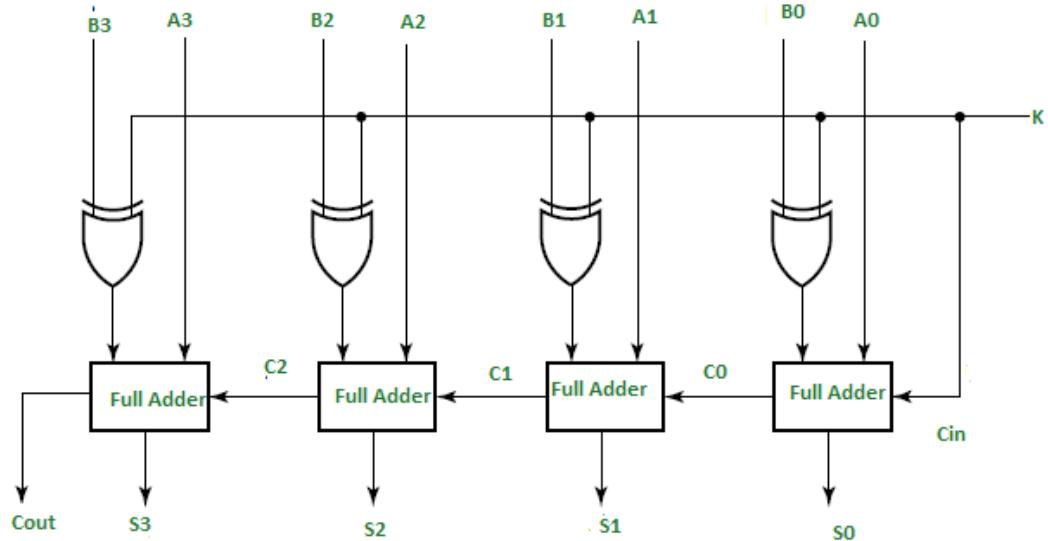

| 5.8  | Structure of the 4-bit binary adder-subtractor. The control signal K corresponds to the ALU_Sel[0] bit from the instruction opcode [18]. . . . .                                                                                                                               | 55 |

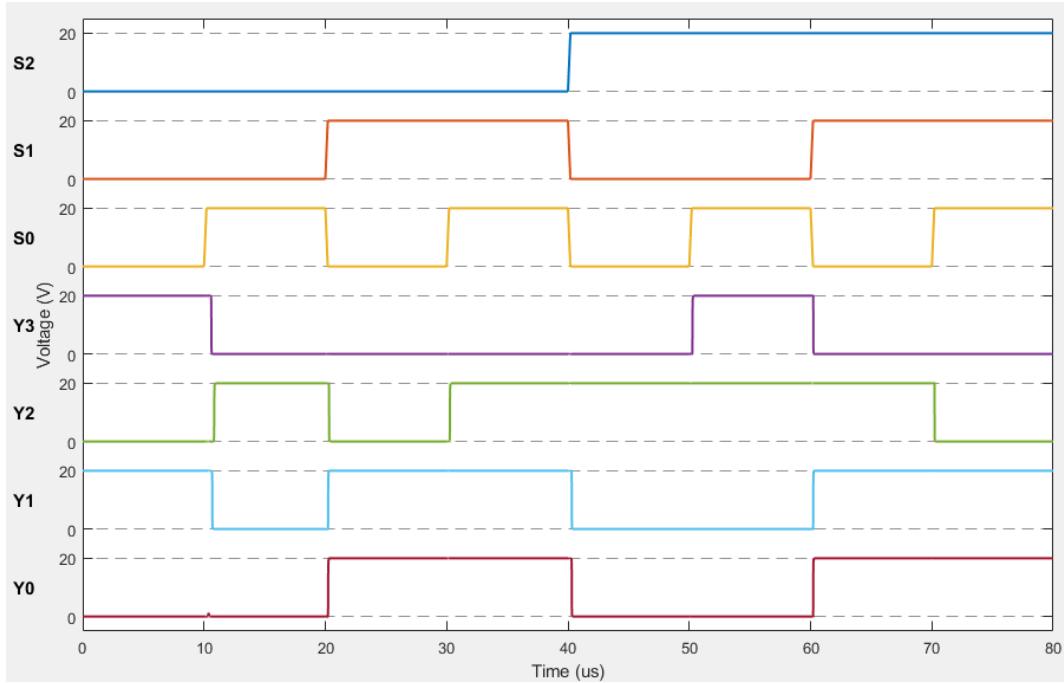

| 5.9  | Transient simulation waveform of the 4-bit ALU at 500 °C. The resulting output (Y3-Y0) corresponds to the theoretical values listed in Table 5.1. . . . .                                                                                                                      | 56 |

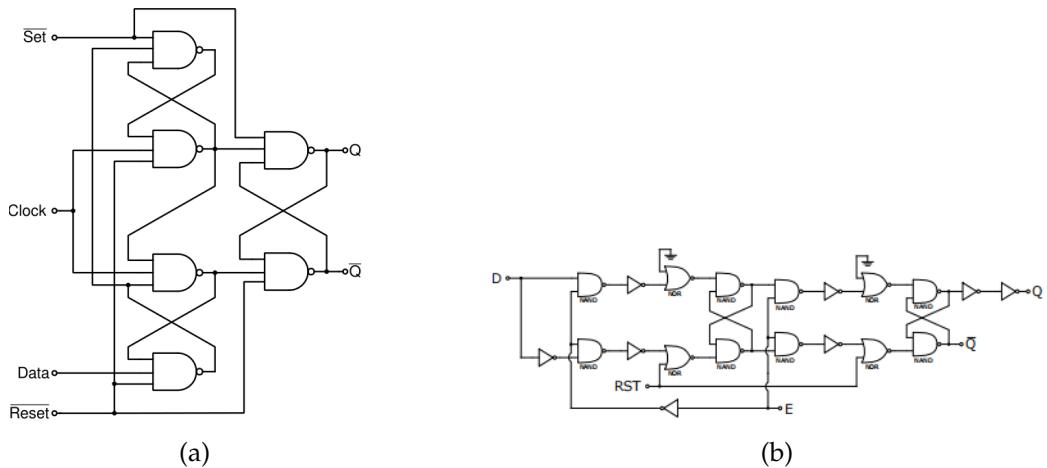

| 5.10 | Comparison of (a) Edge triggered D flip flop structure used in this work (34 transistors) [25] and (b) D flip flop structure from prior work by Romijn et al (66 transistors) [21]. . . . .                                                                                    | 57 |

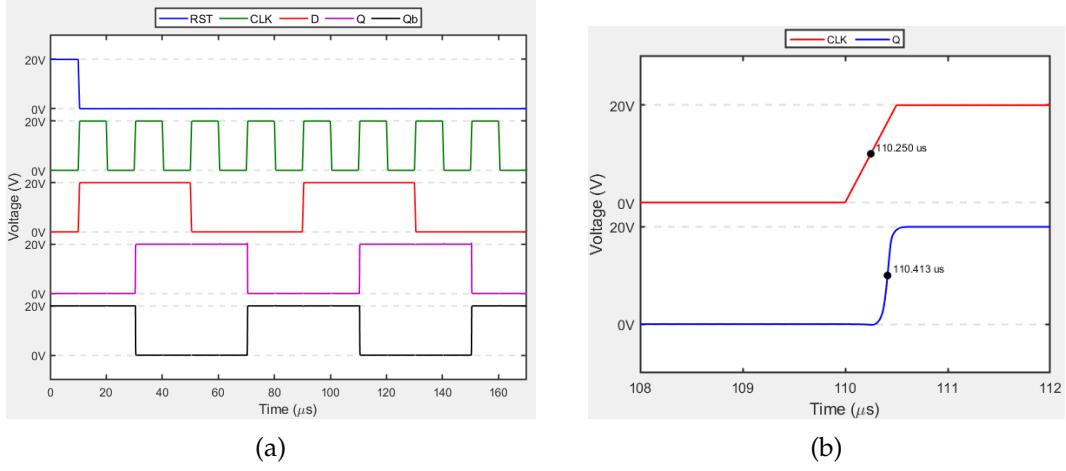

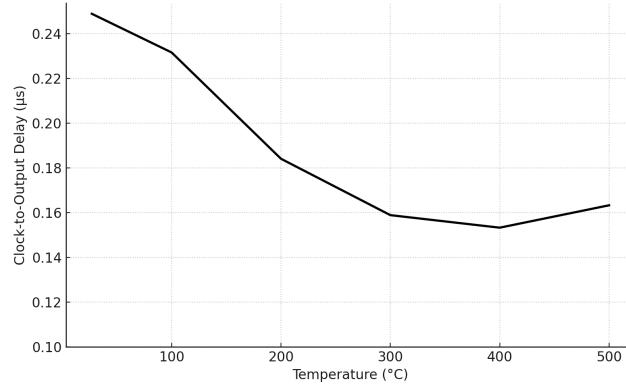

|                                                                                                                                                                                                                                                                                                                                                                                     |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.11 (a) Transient simulation of the adopted DFF at 500 °C and (b) measurement of DFF clock-to-output delay ( $T_{CQ}$ ). . . . .                                                                                                                                                                                                                                                   | 58 |

| 5.12 Simulated DFF $T_{CQ}$ with temperature. . . . .                                                                                                                                                                                                                                                                                                                               | 58 |

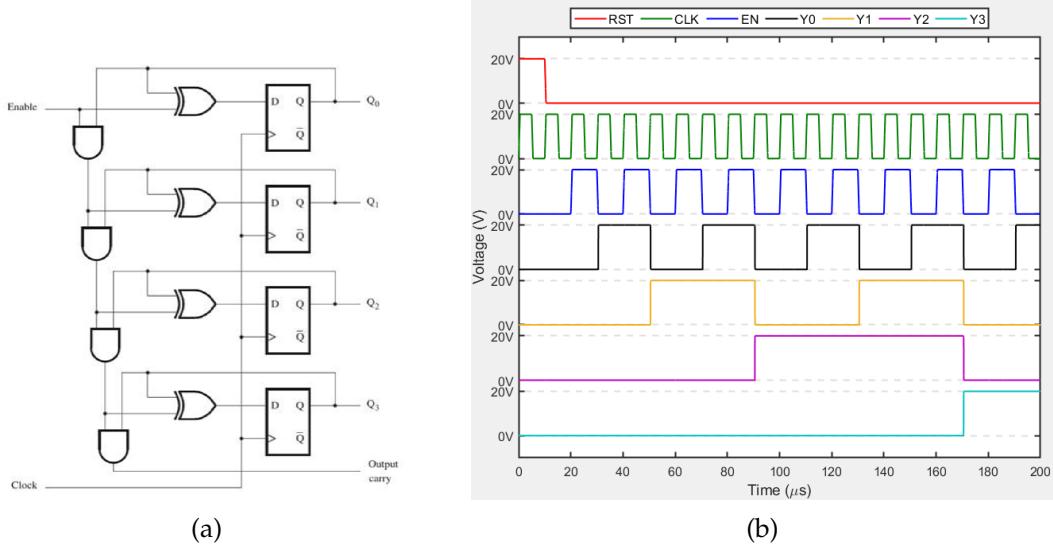

| 5.13 (a) 4-bit synchronous counter schematic [24] and (b) transient simulation of the program counter at 500 °C. . . . .                                                                                                                                                                                                                                                            | 60 |

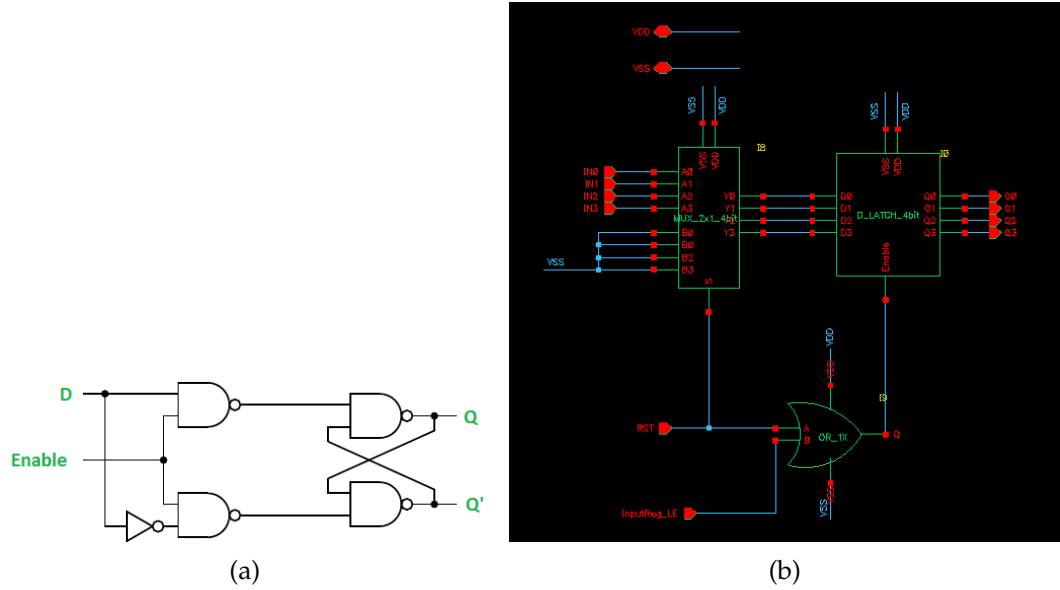

| 5.14 (a) Basic D latch structure used for the input module and (b) 4-bit input latch implementation. . . . .                                                                                                                                                                                                                                                                        | 61 |

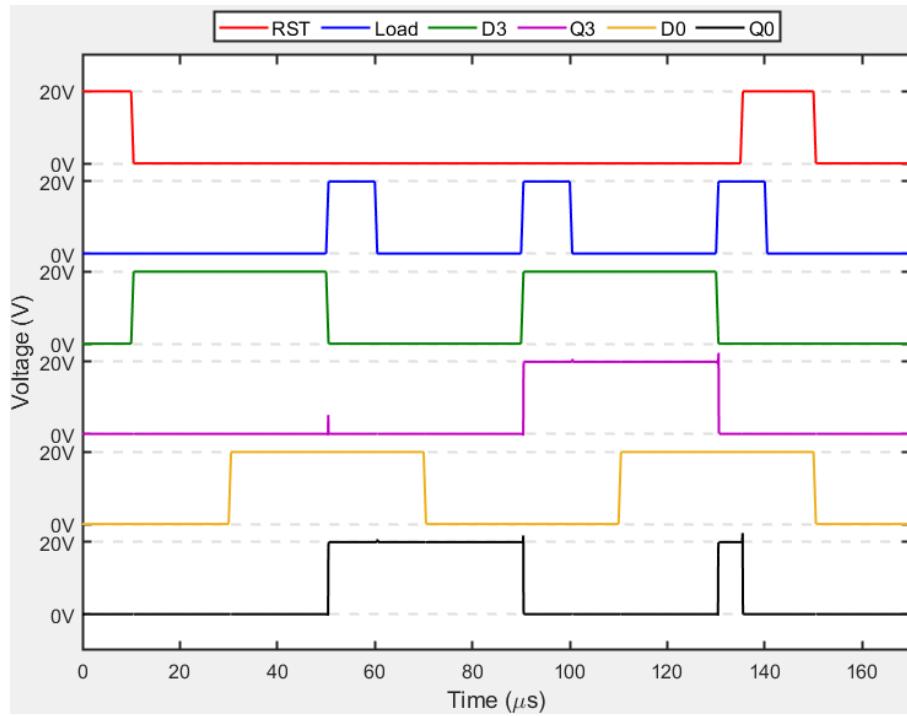

| 5.15 Transient simulation of the input latch at 500 °C showing sampling, holding, and reset operations. . . . .                                                                                                                                                                                                                                                                     | 61 |

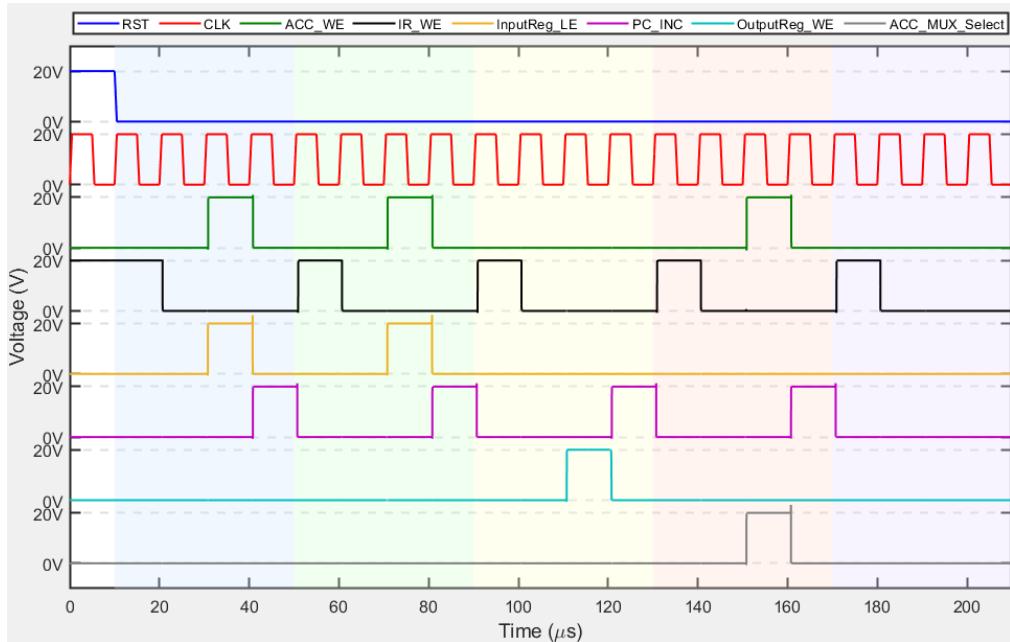

| 5.16 Transient simulation of the control unit at 500 °C showing the five-instruction sequence ( $IN$ , $NOP$ , $OUT$ , $CLR$ , $HALT$ ). Color-coded intervals represent the execution periods of each instruction. . . . .                                                                                                                                                         | 62 |

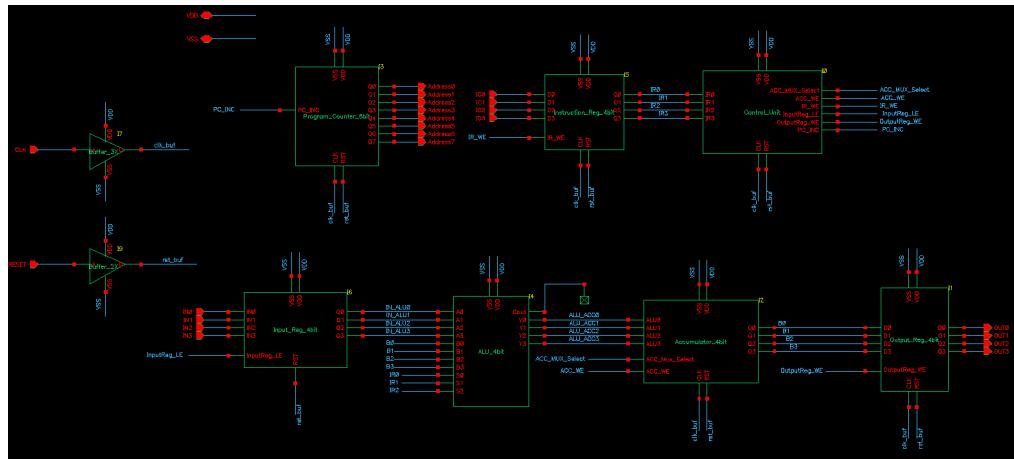

| 5.17 Top-level schematic of the 4-bit SiC processor in Virtuoso. . . . .                                                                                                                                                                                                                                                                                                            | 63 |

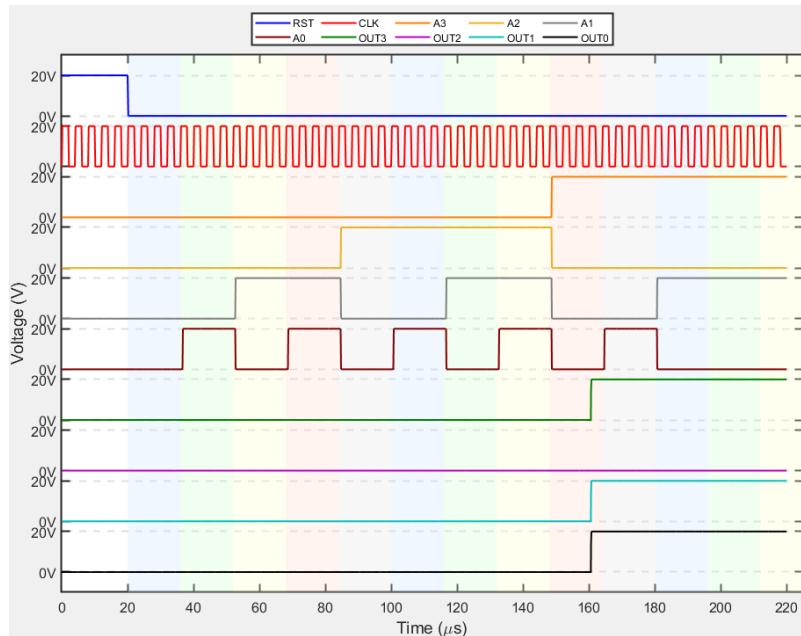

| 5.18 Top-level transient simulation of the instruction register (IR3–IR0) and accumulator (B3–B0) at 500 °C. Different color-coded regions represent the execution intervals of each instruction. The simulated sequence matches the expected functional behavior listed in Table 5.2. . . . .                                                                                      | 65 |

| 5.19 Top-level transient simulation of the output register and external ROM addressing (A3–A0) during the same instruction sequence at 500 °C. . . . .                                                                                                                                                                                                                              | 65 |

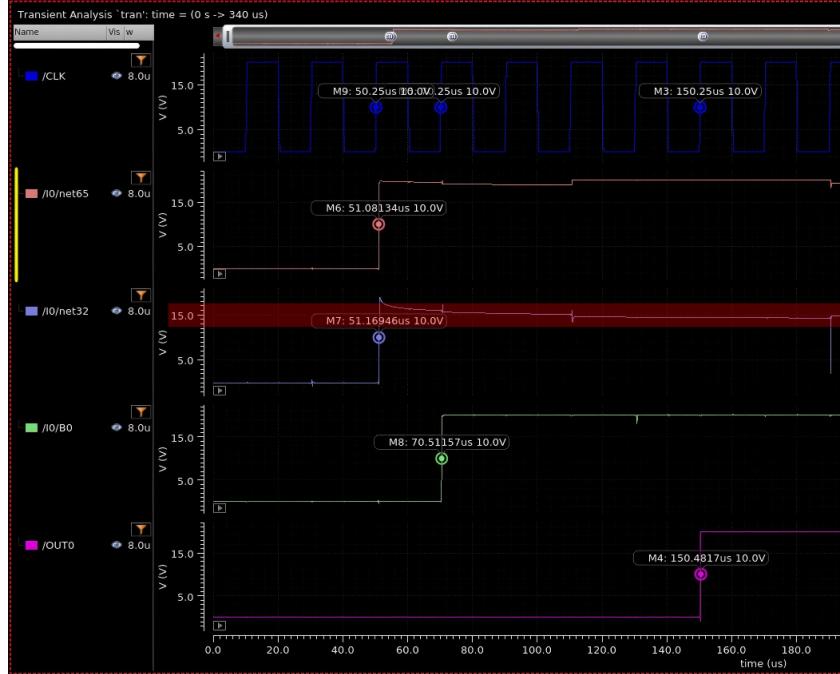

| 5.20 Simulated waveform showing voltage degradation at the accumulator input before MUX replacement. The accumulator input signal (net32, highlighted red) is clamped at approximately 15 V for logic high due to incorrect TG-MUX biasing. . . . .                                                                                                                                 | 67 |

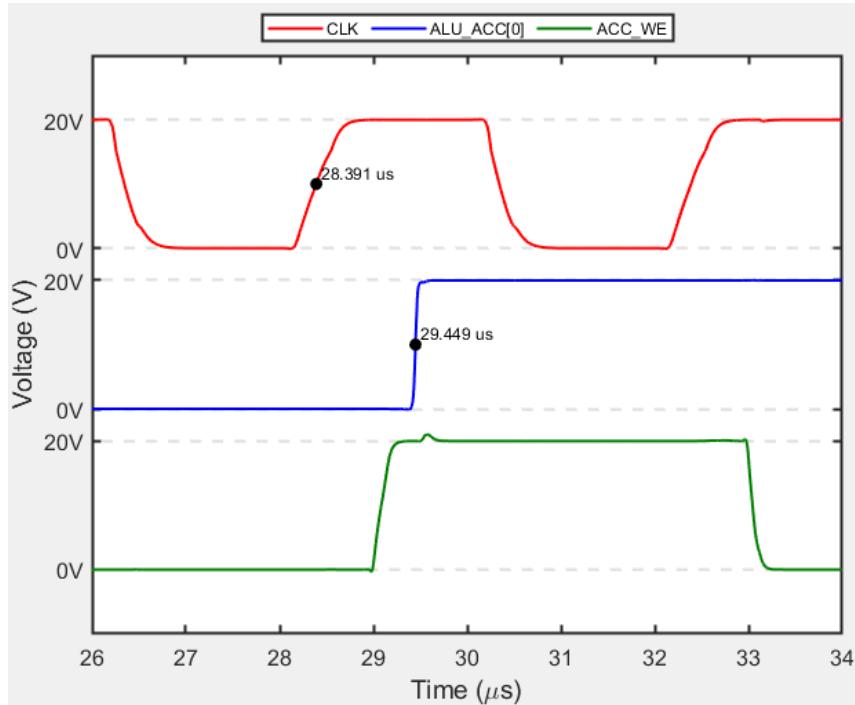

| 5.21 Simulated waveform after replacing the TG-MUX with a CMOS logic MUX. The accumulator input signal (ALU_ACC0, highlighted red) now exhibits a full 0–20 V voltage swing. . . . .                                                                                                                                                                                                | 67 |

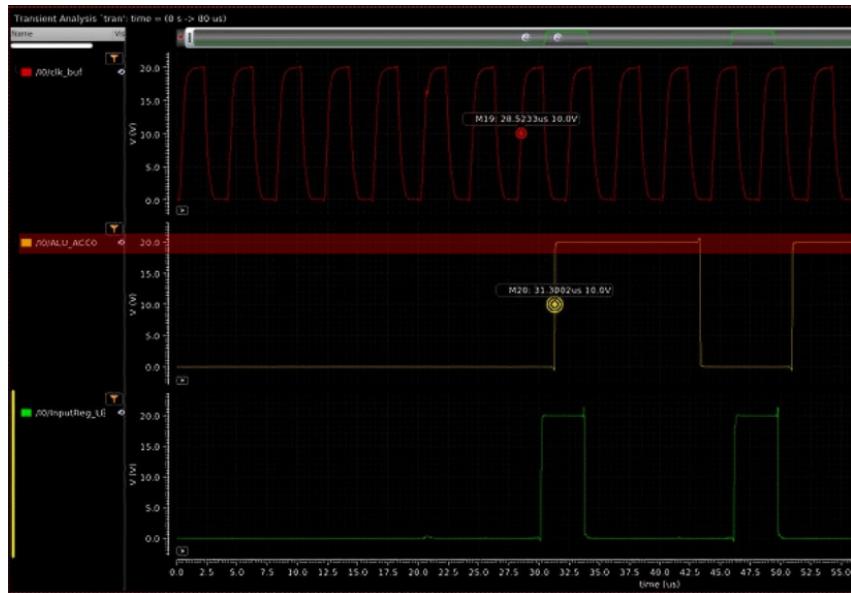

| 5.22 Transient simulation of the arithmetic logic execution path delay at 500°C. . . . .                                                                                                                                                                                                                                                                                            | 68 |

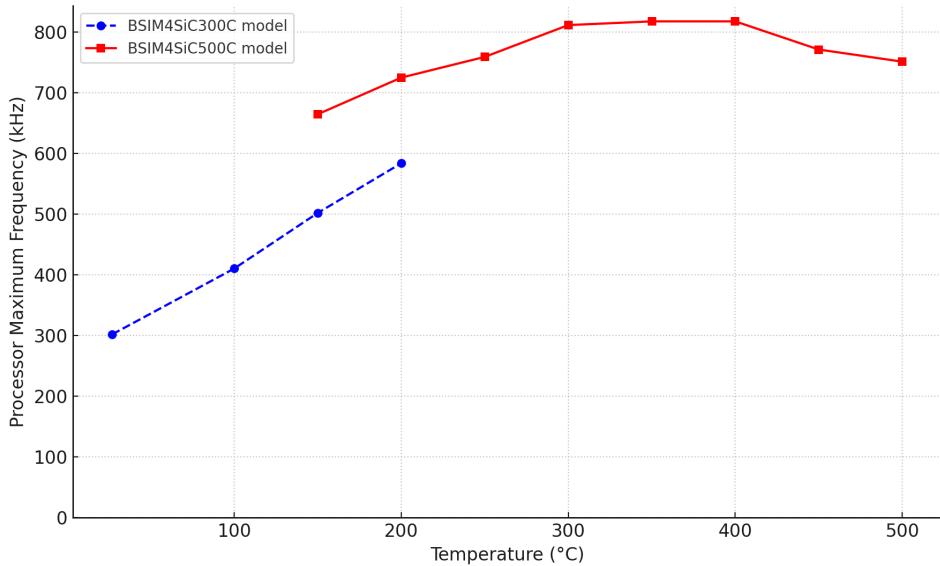

| 5.23 Operation of the RISC processor from the room temperature to 500°C using different models. . . . .                                                                                                                                                                                                                                                                             | 70 |

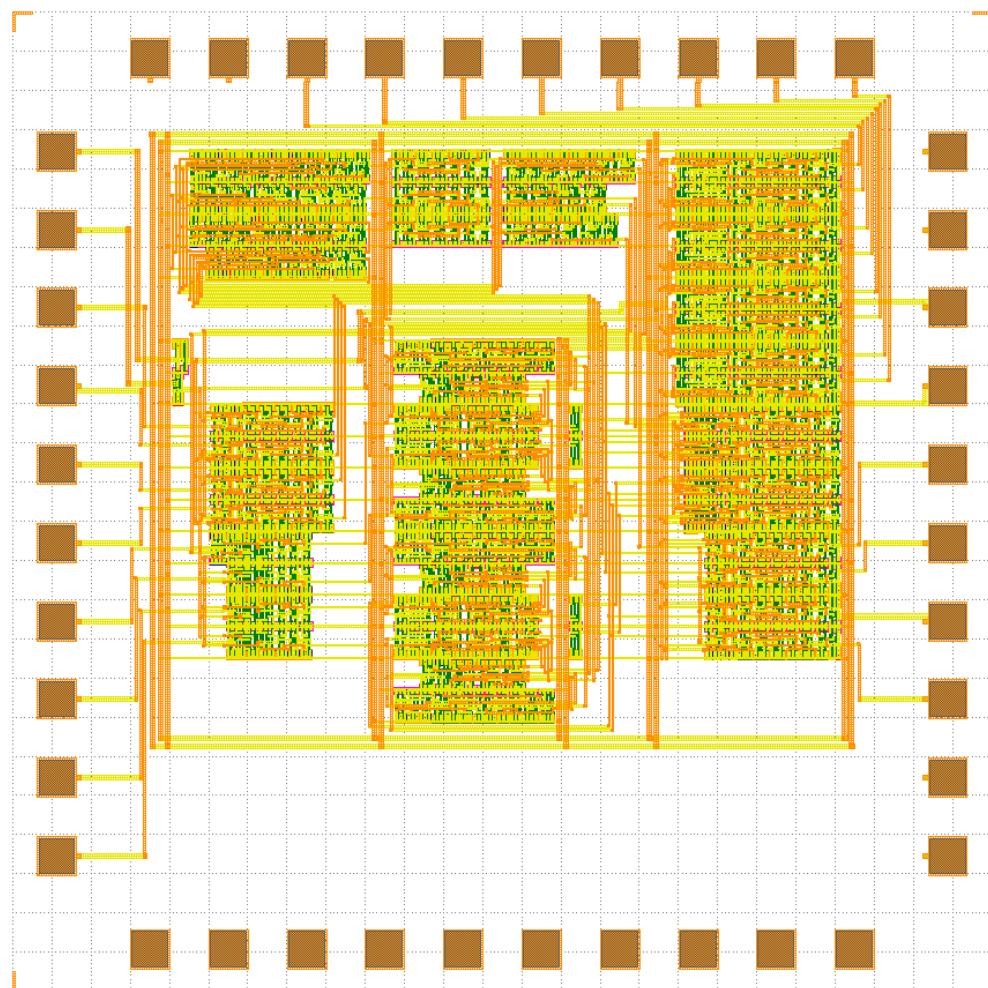

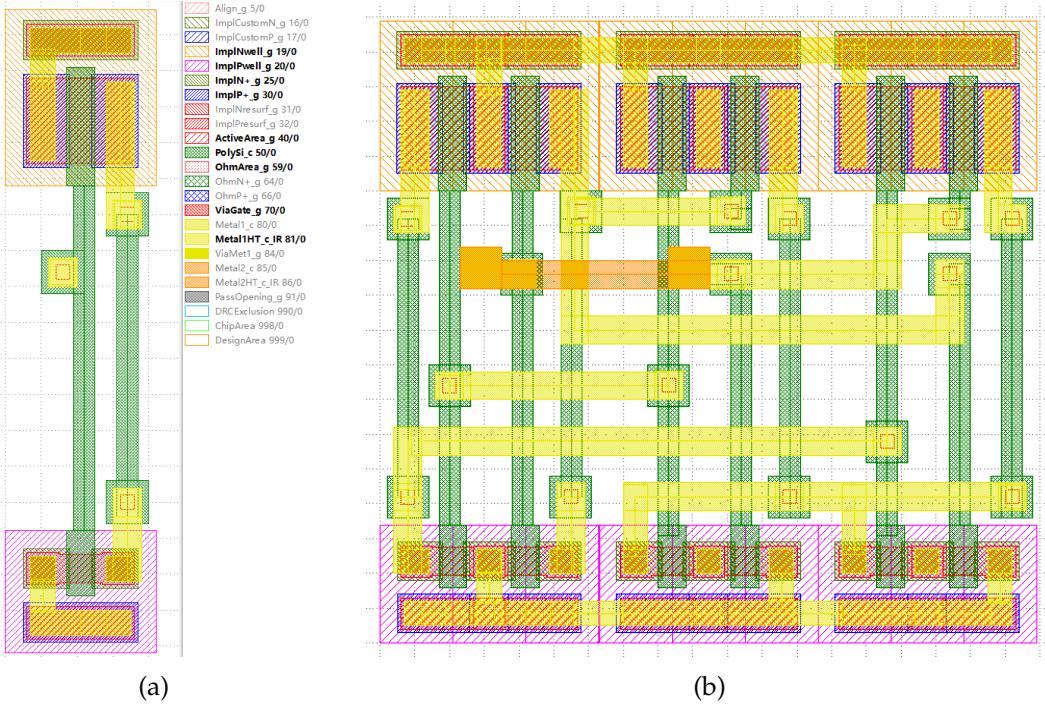

| 6.1 Standard-cell layouts implemented in the IISB 4H-SiC CMOS process: (a) Inverter (INV) standard cell layout showing the 6-track routing channel and layer information; (b) XOR standard cell layout, where Metal 2 is employed to relieve M1 congestion. . . . .                                                                                                                 | 74 |

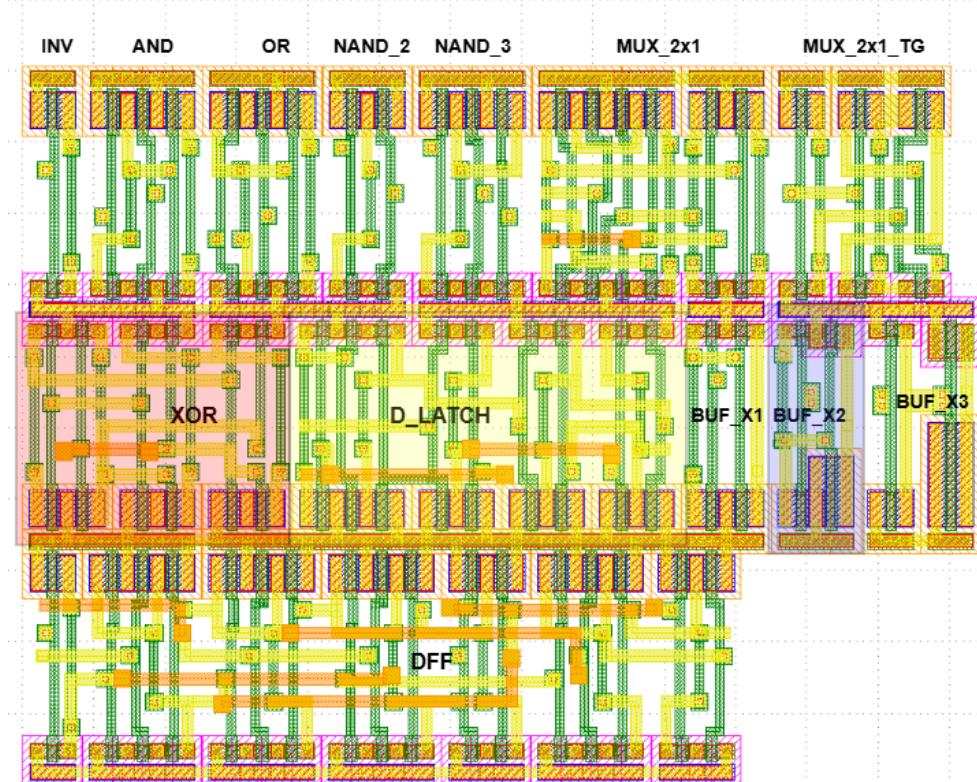

| 6.2 Complete library of digital standard cells implemented in the processor design. All cells have been verified through Layout Versus Schematic (LVS) and Design Rule Check (DRC) checks to ensure inter-cell connectivity consistency and design-rule compliance. (Note: MUX_2x1_TG represents a transmission-gate-based MUX, and BUF_1X denotes a single-stage buffer) . . . . . | 75 |

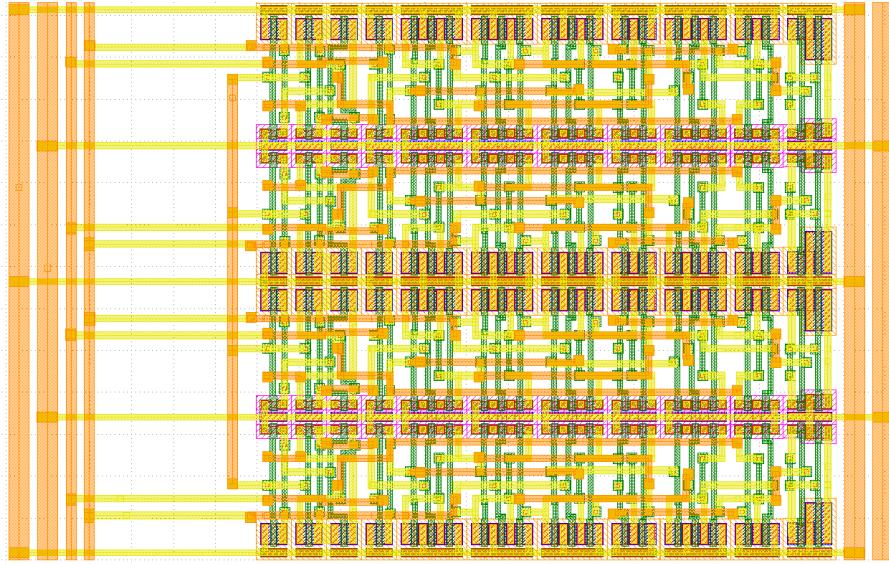

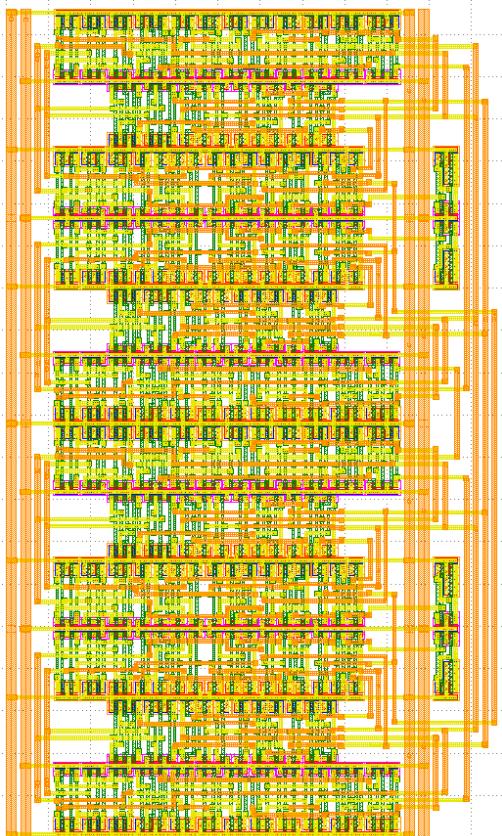

| 6.3 Layout of the 4-bit Output Register module. . . . .                                                                                                                                                                                                                                                                                                                             | 77 |

| 6.4 Layout of the main computational blocks: (a) 4-bit ALU and (b) 8-bit Program Counter (PC). . . . .                                                                                                                                                                                                                                                                              | 78 |

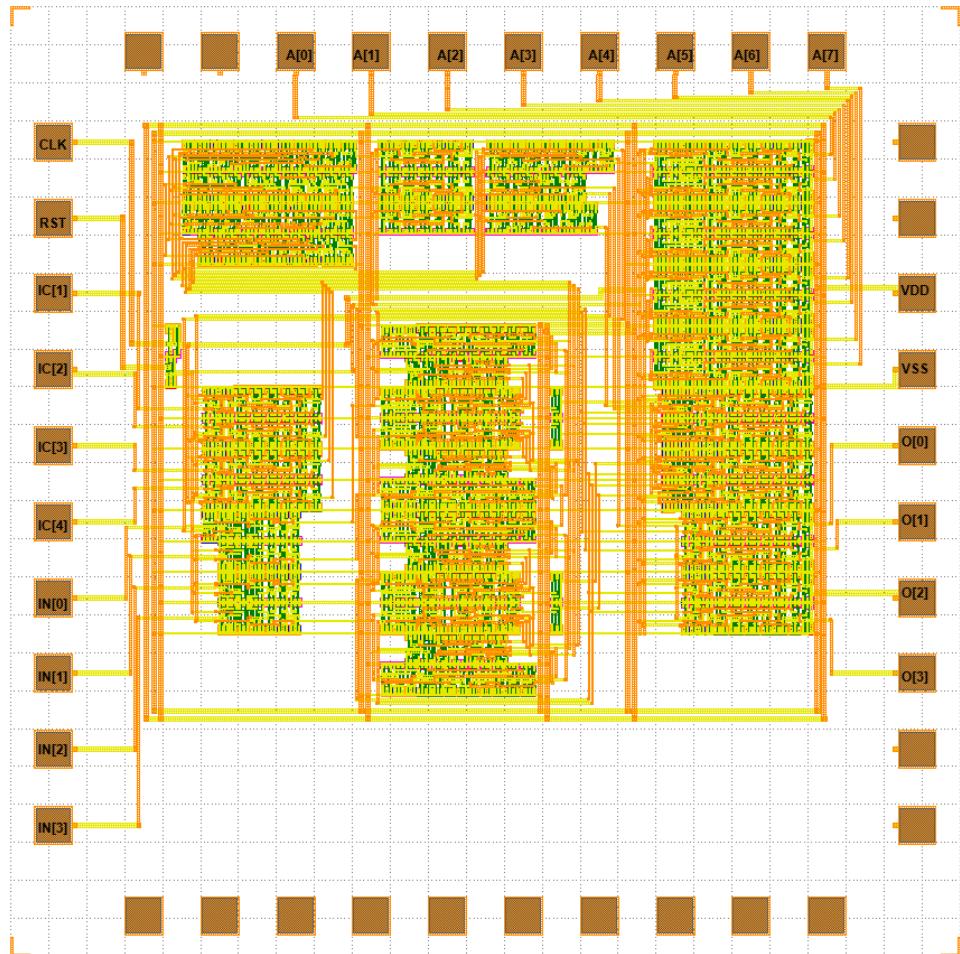

| 6.5 Layout of the Control Unit implementing the processor FSM. . . . .                                                                                                                                                                                                                                                                                                              | 78 |

## LIST OF FIGURES

# Chapter 1

---

## Introduction

### 1.1 Motivation

Rapid advancements in fields such as aerospace, nuclear energy, and automotive industries demand electronic systems capable of reliable operation under extreme environmental conditions. These conditions include high temperatures, high radiation levels, and severe vibrations. However, conventional silicon-based semiconductor technology faces its physical limits. In terms of breakdown voltage, thermal tolerance, and operating frequency, silicon technology struggles to meet the requirements of these harsh applications.

Among various wide-bandgap (WBG) semiconductors, silicon carbide (SiC) attracts significant attention due to its excellent properties. SiC exhibits outstanding thermal stability, high breakdown voltage, and robustness in harsh environments [30]. Crucially, SiC is also unique among WBGs for having an established complementary transistor (CMOS) platform [30]. These characteristics make it an ideal choice for high-temperature digital logic applications. Compared with traditional silicon, SiC devices can maintain reliable operation at much higher temperatures. This is thanks to their stronger electric field tolerance and significantly reduced leakage current characteristics.

Despite SiC's clear theoretical advantages and some successful demonstrations of SiC-based integrated circuits (ICs), it remains an emerging technology. This is particularly true for digital circuit integration, which is still in a preliminary stage. Although the feasibility of SiC CMOS technology has been proven, aspects like device performance, process maturity, and the associated design toolchain lag behind mature silicon technologies. Therefore, validation through a complete chip design, fabrication, and testing process is essential. Such validation is needed to ascertain the true potential and reliability of SiC CMOS technology for realizing complex digital systems, like processors.

Designing and implementing a SiC-based processor serves not only as an effective vehicle for validating the technology but also lays the groundwork for deploying more advanced computation and control systems in extreme environ-

ments. Potential applications include sensor interfaces for deep-space exploration missions, downhole electronics for geothermal exploration, or high-temperature controllers within the powertrain of electric vehicles. This thesis aims to address this challenge by designing a 4-bit RISC processor, thereby providing practical evidence for the feasibility of SiC digital system-level integration.

## 1.2 Research Objective

While SiC CMOS technology offers significant potential for high-temperature digital applications, its current development faces practical challenges. Specific to the Fraunhofer IISB  $2 \mu\text{m}$  4H-SiC CMOS process used in this research, its status as an emerging technology presents notable limitations for digital circuit integration. Firstly, constrained by process capabilities, the technology features a relatively low transistor density, restricting the available logic resources within a limited die area. Secondly, it lacks a mature automated digital design flow and comprehensive Process Design Kit (PDK) support. This means standard automated RTL-to-layout toolchains cannot be directly applied, complicating design complexity and verification. Under these constraints, designing a functional processor to validate the technology's system-level integration capability is inherently challenging.

To address these challenges and verify the potential of SiC CMOS technology in digital systems, this thesis sets out the following specific tasks:

- Explore and define an "ultra-minimalist" processor architecture suitable for the limitations of this SiC process.

- Establish a hybrid design and verification flow combining existing open-source tools with manual circuit-level design.

- Develop and characterize a basic SiC CMOS digital standard cell library, optimizing for high-temperature performance and area efficiency.

- Verify the processor's functional correctness and timing performance across a wide temperature range, from room temperature up to  $500^\circ\text{C}$ , through detailed circuit-level simulations.

- Complete the full-custom physical layout design of the processor with process design rules compliance, adherence to die area constraints, and targeted layout optimization.

Therefore, the overall objective of this study is to design, simulate, and complete the layout implementation of a 4-bit RISC processor based on the Fraunhofer IISB  $2 \mu\text{m}$  4H-SiC CMOS process, verifying its potential for reliable operation at extreme temperatures up to  $500^\circ\text{C}$ . Accomplishing this objective will establish a solid technical foundation for the future development of more complex digital systems based on this SiC process.

### 1.3 Thesis Outline

The thesis comprises seven chapters:

1. Introduction: This chapter states the research motivation, defines the problem, and sets the research objectives.

2. Literature Review: This chapter reviews SiC material and process characteristics, along with the state-of-the-art in SiC digital circuits and processors.

3. Processor Architecture Design: This chapter introduces the ultra-minimalist design philosophy, defines the ISA, and describes hardware modules including the ALU, registers, PC, and FSM control unit.

4. Logical Design and Functional Verification: This chapter covers RTL implementation, behavioral simulation verification, logic synthesis, and timing optimization.

5. Circuit-Level Design and Simulation: This chapter discusses transistor sizing, standard cell library design, module circuit implementation, high-temperature simulation, and performance analysis.

6. Layout Design and Verification: This chapter details standard cell and module layouts, top-level place and route strategies, and DRC/LVS verification.

7. Conclusions and Future Work: This chapter summarizes the main contributions and looks ahead to future research directions such as fabrication testing, flow optimization, and architecture expansion.

# Chapter 2

---

## Literature Review

The literature review establishes the technological and research background for this work. It first introduces the material and device properties of 4H-SiC relevant to CMOS integration, then surveys the evolution of SiC digital circuit design, and finally summarizes previous processor-level demonstrations that form the foundation for the 4-bit RISC processor developed in this thesis.

### 2.1 Properties of SiC Devices for CMOS Integrated Circuits

Rapid advancements in aerospace, nuclear, and automotive technologies have created a growing demand for electronic systems capable of reliable operation under extreme environmental conditions. However, conventional silicon-based semiconductor technology is approaching its physical limits in breakdown voltage, thermal tolerance, and operating frequency, restricting its suitability for such harsh applications. Among various wide-bandgap semiconductors, silicon carbide (SiC) uniquely combines strong theoretical advantages with a relatively mature CMOS platform that has demonstrated reliable IC operation at elevated temperatures. This section reviews the fundamental material and device characteristics underlying SiC CMOS circuit design and introduces the specific process technology used in this work—the Fraunhofer IISB 4H-SiC CMOS process.

#### 2.1.1 Fundamental Material Properties of 4H-SiC

Silicon Carbide is a compound semiconductor composed of silicon (Si) and carbon (C), classified as a wide bandgap (WBG) material. Among its more than 250 crystalline forms, or polytypes, the 4H-SiC variant has become the material of choice for high-power, high-frequency, and high-temperature electronic devices due to its superior electrical characteristics [21, 30]. Compared to conventional Si, 4H-SiC demonstrates significant advantages across several key physical properties.

Figure 2.1: 4H-SiC wafer with sensor arrays and integrated circuits in the Fraunhofer IISB technology [3]

### Wide Bandgap

The most fundamental advantage of 4H-SiC is its wide bandgap, approximately 3.26 eV, which is nearly three times that of silicon's 1.12 eV [21, 30]. This property is the cornerstone of its high-temperature capability. A wider bandgap results in an extremely low intrinsic carrier concentration, meaning that far fewer charge carriers are generated by thermal energy. This dramatically suppresses leakage currents, which are a primary failure mechanism for silicon devices as temperature rises. Consequently, SiC devices can operate reliably at temperatures far exceeding silicon's typical limit of 150-175°C, with demonstrated functionality at 600°C and beyond [22]. Furthermore, a wider bandgap means a higher electric field is required to cause avalanche breakdown, contributing to the material's superior high-voltage performance [1, 8].

### High Critical Electric Field

4H-SiC possesses a critical electric field strength of about 2.2 MV/cm, nearly ten times higher than that of silicon ( $\sim 0.3$  MV/cm) [30]. This has a profound impact on the design of power devices. For a device to block a certain voltage, it requires a drift region of a specific thickness. Because SiC can withstand a much higher electric field, it requires a significantly thinner drift region to block the same voltage

## 2.1. Properties of SiC Devices for CMOS Integrated Circuits

---

compared to a silicon device. This directly leads to a lower specific on-resistance ( $R_{on}$ ) and, consequently, a smaller required chip area for a given current and voltage rating. This reduction in size and resistance enables higher power density and faster switching speeds [7].

### High Thermal Conductivity

In addition to its electrical properties, 4H-SiC exhibits excellent thermal conductivity of approximately  $3.7 \text{ W/cm}\cdot\text{K}$ , more than double that of silicon ( $\sim 1.5 \text{ W/cm}\cdot\text{K}$ ) [21, 30]. This property is crucial for reliability in high-power and high-temperature applications. It allows heat generated during device operation to be dissipated much more efficiently, lowering the junction temperature of the chip. This superior thermal management capability not only enhances the device's long-term reliability and operational lifetime but also reduces the dependency on bulky external cooling systems, facilitating system miniaturization [11].

Table 2.1: Comparison of key material properties between 4H-SiC and Silicon.

| Property                                                          | 4H-SiC      | Silicon (Si) |

|-------------------------------------------------------------------|-------------|--------------|

| Bandgap (eV)                                                      | $\sim 3.26$ | $\sim 1.12$  |

| Critical Electric Field (MV/cm)                                   | $\sim 2.2$  | $\sim 0.3$   |

| Thermal Conductivity (W/cm·K)                                     | $\sim 3.7$  | $\sim 1.5$   |

| Electron Sat. Drift Velocity ( $10^7 \text{ cm/s}$ )              | $\sim 2.0$  | $\sim 1.0$   |

| Channel Electron Mobility ( $\text{cm}^2/\text{V}\cdot\text{s}$ ) | $< 50$      | $> 400$      |

### Disadvantages and Processing Challenges

Despite its advantages, SiC technology is significantly less mature than silicon, presenting several key challenges in material growth and device fabrication.

- **Material Quality and Cost:** SiC substrate manufacturing is more complex and costly. SiC wafers have a higher density of crystallographic defects that can degrade device performance. Furthermore, SiC wafers are smaller, limiting manufacturing scalability and increasing per-device cost [30].

- **Poor Oxide Interface Quality:** The interface between SiC and its thermally grown oxide ( $\text{SiO}_2$ ) suffers from a high density of interface traps ( $D_{it}$ ). These traps scatter electrons, leading to significantly lower channel mobility in SiC MOSFETs ( $< 50 \text{ cm}^2/\text{V}\cdot\text{s}$ ) compared to silicon devices ( $> 400 \text{ cm}^2/\text{V}\cdot\text{s}$ ). This is a primary obstacle for high-performance SiC CMOS circuits [22, 30].

- **Threshold Voltage Instability:** The high trap density at the SiC/ $\text{SiO}_2$  interface can also lead to threshold voltage ( $V_{th}$ ) instability due to charge trapping, which compromises long-term reliability [12, 30].

## 2. LITERATURE REVIEW

---

- **Difficult Processing:** SiC is an extremely hard and chemically inert material, which makes processes like etching challenging. High temperatures ( $>1600^{\circ}\text{C}$ ) are required for ion implantation activation, adding complexity to the fabrication process [30].

From a device-level perspective, the fundamental properties of 4H-SiC translate into a unique performance profile that makes it the ideal choice for ICs in high-temperature environments. The wide bandgap ensures that even at several hundred degrees Celsius, the transistors maintain an extremely low off-state leakage current, a critical feature that silicon cannot provide. While the high critical electric field is most famous for enabling smaller, more efficient high-voltage power devices, it also contributes to the overall robustness of the transistors. Crucially, the high thermal conductivity allows the integrated circuit to effectively dissipate its own heat, ensuring stable operation and preventing thermal runaway. Although SiC's performance at room temperature is hampered by low channel mobility and other processing challenges, its unparalleled reliability and functionality at high temperatures make it the superior and often only viable technology for demanding applications in aerospace, automotive, and energy exploration.

### 2.1.2 The Fraunhofer IISB 4H-SiC CMOS Technology

The processor presented in this thesis is designed and implemented using the advanced 4H-SiC CMOS platform developed by the Fraunhofer Institute for Integrated Systems and Device Technology (IISB). This process is available through the EuropRACTICE Multi-Project Wafer (MPW) service and is specifically tailored for IC research in harsh environments, particularly at high temperatures [3]. The technology features a double-well structure on an n-type substrate, a nominal operating voltage of 20 V, and a minimum gate length of  $2 \mu\text{m}$  [14]. Key fabrication steps include ion implantation, high-temperature activation annealing exceeding  $1700^{\circ}\text{C}$ , the use of an n-type polysilicon gate, and distinct optimized ohmic contact processes for n-type and p-type regions [14].

As illustrated by the cross-section of the SiC MOSFET in Fig. 2.2, the process is built on an n-type epitaxial layer grown on an n-type substrate and involves multiple implantation steps to form the n-well, p-well, and shallow n<sup>+</sup>/p<sup>+</sup> regions. A thermally grown oxide layer of approximately 55 nm is used, followed by nitric oxide (NO) annealing to reduce the SiC/SiO<sub>2</sub> interface trap density. The polysilicon gate exhibits a sheet resistance of approximately  $15\text{--}17 \Omega/\square$ . Ni-Al and Ti-Al contacts are employed to achieve low-resistance ohmic contacts for n-type and p-type regions, respectively [15].

### Temperature-Dependent Device Characteristics

MOSFETs fabricated in this technology have been experimentally characterized across a wide temperature range from room temperature to  $500^{\circ}\text{C}$ . As shown in

## 2.1. Properties of SiC Devices for CMOS Integrated Circuits

Figure 2.2: Top view and cross section of the SiC MOSFET with metal layer in the Fraunhofer IISB 4H-SiC CMOS process [14].

Fig. 2.3, both n-channel and p-channel devices exhibit a strong temperature dependency in their drain current ( $I_{DS}$ ) versus drain–source voltage ( $V_{DS}$ ) behavior. The drain current increases significantly with temperature and gradually saturates at higher temperatures. This phenomenon can be attributed to several physical effects: at low temperatures, limited dopant ionization and a high density of interface traps restrict carrier mobility; as temperature rises, carriers gain sufficient energy to overcome interface traps and contact resistance barriers, resulting in enhanced mobility and drive current. At temperatures above 400 °C, phonon scattering becomes dominant, leading to mobility saturation.

The threshold voltage also shows a pronounced temperature dependence, as illustrated in Table 2.2. For NMOS transistors,  $V_{th}$  decreases from approximately +4.8 V at room temperature to around 0 V at 500 °C. For PMOS devices, it shifts from about -8.2 V to -5.8 V over the same range [15]. The NMOS devices are

## 2. LITERATURE REVIEW

Figure 2.3: Measured and simulated  $I_{DS}$ – $V_{DS}$  characteristics of (a) NMOS and (b) PMOS transistors in the Fraunhofer IISB 4H-SiC CMOS process. The drain current increases notably with temperature, demonstrating enhanced carrier mobility and improved drive strength at elevated temperatures [15].

more sensitive to temperature. This heightened sensitivity stems from the higher doping concentration in the p-well combined with the more significant impact of partial dopant ionization characteristic of p-type dopants in SiC. These factors lead to larger temperature-induced variations in the Fermi potential compared to the n-well. Consequently, a 20 V supply voltage is adopted in circuit design to ensure sufficient logic-level swing and robust noise margins across the entire temperature range.

In addition, the wide bandgap of SiC ensures that off-state leakage currents remain negligible even above 300 °C [30]. This low-leakage operation, combined with the aforementioned enhancement of carrier mobility and drive current at elevated temperatures, supports highly reliable operation in harsh environments. Experimental and simulated results show good agreement up to 400 °C, while deviations appear beyond this point, mainly due to model limitations in the current PDK temperature range [15].

Overall, the Fraunhofer IISB 4H-SiC CMOS process enables reliable device operation at supply voltages of 20 V and temperatures up to 500 °C. Its combination of low leakage current, temperature-enhanced carrier mobility, and verified high-temperature reliability makes it a mature and accessible platform for SiC-based circuit research. The technology forms the foundation for the processor design presented in this thesis, serving as the fabrication platform on which all circuit-level design, simulation, and validation are based.

Table 2.2: Extracted values of the threshold voltage ( $V_{th}$ ), channel-length modulation parameter ( $\lambda$ ), and peak field-effect mobility ( $\mu_{FE,peak}$ ) from room temperature to 500°C. Mobility data extracted from the report by Mo et al. [15].

| 100 $\times$ 6 $\mu m^2$ PMOS |              |                        |                                          |

|-------------------------------|--------------|------------------------|------------------------------------------|

| Temp. (°C)                    | $V_{th}$ (V) | $\lambda$ ( $V^{-1}$ ) | $\mu_{FE,peak,p}$ ( $cm^2V^{-1}s^{-1}$ ) |

| RT                            | -8.20        | $1.21 \times 10^{-2}$  | $\sim 3.5$                               |

| 100                           | -7.60        | $1.26 \times 10^{-2}$  | $\sim 5.5$                               |

| 200                           | -6.90        | $1.23 \times 10^{-2}$  | $\sim 7.0$                               |

| 300                           | -6.40        | $1.17 \times 10^{-2}$  | $\sim 7.5$                               |

| 400                           | -6.05        | $1.12 \times 10^{-2}$  | $\sim 7.5$                               |

| 500                           | -5.80        | $1.43 \times 10^{-2}$  | $\sim 7.0$                               |

| 100 $\times$ 6 $\mu m^2$ NMOS |              |                        |                                          |

|-------------------------------|--------------|------------------------|------------------------------------------|

| Temp. (°C)                    | $V_{th}$ (V) | $\lambda$ ( $V^{-1}$ ) | $\mu_{FE,peak,n}$ ( $cm^2V^{-1}s^{-1}$ ) |

| RT                            | 4.80         | $2.66 \times 10^{-3}$  | $\sim 18$                                |

| 100                           | 3.55         | $2.81 \times 10^{-3}$  | $\sim 20$                                |

| 200                           | 2.30         | $2.76 \times 10^{-3}$  | $\sim 21$                                |

| 300                           | 0.70         | $3.10 \times 10^{-3}$  | $\sim 21$                                |

| 400                           | 0.25         | $3.24 \times 10^{-3}$  | $\sim 20$                                |

| 500                           | 0.05         | $1.40 \times 10^{-3}$  | $\sim 19$                                |

## 2.2 Digital Circuit Design in SiC Technology

The realization of reliable digital circuits in silicon carbide (SiC) CMOS technology represents a crucial step toward enabling fully integrated systems that can operate in harsh environments beyond the limits of conventional silicon electronics. While the previous section introduced the material properties of 4H-SiC and the process characteristics of the Fraunhofer IISB CMOS platform, this section focuses on how those underlying physical and process parameters influence circuit-level design considerations, challenges, and performance. Over the past three decades, continuous progress in SiC fabrication and circuit methodologies has expanded the technology's capability from fundamental logic gates to complex architectures, including data converters and processor-level implementations. This section reviews the evolution of SiC digital circuit design, beginning with early pioneering efforts in 6H- and 4H-SiC technologies, followed by recent advancements achieved in the Fraunhofer IISB 4H-SiC CMOS platform, and concluding with a summary of the key design characteristics and insights that guide modern SiC digital circuit development.

### 2.2.1 Pioneering Work in Early SiC Processes

The development of silicon carbide (SiC) digital integrated circuits has advanced from elementary logic gates to complex, high-temperature systems over the past three decades. Before the establishment of the Fraunhofer IISB CMOS platform, several institutions worldwide demonstrated pioneering implementations of SiC-based digital electronics, establishing the foundation for modern wide-bandgap CMOS design. This section reviews representative milestones achieved using various early SiC processes.

#### Early 6H- and 4H-SiC Demonstrations (Purdue University, USA)

The first digital circuits realized in SiC were based on 6H-SiC NMOS technology. Cooper *et al.* [31] implemented inverters and ring oscillators operating up to 300 °C, marking the earliest functional demonstration of digital logic in SiC. Subsequently, Ryu *et al.* [23] fabricated the first complementary SiC CMOS logic circuits, including logic gates and D-flip-flops operating at 5 V. Although these works proved the feasibility of digital integration in SiC, the devices suffered from low PMOS mobility, large threshold-voltage asymmetry, and high contact resistance, which constrained circuit complexity and switching speed.

#### GE Global Research 6H-SiC Digital Modules

At GE Global Research, Ghandi *et al.* [4] developed a 4-bit counter and an 8-bit timing generator using a custom SiC CMOS process. The circuits maintained continuous operation for more than 1,000 hours at 300 °C and survived 20 G random vibration and 215 G mechanical shock. These results represented the first verified demonstration of long-lifetime and mechanically robust SiC CMOS digital circuits, confirming their potential for harsh-environment telemetry and control applications.

#### Raytheon HiTSiC® 4H-SiC CMOS Process

Raytheon UK developed the 1.2 μm HiTSiC® 4H-SiC CMOS process, enabling systematic design of complex digital logic. As shown in Fig 2.4, Kuhns *et al.* [10] implemented seventeen digital circuits in this technology, including finite-state machines (FSMs), ripple-carry adders (RCAs), shift registers, ring oscillators, and asynchronous NULL Convention Logic (NCL) circuits. All designs operated correctly up to 300 °C, demonstrating stable functionality and timing robustness in high-temperature environments. In a subsequent tape-out, a Digital-to-Analog Converter (DAC) Controller shown in Fig 2.5a was also fabricated to demonstrate digital control for mixed-signal applications. According to Fig 2.5b, the 18-state FSM-based DAC Controller operated reliably up to 300 °C with a maximum clock frequency of about 4.1 MHz [10]. This design further verified the process's ca-

pability to support moderately complex synchronous digital systems for high-temperature environments.

Figure 2.4: Tapeout 1: Digital Circuits in HiTSiC® 4H-SiC CMOS [10]

Figure 2.5: (a) DAC controller layouts in HiTSiC® 4H-SiC CMOS and (b) corresponding graphical performance data of DAC controller [10].

### Extended High-Temperature Operation and SoC Integration

Building on the HiTSiC platform, Holmes *et al.* [6] demonstrated the extended operation of SiC CMOS circuits at 470–500 °C, corresponding to the Venus-surface environment. They tested ring oscillators, clock generators, and D-flip-flop registers for more than 100 hours of continuous operation, confirming the long-term functionality of the technology. Based on these results, the authors synthesized a 16-bit OpenMSP430 microcontroller core and a 1 kB SRAM using a custom high-temperature digital cell library, providing the first conceptual step toward a programmable SiC processor architecture. Subsequent reports indicated that

## 2. LITERATURE REVIEW

---

the HiTSiC platform later became unavailable [15], leading to increased focus on currently accessible technologies.

Table 2.3: SiC Digital Circuits in Early SiC Processes

| Year | Process / Organization                             | Digital Circuit Type                                           | Max Temp (°C) |

|------|----------------------------------------------------|----------------------------------------------------------------|---------------|

| 1994 | 6H-SiC NMOS (Purdue University, USA)               | Inverters, Ring Oscillators [31]                               | 300           |

| 1997 | 6H-SiC CMOS (Purdue University, USA)               | Logic Gates, D-Flip-Flops [23]                                 | 300           |

| 2014 | Custom SiC CMOS (GE Global Research)               | 4-bit Counter, 8-bit Timing Generator [4]                      | 300           |

| 2016 | HiTSiC® 4H-SiC CMOS (Raytheon UK)                  | FSMs, RCAs, SRs, NCL Counters, MAC Unit, DAC [10]              | 300           |

| 2016 | HiTSiC® 4H-SiC CMOS (Ozark IC / Univ. of Arkansas) | Ring Oscillator, Clock Generator, DFF Register, 16-bit MCU [6] | 470–500       |

### Summary

Table 2.3 summarizes representative early SiC digital circuits fabricated by different organizations and their maximum validated operating temperatures. These pioneering efforts collectively established the feasibility of SiC CMOS digital design and proved that reliable high-temperature operation is achievable far beyond the limits of silicon technology. These foundational efforts ultimately led to currently accessible technologies like the Fraunhofer IISB platform discussed in Section 2.2.2, which became increasingly important as some earlier pioneering processes faced availability challenges.

#### 2.2.2 Digital Circuits in IISB 4H-SiC CMOS Process

The 4H-SiC CMOS platform developed by the Fraunhofer IISB serves as the process foundation for our processor design. Its detailed fabrication flow, including the double-well structure, 20 V nominal supply, and minimum gate length of 2  $\mu$ m, has been described previously in Section 2.1.2. This platform is distributed through the Europractice Multi-Project Wafer (MPW) service and is specifically tailored for the research and development of integrated circuits operating in harsh environments [22].

Early fabrication runs in the IISB 4H-SiC CMOS technology focused on validating the fundamental digital building blocks such as inverters, NAND/NOR gates, multiplexers, and D-type flip-flops [22]. These circuits confirmed that complementary logic can be stably implemented under a 20 V supply, maintaining consistent switching thresholds and voltage transfer characteristics across temperature up to 200 °C. The results established the technological readiness of the SiC CMOS platform for reliable high-temperature logic design.

To explore the scalability of sequential circuits and on-chip memory, a six-transistor (6T) static random-access memory (SRAM) cell shown in Figure 2.6 was implemented and experimentally characterized [21]. The cell maintained correct bistable operation and data retention at 200 °C, verifying that matched pull-up and

pull-down transistor pairs can be achieved despite the inherent mobility asymmetry between NMOS and PMOS devices. This achievement marks a major step toward embedding digital storage in SiC-based systems.

Beyond logic and memory, the Fraunhofer IISB process has also been employed for data-conversion circuits. A two-bit flash analog-to-digital converter (ADC) was first realized and tested successfully [22], followed by higher-resolution designs—a four-bit flash ADC and a six-bit successive-approximation (SAR) ADC—implemented on the same platform [17]. The measured and simulated results demonstrated good linearity and functionality up to 200–300 °C, highlighting the process’s capability for mixed-signal integration and control logic at high temperature. Comparable investigations on SiC-based converters were also reported in [20, 28], confirming the advantage of wide-bandgap CMOS for data conversion beyond the thermal limits of silicon.

More recently, the same technology has enabled large-scale integration of functional subsystems. Romijn *et al.* realized a 64-pixel ultraviolet (UV) image sensor with on-chip readout circuitry fabricated entirely in SiC CMOS [21]. The chip integrates pixel-level photodiodes, analog amplifiers, digital scanning logic, and timing generators on a single die, operating stably up to 200 °C. Such system-level integration demonstrates the transition from discrete logic elements toward full system-on-chip (SoC) architectures within the IISB 4H-SiC CMOS technology.

Through successive design iterations, the Fraunhofer IISB platform has evolved from basic logic validation to complex digital and mixed-signal subsystems, forming a scalable and reliable foundation for future high-temperature processors and sensor systems. Representative fabricated circuits are summarized in Table 2.4.

Table 2.4: Digital Circuits in the Fraunhofer IISB 4H-SiC CMOS Process

| Year | Circuit Type                                   | Key Specifications                                                                  | Max Temp (°C) |

|------|------------------------------------------------|-------------------------------------------------------------------------------------|---------------|

| 2022 | Inverter, NAND/NOR, MUX, D-FF [22]             | 20 V supply, 85% yield                                                              | 200           |

| 2022 | 6T SRAM Cell [22]                              | SNM 7.1/4.4/7.5 V                                                                   | 200           |

| 2022 | 2-bit Flash ADC [22]                           | 68 devices, linear conversion                                                       | 200           |

| 2022 | 64-Pixel UV Image Sensor SoC [21]              | Digital readout array integration                                                   | 200           |

| 2023 | 4-bit Flash ADC, 6-bit SAR ADC [15]            | 266 transistors, 8.8×1.9 mm <sup>2</sup> ; 821 transistors, 4.9×4.9 mm <sup>2</sup> | 300           |

| 2024 | Sensor Interface and ADC Readout Circuits [15] | Fully integrated readout chain                                                      | 200           |

### 2.2.3 Design Characteristics and Considerations of SiC Digital Circuits

Silicon carbide (SiC) CMOS technology exhibits a set of distinctive design characteristics that fundamentally differ from conventional silicon-based logic circuits, offering both remarkable advantages and unique design challenges. Its most prominent strength lies in maintaining reliable functionality under extreme environmental conditions.

Experimental demonstrations conducted using the Fraunhofer IISB 4H-SiC CMOS process have verified stable operation of digital and mixed-signal circuits

## 2. LITERATURE REVIEW

Figure 2.6: Measured  $Q/\bar{Q}$  SRAM cell butterfly curves for different temperature levels of (a) hold, (b) read, and (c) write mode including (d) circuit and micrograph on die (0, 2). A sweep of  $Q/\bar{Q}$  and the maximum size squares are drawn for SNM derivation and a single sweep is depicted for the write mode in favor of readability [21].

including counters, FSMs, ADCs, and SRAMs at temperatures exceeding 300 °C, a performance level unattainable with silicon CMOS [15, 22]. This outstanding high-temperature reliability simplifies system-level design by reducing or even eliminating the need for bulky cooling systems and thermal shielding, enabling more compact and efficient electronic architectures suitable for aerospace, automotive, and geothermal applications. Furthermore, the thermal and electrical stability of SiC devices allows digital and mixed-signal circuits to be co-located with high-power components or sensors, minimizing parasitic effects and improving signal integrity and response speed [22].

However, these advantages are accompanied by several circuit-level limitations that are also evident in the same technology process. A pronounced channel mobility asymmetry between NMOS and PMOS transistors results in highly unbalanced drive strengths, requiring large device width ratios to achieve proper logic-level symmetry [21]. This inevitably increases circuit area, input capacitance, and dynamic power consumption. Additionally, the relatively high and asymmetric threshold voltages—typically above +2 V for NMOS and below -6 V for PMOS—necessitate operation at higher supply voltages in the range of 15–20 V, which further exacerbates static and dynamic power dissipation [15]. Timing closure in synchronous systems is also complicated by the strong temperature dependence of both threshold voltage and propagation delay. As temperature increases, carrier mobility degradation is counterbalanced by a reduction in threshold voltage, often resulting in faster switching at elevated temperatures. This behavior can lead to setup and hold-time violations across wide thermal ranges if design margins are not properly considered in digital circuits.

Furthermore, the Fraunhofer IISB 4H-SiC CMOS process remains in an early stage of technological maturity. Due to the limited number of metal layers, high p-type contact resistance, and partially developed process design kits (PDKs), the design flow still relies heavily on manual optimization and conservative timing margins [22]. Consequently, SiC digital circuits are typically realized with simplified architectures and robust design margins to ensure functional stability under high-temperature operation. Nevertheless, continuous advances in device fabrication and circuit design have steadily increased the level of integration—progressing from basic logic gates to memory arrays, data converters, and even processor-level implementations. These advancements demonstrate that, despite inherent material and device constraints, the Fraunhofer IISB 4H-SiC CMOS technology employed in this work has evolved into a reliable foundation for high-temperature digital systems. It provides the technological foundation for the processor architecture described in the following chapter.

## 2.3 RISC Processor Design and Integration in SiC Technology

Having established the design principles for SiC digital circuits, this section shifts the focus to system-level integration by exploring the design of a RISC processor in SiC technology. It reviews minimalist RISC architectures that serve as practical validation platforms for emerging semiconductor technologies and examines existing SiC processor demonstrations that provide design insights for the 4-bit processor implemented in this work.

### 2.3.1 Minimalist RISC Processors as Validation Vehicles

The concept of the minimalist processor originated in computer architecture education, where the main objective was to reveal the fundamental working principles of a processor through an extremely simplified hardware structure. Early didactic CPUs, typically 4-bit or 8-bit, were not designed for performance but to demonstrate instruction fetch, decode, and execution processes using the smallest possible logic scale. This design philosophy emphasized de-complexification by reducing the instruction set, minimizing register count, and limiting addressing modes, resulting in a functionally complete yet structurally transparent processor architecture [13].

As research needs expanded, such architectures evolved from teaching models into valuable experimental platforms for emerging technologies. Compared to commercial microprocessors, minimalist RISC architectures offer clear structural transparency and controllability, enabling focused studies of timing stability, power characteristics, and high-temperature reliability. These architectures allow researchers to directly evaluate the impact of device and process characteristics on system-level performance without interference from complex pipeline stages, branch prediction, or multi-port register files [29].

In contrast to complex instruction set (CISC) architectures, the essence of RISC lies not in having fewer instructions, but in employing a fixed instruction length and simplified addressing modes that enhance decoding efficiency and timing regularity [32]. RISC processors typically adopt hardwired or finite-state-machine (FSM) control units, dividing execution into fixed stages of *fetch*, *decode*, and *execute* to ensure deterministic timing and minimize logic depth [16]. Such control organization improves both reliability and timing predictability, which is an essential advantage for implementation in immature or constraint-heavy fabrication technologies.

Typical minimalist RISC processors exhibit the following key features as shown in the block diagram of a typical RISC processor (Figure 2.7) [13, 16, 29]:

- **Harvard architecture:** Program and data memories are physically separated, avoiding bus contention and allowing parallel instruction fetch and data operations.

- **Accumulator-based design:** Arithmetic and logical operations share a single accumulator as both operand and result register, eliminating the need for a complex multi-port register file.

- **Finite-state-machine control:** The control unit generates sequential timing signals based on instruction decoding. With a compact instruction set, the FSM requires only a few states, leading to simple, transparent logic that is easily verifiable.

- **Fixed-cycle execution:** Each instruction completes in a predefined number of clock cycles (typically three or four), facilitating deterministic timing analysis and system verification.

Figure 2.7: The block diagram of a minimalist RISC processor showing the core modules and data flow between the ALU, ACC, control unit, ROM, and RAM [13].

The relationship between processor performance and its key parameters can be expressed as:

$$T_{\text{exec}} = N_{\text{instr}} \times \text{CPI} \times T_{\text{critical}} \quad [32]$$

where  $T_{\text{critical}}$  is the critical-path delay determining the maximum operating frequency. Minimalist RISC architectures reduce  $T_{\text{critical}}$  by minimizing combinatorial logic.

## 2. LITERATURE REVIEW

---

tional depth, shortening signal paths, and enforcing a fixed control sequence. This design approach sacrifices instruction complexity in exchange for improved timing reliability and process robustness, which are particularly beneficial for wide-bandgap semiconductor technologies such as SiC CMOS.

Such structural simplicity not only minimizes area and logic overhead but also enhances design verifiability and portability, making minimalist processors ideal as first-silicon validation vehicles in emerging technologies [29]. In wide-bandgap processes such as 4H-SiC CMOS, process rules, parasitic models, and EDA tools are still under development. With their shallow logic depth and compact interconnect structure, minimalist RISC processors enable rapid system-level demonstration and characterization [13]. Consequently, they have been widely employed as system-level validation chips, serving as foundational testbeds for assessing logic reliability, timing consistency, and high-temperature operation in new semiconductor technologies.

### 2.3.2 Existing SiC Processor Demonstrations and Integration Insights

Early studies on silicon carbide (SiC) digital circuits mainly focused on verifying the high-temperature functionality of basic logic modules, as discussed previously in Section 2.2. As the 4H-SiC CMOS process matured, researchers began to construct the first SiC digital system prototypes capable of performing both control and arithmetic operations, marking an initial step toward system-level integration. Kuhns *et al.* implemented a set of complex digital circuits in the Raytheon HiTSiC® CMOS process, including finite-state machines, asynchronous counters, multiply-accumulate units, and DAC controllers [10]. These circuits operated reliably at 300 °C, demonstrating that SiC CMOS technology was capable of supporting higher levels of digital integration and control logic functionality.

Holmes *et al.* further advanced SiC CMOS technology toward processor-level verification, aiming to achieve long-term stable operation of SiC microcontroller systems under a 470 °C environment [6]. Based on the HiTSiC® CMOS process, the study established high-temperature device models and developed a digital logic design flow applicable to 470 °C operation. Long-duration testing of CMOS ring oscillators, clock generators, and register files was performed, and their corresponding wafer layouts are shown in Figure 2.8a. As a representative example, the simulation analysis of ring oscillators at elevated temperatures (Figure 2.8b) confirmed stable circuit operation, confirming stable behavior and verifying the reliability of the SiC CMOS devices up to 470 °C [6]. Using the extracted experimental data, the team derived temperature-dependent parameters such as threshold voltage shift, mobility degradation, and aging effects, thereby constructing SPICE and timing libraries at 470 °C. High-temperature simulation analyses based on these models revealed that the conventional 5:1 PFET-to-NFET width ratio caused excessive delay mismatch and overdriving above 300 °C, whereas a 3:1 ratio provided superior drive balance and timing consistency at extreme temperatures [6]. Consequently, a new digital standard-cell library was developed, including ba-

### 2.3. RISC Processor Design and Integration in SiC Technology

sic elements such as logic gates, latches, and flip-flops, which provided a unified foundation for subsequent processor synthesis and system-level design.

Figure 2.8: (a) Die micrographs of CMOS clock generator, CMOS and NMOS ring oscillators, and D-type flip-flop and (b) Operation of ring oscillator using simulation models from room temperature to 470 °C [6].

With the optimized device models and logic library, the team synthesized and simulated a 16-bit SiC microcontroller based on the open-source OpenMSP430 architecture [5]. The system adopted a Von Neumann structure, integrating 1 kB SRAM, a clock generator, and standard I/O interfaces within an active area of approximately 250 mm<sup>2</sup> (Figure 2.9a). Corresponding simulation results shown in Figure 2.9b indicated stable operation at around 800 kHz under a 12 V supply and 470 °C [6]. Additional lifetime tests on the ring oscillator, non-overlapping clock generator, and 8-bit register file confirmed stable functionality during 100 hours of continuous high-temperature operation. These findings validated the effectiveness of the 3:1 sizing strategy and high-voltage biasing for maintaining logic integrity and timing stability, providing essential guidelines for future system-level processor design [6].

The work by Holmes and colleagues further demonstrated the scalability of SiC CMOS microcontroller integration. Several peripheral modules, including an 8-bit ADC, comparator, communication interface, and gate-driver circuits, were proposed and partially verified to interface with the SiC microcontroller [6, 10]. These results illustrate that SiC CMOS technology can support not only digital logic and memory modules but also mixed-signal peripherals, paving the way toward high-temperature SiC-based system-on-chip (SoC) platforms. Overall, the study established a significant milestone in the evolution from discrete SiC digital modules to a complete programmable microcontroller system, confirming the feasibility of wide-bandgap CMOS technology for processor-level integration in extreme environments. These developments provide valuable insights and technical foundations for the minimalist 4-bit RISC processor design presented in this work.

## 2. LITERATURE REVIEW

Figure 2.9: (a) Layout of SiC-CMOS microcontroller core implemented with placed and routed SiC-CMOS digital standard cells and (b) digital simulation (ADD operation) using 470°C extracted timing models [6].

### 2.3.3 Summary and Outlook

In summary, minimalist RISC architectures, characterized by structural simplicity, deterministic timing, and design transparency, have proven highly suitable for validating emerging semiconductor technologies. Over the past decade, SiC CMOS research has progressed from demonstrating basic logic circuits to exploring processor-level system integration. The 16-bit microcontroller proposed by Holmes *et al.* [6] represented a major step in this evolution, providing a complete design flow and high-temperature simulation validation up to 470 °C. However, the design remained at the simulation and low-frequency verification stage without fabrication, indicating that SiC processor research is still primarily focused on feasibility-level evaluation.

Building upon these developments, the present work implements a minimalist 4-bit RISC processor in the Fraunhofer IISB 4H-SiC CMOS process. This design provides a compact and fabricable platform for system-level validation, enabling further investigation of integration capability and performance reliability of SiC CMOS digital circuits under extreme temperature conditions.

## Chapter 3

---

# Processor Architecture Design

This chapter aims to design and describe in detail a minimalist 4-bit processor, with the core objective of serving as a test vehicle to validate the feasibility and reliability of SiC CMOS technology for digital systems. The chapter begins by outlining the 'ultra-minimalist' design philosophy adopted to mitigate the constraints of the emerging SiC process. It then details the custom Instruction Set Architecture (ISA) and the overall top-level architecture of the processor, including its core modules and external interfaces. A significant portion is dedicated to the Control Unit, explaining its Finite State Machine (FSM) based design. The chapter concludes by discussing the functional implementation possibilities and summarizing the key design accomplishments.

### 3.1 Design Philosophy

This design of the minimalist 4-bit Processor is based on the Fraunhofer IISB 2  $\mu\text{m}$  4H-SiC CMOS process. This technology is developed for applications in harsh environments, such as high operating temperatures [30]. However, as an emerging technology, its integration level for digital circuits is still in a preliminary stage. Limited by the capabilities of process equipment such as lithography tools, the minimum gate length of this process is 2  $\mu\text{m}$ , which results in a transistor density significantly lower than that of mainstream silicon-based processes[14]. Consequently, within the limited chip area of 5x5 mm<sup>2</sup>, the available logic resources are highly constrained, accommodating an estimated maximum of only around 3000 transistors. To minimize design risks under this strict area constraint and to maximize the probability of a successful first-pass tape-out with this emerging process, this design adopts an "ultra-minimalist" architectural philosophy.

To achieve this goal, several key decisions were made: First, the program memory (ROM) was moved entirely off-chip to maximize the available die area for the processor core. Second, area-intensive on-chip general-purpose RAM was eliminated and replaced with basic input and output registers. Finally, and most critically, an "instruction set-hardware co-design" strategy was employed. By design-

### 3. PROCESSOR ARCHITECTURE DESIGN

---

ing a highly optimized and concise instruction set, we shifted hardware complexity to the software (instruction set encoding) layer, thereby minimizing the gate count and area of the control unit.

This design enables the processor to efficiently execute predefined, linear arithmetic and logic operations, bit manipulations, and simple timing control tasks. It is precisely this inherent simplicity and predictable linear execution flow that make it a very robust design, ideal for executing high-reliability, fixed sequential control tasks in extreme physical environments such as aerospace.

## 3.2 Instruction Set Architecture (ISA)