# MSc THESIS

# Performance Validation of Networks on Chip

Karthik Chandrasekar

#### Abstract

VSZAS

**CE-MS-2009-08**

Network-on-Chip (NoC) is established as the most scalable and efficient solution for the on-chip communication challenges in the multicore era, since it guarantees scalable high-speed communication with minimal wiring overhead and physical routing issues. However, efficiency of the NoC depends on its design decisions, which must be made considering the performance requirements and the cost budgets, specific to the target application. In the NoC design flow, merely verifying and validating the design for its adherence to the application's average communication requirements may be insufficient, when the need is to get the best performance within tight power and area budgets. This calls for NoC design validation and optimization under real-time congestions and contentions imposed by the target application. However, application availability issues (due to Intellectual Property restrictions), force us to look at alternative solutions to mimic the target application behavior and help us arrive at an efficient and optimal NoC design. This thesis is a step in the said direction, and proposes a performance analysis and validation tool (infrastructure) that employs synthetic and application trace-based traffic generators, to efficiently emulate the expected communication behavior of the target application. Novel methods are suggested to

model and generate deterministic and random traffic patterns and to port reference application traces from and to different interconnect architectures (from buses to NoCs or vice versa). Further, these traffic generators are supported by efficient traffic management/scheduling schemes, that aid in effective analysis of the NoC's performance. The proposed tool, also includes a statistics collection and performance validation module that checks the designed network for adherence to the performance requirements of the target application and explores trade-offs in performance and area/power costs to arrive at optimal architectural solutions. The significance of this tool, lies in its ability to comprehensively validate a given NoC design and suggest optimizations, in the light of the target applications expected run-time communication behavior.

Faculty of Electrical Engineering, Mathematics and Computer Science

#### THESIS

# submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE

in

#### COMPUTER ENGINEERING

by

Karthik Chandrasekar born in Chennai, India

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

by Karthik Chandrasekar

#### Abstract

etwork-on-Chip (NoC) is established as the most scalable and efficient solution for the on-chip communication challenges in the multi-core era, since it guarantees scalable highspeed communication with minimal wiring overhead and physical routing issues. However, efficiency of the NoC depends on its design decisions, which must be made considering the performance requirements and the cost budgets, specific to the target application. In the NoC design flow, merely verifying and validating the design for its adherence to the application's average communication requirements may be insufficient, when the need is to get the best performance within tight power and area budgets. This calls for NoC design validation and optimization under real-time congestions and contentions imposed by the target application. However, application availability issues (due to Intellectual Property restrictions), force us to look at alternative solutions to mimic the target application behavior and help us arrive at an efficient and optimal NoC design. This thesis is a step in the said direction, and proposes a performance analysis and validation tool (infrastructure) that employs synthetic and application trace-based traffic generators, to efficiently emulate the expected communication behavior of the target application. Novel methods are suggested to model and generate deterministic and random traffic patterns and to port reference application traces from and to different interconnect architectures (from buses to NoCs or vice versa). Further, these traffic generators are supported by efficient traffic management/scheduling schemes, that aid in effective analysis of the NoC's performance. The proposed tool, also includes a statistics collection and performance validation module that checks the designed network for adherence to the performance requirements of the target application and explores trade-offs in performance and area/power costs to arrive at optimal architectural solutions. The significance of this tool, lies in its ability to comprehensively validate a given NoC design and suggest optimizations, in the light of the target applications expected run-time communication behavior.

| Laboratory<br>Codenumber | : | Computer Engineering<br>CE-MS-2009-08   |

|--------------------------|---|-----------------------------------------|

| Committee Members        | : |                                         |

| Advisor:                 |   | Dr. ir. Georgi Gaydadjiev, CE, TU Delft |

| Advisor:                 |   | Prof. Giovanni De Micheli, LSI, EPFL    |

| Chairperson:             |   | Prof. Kees Goossens, CE, TU Delft       |

| Member:                  |   | Dr. ir. Rene van Leuken, CAS, TU Delft  |

To my parents

# Contents

| List of Figures  | vii |

|------------------|-----|

| List of Tables   | ix  |

| Acknowledgements | xi  |

| 1        | Inti | roduction                                        | 1              |

|----------|------|--------------------------------------------------|----------------|

|          | 1.1  | Why Networks On Chip?                            | 1              |

|          | 1.2  | Network on Chip Architecture                     | 2              |

|          | 1.3  | Network on Chip Design Flow                      | 3              |

|          | 1.4  | Xpipes NoC Design Flow                           | 4              |

|          | 1.5  | Motivation and Objective                         | 5              |

|          | 1.6  | Contributions                                    | $\overline{7}$ |

|          | 1.7  | Thesis Organization                              | 8              |

| <b>2</b> | Xpi  | pes and MPARM                                    | 9              |

|          | 2.1  | Xpipes NoC                                       | 9              |

|          | 2.2  | Xpipes Building Blocks                           | 9              |

|          |      | 2.2.1 Network Interfaces                         | 10             |

|          |      | 2.2.2 Switches                                   | 10             |

|          |      | 2.2.3 Links                                      | 11             |

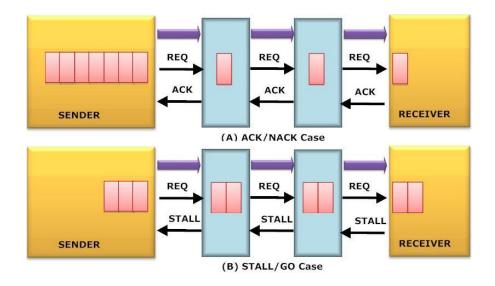

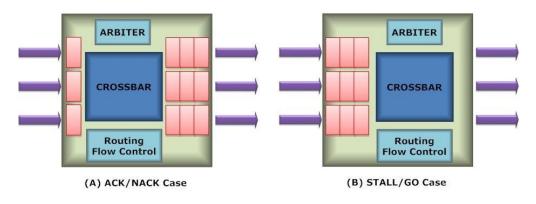

|          | 2.3  | Xpipes Flow Control Protocols                    | 11             |

|          | 2.4  | Xpipes Compiler                                  | 13             |

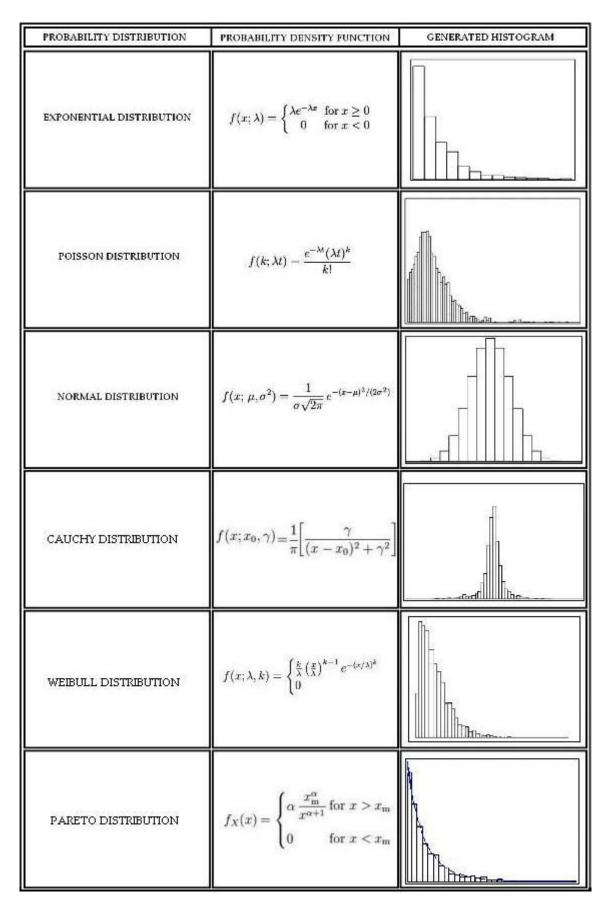

|          | 2.5  | MPARM platform                                   | 13             |

|          | 2.6  | Using Xpipes Compiler and MPARM                  | 15             |

| 3        | Syn  | thetic Traffic Modeling and Generation           | 17             |

|          | 3.1  | Need for Traffic Models                          | 17             |

|          | 3.2  | Modeling Traffic Injection                       | 17             |

|          | 3.3  | Modeling Synthetic Traffic                       | 19             |

|          | 3.4  | Modeling Traffic using Probability Distributions | 20             |

|          | 3.5  | Modeling Traffic using Traffic Patterns          | 23             |

|          | 3.6  | Traffic Management/Scheduling Scheme             | 25             |

|          |      | 3.6.1 Maximum Throughput Scheduling              | 27             |

|          |      | 3.6.2 Weighted Fairness Scheduling               | 27             |

|          |      | 3.6.3 Analyzing Scheduling Impact                | 27             |

|          | 3.7  | Challenges in Synthetic Traffic Generation       | 28             |

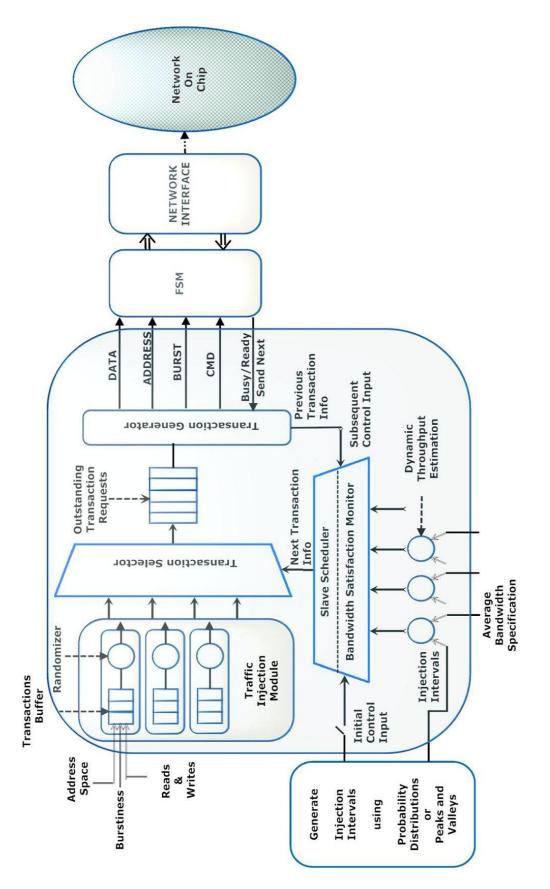

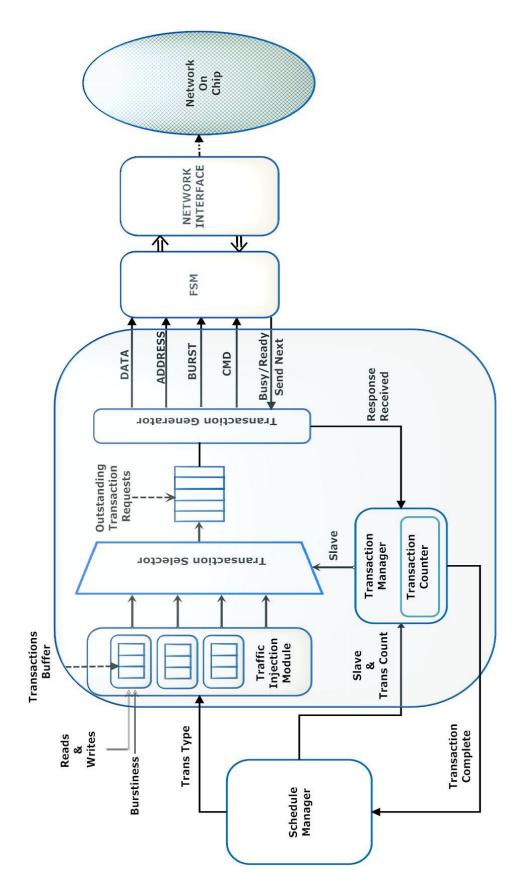

|          | 3.8  | Synthetic Traffic Generator Architecture         | 30             |

| App   | blication Trace Modeling and Regeneration                                                                                                                                                    | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1   | Why model application traces?                                                                                                                                                                | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.2   | Issues in Modeling Traces                                                                                                                                                                    | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.3   | Trace Modeling Methodology                                                                                                                                                                   | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

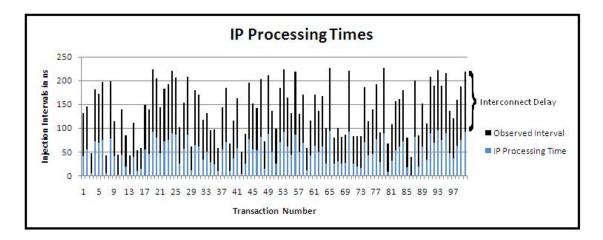

|       | 4.3.1 Estimating IP processing times                                                                                                                                                         | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

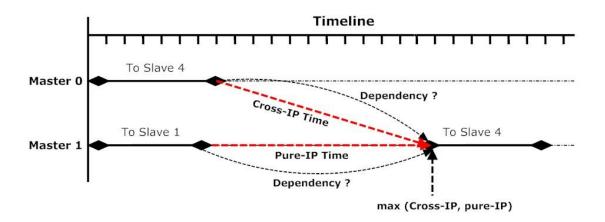

|       | 4.3.2 Deriving Application's Approximate Static Schedule                                                                                                                                     | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

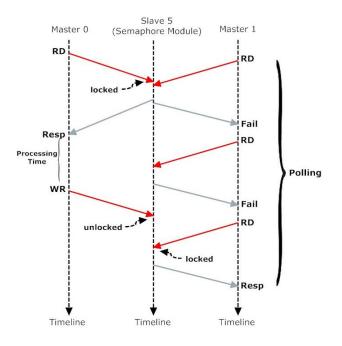

|       | 4.3.3 Employing Application's Dynamic Schedule                                                                                                                                               | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.4   | The Schedule Manager                                                                                                                                                                         | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

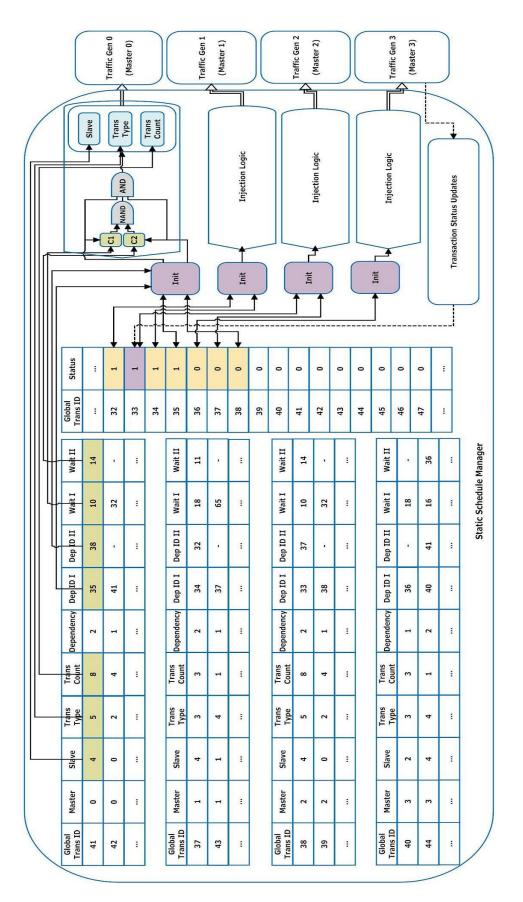

|       | 4.4.1 Static schedule manager                                                                                                                                                                | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

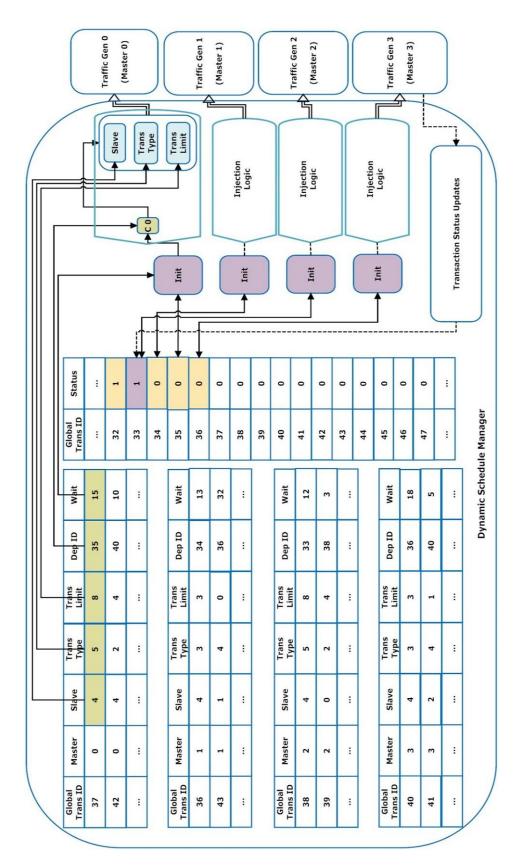

|       |                                                                                                                                                                                              | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.5   | 0                                                                                                                                                                                            | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.6   | Trace-based Traffic Generator Architecture                                                                                                                                                   | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Per   | formance Validation and Simulation Results                                                                                                                                                   | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.1   | Why Performance Validation?                                                                                                                                                                  | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.2   | Challenges in Statistics Collection                                                                                                                                                          | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.3   | Performance Metrics                                                                                                                                                                          | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | 5.3.1 Latency Measures                                                                                                                                                                       | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | 5.3.2 Buffering $\ldots$                                                                                                                                                                     | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.4   | Benchmarks Description                                                                                                                                                                       | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

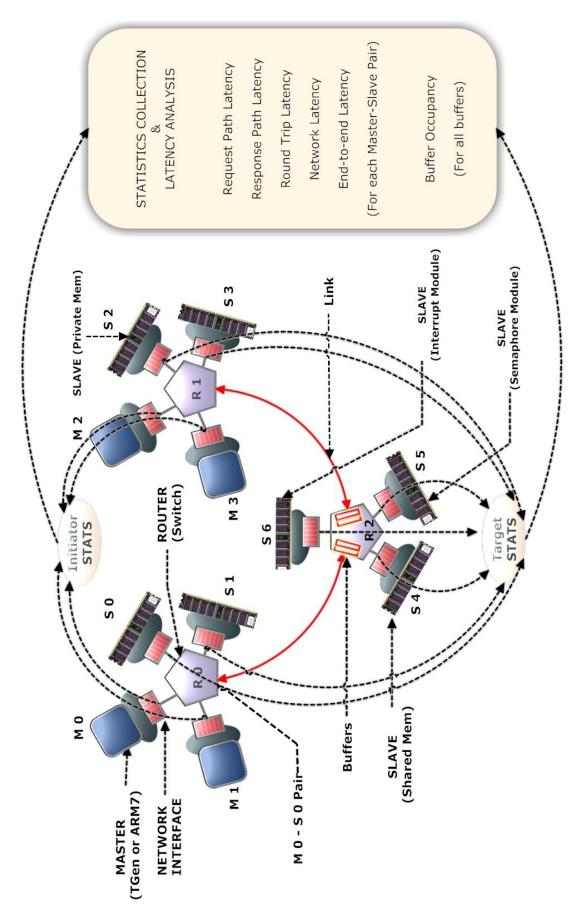

| 5.5   | Topology Specification and Simulation Setup                                                                                                                                                  | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.6   | Simulations                                                                                                                                                                                  | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | 5.6.1 Latency Observations                                                                                                                                                                   | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | 5.6.2 Performance Validation and Optimization                                                                                                                                                | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Cor   | clusion and Future Work                                                                                                                                                                      | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6.1   | Conclusion                                                                                                                                                                                   | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6.2   | Future Work                                                                                                                                                                                  | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| bliog | graphy                                                                                                                                                                                       | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Mic   | ro-Benchmarks - Source                                                                                                                                                                       | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A.1   | asm-matrixind                                                                                                                                                                                | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1 0   | asm-matrixdep                                                                                                                                                                                | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br><b>Per</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br><b>Con</b><br>6.1<br>6.2<br><b>Con</b><br>6.1<br>6.2<br><b>Ebliog</b><br><b>Mic</b><br>A.1 | 4.2       Issues in Modeling Traces         4.3       Trace Modeling Methodology         4.3.1       Estimating IP processing times         4.3.2       Deriving Application's Approximate Static Schedule         4.3.3       Employing Application's Dynamic Schedule         4.4       The Schedule Manager         4.4.1       Static schedule manager         4.4.2       Dynamic schedule manager         4.4.2       Dynamic schedule manager         4.5       Challenges in Traffic Generation from Traces         4.6       Trace-based Traffic Generator Architecture         Performance Validation and Simulation Results         5.1       Why Performance Validation?         5.2       Challenges in Statistics Collection         5.3       Performance Metrics         5.3.1       Latency Measures         5.3.2       Buffering         5.4       Benchmarks Description         5.5       Topology Specification and Simulation Setup         5.6.1       Latency Observations         5.6.2       Performance Validation and Optimization         5.6.2       Performance Validation and Optimization         6.1       Conclusion         6.2       Future Work         6.1       Conclusion |

# List of Figures

| Conceptual view of Network on Chip             | 2                                  |

|------------------------------------------------|------------------------------------|

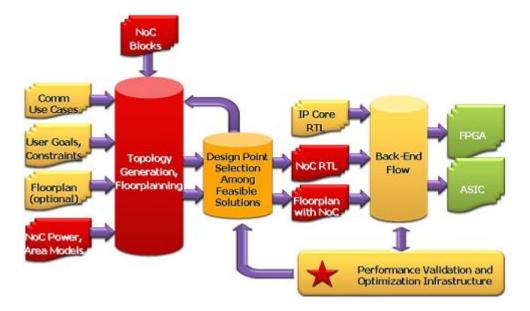

| Xpipes Network on Chip Design Flow             | 5                                  |

| Overview of Xpipes NoC Architecture            | 9                                  |

| Xpipes pipelined link block diagram            | 12                                 |

| Buffering in Switches                          | 12                                 |

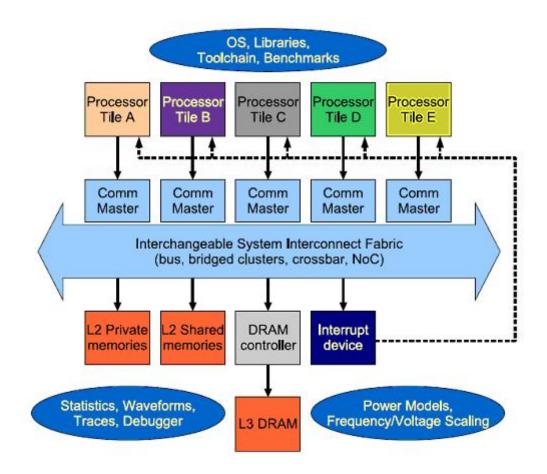

|                                                | 14                                 |

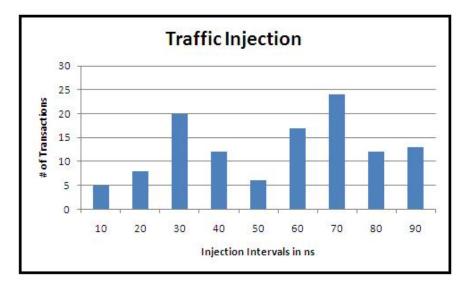

| Traffic Injection Histogram                    | 17                                 |

| Traffic Injection Timeline                     | 18                                 |

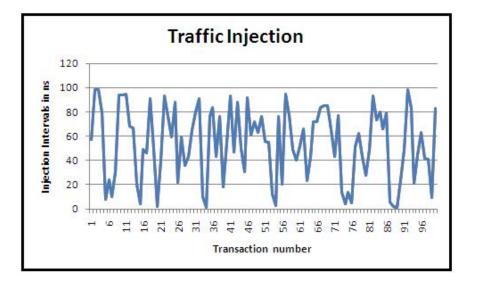

| Probability Distributions                      | 21                                 |

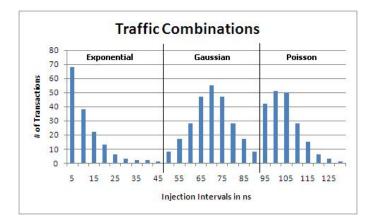

| Combination of Probability Distributions       | 22                                 |

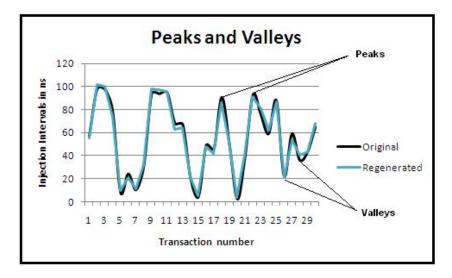

| Peaks and Valleys Approach                     | 23                                 |

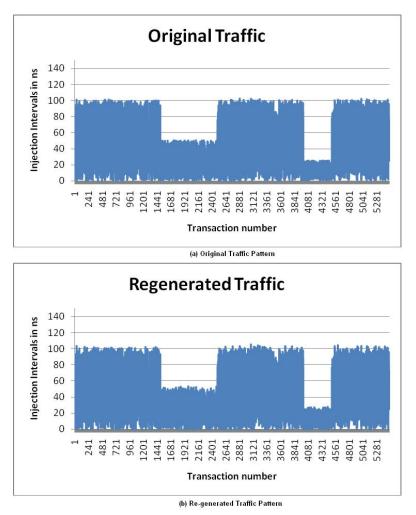

| Application Traffic (Original and Regenerated) | 24                                 |

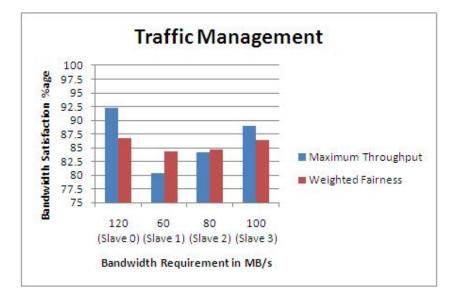

| Efficient Traffic Management Schemes           | 28                                 |

| Synthetic Traffic Generator Architecture       | 31                                 |

| IP processing times and Interconnect Delays    | 34                                 |

| Dependencies between transactions              | 34                                 |

| Synchronization Event                          | 39                                 |

|                                                | 40                                 |

| Static Schedule Manager                        | 42                                 |

| Dynamic Record Description                     | 43                                 |

|                                                | 44                                 |

|                                                | 47                                 |

| Simulation Setup                               | 56                                 |

|                                                | 61                                 |

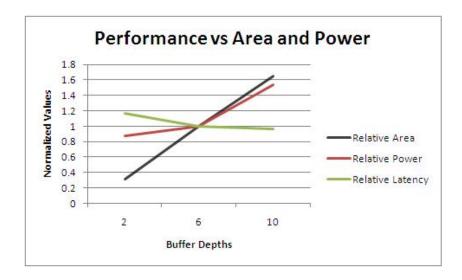

| Performance vs Area and Power                  | 61                                 |

|                                                | Xpipes Network on Chip Design Flow |

# List of Tables

| 5.1 | Latency measures for asm-matrixdep         | 58 |

|-----|--------------------------------------------|----|

| 5.2 | Latency measures for asm-matrixind         | 59 |

| 5.3 | Latency measures for synthetic benchmark   | 59 |

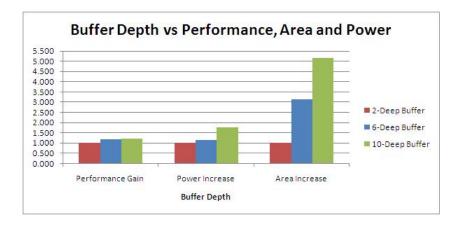

| 5.4 | Buffer Occupancy and Buffer Area and Power | 60 |

| 5.5 | Impact of Buffer Depth on Performance      | 60 |

# Acknowledgements

Firstly, I would like to thank Prof. Giovanni De Micheli for giving me the opportunity to work on my MSc thesis, in his group (LSI) at EPFL, Switzerland. I would also like to express my gratitude to Dr. Federico Angiolini (Post. Doc at LSI, EPFL) for his guidance and support throughout the length of this thesis work. I would also like to thank Dr. Srinivasan Murali (Post. Doc at LSI, EPFL), Antonio Pullini and Ciprian Seiculescu (PhD students at LSI, EPFL), Jaume Joven (PhD student at UAB, Spain) and Dara Rahmati (PhD student at Sharif University, Iran) for their ideas, suggestions and all help during the course of my work at EPFL.

I would specially like to thank Prof. Georgi Gaydadjiev, who has been ever supportive and helpful, since my first days at TU Delft, for accepting to supervise my thesis from Delft and providing timely suggestions and ideas to improve my work.

I would also like to thank Prof. Kees Goossens for giving several suggestions to improve the thesis contents; hopefully some of them have been accomodated. I would also like to thank Prof. Rene van Leuken for accepting to judge my thesis defense and suggesting changes and corrections to the report.

Finally, I would like to thank my parents for all their love and support and Prof.Venkateswaran at WARFT for motivating me to undertake research during my bachelor's itself. Last but not the least, I would like to thank my friends Madhavan and Vinoth for the wonderful time we spent together in the last 2 years.

Karthik Chandrasekar Delft, The Netherlands November 30, 2009

# 1.1 Why Networks On Chip?

The ever increasing demand for processor performance countered by the power consumption barrier has lead computer architects to design multi-processor and multi-core single chip architectures [26] [1]. As technology scales beyond deep sub-micron and offers increasing integration density, the assembling of a complete system consisting of a large number of IP blocks (e.g. processors, accelerators, memories, I/O controllers) on the same silicon die has become technically feasible.

Today, chips comprise of tens or even hundreds of these building blocks, often very heterogeneous in pin-out, performance, geometric size and shape, clocking requirements, etc. As the complexity of such MPSoC designs skyrockets, one of the crucial bottlenecks has been identified as the on-chip interconnection infrastructure [23].

Most current SoC designs are based on shared buses due to their low cost. Unfortunately, scalability is limited on shared buses due to the serialization of multiple access requests. Among the key design challenges for an efficient communication infrastructure, some of the most prominent ones include, bandwidth scalability, efficient wiring and accurate routing of data.

A solution to these challenges has been identified in Networks-on-Chip (NoC) [15], where the communication is always point-to-point and packet-switched and messages are transferred from source to destination across several links and switches (routers). While this allows unlimited bandwidth scalability (i.e. by adding more on-chip routers and links), it also ensures that the wiring is kept tidy and length bounded.

NoCs are now being considered by many, as a viable alternative to design scalable communication architecture for present and future generation SoCs [32]. In multimedia processors, inter-core communication demands often scale up to the range of GB/s and this demand is expected to peak with the integration of several heterogeneous high performance cores into a single chip. To meet such increasing bandwidth demands, state-of-the-art buses such as STBus and AMBA, instantiate multiple buses operating in parallel thereby providing a crossbar-like architecture, which however, still remains inherently non-scalable. To effectively tackle the interconnect complexity of MPSoCs, a scalable and high performance interconnect architecture is needed and hence, NoCs [24] [16].

#### **1.2** Network on Chip Architecture

Emerging System-on-Chip (SoC) designs consist of a number of interconnected heterogeneous devices. NoCs can be described as the on-chip interconnect that connects up these heterogeneous IP blocks, provides support for multiple clock domains on a single chip and facilitates communication across the IP blocks based on predefined protocols and routing schemes. For efficient functioning of NoCs, the three components: the Network Interfaces, the Routers and the Links play very significant roles. A conceptual view of the Network on Chip architecture is depicted in Figure 1.1.

Figure 1.1: Conceptual view of Network on Chip

As can be seen in the figure above, the different IP cores such as CPU, Accelerators, DMAs, I/O etc., are connected to the NoC infrastructure through the Network Interfaces, which in turn connect to a port on any of the Routers which then connect among themselves, forming the NoC.

The Network Interface is employed to provide protocol-specific communication, by converting core-specific signals into a common packet format, performing packetization/depacketization of data and implementing the service level protocols associated with each transaction in the NoC. In simple terms, a Network Interface translates messages from its IP core to a standard protocol when its IP core sends messages into the network and from the standard protocol to that of its IP core when it receives messages, thus supporting SoCs that accommodate heterogeneous IP cores and coordinating the transmission and reception of packets from/to the core. The Routers are used to establish the links across the IPs, such that the data packets can be transferred from any source to any destination while making routing decisions at the switches. The routers can be arbitrarily connected to each other and to NIs, based on a specified topology. They include routing, switching and flow control logic. Routing schemes help in finding a path between any source and destination IP block, while minimizing the number of hops to transport packets across the NoC infrastructure in a parallel and pipelined fashion.

The connecting links are also a critical component of NoCs. They connect NIs and routers and help in transmitting data packets over the network. The routers are used to route the packets from source to destination, while links are used to connect the various cores and routers together.

Besides these three main components, the flow control techniques also play a significant role in the working of NoCs by defining how packets should be moved through the network while providing performance guarantees in Quality of Service (QoS). Flow control techniques also help in dealing with situations where two packets arrive at the same link at the same time (contention).

#### **1.3** Network on Chip Design Flow

Designing NoCs to meet the functional specification is a complex task and it involves lot of design trade-offs. As a consequence, the entire design process [27] [18] is categorized into several phases. The design choices made at each phase have a significant impact on the overall performance of the NoC and the following phases as well. For instance, a design choice made during topology selection phase will have an impact on the overall performance and will also influence the consequent phases like mapping, routing scheme selection etc. In general, the distinct phases in NoC Design flow can be classified as:

(a) **Application Description** - It is responsible for providing a unified representation of the communication patterns. In certain cases these patterns also include communication types, frequencies etc. The general characterization is done by means of a graph where each vertex represents a computational module in the application referred to as task and the edge denotes the dependencies between the tasks. All the entities are annotated with additional information specifying other communication characteristics. Alternatively a spreadsheet can also be used, wherein each worksheet can give a description of the applications communication requirement for a particular use case.

(b) **Topology Selection** - It involves exploring various design objectives such as average communication delay, area, power consumption etc. While advantages of resorting to regular topologies hold for homogeneous SoCs, this is no longer true in the case of heterogeneous SoCs. The design choices span between full custom topologies and standard regular topology. The designer could even adopt a hierarchical topology scheme to satisfy the system requirements. Also, the floorplan information can aid in topology design/selection process.

(c) **IP Mapping** - It is the process of determining how to map the selected IPs on the communication architecture and also satisfy the design requirements. Different approaches have been proposed to achieve efficient mapping involving branch and bound algorithm, multi-objective mapping etc.

(d) **Architecture Configuration** - It involves fixing up of buffer sizes, routing and switching schemes etc. Different strategies are adopted by various design flows to select values that suit the architecture's communication requirements. Here, since the design space considered is fairly large and complex, some heuristic based exploration techniques are employed to arrive at near-optimum solution.

(e) **Design Synthesis** - It involves description of the network components in hardware modeling language and this is achieved by using tools, in the synthesis phase. Also, standard network component libraries for switches, routers and network interfaces can be used.

(f) **Design Validation and Simulation** - Validation of the implementation of the NoC architecture is useful in verifying the design against the initial requirements in terms of communication latencies, throughput, area and power.

The cost and performance numbers are obtained by simulations and depend on the selected network components and the topology, and the setting of their corresponding parameters. This final phase of the design flow also helps tune the NoC parameters to suit the target application's behavior.

In the next section, we specifically look into the design flow of the Xpipes NoC [22] [17], which is the case study NoC being used in this thesis, for simulation purposes.

# 1.4 Xpipes NoC Design Flow

The Xpipes NoC Design Flow [13] is used to generate efficient NoCs using Xpipes architecture [17] with custom topology to satisfy the design constraints of the application. The objective is of the design flow is to minimize network's power consumption and the number of hops.

The Xpipes design flow also uses a floor-planner to estimate design area and wire lengths for selecting topologies that meet the requirements both in terms of power consumption and target frequency of operation. This helps achieve fewer design re-spins, as accurate floor-plan information is made available early in the design cycle. Also deadlock free routing methods are considered to ensure proper NoC operation.

In the first phase of the design flow, the constraints and objectives to be satisfied by the NoC architecture are specified. Information on application traffic characteristics, area delay and power models etc are also obtained.

In the second phase, the NoC which satisfies all the constraints is automatically synthesized. There are different steps involved in this phase. Firstly, frequency and link width are varied between a set of suitable values. Then the synthesis step is performed for each set of architectural parameters thereby exploring the various design choices. This step involves establishing connectivity between the switches and cores and finding deadlock free routes for the different traffic flows. In the last phase, RTL code required for the various network components instantiated in the design is automatically generated. It uses Xpipes library [35], which comprises of soft macros of the components and Xpipes Compiler [29]to interconnect network elements with the core. The design flow of the Xpipes NoC is shown in Figure 1.2 and is based on the Xpipes design flow suggested in Figure 1.5 in [12] and Figure 3.1 in [33].

Figure 1.2: Xpipes Network on Chip Design Flow

As can be seen in the figure above, performance goals and power and area budgets are obtained from the user and the NoC components in different configurations and their corresponding power and area models are obtained from the Xpipes NoC library. Based on these requirements and constraints, a suitable architecture and topology is generated and using optimization heuristics, a set of feasible architectural solutions is obtained. The Xpipes compiler then generates the RTL for one of the design solutions.

#### **1.5** Motivation and Objective

As mentioned in the previous section, in the Xpipes NoC Design Flow, all the performance objectives (in terms of average throughput and latency requirements) and design constraints (in terms of power and area budgets) are specified in the first phase itself and proper adherence to the same is verified throughout, with the aim to guarantee high performance and low power and area costs. However, the design process is yet incomplete, since there is still a need to verify the network design for performance and efficiency against real-time constraints (congestions and contentions) imposed by a real application/benchmark, so as to arrive at a concrete and optimal NoC design for a given application.

It is well established that parallel injection of traffic from different IP cores or processors in an MPSoC environment, causes contention for network's resources. Although, links are designed to provide adequate bandwidth to meet the average requirements of the application, traffic injection instances with high levels of contention, lead to congestion, due to the design choices for network components, thus affecting the network's performance. To overcome or subside this issue, network's designers tend to over-design the NoC, such that despite the congestions and contentions, the throughput and latency requirements of the application are met. However, such over-design adversely impacts the power and area costs and hence, calls for an additional effort to validate and optimize the design such that the performance objectives and cost constraints are met.

In order to arrive at efficient and optimal network design solutions, it becomes essential to verify the same against the run-time behavior of the target application, since that would present a very realistic picture of the network's performance at run-time and thereby, an accurate estimate of the required over-design. Hence, it becomes extremely crucial to incorporate such a phase in the design process to arrive at an efficient and optimal design of the NoC, as can be seen in Figure 1.2.

This can be done with adequate information about the target application from the user, though it may well be very restricted due to application's Intellectual Property issues. What may be available could be information such as, expected traffic pattern or a trace obtained from a reference system, which uses a different existing interconnect such as a shared bus. Hence, it is suggested to instead employ synthetic or application trace-based traffic generators, that effectively emulate the expected behavior of the target application.

The synthetic traffic generators produce traffic based on given probability distributions or traffic shapes or patterns that can be expected for the given application in the given system setup. This description may be specified by the user, as a substitute for application details such as source code or scheduling information.

The application trace-based traffic generators re-produce traffic from a reference application trace (obtained from a reference system), by modeling and porting the same to the NoC-based simulated system. The reference trace may be made available from a cycle-accurate reference simulator system or a functional simulator system, with unknown or constant reference interconnect delays, which needs to be filtered out when porting the trace. Modeling and porting of traces also involves deriving of application's realistic schedule, which helps maintain transaction ordering and application control flow. Such measures, assure that the process of modeling and porting the reference trace, yield a more accurate estimate of the application's expected run-time behavior, when compared to the synthetic traffic generation mechanism, by estimating and reproducing complex dependencies in the application such as during synchronization.

In comparison to a relevant recent effort in this direction in [31] where there is a need to use system-level information such as knowledge of semaphore variables and pre-defined memory address map to detect synchronization events, the suggested approach provides a more generic approach with the ability to automatically detect dependencies across all the transactions in the application, without using any such system-dependant information.

In this thesis, we address both the scenario's (synthetic and trace-based traffic generation) assuming availability of application information in both the formats (as traffic patterns/distributions and reference application traces), and can expect efficient validation and optimization. While the former method, is meant to give a direction for validation and optimization, the latter provides more accurate estimates of the network's performance and design issues.

The objective of this thesis is to come up with a performance validation tool/infrastructure which incorporates such traffic generators that help in performance validation and optimization of the NoC design. The thesis aims to addresses the following major challenges:

- Using traffic generators to model and re-generate target application's expected run-time behavior.

- Validation of the NoC design to meet the application's requirements.

- Suggest optimizations arriving at the best tradeoffs among performance and area/power constraints.

#### **1.6** Contributions

To develop an infrastructure for performance analysis, validation and design optimization of NoCs, the tool employs synthetic and trace-based traffic generators, which effectively produce synthetic traffic and efficiently emulate traffic behavior of real applications, respectively.

In addition, novel methods are suggested to mimic non-deterministic traffic patterns in synthetic traffic generators and to arrive at traffic models that realistically capture the application communication behavior and schedule across the IP cores in trace-based traffic generators. In synthetic traffic generation, traffic patterns using relevant probability distributions/analytical models are generated. In trace-based traffic generation, reference traces are employed and appropriate methods to migrate and emulate the same to different environments/interconnect, are suggested.

In order to obtain application traces, a set of benchmarks are executed on a cycle-accurate MPSoC emulator called MPARM [14], which employs ARM7 [30] processors.

The process of collecting statistics involves capturing the type and the timestamp of communication events at the boundary of every IP core in a reference environment. This opens up the possibility for communication infrastructure exploration and optimization and for the investigation of its impact on system performance at the highest level of accuracy under realistic workloads and different system configurations.

The performance validation tool/infrastructure proposed in this thesis helps in validating system level design decisions and verification of the implementation. It addresses the performance vs area and power tradeoffs and helps validate and optimize the NoC performance. In short, this thesis proposes a comprehensive infrastructure for performance analysis and trade-off exploration for on-chip communication architectures.

# 1.7 Thesis Organization

Chapter 2 of this thesis gives an overview of the Xpipes NoC architecture, the Xpipes Compiler and the MPARM MPSOC platform and their relevance to this study. Chapter 3 discusses synthetic traffic generation using relevant probability distributions, besides suggesting an efficient 'peak and valleys' approach for modeling non-deterministic distributions/curves in traffic patterns. It also suggests an efficient traffic management/scheduling scheme for the traffic generator, that defines the spatial distribution of the traffic in the network, in order to assure maximum possible stress on all links and to check for robustness of the NoC. Chapter 4 suggests a methodology for estimating IP processing times and deriving an application's static schedule from a reference trace. It also suggests a method for employing an application's dynamic schedule for better representation of the application's behavior, besides describing the implementation of the appropriate schedule managers. Chapter 5 describes the methodology involved in statistics collection and analysis and presents a set of simulation results for a benchmark application. Chapter 6 concludes the thesis, highlighting the significance of the work and exploring opportunities for future work.

## 2.1 Xpipes NoC

The Xpipes NoC [22] library provides efficient synthesizable, high frequency and low latency components (such as Network Interfaces, Routers and Links) which can be parameterized in terms of buffer depth, flit width, arbitration policies, flow control mechanisms etc. The Xpipes Compiler is employed to interconnect these network elements with the cores.

Xpipes NoC [17] is fully synchronous and yet supports multiple frequencies in the NIs. Routing is statically determined in the NIs. Xpipes uses wormhole switching [2] and best-effort services [3] for data transfers. There is also support for QoS provisions. Xpipes supports both input and/or output buffering, depending on flow control requirements and designer choices. In fact, since Xpipes supports multiple flow controls, the choice of buffering strategy is entwined with the selection of the flow control protocol. Xpipes also chooses to employ parallel links over virtual channels to resolve bandwidth issues, in order to reduce implementation costs.

# 2.2 Xpipes Building Blocks

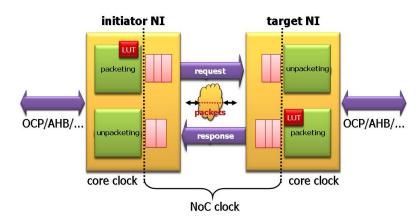

The most critical components in any NoC architecture are the Network Interfaces, the Routers and the Links. An NoC is instantiated by interconnecting these network elements in different configurations to form a topology, which may either be specific, such as mesh or ring, or allow for arbitrary connectivity, matching the requirements of the target application. An overview of the Xpipes NoC architecture is depicted in Figure 2.1.

Figure 2.1: Overview of Xpipes NoC Architecture

As can be seen in the figure above, the Xpipes NoC has a simple architecture with a Network Interface for each of the sources and one for each of the targets. The Network Interface includes separate request and response paths, which include packetizing and de-packetizing logic. The arbitration happens at the routers, which decides which master/source gets priority on the links down stream. The Xpipes NIs also support multiple clock domains at the sources and targets. The Xpipes NoC building blocks are explained in detail in the following sub-sections.

#### 2.2.1 Network Interfaces