Investigation of the inductor's parasitic capacitance in the high frequency switching of the high voltage cascode GaN HEMT

Nikolaos Galanos

# Investigation of the inductor's parasitic capacitance in the high frequency switching of the high voltage cascode GaN HEMT

Nikolaos Galanos

Master of Science Thesis

Supervisors:

Dr. J. Popovic-Gerber

Dr. M.B. Gerber

Electrical Power Processing

Department of Electrical Sustainable Energy

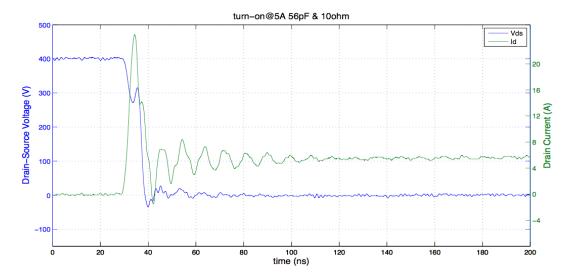

Faculty of Electrical Engineering, Mathematics and Computer Science

Delft University of Technology

April 16, 2015

## Abstract

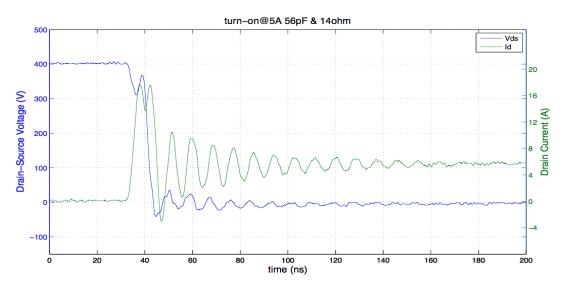

The concept of the More Electric Aircraft, where the majority of the aircraft's secondary needs will be supplied by electrical power, is under continuous research over a number of years in order to conform the recent demand for more efficient and environmentally friendly aircrafts. Advancements in power electronics have contributed towards the realization of that demand, by introducing lightweight, high-power density and highly efficient in harsh environment power electronics. The increase in power density of power electronic systems was made feasible, so far, by developments in the semiconductors field, namely by semiconductors that can operate at higher switching frequencies and generate less power loss. Wide-bandgap devices, such as Gallium Nitride (GaN) transistors, have emerged as possible candidates to replace silicon and even silicon carbide devices in various power conversion applications offering potential benefits for high frequency power conversion due to their intrinsic material properties. Another step towards higher power densities is to utilize appropriate circuit topologies since they can reduce the stress upon the components and the cooling requirements. However, as the frequency goes up, the switching behavior of the device is not only influenced by the die itself and the device package's and circuit's parasitic elements can not be neglected any more. One of these parasitic elements is the the equivalent parasitic capacitance (EPC) of the magnetic component, which is part of almost every topology.

This thesis project aims at two things: first, to observe the switching behavior of a high-voltage cascode GaN High Electron Mobility Transistor (HEMT) under inductive clamped load condition, which is the same commutation mode for the power devices as switching in a PWM, hard-switching type converter and second, to investigate the influence of the magnetic component's EPC on the switching behavior of the GaN HEMT. For this, an analytical loss model of the device was developed and a double-pulse tester (DPT), which is considered to be a very good example of that load condition, was optimally designed and manufactured in order to verify the analytical model. Two pulses are launched to the device under test (DUT) and the switching transitions of the DUT can be captured for any desired current and voltage rating under hard-switching conditions. Moreover, when operating under that load conditions, applying active devices with reverse recovery charge has significant influence on the switching behavior of the DUT, so both cases will be examined. Finally, in order to characterize the device and eventually verify the analytical loss model, current and voltage measurements need to be taken during the turn-on and turn-off switching transitions. As the GaN HEMT is capable of switching are very high speed, there are issues and limitations that need to be taken into consideration in order to ensure the fidelity and the accuracy of these high frequency measurements.

## Acknowledgements

This research has been carried out at the Delft University of Technology, The Netherlands, in the group of Electrical Power Processing (EPP). This project has been a great experience and many people have contributed to its successful completion. I would like to take this opportunity to express my gratitude to them.

First, I would like to express my sincere gratitude to my supervisors Jelena Popovic-Gerber and Mark Gerber. I am truly grateful to them for trusting in my ability to complete this work and for their help and guidance throughout the duration of this thesis. Discussions with them have always been more than enlightening and thought provoking. I would also like to thank Mark for guiding me during the experimental part of this thesis and for sharing his knowledge with me. Their patience and kindness are greatly appreciated.

I would also like to thank Dr. Emile Brink for his help during this thesis. He was always available to discuss my questions, especially, regarding the magnetics and to share his knowledge and experience during the experimental measurements of this thesis project. A great thanks, also, goes to Ivan Josifovic and Wenbo Wang whose help and discussions during the practical part of this thesis were extremely important.

Thanks also to my fellow master students: Foivos, Joost, Didier, Einar, Ralino, Andreas, Sotiris, Vasilis, and my friends, Alexandros and Konstantinos, for the great time we had the past two years.

At this point, I would like to thank AERONAMIC B.V. for founding my research.

Finally, I would like to thank my parents, Theodoros and Anastasia. They have always supported me and been there to make sure I had everything I needed. Without their love and encouragement, I couldn't have make it so far. I would also like to thank my girlfriend, Vivi, for her love and support.

## Contents

| $\mathbf{A}$ | bstra                 | act                                                              | iii       |

|--------------|-----------------------|------------------------------------------------------------------|-----------|

| A            | ckno                  | owledgments                                                      | V         |

| C            | onter                 | nts                                                              | vii       |

| 1            | Intr                  | roduction                                                        | 1         |

|              | 1.1                   | More Electric Aircraft (MEA)                                     | 1         |

|              | 1.2                   | Power Density                                                    | 3         |

|              | 1.3                   | DC/DC Power Converters                                           | 5         |

|              | 1.4                   | Thesis objective                                                 | 5         |

|              | 1.5                   | Thesis Layout                                                    | 6         |

| 2            | Hig                   | gh Frequency Power Converters - The Emergence of the Gallium Ni- |           |

|              | $\operatorname{trid}$ | de Transistors                                                   | 7         |

|              | 2.1                   | DC/DC Power Converters                                           | 7         |

|              | 2.2                   | Power Density                                                    | 12        |

|              | 2.3                   | Semiconductors for High Frequency Applications                   | 16        |

|              |                       | 2.3.1 High Voltage GaN-HEMT in cascode configuration             | 21        |

|              |                       | 2.3.2 Switching Losses                                           | 22        |

|              | 2.4                   | Discussion                                                       | 28        |

| 3            |                       | alytical Loss Model of High Voltage GaN HEMT in cascode config-  |           |

|              |                       | tion                                                             | <b>29</b> |

|              | 3.1                   | Switching characteristics of the device                          | 29        |

|              | 3.2                   | Analysis of the switching transitions                            | 32        |

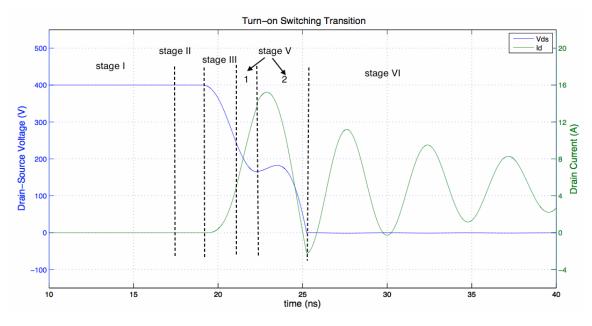

|              |                       | 3.2.1 Turn-on transition                                         | 33        |

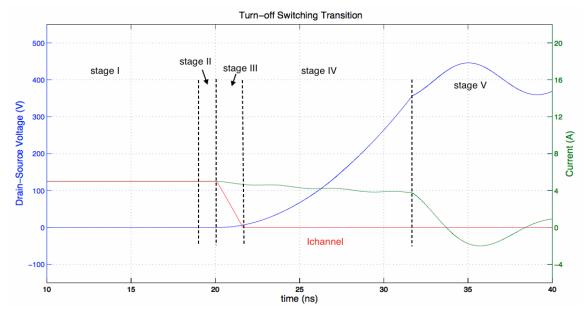

|              |                       | 3.2.2 Turn-off transition                                        | 38        |

|              |                       | 3.2.3 Calculated results of the analytical model                 | 43        |

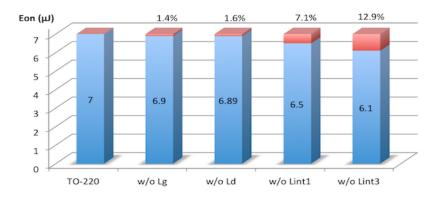

|              | 3.3                   | Investigation of package parasitic inductances influence         | 45        |

|              | 3.4                   | Discussion                                                       | 48        |

| 4            |                       | asurements in high frequency power electronics applications      | 49        |

|              | 4.1                   | Important Issues in Measurements                                 |           |

|              |                       | 4.1.1 Bandwidth Considerations                                   |           |

|              |                       | 4.1.2 V-I Alignment                                              | 51        |

|    | 4.2        | Voltage Measurement Techniques                                          | 52  |  |

|----|------------|-------------------------------------------------------------------------|-----|--|

|    |            | 4.2.1 Voltage Divider Probes                                            | 52  |  |

|    |            | 4.2.2 Differential Probes                                               | 52  |  |

|    |            | 4.2.3 Single-ended Passive Voltage Probes                               | 53  |  |

|    | 4.3        | Current Measurement Techniques                                          | 54  |  |

|    |            | 4.3.1 Rogowski Coil                                                     | 54  |  |

|    |            | 4.3.2 Current Transformer                                               | 55  |  |

|    |            | 4.3.3 Hall Effect Sensor                                                | 56  |  |

|    |            | 4.3.4 Giant Magnetoresistive Current Sensor                             | 57  |  |

|    |            | 4.3.5 Giant Magnetoimpedance Current Sensor                             | 58  |  |

|    |            | 4.3.6 Coaxial Shunt                                                     | 59  |  |

|    |            | 4.3.7 Summary of the discussed current measurement techniques           | 61  |  |

|    | 4.4        | Discussion                                                              | 61  |  |

| 5  | Inve       | estigation of the influence of the inductor's parasitic capacitance     | 63  |  |

|    | 5.1        | The Double-Pulse Tester                                                 |     |  |

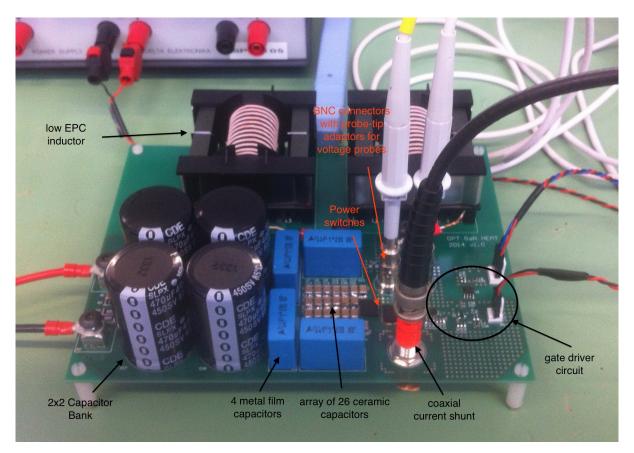

|    | 5.2        | The DPT hardware Setup                                                  | 65  |  |

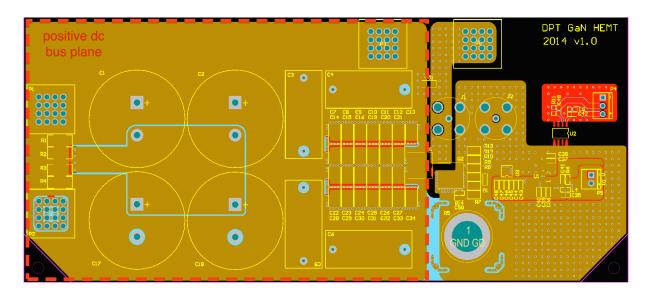

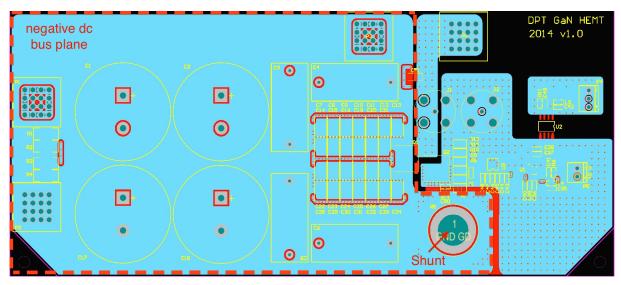

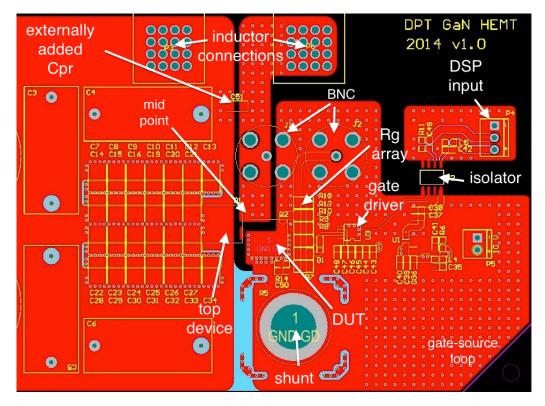

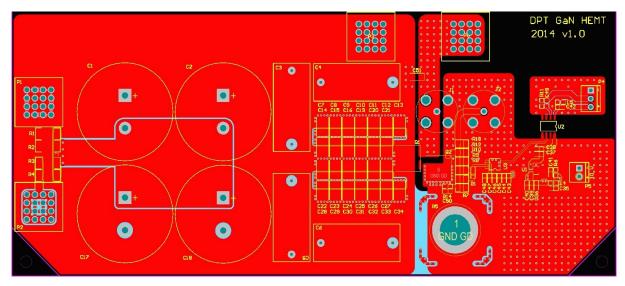

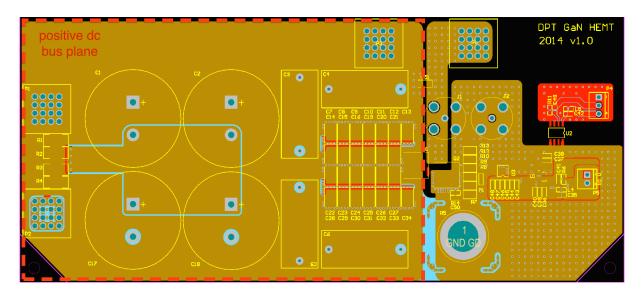

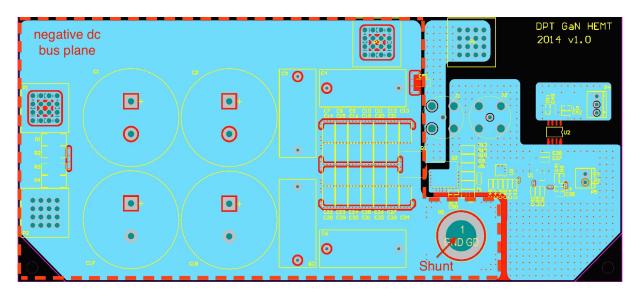

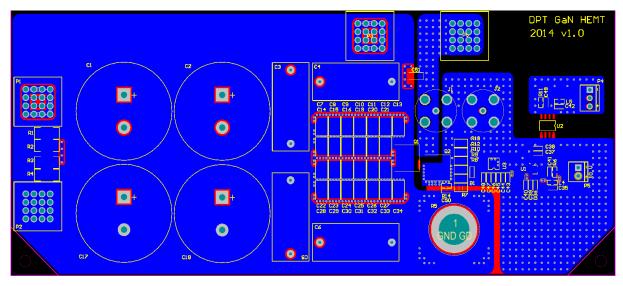

|    |            | 5.2.1 Printed Circuit Board design                                      | 66  |  |

|    |            | 5.2.2 Measurement Techniques                                            | 69  |  |

|    |            | 5.2.3 Low EPC inductor design                                           | 70  |  |

|    | 5.3        | Verification of the analytical loss model                               |     |  |

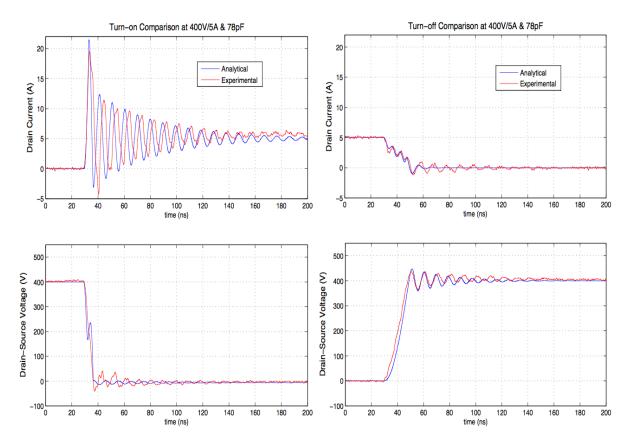

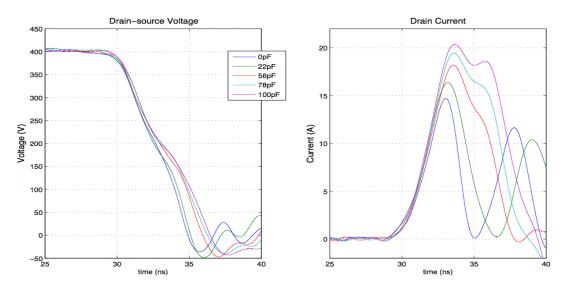

|    |            | 5.3.1 Investigation of the GaN HEMT's switching behavior                | 72  |  |

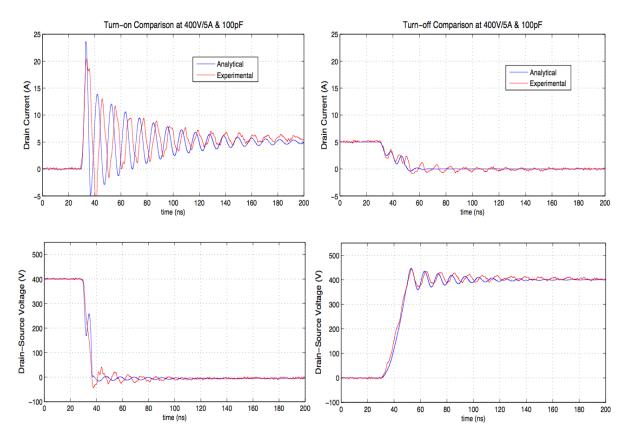

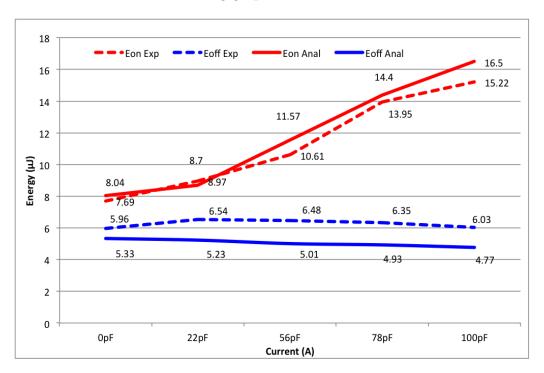

|    |            | 5.3.2 Parametric Study of the inductor's EPC on the switching behavior  |     |  |

|    |            | of the GaN HEMT                                                         | 76  |  |

|    | 5.4        | Investigation of the GaN HEMT's switching behavior with an active top   |     |  |

|    |            | switch                                                                  | 82  |  |

|    |            | 5.4.1 Parametric Study of the inductor's EPC on the switching behavior  |     |  |

|    |            | of the GaN HEMT with an active top switch                               | 84  |  |

|    |            | 5.4.2 Influence of the gate resistance on the switching behavior of the |     |  |

|    |            | GaN HEMT with an active top switch and additional EPC                   |     |  |

|    | 5.5        | Comparison of the two examined cases                                    |     |  |

|    | 5.6        | Discussion                                                              | 90  |  |

| 6  |            | nclusion                                                                | 93  |  |

|    | 6.1        | Conclusions                                                             |     |  |

|    | 6.2        | Suggestions for future work                                             | 95  |  |

| Bi | bliog      | graphy                                                                  | 97  |  |

| Aj | Appendices |                                                                         |     |  |

| Δ  | DP'        | T schematic and PCR layouts                                             | 109 |  |

## Chapter 1

## Introduction

The trend of the More Electric Aircraft (MEA), where the majority of the aircraft's secondary needs are supplied by electrical power, is under continuous research over a number of years: the concept of an electric aircraft has been questioned since World War II [1–4]. Nevertheless, the lack of electric power generation capabilities along with the volume requirements of the power components laid the approach unfeasible. On the other hand, the rapidly developed hydraulic power systems were providing less complex systems, causing them to be adopted as the standard technology for secondary power. The recent demand for more efficient and environmentally friendly aircrafts along with the advances in power electronics and high power density electrical machines have opened up new opportunities leading the aerospace market to overcome its conservatism and renew the interest in MEA.

In this chapter a short description of the project's background will be given. In section 1.1 the basic concepts behind the realization of the MEA will be shortly described and the connection with the advancements in the area of power electronics will be made. Section 1.2 will introduce the principles behind power density increase and how the advancements in the semiconductor's field can contribute to it. Section 1.4 describes the thesis objective of this thesis project. Finally, section 1.5 gives the structure of this thesis.

## 1.1 More Electric Aircraft (MEA)

In conventional aircraft architectures most of the power, produced by fuel in the engines, is used as propulsive power to move the aircraft. The rest is extracted by the main engine with different principles and is converted into secondary power types in order to drive the non-propulsive aircraft systems [2], [3]:

- *Mechanical power*: obtained from the engine by means of mechanical gearboxes and used to drive hydraulic pumps, fuel pumps, lubrication pumps and electrical generators.

- Pneumatic power: extracted by the engine's bleeding compressor and used to power the Environmental Control System (ECS), cabin pressurization and the wing antiicing system.

- *Hydraulic power*: obtained from the main hydraulic pump and used to drive primary and secondary flight control actuators, landing gear for deployment and braking and other ancillary systems.

- *Electrical power*: obtained from the main generator to drive subsystems like avionics, lighting, galleys and other commercial loads.

Through the years, each system has become more and more complex, so the manufactures can satisfy the increasing demands of the passengers for comfort and more facilities, resulting in reduction of the efficiency of the whole system. Moreover, these systems tended to be heavy, inefficient and required frequent maintenance, i.e. pneumatic and hydraulic systems have the drawback that a potential leakage of fluids is difficult to be detected and also not easily accessible. All these, along with the recent developments in the field of power electronic systems, fault-tolerant electric machines, electro-hydrostatic and electromechanical actuators have led the aerospace market towards the reduction/removal of the mechanical complexity and its replacement with electronics.

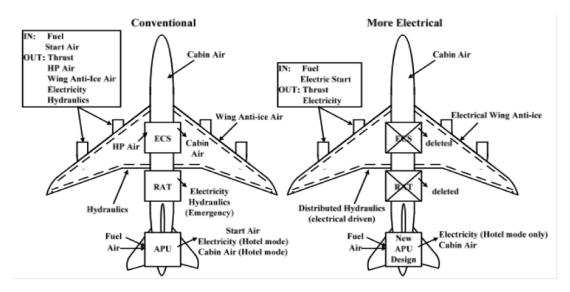

The concept of a More Electric Aircraft is based on using the electrical power for extracting and distributing these non-propulsive powers (see figure 1.1). Over the years a lot of research has been conducted regarding the benefits of an electric aircraft in the following areas [2]: Flight Control Technology, Wing Technology, Engine Power Extraction, Flight Control Actuation, Advanced Electrical Power Systems. Summarizing these studies, the technologies that can realize the MEA initiative can be summarized in the following four key concepts suggested by R. E. J. Quigley in [5]:

- The engine Starter/Generator: lightweight motors will be mounted directly on the main shaft (internal engine Starter/Generator) allowing the elimination of the engine tower shaft and the accessory gearboxes will be replaced by electronic power converters. The starter/generator will be used to provide the aircraft electric power while it enables emergency power extraction under windmill conditions [6]. Elimination of the gearing and gear separation forces will also allow the integration of Advanced Magnetic Bearing (AMB) systems into the internal starter/generator leading to the removal of the engine oil system along with the lubrication systems.

- Electric primary flight control actuation: in conventional aircrafts the actuation system of the flight surfaces is realized by a centralized hydraulic system (hydraulic pumps, motors and actuators). In the current control technology, known as Fly-By-Wire (FBW), the flight control surfaces are being controlled electrically and activated hydraulically. A new control technology, known as Power-By-Wire (PBW), is examined for the concept of MEA and it aims at replacing the existing systems with electrical equivalent and using electromechanical actuators to control each surface in a de-centralized system [7,8]. Advances in power electronics have led the FBW technology to its current stage, but further advances are needed in order for PBW to take over.

- Integrated auxiliary/emergency Power Unit (IPU): electrically-driven compressors and other heating/cooling units will be used to provide cabin air conditioning, pressurization and other vital services eliminating many issues from the current mechanically-linked auxiliary power units. Consequently, a better cabin environment for the passengers will be provided along with reduction in fuel consumption.

Moreover, the elimination of the gearing will enable the use of AMB same as in the internal starter/generator.

• A fault-tolerant Power Management And Distribution (PMAD) and motor drive system: with ability to drive all the subsystems of the aircraft at most efficient power in order to match every load and cooling requirements. The PMAD system is constituted by power electronic converters and inverters while advancements in these areas will directly impact the viability and overall performance of the aircraft.

Figure 1.1: Comparison between conventional aircraft systems and MEA systems [6]

Conclusively, the electrical systems are expected to reduce the complexity, weight, operation costs and environmental impact while at the same time increase reliability, survivability and viability of the aircrafts by removing the hydraulic, mechanical and pneumatic systems. This change is also expected to have an effect upon the overall aircraft performance, since the concept addresses more energy-efficient ways of converting and utilizing aircraft power.

Looking at the four concepts listed above, it is easily observed that for the realization of each one of them, power electronics are of vital importance. Lightweight, high-power density and highly efficient in harsh environment power electronics are needed for conversion and control of the power over the distribution system of the aircraft [9–11]. However, increasing power density in power electronics modules is a complex issue and demands thorough investigation in many aspects in order to be optimized.

#### 1.2 Power Density

There is a great desire in power conversion, during the past few years, for higher power density while maintaining the efficiency at high levels. For starters, Power Density [kw/liter], defined as the ratio of the converter output power and its volume, is the factor that defines the compactness of the converter design. Therefore, this desire is also characterized by the requirements for lower volume, lower weight and lower production costs. Since the inception of the power electronic converters, power density has increased linearly by

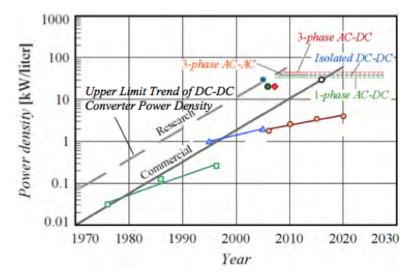

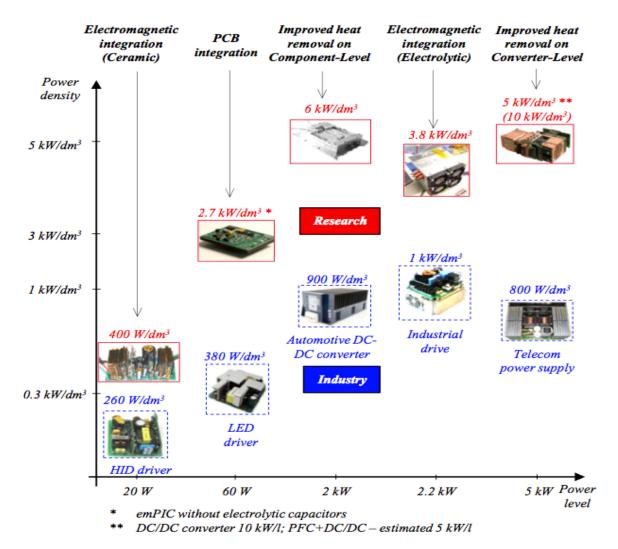

decade. Specifically, as it can be seen in figure 1.2 that the dc/dc converter power density increases by an order of magnitude per decade.

Figure 1.2: Power Density trends over the past few years [12]

The most important thing in achieving higher power densities is to understand the technological barriers that restrain this development. Therefore, the main elements that can affect the converters power density are named below:

- Power Semiconductor Modules

- Control Circuit

- Power Passive Components (filter components / transformers)

- Cooling System

- Interconnection / Packaging

The components that require the largest volume in the converter are the passive components such as capacitors, inductors, and transformers used for filtering, energy storage and cooling systems. The volume of these components is strongly related to the switching frequency of the converter. Moreover, the design of the capacitor and inductor depends on the topology of the dc/dc converter. As the switching frequency is increased, the volume of the inductor and capacitor decreases and so the overall power density increases. According to that, the increase in the power density has been achieved, so far, by increasing the switching frequency. Nonetheless, specific limitations occur at higher switching frequencies, as the switching losses of the semiconductors devices increase, proximity and core losses in the magnetic components also increase and problems occur due to parasitic inductances and capacitances of the circuit, which can no more be neglected.

Regarding the semiconductor devices, new wide-bandgap semiconductors, such silicon carbide (SiC) and gallium nitride (GaN), are being introduced over the past few years and they are considered possible candidates to replace silicon devices in many power conversion applications. GaN semiconductors present better material properties regarding the bandgap, electron mobility and electron saturation velocity than Si and SiC devices, which make them more suitable for higher frequencies and higher voltage operation. They

also have much smaller on-resistance resulting in extremely low conduction losses. Furthermore, these semiconductors have higher maximum operating junction temperatures. Consequently, since the volume of the cooling system is determined by the power loss of semiconductor power devices, by enabling reductions in losses and higher temperature operation, converter thermal management requirement can be decreased. However, utilizing these devices can not be achieved by simple replace them in the existing systems since they come with specific limitations and drawbacks:

- As the switching frequency goes up, the switching loss of device is not only influenced by the die itself, but also by the parasitic inductors of the device package and PCB layout. This, basically, puts a limit on high frequency operation and especially for hard switching operation. Device's junction capacitors also introduce significant switching loss and deteriorate the switching transition. Conclusively, soft switching technique is still critical for high-voltage GaN transistors in order to achieve high efficiency in high frequency operation [13].

- The much smaller surface of GaN devices results in changing the way the dissipated heat is being handled. Therefore, getting the heat out the GaN dies is much more challenging and spreading the heat over multiple sourced becomes necessary [14].

Another step towards higher power densities is to utilize appropriate circuit topologies since they can reduce the stress upon the components and the cooling requirements.

## 1.3 DC/DC Power Converters

Nowadays, dc/dc power converters mostly utilize the so called switch-mode conversion in order to convert a dc input into a controlled dc output with a desired voltage level. There are several dc/dc converter topologies, each one with different characteristics and advantages, giving the possibility to engineers to choose based on their needs. Part of every topology are the magnetic field storage components that can be used to store energy temporarily and release it later on according to the operation principles of each topology.

On the contrary, the same magnetic components will introduce limitations when higher power densities are pursued. For example, when the power converter is operating at high switching frequencies, the equivalent parasitic capacitance (EPC) of the magnetic component can no longer be neglected, as it can have significant impact on the switching behavior of the switches [15].

### 1.4 Thesis objective

This master thesis project is conducted in collaboration with Aeronamic B.V. in order to support the development of a high power density, high efficiency dc/dc power converter for aerospace application. The main objective is to evaluate the switching behavior of the high-voltage GaN HEMT in cascode configuration under hard-switching conditions and investigate the impact of the magnetic component's EPC on the switching performance of this device.

In order to achieve the objective stated above, there are a few research questions that have to be answered:

- How can the use of GaN devices contribute to the development of power electronics?

- What are the advantages of these devices compared to previous ones and how can they improve the converter's performance?

- What are the drawbacks/limitations that they have and what must be done in order to overcome them?

- Why do the parasitic elements of the circuit become more critical with the use of such devices?

- How does the equivalent parasitic capacitance of the magnetic component influence the switching behavior of the power switches?

## 1.5 Thesis Layout

Based on the above objective, the thesis is organized as follows:

Chapter 2 introduces the theoretical background required during this thesis work. The principles of the dc/dc conversion are discussed along with topologies and techniques that can be used depending on the application. The concept of the power density is introduced and the reasons why the emergence of wide-bandgap semiconductors, such as silicon carbide (SiC) and gallium nitride (GaN), can contribute towards the increase of this concept are presented. Finally, the switching transitions of such devices is discussed.

Chapter 3 discusses an analytical loss model of the high voltage GaN HEMT in cascode configuration. The 600V GaN HEMT is tested under clamped inductive load conditions by a double-pulse tester (DPT) circuit. The contribution of the thesis begins in this chapter as the influence of the inductor's EPC on the switching behavior of the GaN HEMT is incorporated into the analytical model.

Chapter 4 presents issues that need to be taken into consideration when voltage and current measurements in high frequency power electronics applications are needed. Solving these issues can ensure the fidelity and the accuracy of the results. Moreover, different voltage and current measuring techniques are presented.

Chapter 5 investigates the influence of the inductor's EPC. Furthermore, it discusses the design and manufacturing of a DPT circuit in order to verify the results of the analytical model.

Chapter 6 gives the main conclusions of the thesis and recommendations for future research.

## CHAPTER 2

# High Frequency Power Converters The Emergence of the Gallium Nitride Transistors

A lot of research has been conducted recently on the area of wide-bandgap semiconductors, such as silicon carbide (SiC) and gallium nitride (GaN), showing remarkable advantages in high-frequency and high-power applications. The capability of these devices to operate at both higher temperature and higher efficiencies promises significant improvements on the reliability and viability of the power electronic modules.

Section 2.1 presents a short description of the principles of the dc/dc conversion and an explanation of the topology operation. In section 2.2, the way of achieving higher power densities together with the limitations will be described and the state-of-the-art power densities in dc/dc converters will be discussed. Finally, section 2.3 gives an overview of the GaN technologies, presents some already existing applications of such devices and discusses the a drawback of this devices when operating at high frequencies, the switching loss.

## 2.1 DC/DC Power Converters

During the past few years, there is a general trend in the area of power conversion to higher power densities while maintaining high efficiencies, mainly driven by reduced weight/space in applications like automotive, aircrafts [12], and microprocessors [16]. However, in order to understand the procedure through which power density may be increased within a power converter, an understanding of the general principle behind the dc/dc voltage conversion and an explanation of the topology's operation, from which the topic of this thesis was born, are considered necessary.

## DC/DC Conversion Methods

The first and oldest method of achieving dc/dc voltage conversion is by means of linear voltage regulators. They adjust a variable resistor in order to provide a constant output

voltage, dissipating the excess electric power in the form of heat. They are inexpensive, quite simple to use and provide a very low noise output, but they suffer from inefficiency when there is large difference between the input and the output voltage. However, when higher efficiency and smaller size or lighter weight are demanded, switched-mode conversion is used. Switching regulators utilize one or more switches in order to maintain an average output value. Magnetic field storage components (inductors) or electric field storage components (capacitors) are used to store the input energy temporarily and release it later in order to transform a dc voltage from one level to another. Nevertheless, complexity is increased and precautions must be taken in order to avoid the electromagnetic interference caused by the high frequency switching.

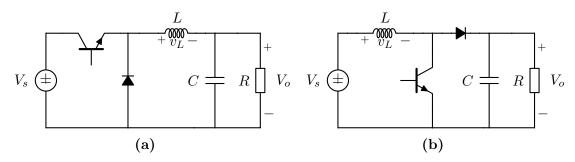

Switched-mode dc/dc converters are used to convert an unregulated dc input into a controlled dc output at a desired voltage level. There are many dc/dc converters topologies, but only two of them are considered the basic ones: the buck converter (also known as step-down converter because it steps the output voltage down) shown in figure 2.1a and the boost converter (also known as step-up converter because it steps the output voltage up) shown in figure 2.1b. The rest of the converters are either combination of the two (like buck-boost and Cuk converters) or they are derived from either the buck converter (like half-bridge and full-bridge converters) or the boost converter (like the flyback converter). For a given input voltage, the output voltage is controlled by adjusting the on and off durations ( $t_{on}$  and  $t_{off}$  respectively) of the switch. One of the most common method for controlling the output voltage utilizes a constant switching frequency and, hence, a constant switching time period  $(T_s = t_{on} + t_{off})$ . In this method, known as pulse-width modulation (PWM) switching, the switch duty cycle, which is defined as the ratio of the on duration to the switching time period  $(D = t_{on} / T_s)$ , is varied by changing the on duration of the switch and consequently the average output voltage is controlled. Other control methods with variable switching frequency exist too, but this variation in the switching frequency makes the filtering of the ripple components in the converter's input and output waveforms more difficult [17].

Figure 2.1: Basic dc/dc converter topologies. (a) Buck Converter & (b) Boost Converter

In many applications, it is considered desirable to incorporate a transformer into the switching converter. The main reason for this incorporation is to provide galvanic isolation between the input and the output of the converter. Adding a transformer into the switching converter not only offers isolation, but also the possibility to choose the value of the voltage and current in the secondary side by the proper choice of the turns ratio. This can eventually help minimizing the voltage and current stresses imposed on the transistors and diodes [18]. Moreover, multiple dc outputs can also be created, by simply adding multiple secondary windings and secondary-side circuits. There are several

ways of adding transformer isolation into a dc/dc converter and almost all the isolated converters are isolated versions of the non-isolated ones. For example, the full-bridge, half-bridge, forward, and push-pull converters are commonly used isolated versions of the buck converter. Similar isolated versions of the boost converter are also known (by inverting the source and load of the buck-derived isolated converters, transformer isolated boost converters can be derived). The flyback converter is an isolated version of the buck-boost converter and isolated versions of the SEPIC and  $\acute{C}uk$  converter are also well known.

Non-isolated converters, are very common these days and widely used in computers, telecommunication systems, portable electronics and many other applications. They are usually built directly on the motherboard and very close to the load, hence they are also called point-of-load (POL) converters. They are usually constructed with discrete components and, thus, operate at a lower frequency around 100-600kHz to achieve a decent efficiency. In order to achieve higher power density in POL converters, significant increase in the switching frequency and level of integration need to be achieved. Therefore, there is currently a lot of research conducted in industry to develop a high-frequency integrated POL converter [19]. Isolated dc/dc converters are also widely used in many applications and depending on the power level of the application different topology is selected, i.e. flyback and forward are usually selected for low power applications while half-bridge and full-bridge are used for medium or high power applications.

These converters can also be categorized based on whether there is a direct path between the input and the output terminals during at least one switching state, known as direct converters, or there is no direct path between the terminals in any state, known as indirect converters [20]. It is quite noteworthy that the presence of transformers or additional filters does not reverse the above characteristic. Examples of direct topologies include the buck, boost, forward while examples of indirect topologies include the buck-boost, the  $\acute{C}uk$ , the flyback. The direct topology is preferred for high power density applications because the direct connection between the terminals allows part of the electrical energy that must be transferred from the input to the output, to be transferred without having to be stored first in the passive components.

#### Soft-Switching PWM converters

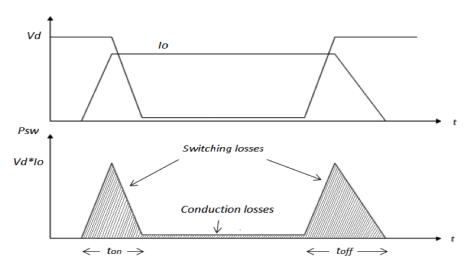

Integral part of the dc/dc converters are the semiconductor devices that are used as switches. These devices are followed by conduction and switching losses that usually dominate the other converter losses. Switching loss constitutes a significant source of inefficiency of the converters and they will be studied separately later on in this thesis. Although, the turn-on and turn-off transitions of the semiconductor devices, nowadays, are in the range of nanoseconds to microseconds, the instantaneous power loss that occurs in the semiconductor devices during these transitions can be very large (see figure 2.4).

The basic PWM converters are hard-switched. They transfer power across their terminals by means of abrupt switching between the turn-on and turn-off states of the semiconductor devices. This hard-switching operation, however, results in significant increase in the switching loss and stress upon the switches, especially at higher frequencies. Therefore, increasing the switching frequency in order to achieve higher power density and at the same time having high efficiency, is limited with these converters. Following the contin-

uously increasing demand for higher power density and higher efficiency, soft-switching PWM converters have developed. Soft-switching is realized by either zero voltage switching (ZVS) or zero current switching (ZCS), causing a notable reduction in the switching losses and stresses compared to the basic PWM converters. In order to achieve the ZVS or ZCS, additional energy needs to be stored in the topology [21], [22]. This energy usually comes from an auxiliary circuit or by operating the topology in such a way that the additional energy is stored in the already available passive components. In addition, the energy that is stored in the output capacitances of semiconductor devices and in the leakage and stray inductances of the circuit, can also be used to achieve the ZVS or ZCS.

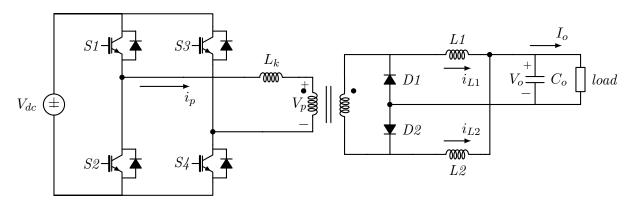

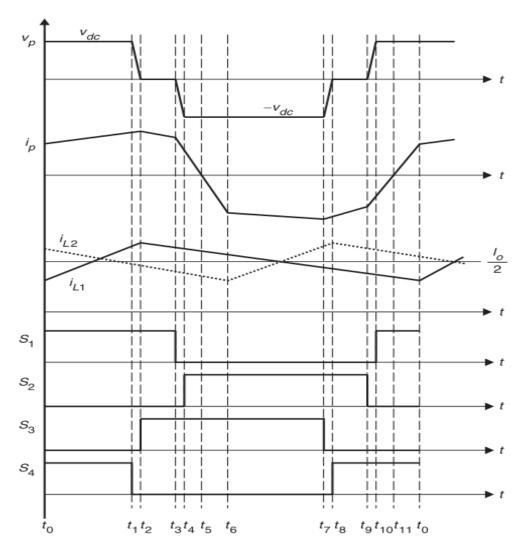

The full-bridge PWM converter is one of the most widely used circuits in high-power applications and through the years different ZVS and ZCS techniques have been proposed in order to improve the performance of the converter [23–29]. The background of this thesis is a high power density, high efficiency application where a full-bridge converter with the phase-shift technique to achieve ZVS and control the output voltage at constant frequency with a current doubler rectifier (CDR) at the secondary side of the transformer to improve the performance of the converter, shown in figure 2.2, was developed.

Figure 2.2: A full-bridge converter with a CDR at the transformer secondary side

The principle behind this operating mode of the full-bridge PWM converter is to utilize the circuit parasitics, which at higher frequencies become very important for the converters performance, in order to achieve ZVS for all the switching devices. More specifically, it utilizes the leakage inductance of the transformer and the output parasitic capacitance of the power switches to achieve zero volt turn-on switching transitions. As already mentioned above, it uses the phase-shift technique to achieve ZVS. In this technique, the switching transition of the switches in the leg S1 - S2 is delayed (phase-shifted) with respect the switching transition of the switches in the leg S3 - S4, instead of turning on the diagonally opposite switches in the bridge simultaneously, determining the duty cycle of the converter (in figure 2.3 this time shift occurs at intervals t2-t3 between S1, S3 and at t8-t9 between S2, S4).

Looking at figure 2.3, power switches S1 and S4 are turned on before time t1, when S4 is turned off. A dead time interval is then added between the S4 turn-off and S3 turn-on. During that interval, the output capacitance of S4 is charged from 0 to  $v_{dc}$ , while S3's output capacitance is discharged from  $v_{dc}$  to 0. Thus, the S3 can be turned on under ZVS operations at time t2. Likewise, at time t3, power switch S1 is turned off and a dead time interval is added before S2 turn-on. During that interval, the output

Figure 2.3: Key waveforms of the full-bridge dc/dc converter with CDR [30]

capacitance of S1 is charged from 0 to  $v_{dc}$ , while S2's output capacitance is discharged from  $v_{dc}$  to 0, so the S2 can be turned on under ZVS operation. Consequently, in order to ensure the ZVS, the dead time intervals between the S4 turn-off and S3 turn-on, as well as between the S1 turn-off and S2 turn-on, must be enough for the charging/discharging procedure [23].

However, the procedure through which ZVS is achieved for both legs of the bridge is different. For the transistors S3, S4, the energy to charge and discharge the output capacitance of these switches, is provided by the leakage inductance of the transformer plus the output filter inductor. Consequently, the amount of the inductive energy available for ZVS is higher, which makes it easier to achieve ZVS for these switches. On the other hand, for the transistors S1, S2 the ZVS is provided by the resonance between the leakage inductance and the output capacitances of the switches, which causes one of the main drawbacks of this operating mode. In order to ensure the ZVS operation, the energy stored in the transformer's leakage inductance, which is used as the resonant inductance, must be greater than the energy stored in the the output capacitances of the switches, which are the resonant capacitance. Due to the small value of the leakage inductance, the current through it might not be enough to charge/discharge the output capacitance

of the switches during operation of reduced output power. This dependency of the load current might cause the converter to loss the soft-switching characteristic for light loads. In addition, for high switching frequency operation, the parasitic capacitance of the transformer's primary winding should be taken into consideration. This capacitance is added to the resonant capacitance, increasing the energy stored in it and eventually, higher energy required to be stored in the leakage inductance in order to ensure ZVS. A more detailed explanation of the converters operation and possible solutions to increase the ZVS range by utilizing the magnetizing inductance of the transformer are given in [23], [28], [30].

The full-bridge phase-shifted dc/dc converter is considered capable of achieving high efficiency while the ZVS allows operation with reduced switching losses and stresses on the devices, which allows the increase of the switching frequency for improved power density. It is characterized by relative simplicity and offers a constant frequency operation, along with other benefits such as low EMI and the integration of the parasitic components in the power circuit. However, it requires an optimized transformer design regarding the parasitic capacitance of the windings because it can affect the performance of the converter.

## 2.2 Power Density

High power density is considered, nowadays, a critical and favorable system feature for many applications, i.e. in telecommunicantion power supplies [31] and in industrial drives [32]. The increase in power density of power electronic systems was made feasible, so far, by developments in the semiconductors field, namely by semiconductors that can operate at higher switching frequencies and generate less power loss. However, before discussing further the increase in power density, the concept of power density itself must first be defined. The power density of a power converter is defined as the ratio of electrical power delivered from the converter to the total volume occupied by the converter. Mathematically is given by the equation below:

$$\rho = \frac{P_{out}}{V_{total}} \tag{2.1}$$

where,  $\rho$  is the power density measured in  $[W/m^3]$ ,  $P_{out}$  is the rated or maximum electrical output power of the power converter in [W] and  $V_{total}$  is the total volume of the power converter, including all the components and the coolant used in the converter in  $[m^3]$ .

Power density is a useful figure of merit (FOM) that connects the amount of power, which is being processed or converted in the given volume of the converter. Nevertheless, power density does not take into account the maximum base plate temperature of the converter. Therefore, when converters with base plate are examined, a more meaningful FOM would be considered the thermal density, which does make reference to the heat dissipation related to the base plate area of the module [33].

By the equation 2.1 given above, we can easily conclude that increasing the power density can be achieved by:

1. Increasing the power delivered by the module and/or

2. Reducing the volume of the module for a given power rating.

Increasing the converter's delivered power can be achieved by either increasing its efficiency for a fixed input power, or increasing the switching frequency for a given energy density of the passive components. An increase in the efficiency of the converter implies that the losses in both the active and passive components will be reduced, which can be achieved by utilizing appropriate converter topologies (like discussed in section ??) and techniques that can improve the efficiency of the converter, like soft switching techniques [29], [34]. On the other hand, increasing the switching frequency in a power converter, as already mentioned above, has become possible due to the development of semiconductors but by looking at the equation 2.2 below:

$$P_{out} = E_{cycle} \cdot f_s \tag{2.2}$$

where,  $P_{out}$  is the output power in [W],  $E_{cycle}$  is the energy delivered per switching cycle in [J] and  $f_s$  is the switching frequency in [Hz], we can observe that an increase in the switching frequency can indirectly affect the power density by both increasing the output power for a given energy density of the passive components and decreasing the volume of the power converter by reducing the energy delivered from the power converter per switching cycle.

The energy delivered from the power converter per switching cycle is determined by the volume of the passive components and the topology in which they are being used. These parameters define the energy density of the passive components and by keeping this energy density constant while increasing the switching frequency, the power delivered by the converter can be increased, according to equation 2.2. Alternatively, it can be considered that:

- A higher frequency, in principle, means that the circuit needs to process a proportionally smaller amount of energy during each cycle for a constant amount of output power, resulting in a reduced amount of energy stored in the passive components, and

- The volume of the passive components is mostly determined by the "place" required to store the electromagnetic energy (dielectric or magnetic material) and the space required to establish the electromagnetic fields (inductor windings and capacitor plates).

Therefore, since less amount of energy is to be stored, the sizes of energy storage and transfer components such as inductors, filters, resonant tanks, decoupling capacitors, power transformers, depending on the frequency operation, will eventually scale down as the frequency increases, and the total volume of the converter module will decrease. A more detailed explanation of how the power density can be increased is given by M. B. Gerber in [35].

Passive components are integral parts of most power converters, performing various functions, like energy storage, voltage and current filtering, and they usually occupy the largest volume in the converter module. So, it would be considered justifiable to push the switching frequency as high as possible to achieve a significant decrease in the power density of the converter. However, certain limitations occur at higher switching frequencies, since

an increase in the switching frequency will also increase the losses in the converter and the influence of the parasitic inductances and capacitances become more critical.

Assuming, for simplicity, the piecewise linear approximation for the switching waveforms of a semiconductor device [17] shown in figure 2.4, the average switching power losses due to turn-on and turn-off transitions can be derived by:

$$P_s = \frac{1}{2} V_d I_o f_s (t_{on} + t_{off})$$

(2.3)

Figure 2.4: Piecewise linear approximation for switching waveforms of a semiconductor device [17]

From the equation 2.3 it is shown that the semiconductor device's switching losses are linearly proportional to the switching frequency. Additionally, at some frequency the losses in the magnetic components start to increase faster (passive component's losses tend to increase exponentially with switching frequency) than the value of the inductance decreases, requiring larger cores in order to reduce the losses, while skin and proximity effects will make the use of more spacious winding techniques necessary [36]. Both semiconductor and magnetic losses generate heat in the power converter, creating in that way the interaction between the electrical and thermal designs, since the heat has to be removed from the converter according to the thermal design.

#### Thermal Management

Power density improvement has mainly been driven by the development of semiconductors able to operate at higher switching frequencies and generate lower power loss, resulting in smaller size of heat sinks. Increasing the switching frequency of the semiconductors results in a reduced amount of energy stored in passive components, leading to smaller-size passives. Consequently, the converter volume and the surface areas available for the cooling of the components are reduced. However, this growing demand for higher power density has pushed the operating temperature of the components to increase at the point where the components approach their thermal limits and, for the given generation of semi-conductors, the power electronics engineers have turned their focus on the component's spatial layout and thermal management for further increase in the power density [37].

Passive components, which are considered low heat density components, come from various manufacturers and in different shapes and sizes. Heat removal from such components is based on their separate heat management embedded in the component itself and on the existence of substantial amount of air around the components (convection heat removal). When these conventional pre-manufactured components are used on single PCBs like is usually done in commercial dc/dc converters, a significant percentage of the volume is occupied by air [33]. This results in an inefficient thermal design and will eventually prevent the increase in power density.

In order to achieve higher power densities while reducing the amount of air around the passive components, heat removal from the power converters has to be based on conduction heat transfer. In many applications, though, the common cooling techniques, such as heat sinks, will no longer be capable of meeting the thermal management demands and more advanced and efficient thermal techniques will be required to effectively remove the heat from the power converters. There are many technologies emerging but the most promising are considered to be the liquid cooling, refrigeration and spray cooling [38]. On the other hand, there are applications, like lighting, automotive, where using cooling fans are not preferred. In these cases the passive components are forced to operate close to their thermal limits and in order to prevent any failures, sacrifices regarding the system power density through allowing more air the components have to be made. Moreover, C. Xiao in [39] proved that pursuing higher frequency alone does not necessarily lead to higher power densities and efficiencies, but there are compromises that should be made depending on the application.

The low power densities of the commercial power electronic converters, caused by the: the poor 3D converter volume utilization and the non-optimized thermal management, has led the thermal management, three-dimension spatial layout and passive components integration technologies to become more and more important factors in reaching higher converter power density and longer converter lifetime. For this reason, a lot of research has been conducted in the past years on these fields, showing significant power density improvements [35], [40], [41], [42], [43] (see figure 2.5). However, the manufacturers of commercial power electronics are not willing to adopt these new technologies, mainly due to their complexity and high cost.

Finally, the converter application and the power level have a significant influence in the power density of the power electronic products. In general, lower power converters present a lower power density than converters designed for higher power applications. The reason for this is that the control circuit, measurements, auxiliary power supplies and semiconductor devices occupy a larger percentage of the overall volume in low power converters, while their size does not increase significantly with the power level. In example, circuitry within a switching control device, nowadays, is small and power dense, and while the semiconductor devices and their control constitute the primary electrical elements of a power converter module, power density isn't significantly affected by either. On the other hand, at higher power levels the thermal management elements occupy a smaller portion of total converter volume as the higher power converters are cooled by forced convection, which is more effective than the natural convection cooling typically used in the lower power converters.

Figure 2.5: Power density of the converters versus power level in industry and research communities [42]

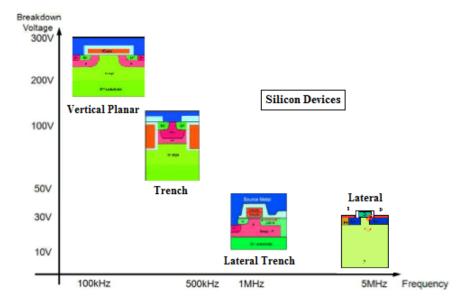

#### 2.3 Semiconductors for High Frequency Applications

#### Evolution of Power Semiconductors

Achieving higher power densities and higher level of integration has been made possible so far by the improved semiconductors. Until now, silicon-based power devices have managed to monopolize the power electronics and power system applications, by offering multiple advantages to power electronics designers. Specifically in power electronics, there are numerous silicon-based devices that are widely used, such as diodes, thyristors, insulated-gate bipolar transistors (IGBTs) and metal-oxide-semiconductor field-effect transistors (MOSFETs). Power MOSFETs appeared in 1976 as alternatives to bipolar transistors and, within the past decades, they became very popular in power supplies community and in many other applications, due to their superior performance over the other devices. During these years, in order to improve the switching performance and to effectively serve in various applications, different silicon-based MOSFET structures (figure 2.6) have been introduced achieving great improvements in figures of merit (FOMs) [44].

However, although silicon MOSFETs are suitable for high switching frequency appli-

Figure 2.6: Semiconductor device structures [44]

cations, they are considered inadequate for high voltage applications. They suffer from high conduction losses due to their high on-state resistance  $(R_{DS,on})$ , which increases exponentially with the blocking voltage. As the need for devices with higher voltage and switching frequency capability is growing, silicon-based power devices suffer from limitations due to some inherent material properties, such as low bandgap energy, small critical electric field, low thermal conductivity, and switching frequency limitations [45]. Due to these limitations, the use of silicon-based devices is considered to start reaching a limit.

#### Wide-bandgap Power Semiconductors

On the contrary, wide-bandgap semiconductors, such as silicon carbide (SiC) and gallium nitride (GaN), are considered promising to solve these issues. Their advanced behavior is due to intrinsic material properties and can be seen from a comparison of these parameters [46]:

- Energy bandgap: wide-bandgap semiconductors have wider energy bandgaps ("wider" is usually defined as larger than 2eV) compared to silicon devices, resulting in a much lower leakage current and consequently in higher operating temperatures.

- Critical electric field: wide-bandgap semiconductors have higher critical electric field, which allows a significant reduction in the blocking layers thickness while containing higher doping concentrations, resulting in significantly lower on-resistance.

- *Electron saturation velocity*: wide-bandgap semiconductors have higher electron saturation velocity, which leads to higher operating frequencies.

- Thermal conductivity: indicates how easily the dissipated power can be extracted from the device. Especially SiC has high thermal conductivity, which leads to better heat spreading and allows operation in higher power densities.

For these reasons, the wide-bandgap devices have received much attention for the past several decades. Silicon carbide device technology has gone from research to commercial

| Parameter                                                                                                  | Si   | 4H-SiC | GaN  |

|------------------------------------------------------------------------------------------------------------|------|--------|------|

| Energy bandgap, $E_g(eV)$                                                                                  | 1.12 | 3.2    | 3.4  |

| Critical electric field, $E_c(MV/cm)$                                                                      | 0.25 | 2.2    | 3    |

| Saturated drift velocity, $V_{sat}(10^7 \text{ cm/s})$<br>Thermal conductivity, $\lambda \text{ (W/cm-K)}$ |      | 2.0    | 2.5  |

|                                                                                                            |      | 3.8    | 1.3  |

| Electron mobility, $\mu \ (cm^2/{\rm Vs})$                                                                 | 1350 | 950    | 1000 |

| Permittivity, $\varepsilon_r$                                                                              | 11.9 | 10     | 9.5  |

Table 2.1: Summary of key semiconductor material properties

production with the launch of Schottcky diode by Infineon [47] and Cree [48] since 2001. On the other hand, gallium nitride device technology has gone commercial quite recently, by EPC that provides devices with breakdown voltage up to 200V and by Transphorm with 600V devices. There are more companies working on their development, such as IR, MicorGaN, Panasonic and others. Table 2.1 summarizes the key material properties for SiC and GaN compared to Si [49].

The best way to convert these material parameters into a comparison of device performance is by calculating the best theoretical performance that could be achieved in each of these candidates. For that reason, different FOMs have been proposed over the years [44]. In example, the specific on-resistance  $(R_{DS,on})$  is considered an important parameter since it indicates how much resistive loss the device generates in the conduction mode and is calculated from equation 2.4 given below:

$$R_{DS,on} = \frac{4V_B^2}{\varepsilon \mu_n E_c^3} \tag{2.4}$$

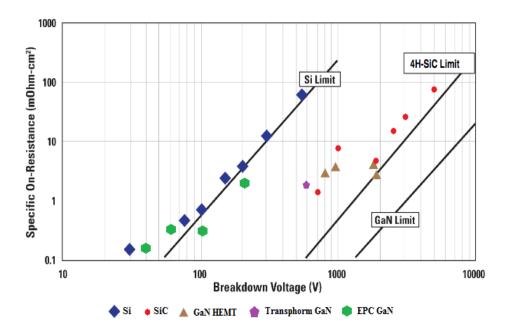

where,  $V_B$  is the breakdown voltage,  $\varepsilon$  is the permittivity,  $\mu_n$  is the electron mobility and  $E_c$  is the critical electric field. It can be seen from the above equation that  $R_{DS,on}$  is reversely proportional to critical electric field and since the  $E_c$  of SiC and GaN are 8-9 and 12 times higher than that of Si, respectively, one can easily understand the important advantage of using wide-bandgap semiconductors. Figure 2.7 shows a comparison of the specific on-resistance versus breakdown voltage for Si, SiC and GaN devices.

However, the specific on-resistance versus the breakdown voltage is considered adequate only in low frequencies where the device loss is dominated by its conduction loss. When investigating the use of a device in high frequencies, designers prefer to use another FOM that is the product of gate-drain charge  $(Q_{qd})$  and on-resistance  $(R_{DS,on})$ .

#### Emergence of Gallium Nitride HEMTs

Gallium Nitride transistor has emerged as possible candidate to replace silicon and even silicon carbide devices in various power conversion applications. GaN devices offer potential benefits for high frequency power conversion, due to their material properties listed in table 2.1 above. Their operation is similar to the MOSFETs, as it is based on a conductive path formed by a channel of electrons between the drain and the source, which is controlled by the gate-source voltage. Currently, there are no available homoepitaxial GaN waffers yet, most technologies are based on a GaN epitaxy on either SiC, sapphire

Figure 2.7: Comparison of Si, SiC and GaN specific on-resistances [50]

or silicon wafers, which basically constitutes an important disadvantage of GaN devices over SiC MOSFETs. Although, SiC substrates have much higher thermal conductivity than Si ones, the majority of GaN transistors intended for power electronics use are built on a Si substrate, in order to simplify fabrication and reduce cost. However, GaN-on-SiC HEFTs are also examined and a review can be found in [51].

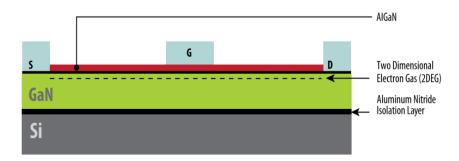

A typical structure of a GaN device is shown in figure 2.8. An Aluminum Nitride (AlN) transition layer that isolates the GaN from the Si substrate, exists on top of the Si substrate. The next layer is the base of the GaN transistor, a thick layer of highly resistive un-doped GaN, and on top of that lies a thin layer of highly conductive AlGaN. The combination of the thin AlGaN layer on top of a high quality GaN surface creates a two-dimensional electron gas (2DEG) layer, which acts as the electron channel, and makes the GaN transistor a high electron mobility transistor. Drain and source electrodes form an ohmic contact with the underlying 2DEG, which creates a short circuit between them until the 2DEG layer is depleted by the gate electrode that is placed on top of the AlGaN layer.

Figure 2.8: The basic GaN transistor structure [52]

Furthermore, at the heteroepitaxial devices the lattice mismatch and thermal coefficients of expansion mismatch between the substrate and the GaN layer can lead to stress of

the materials. In order to achieve material matching between the substrate and the GaN layer, the AlN layer is used. However, this layer makes the manufacturing of vertical devices not possible and, thus, the main device design of a GaN is a lateral FET structure. On the other hand, lateral structure requires large chip areas in order to achieve high breakdown voltages, which is translated into high costs and manufacturing difficulties, making them unsuitable for high voltage applications.

The GaN transistor can be categorized, depending on its physical structure, as operating in either enhancement mode or in depletion mode. The most notable difference between the two is that the enhancement mode GaN is a normally-off device that requires a positive voltage to turn-on, while the depletion mode GaN is a normally-on device that requires a negative voltage to turn-off. Their difference is that at the enhancement mode structure, the gate electrode is placed properly on top of the AlGaN layer so that a depletion region is formed underneath it, instead of the 2DEG layer. The requirement of negative voltage in order to turn-off is a significant disadvantage for the normally-on devices.

Currently, for low voltage applications, there are two types of GaN transistors available on the market: the depletion mode GaN transistors from International Rectifier (IR) [53] and the enhancement mode GaN transistors from Efficient Power Conversion Corporation (EPC) [54]. Until now, the application of the enhancement mode GaN transistor is limited due to critical driving issues as addressed in [55], [56]. The enhancement mode GaN transistor has gate voltage limits between -5V to 6V and it is designed to achieve maximum performance with a gate voltage between 4.5-5V. This leaves a very small margin for safe operation and a quite demanding gate driving design need to be considered. On the contrary, the depletion-mode GaN transistor is preferred due to simple and safe gate drive, since it has gate voltage limits between -10V to 6V and it is designed in such a way so that the device is driven on at 0V and driven off at -3.3V. However, this means that both positive and negative power supplies are needed for the driver.

A lot of research has been conducted the past years regarding the low voltage GaN transistors showing significant improvements for the point of load (POL) converters. D. Reusch presented a 12V, 20A, 2MHz converter with an efficiency of 83% and power density  $750W/in^3$  doubling the power density of POL converters until that time [56]. S. Ji demonstrated three 12V to 1.2V POL modules in [55] achieving even higher power densities than before: a single phase 20A,  $900W/in^3$ , 2MHz converter with enhancement mode GaN transistors, a single phase 10A,  $1100W/in^3$ , 5MHz, and a two-phase 20A,  $1100W/in^3$ , 5MHz using depletion mode GaN transistors. Next, M. Acanski in [57] showed that enhancement mode GaN transistors used for a 12V to 48V boost converter, aimed for PV applications, achieved better performance compared to their Si counterparts for power values over 60W while operating at double the switching frequency. These results prove the significant contribution of GaN devices for low voltage high power density applications, as it combines better efficiency and smaller size components.

For higher voltage rating GaN HEMTs (600V), the depletion mode device technology is considered more mature and its performance has been studied by W. Saito in [58], where a 120W, 1MHz boost converter with an efficiency of 94.2% and a peak voltage of 350V is demonstrated, and by Y. Wu, who presented a 175V to 350V, 300W boost

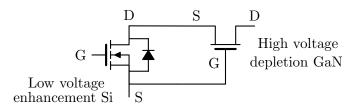

converter at 1MHz with an efficiency of 97.8% in [59]. However, the depletion mode device is a normally-on device, which means that the device is conducting in the absence of applied voltage. This requires the driving circuit to be operating before the input voltage is applied on the devices, otherwise a short circuit between the input and the output will happen. In order to use a high-voltage depletion mode GaN transistor in a circuit design, a low voltage Si MOSFET is used to drive the high voltage GaN transistor, which is well known as a cascode structure and helps to generate a normally-off condition from a normally-on device [60].

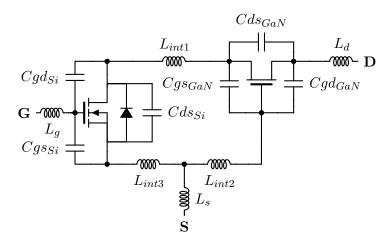

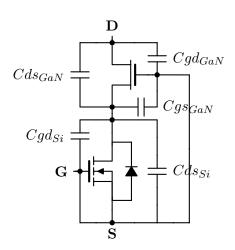

#### 2.3.1 High Voltage GaN-HEMT in cascode configuration

In high voltage depletion mode GaN HEMTs, the driving circuit can operate in a voltage range between -30V to 2V and -5V is required to fully turn-on, which ensures a sufficient safety driving margin. To easily apply the depletion mode GaN HEMT in a circuit design, a cascode structure is used. In this configuration, only the low voltage Si MOSFET is actively controlled while its drain-source voltage acts as a control for the GaN HEMT. Specifically, the GaN HEMT's gate is connected to the Si MOSFET's source, causing its drain-source voltage to become the negative gate-source voltage of the GaN HEMT and provide the negative gate voltage required to pinch off its channel as shown in figure 2.9.

Figure 2.9: GaN HEMT in cascode configuration

The cascode GaN HEMT takes advantage of both Si MOSFET and GaN HEMT. The GaN HEMT blocks high voltage with high switching speed while the Si MOSFET provides more rugged gate-source voltage and more stable threshold. The principle of cascode GaN HEMT operation is quite straightforward. Basically, the on/off state of the high voltage GaN HEMT is being controlled by the on/off state of the low voltage Si MOSFET. During turn-on period, the low voltage Si MOSFET turns on first, and when the gate-source voltage exceeds the threshold, the drain-source voltage which is also the source-gate voltage of GaN HEMT will decrease. Consequently, the GaN HEMT will turn on when the gate-source voltage exceeds the threshold. Similarly, during turn-off period, the Si MOSFET turns off first, and the drain-source voltage increases. GaN HEMT will turn off when gate-source voltage drops below the threshold. Controlling the on/off state of the low voltage Si MOSFET in order to control the on/off state of the high voltage GaN HEMT makes the cascode GaN HEMT compatible with the commercial drivers.

In an inverter application, even if the transistor is turned off, reverse conductivity of the switch is required. In case of the cascode configuration, the reverse current flows through the body diode of the low voltage Si MOSFET and its drain-source voltage becomes the negative value of the diode's forward voltage. Thus, the GaN HEMT gate-source path becomes slightly positive biased resulting in a turn-on of its channel. As a consequence, if the Si MOSFET is turned off, reverse current flows through the MOSFET body diode and reverse direction of the GaN channel [61].

#### Cascode GaN HEMT Applications

The behavior of the high voltage cascode GaN HEMT has already been examined in few publications showing noteworthy results. However, its use still remains in research level. X.Huang in [13] compared the cascode GaN HEMT and a state of the art Si MOSFET while operating on a 380V to 200V, 500kHz hard-switching buck converter. He proved that the low reverse recovery charge and the relatively small output capacitance of the cascode GaN HEMT will lead to smaller transitions times and eventually to an improved efficiency of the buck converter. Moreover, a 1MHz, 300W, 400V/12V LLC resonant converter was used in the same publication to show the advantages of the GaN HEMT over the Si MOSFET. An LLC resonant converter was also used by W.Zhang in [62], in order to compare the performance of the topology when 600V Cascode GaN HEMT and state of the art Si CoolMOS are used. The results showed that the total device loss was improved by 42% with the GaN device, while the total efficiency was improved only by 0.5%. When a LLC resonant converter operates at the resonant frequency, ZVS for the primary switches and ZCS for the secondary switches can achieved. Thus, the GaN HEMT is considered more suitable due to its small output capacitance enabling both low magnetizing current and dead time, which will cause smaller conduction and switching losses. However, it was observed, and it will also be shown in this thesis project, that the turn-on switching loss of the GaN HEMT is quite high and soft-switching is required in high frequency operation.

Next, J. Everts presented in [63] a 76V to 142V boost converter with enhancement mode GaN transistor achieving efficiency of 96.1% at 106W, 512.5kHz, and 93.9% at 97.5W, 845.2kHz.

#### Measurement Challenges

Additionally, the measurements of the electrical quantities are becoming more challenging as the power converters are moving into higher frequency and smaller volume. In order to accurately determine the switching power losses of semiconductor devices, current and voltage measurements need to be taken during the turn-on and turn-off switching transients. However, they are characterized by very high current and voltage rates of change, making the gathering of accurate measurements of their switching behavior a challenge. Therefore, high performance voltage and current measurement equipment has to be used. For measuring high frequency signals, conventional measurement equipment are no longer suitable due to their limited bandwidth and dynamic frequency response limitations. The interferences from high dv/dt or di/dt signals and the intrusion of probes and oscilloscopes into the circuits result in measurement deviations. Consequently, accurate power loss measurements are becoming increasingly difficult as frequency is being pushed higher [39]. A discussion about the measurement equipment and techniques that can be used in higher frequencies will be given in chapter 4 of this thesis.

#### 2.3.2 Switching Losses

The emergence of the wide-bandgap semiconductor devices has made it possible for the power electronics designers to push the switching frequency into much higher levels in order to achieve higher power density and the miniaturization of the power converters. However, increasing the switching frequency is strongly connected with higher switching

losses and thermal stresses on the switching devices that can significantly lower the power efficiency and the overall performance of the converter module.

In order to optimally design a high frequency switching power converter, an estimation of the power losses is considered mandatory before moving to the thermal design and the power device selection. Power devices have a maximum allowable junction temperature that ensures safe operation and in the same time constitutes a limiting factor whether a power device can be used into a specific application or not. However, a direct measurement of the junction temperature is not always possible and for this reason an accurate calculation of the conduction and switching losses of the switching device is required. The conduction losses can be estimated relatively easily, since they require values that are easy to compute or are already known, such as the on-resistance or voltage-drop over the device, rms current through the device and duty cycle. On the contrary, the switching losses are often hard to estimate or they require lots of time consuming measurements. Consequently, an accurate loss model is required in order to investigate the performance of a circuit.

There is an abundance of publications dealing with loss models, each achieving unique balance between accuracy and simulation time. As discussed in [64], the loss models can be distinguished in three main types: the physics-based model, the behavior model and the analytical model.

- Firstly, the physics-based models require the physical parameters of the device and the circuit in order to accurately calculate the device losses by utilizing finite element analysis (FEA) tools. However, it is time consuming and more important is the fact that the designers don't know the exact parameters of the device.

- Secondly, the behavior models use the device behavior model, provided by the vendors, for calculating the device losses by using Pspice or SABER simulation tools. Its simulation speed is faster than the physics-based model and it presents a sufficient balance between accuracy and simulation time [65].

- Finally, analytical models are math based and the loss expressions are derived by the equivalent circuits during each step of turn-on and turn-off transitions of the device. It is the fastest method and it is considered suitable for data processing, but they lack in accuracy.

Using loss models, many design parameters and components can be compared in order to achieve a design with the optimal combination of efficiency and cost. From the three categories previously described, analytical models are usually much preferable when designing a converter due to the simplicity, the suitability for parametric analysis, and the small simulation times.

The most simple analytical loss model uses piecewise linear waveforms for the switch turn-on and turn-off transitions (figure 2.4). However, as the switching frequency increases, parasitic inductances resulting from the Printed Circuit Board (PCB) layout and device package start to influence the switching performance more and more as they may oscillate with the parasitic capacitances of the switching device. Therefore, neglecting the influence of the parasitic elements is no longer tolerable, as they extend the switching times and the oscillations will induce excessive voltage and current stresses on the switch,

causing destructive results. In order to improve the accuracy of the analytical model, the parasitic elements of the device and the circuit need to be taken into consideration.

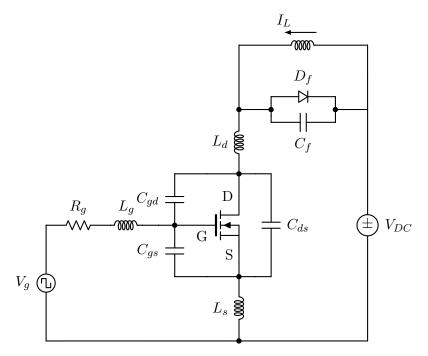

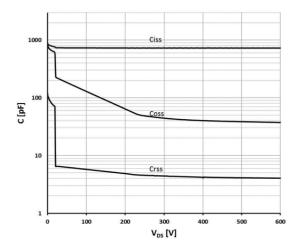

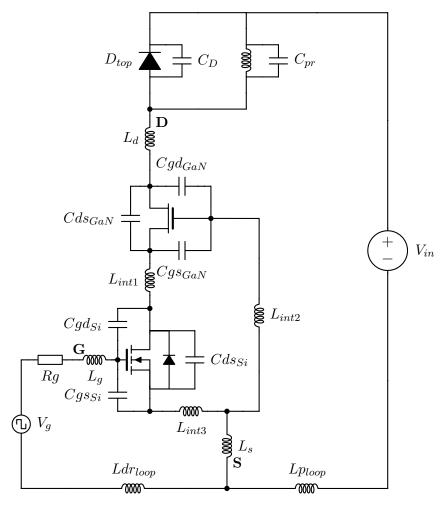

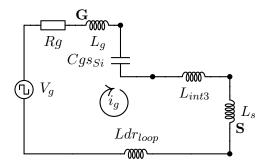

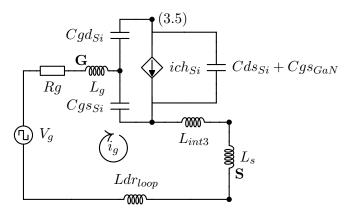

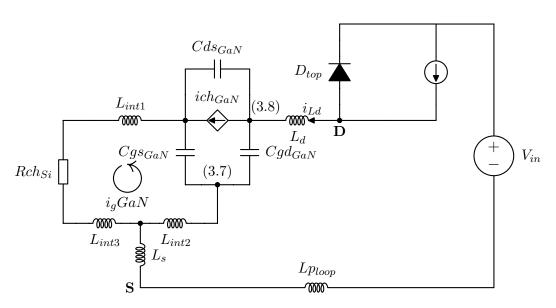

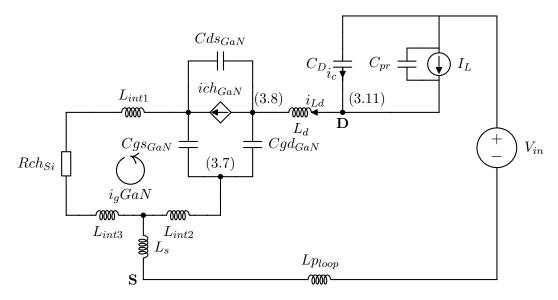

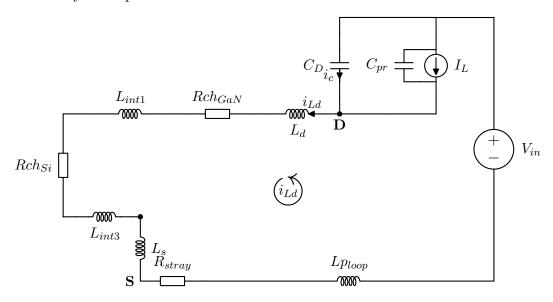

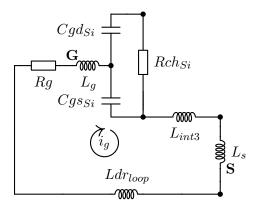

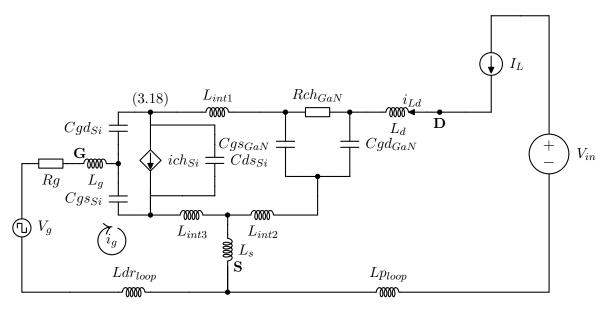

## MOSFET Switching Characteristics and Influence of the Parasitic Elements

A power MOSFET is mostly used in the literature in order to investigate the influence of the parasitic elements and the nonlinearity of the device capacitances in the switching performance [64], [66–71]. However, the definitions for the switching characteristics are general and they can also be used for other switching devices. The switching behavior of the power MOSFET is tested under the condition of clamped inductive load and a typical example of such load is the double-pulse tester (DPT) (figure 2.10). At the end of the first pulse and beginning of the second pulse measurements of the gate-source voltage  $(V_{gs})$ , drain-source voltage  $(V_{ds})$  and drain current  $(I_d)$  can be taken in order to characterize the device's switching transients. The main goal of this section is not to explain in detail the operation of the power MOSFET but to give a briefly description of the turn-on and turn-off transitions and the influence of the parasitic elements in each one of them.

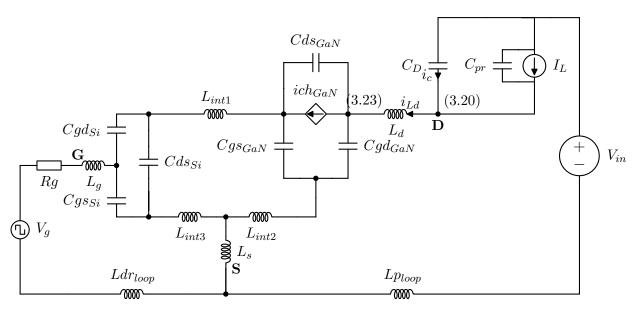

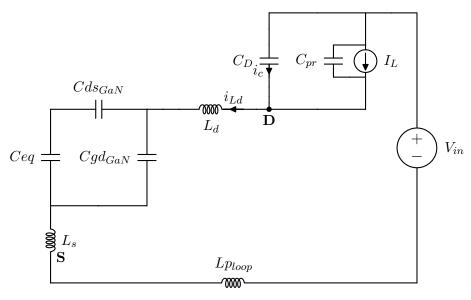

Figure 2.10: Double-pulse Tester schematic including the parasitic elements

#### Turn-on Switching Transient

The turn-on transition of the MOSFET is usually divided into four phases. In this section, the influence of the parasitic elements in each phase will be presented by a few equations. For more detailed reading, the reader is highly recommended to refer to the references mentioned above.

#### Phase 1: turn-on delay time

The gate voltage  $(V_{dr})$  is applied to the gate and the input capacitance  $(C_{iss})$  of the MOSFET is being charged. The input capacitance is a combination of the  $C_{qs}$  and  $C_{qd}$

and along with the gate resistance  $(R_g)$  determine the time constant of the gate voltage's increase. Since the  $C_{gs}$  is the biggest part of the input capacitance, an increase in the  $C_{gs}$  will increase the delay time making the  $V_{gs}$  slower.

The parasitic inductance  $L_g$  is usually neglected from the analytical models, as it is minimized by placing the gate drive circuit as close as possible to the switch. However, it tends to resonate with input capacitance, causing oscillations to the  $V_{gs}$ , but without really influencing the  $V_{ds}$  and  $I_d$ . The  $C_{gd}$  doesn't play significant role in this phase because it is relatively small compared to  $C_{gs}$  and its value is dependent to the  $V_{ds}$ , which is constant during this phase. This phase ends when the  $V_{gs}$  reaches its threshold value.

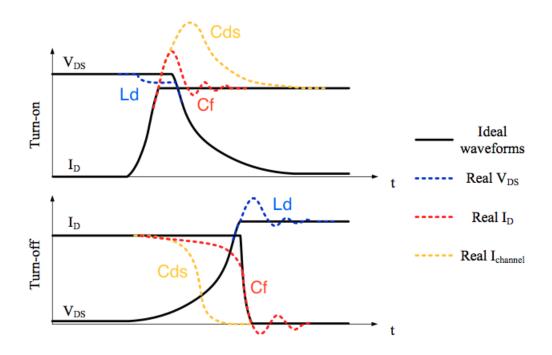

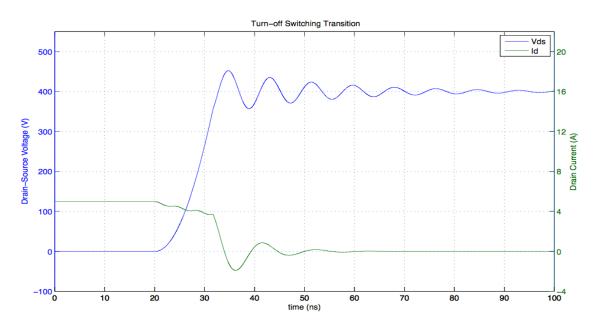

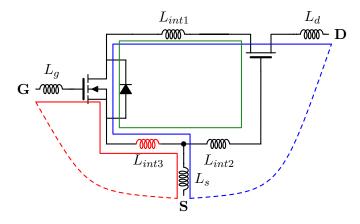

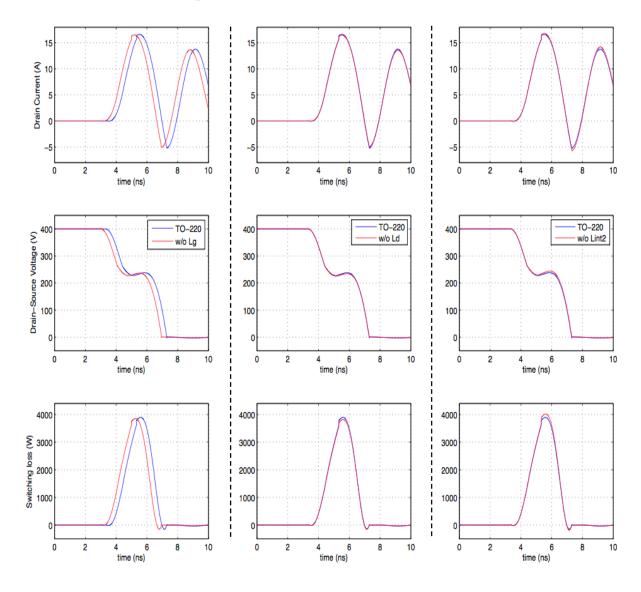

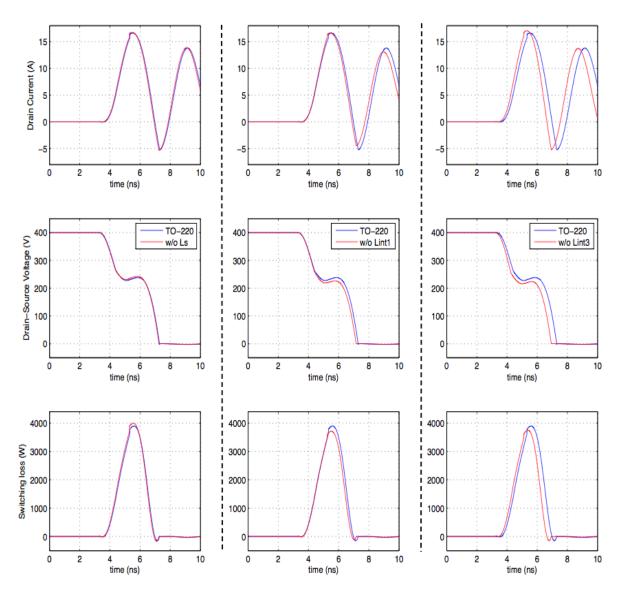

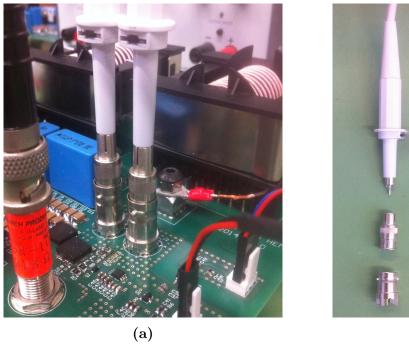

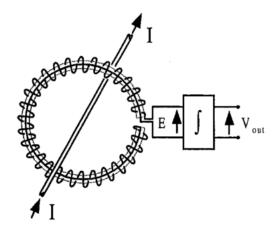

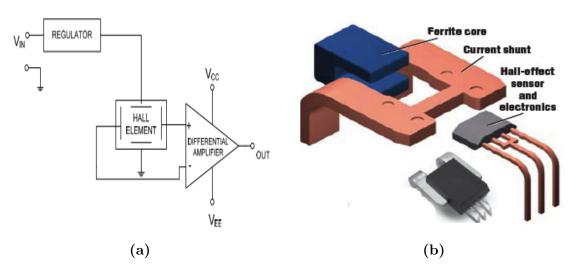

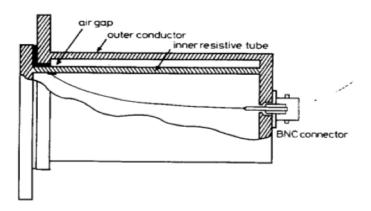

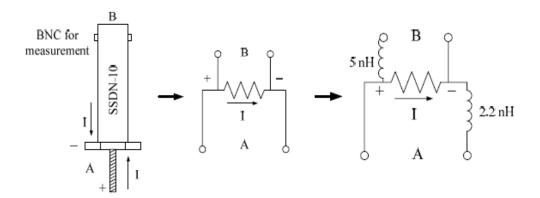

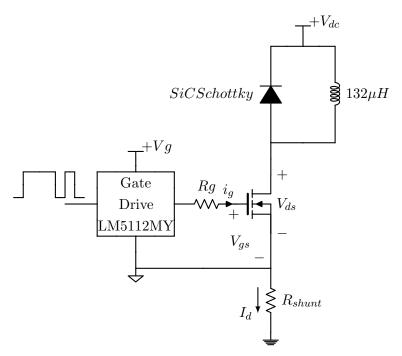

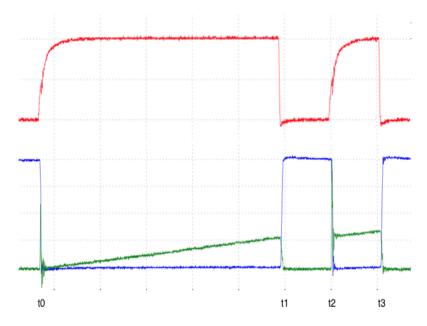

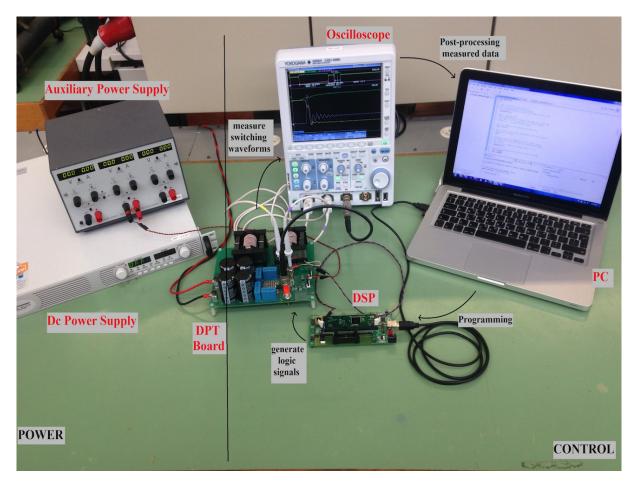

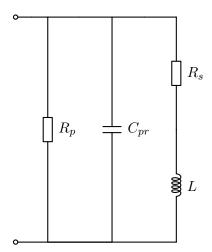

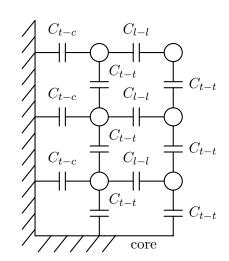

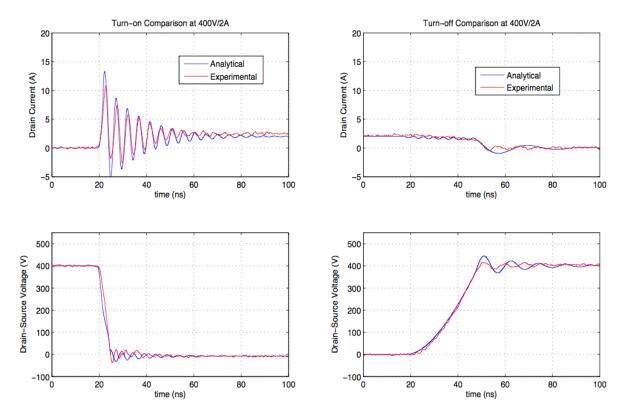

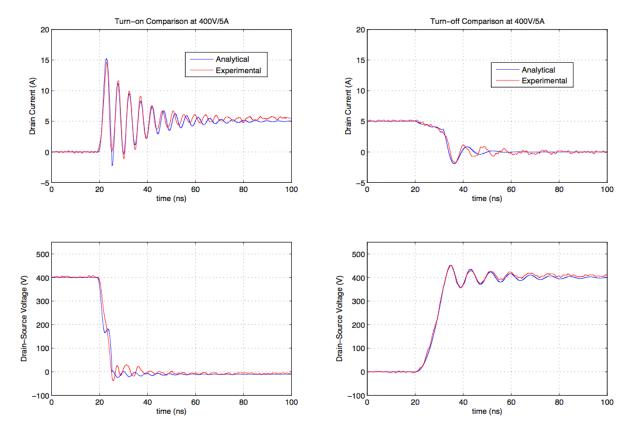

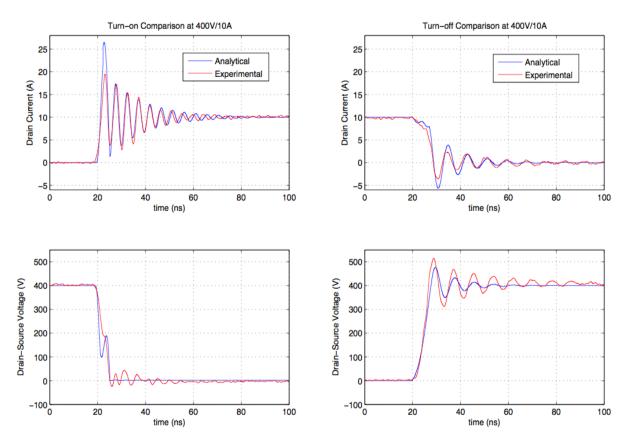

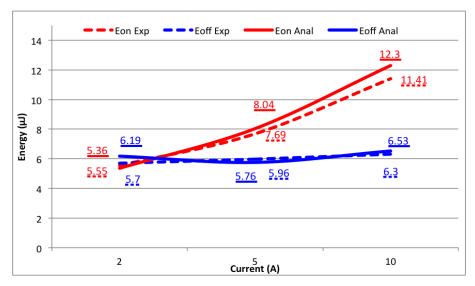

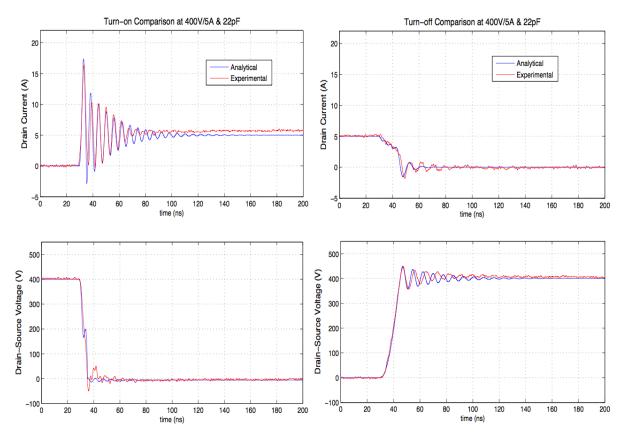

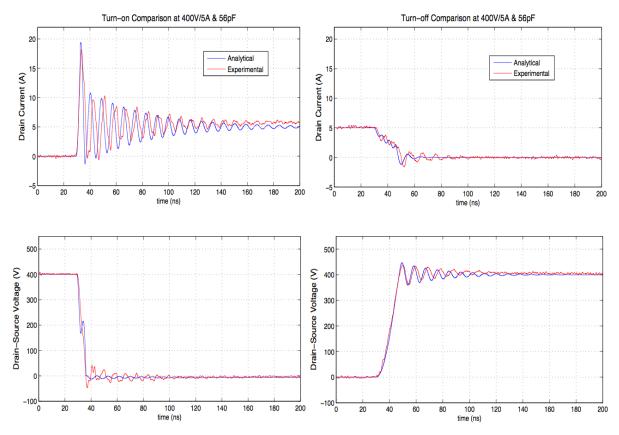

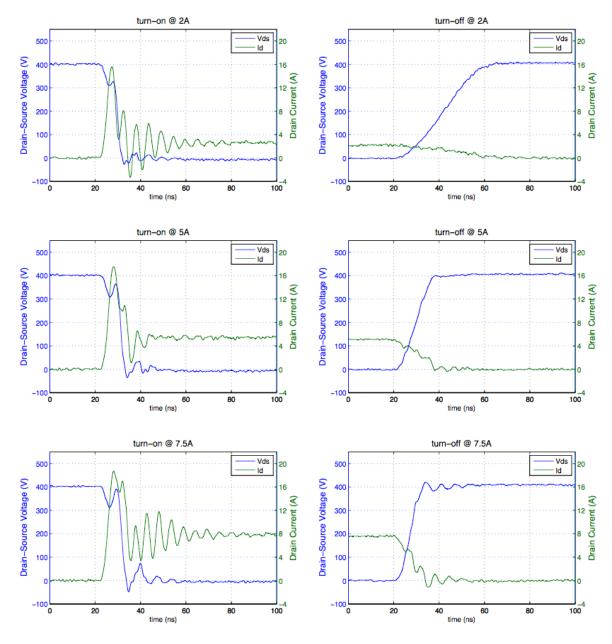

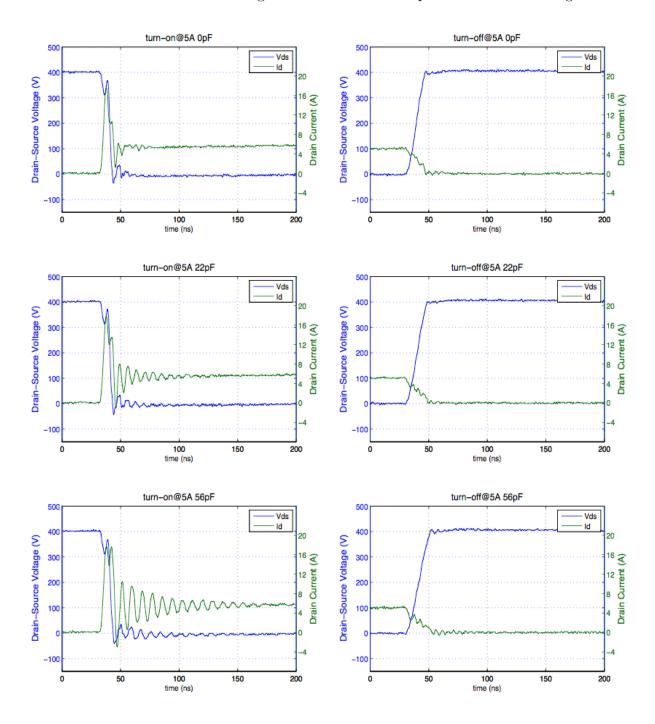

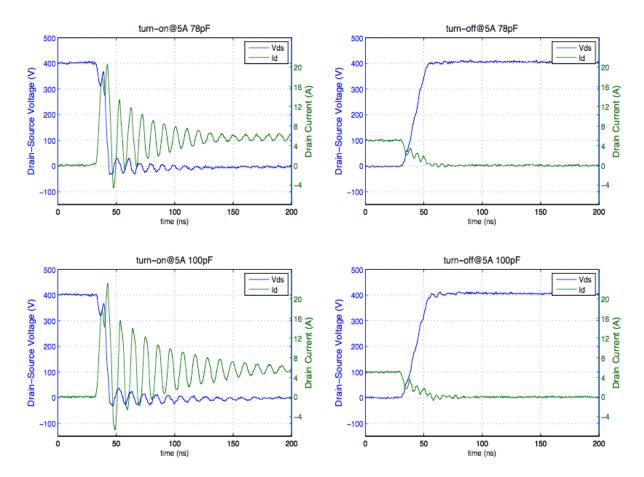

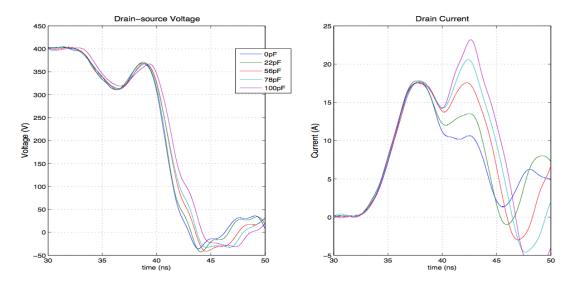

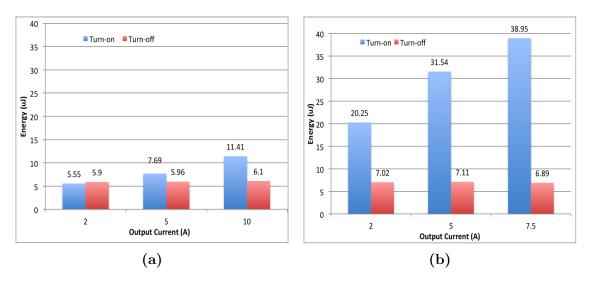

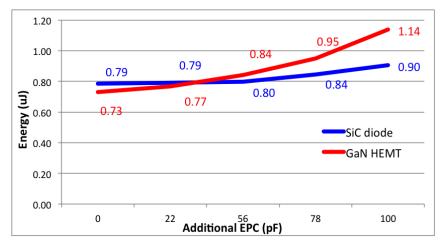

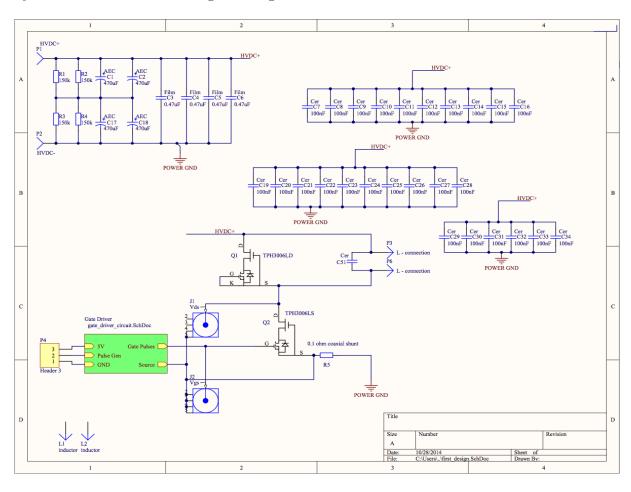

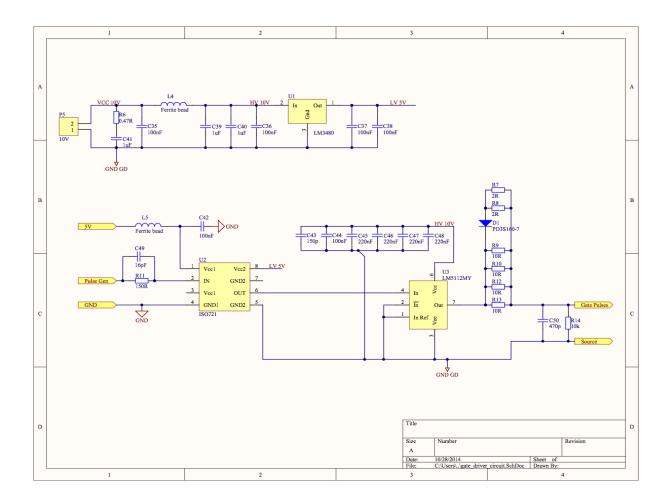

#### Phase 2: current rise period