**Delft University of Technology**

#### **Temporal Noise Reduction in CMOS Image Sensors**

Ge, X.

DOI 10.4233/uuid:386c834b-a534-4c0e-8710-1234cfd6bd9e

Publication date 2021

**Document Version** Final published version

Citation (APA) Ge, X. (2021). Temporal Noise Reduction in CMOS Image Sensors. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:386c834b-a534-4c0e-8710-1234cfd6bd9e

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

#### Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

# Temporal Noise Reduction in CMOS Image Sensors

# Temporal Noise Reduction in CMOS Image Sensors

# Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus Prof.dr.ir. T.H.J.J. van der Hagen, voorzitter van het College voor Promoties, in het openbaar te verdedigen op woensdag 15 september 2021 om 10:00 uur

door

### **Xiaoliang GE**

Elektrotechnisch ingenieur Technische Universiteit Delft, Nederland geboren te Beijing, China Dit proefschrift is goedgekeurd door de promotor:

Prof.dr.ir. A.J.P. Theuwissen

Samenstelling promotiecommissie:

| Rector Magnificus,             | voorzitter                               |

|--------------------------------|------------------------------------------|

| Prof.dr.ir. A.J.P. Theuwissen, | Technische Universiteit Delft, promoter  |

|                                |                                          |

| Onafhankelijke leden:          |                                          |

| Prof.dr. K.A.A. Makinwa        | Technische Universiteit Delft            |

| Prof.dr.ir. G.C.M. Meijer,     | Technische Universiteit Delft            |

| em. Prof.dr.ir. W.M.C. Sansen, | Katholieke Universiteit Leuven           |

| Prof.dr. C.C. Enz              | Ecole Polytechnique Federale de Lausanne |

| Dr.ir. G. Meynants             | Katholieke Universiteit Leuven           |

| Dr.ir. P. Centen               | PeerImaging                              |

| Reserve lid:                   |                                          |

| Prof.dr.ir. L.C.N. de Vreede   | Technische Universiteit Delft            |

Het onderzoek beschreven in dit proefschrift in financieel ondersteund door de Stichting voor Technische Wetenschappen (STW).

*Printed by:* Ridderprint BV|www.ridderprint.nl

Copyright © 2021 by X. Ge

All rights reserved. No part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without the prior written permission of the author.

ISBN: 978-94-6416-807-5

An electronic version of this dissertation is available at http://repository.tudelft.nl/.

# Contents

| 1 | Intr | roduction 1                                         |

|---|------|-----------------------------------------------------|

|   | 1.1  | Background of Low-Noise CMOS Image Sensors 2        |

|   | 1.2  | Challenges and Motivations 6                        |

|   | 1.3  | Context of the Research                             |

|   | 1.4  | Thesis Organization11                               |

|   |      | erences                                             |

| 2 | Ten  | poral Noise Reduction Using pMOS Unity-Gain         |

|   | Sou  | rce Follower and Optimized Column Amplifier 21      |

|   | 2.1  | Introduction                                        |

|   | 2.2  | Sensor Architecture                                 |

|   |      | 2.2.1 Pixel Structure                               |

|   |      | 2.2.2 Column Amplifier Structure                    |

|   |      | 2.2.3 Implementation Details                        |

|   | 2.3  | Experiment Results                                  |

|   | 2.4  | Conclusions                                         |

|   | Refe | erences                                             |

| 3 |      | poral Noise Analysis and Measurement of n-          |

|   | Тур  | e and p-Type Pixels with CMS Technique 33           |

|   | 3.1  | Introduction                                        |

|   | 3.2  |                                                     |

|   |      | 3.2.1 Noise Sources of Pixel                        |

|   |      | 3.2.2 CMS Operation and Noise Reduction Effect . 38 |

|   | 3.3  | Noise Calculation with CMS Technique 40             |

|   | 3.4  | Noise Measurement with CMS Technique 46             |

|   | 3.5  | Conclusions                                         |

|   | 3.6  | Discussion                                          |

|   | Refe | erences                                             |

| 4 | Ten  | ıporal  | Noise Reduction Using Programmable-Gain      |

|---|------|---------|----------------------------------------------|

|   | Am   | plifier | and Digital CMS Reference-adaptive ADC 55    |

|   | 4.1  | Introd  | luction                                      |

|   | 4.2  | Senso   | or Architecture                              |

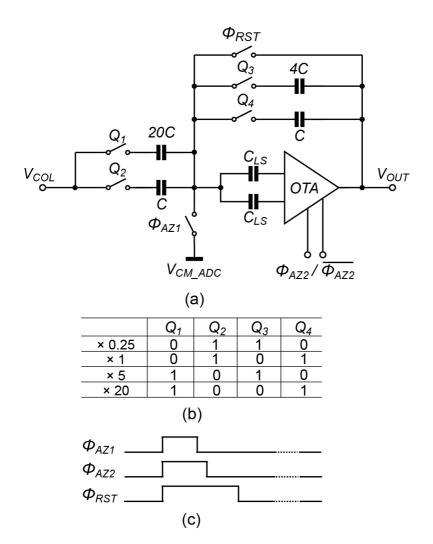

|   | 4.3  | Analo   | g-Front-End Design59                         |

|   |      | 4.3.1   | Noise Analysis of thin oxide vs. thick oxide |

|   |      |         | layer MOS devices                            |

|   |      |         | Analog-front-end Circuit Implementation 60   |

|   | 4.4  | -       | 1 CMS ADC Design                             |

|   |      |         | Concept of Proposed ADC                      |

|   |      |         | Coarse Phase Conversion                      |

|   |      |         | Fine Phase Conversion                        |

|   |      | 4.4.4   | Silicon realization                          |

|   | 4.5  | Measu   | arement Results                              |

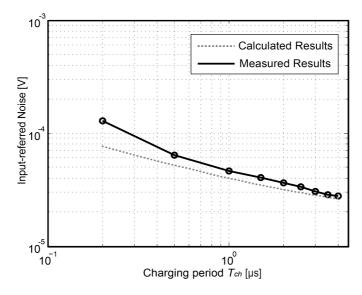

|   |      | 4.5.1   | AFE and ADC Measurement Results 78           |

|   |      | 4.5.2   | Sensor Temporal Noise Measurement Re-        |

|   |      |         | sults                                        |

|   |      |         | Performance Discussion                       |

|   | 4.6  | Concl   | usions                                       |

|   | Refe | erences | 8                                            |

| 5 | Ten  | iporal  | Noise Reduction Using Gm-Cell-Based Pixel    |

|   | and  | Perio   | d-Controlled Variable Conversion Gain 91     |

|   | 5.1  | Introd  | luction                                      |

|   | 5.2  | Opera   | ting Principle                               |

|   |      | 5.2.1   | Concept of Gm-Cell-Based Pixel 94            |

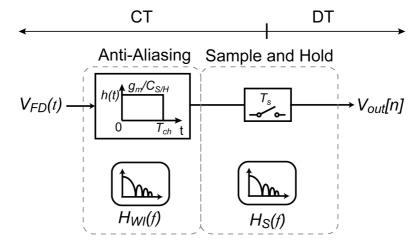

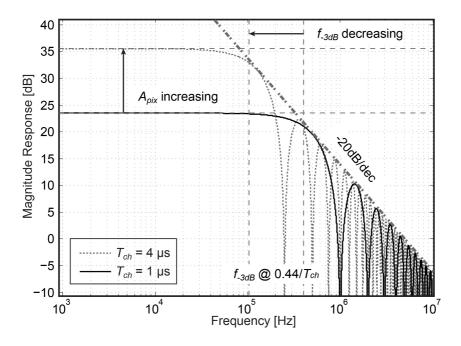

|   |      | 5.2.2   | Periodic Filtering Model of the Charge Do-   |

|   |      |         | main Sampling                                |

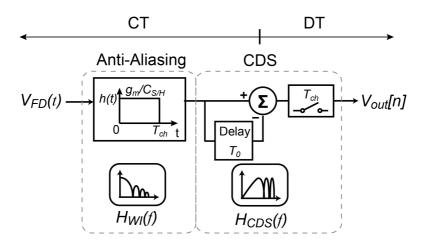

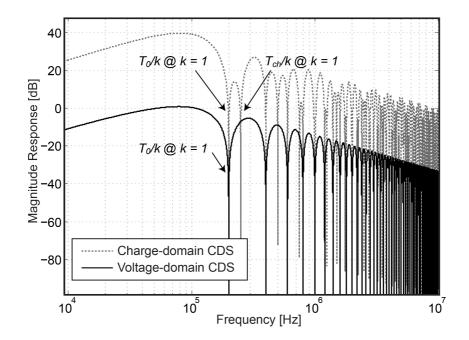

|   |      | 5.2.3   | Periodic Filtering Model of the Charge Do-   |

|   |      |         | main CDS                                     |

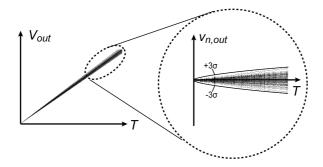

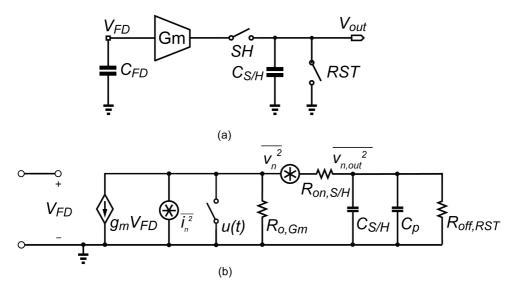

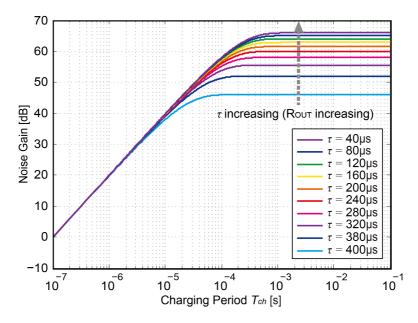

|   | 5.3  | Noise   | Analysis of a Gm-Cell-Based Pixel 99         |

|   |      | 5.3.1   | Nonstationary Noise Theory Analysis 100      |

|   |      | 5.3.2   | Equivalent Noise Model and Noise Gain102     |

|   |      | 5.3.3   | Noise Model of Charging Phase                |

|   |      | 5.3.4   | Noise Model of Discharging Phase             |

|   |      | 5.3.5   | Overall Input-Referred Noise                 |

|    | 5.4  | Circuit and Sensor Implementation         | 114        |

|----|------|-------------------------------------------|------------|

|    |      | 5.4.1 Pixel and Auxiliary Circuits Design | 114        |

|    |      | 5.4.2 Pixel Operating and Timing Diagram  | 117        |

|    |      | 5.4.3 Silicon Realization                 | 118        |

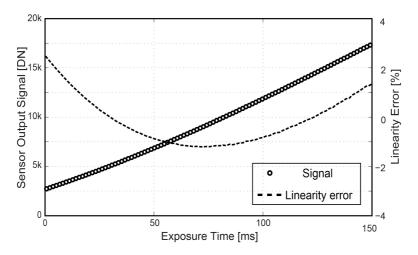

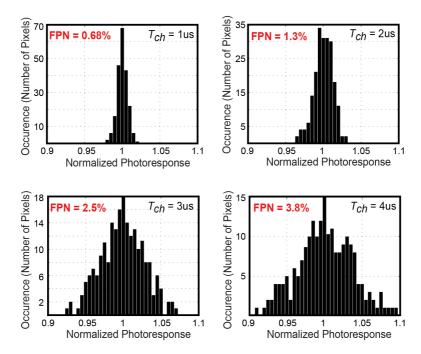

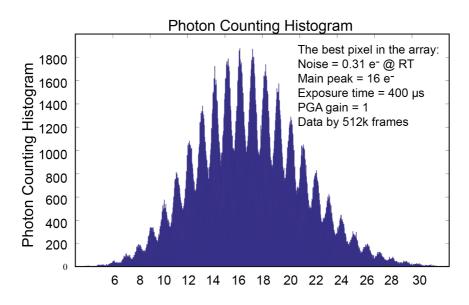

|    | 5.5  | Experiment Results                        | 119        |

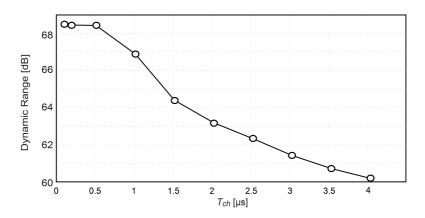

|    |      | 5.5.1 Conversion Gain and Dynamic Range . | 119        |

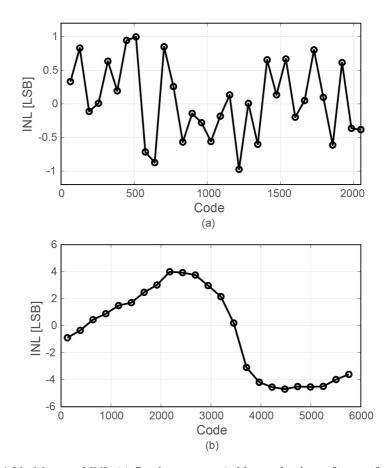

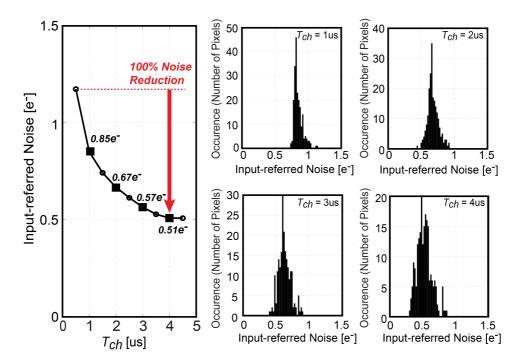

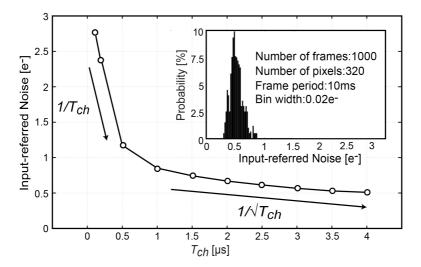

|    |      | 5.5.2 Temporal Noise                      |            |

|    |      | 5.5.3 Linearity and Fixed Pattern Noise   | 122        |

|    |      | 5.5.4 Results Summary                     |            |

|    |      | Conclusions                               |            |

|    | Refe | erences                                   | 128        |

| 6  | Con  | clusions and Future Work                  | 133        |

|    | 6.1  | Conclusions                               | 134        |

|    | 6.2  | Future Work                               | 138        |

|    | Refe | erences                                   | 140        |

| Sı | ımm  | ary                                       | 143        |

| Sa | ımen | watting                                   | 145        |

|    |      |                                           |            |

| A  | kno  | wledgements                               | 147        |

|    |      | wledgements<br>Publications               | 147<br>149 |

# Introduction

# **1.1.** Background of Low-Noise CMOS Image Sensors

Image sensors are the heart of a digital imaging system. They act as the interface between the optical field and the electric field, converting light information into electrical signals. After half a century of evolution, CMOS image sensors (CISs) have been established as a family of indispensable solid-state imaging devices, by virtue of their massive commercialization and consistent technical innovation. The development of image sensors has never stopped in revolutionizing the technology and expanding the application scopes. In the early days, thanks to the growing demand for portable electronic devices, the low-cost and low-power consumption features of CISs helped them gradually overtake charge-coupled-devices (CCDs) in the commercial market. Nevertheless, the performance of conventional CIS were not on-par with CCD sensors, especially in With a series of remarkable technology sensitivity and noise. breakthroughs, in particular the development of pinned-photodiodes (PPDs) [1], CISs have overcome the performance barrier and began to seize niche market that used to belong CCDs. To date, the applications of CISs have gone beyond photography. The demand for photon-efficient imaging systems keeps growing in many emerging applications, such as space and medical imaging, night vision and diverse scientific imaging, calling for the development of CIS with higher sensitivity and lower noise.

Among these niche applications, single-photon imaging is the holy grail of photon sensing. It is an extension of photon-starved imaging where the systematical sensitivity of photon-detection is enhanced to the level that the arrival of individual photons can be spatially resolved. This ultimate precision photon detection can be utilized in a wide range of applications, from biological imaging to remote sensing. For example, in nuclear medical imaging, single-photon imaging is one of the key technologies that enable human positron emission tomography (PET) and single photon emission computed tomography (SPECT) scan equipment. This equipment is of great significance for the diagonsis and therapy of a variety of challenging diseases, such as cancer, Alzheimer and Parkinson [2]-[3].

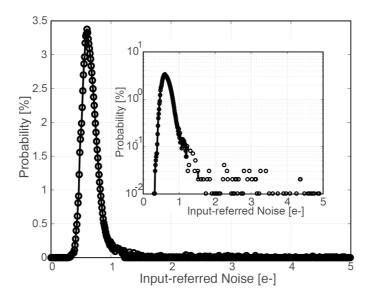

One of the most crucial evaluation parameter of the single photon detection confidence level is the CIS pixel's input-referred noise [5]. Given that the electronic charge detection is a statistical process, the sensor may

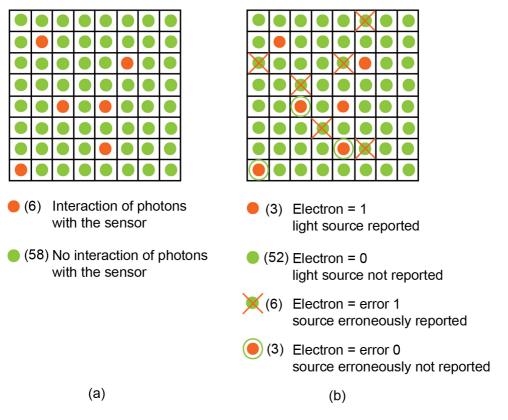

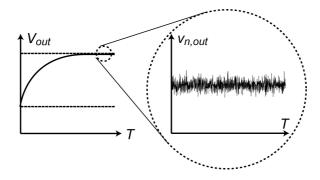

Figure 1.1: Illustration of the consequences of the noisy electronic charge conversion process taking place in the image sensor (redraw from [4])

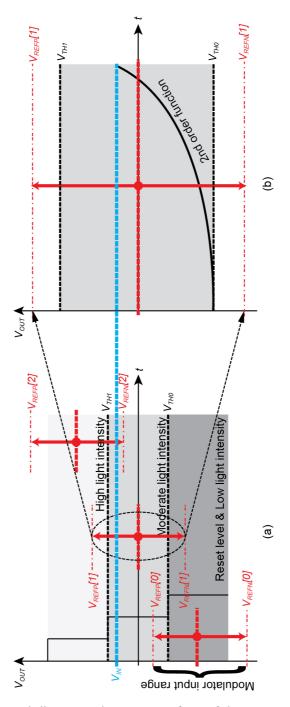

not be able to identify photons correctly under a low-intensity light condition if the electronic noise of the charge detection process is too large. Figure 1.1 is a graphical illustration of a noisy photon detection process, where (a) represents the distribution of photons interacting with the image sensor and (b) illustrates results of the electronic photon-charge detection within the image sensor [4].

In order to calculate the maximum noise level that can be tolerated in the electronic photon-charge detection process, a Gaussian distribution of detection noise is assumed. The noise probability density function  $p_D(x)$  normalized by LSB is then given by [4]:

$$p_D(x) = \frac{1}{\sqrt{(2\pi)} \cdot \sigma_D} e^{-\frac{(x-\mu)^2}{2\sigma_D^2}}$$

(1.1)

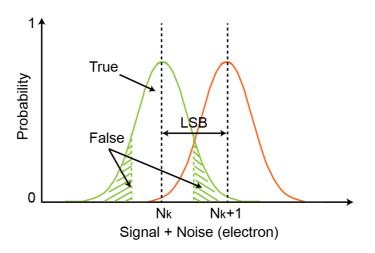

Figure 1.2: Quantization error by noise (redraw based on [5])

where  $\mu = 0$  is the mean of the distribution and  $\sigma_D$  is the standard deviation and LSB is the quantization step. Figure 1.2 illustrates the noise distribution at two different quantization levels, where  $N_k$  and  $N_k + 1$  stands for the kth and k + 1-th quantized level. When the signal is located between  $N_k - LSB/2$  and  $N_k + LSB/2$ , miscounting will not happen and the event will be labeled as "True". When the signal is out of the "True" interval, then the miscounting will occur and therefore the event is labeled as "False". To quantitatively estimate this probability, an expression which describes the probability p of incorrect counting in a pixel can be derived as:

$$p = 2 \int_{\frac{1}{2}LSB}^{\infty} p_D(x) dx = erfc(\frac{LSB}{\sqrt{8}\sigma_D})$$

(1.2)

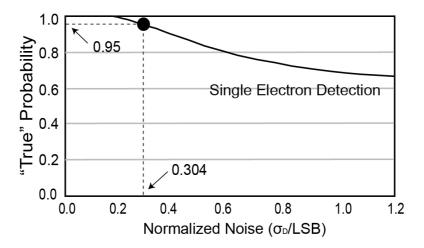

where erfc is the complementary error function. Figure 1.3 presents the probability p dependence over the noise standard deviation normalized by LSB, i.e.  $\sigma_D/LSB$ . The probability is increased when  $\sigma_D/LSB$  is decreased. For a handy calculation, Winitzki's approximation of the error function erf(x) is adopted to assist estimating which  $\sigma_D$  is required to reach a given probability p. As a results, if the case of single-electron detection is assumed,  $\sigma_D/LSB$  should be 0.304 when the true probability is 0.95, which is equivalent to a noise level of 0.304 e<sup>-</sup> (LSB = 1 electron).

Currently, single-photon detection is also being pursued by other solid-state imaging techniques, such as single-photon avalanche photodiodes (SPADs) and electron multiplication CCDs (EMCCDs). The

Figure 1.3: Target noise level for photon single electron detection (redraw from [5])

former intensifies the photo-generated signals through impact ionization [10], while the latter does this by triggering an avalanche process [6]. In this way, they show excellent performance with respect to signal-to-noise ratio (SNR) and input-referred noise under photon-starved conditions. However, the limitations of each method are as follows:

- SPADs are not able to integrate the photo-electrons, thus require a counter in each SPAD element to record the output of each readout cycle. This approach enables a high operating speed and temporal resolution, however, also increases the complication of the readout structure in SPAD pixels. What's worse, due to the existence of dead time, the cycle time for these devices is less than 100%. Dark counting also introduces count errors and limits the performance. Furthermore, the light sensitivity is restricted by a low fill-factor and low quantum-efficiency (QE), especially in the range of long wavelength. Finally, the fabrication of high-resolution SPAD in a CMOS process suffers from a relatively low yield [7]-[9].

- EMCCDs usually need extra cooling to avoid the impact of dark current. In addition, they are sensitive to temperature variation and voltage variation of the clock pulses. Furthermore, an aging effect also constrain their on-the-shelf storage period and causes reliability issues. Lastly, their very high operating voltages (up to 50V) makes

it difficult to fabricate EMCCDs in a conventional CMOS process [11]-[12].

In contrast to SPADs and EMCCDs, standard CISs doesn't have the above mentioned drawbacks. Furthermore, since the CIS process is based on well-established CMOS technology, process scaling provides much more potential for the development of CIS. Over the last two decades, the pixel pitch has shrunk significantly, from 8  $\mu$ m in 2000 to 0.61  $\mu$ m [13] in 2020. Nowadays, the pixel pitch shrinking race is still on-going and it is difficult to predict its end. On the other hand, the CMOS technology also enables the integration of image sensors with on-chip application-specific integrated circuits (ASICs), which include signal conversion circuits, memories, digital signal processors (DSP), etc.. Such high-level integration not only improves the image quality but also satisfies the growing demands for intelligent sensing functions. Therefore, a low-noise CIS will be an attractive candidate for single-photon imaging and the associated niche applications.

# **1.2.** Challenges and Motivations

As mentioned above, the interest in single-photon imaging has stimulated the research of low-noise CISs. However, the challenge of reducing the noise in a CIS has been around for a long time. The amount of noise from the imager's output signal depends on a number of different noise sources, the origins of which are complicated and often process dependent. All these factors impose a great challenge to realize a low noise CIS.

Table 1.1 gives an overview of different categories of CIS noise sources. In general, the noise generated in the imager can be categorized as temporal noise and fixed pattern noise (FPN), which represent the signal variation in the time domain and the spatial domain respectively. In terms of FPN, this consists of the dark signal non-uniformity (DSNU) and the dark current non-uniformity (DCNU) under dark condition, and the photo-response nonuniformity (PRNU) under illumination. As FPN is fixed in spatial position, it is relatively easy to correct by means of double sampling, calibration or digital signal processing procedures.

Temporal noise is typically recognized as the fundamental limit of the imager performance in terms of noise. It is composed of several major noise components, such as the photon shot noise under illumination, the

| Tal | bl | e 1 | 1.1 | l: | N | loise | sumi | mary |

|-----|----|-----|-----|----|---|-------|------|------|

|-----|----|-----|-----|----|---|-------|------|------|

|              | Fixed pattern noise (FPN)               | Temporal noise                                                                                      |  |

|--------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------|--|

| Dark         | Dark signal non-uniformity<br>(DSNU)    | Dark current shot noise                                                                             |  |

|              | Dark current non-uniformity<br>(DCNU)   | Read-out noise (reset noise,<br>thermal noise, random telegraph<br>signal (RTS) noise, $1/f$ noise) |  |

| Illumination | Photo-response non-uniformity<br>(PRNU) | Photon shot noise                                                                                   |  |

dark current shot noise and the read-out noise. The latter generally includes reset noise, thermal noise. random telegraph signal (RTS) noise and 1/fnoise. Although a number of circuit techniques can be employed to minimize the above noise components, they never come without a cost, as any addition to pixel-level devices, signal readout circuits and signal processing functions may have an impact on the input-referred noise of an imager. Furthermore, temporal noise reduction always comes with tradeoffs between chip area, frame-rate, design complexity, power consumption and cost or risk.

To address these challenges, the pursuit of system-level and circuit-level innovations and optimizations for CIS noise never ends. The motivation of this thesis is to tackle the dominant noise sources in CISs and improve the sensor performance by reducing the sensor's dark temporal noise level with both novel techniques and optimizations.

# **1.3.** Context of the Research

The first high-performance photodiode-type active pixel sensor (APS) for solid-state imaging was successfully demonstrated in 1995 [14]. Fabricated in a 1.2  $\mu$ m process, this pioneering CIS design adopted a three-transistor (3T) pixel structure with CMOS fabrication facilities. As the reset noise was uncorrelated in this work, designers spent a lot of efforts in investigating and compressing it. Although the later proposed soft reset [15], active reset [16]-[17] and in-pixel capacitive-coupled noise canceller (CCNC) scheme [19] are capable of reducing the reset noise, the remaining noise still constrains the image performance.

Fortunately, it didn't take long time for designers to realize the necessity of migrating pinned-photodiode (PPD) process from CCD to CMOS imagers [1]. In 1997, the first PPD-type CIS with four-transistor (4T) pixel structure was implemented. This work achieved a low dark current level, good spectral response (with shorter wavelength), and most importantly, a low temporal noise level (at the rolling shutter mode). Until now, the 4T pixel scheme is still widely used and quite a lot of innovative pixel architectures are based on this revolutionary design. In contrast with 3T pixels, the reset noise for 4T pixels can be removed completely by correlated double sampling (CDS). Combined with a lower floating diffusion (FD) capacitance and a higher conversion gain (CG), the dark temporal noise level is dramatically reduced. This leaves the 1/f and RTS noise from the in-pixel source follower (SF) transistors and thermal noise generated by readout circuits as major noise sources for CMOS imagers. In the following, a brief overview of recently developed CIS noise reduction methodologies will be discussed.

#### Source Follower Process and Operation Optimization

Beginning from the early 2000s, substantial efforts from a number of research groups have been made to analyze, characterize and model the 1/f and RTS noise with various SF transistor sizes [21]-[22], shapes [25], CDS periods [23], extracted time constants [24]-[25] and biasing voltages and currents [27]. The resulting findings are of great importance for understanding the mechanisms of noise and giving insights on the noise reduction for SFs thereafter.

Besides the above-mentioned research efforts, the continuous improvement of CIS process provides the possibility of reducing the process-dependent noise contribution in SFs. Buried channel and its variants with optimized junction profile were reported to be used in a pixel-level SF transistor [28]-[29]. In order to suppress the interface traps-induced noise, the focus of this approach is to move the conducting carriers away from the Si-SiO<sub>2</sub> interface for nMOS transistors. For the same purpose, the pMOS-based pixel was reported, coming along with the development of hole-based PPDs [30]-[31]. Fluorine implantation is another optimization process for SF transistors [32]. By passivating the dangling bonds in the Si-SiO<sub>2</sub> interface with fluorine atoms, the SiO<sub>2</sub> imperfection is mitigated and hence leads to a reduced 1/f noise. Beyond

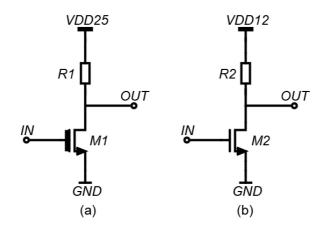

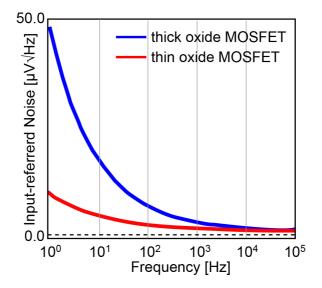

that, an ultraviolet (UV) annealing process [33] and the hydrogen-assisted low pressure radical oxidation (LPRO) process [34], which are typically applied in CMOS logic and flash process, were also introduced to CIS process form improving the CIS noise performance. Compared to the above mentioned methodologies, the implementation of a thin gate oxide device as SF has been considered as a more economical solution [35]. Such devices have a gate oxide ( $G_{ox}$ ) capacitance per unit area ( $C_{ox}$ ) that is higher than the counterparts with a thick  $G_{ox}$ . From the well-known flicker noise model [36],  $\overline{v_n^2} = K/C_{ox}^2WLf$ , where K is a process-dependent constant, W and L are the width and length of a transistor, f is the frequency, we can see that a higher  $C_{ox}$  is advantageous for suppression of the 1/f noise portion.

#### Floating Diffusion Capacitance Reduction

Concurrent with the above advances in process developments for in-pixel transistors, several research groups have been working on the reduction of the floating diffusion (FD) node capacitance, with the motivation of boosting the signal before the occurance of readout noise. To minimize the parasitic coupling capacitance between the transfer gate (TG) and the FD node, an effective technique was proposed in [37]. In this work, the PPD p+ pinning layer is extended to the edge of the FD, forming a fully-depleted-diode between the TG and the FD, which helps to minimize the TG-FD coupling capacitance. Similarly, inspired by а pinned-photodiode pump-gate (PPD-PG) device [38], a vertical transfer pump-gate with a distal FD was demonstrated in a prototype CIS [39]. Furthermore, in order to eliminate the parasitic capacitance between the FD and the reset gate (RST), a tapered reset transistor and a gate-less reset method [40] were proposed. The former one employs a tapered channel on the FD side to reduce the overlap width, and the latter one adopts the punch-through operation to completely remove the RST transistor and its associated parasitic capacitance. In addition, instead of minimizing the TG-FD and RST-FD parasitic capacitance individually, a general solution was proposed in [41] and [42]. In this work, a self-aligned source-drain offset structure is implemented by omitting the lightly doped drain (LDD) implantation and the channel stop under FD, which leads to the decrease of the p-n junction capacitance and the gate overlap capacitance.

#### Circuit-level Technique for Noise Reduction

Besides process-level explorations, innovative circuit-level solutions and good design practices for noise reduction in a CIS keep emerging.

To achieve a single-photon detection performance, an effective way is to apply high gain at the front stage of the signal path. [43] and [44] attempted to realize a pixel-level open-loop amplification with nMOS and pMOS transistors respectively. Such a pixel architecture could provide a flicker noise limited noise performance, but it is not compatible with a small pixel pitch. As an alternative, in-pixel differential common-source amplifiers were proposed, which are capable of fitting into a pixel size as small as 1.45  $\mu$ m, while outperforming in terms of noise [45]-[46].

Compared to the pixel-level circuit, integrating a read-out path at the column level further relaxes power and area constraints, therefore provides higher flexibility for noise canceling while maintaining a good trade-off with other key specs. For example, low noise and high dynamic range (DR) are essential specifications for a CIS operating in both dark and bright conditions. Employing an adaptive gain is a very effective approach to achieve both features simultaneously [47]. With the assistance of look-ahead circuits, the readout circuit is switched to a higher gain to reduce the random noise when a pixel signal is lower than a certain threshold level. To avoid exceeding the amplifier output range, the gain is reduced when the pixel signal goes beyond the threshold [48]. Such an approach suppresses the noise while keeping the pixel signal range, leading to a DR that is wider than an ADC-only readout circuit.

Digital correlated multiple sampling (CMS) has been recognized as an effective technique for the suppression of both thermal noise and 1/fnoise, but at the cost of low frame-rate [49]. To achieve low-noise in high frame-rate applications, several techniques based on the most widely used single-slope (SS) analog-to-digital converters (ADCs) have been proposed. Example include the conditional CMS SS-ADC [50], the gain-adaptive SS-ADC [51], the differential slope with accelerated counter ADC [52], the pseudo-multiple sampling [53], the time-stretched SS-ADC [54], and so on. Besides, quite a few different ADC architectures have been successfully demonstrated to leverage the CMS function while keeping a good frame-rate. Such contributions include the inverter-based  $\Delta\Sigma$  ADCs [55], phase-delay-counting dual-slope ADCs [56] the and the folding-integration/cyclic ADCs [57].

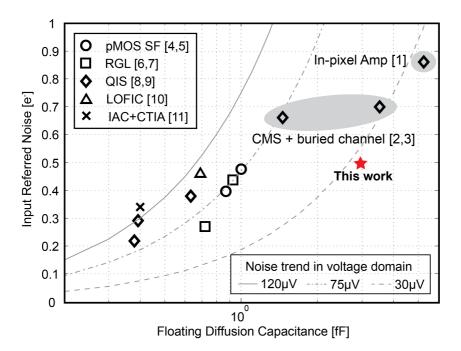

#### State-of-the-art

With the incorporation of continuously developed CIS process and innovative solutions, the past decade has witnessed the realization of several CISs with sub-electron noise performance. These results are summarized in Table 1.2.

### **1.4.** Thesis Organization

This thesis consists of six chapters. The rest of this thesis is arranged as follows.

Exploiting the advantage of a pMOS transistor over its nMOS counterpart in minimizing low frequency noise, a body-effect free pMOS-based SF pixel with standard n-type PPD scheme is proposed in **Chapter 2**. It has been demonstrated in a prototype with a power-supply rejection ratio (PSRR) enhanced single-ended amplifier as the column-parallel readout circuit. The noise performance has been characterized, demonstrating the effectiveness of this technique.

**Chapter 3** presents the calculation, the measurement and a comparative analysis of the temporal noise in n-type and p-type pixels. In this chapter, the noise power spectral density (PSD) of in-pixel source followers has been evaluated. Then, the CMS noise transfer function for both cases has been investigated in the frequency domain. Afterwards, a temporal readout noise measurement based on the histogram variance of the output signal for both pixels involving CMS has been performed. The measured results show that the input-referred temporal noise level of n-type and p-type pixels reach 1.1  $e_{rms}^-$  and 0.88  $h_{rms}^+$  respectively.

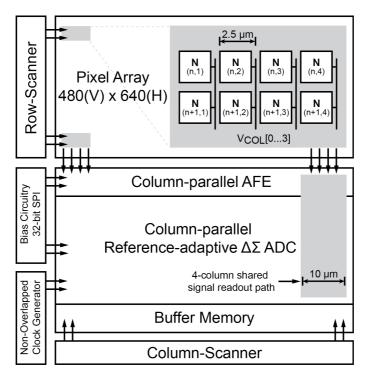

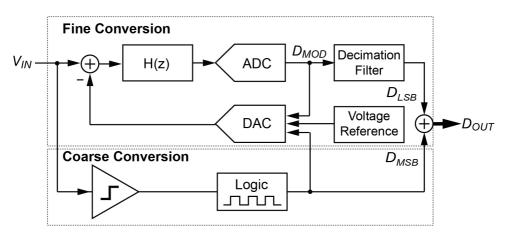

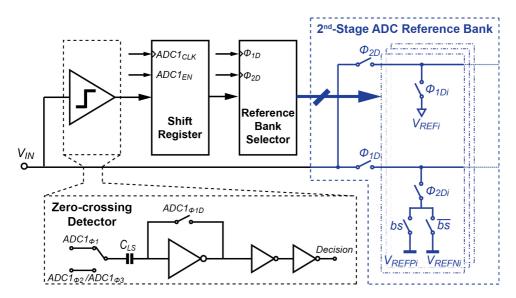

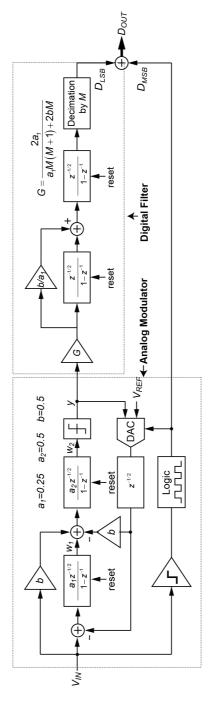

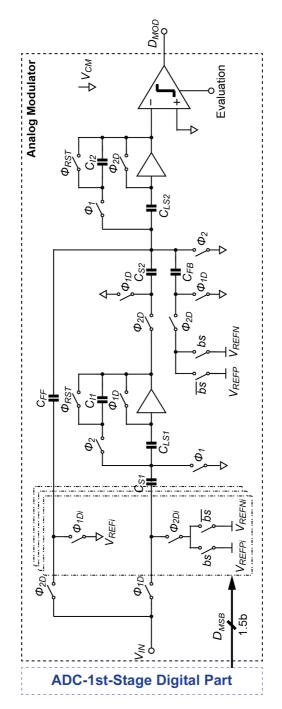

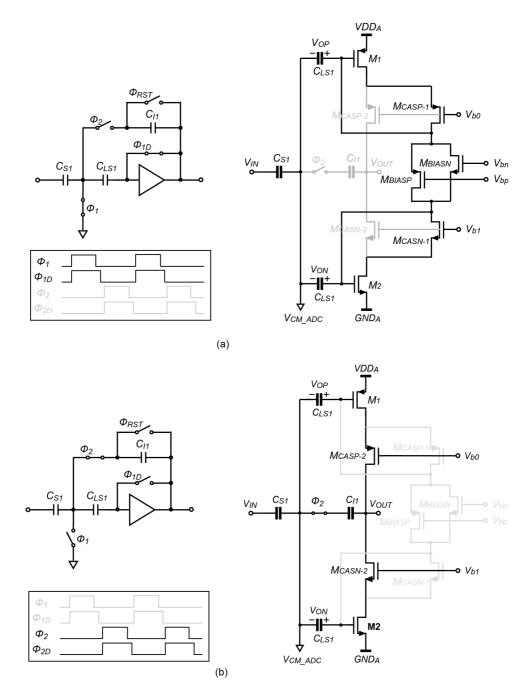

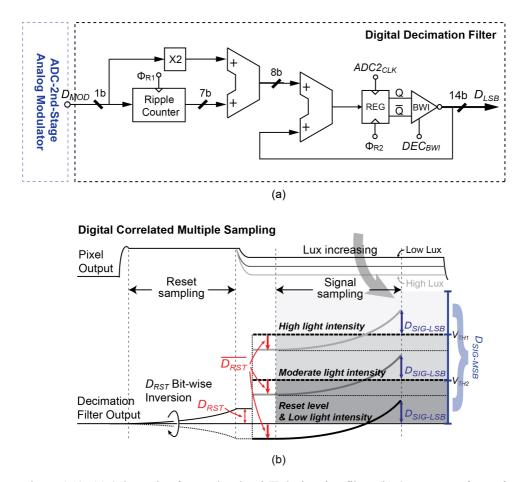

Based on the analysis and measurement results from Chapter 3, a prototype equipped with a high-gain stage and a digital CMS technique is presented in **Chapter 4**. Implemented in a 65 nm CIS back-side-illumination (BSI) technology, the proposed architecture incorporates a column-parallel inverter-based analog-front-end (AFE) circuit and a digital CMS reference-adaptive  $\Delta\Sigma$  ADC along the readout path. This prototype design reaches an input-referred noise of 0.55  $e_{rms}^-$  within a row time of 5 µs.

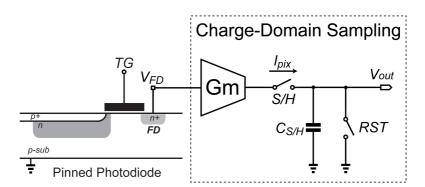

As mentioned in Section 1.3, an efficient approach to reduce the noise floor is to place a high gain stage as close as possible to the photo-detector as possible. This is demonstrated in **Chapter 5**, where a Gm-cell-based pixel targeting a deep sub-electron temporal noise CIS is presented. To

| Reference         | Noise reduction approach                                  | Read-<br>noise<br>[e <sup>-</sup> <sub>rms</sub> ] | Pixel<br>pitch<br>[µm] | Process<br>node<br>[nm] |

|-------------------|-----------------------------------------------------------|----------------------------------------------------|------------------------|-------------------------|

| ISSCC2011<br>[44] | in-pixel amplifier                                        | 0.86                                               | 11                     | 180                     |

| ISSCC2012<br>[49] | buried channel SF + CMS +<br>high-gain column amplifier   | 0.7                                                | 10                     | 180                     |

| VLSI2015<br>[58]  | high CG (self-aligned S/D<br>offset)                      | 0.5                                                | 5.5                    | 180                     |

| VLSI2015<br>[50]  | conditional CMS + high-gain<br>column amplifier           | 0.66                                               | 1.1                    | -                       |

| EDL 2015<br>[59]  | high CG (pump-gate with distal<br>FD + tapered reset gate | 0.28                                               | 1.4                    | 65                      |

| IISW2015<br>[60]  | thin oxide layer SF + high-gain<br>column amplifier       | 0.5                                                | 10                     | 180                     |

| IISW2015<br>[61]  | inversion-accumulation cycling                            | 0.34                                               | 25                     | 180                     |

| ISSCC2017<br>[62] | high CG (reset-gate-less FD)                              | 0.44                                               | 11.2                   | 110                     |

| IISW2017<br>[63]  | high CG (JFET SF)                                         | 0.34                                               | 1.4                    | 45/65                   |

| IEDM2018<br>[64]  | high CG                                                   | 0.8                                                | 1.5                    | -                       |

| IEDM2018<br>[65]  | high CG                                                   | 0.68                                               | 3                      | 90                      |

| IISW2019<br>[66]  | high CG                                                   | 0.83                                               | 2.8                    | -                       |

| ISSCC2020<br>[46] | in-pixel differential amplifier +<br>CMS                  | 0.5                                                | 1.45                   | 90/55                   |

| ISSCC2020<br>[67] | $h_1\sigma h(C)$                                          |                                                    | 3                      | 90/65/40                |

#### Table 1.2: Sub-one electron noise results summary

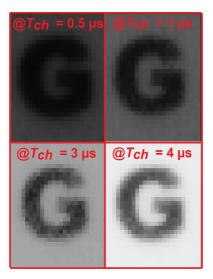

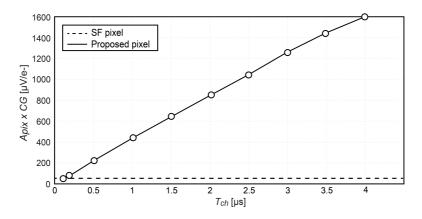

overcome the trade-off between high DR and low input-referred noise, a pixel-level variable-gain has been realized in a period-controlled manner. As such, the read-out path CG can be programmed according to the specific application of the CIS without any reconstruction of the hardware. This prototype achieves an input-referred noise of 0.5  $e_{rms}^{-}$  within a correlated double sampling (CDS) period of 5 µs and a row read-out time of 10 µs.

**Chapter 6** summarizes this thesis with discussions and a conclusion. Recommendations for future research are also presented.

# References

- R. Guidash, et al., "A 0.6µm CMOS Pinned Photodiode Color Imager Technology," Proc. IEDM, Washington DC, USA, Dec. 1997, pp. 927-929.

- [2] R. Weissleder, et al., "Scaling down imaging: molecular mapping of cancer in mice," Nature Rev. Cancer, vol.2, no.1, Jan. 2002, pp. 11-18.

- [3] S. Meikle et al., "Complementary molecular imaging technologies: high-resolution SPECT, PET and MRI," Drug Discovery Today: New Technology, vol.3, no.2, 2006, pp.187-194.

- [4] P. Seitz and A.J.P.Theuwissen (Eds.), Single-Photon Imaging, Berlin, Germany: Springer, 2011, ISBN 978-3-642-18443-7, pp. 9-10.

- [5] N. Teranishi, "Required conditions for photon-counting image sensors," IEEE Trans. Electron Devices, vol. 59, no. 8, pp. 2199–2205, Aug. 2012.

- [6] B. F. Aull et al., "Geiger-mode avalanche photodiodes for three dimensional imaging," Lincoln Laboratory Journal, vol. 13, pp. 335-349, 2002.

- [7] N. Dutton et al., "320× 240 oversampled digital single photon counting image sensor," Proc. Symposium on VLSI Circuits, Honolulu, USA, Jun. 2014, pp. 1-2.

- [8] N. Dutton et al., "Oversampled ITOF imaging techniques using SPADbased quanta image sensors," Proc. IISW, Vaals, Netherlands, Jun. 2015, 6.04.

- [9] M. Perenzoni et al., "A 160×120-pixel analog-counting single-photon imager with Sub-ns time-gating and self-referenced column-parallel A/D conversion for fluorescence lifetime imaging," ISSCC Dig. Tech. Papers, San Francisco, US, Feb. 2015, pp.1-3.

- [10] J. Hynecek, "Impactron-a new solid state image intensifier," IEEE Trans. Electron Devices, vol. 48, no. 10, pp. 2238-2241, Oct. 2001.

- [11] M. S. Robbins et al., "The noise performance of electron multiplying charge-coupled devices," IEEE Trans. Electron Devices, vol. 50, no. 5, pp. 1227-1232, July 2003.

- [12] C. Parks et al., "A 30 fps 1920 x 1080 pixel electron multiplying CCD image sensor with per-pixel switchable gain," Proc. IISW, Vaals, Netherlands, Jun. 2015.

- [13] J. Yun et al., "A Small-size Dual Pixel CMOS Image Sensor with Vertically Broad Photodiode of 0.61 µm pitch," Proc. IISW, Snowbird, USA, Jun. 2019, R03.

- [14] R. Nixon et al., "128x128 CMOS Photodiode-Type Active Pixel Sensor with On-Chip Timing, Control and Signal Chain Electronics," Proceeding of SPIE, San Jose, US, vol. 2415, May 1995, pp. 117-123.

- [15] H. Tian et al., "Analysis of Temporal Noise in CMOS Photodiode Active Pixel Sensor," IEEE Journal of Solid-State Circuits, vol. 36, Jan.2001, pp. 92-101.

- [16] B. Fowler et al., "Low Noise Readout Using Active Reset for CMOS APS," Proceedings of SPIE, San Jose, US, vol. 3965, May 2000, pp. 126-135.

- [17] B. Pain et al., "Reset Noise Suppression in Two-Dimensional CMOS Photodiode Pixels through Column-Based Feedback Reset," Technical Digest IEDM, San Francisco, US, Dec. 2002, pp. 809-812.

- [18] K. Nishimura et al., "An Over 120dB Simultaneous-Capture Wide-Dynamic-Range 1.6e- Ultra-Low-Reset-Noise Organic-Photoconductive-Film CMOS Image Sensor," ISSCC Dig. Tech. Papers, San Francisco, US, Feb. 2016, pp.110-111.

- [19] K. Nishimura et al., "An 8K4K-Resolution 60fps 450ke- Saturation-Signal Organic-Photoconductive-Film Global-Shutter CMOS Image Sensor with In-pixel Noise Canceller," ISSCC Dig. Tech. Papers, San Francisco, US, Feb. 2018, pp.82-83.

- [20] B. Pain et al., "Excess Noise and Dark Current Mechanisms in CMOS Imagers," IEEE Workshop in CCD and Advanced Image Sensors, Karuizawa, Japan, June 2005, pp. 145-148.

- [21] P. Martin-Gaonthier et al., "RTS noise impact in CMOS image sensors readout circuit," IEEE ICECS, Yasmine Hammamet, Tunisia, Dec. 2009.

- [22] A. Lahav et al., "Optimization of Random Telegraph Noise Non Uniformity in a CMOS Pixel with a pinned-photodiode," Proc. IISW, Ogunquit, US, Jun. 2007, pp. 230-233.

- [23] X. Wang et al., "Random telegraph signal in CMOS image sensor pixels," Technical Digest IEDM, Washington DC, US, Dec. 2006, pp. 115-118.

- [24] C. Chao et al., "CMOS Image Sensor Random Telegraph Noise Time Constant Extraction From Correlated To Uncorrelated Double Sampling," IEEE J. Electron Devices Society, vol. 5, no. 1, pp. 79–89, Jan. 2017.

- [25] S. Ichino et al., "Statitical Analysis of Random Telegraph Noise in Source Follower Transistors with Various Shapes," Proc. IISW, Hiroshima, Japan, Jun. 2017, pp. 39-42.

- [26] R. Kuroda et al., "Impact of Random Telegraph Noise with Various Time Constants and Number of States in CMOS Image Sensors," Proc. IISW, Hiroshima, Japan, Jun. 2017, pp. 43-46.

- [27] K. Abe et al., "Analysis of Source Follower Random Telegraph Signal Using nMOS and pMOS Array TEG," Proc. IISW, Ogunquit, US, Jun. 2007, pp. 62-65.

- [28] X. Wang et al., "A CMOS image sensor with a buried-channel source follower," ISSCC Dig. Tech. Papers, San Francisco, US, Feb. 2008, pp.62-63.

- [29] T. Hsu et al., "Novel Device with Ultra Low Noise for Smaller CMOS Image Sensor Pixel," Proc. IISW, Snowbird, USA, Jun. 2013, 4.02.

- [30] E. Stevens et al., "Low Crosstalk and Low-Dark-Current CMOS Image Sensor Technology Using a Hole-Based Detector," ISSCC Dig. Tech. Papers, San Francisco, US, Feb. 2008, pp.60-61.

- [31] J. Tower et al., "BSI Low Light Level CMOS Image Sensor Employing P-type Pixel," Proc. IISW, Snowbird, USA, Jun. 2013, 5.12.

- [32] M. Ha et al., "Temporal Noise Improvement Using the Selective Application of the Fluorine Implantation in the CMOS Image Sensor," Proc. IISW, Hiroshima, Japan, Jun. 2017, pp. 32-34.

- [33] J Jung et al., "Decreasing Dark Current of CMOS Image Sensors by New Postmetallization Annealing and Ultraviolet Curing," Japanese J. of Applied Physics, vol.47, no.1, 2008, pp.139-141.

- [34] J. Han et al., "Study on the Characteristics of SiO2 Films Prepared by Hydrogen-Assisted LPRO using Batch-type Equipment," J. of the Korean Physical Society, vo.49, no.5, 2016

- [35] A. Boukhayma, et al., "A 0.4e-rms Temporal Readout Noise 7.5μm Pitch and a 66% Fill Factor Pixel for Low Light CMOS Image Sensors," Proc. IISW, Vaals, the Netherlands, Jun. 2015, pp. 365–368.

- [36] W. M. C. Sansen, Analog Design Essentials, Springer, 2006, ISBN-13 978-0-387-25747-1 (e-book), pp. 127.

- [37] M. Seo, et al., "A low noise wide dynamic range CMOS image sensor with low-noise transistors and 17b column-parallel ADC," IEEE Sensors. J. vol. 13, no. 8, pp. 2922-2929, Aug. 2013

- [38] S. Velichko et al., "Low noise high efficiency 3.75 μm and 2.8 μm global shutter CMOS pixel arrays," Proc. IISW, UT, USA, Jun. 2013, pp. 389–392.

- [39] J. Ma and E. R. Fossum, "A pump-gate jot device with high conversion gain for a quanta image sensor," IEEE J. Electron Devices Soc., vol. 3, no. 2, pp. 73–77, Mar. 2015.

- [40] M. Seo, et al., "A 0.27e-rms read noise 220-μV/e-conversion gain reset-gate-less CMOS image sensor with 0.11-um CIS process," IEEE Electron Device Lett., vol. 36, no. 12, pp. 1344–1347, Dec. 2015.

- [41] S. Adachi et al., "A 200-μV/e-CMOS image sensor with 100ke-full well capacity," IEEE J. Solid-State Circuits, vol. 43, no. 4, pp. 823– 830, Apr. 2008.

- [42] F. Kusuhara et al., "Analysis and reduction of floating diffusion capacitance components of CMOS image sensor for photon-countable sensitivity," Proc. IISW, Vaals, The Netherlands, Jun. 2015, pp. 120– 123.

- [43] J. Yang et al., "A 3MPixel Low-Noise Flexible Architecture CMOS Image Sensor," ISSCC Dig. Tech. Papers, San Francisco, USA, Feb. 2006, pp. 2004-2013.

- [44] C.Lotto et al., "A Sub-Electron Readout Noise CMOS Image Sensor with Pixel-Level Open-Loop Voltage Amplification," ISSCC Dig. Tech. Papers, San Francisco, USA, Feb. 2011, pp. 402–403.

- [45] J. Choi et al., "A 1.36uW Adaptive CMOS Image Sensor with Reconfigurable Modes of Operation From Available Energy/Illumination for Distributed Wireless Sensor Network," ISSCC Dig. Tech. Papers, San Francisco, USA, Feb. 2012, pp. 112–113.

- [46] M. Sato et al., "A 0.50e-rms Noise 1.45µm-Pitch CMOS Image Sensor with Reference-Shared In-Pixel Differential Amplifier at 8.3Mpixel 35fps," ISSCC Dig. Tech. Papers, San Francisco, USA, Feb. 2020, pp. 108–109.

- [47] H. Totsuka et al., "An APS-H-Size 250Mpixel CMOS Image Sensor Using Column Single-Slope ADCs with Dual-Gain Amplifiers," ISSCC Dig. Tech. Papers, San Francisco, USA, Feb. 2016, pp. 116– 117.

- [48] M. Sakakibara et al., "A High-Sensitivity CMOS Image Sensor With Gain-Adaptive Column Amplifiers," IEEE J. Solid-State Circuits, vol. 40, no. 5, May 2005, pp. 1147-1156

- [49] Y. Chen et al., "A 0.7e-rms Temporal-Readout-Noise CMOS Image Sensor for Low-Light-Level Imaging," ISSCC Dig. Tech. Papers, San Francisco, US, Feb. 2012, pp. 385–386.

- [50] S. Yeh et al., "A 0.66e-rms Temporal-Readout-Noise 3D-Stacked CMOS Image Sensor with Conditional Correlated Multiple Sampling (CCMS) Technique," Symposium on VLSI Circuits Dig. Tech. Papers, Kyoto, Japan, Jun. 2015, pp. C84–C85.

- [51] Y. Oike et al., "8.3M-Pixel 480-fps Global-Shutter CMOS Image Sensor with Gain-Adaptive Column ADCs and Chip-on-Chip Stacked Integration," IEEE J. Solid-State Circuits, vol. 52, no. 4, pp. 985–993, Apr. 2017.

- [52] K. Kitamura et al., "A two conversions/sample, differential slope multiple sampling ADC with accelerated counter architecture," Proc. IISW, Vaals, The Netherlands, Jun. 2015. pp. 417–420.

- [53] Y. Lim et al., "A 1.1e-temporal noise 1/3.2-inch 8Mpixel CMOS image sensor using pseudo-multiple sampling," ISSCC Dig. Tech. Papers, San Francisco, USA, Feb. 2010, pp. 396–397.

- [54] I. Park et al., "A 76mW 500fps VGA CMOS Image Sensor with Time-Stretched Single-Slope ADCs Achieving 1.95e- Random Noise," ISSCC Dig. Tech. Papers, San Francisco, USA, Feb. 2020, pp. 100– 101.

- [55] Y. Chae et al., "A 2.1 M Pixels, 120 Frame/s CMOS Image Sensor With Column-Parallel  $\Delta\Sigma$  ADC Architecture," IEEE J. Solid-State Circuits, vol. 46, no.1, Jan. 2011, pp. 236–247.

- [56] H. Thai et al., "A 0.18-µm CMOS Image Sensor With Phase-Delay-Counting and Oversampling Dual-Slope Integrating Column ADCs Achieving 1e-rms Noise at 3.8-us Conversion Time," IEEE J. Solid-State Circuits, vol. 53, no.2, Feb. 2018, pp. 515–526.

- [57] M. Seo et al., "A Low-Noise High Intrascene Dynamic Range CMOS Image Sensor With a 13b to 19b Variable-Resolution Column-Parallel Folding-Integration/Cyclic ADC," IEEE J. Solid-State Circuits, vol. 47, no.1, Jan. 2012, pp. 272-283.

- [58] S. Wahashima et al., "A Linear Response Single Exposure CMOS Image Sensor with 0.5e- Readout Noise and 76ke- Full Well Capacity," Symposium on VLSI Circuits Dig. Tech. Papers, Kyoto, Japan, Jun. 2015, pp. C88–C89.

- [59] J. Ma et al., "Quanta Image Sensor Jot With Sub 0.3e- r.m.s. Read Noise and Photon Counting Capability," IEEE Electron Device Letters, vol. 36, no. 9, pp. 926–928, Sep. 2015.

- [60] A. Boukhayma et al., "A sub-0.5 electron read noise VGA image sensor in a standard CMOS process," IEEE J. Solid-State Circuits, vol. 51, no. 9, pp. 2180–2191, Sep. 2016.

- [61] Q. Yao et al., "CMOS image sensor reaching 0.34e-rms read noise by inversion-accumulation cycling," Proc. IISW, Vaals, the Netherlands, Jun. 2015, pp. 369–372.

- [62] M. Seo et al., "A 0.44 e-rms read-noise 32fps 0.5 Mpixel Highsensitivity RG-less-pixel CMOS image sensor using bootstrapping reset," ISSCC Dig. Tech. Papers, San Francisco, USA, Feb. 2017, pp. 80–81.

- [63] J. Ma et al., "Experimental Comparison of MOSFET and JFET 1.1μm Pitch Jots in 1Mjot Stacked BSI Quanta Image Sensors," Proc. IISW, Hiroshima, Japan, Jun. 2017, pp. 226–229.

- [64] V. Venezia et al., "1.5µm Dual Conversion Gain, Backside Illuminated Image Sensor Using Stacked Pixel Level Connections with 13ke-Full-Well Capacitance and 0.8e- Noise," Proc. IEDM, San Francisco, USA, Dec. 2018, pp. 217-220.

- [65] S. Iida et al., "A 0.68e-rms Random-Noise 121dB Dynamic-Range Sub-pixel architecture CMOS Image Sensor with LED Flicker Mitigation," Proc. IEDM, San Francisco, USA, Dec. 2018, pp. 221-225.

- [66] J. Solhusvik et al., "A 1280x960 2.8μm HDR CIS with DCG and Split-Pixel Combined," Proc. IISW, Snowbird, USA, Jun. 2019, R32.

[67] Y. Sakano et al., "A 132dB Single-Exposure-Dynamic-Range CMOS Image Sensor with High Temperature Tolerance," ISSCC Dig. Tech. Papers, San Francisco, USA, Feb. 2020, pp. 106–107.

# 2

# Temporal Noise Reduction Using pMOS Unity-Gain Source Follower and Optimized Column Amplifier

This chapter is an extended version of the following published article:

<sup>•</sup> X.Ge and A. Theuwissen, "A CMOS Image Sensor with Nearly Unity-Gain Source Follower and Optimized Column Amplifier" in *Proc. IEEE SENSORS*, Oct. 2016, pp. 1–3, doi: 10.1109/ICSENS.2016.7808589.

# **2.1.** Introduction

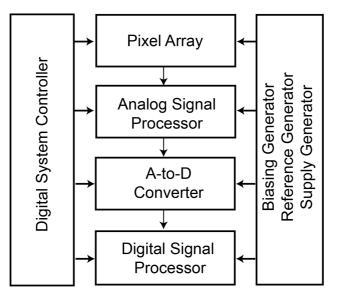

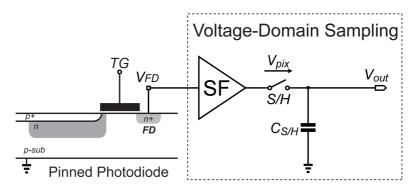

T he conceptual diagram of a typical architecture for a CMOS image sensor (CIS) is depicted in Figure 2.1. It consists of several electrical function modules: pixel array, analog signal processor, A-to-D converter (ADC), and digital signal processor, which are the main building blocks that directly process the received optical signal. The digital system controller and the biasing/reference/supply generator are the auxiliary blocks that support and control the signal processing flow of the CIS. In most CIS applications, the imaging quality at low light levels is highly susceptible to noise originating from these blocks, especially from a variety of sources along the signal processing chain[1], both in temporal and spatial domain.

Among these noise sources, the low frequency noise, i.e. random telegraph signal (RTS) noise and flicker noise (1/f), are generated by the in-pixel source follower (SF), and the latter one has been recognized as one of the most significant noise contributors [2, 3]. Despite the fact that the exact physical mechanism for both 1/f and RTS noise is still under debate, it is widely agreed that these low frequency type noises are caused by lattice defects at the interface of the Si-SiO<sub>2</sub> channel of the CMOS transistor [4, 5]. Given the fact that holes have lower mobility than electrons, the rate of trapping/re-emission events for a pMOS transistor is reduced compared to nMOS.

Therefore, implementing a SF with a pMOS transistor can provide a substantial low frequency noise reduction, and so has been investigated in a few recent works [2–5]. However, this approach also suffers from a voltage gain degradation due to the higher body effect trans-conductance of pMOS transistors, which increases the noise contribution of succeeding circuits when referred to the input of the source follower. Thus, a body-effect free design strategy for pixel-level circuit is called for.

Another dominant noise source in the CIS is located at the analog signal processor. In CIS systems with a column-level readout scheme, such an analog processor is usually embodied as a column-parallel amplifier with correlated double sampling (CDS) function. By linearly amplifying the signals from pixel elements, this amplifier provides a proper gain to boost the signal and reduces the noise contribution from the succeeding circuits. In terms of the noise sources of the amplifier, intrinsic noise generated by MOS transistors (inside the amplifier) is certainly one of the main sources.

$\mathbf{2}$

Figure 2.1: Conceptual diagram of a typical CIS architecture

Apart from that, the interference on the supply and ground lines caused by the switching activity of co-integrated digital processing circuits also plays a role, impacting the noise performance of the CIS. Hence, developing and optimizing a low-noise amplifier with improved power-supply rejection ratio (PSRR) and small silicon area becomes the main challenge for a column-parallel analog-front-end circuit of CIS.

In this work, considering the advantage of the pMOS transistor over its nMOS counterpart in minimizing the low frequency noise, we propose to investigate how a pMOS SF without body effect can further reduce the input-referred noise in the CIS. Moreover, in order to improve the PSRR of the column-level analog readout circuits and hence their noise performance, a single-ended cascode common source amplifier with local regulation adopted ground line has been as the operational trans-conductance amplifier (OTA) at the column level [6]. A prototype CIS has been built and fabricated in a 0.18 µm CIS process to prove the concept. Its noise performance has been characterized to further demonstrate the effectiveness of the proposed techniques.

# **2.2.** Sensor Architecture

#### **2.2.1.** Pixel Structure

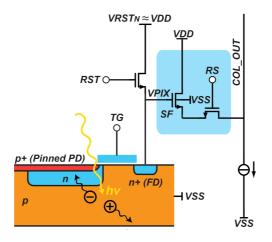

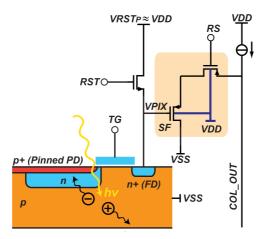

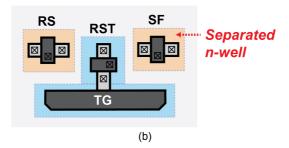

Figure 2.2 and Figure 2.3 show the pixel-level structures of a CIS, which employ nMOS and pMOS as the source follower, respectively. As discussed above, one of the pixel structures dedicated for low-noise CMOS image sensors uses a pMOS transistor as the SF in combination with a standard n-type PPD. In order to maintain the source-body junction reverse biased, the bulk terminal of the pMOS-based SF is conventionally connected to the supply voltage, sharing a common n-well with other pMOS transistors (*RST, RS*) in the same pixel, which results in the body effect.

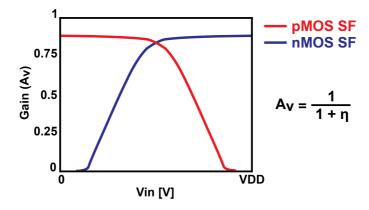

The MOS body effect trans-conductance  $g_{mb}$  refers to the change in the drain current by a change in body-source voltage  $V_{BS}$  with all other terminals held at a constant voltage [7]. To account for the fact that this  $g_{mb}$  is acting like a second gate, a  $V_{BS}$  controlled current source connected between the source and drain terminals can be used to model this dependence in the MOS small-signal model. Also in small-signal analysis, the body effect trans-conductance  $g_{mb}$  is often expressed as a fraction of the gate trans-conductance  $g_m$ . In an ideal case, the output resistance of both the current source and the SF are infinite, then the voltage gain  $(A_v)$  of the source follower approaches  $g_m/(g_m+g_{mb}) = 1/(1+\eta)$ . According to [7], the ratio  $\eta = g_{mb}/g_m$  increases with a higher substrate doping concentration and a lower body-source voltage.

Assume VPIX (VRST<sub>N</sub> and VRST<sub>P</sub> as shown in Figure 2.2 and Figure 2.3) is the reset level of pixel, the  $V_{BS}$  for nMOS SF and pMOS SF cases are given as:

nMOS SF:

$$V_{SBn} = (VPIX - V_{GS}) - VSS \tag{2.1}$$

pMOS SF:

$$V_{SBp} = (VPIX + V_{GS}) - VDD$$

(2.2)

where  $V_{GS}$  is the gate-source potential, VDD and VSS are the supply and ground of the pixel. Then we see that the body-source potential  $V_{BS}$  for pMOS SF is typically much lower than that of the nMOS SF. Therefore, the in-pixel pMOS SF suffers from a more pronounced body effect and hence results a much lower voltage gain (Figure 2.4), whose value depends on the input level.

Figure 2.2: Schematic of a nMOS-based SF pixel structure with body effect

Figure 2.3: Schematic of a pMOS-based SF pixel structure with body effect

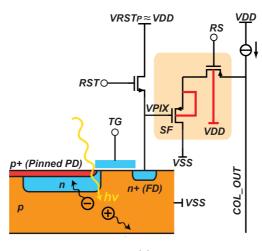

As shown in Figure 2.5, an effective approach to eliminate this undesirable body effect of an in-pixel SF is to employ a separated n-well for the SF transistor instead of sharing the common n-well with other in-pixel transistors [8]. Benefiting from this separation, the bulk terminal of the SF can be directly tied to the source terminal. Thus, the contribution of  $g_{mb}$  to the overall output trans-conductance of the SF could be ignored. As such, the voltage gain of a pMOS SF without body effect approaches unity. The simulation results show that the proposed SF structure achieves a -95mdB (0.988) voltage gain, which is nearly unity.

Figure 2.4: nMOS and pMOS SF cases: voltage gain of SF vs. input voltage

(a)

Figure 2.5: (a) Schematic of a pMOS-based SF pixel structure without body effect and (b) the corresponding in-pixel transistors layout

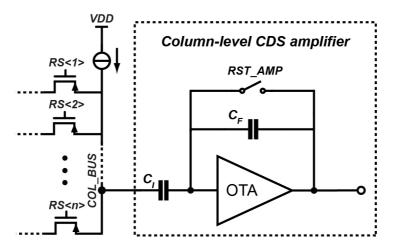

Figure 2.6: The column-parallel amplifier with CDS function

#### **2.2.2.** Column Amplifier Structure

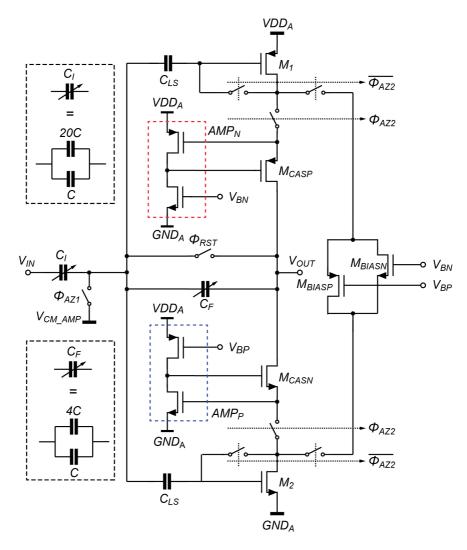

Following the pixel-level SF readout structure, the CIS front-end signal conditioning in each column is performed by a switched-capacitor CDS amplifier, as shown in Figure 2.6. In order to achieve an input-referred noise level that is small enough compared to the pixel's output noise, an improved common-source cascode amplifier has been used as the OTA for the column amplifier.

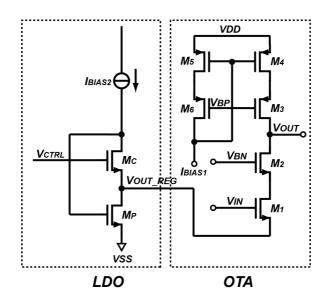

A conventional common-source cascode stage is inherently single-ended and senses the voltage difference between the input node and the ground rail. Accordingly, any noise that appears on the ground rail will also be manifest at the output node. To address this problem, we propose to locally generate a ground rail with a column-level low-dropout (LDO) regulator for each column amplifier, so as to reject interference from the common ground. Due to the fact that the loading currents for this column-level LDO regulator are known and approximately constant, the scheme implementation of this regulator can be kept simple to fit to the column pitch. A single-transistorcontrolled (STC) LDO based on a flipped voltage follower [9] is adopted as the topology for the regulator as shown in Figure 2.7. When  $V_{OUT REG}$ varies,  $M_C$  provides an error voltage at its drain, so as to control the drain current delivered by  $M_P$  and to regulate . With this control, the STC LDO is capable of providing sufficient loop gain and hence provides a PSRR to ground better than -38 dB within the frequency range of interest according to the simulation results

Figure 2.7: Common source cascode amplifier with local ground-rail regulator

### 2.2.3. Implementation Details

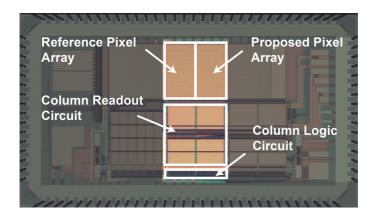

To evaluate the proposed noise reduction techniques, a CIS pixel array has been divided into two sub-arrays, one of which is implemented with the conventional pMOS-based SF structure with body effect as the reference pixel, and the other with the proposed SF structure without body effect. Each sub-array contains  $32(H) \times 64(V)$  pixels and features the same pixel pitch of 11 µm. Moreover, the size of the floating diffusion (FD) node and the studied SF transistors for both pixel sub arrays are identical in the layout.

The column-level switched-capacitor amplifiers are placed at the bottom of the pixel array with 11  $\mu$ m pitch. To enhance the dynamic range of the column amplifier, a programmable gain function is implemented by including switchable input and feedback capacitors. Five gain levels (×1, ×2, ×4, ×8, ×16) are provided, among which the ×16 gain step is designed to achieve the highest sensitivity and the best noise performance.

### 2.3. Experiment Results

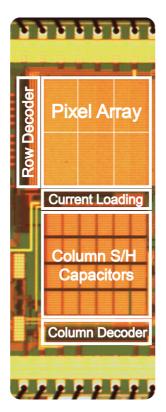

The test sensor with the proposed readout architecture has been fabricated in a  $0.18 \mu m$  CIS process technology. Figure 2.8 presents a microphotograph of the prototype chip.

Figure 2.8: Photograph of the prototype sensor

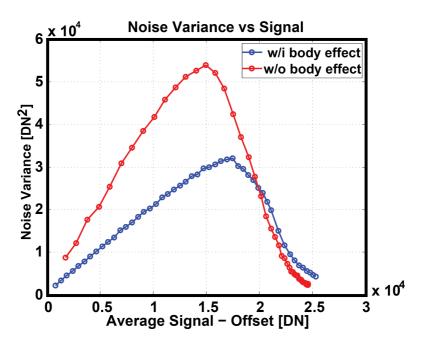

Figure 2.9: Conversion gain for pMOS source follower w/i and w/o body effect.

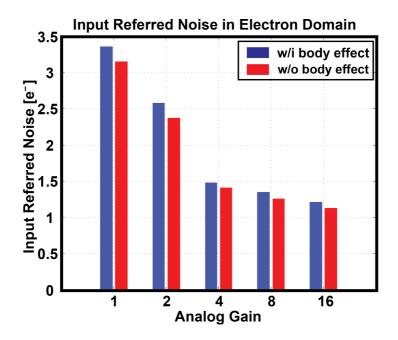

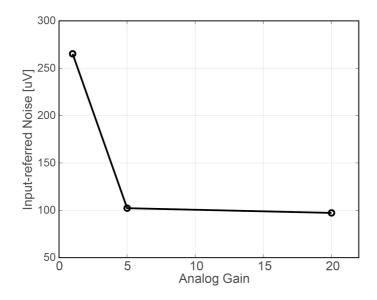

Figure 2.10: Input-referred noise vs. column amplifier gain.

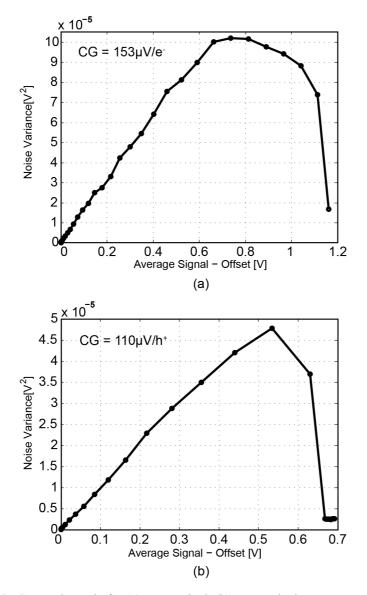

Figure 2.9 shows the measured plot of the noise variance as a function of the average output signal voltage value for both pixels. The conversion gain (CG) after the source follower for the reference pixel with body effect is 71  $\mu$ V/e<sup>-</sup>, while for the proposed pixel without body effect it is 122  $\mu$ V/e<sup>-</sup>. As the measured resultant CG is not only determined by the FD capacitance but also is associated to the voltage gain of the source follower. The proposed SF structure improves the conversion gain after the in-pixel SF by 42% compared to the reference pixel.

Temporal noise characterization has been done in dark and implemented by using the reset voltage as an input for the SF and keeping the transfer gate TG and the reset gate RST on during the measurement period. During the measurement, only correlated double sampling (CDS) was implemented. The RMS temporal noise is first measured by a board-level 16bit ADC and then referred to the electron domain by dividing it with the measured conversion gain. Figure 2.10 shows the input-referred noise for proposed pixels as a function of the column-parallel amplifier gain. For the gain steps of 1 and 2, the proposed pixel structure improves the input-referred noise by 10%. As the gain of the column amplifier

increases, the difference of the noise levels between the two types of pixels becomes smaller, which indicates that the effectiveness of succeeding noise reduction by the high gain of the column amplifier becomes dominant. By adopting the proposed pixel structure and amplifier configuration, the prototype CIS features an input-referred noise of  $1.1 \text{ e}^-$  with a column-level ×16 analog gain.

### **2.4.** Conclusions

A CMOS image sensor targeted for low noise applications has been presented in this chapter. It adopts various techniques both at pixel level and column level, including in-pixel nearly unity gain pMOS-based source followers and improved column-parallel amplifiers. By connecting the body terminal to the source, the loss of voltage gain from unity has been avoided for the in-pixel source follower. A single-ended cascode amplifier with ground-rail regulation is employed to achieve a better PSRR to ground. The prototype sensor with proposed readout architecture reaches a  $1.1 e^-$  input-referred temporal noise with a column-level ×16 analog gain.

### References

- M. Sakakibara et al., "A High-Sensitivity CMOS Image Sensor With Gain-Adaptive Column Amplifier," IEEE J. Solid-State Circuits, vol. 40, no. 5, pp. 1147-1156, May 2005.

- [2] E. Stevens et al., "Low-crosstalk and Low-Dark-Current CMOS image sensor technology using a Hole-Based Detector," Proc. ISSCC Dig. Tech. Papers, 2008, pp. 60-61, 595.

- [3] G. Yang et al., "BSI Low Light Level CMOS Image Sensor Employing p-type Pixel," Proc. IISW, Snowbird, USA, 2013.

- [4] B. Mamdy et al., "A low-noise, p-type, vertically-pinned and backside- illuminated pixel structure for image sensor application," Proc. IISW, Vaals, the Netherlands, 2015.

- [5] A. Boukhayma et al., "Temporal Readout Noise Analysis and Reduction Techniques for Low-Light CMOS Image Sensor," IEEE Trans. Electron Dev, vol. 63, no. 1, pp. 72-78, January 2016.

- [6] T. Christen, "A 15-bit 140  $\mu$ W scalable-bandwidth inverter-based  $\Delta\Sigma$  modulator for a MEMS microphone with digital output," IEEE J. Solid-State Circuits, vol. 48, no. 7, pp. 1605-1614, July 2013.

- [7] D. Binkley, Tradeoffs and Optimization in Analog CMOS Design: John Wiley & Sons Ltd, 2008, ISBN 978-0-470-03136-0, pp.121-122.

- [8] B. Razavi, Design of Analog CMOS Integrated Circuits: McGraw-Hill, 2001, ISBN 0-07-118815-0, pp. 231-232.

- [9] T. Man et al., "Development of Single-Transistor-Control LDO Based on Flipped Voltage Follower for SoC," IEEE Trans.Circuits Syst. I, Reg. Papers, vol. 55, no. 5, pp. 1392-1401, June 2008.

# 3

### Temporal Noise Analysis and Measurement of n-Type and p-Type Pixels with CMS Technique

This chapter is an extended version of the following published article:

<sup>•</sup> X.Ge, B. Mamdy and A. Theuwissen, "A comparative noise analysis and measurement for n-type and p-type pixels with CMS technique" in *IS&T International Symposium on Electronic Imaging*, Feb., 2016.

### **3.1.** Introduction

The increasing requirement for better visualizations under low light L conditions, especially in medical and diverse scientific fields, calls for the development of low noise CMOS image sensors. Such image sensor will be capable of operating under photon starved conditions and capturing visually distinguishable images, while being more cost efficient, power efficient [1] and providing higher spatial resolution than alternative imaging techniques [2]. Among different noise performance improving techniques and structures, a p-type pixel has been considered as one of the promising candidates for a low-noise CMOS image sensor. Thanks to the combination of a hole-based photo detector coupled with dedicated pMOS transistors, p-type pixels feature several advantages over their n-type counterparts, including lower dark current and better low frequency noise characters [3], [4], as well as more radiation hardness for the p-type pixel. However, compared with nMOS transistors, the use of pMOS as a source follower in p-type pixels suffers from a larger thermal noise due to its lower trans-conductance. Consequently, the doubled thermal noise power after correlated double sampling (CDS), together with the residual 1/f noise power, becomes one of the most significant factors that prevents the temporal noise of p-type pixels from achieving sub-carrier (electron or hole) temporal noise level. Different from doubling the thermal noise caused by CDS, as a circuit level noise reduction technique, correlated multiple sampling (CMS) has proved very effective not only for 1/f noise reduction, but also for thermal noise reduction [5]. However, its application to p-type pixels has not yet been analyzed or characterized in the open literature. Hence, an analysis and measurement of the CMS noise reduction effect for p-type pixels in comparison with n-type ones is meaningful for further temporal noise minimization.

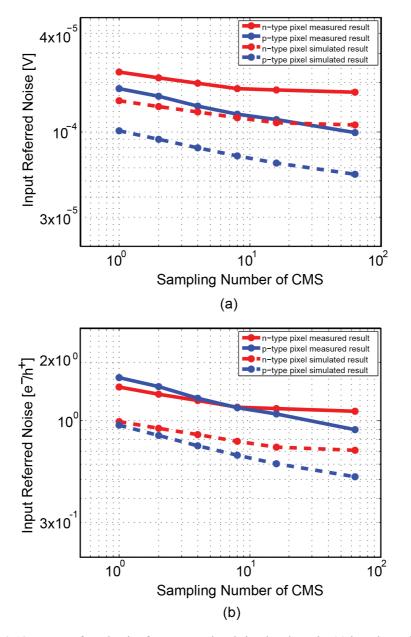

In this work, a temporal noise calculation and measurement, as well as a comparative analysis for both n-type and p-type pixels targeted for low noise image sensor application is presented. First, the noise power spectral density (PSD) of in-pixel source followers is evaluated, followed by an analysis of the sources of different noise components, such as thermal noise and 1/f noise. Then, the CMS noise transfer function for both n- and p-type pixels has been investigated in the frequency domain. Afterwards, a measurement of the temporal readout noise measurement based on the histogram variance value of the output signal for both pixels involving CMS has been performed. The measured results show that the input-referred temporal noise level of n-type and p-type pixels reach  $1.1e^{-}$  and  $0.88h^{+}$  respectively.

## **3.2.** Noise Analysis with CMS Technique **3.2.1.** Noise Sources of Pixel

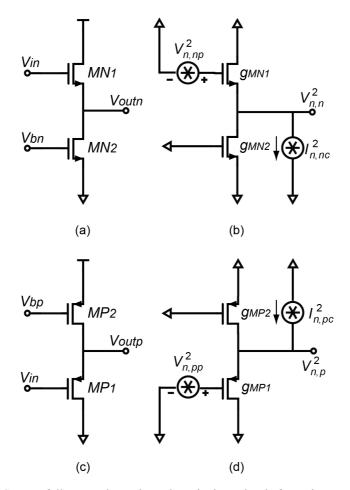

In the following noise calculation, we consider the flicker noise and thermal noise originated from the pixel part as the dominant noise source. Figure 3.1 shows the schematic of source followers used in n-type and p-type pixels as well as the circuit including noise sources. The nMOS  $MN_1$  and pMOS  $MP_1$  are the pixel-level input transistors, while  $MN_2$  and  $MP_2$  serve as the bias current source transistors which are implemented at the column-level,  $V_{bn}$  and  $V_{bp}$  are the equivalent biasing voltage for the current sources,  $V_{in}$  is the input voltage,  $V_{outn}$  and  $V_{outp}$  are the output voltages. In the noise model,  $g_{mn1}, g_{mn2}, g_{mp1}$  and  $g_{mp2}$  are the trans-conductances,  $V_{n,np}^2, V_{n,pp}^2, I_{n,nc}^2$ , and  $I_{n,pc}^2$  are the noise sources, the output noise is expressed as  $V_{n,n}^2$  and  $V_{n,p}^2$ .

An established fact for in-pixel source followers is that the driving source impedance is moderate while the input impedance is quite high. Therefore, in this noise model, the input-referred noise current source can be neglected, and only the noise voltage source needs to be taken care of [6]. Assuming that all transistors operate in saturation, the noise PSD for n-type [7] and p-type source followers can be represented as:

$$\begin{split} S_{n,n}(f) &= \overline{v_{n,n}^2} = \frac{3}{8} kT \frac{1}{g_{mn1}} (1 + \frac{g_{mn2}}{g_{mn1}}) \\ &+ [N_{fmn1} + N_{fmn2} (\frac{g_{mn2}}{g_{mn1}})^2] \frac{1}{f} \quad (3.1) \end{split}$$

$$\begin{split} S_{p,n}(f) &= \overline{v_{n,p}^2} = \frac{3}{8} kT \frac{1}{g_{mp1}} (1 + \frac{g_{mp2}}{g_{mp1}}) \\ &+ [N_{fmp1} + N_{fmp2} (\frac{g_{mp2}}{g_{mp1}})^2] \frac{1}{f} \quad (3.2) \end{split}$$

where  $k = 1.3807 \times 10^{-23}$  J/K is the Boltzmann constant, T is the absolute temperature, f is the frequency, and  $N_{fmn1}$ ,  $N_{fmn2}$ ,  $N_{fmp1}$  and  $N_{fmp2}$  are the flicker noise parameter of  $MN_1$ ,  $MN_2$ ,  $MP_1$  and  $MP_2$ , respectively.

Figure 3.1: Source follower schematic and equivalent circuit for noise analysis. (a) n-type source follower; (b) n-type source follower including noise sources; (c) p-type source follower; (d) p-type source follower including noise sources.

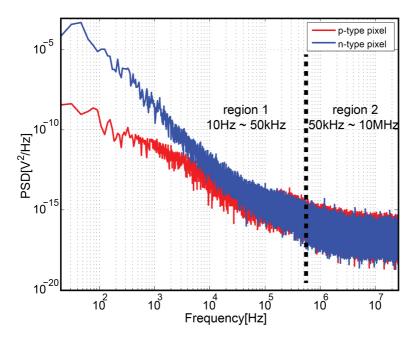

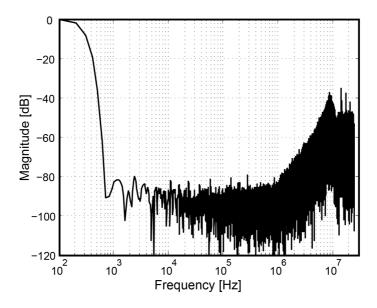

Figure 3.2: The noise PSD for the n-type and p-type pixel.

The noise PSD of the p-type and n-type pixels have been first extracted from the measurement. The measurement details will be mentioned in Section 3.4. As shown in Figure 3.2, the p-type pixel exhibits less 1/f noise power density in the low frequency region than the n-type one, due to a naturally formed "buried channel" inside the pMOS transistor, which could carry the holes in the channel at some distance from the "dirty" silicon oxide-silicon interface.

Moreover, the thermal noise or the noise floor is also obtained from the extracted data, which are  $1.68 \times 10^{-15} \text{ V}^2/\text{Hz}$  for the n-type source follower and  $2.76 \times 10^{-15} \text{ V}^2/\text{Hz}$  for the p-type one respectively. The thermal noise PSD in this feature is due to the fact that the thermal noise of source followers is determined by the trans-conductance  $g_{mn1}$  and  $g_{mp1}$ . If the input transistors in the n-type and p-type pixels have the same width/length ratio and are biased with the same current,  $g_{mp1}$  for the pMOS transistor will be smaller than  $g_{mn1}$  as a result of a lower carrier mobility of the holes.

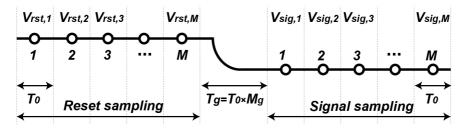

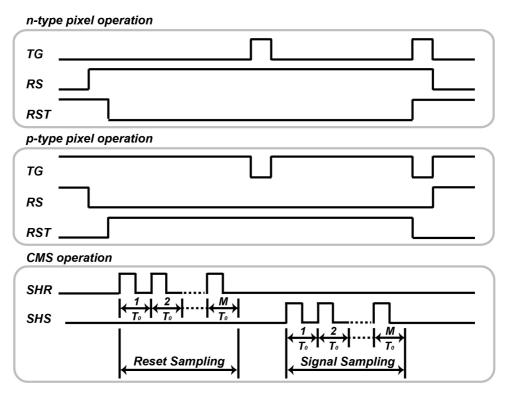

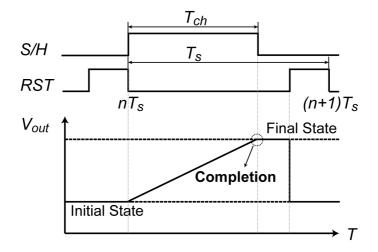

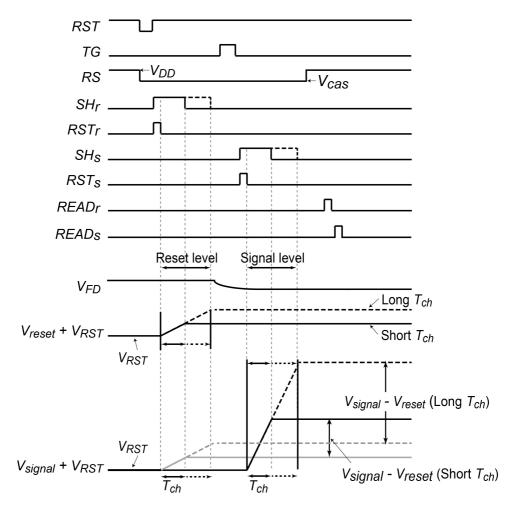

**3.2.2.** CMS Operation and Noise Reduction Effect The CMS operation has been considered as an alternative to the CDS operation for CIS system [8]. The sampling diagram of CMS operation for CIS is depicted in Figure 3.3. In Figure 3.3,  $T_0$  is the sampling period;  $T_g = M_g T_0$  is the interval period between two groups of multiple sampling, where  $M_q$  is an integer. Firstly, reset levels  $(V_{rst,1}, V_{rst,2}...V_{rst,M})$  and signal levels  $(V_{sig,1}, V_{sig,2}...V_{sig,M})$  are sampled for M times sequentially. The delay between each correlated sampling levels (e.g.  $V_{rst,1}$  and  $V_{sig,1}$ ,  $V_{rst,2}$  and  $V_{sig,2}$ ) is  $(M + M_a)T_0$ . Then, the sum of reset levels and signal levels, which are obtained from M-times sampling, are subtracted from each other. Finally, the output signal can be derived by dividing the differential result by the factor of M. As such, the correlated noise and the low frequency noise can be eliminated and reduced by the subtraction or differentiation in a way similar to standard CDS. In addition, the input-referred thermal noise amplitude also gets a reduction with a factor that is inversely proportional to  $\sqrt{M}$  thanks to the averaging effect [8]-[10].

Due to the differentiation and averaging procedures in the CMS configuration, the effectiveness of the CMS noise canceller can be characterized as a pass-band narrowing operation, or a noise power density reduction operation by oversampling [11]-[12].

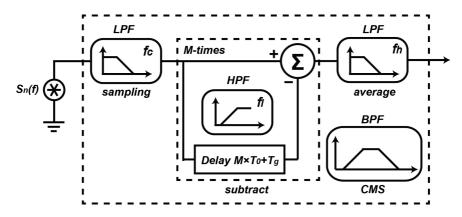

Let's first consider that the noise reduction effect of CMS as the result of the bandwidth-narrowing operation. As interpreted by Figure 3.4, in the initial sampling phase, the signal is first sampled by the sampling circuits with a cut-off frequency  $f_c$ . Next, the operation of subtracting two correlated levels can be interpreted as a discrete time high-pass filter with an equivalent cut-off frequency  $f_l$ , which corresponds to the time interval between two group sampling operations. Finally, the output noise power are low-pass filtered for the second time with another equivalent cut-off frequency  $f_h \gg$  $f_c$  by virtue of the bandwidth limitation effect. Therefore, the entire CMS operation is equivalent to a continuous time band-pass filter whose first zero  $f_l$  and first pole  $f_h$  are respectively located at:

$$f_l = \frac{1}{2\pi (M + M_g)T_0}$$

(3.3)

$$f_h = \frac{\sqrt{2}}{\pi (M + M_g) T_0}$$

(3.4)

Figure 3.3: The sampling diagram of CMS operation

Figure 3.4: The simplified model of a CMS circuit

As such, the bandwidth of the band-pass filter can be defined as:

$$f_h = \frac{2\sqrt{2} - 1}{2\pi (M + M_q)T_0}$$

(3.5)

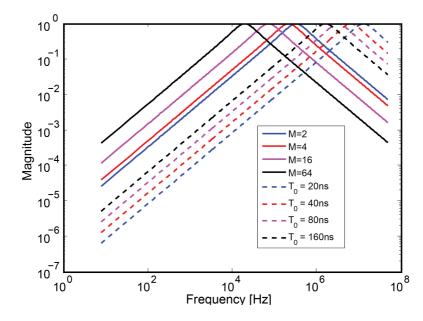

Figure 3.5 shows the equivalent transfer function of the CMS band-pass filter as a function of  $(M + M_g)T_0$ . With a fixed sampling period  $T_0$ , and a decreasing M, the pass-band shifts to a higher frequency band with a widened bandwidth. Consequently, more low frequency noise could be attenuated, while more thermal noise in the high band will be integrated due to the wider bandwidth. On the other hand, if M is a constant value and  $T_0$ increases, both the resonant frequency and the pass-band will be shifted along with the sampling period. Thus, the effectiveness of noise reduction for both 1/f noise and thermal noise is greatly depending on M or  $T_0$ .

Instead of considering the CMS thermal noise reduction effect as a bandwidth narrowing operation, it can also be characterized as an oversampling operation, i.e. applying a sampling frequency higher than the

Figure 3.5: Equivalent CMS band-pass transfer function

Nyquist rate. If the sampling rate of CMS is increased from the Nyquist criterion  $f_{s,ny} = 1/(M + M_g)T_0$  to a new frequency  $f_s = 1/T_0$ , the noise power density of the white band thermal noise is reduced with the ratio of the sample rates, N, where

$$N = \frac{f_s}{f_{s,ny}} = M + M_g \tag{3.6}$$

Therefore, with a fixed sampling interval  $(M + M_g)T_0$ , as M increases, the thermal noise is reduced by a factor of  $\sqrt{M}$  while the reduction of the 1/f noise in the low frequency region keeps the same for different M. Accordingly, for a given sampling interval, with a larger value of M and a shorter sampling period  $T_0$ , a relatively smaller thermal noise can be obtained without sacrificing the reduction of the 1/f noise.

### **3.3.** Noise Calculation with CMS Technique

Based on the above analysis, the post-CMS noise behavior for both n-type and p-type pixels can be modeled in MATLAB by calculating their output noise power spectrum density  $S_n(f)$  as well as the noise transfer function, and their final integrated noise power can be estimated. The input noise PSD  $S_n(f)$  used in this calculation is extracted from the test chips as presented in Section 3.2.1. Furthermore, the output noise power spectrum after CMS process can be expressed in frequency domain as:

$$\overline{v_{n,CMS}^2} = \frac{1}{M^2} \int_0^\infty S_n(f) \frac{1}{1 + (f/f_c)^2} |H_{CMS}(f)|^2 df \qquad (3.7)$$

where  $H_{CMS}(f)$  equals to:

$$|H_{CMS}(f)| = |\frac{2sin(\pi f \cdot MT_0)sin(\pi f \cdot (M + M_g - 1)T_0))}{sin(\pi f \cdot T_0)}| \qquad (3.8)$$

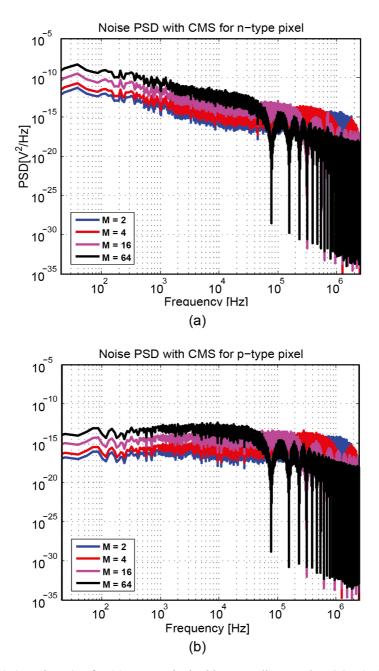

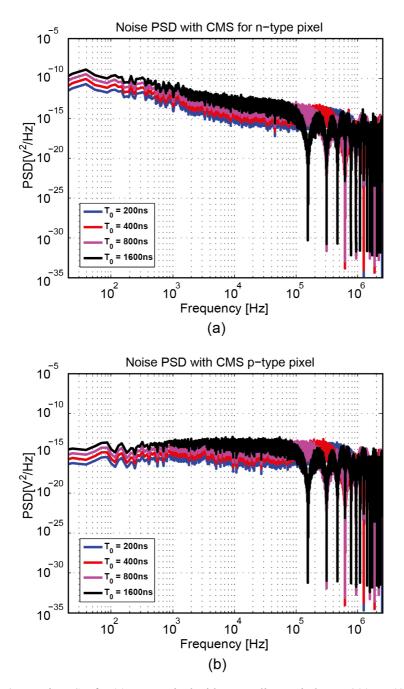

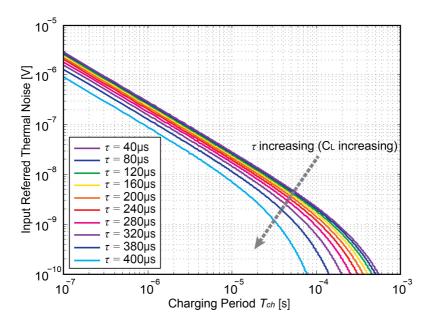

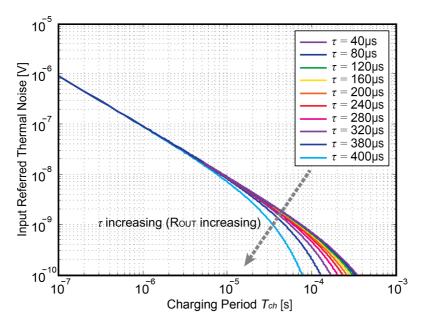

Figure 3.6 to Figure 3.8present the calculated results. In Figure 3.6 (a) and (b), the noise PSD for both type pixels are calculated by using the constant sampling period  $T_0$ = 100 ns and a variety of values for the number of sampling times M = 2, 4, 16 and 64. Note that as M increases, the noise PSD decreases at higher frequency region and increases at lower frequency region. This indicates that as a result of a longer interval period  $(M + M_g)T_0$ , with M increasing, the 1/f noise suppression effect by CMS operation declines while the thermal noise reduction tendency remains.

Figure 3.7 (a) and (b) shows the noise PSD as a function of sampling period  $T_0$ = 200 ns, 400 ns, 1600 ns and 6400 ns with a constant sampling number M = 4. The noise PSD reduction for both 1/f noise and thermal noise are primarily consistent with the results in (a) and (b), This indicates that, for a constant sampling number M, increasing  $T_0$  also leads to a lower resonant frequency for the pass-band bandwidth, thus reducing the effectiveness of CMS for 1/f noise reduction.

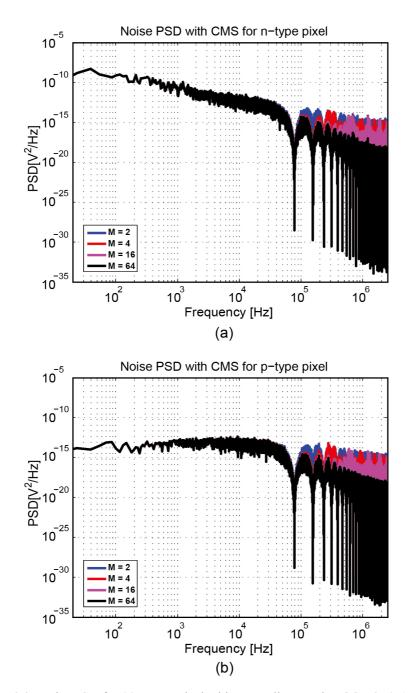

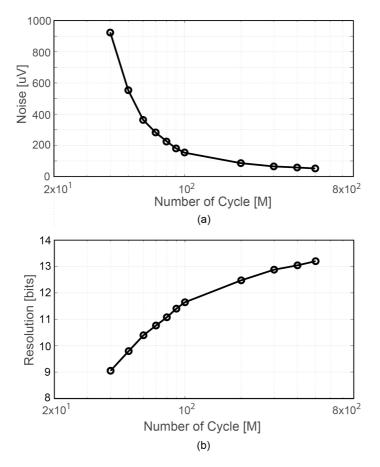

As shown in Figure 3.8 (a) and (b), the noise PSD is obtained as a function of  $M_g = 2$ , and M = 2, 4, 16 and 64 within a fixed sampling interval  $(M + M_g)T_0 = 6.4 \ \mu s$ . Significant noise reduction in the high frequency region can be observed, while the noise PSD in low frequency region keeps almost the same with variant M. Thus, thanks to the oversampling operation, the wide-band thermal noise can be effectively compressed with an increased M, while the effectiveness of low frequency noise reduction stays the same.

In order to clarify and estimate the residual value of different noise components after CMS operation; the noise PSD in different frequency regions (e.g. region 1 and 2, as shown in Figure 3.2) has been integrated

Figure 3.6: Noise PSD for (a) n-type pixel with a sampling number M = 2, 4, 16, 64 and sampling period  $T_0 = 100$  ns; (b) p-type pixel with a sampling number M = 2, 4, 16, 64 and sampling period  $T_0 = 100$  ns.

42

Figure 3.7: Noise PSD for (a) n-type pixel with a sampling period  $T_0 = 200$  ns, 400 ns, 800 ns, 1600 ns and sampling number M = 4; (b) p-type pixel with a sampling period  $T_0 = 200$  ns, 400 ns, 800 ns, 1600 ns and sampling number M=4.

Figure 3.8: Noise PSD for (a) n-type pixel with a sampling number M = 2, 4, 16, 64 and  $(M + M_g)T_0$  equals to a constant 6.4 µs; (b) p-type pixel with a sampling number M = 2, 4, 16, 64 and  $(M + M_g)T_0$  equals to a constant 6.4 µs.

Figure 3.9: Integrated simulated noise for n-type and p-type pixel at region1 and region2

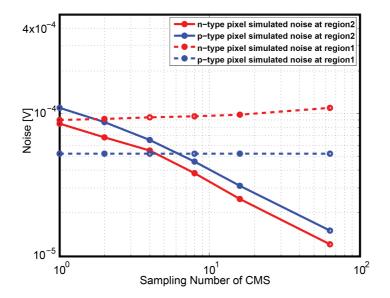

separately. Figure 3.9 compares the n-type and p-type noise in each region after CMS operation as a function of M, where M = 1, 2, 4, 8, 16, 64 and  $T_0 = 100$  ns. At M = 1, the integrated noise in region 1 for the n-type transistor is higher than that of the p-type noise, and lower in region 2, which indicates that a n-type pixel has a larger 1/f noise while a p-type pixel suffers from a higher thermal noise, as has been analyzed in Section 3.2.1. As M increases, on one hand, the integrated noise level in the high frequency region (region 2) for both types of pixels is suppressed until M = 64, with a factor of 72% for the n-type pixel and 80% for the p-type pixel respectively. On the other hand, the integrated noise amplitude in the low-frequency region (region 1) is slightly increased in proportion to M. These results suggest that it is the low frequency noise that limits the total noise reduction effect of the pixel source follower.

In summary, based on the above calculation, by means of the CMS operation, the final noise reduction factor is 31% for the n-type pixel and 50% for the p-type.

## **3.4.** Noise Measurement with CMS Technique

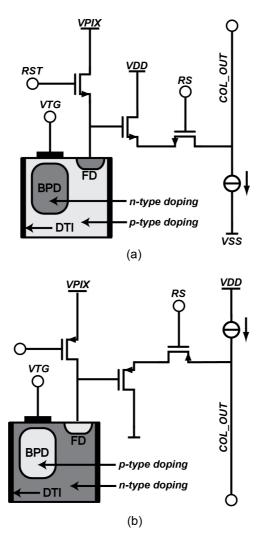

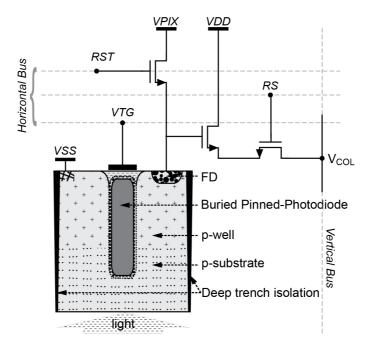

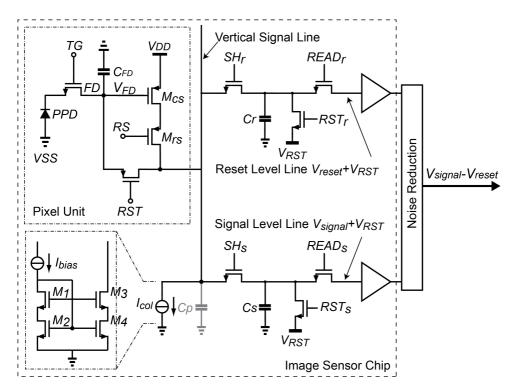

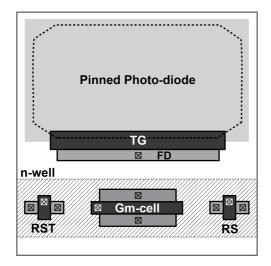

To evaluate the CMS noise reduction effect for p-type pixels in comparison with n-type ones, 2 sub-groups of pixels have been implemented in the test chip. One of which is fabricated with n-type pixels process and the other one with p-type pixel process. The front-end-of-line (FEOL) and back-end-of-line (BEOL) of both pixel types were designed and processed respectively in 90 nm and 65 nm technology, respectively. Both sub-groups feature the same pixel pitch of 2.5  $\mu$ m. As shown in Figure 4.2 (a) and (b), the 3D pixel structure isolated by deep trench isolation (DTI) technology integrates a back-side-illuminated buried vertically pinned-photodiode (BPD) as well as a planar transfer gate (TG) in each pixel [13, 14]. Unlike the arrayed image sensor, the test chip includes only one effective pixel for each test structure owing to the area limitation. For both pixels, the gate width and length of the studied SF transistors are 0.2  $\mu$ m/0.7  $\mu$ m. The current sources for both SFs are set to 2  $\mu$ A.

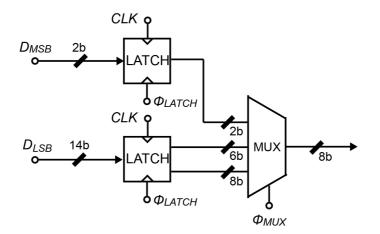

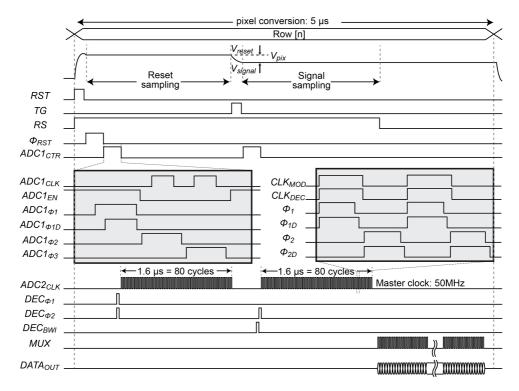

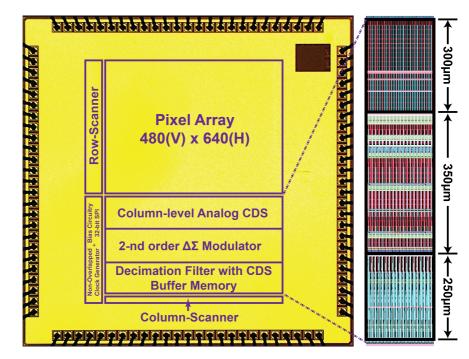

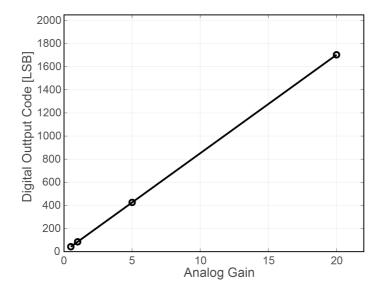

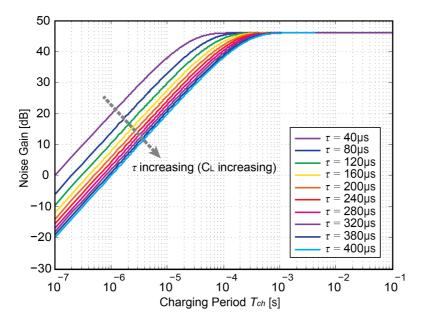

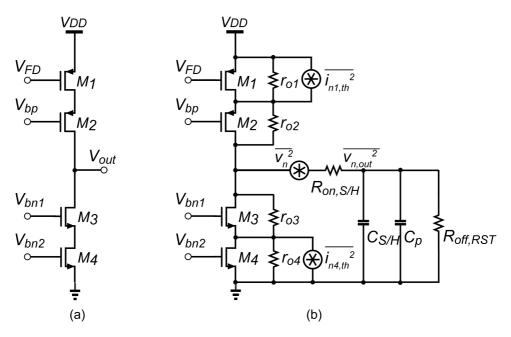

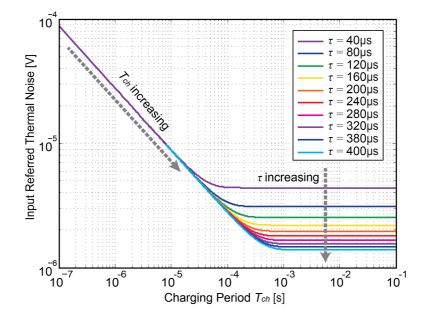

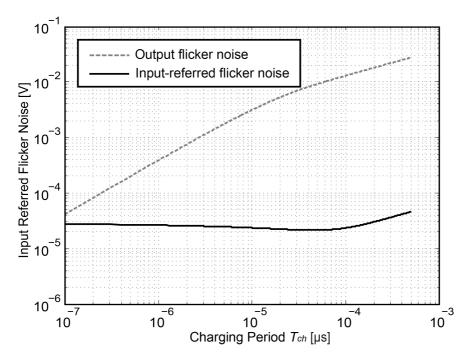

In comparison with standard n-type pixels, all doping species type used to form the BPD and TG are inverted in the p-type pixel and the in-pixel MOS transistors are also switched from nMOS to pMOS. Hence, as can be seen from Figure 3.11, the transistor gate in the p-type pixel has to be driven low to switch on and high to switch off, while the other timing details remains the same.