# Review of Inorganic Non-metallic Materials in Power Electronics Packaging Application

Chen, Junwei; Tian, Tiancheng; Gu, Chao; Zeng, Huidan; Hou, Fengze; Zhang, Guoqi; Fan, Jiajie

10.1109/TPEL.2025.3550882

**Publication date**

**Document Version** Final published version

Published in

IEEE Transactions on Power Electronics

Citation (APA)

Chen, J., Tian, T., Gu, C., Zeng, H., Hou, F., Zhang, G., & Fan, J. (2025). Review of Inorganic Non-metallic Materials in Power Electronics Packaging Application. *IEEE Transactions on Power Electronics*, 40(8), 10509-10530. https://doi.org/10.1109/TPEL.2025.3550882

# Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# Review of Inorganic Nonmetallic Materials in Power Electronics Packaging Application

Junwei Chen, Tiancheng Tian, Chao Gu, Huidan Zeng, Fengze Hou, Senior Member, IEEE, Guoqi Zhang, Fellow, IEEE, and Jiajie Fan, Senior Member, IEEE

Abstract—Power electronics devices, pivotal in advancing electronic system technology, are essential for energy saving, enhancing power control efficiency, reducing noise, and minimizing size and volume. The evolution of power modules is based on innovative packaging structures, technologies, and materials. This article provides a comprehensive review of inorganic nonmetallic packaging materials and technologies in power electronics packaging. It first analyzes the packaging structures and trends of power electronics. The article then discusses inorganic nonmetallic encapsulants such as cement and glass in detail. It also reviews traditional ceramic substrates and elaborates on the advantages of multilayer ceramic technologies, including low-temperature co-fired ceramics, as substrates, while looking forward to the commercialization of inorganic composite substrates such as SiCp/Al matrix composites and diamond. Subsequently, the article overviews inorganic nonmetallic fillers for thermal interface materials, emphasizing the application of two-dimensional materials such as graphene and boron nitride, and introduces inorganic nonmetallic phase change materials. Finally, it explores the application and future development trends of inorganic nonmetallic materials in embedded packaging technologies.

*Index Terms*—Embedded packaging technology, encapsulation materials, inorganic nonmetallic materials, power electronics packaging, substrate materials, thermal interface materials.

# I. INTRODUCTION

OWER electronic devices are essential components in contemporary electronic systems that enable the effective conversion of various types of electrical energy. High-

Received 19 January 2025; accepted 8 March 2025. Date of publication 14 March 2025; date of current version 26 May 2025. This work was supported in part by the National Natural Science Foundation of China under Grant 52275559. Recommended for publication by Associate Editor K. Ngo. (Corresponding author: Jiaije Fan.)

Junwei Chen, Tiancheng Tian, Chao Gu, and Jiajie Fan are with the Institute of Future Lighting, Academy for Engineering & Technology, Shanghai Engineering Technology Research Center of SiC Power Device, Fudan University, Shanghai 200433, China (e-mail: chenjw24@m.fudan.edu.cn; 24110860049@m.fudan.edu.cn; jiajie\_fan@fudan.edu.cn).

Huidan Zeng is with the School of Materials Science and Engineering, East China University of Science and Technology, Shanghai 200237, China (e-mail: hdzeng@ecust.edu.cn).

Fengze Hou is with the Institute of Microelectronics of Chinese Academy of Sciences, Beijing 100029, China (e-mail: houfengze@ime.ac.cn).

Guoqi Zhang is with the Department of Microelectronics Engineering, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: g.q.zhang@tudelft.nl).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TPEL.2025.3550882.

Digital Object Identifier 10.1109/TPEL.2025.3550882

power energy conversion equipment, such as those used in rail transportation, electromagnetic emission systems, renewable energy conversion, and smart grids, must operate under rapid response, high frequency, and transient conditions. These systems frequently encounter challenges such as high peak startup currents, prolonged fault operations, and complex multiphysics field coupling involving electrical, thermal, and mechanical elements [1], [2]. Wide bandgap (WBG) semiconductors, such as silicon carbide (SiC) devices, can push the output power of power conversion equipment to exceed the 100 MW level through organic series/parallel connections. Additionally, low-inductance packaging technology, which involves heterogeneous integration, supports the technical foundation for elevating the switching frequencies from hundreds of Hz to 10 MHz, thereby boosting the power density of the equipment [3], [4].

WBG power components surpass traditional silicon (Si), yet the latest generation of high-voltage, high-power devices faces challenges of doubled electrical stress, wider temperature fluctuations, more severe electromagnetic compatibility issues, and harsher thermal environments [5], [6]. The intensified coupling of electrical, magnetic, thermal, and mechanical stress fields has exacerbated the conditions, doubling the failure rate [3], [7]. The high failure rate of power devices stems primarily from the internal interconnection among various heterogeneous materials, involving electrical, thermal, and microscopic mechanical forces [6]. Externally, these devices encounter complex and variable operating conditions, such as radiation, humidity, and chemical corrosion [8], [9], [10]. Harsh environmental factors like high temperature and humidity can penetrate and diffuse into nonhermetic packaging materials (e.g., epoxy resin, silicone gel) with low glass transition temperatures (Tg), potentially leading to electrochemical corrosion and even the "popcorn" effect [10]. Even high radiation conditions can result in the degradation of the reliability of the die's oxide layer [11], [12]. In contrast, inorganic nonmetallic materials, with superior thermal stability, electrical insulation, and mechanical strength, are increasingly preferred for power device packaging [13]. These materials offer protection from mechanical, chemical and radiation hazards, enable heat dissipation, and ensure efficient signal and power distribution for optimal performance. Therefore, this work provides a comprehensive review of inorganic nonmetallic packaging materials for power electronics packaging. It compares the various technologies, materials, their advantages, and the main challenges encountered so far. Finally, potential future

0885-8993 © 2025 IEEE. All rights reserved, including rights for text and data mining, and training of artificial intelligence and similar technologies. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

development directions are summarized, which can serve as a guide for future work in this field.

In this article, the organization is as follows. In Section II, the development trends of power electronics packaging materials and structures are reviewed. The different packaging forms of power devices, the inorganic nonmetallic packaging materials used, and future development trends are overviewed. In Section III, inorganic nonmetallic encapsulation materials (mainly cement and glass) are thoroughly surveyed. In Section IV, a comprehensive review of inorganic nonmetallic substrate materials for power electronics is provided. In Section V, the majority of existing inorganic nonmetallic fillers for thermal interface materials (TIMs) and phase change materials (PCMs) are discussed. In Section VI, the advantages, challenges, and potential development directions of embedded packaging technology are examined. Finally, Section VII concludes this article.

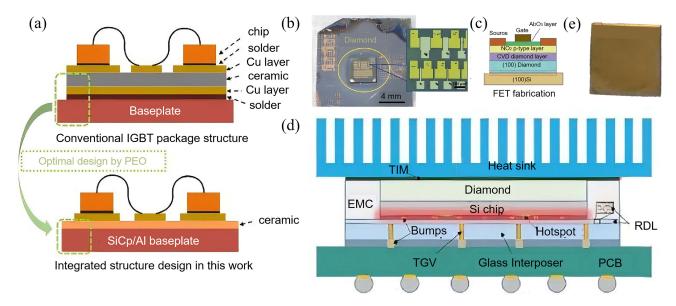

# II. POWER ELECTRONICS PACKAGING MATERIALS AND STRUCTURES DEVELOPMENT TRENDS

The growing demand for high-efficiency, reliable, and lightweight equipment in industrial and energy systems has heightened the importance of power semiconductor devices operating at higher voltage and current levels [14], [15]. Traditional Si-based insulated-gate bipolar transistors (IGBTs) have nearly reached their theoretical performance limits. The new generation of semiconductor materials, which involves SiC-driven superior electrical and thermal performance, enables higher power density and reduced power loss [16]. By reducing thermal resistance (Rth J–C) and increasing the maximum operating temperature (Tj max) of modules to exceed 200 °C, they enhance power density, current capability, and long-term reliability [4], [5], [17], [18], [19]. SiC MOSFETs, with their lower die area for a given ON-state resistance, result in reduced capacitance, giving them the potential for faster switching.

However, with the gradual maturity of new material power semiconductor devices such as SiC and GaN chips, as well as the development of more advanced chip technologies, the current power device packaging technologies are increasingly unable to meet the packaging requirements of these chip technologies. This trend limits the full potential of chip performance, such as operating temperature, short-circuit capability, switching speed, and efficiency. To overcome these challenges, design enhancements, such as Kelvin connections, orthogonal placement of power coupled with gate loops, and symmetrical layouts of power and gate circuits, improve performance and reliability [18], [19], [20]. However, packaging design usually emphasizes only electrical and thermal performance metrics within the device, including parasitic parameters and variations in temperature and pressure in real-world applications, which are often neglected. Consequently, maintaining consistent device performance across various scenarios becomes challenging. To address these issues, a range of advanced packaging materials and technologies, as well as packaging formats, are being developed and refined.

Mechanical performance (CTE matches chip)

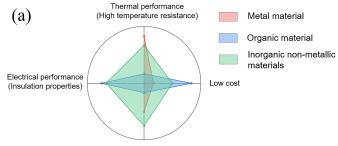

Fig. 1. (a) Relevant properties comparison of metals, organic materials, and inorganic nonmetallic packaging materials. (b) Schematic of a conventional packaging power device.

#### A. Power Electronics Packaging Materials

The performance of packaging materials largely determines the performance of power devices. The materials required for power devices are mainly categorized into metals, organic materials, and inorganic nonmetallic materials. With the advancement of power electronics technology, the requirements for the electrical, thermal, and mechanical properties of materials have become increasingly demanding. A comparison of the relevant properties is shown in Fig. 1(a) and a schematic of a conventional packaging power device is shown in Fig. 1(b). Metals, with their excellent electrical conductivity, play a crucial role in internal electrical interconnections, such as die attach materials, wire bonding, and gold stud bumps used for interconnections [21], [22], [23], [24], [25], [26]. In addition, the superior thermal conductivity of metals makes them ideal for use as power device frame materials and heat sinks. Organic materials, on the other hand, are widely used in encapsulants and TIMs due to their outstanding insulating properties, ease of processing, and bonding capabilities. Inorganic nonmetallic materials are renowned for their excellent mechanical properties and thermal stability. They are commonly used as substrate materials for power devices and have also found applications in encapsulants and thermal interface materials, among other areas.

### B. Discrete Packaging

Discrete power devices, including power transistors, thyristors, MOSFETS, and IGBTs, are commonly used in medium and low-power applications, such as consumer electronics and industrial drives. Packaging options represented by TO-247, SOT227, D3PAK, and D2PAK are favored for their simplicity,

| Device types                      | Sample types          | Types of inorganic packaging material | Organization                     | Year | Ref. |

|-----------------------------------|-----------------------|---------------------------------------|----------------------------------|------|------|

| Si MOS                            |                       | Passivation glass                     | East China University of         | 2024 | [28] |

| SiC SBD                           | 0 3                   | Encapsulation glass                   | Science and Technology           | 2023 | [29] |

| SiC SBD                           |                       | Encapsulation cement                  | University of Central<br>Florida | 2008 | [30] |

| Power transistor for GaN-SiC HEMT | AMPLEON<br>OZPAM SEPP | Ceramic shell                         | Ampleon<br>(CLF24H4LS300P)       |      |      |

TABLE I

USE OF INORGANIC NONMETALLIC MATERIALS IN PACKAGING FOR DISCRETE POWER DEVICE

cost-effectiveness, and versatility. Packaging choices depend on component type, application needs, thermal management, electrical properties, and hermetic sealing. Inorganic nonmetallic materials (see Table I), widely used for insulation in power devices, such as passivate P-N junctions with fused silicate glass, serve as encapsulants to isolate and protect the device environment. These materials, particularly in high-voltage and high-power rectifiers, outperform traditional polymers including e-resins and polyimides. Ceramic materials, known for their high insulation, thermal stability, and mechanical strength, are well-suited for shell packaging that requires mechanical support, environmental protection, and electrical connectivity in high-reliability electronics, such as those used in aerospace and military sectors [27]. Glass, valued for its excellent bonding capabilities, is also employed to seal bases and caps in cavity structures and metal can packages requiring airtightness. In extreme environments, involving space exploration and nuclear power, the integration of high-performance inorganic nonmetallic materials with simple, discrete device designs ensures reliable operation under high temperatures, radiation, and frequency bandwidth demands.

#### C. Module Packaging

Advancements in power device manufacturing technologies, processes, and packaging, are driving the evolution of power conversion equipment to address higher power requirements and more demanding operating conditions [17], [31]. Discrete power devices, which handle loads individually, face limitations due to their cooling capacity and material current-carrying limits. In high-voltage applications, elevated internal electric fields can easily lead to breakdown and failure. Consequently, power modules, which optimize the cost benefits of existing power devices through series and parallel configurations, have emerged as the preferred solution for high-power applications devices [32].

High-voltage devices consist of interconnected heterogeneous structures that integrate various materials. The conductive, thermal, and strain properties of these materials are closely interrelated. To boost power levels, it is crucial to enhance the maximum operating temperature of power chips, which involves advancements in high-melting-point semiconductor materials, high-temperature soldering technologies, and plastic encapsulation with a broad operating temperature range for chips and packaging. Most available SiC modules are advanced versions of Si-based IGBT modules. Infineon's PrimePACK modules have increased the number of parallel chips from 4 to 6, raising the current capacity from 450 to 1000 A. Additionally, the switching speed of internal chips has improved from tens of nanoseconds to a few nanoseconds to meet high power density and efficiency requirements. Infineon's easy modules demonstrate improved packaging density, being 60% smaller in volume [18], [19], [32], [33]. Table II illustrates new power module products and their performance, highlighting the application of inorganic nonmetallic material components in increasingly complex module structures. These advancements reflect a trend towards reduced inductance and thermal resistance. This shift indicates higher demands on packaging materials. As the power density and current levels of WBG semiconductors, including SiC and GaN, increase along with complex operating environments and impact loads, power devices encounter significant time-varying losses and thermal stress during their service life. These conditions can cause mechanical fatigue and damage to internal materials, leading to aging and potential failure of the device packaging structure [34], [35], [36].

# III. ENCAPSULATION MATERIALS

Encapsulation materials are essential in power electronic modules, serving to isolate the internal and external environments of the module and prevent electrical breakdown, chemical corrosion, moisture infiltration, and harmful radiation [49].

TABLE II

USE OF INORGANIC NONMETALLIC MATERIALS IN ADVANCED POWER MODULE

| Device<br>types                | Sample types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Dimen<br>sion<br>(mm)  | Types of<br>Inorganic<br>packaging<br>material | Inductance (nH) | Rth<br>(°C/W | Organization                                                    | Year | Ref. |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------|-----------------|--------------|-----------------------------------------------------------------|------|------|

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 79.2×<br>66.4×<br>10.8 | LTCC-<br>derived<br>interposer                 | 2.3             |              | University of Arkansas                                          |      | [37] |

|                                | A. A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34×40<br>× 1.13        | Al <sub>2</sub> O <sub>3</sub> -<br>DBC        | 1.3             |              | Huazhong University of Science and Technology                   |      | [18] |

| DCC                            | o hand had                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24 ×<br>18 ×<br>3.6    | AIN-DBC                                        | 1.51            |              | Stony Brook University                                          | 2024 | [38] |

| DSC                            | AC DC- terminal Low side gate High side gate DC+ terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ı                      | AlN<br>ceramic<br>layer                        | 0.93            | 0.073        | University of Arkansas                                          |      | [39] |

|                                | Troping Co.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                        | AIN-DBC                                        | 3               | 0.081        | Huazhong University of Science and Technology                   |      | [20] |

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        | Al <sub>2</sub> O <sub>3</sub> -<br>DBC        | 2.02            |              | Xi'an Jiaotong University                                       | 2022 | [40] |

|                                | Te taken (in the control of the cont |                        | Si <sub>3</sub> N <sub>4</sub> -<br>AMD        | 3.8             |              | Xi'an Jiaotong University                                       | 2021 | [41] |

| PCB<br>embedd<br>ed<br>package |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        | AIN<br>baseplate                               | 1.1             |              | The Ohio State<br>University                                    | 2020 | [42] |

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        | Multilaye<br>r ceramic<br>substrate            | ≤ 1.6 nH        |              | Fraunhofer Institute for<br>Reliability and<br>Microintegration | 2019 | [43] |

|                                | 45 mm 55 mm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 45×55                  | AIN-DBC                                        | 3.9             |              | Virginia Polytechnic<br>Institute and State<br>University       |      | [44] |

TABLE II (CONTINUED)

| Device<br>types | Sample types                                                   | Dimen<br>sion<br>(mm) | Types of<br>Inorganic<br>packaging<br>material | Inductance (nH) | Rth<br>(°C/W             | Organization                                              | Year | Ref. |

|-----------------|----------------------------------------------------------------|-----------------------|------------------------------------------------|-----------------|--------------------------|-----------------------------------------------------------|------|------|

| Hybrid          | Chipat terminal IX- terminal (tate connects)  DC- terminal IX- | <u>s.</u>             | Al <sub>2</sub> O <sub>3</sub> -<br>DBC        | 1.8             |                          | Huazhong University of<br>Science and Technology          | 2020 | [45] |

| Package         |                                                                | 106×6<br>2            | AIN-DBC                                        | 0.79            |                          | Huazhong University of<br>Science and Technology          | 2018 | [46] |

| SKiN            |                                                                |                       | DBC                                            | 2.5             |                          | Semikron                                                  | 2022 | [21] |

| Other           |                                                                |                       | Cement-<br>based<br>encapsula<br>tion          |                 | 0.453                    | Process Technology &<br>Material Danfoss Si<br>Power GmbH | 2022 | [47] |

| package         |                                                                | 47.5×<br>52.6×<br>9.3 | Si <sub>3</sub> N <sub>4</sub> -<br>AMD        |                 | 0.483<br>(simul<br>ated) | Microchip Technology<br>Inc.                              | 2020 | [48] |

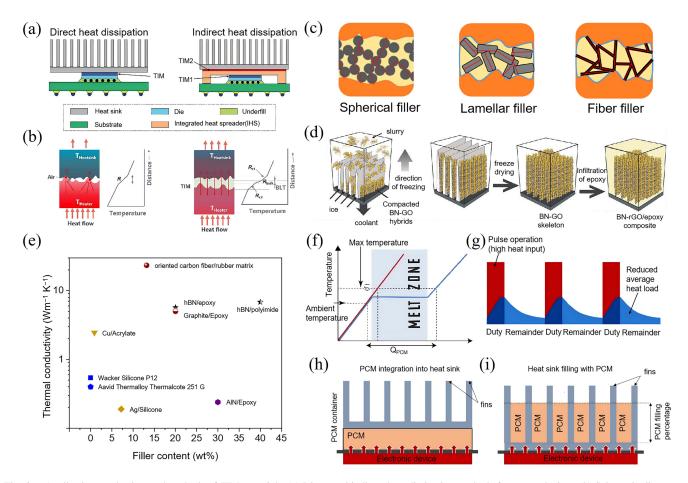

They also minimize mechanical stress and impacts, thereby ensuring an effective insulation system for the module [50]. High-performance encapsulant materials should offer voltage isolation with a good dielectric strength (compared to air's 3 kV/mm), effectively suppress leakage currents with high electrical resistivity ( $>10^{12}~\Omega$ ), provide mechanical protection through an appropriate coefficient of thermal expansion (CTE) and modulus, and maintain thermal stability across suitable curing and application temperatures [51]. While polymers are commonly used for encapsulation, inorganic nonmetallic materials such as cement and glass can also be used in power device encapsulation [49], [52], [53].

### A. Polymer-Based Encapsulation Materials

Epoxy resin is a traditional hard encapsulation material widely used in electronic packaging due to its excellent adhesion strength and chemical resistance. The glass transition temperature (Tg) of epoxy molding compound (EMC) typically ranges from 125 to 175 °C, which is a key parameter for evaluating thermal stability. For power modules, the maximum operating temperature should generally be kept below the Tg of the encapsulant. To address the low Tg and poor thermal stability of epoxy resin, inorganic fillers can be added to create efficient thermal paths, improving heat dissipation. However, this may introduce defects and cause issues such as poor processability and higher manufacturing costs as the filler content increases.

For example, when using dicyclopentadiene and naphthalene epoxy resin with an acid anhydride hardener to implement cross-linking reactions, it is possible to achieve a high cross-link density, raising the Tg above 270 °C [54]. However, this may negatively impact flowability and increase water absorption. Higher cross-link densities also require higher curing temperatures (e.g., over 300 °C for polyimide), which can increase the material's brittleness and reduce its toughness. Therefore, improving the high-temperature performance of epoxy resin often comes at the cost of reduced processability and durability.

Silicone gel, on the other hand, is a soft encapsulant known for its ability to recover from damage caused by mechanical stress or electrical degradation, such as electrical treeing [55], [56]. However, its low Tg (below  $-60^{\circ}$ C) means that its thermal performance is mainly assessed by the onset temperature of degradation. Commercial silicone gel typically remains stable between -45 and 200°C. The high CTE of silicone gel (>100 ppm/°C) can create a risk of lead detachment under thermal stress, although its low modulus helps mitigate this risk to some extent. However, it also introduces mechanical wear issues. Furthermore, silicone gel is moisture-sensitive, meaning that careful thickness design is crucial for ensuring a crack-free lifetime, and it also affects both heat dissipation and adhesion. The addition of inorganic nonmetallic fillers can reduce CTE, control partial discharge, and lower the electric field, but these improvements come with similar issues to those encountered with epoxy resin. To enhance thermal stability, high-temperature

nonpolar dibenzyltoluene liquid could be considered as a substitute [54]. These insulating liquids offer good thermal and dielectric performance but lack the mechanical support required to protect power module components, necessitating additional design or material considerations.

WBG semiconductor materials enable devices to operate under high temperature and power conditions. However, polymer-based encapsulation materials often fall short in high-temperature performance, limiting device improvements. In contrast, inorganic nonmetallic materials, known for their robust thermal stability, are therefore preferred for high-temperature encapsulation materials [50], [57].

#### B. Cement-Based Encapsulation Materials

Cement, a hydraulically setting inorganic binder material often known as wet-setting ceramics, offers several benefits including high-temperature resistance (> 1000 °C), high thermal conductivity (0.58-6 W·m<sup>-1</sup>.°C<sup>-1</sup>), good chemical stability, high flowability, strong plasticity, ease of processing, and low cost. The University of Central Florida used hydro-set ceramic materials (Cermacast 673N) to develop a 2×2 mm<sup>2</sup> SiC Schottky diode prototype, which operated normally at 300 °C [30]. The Air Force Research Laboratory encapsulated SiC power modules with ceramic-filled adhesives (Resbond 919 and 920), which successfully passed thermal shock tests (-55 to 200 °C) and high-temperature reverse bias tests (2 kV and 250 °C) [58]. Kaessner et al. [59] at the University of Tuebingen investigated calcium aluminate cement (CCC) encapsulation materials, consisting of an iron-free calcium aluminate cement (CAC) matrix and alumina. However, the high pH value of this cement corroded the metal layer on the chip surface, causing the devices to fail reliability tests. Consequently, Kaessner employed a ceramic encapsulation material (CE) with a hydratable alumina matrix and alumina filler particles with a lower pH value. This material successfully encapsulated custom power modules—featuring Semikron CAL diodes and Infineon IGBT4s soldered onto a DCB substrate—using a special curing process at 60 and 150 °C for 3 h each. The devices passed high temperature reverse bias (HTRB) test [60]. Fudan University enhanced the thermal conductivity of cement composite encapsulation materials by incorporating Al<sub>2</sub>O<sub>3</sub> fillers into CAC and utilized a finite element model (FEM) to predict the thermal conductivity of various filler composites, streamlining the development process [61]. Concurrently, Kaessner et al. [59] employed phosphate cement (PC) to encapsulate Mini power modules (MiniPIM, Danfoss Silicon Power), featuring two direct bonded copper ceramic (DBC) substrates soldered onto a standard copper baseplate, each substrate with two IGBTs and two diodes connected via solder joints and Al-wire bonding. These devices excelled in reliability tests, passing HTRB and high voltage-high humidity high temperature reverse bias tests and enduring 70 000 power cycles, which is 3.5 times longer than conventional Si-encased modules. Additionally, the Fraunhofer Institute for Microstructure of Materials and Systems assessed the effects of cement encapsulation on the Econo3 power module using numerical methods. The results demonstrate enhanced reliability

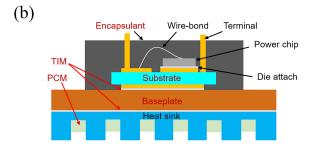

Fig. 2. Overview of the process of main developing cement encapsulation materials [47], [59], [60], [63]. Reproduced with permission. IEEE, copyright 2018, IEEE, copyright 2019 Elsevier Ltd.

in PC-cement-encapsulated power modules [62]. Kaessner, in collaboration with FuE-Zentrum Fachhochschule Kiel GmbH, enhanced the design by adding a copper layer thermal mass circuit (TMC) atop the cement-encapsulated modules, which connected to the heat sink. Test results reveal that, compared to modules using only CE materials, the TMC structure reduces the maximum inlet coolant temperature (Ti) by 7.6 °C and lowers the junction temperature (Tj) by 12.9 °C compared to the results in [63]. Kaessner later introduced the TriCool module concept, featuring CE cement encapsulation material [47]. The TriCool module includes three base units with central coolant inflow and return, each featuring a 3-mm Cu bottom plate. The adjacent bottom plates' DBCs connect via internal and external busbars, enabling water cooling in the central return zone [47]. Unlike TMC, the TriCool design offers a fully restructured module body with a triangular shape, significantly lowering Tj and Rth. Compared to standard CE material modules, the TriCool achieves a 24.96 °C reduction in T<sub>i</sub> and a 28.94% decrease in Rth. The main development process of cement encapsulation materials is depicted in Fig. 2.

## C. Glass-Based Encapsulation Materials

Glass is a promising inorganic high-temperature encapsulation material, which offers adjustable softening temperature, sintering temperature, as well as thermal expansion coefficient (CTE). Its exceptional thermodynamic and chemical stability, coupled with excellent electrical insulation, durability, and mechanical strength, makes it highly suitable for high-power module applications.

Liu et al. [64] at Virginia Tech initially evaluated the compatibility of lead glass powder (Ceradyne, Inc.) with DBC substrates. They encapsulated a DBC substrate with electrodes using molten glass at 500 °C directly and compared the samples with those encased in commercial polymer materials, maintaining them at 250 °C for 1000 h. The results indicated that the partial discharge inception voltage (PDIV) of the polymer-encapsulated samples dropped over 80% within 100–200 h, while the glass-encapsulated samples retained a high breakdown field strength of 4.5 kV after 1000 h [64], [65]. However, a self-made SiC MOSFET module, encapsulated with the same method, experienced performance degradation due to damage to the MOSFET'S

Fig. 3. Overview of the processes and comparisons of two different glass encapsulation techniques [64], [67]. Reproduced with permission. copyright 2021, IEEE, copyright 2025 Elsevier Ltd.

oxide layer. To mitigate the thermal-mechanical stress from the differing CTEs of glass and DBC during cooling, the team introduced a polyimide (PI) layer between the glass and chip. The static characteristics of the glass-encapsulated samples aligned with the device datasheet values. Despite the PI buffer layer reducing interface stress, micropores could still lower PDIV. To resolve this problem, the team developed a buffer layer using a nonlinear resistive polymer-nanoparticle composite material, which improved insulation without affecting thermal performance [66]. Researchers from East China University of Science and Technology and Fudan University addressed the issue by altering the BaO and ZnO ratios in bismuth-based glass. This modification reduced the encapsulation temperature while preserving excellent insulation properties [29]. They used a sealing technique at 475 °C with glass powder to successfully encapsulate a TO-247 SiC Schottky barrier diode (SBD) [29]. However, the issues of high packaging temperature (475 °C for 35 min) and high CTE (= 11.48 ppm/°C) persisted. Subsequently, the team incorporated PbTiO<sub>3</sub> ceramic powder to adjust the CTE of the glass-based encapsulating material for SiC power devices, using a process at 450 °C. The encapsulated device passed static performance tests with a low thermal resistance of 0.45 °C/W, maintaining excellent performance even after 1176 h of hightemperature aging and remaining nearly unchanged throughout thermal cycling between temperatures of –50 to 150 °C for 100 cycles [67]. Unlike traditional encapsulation materials with low thermal stability (< 200 °C), glass-encapsulated SiC devices can function at temperatures up to 300 °C. The methods and comparative results of the two different glass encapsulation techniques are illustrated in Fig. 3.

As the junction temperature of wide-bandgap power devices continues to increase, the limitations of polymer encapsulation materials become more apparent, particularly in terms of thermal management and thermo-mechanical robustness. Inorganic nonmetallic materials offer a promising solution to this challenge. However, ceramic materials, which typically require high sintering temperatures, are not viable options for encapsulation. Instead, cement and glass stand out due to their favorable processability, thermal, and electrical properties. Moreover, both cement and glass are traditional radiation shielding materials, making them highly suitable for applications in high-radiation environments, such as deep space exploration and nuclear power plants, where device reliability is crucial [68], [69]. Despite their potential, using cement and glass as encapsulation materials for power devices presents several challenges. For cement, the porous structure weakens electrical insulation and corrosion resistance, which can reduce device performance, particularly in high-humidity environments. Additionally, the alkaline hydration process can lead to electrochemical reactions, resulting in electrical failures. Cement's poor adhesion to other materials often necessitates high-temperature-induced dehydration or the use of additional coatings to improve bonding. Glass, on the other hand, presents challenges such as high processing temperatures (over 450 °C) and thermal-mechanical stress due to mismatched CTE with the substrate. Furthermore, its high dielectric constant (8–12) and relatively high Young's modulus (58 GPa) complicate its use in power device applications [70]. To address these issues, solutions such as incorporating a buffer layer between the glass encapsulant and the ceramic substrate have been proposed [71], [72]. Another approach involves modifying the glass's intrinsic properties to reduce its softening temperature, CTE, and Young's modulus. Although cement and glass encapsulation materials generally exhibit relatively low thermal conductivity, their thermal performance remains superior to that of conventional polymer-based encapsulants available on the market. Raw materials for these inorganic encapsulants are easily sourced from traditional suppliers, but packaging equipment often requires significant upgrades or redesigns to accommodate these materials effectively. Continued research and development are essential to overcoming these challenges and ensuring the broader application of cement and glass as encapsulants in power devices.

# IV. SUBSTRATE MATERIALS

In power module packaging, substrates serve as both mechanical support for power chips and dielectric layers for electrical insulation of circuits while facilitating thermal management for active devices [73], [74]. However, existing organic substrate materials face notable drawbacks, including high thermal expansion (CTE) coefficients, warping, excessive shrinkage, and insufficient temperature resistance, making them unsuitable for the higher junction temperatures of next-generation WBG power devices. Consequently, adopting inorganic nonmetallic materials as dielectric barrier layers to meet more stringent thermal demands has gained importance [75]. Ceramic substrates are commonly used in high-performance, high I/O density products due to their excellent CTE compatibility with power chip materials and strong reliability under high-temperature processing or application conditions. However, inorganic nonmetallic substrate materials are preferred for power chips because they offer

| Types | Materials/<br>Merchants        | CTE<br>(ppm/°C) | Thermal conductivity (W·m <sup>-1</sup> ·°C <sup>-1</sup> ) | Heat<br>tolerance<br>(°C) | Redistribution<br>layer<br>materials                | Advantages                                                          | Disadvantages                                                                    |  |

|-------|--------------------------------|-----------------|-------------------------------------------------------------|---------------------------|-----------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------|--|

| TFC   | Al <sub>2</sub> O <sub>3</sub> | 7–9             | 20–30                                                       | 200                       | An Ac Cu                                            | Technically advanced,                                               | Surface roughness and                                                            |  |

| IFC   | AlN                            | 4.2–7           | 120–200                                                     | 300                       | Au, Ag, Cu straightforward process, cost-effective. |                                                                     | misalignment                                                                     |  |

| DDC   | 2-3                            |                 | 20–30                                                       | 500                       | C                                                   | Accurate alignment, no sintering                                    | Copper foil is excessively thick                                                 |  |

| DBC   | AlN                            | 4.2–7           | 120–200                                                     | 500                       | Cu                                                  | shrinkage, and differential issues.                                 | and requires processing.                                                         |  |

|       | Al <sub>2</sub> O <sub>3</sub> | 7–9             | 20–30                                                       |                           |                                                     | Accurate alignment, no sintering shrinkage, no differential issues, | The copper layer is too thin and needs electroplating to increase its thickness. |  |

| DPC   | AIN                            | 4.2–7           | 120–200                                                     | <300                      | Cu                                                  | and capable of producing<br>10–50 µm lines.                         |                                                                                  |  |

|       | Al <sub>2</sub> O <sub>3</sub> | 7–9             | 20–30                                                       |                           | Cu                                                  | Accurate alignment, no sintering shrinkage, no differential issues, | Requires electroplating to thicken, incurs high costs, requires limited          |  |

| AMB   | AlN                            | 4.2–7           | 120–200                                                     | <400                      |                                                     | and capable of producing 10–50<br>µm lines with good thermal        | suitable active solders, and the solder's composition and process                |  |

|       | Si <sub>3</sub> N <sub>4</sub> | 2.7-4.5         | 40–100                                                      |                           |                                                     | conductivity and high reliability.                                  | crucially affect the welding quality.                                            |  |

TABLE III

COMPARISON OF TRADITIONAL CERAMIC SUBSTRATES AND PROPERTIES

superior mechanical support, thermal stability, electrical insulation, and shielding properties. As power modules evolve with increased integration, power density, and operating frequency, the challenge of meeting the electronic industry's varied demands for thermal conductivity, mechanical strength, and dielectric properties with a single material has led to the development of composite substrates that combine the advantages of different materials to meet these evolving needs.

# A. Conventional Ceramic Substrate

Inorganic nonmetallic materials such as Al<sub>2</sub>O<sub>3</sub>, BeO, AlN, and Si<sub>3</sub>N<sub>4</sub> are widely utilized in power module packaging through advanced packaging technologies including thick film ceramic substrate (TFC), DBC, active metal brazing (AMB), and direct-plated copper ceramic substrate (DPC). Table III presents common substrate performances [76]. Each method has distinct advantages. TFC substrates are economical and simple to produce but have limited current-carrying capacity due to their thin metal layers ( $< 1 \mu m$ ), making them unsuitable for high-power devices. DPC substrates enable lowtemperature processing (around 300 °C), reducing circuit damage risk; however, their performance depends heavily on process accuracy. DBC substrates provide superior thermal conductivity and stability in high-power applications, making them prevalent in IGBT production. However, they are susceptible to thermal stress and copper delamination due to mismatched thermal expansion coefficients. AMB substrates address these issues by bonding thicker copper layers at lower temperatures using active metal solders. This approach enhances compatibility with Si<sub>3</sub>N<sub>4</sub> and SiC materials and shows potential for applications involving SiC semiconductors. However, AMB's use of rare-earth elements in solders presents storage and handling challenges. After fabrication, all ceramic substrates require metallization and surface patterning through image transfer technology for electrical connections. The electroplating

process, however, demands strict environmental controls. Recently, resource recovery and closed-loop systems have become key trends in pollution control within the electroplating industry.

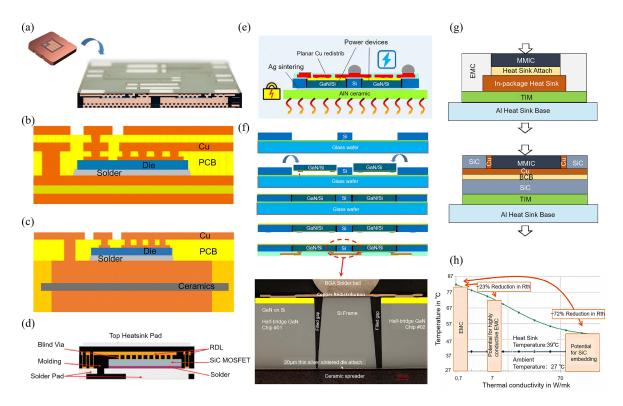

# B. High-Temperature Co-Fired Ceramics (HTCC)

With advancements in power device manufacturing technologies, processes, and packaging, power conversion equipment is increasingly capable of handling higher power levels and more demanding operating conditions. Conventional PCB substrates, including FR4 and high-performance polytetrafluoroethylene, are inadequate for power modules used in harsh environments and high-reliability applications. High-temperature co-fired ceramics (HTCC) and low-temperature co-fired ceramics (LTCC), integral to multilayer ceramic technology, facilitate the layering of multiple dielectric and metal layers. They incorporate distributed and staggered via holes, allowing the creation of complex multilayer structures with embedded cavities and components. This advancement enables device miniaturization and high-frequency applications, providing significant design flexibility and facilitating the production of new power modules. Performance data for typical application products are detailed in Table IV [73].

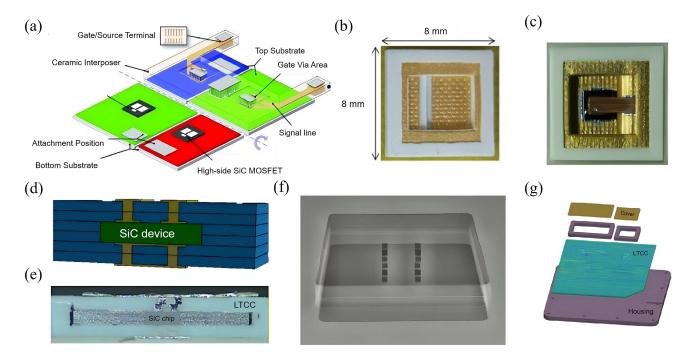

HTCC is usually composed of high thermal conductivity ceramic powders such as AlN or  $\mathrm{Si}_3\mathrm{N}_4$ , processed through tape casting and cofired at temperatures exceeding 1350 °C. The thermal conductivity of the composite material ranges from 20–200 W·m $^{-1}$ .°C $^{-1}$ , depending on the composition and purity of the ceramic powders. Researchers at Huazhong University of Science and Technology tackled challenges related to bonding wires in conventional packaging designs, including elevated parasitic inductance, inadequate high-temperature performance, and substantial thermal–mechanical stress. Fig. 4(a) illustrates their proposed robust, high-temperature-resistant packaging design based on HTCC that omits bonding wires, reducing stress

| Types | Materials/<br>merchants        | CTE<br>(ppm/°C | Thermal conductivity (W·m <sup>-1</sup> .°C <sup>-1</sup> ) | Heat<br>toleranc<br>e (°C) | Redistribu<br>tion layer<br>materials | Advantage<br>s                                                                            | Disadvantages                                                                                                                          |  |

|-------|--------------------------------|----------------|-------------------------------------------------------------|----------------------------|---------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| нтсс  | AlN                            | I              | 16–24                                                       | 1000                       | W, Mo,<br>Mn                          | The process is well- established and cost- effective.                                     | Alignment accuracy is low, the circuit surface is rough, and the high sintering temperature results in substantial energy consumption. |  |

|       | Al <sub>2</sub> O <sub>3</sub> | 7.1            | 2–3                                                         |                            | Au, Ag,<br>Cu                         | The process is proven, offering high electrical performan ce and adjustable performan ce. |                                                                                                                                        |  |

|       | DuPont<br>9K7                  | 4.4            | 4.6                                                         | 850                        |                                       |                                                                                           | Low alignment precision,<br>rough circuit surface, and<br>surface shrinkage.                                                           |  |

| LTCC  | Ferro<br>A6M                   | 7              | 2                                                           |                            |                                       |                                                                                           |                                                                                                                                        |  |

|       | Heraeus<br>HL200               | 6.1            | 2.6                                                         |                            |                                       |                                                                                           | -                                                                                                                                      |  |

| ULTCC | muLtcc40                       | 4.5            |                                                             | 480                        |                                       | Cost-effective                                                                            | Inappropriate materials and weak dielectric properties.                                                                                |  |

|       | TiO <sub>2</sub> A-<br>30GO17  | 7.4            |                                                             | 400                        | Al,<br>nanosilver                     | and energy-<br>efficient.                                                                 |                                                                                                                                        |  |

|       | TiO <sub>2</sub> R-<br>30GO17  | 8.3            |                                                             | 400                        |                                       |                                                                                           |                                                                                                                                        |  |

TABLE IV

COMPARISON OF DIFFERENT MULTILAYER CERAMIC SUBSTRATES AND THEIR PROPERTIES

and enhancing overall reliability [74]. However, the elevated sintering temperature of HTCC constrains the selection of metallic conductor materials, primarily limiting them to metals with high melting but lower conductivity points, such as tungsten, molybdenum, and manganese. Consequently, HTCC is better suited for manufacturing passive components, such as high-temperature-resistant resistors and capacitors, within wide-bandgap power modules.

# C. Low-Temperature Co-Fired Ceramics (LTCC)

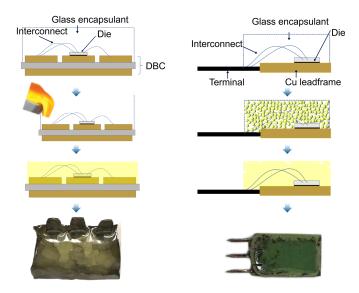

LTCC achieves a sintering temperature below 900 °C by incorporating 30–50% low-melting-point glass into the raw porcelain belt. This strength allows the use of materials with superior electrical conductivity, such as gold, silver, and copper, for electrodes and wiring. LTCC modules are distinguished by their compact design, outstanding mechanical and thermal shock resistance, and exceptional electrical performance, including dielectric loss several orders of magnitude lower than that of RF4 [77]. Consequently, LTCC is unmatched in high-frequency applications, with no organic material matching its performance in frequency, size, and cost. One straightforward manufacturing method for LTCC power modules is surface mount device (SMD) technology. The Electronics and Telecommunications Research Institute first utilized SMD technology for packaging SiC SBDs within multilayer ceramics. They embedded bare

SiC SBD chips into the LTCC substrate cavities and employed flat Cu clip bonding to minimize parasitic inductance [see Fig. 4(b)] [75]. Compared to conventional TO-220 package products, this approach reduces the parasitic inductance (Q\_rr) by 18.7% and outperforms commercial SMD SiC SBD products in efficiency and thermal performance [see Fig. 4(c)] [76]. Similar technology has also been implemented in the manufacture of power inductors [78]. The Fraunhofer Institute for Ceramic Technologies and Systems and Integrated Systems and Device Technology developed a new packaging concept that integrated power semiconductor devices into LTCC using a combination of silver foil and solid body integration, to enhance the operational temperature of SiC power devices to over 400 °C [79]. By employing pressure-assisted sintering and constraining sacrificial layers, the lateral shrinkage of LTCC material was eliminated, allowing the successful integration of SiC devices into commercial LTCC substrates. The electrical interconnections of the embedded SiC chips were then validated by measuring the resistance between the top and bottom of the LTCC pre-packaged module [see Fig. 4(d)–(f)] [80], [81]. Additionally, new techniques for embedding SiC devices into ultralow-temperature co-fired ceramics (ULTCC), which can be sintered at 500 °C, are explored as an alternative due to LTCC's higher sintering temperature [82]. Embedded LTCC technology is a highly effective packaging solution for protecting electronic devices from high temperatures and corrosive gases. The LTCC-

Fig. 4. Power device featuring an multilayer ceramic substrate. (a) Internal photographs of the power module based on HTCC packaging structure. (b) Internal photographs of the fabricated leadless LTCC-based SiC SBD SMD package. (c) Embedding a SiC semiconductor device in a pre-metallized LTCC multilayer. (d) Embedding a SiC device in a pre-metallized LTCC multilayer stack, cross-sectional view. (e) X-ray image. (f) and (g) LTCC-based all-in-one CAMP package [75], [80], [81], [82], [84]. Reproduced with permission. copyright 2024, IEEE, copyright 2020, IEEE, copyright 2020, IEEE, copyright 2023, IEEE, copyright 2022 Elsevier Ltd., copyright 2022 cnki.

based interposer provides a robust structure, electrical isolation, and ease of fabrication [37]. Recently, advancements in space technologies utilizing WBG semiconductor materials such as gallium nitride (GaN) and GaN-based alloys have prompted research into solid-state power amplifiers (SSPA) as alternatives to traveling wave tube amplifiers [83], [84]. The China Academy of Space Technology (Xi'an) integrated packaging technology to develop a GaN-based SSPA using a phase-shift-full-bridge topology, showcasing LTCC's capability to support deep space exploration with WBG power modules [see Fig. 4(g)] [84]. Due to its numerous advantages, LTCC is extensively used in the manufacture of automotive power electronics. Delco Electronics, a General Motors subsidiary, utilizes LTCC technology to manufacture engine control modules, while Magneti Marelli's Electronics in Italy employs it for automotive oil valve control modules incorporating power MOS devices.

Although LTCC provides notable benefits for power module packaging, it also has some limitations. The high glass content in the LTCC raw porcelain belt results in a relatively low thermal conductivity, potentially impacting the reliability of high-density LTCC modules. To mitigate this issue, researchers often incorporate high thermal conductivity ceramics such as Si<sub>3</sub>N<sub>4</sub>, BN, and diamond into the raw porcelain belt, and optimize the material's electrical performance with advanced microcrystalline glass [85]. For LTCC processes, thermal vias offer an effective thermal management solution. This technique involves creating vertical vias under heat sources in integrated LTCC devices and cofiring them with high thermal conductivity materials involving silver (Ag), silver-palladium (AgPd), and platinum

(Pt). This method enables efficient heat transfer to heat sinks or the device exterior [86], enhances heat dissipation efficiency, and maintains the device's thermal stability. Future developments in LTCC technology will focus on improving heat dissipation performance, lowering sintering temperatures through the ULTCC development, and reducing dielectric constant and dielectric loss. These advancements will further enhance LTCC materials' suitability for high-performance electronic packaging, addressing the growing demands for miniaturization, reduced weight, and increased reliability in electronic devices.

# D. SiCp/Al Matrix Composites and Diamond