# Saddle Add-On Metallization for RF-IC Technology

Joachim N. Burghartz, Fellow, IEEE, Behzad Rejaei, and Hugo Schellevis

Abstract—A cost-effective add-on process module for reducing ohmic losses of radio-frequency (RF) inductors and interconnects in RF/BiCMOS and RF/CMOS technologies built on CMOS logic processes is proposed. The module is based on the local thickening of the top metal layer of the thin CMOS interconnects through copper (Cu) electroplating in selected areas. The combination of dense Cu-interconnects in the CMOS logic sections, of thick Cu top-level wiring through local Cu electroplating in the RF sections, and of aluminum (Al) capping of the bond pads provides an optimum tradeoff between packaging requirements, quality of passive components and interconnects, and cost. A special wet-etch process sequence for removal of the Cu-seed and adhesion films from the exposed top metal layer is described. A record quality factor of  $\sim 13$  for a 10-nH inductor on a conventional 5- $\Omega$ -cm silicon substrate is demonstrated.

Index Terms—BiCMOS integrated circuits, CMOS integrated circuits, conductivity, conductors, copper, electromagnetic induction, inductors, integrated circuits, losses, magnetic fields, microwave devices, passive circuits, scattering parameters measurements, silicon.

#### I. INTRODUCTION

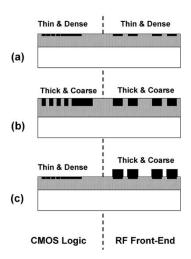

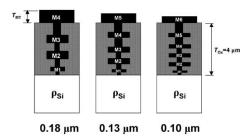

T HAS BECOME common practice in the development of high-performance RF/BiCMOS and RF/CMOS to migrate an existing CMOS logic process along with the associated ASIC libraries to radio-frequency (RF) process development and to adopt the interconnect scheme unaltered from CMOS [1], [2]. Such interconnects are designed for a minimum pitch (width + space) for the particular metal layer thickness to achieve maximum integration density. An optimized layout of an integrated spiral inductor, however, is based on a rather large metal pitch in order to minimize the ohmic losses in the spiral coil [3]. The straightforward migration of the CMOS interconnect scheme to the RF process [Fig. 1(a)] leads to a comparably low quality factor (Q) of spiral inductors. This situation worsens with CMOS downscaling [4], which is surprising at first since the number of metal layers increases as the CMOS is advanced [5]. With downscaling, however, the thicknesses of metal and dielectric layers are reduced. It can be seen from the simplified sketch of three technology generations in Fig. 2, that the distance between the top metal layer and the silicon substrate remains at first order constant. The thickness of the upper metal layers, at which usually the spiral coil of the inductor is built, however, is reduced with downscaling. That means, that for a given inductor area the oxide capacitance to the substrate stays constant and the coil resistance increases

Manuscript received September 22, 2003; revised November 25, 2003. The review of this paper was arranged by Editor M.-C. Chang.

The authors are with the Electronic Components, Technology, and Materials (ECTM), Delft Institute for Microelectronics and Submicron Technology (DIMES), Delft University of Technology 2600 GA Delft, The Netherlands (e-mail: burgh@dimes.tudelft.nl).

Digital Object Identifier 10.1109/TED.2004.823325

Fig. 1. Illustration of three multilevel interconnect technologies migrated from CMOS logic to RF/BiCMOS or RF/CMOS. (a) Unaltered interconnect scheme with a thin top metal layer that is insufficient for integration of RF passive components. (b) Interconnect stack with fat top metal layer that has reduced effectivity for interconnecting logic CMOS. (c) The combination of thin/dense interconnects for logic CMOS and fat metallization for RF passive components.

Fig. 2. Interconnect schemes for three CMOS generations [4]. Only one global metal layer is assumed for each technology generation.

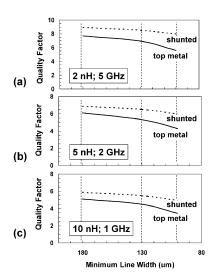

with technology advancements. The consequence is that the maximum  $Q(Q_{\mathrm{max}})$  is decreased and shifted to a higher frequency  $[f(Q_{\text{max}})]$  [3]. Inductor redesign for maximum Qat the target frequency would result in wider metal lines and thus larger coil area and higher capacitance to the substrate [3]. The  $Q_{\text{max}}$ -values for given inductance and  $f(Q_{\text{max}})$ , which can be reached through an optimum inductor layout, therefore tend to decrease with technology downscaling (Fig. 3). This trend can to some extent be alleviated by taking advantage of shunting of metal layers (Fig. 3) [6]. Nevertheless, moving to a more advanced technology generation to utilize higher device performance for larger bandwidth is strongly hampered by the fact that the inductor-Q cannot be raised in proportion with the device performance. The inductor-Q can be improved by increasing the thickness of the top metal layer adopted from the CMOS [7], [8]. The associated large metal pitch, however, will make this layer rather ineffective for interconnecting the dense CMOS logic sections [Fig. 1(b)]. From an economic point of

Fig. 3. (Solid lines) Simulated quality factors of optimized 2, 5, and 10-nH inductors for three CMOS generations. Coils built at the top metal layer are compared to (dashed lines) inductors that have shunted M3/M4, M3/M4/M5, and M3/M4/M5/M6 layers for 180, 130, and 100-nm CMOS, respectively. (For details about the simulation program, see Section III.).

view one would then practically invest in an additional overly thick ("fat") metal layer to mainly boost the inductor-Q. In any case one would accept a weak tradeoff, either economically or in circuit performance. It is thus obvious that the most desirable interconnect scheme in a RF integration process would provide both thin and dense wiring for the logic circuits and thick and coarse metal for fabrication of the RF passive components [Fig. 1(c)].

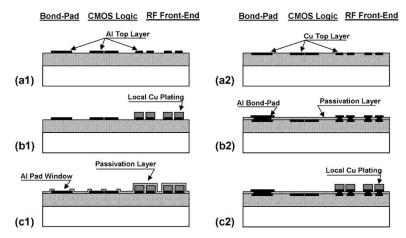

An additional complication arises with the copper (Cu) multilevel interconnects of the current advanced CMOS in conjunction with the requirements for wire bonding. Copper, on the one hand, is attractive for inductor design since its resistivity is only about 60% of that of aluminum (Al). Although high-Q inductors have been demonstrated by using Al-interconnects [8], the best results so far were achieved with Cu-metallization [9]. The multi-level interconnect schemes of almost all advanced CMOS integration processes are based on Cu metallization [1], [10], [11]. A Cu top layer, on the other hand, does not provide a reliable bond-wire connection due to excessive Cu oxidation [12]. Cu-interconnect schemes must therefore either include an Al-cap covering the bond pads [12], [13], or that top metal layer of the Cu-interconnect stack must be an Al layer [7]. The Al-cap is typically applied after deposition of the dielectric passivation layer and the opening of the bond pads, i.e., at the end of the chip fabrication process. Extension of the Al-cap layer, applied prior to the passivation, to cover all top metal wires with thick Al is not well possible due to the density requirements in the CMOS logic sections. That is, because removing such a thick Al film from the top metal layer in the CMOS logic sections to leave the Al in place only over the bond pads and in the coarse RF circuit sections is very difficult because of the poor selectivity of the Al dry-etch removal over the Cu. Only a local application of the Al-cap layer after the passivation, e.g., over the bond pads and the inductor coils, seems feasible. The thickness of the Al-cap layer is limited due to process constraints and thus leads only to a slight improvement in inductor-Q. It is evident that the Al-cap requirement does not apply to the more conservative Al-interconnect schemes [14]. The poor trade-off between wireability of the dense CMOS logic circuits and the quality of the RF passive components, however, is of concern in terms of the optimum local thickness of the top metal layer. Desired is thus a processing scheme that provides dense wiring in the CMOS sections and a thick Cu layer over certain RF structures [Fig. 1(c)], while Al bond pads are provided. That leads to two attractive tradeoffs in current RF integration processes Fig. 4(a1)–(c1) and (a2)–(c2).

- 1) In an Al-interconnect stack or a Cu-interconnect scheme with an Al top layer [Fig. 4(a1)] a local thickening of the metal in the RF sections can be arranged by local Cu-plating [Fig. 4(b1)]. A passivation layer, in which windows are opened over the bond pads, is added at the end [Fig. 4(c1)].

- 2) In the full Cu-interconnect scheme [Fig. 4(a2)] an Al bond pad is formed after the passivation [Fig. 4(b2)]. That Al layer is also placed over certain RF structures. Finally, local thickening of the metal by Cu-plating is achieved over those RF features [Fig. 4(c2)]. Metal passivation is then only provided in the dense CMOS sections.

A third relevant case relates to a full Cu-interconnect scheme followed by local Cu-plating over the RF features and by the dielectric passivation and the formation of the Al bond pad. That concept, however, is less favorable compared to the tradeoffs illustrated above, as will be shown later.

In this paper, we present a novel metallization add-on module, called Saddle add-on metallization (SAM) that enables those desired tradeoffs at minimum additional cost. The SAM concept and process are described in Section II. Experimental results, through which the effectiveness of SAM is demonstrated, are discussed in Section III. Conclusions follow in Section IV.

#### II. SAM CONCEPT AND PROCESS

The reduction of the metal losses in an integrated spiral inductor is most important at low RF, at which the inductor area tends to be large and the inductor-Q is limited by the ohmic losses in the coil [3]. Both reduction of the ohmic loss and of the coil area can be achieved by raising the metal thickness, as explained in Section I. Schemes, in which an additional fat metal layer, separated by a thick dielectric layer from the CMOS interconnect stack, is provided, had been published [7]. Those structures aim for addressing both ohmic coil losses and substrate losses at the same time [3], [6]. Even though effective, those add-on processes require at least two additional mask layers and nonstandard process steps and are therefore quite costly. Furthermore, reducing the substrate losses by spacing the inductor coil away from the substrate may be far less relevant than lowering the ohmic losses in the coil at low RF. That is, because future RF integration processes will likely adopt high-resistivity silicon (HRS) substrates to reduce substrate losses and crosstalk at the same time [15], [16]. Sole reduction of the metal losses may thus be sufficient, if achieved at reduced cost. This is the main objective of the SAM concept, in which the top metal layer is increased in thickness only where needed and not where the inherent large metal pitch causes a disadvantage [4]. The SAM

Fig. 4. Illustration of the introduction of SAM into an interconnect scheme with either an Al [left: (a1)–(c1)] or a Cu [right: (a2)–(c2)] top metal layer.

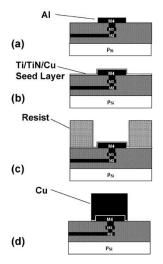

Fig. 5. SAM for local increase of top metal layer thickness. (a) CMOS interconnect stack after finalizing the top Al-layer fabrication. (b) After Ti–TiN adhesion and Cu-seed layer deposition. (c) After formation of the photoresist mold. (d) After Cu-electroplating and resist and seed/adhesion layer removal.

process module is applied right after the multi-level interconnect fabrication of the CMOS and prior to the Al-capping of the bond pads [Figs. 4(b) and 5(a)]. First, a Ti–TiN barrier layer (10/50 nm) and a Cu seed layer (200 nm) are deposited onto the wafer before any passivation layer is added, as it is usually done after the final metal layer fabrication [Fig. 5(b)]. The Ti layer is included to improve the adhesion between the seed layer and the Al. Next, a deep photoresist mold is aligned to the top CMOS metal layer with some overlap at the edges [Fig. 5(c)]. The mold is then filled with Cu by electroplating, forming a Cu-saddle over the top metal layer of the CMOS process after the photoresist is stripped off [Fig. 5(d)].

An important aspect of the SAM process module is the possibility for selective removal of the Cu seed and Ti–TiN adhesion layers over the exposed top Al layer. Only if this removal can be done with sufficiently high selectivity can the SAM module be applied with only one photomask. This is an important issue because otherwise the economic advantage over the mentioned concepts based on an additional uniform fat metal layer with thick isolating dielectric underneath would be marginal [7], [8]. In the following, a novel seed/adhesion layer removal process, which is instrumental in achieving that goal,

Fig. 6. Indication of etch rate selectivities (average and std. variation) by sheet resistance measurements over time. (a) Cu-seed removal with selectivity to the Ti–TiN adhesion layer with underlying Al layer. (b) Ti–TiN adhesion layer removal from the Al.

is described. Appropriate selectivities of the different etches had been attempted in the development of the SAM module. After the photoresist mold is stripped off both the plated SAM structure and the Cu seed layer are exposed. Since the Cu-seed layer is very thin in comparison to the SAM, a short wet etch in Na<sub>2</sub>S<sub>2</sub>O<sub>8</sub>/H<sub>2</sub>SO<sub>4</sub>/H<sub>2</sub>O<sub>2</sub> is used for its removal. Only  $\sim 200$  nm of Cu of the SAM features will be removed. This Cu etch is developed to have a high selectivity to Ti-TiN (160:1) and to Al, so that the Cu seed layer can entirely be removed without much affecting the metal layers underneath [Fig. 6(a); Table I]. Complete removal of the Cu-seed prior to the Ti–TiN etch (NH<sub>4</sub>OH/H<sub>2</sub>O<sub>2</sub>/H<sub>2</sub>O) is crucial because the etch rate of Al is considerably high in the Ti–TiN etch and the loss of the Al should be minimized by keeping the Ti–TiN etch as short as possible. Fig. 6(b) shows the sheet resistance measured during the Ti-TiN etch after the Cu-seed layer was removed. The small change in sheet resistance during the first 6 min is obviously a result of the four-point probes of the test apparatus punching through the thin Ti-TiN film so that the thinning of that film was not well apparent in the sheet resistance measurements. After that time the sheet resistance started to change even

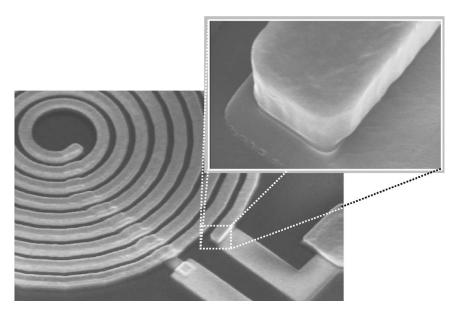

Fig. 7. SEM micrograph of a nine-turn inductor coil built with  $1-\mu$ m-thick Al top interconnect layer combined with a 3.4- $\mu$ m-thick SAM layer (prior to the passivation). The contour of the SAM add-on layer is shown by the SEM in the inset.

$\begin{array}{c} \text{TABLE} \quad I \\ \text{ETCH RATES OF CU, TI/TiN, AL, AND SiO}_2 \text{ for the Cu-ETCH} \\ \text{(Na}_2\text{S}_2\text{O}_8/\text{H}_2\text{S}_{\text{O}_4}/\text{H}_2\text{O}_2) \text{ and the Ti/Tin ETCH (NH}_4\text{OH/H}_2\text{O}_2/\text{H}_2\text{O})} \\ \text{USED FOR THE REMOVAL OF THE SEED/ADHESION LAYERS} \end{array}$

| Type<br>of<br>Etch: | Etch Rate (nm/min.) of:  Cu Ti/TiN Al SiO <sub>2</sub> |     |      |     |

|---------------------|--------------------------------------------------------|-----|------|-----|

| Cu                  | 57                                                     | ~ 0 | 0.35 | -   |

| Ti/TiN              | 14.8                                                   | 4.2 | 3.45 | ~ 0 |

though the Ti–TiN removal was not completed, as evident from visual inspection [Fig. 6(b)]. Apparently, etching of the underlying Al layer already took place through pinholes in the Ti–TiN film before the Al film was exposed. Nevertheless, only  $\sim 3\%$  of the Al layer was sacrificed, so that this etch combination qualified well for the removal of the Cu-seed and Ti–TiN adhesion layers. The loss of Cu thickness of the SAM features will be another  $\sim 200$  nm, amounting to a total Cu loss of  $\sim 400$  nm during the Cu-seed and Ti–TiN layer removal.

The loss in thickness of the top metal layer is considerably increased if a full Cu-interconnect stack is used, which is mentioned in Section I as the third relevant processing option. The etch rate of Cu in the Ti–TiN etch is  $\sim$  four times higher than that of Al (Table I). That means that  $\sim$  150 nm of Cu thickness of the top metal layer would be sacrificed, if one assumes the same pinhole effect as observed for the Ti–TiN removal over Al [Fig. 6(b)]. That process option would therefore only become feasible if one reduces the pinhole density of the Ti–TiN film considerably and if one optimizes the Ti–TiN etch to have a lower etch rate of Cu relative to that of Ti–TiN.

#### III. EXPERIMENTS AND DISCUSSIONS

Circular spiral coils were built by using the equivalent M3 and M4 layers of a four-metal level,  $0.18-\mu m$  CMOS process

on a 2-5  $\Omega$ -cm silicon substrate. The M4 layer (1- $\mu$ m-thick Al, spaced 4  $\mu$ m from the silicon substrate) was used for the coils with the underpass contact at M3 (0.7- $\mu$ m-thick). A 4- $\mu$ m-deep photoresist mold was used, and the final SAM Cu thickness was 3.4  $\mu$ m. Fig. 7 shows the SEM micrograph of a Cu-plated spiral inductor prior to the passivation [Fig. 4(b)]. From the inset it can be seen that the sidewalls of the SAM layer were sufficiently steep and its surface was flat. It should be noted that the uniformity of the electroplating process was optimized by adding an auxiliary electrode, which was connected to a current source different from that used for plating the wafer, separately near the wafer edge [17].

The spiral inductors were designed and optimized by using a fast, physics-based model on basis of a concentric-ring approximation [18]. In that model, the circular spiral coil is replaced by a series connection of concentric rings with the same number of turns (N), track-width (W), and spacing (S). The overall diameter of the system is determined by equating the overall lengths of the spiral coil and the system of rings. Exploiting the rotational symmetry of the concentric-ring system, one can then simplify the field equations to arrive at a fast, semi-analytical, physics-based model. The model takes into account substrate RF loss as well as the nonuniform distribution of the current density in the inductor windings due to the skin- and current-crowding effects. The concentric-ring model has been shown to be in good agreement with experimental data [3].

Fig. 8 shows experimental and simulated characteristics of a 10-nH SAM inductor, designed for  $Q_{\rm max}$  at 1 GHz. A value  $Q_{\rm max}=13.25$  was measured; this was a 3.2-fold increase over the Al inductor prior to SAM (not shown in Fig. 8). Even, if the Al coil is optimized for the  $Q_{\rm max}$  at 1 GHz by varying conductor width (W), spacing (S), and number of turns (N), the resulting  $Q_{\rm max}$  is still 2.8 times lower than that of the SAM inductor. The simulation results in Fig. 8 also show that layer shunting does little to reduce that difference. Shunting reduces the ohmic loss in the conductor, but increases the substrate RF

Fig. 8. Comparison of optimized 10-nH inductors, built at M4 or with shunted metal, to an inductor fabricated with SAM (markers: data; lines: simulations).

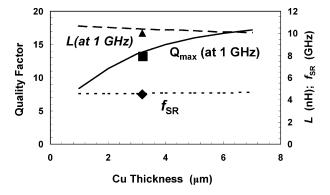

Fig. 9. Simulated Q, L, and  $f_{\rm SR}$  of a 10-nH SAM inductor as function of Cu thickness. Markers indicate the experimental results.

loss by reducing the substrate-coil spacing leading to a larger substrate-coil parasitic capacitance [6]. SAM, however, does not reduce the substrate-coil separation. The reasonably good agreement of simulation and measurement allows for extrapolation of design parameters to gain further insight into the merits of the SAM process. One can, e.g., study the potentially diminished effectiveness of SAM with increasing Cu-thickness due to skin effect and interwire capacitance (between adjacent windings with sidewalls facing each other). In order to study these effects we have simulated the inductance, the maximum quality factor, and the resonance frequency of a  $\sim$  10-NH, Cu-plated coil as function of Cu-thickness (Fig. 9). The skin effect was indeed evident from the trend to saturation of  $Q_{\mathrm{max}}$  with increasing Cu-thickness. The inter-wire capacitance was increased only slightly and was compensated by a decreasing inductance with SAM thickness, so that  $f_{SR}$  was affected only very little (Fig. 9). As a result,  $Q_{\rm max}$  of the 10-nH coil can in principle be brought to a value of  $\sim 18$  by raising the SAM thickness to  $\sim 8 \,\mu \text{m}$  without any considerable degradation of the electrical characteristics. It is important to note that, in contrast to sputtered Al, Cu plating is a cold process and thus little prone to mechanical stress. Such thick SAM layers are therefore well feasible from a process technology point of view.

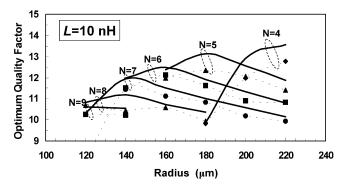

Fig. 10 indicates how the 10-nH SAM inductor can be optimized for both  $Q_{\rm max}$  and coil area. Using the concentric-ring model, we have calculated the maximum attainable quality factor obtained by optimizing the width (W) and spacing (S) of the coils for a given radius (R) and number of turns (N).

Fig. 10. Quality factor of optimum 10-nH coil designs at fixed numbers of turns (N) as a function of radius at the target frequency of 1 GHz. Experimental results (markers, dashed lines) and simulations (solid lines) are compared (5%-10% difference).

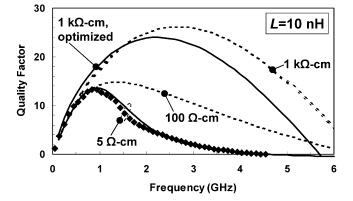

Fig. 11. Quality factor versus inductance of the 10-nH inductor on a 5- $\Omega$ -cm silicon substrate (lines = simulation; markers = measurement), and simulated characteristics on 100- $\Omega$ -cm and 1 k- $\Omega$ -cm substrates. Also shown is a redesign of the coil on 1 k- $\Omega$ -cm silicon.

The experimental results (represented by markers and dashed lines) are 5-10% below the simulated ones. Note that reduction of the coil radius from 220 to 120  $\mu m$  (70% area reduction) only leads to a 15% lower  $Q_{\rm max}$ . SAM thus allows one to build a 10-nH inductor with nine turns and  $Q_{\rm max}=11.5$  at only 240  $\mu m$  diameter on 5- $\Omega$ -cm silicon (Fig. 10).

The extrapolations to higher substrate resistivities in Fig. 11 indicate, that the effect of SAM in reducing ohmic losses in the coil is far more significant at 1 GHz than the substrate losses. Simulations for the 10-nH coil of Fig. 5 show that changing the substrate resistivity from 5 to  $100~\Omega$ -cm barely increases Q at 1 GHz, whereas the increase in  $Q_{\rm max}$  upon using a high-resistivity 1 k- $\Omega$ -cm wafer is only 25%. Had we optimized the geometry of the coil for the high-resistivity substrate, the difference would hardly have been noticeable at 1 GHz (Fig. 11).

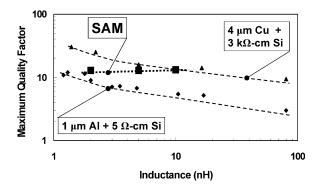

The effectiveness of SAM in improving the quality factor of integrated inductors becomes evident if one compares the results obtained, with the (experimental) values for  $Q_{\rm max}$  at different inductances, achieved for a conventional interconnect process (1- $\mu$ m Al, 10  $\Omega$ -cm Si) [3] and an innovative process based on a 4- $\mu$ m Cu interconnect process on a 3 k $\Omega$ -cm float-zone silicon substrate [19]. The result for the 10-nH SAM inductor nearly matches that achieved with the innovative process, in spite of the conventional 5- $\Omega$ -cm substrate used, indicating once again the importance of ohmic loss reduction by SAM. For smaller inductors, however, where the maximum quality factor  $Q_{\rm max}$

Fig. 12. Maximum Q versus inductance for 2-, 5-, and 10-nH SAM inductors on 5- $\Omega$ -cm silicon in comparison to results for conventional  $(1-\mu m \text{ Al}, 5-\Omega\text{-cm Si})$  and optimum  $(4-\mu m \text{ Cu}, 3-k\Omega\text{-cm Si})$  interconnect processes [8].

is achieved at higher frequencies, substrate RF loss becomes dominant. Nevertheless, considerable enhancement of  $Q_{\rm max}$  is evident at all inductance values addressed in Fig. 12.

### IV. CONCLUSIONS

SAM offers a cost-effective add-on process module for reduction of ohmic losses in RF inductors and interconnects. SAM is based on the local thickening of the top metal layer of the thin CMOS interconnects by Cu-plating and is particularly suitable for enhancing RF/BiCMOS and RF/CMOS technologies build on logic CMOS processes. The SAM process presented here is optimized for an Al top metal layer or a Cu top metal layer with an Al cap. The effectiveness of SAM is expressed by a record quality factor of  $\sim 13$  achieved for a 10-nH inductor on a conventional 5- $\Omega$ -cm silicon substrate. SAM is particularly effective in improving the quality factor of large inductors operating at low radio frequencies. Furthermore, it allows the reduction of the size of large inductors without any significant loss of quality factor.

# ACKNOWLEDGMENT

The authors wish to acknowledge Dr. L. Boellaard for help and discussions about the Cu-plating process.

## REFERENCES

- [1] A. Joseph, D. Coolbaugh, M. Zierak, R. Wuthrich, P. Geiss, Z. He, X. Liu, B. Orner, J. Johnson, G. Freeman, D. Ahlgren, P. Jagannathan, L. Lanzerotti, V. Ramachandran, J. Malinowski, H. Chen, J. Chu, P. Gray, R. Johnson, J. Dunn, and S. Subbanna, "A. 0.18  $\mu$ m BiCMOS technology featuring 120/100 GHz ( $f_{\rm T}/f_{\rm max}$ ) HBT and ASIC-compatible CMOS using copper interconnect," in *Proc. BCTM*, 2001, pp. 143–146.

- [2] J. N. Burghartz, "Silicon RF technology The two generic approaches," in *Proc. ESSDERC*, 1997, pp. 143–153.

- [3] J. N. Burghartz and B. Rejaei, "On the design of RF spiral inductors on silicon," *IEEE Trans. Electron Devices*, vol. 50, pp. 718–729, Mar. 2003.

- [4] B. Rejaei, J. Burghartz, and H. Schellevis, "Saddle add-on metallization (SAM) for RF inductor implementation in standard IC interconnects," in *IEDM Tech. Dig.*, 2002, pp. 467–470.

- [5] ITRS Roadmap [Online]. Available: http://public.itrs.net/Files/ 2001ITRS/Interconnect.pdf

- [6] J. N. Burghartz, M. Soyuer, and K. A. Jenkins, "Microwave inductors and capacitors in standard multilevel interconnect silicon technology," *IEEE Trans. Microwave Theory Tech.*, vol. 44, pp. 100–104, Jan. 1996.

- [7] R. Groves, J. Malinowski, R. Volant, and D. Jadus, "High Q inductors in a SiGe BiMOS process utilizing a thick metal process add-on module," in *Proc. BCTM*, 1999, pp. 149–152.

- [8] B. K. Kim, B. K. Ko, and K. Li, "Monolithic planar RF inductor and wave guide structures on silicon with performance comparable to those in GaAs MMIC," in *IEDM Tech. Dig.*, 1995, pp. 717–720.

- [9] D. C. Edelstein and J. N. Burghartz, "Spiral and solenoidal inductor structures on silicon using Cu-damascene interconnects," in *Proc. IITC*, 1998, pp. 18–20.

- [10] P. Gilbert, I. Yang, C. Pettinato, M. Angyal, B. Boeck, C. Fu, T. Van-Gompel, R. Tiwari, T. Sparks, W. Clark, C. Dang, J. Mendonca, B. Chu, K. Lucas, M. Kling, B. Roman, E. Park, F. Huang, M. Woods, D. Rose, K. McGuffin, and A. Nghiem, "A high performance 1.5 V, 0.10 μm gate length CMOS technology with scaled copper metallization," in *IEDM Tech. Dig.*, 1998, pp. 1013–1016.

- [11] K. Kuhn, M. Agostinelli, S. Ahmed, S. Chambers, S. Cea, S. Christensen, P. Fischer, J. Gong, C. Kardas, T. Letson, L. Henning, A. Murthy, H. Muthali, B. Obradovic, P. Packan, S. W. Pae, I. Post, S. Putna, K. Raol, A. Roskowski, R. Soman, T. Thomas, P. Vandervoorn, M. Weiss, and I. Young, "A 90 nm communication technology featuring SiGe HBT transistors, RF CMOS, precision R-L-C RF elements and 1 μm² 6-T SRAM cell," in *IEDM Tech. Dig.*, 2002, pp. 73–76.

- [12] T. A. Tran, L. Yong, B. Williams, S. Chen, and A. Chen, "Fine pitch probing and wirebonding and reliability of aluminum capped copper bond pads," in *Proc. Electronic Components Technology Conf.*, 2000, pp. 1674–1680.

- [13] G. Hotchkiss, J. Aronoff, J. Broz, C. Hartfield, and R. James, "Probing and wire bonding of aluminum capped copper pads," in *Proc. 40th Annual International Reliability Physics Symp.*, 2002, pp. 140–143.

- [14] P. Deixler, R. Colclaser, D. Bower, N. Bell, W. De Boer, D. Szmyd, S. Bardy, W. Wilbanks, P. Barre, M. v Houdt, J. C. J. Paasschens, H. Veenstra, E. v d Heijden, J. J. T. M. Donkers, and J. W. Slotboom, "QUBiC4G: A f<sub>T</sub>/f<sub>max</sub> = 70/100 GHz 0.25 μm low power SiGe-BiCMOS production technology with high quality passives for 12.5 Gb/s optical networking and emerging wireless applications up to 20 GHz," in *Proc. BCTM*, 2002, pp. 201–204.

- [15] K. Benaissa, J.-Y. Yang, D. Crenshaw, B. Williams, S. Sridhar, J. Ai, G. Boselli, Z. Song, T. Shaoping, S. Ashburn, P. Madhani, T. Blythe, N. Mahalingam, and H. S. Shichijo, "RF CMOS on high-resistivity substrates for system-on-chip applications," *IEEE Trans. Electron Devices*, vol. 50, pp. 567–576, Mar. 2003.

- [16] E. Valletta, J. van Beek, A. den Dekke, N. Pulsford, H. F. F. Jos, L. C. N. de Vreede, L. K. Nanver, and J. N. Burghartz, "Design and characterization of integrated passive elements on high ohmic silicon," in *Proc. IEEE MTT-S Int. Microwave Symp.*, vol. 2, June 8–13, 2003, pp. 1235–1238.

- [17] E. Boellaard, J. N. Burghartz, and C. I. M. Beenakker, "Copper electroplating for integrated RF devices," in *Proc. Semiconductor Advances Future Electronics*, 1999, pp. 733–738.

- [18] B. Rejaei, J. L. Tauritz, and P. Snoeij, "A predictive model for Si-based circular spiral inductors," in *Proc. Topical Meeting Silicon Monolithic Integrated Circuits RF Systems*, 1998, pp. 148–154.

- [19] J. N. Burghartz, D. C. Edelstein, K. A. Jenkins, and Y. H. Kwark, "Spiral inductors and transmission lines in silicon technology using copper-damascene interconnects and low-loss substrates," *IEEE Trans. Microwave Theory Tech.*, vol. 45, pp. 1961–1968, Nov. 1997.

**Joachim Burghartz** (M'90–SM'92–F'02) received the M.S. degree from the RWTH Aachen, Germany, in 1982 and the Ph.D. degree from the University of Stuttgart, Stuttgart, Germany, in 1987.

From 1987 to 1998, he was with the IBM T. J. Watson Research Center, Yorktown Heights, NY, working on selective epitaxial growth of silicon, high-speed Si and SiGe bipolar integration processes,  $0.18-\mu$ m CMOS, the integration of spiral inductors and other passive components for RF applications, and on RF circuit design. In 1998

he became Full Professor at the Technical University of Delft, Delft, The Netherlands, where he has set up a research program in RF silicon technology, including topics in novel materials, micromachining post-process modules, wafer-level chip-scale packaging, passive components, circuit integration processes, compact transistor modeling, high-frequency characterization, and RF circuit design. Since March 2001, he has been the Scientific Director of the Delft Institute for Microelectronics and Submicrontechnology (DIMES).

Dr. Burghartz has served, or is currently serving, in conference committees such as IEDM, BCTM, and ESSDERC/ESSCIRC. He is an Associate Editor of the IEEE Transactions on Electron Devices.

**Behzad Rejaei** received the M.Sc. degree in electrical engineering from the Delft University of Technology, Delft, the Netherlands, in 1990 and the Ph.D. degree in theoretical condensed matter physics from the University of Leiden, Leiden, the Netherlands, in 1994.

He was a post-doctoral research fellow in the Theoretical Physics Department at the University of Leiden in 1994 and 1995 and in the Department of Applied Physics at the Delft University of Technology from 1995 to 1997. Since 1997 he has

been with the Department of Information Technology and Systems at the Delft University of Technology where he is currently an Associate Professor. His research interests are in the areas of electromagnetic modeling of integrated passive components and physics of ferromagnetic devices.

transfer technology.

**Hugo Schellevis** received the degree in chemical engineering in 1986 from the Institute of Technology in Amsterdam, Amsterdam, The Netherlands. In 1996, he received the M.S. degree in chemical engineering from the University of Amsterdam.

In 1987, he joined the Delft Institute for Microelectronics and Submicrontechnology (DIMES) IC Process Research Sector, Delft University of Technology, Delft, The Netherlands, as a Process Engineer. Currently, his main research interest is the development of metallization processes, and substrate