# Integrated Transceivers for Emerging Medical Ultrasound Imaging Devices

# A Review

Chen, Chao; Pertijs, Michiel A.P.

10.1109/OJSSCS.2021.3115398

**Publication date**

**Document Version** Final published version

Published in

IEEE Open Journal of Solid-State Circuits

Citation (APA)

Chen, C., & Pertijs, M. A. P. (2021). Integrated Transceivers for Emerging Medical Ultrasound Imaging Devices: A Review. *IEEE Open Journal of Solid-State Circuits*, *1*, 104-114. Article 9547382. https://doi.org/10.1109/OJSSCS.2021.3115398

# Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

Received 16 July 2021; revised 8 September 2021; accepted 14 September 2021. Date of publication 24 September 2021; date of current version 19 October 2021.

Digital Object Identifier 10.1109/OJSSCS.2021.3115398

# Integrated Transceivers for Emerging Medical Ultrasound Imaging Devices: A Review

CHAO CHEN<sup>®</sup> (Member, IEEE), AND MICHIEL A. P. PERTIJS<sup>®</sup> (Senior Member, IEEE) (Invited Paper)

Electronic Instrumentation Laboratory, Delft University of Technology, 2628 CD Delft, The Netherlands CORRESPONDING AUTHOR: M. PERTIJS (e-mail: m.a.p.pertijs@tudelft.nl)

ABSTRACT As medical ultrasound imaging moves from conventional cart-based scanners to new form factors such as imaging catheters, hand-held point-of-care scanners and ultrasound patches, there is an increasing need for integrated transceivers that can be closely integrated with the transducer to provide channel-count reduction, improved signal quality and even full digitization. This paper reviews compact and power-efficient circuit solutions for such transceivers. It starts with a brief overview of ultrasound transducer technologies and the operating principles of the ultrasound transmit-receive signal path. For transmission, high-voltage pulsers are reviewed, from compact unipolar pulsers to multi-level pulsers that provide amplitude control and improved power efficiency. The review of receive circuits starts with low-noise amplifiers as the power- and performance-limiting building block. Solutions for time-gain compensation are discussed, which are essential to reduce signal dynamic range by compensating for the decaying echo-signal amplitude associated with propagation attenuation. Finally, the option of direct digitization of the echo signal at the transducer is discussed. The paper ends with a reflection on future opportunities and challenges in the area of integrated circuits for ultrasound applications.

**INDEX TERMS** Ultrasound imaging, high-voltage pulsers, analog front-ends, low-noise amplifiers, timegain compensation, in-probe digitization.

## I. INTRODUCTION

LTRASOUND imaging is widely used to assist diagnosis and guide treatments in a broad range of medical applications, such as obstetrics and cardiology. Although ultrasound imaging has been around for decades, new developments are poised to radically change the way ultrasound is used. First, the form factor is changing. While ultrasound imaging is still mostly based on hand-held probes connected to a bulky imaging system, it is now becoming available in the form of pocketsize handheld scanners [1], endoscopes [2], catheters [3], pills [4] and patches [5] (Fig. 1). Second, ultrasound imaging is moving from 2D to 3D. While conventionally a 1D transducer array is used to produce 2D cross-sectional images, 2D arrays that can generate 3D images become increasingly common, not only in hand-held probes, but also in miniature probes like endoscopes and imaging catheters [2], [3]. Third, ultrasound is moving out of the hands of an expert sonographer into more widespread use by clinicians in general and, eventually, by the

general public, calling for cost reduction and increased user-friendliness [1].

Integrated circuits play a key role in these developments. The electronics architecture of conventional imaging systems, based on commercial off-the-shelf components, is not scalable to the mentioned new form factors in terms of size and power consumption. Moreover, in terms of channel count, these architectures are not scalable to 3D imaging. Integrated transceiver circuits, closely integrated with the ultrasound transducer array, can solve these problems, *e.g.*, [2], [7], [8]. Combined with the move from conventional labour-intensive and expensive bulk-piezoelectric transducer technology to micro-machined transducers, integrated circuits also pave the way to the cost reduction needed for more widespread use [1].

This paper reviews recent advances in the design of integrated ultrasound transceivers. Section II starts with a review of transducer technologies and ultrasound system architectures, highlights the enabling role of integrated transceivers for new applications, and links system requirements to

FIGURE 1. Examples of emerging medical ultrasound imaging devices (clockwise from the left): a hand-held point-of-care ultrasound scanner (image courtesy of Butterfly Network) [1]; a 3D intra-cardiac imaging catheter [3]; an artists impression of a 3D transesophageal ultrasound probe [2]; a pill-shaped ultrasonic endoscopy device (image courtesy of Univ. of Glasgow) [4]; an artist's impression of a wearable ultrasound patch (image courtesy of ULIMPIA project) [6].

front-end building-block specifications. Section III discusses recent advances in integrated transmitter circuits, while Section IV focuses on receiver circuits. Finally, Section V draws conclusions and provides an outlook.

#### **II. ULTRASOUND SYSTEM ARCHITECTURE**

#### A. ULTRASOUND TRANSDUCERS

In an ultrasound imaging system, the transducer is responsible for emitting acoustic waves into the body and for recording the returning echo signals [9], [10]. While information about the depth from which an echo originates can be derived from its arrival time, the ability to resolve objects or scatterers laterally is obtained by means of beamforming. For this, ultrasound transducers tend to be divided into an array of elements. For 2D imaging, 1D arrays (linear arrays or phased arrays) are used, with up to 256 elements. For 3D imaging without resorting to mechanical translation or rotation of a 1D array, a 2D array is needed (also referred to as a matrix transducer), which can consist of thousands of elements. The overall size (aperture) of the array relates to the field of view and spatial resolution that are required, while the element pitch tends to be dictated by beamforming requirements (in particular the need to avoid grating lobes). For phased-array transducers, this implies that a pitch of about half the wavelength is needed [9].

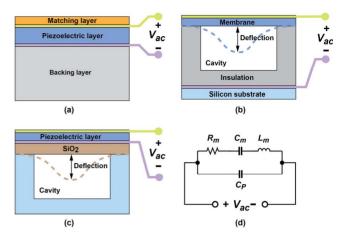

The vast majority of ultrasound probes in use today is based on bulk piezoelectric transducers (Fig. 2a) [9]. A layer of piezoelectric material, typically a piezoceramic such as lead-zirconate-titanate (PZT) or a piezocomposite, is mechanically diced into elements and equipped with top and bottom electrodes. An AC voltage applied to these electrodes is converted into a pressure wave through the piezoelectric effect, while, conversely, an incoming pressure wave can be detected as a charge displacement or voltage change on the electrodes. Mechanically, such a transducer is a thickness-mode resonator tuned to the frequency range of interest, typically with a low quality factor to allow transmission of short pulses. To ensure effective coupling of the

FIGURE 2. Schematic representation of (a) a bulk piezoelectric transducer, (b) a capacitive micromachine ultrasound transducer (CMUT), (c) a piezoelectric micromachined ultrasound transducer (PMUT), and (d) the Butterworth-Van Dyke equivalent circuit model.

acoustic waves into the medium in spite of mismatches in acoustic impedance, backing and matching layers are used. Fabrication of bulk piezoelectric transducer arrays, in particular 2D arrays, is relatively complex, time-consuming, and hence expensive.

To overcome these fabrication challenges, wafer-scale batch-fabrication techniques have been explored extensively as an alternative [11], [12]. The resulting micro-machined ultrasound transducers (MUTs) are based on a thin flexible membrane fabricated using surface or bulk micro-machining techniques. In the case of piezoelectric MUTs (PMUTs), a thin piezoelectric film with electrodes is deposited on the membrane (Fig. 2b) [12].

In the case of capacitive MUTs (CMUTs), the membrane is electrostatically actuated by means of electrodes in the membrane and in the substrate underneath (Fig. 2c) [11]. Typically, a relatively large DC bias voltage is applied to statically deflect the membrane and linearize its behavior. A smaller superimposed AC voltage is used for transmission, while for reception, the charge displacement due to capacitance changes associated with membrane deflection is detected.

In spite of their very different operating principles, the electrical impedance of all three mentioned transducer types can be modeled, to first order, using a so-called Butterworth Van-Dyke model (Fig. 2d), which includes a resonant branch  $(R_m, L_m, C_m)$  that models the mechanical resonance of the transducer, and a capacitor  $(C_p)$  that represents its electrical capacitance [13]. This single-port model proves useful in modeling the load that the transducer represents at the output of a transmit circuit, and in modeling of the transducer as a small-signal source at the input of an LNA, where a source can be included in the resonant branch to represent the acoustic input, and the thermal noise associated with  $R_m$  represents the noise contribution of the transducer. For a more accurate representation of the acoustic domain, a two-port model can be adopted [14].

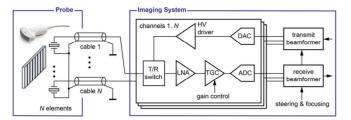

FIGURE 3. Block diagram of a conventional ultrasound imaging system.

#### B. CONVENTIONAL ULTRASOUND IMAGING SYSTEMS

Fig. 3 shows a block diagram of a conventional ultrasound imaging system interfacing with a probe containing an array of N transducer elements, each of which serves to transmit (TX) and receive (RX) acoustic waves [10]. These elements are connected using cables to transceiver channels in the imaging system. For transmission, the elements are driven by pulses timed by a TX beamformer to achieve a desired spatial distribution of the acoustic wave, typically focusing it at a point along the scan line to be imaged. To generate enough pressure to yield detectable echo signals even at the deepest point to be imaged, where propagation attenuation strongly reduces the signal amplitude, the transducer elements are typically driven with high-voltage (HV) pulses, with amplitudes ranging from tens of Volt to even more than 100 V. These pulses are fed to the elements through transmit/receive (T/R) switches that protect the receive circuits during pulse transmission.

After transmission, the echo signals received by each transducer element are amplified by a low-noise amplifier (LNA). In an attenuating medium such as the human body, the first echo signals that return to the probe, which come from scatters close to the probe, have higher amplitudes than echoes arriving later, which come from deeper scatters and hence are subject to more propagation attenuation [9]. This decreasing amplitude is compensated for by a time-gain compensation (TGC) amplifier, which provides a gain that increases linearly-in-dB with time [10]. Thus, the dynamic range is strongly reduced. The echo signals are then digitized by an analog-to-digital converter (ADC) (typically preceded by an anti-aliasing filter, not shown in Fig. 3).

An RX beamformer combines the digitized echo signals, in the simplest case by means of a delay-and-sum operation, so as to constructively add signals coming from a desired focal point while suppressing signals from other locations [9], [10]. The output of the RX beamformer is further processed to render an image. In the case of brightness-mode (B-mode) imaging, both the TX and the RX beamformer focus on a point along a scan line in the medium. Envelope detection of the output of the RX beamformer then yields the image brightness along the corresponding line in the image. Multiple scan lines are combined to form the image, each of which requires a cycle of pulse transmission and echo reception [9].

FIGURE 4. Smart ultrasound probe with in-probe ASIC.

Due to the one-to-one correspondence between transducer elements, cables and transceiver channels in the architecture of Fig. 3, the number of elements is limited by practical constraints in cable count and system size to at most 256 for high-end imaging systems, *e.g.*, [15]. This limits the use of matrix transducers needed for 3D imaging, which readily consist of thousands of elements.

#### C. INTEGRATED CIRCUITS IN THE PROBE

A primary motivation to integrate ASICs into ultrasound probes is to bridge the gap between the high number of transducer elements needed for 3D imaging, and the limited number of system channels (Fig. 4a). Various approaches have been taken to do so, including multiplexing [16]–[18] and sub-array beamforming [2], [7], [19]. In these cases, the ASIC provides analog output signals to the imaging system. ASICs also help to improve signal-to-noise ratio (SNR), as they locally amplify the echo signals received by the transducer elements, thus avoiding the signal attenuation associated with connecting the small, high-impedance elements of a matrix transducer to long cables.

The functionality of in-probe ASICs can go well beyond channel-count reduction. For instance, the ASIC can provide full digitization (Fig. 4b) and further processing of the echo signals [8], [20]. In the case of portable ultrasound probes, this is an essential step, as the imaging system with analog front-ends and ADCs has been replaced by a smartphone or tablet [1]. Thus, the data acquisition functionality that was traditionally implemented in the imaging system moves into the ASIC, while the image processing is implemented in software.

#### D. TRADE-OFFS IN TRANSCEIVER DESIGN

Key building blocks of any in-probe ASIC are the elementlevel transceiver circuits. They determine to a large extent the performance in terms of SNR, and tend to dominate power consumption, and should therefore be carefully optimized.

Essential for this optimization is the analysis of the transmit-receive signal path, a typical example of which is illustrated in Fig. 5, in which each transducer element is driven by a pulser. The pressure generated at the surface of the elements depends on the amplitude of the applied pulse, and the transmit efficiency (expressed in Pa/V) of the transducer. In the case of focused transmission, the pulses

FIGURE 5. Transmit-receive signal path (with pulse transmission in red, and echo reception in blue).

are timed by the transmit beamformer such that the generated acoustic waves converge at the desired focal point. The pressure at this focal point can then be found by taking into account the TX beamforming gain and the propagation attenuation in the medium.

The acoustic wave will reflect from interfaces between regions with different acoustic impedance in the medium, leading to echoes that return to the transducer. The amplitude of an echo depends on the reflection coefficient associated with the interface, and the geometrical spreading and attenuation that the echo experiences as it travels back to the transducer. The resulting surface pressure at one of the elements then translates to a voltage through the transducer's receive sensitivity (expressed in V/Pa). This signal is amplified by the LNA and TGC and digitized, and finally combined with the signals from other elements by the receive beamformer. Here, the correlated signals from the different channels add up constructively, while uncorrelated noise does not, giving an RX beamforming gain. Note that other configurations are possible, e.g., part of the beamforming may take place in the analog domain before digitization [19]. Still, a similar analysis will apply.

The system shown in Fig. 5 has many design parameters that need to be chosen to achieve a desired SNR at the RX beamformer output while minimizing power consumption. For a given array configuration, a given beamforming scheme and given transducer characteristics, the amplitude of the signal received by an individual transducer element is mainly dictated by the amplitude of the applied TX pulse, while the noise floor is limited by the noise of the element. The final SNR is degraded by the noise figure (NF) of the receive circuits, which can be improved at the expense of power consumption, and enhanced by the RX beamforming gain. Clearly, a minimum TX amplitude can be found for which the desired SNR is achieved in the ideal case of a noise-free receive circuits, i.e., a NF of 0 dB. In many cases, this amplitude already exceeds tens of Volts, calling for HV pulsers implemented in special HV CMOS technology. The practical TX amplitude will need to be chosen higher, so as to leave room for a realistic NF, leading to a trade-off between TX power consumption and RX power consumption. Often, even at the highest TX amplitude supported by the CMOS technology, (average) TX power consumption is still far from dominant, due to the

FIGURE 6. Variants of unipolar square-wave pulser front-ends: (a) a simple implementation using a single HV NMOS pull-up transistor [24]; (b) an HV cross-coupled level shifter [25]; (c) an HV inverter [26], [27].

very short duration of pulse transmission compared to echo reception.

#### **III. INTEGRATED TRANSMITTER CIRCUITS**

While in conventional ultrasound systems, HV signals to drive the transducer elements are generated in the imaging system, the emerging devices addressed in this paper call for integration of TX functionality closer to the transducer. This can take the form of HV switching or multiplexing, which allows multiple transducer elements to be connected to a single TX channel in the imaging system [16]-[18]. However, to avoid the reduction in frame rate associated with multiplexing, it is desirable to generate the HV signals at the element level. Depending on the type of voltage waveform required, ultrasound transmitter circuits can be classified into two categories: pulsers and linear amplifiers. While both categories have been extensively adopted in discrete-circuit ultrasound systems [21]–[23], pulsers have been more widely adopted in integrated systems for their simplicity and superior power efficiency. Recent advances in solid-state circuit technologies, especially the rapidly expanding HV process options, have enabled several new on-chip transmitter solutions that address the diverse demands of emerging integrated ultrasound systems. This section reviews the latest advances of integrated transmitter circuits, with a special focus on emerging techniques for pulser design. A performance summary for state-of-the-art integrated pulsers is presented in TABLE 1.

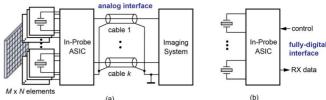

#### A. SQUARE-WAVE PULSERS

As the simplest transmitter architecture, a square-wave pulser generates a wide-band excitation voltage that alternates between two voltage levels at a fixed or varying frequency. Unipolar square-wave pulsers were first adopted in integrated ultrasound transceivers for their simplicity. During transmission, their output swings between the ground potential and a single HV supply, either positive or negative. This typically can be realized using a small number of HV transistors. For example, in [24] Gurun *et al.* used a single HV NMOS transistor and a pull-up resistor to establish a compact pulser (Fig. 6a) for a high-frequency IVUS catheter where the space

TABLE 1. Performance comparison for state-of-the-art integrated pulsers.

|                             | [25]                 | [26]                 | [7]                       | [38]                 | [39]                      | [30]                 | [37]                  | [8]                       | [40]                 | [41]                |

|-----------------------------|----------------------|----------------------|---------------------------|----------------------|---------------------------|----------------------|-----------------------|---------------------------|----------------------|---------------------|

| Target<br>transducer        | CMUT                 | CMUT                 | PZT                       | CMUT                 | CMUT                      | PMUT                 | PZT                   | CMUT                      | PMUT                 | N/A                 |

| Transducer capacitance [pF] | 2.5                  | 23                   | N/A                       | 40                   | 8                         | 15.4                 | 18                    | < 8                       | 37.7                 | 820                 |

| Process                     | 1.5 μm<br>HV<br>CMOS | 0.18 μm<br>BCD-SOI   | 0.18 μm<br>HV SOI<br>CMOS | 0.18 μm<br>HV CMOS   | 0.18 μm<br>60V HV<br>CMOS | 0.18 μm<br>LV CMOS   | 0.18 μm<br>BCD        | 0.13 μm<br>BCD            | 0.18 μm<br>BCD       | 0.18 μm<br>BCD      |

| Max pulse<br>voltage [V]    | 25V                  | 100V                 | 138V                      | 30V                  | 85 V                      | 13.2V                | 60V                   | 50V                       | 28.7V                | 30V                 |

| Polarity                    | Unipolar             | Unipolar             | Bipolar                   | Unipolar             | Unipolar                  | Unipolar             | Bipolar               | Bipolar                   | Unipolar             | Unipolar            |

| Pulse shaping               | No                   | No                   | Yes                       | Yes                  | Yes                       | Yes                  | Yes                   | Yes                       | Yes                  | No                  |

| Voltage levels              | 2                    | 2                    | 3                         | 3                    | 3                         | 3                    | 3                     | 7                         | 7                    | 2                   |

| TX freq. [MHz]              | N/A                  | 10                   | 1.5-2                     | 3.3                  | 8.33                      | 5                    | 7.5                   | 1-10                      | 1                    | N/A                 |

| Dynamic power saving        | 0%                   | 0%                   | 0%                        | 38% (@3.3<br>MHz)    | 0%                        | 32.8% *<br>(@5 MHz)  | N/A                   | 0%                        | 57.9%<br>(@1MHz)     | 73.1%               |

| On-chip area                | 0.02 mm <sup>2</sup> | 0.12 mm <sup>2</sup> | 0.04 mm <sup>2</sup>      | <0.3 mm <sup>2</sup> | 0.2 mm <sup>2</sup>       | 0.02 mm <sup>2</sup> | 0.167 mm <sup>2</sup> | <0.015<br>mm <sup>2</sup> | 10.8 mm <sup>2</sup> | 5.4 mm <sup>2</sup> |

| Off-chip component          | N/A                  | N/A                  | N/A                       | DC/DC<br>converters  | Capacitor<br>(100 pF)     | N/A                  | N/A                   | N/A                       | Capacitors (> 3 nF)  | Inductor            |

<sup>\*</sup>Only for dynamic power spent on charging and discharging parasitic capacitance to ground.

is limited. However, the current drawn when the pulser output is low results in power waste, and the pull-up resistor usually limits the pulse rising time when interfacing with a capacitive load, e.g., a CMUT [11]. Alternatively, Wygant et al. employed a cross-coupled level-shifter with HV cascodes to eliminate static current while supporting up to 25-V unipolar pulses [25]. As shown in Fig. 6b, the cross-coupled pair at the high-side provides positive-feedback to ensure fast switching when driving highly capacitive MUTs. However, excess silicon area is required for the HV cascode pair. An inverter-type pulser [26], [27] as shown in Fig. 6c provides a better balance between power and area-efficiency. This requires an extra level-translator to drive the high-side PMOS relative to the HV supply (HVDD). It can be implemented using either a low-power capacitively-coupled latch, similar to [28], or a pull-up resistor in parallel with voltage-clamping diodes [8], [26]. Adding extra digital buffers between the level-translators and the gates of HV transistors helps to speed up switching [26], but requires a floating ground at the voltage of HVDD- $V_{GS}$ , where  $V_{GS}$  is the gate-source voltage of the HV transistor. Alternatively, some designs [29], [30] proposed to generate HV pulses using stacked LV transistors, but this is associated with increased circuit complexity and potential reliability concerns.

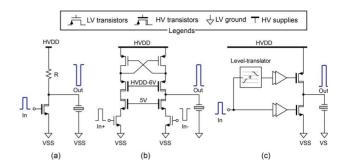

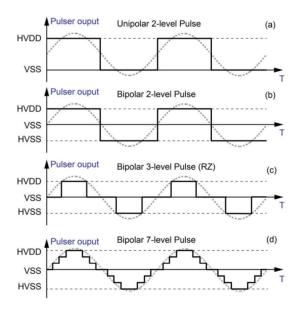

A drawback of unipolar pulsers is that their output waveforms comprise a DC component (Fig. 7a), leading to a significant amount of the transmitted energy distributed around even-order harmonics [21]. This results in a loss of the round-trip SNR compared to a bipolar pulse with the same transmit pulse voltage. Moreover, it is not compatible with techniques like tissue harmonic imaging [31], which

FIGURE 7. Typical pulse waveforms: (a) unipolar 2-level; (b) bipolar 2-level; (c) bipolar 3-level with return-to-zero; (d) bipolar 7-level.

improves the imaging quality by using second-order harmonics of tissue echoes. Furthermore, the utility of other non-linear imaging techniques, such as pulse inversion [32] and chirp coding [33], are also rather limited in unipolar pulsers. Integrated bipolar pulsers overcome these limitations by generating excitation signals that symmetrically transits between positive and negative HV voltage levels, as shown in Fig. 7b. The typical implementation of a bipolar pulser uses either an HV inverter [8] or a source-follower-based

push-pull stage [7] with positive and negative HV supplies as the front-end stage.

### B. MULTI-LEVEL PULSERS

Multi-level pulsing (Fig. 7c, 7d) is becoming increasingly important for integrated ultrasound imagers because it 1) improves the transmission linearity and 2) allows temporal and spatial apodization by applying pulse-shaping to individual elements in a transducer array. Both contribute to sidelobe reduction and contrast enhancement in the reconstructed image. Moreover, some multi-level pulsing techniques help in saving the dynamic power dissipation associated with charging or discharging the capacitive load, provided that part of the charge can be recycled, *e.g.*, to regulated supplies during intermediate voltage transitions [34]. Finally yet importantly, for CMUTs that operate in the collapse mode [35], a multi-level pulsing profile reduces the membrane velocity at contact, which helps in improving the device reliability [1], [36].

As the simplest form of multi-level pulser, a 3-level pulser can be obtained by adding return-to-zero (RZ) switching to a bipolar square-wave pulser. In [37], this was realized by adding a direct discharging path from the transducer to ground via a HV floating-gate driver and a grounding switch. Alternatively, in [7] this grounding switch is added to the output of a pre-driver stage rather than the source-follower push-pull stage that drives the transducer directly. This helps in reducing the size of the switch transistor, but also eliminates potential savings of the switching power required for driving the transducer capacitance. In contrast, the design in [37] achieves  $\sim$ 50% dynamic power reduction as it resembles a 3-level charge-recycling pulser, which will be discussed below.

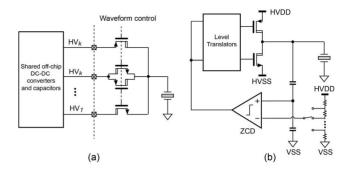

The general concept of N-level charge-recycling pulsers and its use in integrated ultrasound front-ends was first proposed in [38]. As shown in Fig. 8a, it employs (N-1) HV switches, each connected to a regulated voltage source, to charge and discharge the transducer in a stepwise manner. Rather than directly discharging the transducer capacitance to ground as in the case of square-wave pulsers, a 1/(N-1) portion of the charge stored on the transducer capacitance is recycled back to the regulated supply when the pulser transits between different voltage levels. As such, the dynamic power consumption ( $CVf^2$ ) is reduced by a factor of N-1. A shortfall of this architecture is that it requires excessive HV switches when N > 3, which call for significant silicon area and dynamic driving power for driving internal gates rather than the transducer. Moreover, the need for multiple off-chip HV voltage sources complicates the system hardware. These problems prevent the application of charge-recycling multilevel pulsers in a large transducer array that calls for high integration density.

An alternative charge-recycling mechanism was proposed in [30], in which the two electrodes of a differential PMUT element are shorted to discharge the element, rather than switching both electrodes to ground. This helps to

FIGURE 8. Pulser architectures that enable multi-level pulse shaping: (a) a charge-recycling pulser leveraging off-chip HV supplies [37]; (b) a feedback-based pulser [7].

reduce the energy spent on charging and discharging parasitic capacitance to ground. In [39] and [40], a capacitive supply-multiplication scheme was proposed that substantially reduces power consumption, albeit at the cost of very large capacitors. Finally, the energy stored on the transducer capacitance can also be recycled using an inductor, for which power savings up to 75% have been reported [41]. However, the need for an off-chip inductor for each pulser makes this approach unsuitable for use with transducer arrays.

As discussed in Section II-D, in an integrated ultrasound imaging system with a low TX/RX duty cycle, the transmission usually does not dominate the power consumption. This creates room for designers to trade the capability of dynamic energy saving for a more compact multi-level pulser. Sanchez et al. proposed a feedback-based 7-level pulser small enough to be closely integrated with ceptual schematic. It employs a capacitive voltage divider to scale down the HV pulser output voltage to a lowvoltage (5V) domain, where a zero-crossing-detector (ZCD) and a digital feedback controller operate. There, the divided voltage is first compared with a scaled-down level-reference that is dynamically selected from a local voltage ladder. The decision is then sent to the digital controller to control the HV front-end to charge or discharge the transducer towards a target voltage. As neither HV transistors nor off-chip HV supplies are required in constructing the intermediate voltage levels, this solution permits the implementation of a highly compact multi-level pulser. It is worth noting that the accuracy of these voltage levels is directly affected by the ZCD overshoot [42], which can be optimized by implementing a dedicated ZCD bias control.

#### **IV. INTEGRATED RECEIVERS**

# A. LOW-NOISE AMPLIFIERS

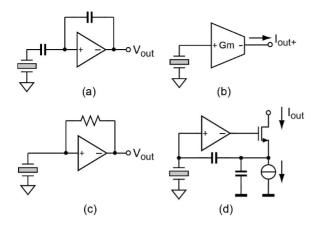

In most integrated ultrasound systems, an LNA is the first building block in the receive chain that interfaces with the transducer directly. It provides linear amplification of the echo signals to suppress the noise contribution from succeeding circuits. Depending on the impedance characteristic of the target transducer and the desired output format for further signal processing, such amplification can be

FIGURE 9. Ultrasound LNA topologies: (a) a capacitive-feedback voltage amplifier (VA); (b) a transconductance amplifier (TCA); (c) a resistive-feedback transimpedance amplifier (TIA); (d) a capacitive-feedback current amplifier (CA).

embodied as a voltage gain [43], a current gain [44], a transimpedance gain [45] or a transconductance gain [46]. As the LNA usually dominates the noise performance of an integrated receiver, it requires a considerable amount of power and area to guarantee an adequate NF for the entire system. In most cases, the majority of the receiver power is consumed by the LNA. A smart choice of the LNA topology requires an optimal trade-off between noise, power and area based on in-depth knowledge of transducer characteristics.

Among different LNA architectures, voltage amplifiers (VA) (Fig. 9a) [47], [48] and transconductance amplifiers (TCA) (Fig. 9b) [46] sense the transducer's voltage by creating a relatively high input impedance, while transimpedance amplifiers (TIA) (Fig. 9c) [26], [45], [49], [50] and current amplifiers (CA) (Fig. 9d) [51] sense the current by establishing a low input impedance virtual ground. Therefore, in integrated systems, VA and TCA are usually used to interface with transducers with lower impedance (< 2  $k\Omega$ ), such as PZTs [52], [53] and PMUTs [30], [46], while TIA and CA are commonly adopted for CMUTs and polyvinylidene fluorides (PVDF) transducers [54], [55] which often exhibit relatively higher impedance (> 10  $k\Omega$ ) [56]. Note that the transducer impedance is a complex function of its physical dimension, material, fabrication process and acoustic load. Therefore, for custom integrated systems a tailored analysis based on the specific transducer impedance profile is required to determine the optimal topology [57]. For example, the fine-pitch  $(< 100 \mu m)$  PZTs for high-frequency IVUS applications as presented in [18] show a relatively high impedance (5 k $\Omega$ ), making current sensing with a TIA the more energy-efficient choice.

On the basis of an efficient LNA architecture, various circuit techniques have been developed to further optimize the noise-power trade-off and area-efficiency. For instance, capacitive feedback has been exploited in both VAs [17], [47], [58] and TIAs [24], [26], [54], [59] to eliminate the noise contribution from the feedback path, at the

cost of a slightly reduced bandwidth [60]. On the other hand, current-reuse amplifiers, either single-ended [2] or differential [8], [18], have been widely adopted in the implementation of the core amplifier to boost the current-efficiency and save area.

Besides noise, power and area, there are several specification parameters that should be considered when designing an ultrasound LNA for use in massively parallel arrays. For example, any subtle correlated signal that applies to an array of LNA channels, such as digital interference coupled to the analog supply, will get magnified with an extra gain of  $\sqrt{N}$  (N being the array size) relative to its uncorrelated counterpart after array-level summing, averaging [8] or beamforming [2], [19]. This may result in distinct artifacts in the reconstructed ultrasound image [7], even if the original correlated noise is lower than the noise floor of individual LNA channels. Consequently, a power-supply rejection capability that is proportional to the size of the array is critical for LNA array design. Adding distributed supply regulators to each LNA subgroup is an effective way to address this challenge [47]. Similarly, any electrical crosstalk between neighboring LNA channels might cause elevation of side lobes, leading to artifactual echoes beside the main beam. Therefore, careful layout efforts are typically required to shield sensitive signals from each other despite their physical proximity.

As a summary, TABLE 2 lists a performance summary and comparison for state-of-the-art ultrasound LNAs targeting different types of transducers. We adopt the acoustic-domain noise-efficiency-factor (ANEF) [37] as a figure-of-merit (FoM) for this comparison:

$$ANEF = p_{n,in} \cdot \sqrt{P_{LNA}} \tag{1}$$

where  $p_{n,in}$  is the input-referred acoustic pressure noise spectral density averaged across the passband, and  $P_{LNA}$  is the power consumption of the LNA. It measures the efficiency in trading the LNA power consumption for the minimum input-referred acoustic pressure noise. As noise is measured in the acoustic rather than the electrical domain, the transducer and the LNA are considered as a whole in the evaluation of the noise efficiency, which reflects the importance of selecting the optimal LNA architecture for maximizing the transducer receive sensitivity.

# B. TIME-GAIN COMPENSATION AMPLIFIERS

There are various approaches to establish a TGC amplifier. Depending on how the gain control is implemented, these architectures fall into two main categories: programmable gain amplifiers (PGAs) with discrete gain steps, and variable gain amplifiers (VGAs) with continuous gain control. In both cases, the gain varies (approximately) exponentially with either the digital gain code or the analog control voltage, delivering a linear-in-dB time-gain profile.

A compelling advantage of PGAs for an integrated ultrasound system is that their gain steps can be precisely and robustly set, which is essential in ensuring the

TABLE 2. Performance comparison for state-of-the-art integrated ultrasound front-end amplifiers.

|                                                | [49]                  | [45]                          | [38]                          | [50]                          | [26]                           | [47]                          | [48]                    | [43]                  | [51]                            |

|------------------------------------------------|-----------------------|-------------------------------|-------------------------------|-------------------------------|--------------------------------|-------------------------------|-------------------------|-----------------------|---------------------------------|

| Target transducer                              | CMUT                  | CMUT                          | CMUT                          | CMUT                          | CMUT                           | PZT                           | PZT                     | PMUT                  | PZT                             |

| Process                                        | 0.8 μm<br>CMOS        | 1.5 μm HV<br>CMOS             | 0.18 μm<br>HV CMOS            | 0.18 μm<br>HV CMOS            | 0.18 μm<br>BCD-SOI             | 0.18 μm<br>CMOS               | 0.35 μm<br>CMOS         | 0.13 μm HV<br>CMOS    | 0.18 μm<br>BCD                  |

| Topology                                       | TIA                   | Resistive-<br>feedback<br>TIA | Resistive-<br>feedback<br>TIA | Resistive-<br>feedback<br>TIA | Capacitive-<br>feedback<br>TIA | Capacitive-<br>feedback<br>VA | Open-loop<br>VA         | Open-loop<br>VA       | Capacitive -<br>feedback<br>TIA |

| Voltage gain [dB]                              | 16                    | N/A                           | N/A                           | N/A                           | 14.2                           | -12/6/24                      | 16.5-31                 | 21.8                  | N/A                             |

| Transimpedance gain [dBΩ]                      | N/A                   | 112                           | 96.6                          | 104-116                       | N/A                            | N/A                           | N/A                     | N/A                   | 70-107                          |

| Bandwidth [MHz]                                | 11                    | 25                            | 5.2                           | 10.2                          | 10                             | 9.8                           | 6.6                     | 22                    | 7                               |

| Power/ch.<br>[mW]                              | 2                     | 9                             | 14.3                          | 1.4                           | 1                              | 0.135                         | 7.8                     | 0.3                   | 5.2                             |

| Input-referred Noise                           | 6.5 nV/√Hz<br>@ 1 MHz | 0.9<br>mPa/√Hz<br>@4.4MHz     | 0.55<br>mPa/√Hz<br>@3MHz      | 0.41<br>pA/√Hz @8<br>MHz      | 0.55<br>mPa/√Hz *              | 5.5 nV/√Hz<br>@ 2.5 MHz       | 5.4 nV/√Hz<br>@ 2.5 MHz | 7.1 nV/√Hz<br>@ 3 MHz | 1.7 pA/√Hz<br>@ 5 MHz           |

| Area/ch. [mm <sup>2</sup> ]                    | 0.012                 | N/A                           | N/A                           | 0.032                         | N/A                            | 0.01                          | 0.034                   | 0.0006                | 0.12                            |

| $\frac{\text{ANEF}}{[mPa \cdot \sqrt{mW/Hz}]}$ | 17                    | 1.4                           | 2.1                           | 2.7                           | 1                              | 0.22                          | 0.51                    | N/A                   | 0.78                            |

<sup>\*</sup> Averaged across the bandwidth from 4.4 to 15.4 MHz.

gain uniformity across a large array. These discrete gains steps can be defined by digitally-programmable ratiometric passive component networks, such as resisattenuators [8], resistive feedback [52], [53], [61], capacitive feedback [18], [20], [62] and current-steering feedback [63]. In addition, the PGA gain steps can be distributed across multiple amplifier stages, with coarse gain steps realized in the LNA and fine gain steps implemented in the succeeding PGA stages [20]. This helps in extending the gain range while keeping an acceptable area efficiency. The downside of a discrete-gain TGC scheme is that the switching transients between gain steps introduce both timedomain discontinuity and digital interference to the received signal, which can lead to noticeable image artifacts [1]. This problem can be mitigated by making the gain steps sufficiently small, typically below 0.5dB/step [8], [62], but at the cost of excessive silicon area due to the increased number of steps to cover the desired gain range.

In contrast, a VGA implements the TGC function by controlling the gain with a continuous-time signal, typically a ramping analog voltage. This avoids the switching transient issue associated with discrete gain steps. On the other hand, the translation from the linear control voltage to a decibelscale gain profile inevitably increases the circuit complexity, especially in the analog domain. One approach is to control the bias point of bipolar or MOS transistors operating in their non-linear region [64]-[66] to realize an (approximately) exponential transducer function. This is, however, only effective within a limited gain range and vulnerable to process, voltage and temperature (PVT) variations, which complicates its adoption in large ultrasound arrays. An alternative approach is to implement continuous interpolation between discreate gain steps. A classic example is the design proposed by Gilbert in 1991 [67], which employs

a resistive ladder attenuator and an N-path current-controlled transconductance stage to smoothly interpolate between the attenuator's outputs. Its demand for multiple transconductance stages makes its power and area efficiency less appealing for modern compact ultrasound devices. A more efficient solution that shares a similar concept is to use a differential pair to smoothly steer the output current of an amplifier between different taps of a discrete-type feedback network. By controlling the voltage applied to the differential pair, a continuous interpolation to the current gain of the amplifier can be realized. This approach was first proposed in [68] and recently got demonstrated in a compact variable-gain ultrasound TIA with compelling gain linearity and noise-power efficiency [51].

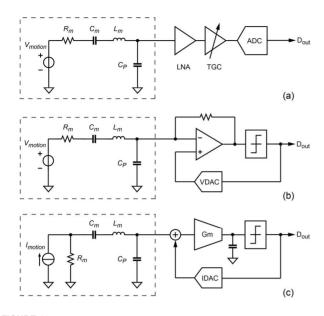

# C. ELEMENT-LEVEL DIGITIZATION

While most state-of-the-art integrated systems perform signal conditioning, pre-beamforming or sub-aperture averaging in the analog domain before digitization, there has been a growing trend to move the analog-to-digital interface further towards the transducer element. From the system perspective, element-level digitization has several important advantages: it grants direct access to the RF data from individual elements, eliminates the constraint of fixed-aperture analog beamforming on the flexibility of imaging algorithms, and enables the integration of more powerful digital processing functions and artificial intelligence within a single ultrasound imaging device [1], [69].

The main obstacle on the road to element-level digitization is the mismatch between the large number of transducer elements and the limited power and area budget for per-element ADCs. Various attempts have been made to tackle this challenge. Kim *et al.* demonstrated a digital beamformer using element-level SAR ADCs

**FIGURE 10.** Element-level digitization topologies: (a) Stand-alone ADCs following an analog front-end [30], [62], [70], [71]; (b) an element-level ADC exploiting the transducer as a resonator of a bandpass  $\Delta\Sigma$  modulator [72]; (c) an element-level ADC exploiting the transducer as a passive integrator of a lowpass  $\Delta\Sigma$  modulator [73].

following conventional analog front-ends [70]. The ADC employs a conventional charge-redistribution capacitive DAC, hence requiring substantial silicon area, preventing it from being pitch-matched integrated with the transducer array. Chen *et al.* addressed this issue by leveraging a nanoscale CMOS process, and managed to integrate a  $\Delta\Sigma$  ADC along with an analog front-end within the area of a single CMUT element [62], albeit at an energy efficiency that is not yet competitive with the analog approach.

It has become increasingly clear that ADC techniques customized for ultrasound signal processing would be the key to enabling element-level digitization. Lee *et al.* proposed a dynamic-bit-sharing technique based on the similarity of beamformed ultrasound signals, which allows adjacent element-level SAR ADCs in a 2×2 subarray to share the most-significant-bits, thus saving power [30]. Another hardware-sharing idea was proposed in [71], where a hybrid SAR/single-slope ADC shares its ramp generator with adjacent channels in a 2×2 subarray for area reduction. Both designs demonstrate promising area and power efficiency.

While all above approaches keep the analog front-end prior to the element-level ADC (Fig. 10a), a more radical solution is to establish the analog-to-digital interface right around the transducer element, turning it into an electromechanical filter of a closed-loop signal modulator. The feasibility of such direct digitization was first demonstrated in [72], where a piezoelectric transducer element is exploited as a resonator in a second-order bandpass  $\Delta\Sigma$  ADC (Fig. 10b). Alternatively, a CMUT element which exhibits a more capacitive impedance can serve as a passive integrator in a continuous-time low-pass  $\Delta\Sigma$  modulator (Fig. 10c), as described in [73]. The omission of front-end

amplifiers grants these direct-digitization solutions an advantage in both power and area-efficiency. Future work will focus on integrating analog or semi-digital TGC functions into the loop, so as to extend the dynamic range of the ADC without compromising its efficiency.

#### V. CONCLUSION

This paper has reviewed circuit solutions for emerging ultrasound imaging devices, such as 3D imaging catheters, portable ultrasound scanners and wearable ultrasound patches. Despite the quite different operating principles of the transducer technologies currently available (bulk piezoelectric transducers, CMUTs and PMUTs), their electrical characteristics are quite similar, and hence similar circuit architectures can be applied. The paper has focused on the front-end building blocks that interface with the transducer elements and tend to limit power consumption and performance: high-voltage pulsers for transmission and low-noise amplifiers and time-gain compensation for reception. The paper has also reviewed advanced techniques, such a multi-level pulsing and element-level digitization.

Currently, most in-probe ASICs act as an interface between the transducer and a conventional imaging system, providing amplification for improved SNR, and channelcount reduction for 3D imaging, by multiplexing or sub-array beamforming. An emerging trend [7], [19], [29], [70] is moving from analog outputs to full in-probe digitization, to provide a robust digital interface to the system. This will enable further data reduction by means of in-probe digital signal processing. Moreover, standardized digital interfaces could ease the integration with other tools supporting the physician. Eventually, this can lead to the disappearance of imaging systems, with all front-end electronics integrated on-chip in the probe, and image processing moved to software [1]. Compared to PCB-based solutions [74], this is an essential step to reduce the size and cost of handheld ultrasound scanners. It is even more crucial for future wearable ultrasound devices [5], which can take ultrasound to home use, for instance for long-term monitoring applications. Such devices will have to operate from a small battery and communicate wirelessly, for instance with a smart phone. This will come with many new challenges, such as the need for drastic data reduction and improvements in power efficiency, that call for further advances in integrated circuit design for ultrasound applications.

#### **REFERENCES**

- J. M. Rothberg *et al.*, "Ultrasound-on-chip platform for medical imaging, analysis, and collective intelligence," *Proc. Nat. Acad. Sci.*, vol. 118, no. 27, 2021, Art. no. e2019339118.

- [2] C. Chen et al., "A front-end ASIC with receive sub-array beamforming integrated with a 32 × 32 PZT matrix transducer for 3-D transesophageal echocardiography," *IEEE J. Solid-State Circuits*, vol. 52, no. 4, pp. 994–1006, Apr. 2017.

- [3] D. Wildes et al., "4-D ICE: A 2-D array transducer with integrated ASIC in a 10-Fr catheter for real-time 3-D intracardiac echocardiography," IEEE Trans. Ultrason., Ferroelectr., Freq. Control, vol. 63, no. 12, pp. 2159–2173, Dec. 2016.

- [4] H. S. Lay et al., "Integrated front end circuitry for microultrasound capsule endoscopy," in Proc. IEEE Int. Ultrason. Symp. (IUS), Kobe, Japan, 2018, pp. 1–4.

[5] C. Wang et al., "Monitoring of the central blood pressure waveform

- [5] C. Wang et al., "Monitoring of the central blood pressure waveform via a conformal ultrasonic device," Nat. Biomed. Eng., vol. 2, no. 9, pp. 687–695, 2018.

- [6] Project ULIMPIA. Towards the Next Generation Smart Body Patches. Accessed: Sep. 20, 2021. [Online]. Available: http://ulimpia-project.eu/

- [7] Y. Igarashi et al., "Single-chip 3072-element-channel transceiver/128-subarray-channel 2-D array IC with analog RX and all-digital TX beamformer for echocardiography," IEEE J. Solid-State Circuits, vol. 54, no. 9, pp. 2555–2567, Sep. 2019.

- [8] N. Sanchez et al., "34.1 An 8960-element ultrasound-on-chip for point-of-care ultrasound," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), vol. 64. San Francisco, CA, USA, 2021, pp. 480–482.

- [9] T. L. Szabo, Diagnostic Ultrasound Imaging: Inside Out. Boston, MA, USA: Academic, 2004.

- [10] R. Wodnicki, B. Haider, K. E. Thomenius, and K. Iniewski, "Electronics for diagnostic ultrasound," in *Medical Imaging: Principles, Detectors, and Electronics*. Hoboken, NJ, USA: Wiley, 2009, pp. 165–220.

- [11] K. Brenner, A. S. Ergun, K. Firouzi, M. F. Rasmussen, Q. Stedman, and B. P. Khuri-Yakub, "Advances in capacitive micromachined ultrasonic transducers," *Micromachines*, vol. 10, no. 2, p. 152, 2019.

- [12] Y. Qiu et al., "Piezoelectric micromachined ultrasound transducer (PMUT) arrays for integrated sensing, actuation and imaging," Sensors, vol. 15, no. 4, pp. 8020–8041, 2015.

- [13] K. S. Van Dyke, "The piezo-electric resonator and its equivalent network," *Proc. Inst. Radio Eng.*, vol. 16, no. 6, pp. 742–764, Jun. 1928.

- [14] R. Krimholtz, D. A. Leedom, and G. L. Matthaei, "New equivalent circuits for elementary piezoelectric transducers," *Electron. Lett.*, vol. 6, no. 13, pp. 398–399, 1970.

- [15] E. Boni et al., "ULA-OP 256: A 256-channel open scanner for development and real-time implementation of new ultrasound methods," *IEEE Trans. Ultrason., Ferroelectr., Freq. Control*, vol. 63, no. 10, pp. 1488–1495, Oct. 2016.

- [16] K. Hara, J. Sakano, M. Mori, S. Tamano, R. Sinomura, and K. Yamazaki, "A new 80V 32x32ch low loss multiplexer LSI for a 3D ultrasound imaging system," in *Proc. 17th Int. Symp. Power Semicond. Devices ICs*, Santa Barbara, CA, USA, 2005, pp. 359–362.

- [17] E. Kang et al., "A reconfigurable ultrasound transceiver ASIC with 24 × 40 elements for 3-D carotid artery imaging," *IEEE J. Solid-State Circuits*, vol. 53, no. 7, pp. 2065–2075, Jul. 2018.

- [18] M. Tan et al., "A front-end ASIC with high-voltage transmit switching and receive digitization for 3-D forward-looking intravascular ultrasound imaging," *IEEE J. Solid-State Circuits*, vol. 53, no. 8, pp. 2284–2297, Aug. 2018.

- [19] B. Savord and R. Solomon, "Fully sampled matrix transducer for real time 3D ultrasonic imaging," in *Proc. IEEE Ultrason. Symp.*, Honolulu, HI, USA, 2003, pp. 945–953.

- [20] C. Chen et al., "A pitch-matched front-end ASIC with integrated sub-array beamforming ADC for miniature 3-D ultrasound probes," *IEEE J. Solid-State Circuits*, vol. 53, no. 11, pp. 3050–3064, Nov. 2018.

- [21] W. Qiu, Y. Yu, F. K. Tsang, and L. Sun, "A multifunctional, reconfigurable pulse generator for high-frequency ultrasound imaging," *IEEE Trans. Ultrason., Ferroelectr., Freq. Control*, vol. 59, no. 7, pp. 1558–1567, Jul. 2012.

- [22] X. Xu, J. T. Yen, and K. K. Shung, "A low-cost bipolar pulse generator for high-frequency ultrasound applications," *IEEE Trans. Ultrason.*, *Ferroelect., Freq. Control*, vol. 54, no. 2, pp. 443–447, Feb. 2007.

[23] J. A. Brown and G. R. Lockwood, "Low-cost, high-performance pulse

- [23] J. A. Brown and G. R. Lockwood, "Low-cost, high-performance pulse generator for ultrasound imaging," *IEEE Trans. Ultrason., Ferroelectr., Freq. Control*, vol. 49, no. 6, pp. 848–851, Jun. 2002.

- [24] G. Gurun et al., "Single-chip CMUT-on-CMOS front-end system for real-time volumetric IVUS and ICE imaging," *IEEE Trans. Ultrason.*, Ferroelectr., Freq. Control, vol. 61, no. 2, pp. 239–250, Feb. 2014.

- [25] I. O. Wygant et al., "Integration of 2D CMUT arrays with front-end electronics for volumetric ultrasound imaging," *IEEE Trans. Ultrason.*, Ferroelectr., Freq. Control, vol. 55, no. 2, pp. 327–342, Feb. 2008.

- [26] M. Sautto et al., "A CMUT transceiver front-end with 100-V TX driver and 1-mW low-noise capacitive feedback RX amplifier in BCD-SOI technology," in Proc. ESSCIRC, Venice Lido, Italy, 2014, pp. 407–410.

- [27] H.-Y. Tang, Y. Lu, S. Fung, D. A. Horsley, and B. E. Boser, "11.8 integrated ultrasonic system for measuring body-fat composition," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, San Francisco, CA, USA, 2015, pp. 1–3.

- [28] L. Xu, J. H. Huijsing, and K. A. Makinwa, "A±4-A high-side current sensor with 0.9% gain error from— 40 C to 85 C using an analog temperature compensation technique," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3368–3376, Dec. 2018.

- [29] A. Banuaji and H.-K. Cha, "A 15-V bidirectional ultrasound interface analog front-end IC for medical imaging using standard CMOS technology," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 61, no. 8, pp. 604–608, Aug. 2014.

- [30] J. Lee et al., "A 36-channel auto-calibrated front-end ASIC for a pMUT-based miniaturized 3-D ultrasound system," IEEE J. Solid-State Circuits, vol. 56, no. 6, pp. 1910–1923, Jun. 2021.

- [31] F. Tranquart, N. Grenier, V. Eder, and L. Pourcelot, "Clinical use of ultrasound tissue harmonic imaging," *Ultrasound Med. Biol.*, vol. 25, no. 6, pp. 889–894, 1999.

- [32] C.-C. Shen, Y.-H. Chou, and P.-C. Li, "Pulse inversion techniques in ultrasonic nonlinear imaging," *J. Med. Ultrasound*, vol. 13, no. 1, pp. 3–17, 2005.

- [33] R. Y. Chiao and X. Hao, "Coded excitation for diagnostic ultrasound: A system developer's perspective," *IEEE Trans. Ultrason.*, Ferroelectr., Freq. Control, vol. 52, no. 2, pp. 160–170, Feb. 2005.

- [34] L. J. Svensson and J. G. Koller, "Driving a capacitive load without dissipating fCV/sup 2," in *Proc. IEEE Symp. Low Power Electron.*, San Diego, CA, USA, 1994, pp. 100–101.

- [35] O. Oralkan et al., "Experimental characterization of collapse-mode CMUT operation," *IEEE Trans. Ultrason., Ferroelectr., Freq. Control*, vol. 53, no. 8, pp. 1513–1523, Aug. 2006.

- [36] K. K. Park, O. Oralkan, and B. T. Khuri-Yakub, "A comparison between conventional and collapse-mode capacitive micromachined ultrasonic transducers in 10-MHz 1-D arrays," *IEEE Trans. Ultrason.*, Ferroelectr., Freq. Control, vol. 60, no. 6, pp. 1245–1255, Jun. 2013.

- [37] M. Tan et al., "A 64-channel transmit beamformer with±30-V bipolar high-voltage pulsers for catheter-based ultrasound probes," *IEEE J. Solid-State Circuits*, vol. 55, no. 7, pp. 1796–1806, Jul. 2020.

- [38] K. Chen, H.-S. Lee, A. P. Chandrakasan, and C. G. Sodini, "Ultrasonic imaging transceiver design for CMUT: A three-level 30-Vpp pulseshaping pulser with improved efficiency and a noise-optimized receiver," *IEEE J. Solid-State Circuits*, vol. 48, no. 11, pp. 2734–2745, Nov. 2013.

- [39] G. Jung, C. Tekes, A. Pirouz, F. L. Degertekin, and M. Ghovanloo, "Supply-doubled pulse-shaping high voltage pulser for CMUT arrays," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 65, no. 3, pp. 306–310, Mar. 2018.

- [40] K.-J. Choi, H. G. Yeo, H. Choi, and D.-W. Jee, "A 28.7V modular supply multiplying pulser with 75.4% power reduction relative to CV<sup>2</sup>f," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 68, no. 3, pp. 858–862, Mar. 2021.

- [41] J. Choi et al., "34.4 an energy-replenishing ultrasound pulser with 0.25 CV<sup>2</sup>f dynamic power consumption," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, vol. 64. San Francisco, CA, USA, 2021, pp. 486–488.

- [42] J. K. Fiorenza, T. Sepke, P. Holloway, C. G. Sodini, and H.-S. Lee, "Comparator-based switched-capacitor circuits for scaled CMOS technologies," *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2658–2668, Dec. 2006.

- [43] I. Zamora, E. Ledesma, A. Uranga, and N. Barniol, "Miniaturized 0.13-\(\mu\)m CMOS front-end analog for AlN PMUT arrays," Sensors, vol. 20, no. 4, p. 1205, 2020.

- [44] J. H. Eriksrød and T. Ytterdal, "A 65nm CMOS front-end LNA for medical ultrasound imaging with feedback employing noise and distortion cancellation," in *Proc. Eur. Conf. Circuit Theory Design (ECCTD)*, Dresden, Germany, 2013, pp. 1–4.

- [45] I. O. Wygant et al., "An integrated circuit with transmit beamforming flip-chip bonded to a 2-D CMUT array for 3-D ultrasound imaging," *IEEE Trans. Ultrason., Ferroelectr., Freq. Control*, vol. 56, no. 10, pp. 2145–2156, Oct. 2009.

- [46] R. J. Przybyla, H.-Y. Tang, A. Guedes, S. E. Shelton, D. A. Horsley, and B. E. Boser, "3D ultrasonic rangefinder on a chip," *IEEE J. Solid-State Circuits*, vol. 50, no. 1, pp. 320–334, Jan. 2015.

- [47] C. Chen, Z. Chen, Z.-Y. Chang, and M. A. P. Pertijs, "A compact 0.135-mW/channel LNA array for piezoelectric ultrasound transducers," in *Proc. Eur. Solid-State Circuits Conf. (ESSCIRC)*, Graz, Austria, Sep. 2015, pp. 404–407.

- [48] G. Peyton, B. Farzaneh, H. Soleimani, M. G. Boutelle, and E. M. Drakakis, "Quadrature synthetic aperture beamforming front-end for miniaturized ultrasound imaging," *IEEE Trans. Biomed. Circuits Syst.*, vol. 12, no. 4, pp. 871–883, Aug. 2018.

- [49] İ. Cicek, A. Bozkurt, and M. Karaman, "Design of a front-end integrated circuit for 3D acoustic imaging using 2D CMUT arrays," *IEEE Trans. Ultrason., Ferroelectr., Freq. Control*, vol. 52, no. 12, pp. 2235–2241, Dec. 2005.

- [50] K. Chen, H.-S. Lee, and C. G. Sodini, "A column-row-parallel ASIC architecture for 3-D portable medical ultrasonic imaging," *IEEE J. Solid-State Circuits*, vol. 51, no. 3, pp. 738–751, Mar. 2016.

- [51] E. Kang et al., "A variable-gain low-noise transimpedance amplifier for miniature ultrasound probes," *IEEE J. Solid-State Circuits*, vol. 55, no. 12, pp. 3157–3168, Dec. 2020.

- [52] Z. Yu et al., "Front-end receiver electronics for a matrix transducer for 3-D transesophageal echocardiography," *IEEE Trans. Ultrason.*, Ferroelectr., Freq. Control, vol. 59, no. 7, pp. 1500–1512, Jul. 2012.

- [53] C. Chen et al., "A prototype PZT matrix transducer with low-power integrated receive ASIC for 3-D transesophageal echocardiography," *IEEE Trans. Ultrason., Ferroelectr., Freq. Control*, vol. 63, no. 1, pp. 47–59, Jan. 2016.

- [54] V. Daeichin et al., "A broadband polyvinylidene difluoride-based hydrophone with integrated readout circuit for intravascular photoacoustic imaging," *Ultrasound Med. Biol.*, vol. 42, no. 5, pp. 1239–1243, 2016.

- [55] H. J. Weller, D. Setiadi, and T. D. Binnie, "Low-noise charge sensitive readout for pyroelectric sensor arrays using PVDF thin film," Sens. Actuat. A, Phys., vol. 85, nos. 1–3, pp. 267–274, 2000.

- [56] I. Wygant, "A comparison of CMUTs and piezoelectric transducer elements for 2D medical imaging based on conventional simulation models," in *Proc. IEEE Int. Ultrason. Symp.*, Orlando, FL, USA, 2011, pp. 100–103.

- [57] C. Chen, "Front-end ASICs for 3-D ultrasound: From beamforming to digitization," Ph.D. dissertation, Dept. Elect. Eng., Delft Univ. Technol., Delft, The Netherlands, 2018.

- [58] G. Berkol, P. G. M. Baltus, P. J. A. Harpe, and E. Cantatore, "A 2.67 μJ per measurement FMCW ultrasound rangefinder system for the exploration of enclosed environments," *IEEE Solid-State Circuits Lett.*, vol. 3, pp. 326–329, 2020.

- [59] D. Reda, E. Hegazi, K. N. Salama, and H. F. Ragai, "Design of low noise transimpedance amplifier for intravascular ultrasound," in *Proc. ISCAS*, Beijing, China, 2009, pp. 57–60.

- [60] M. Sautto, A. S. Savoia, F. Quaglia, G. Caliano, and A. Mazzanti, "A comparative analysis of CMUT receiving architectures for the design optimization of integrated transceiver front ends," *IEEE Trans. Ultrason., Ferroelectr. Freq. Control*, vol. 64, no. 5, pp. 826–838, May 2017.

- [61] Y. Wang, M. Koen, and D. Ma, "Low-noise CMOS TGC amplifier with adaptive gain control for ultrasound imaging receivers," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 58, no. 1, pp. 26–30, Jan. 2011.

- [62] M.-C. Chen et al., "A pixel pitch-matched ultrasound receiver for 3-D photoacoustic imaging with integrated delta-sigma beamformer in 28-nm UTBB FD-SOI," IEEE J. Solid-State Circuits, vol. 52, no. 11, pp. 2843–2856, Nov. 2017.

- [63] H. Elwan, A. Tekin, and K. Pedrotti, "A differential-ramp based 65 dB-linear VGA technique in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 44, no. 9, pp. 2503–2514, Sep. 2009.

- [64] Q.-H. Duong, Q. Le, C.-W. Kim, and S.-G. Lee, "A 95-dB linear low-power variable gain amplifier," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 53, no. 8, pp. 1648–1657, Aug. 2006.

- [65] H.-H. Nguyen, H.-N. Nguyen, J.-S. Lee, and S.-G. Lee, "A binary-weighted switching and reconfiguration-based programmable gain amplifier," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 56, no. 9, pp. 699–703, Sep. 2009.

- [66] I. Choi, H. Seo, and B. Kim, "Accurate dB-linear variable gain amplifier with gain error compensation," *IEEE J. Solid-State Circuits*, vol. 48, no. 2, pp. 456–464, Feb. 2013.

- [67] B. Gilbert, "A low-noise wideband variable-gain amplifier using an interpolated ladder attenuator," in *ISSCC Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 1991, pp. 280–281.

- [68] B. R. Veillette, "Variable gain current amplifier with a feedback loop including a differential pair," Google Patents US6 798 291 B2, 2004.

- [69] B. Lam, M. Price, and A. P. Chandrakasan, "An ASIC for energy-scalable, low-power digital ultrasound beamforming," in *Proc. IEEE Int. Workshop Signal Process. Syst.*, Dallas, TX, USA, 2016, pp. 57–62.

- [70] Y.-J. Kim et al., "A single-chip 64-channel ultrasound RX-beamformer including analog front-end and an LUT for non-uniform ADC-sampleclock generation," *IEEE Trans. Biomed. Circuits Syst.*, vol. 11, no. 1, pp. 87–97, Feb. 2017.

- [71] J. Li et al., "A 1.54 mW/element 150μm-pitch-matched receiver ASIC with element-level SAR/shared-single-slope hybrid ADCs for miniature 3D ultrasound probes," in *Proc. Symp. VLSI Circuits*, Kyoto, Japan, 2019, pp. C220–C221.

- [72] M. D'Urbino et al., "An element-matched electromechanical ΔΣ ADC for ultrasound imaging," *IEEE J. Solid-State Circuits*, vol. 53, no. 10, pp. 2795–2805, Oct. 2018.

- [73] C. Chen, K. Chen, L. K. Chiu, Y.-J. Kook, and K. G. Fife, "Apparatuses including a capacitive micromachined ultrasonic transducer directly coupled to an analog-to-digital converter," U.S. Patent 16 443 931, 2019.

- [74] P. A. Hager and L. Benini, "LightProbe: A digital ultrasound probe for software-defined ultrafast imaging," *IEEE Trans. Ultrason.*, Ferroelectr., Freq. Control, vol. 66, no. 4, pp. 747–760, Apr. 2019.

**CHAO CHEN** (Member, IEEE) received the B.Sc. degree in micro-electronics from Tsinghua University, Beijing, China, in 2010, and the M.Sc. (*cum laude*) and Ph.D. degrees in micro-electronics from the Delft University of Technology, Delft, The Netherlands, in 2012 and 2018, respectively.

Since 2017, he has been a Senior Analog IC Designer with Butterfly Network, Inc., Guilford, CT, USA, where he is currently a Consultant focusing on the development of next-generation

integrated circuits for portable ultrasound. Since 2021, he has been also with the Delft University of Technology, where he holds a position as a Postdoctoral Researcher. He has authored and coauthored more than 30 publications and holds three U.S. patents. His current research interests include integrated circuits for medical imaging, low-power sensor interfaces, and high-resolution data converters.

Dr. Chen was a recipient of the 2017 IEEE International Ultrasonics Symposium Best Student Paper Award, the 2013 International Solid-State Circuits Conference STGA Award, and the 2011 Nuffic Huygens Scholarship. He was also a co-recipient of the 2017 Asian Solid-State Circuits Conference Best Student Paper Award and the 2020 ISSCC Technology Innovation Award. For his Ph.D. research on front-end application-specified integrated circuit design for 3-D medical ultrasound, he received the 2019 Else Kooi Award. He has served as a Member of the technical program committee in several academic conferences, including the 2018 IEEE Asia–Pacific Conference on Circuits and Systems and the 2021 International Conference on ASIC.

MICHIEL A. P. PERTIJS (Senior Member, IEEE) received the M.Sc. and Ph.D. degrees (*cum laude*) in electrical engineering from the Delft University of Technology, Delft, The Netherlands, in 2000 and 2005, respectively.

From 2005 to 2008, he was with National Semiconductor, Delft, where he designed precision operational amplifiers and instrumentation amplifiers. From 2008 to 2009, he was a Senior Researcher with imec/Holst Centre, Eindhoven, The Netherlands. In 2009, he joined

the Electronic Instrumentation Laboratory, Delft University of Technology, where he is currently an Associate Professor. He heads a research group focusing on integrated circuits for medical ultrasound and energy-efficient smart sensors. He has authored or coauthored two books, four book chapters, 15 patents, and over 140 technical papers. He received the International Solid-State Circuits Conference (ISSCC) 2005 Jack Kilby Award for Outstanding Student Paper and the IEEE JOURNAL OF SOLID-STATE CIRCUITS 2005 Best Paper Award. For his Ph.D. research on high-accuracy CMOS smart temperature sensors, he received the 2006 Simon Stevin Gezel Award from the Dutch Technology Foundation STW. In 2014, he was elected Best Teacher of the EE program at Delft University of Technology. He served as an Associate Editor for the IEEE OPEN JOURNAL OF THE SOLID-STATE CIRCUITS SOCIETY and the IEEE JOURNAL OF SOLID-STATE CIRCUITS. He is a member of the technical program committee the European Solid-State Circuits Conference, and also served on the program committees of ISSCC and the IEEE Sensors Conference.