# Wideband Hybrid-Class Power Amplifier for Base Station Applications Using LDMOS with Envelope Tracking System

By T. Zhang

TU-Delft Mentors: Dr. ing. L.C.N. de Vreede S.M. Alavi

> NXP Mentors: Edmund Neo John Gajadharsing

Delft University of Technology, July 2009

A thesis submitted to the Electrical Engineering, Mathematics and Computer Science Department of Delft University of Technology in partial fulfillment of the requirements for the degree of Master of Science.

## Abstract

Conventional RF power amplifiers are normally designed for peak efficiency at maximum output power. However, for WCDMA application, the power amplifier often operates at 6-8 dB power back-off. Consequently, when the power is backed-off from its peak point, the efficiency of conventional power amplifier drops sharply.

The envelope elimination and restoration (EER) and envelope tracking (ET) systems are two of the most promising techniques that can provide high efficiency at power back-off point. In this project, a RF power amplifier optimized for average efficiency according to the PDF of WCDMA signal has been designed using NXP generation 7 LDMOS.

In addition, to meet the increasing demand for wireless communication terminals to handle wideband operation, a 1GHz bandwidth power amplifier optimized for efficiency at power back-off has been designed and fabricated. The measurement results are proved to have a good agreement with simulation results.

## Acknowledgements

First, I would like to express my sincere gratitude to my TU-Delft mentor Dr. Leo de Vreede for providing me such a good opportunity to conduct this interesting project and for his guidance and encouragement during the project.

Second, I would also like to thank S.M. Alavi for his help in the research on the principles of class-J operation. Special thanks are given to Mr. Marco Pelk and Mr. Atef Akhnoukh for the help of drawing layout, to Mr. Jawad Qureshi for his help in measurement.

Next, I would like to thank NXP semiconductors for providing me a traineeship opportunity and my NXP mentors: Mr. Fred van Rijs, Mr. Mark v.d, Mr. Heijden, Mr. Mustafa Acar and Mr. W.C.Edmund Neo for their valuable discussions.

Finally, my family and friends have always given me strong support and encouragement in my studies. Without them, this work would never have been accomplished.

# Content

| Introduction1                                                              |

|----------------------------------------------------------------------------|

| Chapter 1 Principle of class A/AB/B/C/E/F2                                 |

| Section1: Reduced conduction angle power amplifier2                        |

| Class-A                                                                    |

| Class-B4                                                                   |

| Class-AB5                                                                  |

| Class-C5                                                                   |

| Section 2: Switching mode power amplifier6                                 |

| Class-F7                                                                   |

| Class-E8                                                                   |

| Section 3: Harmonic tuned waveform10                                       |

| Section 4: Efficiency in power back-off operation10                        |

| Section 5: EET and ET system12                                             |

| EER system12                                                               |

| ET system13                                                                |

| Section 6 Conclusions13                                                    |

| Chapter 2 Harmonic Tuned Class-J Power Amplifier14                         |

| Section 1: Improvement of the efficiency of power amplifier14              |

| Section 2: Short all the harmonics: Class-AB/B operation15                 |

| Section 3: How the harmonics tune the fundamental frequency waveform16     |

| Section 4: Solutions for class-J operation17                               |

| Section 5: Sub-optimum class-J operation24                                 |

| Section 6 Conclusions29                                                    |

| Chapter 3 Design of a "Narrowband" Hybrid Class Power Amplifier for EER or |

| ET system operation                                                        |

| Section 1: Device properties31                                             |

| Section 2: Optimizing the load condition for single supply voltage         |

| Section 3 Optimizing load condition for efficiency at power back-off46     |

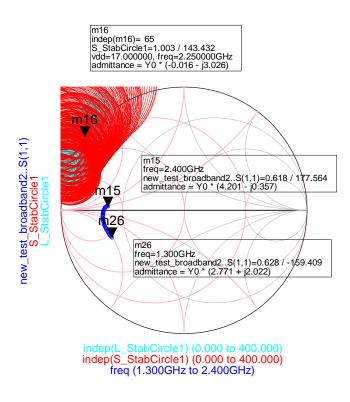

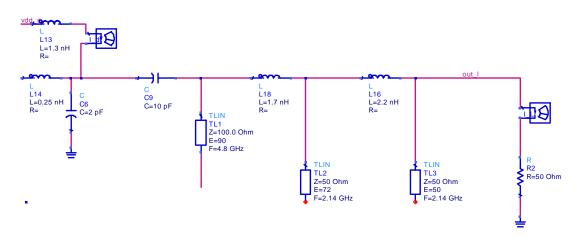

| Section 4. The stability issue63                                           |

| Section 5. Realization67                                                   |

| Section 6: Conclusions74                                                   |

| Chapter 4 Wideband Hybrid-Class Power Amplifier for EER and ET Systems     |

| Section 1. Wideband power amplifier design                                 |

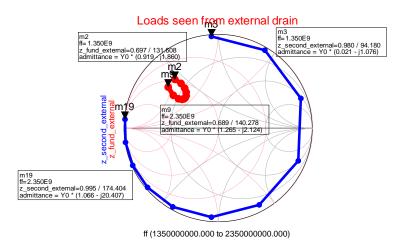

| Section 2. Optimum load conditions for wideband power amplifier            |

| Section 3. Matching network for realization                                |

| Section 4. Design bandwidth for wideband power amplifier                   |

| Section 4. Design bandwidth for wideband power amplifier                   |

| Section 6 A 1 GHz bandwidth hybrid power amplifier optimized for supply    |

| voltage modulation                                                         |

| Section 7 Conclusions                                                      |

|                                                                            |

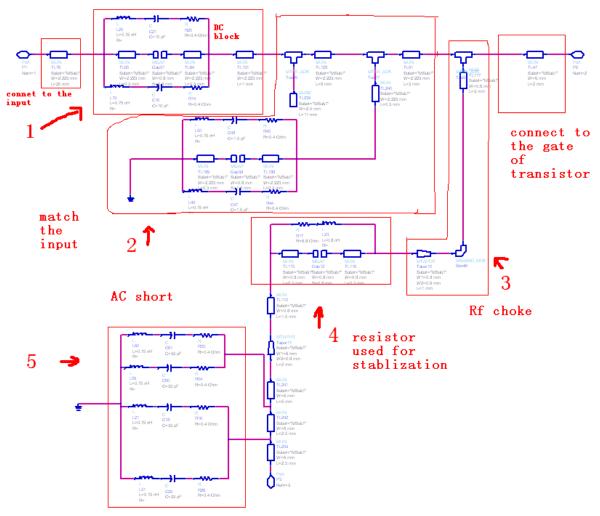

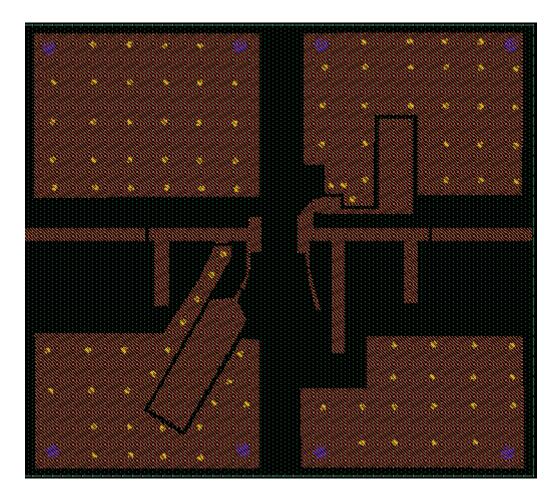

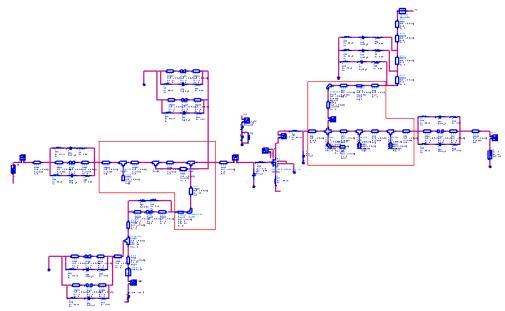

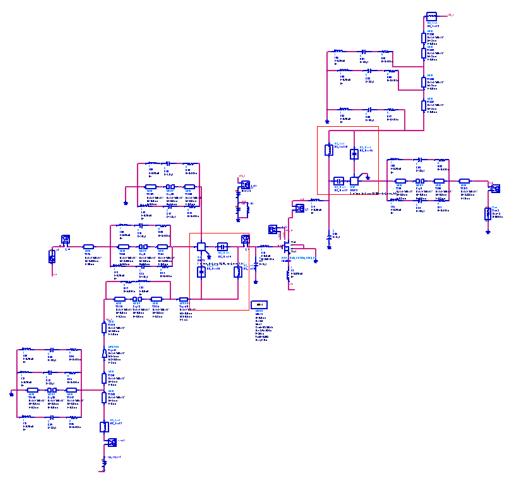

| Chapter 5 Layout and Testing                                         | 103  |

|----------------------------------------------------------------------|------|

| Section 1: Layout of 1 GHz bandwidth hybrid class power amplifier    | 103  |

| Section 2: Momentum simulation results                               | 103  |

| Section 3: Measurement results                                       | 107  |

| Section 4 Conclusions                                                | 112  |

| Chapter 6 Conclusions                                                | 113  |

| Appendix 1 PDF of WCDMA signal for 12 W power amplifier              | 114  |

| Appendix 2 A 750 MHz Bandwidth Class-J Power Amplifier for Single Su | pply |

| Voltage                                                              | 115  |

| Appendix 3 A 600MHz Bandwidth Hybrid-class Power Amplifier Optim     | ized |

| for Supply Voltage Modulation                                        | 129  |

| Appendix 4 Hybrid-Class Power Amplifier Realized with 2W LDMOS       | 135  |

| Bibliography                                                         | 138  |

## Introduction

The function of a power amplifier is to take a RF input signal and transfer it to an output signal with significantly larger amplitude. This is only possible at the cost of DC power, which is converted to the RF / microwave domain. There are a great variety of different PA operating classes in use, e.g. class-A, class-B, class-C and etc., as well as, high complexity amplifier architectures that can improve the efficiency-linearity trade-off of the power amplifier (e.g. envelope elimination, envelope tracking, Doherty, out-phasing etc.).

Recently, due to the development of high data rate wireless systems, the power amplifier is more and more required to have different operation modes and operating frequencies (e.g. WCDMA, WiMAX etc.). So, wideband operation has now become an important design parameter as well. In this thesis, we aim for an octave bandwidth power amplifier, optimized for supply voltage modulation. In view of this the outline of the thesis is as follows.

In chapter 1, we discuss the principles of class A/AB/B/C/E and F operation and introduce some higher complexity amplifier concepts currently in use to improve the efficiency performance in power back-off operation.

In chapter 2 we will introduce the principles of class-J operation. Class-J is a relative of new class of device operation, which is gaining interest due to its better wideband capabilities.

Since the focus of this project is to design a power amplifier suitable for an envelope tracking system, using NXP's latest generation 7 of LDMOS technology, in chapter 3 we invest, which class of device operation is the most suitable for application. With this information an initial power amplifier design has been defined.

In chapter 4, wideband amplifier design is introduced; three different versions with slightly different bandwidths are evaluated for their performance.

In chapter 5, the final design, layout and testing results are presented of the octave wideband power amplifier.

## Chapter 1 Principle of class A/AB/B/C/E/F

In this chapter, we well discuss the principles of some basic operation classes of power amplifiers, as well as the concept of amplifier operation in power back-off. The principles of envelope elimination and restoration and envelope tracking system will also be introduced in this chapter.

### **Operation classes for power amplifiers:**

For different ways of device operation, people classify the power amplifiers to different classes. Class A/AB/B/C can be classified to one category. When the power amplifier operates at class A/B/C/AB, the transistor operates like a current source. Class E/F/J can be classified to another category. In these classes the transistor operates like a switch.

### Section1: Reduced conduction angle power amplifier

Let's first talk about the class A/B/C/AB power amplifier. The difference of these classes is the conduction angle (figure 1.1).

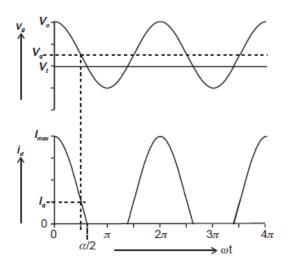

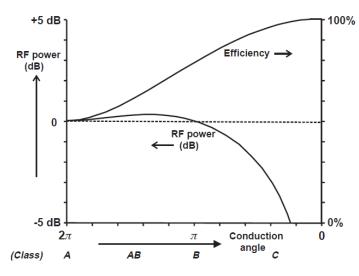

Figure 1.1 Reduced conduction angle when operating as a power amplifier  $\alpha$  represents the conduction angle of power amplifier [1]

| Class | Gate bias point | Current | Conduction angle |

|-------|-----------------|---------|------------------|

| А     | 0.5             | 0.5     | 2pi              |

| AB    | 0-0.5           | 0-0.5   | Pi-2pi           |

| В     | 0               | 0       | pi               |

| С     | <0              | 0       | 0-pi             |

Table 1.1 Bias point and conduction angle of different classes (the signal voltage and current swing are normalized to 1) [1]

### Class-A:

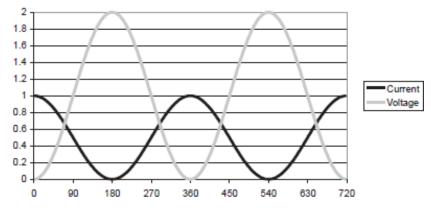

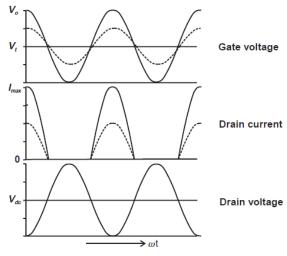

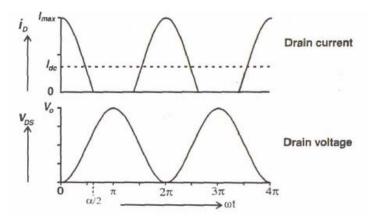

From these classes, class-A has the highest linearity and the transistor is equivalent to a current source. The drain current and voltage waveforms of class-A operation are given in figure 1.2:

Figure 1.2 (b) Drain voltage and Drain current in class-A operation [1]

In order to enable the power amplifier operate in its linear region, the amplifier's gate and drain bias voltage should be chosen properly. The swing of the drain current for class-A operation should be between zero and Imax (with Imax being the saturation current of the transistor.). The swing of the drain voltage should be between zero and breakdown voltage of the device. The conduction angle is  $2\pi$  for class-A operation means the device is on all the times. It also means that the device loses power all the times.

Let's calculate the maximum efficiency and output power of class-A operation:

The drain current for an amplifier with reduced conduction angle:

$$i_{d}(\theta) = I_{q} + I_{pk} \Box \cos \theta, -\alpha / 2 < \theta < \alpha / 2;$$

= 0, -\pi < \theta < -\alpha / 2; -\alpha / 2 < \theta < \pi [1] (1)

Where id is the drain current, Iq is the quiescent current, Ipk is the amplitude of drain current, Imax is the peak value of drain current,  $\alpha$  is the conduction angle.

$$\cos(\alpha/2) = -\frac{I_q}{I_{pk}} \quad \text{and} \quad I_{pk} = \operatorname{Im}_{ax} - I_q \tag{2}$$

So,

$$i_d(\theta) = \frac{I_{\max}}{1 - \cos(\alpha/2)} \Box(\cos\theta - \cos(\alpha/2))$$

(3)

The DC component is as follows:

$$I_{dc} = \frac{1}{2\pi} \int_{-\alpha/2}^{\alpha/2} \frac{\lim \alpha}{1 - \cos(\alpha/2)} \left[ (\cos\theta - \cos(\alpha/2)) \right] d\theta$$

$$= \frac{\lim \alpha}{2\pi} \frac{2 [\sin(\alpha/2) - \alpha [\cos(\alpha/2)]}{1 - \cos(\alpha/2)}$$

(4)

The magnitude of nth harmonic is:

$$I_n = \frac{1}{\pi} \prod_{-\alpha/2}^{\alpha/2} \frac{\mathrm{Im}\,_{ax}}{1 - \cos(\alpha/2)} \prod (\cos\theta - \cos(\alpha/2)) \log(n\theta) \mathbb{I} d\theta \qquad (5)$$

The fundamental harmonic component of drain current is:

$$I_1 = \frac{\operatorname{Im} \alpha x}{2\pi} \frac{\alpha - \sin \alpha}{1 - \cos(\alpha/2)}$$

(6)

For class-A operation, the conduction angle is  $2\pi$ . So, the dc component of drain current is:

$$I_{dc}(class A) = \frac{I_{m ax}}{2}$$

(7)

The fundamental harmonic component of drain current:

$$I_1(class A) = \frac{\lim ax}{2}$$

(8)

The DC and fundamental harmonic component of drain voltage:

$$V_{dc}(class A) = \frac{V_{\text{max}}}{2}$$

(9)

$$V_1(class A) = \frac{V_{\text{max}}}{2}$$

(10)

The DC dissipation power of class-A operation power amplitude:

$$P_{dc} = V_{dc} \square I_{dc} = \frac{V_{\max} \square_{\max} a_x}{4}$$

(11)

The output power for class-A operation:

$$P_{out} = \frac{1}{2} \nabla_1 \Box_1 = \frac{V_{\max} \Box_{\max}}{8}$$

(12)

The maximum drain efficiency of class-A operation:

$$\eta = \frac{P_{out}}{P_{dc}} = \frac{1}{2} = 50\%$$

[1] (13)

So, for class-A operation, the maximum drain efficiency 50%.

### **Class B:**

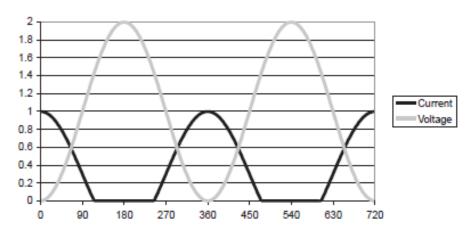

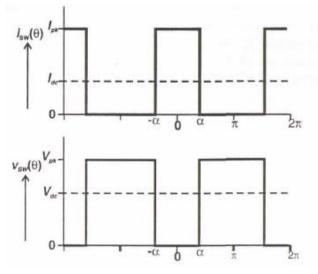

The class B amplifier has half-sine drain current waveform and the drain voltage waveform is full-sine wave. Obviously, the overlap of the drain current and voltage is less, which means the dc power dissipation is less and therefore its efficiency is higher. However, the linearity of class-B operation is not as good as class-A operation. The voltage and current waveform of class B amplifier is in figure 1.3:

Figure 1.3 Drain voltage and Drain current of class-B operation [1]

The efficiency of class-B operation:

From equations (4) to (6), we can obtain the dc and fundamental harmonic components of drain current. The conduction angle of class-B operation is  $\pi$ .

$$I_{dc}(class B) = \frac{I_{m ax}}{\pi}$$

[1] (14)

$$I_1(class B) = \frac{I_{max}}{2}$$

(15)

The dc and fundamental harmonic components of drain voltage:

$$V_{dc}(class B) = \frac{V_{\text{max}}}{2}$$

(16)

$$V_1(class B) = \frac{V_{\text{max}}}{2}$$

(17)

The dc and output power:

$$P_{dc} = V_{dc} \square I_{dc} \tag{18}$$

$$P_{out} = \frac{1}{2} \Box I \Box V_1 \tag{19}$$

The maximum drain efficiency for class-B operation:

$$\eta = \frac{P_{out}}{P_{dc}} = \frac{\pi}{4} \approx 78.5\%$$

[1] (20)

The theoretical maximum class-B operation is 78.5%.

### Class AB:

Class AB is a compromise between class A and B. The conduction angle for class-AB operation is between  $\pi$  and  $2\pi$ . The larger the conduction angle is typically the better the linearity is, but the lower the efficiency is, and vice versa. So, the theoretical maximum drain efficiency is between 50% and 78.5%.

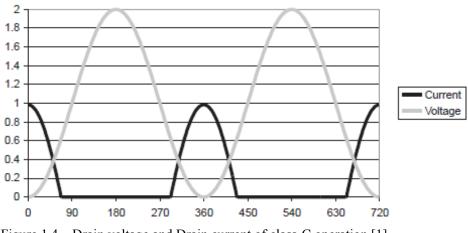

### Class C:

In Class C operation the conduction angle is between 0 and  $\pi$ . Using equation (4) to (6), we can calculate the drain efficiency of class-C operation. It isn't a constant and depends on the conduction angle. If the conduction angle is 0, theoretically we can

obtain 100% drain efficiency. However, this also means that there is no power deliver to the load. So, 0 conduction angle is meaningless. In this class of operation we need to make a trade –off between efficiency and output power. The lower the conduction angle is, the higher the efficiency is and less output power is. The waveforms of class-C operation:

Figure 1.4 Drain voltage and Drain current of class-C operation [1]

The drain efficiency and output power versus conduction angle (figure 1.5):

Figure 1.5 The drain efficiency and output power versus conduction angle [1]

### Section 2: Switching mode power amplifier

Class-E and class-F power amplifiers are switching mode power amplifier. The transistor acts like a switch. The theoretical maximum drain efficiency for both classes can be as high as 100%. However, due to the non-ideal conditions of device (limited switching time, parasitics and etc), 100% drain efficiency is difficult to reach [2]. Comparing with class-C operation, class-E and class-F power operation don't need to make a compromise between efficiency and output power.

### **Class F:**

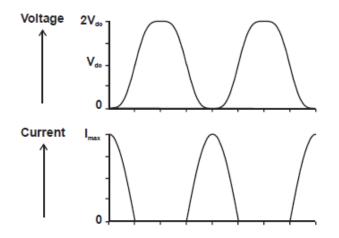

For an ideal class-F power amplifier, the voltage waveform should be an ideal square waveform. When the transistor on, the drain voltage is zero. In other words, the drain voltage is shaped to minimize the overlap of drain voltage and current. However, normally the ideal square waveform condition is hard to meet and drain voltage waveform is a sub-optimum square waveform. The waveforms of sub-optimum class-F power amplifier are:

Figure 1.6 Drain current and voltage of sub-optimum class-F power amplifier

The square waveform only contains odd-order harmonics. There are three factors which influent the shape of waveform.

- 1. The phase relations between fundamental and higher order harmonics. For ideal square waveform, the peak of fundamental and the valleys of higher order harmonics should be synchronized.

- 2. The amplitude relations of fundamental and higher order harmonics.

Figure 1.7 Third order harmonic shaped waveform (different amplitude of third harmonic) [1]

The fundamental harmonic is:

$$\cos\theta$$

[1] (21)

The third harmonic is:

$$-V_3\cos(3\theta) \tag{22}$$

The superimposition of these two harmonics:

$$V = \cos\theta - V_3 \cos(3\theta) \tag{23}$$

The amplitude ratio of fundamental and third harmonic is very important too. As shown in figure 1.7, when the ratio is 1/6, the superimposited waveform is very flat. When the ratio is less than 1/9, the superimposition is still looks like a sinusoid. 3. The number of harmonics:

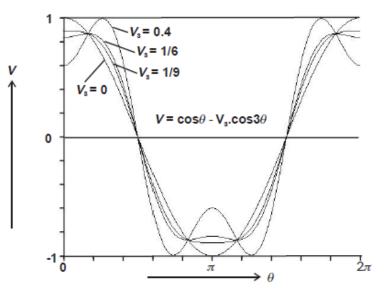

Figure 1.8 Square waveform with different number of odd-order harmonics. m represents the number of odd-order harmonics [1]

We can see from figure 1.8 that when the number of odd-order harmonics increases, the waveform becomes more and more like an ideal square waveform.

So, with finite number of harmonics or other non-ideal conditions, the efficiency of class-F power amplifier drops from theoretical value of 100%

### **Class-E:**

Class-E power amplifier is also a kind of switching mode amplifier. For an ideal class-E operation, three requirements for drain voltage and current should be meet [2]:

- (1) The rise of the voltage cross the transistor at turn-off should be delayed until after the transistor is off.

- (2) The drain voltage should be brought back to zero at the time of transistor turn-on.

- (3) The slope of the drain voltage should be zero at the time of turn-on.

These conditions can only be met by controlling an infinite number of harmonics.

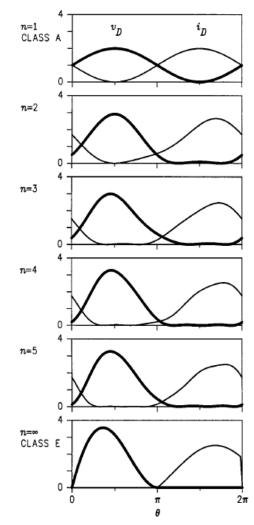

When the number of harmonics is limit, the efficiency drops from theoretical value of 100% and we call that kind of operation sub-optimum class-E. The drain voltage waveform varies with different number of harmonics are shown in figure 1.9.

Figure 1.9 The drain voltage waveform varies with different number of harmonics. n represents the number of harmonics [3]

When the harmonic number is 2, the drain voltage only contains fundamental and second harmonic components. We call it class-J operation. The detail discussion on class-J operation is in next chapter. So, class-J is also a kind of sub-class E operation. When the number of harmonic increases to infinite, there is no overlap of drain voltage and current (figure 1.9) and 100% efficiency can be achieved. However, in practical situations, it's a very hard task due to the existence of on resistor or other parasitics of the transistors. Basically, the class-E power amplifier we call is in sub-class E operation.

The equations to calculate the optimum fundamental load for class-E operation:

$$R = \frac{0.58 \times V_{DD}^2}{P_{out}}$$

(24)

The table of optimum harmonics load for ideal class-E operation [3]:

| k  | <i>v</i> <sub>k</sub> | $ I_k $ | Z <sub>k</sub> for R=1 | $Z_k$ for $R_1 = 1$ |

|----|-----------------------|---------|------------------------|---------------------|

| 0  | 1.000                 | 0.5762  |                        |                     |

| 1  | 1.639                 | 0.8691  | 1.5260 + j1.1064       | 1 + j0.725          |

| 2  | 0.8477                | 0.3120  | -12.7233               | -11.7846            |

| 3  | 0.2222                | 0.1224  | -j1.8155               | -j1.1897            |

| 4  | 0.1433                | 0.1056  | -j1.3616               | -j0.8923            |

| 5  | 0.08001               | 0.07344 | -/1.0893               | -j0.7138            |

| 6  | 0.05907               | 0.06536 | - 10.9038              | - 10.5923           |

| 7  | 0.04082               | 0.05246 | - 10.7781              | -10.5099            |

| 8  | 0.03236               | 0.04774 | - j0.6778              | -j0.4448            |

| 9  | 0.02470               | 0.04081 | - 10.6052              | -i0.3966            |

| 10 | 0.02045               | 0.03773 | -j0.5420               | - j0.3552           |

Figure 1.10 Table of optimum load for class-E operation harmnics

### Section 3: Harmonic tuned waveform

Actually, as we have shown above, we can use different harmonics to tune the full-sine drain voltage waveform. In this way, we are able to shape the drain voltage waveform and get desired operation classes. We summarize the relation of harmonics and operation classes as follows [3]:

Class-F: Drain voltage is a square waveform which contains only odd order harmonics. Drain current is a half-sine wave which contains only even order harmonics.

Class-C: All harmonics reactance are shorted. The drain current is shaped to a narrow pulse.

Class-E: The reactance for all harmonics are negative and comparable in magnitude to the fundamental frequency load resistance.

### Section 4: Efficiency in power back-off operation

In WCDMA system, the power amplifier typically operates most of the time at 6 to 11 dB power back-off of the peak power point (high peak to average ratio for output power). All the efficiency considerations we have discussed above relate to the efficiency at peak output power. So it is also important to define the efficiency if we decrease the input power so that the power amplifier operates at its power back-off point.

For this purpose we take class-B as an example. The optimal load for class-B power amplifier to reach the peak power and still maintain the linearity for power amplifier is:

$$R_{opt} = \frac{2 \times V_{dc}}{\mathrm{Im} \ ax}$$

[1] (25)

Imax is the maximum drain current and Vdc is the drain supply voltage. The amplitude of fundamental drain voltage is:

$$Y_{fund} = V_{dc} \tag{26}$$

The amplitude of fundamental drain current is:

$$I_{fund} = \frac{\mathrm{Im}\ ax}{2} \tag{27}$$

The output power is:

$$P_{fund} = \frac{1}{2} \times \operatorname{Re}(V_{fund} \times I_{fund}) = \frac{V_{dc} \times \operatorname{Im} ax}{4}$$

(28)

The DC power dissipation is:

$$P_{DC} = V_{dc} \times I_{dc} = \frac{V_{dc} \times \operatorname{Im} ax}{\pi}$$

(29)

The maximum drain efficiency is:

$$eff = \frac{P_{fund}}{P_{DC}} = \frac{\pi}{4}$$

[1] (30)

So, the maximum drain efficiency is (78.5%) as we have previously found.

Now, if we reduce the amplitude of the input voltage by a factor of 2 (6 dB power back-off), the drain current also reduces by a factor of 2 (the drain current is well below the saturation current). The drain supply voltage keeps a constant. The amplitude of fundamental drain voltage becomes:

$$V_{fund} = \frac{\operatorname{Im} ax}{2 \times 2} \times R_{opt} = \frac{V_{dc}}{2}$$

(31)

The output power becomes:

$$P_{fund} = \frac{1}{2} \times \operatorname{Re}(V_{fund} \times I_{fund}) = \frac{V_{dc} \times \operatorname{Im} ax}{16}$$

(32)

The DC power dissipation becomes:

$$P_{DC} = V_{dc} \times I_{dc} = \frac{V_{dc} \times \operatorname{Im} ax}{2\pi}$$

(33)

So, the maximum efficiency:

$$eff = \frac{P_{fund}}{P_{DC}} = \frac{\pi}{8}$$

[1] (34)

The maximum drain efficiency also reduces by a factor of 2.It becomes 39.5%. We can see the drain efficiency drops a lot at 6 dB power back-off point (factor four lower output power).

Figure 10 shows us the reason for why the efficiency drops quickly. The load is optimized for a certain value of input power (drain current). When the drain current reduces from Imax and load remain constant, the drain voltage can't reach the rail-to-rail swing (dotted line in figure 1.11). So, the output power and drain efficiency drop a lot.

# Figure 1.11 Drain voltage and current (Solid line at peak power, dotted line at power back off point) [1]

Now we discuss how to keep the efficiency at power back-off point. From the equations above, we can conclude that we have two ways to keep the efficiency at the power back-off point. One is we have a varying load with time at the output. When the power amplifier operates at a power which is much lower than the peak power, the load should increase corresponding to keep the efficiency:

If the load increases by a factor 2, the drain voltage becomes:

$$V_{fund} = \frac{\operatorname{Im} ax}{2 \times 2} \times 2 \times R_{opt} = V_{dc}$$

[1] (35)

The output power:

$$P_{fund} = \frac{1}{2} \times \operatorname{Re}(V_{fund} \times I_{fund}) = \frac{V_{dc} \times \operatorname{Im} ax}{8}$$

(36)

The DC power dissipation:

$$P_{DC} = V_{dc} \times I_{dc} = \frac{V_{dc} \times I_{m ax}}{2\pi}$$

(37)

The drain efficiency:

$$eff = \frac{P_{fund}}{P_{DC}} = \frac{\pi}{4}$$

[1] (38)

So, the drain efficiency keeps the same. However, the output power drops only by a factor of 2. From the derivation above, a varying load with time can keep the efficiency at power back-off point. This is the principle of a Doherty power amplifier.

Another way to keep the efficiency is we modulate the supply voltage according to the envelope of input signal. If the supply voltage has the same envelope as input power when the input power varies, the efficiency can be maintained.

### Section 5: EET and ET system

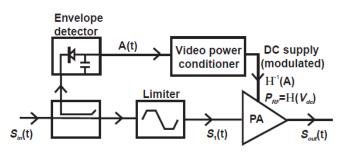

There are two similar systems for this ideal: Envelope Elimination and Restoration (EER) system and Envelope tracking (ET) system. We introduce both of them here. **EER system:** Envelope Elimination and Restoration (Figure 1.12):

Figure 1.12 Envelope Elimination and Restoration System

EER system is able to provide high power efficiency without compromising linearity. In EER system, a modulated RF signal is split into its polar components, envelope and phase, by a phase detector and a limiter respectively. The input signal is a constant envelope signal that can be amplified by a well-saturated amplifier. A well-saturated amplifier can be approximated by an RF voltage generator whose output amplitude is proportional to the dc supply voltage. On the other hand, the input signal only contains phase information. The limiter eliminates the possibility of AM-PM distortion so that the output of the PA still retains the undistorted phase characteristic of the input. The envelope information can be restored at the output by supply voltage modulation. The modulating signal is derived from an envelope detector. If the envelope of the input single can be restored perfectly at the output and there is no other power dissipation of components in the system (like the envelope detector), the efficiency can be maintained over a wide range of output power. However, there is always some power dissipation in the other components in the system [1] [4] [5].

### ET system:

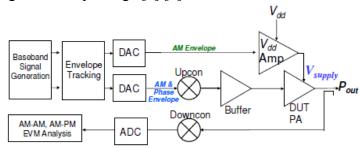

Envelope tracking system is similar to the envelope elimination and restoration system. The ET system differs from the EER system in two ways: 1. The RFPA in the system is a linear PA. 2. The input signal of the RFPA contains both amplitude and phase information [6] (figure 1.13). In ET system, the supply voltage increases in proportion to the increasing drive voltage. So, maximum efficiency is maintained and the output power increases linearly with input drive power. Comparing with ET system, the modulation control voltage of ET system doesn't have to be an exact replica of the signal envelope. The supply voltage could be tracked for just the upper few dB of the signal envelope range [1] [4].

Figure 1.13 Envelope tracking system [4]

### Section 6 Conclusion:

In this chapter, we introduced the principle of different operation classes and the systems to improve the performance of power amplifier at power back-off point. In chapter 3, we will design a power amplifier for different operation classes with NXP new generation LDMOS and find out which class is the most suitable one for our device.

### **Chapter 2 Harmonic Tuned Class-J Power Amplifier**

In the previous chapter, we have discussed the principles of conventional operation classes for power amplifiers. In this chapter we will discuss the principles of class-J operation. The definition of class-J operation is we use a second harmonic termination to tune the shape of drain voltage waveform. In this way, we can improve the performance of power amplifier. Let's discuss it in more detail.

### Section 1: Improvement of the efficiency of power amplifier

When we design a power amplifier, efficiency (drain efficiency, PAE) is an important performance. The equation for calculating the drain efficiency is:

$$Drain\_eff = \frac{P_{find}}{P_{dc}} \tag{1}$$

Drain\_eff represents the drain efficiency.  $P_{fund}$  and  $P_{dc}$  represent fundamental harmonic power and DC power respectively.

From the equation, we find that there are two ways to improve the efficiency performance.

(1) One is to increase the fundamental harmonic power. This means that all the output power should be at the fundamental frequency and there is no power dissipation at higher order harmonics. So, even if we want to use the harmonics to tune the waveform of drain voltage or drain current, the higher order harmonics' loads (higher than order 2) should be pure reactive. However, because of some parasitic resistance of the device, there is always some loss of at these higher order harmonics. But, this loss is typically small compared with the fundamental harmonic power. So, what we need to do is to keep all the higher order harmonics' loads reactive to minimize this loss.

(2) The second way to improve the efficiency is to minimize the dc power dissipation. The DC power is as follow:

$$P_{dc} = \frac{1}{T} \int I_d \times V_d \Box dt \tag{2}$$

From equation 2, we can learn that if we want to reduce the DC power dissipation, we need to reduce the product of current and voltage, consequently we should make the overlap of the drain current and voltage as low as possible at all times (Figure 2.1 and 2.2):

Figure 2.1 Drain current and voltage of class-AB/B PA

Figure 2.2 Drain current and voltage of an ideal switching PA [1]

We can perform the Fourier transform for the waveform in figure 2.1 and get the DC components of drain current and voltage. If the current and voltage are both high across the active device, DC components always exist at the same time and there will be power dissipation. Note that in figure 2.2, the ideal switching mode power amplifier has no drain current and voltage simultaneous, that means there is no power dissipation. All the DC power is transformed to signal power. For this ideal switching PA, the efficiency is 100%. But, this kind of PA is not easy to realize, what we can do is to use the harmonics to tune the waveform in figure 2.1 and make the overlap of drain current and voltage as small as possible.

### Section 2: Short all the harmonics: Class-AB/B operation:

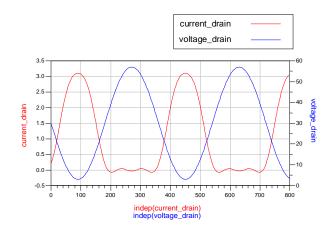

Before we invest the influence of harmonics on the efficiency performance of power amplifier, we first study the operation of class-AB/B. For class-AB/B power amplifier, all the harmonics are shorted except the fundamental harmonic. The drain current and drain voltage of class-AB/B power amplifier are as follow:

Figure 2.3 Drain voltage and current of class-AB/B operation (blue, drain voltage, red, drain current. X axis is phase of waveforms in degrees. Y axis is in Amperes and volts for current and voltage respectively)

The drain current of the class-AB/B power amplifier is half-sine wave. The equation for the half-sine wave is as follow:

half\_sin(

$$\theta$$

) = 1 +  $\frac{\pi}{2}$  × sin( $\theta$ ) +  $\sum_{n=1}^{\infty} -2 \times \frac{1}{n^2 - 1} \times \cos(n\theta), n = 2k, \forall n, k \in N$  [6] (1)

Here we normalize all the currents to the DC component. So, the DC current equals 1, the amplitude of fundamental harmonic current will be  $\frac{\pi}{2}$ . The amplitudes for higher order harmonics are defined as  $-\frac{2}{n^2-1}$ . From the equation we can see the half-sine wave contains only even-order harmonics and the fundamental harmonic.  $\theta$  represents the phase angle. The drain voltage of class-AB/B operation contains only the fundamental harmonic since all harmonics except the fundamental harmonic are shorted.

Obviously, if we can use the harmonics to make the drain voltage sharper, the overlap of the drain current and voltage can be reduced and the efficiency will increase.

#### Section 3: How the harmonics tune the fundamental frequency waveform

For class-F operation, the odd order harmonics are used to shape the drain voltage to a square waveform. For class-E operation, the drain voltage waveform is shaped by the harmonics so that the drain voltage and the slope of drain voltage is zero when the transistor is on. However, the harmonic tune conditions for ideal class-E/F operations are difficult to meet. Due to the existence of output capacitance of transistor, higher order harmonics are therefore difficult to tune. So, typically we can just tune the second harmonic in a practical matching network. This is main motivation for the use of class-J operation. The question is now how does the second harmonic affect the

performance of PA. Let's discuss it step by step.

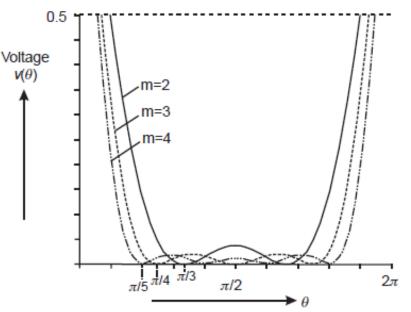

First, we show how the second harmonic affects the drain voltage waveform (figure 2.4):

Figure 2.4 Phase relation of fundamental and second harmonic waveforms (x axis, phase angle in degree, y axis, voltage in V. Red, fundamental harmonic voltage. Blue, second harmonic voltage. Pink, superimposition of these two voltage)

Figure 2.4 shows us that the drain voltage becomes shaper after tuning by second harmonic. This is what we want. For our first impression, the efficiency performance will be improved. However, is the problem really so simple? Let's calculate the theoretical efficiency of class-J operation.

### Section 4: Solutions for class-J operation

If the waveform only contains dc, fundamental and second harmonic components, we call it pseudo half sinusoidal (PHS) [6]. The PHS of drain current is as follow:

PHS\_Isin(

$$\theta$$

)=Idc+Ifund+Isecond

=Idc×(1+ $\frac{\pi}{2}$ ×sin( $\theta$ )- $\frac{2}{3}$ ×cos(2 $\theta$ )) [6] (4)

PHS\_Isin( $\theta$ ) is the drain current, Idc is the dc current, Ifund is the fundamental harmonic current and Isecond is the second harmonic current. For simplicity, we normalize the currents to DC current:

$$I_{dc} = 1 \tag{5}$$

$$I_{\text{fund}} = \frac{\pi}{2} \times \sin(\theta) \tag{6}$$

$$I_{\text{second}} = -\frac{2}{3} \times \cos(2\theta) \tag{7}$$

Now we have knowledge on the composition of current, in order to obtain the loads, we also need to know the composition of voltage. From figure 2.8, it works out that the voltage waveform and current have reverse sign (fundamental component of drain voltage has a 180 degrees phase reversal with the drain current and the second harmonic component of drain voltage has a 360 degrees phase reversal of drain

current), which is due to the nature of the schematic (see figure 2.5).

Figure 2.5 The drain current and voltage have reversed phase relation intrinsically. (see ID and Vds in the graph)

In the previous expressions of drain current and voltage, this phase reversal hasn't been taken into account yet.

The load for the second harmonic: on first sight it might seems that the second harmonic load can be arbitrary value. Actually, as we discussed in section 1, in order to transform as much power from dc to fundamental frequency as more as possible, we should minimize the power dissipation at higher order harmonics. Therefore, the second harmonic load we used should be pure reactive. It can be inductive or capacitive. Inductive load means the second harmonic voltage will lead 90 degrees with the drain current. And a capacitive load means the second harmonic voltage will lag 90 degrees with the drain current. So, if we want to synchronize the peak of the fundamental and second harmonic waveform like that in figure 2.4, the fundamental load should make the fundamental voltage lead or lag 45 degrees with the drain current. This also means that: for the typical class-J operation, there are two solutions for the fundamental and second harmonic loads. Let's discuss both of them.

The pseudo half sine (PHS) form of drain voltage:

$$PHS_V \sin(\theta) = 1 + A \times \sin(\theta) - B \times \cos(2\theta)$$

[6] (8)

A and B is the amplitude of fundamental and second harmonic voltage respectively. All of the amplitudes are normalized to Vdc.

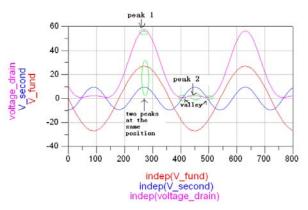

If we obtain the derivative of this equation and make it equal to zero, we can get the two peaks and two valleys of PHS\_Vsin [1]:

$$peak_{1,2} = 1 \pm A + B \textcircled{a} \theta_1 = \frac{\pi}{2}, \theta_2 = \frac{3\pi}{2}$$

[6] (9)

$$\min_{1,2} = 1 - B - \frac{A^2}{8B} @ \theta_1 = \pi + \arcsin(\frac{A}{4B})$$

$$@ \theta_2 = 2\pi - \arcsin(\frac{A}{4B})$$

(10)

18

The minimum value of PHS waveform should be zero:

$$\min_{1,2} = 0 \Longrightarrow 1 - B - \frac{A^2}{8B} = 0 \Longrightarrow A^2 = 8B(1 - B)$$

(11)

$$A^{2} = 8B(1-B) \Longrightarrow B = \frac{1}{2} + \frac{1}{2}\sqrt{1 - \frac{A^{2}}{2}}$$

(12)

From equation 17, we can get the maximum and minimum values of A and B respectively:

$$1 - \frac{A^2}{2} \ge 0 \Longrightarrow \frac{A^2}{2} \le 1 \Longrightarrow A \le \sqrt{2}$$

(13)

$$A_{Max} = \sqrt{2} \& B_{Min} = \frac{1}{2}$$

[6] (14)

The first solution: we can get the first solution by check the drain current and voltage relationship.

From equation 9 we get the drain current equation:

$$I_{drain}(\theta) = \frac{I_{Peak}}{\pi} + (\frac{I_{Peak}}{2}) \times \sin(\theta)$$

$$-\frac{2 \times I_{Peak}}{3 \times \pi} \times \cos(2\theta)$$

(15)

$$I_{dc} = \frac{I_{Peak}}{\pi} \tag{16}$$

$$I_{fund} = \frac{I_{Peak}}{2} \times \sin(\theta) \tag{17}$$

$$I_{\text{sec ond}} = -\frac{2 \times I_{Peak}}{3 \times \pi} \times \cos(2\theta)$$

(18)

For the first solution, if the load for second harmonic is capacitive. The second harmonic voltage should lead 90 degrees with the phase of drain current :

$$V \sec ond = -B\cos(2\theta + \pi - \frac{\pi}{2}) = -B\cos(2(\theta + \frac{\pi}{4}))$$

(19)

B is amplitude of Vsecond, the pi in the equation is caused by the reverse phase relation of drain current and voltage as shown in figure 2.5.

In order to synchronize the peaks of the fundamental and second harmonic voltage wave, the fundamental harmonic voltage waveform should lags 45 degrees with the phase of drain current:

$$V_{fund} = A \times \sin(\theta + \pi + \frac{\pi}{4}) \tag{20}$$

Where A is the amplitude of Vfund. The pi is caused by the reverse phase relation of drain current and voltage as shown in figure 2.5.

Now we calculate the drain efficiency. The output voltage and on the load is Vout and Iout (see figure 2.5):

$$V_{out}(\theta) = V_{fund \_out} + V \text{ sec ond \_out}$$

=  $A \times V dc \times \sin(\theta + \frac{\pi}{4}) - B \times V dc \times \cos(2\theta - \frac{\pi}{2})$  (21)

$$I_{out}(\theta) = I_{fund\_out} + I_{sec ond\_out}$$

=  $(\frac{I_{Peak}}{2}) \times \sin(\theta) - \frac{2 \times I_{Peak}}{3 \times \pi} \times \cos(2\theta)$  (22)

The output voltage and the current flow into the load have in-phase relation and they don't contain DC component.

Now, we can calculate the output power and efficiency of class J operation. The DC power dissipation can be calculated from the DC components of drain voltage and current:

$$P_{dc} = I_{dc} \times V_{dc} = \frac{I_{Peak}}{\pi} \times V_{dc}$$

<sup>(23)</sup>

The output power can be calculated from the output voltage and current on the load:

$$P_{out} = \frac{1}{2} \times \operatorname{Re}[V_{fund\_out} \times \operatorname{conj}(I_{fund\_out})]$$

$$= \frac{1}{2} \times \operatorname{Re}[AV_{dc}e^{j\omega(\frac{\pi}{4})} \times \frac{I_{Peak}}{2}] =$$

(24)

$$\frac{I_{Peak} \times V_{dc}}{4} \times \cos(\frac{\pi}{4}) \times A$$

The drain efficiency:

$$\eta = \frac{P_{out}}{P_{dc}} = \frac{\pi}{4} \times \frac{1}{\sqrt{2}} \times A \tag{25}$$

The maximum efficiency can be obtained when A reaches its maximum value. We have found that the maximum value for A is  $\sqrt{2}$ . So, the maximum efficiency is:

$$\eta_{\max} = \frac{P_{out}}{P_{dc}} = \frac{\pi}{4} \times \frac{1}{\sqrt{2}} \times \sqrt{2} = \frac{\pi}{4} \approx 78.5\%$$

[6] (26)

So, the theoretical highest drain efficiency of class-J operation is 78.5% and if we want to achieve this peak efficiency, we need to choose A as  $\sqrt{2}$  and B as1/2.

$$A = \sqrt{2} \tag{6} \tag{27}$$

$$B = \frac{1}{2} \tag{28}$$

Therefore, the drain voltage is:

)

$$V_{drian}(\theta) = V_{dc} + \sqrt{2} \times V_{dc} \times \sin(\theta + \pi + \frac{\pi}{4}) - \frac{1}{2} \times V_{dc} \times \cos(2\theta + \pi - \frac{\pi}{2}) \quad (29)$$

$$V_{fund} = \sqrt{2} \times V_{dc} \times \sin(\theta + \pi + \frac{\pi}{4})$$

(30)

$$V_{\text{sec ond}} = -\frac{1}{2} \times V_{dc} \times \cos(2\theta + \pi - \frac{\pi}{2})$$

(31)

The pi in equations (29) and (30) is due to the nature of schematic (see figure 2.5). So, it should be eliminated when we calculate the loads. From equations (16) to (17) and equations (30) to (31), we can calculate the fundamental and second harmonic loads:

$$Zload_{fund} = \frac{2\sqrt{2} \times V_{dc}}{I_{Peak}} \angle \frac{\pi}{4}$$

(32)

$$Zload \text{ sec ond} = \frac{3 \times V_{dc} \times \pi}{4 \times I_{Peak}} \angle -\frac{\pi}{2}$$

(33)

We can choose the values of Vdc and Ipeak to check the loads on the Smith chart. We assume Vdc=30 V and Ipeak=2.5 A.

$$Zload_{fund} = 34 \times \angle \frac{\pi}{4}$$

(34)

$$Zload \text{ sec ond} = 28.3 \angle -\frac{\pi}{2}$$

[6] (35)

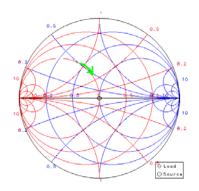

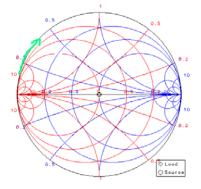

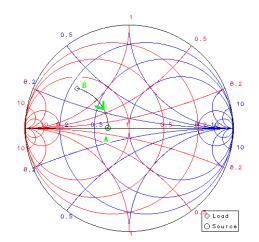

The loads on the Smith chart (figure 2.6):

Figure 2.6 The fundamental and second harmonic loads (red, fundamental harmonic, blue, second harmonic, normalized to 50 Ohms )

We can get an alternative solution on the Smith chart, where the load for second

harmonic of solution 2 is inductive (figure 2.7):

Figure 2.7 The loads of solution 2 (red, fundamental harmonic, blue, second harmonic, normalized to 50 Ohms)

The drain voltage and current waveform for solution 1 and 2:

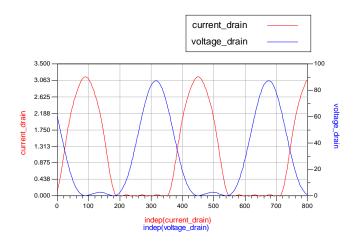

Figure 2.8 (a) Drain voltage (blue) and current (red) waveforms for solution 1 of class-J operation

Figure 2.8 (a) Drain voltage (blue) and current (red) waveforms for solution 2of class-J operation

So, the two solutions for class-J operation are:

$$Zload_{fund} = \frac{2\sqrt{2} \times V_{dc}}{I_{Peak}} \angle \pm \frac{\pi}{4}$$

(36)

$$Zload \text{ sec ond} = \frac{3 \times V_{dc} \times \pi}{4 \times I_{Peak}} \angle \mp \frac{\pi}{2}$$

(37)

$$P_{outpeak} = \frac{1}{4} \times V_{dc} \times I_{peak}$$

(38)

The loads in terms of peak power are:

$$Z_{fund} = \frac{V_{dc}^2}{\sqrt{2} \times P_{outpeak}} \angle \pm \frac{\pi}{4}$$

(39)

$$Z_{\text{sec ond}} = \frac{3\pi \times V_{dc}^2}{16 \times P_{outpeak}} \angle \mp \frac{\pi}{2}$$

[6] (40)

Vdc is the dc voltage component of drain voltage and Ipeak is the peak amplitude of drain current.

In this section, we have discussed the efficiency that class-J operation can provide together with the optimal loads for fundamental and second harmonics. We can call this ideal class-J operation. For ideal class-J operation, the maximum drain efficiency is 78.5%, which is the same as that of class-B operation. However, this efficiency is reached without providing a perfect short for the second and higher order harmonics, something that is not always practical (for example, there is a series inductor of package) in wideband design. So, for single frequency design, we should test which class is works best for our device. While for wideband design, we can make use of the 2<sup>nd</sup> harmonic termination to achieve better results, when second harmonic shorts are not practical. In the next section, we will discuss some practical considerations.

### Section 5: Sub-optimum class-J operation

In section 4, we have obtained the solutions for ideal class-J operation. From equations (36) to (40) we can see: for fixed values of dc voltage and Ipeak or a peak output power, the optimal loads for fundamental and second harmonics are constants for a given operating frequency.

But if we want to design a wideband power amplifier, we will have constant values for the components of our matching network (for example, an fixed inductor, capacitor or transmission line). Use of these components will result in a not constant reactance versus frequency. For example, when we have an inductive load, the load is given by:

$$G_{loadfund} = g_{fund} + \frac{1}{j\omega L_{fund}}$$

(41)

gfund is the conductance of the load, and with the frequency changes, the imaginary

part  $\frac{1}{j\omega L f_{und}}$  will shift on the smith chart (figure 2.9):

Figure 2.9 With increasing frequency, the imaginary part of the load will shift on the smith chart in the direction of the green arrow

Another complication is that the reactance of parasitic output capacitance of the device  $i\omega C_{parasitic}$  will also change with frequency. Even worse this parasitic output

capacitance is not a linear capacitor with supply voltage. In fact it is a very strong function of supply voltage, which will cause the optimum load shift on the Smith chart with supply voltage modulation as well. So, for a wideband power amplifier with supply voltage modulation, it's almost impossible to match every load of different frequency to the optimum load. This is the reason why we discuss here sub-optimal class-J operation.

For optimum class-J, two conditions should be met:

(1) The peak of the fundamental voltage waveform should synchronize with the second harmonic voltage waveform (as shown in figure 2.4). And only this condition is met, the superimposition of these two waveforms will have two peaks and two valleys.

(2) The amplitude ratio of fundamental and second harmonic voltage should be a certain value. From equation (35) we know the amplitude ratio of fundamental and second harmonic voltage is A/B. For the optimal load,  $A=\sqrt{2}$ ,  $B=\frac{1}{2}$ . So,

$$\frac{A}{B} = 2\sqrt{2} = 2.828$$

For sub-optimal class-J operation, we indeed have used the second harmonic to tune the drain voltage waveform, but we don't meet the two conditions above exactly.

First, as we have discussed above, for wideband power amplifier, the fundamental loads for every frequency can't be matched to the optimal load. So, let's discuss how are the waveforms like, if the load deviates from the optimum value. For example:

When it's the optimum load is give by:  $Zload_{fund} = \frac{2\sqrt{2} \times V_{dc}}{I_{Peak}} \angle \frac{\pi}{4}$

The waveform is:

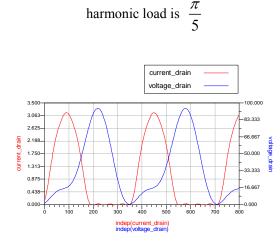

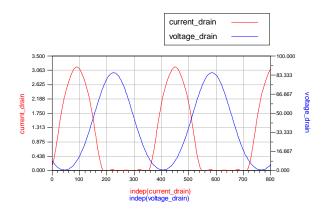

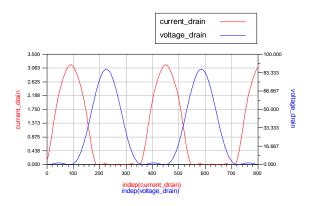

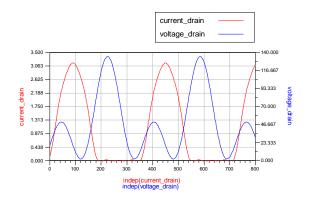

Figure 2.10 Drain current and voltage waveforms for optimal load When the phase angle changes to  $\frac{\pi}{5}$  and  $\frac{\pi}{3}$ , the waveforms are:

Figure 2.11 (a) Drain current and voltage waveforms when the phase angle of fundamental

harmonic load is  $\frac{\pi}{3}$

| Phase angle of fundamental load | Drain efficiency |

|---------------------------------|------------------|

| Pi/5                            | 69.2%            |

| Pi/4                            | 78.5%            |

| Pi/3                            | 62.4%            |

Table 2.1

Phase angle of fundamental load versus drain efficiency

We can see, when the fundamental load have phase angle different from the optimal load, the waveforms of drain voltage also differ (compare figure 2.11). The related drain efficiency performance for different phase angles of fundamental load are shown in table 2.1.

Because of some parasitical series resistance of device, the second harmonic load is also not pure reactive. This will also change the phase angle of second harmonic voltage and causing similar problems as above.

Second, as we have previously discussed above, another factor which affect the shape of drain voltage waveform is amplitude ratio of fundamental and second harmonic voltage. The ratio for optimal class J is  $\frac{A}{B} = 2\sqrt{2} = 2.828$ . What happens if we change this ratio? To investigate this we choose the ratio as 9, 3, 1 respectively and check the drain voltage waveform:

Figure 2.12 (a) The influence of amplitude ratio of fundamental and second harmonic voltage. A/B=9. The DC voltage is adjusted to 38.5 V to make the drain voltage valley reach 0.

Figure 2.12 (b) The influence of amplitude ratio of fundamental and second harmonic voltage. A/B=2. The DC voltage is 30 V to make the drain voltage valley reach 0.

Figure 2.12 (c) The influence of amplitude ratio of fundamental and second harmonic voltage. A/B=1. The DC voltage is adjusted to 50 V to make the drain voltage valley reach 0.

We calculate the efficiency of the efficiency from different ratio of A and B and get

the following results:

| Ratio of A/B | Drain efficiency |

|--------------|------------------|

| 9            | 64.9%            |

| 3            | 76.2%            |

| 1            | 56.5%            |

Table 2.2 Ratio of A/B versus drain efficiency

We can see: when the ratio is 9, the amplitude of second harmonic voltage is much smaller than that of fundamental harmonic voltage. The drain voltage is almost the same as the waveform of class-AB/B. When the ratio decreases to 3, the voltage waveform is more flat in this lower range, so. it's close to the optimal class-J waveform. When the ratio reduces to 1, the amplitudes of the fundamental and second harmonic voltage waveform are equal. The lower peak of the drain voltage becomes higher. The higher peak of fundamental voltage becomes shaper, which will exceed the breakdown voltage when the supply voltage of PA is high.

When the ratio of A/B is around 3, the efficiency performance is the best. When the ratio becomes higher or lower, the efficiency drops.

Two factors will affect the amplitude ratio. One is the phase angle and load value of fundamental harmonic load. The other is the value of second harmonic reactive load. If we have an inductive load, the imaginary part of the load will shift with frequency on the smith chart as shown in figure 2.12.

Figure 2.13 Imaginary part of load shifts with frequency (green arrow)

The amplitude of second harmonic voltage is determined by the values of second harmonic load: jwL. When w or L increases, the amplitude of second harmonic voltage will increase. So, we can choose the value of L to tune the ratio A/B.

We discussed the sub-optimal class J operation above. It's will prove to be applicable for supply voltage modulation and wideband design. For other practical problems of sub-optimum class-J, we will discuss them in next chapter when we realize the circuit.

### Section 6 Conclusion:

In this chapter, we discussed the principles of class-J and sub-optimum class-J operation. The optimum class-J operation can give us a peak drain efficiency of 78.5%. We can obtain class-J waveform if we use second harmonic to tune the drain voltage waveform of class-AB/B operation. This kind of operation is meaningful when we can't perfectly short the second harmonic. In next chapter, we will discuss how to realize a class-AB/B and class-J power amplifier.

### Chapter 3 Design of a "Narrowband" Hybrid Class Power

### **Amplifier for EER or ET system operation**

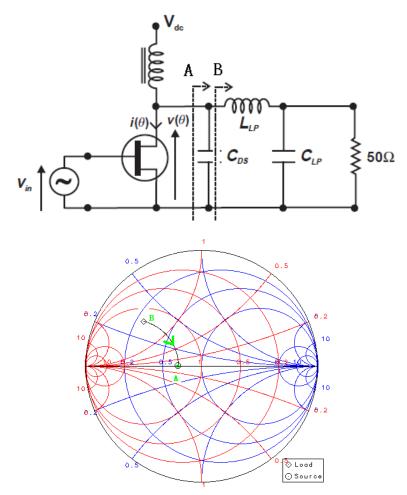

In this chapter, we will discuss the optimum loading for a power amplifier using hybrid-class operation and its related matching network.

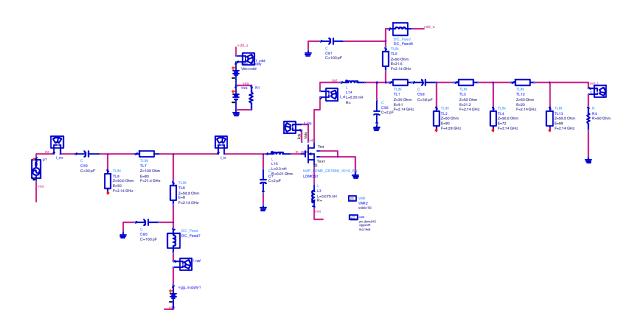

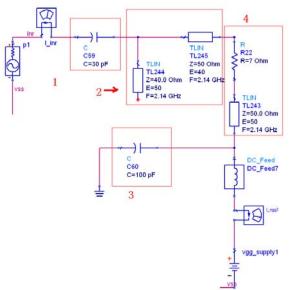

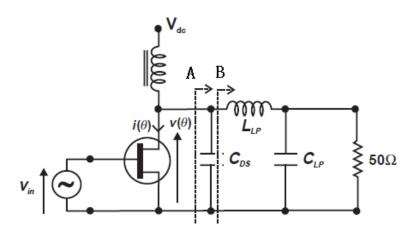

The definition of hybrid-class power amplifier in this work refers to the situation that the power amplifier changes operation class with frequency, or time-varying supply voltage. A narrowband power amplifier in an EER (Envelope Elimination and Restoration) or ET (Envelope Tracking) system, can operate at different classes at different supply voltages. For our design in this chapter, the power amplifier operates in class-J/E at lower supply voltages and in class-AB/B at higher supply voltages. We will discuss this operation in more detail in the following sections. For the wideband power amplifier, the amplifier does not only change operation class with supply voltage modulation, but also with frequency. We will talk about the wideband hybrid class PA in the next chapter.

In this chapter we first discuss a "narrowband" hybrid power amplifier design. As we have discussed in chapter 2, we short all the harmonics except the fundamental to make a class-AB/B power amplifier. Or, we can use the second harmonic to tune the drain voltage waveform to make a class-J power amplifier. Both of them have a theoretical peak efficiency of 78.5%. But, due to device parasitics behave differently. Which class operation is more suitable for our device, still needs to be investigated. Of course, the efficiency is only one of the specifications. The other specifications, like power gain, peak output power, peak drain efficiency, etc, are also very important. So, we will realize both classes to find the best operation for our device.

Before beginning our design, we should first have some knowledge of the device we use. So, in section 1, we discuss the device properties and package parasitics.

In section 2, we design two "narrowband" power amplifiers optimized for fixed supply voltage operation.

We design a "narrowband" power amplifier optimized for the efficiency at power back-off in section 3 and comment on the advantages and disadvantages of it.

In Section 4 and 5, we use lumped elements and transmission lines to complete the PA design.

### **Section 1: Device properties:**

Before we start to design, we first should know the properties of the device. The device properties are as follows:

- 1. Device: NXP's latest generation 7 LDMOS technology, (12 W output power).

- 2. Channel length: 750 um

- 3. Cell pitch: 250 um

- 4. Cells: 7

- 5. Drain breakdown voltage: 65 V

- 6. Gate breakdown voltage: Larger than 20 V

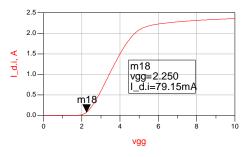

- 7. Threshold voltage: 2.25volts (figure 3.1):

Figure 3.1 The threshold voltage of the LDMOS (I\_d represents drain current and vgg is the gate voltage).

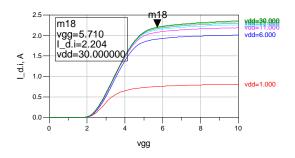

8. Saturation drain current: For different drain supply voltages, the saturation drain current is different. It's between 1.7 (@6V vdd) to 2.2 (@30 V vdd) Amperes, and the corresponding gate voltage is around 5 to 6 volts (figure 3.2). The maximum linear output power of the device is determined by the saturation currents.

Figure 3.2 Saturation currents of the device. Different colors represent different drain supply voltages. Vgg is the gate voltage (in Volts) and I\_d (in Amperes) is the drain current.

9. Parasitic capacitance and resistance of the device: The parasitic components of the device will affect the input and output matching. Especially, the output capacitor of the device has non-linear relation with the supply voltage. The reactance value of this output capacitor will also shift with frequency, which will make the wideband matching more complicated.

We choose the central frequency (2.14 GHz) for testing and check how the parasitic capacitances and resistances vary with the supply voltage (Vdd).

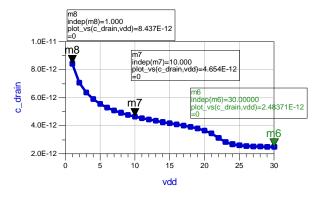

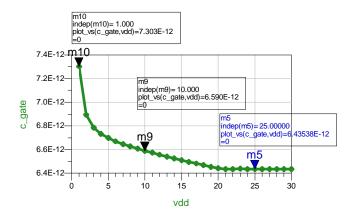

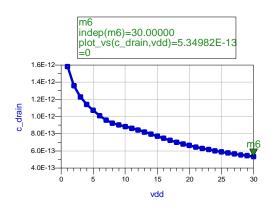

Drain capacitance (figure 3.3):

Figure 3.3 Drain parasitic capacitance versus supply voltage (The units are F and V respectively)

We can see from figure 3.3 that the drain parasitic capacitance is 8.43 pF at 1 volt and strongly decreases with rising vdd.

For the gate parasitic capacitance consider (figure 3.4):

Figure 3.4 Gate parasitic capacitance versus supply voltage (The units are F and V respectively)

When the supply voltage varies from 10 V to 30 V, the gate parasitic capacitance doesn't change so much (6.59 pF to 6.43 pF, Figure 3.4). So, for operation with supply voltage modulation, the gate parasitical capacitance is not a big problem. The output capacitance affects the matching. For example, if we want to design a

class-B power amplifier, the optimum load for this PA is Zload, which should be a purely resistive load. However, due to the existence of output capacitance, we need an inductive load to compensate this capacitor. See figure 3.5.

Figure 3.5 The load seen from reference plane A and B

In the above graph of figure 3.5, from reference plane B we get an inductive load as shown in lower graph of figure 3.5. Cds is the output capacitor. So, seen from reference plane A, the load should be pure resistive (point A on the Smith chart). This kind of compensation for single frequency design is easy to do. But, when applying supply voltage modulation and wideband operation, it becomes more difficult since the reactance value of this capacitor will change a lot with supply voltage and frequency. In addition we want a simple matching topology with fixed value components to compensate it. The method to solve this problem will be discussed in the later sections.

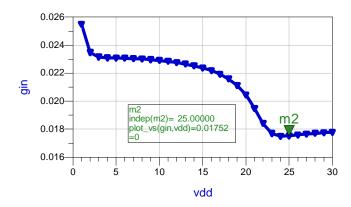

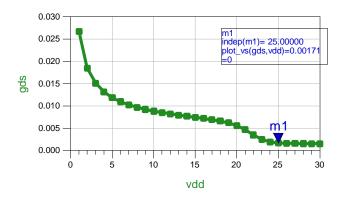

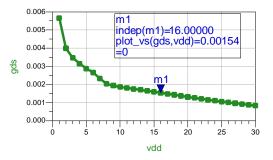

The gate and drain parasitic conductance will also vary with supply voltage (figure 3.6):

Figure 3.6 (a) Gate (gin) parasitic conductance vary with supply voltage (The units are S and V respectively)

Figure 3.7 (b) Drain (drain) parasitic conductance vary with supply voltage (The units are S and V respectively)

The gate conductance is around 0.02 S which is equivalent to a shunt resistance of 50 Ohms for different supply voltage values. And, the drain conductance reduces from 0.025 to 0.0017 S (resistance from 50 Ohms to 500 Ohms) with supply voltage increases from 10 to 30 volts. This parasitic conductance will cause power dissipation. So, the device will have more power loss, lower efficiency and lower power gain at lower supply voltage than that at higher supply voltage.

When we design the input and output matching network, we should take these parasitic components into account:

$$Y_{opt} = \frac{1}{Z_{opt}} = g_{opt} + jb_{opt} \tag{1}$$

$$g_{opt} = g_{load} + g_{parasitic} \tag{2}$$

$$b_{opt} = b_{load} + b_{parasitic} \tag{3}$$

So, the loads we want to design:

$$g_{load} = g_{opt} - g_{parasitic} \tag{4}$$

$$b_{load} = b_{opt} - b_{parasitic} \tag{5}$$

$$Y_{load} = g_{load} + jb_{load} = \frac{1}{Z_{load}}$$

(6)

10. Parasitic of package: The package used in our design is NXP SOT 467 package. In order to include the effect of the package in our design, we should model the parasitical components of the package.

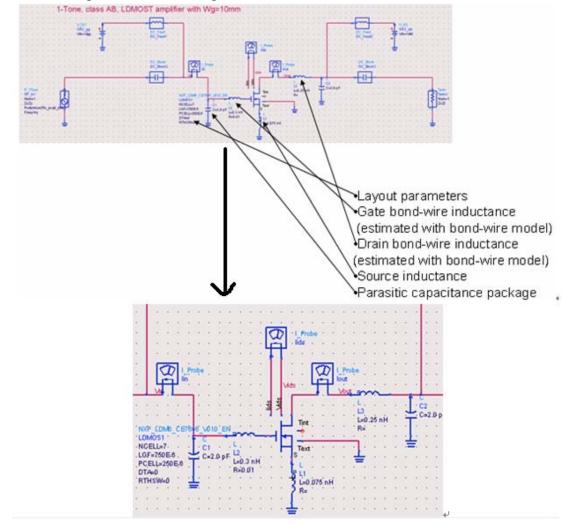

As shown in Figure 3.8, the drain, gate and source bond wires have been modeled:

Figure 3.8 The modeled components of package parasitic

The parasitic inductance at source is 0.075 nH. The parasitic inductance, resistance and capacitance at gate are 0.075 nH, 0.01 Ohm and 2.0 pF respectively. The parasitical inductance and capacitance at drain is 0.25 nH and 2.0 pF respectively.

For the gate and drain package parasitics, we can absorb them in our matching design. As long as we achieve the optimum load, the performance will be the same.

**Suitable operation class for NXP LDMOS:** Due to the existence of parasitics of device and package, we need to identify, which class of operation is more suitable for this device. Typically, we can improve the efficiency with harmonic tuning. However, if the frequency is very high, the loss of parasitics will become significant. There will also be some loss at the harmonics. In this case, we can get higher efficiency when the harmonics are shorted.

**Performance at power back-off:** In addition, to find the optimum operation conditions we should consider the fact that in an operation with a WCDMA signal, the supply voltage varies a lot with time. In terms of output power, the power amplifier will operate most of the time at 6 to 11 dBm power back off. So, our target will be not to get the highest efficiency at a single supply voltage point, but, obtain the highest average efficiency according to the PDF of WCDMA signal (appendix 1).

# Section 2: Optimizing the load condition for single supply voltage

Before considering the optimum load condition for power back-off, we first discuss how to optimize the load condition for single supply voltage with class-AB/B and class-J operations.

**Class-AB/B operation optimized for single supply voltage:** For class-AB/B operation, we should short the harmonics and only emphasis on the fundamental frequency load. We summarize the steps to find the optimum load of class-AB/B operation for single supply voltage.

1. The first step is to choose the input power. The input of power amplifier is a large signal which will change its bias condition. Each device has its own 1 dB compression point in terms of output power for a single supply voltage value, the corresponding input power we call it input 1 dB compression point. Mostly, the input power should be chosen as the input 1 dB compression point. Otherwise, the power amplifier can't achieve the maximum output power. But, if we choose the input power much higher than the input 1 dB compression point, the device will be over-driven too much, which will make the power amplifier degrade or will yield even device failure over time. We don't know the 1dB compression point before we finish our design. So, the strategy is we first estimate the input power value according to the gain of the device technology. After finish the matching network, we check the 1 dB compression point and adjust the input power.

2. The second step is the design of input matching. In order to guarantee we can transform the highest power from source to the transistor, the input of the transistor should be conjugate matched. The stability issue will be discussed in the following sections.

3. The third step is to estimate the optimum output load. For class-AB/B power amplifier, the equation for calculating the optimum load is  $\frac{Vdd^2}{2 \times P_{out}}$ , where Vdd is the

supply voltage, Pout is the output power you want to obtain. Normally, it's the maximum linear output power for a device for a given voltage as we discussed previously. However, this equation can only be used to calculate the optimum load for ideal device (no parasitic). The real device always contains some parasitic capacitance and resistance and we should compensate for them. So, we can get a load whose real part is the optimum resistor for class-AB/B and imaginary part can compensate the output capacitance of the device (as shown in equation 1 to 6).

4. In step 3, we should have a good estimation for the optimum load. But, there are still some non-ideal situations of the device which can't be predicted. So, load-pull simulations are necessary. So, in step 4, we do the load-pull simulation to find out the point on the Smith chart where the efficiency is the highest. Notice that the peak efficiency and the peak output power do not necessarily are at the same point in the Smith chart. We should make a compromise between them to make sure we can achieve a good efficiency performance and peak output power simultaneous.

Now, we start the test to find the optimum load of class-AB/B operation with single supply voltage:

1. These are the simulation parameters:

(1). Drain supply voltage: 30 Volts;

- (2). Gate voltage: 2.25 Volts (the threshold voltage of this device)

- (3). Design frequency: central frequency of WCDMA signal, 2.14 GHz

(4). Input power: the input power are chosen as 23 dBm. The reason is: normally, the base station power amplifier has a gain of 15 to 20 dB, and this device's maximal linear output power is 12W (40.7 dBm). Thus, the input power should be output power minus power gain, which is between 20 to 25 dBm. Here, we make a compromise to choose 23 dBm as our input power. After finishing the matching for the device, we can check the 1 dB compression point to modify the input power.

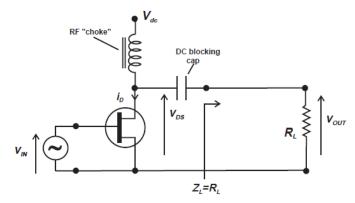

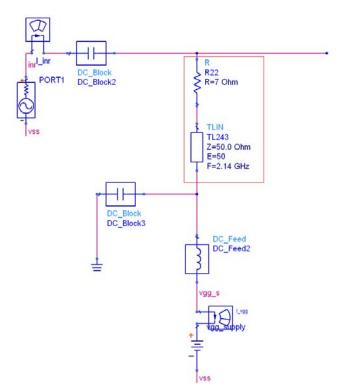

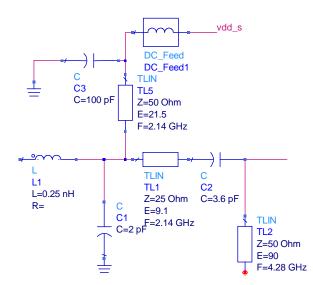

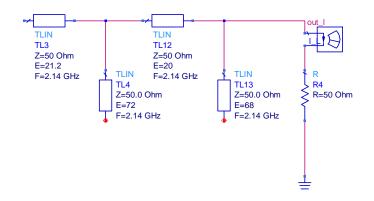

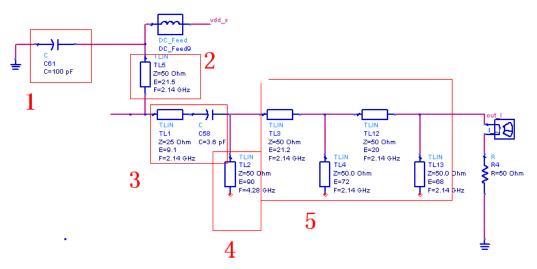

2. The test schematic for input and output matching (Figure 3.9):

Figure 3.9 Testing schematic for input and output matching. The arrows represent the reference planes and direction we see the loads of matching networks.

We use the ideal equations components of ADS to find the optimum loads for input and output matching before we realize it. The reference planes and direction we see the loads are shown in figure 3.9 (position A and B). All the load conditions we will discuss later are all seen from this direction. Here we don't include the drain parasitics of package because we can include these in the load realization after we have found the optimum load.

3. Input matching: conjugate match the input (figure 3.10 and 3.11):

Figure 3.10 S11 parameter of the device before (left) and after (right) input matching. (Normalized to 50 Ohms)

Figure 3.11 S 11 of the device after input matching

Figure 3.11 shows that the device has been conjugate matched at 2.14 GHz

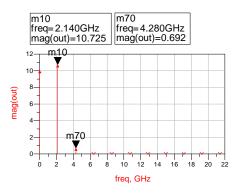

4. Base on this conjugate input match, we do the output matching. The power amplifier operates at class-AB/B, so, the second harmonic (4.28 GHz) and higher order harmonics (6.42GHz, 8.56 GHz, etc.) should be shorted (Figure 3.12). Then, we estimate the optimum value of fundamental load for 30 V supply voltage. The equation to calculate the optimum load:

$$\frac{VDD^2}{2 \times pout} = \frac{30^2}{2 \times 12} = 37.5Ohm \,\mathrm{s}$$

(7)

Vdd is the supply voltage and pout represents the peak output power (for this device, it's 12 W). So, for convenience, the Smith chart for load matching can be normalized to 30 Ohms.

Then, we check the drain output capacitor of this device: It's around 2.5 pF and -j\*29.7 Ohm / j\*0.034 S at 2.14 GHz. We need an inductive imaginary part of the output load to compensate the effect of drain parasitical capacitor. The inductive part should be j\*29.7 Ohms/ -j\*0.034 S. When it normalizes to 30 Ohms, it's around 1.

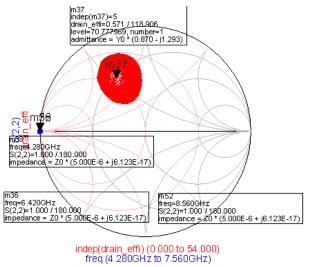

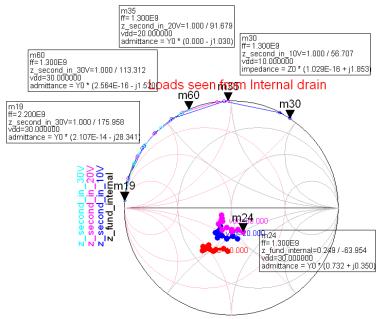

So, the estimated optimum output load should be around 0.027–j\*0.034 S (0.8–j\*1 S, when normalized to 30 Ohms). In order to find the true optimum output load in this case, we must do the load-pull simulations based on the estimated value. The load-pull simulation results are as shown in figure 3.12:

Figure 3.12 Load- pull simulation results for class-AB operation The Smith chart is normalized to 30 Ohms (blue, higher order harmonics loads. Red, fundamental harmonic efficiency contours. The contours represent the region where efficiency is higher than 60%)

From figure 3.12, we can see the second and higher order harmonics are shorted (blue). The optimum fundamental harmonic load can be found from efficiency contours on the Smith chart (red). At the same time, we should consider whether the

power amplifier reaches the peak power (40.7 dBm). So, we also need to check the power contours on the Smith chart (Figure 3.13)

Figure 3.13 Output power contours (contours for output power higher than 40 dBm). The Smith chart is normalized to 30 Ohms

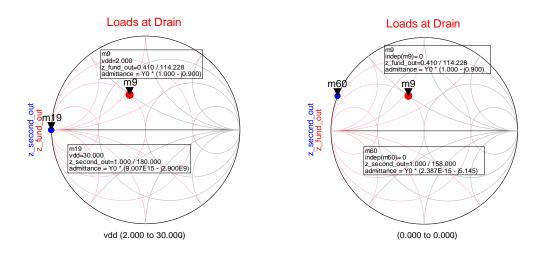

The peak drain efficiency and peak output power point are not at the same position. Trade-off should be made between efficiency and output power. The highest efficiency point is 0.87-j\*1.29 S which is very close to the estimated value (0.8 - j\*1 S). Here, we choose load value 1-j\*1.25 S. With this load, the drain efficiency is around 65% and the peak power is 40.7 dBm. We match the output to this optimum load using ADS ideal components and check the performance (Figure 3.14).

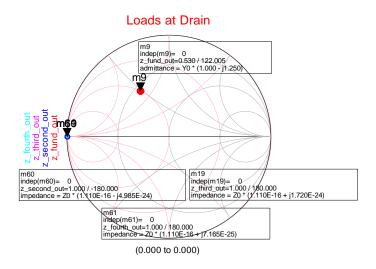

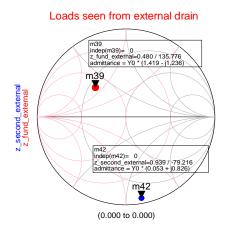

Figure 3.14 (a) The optimum output load seen from external drain (including package parasitics and excluding device parasitics) for 2.14 GHz and 30 V supply voltage. The Smith chart is normalized to 30 Ohms

Figure 3.14 (b) The optimum output load seen from internal drain (including both package and device parasitics) for 2.14 GHz and 30 V supply voltage. The Smith chart is normalized to 30 Ohms

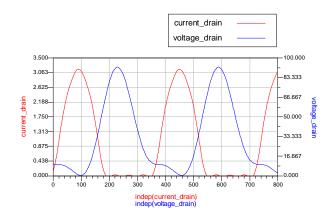

The performances of the load condition in figure 3.14 are as follows:

Figure 3.14 (a) Drain current (red) and voltage (blue).

| drain_efficiency | added_efficiency | output_power_dbm | power_gain |

|------------------|------------------|------------------|------------|

| 70.489           | 69.391           | 40.870           | 18.075     |

|                  |                  |                  |            |

|                  |                  |                  |            |

Figure 3.14 (b) Simulation results of load condition in figure 3.14

The peak drain voltage is 56 V which is lower than the drain breakdown voltage (65

V). The peak drain current is 1.8 A which is also below the saturation current. The output power is 40.87 dBm which approximates the peak power and the drain efficiency is 70.5%. PAE is 69.3%. The output power gain is 18 dB.

As we have mentioned previously, in WCDMA system, the power amplifier often operates 6 dB or more from the peak power. So, we should check how this output load performs at power back-off point if we vary the supply voltage.

**Class-J operation optimized for single supply voltage:** Both the class-E and class-J power amplifiers use the harmonics to tune the drain voltage to obtain better efficiency performance. The difference is ideal class E power amplifier use infinite harmonics  $(2^{nd}, 3^{rd}, 4^{th}, 5^{th}, \ldots)$  harmonics) to tune the drain voltage. For ideal class E operation, the drain voltage should meet two requirements: 1. Drain voltage should be zero when the transistor on. 2. The slope of the drain voltage should be zero when the transistor on. But, due to the non-ideal conditions of the device (parasitic capacitances and resistances), the ideal class E requirements are difficult to meet. So, we often only tune the  $2^{nd}$  and  $3^{rd}$  harmonic to get sub-optimum class-E power amplifier solutions.

Class-J can be considered as the middle class Between class-AB and sub-optimum class-E. For class-J operation, we only tune the second harmonic. In this way, we can make our matching network simpler and the performance isn't in practice much lower than for class E.

The steps to find out the optimum load of class-J operation with single supply voltage:

- 1. Input power is chosen as 24 dBm. The reason is similar to class-AB/B operation.

- 2. Again, the same, we conjugate match the input of the transistor.

- 3. For class-J operation, we should estimate the loads for both fundamental harmonic and 2nd harmonic. We have discussed in chapter 3: for class-J operation, there are 2 solutions for the load. The fundamental load is inductive (capacitive) and the second harmonic load is capacitive (inductive). For our design we choose capacitive fundamental load and inductive 2<sup>nd</sup> harmonic load. The reason is we have an output capacitor of the device. If we choose inductive fundamental load, it should be more inductive for output capacitance compensation consideration. The fundamental load may be very near the edge of the Smith chart. It's not convenient for our design.

The equation to calculate the fundamental harmonic load is:

$$Z_{fund} = \frac{V_{DD}^2}{\sqrt{2} \times P_{peak}} \angle -\frac{\pi}{4} = \frac{30^2}{\sqrt{2} \times 12} \times (\cos(-\frac{\pi}{4}) + \sin(-\frac{\pi}{4})) = 37.5(1-j)$$

(8)

When it's normalized to 30 Ohms, it's 1.25\*(1-j).

$$Y_{fund} = \frac{1}{Z_{fund}} = 0.4 + j0.4 \tag{9}$$

The output parasitical capacitor is around 2.5 pF at 30 supply voltage. It's j\*0.034 S at 2.14 GHz, and j\*1 S when normalized to 30 Ohms.

Thus, the fundamental harmonic load on the Smith chart should be:

0.4+j\*0.4-j\*1=0.4-j\*0.6 S. (normalized to 30 Ohms) (10) And the second harmonic load is:

$$Z \sec ond = \frac{3\pi \times V_{DD^2}}{16P_{peak}} \angle \frac{\pi}{2} = j44.2Ohms$$

(11)

$$Y_{\text{sec ond}} = \frac{1}{Z_{\text{sec ond}}} = -j0.0226S \tag{12}$$

When it's normalized to 30 Ohms, it's -j\*0.68 S.

The output parasitical capacitor is around 2.5 pF at 30 supply voltage. It's j\*0.068 S at 4.28 GHz, and j\*2 S when normalized to 30 Ohms.

Thus, the second harmonic load on the Smith chart should be:

-j\*0.68-j\*2=j\*2.68 S (normalized to 30 Ohms) (13)

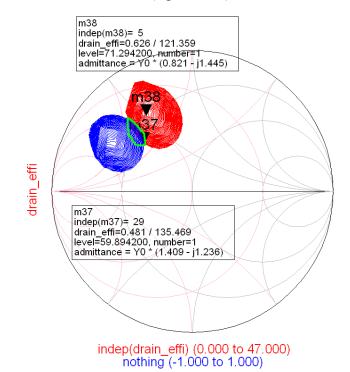

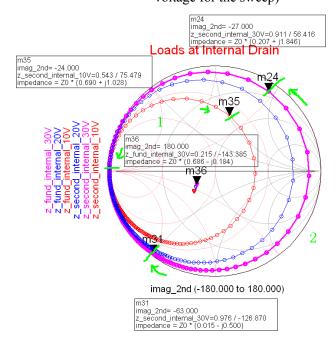

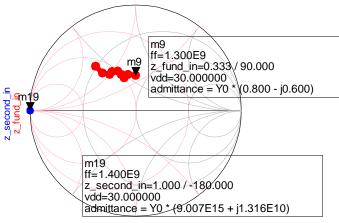

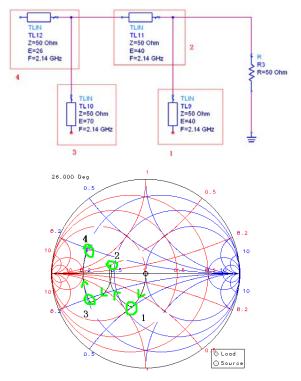

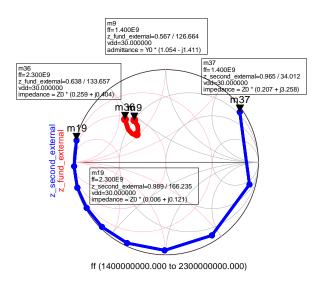

4. Load-pull simulation: Now, we have three variables: real and imaginary part of fundamental harmonic load and imaginary part of second harmonic load (the second harmonic load should be a pure reactance to minimize the loss at second harmonic load). We choose a second harmonic load value and do the load-pull simulations for fundamental load (figure 3.15).

Figure 3.15 High efficiency region by load-pull. (the Smith chart is normalized to 30 Ohms. Red, high efficiency region for fundamental load. Blue, second harmonic load)

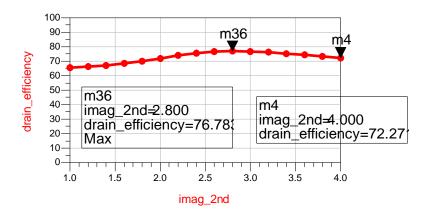

5. From figure 3.15 and based on the estimation of fundamental harmonic load, we choose 0.4-j\*1 S (normalized to 30 Ohms) as our fundamental harmonic load. And then, we sweep the second harmonic load (Figure 3.16).

Figure 3.16 Sweep second harmonic loads (the second harmonic reactance is normalized to 30 Ohms)

6. We choose the optimum load for second harmonic we repeat step 4 and 5 twice or three times, we can find the optimum loads for both fundamental and second harmonic.

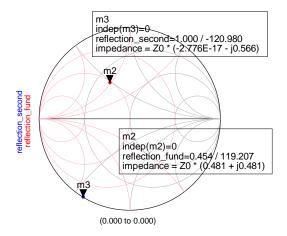

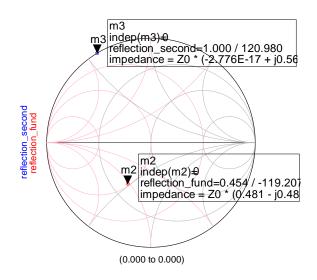

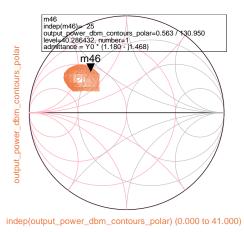

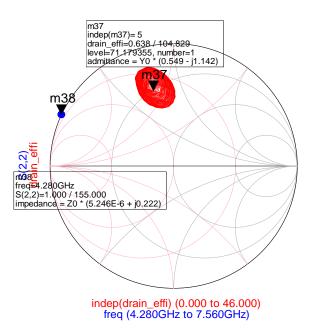

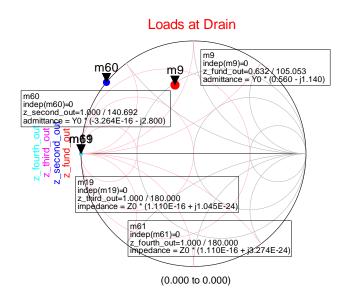

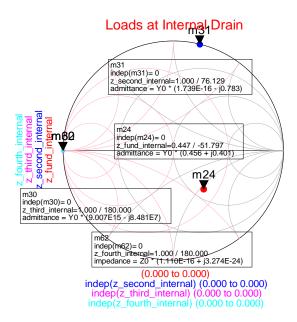

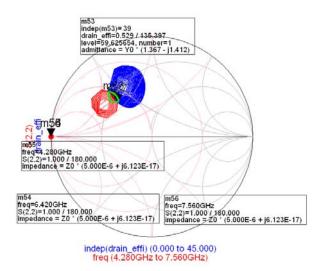

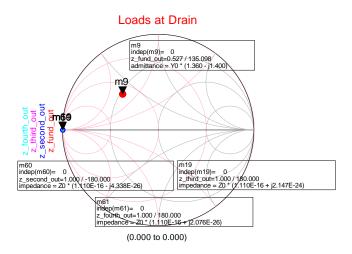

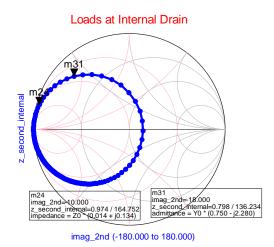

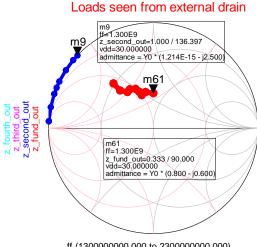

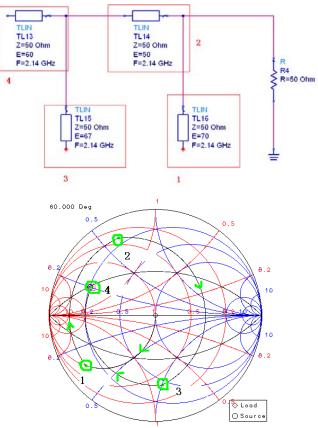

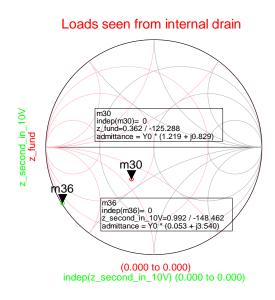

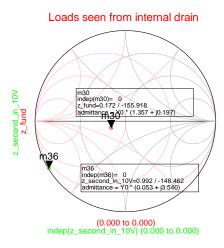

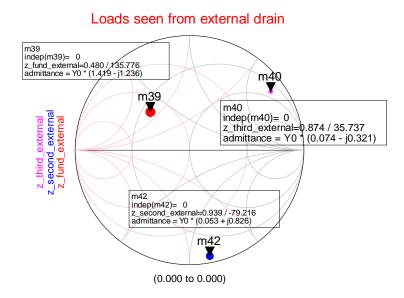

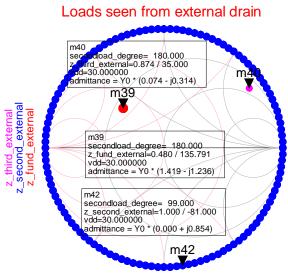

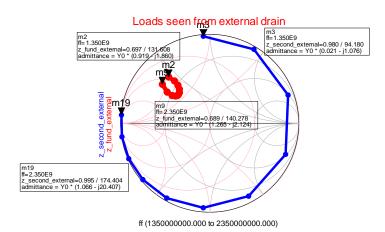

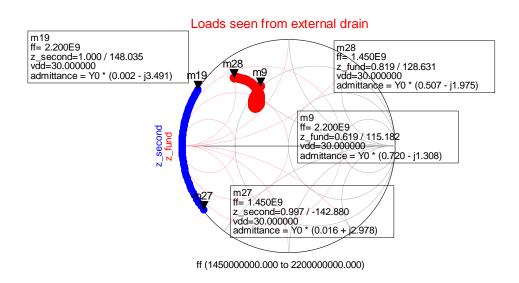

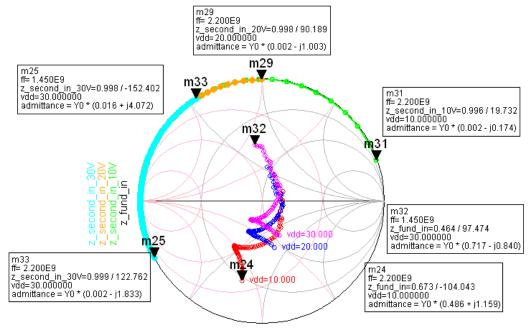

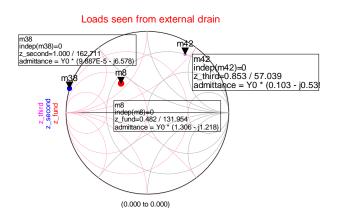

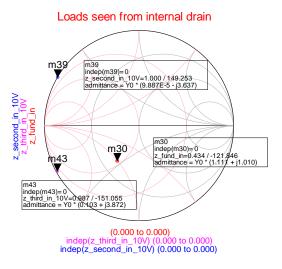

The optimum load condition of class-J operation for 30 V supply voltage: (Figure 3.17):

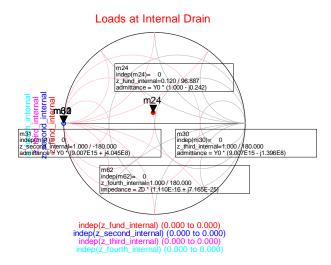

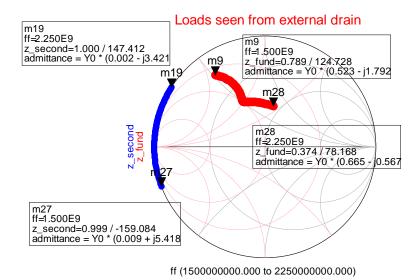

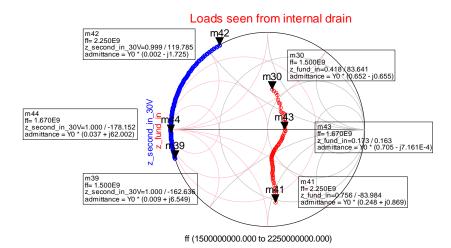

Figure 3.17 (a) Optimum loads for 2.14 GHz, 30 V supply voltage class-J power amplifier (normalized to 30 Ohms, seen from external drain)

Figure 3.17 (b) Optimum loads for 2.14 GHz, 30 V supply voltage class-J power amplifier (normalized to 30 Ohms, seen from internal drain)

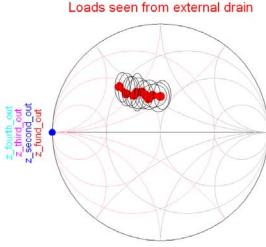

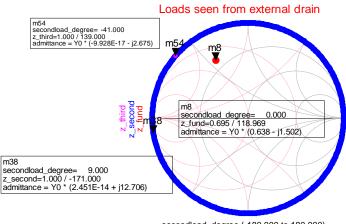

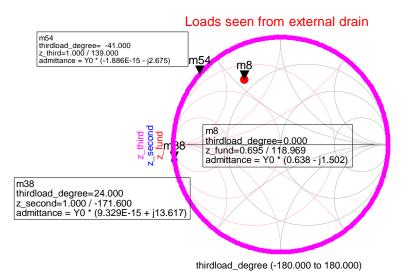

The load seen from external drain:

Fundamental load: 0.56-j\*1.14 S (normalized to 30 Ohms, the same for the follows) Second harmonic load: -j\*2.8 S

The load seen from internal drain: Fundamental harmonic load: 0.46+j\*0.4 S Second harmonic load: -j\*0.78 S These two values are very close to the values we estimate from the equations.

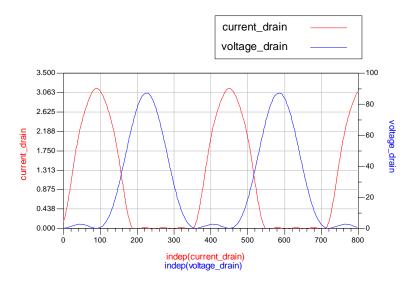

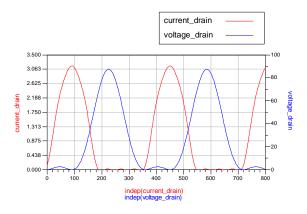

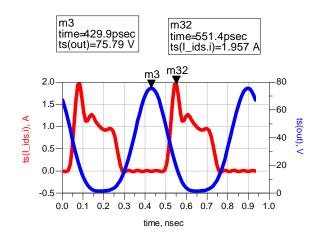

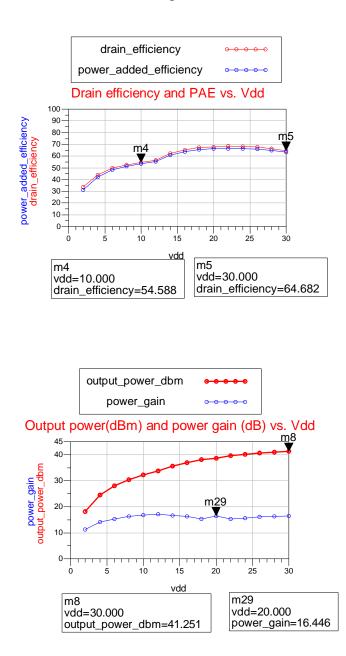

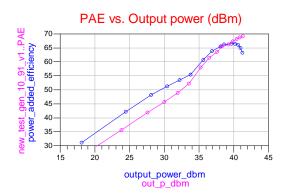

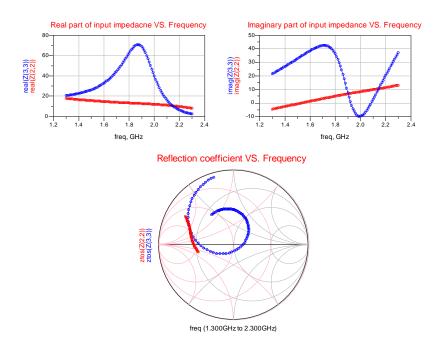

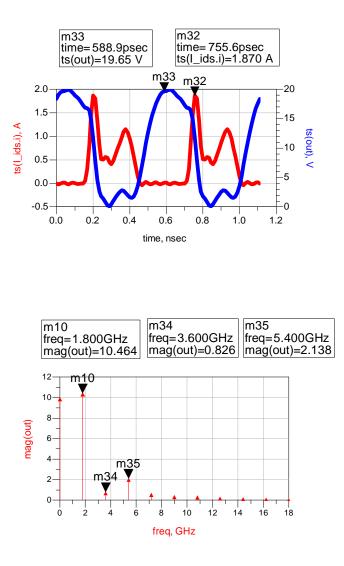

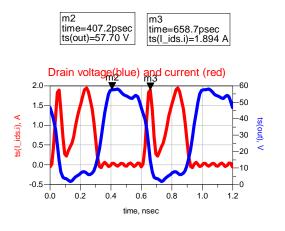

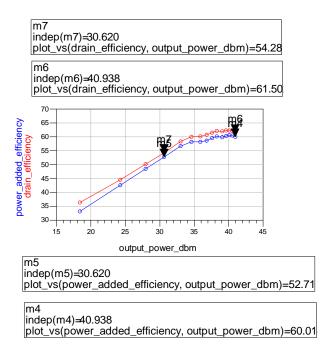

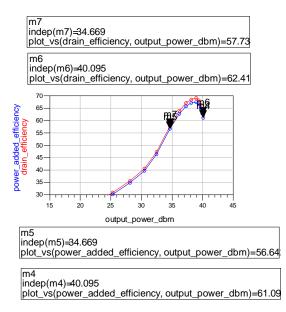

The other simulation parameters are the same as those of class- AB/B operation. The simulation results (Figure 3.18):

| drain_efficiency | power_added_efficiency | output_power_dbm | power_gain |

|------------------|------------------------|------------------|------------|

| 77.282           | 76.291                 | 41.089           | 18.923     |

|                  |                        |                  |            |

|                  |                        |                  |            |

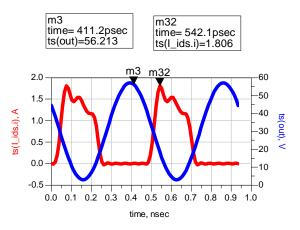

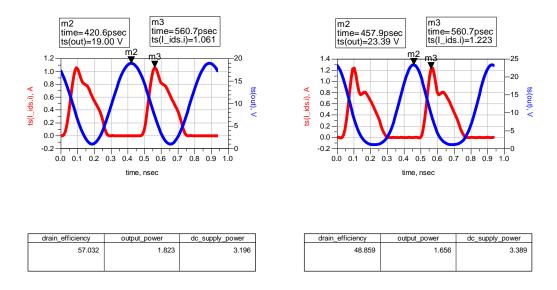

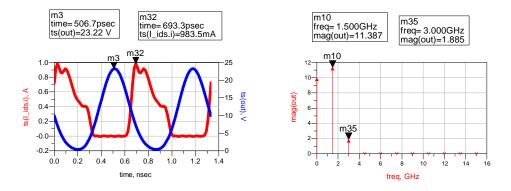

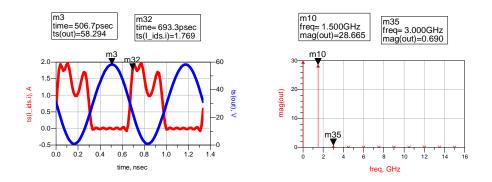

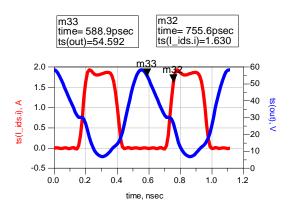

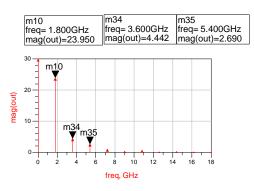

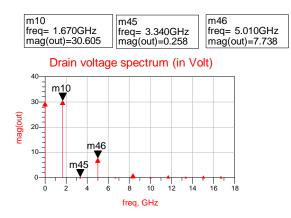

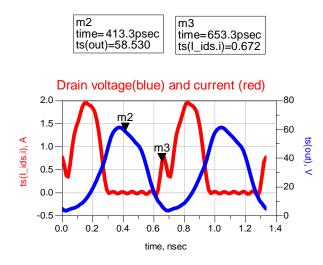

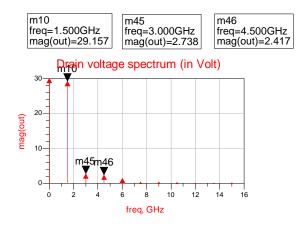

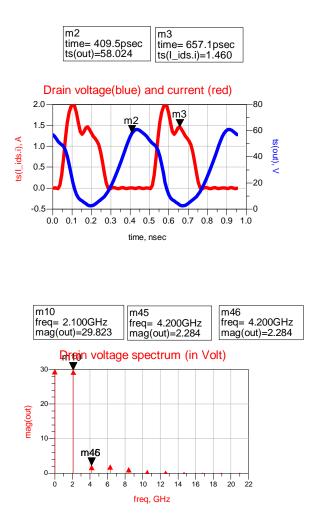

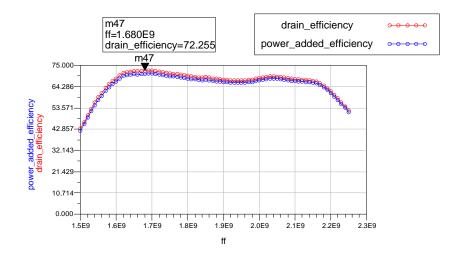

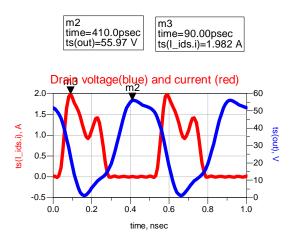

Figure 3.18 Simulation results of load condition in figure 3.17. Upper graph, blue and red represents drain voltage and current respectively.

For class-J operation, the drain efficiency rises to 77.3%. The gain is 18.9 dB (all other test conditions are the same except the load condition compared with class-AB/B). We see from figure 3.18, the drain voltage waveform is more flat at lower drain voltage compared with class-AB/B and its peak is more shaper. But, we also notice that the peak drain voltage is 75.8 V, which is much higher than the drain breakdown voltage (65 V). This is a restriction for class-J.

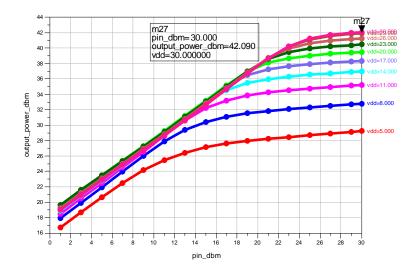

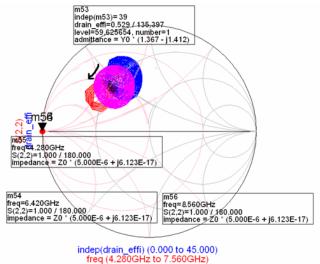

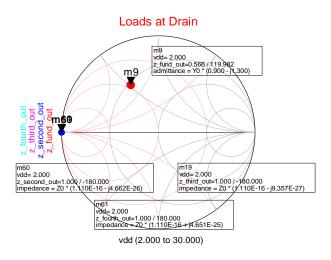

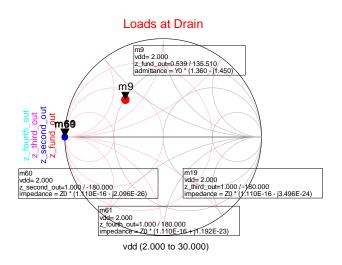

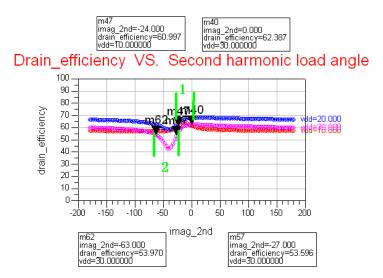

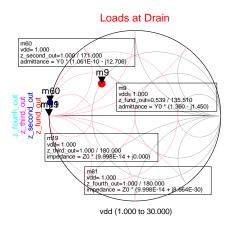

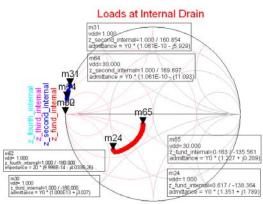

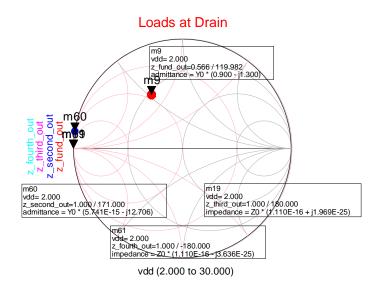

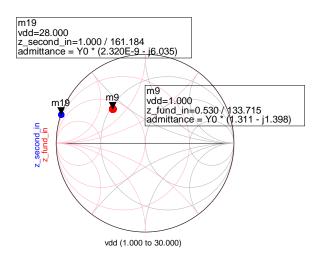

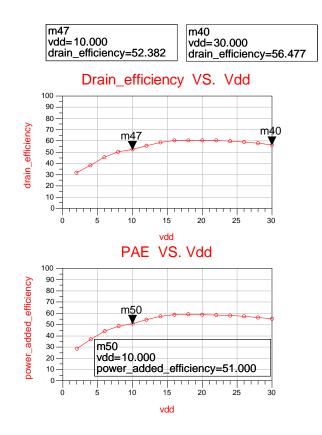

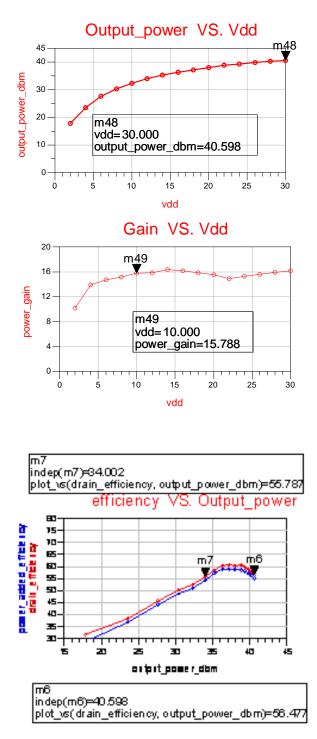

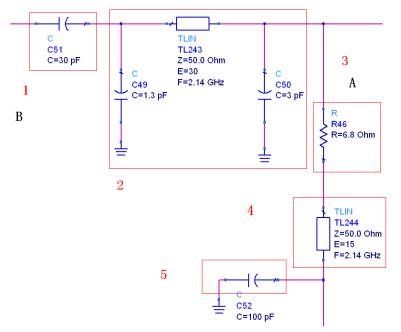

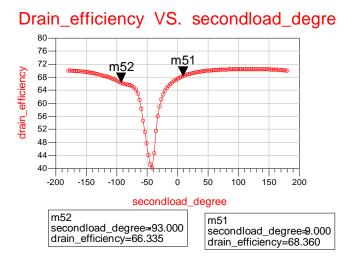

Hybrid-class PA for varying supply voltage: The class-J operation can provide higher efficiency with this LDMOS but it has a risk of exceeding the breakdown voltage at higher supply voltages. If we can use class-J operation at lower supply voltage and class-AB/B at higher supply voltage, we can increase the efficiency at power back-off and don't exceed the breakdown voltage at higher supply voltage. In chapter 2, we have discussed that when the ratio of amplitudes for second and fundamental component of drain voltage is less than 1/10, the drain voltage waveform is almost like a class-AB/B waveform. When this ratio rises to 1/3, the drain voltage waveform becomes like a class-J waveform. So, we can choose the second harmonic load to tune this ratio at lower and higher supply voltages so that the power amplifier operates at class-J at lower supply voltage and class-AB/B at higher supply voltage. This is the main idea of hybrid-class power amplifier.

# Section 3 Optimizing load condition for efficiency at power back-off:

As we have mentioned previously, in WCDMA system, the power amplifier often operates 6 dB or more from the peak power. So, in this section we try to find the optimum load condition for average efficiency (according to the PDF of WCDMA signal, appendix 1).