# Mitigation of Voltage Sags in Industrial Power Plants with Medium Voltage DC Distribution System

M.Sc. Thesis

## Michella Weverink

Department of Electrical Power Processing Delft University of Technology

February 2009

Author: Michella Weverink Supervisors: S.W.H de Haan (TUD)

> J. Langedijk (Siemens) R.L. Hendriks (TUD)

## **ABSTRACT**

Unplanned downtime in industrial power systems causes high loss of revenues. These downtimes are often caused by voltage sags of durations up to 1 s. Currently many systems exist which can help to mitigate these voltage sags such as Dynamic Voltage Restorer, UPS and FACTS based devices. With the recent development in semiconductors the voltage-source-converter based high-voltage direct-current (VSC-HVDC) system has also become feasible to deal with power quality problems. With the Siemens Multifunctional Power Link (SIPLINK) also industrial customers can benefit from the advantages of the VSC technology. These benefits are due to the VSC making use of pulse width modulation (PWM) and are amongst others short circuit reduction and independent control of active and reactive power.

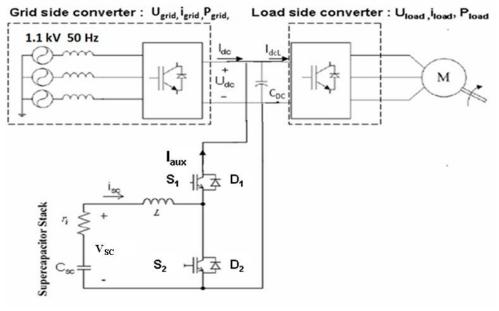

In this thesis the applicability of SIPLINK to mitigate voltage sags in an industrial power system is studied. Two different solutions are researched which make use of the VSC technology. One solution is based on the current rating of the converters such that the converter can continue to extract nominal power from the grid in an undervoltage situation. This method is called overrating of the system. The other is based on an auxiliary supply containing supercapacitors to replenish the grid power that is reduced during undervoltage. The research is carried on in Matlab/Simulink making use of the SimPowerSystems package. An industrial grid with three medium voltage induction motors serves as a base case for these two solutions. The important parameter to be monitored will be the speed of the motors during a sag with and without mitigation of any form.

To simulate the applicability of an overrated SIPLINK to mitigate sags a symmetrical voltage sag of 45% (i.e. 55% remaining voltage) is applied to the grid that lasts 50 ms and another that lasts 1 s. The results will show that an 80% overrated converter is enough to mitigate these sags. To test the applicability of sag mitigation by supercapacitor, symmetrical voltage sags of 90% and 10% are applied to the grid each lasting 50 ms and 1 s. The results will show that fast mitigation can be accomplished this way.

Keywords: VSC-HVDC, vector controller, voltage sags, supercapacitor

## **ACKNOWLEDGEMENT**

This research work was carried out at the Faculty of Electrical Engineering Mathematics and Computer Sciences with the Electrical Power Processing department of Delft University of Technology.

First I would like to express my sincere appreciation to Jan Langedijk, my supervisor from Siemens, for allowing me to do my master thesis research with the Siemens company under his and the other qualified Siemens' experts guidance. Thanks to this opportunity I have been able to experience the different aspects of engineering. A special thanks goes to Siemens Erlangen engineers dr. Juergen Möser and Andreja Rasic for their tremendous help.

My deepest gratitude goes to associate professor Sjoerd de Haan and PhD. student Ralph Hendriks, my supervisors at the university for their guidance during the research.

I would also like to thank John Meijers and Peter Kleijnen for supplying me with information from their company EdeA to use for a case study.

I gratefully acknowledge my colleagues and friends at the Department of Power Engineering and Telecommunications for making such a productive work environment.

Last but not least, I would like to thank my beloved John and my family for their constant love and support.

# **Table of contents**

|    |       | CT                                                               |      |

|----|-------|------------------------------------------------------------------|------|

| A  |       | WLEDGEMENT                                                       |      |

| 1. |       | duction                                                          |      |

|    | 1.1   | Background                                                       |      |

|    | 1.2   | Objective of the thesis and method of approach                   | . 10 |

|    | 1.3   | Sags investigated                                                |      |

|    | 1.4   | Existing solutions for sag mitigation                            | . 12 |

|    | 1.5   | Case Study: The Industrial Network                               | . 16 |

|    | 1.5.1 | The actual network                                               | . 16 |

|    | 1.5.2 | The Simulink SimPowerSystems model                               | . 18 |

|    | 1.6   | Medium Voltage Direct Current                                    | . 18 |

|    | 1.6.1 | Introduction                                                     | . 18 |

|    | 1.6.2 | VSC-HVDC System Description                                      | . 18 |

|    | 1.6.3 | Proposed MVDC Enhanced Industrial Network                        | . 21 |

|    | 1.7   | Mitigation systems concept                                       | . 22 |

|    | 1.7.1 | Global Power Balance                                             | . 22 |

|    | 1.7.2 | Converter overrating                                             | . 23 |

|    | 1.7.3 | B Auxiliary supply                                               | . 24 |

|    | 1.8   | Thesis Outline                                                   | . 25 |

| 2. | Qua   | ntitative analysis of EdeA industrial plant                      | . 27 |

| 3. | Stora | age Methods for Energy Compensation                              | . 31 |

|    | 3.1   | Storage Devices                                                  | . 31 |

|    | 3.2   | Comparison and conclusion of energy storage technologies         | . 35 |

| 4. | Ope   | ration of VSC-HVDC and Siemens Multifunctional Power Link Design | . 37 |

|    | 4.1   | Operation of VSC- HVDC                                           | . 37 |

|    | 4.2   | Design of DC capacitor                                           |      |

|    | 4.3   | Control system of the VSC- MVDC                                  | . 40 |

|    | 4.3.1 | The inner current controller                                     | . 41 |

|    | 4.3.2 | The outer controllers                                            | . 45 |

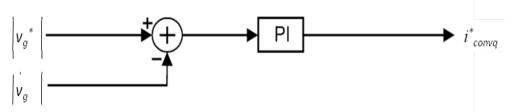

|    | 4.4   | Siemens Multifunctional Power Link (SIPLINK)                     | . 48 |

|    | 4.4.1 | SIPLINK System Design                                            | . 48 |

|    | 4.4.2 | 2 SIPLINK System Control                                         | . 49 |

|    | 4.4.3 | SIPLINK configurations for industrial power grids                | . 50 |

|    | 4.4.4 | SIPLINK SimPowerSystems Model                                    | . 53 |

| 5. | Supe  | ercapacitor Interfacing                                          |      |

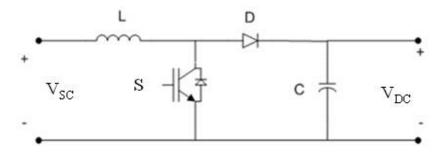

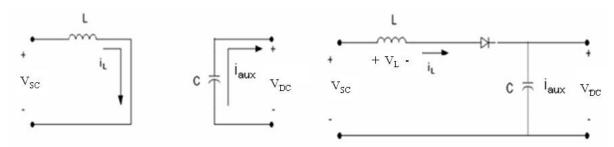

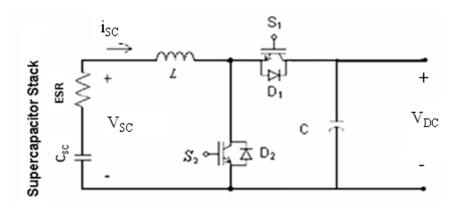

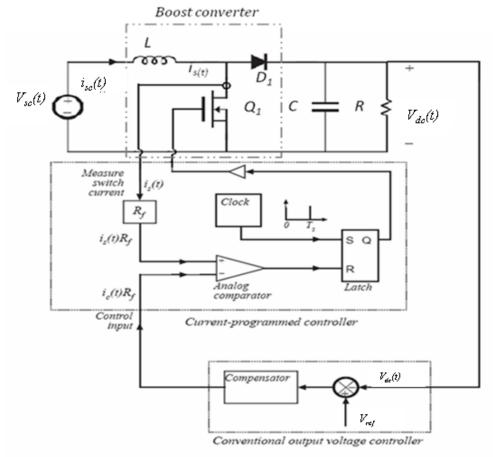

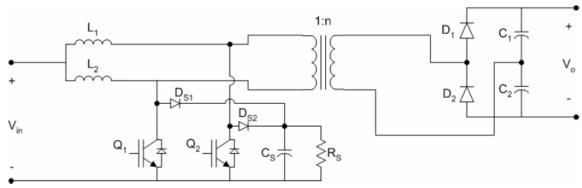

|    | 5.1   | Bidirectional boost converter topology                           | . 57 |

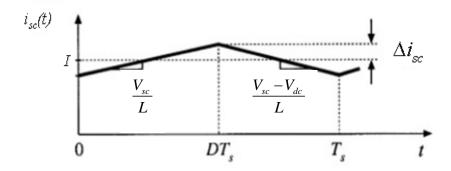

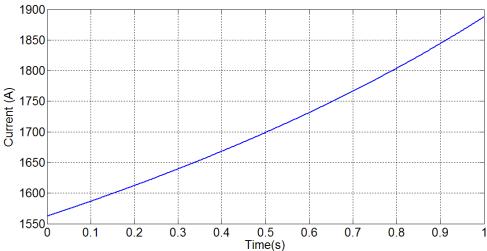

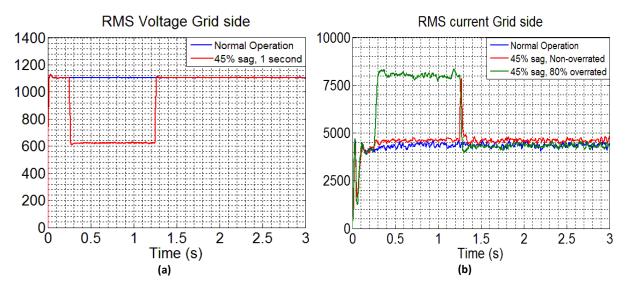

|    | 5.2   | Boost converter Inductor Design                                  |      |

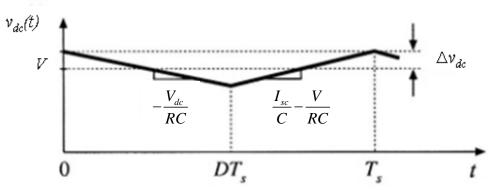

|    | 5.3   | Boost converter Output Capacitor Design                          | . 62 |

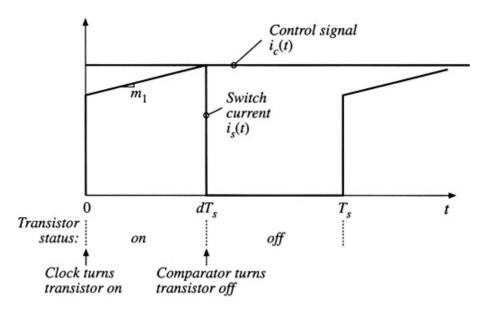

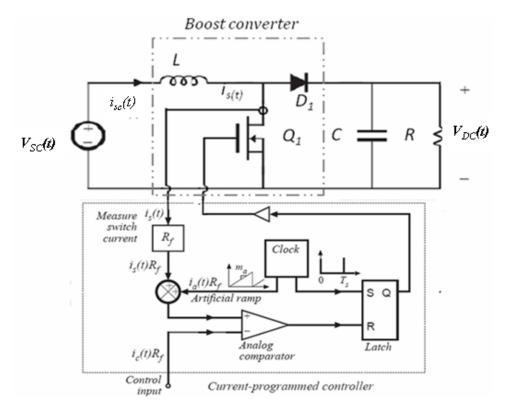

|    | 5.4   | Boost converter Current mode controller design                   |      |

|    | 5.4.1 |                                                                  |      |

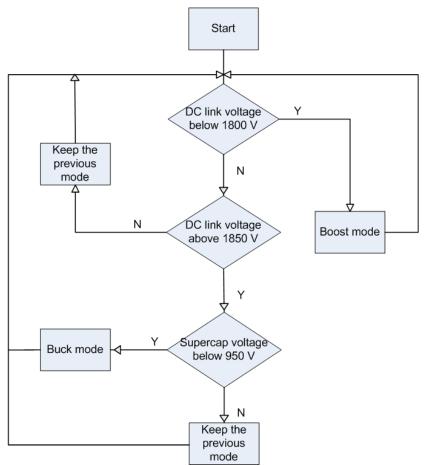

|    | 5.5   | Buck Mode or supercapacitor charging                             | . 68 |

|    | 5.6   | Supercapacitor sizing                                            |      |

|    | 5.7   | Control of supercapacitor based voltage sag mitigation system    |      |

| 6. | Case  | study for voltage sag mitigation solutions                       | . 73 |

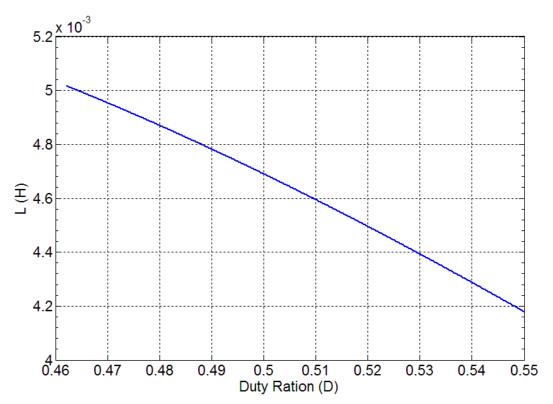

|    | 6.1   | Mitigation by overrated SIPLINK                                  |      |

|    | 6.2   | Mitigation by supercapacitor enhanced SIPLINK                    |      |

|    | 6.2.1 | $\iota$ $\iota$ $\iota$                                          |      |

|    | 6.2.2 | Inductor calculation                                             | . 78 |

|    | 6.2.3 | Slope compensation                                               | . 80 |

| 7. Results Voltage Sag Mitigation Solutions                              | 81  |

|--------------------------------------------------------------------------|-----|

| 7.1 Results Sag Mitigation by Overrated SIPLINK                          | 82  |

| 7.2 Results Sag Mitigation by supercapacitor                             | 88  |

| 8. Economical and Implementation aspects of SIPLINK with Boost Converter |     |

| Compensation                                                             | 97  |

| 9. Summary and Recommendation                                            |     |

| 9.1 Summary                                                              | 99  |

| 9.1.1 Mitigation by converter overrating                                 | 99  |

| 9.1.2 Mitigation by supercapacitor based auxiliary supply                | 100 |

| 9.2 Recommendation                                                       |     |

| REFERENCE                                                                | 103 |

| Appendix A. Motor and Transformer parameters                             | 105 |

|                                                                          |     |

## 1. Introduction

## 1.1 Background

Unplanned downtime of industrial plants can be costly due to loss of production. A part of the unplanned downtime is caused by interruption of the power supply. Absence of power can be one of the reasons; however their frequency of occurrence is relatively low. Mostly the problems are caused by voltage sags of relative short duration, in the order of hundreds of milliseconds. These plants go down for instance because control systems reboot or because drives are switched off by an undervoltage protection system.

Voltage sags are defined as a momentary decrease in the RMS voltage, with a duration ranging from half a cycle up to 1 minute. These sags are caused by fault conditions within the power plant or power system, and last until the fault is cleared by a fuse or breaker. Typical causes for voltage sags on the utility side are lightning, wind, contamination of insulators, animals or accidents [1]. Also failures in the plant or the start up of large motors may lead to a sag. "The depth of the event that is seen by the industrial customer is determined by the magnitude of the fault current, stiffness of the grid, and how close the customer's facility is to the site of the fault. The duration of the event is related to the breaker-clearing time on the utility system."[2]

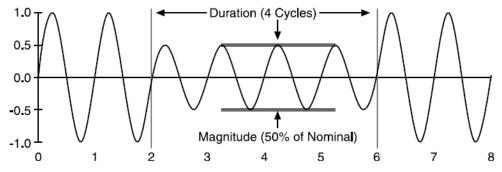

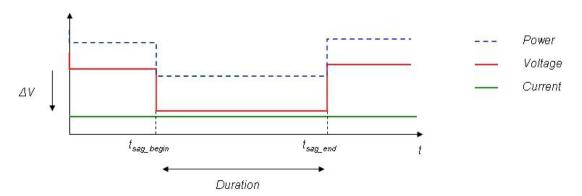

Because of their origin, the sags themselves are hard to avoid. However, avoiding these sags to penetrate to the plants could help to keep the plants alive during the sag and to reduce the unplanned down time. Typical sags are defined in terms of duration and magnitude (see Figure 1.1).

Figure 1.1: Voltage sags are described by Magnitude and Duration[2]

Industrial plants with great sensitivity to voltage sags and other power quality problems can choose from a variety of power-electronic solutions. An Uninterruptible Power Supply (UPS) can provide ride through capability against voltage interruptions and sags, depending on the storage capacity of the battery block, for several minutes or even hours. A Dynamic Voltage Restorer (DVR) can alleviate a range of dynamic power quality problems such as voltage sags and swells[3]. A static synchronous compensator (STATCOM) has the ability to either generate or absorb reactive power at a faster rate than classical solutions. This allows for the mitigation of flicker and alleviation of stability problems[3]. Application of a high voltage direct current (HVDC) system based on Insulated Gate Bipolar Transistors (IGBTs) (so called VSC-HVDC) could possibly also provide a solution. HVDC transmission is based on high power electronics and uses semiconductor technology to transport energy over long distances and also for the connection of non-synchronized grids. For a long time classic HVDC, which makes use of thyristors has been used. With newly developed semiconductors and control

equipment HVDC based on voltage source converters (VSCs) is now possible. This VSC-HVDC which is commercially available through the name HVDC Light[4] or HVDC<sup>PLUS</sup> [5], is based on IGBTs and several commercial projects are already in operation. For medium voltage grids, Siemens' SIPLINK which is also based on VSCs is available on the market and can be considered when searching for a solution for power quality problems. With HVDC the AC voltage at the load side is isolated from the voltage at the supplying AC grid. Therefore the use of DC links can possibly provide new solutions to power quality related problems in industrial systems.

## 1.2 Objective of the thesis and method of approach

This master project focuses on how systems like SIPLINK can offer a solution for mitigation of voltage sags for industrial plants due to their ability to isolate the instantaneous power flow in the power grid from the power flow to the load. To achieve this task the use of computer simulations is needed. These computer simulations are made with Matlab/Simulink.

The objective is to investigate the applicability of an MVDC system that is equipped with proper ride through capabilities, in an industrial grid to solve power quality problems. In particular the mitigation of voltage sags is researched. To test the theories presented in this thesis a case study is done where the solutions for voltage sag mitigation with MVDC is tested. The case study involves modeling of the system which is carried on in three steps.

First a model for an industrial grid is needed. An industrial grid is a grid which contains several medium voltage levels each connected through transformers. The grid should supply several industrial size (several hundreds VA) motors with or without their corresponding drives. These motors can be a combination of induction and/or synchronous motors but mainly induction motors. A Simulink model is made of the industrial plant. This model will be used to verify the performance of the motors under a voltage sag with and without voltage sag compensation based on Siemens' SIPLINK and is the basis for the case study.

Second a model of SIPLINK is made in Simulink. This model is adapted from a model made by Siemens engineers in Erlangen, Germany. The adaptations include setting the proper voltage levels to be used, setting the controls of the system and upgrading the model to have higher power handling capabilities which coincide with the power from the industrial plant from the case study.

Third two methods for mitigation of voltage sags with an MVDC system are researched. The first method will determine how overrating of the MVDC system to handle higher currents can help mitigate sags. Second a method using an auxiliary supply in combination with a storage device is investigated. For the second method also a Simulink model will need to be derived and the performance tested in combination with the MVDC system and the industrial power plant under a voltage sag.

Based on a case study involving the model for the industrial grid and the SIPLINK model, the answer for the question of whether or not the two methods described in step 3 are possible solutions for the mitigation of a voltage sag in an industrial plant should be given.

## 1.3 Sags investigated

As mentioned before there are many causes to voltage sags in a power system. These causes are difficult to eliminate but nonetheless the effects can be great. Equipment mal-operation due to voltage sags and other disturbances can lead to high costs. An interrupted automotive assembly line cost one U.S. manufacturer \$250000 a month until it was corrected. Interruptions to semiconductor hatch processing cost \$30000 - \$1 million per incident[3]. There are endless combinations of sag duration and magnitudes possible. This paragraph is dedicated to defining the types of sags that will be investigated. A voltage sag coming from the supplying high voltage AC network will be investigated. For the duration of the sag a survey done by UNIPEDE was consulted.

The Distribution Study Committee of UNIPEDE appointed a group of experts, DISDIP, to improve the knowledge of the rates of occurrence and severity of voltage dips and short interruptions in public electricity supply networks. This group arranged a coordinated series of measurements in nine countries (Austria, France, Italy, Netherlands, Norway, Sweden, Switzerland, United Kingdom, and Germany) which provide statistical information based on over 80 system-years of monitoring experience covering a wide range of environmental and geographical conditions.

The measurements were performed at 85 sites on medium voltage networks. Of these, 33 sites were cable systems and 52 sites were mixed overhead-cable systems[2]. The results from the measurements are shown in Table 1.1. From this table it can be seen that the majority of the sags (57 %) have a remaining voltage magnitude of 70 - 90 % and have a duration of up to 1 second. 19 % of the sags occur between 40-70 % remaining voltage and have a duration of up to 1 second. Sags of 10-40 % remaining voltage occur 7 % of the time with a duration between 100 ms up to 1 second. Complete interruptions of up to 1 second occurred 10 % of the time. Sags above 1 second occur only 5 % of the time for all sag magnitudes.

| Remaining Voltage | <u>10-100</u> ms | $100\text{-}500\mathrm{ms}$ | 500 ms-1sec | 1-3sec | 3-20sec | 20-60 sec |

|-------------------|------------------|-----------------------------|-------------|--------|---------|-----------|

| 70-90%            | 27%              | 27%                         | 3%          | 1%     | 0%      | 0%        |

| 40-70%            | 3%               | 15%                         | 1%          | 0%     | 0%      | 0%        |

| 10-40%            | 0%               | 6%                          | 1%          | 0%     | 0%      | 0%        |

| 0% (Interruption) | 0%               | 3%                          | 7%          | 1%     | 1%      | 2%        |

Table 1.1: UNIPEDE DISDIP Survey, All Sites, Based on Events Per Site Per Year (84.6 total dip events per site per year between 10ms - 60 Sec)

From the above table a decision is made to design for the dimensioning of the sag compensation. Since most sags are under 1 second, this is chosen as the maximum sag duration. The most severe sag to be investigated will be 10 % remaining voltage for a duration of 1 second. Also the least severe, but more common sag of 90 % remaining voltage for 50 ms is investigated.

The sags enforced on the system are described in Table 1.2:

| Remaining Voltage | <b>Duration</b> (ms) |      |  |  |

|-------------------|----------------------|------|--|--|

| 90%               | 50                   | 1000 |  |  |

| 10%               | 50                   | 1000 |  |  |

Table 1.2: Voltage Sags enforced on industrial system

The results of the sags enforced on the industrial system and the performance of the total system with an overrated SIPLINK and a SIPLINK with an auxiliary supply will be presented and compared in this thesis.

## 1.4 Existing solutions for sag mitigation

Paragraph 1.1 mentioned a UPS, DVR, STATCOM and HVDC as possible solutions for the improvement of power quality related problems like voltage sags. Common sags are described in the previous paragraph. This paragraph briefly explains the principles of the abovementioned solutions.

## **Uninterruptible Power Supply (UPS)**

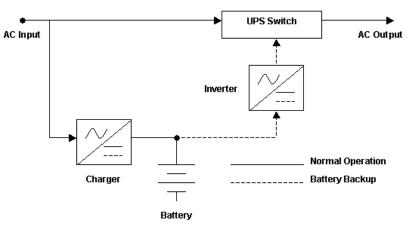

An uninterruptible power supply (UPS), is a device that maintains a continuous supply of electric power to connected equipment by supplying power from a separate source, most often a battery, when utility power is not available. It provides instant protection from a momentary power interruption and is often referred as an emergency power system. A UPS is typically used to protect computers, telecommunication equipment or other electrical equipment which are sensitive to power quality problems. UPS units come in sizes from a few hundred watts to several megawatts [6]. There are three types of UPS: off-line, line-interactive and double conversion or on-line. An off-line UPS remains in idle mode for most of the time and switches from utility power to its own power source almost instantaneously during a power failure, see Figure 1.3. In this figure the solid line represents the normal operation. Here the AC input feeds the load through an UPS switch which allows the load to be fed by normal AC or UPS power. The dashed line is the operation during a failure. The AC output is fed with power coming from the battery backup. The advantage of this topology is that it is low cost and lightweight. The disadvantages are the output voltage is not regulated, there is a transfer time or "dead" time when switching operating modes, there is no harmonic protection and the system does not protect against any other disturbances other than blackouts.

Figure 1.2: Simplified Off-line UPS[6]

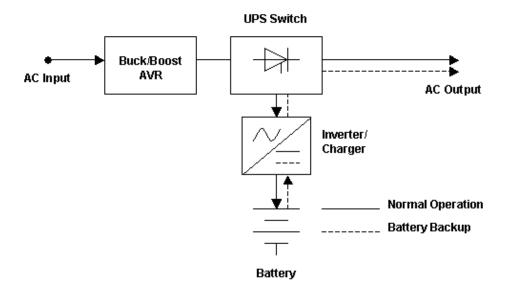

Figure 1.3: Simplified Line-Interactive UPS[6]

A line-interactive UPS is similar to an offline UPS but has a multi-tap variable-voltage autotransformer making it possible to tolerate sags and swells of the voltage without consuming the limited reserve battery power. An autotransformer is a one winding transformer in which the primary and secondary coils both have some or all of the windings in common. By changing to different power taps on the autotransformer the UPS is able to compensate for the occurring sags and swells. It does this by briefly switching to battery backup when a decrease in AC input is sensed. This is followed by the transformer tap switching and boosting the input and then turns the unit to off-line operation. During an overvoltage a similar response occurs but this time the AC is lowered. The advantages are the moderate costs, small and lightweight and it serves well during a brown-out operation. A disadvantage is the higher cost of the system.

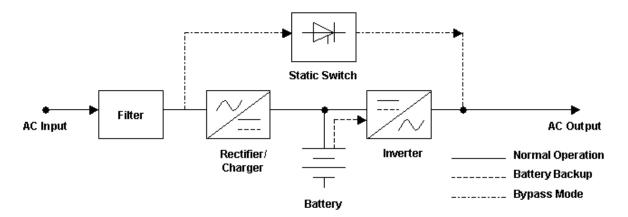

An on-line UPS continuously powers the load from its energy reserve which can be stored in a battery or flywheel. These reserves are simultaneously being recharged from the AC supply. An on-line UPS absorbs the incoming AC supply, the filter removes the harmonics. The signal is then converted to DC then inverted to AC to supply critical power loads. An inverter supplies regulated AC power to loads at all times; either from rectified mains or a battery with an on-line UPS. In the event of a blackout, there is no transfer time or break in power supply. This configuration provides protection against all common power problems and is therefore known as a power conditioner and a line conditioner.

Figure 1.4: Simplified On-line UPS[6]

The advantages from this system are a stable AC voltage and frequency without harmonics to load. There is no switching between AC and battery so there is no transfer time or "dead" time. The disadvantages are the higher costs and the complexity of the system.

#### **Dynamic Voltage Restorer (DVR)**

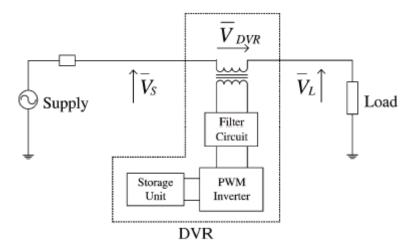

A Dynamic Voltage Restorer (DVR) is a series compensator. It is comprised of a voltage source inverter (VSI), an energy storage (i.e. battery) supplying real power, a controller that provides gating signals for VSI control, three single-phase injecting transformers, capacitors that filter out inverter switching harmonics in the battery current and LC filters that functions to filter out switching harmonics in the injecting voltages. "The purpose of injection transformers is to accurately couple an oscillator signal into a feedback loop with minimum distortion and/or capacitive coupling." [7] For this reason, the transformers have a low magnetizing current and flat coupling over the specified frequency ranges. In normal power supply condition the DVR can be seen as in idle state. During a voltage sag the controller produces an error signal to control the DVR in such a way that a comparable amount of voltage is injected in series to the secondary side of the distribution transformers via the injecting transformers. Figure 1.5 shows the general structure of the DVR.

Figure 1.5: DVR structure[8]

#### **STATCOM**

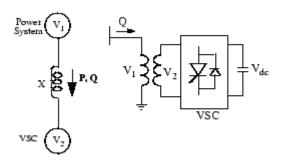

The STATCOM is a shunt device of the Flexible AC Transmission Systems (FACTS) family using power electronics. It regulates voltage by generating or absorbing reactive power. When system voltage is low, the STATCOM generates reactive power. When system voltage is high, it absorbs reactive power.

Variation of the reactive power is performed by means of a Voltage-Sourced Converter (VSC) connected on the secondary side of a coupling transformer. The principle of operation is described in Figure 1.6. The power and reactive power are given by equations (1.1) and (1.2) respectively.

$$P = \frac{V_1 V_2 \sin \delta}{X} \tag{1.1}$$

$$Q = \frac{V_1(V_1 - V_2 \cos \delta)}{X}$$

(1.2)

where

$V_1$  = line to line voltage of source  $V_1$

$V_2$  = line to line voltage  $V_2$

X = Reactance of interconnection transformers and filters

$\delta$  = angle of  $V_1$  with respect to  $V_2$

Figure 1.6: Operating principles of the STATCOM, adapted from [9]

In steady state operation the voltage  $V_2$  which is generated by the VSC is in phase with  $V_I$  i.e.  $\delta = 0$ . In this mode only reactive power is flowing since P = 0. If  $V_2$  is lower than  $V_I$ , reactive power Q is flowing from  $V_I$  to  $V_2$  thus the STATCOM is absorbing reactive power. If  $V_2$  is higher than  $V_I$ , Q is flowing from  $V_2$  to  $V_I$  making the STATCOM generate reactive power. The amount of reactive power during steady state operation. i.e.  $\delta = 0$  is given by

$$Q = \frac{V_1(V_1 - V_2)}{X} \tag{1.3}$$

Depending on the power rating of the STATCOM, different technologies are used for the power converter. High power STATCOMs (several hundreds of Mvars [9]) normally use GTO-based, square-wave voltage-sourced converters (VSC), while lower power STATCOMs (tens of Mvars) use IGBT-based (or IGCT-based) pulse-width modulation (PWM) VSC.

#### **High Voltage DC (HVDC)**

HVDC technology is a high power electronics technology that make it efficient to transmit large amounts of power over long distances in electric power systems. This can be done using transmission lines or underground/submarine cables. With HVDC it is also possible to interconnect systems with differing frequencies.

There are two types of HVDC systems. Classic HVDC technology makes use of thyristors, while the newer family of HVDC makes use of Insulated Gate Bipolar Transistors (IGBTs) in a voltage source converter (VSC) topology. HVDC technology consists of a rectifier and an inverter with a DC link in between. Pulse width modulation (PWM) is used to create any voltage desired. With HVDC it is possible to separate the grid from the load, thus making it possible to isolate faults originating from the grid from penetrating to the load. For research on how HVDC can improve power quality the author refers the reader to [3] and [10].

## 1.5 Case Study: The Industrial Network

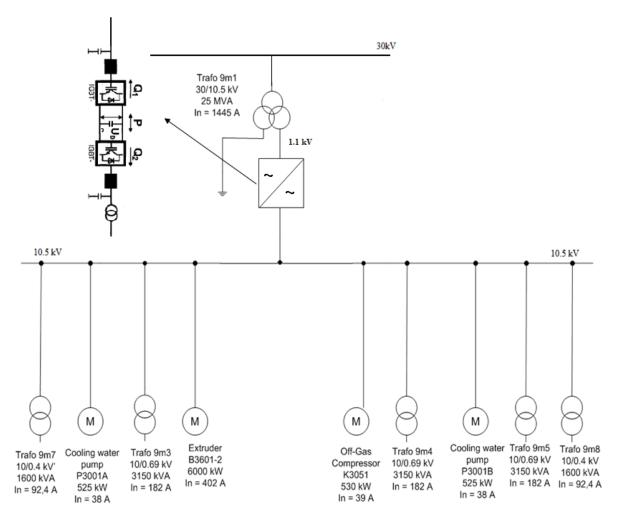

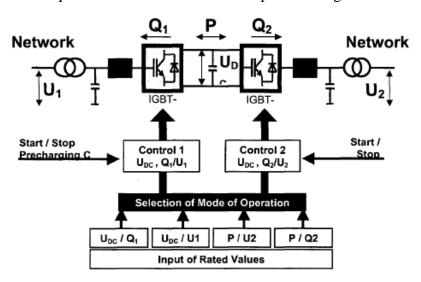

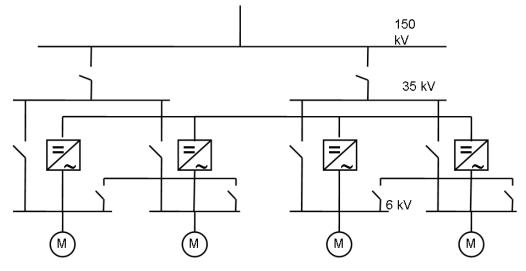

This paragraph deals with the specifications of the industrial grid which forms the basis for the case study. The industrial grid is needed to test the applicability of the sag mitigation solutions that are presented later on in this thesis. An industrial grid characterizes itself as having different levels of medium voltage, connected through transformers and having multiple motors. These motors can be synchronous or asynchronous (induction) motors. An example of this is the industrial grid from EdeA. EdeA is a company responsible for the exploitation of installations which produce steam, electricity and different kinds of water, air and technical gasses and distributes these to the plants of DSM and Sabic in Geleen. Substation PPF3 is part of the distribution network of Kerensheide and has different levels of medium voltage connected through transformers as well as several induction motors. It is for this reason that this substation is chosen to model an industrial grid and it will be used further in this thesis as the base case. Substation PPF3 is modeled in Matlab using Simulink with the SimPowerSystems toolbox.

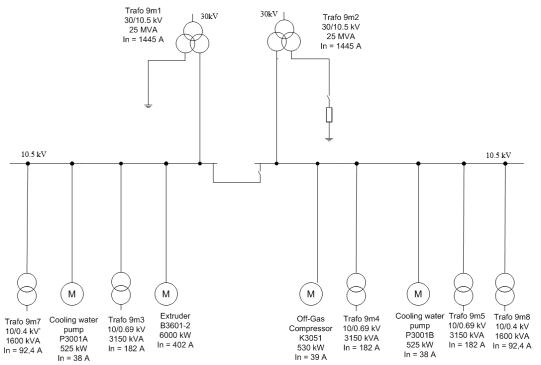

#### 1.5.1 The actual network

The network of Kerensheide starts at 150 kV which is provided by Essent B.V a utility company. It is then transformed down via 3 transformers, two of which are depicted in Figure 1.7, to 30 kV and then to 10 kV. A substation at 2 kV and one at 6 kV also exists. The substation PPF3 is connected to the 30 kV line via two three winding transformers 9m1 and 9m2. These transform the voltage down to 10 kV. At the 10 kV bus four asynchronous squirrel cage motors are directly connected, two for the use as cooling pumps, one as a compressor and one as an extruder. Also five transformers are connected. Three transform the voltage down to 0,69 kV and two to 0,4 kV. In Table 1.3 and Table 1.4 the data for the motors and transformers are summarized.

| Transform          | ners 150 | /30 kV  | Transformers 30/10 kV |         |         |         |

|--------------------|----------|---------|-----------------------|---------|---------|---------|

| Transf.            |          | 1 (2m1) | 2 (2m2)               | 3 (2m3) | 1 (9m1) | 2 (9m2) |

| $U_{prim}$         | [kV]     | 150,0   | 150,0                 | 150,0   | 30,0    | 30,0    |

| U <sub>sec</sub>   | [kV]     | 32,5    | 32,5                  | 32,5    | 10,5    | 10,5    |

| S <sub>rat</sub>   | [MVA]    | 70,0    | 70,0                  | 70,0    | 25,0    | 25,0    |

| U <sub>k</sub> rat |          | 14,28%  | 15,30%                | 14,28%  | 9,99%   | 10,06%  |

| Vector             |          | YNd7    | YNd7                  | YNd7    |         |         |

| group              |          |         |                       |         | YNyn0 d | YNyn0 d |

| Uworking           | [kV]     | 31,5    | 31,5                  | 31,5    | 31,5    | 31,5    |

Table 1.3: Transformers

| Name    | Motor        | P[MW] | U <sub>rat</sub> [V] | P <sub>n</sub> [MW] | I <sub>n</sub> [A] | I <sub>a</sub> [A] | $I_a/I_n$ | Remark |

|---------|--------------|-------|----------------------|---------------------|--------------------|--------------------|-----------|--------|

| K3501   | Compressor   | 0,530 | 10,000               | 0,530               | 39                 |                    |           | Active |

| B3601-2 | Extruder     | 6,000 | 10,000               | 6,000               | 402                | 1930               | 4,8       | Active |

| P3001A  | Cooling pump | 0,525 | 10,000               | 0,525               | 38                 |                    |           | 50% in |

| P3001B  | Cooling pump | 0,525 | 10,000               | 0,525               | 38                 |                    |           | 50% in |

Table 1.4: Motors

The low voltage transformers are summed together and result in  $S_{rat} = 12650 \text{ kVA}$  with  $U_k = 6 \%$ . Here  $S_{rat}$  is the rated apparent power and  $U_k$  is the short circuit voltage. Also the low voltage load equals a total of 3,2 MW of which 80 % is from motors and 20 % is ohmic. The total load of the system is  $P_{tot} = 10.78 \text{ MVA}$ . A schematic overview of substation PPF 3 is given in Figure 1.7.

Figure 1.7: Schematic overview of substation PPF 3 of the EdeA network

## 1.5.2 The Simulink SimPowerSystems model

In this paragraph the Simulink model made with the SimPowerSystems toolbox is presented. This model will later be used as a case study to research the effects of voltage sags with and without sag mitigation. The reason for using the SimPowerSystems toolbox is because many elements such as transformers, motors, breakers and power electronics are readily available in individual blocks. For the model it was decided to only take one of the 150/30 kV transformers and one 30/10 kV transformer, 2m1 and 9m1 respectively. This was done because these two transformers are large enough to support the entire load on PPF3 and by leaving the non relevant transformers out also calculation time is saved. For the Simulink dynamic model of the asynchronous motors also values for rotor and stator resistances and inductances were needed along with values for the inertia, pole pairs and friction factor. These values are mostly only provided by the manufacturer upon request and are not available in this case. For this reason approximations for these values were sought. The correctness of these approximations were determined by looking at speed current, torque and voltage characteristics and compared to the values from Table 1.4. The motor and transformer parameters can be found in Appendix A.

For the pumps a quadratic mechanical torque characteristic was assumed. This is the most common characteristic for a pump. For the other motors a constant mechanical torque was assumed.

For final modelling the motors with quadratic mechanical torque characteristics on the same bus are aggregated as one motor and the motors with constant mechanical torque also. This is done to reduce simulation time.

# 1.6 Medium Voltage Direct Current

#### 1.6.1 Introduction

This chapter presents general aspects of VSC-HVDC transmission. VSC-MVDC systems are based on the same principle but have lower power handling capabilities and lower voltages.

## 1.6.2 VSC-HVDC System Description

The classic HVDC, which makes use of thyristors is widely used all over the world. More recently a new type of HVDC has become available. It makes use of advanced semiconductor technology like Insulated Gate Bipolar Transistors (IGBTs) and Gate Turn-Off Thyristors (GTOs) for the conversion from AC to DC and vice versa. The converters are voltage source converters (VSCs) which operate with high switching frequencies (1-2kHz) utilizing pulse width modulation (PWM) [3]. Due to this use of PWM to create the desired waveform, it is possible to create any waveform, phase angle and magnitude of the fundamental frequency component.

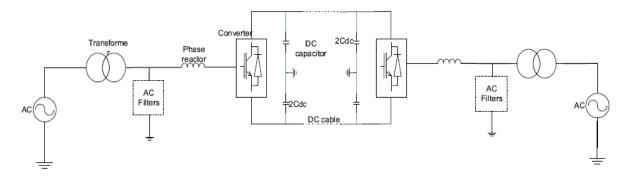

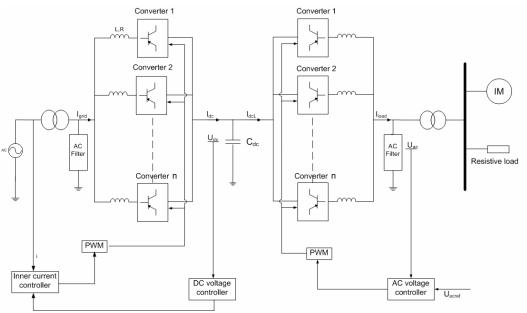

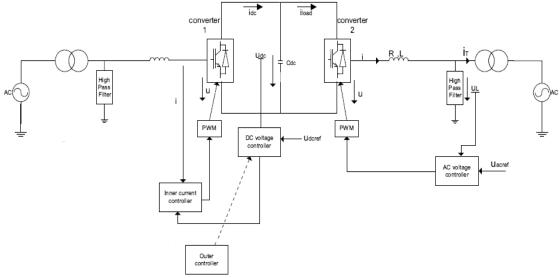

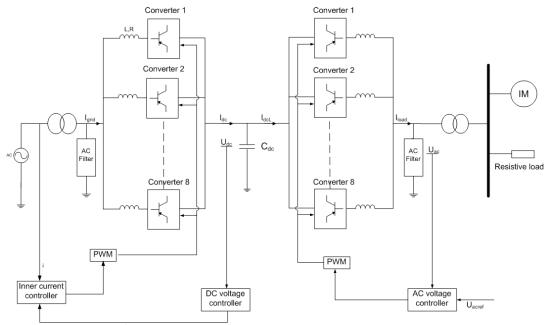

A typical VSC-HVDC system consists of, converters, transformers, phase reactors, AC filters, DC capacitors and DC cables. This is shown in Figure 1.8.

Figure 1.8: A VSC-HVDC system[10]

#### **Converters**

The converters are made with IGBT power semiconductors, one converter functions as a rectifier, the other as an inverter. The application of the VSC-HVDC system determines how the two converters are connected i.e. back to back or via a DC cable. Different rated powers can be achieved connecting the converters in series and parallel. The number of devices needed is determined by the rated power of the bridge and the power handling capabilities of the switching devices.

#### **Transformers**

Transformers are used to connect the converters to the AC system. They are responsible for providing the right voltage level to each converter. The leakage reactance of the transformer also acts as a phase reactor, used for the control of the active and reactive power. A good amount of harmonic filtering can also be achieved due to the reactors of the transformers.

#### **Phase reactors**

"The phase reactors are used for controlling both the active and reactive power flow by regulating currents through them"[3]. They also function as ac filters to filter out the harmonic contents of the AC currents which are caused by the switching action of the VSCs. The transformer leakage reactance together with the phase reactor allow the VSC output voltage to shift in phase and amplitude with respect to the AC system. Control of the converter active and reactive power output can be achieved in this manner.

#### **AC** filters

The switching action of the IGBTs produce ac voltages which contain high order harmonic components. These harmonic components need to be prevented from entering the ac system, causing malfunctioning of ac system equipment and/or radio and telecommunication systems. For this high-pass filters are needed. "With VSC converters there is no need to compensate any reactive power consumed by the converter itself and the current harmonics on the ac side are related directly to the PWM frequency" [10] . Usually second and third order filters are used for HVDC systems. These are shown in Figure 1.9.

Figure 1.9: Passive high pass filter. (a) Second-order filter (b) Third-order filter, from [10]

## **DC** capacitors

On the DC side there are capacitors, the size of these capacitors depends on the required DC voltage. During transients they act as an energy buffer to keep the power balance. The capacitors also reduce the voltage ripple on the DC side.

#### **DC** cables

The cables used in VSC-HVDC applications make use of insulation that is made up from extruded polymer. This material is resistant to DC voltage. "Polymeric cables are the preferred choice for HVDC, mainly because of their mechanical strength, flexibility, and low weight" [10].

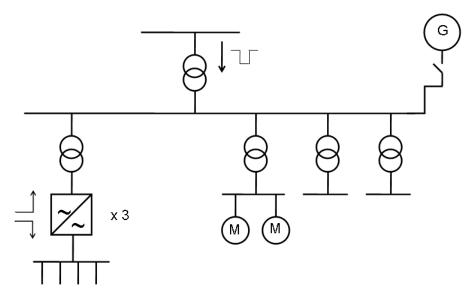

## 1.6.3 Proposed MVDC Enhanced Industrial Network

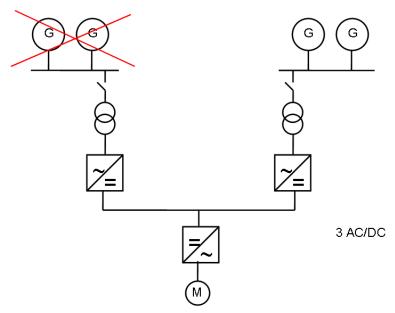

For the research of the mitigation concepts to be proposed, the interconnection of the industrial grid from Figure 1.7 and the MVDC system of Figure 1.8 as shown in Figure 1.10 is proposed. As shown in Figure 1.7 there are two transformers 9m1 and 9m2 in the substation, both of which can sustain the entire load alone in case of failure of one transformer. The reason for the two transformers is to add redundancy in the case of a failure. Also during the startup of the motors, high amounts of current need to be drawn from the grid often times surpassing the capability of one transformer. Thus both transformers are needed. From Figure 1.10 it follows that the 10.5 kV bus will be connected through two MVDC systems. This is the topology that will be simulated. It is assumed that the transformer 9m1 on site can generate the 1100 V needed for the converter terminals. Other topologies exist and are described in paragraph 4.4.3. For redundancy a second branch with a transformer and SIPLINK converter can be added. This topology was not simulated to save calculation time. The system is modelled to be able to withstand normal overloads which include starting up of motors one at a time.

Figure 1.10: Proposed MVDC enhanced industrial grid

## 1.7 Mitigation systems concept

As previously noted, a voltage sag involves a decrease in voltage magnitude for a very short period of time. With an unaltered current magnitude, this voltage sag then also implies a temporary decrease in the transferred power to the load. This temporary decrease can be disastrous for equipment as motors and computers in an industrial plant. In order to mitigate these voltage sags, extra power needs to be injected into the system. The system in this thesis is an industrial plant which is connected to the grid through a Medium Voltage DC Link specifically Siemens' Multifunctional Power Link or SIPLINK. The valves in the converter limit the short circuit current. Faults in the AC grid will not propagate to the load because of the use of these current limiting converters. This increases plant availability because the load side can be protected from the grid side. In this system however the load is not protected from short dips in the voltage. For cost and converter response reasons, the DC link capacitor is designed to be small. This is explained later in chapter 4. The DC link capacitor thus can provide a buffer for when there are transients in the system, but is not large enough to provide ride through capability in the event of a voltage sag with durations of over a few tens of milliseconds. In order to increase the power that is being transmitted to the DC link in the event of a voltage sag, two methods have been chosen. The first is the overrating of the SIPLINK system and the second is increasing the power by adding an extra auxiliary supply to the link. A global representation of the power balance as well as the mitigation methods is given next.

#### 1.7.1 Global Power Balance

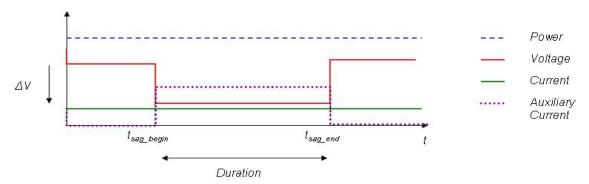

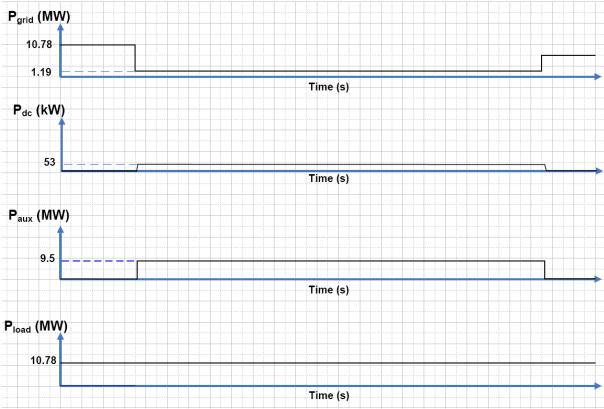

During a voltage sag, the voltage drops in magnitude as given in Figure 1.1. This causes a sag in the power magnitude according to the power equation P=VI. The power balance for this equation is shown in Figure 1.11, where all quantities represent the converter grid side components.

Figure 1.11: Power Balance during a voltage sag

In order to prevent equipment from malfunctioning, the power lost needs to be compensated for.

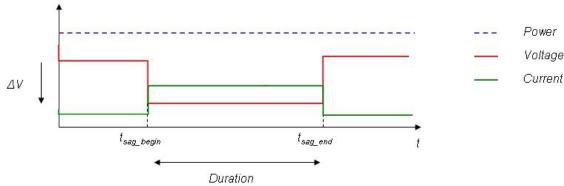

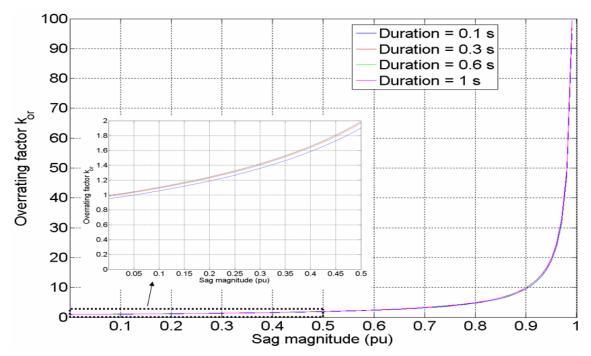

## 1.7.2 Converter overrating

By converter overrating it is meant that the grid current drawn by the converter is temporarily increased with respect to the load or working current in order to satisfy the equation P=VI, to maintain a constant power P. The power balance is then given by Figure 1.12.

Figure 1.12: Power Balance during overrating of converters

The increase of the grid current drawn by the converter can be done in two ways.

- 1. The converter can be operated below its rated or nominal current. In this case in the event of a voltage sag, the current can be increased up to its maximum constant current  $I_{conv,rat}$ .

- 2. More converters can be connected in parallel to increase the current handling capability of the total system as in Figure 1.13. In all cases the extra current is drawn from the grid which is assumed to have a large short circuit power. In both cases the overrating percentage determine the costs. This percentage is determined by (1.4).

$$k_{or} = \frac{I_{conv,rat}}{I_{load,rat}} \tag{1.4}$$

Where  $I_{conv,rat}$  is the nominal converter current and  $I_{load,rat}$  is the rated load current.

Figure 1.13: Overrating by addition of extra converters

## 1.7.3 Auxiliary supply

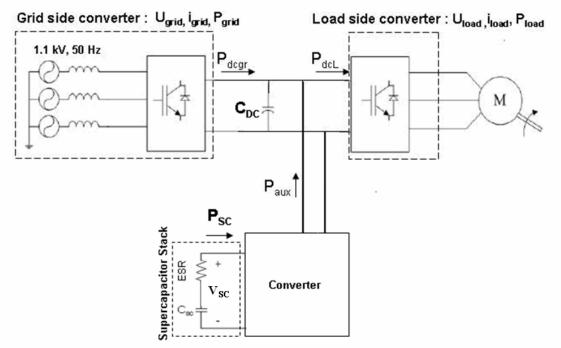

In this case mitigation of a voltage sag is done by stabilizing  $P_{dcL}$  (see Figure 1.15) during a voltage sag. Apart from increasing the operating current of the converter by drawing it from the grid, also extra current can be injected in the DC link through an auxiliary supply. The extra current comes from an extra storage device. In this case the power balance is represented by Figure 1.14.

Figure 1.14: Power Balance with Auxiliary supply

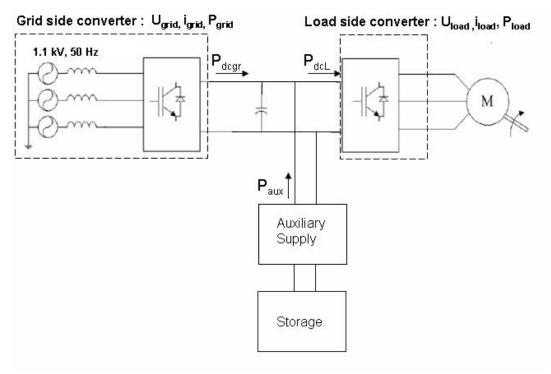

The representation of the system with the auxiliary supply is given in Figure 1.15.

Figure 1.15: MVDC system with auxiliary supply

The power balance for this configuration is given as

$$P_{dcL} = P_{dcgr} + P_{aux} (1.5)$$

From the power balance it can be seen that the power transmitted to the load i.e.  $P_{dcL}$  remains unaffected because of the injection of extra current from the auxiliary supply.

#### 1.8 Thesis Outline

Chapter 2 presents a quantitative analysis of the EdeA industrial plant. Actual values for power, voltage and currents will be given that will be used later in the research as a case study. Chapter 3 focuses on the different storage methods and a comparison is given.

Chapter 4 will give an overview of the VSC-HVDC technology. The structure and the control system will be described in detail. A mathematical model of the control system is presented. The Siemens Power Link (SIPLINK) model will be presented and discussed. Also the current SIPLINK technology and practical information of the system as well as applications for it are presented in this chapter.

Chapter 5 will present the theory behind the interfacing of the storage method chosen in chapter 3.

Chapter 6 presents the case study and actual values for the used elements are calculated. Also the results of computer calculations of voltage sag mitigation by converter overrating and auxiliary supply are presented.

Chapter 7 will give simulation results for the designed SIPLINK system and industrial plant with different sags applied. Mitigation of these sags by converter overrating and by auxiliary supply is analysed.

Chapter 8 presents an overview of the costs involved in applying such an MVDC system to prevent power quality problems.

Finally, a summary is given and some suggestions for future research are pointed out in Chapter 9.

# 2. Quantitative analysis of EdeA industrial plant

Voltage sags are one of the most common occurrences in industrial power distribution systems. Although the duration of typical sags is between 10 – 500 milliseconds, and the depth of the sag is usually lower than 30% of the rated voltage value, this disturbance can trip the protections of an adjustable speed drive or introduce brief speed fluctuations which may damage the final product. This can lead to losses in revenue. With a system like SIPLINK in an industrial grid it will be possible to make use of the benefits like linking to a neighbouring network in the event of a load expansion or infeed failure. See chapter 4.4.3 for examples of SIPLINK applications. However with the adjustments described in chapter 1.7 it will also be possible to protect the load from voltage sags originating in the higher level supply grids. This chapter deals with two possible solutions for voltage sag mitigation. The first is the overrating of the converters. Usually the converter load current is close to the converter rated current. In case of a voltage sag there will be limited capability for the converters to supply the power necessary to the loads. By increasing the current limit i.e. overrating the system, it enables the converter to draw more current from the grid to try to maintain the power level of the load. The current limit setting is an important parameter in the design of an industrial power grid with VSC-HVDC links. There are three important parameters to be considered.

- 1. During steady state, the system should be able to supply any possible load

- 2. The starting of equipment should be supported i.e. normal overloads

- 3. The system must withstand internal and external faults which may lead to the interruption of the plant operation and/or damage to the equipment

Of course there is a limit to the overrating and this is defined in a great deal by the costs of the system. The second solution for voltage sag mitigation is increasing the rating of the DC link. This will be done by injecting extra current in the DC link from an auxiliary supply in the event of a voltage sag to maintain the DC link at its rated value. An appropriately sized energy storage device with proper interfacing will be used for that purpose. During a sag the storage device is used and the power is injected in the DC link. After the sag has cleared the storage device is to be charged back up to its initial state. To illustrate the actual power, voltage and current magnitudes that will be used for calculations further on in this thesis, an energy and power balance is given. The values for all components described in the previous paragraphs are calculated for the case of the EdeA substation. Voltage sag mitigation is introduced for the EdeA substation which is already described in chapter 1.5.1.

From Table 1.2 in section 1.3 it is clear that the most severe case to be investigated is that of a sag with 10 percent remaining voltage lasting 1 second. The maximum mitigation capability of any of the solutions provided is determined by this condition. To determine the power that is needed from the mitigation solution, the following parameters are introduced:

$P_{grid}$  = The power supplied by the grid

$P_{grid,dip}$  = The power supplied by the grid during a voltage sag

$P_{dc}$  = The power in the DC link

$P_{aux}$  = The power provided by the mitigation solution

$P_{load}$  = The power drawn by the load

These parameters are used in equations (2.1) to (2.5) for the calculation of the power supplied by the grid during a voltage sag. This ultimately leads to an equation for the power needed from any of the mitigation solutions.

During normal operation the power balance is given by

$$P_{load} = P_{grid} + P_{DC} (2.1)$$

During a voltage sag the power balance is given by

$$P_{load} = P_{grid - dip} + \frac{dE_{dc}}{dt} = V_{dip}I_{conv,rat} + \frac{\frac{1}{2}C_{DC}\Delta(V_{DC})^{2}}{\Delta t}$$

(2.2)

In this equation  $P_{grid,dip}$  is defined by the remaining voltage during a voltage sag i.e.  $V_{dip}$  (Equation (2.3)) multiplied by the maximum current of the converter  $I_{conv,rat}$ .

$\Delta V_{DC}$  is the difference between the converter rated DC voltage and the minimum allowable DC voltage.

Remaining voltage during voltage sag  $V_{dip}$  is defined by:

$$V_{dip} = V_{grid} \times dip\% \tag{2.3}$$

Where dip% is the percentage of the remaining grid voltage and  $V_{grid}$  is given.

To determine the effect of overrating on the system, (2.2) can be rewritten, using (1.4) i.e.

$$P_{load} = P_{grid - dip} + \frac{dE_{dc}}{dt} = V_{dip}k_{or}I_{load} + \frac{\frac{1}{2}C_{DC}\Delta(V_{DC})^{2}}{\Delta t}$$

(2.4)

For mitigation with an auxiliary supply, equation (2.2) is written as

$$P_{load} = P_{grid - dip} + \frac{dE_{dc}}{dt} = V_{dip} I_{conv, rat} + \frac{\frac{1}{2} C_{DC} \Delta (V_{DC})^2}{\Delta t} + P_{aux}$$

(2.5)

where  $P_{aux}$  is the power originating from the auxiliary supply.

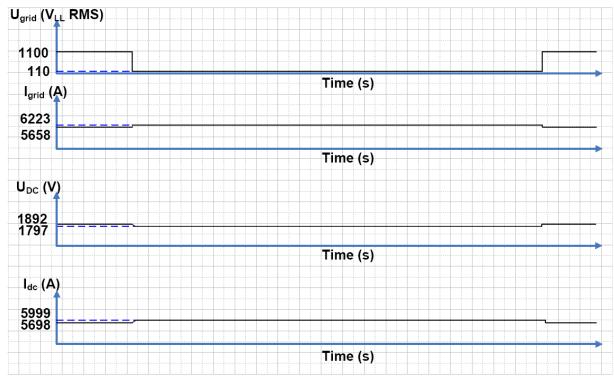

During this sag condition the power for the EdeA network connected by SIPLINK is given graphically by Figure 2.2. For this thesis it is chosen that the converters are overrated by 10 percent. This means that the rated current of the converter is 10 percent higher than the load current. During a voltage sag the converter operates at its maximum/rated current. This value is chosen in costs point of view. As mentioned in the previous chapter, the higher the system is overrated, the higher the costs because of the use of more and/or larger converters.

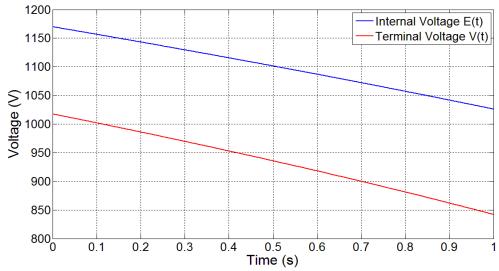

Figure 2.1 and Figure 2.2 illustrate graphically the voltage, current and power conditions that hold during a worst case voltage sag. The worst case voltage sag is defined as a 90 percent voltage sag during 1 second.

Figure 2.1: Voltages and currents during a worst case voltage sag

Figure 2.2: Power balance during a worst case voltage sag

From the above figures it is apparent that during the worst case voltage sag the power supplied to the grid is 1.19 MW. The power from the DC link is relatively small because of the small capacitor used. A small capacitor is needed for fast converter reaction times.

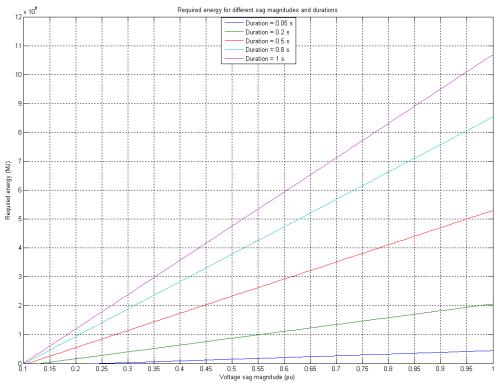

Using equation (2.5) different values for  $P_{aux}$  can be found by varying the voltage sag magnitude and the duration of the sag. The values are presented graphically in Figure 2.3. It is apparent from this figure that the longer and the deeper the sag, the more energy is needed to support the load.

Figure 2.3: Required compensation energy for different sag magnitudes and durations

# 3. Storage Methods for Energy Compensation

## 3.1 Storage Devices

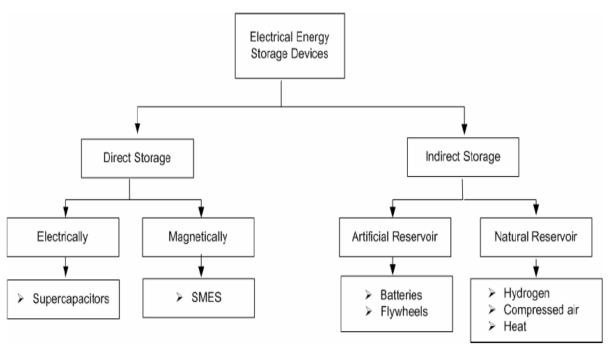

To store the energy that is needed for the boost converter compensation circuit a number of devices can be used. Each with their own advantages and disadvantages. The storage methods can be divided into direct and indirect storage methods. Indirect storage methods convert the energy from electrical to a different form. In direct storage devices the energy is stored without transforming the energy to a different form. Examples of indirect storage methods are compressed air, heat, hydrogen or rotating flywheels. Most of these storage methods are not very efficient because much of the energy is lost in the conversion process. The direct storage category can be divided in electrical and magnetic storage. The different energy storage methods available grouped by direct and indirect storage and by their specific storage reservoir is shown in Figure 3.1. The application of an energy storage technology is characterized by two factors. The first factor is typical to the storage method itself, and that is the amount of energy that can be stored in the device. The second factor is the rate at which the energy can be transferred into or out of the storage device.

Figure 3.1: Electrical energy storage methods[11]

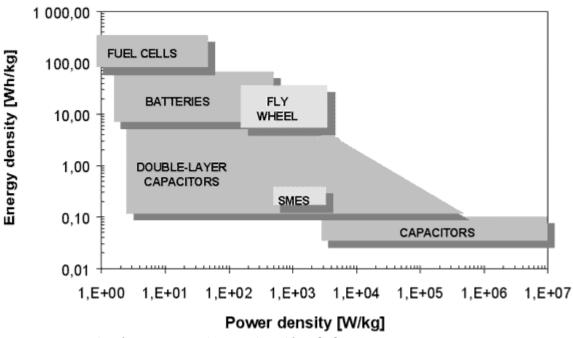

The "Ragone plot" from Figure 3.2 shows the power and energy classification of each storage method. This type of graph presents the power densities of the various energy storage devices, measured along the vertical axis is set against their energy density, measured along the horizontal axis.

Figure 3.2 Ragone plot of energy storage devices, adapted from [12]

Next an elaboration on the more proven storage technologies i.e. battery, flywheel and supercapacitor follows.

#### 1. Battery

Energy is stored electrochemically in batteries. "All battery systems are made up of a set of low voltage/power cells connected in series to achieve the desired terminal voltage, and in parallel to provide the desired power rating" [11]. There are currently various battery technologies available. Lead acid batteries are the most common due to cost issues but currently lithium ion is becoming more popular every day. Batteries characterise themselves by their high energy density and high energy capability, life span and lower initial cost. The voltage profile of a battery is flat. This means that the voltage remains nearly constant until the battery is depleted. This has benefits for control of power electronics. Due to their chemical kinetics, batteries cannot handle high power levels for long time periods. Also rapid discharge cycles may shorten the battery life leading to early replacement. Because of increasing environmental awareness batteries, which contain hazardous materials and generate toxic gasses during the charge and discharge cycles, are becoming more costly in their use. This is due to the additional costs of disposal of the hazardous materials that are implied by ever stricter environmental regulations.

Advantages: low cost

Disadvantages: short cycle life, need maintenance and replacement, weight

#### 2. Flywheel

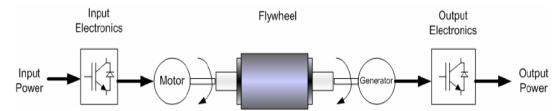

A flywheel works on the principal of a rotating mass being accelerated to a very high speed and maintaining the energy as rotational energy. The rotating mass is coupled to a motor-generator set through a shaft. A schematic of the flywheel components is shown in Figure 3.3. In many applications a power electronic converter is connected to the motor-generator s to provide power for a wide range of applications.

Figure 3.3: Flywheel system schematic[11]

The stored energy depends on the moment of inertia of the rotating mass and on the rotational velocity of the flywheel. See equation (3.1).

$$E = \frac{1}{2}J\omega^2 \tag{3.1}$$

In this equation E is the kinetic energy stored, J is the moment of inertia of the rotating mass and  $\omega$  is the rotational velocity of the flywheel. When the mass has a cylindrical shape, which is usually the case, the moment of inertia can be calculated using equation (3.2).

$$J = \frac{r^2 ml}{2} \tag{3.2}$$

Where m is the mass of the cylinder, r is the radius and l is the length.

By decreasing the speed of the flywheel, the rotational energy stored can be converted back to electrical energy. In this case the motor-generator set operates as a generator and the power can then be transferred to the outside.

Charging of the flywheel occurs during acceleration of the rotational velocity. The motor-generator set then works as a motor. From (3.1) it follows that the energy storage capability of the flywheel can be improved by either increasing the moment of inertia, increasing the rotational velocity of the mass or a combination of both.

High power flywheels are being developed through the increase of the moment of inertia. This is achieved by increasing the radius of the spinning mass and constructing the mass using materials as iron or steel. In this manner rotational velocities of up to 10000 rpm can be achieved [11]. This approach is commercially attractive because standard electric motors, mechanical components and power electronics can be used making for easy implementation. The second approach is based on the constructing rotors with a smaller radius and constructing them from composite materials. This results in smaller moments of inertia but allow for rotational velocities as high as 100 000 rpm [11]. The second method produces lighter and smaller flywheels with equal or increased storage capability compared to the previous technology.

In the flywheel technology losses are mainly produced by air drag and bearing losses. These become more important with increasing velocity. To reduce the air drag losses, flywheels are mounted in near vacuum containers. Bearing losses are reduced by mounting the flywheels on magnetic bearings. With the rotational losses nearly eliminated, the flywheel can have high charge and discharge efficiency leaving the transfer of peak power dependant only on the design of the motor-generators and the converters.

Strong containment vessels are required as a safety precaution because of the chance for "flywheel explosion". Flywheel explosion means the flywheel shatters due to the tensile strength of the flywheel being exceeded because of the high centrifugal forces produced by the rotational mass. This of course increases the total mass of the system and the extra weight subsequently brings with it a reduction of the energy density [W/kg]

Advantages: Durable, not affected by temperature changes as batteries, less damaging to the environment because of the use of inert materials. The exact amount of stored energy can be determined by measuring the rotational velocity.

Disadvantages: Stationary, requires much safety precautions due to the forces produced by the rotating mass. This adds weight thus reducing the energy density [W/kg].

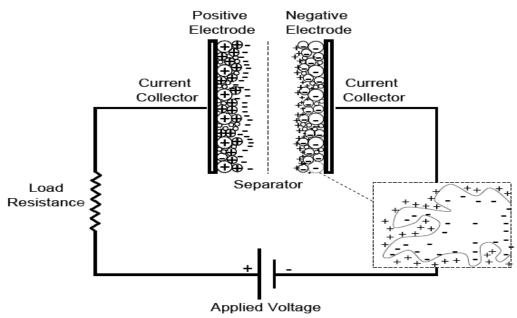

## 3. Supercapacitor

"Supercapacitors, also known as ultracapacitors or electrochemical capacitors, utilize high surface area electrode materials and thin electrolytic dielectrics to achieve capacitances several orders of magnitude larger than conventional capacitors." [13] With these material properties the supercapacitor can have higher energy densities while keeping the high power density which is characteristic for conventional capacitors.

Standard capacitors are made of two conducting electrodes with in between an insulating dielectric material. They are governed by the following equations: Capacitance C is defined as the ratio of stored (positive) charge Q to the applied voltage V:

$$C = \frac{Q}{V} \tag{3.3}$$

In a conventional capacitor, the capacitance C can also be described by (3.4). Here C is directly proportional to the surface area A of each electrode and inversely proportional to the distance D between the electrodes:

$$C = \varepsilon_0 \varepsilon_r \frac{A}{D} \tag{3.4}$$

Where  $\varepsilon_0$  is the dielectric constant or permittivity of free space and  $\varepsilon_r$  is the dielectric constant of the insulating material. The energy E stored in a capacitor is given by equation (3.5):

$$E = \frac{1}{2}CV^2 \tag{3.5}$$

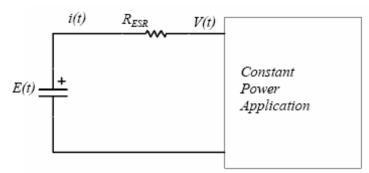

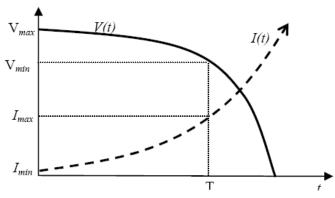

"The internal components of the capacitor (e.g., current collectors, electrodes and dielectric material) also contribute to the resistance quantity which measured in aggregate by a quantity know as the equivalent series resistance (ESR)." [13]

The basic principles of a conventional capacitor given by the previous equations also hold for a supercapacitor. Supercapacitors have however larger surface areas and thinner dielectrics.

This increases the distance D between the electrodes leading to an increase in capacitance and energy according to (3.4) and (3.5).

A schematic of the supercapacitor is given in Figure 3.4.

Figure 3.4: Schematic of an electrochemical double-layer capacitor, adapted from [13]

Advantages: Low impedance compared to battery, quick charge/discharge, high life cycle (up to 500000 cycled times), operating temperature range (-30° C - 70° C) Disadvantages: Linear discharge voltage prevents use of the full energy spectrum because of the limited operating voltage, low energy density, cells have low voltages: 1-3 V for all technology, high self discharge, voltage balancing needed when connecting multiple capacitors in series.

# 3.2 Comparison and conclusion of energy storage technologies

From the previous discussion it follows that energy storage methods differ in their energy densities, power densities and other important parameters as equivalent series resistance and charge and discharge time. A comparison of the different technologies is therefore necessary in order to accomplish the highest performance for each application. From Figure 3.2 it is clear that there is a big difference between the different storage devices discussed. When energy density is an important factor, batteries appear to be the better choice compared to flywheels and supercapacitors according to Figure 3.2. Another important parameter to be considered is the power density, which measures the energy stored per unit of weight of the device. Here the supercapacitor seems to be the better option as it is better able to deliver pulsating currents due to its fast charge and discharge capabilities.

Also important to consider in the comparison of energy storage devices is the equivalent series resistance value. A high value means higher losses and more voltage drop at the moment when the load demands current. When comparing this parameter, the supercapacitor appears to be more convenient with ESR's in the range of 10 times lower than that of batteries and comparable to flywheels [13]. Size constraints presented by modern power electronic

applications make the volume and weight of the storage devices also an important parameter to take into consideration. Having a smaller volume and weight, supercapacitors offer a better alternative than batteries and flywheels. Flywheels are also lighter than batteries because of the use of composite materials, but their volume is bigger because of the use of different protective measures.

Costs are also important in the comparison between the different storage devices. In this case batteries appear to have the lowest initial cost because it is a proven technology. But this is not including the maintenance costs. Supercapacitors and flywheels have higher initial costs but require little maintenance during all their life span as compared to batteries. The life span of batteries is averaged to be at five years. But if subjected to extreme conditions such as low/high temperatures and pulsating current loads, the lifetime is estimated to be at three years [13]. Supercapacitors have a life span of about ten years but this depends on the actual charge discharge cycles it is subjected to. The normal charge discharge cycle of a supercapacitor can be over 1 million. This charge discharge cycle is independent of environmental conditions or because of pulsating loads. The life span of flywheels is also independent of the environmental conditions and of the type of load that is connected to its terminals [13]. Their life span is estimated to be around 20 years.

For this comparison it is imperative to consider that supercapacitors and flywheels are not mature technologies. Therefore their ongoing continuous improvement will lead to reduction of their costs and increase in energy density comparable to batteries. Though batteries are a proven technology and are widely used in power electronics, few improvements have been done to improve their power densities or reduce their size and weight. The chemical compositions also pose a limitation to the lowering of the ESR or to improve their transient response.

From this comparison supercapacitors appear to be suitable to be used in this thesis research in combination with power electronics to provide voltage sag ride through. Despite their low energy density it presents a good advantage over the two energy storage devices for this application. This advantage is due to the high power density. Voltage sags are in the order of seconds. The load requires then a pulsating burst of power and the supercapacitor is the best candidate to deliver the pulsating current needed. From the point of view of internal losses supercapacitors offer the better alternative because of their very low equivalent series resistance. See Table 3.1 for a comparison of the different storage devices if all the stored energy is needed in 60 seconds.

| Storage device      | peak power<br>[W/kg] | power 60''<br>[W/kg] | life<br>[number of deep<br>discharges] | cost<br>[€/kW <sup>60"</sup> ] | availability   |

|---------------------|----------------------|----------------------|----------------------------------------|--------------------------------|----------------|

| Advanced battery    | 600                  | 100                  | <300                                   | 50-100                         | commercial     |

| Flywheel            | 300                  | 130                  | >100.000                               | 400-800                        | prototypes     |

| Supercapacitor bank | 3500                 | 250                  | >10.000                                | 100-120                        | pre-industrial |

Table 3.1: Comparison of storage devices for complete discharge in 60 seconds [14]

# 4. Operation of VSC-HVDC and Siemens Multifunctional Power Link Design

This chapter will give an overview of the VSC-HVDC technology. The structure and the control system will be described in detail in Sections 4.1 up to 4.3. A mathematical model of the control system is presented in these sections. The Siemens Power Link (SIPLINK) model will be presented and discussed in Section 4.4. Also the current SIPLINK technology and practical information of the system as well as applications for it are presented in this section.

# 4.1 Operation of VSC- HVDC

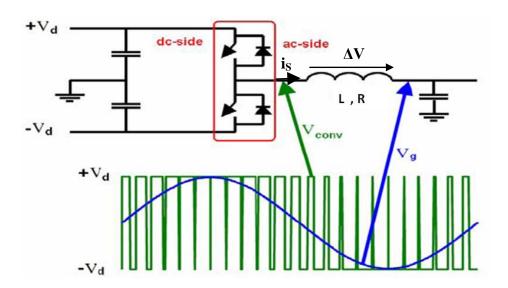

"The fundamental operation of the VSC-HVDC may be explained by considering each terminal as a voltage source connected to an AC transmission network via series reactors" [10]. A DC link connects the two terminals as can be seen in Figure 1.8. One converter side is zoomed in and shown in Figure 4.1.

VSC converters are theoretically capable of producing any waveform depending only on the choice of the direct voltage level and the switching frequency. To generate these waveforms Pulse Width Modulation (PWM) is used.

Figure 4.1: Schematic representation of one VSC converter[15]

The amplitude, the phase and the frequency of the VSC bridge can be controlled independently from each other. The instantaneous phase voltage which relates the aforementioned independently controlled parameters is described by the following equation.

$$V_{conv} = \frac{1}{2} V_{DC} m_a \sin(\omega t + \delta) + \text{harmonic terms}$$

(4.1)

where  $m_a$  is the modulation index, a number between 0 and 1, and is defined by the ratio of the peak value of the modulating wave and the peak value of the carrier wave;  $\omega$  is the

fundamental frequency,  $\delta$  is the phase shift of the output voltage depending on the position of the modulation wave[10].

By adjusting  $m_a$  and  $\delta$  any combination of voltage magnitude and phase shift in relation to the fundamental-frequency voltage in the AC system can be created.

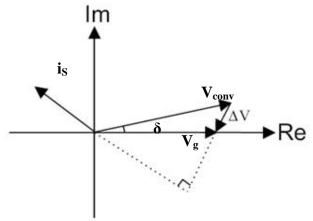

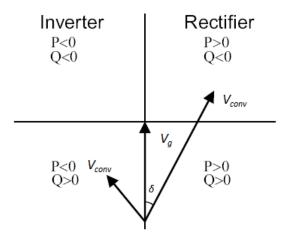

This is called direct control. The resulting voltage drop  $\Delta V$  across the inductance L can be varied to control the active and reactive power flows. The phasor representation for the fundamental frequency for a VSC operating as an inverter is shown in Figure 4.2. Here the converter is supplying reactive power to the AC system.

Figure 4.2: Phasor diagram of VSC inversion

By changing the phase angle  $\delta$  between the fundamental frequency converter voltage  $V_{conv}$  and the grid voltage  $V_g$ , the active power flow between the converter and the AC system can be controlled.

The active and reactive power are calculated according to (4.2) and (4.3).

$$P = \frac{V_g V_{conv}}{\omega L} \sin \delta \tag{4.2}$$

$$Q = \frac{V_g \left( V_g - V_{conv} \cos \delta \right)}{\omega L} \tag{4.3}$$

From equation (4.3) it can be seen that the reactive power flow is controlled by the amplitude of  $V_g$ . The amplitude of  $V_g$  in turn is controlled by the width of the pulses of the converter bridge. The DC voltage determines the maximum fundamental-frequency voltage from the converter. The sign of the active and reactive power depend on the phase and the amplitude of the converter bridge voltage. Figure 4.3 represents the situation when the line voltage  $V_g$  is constant. The location of the  $V_{conv}$  phasor determines whether the converter is in rectifier or inverter mode.

Figure 4.3: Phasor diagram (fundamental) and direction of power flows, adapted from [10]

In Figure 4.3, if the grid side voltage  $V_g$  leads the converter bridge voltage  $V_{conv}$ , the active power flows from the AC network to the converter. The converter is in rectifier mode.

With VSC-HVDC it is possible to transfer active power in both directions. This active power is equal on the AC side as well as the DC side in steady state. In order to accomplish this, one converter should control the DC voltage and the other should control the active power transmitted. Thus for proper operation of the system, there should always be DC voltage control and active power control done by either one of the converters. The controllable active power can be transferred in both directions equally and is only limited by the power rating of the converter. "The reactive power generation and consumption can be used for compensating the needs of the connected network." [10]

# 4.2 Design of DC capacitor

To control the input currents to be sinusoidal with a pulse width modulated signal with  $m_a \le 1$ , the DC voltage should be appropriately chosen. PWM switching actions create harmonics in the current flowing to the DC link. Therefore care must be taken when designing the DC side capacitor. The harmonics in the currents cause a ripple in the DC voltage and the size of the DC side capacitor and the switching frequency determines the magnitude of this ripple. Apart from the steady state operation, the design of the DC capacitor should focus on the operation of the system during disturbances in the AC system. During disturbances large power oscillations may occur on the AC side which will in turn lead to oscillations in the DC voltage which could lead to overvoltages stressing the valves. The capacitor should thus provide an energy buffer to keep the power balance during transients. A small capacitor results in faster converter response. The DC side capacitor is characterized by a time constant given by equation (4.4) [3].

$$\tau = \frac{\frac{1}{2}C_{DC}U_{DCN}^{2}}{S_{N}} \tag{4.4}$$

Here  $U_{DCN}$  is the rated DC voltage and  $S_N$  is the nominal apparent power of the converter. "The time constant is equal to the time constant needed to charge the capacitor from zero to rated voltage  $U_{DCN}$  if the converter is supplied with a constant active power equal to  $S_N$ " [3].

Choosing a small time constant can satisfy small ripple and small transient overvoltages on the DC voltage. A relatively small time constant also allows for fast active and reactive control. Controller speed of less than 5ms is not practical because the connection will not react. This is true only for the control of the active power since the reactive power is generated locally and does not require the DC link [10].

# 4.3 Control system of the VSC- MVDC

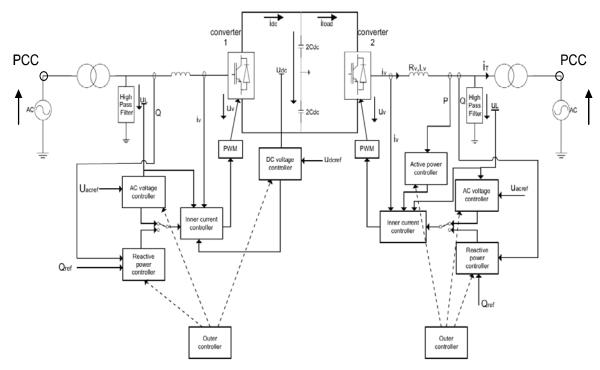

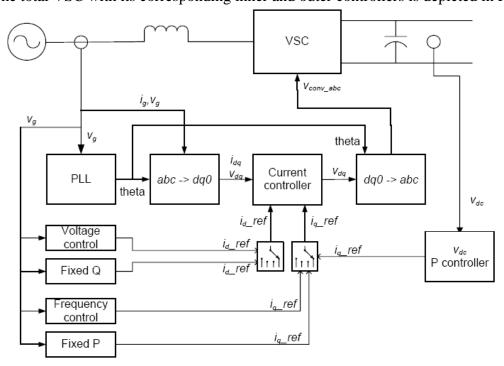

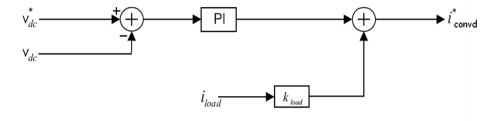

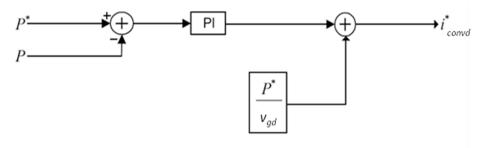

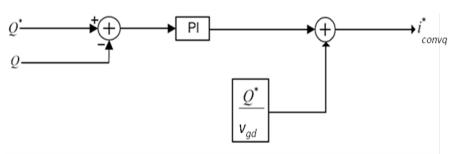

The control system of the VSC-HVDC is a cascade control and typically consists of a faster vector controller. This vector controller is completed by additional controllers which supply the references for the vector controller. The vector controller is thus the inner loop and the additional controllers are the outer loop. The values being controlled are the direct axis "d" and the quadratic axis "q" components of the converters at both sides. The control modes are: in the "d" axis, either the active power flow at the PCC or the pole-to-pole DC voltage; in the "q" axis, the reactive power flow at the PCC [16]. Also an AC voltage control can be added. See Figure 4.4. To determine the "d" and "q" components first a Clark transformation is performed on the three-phase quantities. This transforms these quantities to space vector components α and β (real and imaginary part). Next the Park transformation is performed which computes the direct axis "d" and the quadratic axis "q" (two axis rotating reference frame) from the  $\alpha$  and  $\beta$  quantities. These quantities are fed to the outer controllers which in turn calculate reference values for the inner current controller. The outer controllers include the DC voltage controller, the AC voltage controller, the active power controller, the reactive power controller or the frequency controller. The reference value for the active current can be derived from the DC voltage, the active and the frequency controller whereas the reference value for the reactive current can be obtained from the AC voltage and reactive power controller. In these controllers integrators can be used to eliminate steady state errors. Obviously not all controllers can be used at the same time but depending on the application different kinds of controllers can be chosen. In that case each of the controllers generates a reference value for the inner current controller and the inner current controller calculates the voltage drop over the converter reactor that will lead to the desired current. In Figure 4.4 an overview is given of the overall control structure of the VSC-HVDC.

Figure 4.4: Overall control structure of the VSC-HVDC[10]

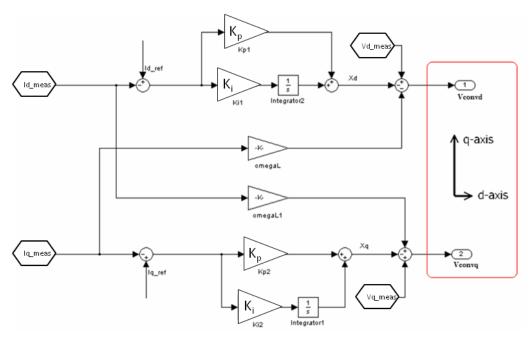

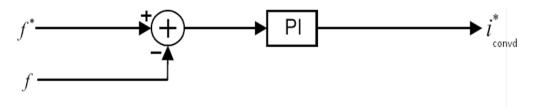

#### 4.3.1 The inner current controller

To better explain the mathematics associated with the inner current controller, Figure 4.1 is used for illustrative purposes. This is part of Figure 4.4 zoomed in. The inner current controller loop is based on the basic relationships for this model and can be implemented in the dq-frame. The inner current controllers consist of a PI regulator, a feedforward control of the AC voltage and a decoupling factor which is current depending. When neglecting waveform distortion, simple control algorithms can be derived for balanced system operation because the dq voltages are constant.

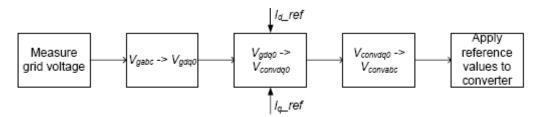

The process shown in Figure 4.5 is followed to obtain reference values for the converters.

Figure 4.5: Schematic overview of current control[17]

For each of the phases a,b and c equation (4.5) holds:

$$V_g - V_{conv} = L\frac{di}{dt} + Ri \tag{4.5}$$

The voltages over the reactor  $R+j\omega L$  are described by the differential equation:

$$\frac{d}{dt} \begin{bmatrix} i_{a} \\ i_{b} \\ i_{c} \end{bmatrix} = \begin{bmatrix} -\frac{R}{L} & 0 & 0 \\ 0 & -\frac{R}{L} & 0 \\ 0 & 0 & -\frac{R}{L} \end{bmatrix} \begin{bmatrix} i_{a} \\ i_{b} \\ i_{c} \end{bmatrix} - \begin{bmatrix} \frac{1}{L} & 0 & 0 \\ 0 & \frac{1}{L} & 0 \\ 0 & 0 & \frac{1}{L} \end{bmatrix} \begin{bmatrix} V_{conva} \\ V_{convb} \\ V_{convc} \end{bmatrix} + \begin{bmatrix} \frac{1}{L} & 0 & 0 \\ 0 & \frac{1}{L} & 0 \\ 0 & 0 & \frac{1}{L} \end{bmatrix} \begin{bmatrix} V_{ga} \\ V_{gb} \\ V_{gc} \end{bmatrix} \tag{4.6}$$

The transformation between the abc-components and the dq0-components is defined by [18]

$$V_{abc} = \mathbf{P}V_{da0} \tag{4.7}$$

and

$$I_{abc} = \mathbf{P}I_{da0} \tag{4.8}$$

In which the orthogonal Park transformation is used and is given by the matrix **P**

$$\mathbf{P} = \sqrt{\frac{2}{3}} \begin{bmatrix} \frac{1}{2}\sqrt{2} & \cos\left(\theta - \frac{2\pi}{3}\right) & -\sin\left(\theta - \frac{2\pi}{3}\right) \\ \frac{1}{2}\sqrt{2} & \cos\left(\theta - \frac{2\pi}{3}\right) & -\sin\left(\theta - \frac{2\pi}{3}\right) \\ \frac{1}{2}\sqrt{2} & \cos(\theta) & -\sin(\theta) \end{bmatrix}$$

(4.9)

with  $\mathbf{P}^{-1} = \mathbf{P}^T$

The angle  $\theta$  is measured by a phase-locked loop (PLL) system. In Simulink this is done by the Phase Locked Loop block. "The Phase Locked Loop block measures the system frequency and provides the phase synchronous angle  $\theta$  (more precisely  $[\sin(\theta), \cos(\theta)]$ ) for the dq Transformations block. In steady state,  $\sin(\theta)$  is in phase with the fundamental (positive sequence) of the  $\alpha$  component and phase A of the PCC voltage ( $U_{abc}$ )."[16] The voltages  $v_{convd}$  and  $v_{convq}$  are calculated by the current controller after the transformation to dq-quantities. To do this first the network equations of the ac side will be derived with Kirchhoff's laws. In the next section the following vector representations are used

$$V = \begin{bmatrix} v_a \\ v_b \\ v_c \end{bmatrix} \tag{4.10}$$

And

$$V' = \begin{bmatrix} v_d \\ v_q \\ v_0 \end{bmatrix} \tag{4.11}$$

The transformation from three phase quantities to the dq-frame is given by

$$V = PV' \tag{4.12}$$

The same holds for the current components. In the following equations the subscripts *conv* represent the converter side and *g* represents the grid side components.

Applying Kirchhoff's laws and applying the Park transformation as performed in [17] results in:

$$V_{g} = RI + L\frac{d}{dt}(I) + V_{conv}$$

$$PV_{g}' = RPI' + L\frac{d}{dt}(PI') + PV_{conv}'$$

$$V'_{g} = \mathbf{P}^{-1}RPI' + \mathbf{P}^{-1}L\frac{d}{dt}(PI') + V'_{conv}$$

$$V'_{g} = R'I' + \mathbf{P}^{-1}L\frac{d\mathbf{P}}{dt}I' + \mathbf{P}^{-1}L\mathbf{P}\frac{dI'}{dt} + V'_{conv}$$

$$V'_{g} = R'I' + L'\mathbf{P}^{-1}\frac{d\mathbf{P}}{dt}I' + L\frac{dI'}{dt} + V'_{conv}$$

$$\begin{bmatrix} v_{gd} \\ v_{gq} \\ v_{g0} \end{bmatrix} = \begin{bmatrix} R & 0 & 0 \\ 0 & R & 0 \\ 0 & 0 & R \end{bmatrix} \begin{bmatrix} i_{d} \\ i_{q} \\ i_{0} \end{bmatrix} + \begin{bmatrix} 0 & -\omega L & 0 \\ \omega L & 0 & 0 \\ 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} i_{d} \\ i_{q} \\ i_{0} \end{bmatrix} + \begin{bmatrix} v_{convd} \\ v_{convq} \\ v_{convo} \end{bmatrix}$$

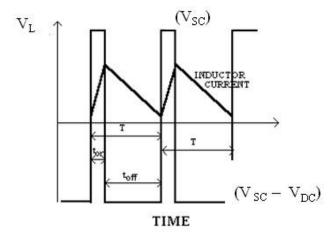

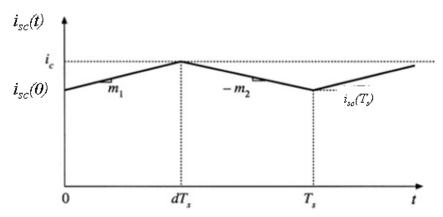

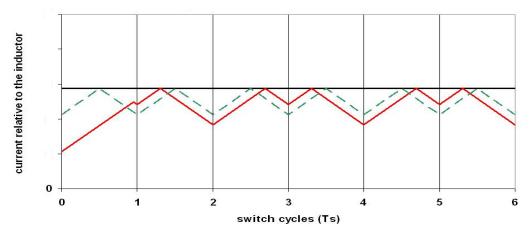

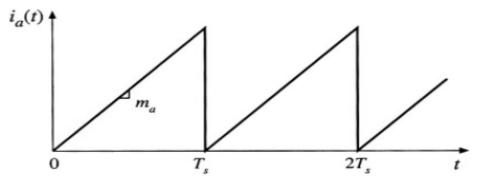

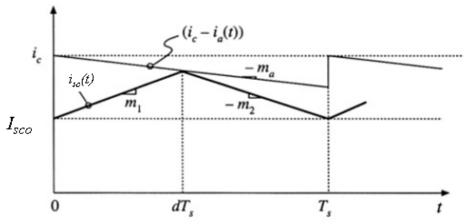

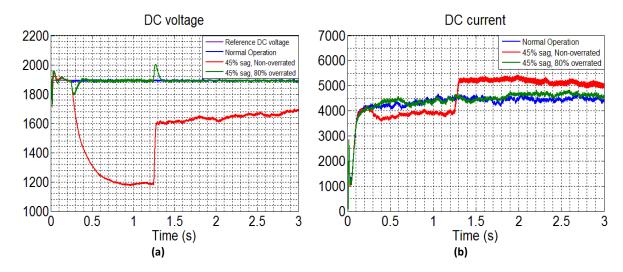

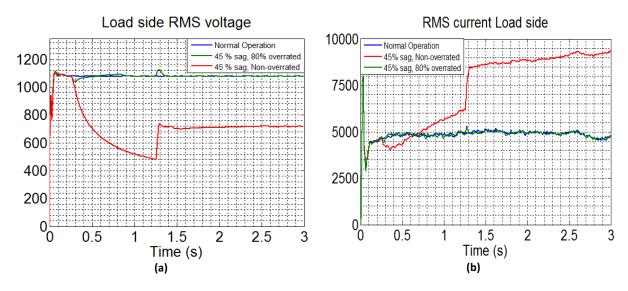

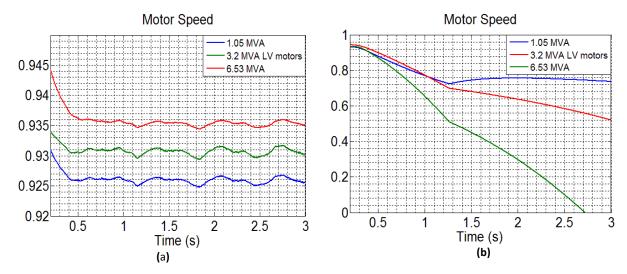

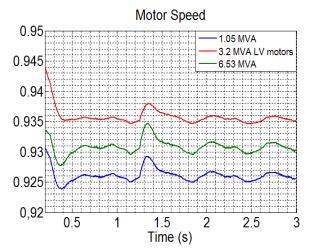

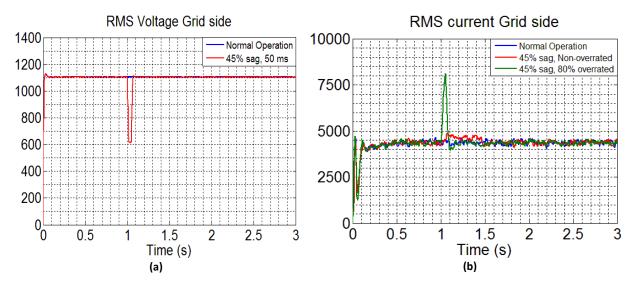

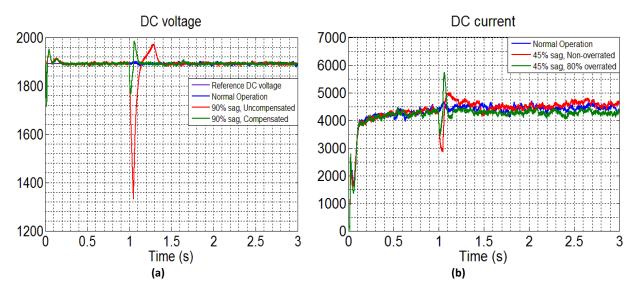

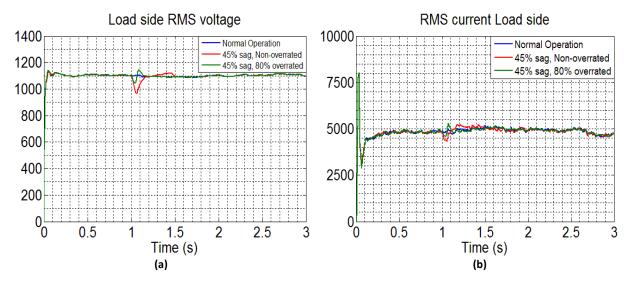

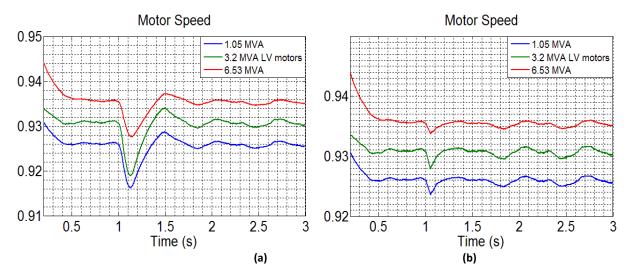

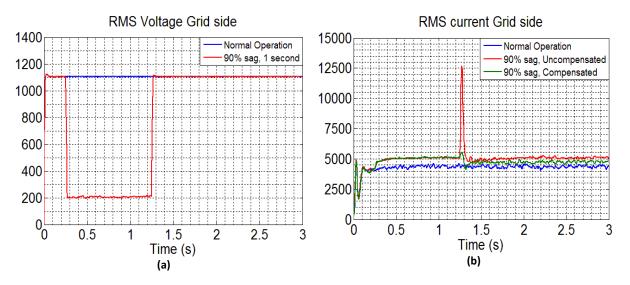

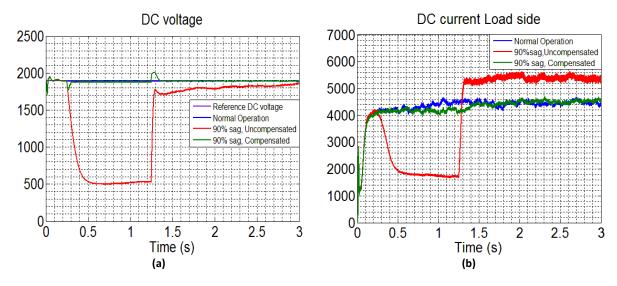

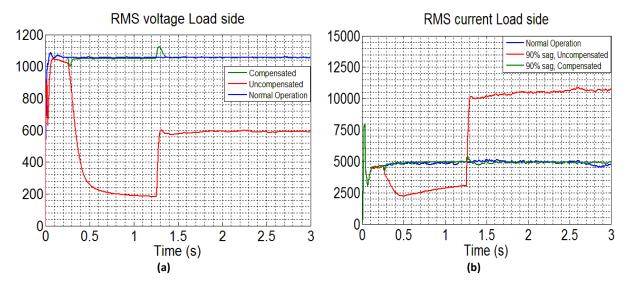

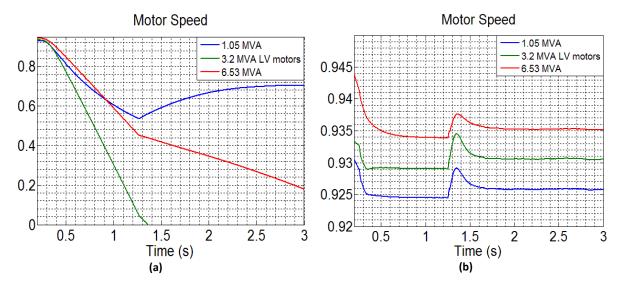

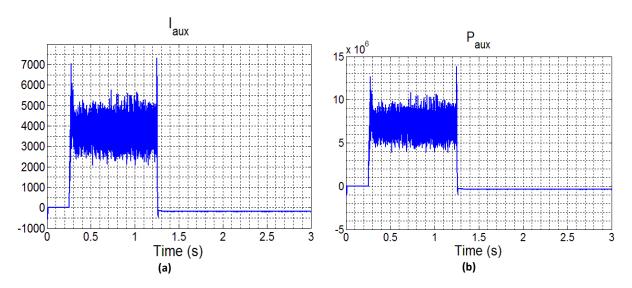

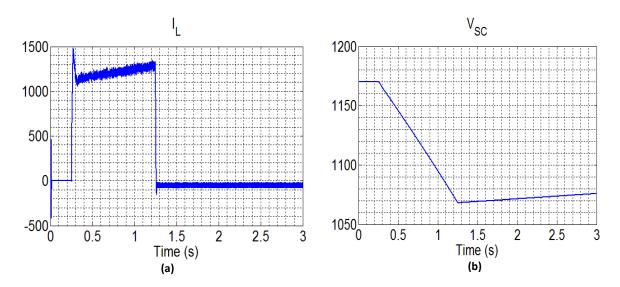

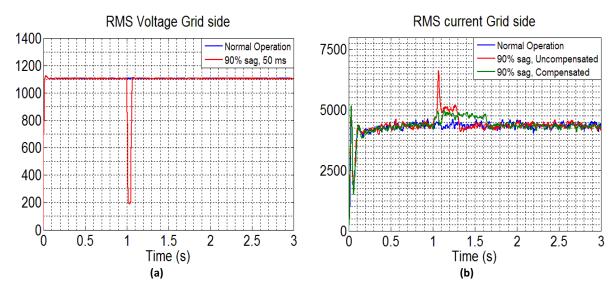

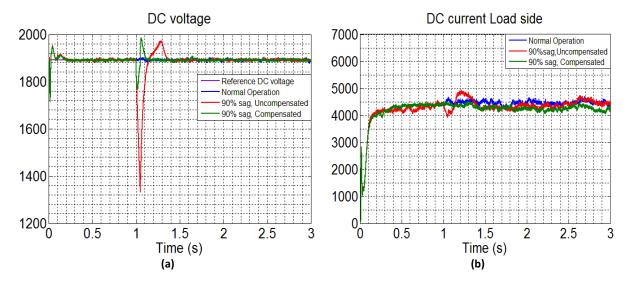

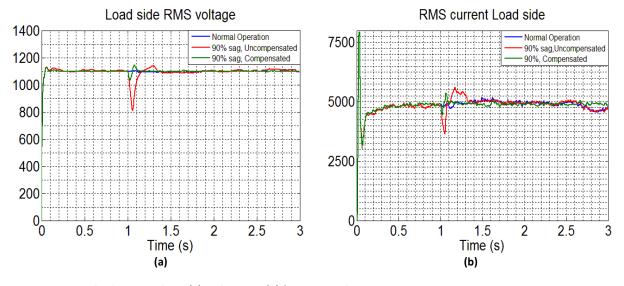

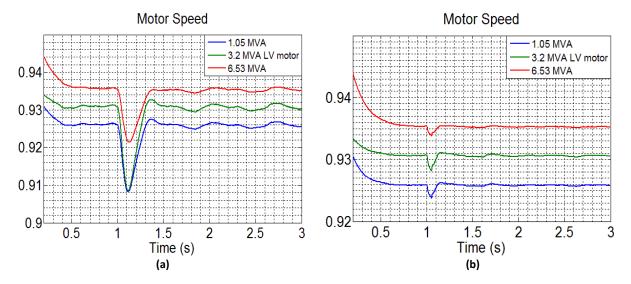

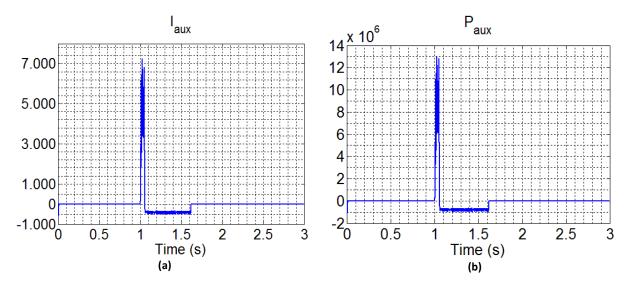

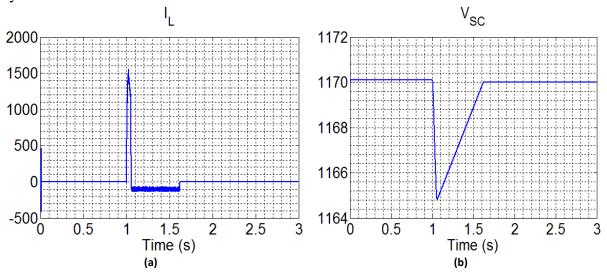

$$(4.13)$$