### M.Sc. Thesis

### System-level Fault-Tolerance Analysis of Small Satellite On-Board Computers

**Dmitry Burlyaev**

#### Abstract

Commercial Off-The-Shelf (COTS) electronic components offer cost-effective solutions for the development of On-Board Computers (OBCs) in the small satellite industry. However, the COTS parts are not originally designed to withstand the space radiation environment. Traditional fault-tolerance practices rely on expensive radiation tests or are based on circuit-level knowledge which are not easily available. This work proposes a novel simulation-based statistical approach to assist the satellite designers in performing OBC fault-tolerance analysis.

The presented novel approach is based on high-level system modeling and an object-oriented fault injection mechanism. Such a technique allows the comparison between fault-tolerance techniques and reveals the consequences of radiation effects in the COTS parts at early development stages.

The work covers the implementation of the proposed simulation framework which includes the OBC and fault modeling. The fault models are based on the conducted radiation environment analysis. The range of software and hardware fault detection and mitigation techniques are investigated as case studies. They include time and hardware Triple-Modular Redundancy (TMR), FPGA-based memory scrubbing with Hamming encoding, and watchdog/co-processor monitoring. The case studies reveal that the proposed approach can be used to choose suitable fault-tolerance techniques, increase their efficiency, and reduce the required hardware resources.

## System-level Fault-Tolerance Analysis of Small Satellite On-Board Computers

#### THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

EMBEDDED SYSTEMS

by

Dmitry Burlyaev born in Kamensk-Uralsky, Russian Federation

This work was performed in:

Circuits and Systems Group

Department of Microelectronics & Computer Engineering

Faculty of Electrical Engineering, Mathematics and Computer Science

Delft University of Technology

#### **Delft University of Technology**

Copyright © 2012 Circuits and Systems Group All rights reserved.

# DELFT UNIVERSITY OF TECHNOLOGY DEPARTMENT OF MICROELECTRONICS & COMPUTER ENGINEERING

The undersigned hereby certify that they have read and recommend to the Faculty of Electrical Engineering, Mathematics and Computer Science for acceptance a thesis entitled "System-level Fault-Tolerance Analysis of Small Satellite On-Board Computers" by Dmitry Burlyaev in partial fulfillment of the requirements for the degree of Master of Science.

| Dated: 2 July 2012 |                                                               |

|--------------------|---------------------------------------------------------------|

| Chairman:          | Prof. dr. ir. Alle-Jan Van der Veen, CAS, TU Delft            |

| Advisor:           | Dr. ir. Rene van Leuken, CAS, TU Delft                        |

| Committee Members: | Dr. ir. Said Hamdioui, CE, TU Delft                           |

|                    | Ir. Maxime Castera, Innovative Solutions In Space B.V. (ISIS) |

### Abstract

COTS electronic components offer cost-effective solutions for the development of OBCs in the small satellite industry. However, the COTS parts are not originally designed to withstand the space radiation environment. Traditional fault-tolerance practices rely on expensive radiation tests or are based on circuit-level knowledge which are not easily available. This work proposes a novel simulation-based statistical approach to assist the satellite designers in performing OBC fault-tolerance analysis.

The presented novel approach is based on high-level system modeling and an objectoriented fault injection mechanism. Such a technique allows the comparison between fault-tolerance techniques and reveals the consequences of radiation effects in the COTS parts at early development stages.

The work covers the implementation of the proposed simulation framework which includes the OBC and fault modeling. The fault models are based on the conducted radiation environment analysis. The range of software and hardware fault detection and mitigation techniques are investigated as case studies. They include time and hardware TMR, FPGA-based memory scrubbing with Hamming encoding, and watchdog/co-processor monitoring. The case studies reveal that the proposed approach can be used to choose suitable fault-tolerance techniques, increase their efficiency, and reduce the required hardware resources.

# Acknowledgments

I would like to express my deep gratitude to my university thesis advisor Dr. ir. Rene van Leuken, CAS, TU Delft for his invaluable input to my research progress and support in the academic world. I also would like to thank the company ISIS for the given freedom in the thesis topic choice and the industrial insight into satellite-related problems. I am very grateful to Software and Simulation departments of ISIS company and their leaders: Maxime Castera and Arthur Overlack.

I express the warmest thanks to my parents for everyday support and help in the choice of my path.

Dmitry Burlyaev Delft, The Netherlands 2 July 2012

# Contents

| $\mathbf{A}$  | bstra           | $\operatorname{\mathbf{ct}}$                           | v    |

|---------------|-----------------|--------------------------------------------------------|------|

| A             | cknov           | wledgments                                             | vii  |

| C             | onten           | ats                                                    | ix   |

| $\mathbf{Li}$ | st of           | Figures                                                | xiii |

| $\mathbf{Li}$ | st of           | Tables                                                 | xv   |

| $\mathbf{A}$  | crony           | vms                                                    | xvii |

| 1             | $\mathbf{Intr}$ | oduction                                               | 1    |

|               | 1.1             | Motivation                                             | 1    |

|               | 1.2             | Thesis goal                                            | 2    |

|               | 1.3             | Contributions                                          | 2    |

|               | 1.4             | Outline                                                | 3    |

| 2             | Ove             | erview: OBC for Small Satellite missions               | 5    |

|               | 2.1             | Micro and Nano satellite mission overview              | 5    |

|               | 2.2             | OBC satellite subsystem                                | 6    |

|               |                 | 2.2.1 Overview of OBC requirements                     | 7    |

|               |                 | 2.2.2 OBC fault-tolerance                              | 8    |

|               | 2.3             | Conclusions                                            | 9    |

| 3             | Spa             | ace Radiation Effects, Faults Detection and Mitigation | 11   |

|               | 3.1             | Space Radiation Environment Overview                   | 11   |

|               |                 | 3.1.1 Space Radiation Environment Assessment           | 12   |

|               |                 | 3.1.2 Fault rate Assessment                            | 15   |

|               |                 | 3.1.3 Radiation effects in COTS components             | 15   |

|               |                 | 3.1.4 Conclusion                                       | 22   |

|               | 3.2             | Radiation fault-tolerance techniques                   | 24   |

|               |                 | 3.2.1 Architectural-level techniques                   | 25   |

|               |                 | 3.2.2 Component-level techniques                       | 26   |

|               | 3.3             | Conclusions                                            | 29   |

| 4             | ово             | C modeling                                             | 31   |

|               | 4.1             | SystemC TLM modeling                                   | 31   |

|               | 4.2             | Related Works                                          | 31   |

|               | 4.3             | OBC architecture modeling - SmartFusion SoC model      | 32   |

|               |                 | 4.3.1 FPGA fabric modeling as a SoC component          | 34   |

|               | 4.4             | OBC system-level redundancy - I2C communication        | 36   |

|               |                 | 4.4.1 OBC model extension by I2C controller model      | 36   |

|   |     | 4.4.2 Model of interconnected OBCs (stacked OBC)                      |

|---|-----|-----------------------------------------------------------------------|

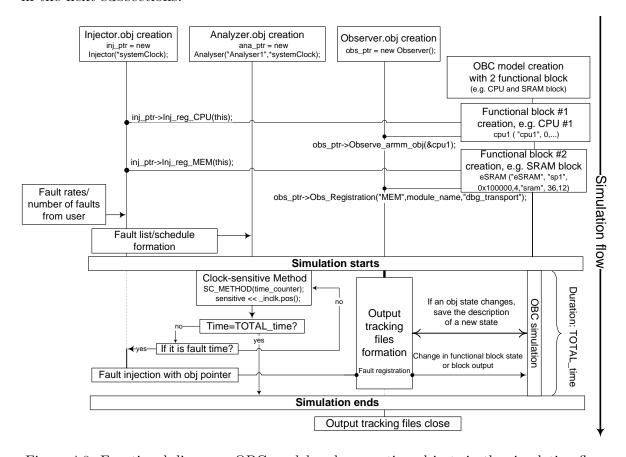

|   | 4.5 | Supporting modules                                                    |

|   |     | 4.5.1 Injector                                                        |

|   |     | 4.5.2 Analyzer                                                        |

|   |     | 4.5.3 Observer                                                        |

|   | 4.6 | Conclusions                                                           |

| 5 | Rac | liation effects modeling 4                                            |

|   | 5.1 | Radiation fault modeling                                              |

|   |     | 5.1.1 CPU fault models                                                |

|   |     | 5.1.2 SRAM and DRAM fault models                                      |

|   |     | 5.1.3 Flash-based memory fault models                                 |

|   |     | 5.1.4 Flash-based FPGA fault models                                   |

|   |     | 5.1.5 Failure modes                                                   |

|   | 5.2 | Conclusions                                                           |

| 6 | Sim | ulation steps 4                                                       |

|   | 6.1 | Statistical fault-tolerance analysis                                  |

|   | 6.2 | Multidimensional analysis of memory fault consequences                |

|   | 6.3 | Conclusions                                                           |

| 7 | Mo  | del Verification, Validation, and Limitations 5                       |

|   | 7.1 | Model Verification                                                    |

|   | 7.2 | Model Validation                                                      |

|   | 7.3 | Model Limitations                                                     |

| 8 | Cas | e studies 5                                                           |

|   | 8.1 | Case Study: Recursive algorithm                                       |

|   |     | 8.1.1 SEU injection into CPU registers                                |

|   |     | 8.1.2 SEFI injection into CPU                                         |

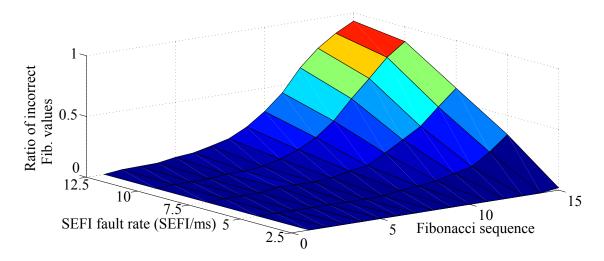

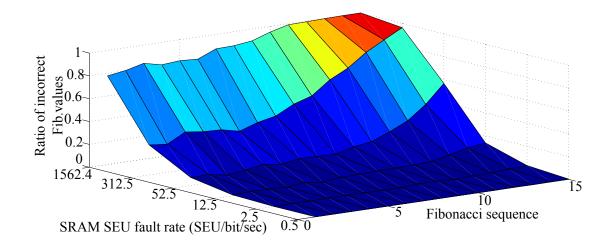

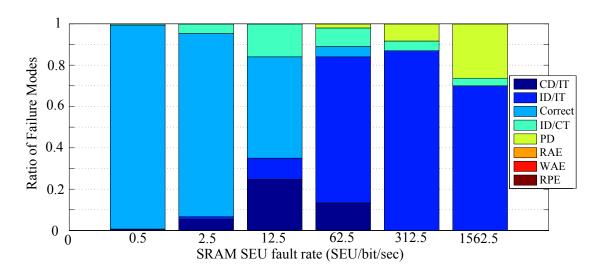

|   |     | 8.1.3 SEU injection into SRAM memory                                  |

|   | 8.2 | Case Study: JPEG image compression                                    |

|   | 8.3 | Memory scrubbing technique implementation                             |

|   | 8.4 | Case Study: Kalman filter of Attitude Determination and Control Al-   |

|   |     | gorithm                                                               |

|   | 8.5 | Case Study: Multidimensional analysis of memory fault consequences in |

|   |     | Adaptive filter                                                       |

|   |     | 8.5.1 Code execution without fault mitigation techniques 6            |

|   |     | 8.5.2 Code execution with fault mitigation                            |

|   |     | 8.5.3 System-level behavior                                           |

|   |     | 8.5.4 Clustering algorithm                                            |

|   |     | 8.5.5 Conclusions                                                     |

|   | 8.6 | Simulation time of the case studies                                   |

| 9            | Conclusions and Future Work                                                                          | 73 |

|--------------|------------------------------------------------------------------------------------------------------|----|

|              | 9.1 Conclusions                                                                                      | 73 |

|              | 9.2 Future Work                                                                                      | 75 |

| Bi           | bliography                                                                                           | 77 |

| A            | Appendix A                                                                                           | 87 |

|              | A.1 The Space Environment Information System (SPENVIS) settings for Radiation Environment Estimation | 87 |

| В            | Appendix B                                                                                           | 89 |

|              | B.1 MATLAB Fault rate estimation algorithm                                                           | 89 |

| $\mathbf{C}$ | Appendix C                                                                                           | 91 |

|              | C.1 Printout of Two OBCs communication through I2C bus                                               | 91 |

| D            | Appendix D                                                                                           | 95 |

|              | D.1 Top object of OBC model - code explanation                                                       | 95 |

# List of Figures

| 2.1<br>2.2 | 3U CubeSat with deployed antenna and solar panels                       | 5<br>7 |

|------------|-------------------------------------------------------------------------|--------|

| 3.1        | Solar Wind [2]                                                          | 11     |

| 3.2        | Van Allen Belts and South Atlantic Anomaly (SAA)[2]                     | 12     |

| 3.3        | Proton concentrations within $SAA[2]$                                   | 12     |

| 3.4        | Simulation results: Total Ionizing Dose (TID) vs aluminium shielding    |        |

|            | width                                                                   | 13     |

| 3.5        | Simulation results: Spacecraft shielded LET(Si) spectrum                | 14     |

| 3.6        | Threshold voltage shifting at different TID levels [3]                  | 20     |

| 3.7        | Single-Event Phenomenon (SEP) sensitivity wrt frequency [4]             | 21     |

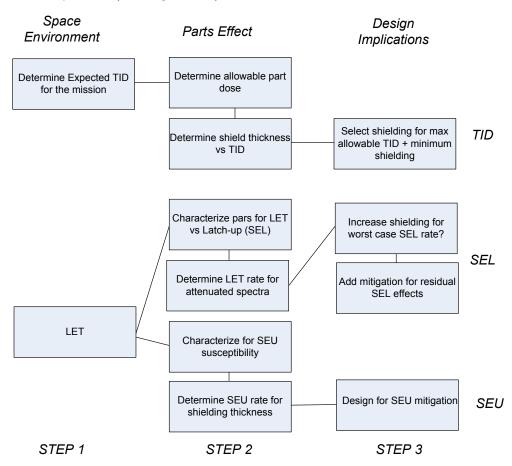

| 3.8        | Design process for use of commercial parts in Low Earth Orbit (LEO) [5] | 24     |

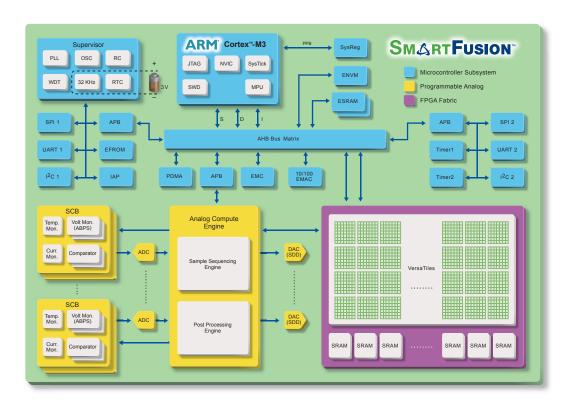

| 4.1        | SmartFusion System-on-Chip (SoC) Block Diagram[6]                       | 33     |

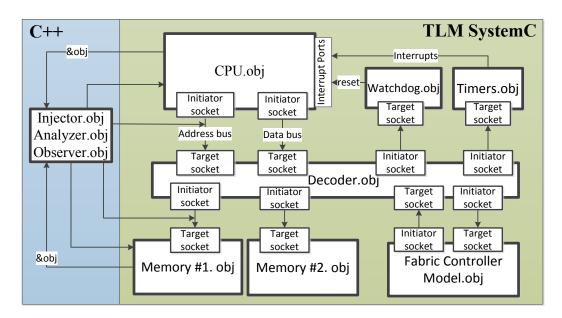

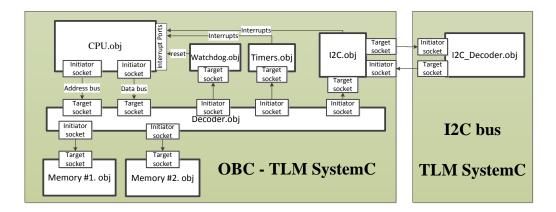

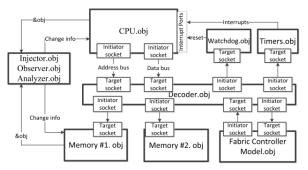

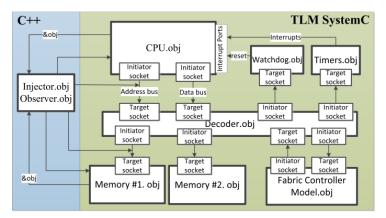

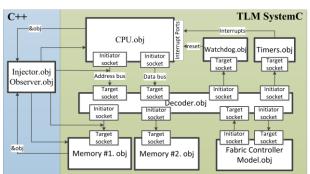

| 4.2        | Framework model structure: OBC model and supporting modules             | 33     |

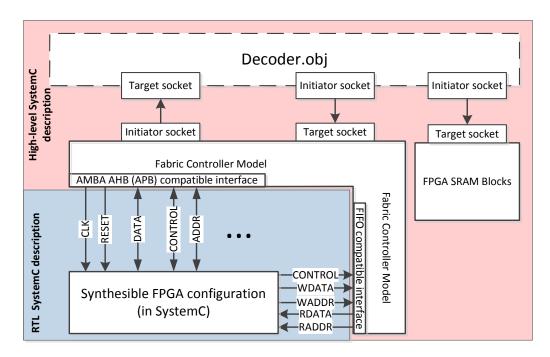

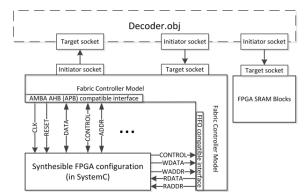

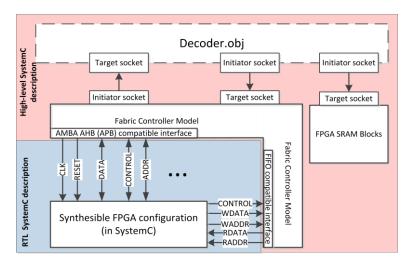

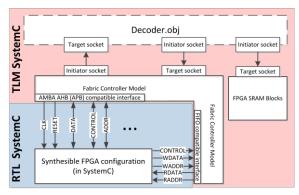

| 4.3        | The FPGA fabric model as a part of the OBC model                        | 35     |

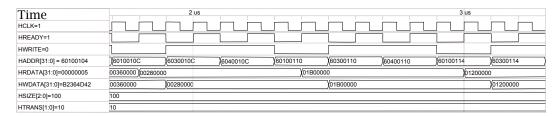

| 4.4        | AMBA AHB protocol consistency for single write and read cycles          | 36     |

| 4.5        | Example of the communication between the FPGA model and modeled         |        |

|            | SRAM blocks                                                             | 36     |

| 4.6        | Model of the OBC connected to I2C CubeSat bus                           | 37     |

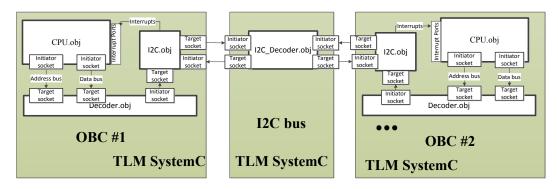

| 4.7        | Model structure of two interconnected OBCs through I2C CubeSat bus      | 37     |

| 4.8        | Functional diagram: OBC model and supporting objects in the simula-     | 20     |

| 4.0        | tion flow                                                               | 38     |

| 4.9        | Example of the fault list generated by the Injector module              | 39     |

| 5.1        | Single-Event Upset (SEU) model representation                           | 42     |

| 5.2        | One-dimensional Multiple-Cell Upsets (MCU) model representation $$ .    | 42     |

| 5.3        | Spatial MCU model representation                                        | 43     |

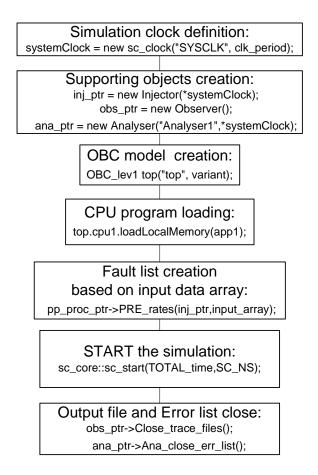

| 6.1        | Steps of one simulation iteration                                       | 48     |

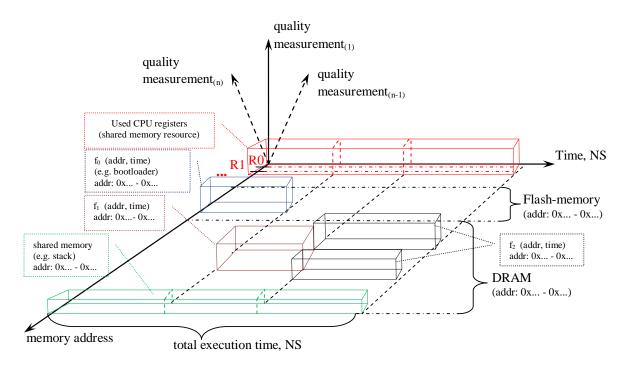

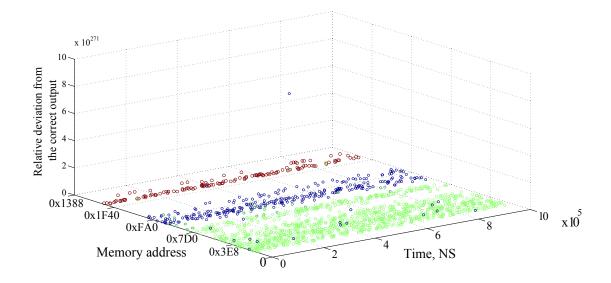

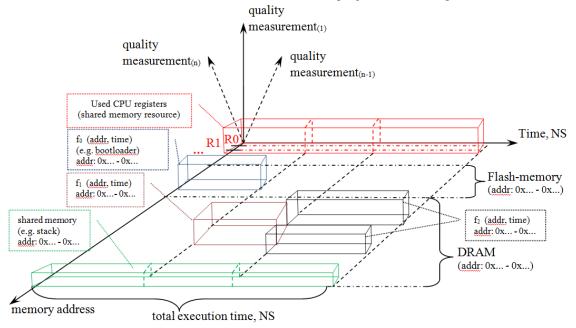

| 6.2        | The representation of the multidimensional analysis                     | 49     |

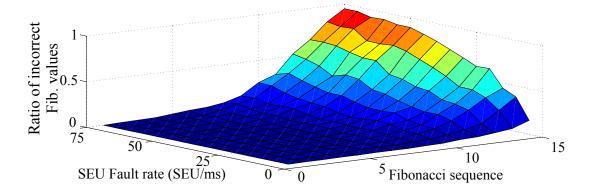

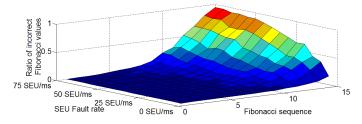

| 8.1        | Influence of SEU rate in CPU on incorrect result ratio                  | 54     |

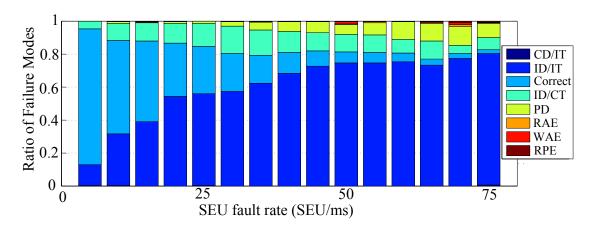

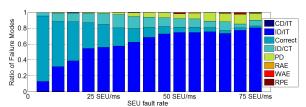

| 8.2        | Influence of SEU rate in CPU on Failure Mode ratio                      | 54     |

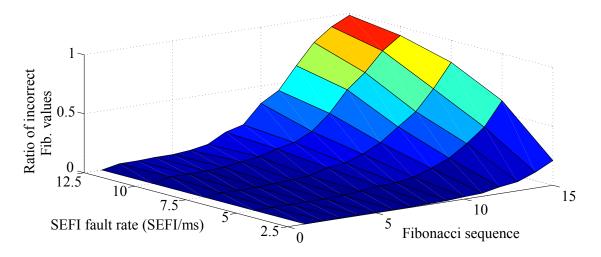

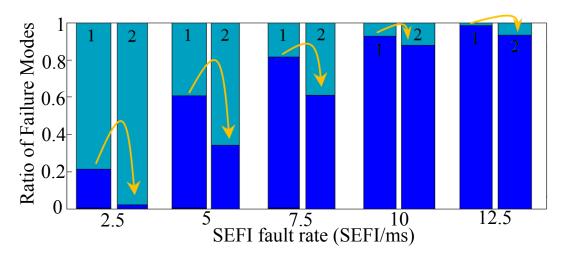

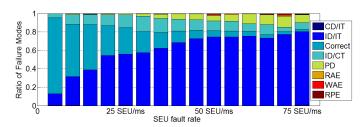

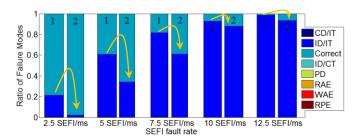

| 8.3        | Influence of SEFI rate on incorrect result ratio - untuned watchdog     | 55     |

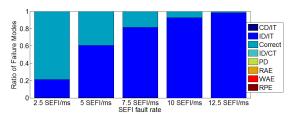

| 8.4        | Influence of SEFI rate on Failure Modes with the unturned (marked with  |        |

|            | "1") and tuned watchdog (marked with "2")                               | 55     |

| 8.5        | Influence of SEFI rate on incorrect result ratio - tuned watched        | 56     |

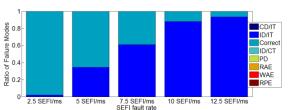

| 8.6        | Influence of SEU rate in SRAM on Failure Mode, without mitigation       | ドワ     |

| 8.7        | techniques                                                              | 57     |

| 0.1        | techniques                                                              | 57     |

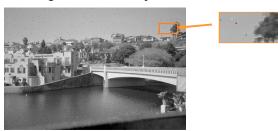

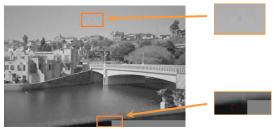

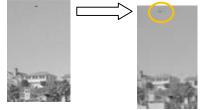

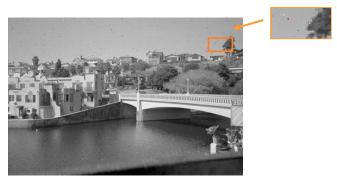

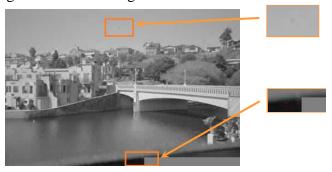

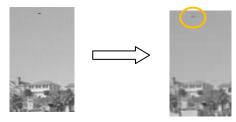

| 88         | The source image for JPEG compression procedure                         | 58     |

| 8.9  | The output image after JPEG compression procedure                        | 59 |

|------|--------------------------------------------------------------------------|----|

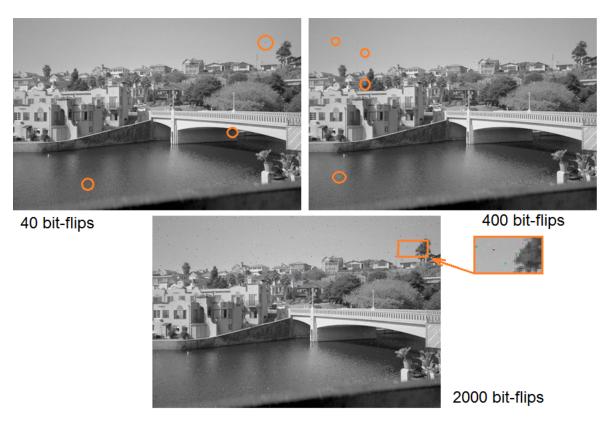

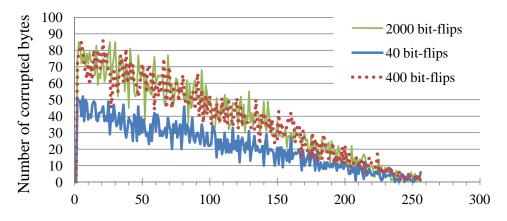

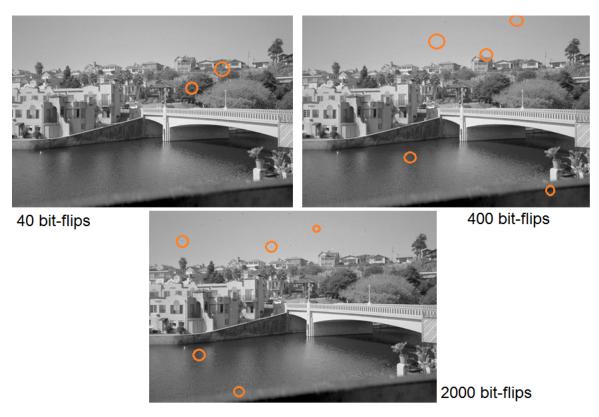

| 8.10 | Example of the source image SEU corruption - w/o mitigation techniques   | 60 |

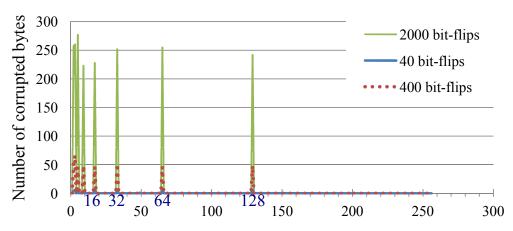

| 8.11 | Difference distribution of unequal bytes in the source images w/o mitig- |    |

|      | ation techniques                                                         | 60 |

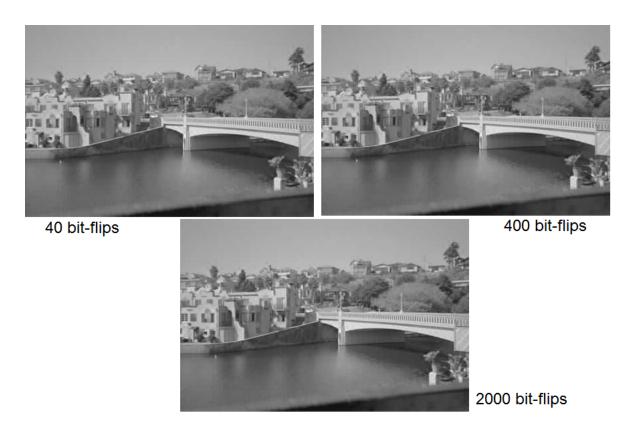

| 8.12 | JPEG compression output under the source image corruption by SEUs        |    |

|      | w/o mitigation techniques                                                | 61 |

| 8.13 | Difference distribution of unequal bytes in the compressed image w/o     |    |

|      | mitigation techniques                                                    | 61 |

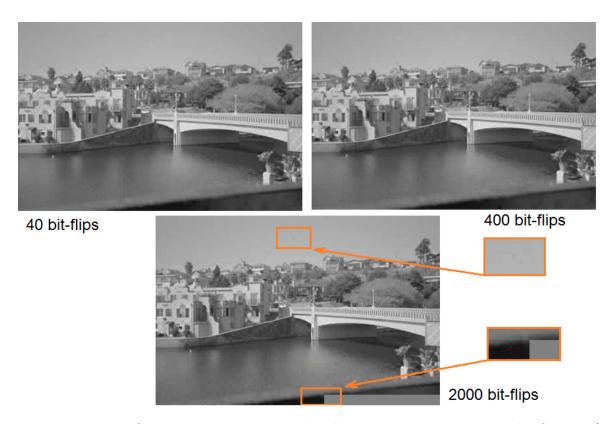

| 8.14 | The source image SEU corruption - with Memory Scrubbing                  | 62 |

| 8.15 | JPEG compression output - with Memory Scrubbing                          | 63 |

| 8.16 | JPEG compression with introduced 56-bit long MCU; the source and         |    |

|      | the output                                                               | 63 |

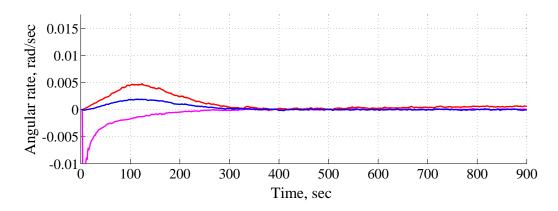

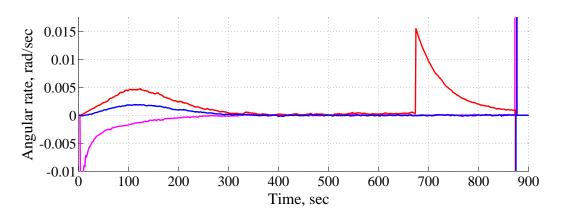

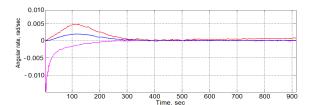

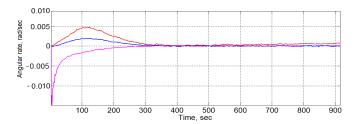

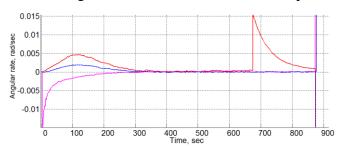

| 8.17 | Correct Kalman filter output                                             | 64 |

| 8.18 | Kalman filter output with SEUs introduction                              | 64 |

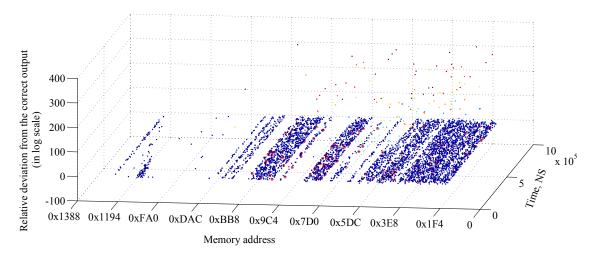

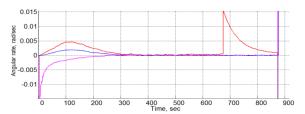

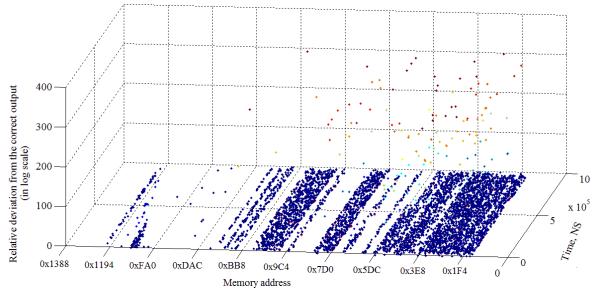

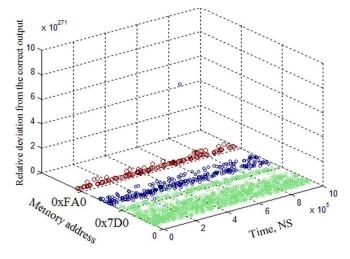

| 8.19 | The simulation result of the adaptive filtering computation with one SEU |    |

|      | introduction (20 000 iterations)                                         | 67 |

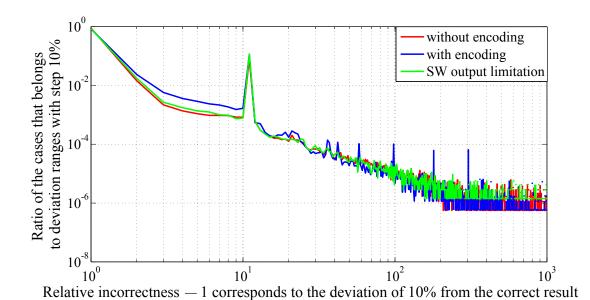

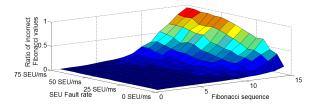

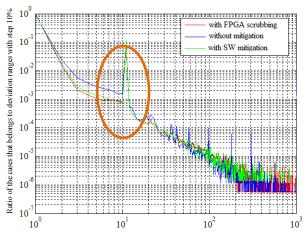

| 8.20 | Histogram of system fault-tolerance with and without fault-mitigation    |    |

|      | techniques (20 000 iterations)                                           | 68 |

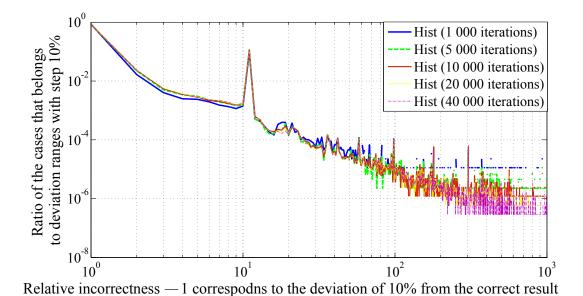

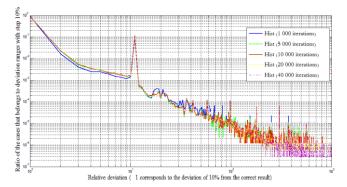

|      | The dependency of system behavior on the number of simulation iterations | 69 |

| 8.22 | Clustering algorithm output                                              | 71 |

# List of Tables

| 2.1 | Main OBC requirements                                                    | 9  |

|-----|--------------------------------------------------------------------------|----|

| 3.1 | DRAM radiation sensitivity - empirical data                              | 16 |

| 3.2 | SRAM radiation sensitivity - empirical data                              | 17 |

| 3.3 | Flash-based FPGAs radiation sensitivity - empirical data                 | 21 |

| 3.4 | Radiation sensitivity of COTS components, the worst case                 | 22 |

| 3.5 | Flash memory radiation sensitivity - empirical data                      | 23 |

| 8.1 | The source image parameters                                              | 57 |

| 8.2 | The output image parameters                                              | 58 |

| 8.3 | The output of CatapultC Synthesis for TMR and Hamming-based              |    |

|     | memory scrubbing FPGA co-processors                                      | 64 |

| 8.4 | The Memory Sections where SEUs are Injected                              | 66 |

| 8.5 | Simulation Time for the Version without Protection - One Iteration       | 66 |

| 8.6 | Simulation Time for the Version with FPGA-based Protection - One         |    |

|     | Iteration                                                                | 67 |

| 8.7 | Simulation Time for the Version with Software Protection - One Iteration | 68 |

| 8.8 | Simulation Results, System Fault-Tolerance with and without Fault-       |    |

|     | Mitigation Techniques                                                    | 68 |

| 8.9 | The Simulation Time of the Case Studies                                  | 72 |

### Acronyms

ADC Analog-to-Digital Converter. ADCS Attitude Determination and Control System Algorithm. ASIC Application-Specific Integrated Circuit. **BRAM** Block Random-Access Memory (RAM). CalPoly California Polytechnic State University. CMOS Complementary Metal-Oxide-Semiconductor. COTS Commercial Off-The-Shelf. CPU Central Processing Unit. DAC Digital-to-Analog Converter. DFF D Flip-Flop. Dhrystone MIPS(Million Instructions Per Second). **DMIPS** DRAM Dynamic RAM. ECC Error-Correcting Code. EDAC Error-Dectection And Correction. ESA European Space Agency. FGFloating Gate. FIM Fault Injection Module. **FMEA** Failure Mode and Effect Analysis. **FPGA** Field-Programmable Gate Array. FSM Finite State Machines. GCRs Galactic Cosmic Rays. GGGuard Gate. GPP General-Purpose Processor. GPR General-Purpose Register. GPS Global Positioning System. GUI Graphical User Interface. IC Integrated Circuit. ΙP Intellectual Property. ISIS Innovative Solutions In Space B.V.. JTAG Joint Test Action Group. LCI Logic Cell Like-Inverter. LEO Low Earth Orbit.

LET Linear Energy Transfer. LMA Load Memory Address. LSI Large Scale Integration.

MBU Multiple-Bit Upsets.

MCU Multiple-Cell Upsets.

MLC Multi-Level Cell.

MPU Micro-Processor Unit.

NASA National Aeronautics and Space Administration.

OBC On-Board Computer.

OS Operating System.

OTP One-Time Programmable. OVP Open Virtual Platforms.

PC Personal Computer. PCB Printed Circuit Board.

PROM Programmable Read-Only Memory.

QoS Quality of Service.

RAM Random-Access Memory. RTL Register-Transfer Level.

RTOS Real-Time Operating System.

SAA South Atlantic Anomaly. SDRAM Synchronous Dynamic RAM.

SEE Single-Event Effect.

SEFI Single-Event Functional Interrupt.

SEL Single-Event Latchup. SEP Single-Event Phenomenon.

SERVIS Space Environment Reliability Verification Integrated Systems.

SET Single-Event Transient.

SEU Single-Event Upset.

SHE Single Hard Error.

SIFT Software Implemented Fault Tolerance.

SLC Single-Level Cell. SoC System-on-Chip.

SPENVIS The Space Environment Information System.

SPI Serial Peripheral Interface.

SPR Special-Purpose Register.

SRAM Static Random-Access Memory.

TID Total Ionizing Dose.

TLM Transaction-Level Modeling.

TMR Triple-Modular Redundancy.

VMA Virtual Memory Address.

Introduction

The On-Board Computer (OBC) of a satellite is its central subsystem that processes information transmitted to the satellite and information provided by other on-board subsystems (radio, power, payload, etc.)[7, p.348]. In spite of adverse effects of harsh radiation environment, the OBC performance degradation should be minimized and the efficiency of software/hardware fault-tolerance techniques have to be analysed to provide clear understanding about satellite mission capabilities.

The radiation fault-tolerance techniques have become an especially active research topic when newly introduced small satellites and CubeSats[8] began to use low-cost Commercial Off-The-Shelf (COTS) components that are not designed to work in the space radiation environment and, as a result, susceptible to the radiation effects.

In the next Sections the research motivation is given, the need to develop a simulation-based approach for the OBC fault-tolerance analysis is explained, the main contributions of this work are listed, and the thesis organization is presented.

#### 1.1 Motivation

The main requirement for small satellite OBCs is their tolerance towards the faults induced by radiation. While the complexity of each component and whole systems are growing, the existing analytical methods for fault-tolerance analysis became infeasible for complex heterogeneous systems and for COTS components whose Integrated Circuit (IC)-level is unknown for the satellite designers.

The face-off between the requirements on the fault-tolerance and low-cost (COTS-based design) are partially solved by using COTS parts with flight heritage and satellite aluminium shielding. The former practice limits the OBC power efficiency and performance, while the latter one increases the price of a satellite launch. The up-to-date COTS devices can be used but require additional fault-tolerance analysis and clear understanding of the radiation effects consequences. Thus, an important existing question is how to assess the efficiency of the applied fault-tolerance techniques for particular applications and device set.

The benefits and correctness of implemented fault-tolerance techniques can be assessed under the radiation tests at the final development stage. However, if the radiation test is failed, the expensive and time-consuming re-design is required. The comparative analysis of the mitigation techniques and system-level debugging for fault-tolerance are impossible due to high cost of radiation tests. Moreover, radiation testing does not guarantee the injection of specific errors, nor explain their nature or the system behavior [9, 10].

Additionally, the existing simulation methods for the OBC fault-tolerance analysis are based on IC-level which is unknown for the final user of COTS components.

Moreover, circuit-level simulations are time-consuming and cannot be used for extensive statistical analysis.

Due to the complexity of each electronic component and the system as a whole, the utilization of high-level abstraction modeling language, such as SystemC, is imperative. The system-level fault-tolerance analysis through simulation is examined in this work.

#### 1.2 Thesis goal

The goal of this thesis is the creation of the simulation framework that enables statistical system-level fault-tolerance analysis of the OBC. The framework should assist software developers and system designers to write OBC software and conduct Failure Mode and Effect Analysis (FMEA) at early development stages. It should clarify radiation effect consequences for typical CubeSat missions. Consequently, the evaluation of the space radiation environment is required and the corresponding fault models have to be built.

The work should include several case studies where the framework utilization is explained and the interpretation of the simulation results are given.

The framework should support software portability to real hardware. It should be scalable and general enough to be easily adapted for other OBC architectures.

#### 1.3 Contributions

The contributions of this thesis are:

- A novel statistical approach for system-level fault-tolerance analysis of satellite OBCs is built (Section 6.1) and based on the high-level simulation framework of two main components: SystemC-based OBC model (Section 4.1-4.4) and C++-based fault injection mechanism (Section 4.5). The requirement on the hardware-software co-design and co-simulation is met with Transaction-Level Modeling (TLM) methodology [11]. The provided portability enables software-hardware co-simulation and co-design in a way that the written software and Field-Programmable Gate Array (FPGA) configuration are portable to the real OBC hardware.

- The radiation environment for typical CubeSat missions is assessed using European Space Agency (ESA) The Space Environment Information System (SPENVIS) project(Section 3.1.1). The interconnection between the assessed radiation environment, the electronic components' cross section, and fault-rates is defined (Section 3.1.2).

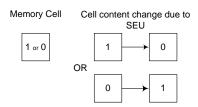

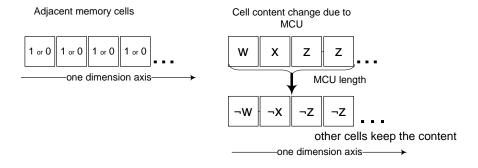

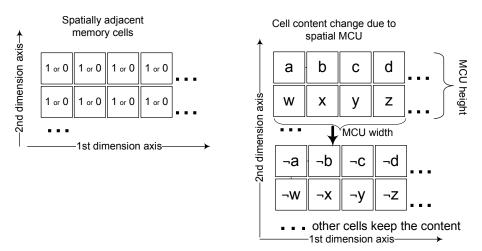

- The radiation sensitivity of modern electronic components is investigated using the published empirical observations. The maximum fault-rates are calculated for different types of electronic parts (SRAM, DRAM, Flash memories, etc.)(Section 3.1.3). The corresponding fault-models of possible radiation effects are built: the models of Single-Event Upset (SEU), Multiple-Cell Upsets (MCU), and Single-Event Functional Interrupt (SEFI) (Chapter 5).

- The model of the OBC based on SmartFusion System-on-Chip (SoC) is built(Section 4.3). It incorporates Cortex-M3 ARM core (an instruction-accurate model obtained from Open Virtual Platforms (OVP) project [12]), Flash-based FPGA co-processor, the central AMBA bus (replaced by the Decoder unit), several memory storages, watchdog, and timers. It is also shown how to build the stacked OBC model with I2C-controller utilization(Section 4.4).

- Using the created OBC model, the work investigates the fault consequences for the recursive and compression algorithms (Sections 8.1-8.3) as well as for the Kalman and adaptive filters of Attitude Determination and Control System Algorithm (ADCS)(Sections 8.4-8.5).

- The work shows how to compare the efficiency of such software and hardware mitigation techniques as time Triple-Modular Redundancy (TMR) and FPGA-based memory scrubbing (Section 8.5.2).

- The work shows that the simulation results can be used for the optimization of mitigation techniques, e.g. for FPGA-based memory scrubbing with Hamming encoding and watchdog monitoring (Sections 8.5.4, 8.1.2). The dedicated clustering algorithm has been developed for this purpose (Section 8.5.4).

Three conference papers have been written based on the results presented in this thesis. The work has been appreciated in Europe and USA where it was presented at ESA 4S Symposium[13] and North-Atlantic Testing Workshop[14] in 2012. The third written paper [15] is being under the review of XXVII Conference on Design of Circuits and Integrated Systems by the moment of this MSc thesis defence.

#### 1.4 Outline

The rest of the work is organized as follows:

Chapter 2 observes small satellite and CubeSat missions; it also discusses the typical OBC properties. Chapter 3 describes the space radiation environment, provides the assessment of CubeSat radiation conditions, and briefly observes well-known fault-tolerance techniques. Chapter 4 explains the principles of the chosen OBC modeling approach and introduces the OBC model based on SmartFusion SoC[6]. Chapter 5 explains the fault models used in the simulation framework. Chapter 6 generalises the FMEA with the proposed simulation approach and multidimensional analysis. Chapter 7 observes the OBC model validation, verification, and limitations. Chapter 8 contains the case studies, their interpretation, and explanation how to use the framework for the OBC fault-tolerance analysis. In the last chapter of this work conclusions are drawn and directions for future work are given.

The previous chapter explains the need to create a new approach for the fault-tolerance analysis of small satellite OBCs. Hereafter, the overview of small satellite missions is presented (Section 2.1), and the typical OBC properties are discussed (Section 2.2).

#### 2.1 Micro and Nano satellite mission overview

Nano and Micro satellites (for brevity small satellites in this work) are satellites with mass ranges of [1..10) kg and [10..100) kg consequently [16, p.30]. COTS-based Nanosatellites (or CubeSats) (Figure 2.1) were introduced in 1999 by California Polytechnic State University (CalPoly) and Stanford University [17, 18]. CubeSats became very popular in the scientific community due to the mission low cost. The low mission cost dictates the use of COTS components and the reduction of satellite mass by the elimination of heavy shielding. Both factors make satellite subsystems highly susceptible to the space radiation. However, the satisfactory results of missions like Hiten [19], TSUBASA [20], and Space Environment Reliability Verification Integrated Systems (SERVIS) [10] certified the feasibility of COTS parts utilization in space.

Figure 2.1: 3U CubeSat with deployed antenna and solar panels

Nowadays, small satellites start to be used in long-term research projects, including

commercial ones where the mission success depends not only on the launch success but on the provided Quality of Service (QoS)[21, 22, 23]. Despite of high radiation-tolerance requirements, system engineers are compelled to use COTS components due to their low cost, availability on the electronic market, and cutting edge performance[5].

A satellite system can be always divided into two main parts: a satellite platform and a payload, in other words, a core component and a variable sybsystem [24]. The core component consists of the communication, power, altitude control, and the OBC subsystems [25]. These subsystems should possess re-usability property and meet possible requirements of future missions to reduce time-to-market and non-recurrent costs.

One of the distinguishing characteristics of small satellite missions is the short period of satellite visibility to the ground station: with the typical altitudes of 300-750 km above the sea level, the direct satellite visibility is limited to 3-14 minutes for one ground station[26]. In conjunction with the limited communication data-rate[27, 28], the short pass-by time introduces the higher requirements on the on-board processing power[23]. This requirement is enforced by advancements in payload technology that result in high demand of powerful on-board processing[2].

As for any autonomous vehicle with a rechargeable energy source, satellite subsystems have to consume as low power as possible. This requirement is dictated by the limited number of charge/discharge cycles for lithium ion batteries and solar panels efficiency. A power efficient OBC reduces the amplitude of lithium ion batteries charge/discharge cycles, which prolongs the batteries operational life[29].

All the telemetry and OBC commands are transmitted between the subsystems via a command and data handling bus. In CubeSats this bus is standardized by PC/104 bus standard[30] as well as the used Printed Circuit Board (PCB) size is limited by 10x10 centimeters[31, 8].

The kernel part of the satellite that performs the majority of mission tasks is the OBC. The OBC takes responsibility for the satellite auto-operation within the power, mass, size limitations and radiation-tolerance requirements discussed above. In details, the typical OBC of small satellites is analyzed in the next Section 2.2.

#### 2.2 OBC satellite subsystem

The satellite OBC is a computer or a system of computers that processes various information transmitted to the satellite or from other on-board subsystems[7, p.348](see Figure 2.2). The OBC performs all main operations, stores on-board data, and executes the telecommands sent by the ground station[32, 24]. The OBC architecture has to be flexible and general-purpose to increase its reusability[33].

The OBC should have the characters of future small satellites: short time-to-market, high functional integration, flexibility, and low expenses with maximized fault-tolerance [34, 24, 32]. Since the physical upgrade and repair of satellite electronics are impossible after its launch, there is great need for condition-based maintenance, self-repair and upgrade capabilities [35, 23, 36].

The overview of main requirements to the OBC design is presented in the next Section 2.2.1.

Figure 2.2: Existing OBC for Nano satellites [1]

#### 2.2.1 Overview of OBC requirements

To define the requirements on the OBC subsystem it is necessary to analyze the functionality it should perform:

#### 2.2.1.1 Processing power

The execution of an existing ADCS requires at least 80 DMIPS(according to an internal Innovative Solutions In Space B.V. (ISIS) document). The unavailability of the correct ADCS results for more than 5 minutes may cause the satellite orientation loss with following communication loss and solar panels efficiency reduction.

The camera NanoCam[37] can be taken as a case study to conduct an analysis of possible workload by a imaging payload. NanoCam can provide two pictures per second through an I2C interface. The picture JPEG compression will take 317 ms and 45 kB Random-Access Memory (RAM) on modern processors as Cortex-M3[38].

According to the aforementioned application requirements, the appropriate processor will have at least 100-110 DMIPS of performance. One of such processors is ARM Cortex-M3 with 1.25 DMIPS/MHz and frequencies higher than 80 MHz[39].

#### 2.2.1.2 Memory capacity

Based on the NanoCam and altitude/orbit control algorithm characteristics, the OBC needs at least 32 Mbytes of RAM to temporary keep and process pictures, measurements, and payload data. Additionally, non-volatile high-capacitive memory storage is needed to keep the telemetry and payload data until sending it to the ground station. High-capacitive SD Flash memory is usually utilized for this purpose [1, 40].

#### 2.2.1.3 Peripherals

Missions are becoming more diverse and complex; thus, satellites should be able to accommodate various payloads[41]. Consequently, the OBC should demonstrate high flexibility in term of available peripherals. The command and data handling bus (see Section 2.1) requires one I2C bus; another I2C will be needed for a Global Positioning System (GPS) receiver[42], camera, or Nano-RTU[43]. Two Serial Peripheral Interface (SPI) interfaces can be utilized for communication with payloads. Sometimes both SPI are used for one payload subsystem, e.g. in Nano satellites Tracking system[44].

#### **2.2.1.4** Software

The principal requirement on the OBC software is bug-free. Additionally, in-flight software update techniques and corresponding boot loader capabilities are desirable[32]. This approach will make the OBC architecture capable to recover from software bugs by software in-flight reloading. Since except health-checking functionality the OBC should perform ADCS, payload data processing, etc., the OBC tasks have different importance. Utilization of a Real-Time Operating System (RTOS) provides several priority levels for tasks execution[32].

#### 2.2.2 OBC fault-tolerance

The previous Sections 2.1-2.2.1 explained the OBC importance and its main functional characteristics. However, no OBC functionality can be provided if the OBC is not a fault-tolerant system. The definitions of fault-tolerance and faults are discussed in a few next paragraphs.

On one hand, a fault can be defined as the primary cause of changes in the system structure or parameters that eventually lead to a degraded system performance or even system functional loss[45, p.1-2]. Several examples of fault are listed hereafter[45, p.1]:

- An internal event in the system which breaks an information link.

- A wrong control action given by the human operator that brings the system out of the required point.

- It may be a system design error that remained undetected until the system came into a certain operation point where this error reduced the performance considerably.

In order to avoid the negative fault consequences, the faults have to be found as quickly as possible and the system has to be returned the the correct state as soon as possible. These two steps: detection and recovery are carried out by different fault-detection and fault-mitigation techniques (see Section 3.2). In conjunction these techniques form fault-tolerance techniques. Systems use these techniques to meet the limitations on the performance degradation caused by the introduced faults. As a result, a system becomes fault-tolerant if the balance between the applied fault-mitigation techniques and the faults' severity is kept.

On other hand, the term "fault" can correspond to the representation of a radiation effect at the abstracted function level. In the contest of system defects, the term fault corresponds to the representation of a defect at the abstracted function level [46, p.57-58]. The terms "radiation fault modeling" and "radiation fault models" will be used in this work with the meaning of the representation of a radiation effect at the abstracted function level. The term "fault" in the space industry is more commonly used according to the aforementioned definition from [45, p.1-2].

In the case of small satellite OBCs, the fault-tolerant OBC is the systems that uses fault-tolerance techniques to minimize the negative consequences of the radiation effects.

#### 2.3 Conclusions

This chapter presented the main characteristics of the appropriate OBC for small satellite missions. The characteristics are summarized in Table 2.1.

| OBC characteristic                    | Required value                 |

|---------------------------------------|--------------------------------|

| Processing power                      | $\geq 100 \text{ MIPS}$        |

| RAM (volatile memory)                 | $\geq 32 \text{ Mbytes}$       |

| Non-volatile memory storage           | SD card ( $\geq 1$ Gb)         |

| Peripherals                           | $\geq$ two I2C, $\geq$ two SPI |

| Digital-to-Analog Converter (DAC) and | preferably for flexibility     |

| Analog-to-Digital Converter (ADC)     |                                |

| FPGA                                  | preferably for flexibility     |

| Termal conditions                     | industrial standard,           |

|                                       | [-40+70] Celsius               |

| Total power consumption               | $\leq 1 \text{ Watt}$          |

Table 2.1: Main OBC requirements

The processing power concentration in the OBC imposes the strict requirement on correct and stable OBC operation. Taking into account the diverse radiation-induced effects in COTS parts (see Chapter 3) and the absence of an appropriate shielding protection, the adequate fault detection and mitigation techniques[41] have to be used (see Section 3.2).

# Space Radiation Effects, Faults Detection and Mitigation

Space radiation influence on electronics has always been the central issue in the space industry. However, it is necessary to assess the radiation environment particularly for 300-750 km of altitude (see Chapter 2) to understand the impact of radiation on different OBC components (Static Random-Access Memory (SRAM)-based and Flash-based memories, FPGA,etc.)(Sections 3.1.3.1 - 3.1.3.5).

#### 3.1 Space Radiation Environment Overview

Space environment significantly differs from terrestrial conditions, which introduces serious problems for the OBC development and COTS components utilization.

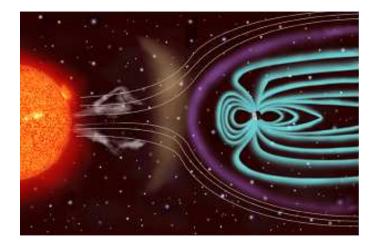

Space-based radiation comprises atomic particles that have been spread by stellar events within the solar system or beyond it (e.g. from The Milky Way galaxy )[2]. The particles stream generated within our solar system is referred to as *the solar wind* (Figure 3.1).

Figure 3.1: Solar Wind [2]

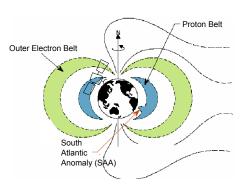

The Earth's magnetosphere traps, slows, or deflects the electrons, protons, and heavy ions (isotopes of atom from Helium to Uranium) emitted during solar events such as solar flares and mass coronal ejection[2]. As a result of protons and electrons interactions with the Earth's magnetic field, they are trapped within the Van Allen belts (Figure 3.2). Thus, the orbits with altitude from 500 to 13 000 km are populated with high energy protons[47].

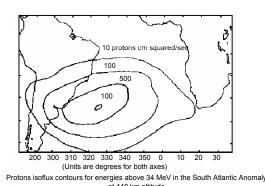

The inner proton Van Allen belt has a region, South Atlantic Anomaly (SAA), where the belt extends downwards the Earth. Consequently, the high concentration of

protons is observed in this region at lower altitudes (see Figure 3.3) and constitutes a serious danger for small satellite missions.

Figure 3.3: Proton concentrations within

Moreover, the statistical correlation between radiation-induced faults in the OBC and solar activities was revealed by the Hiten satellite mission[35].

SAA[2]

Solar flares or spatial anomalies cause variances of one or two orders of magnitude in environmental effects. They cannot cause a system failure but the OBC limited performance degradation is highly expected [5].

#### 3.1.1 Space Radiation Environment Assessment

The radiation effects in electronic components can be classified into Single-Event Phenomenon (SEP)(or Single-Event Effect (SEE)) and Total Ionizing Dose (TID) over the mission lifetime [5, 25, 4]. SEP( or SEE) describes the reaction in a part or a system caused by the impact of radiation[2]. TID is a total amount of radiation that a part or a system is subjected to[2].

#### 3.1.1.1 Total Ionizing Dose (TID)

Protons, heavy ions, and Galactic Cosmic Rays (GCRs) contribute to TID which is measured in "rad" units. TID affects Complementary Metal-Oxide-Semiconductor (CMOS) devices by creating new electrical paths and depositing charge within the component[2]( e.g. in the oxide layers over the silicon[48]). Consequently, the electricity can flow in unexpected way.

In general, TID contributes to the device deterioration over time[34]. Despite the ability of some TID effects to self-anneal, the time needed to recover can be longer than a mission can afford. The OBC parts selection, parts derating, and shielding prevent potential catastrophic failures due to TID[5].

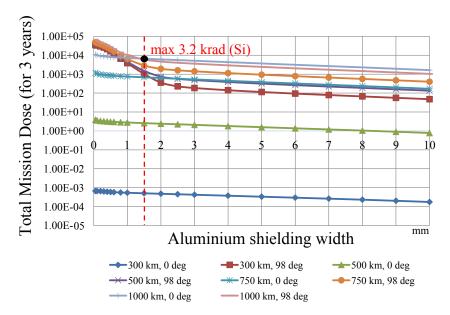

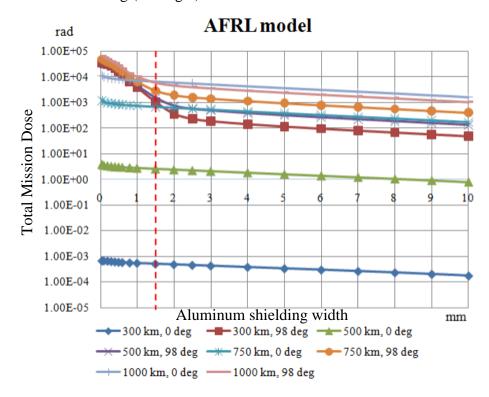

Using ESA SPENVIS[49], TID has been estimated for the typical mission lifetime. The mission lifetime is set to be three years (other simulator settings are described in Appendix A). Various possible mission scenarios (altitude, inclination, and shielding width) have been simulated and presented in Figure 3.4.

Figure 3.4: Simulation results: TID vs aluminium shielding width

Since 1.5 mm aluminium shielding is usually supported by a standard CubeSat structure, 1.5 mm is chosen as a shielding width for small satellites in this work. According to Figure 3.4, the worst case TID scenario for a 3-years mission within 300-750 km altitude corresponds to 3.2 krad. The correctness of this simulation result is supported by the empirical National Aeronautics and Space Administration (NASA) model APEXRAD [50].

#### 3.1.1.2 Single-Event Effects (SEE)

SEEs (or SEPs) are the radiation effects that occur unpredictably with a range of consequences[34]. The consequences depend on the damage caused by the passage of a single high-energy particle through an electrical node[51]. Such particles are protons, heavy ions, and GCRs. Depending on the device electric field configuration, the created charge disposition can cause SEP or it can recombine without any effects [52].

Linear Energy Transfer (LET) is the rate at which ions or other particles loose their energy when penetrating the material [2]. LET is defined as energy deposited per traversing length per material specific density  $(MeV \cdot cm^2/mg)$ [53, p. 11]. Incident energy, particle mass, and material density influence LET and the results of penetration.

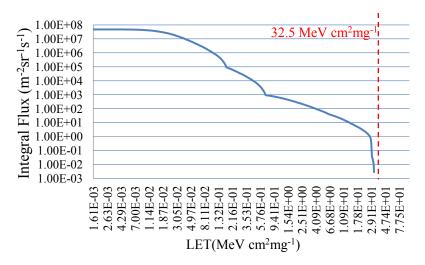

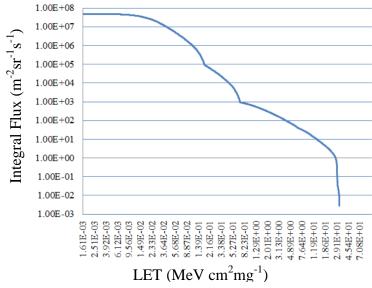

Using ESA SPENVIS[49] tool, the LET spectrum of particles inside the satellite shielding has been found for typical CubeSat missions. As previously, 1.5 mm aluminium shielding was taken as a case study. By comparing different orbital scenarios, the worst case was also found at 750 km and 98 deg inclination (Figure 3.5).

The particle LET spectrum can be considered as equal to zero when the LET is higher than 32.5  $MeV \cdot cm^2/mg$  (see Figure 3.5).

Single-Event Effects (SEE) classification

SEE can be classified to subcategories based on the type of consequences [2, 34, 33]:

Figure 3.5: Simulation results: Spacecraft shielded LET(Si) spectrum

- Single-Event Upset (SEU), or "soft effect" according to [25]

- Single-Event Transient (SET)

- Single-Event Functional Interrupt (SEFI)

- Single-Event Latchup (SEL), or "destructive effect" according to [25]

- Multiple-Cell Upsets (MCU) are topological multiple SEUs [54]

- Multiple-Bit Upsets (MBU) are logical multiple upsets: error bits belong to the same bit-word[54]

- Single Hard Error (SHE) or "hard effect", which denotes a stuck bit [25]

SEU happens when a single particle deposits enough charge at a sensitive node in a microcircuit to cause the circuit state change. SEU appears as "soft error" such as a bit-flip or a spurious command [52]. Thus, the data state of the device is corrupted without the permanent damage of the device. The nature of SHE is the same as SEU has, but the bit cannot be returned to the normal operation by re-writing.

SET corresponds to the ion-strike-induced transient pulse [48]. The pulse can propagate through the network and cause SEU in a storage element. Another SET effect is the interaction with the internal clock signal by widening/narrowing the pulse signal. Consequently, SET influences the speed of systems that are dependent on the clock signal [53, p.12] and may corrupt the synchronized communication between two nodes. The number of errors induced by SET is operating frequency dependant [55].

SEPs also incorporate SEFI that leads the electronic device to enter an unknown state and stop responding[56].

Ionizing interaction of CMOS junction with charged particles causes SEL[53, p.12]. Burnout and gate rupture are possible SEL consequences[5]. The component hangs up too in the case of SEL, but the part consumes excessive current and does not work until the device is power cycled[33].

# 3.1.2 Fault rate Assessment

Since the testing results about the error cross section are published for many COTS components, the rates of radiation effects occurrence(fault rates) can be calculated according to the methodology presented hereafter.

A differential cross section with respect to primary particle flux is defined as [57]:

$$\sigma(\Lambda; \theta, \varphi) = \frac{dN(\Lambda; \theta, \varphi)}{\Phi(\Lambda; \theta, \varphi) dod\Lambda},$$

(3.1)

where do is the solid angular element, dN is the error number due to particles with LET in the range  $\Lambda...\Lambda + d\Lambda$ ,  $\Phi[cm^{-2}srerad^{-1}(MeV \cdot cm^2/mg)^{-1}]$  is differential fluency per LET unit per solid angle.

Consequently, the full error rate can be calculated as:

$$R = \int \int \int \sigma(\Lambda; \theta, \varphi) \phi(\Lambda; \theta, \varphi) d(\cos\theta) d\varphi d\Lambda$$

(3.2)

where  $\phi$  is flux  $(\phi = d\Phi/dt)$

Instead of the cross-section  $\sigma(\Lambda; \theta, \varphi)$ , it is possible to introduce the averaged cross-section  $\langle \sigma(\Lambda) \rangle$  over the full solid angle  $4\pi$ . According to the usual assumption that the direction distribution of cosmic ray and corresponding LET spectrum are isotropic, the flux can be averaged:  $\phi(\Lambda) \cong 4\pi\phi(\Lambda; \theta, \varphi)$

Then, the next formula can be derived from (3.2):

$$R = \int \langle \sigma(\Lambda) \rangle \phi(\Lambda) d\Lambda \tag{3.3}$$

As a result, if at least some discrete values of cross-section measurement results and the flux simulation data are known, the fault rate can be calculated by polynomial approximation and the following integration. The corresponding code has been written in MATLAB to ease the fault rate calculation and presented in Appendix B.1.

## 3.1.3 Radiation effects in COTS components

Modern OBCs use different COTS components (see Chapter 2). Thus, the radiation impact estimation is required for the range of COTS parts. Hereafter, such estimations are presented; the fault rates are calculated according to the methodology of Section 3.1.2 and Appendix B.1.

#### 3.1.3.1 SEE in DRAM

Two opposite trends are observed in DRAM memory [58]:

- the shrinking junction volumes that decrease the collected charge

- the relatively high node-capacitance due to an external three-dimensional cell capacitor

As a result, DRAM fault-tolerance has remained roughly constant over many generations. However, soft errors in the bitline and sense amplifiers become dominant because of the increased operating frequency [58].

The Table 3.1 contains the DRAM fault-tolerance information and its source:

| Device/device component        | TID,<br>krad(Si) | Possible<br>SEE      | Cond.     | Fault rate (worst 5     | Source |

|--------------------------------|------------------|----------------------|-----------|-------------------------|--------|

|                                | maa(SI)          | OLL                  |           | minutes)                |        |

| Latest generation of Synchron- | 50               | SEU and              |           | ,                       | [59]   |

| ous Dynamic RAM (SDRAM)        |                  | $\operatorname{SEL}$ |           |                         |        |

| Peripherals circuits of DRAM   |                  | SEU                  |           |                         | [60]   |

| 64 Mbytes SDRAM (Micron        | 20               | SEL                  | 51        |                         | [61]   |

| company)                       |                  | followed             | MeV-      |                         |        |

|                                |                  | by SHE               | $cm^2/mg$ |                         |        |

|                                |                  | SEFI                 |           |                         | [61]   |

|                                |                  | followed             |           |                         |        |

|                                |                  | by MCU               |           |                         |        |

| 64 Mbytes SDRAM (Elpida        | 40               | no SEL               | 85        |                         | [61]   |

| company)                       |                  | even at:             | MeV-      |                         |        |

|                                |                  |                      | $cm^2/mg$ |                         |        |

|                                |                  | SEU                  |           | $1.4519 \cdot 10^{-8}$  |        |

|                                |                  |                      |           | up-                     |        |

|                                |                  |                      |           | set/bit/day             |        |

|                                |                  | SEFI                 |           | zero                    |        |

|                                |                  | followed             |           |                         |        |

|                                |                  | by MCU               |           |                         |        |

| Micron MT47H256M8HG-37E        |                  | SEU                  |           | $3.9306 \cdot 10^{-9}$  | [62]   |

|                                |                  |                      |           | up-                     |        |

|                                |                  |                      |           | set/bit/day             |        |

|                                |                  | SEFI                 |           | $1.3373 \cdot 10^{-1}$  |        |

|                                |                  | followed             |           | event/dev/day           |        |

|                                |                  | by the               |           |                         |        |

|                                |                  | whole                |           |                         |        |

|                                |                  | page or              |           |                         |        |

|                                |                  | column               |           |                         |        |

|                                |                  | corruption           |           | 11                      | [0.0]  |

| Elpida EDE2108ABSE-8G-E        |                  | SEU                  |           | $3.6796 \cdot 10^{-11}$ | [62]   |

|                                |                  |                      |           | upset/bit/              |        |

|                                |                  | CDDI                 |           | day                     |        |

|                                |                  | SEFI                 |           | $1.5115 \cdot 10^{-2}$  |        |

|                                |                  |                      |           | event/dev/day           |        |

Table 3.1: DRAM radiation sensitivity - empirical data

As a result, DRAM memory is tolerant towards the expected total mission dose of 3.2 krad. According to the estimations, modern DRAM memory components will not experience SEL during usual small satellite missions. However, DRAM memory is

highly susceptible to SEU, SEFI, and MCU. If the OBC contains 32 Mbytes of SDRAM memory, then the memory will experience 4 upsets per day in the worst case.

### 3.1.3.2 **SEE in SRAM**

Beginning from the late 1990s, terrestrial neutron-induced soft errors have become the main reliability issues in SRAM industry [60]. Research [63] explicitly shows that due to technology scaling the SRAM memory is becoming less SEU sensitive but the ratio and the size of MCU are increasing.

The Table 3.2 contains the SRAM fault-tolerance information and its source:

| Device/device     | TID,     | Possible SEE    | Conditions               | Fault rate             | Source |

|-------------------|----------|-----------------|--------------------------|------------------------|--------|

| component         | krad(Si) |                 |                          | (worst 5               |        |

|                   |          |                 |                          | minutes)               |        |

| 16-Mbit 130 nm    |          | MCU growing     | Particle energy:         |                        | [64]   |

| SRAM              |          | with particle   | 21, 46, 96, and          |                        |        |

|                   |          | energy          | $176 \mathrm{MeV}$       |                        |        |

| 65 nm SRAM        |          | 45% of SEE -    |                          |                        | [65]   |

| memory            |          | SEUs, 55%       |                          |                        |        |

|                   |          | -MCUs; MCU is   |                          |                        |        |

|                   |          | shorter 20 bits |                          |                        |        |

| 45 nm Single port |          | SEU             |                          | $1.2777 \cdot$         | [54]   |

| SRAM memory       |          |                 |                          | $10^{-4} \text{ up-}$  |        |

|                   |          |                 |                          | set/bit/day            |        |

|                   |          | no SEL even at: | 60                       |                        |        |

|                   |          |                 | $MeV \cdot cm^{-2}/mg$ , |                        |        |

|                   |          |                 | 125 C, voltage           |                        |        |

|                   |          |                 | 110% of                  |                        |        |

|                   |          |                 | nominal one              |                        |        |

| 65 nm Single port |          | SEU             |                          | 1.2788 ·               | [54]   |

| SRAM memory       |          |                 |                          | $10^{-4} \text{ up}$ - |        |

|                   |          |                 |                          | set/bit/day            |        |

| 90 nm SRAM        |          | SEU             | 800 km with 2.5          | the same               | [66]   |

| memory            |          |                 | mm Al shielding          | as in 2                |        |

|                   |          |                 |                          | previous               |        |

|                   |          |                 |                          | cases                  |        |

|                   |          | no SEL even at: | 117                      |                        |        |

|                   |          |                 | $MeV \cdot cm^{-2}/mg$ , |                        |        |

|                   |          |                 | voltage 120% of          |                        |        |

|                   |          |                 | nominal one              |                        |        |

Table 3.2: SRAM radiation sensitivity - empirical data

As a conclusion, modern SRAM memory will not suffer from SEL and TID during small satellite missions. However, SRAM memory is more susceptible to SEU and especially MCU (more than 50% of all SEE). Taking into account that the amount of SRAM memory(e.g. in Micro-Processor Unit (MPU)) is usually limited by a hundred

of kilobytes, the expected SEU and MCU rate is about 105 upsets per day in the worst 5 minutes of the satellite mission. It corresponds to one upset every 15 minutes.

## 3.1.3.3 Flash memory radiation induced effects

Flash memory is a non-volatile, electronically erasable and programmable memory [67]. The basic storage element includes a control gate stacked over an isolated polysilicon gate in the gate oxide (named Floating Gate (FG)), a source, and a drain [68]. Internal charge pump generators provide higher voltages than external operating supplies for programming and erasing Flash memory. The generators are radiation sensitive parts of Flash-based memory [69]. Another vulnerable part of COTS Flash devices is the complex control circuitry (Finite State Machines (FSM), output buffers).

COTS NAND flash memory is widely used in commercial and space application as a mass storage device due to its high density, high I/O bandwidth, good retention properties, and non-volatility[68, 70]. According to the experiments [71], NOR Flash memory is much more prone to SEU and SEFI effects than NAND one. It can be explained by the relative simplicity of control circuit in NOR memory in comparison with NAND Flash memory.

Critical TID level is directly connected with the reduction of FG retention capability by heavy ions[70].

Typically SEFI corrupts the large part of the memory when the read/write operation is happening. Some SEFIs will self-recover once the device is re-read, other require a power cycle or even re-initialization to return to normal operations.

The Table 3.5 contains the information about the fault-tolerance of Flash-based memory.

As a result, Flash technology offers non-volatility and high density but limited in terms of number of writes cycles and TID(mainly because of the charge pump circuit). Therefore, Flash memory is usually used for long-term storage of critical system configuration data (e.g. programme code or FPGA configuration). Flash memory is usually kept unpowered to extend its life expectancy. The main source of faults in Flash-based devices is complex peripheral circuit.

#### 3.1.3.4 FPGA components radiation induced effects

FPGAs are user-programmable devices that perform the functions of Large Scale Integration (LSI) circuitry. They include from thousands to millions programmable logic elements, each capable of performing any logic function [34]. FPGA reconfigurability, high performance, low cost [4], and relatively low-power consumption are fruitful properties that can be used to develop innovative space systems [72].

FPGA reconfigurability lets system engineers to use the most current configuration of FPGA-based processors and change their configuration during on-orbit stages[34, 73]. Moreover, FPGA enhances the OBC flexibility and adaptivity in terms of peripherals and functionality[24].

FPGA on-the-flight reconfigurability is based on the volatile (SRAM) or non-volatile (Flash) memory cells that store device programming information. These two types of memory technology (SRAM and Flash) separate reconfigurable FPGA devices

into two groups: SRAM-based FPGA and Flash-based FPGA. The third group of FPGAs is based on Anti-fuse technology and presents One-Time Programmable (OTP) devices.

The scaling decrease of Vcc alleviated the SEL susceptibility in newer devices [48]. Meanwhile, due to scaling, functional, and performance advancements of FPGA, SEU susceptibility is growing up.

Fundamentally, the radiation effects in FPGAs are the same as in any other CMOS-based digital IC, but differences of radiation sensitivities originate in switch types[48]. Overview of the FPGA groups for space applications are presented hereafter:

### SRAM-based FPGA

Volatile configuration memory of SRAM-based FPGA provides high speed for reconfiguration and unlimited number of reconfiguration cycles[74]. On the other hand, such memory is sensitive to SEU, SET, and SEFI[72, 73]. When SEU hits the configuration memory cell, the logic or routing is corrupted[75]. Moreover, SET can be transformed into permanent SEU if it changes the configuration data[74, 48]. Changes in the configuration memory can lead to SEFI of the whole component[72, 73]. Since both user and configuration memories are susceptible to SEU and SET, the whole OBC becomes very radiation sensitive [74].

However, the SRAM-based FPGAs are tolerant to TID up to 100-200 krad(Si) [73]. Moreover, their TID tolerance is becoming higher: from functionality loss at 50 krad level ten years ago[48] to 500 krad at Virtex-5 65 nm CMOS FPGA nowadays [53, p. 13].

Toshinori Kuwahara[53] evaluated the device failure rate due to radiation-induced effects at the altitude of 900 km with 99.03 degree of inclination. According to the results, Virtex-II family (XC2VP 50) has 7.4610<sup>-5</sup> device/sec failure rate due to SEU in configuration memory and 2.1010<sup>-5</sup> device/sec failure rate inside Block RAM (BRAM), the user SRAM-based memory. Thus, the configuration of SRAM-based FPGA is corrupted every four hours in space, when the user memory will have an upset approximately twice a day.

### Flash-based FPGA

Non-volatile configuration memory of Flash-based FPGA is less sensitive to SEU since the FPGA uses FG switches that are more tolerant to charge injection [72, 76]. Flash switches are immune to SEP and only logic modules determine the FPGA sensitivity [48].

FGs directly control the programmable interconnection points and the logic blocks in Flash-based FPGAs[77]. However, a FG switch (e.g. in ProASIC3E FPGA) contains two NMOS transistors and their threshold voltage is determined by the stored charge[78]. Testing results showed that the induced charge can cause SET that may temporarily alter the correct circuit implementation in Flash-based FPGA[77].

Since each programming point is potentially sensitive to SET, a temporary change in the routing structure, implemented logic function, or in driven signal value can be provoked. SET can lead to multiple faults when the transient pulses are sampled by the user memory elements (flip-flops and embedded SRAM blocks)[79]. But Flash-based FPGA configuration cannot contain permanent radiation effects, such as SEU[72, 4].

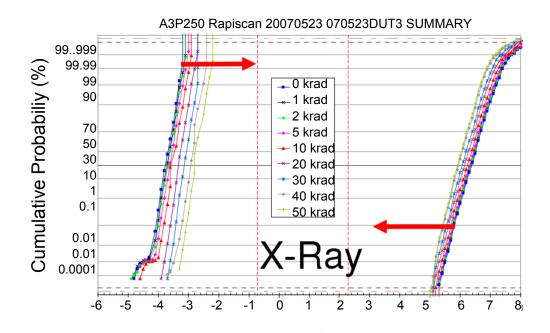

TID can lead to a variation in the threshold voltage of FG transistors disabling their reprogrammability [77, 78] (see Figure 3.6). However, the most dangerous TID effect is the malfunction of the programming and erasing FPGA circuit caused by the radiation-sensitive charge pump (similarly to Flash-based memory) [70].

Figure 3.6: Threshold voltage shifting at different TID levels [3]

The Table 3.3 contains the information about the radiation sensitivity of Flash-based FPGAs.

In summary, logical mapping, placement, and routing of Flash-based FPGAs almost do not influence the device radiation susceptibility if TID < 20 krad(Si). The propagation delay and transistor threshold voltage are slowly increasing until from 20 to 40 krad(Si). The majority of devices experience a functional failure at 40 krad(Si). User memory (flip-flops and embedded SRAM) can also be corrupted when SET are sampled by the user memory elements[79].

## Anti-fuse FPGA

As opposed to previous two FPGA types, Anti-fuse FPGAs can be programmed only once. As a result, the configuration cannot be lost due to radiation effects[73].

TID tolerance of Anti-fuse Actel FPGAs is 100-300 krad(Si), depending on the device and lot. However, Antifuse FPGAs can loose functionality at 30 krad because of TID sensitivity of a charge pump circuit[48]. The sensitivity of the Antifuse devices is determined by the CMOS logic part.

While both Anti-fuse and Flash-based FPGAs are susceptible to SET and SEU in user memory, the price of Anti-fuse FPGAs are unaffordable for small satellite industry.

| Device/     | TID      | Possible SEE or other         | Condition              | Source     |

|-------------|----------|-------------------------------|------------------------|------------|

| device com- | krad(Si) | effects                       |                        |            |

| ponent      |          |                               |                        |            |

| Flash-based | 20       |                               |                        | [53, p.13] |

| ProASIC3    |          |                               |                        |            |

|             | 50-60    | delay degradation within      |                        | [48]       |

|             |          | 10%                           |                        |            |

|             | 40       | SET linearly increases        | frequency >50          | [4]        |

|             |          | with frequency                | MHz(see                |            |

|             |          |                               | Figure 3.7)            |            |

| 30-40       |          | functional failures           |                        | [80]       |

|             |          | $\operatorname{SEL}$          | $68~MeV \cdot cm^2/mg$ | [81]       |

| A3P600      | 20-24    | delay degradation $\leq 10\%$ |                        | [82, 83,   |

| ProASIC3    |          |                               |                        | 84, 78]    |

| Flash-based | 40       | 21% delay degradation; Icc    |                        | [78]       |

| ProASIC3,   |          | growth, due to FG leakage     |                        |            |

| 130-nm      |          | current growth                |                        |            |

|             | 55       | Icc is $200\%$ of nominal one |                        |            |

|             |          | $\operatorname{SET}$          | $1.7298 \cdot 10^{-6}$ |            |

|             |          |                               | upsets/Logic Cell      |            |

|             |          |                               | Like-Inverter          |            |

|             |          |                               | (LCI)/day              |            |

Table 3.3: Flash-based FPGAs radiation sensitivity - empirical data

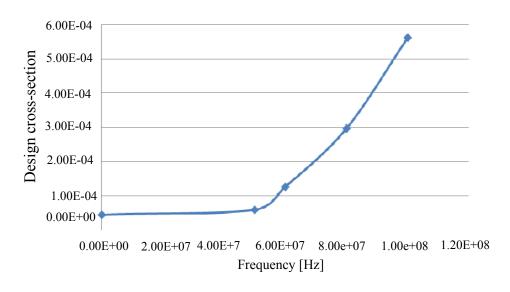

Figure 3.7: SEP sensitivity wrt frequency [4]

#### 3.1.3.5 MPU radiation induced effects

SEU and SEFI threshold for commercial multiprocessors range from 0.2 to 9  $MeV \cdot cm^2/mg$  [85]; such low threshold causes from multiple upsets per day to a single upset per year.

SEU can occur in MPU causing data errors. MPU is also susceptible to SEFI[35]. In comparison with memory storage, SEUs are rare events because of MPU's small sensitive cross-section.

MPU contains General-Purpose Register (GPR) and Special-Purpose Register (SPR) and the corresponding consequences of their corruption are very different. SEU in program counter causes the wrong program flow, meanwhile the SEU in GPR causes the data corruption of the algorithm being executed.

Although, the probability of MPU SEP is small in comparison with memory faults, the number of mitigation techniques were created for MPU due to its importance. Since the cache memory occupies the majority of MPU area, proper mitigation techniques have to be implemented to avoid data corruption caused by cache SEUs and MCUs.

#### 3.1.4 Conclusion

According to the aforementioned analysis, the majority of modern COTS parts are tolerant to the mission TID (see Section 3.1). Meanwhile, SEUs and MCUs stay the main issues in volatile memory when SEFI poses a thread in Flash-based memory .

According to the investigation of published radiation test results, the estimated TID and LET cannot lead to destructive consequences in COTS components (e.g. SEL or SHE). Thus, the presented fault models are focused on SEE (see Chapter 5).

The fault-rates (8.9) are calculated using the output LET spectrum from SPEN-VIS system and cross-sections from empirical observations; the worst case scenario is presented in Table 8.9.

| Component  | Malfunction at | SEL at LET | SEU rate             | SEFI rate (event/ |

|------------|----------------|------------|----------------------|-------------------|

| type       | TID (krad(Si)) | (MeV -     | (upset/bit/          | device/ day)      |

|            |                | cm2/mg)    | day)                 |                   |

| DRAM       | > 20           | 51         | $1.45 \cdot 10^{-8}$ | 0.26              |

| SRAM       | 20             | 117        | $1.27 \cdot 10^{-4}$ | not observed      |

| Flash NAND | 15             | -          | $1.38 \cdot 10^{-9}$ | 0.013             |

| Flash NOR  | 10-20          | -          | tolerant             | 0.0013            |

Table 3.4: Radiation sensitivity of COTS components, the worst case

From radiation-immunity point of view, Flash-based FPGAs better suit small satellite applications in comparison with SRAM FPGAs. At the same time, it is almost inevitable to use hard Central Processing Unit (CPU) to provide high power-efficiency and general-purpose capabilities. Consequently, a heterogeneous SoC with the hard core and Flash-based FPGA fabric is a suitable choice for the OBC of small satellites. SmartFusion SoC[6] meets these two requirements and incorporates Cortex-M3 ARM hard core[86] and ProASIC Flash-based FPGA fabric [87].

| Device/     | TID,   | Possible SEE or         | Cond.                    | Fault rate              | Source   |

|-------------|--------|-------------------------|--------------------------|-------------------------|----------|

| device      | krad   | worn-out                |                          | (worst 5                |          |

| compon-     | (SiO2) |                         |                          | minutes)                |          |

| ent         |        |                         |                          |                         |          |

| NAND        |        | worn-out                | $(10^5)$ - $(10^6)$      |                         | [67]     |

|             |        |                         | Program /                |                         |          |

|             |        |                         | Erase (P/E)              |                         |          |

|             |        |                         | cycles                   |                         |          |

| 4, 8 Gb 60  |        | errors during P/E       | after $10^6 \text{ P/E}$ |                         | [88]     |

| nm NAND     |        | cycles                  | cycles and 100           |                         |          |

| G           | 15.00  | 11 1 1                  | krad                     |                         | [60, 03] |

| Samsung     | 15-28  | some blocks can be      |                          |                         | [68, 2]  |

| 90nm        |        | programmed again after  |                          |                         |          |

| NAND        | 70     | 500 hours unbiased      |                          |                         | [00]     |

| Other tests | 50     | failure of charge pump  |                          |                         | [89]     |

| Other tests |        | circuits 814 krad       |                          |                         | [89]     |

| Other tests |        | SEU in control logic    |                          |                         | [68]     |

| Other tests |        | which is SEFI during    |                          |                         | [00]     |

|             |        | R/W cycles,             |                          |                         |          |

| 4 Gb        |        | SEU                     |                          | $1.3871 \cdot 10^{-9}$  | [90]     |