# INTERCONNECT SCI-EIVES FOR STRETCHABLE ARRAY-TYPE IMCROSYSTEVIS

# Interconnect schemes for stretchable array-type microsystems

## **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus Prof. ir. K. C. A. M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen

op woensdag 6 april 2011 om 12.30 uur

door

# **Sebastian SOSIN**

Master of Science Microsystems Engineering, Universitatea Politehnica București, geboren te Boekarest, Roemenië. Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. P. M. Sarro

#### Samenstelling promotiecommissie:

Rector Magnificus, voorzitter

Prof. dr. P. M. Sarro

Dr. M. Bartek

Technische Universiteit Delft, promotor

Technische Universiteit Delft, copromotor

Prof. dr. R. A. M. Wolters Universiteit Twente

Prof. dr. ir. R. Dekker

Prof. dr. P. J. French

Prof. dr. ir. L. J. Ernst

Prof. dr. J. N. Burghartz

Technische Universiteit Delft

Technische Universiteit Delft

Technische Universiteit Delft

Universität Stuttgart, Duitsland

Prof. dr. ir. C. I. M. Beenakker Technische Universiteit Delft, reservelid

The research presented in this thesis was financially supported by the Dutch Bsik program MicroNed and the Delft Centre for Mechatronics and Microsystems (DCMM).

Sebastian Sosin, Interconnect schemes for stretchable array-type microsystems, Ph.D. thesis, Delft University of Technology, with summary in Dutch.

ISBN: 978-90-5335-390-5

#### Copyright © 2011 by Sebastian Sosin

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without the permission of the author.

Printed by Ridderprint BV, Ridderkerk, the Netherlands

# **Contents**

| 1 | Introduction                                 |          |                                              |    |  |  |

|---|----------------------------------------------|----------|----------------------------------------------|----|--|--|

|   | 1.1                                          | Motiva   | tion                                         | 1  |  |  |

|   | 1.2                                          | Scope of | of the thesis                                | 4  |  |  |

|   | 1.3                                          | Organiz  | zation of the thesis                         | 5  |  |  |

|   | 1.4                                          | Referer  | nces                                         | 6  |  |  |

| 2 | Stretchability of Silicon Based Microsystems |          |                                              |    |  |  |

|   | 2.1                                          | Definit  | ion of stretchability                        | 7  |  |  |

|   | 2.2                                          | Mechai   | nical properties of materials                | 8  |  |  |

|   | 2.3                                          | Materia  | al selection and material data               | 14 |  |  |

|   | 2.4                                          | State of | f the art                                    | 16 |  |  |

|   | 2.5                                          | System   | aspects of stretchable silicon microsystems  | 25 |  |  |

|   | 2.6                                          | Fabrica  | tion compatibility, handling and reliability | 26 |  |  |

|   | 2.7                                          | Conclu   | sions                                        | 28 |  |  |

|   | 2.8                                          | Referer  | nces                                         | 29 |  |  |

| 3 | Stretchable Interconnect Schemes             |          |                                              |    |  |  |

|   | 3.1                                          | Introdu  | action                                       | 30 |  |  |

|   | 3.2                                          | Genera   | l requirements on stretchable interconnects  | 30 |  |  |

|   | 3.3                                          | Geome    | try for stretchability                       | 31 |  |  |

|   |                                              | 3.3.1    | Mesh geometry                                | 31 |  |  |

|   |                                              | 3.3.2    | Spiral geometry                              | 32 |  |  |

|   |                                              | 3.3.3    | Meander and horseshoe geometry               | 32 |  |  |

|   |                                              | 3.3.4    | Parametric structure description             | 33 |  |  |

|   | 3.4                                          | Finite-e | element simulation                           | 35 |  |  |

|   |                                              | 3.4.1    | Meander interconnects analysis               | 38 |  |  |

|   |                                              | 3.4.2    | Horseshoe interconnect analysis              | 39 |  |  |

|   |                                              | 3.4.3    | Mesh interconnect analysis                   | 40 |  |  |

|   |                                              | 3.4.4    | Analysis conclusions                         | 42 |  |  |

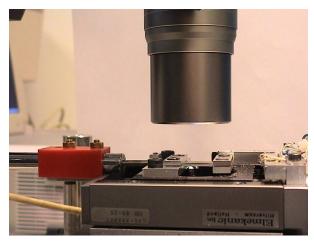

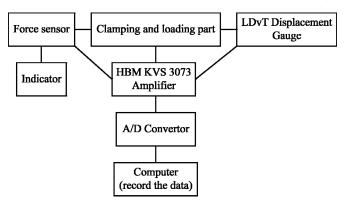

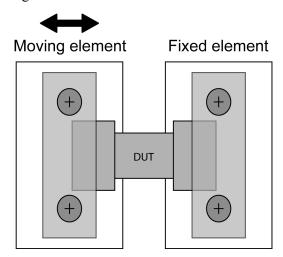

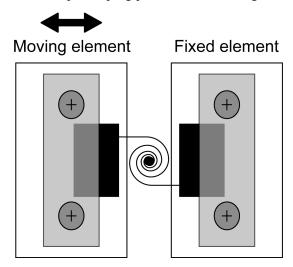

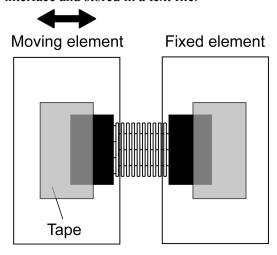

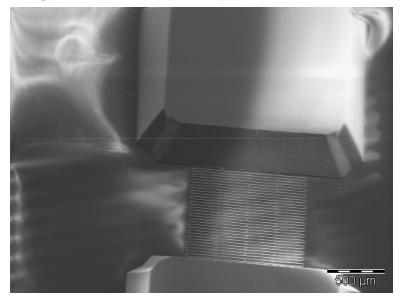

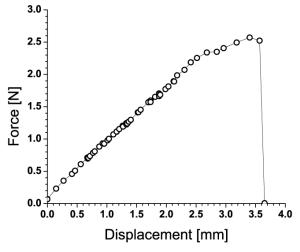

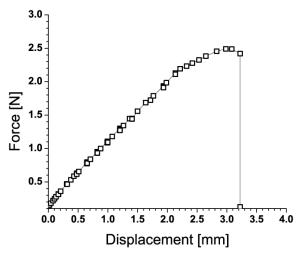

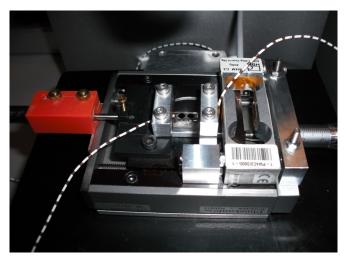

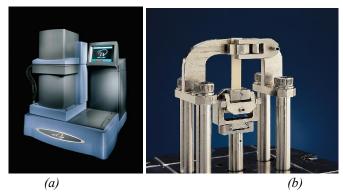

|   | 3.5                                          | Mechai   | nical characterization and test set-up used  | 42 |  |  |

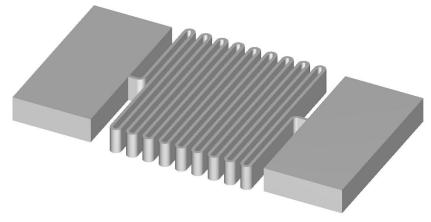

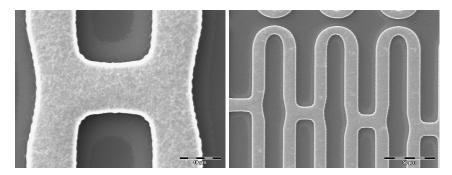

|   | 3.6                                          | High-as  | spect-ratio-silicon springs                  | 44 |  |  |

|   |                                              |          | Design and optimization                      | 45 |  |  |

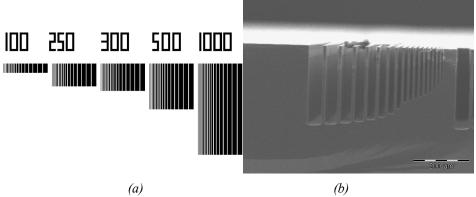

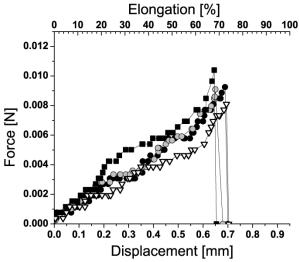

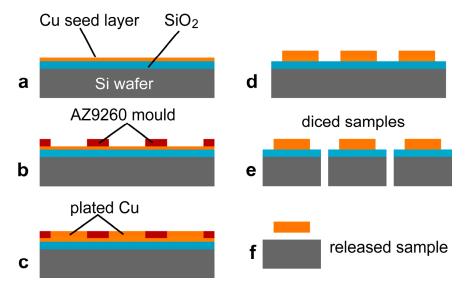

|   |                                              | 3.6.2    | Fabrication                                  | 47 |  |  |

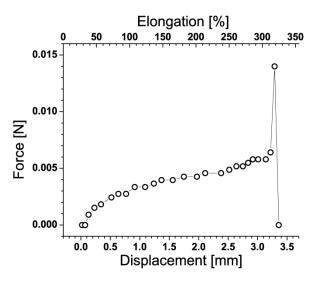

|   |                                              | 3.6.3    | Characterization results                     | 50 |  |  |

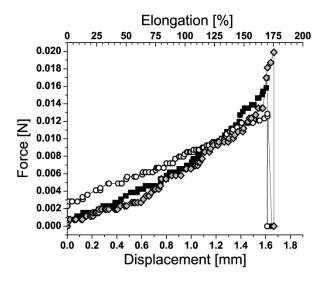

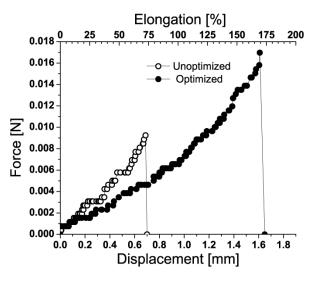

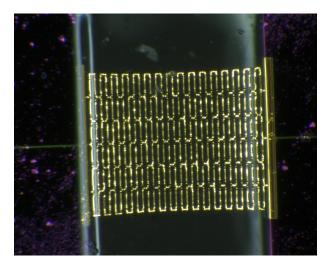

|   | 3.7                                          | Free-sta | anding metal interconnects                   | 54 |  |  |

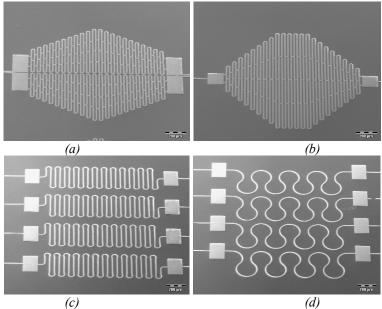

|   |                                              | 3.7.1    | Geometry selection                           | 55 |  |  |

|   |                                              | 3.7.2    | Fabrication                                  | 56 |  |  |

|   |                                              | 3.7.3    | Characterization results                     | 57 |  |  |

|   |                                              | 3.7.4    | Parylene coating for strength modification   | 60 |  |  |

|   | 3.8                                          |          |                                              |    |  |  |

|   | 39                                           | Referen  | nces                                         | 66 |  |  |

| 4    | PDN                             | MS-Embedded Silicon Electronics Arrays                         | 67  |  |

|------|---------------------------------|----------------------------------------------------------------|-----|--|

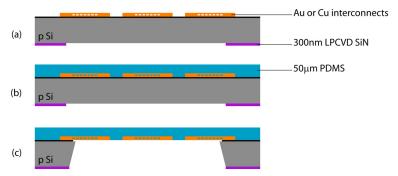

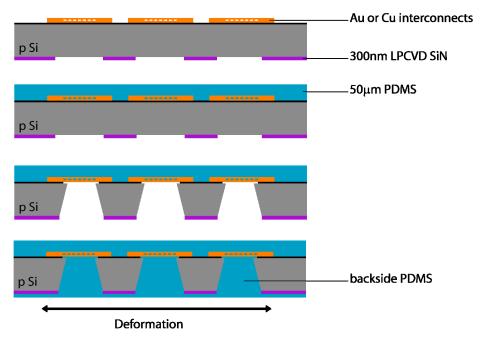

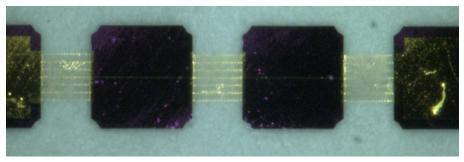

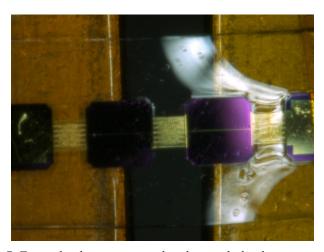

|      | 4.1                             | PDMS-embedded electronics concept                              | 67  |  |

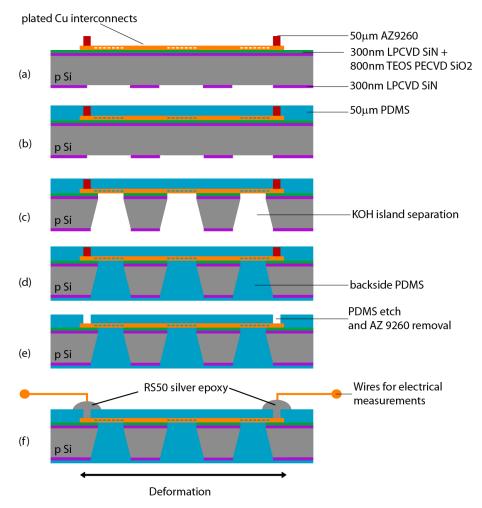

|      |                                 | 4.1.1 Fabrication process development                          | 68  |  |

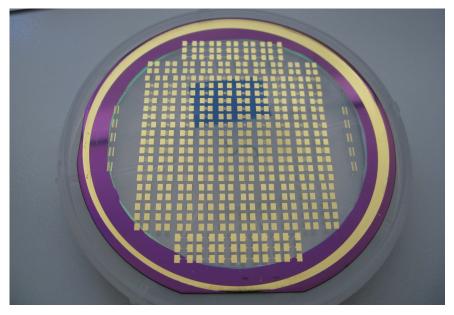

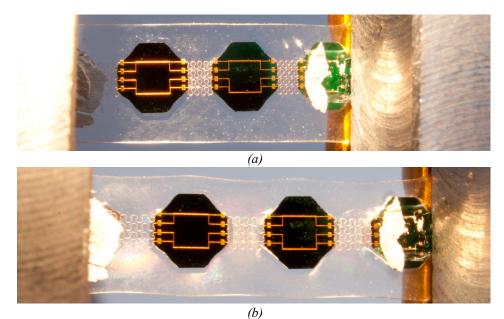

|      |                                 | 4.1.2 Characterization results                                 | 72  |  |

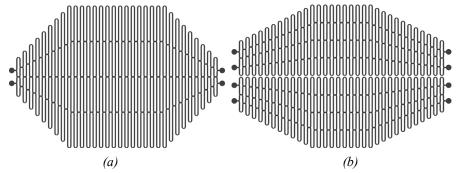

|      | 4.2                             | Mesh shape optimization                                        | 75  |  |

|      | 4.3                             | Fabrication of PDMS-embedded Si electronics arrays             | 76  |  |

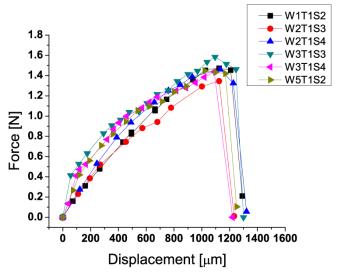

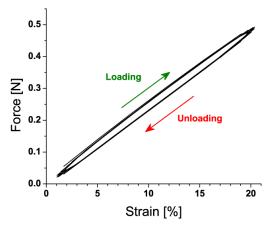

|      | 4.4                             | Array description                                              | 77  |  |

|      | 4.5                             | Measurements                                                   | 78  |  |

|      |                                 | 4.5.1 Tensile testing of fabricated arrays                     | 79  |  |

|      |                                 | 4.5.2 Electrical measurements of fabricated samples            | 80  |  |

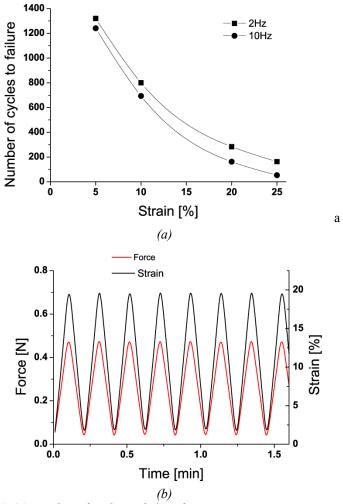

|      |                                 | 4.5.3 Cyclic tensile testing                                   | 83  |  |

|      | 4.6                             | Failure of fabricated PDMS arrays                              | 85  |  |

|      | 4.7                             |                                                                | 88  |  |

|      | 4.8                             | References                                                     | 89  |  |

| 5    | Conclusions and Recommendations |                                                                |     |  |

|      | 5.1                             |                                                                | 90  |  |

|      | 5.2                             |                                                                | 92  |  |

|      | 5.3                             | References                                                     | 93  |  |

| A    | App                             | endix A: High-Aspect-Silicon-Springs Flow Chart                | 94  |  |

| В    | App                             | endix B: Free-Standing Copper Interconnects Flow Chart         | 95  |  |

| C    | <b>App</b><br>Cha               | <b>vendix</b> C: PDMS-Embedded Silicon Electronics Arrays Flow | 96  |  |

| Sur  | nmar                            | y                                                              | 98  |  |

| San  | nenva                           | tting                                                          | 100 |  |

| List | t of P                          | ublications                                                    | 102 |  |

| Acl  | knowl                           | edgements                                                      | 104 |  |

| Abo  | out th                          | e Author                                                       | 106 |  |

# **Chapter 1:**

## Introduction

#### 1.1. Motivation

From its beginning in the 1950s, microelectronics has been working to make better, faster and more reliable IC's. This was quite accurately predicted by Gordon Moore in 1965 when he stated that the number of transistors that can be placed on an integrated circuit will increase exponentially, doubling approximately every two years.

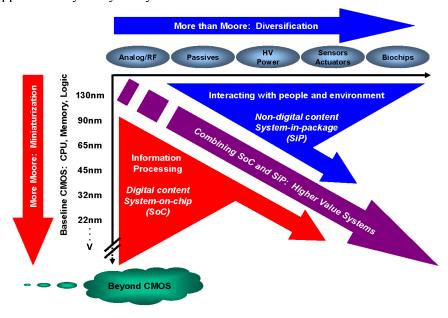

**Figure 1-1.** The combined need for digital and non-digital functionalities in an integrated system is translated as a dual trend in the International Technology Roadmap for Semiconductors: miniaturization of the digital functions ("More Moore") and functional diversification ("More-than-Moore") [1.1].

The microelectronics community is working on finding new solutions to keep Moore's law alive by miniaturization (an approach called "More Moore"). Through transistor scaling, one obtains a better performance-to-cost ratio of products, which drives an exponential growth of the semiconductor market. This in turn allows for further investments in semiconductor technologies which will fuel further scaling

The industry is now faced with the increasing importance of a new trend, "More than Moore" (MtM or better named, "Diversification", see Figure 1-1), where added value to devices is provided by incorporating functionalities that do not necessarily scale according to Moore's law. This research direction deals with products and technology that are based upon or derived from silicon technologies, but do not simply scale according to Moore's law. Typical examples are RF, power/high-voltage devices, passives, sensors, actuators, MEMS, bio-chips, bio-systems, microfluidics, system in a package, solid-state lighting, etc.

Flexible printed circuit boards are being used to fabricate foldable electronics but the deformation is limited to one axis at a time. In recent years, many groups have started investigating microelectronic systems that can truly deform while maintaining their functionality.

One of the best examples of stretchable electronic systems is the concept of "artificial skin." It is supposed to have not only all the sensing capabilities of our skin but also similar mechanical behavior (Figure 1-2).

**Figure 1-2.** Artificial electronic skin being developed by Nokia and Cambridge University [1.2].

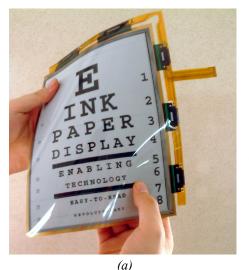

A flexible display such as an e-paper is an important application with promising demonstrators being presented (Figure 1-3). Having rollable/bendable screens reduces weight and increases portability. Applications are in advertising, media, public notice boards, mobile computing, etc.

*(b)*

Figure 1-3. (a) The LG and Phillips E-ink display [1.3], and (b) the Polymer Vision (now Wistron) portable e-reader with a 5-inch fold-up display [1.4].

Shapeable and elastic integrated circuits on soft elastomeric substrates are creating new research opportunities for biomedicine, cell research and medical prosthetics and implants. Cell culture mediums that have soft substrates with integrated circuits and stretchable conductors can improve drug testing and invivo tissue research. Smart medical prosthetics can restore human sensory and motor functions and medical implants that conform to the surrounding tissue can minimize the patient's discomfort. Medical implants that conform to the surrounding tissues by being elastic and flexible can enhance the patients comfort. Bladder implants for treating incontinency, brain electrodes that treat epilepsy and depression, fall-detection monitors for the elderly or intelligent textiles that monitor health conditions are products that can be made better using stretchable electronics.

For consumer electronics, ambient intelligence is the keyword for the next decade. This means that a person carries more and more devices, not only on his body but also inside the body. This affects the way devices are designed: they must be light weighted, must take on the shape of the object in which they are integrated, and must even follow complex movements of these objects, hence the need for stretchability. Shapeable electronics also create a more natural environment for living tissue research or drug testing, leading to faster diagnostics or faster drug development.

Smart textiles, biomedical applications, cell research, medical prosthetics, automotive industry, consumer electronics, displays, all are the domains that will welcome flexible, stretchable and elastic electronic systems.

# 1.2. Scope of the thesis

Most of the research done on stretchable systems focuses on hybrid integration of silicon chips on a pre-fabricated carrier, followed by encapsulation using molding of a rubber-like compound. Several groups working on stretchable electronics have reported elongation levels starting from 12-15 % (Lacour, elastically stretchable TFT inverter [1.5]) up to 40-60 % (polyimide-supported copper interconnects [1.6, 7]). Results from the European Project STELLA show demonstrators intended for applications enclosing or attached to the human body (relatively low elongation levels, up to 10 %) like clothing, smart band aid, shoe insole for diabetes monitoring and activity monitor [1.8].

The goal of this thesis work is to develop a wafer-level CMOS-compatible post-processing module that allows transformation of rigid silicon wafers containing MEMS/CMOS devices into stretchable systems using conventional clean room equipment. The fabrication process does not, however, exclude the possibility of hybrid integration of additional chips. This approach based on the limited silicon wafer size is suitable for applications requiring small-area stretchable systems like biomedical implants.

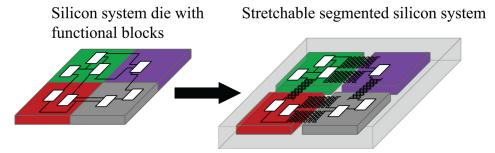

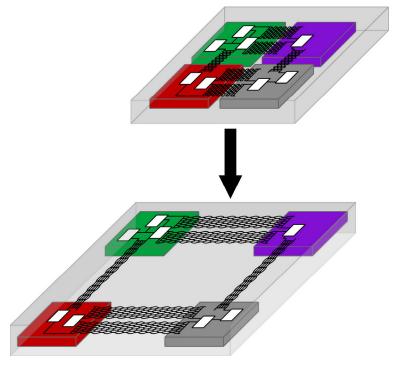

**Figure 1-4.** Illustration of the segmentation method showing (left) monolithic silicon system die with different functional blocks, and (right) segmented system with interconnect network embedded in a protective polymer layer.

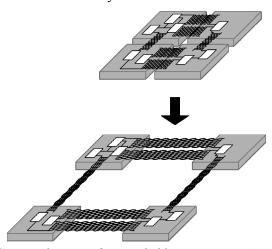

The selected fabrication approach (Figure 1-4) modifies the initially rigid silicon substrate by segmenting it into rigid islands connected by an elastic medium. The elastic medium linking the functional islands must provide electrical connections between the segments (using flexible metal interconnects) and mechanical support (using polymers, structured silicon). The focus of this work is on the stretchable interconnect scheme.

The following chapters present the development process of such a stretchable system, starting from testing of individual spring-like structures to the integration of all components into one stretchable silicon-based array.

The interconnect network must be strong enough to withstand tensile loading without sacrificing electrical performance. For this reason metal layers

#### INTRODUCTION

are selected instead of conductive polymers. While metal layers have limited elasticity, when patterned for stretchability several geometries (such as mesh, meander or horse shoe) can withstand large strains.

The processing compatibility with already integrated MEMS/CMOS devices requires that the post-processing module has adequately low thermal budget and all of the used fabrication steps will have negligible influence on the performance of already integrated devices.

The developed post-processing module is applicable on wafer scale, reducing handling and assembly times, but if needed, hybrid substrates with chips provided by different technologies could be used without major process modifications.

Biomedical applications are one of the most promising areas and biocompatibility should be taken into account when selecting materials and designing process flow.

# 1.3. Organization of the thesis

Chapter 1 presents the motivation behind this work, presenting a short overview of domains where stretchability can increase the performance of existing products.

In Chapter 2 a concise theory of elasticity and material properties used throughout the thesis is introduced. Furthermore, an overview of the state of the art in stretchable electronics research and the fabrication approaches used are given.

Chapter 3 presents the analysis of different free-standing geometries chosen for the stretchable interconnect network. The FE simulations are followed by tensile testing of free-standing High-Aspect-Ratio-Silicon (HARS) springs and copper meshes. Simulation and tensile testing results are used to design a new set of metal interconnects.

Chapter 4 starts with the development of the fabrication process for stretchable silicon electronics arrays. The fabrication process is developed in steps, starting from fabrication of metal interconnects on polydimethylsiloxane (PDMS) membranes and ending with the fabrication of a functional stretchable silicon-based arrays. In the final part of Chapter 4, the results of both mechanical and electrical testing under single and cyclic tensile loading are presented.

Chapter 5 ends the thesis by presenting conclusions and recommendations for future work

## 1.4. References

- [1.1] Arden, W., et al., "More-than-Moore" White Paper, 2010, white paper, International Technology Roadmap for Semiconductors (ITRS).

- [1.2] Stretchable Electronic Skin, Nokia Research Center, Cambridge, UK, http://research.nokia.com/news/9510, Feb. 2011.

- [1.3] Flexible Displays, LG Display: Future Technology, http://www.lgdisplay.com/, Feb. 2011.

- [1.4] Readius eBook reader/cell phone prototype from Wistron/PolymerVision, http://wiki.mobileread.com/wiki/Readius, 2010.

- [1.5] Lacour, S.P., Jones, J., Suo, Z., and Wagner, S., Design and performance of thin metal film interconnects for skin-like electronic circuits, IEEE Electron Device Letters, 2004, 25(4), pp. 179-181.

- [1.6] Verplancke, R., Sterken, T., Axisa, F., and Vanfleteren, J., *Development of a thin-film stretchable electrical interconnection technology for biocompatible applications*, 3<sup>rd</sup> Electronic System-Integration Technology Conference (ESTC), 2010, Berlin, Germany, pp. 1-4.

- [1.7] Axisa, F., Brosteaux, D., De Leersnyder, E., Bossuyt, F., Vanfleteren, J., Hermans, B., and Puers, R., *Biomedical Stretchable Sytems using MID Based Stretchable Electronics Technology*, 29<sup>th</sup> Annual International Conference of the IEEE Engineering in Medicine and Biology Society (EMBS), 2007, Lyon, France, pp. 5687-5690.

- [1.8] European Project, http://www.stella-project.de, Feb. 2011.

# Chapter 2:

# Stretchability of Silicon-Based Microsystems

In the first part of this chapter the theory of material properties used throughout the thesis for analysis of stretchable electronics is presented. The theoretical part is followed by an overview of the state of the art in stretchable electronics with examples of realized stretchable systems. The last part deals with system aspects, fabrication, handling and reliability of stretchable silicon microsystems.

# 2.1. Definition of stretchability

According to Merriam-Webster's dictionary, the verb "to stretch" is defined as "a: to enlarge or distend especially by force; b: to extend or expand as if by physical force." Stretchable electronics systems must function as designed while being able to conform onto complex shapes, expand, and contract reversibly (within certain limits).

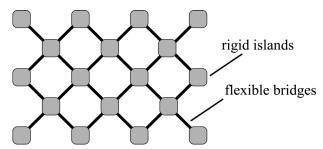

This means that a silicon microsystem has to modify its surface area and shape in order to contract/expand and to preserve its functionality when an external force is applied. A definition valid for all stretchable electronic system research approaches is that a stretchable electronic system is made of a number of rigid or flexible component islands, which are connected by an elastic and electrically conductive medium.

Figure 2-1. Illustration of the stretchable system concept using rigid islands and stretchable interconnects/substrate.

## 2.2. Mechanical properties of materials

The phrase "stretchable silicon array microsystem" can be misleading. Silicon, the main material in almost all the integrated circuits, is intrinsically brittle and rigid, when compared to metals or polymers currently used in microfabrication. Silicon wafers can become flexible by thinning them and useful degrees of flexibility can be achieved for thicknesses below 50  $\mu$ m but large scale elasticity of bulk silicon is impossible to achieve without using some processing tricks and/or additional materials providing elasticity.

When talking about stretchable systems, terms like stress, strain or Young's modulus are used to describe the systems and the materials they are made of. Explaining these terms, even if briefly, is necessary for understanding of the following chapters of this thesis [2.1].

In a body, two atoms or molecules are subjected to attraction or repulsion forces that act along a line joining the two particles. These forces hold together the body and are called "internal forces." Similar to Newton's universal gravity law, they vary inversely as an exponent of the radial distance that joins the two particles.

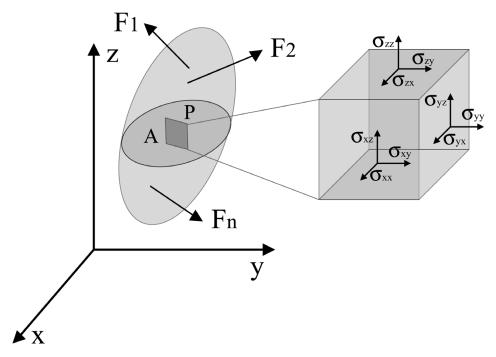

Figure 2-2. Stress in a loaded deformable body.

When the body is subjected to external forces (Figure 2-2), its shape changes thus changing the distance between internal particles. Therefore internal forces also change and if their values exceed a certain limit, the body will break apart.

The change in the intensity of the internal forces is called stress and characterizes the strength of a body.

A single particle P of a body is subjected to many forces that can be replaced by the resulting force that acts on that particle. Depending on the location of the point, the magnitude and direction of the resulting force will vary, meaning that when the body is subjected to external forces, an internal force distribution is generated in the body.

The internal distributed force F on an imaginary surface A through the body divided by this surface area is called *stress on a surface*. The force that is normal to the surface is called the *normal stress* ( $\sigma$ ) on a surface while the force parallel to the surface is called the *shear stress* ( $\tau$ ):

$$\sigma_{AVG} = \frac{F_n}{A} \approx \sigma \tag{2.1}$$

$$\tau_{AVG} = \frac{F_s}{A} \approx \tau \tag{2.2}$$

Normal stress can be described as internal forces developed as material resistance to the *pulling apart* or *pushing together* of two adjoining planes of the imaginary surface. Shear stress can be described as internal forces developed as material resistance to *sliding of two adjoining planes* along the imaginary surface

*Tensile stress* is a normal stress that pulls the surface away from the body while *compressive stress* pushes the surface into the body.

In general, stress is not uniformly distributed over the cross-section of a material body, and consequently the stress at a point in a given region is different from the average stress over the entire area. Therefore, it is necessary to define the stress not over a given area but at a specific point in the body (point "P" in Figure 2-2). According to Cauchy [2.1], the stress at any point in an object assumed to behave as a continuum is completely defined by the nine components  $\sigma_{ij}$  of a second-order tensor known as the Cauchy stress tensor,  $\sigma$ , where  $\sigma_{ii}$  and  $i = j \in (x,y,z)$  represents normal stress components while  $\tau_{ij}$ ,  $i \neq j$ , represents shear stress components (2.3). Shear stress is symmetric, meaning that  $\tau_{ij} = \tau_{ji}$ .

$$[\sigma] = \begin{bmatrix} \sigma_{xx} & \tau_{xy} & \tau_{xz} \\ \tau_{yx} & \sigma_{yy} & \tau_{yz} \\ \tau_{zx} & \tau_{zy} & \sigma_{zz} \end{bmatrix}$$

(2.3)

When a body is subjected to an external force, a change in shape appears. The measure of this change is called *strain*. Strain, defined as the ratio between the change in length  $\delta L$  and the original length  $L_0$ , can be easily converted into

percentage. Such representation of the strain makes it easier to describe the stretching effects on an object's dimensions. As an example, if a 100 cm bar is stretched to 110 cm, then the strain can be expressed as  $\varepsilon = 10 \%$ .

$$\varepsilon = \frac{L - L_0}{L_0} = \frac{\delta L}{L_0} \tag{2.4}$$

and

$$\varepsilon = \frac{\delta L}{L_0} * 100\% \tag{2.5}$$

The *shear strain* is defined as the change in angle from the right angle as shown in Eq. 2.6, where  $\alpha$  is the final angle.

$$\gamma = \frac{\pi}{2} - \alpha \tag{2.6}$$

A material is said to be elastic if it returns to its original, unloaded dimensions when the load is removed. A particular form of elasticity (which applies to a wide range of engineering materials, at least over a part of their load range) produces deformations that are proportional to the loads producing them. Since loads are proportional to the stresses they produce and deformations are proportional to the strain, this also implies that, while materials are elastic, stress is proportional to strain (Eq. 2.7). *Hooke's law*, in its simplest form, was initially stated in 1676 by British physicist Robert Hooke as a Latin anagram, "*Ut tensio, sic vis*" meaning "*As the extension, so the force*."

$$\frac{stress}{strain} = \frac{\sigma}{\varepsilon} = const. \tag{2.7}$$

Considering a linear material model, where there is a linear relationship between stress and strain, Hooke's law can be written as:

$$\begin{cases}

\mathcal{E}_{xx} \\

\mathcal{E}_{yy} \\

\mathcal{E}_{zz} \\

\gamma_{yz} \\

\gamma_{zx} \\

\gamma_{xy}

\end{cases} =

\begin{bmatrix}

C_{11} C_{12} C_{13} C_{14} C_{15} C_{16} \\

C_{21} C_{22} C_{23} C_{24} C_{25} C_{26} \\

C_{31} C_{32} C_{33} C_{34} C_{35} C_{36} \\

C_{41} C_{42} C_{43} C_{44} C_{45} C_{46} \\

C_{51} C_{52} C_{53} C_{54} C_{55} C_{56} \\

C_{61} C_{62} C_{63} C_{64} C_{65} C_{66}

\end{bmatrix}

\begin{cases}

\sigma_{xx} \\

\sigma_{yy} \\

\sigma_{zz} \\

\tau_{yz} \\

\tau_{zx} \\

\tau_{xy}

\end{cases}$$

(2.8)

The matrix  $C_{ij}$  in Eq. 2.8 is called the compliance matrix and it is a symmetric matrix,  $C_{ij} = C_{ji}$ , with  $i, j \in \{1..6\}$ . Isotropic materials require only

#### STRETCHABILITY OF SILICON-BASED MICROSYSTEMS

two independent material constants and Hooke's law for isotropic materials is defined by Eq. 2.9.

$$\begin{cases}

\mathcal{E}_{xx} \\

\mathcal{E}_{yy} \\

\mathcal{E}_{zz} \\

\gamma_{yz} \\

\gamma_{xx} \\

\gamma_{xy}

\end{cases} =

\begin{bmatrix}

C_{11} C_{12} C_{12} & 0 & 0 & 0 \\

C_{12} C_{11} C_{12} & 0 & 0 & 0 \\

C_{12} C_{11} C_{12} & 0 & 0 & 0 \\

C_{12} C_{12} C_{11} & 0 & 0 & 0 \\

0 & 0 & 0 & 2(C_{11} - C_{12}) & 0 & 0 \\

0 & 0 & 0 & 0 & 2(C_{11} - C_{12}) & 0 \\

0 & 0 & 0 & 0 & 0 & 2(C_{11} - C_{12})

\end{cases}$$

$$(2.9)$$

Equation 2.9 can be rewritten in equation form using three material constants (based on the original two): the modulus of elasticity E, Poisson's ratio v and the shear modulus of elasticity G:

$$C_{11} = \frac{1}{E} \tag{2.10}$$

$$C_{12} = -\frac{v}{E} \tag{2.11}$$

$$2(C_{11} - C_{12}) = \frac{1}{G} \tag{2.12}$$

Substituting  $C_{II}$  and  $C_{I2}$  in the last relationship, the shear modulus of elasticity is defined:

$$G = \frac{E}{2(1+\nu)} \tag{2.13}$$

Poisson's ratio is a dimensionless measure of the lateral strain that occurs in a body due to longitudinal strain, if the load on the object is restrained within the elastic range:

$$v = \frac{\mathcal{E}_d}{\mathcal{E}_L} \tag{2.14}$$

The negative sign is usually ignored, leaving the coefficient simply as a ratio of strain magnitudes but it must be remembered that the longitudinal strain induces a lateral strain of opposite sign.

By rewriting Eq. 2.9 with the previous substitutions, a more simplified version, called *generalized Hooke's law*, valid only for linear, elastic, isotropic materials is given by equation:

$$\begin{cases}

\varepsilon_{xx} \\

\varepsilon_{yy} \\

\varepsilon_{zz}

\end{cases} = \frac{1}{E} \begin{bmatrix}

1 & -\nu & -\nu \\

-\nu & 1 & -\nu \\

-\nu & -\nu & 1

\end{bmatrix} \begin{cases}

\sigma_{xx} \\

\sigma_{yy} \\

\sigma_{zz}

\end{cases}$$

(2.15)

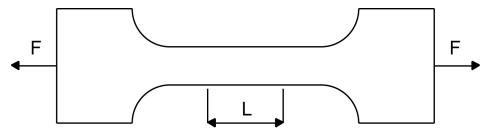

The strength of a material can be determined with a tensile test using a "dog bone", illustrated in Figure 2-3. The "dog-bone" structure has uniform cross section and it is subjected to a gradually increasing tensile load until failure occurs. The length change of the gauge length of the bar is recorded and a graph is produced. Such a graph is called the *tensile stress* – *strain diagram* of the material (see Figure 2-4).

Figure 2-3. "Dog-bone" structure used for tensile measurements.

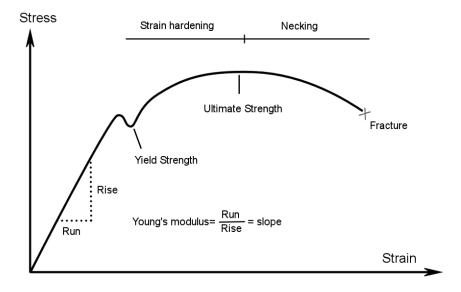

**Figure 2-4.** Typical tensile stress - strain diagram for a ductile material showing various stages of deformation.

Several points can be identified in a tensile stress-strain diagram, depending on the material. If the stress in a body subjected to a load returns to zero once the load is removed, then the material of the body is said to have been strained within the *elastic limit* or that the material is *perfectly elastic*. If under loading the strain is linearly proportional to the load, the material is said to be strained within the limit of *linear elasticity*. When the load produces a stress that exceeds the elastic limit, the strain does not disappear upon the removal of the load.

Yield strength  $\sigma_{YS}$ , (also called elastic limit) is the limit beyond which permanent deformation will occur.

Under tensile stress plastic deformation is characterized by a *strain hardening* region and a necking region and finally, fracture (also called rupture). During strain hardening the material becomes stronger through the movement of atomic dislocations. The necking phase is indicated by a reduction in cross-sectional area of the specimen.

Necking begins after the *ultimate tensile strength* ( $\sigma_U$ ) is reached. Ultimate strength is defined as the maximum stress attained in the stress-strain diagram. During necking, the material can no longer withstand the maximum stress and the strain in the specimen rapidly increases. Plastic deformation ends with the fracture of the material.

As it can be observed in Figure 2-4, the plastic range covers a much wider part of the strain axis than the elastic range. The capacity of a material to allow these large extensions (i.e., the ability to be drawn plastically) is named ductility. Materials with high ductility are named ductile materials.

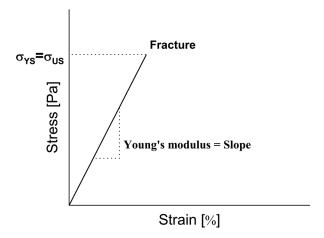

Materials with low ductility are named brittle materials. There is little or no necking at fracture for brittle materials. Brittle materials such as silicon, concrete, carbon fiber and polymers such as poly(methyl-methacrylate) (PMMA) and polystyrene do not have a yield point, and do not strain-harden (Figure 2-5). Therefore, the yield strength and ultimate strength are the same.

*Figure 2-5. Typical stress-strain curve for brittle materials.*

#### 2.3. Material selection and material data

Selection of materials has to take into account several factors: mechanical properties, electrical properties, deposition and patterning methods and IC fabrication compatibility. Materials used for stretchable silicon arrays can be divided into three groups. In the first group, there are materials used for the fabrication of array elements, mainly silicon. Materials used for the stretchable part of an array form the second group. Silicon can also be part of this group, along with metals common in IC fabrication like copper and aluminum. The last group is for materials used as mechanical support and extra protection and it is composed of polymers such as Parylene, PDMS and photosensitive elastomers.

Silicon, a brittle material, if patterned into very thin foils or beams, can be a good candidate for the stretchable part of an array. Although not a good conductor, it can support metal interconnects which have good electrical conductivity.

Electrical conductivity, deposition methods, IC compatibility and mechanical properties are factors that limit the options for metal interconnects. Electrical interconnects between islands are realized using copper or aluminum, most common metals to the IC industry, with well known deposition and patterning techniques and good electrical and mechanical properties. Gold is also used for stretchable interconnects due to its good electrical conductivity and chemical resistance.

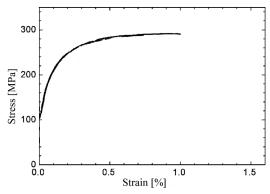

*Figure 2-6.* Stress-strain curve of an electroplated copper film [2.2].

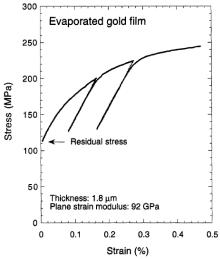

Figure 2-7. Typical stress-strain curve for an evaporated gold film [2.3].

For a stretchable silicon array to function properly, protection against a large number of external factors is necessary. Protection against humidity, gases, corrosive chemicals, electrical insulation or just additional mechanical support can be achieved using polymers. Depending on the design, the array can be fully embedded in a polymer foil or just coated with an insulating layer, similar to regular electrical conductors.

Polymers can also be used during fabrication as a temporary mechanical support layer or just protective coating. PDMS can be spin coated, molded and casted in a wide range of thicknesses. It provides good mechanical protection and electrical insulation by fully embedding a system, providing a large extension interval in the same time.

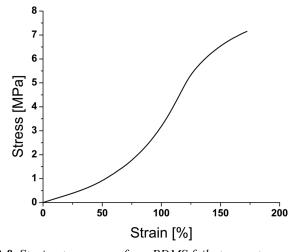

Figure 2-8. Strain-stress curve for a PDMS foil at room temperature [2.4].

*Table 2-1. Material property data of selected materials* [2.4, 5].

(Note: The missing data are either not relevant for given combination of the material property and the material type, or a reliable value was not possible find in the available literature. The values listed are for bulk material properties and are used to illustrate the differences between selected materials. Values for thin films depend on deposition method and can exhibit large variations).

|                                    | Silicon | Copper  | Aluminum | Gold    | PDMS   |

|------------------------------------|---------|---------|----------|---------|--------|

| Young's Modulus<br>[GPa]           | 112.4   | 110     | 68.0     | 77.2    | 0.0017 |

| Yield Strength<br>[GPa]            | 0.120   | 0.262   | 20       | 0.240   |        |

| Ultimate Tensile<br>Strength [GPa] | 0.120   | 0.310   | 50       | 0.302   |        |

| Bulk Modulus<br>[GPa]              | 98.74   | 140     | 76       |         |        |

| Poisson's Ratio                    | 0.280   | 0.343   | 0.35     | 0.42    | 0.5    |

| Shear Modulus<br>[GPa]             | 43.9    | 46.0    | 26       | 27.2    |        |

| Electrical<br>Resistivity [Ω•cm]   | -       | 1.70E-6 | 2.70E-6  | 2.20E-6 | -      |

| Elongation at Break [%]            | -       | -       | -        | -       | 174    |

| Relative Dielectric<br>Constant    |         | -       | -        | -       | 2.8    |

# 2.4. State of the art

The methods of producing stretchable silicon electronics can be divided into two categories [2.6]. Both methods use substrate segmentation to create rigid functional islands connected by a stretchable and electrically conductive medium. The first category gets its stretchability by using very thin semiconductor (brittle) membranes or ribbons that have been compressed using substrate transfer. In the second category the stretchability is achieved by using metal layers that are patterned for stretchability and/or polymers that can accommodate large elongation.

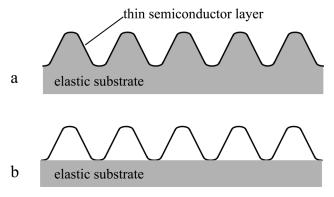

The first approach transforms brittle materials (e.g., single crystalline silicon) into ultra thin membranes, ribbons or wires. With further processing and substrate transfer the material becomes "wavy" and the amplitudes and wavelengths can change according to the applied strain. In plane strains are accommodated through out-of-plane displacements in the wavy structure.

#### STRETCHABILITY OF SILICON-BASED MICROSYSTEMS

Stretchability is achieved by transferring such a thin network of semiconductor islands and ribbons to a pre-stretched elastomer substrate. When the elastomer substrate returns to its relaxed state, semiconductor ribbons form waves (see Figure 2-9). The first wavy configuration involves continuous intimate mechanical coupling between the ribbons and elastomer. In the case of silicon and PDMS, bonding is done by covalent –O-SI-O- linkage that forms due to condensation reactions between surface –OH groups on the PDMS surface and the native oxide of the silicon. When formed with the elastomer substrate in a pre-stretched state, mechanical relaxation creates non-linear buckling or wavy configurations with amplitudes that depend mainly on the elastic properties of PDSM and silicon and thickness of silicon.

Figure 2-9. Schematic illustration of ultra-thin ribbon of "wavy" semiconductor transferred to elastic substrate (a) fully bonded, and (b) partially bonded.

This method has the advantage that the electrical performance and reliability of such a system are similar to those of wafer-scale electronics and has been used to create stretchable conductors, diodes and even fully integrated systems such as an integrated hemispherical electronic eye camera. The method provides practical levels of stretchability up to 15 %, exceeding by ~15 times the intrinsic fracture limit of silicon.

The second wavy configuration uses patterned sites of adhesion on the substrate and/or ribbons to create localized positions of bonding. When the pre stretched substrate is released, the non bonded regions delaminate from the substrate. In this case the waviness can be controlled thus controlling the level of stretchability of the device. With this approach it is possible to achieve reversible stretching to strains of 100 % or more.

All the research results on stretchable silicon electronics have one thing in common: silicon has to be patterned, leading to a network with more or less rigid nodes and flexible/stretchable connexions between nodes.

Silicon wafers can become flexible if thinned to thicknesses under  $100~\mu m$ . The thinner the silicon, the more bendable it becomes. This way, products that rely on unfoldable thin silicon structures have been developed.

Figure 2-10. Stretchable mesh: the square silicon photodetectors, connected by thin ribbons of metal and polymer, are mounted on a hemisphere-shaped rubber surface. The entire device is able to conform to any curvilinear shape due to the flexibility of the ribbons that connect the silicon islands. Credit: Beckman Institute, University of Illinois.

In 2004, Lacour presented stretchable electrical conductors of 25 nm thick gold films with surface waves with  $\sim$ 8.4 µm wavelength and  $\sim$ 1.2 µm amplitude [2.7]. The gold waves showed reproducible and repetitive resistance change and deformation for a cyclic strain variation for 0 % to 15 %. Using the wavy gold interconnects, the same group reported the fabrication of an elastically stretchable TFT circuit (inverter) with identical performances in the relaxed state and after stretching up to 12 % [2.8]. Amorphous silicon TFTs made on polyimide foil are mounted face down on contact pads and interconnected with the stretchable gold conductors. The clear silicone membrane covers the entire field of view and is partly underlaid by millimeter-ruled paper.

#

Figure 2-11. Photograph of the elastomeric inverter. The circuit is shown in its relaxed state [2.8].

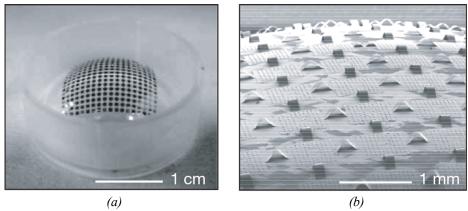

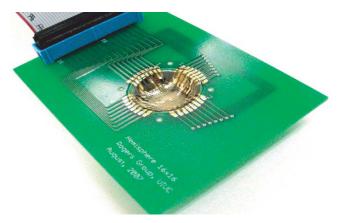

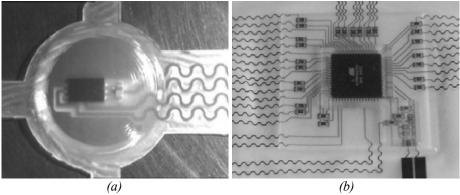

Using a mesh of silicon photodetectors and very thin wavy metal interconnects [2.9], a hemispherical electronic eye camera was fabricated by separating the complex control circuitry from the imager circuitry.

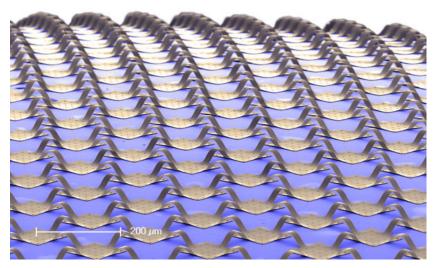

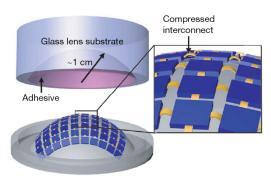

Figure 2-12. (a) Photograph of a hemispherical PDMS transfer element with a compressible focal plane array on its surface and (b) scanning electron microscope image of a portion of the array in (a), illustrating the compressible interconnects [2.9].

The approach uses wafer-scale optoelectronics formed in unusual, twodimensionally compressible configurations and elastomer transfer elements capable of transforming the planar layouts in which the systems are initially fabricated into hemispherical geometries for their final implementation.

Although in this case, the stretchability is exploited only to create fixed 3D-curved imagers, the concept is valid for systems that modify their shape during operation. The imager is an array of identical islands with a small number of inter-island interconnects supported by thin bendable semiconductor bridges.

Figure 2-13. A PCB-mounted hemispherical electronic eye camera [2.9].

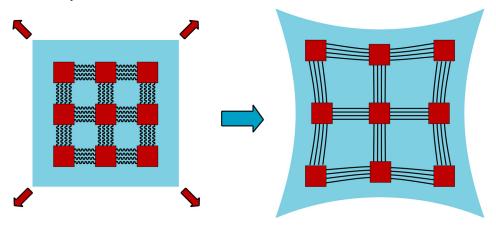

The second approach uses meshes constructed from bendable materials to achieve large and reversible deformation for strains applied on certain axes, while having functional islands in the nodes of the mesh. In this case in plane strains are accommodated by in plane rotations, similar to the movement of a scissors (Figure 2-14). Tensile strains applied at the ends of the structure transform the rectangles of the mesh into diamond like shapes, the mesh becoming longer and narrower.

Figure 2-14. Mesh-shaped semiconductor island stretchable system.

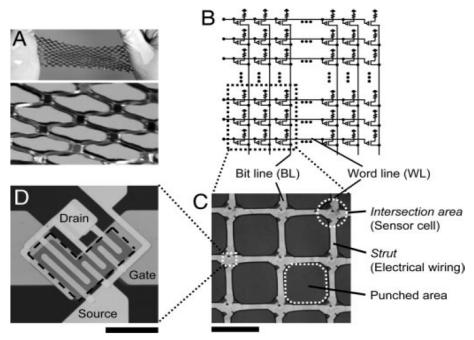

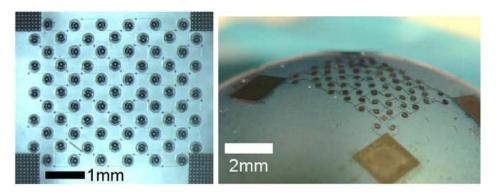

Using the mesh topology, conformable, flexible, large-area networks of pressure and thermal sensors with organic transistor active matrices were fabricated by the Quantum-Phase Electronics Centre of the University of Tokyo [2.10]. Arrays of pressure and temperature sensors are built on a film of 75 µm

thick polyimide or poly (ethylenenaphtalate) (PEN). Stretchability is obtained by using a laser to pattern the film in a mesh-like pattern having nodes containing active IC's, resulting in a system with 25 % stretchability.

Figure 2-15. A conformable network of pressure sensors. (A) A plastic film with organic transistors and pressure-sensitive rubber is processed mechanically to form a unique mesh-shaped structure; (B and C) Circuit diagram of the pressure sensor network (B) together with a picture of the 3x3 sensor cells (C); (D) Microscope image of an organic transistor before shaping the net or integrating it with sensors. Dotted line indicates the semiconductor channel layer. (Scale bar: 1 mm.) [2.10].

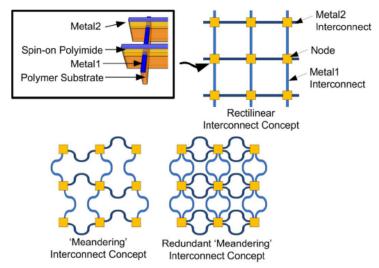

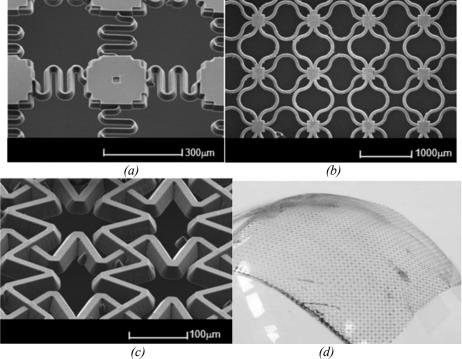

Robust polymer meshes are fabricated using metal patterns both as functional interconnect layers and as in situ masks [2.11]. The method uses laser ablation to pattern polymer layers into rectilinear and meandering designs with single or multilayer metal interconnects.

Fabricated structures can be stretched uniaxially up to 50 % while maintaining good electrical conductivity and structural integrity. "Meandering" interconnects are observed to have a maximum stretchability of greater than 50 % with a change in resistivity of only 5 %. Redundant interconnect mesh have a maximum stretchability of almost 30 % (redundant designs will increase the robustness and viability of interconnects without sacrificing stretchability). A 40 mm by 40 mm interconnect mesh prototype using the redundant mesh design was fabricated as a proof of concept for feasibility of the developed process.

**Figure 2-16.** Interconnect mesh concept for rectilinear, "meandering," and redundant "meandering" interconnects. The interconnects consist of a polymer substrate and two metal layers separated by a spin-on polyimide dielectric layer [2.11].

**Figure 2-17.** (a) Meandering interconnect design with 10 line-width; (b) and (c) Redundant interconnect designs with 40  $\mu$ m line-width; (d) Demonstration of flexibility of 40 mm by 40 mm redundant sensor mesh (conformability to a spherical flask with diameter of 50 mm) [2.11].

#### STRETCHABILITY OF SILICON-BASED MICROSYSTEMS

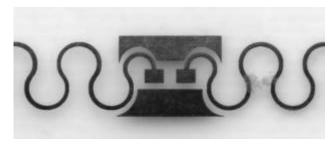

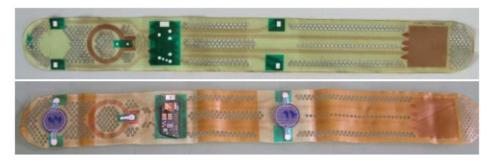

Several stretchable electronics products (for sensor applications for medical electronics and textile electronics) have been developed in the frame of the European project STELLA [2.12]. PCB quality copper sheets (17-70 µm thick) are laminated on thermoplastic polyurethane (TPU) foils (100 µm thick). Following the lamination process, the copper foil is patterned into meanders to define stretchable interconnects. Additional "stiffening" structures are fabricated in the copper patterning step. Their role is to locally prevent substrate stretching, being able to protect the interconnections up to very high elongations (500 % tested). Additional components are assembled (manually or using automated pick & place machine) and soldered to the substrate using low temperature reflow (165 °C). The final encapsulation is done using a cast overmolding process. The profile of the encapsulation is such that the transition between the thick encapsulation and the thinner part containing only the stretchable lines is smoothed out.

*Figure 2-18.* Close-up of stiffening structure around a compnent position [2.12].

One of the products fabricated with this technology is a band aid equipped with pressure sensors and a simple humidity sensor. Pressure sensors are used for monitoring of the pressure on the wound during compression therapy. Data is read out wireless using inductive data transmission with a reach of  $\sim 1 \, \mathrm{m}$  from the antenna. Rather large holes in the polyurethane were included for permeability of air and humidity in order to improve user comfort.

Figure 2-19. Band aid demonstrator [2.12].

A second product is a three point pressure sensor for integration into a shoe insole. Most of the systems are wires only connecting the three sensors which

are located at the heel, the ball of the first and the fifth toe, respectively. In order to provide as much as possible user comfort by allowing circulation of air and moisture, most of the polyurethane surrounding the wires connecting the three sensors was eliminated. However, in order to be easy to handle the remaining structure was laminated into a highly permeable non-woven fabric.

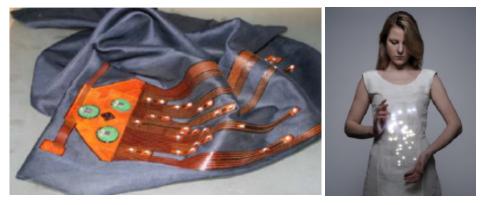

Textile industry already uses polyurethanes for various applications such as glue to join textiles, as ultra thin layer acting being a semi permeable membrane in waterproof textiles, or as interlining separating different layers of cloths from each other. The connection of polyurethanes is a lamination process operated at similar temperatures as ironing. An example of a stretchable electronic system containing acceleration sensors, processors and LEDs was designed and laminated onto a commercial fabric to be integrated into a shirt, see Figure 2-20. A high robustness in many wear cycles has been field proven with this application.

Figure 2-20. Stretchable electronic system laminated to fabrics [2.12]

Since the islands can only bend (if thin enough), the stretching part has to be done by the materials between the islands. Conductive and non conductive polymers, silicone rubbers and metals are some of the choices. These materials have to support the islands, provide electrical connections between the islands and stretch. When looking for the right combination of materials, one has to take into account processing compatibility and properties of individual materials, such as conductivity, elasticity, bio-compatibility, reactivity to chemicals and so on.

Although the goal of stretchable electronics research is to develop systems that can uniformly stretch, changing their dimensions by hundreds of percents, current materials properties (both mechanical and electrical) limit the design and fabrication choices.

While the functional blocks of a stretchable electronic systems are fabricated on a rigid substrate with limited flexibility, the materials used for interconnects and protection are more stretchable. This is why the focus of stretchable electronics is on the stretchability of interconnects and protective polymers while leaving the circuitry largely unchanged on rigid substrates.

### 2.5. System aspects of stretchable silicon microsystems

Traditional chips can have hundreds, even thousands of interconnects. When a system is segmented into functional blocks, two types of interconnects are noticed: interconnects between blocks and interconnects on individual blocks. By rethinking the system for this approach and dividing it into small enough blocks but keeping the number of inter-block interconnects to a minimum, more complex systems can be made stretchable. While in some cases, it is necessary to make the whole system stretchable, in some applications only a part of the segmented system will be stretchable this way minimizing the number of needed stretchable interconnects.

Polymers can be stretched by hundreds of percents before they break but metals have much more limited stretchability. Current research on stretchable metal interconnect schemes shows that metal interconnects stretchability can be increased several times by replacing narrow straight metal lines with more complex shapes such as horseshoe, meanders or meshes.

Using these shapes for metal interconnects can increase stretchability up to several hundred percents but with serious increase of area used by interconnects. One simple line can become stretchable if it is replaced with a meander but the area occupied is several times larger. This limits the number of interconnects thus limiting the complexity of a stretchable microsystem.

Scaling down the interconnect size by using finer lithography can reduce the area but also some other issues have to be taken into account. Work done in the STELLA project shows how discrete components are assembled to a stretchable printed circuit board (SCB). Two techniques are used to minimize the stress on components interconnects: local stiffener structures and polyurethane glob tops with gradually increasing thickness [2.13].

The transition between stretchable (meandering Cu) and rigid parts of the system (once the components are assembled) has to be accounted for. Stiffening of the substrate around components is done to protect the component interconnections against stress due to stretching (Figure 2-18).

Figure 2-21. (a) Encapsulated component with a smooth glob top encapsulation, and (b) fabricated system using polyurethane encapsulation [2.13].

The profile of the glob top encapsulation is such that the transition between the thick, rather stiff encapsulant and the thinner part containing only the stretchable copper lines is smoothed out (Figure 2-21a).

By using a combination of these stress reducing techniques, complex systems can be created and lamination into textiles has been demonstrated (Figure 2-21b).

# 2.6. Fabrication compatibility, handling and reliability

Although there is a large variety of materials that can be used, IC fabrication has strict requirements on chemicals purity, air quality, contaminants and safety. When selecting materials for interconnects (usually metals) or for protection (usually polymers), all the IC fabrication contamination and safety requirements have to be met and processing compatibility of all materials has to be guaranteed.

Once the materials are selected and fabrication process compatibility and contamination issues solved, traditional processing and handling steps can prove to be too aggressive for stretchable systems. A simple example:  $20~\mu m$  thin chips connected with thin metal lines embedded in a soft polymer layer can be tricky to handle during or even after fabrication.

Thin wafers and chips need different handling procedures than traditional thick ones. Wafer dicing uses high pressure water and adhesive foils that can be destructive for some flexible systems.

While regular electronic systems are encapsulated in rigid packages that can be easily handled and connected to circuit boards, new handling and connecting methods have to be developed for stretchable electronics.

Although the goal is to fabricate systems that can sustain large deformation without loosing their functionality, substrate transfer is a common technique to provide the to-be-stretchable systems with enough stiffness needed for traditional IC fabrication and assembly processes. For fabricating diamond like carbon (DLC) islands for stretchable electronics, PDMS foils are mounted on plastic foils for handling during processing and released at the end. A temporary substrate is also employed in the fabrication process for stretchable printed circuit boards, part of STELLA project.

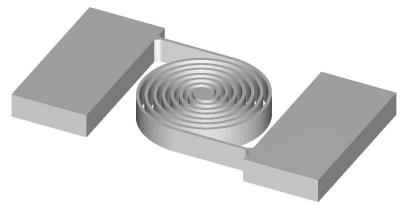

Large area electronics arrays of islands connected with narrow spirals using monolithic silicon use large blocks of silicon needed to handle individual arrays [2.14].

Figure 2-22. Silicon island array using narrow spirals as interconnect (left), showing large blocks needed for handling (right)[2.14].

Spherical camera lenses are first fabricated on rigid substrates using established processing techniques. Transfer to a spherical lens is done in several steps. First, a hemispherical curved PDMS carrier is stretched to a planar shape and then the silicon island array is transferred using van der Waals forces to bond the silicon to the pre-stretched PDMS carrier. In the second stage, the pre stretched PDMS carrier is allowed to return to its relaxed hemispherical shape. In the last step, the silicon array is bonded using glue to the hemispherical lens.

Figure 2-23. Part of hemispherical camera lens fabrication sequence, illustrating transfer to curved surface stages [2.9].

In current research there are two generic approaches used for fabricating stretchable systems, each having its benefits and disadvantages. In the first approach, the substrate is attached to a flexible/stretchable layer, patterned and then stretched. The method is wasteful as in order to create stretchable regions between rigid islands, most of the wafer is removed, leaving only islands attached to the flexible layer. Another problem appears when one island (die) is defective and the whole system becomes unusable. Same problem (even more wasteful) appears if several wafers are bonded and good devices will be introduced in already defective systems. Depending on the fabrication process, the wafer can be processed until the end using standard clean room

equipment/techniques, without the need to develop new methods for handling/processing.

In the second approach, the substrate is patterned, stretched and then, if necessary, attached to the flexible medium [2.11, 14]. The method suffers from the same yield problem as the previous (one bad die ruining the whole system) and a possible additional problem caused by handling and stretching fragile patterned structures.

A variation of the first approach is hybrid integration (using a dummy substrate or a functional substrate). It can solve the handling problems by using established pick-and-place technology to assemble any die configuration on a target substrate (removed or patterned later), increasing the yield by using known good dies. Most research examples previously presented use hybrid integration on a temporary carrier [2.12, 13].

#### 2.7. Conclusions

This chapter presented a theoretical overview of mechanical notions used throughout the thesis to describe the behavior of stretchable electronic systems. Current methods of creating stretchable systems have been described and each fabrication method has been illustrated with relevant state of the art devices. The performances of current devices were presented along with design, fabrication and handling issues specific for stretchable systems. Next chapters will present in detail the selected interconnect geometries, development of wafer-level fabrication process of stretchable silicon electronics embedded in PDMS and testing of the fabricated arrays.

### 2.8. References

- [2.1] Vable, M., *Intermediate Mechanics of Materials*, Oxford University Press, 2008

- [2.2] Xiang, Y., Tsui, T.Y., and Vlassak, J.J., *The mechanical properties of freestanding electroplated Cu thin films*, Journal of Material Research, 2006, 21(6), pp. 1607 1618

- [2.3] Vinci, R.P. and Vlassak, J.J. (2006) *Mechanical Behavior of Thin Films*, Annual Review of Materials Science 26, 431-462.

- [2.4] Wang, L., Mechanical characterization of flexible and stretchable electronic substrates, PhD thesis, Delft University of Technology, 2010

- [2.5] MatWeb, Material Property Data, http://www.matweb.com/, Feb. 2011.

- [2.6] Kim, D.H. and Rogers, J.A., *Stretchable Electronics: Materials Strategies and Devices*, Advanced Materials Journal, 2008, 20(24), pp. 4887-4892.

- [2.7] Lacour, S.P., Jones, J., Suo, Z., and Wagner, S., Design and performance of thin metal film interconnects for skin-like electronic circuits, IEEE Electron Device Letters, 2004, 25(4), pp. 179-181.

- [2.8] Lacour, S.P., Tsay, C., and Wagner, S., *An elastically stretchable TFT circuit*, IEEE Electron Device Letters, 2004, 25(12), pp. 792-794.

- [2.9] Ko, H.C., Stoykovich, M.P., Song, J., Malyarchuk, V., Choi, W.M., Yu, C.J., Geddes, J.B., Xiao, J., Wang, S., Huang, Y., and Rogers, J.A., *A hemispherical electronic eye camera based on compressible silicon optoelectronics*, Nature, 2008, 454(7205), pp. 748-753.

- [2.10] Someya, T., Kato, Y., Sekitani, T., Iba, S., Noguchi, Y., Murase, Y., Kawaguchi, H., and Sakurai, T., *Conformable, flexible, large-area networks of pressure and thermal sensors with organic transistor active matrixes*, PNAS, 2005, 102(35), pp. 12321-12325.

- [2.11] Lin, K.L., Chae, J., and Jain, K., *Design and Fabrication of Large-Area, Redundant, Stretchable Interconnect Meshes Using Excimer Laser Photoablation and In Situ Masking*, IEEE Transactions on Advanced Packaging, 2010, 33(3), pp. 592-601.

- [2.12] Loher, T., Seckel, M., Vieroth, R., Dils, C., Kallmayer, C., Ostmann, A., Aschenbrenner, R., and Reichl, H., *Stretchable electronic systems: Realization and applications*, 11<sup>th</sup> Electronics Packaging Technology Conference (EPTC), 2009, Singapore, pp. 893-898.

- [2.13] Gonzalez, M., Axisa, F., Vanden Bulcke, M., Brosteaux, D., Vandevelde, B., and Vanfleteren, J., *Design of Metal Interconnects for Stretchable Electronic Circuits using Finite Element Analysis*, EuroSime, 2007, London, UK, pp. 1 6.

- [2.14] Dinyari, R., Huang, K., Lanzara, R., Kim, G.J.Y., Feng, J., Vancura, C., Chang, F.K., and Peumans, P., *An Approach to Cost-Effective, Robust, Large-Area Electronics using Monolithic Silicon*, IEDM, 2007, Washington, DC, USA, pp. 217-220.

# **Chapter 3:**

# Stretchable Interconnect Schemes

In this chapter the interconnect schemes and geometries selected for the fabrication of stretchable interconnects are presented. First the general requirements on a stretchable interconnect are defined and suitable interconnect geometries are selected. These are then analyzed using finite-element simulation tools and the obtained results are used for further optimization. In the final part of this chapter, the fabrication and measurement results obtained for free-standing high-aspect-ratio silicon springs and free-standing stretchable metal interconnects are presented.

### 3.1. Introduction

A stretchable silicon microsystem fabricated using a segmented substrate approach will get its stretchability from two sources: the interconnect between segments and the protective polymer. The stretchability of the interconnect depends on two factors: the material and the geometry. The choice of materials is limited to metals or conductive polymers. There are advantages and disadvantages of each material as metals have high electrical conductivity but are elastic for only a rather small tensile strain region, while conductive polymers have comparably poor electrical performances but much more favorable elastic properties.

# 3.2. General requirements on stretchable interconnects

The first question one can ask about a stretchable interconnect scheme is "How much can it stretch?". This can be described as the most obvious requirement of a stretchable interconnect and of a stretchable electronic system. The strain, as presented in Chapter 2, is defined as the ratio between the change in length  $\delta L$  and the original length L.

Depending on the final product requirements, the stretching can be reversible or not. Non-reversible stretching can be useful if the system is designed to cover a large area but it is fabricated in a folded state and finally unfolded to its final size. Reversible stretching is more difficult to achieve for large strain values and fatigue becomes an important failure factor.

Besides the ability to accommodate strains, there are more factors that influence the performance of a stretchable electronic system. All stretchable electronic approaches use lateral segmentation of the substrate, i.e., rigid functional nodes connected by an elastic and electrically conductive medium. The nodes or islands must be supported by the surrounding elastic and conductive network. Depending on the fabrication methods and materials,

mechanical support can be provided by interconnects only (if strong enough), or achieved by application of soft and elastic polymers. The latter being a more frequent choice. In addition to the mechanical support, the polymers can also provide mechanical and/or chemical protection.

In a traditional monolithic chip, the role of interconnects is to carry signals between the different components with minimum losses. When compared to traditional monolithic chips, stretchable systems use a larger area as the chip is divided into functional blocks linked with a stretchable and conductive medium. In a stretchable system, besides carrying electrical signals between individual blocks, interconnects (together with the surrounding supporting medium) must stretch to withstand strain. The interconnect geometry determines its ability to stretch but also determines the electrical resistance. The change of electrical resistance with changing strain must be taken into account when selecting a certain shape and size for the interconnect network as it can seriously affect the system performance.

Depending on the application, a stretchable system might need to stretch more in one direction but nevertheless 2D stretchability is desired. 1D stretching is a (relatively) simple case as all the interconnect designs presented can be stretched mainly in one direction (longitudinal) but can also withstand small transversal deformation

For 2D stretching, there are two cases that can be considered. A simple solution is to use interconnects with 1D stretching ability, distributed along the main stretching axes, obtaining in this way a system that can globally stretch in 2D. Such a system will have limited 2D stretchability as interconnects still have a preferred axis of deformation. Another approach is to use an interconnect shape that can stretch in 2D because of its design. A mesh geometry, similar to woven textiles, is an example of such design.

# 3.3. Geometry for stretchability

Elastic deformation in metals is limited to very small strains. Patterning metals into various shapes gives them the ability to deform elastically, thus recovering their original shape without sustaining damage. Patterned metal tracks can also be supported by silicon geometries patterned for stretchability. The geometries discussed next can be used either way, only as thin metal tracks or as silicon structures supporting the thin metallization.

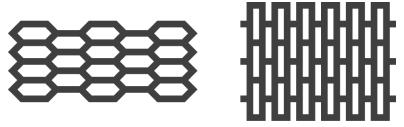

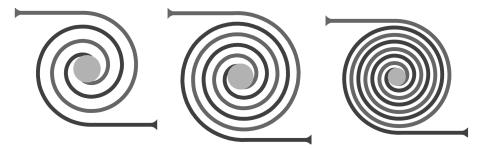

# 3.3.1. Mesh geometry

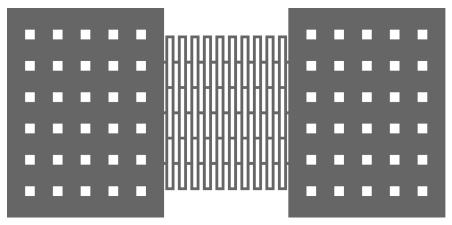

One such pattern is the mesh, consisting of a network of metal beams in a repeated pattern. Although there can be different geometries for a mesh, such as honeycomb, rectangular or diamond like, the effect of tensile strains applied at the ends of the mesh is the same: the elements of the mesh change their shape, in plane strains are accommodated by in plane rotations, similar to the movement of a scissors as the mesh becomes longer and narrower.

Figure 3-1. Different mesh designs: honeycomb (left) and rectangular (right).

Such interconnect has some advantages (it is strong and if some parts are damaged, electrical conductivity is maintained), but its size will greatly limit the number of interconnects that can be realized on a given area. The mesh shape is more suitable for unsupported interconnects as the brittle supporting silicon will greatly reduce the maximum elongation achievable when using only metals.

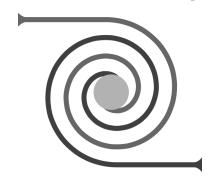

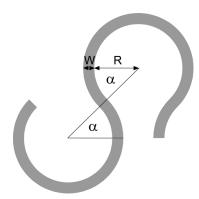

### 3.3.2. Spiral geometry

Two spirals, with opposite rotation directions and connected in the middle (Figure 3-2), can unfold when the ends are pulled apart. Similar to the mesh, islands can be connected with spiral springs or can be fabricated in the centre of the two spirals, acting also as connector between the spirals.

Figure 3-2. Spiral design, showing opposite spirals.

The spiral geometry must rotate to unfold and its ability to unwind will be greatly limited if used as patterned metal embedded in a protective medium. As supporting silicon structure, the width of the arms must be small ( $<1 \mu m$ ) to allow the arms to unfold to almost a straight line [3.1].

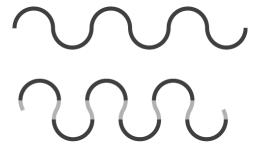

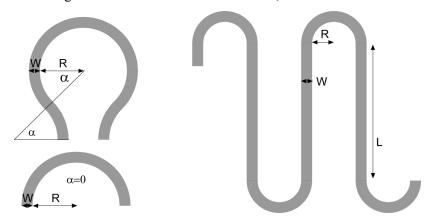

# 3.3.3. Meander and horseshoe geometry

Other patterns that have been investigated are meander and horseshoe. The meander pattern is made of a series of half circles (round caps) connected with vertical straight segments. The transition between the rounded cap and the straight segment can also have a certain curvature that reduces the stress concentration in that area, allowing for a higher deformation. If made from a ductile material, the meander can be stretched to a straight line.

#### STRETCHABLE INTERCONNECT SCHEMES

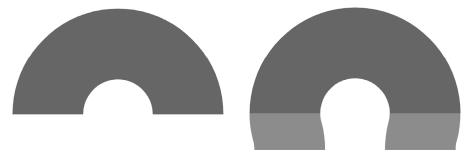

The horseshoe interconnect is very similar to the meander design. It is made of half circle segments with optional smaller segments of opposite curvature that reduce the stress concentration, allowing larger extensions.

**Figure 3-3.** Meander designs showing simple design (left) and design with additional curved segments (light grey) (right).

**Figure 3-4.** Horseshoe designs showing simple design (top) and design with additional curved segments (light grey) (bottom).

These geometries can be easily tuned to support large longitudinal deformation by adjusting the curvature angle of the transition segment. Small size allows large number of interconnects to be used in a system. The meander version uses more area and is suitable to be used as silicon supporting structure as the vertical beams allow larger deformation for a certain strain level when compared to the horseshoe geometry.

# 3.3.4. Parametric structure description

Each of the structures presented is fabricated by repeating a simple element (base element) in 1D or 2D. The base element is defined by a set of geometric parameters, independent of material and processing parameters.

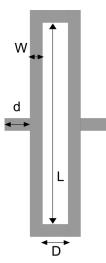

For the rectangular mesh, the base element is defined by four parameters:

- the width of the metal line, W;

- the width of one element, **D**;

- the length of the vertical lines, *L*;

- distance between two elements, d.

Figure 3-5. Mesh base element with parameters.

Starting from this simple design, more complex meshes can be created that have lines with variable width and curved transitions instead of sharp corners.

Meander interconnects are determined by four parameters:

- the width of the metal line, W;

- the radius of the curved element, **R**;

- the length of the vertical lines, *L*;

- the angle of the additional curved element,  $\alpha$ .

Figure 3-6. Meander curved part (left) and meander (right) with parameters.

The horseshoe design is a simplified version of the meander, without the vertical lines. Taking this into account, the horseshoe is determined by the three parameters:

- the width of the metal line, W;

- the radius of the curved element, **R**;

- the angle of the additional curved element,  $\alpha$ .

**Figure 3-7.** Horseshoe interconnect geometry with design parameters.

### 3.4. Finite-element simulations

When constructing an interconnect scheme for a stretchable system, factors such as overall dimension of the system, number and size of interconnects or biocompatibility limit the number of design and fabrication alternatives. Area available for interconnects, total length (increased electrical resistance), maximum elongation and stress (leading to mechanical failure) are the primary factors that have to be considered while selecting a certain interconnect.

Chapter 2 presented an overview of the selected materials and their mechanical and electrical properties. The equations presented are useful when discussing homogeneous materials but current state-of-the-art systems are all heterogeneous. The behavior of heterogeneous systems requires numerical analysis such as finite element simulations.

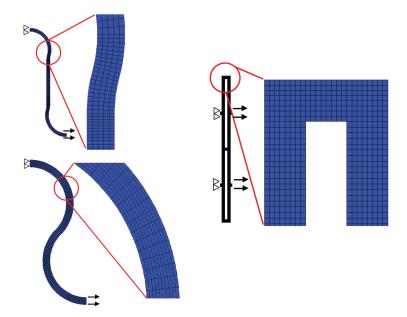

Tensile load simulations were performed to understand the failure causes and to optimize the system for increased elongation and lifetime. Because of the better electrical and mechanical performance but also chemical resistance, copper interconnections are chosen. Several geometries of spring—like structures are numerically tested. For the simulations adequate material parameters are necessary, which were discussed in Chapter 2. The large ratio of width (or length) to thickness offered a challenge to reliable FE simulation. Therefore multilevel FEM simulations were performed. A global-local model has the advantage of subdividing large models into multiple, moderate-size models and thus separating fixed model parts from parts of the model that may undergo design changes [3.2].

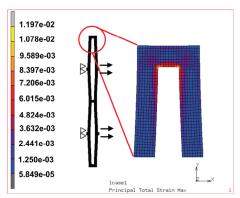

When exploring the suitability of the new designs to survive large extensions, the limiting factor for failure is assumed to be the ultimate equivalent strain in the copper.

As all interconnects are made up from repetition of basic shapes and based on symmetry considerations, FE simulations can be restricted to the basic shapes only (Figure 3-5, Figure 3-6 and Figure 3-7). The models used are illustrated in Figure 3-8. The boundary conditions include fixed x-direction

displacement of nodes at the left end and prescribed x-direction displacements on all boundary nodes at the right end. The rigid body movements are additionally suppressed [3.3].

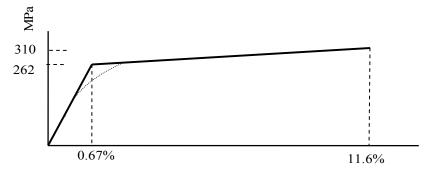

The elastic plastic model for copper has been used [3.4] and material properties are listed in Table 3-2. Experiments were not performed to establish the real elasto-plastic properties of the copper interconnect. Instead an elastoplastic behavior is assumed in the present simulations on the basis of measurement results as published by Dao for a copper line of a thicknesses only a few microns [3.5]. The actual stress-strain curve as given by Dao is shown as the dashed line in Figure 3-9. The Young's modulus and Poisson's ratio (in the elastic region) are 128 GPa and 0.36, respectively. As the elasto-plastic behavior is strongly dependent on the grain size, it is obvious that Dao's stress strain curve can only be considered as a rough indication for the real material behavior of our interconnects. Therefore, the stress strain curve used is a simplified version using a linear hardening slope and steady plastic behavior after reaching the ultimate strength (see Figure 3-9). The ultimate strain according to Dao's measurements is 11.6%. In the FE simulation results, reaching this ultimate strain value is used as a failure criterion, although when this just occurs locally, the whole structure is not really failed and electrical conduction will hardly be affected.

**Figure 3-8.** FE models of free-standing interconnect base parts: (a) meander, (b) horseshoe, and (c) mesh.

The behavior of a sample under tensile stress can be described by using three intervals defined by the yield and ultimate strengths (YS and US). For stress values in the interval [0, YS], the sample gets no damage, only elastic

deformation (100 % reversible deformation). In the second interval [YS, US] samples will not get damaged if extended but will not be able to completely return to the original shape (combination of elastic and plastic deformation). The last interval is [US,  $\infty$ ] where samples will suffer only plastic deformation (0 % reversible deformation), will get damaged and finally break.

Figure 3-9. Stress-strain curve of copper film, dotted line is measurement results according to [3.5]. Solid line is constructed bi-linear behavior as used in the FE simulations.

*Table 3-1. Interconnect parameters.*

| Meander and Horseshoe         |             |    |  |     |  |     |  |

|-------------------------------|-------------|----|--|-----|--|-----|--|

| Parameter                     | Values (μm) |    |  |     |  |     |  |

| Angle α                       | 0           | 15 |  | 30  |  | 45  |  |

| Width <b>W</b>                | 5           |    |  | 10  |  | 20  |  |

| Radius <b>R</b>               | 10          |    |  | 50  |  | 100 |  |

| Length L (meander)            | 250         |    |  |     |  |     |  |

| Mesh                          |             |    |  |     |  |     |  |

|                               | Values (μm) |    |  |     |  |     |  |

| Width <b>W</b>                |             | 5  |  | 10  |  | 20  |  |

| Distances <b>D</b> , <b>d</b> |             | 5  |  | 10  |  | 20  |  |

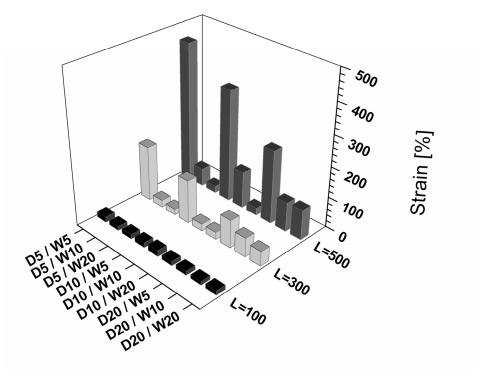

| Length L                      | 1           | 00 |  | 300 |  | 500 |  |

*Table 3-2. Material properties of copper used in simulations.*

| Young's modulus   | 128 GPa |

|-------------------|---------|

| Poisson's ratio   | 0.36    |

| Yield strength    | 262 MPa |

| Ultimate strength | 310 MPa |

### 3.4.1. Meander interconnects analysis

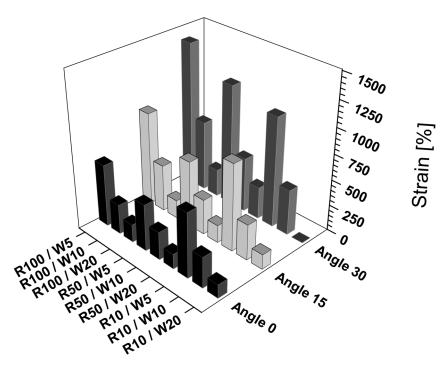

For meander base elements, defined by  $(W, L, R, \alpha)$  (see Figure 3-6), simulations are performed for elongation steps increasing with 5% up to a maximum elongation of 1500%. The maximum equivalent strain on the interconnects under the applied elongation steps is determined and by comparing it with the failure strain (ultimate strain) it is possible to find the sample elongation (or mean strain level) at (assumed) onset of failure.

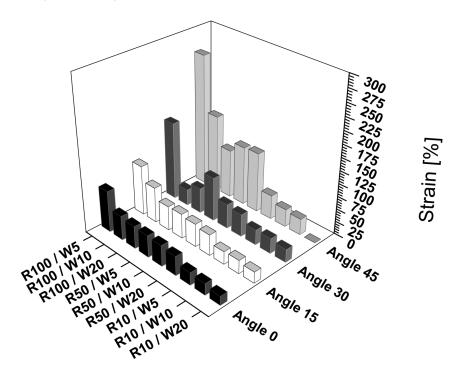

The mean strain at onset of failure (defined here as reaching the ultimate strain of the copper) is presented in Figure 3-10 for various model parameter sets (width W, radius R and angle  $\alpha$ ). It is found that the behavior improves with larger radius R and smaller width W. Also the increase of the angle  $\alpha$  has a positive influence. The best result (being the one with the highest mean strain) is found for W=5  $\mu$ m, R=100  $\mu$ m and  $\alpha$ =30°.

Figure 3-10. The mean strain at onset of failure of the meander shape interconnect for various model parameter sets.

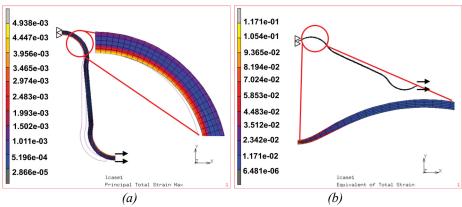

Figure 3-11 shows the equivalent strain distribution at an elongation of 176 % (maximum strain for PDMS) for the meander interconnect with the best results (W=5  $\mu$ m, R=100  $\mu$ m and  $\alpha$ =30°) and at the maximum strain before reaching ultimate strength. The maximum equivalent strains of the free-standing meander interconnects are found within the area of the wave peak (at the inner

side). A combination of tensile force and bending moment in the interconnect line is responsible.

Figure 3-11. Equivalent stress distributions for meander interconnect  $(W, R, \alpha) = (5, 100, 30)$  at (a) 176 % and (b) 1375 % strain.

Since the strain in a metal beam is inversely proportional to its width, if the same curvature is used, the elongation can be increased by using narrower metal lines [3.6].

## 3.4.2. Horseshoe interconnect analysis

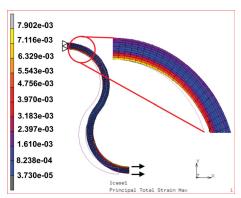

For horseshoe interconnect base elements, simulations are performed for elongation steps increasing with 5 % up to a maximum elongation of 300 %. The maximum equivalent strain of the free-standing horseshoe interconnect is found within the area of the wave peak (at the inner side, see Figure 3-12).

**Figure 3-12.** Equivalent strain distribution for the horseshoe interconnect  $(W, R, \alpha) = (10, 50, 45)$  under prescribed mean deformation (elongation) of 20 %.

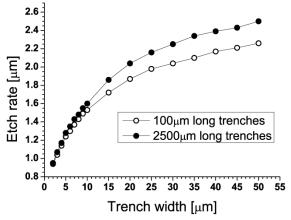

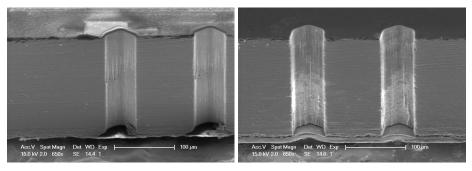

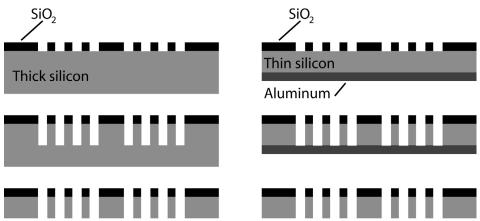

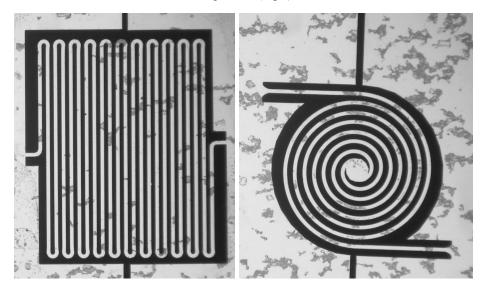

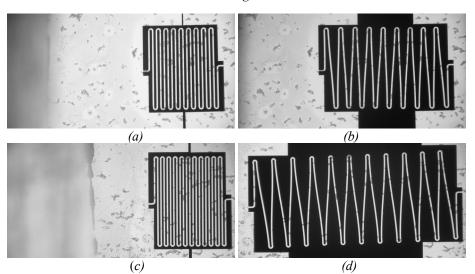

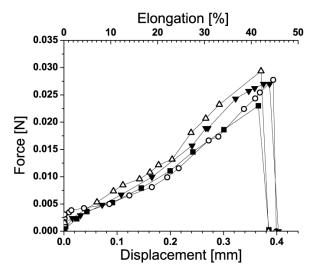

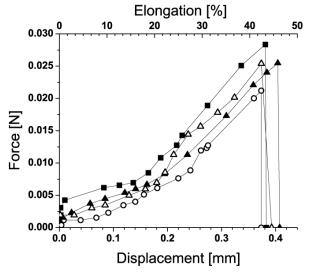

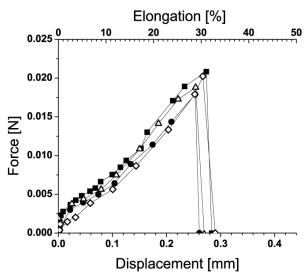

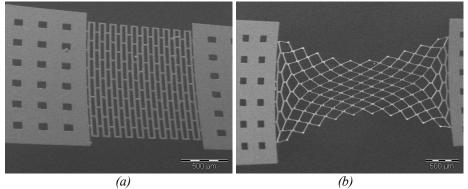

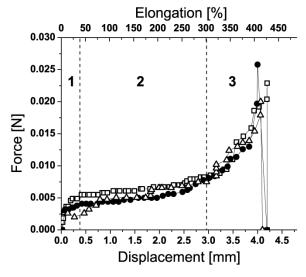

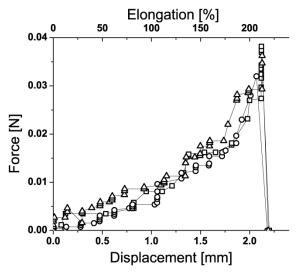

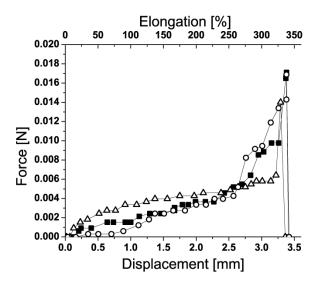

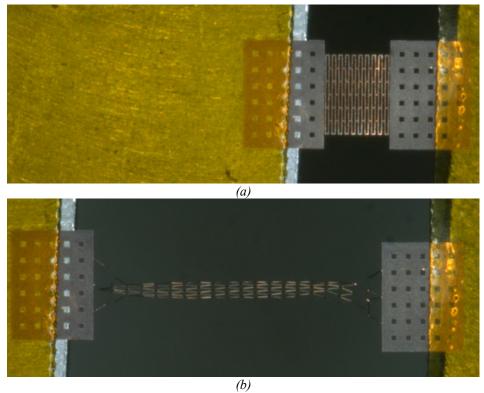

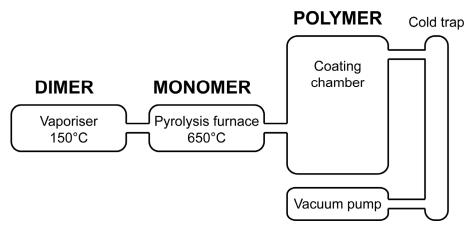

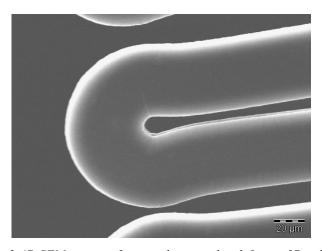

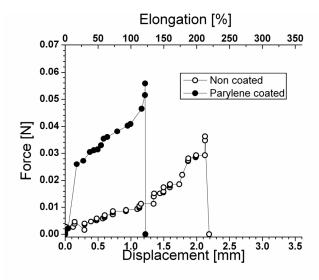

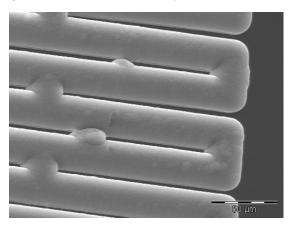

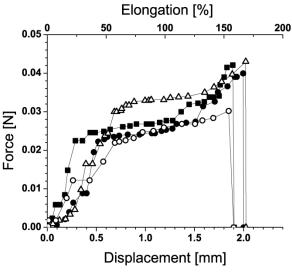

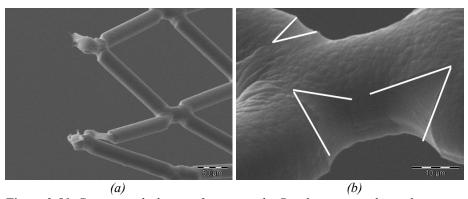

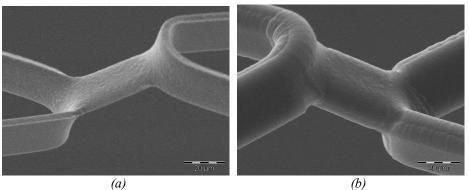

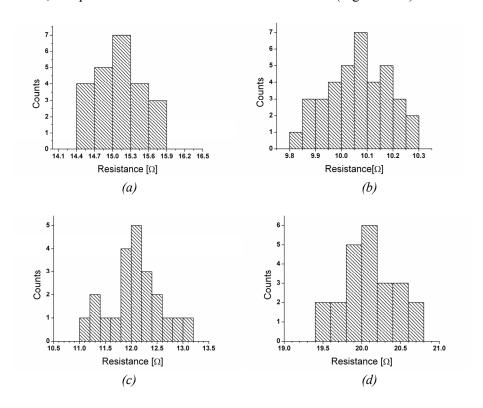

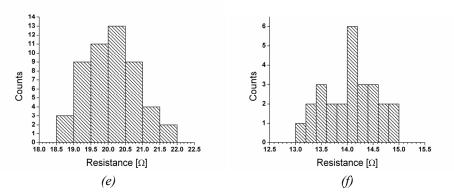

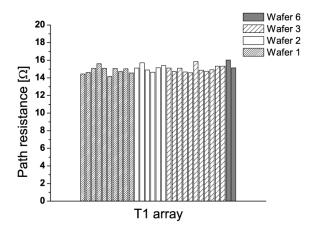

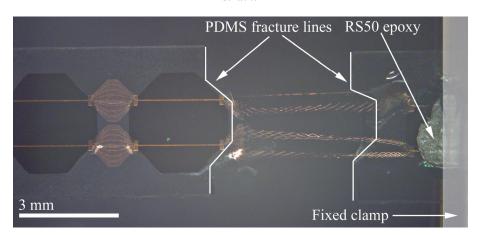

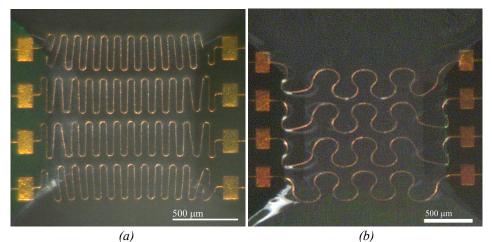

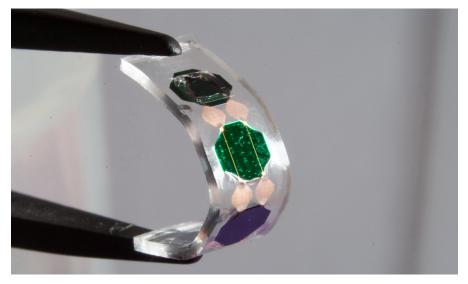

A combination of tensile force and bending moment in the interconnect line is responsible for this behavior. It is found that the behavior improves with larger radius R and smaller width W. Increasing the radius leads to a small