#### **Integration Technologies for Smart Catheters**

Li, J.

10.4233/uuid:667642da-a182-4b7c-bc10-864e4fc16674

**Publication date**

**Document Version** Final published version

Citation (APA)

Li, J. (2024). Integration Technologies for Smart Catheters. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:667642da-a182-4b7c-bc10-864e4fc16674

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

## INTEGRATION TECHNOLOGIES FOR SMART CATHETERS

## INTEGRATION TECHNOLOGIES FOR SMART CATHETERS

#### **Proefschrift**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. dr. ir. T.H.J.J. van der Hagen, voorzitter van het College voor Promoties, in het openbaar te verdedigen op woensdag 28 februari 2024 om 10.00 uur

door

#### Jian LI

Master of Science in Electrical Engineering Delft University of Technology, Delft, The Netherland, geboren te Hebei, China. Dit proefschrift is goedgekeurd door de

promotor: prof. dr. R. Dekker promotor: prof. dr. P. French

#### Samenstelling promotiecommissie:

Rector Magnificus, voorzitter

Prof. dr. R. Dekker, Delft University of Technology, promotor Prof. dr. P. French, Delft University of Technology, promotor

*Onafhankelijke leden:* Prof. dr. I. Vanfleteren

Ghent University, Belgium

Prof. dr. O. Raz, Eindhoven University of Technology

Dr. ir. G. Pandraud, Ommatidia LIDAR, The Netherlands

Prof. dr. L. Sarro, Delft University of Technology

Dr. ir. V. Henneken, Philps Research, The Netherlands

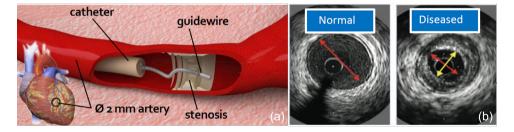

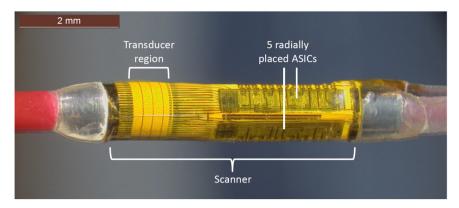

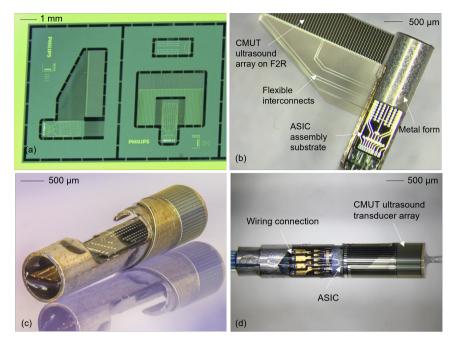

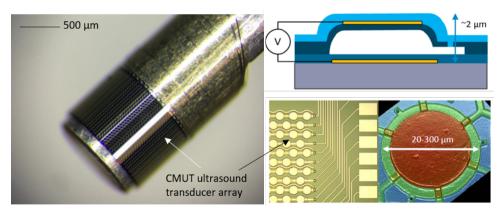

Keywords: Cardiovascular diseases, smart catheters, intravascular ultrasound

(IVUS) catheter, Flex-to-Rigid (F2R), optical transmitters, optical interconnections, trench capacitors, HAR (High Aspect Ratio) DRIE, SOI substrate, cavity-SOI, cavity-BOX, buried hard-etch mask, miniaturization, deep brain stimulation (DBS), foldable devices, MEMS, Microfabrica-

tion, Microassembly

*Printed by:* Ipskamp Printing

Front & Back: Jian Li with assists of OpenAI program DALL-E

Copyright © 2024 by J.Li ISBN 978-94-6366-821-7

An electronic version of this dissertation is available at <a href="http://repository.tudelft.nl/">http://repository.tudelft.nl/</a>.

### **CONTENTS**

| 1 | Intr | oduction                                                       | 1  |

|---|------|----------------------------------------------------------------|----|

|   | 1.1  | Smart Catheters                                                | 2  |

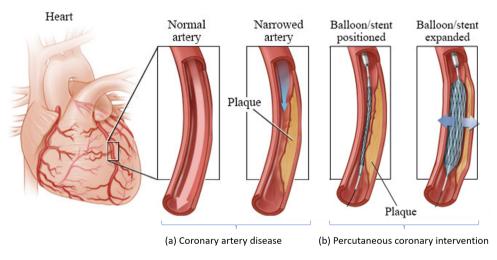

|   |      | 1.1.1 Application field: heart disease diagnosis and treatment | 2  |

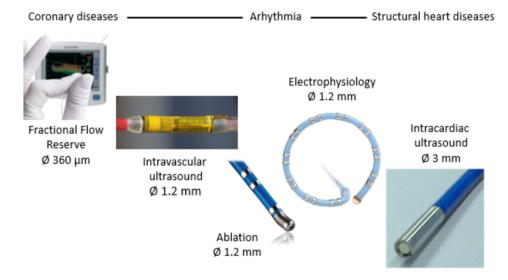

|   |      | 1.1.2 Cardiac catheterization categories                       | 3  |

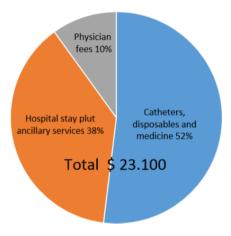

|   |      | 1.1.3 The market size of smart catheterization                 | 4  |

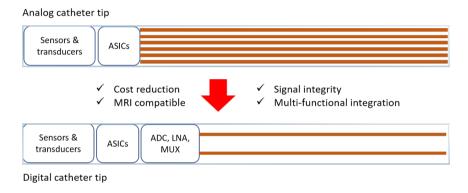

|   |      | 1.1.4 Catheter tip integration: state of the art               | 5  |

|   | 1.2  | The Flex-to-Rigid (F2R) platform                               | 7  |

|   |      | 1.2.1 Beyond the state of the art                              | 7  |

|   |      | 1.2.2 Standard F2R process                                     | 8  |

|   |      | 1.2.3 F2R challenges                                           | 9  |

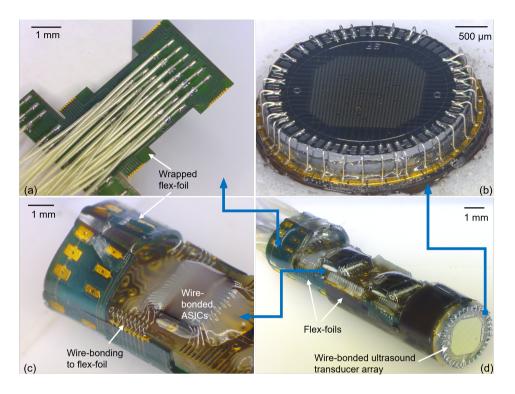

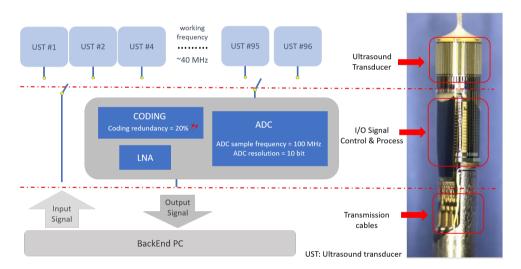

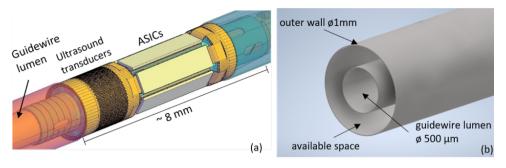

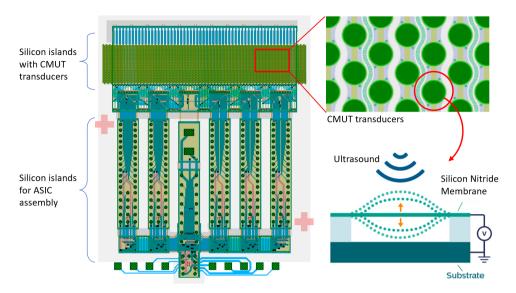

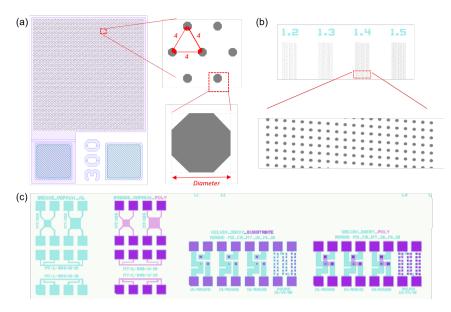

|   | 1.3  | The IVUS catheter                                              | 10 |

|   |      | 1.3.1 State-of-the-art                                         | 11 |

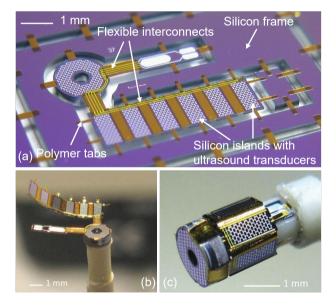

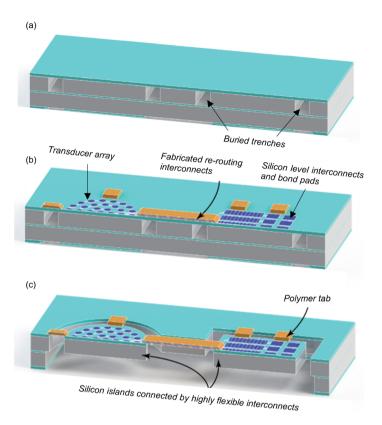

|   |      | 1.3.2 An F2R-based IVUS catheter                               | 12 |

|   | 1.4  | Scope and outline of this thesis                               | 14 |

|   |      | 1.4.1 Scope of the thesis                                      | 14 |

|   |      | 1.4.2 Outline of the thesis                                    | 14 |

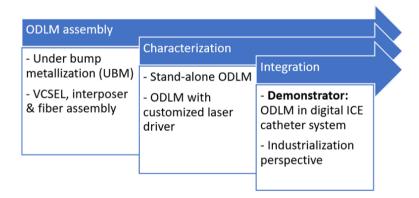

| 2 | Opt  | ical Data Link Module (Part 1)                                 | 19 |

|   | 2.1  | Background                                                     | 20 |

|   |      | 2.1.1 From analog to digital catheters                         | 20 |

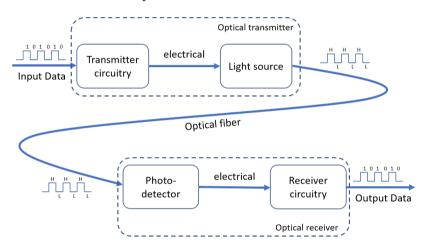

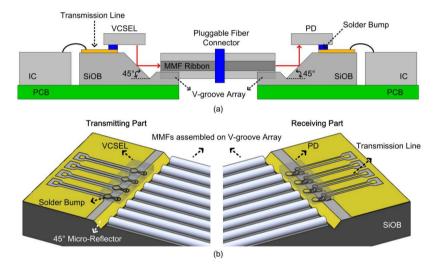

|   |      | 2.1.2 From electrical to optical data transmissions            | 21 |

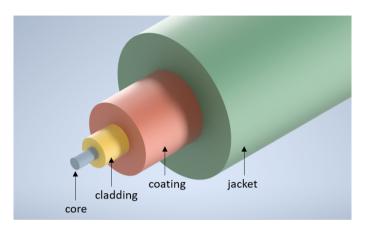

|   |      | 2.1.3 Fiber-optic fundamentals                                 | 22 |

|   |      | 2.1.4 Optical link in IVUS: design requirements                | 26 |

|   |      | 2.1.5 Goal statement & chapter guidance                        | 27 |

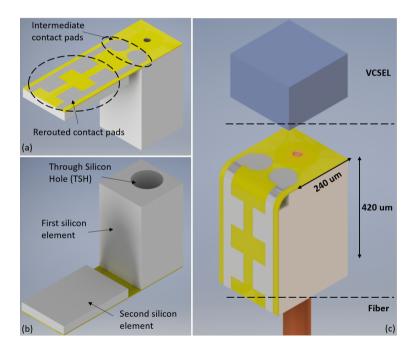

|   | 2.2  | Design of ODLM for a digital IVUS catheter                     | 28 |

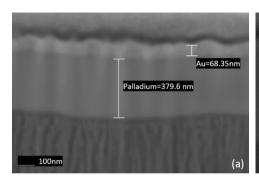

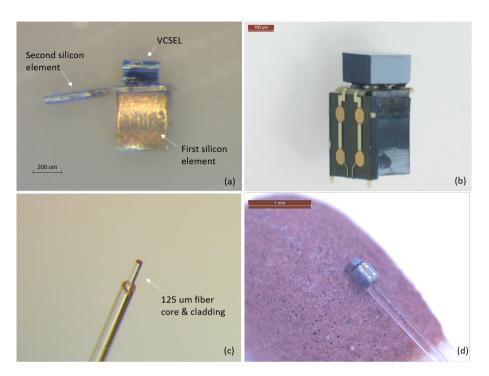

|   | 2.3  | Device Fabrication                                             | 31 |

|   |      | 2.3.1 General process flow                                     | 31 |

|   |      | 2.3.2 Fabrication results                                      | 33 |

|   |      | 2.3.3 Process optimization                                     | 33 |

|   | 2.4  | Conclusion                                                     | 37 |

| 3 | Opt  | ical Data Link Module (Part 2)                                 | 41 |

|   | 3.1  | Introduction                                                   | 42 |

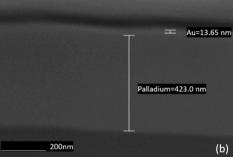

|   | 3.2  | Stand-alone ODLM                                               | 43 |

|   |      | 3.2.1 ODLM assembly                                            |    |

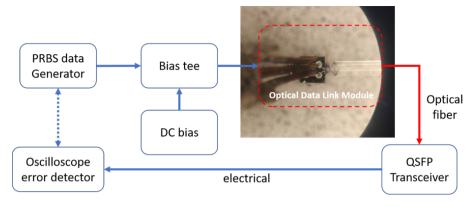

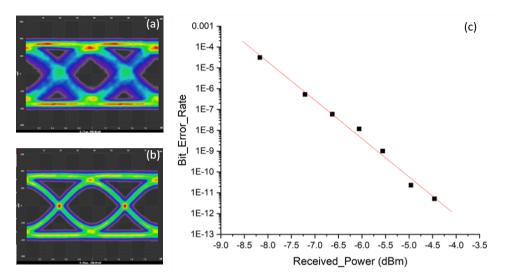

|   |      | 3.2.2 Characterization                                         |    |

viii Contents

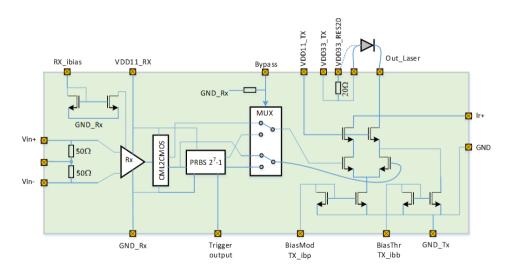

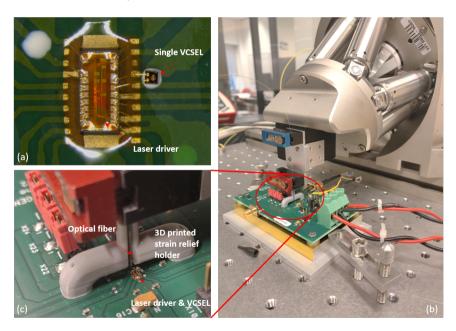

|      | 3.3.2 Driver board evaluation with single VCSEL                         | 47<br>49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                                                         | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

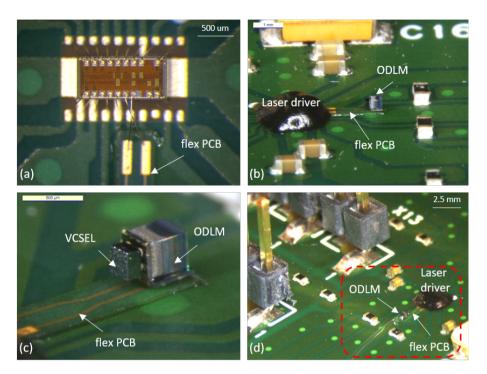

|      | 3.3.3 ODLM integration on driver board                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 0                                                                       | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

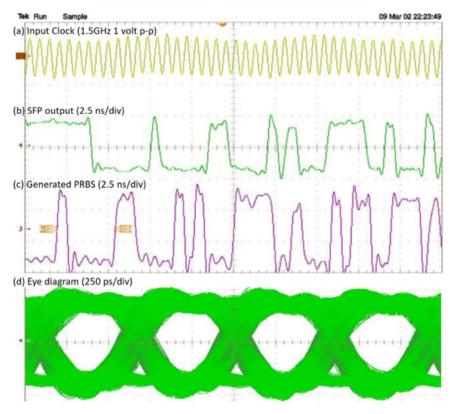

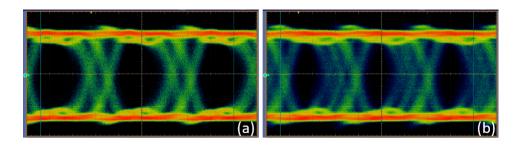

|      | 3.3.4 Characterization                                                  | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

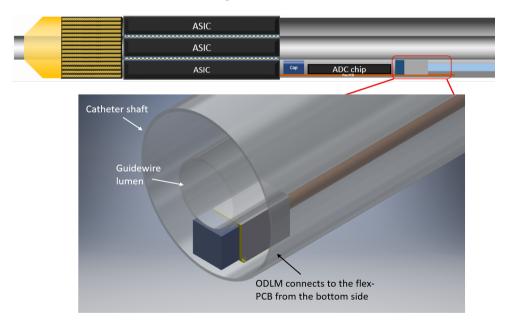

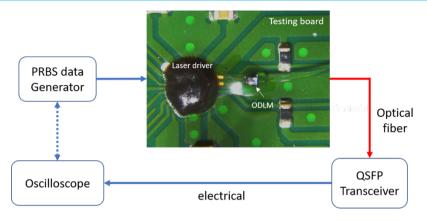

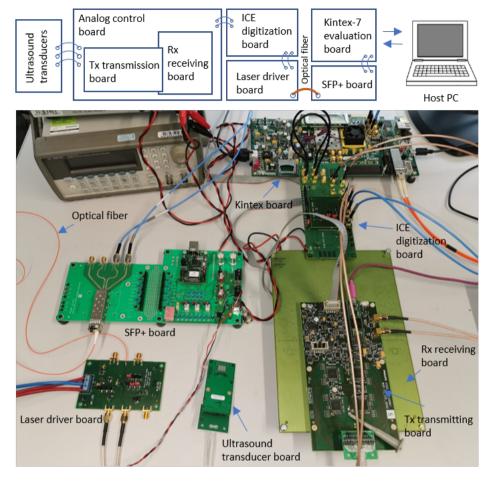

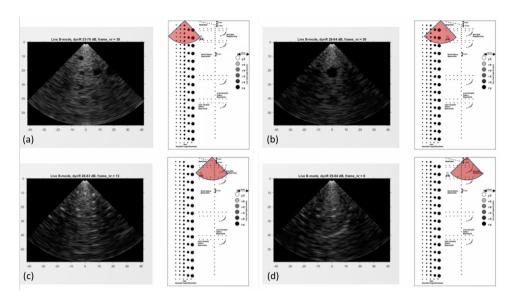

| 3.4  | Demonstrator: The ODLM in a digital Intracardiac Echocardiography (ICE) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | catheter system                                                         | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

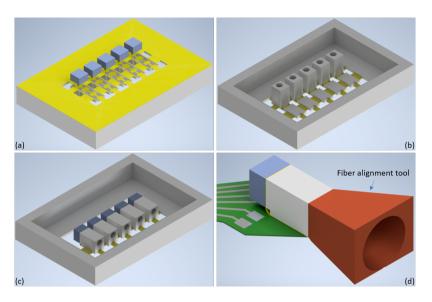

| 3.5  | Industrialization Perspective                                           | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 3.5.1 Device assembly                                                   | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 3.5.2 Device application                                                | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.6  | Conclusion                                                              | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

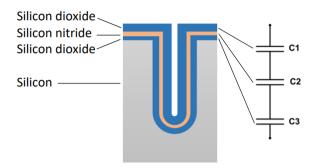

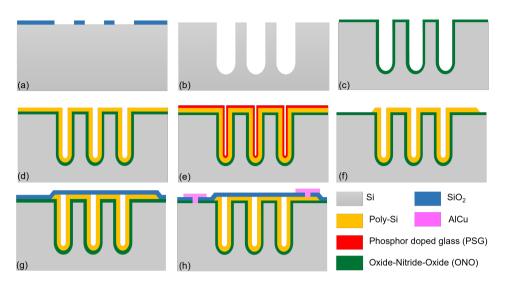

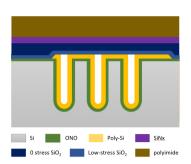

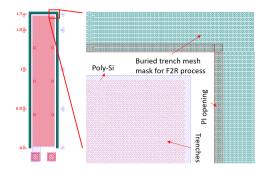

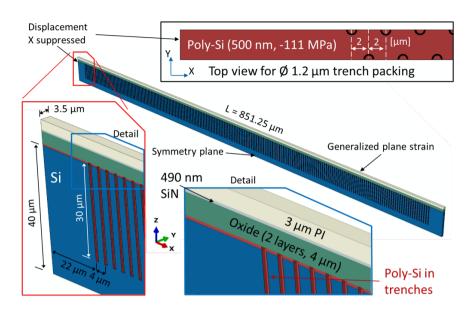

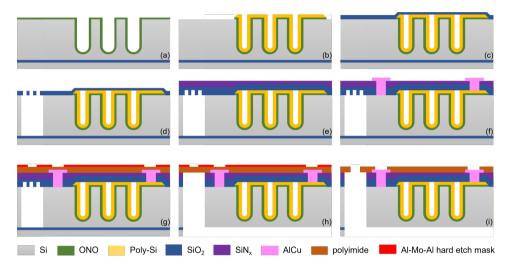

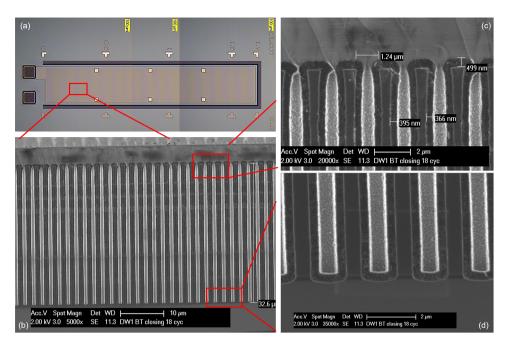

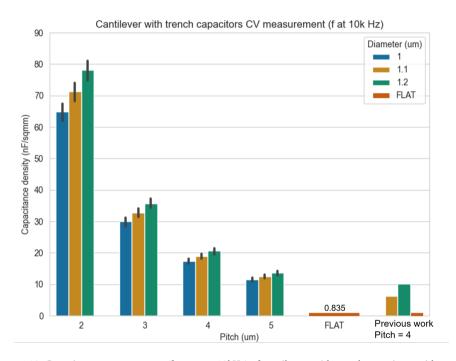

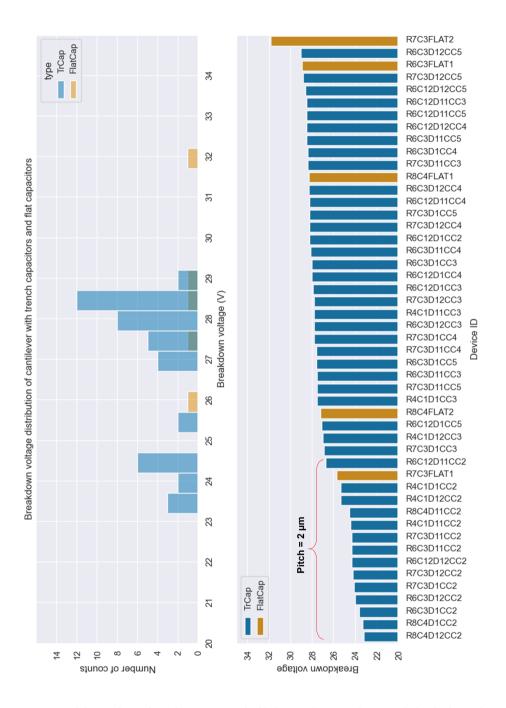

| Hiol | n-density embedded trench canacitors in the F2R                         | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| _    |                                                                         | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ***  |                                                                         | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | · · · · · · · · · · · · · · · · · · ·                                   | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |                                                                         | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.2  |                                                                         | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.2  |                                                                         | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |                                                                         | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |                                                                         | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |                                                                         | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |                                                                         | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.3  |                                                                         | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | ·                                                                       | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |                                                                         | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | •                                                                       | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |                                                                         | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

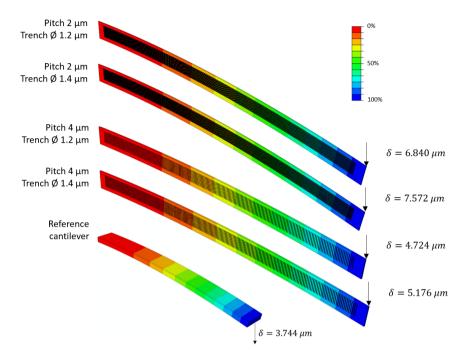

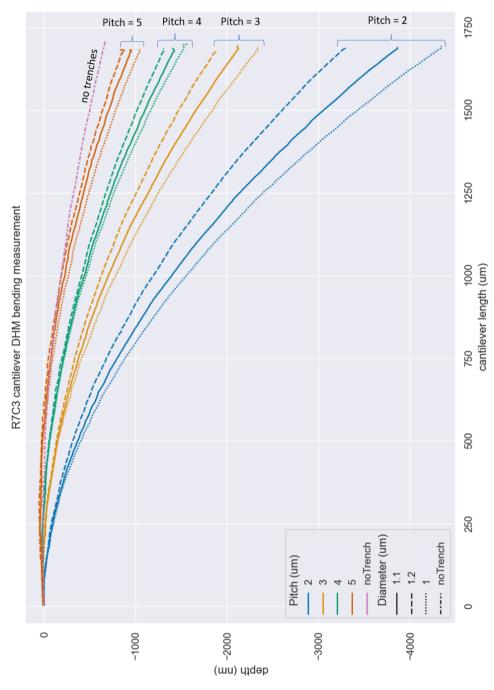

|      | 4.3.5 Stress characterization                                           | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |                                                                         | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.4  |                                                                         | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

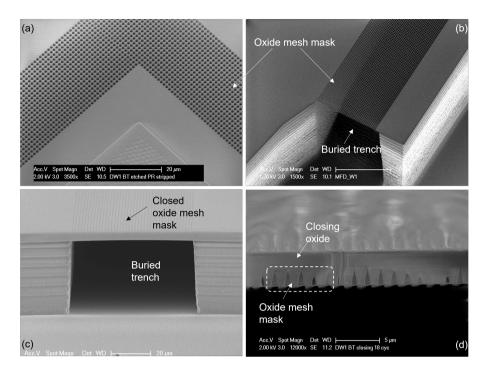

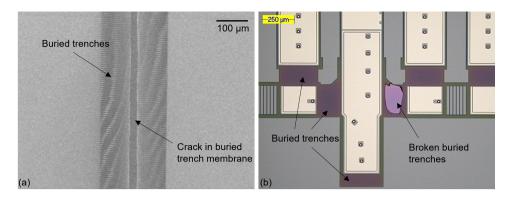

| Cavi | ity ROY SOI                                                             | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | ·                                                                       | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

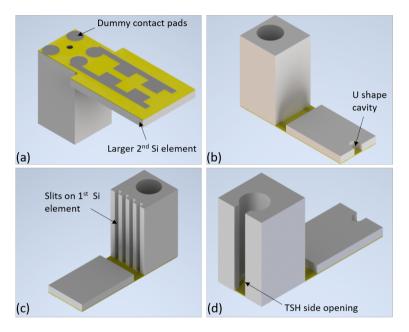

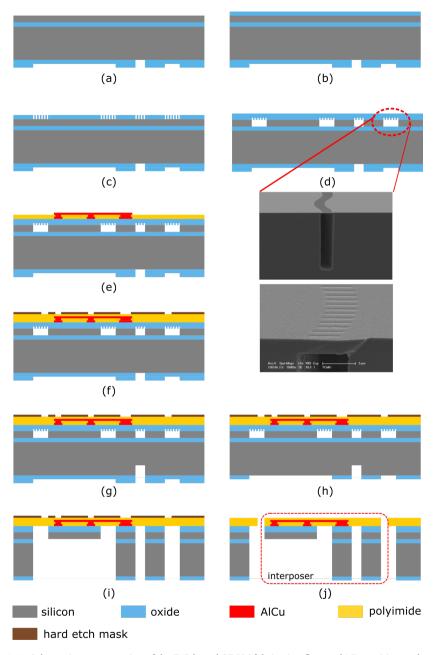

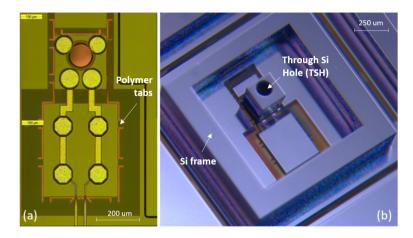

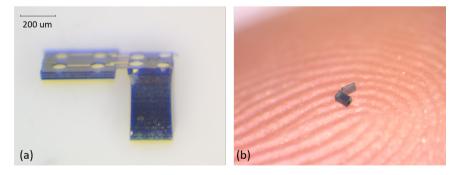

| 0.1  |                                                                         | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |