# MSc Thesis

FPGA-based Fault Emulation for Safety Critical ICs

Nivedita Lohar

# MSc Thesis

# FPGA-based Fault Emulation for Safety Critical ICs

by

### Nivedita Lohar

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Friday, September 22, 2023, at 14:00 hours.

Student Number: 5483565

Project Duration: November 2022 - September 2023

Thesis committee: Prof. Dr. Ir. Said Hamdioui TU Delft, supervisor

Do In Marite Fishersh

Dr. Ir. Moritz Fieback TU Delft, supervisor

Dr. Ir. Caspar Van Vroonhoven

Alessandro Trevisan

Analog Devices, supervisor

Analog Devices, supervisor

TU Delft, committee member

This thesis is confidential and cannot be made public until September 22, 2023.

An electronic version of this thesis is available at http://repository.tudelft.nl/.

### **Abstract**

In 2022, there were over 26 million electric automobiles on the road, a 60% increase with regard to 2021 and more than 5 times the stock in 2018. As automobiles become more electric and systems get increasingly complex, the safety requirements get more stringent. In 2011, the International Organization for Standardization (ISO) established ISO26262 to provide guidance to the semiconductor industry on the development process of safety essential ICs for automotive applications.

When evaluating the safety of a system parallel to the normal functional operation, traditional Design-for-Test (DFT) techniques such as scan chain, Built-In Self-Test (BIST), Joint Test Action Group (JTAG), and boundary scan are no longer viable options for two fundamental reasons. Firstly, safety assessment in the context of automotive applications necessitates evaluation at an application level, going beyond the capabilities of these techniques, which are primarily designed for structural and functional testing. Secondly, during safety checks, it is imperative that the normal operation of the integrated circuit (IC) remains uninterrupted, as the chip is often deployed in critical, real-time systems. These traditional DFT methods, while effective during the IC manufacture and production before they are released in the market, fall short of addressing the dynamic and application-specific safety concerns that arise during the operational lifecycle of safety-critical systems in sectors like automotive engineering.

To address these challenges, fault injection has emerged as the necessary step for safety assessment. ISO26262 explicitly recognizes fault injection as one of the most popular techniques for evaluating a system's safety and determining its Automotive Safety Integrity Level (ASIL). The safety metrics are required for certification of a product with ASIL. Fault injection allows for the creation of realistic fault scenarios and the assessment of how the system responds to these faults during normal operation, aligning more closely with the dynamic and application-specific nature of safety-critical systems in fields of automotive engineering.

Currently, many EDA companies provide Failure Mode Effects and Diagnostic Analysis (FMEDA) platforms for IC safety evaluations. However, these tools are time-consuming and resource-intensive. Additionally, as IC designs become more intricate, there is a reliance on fault reduction techniques such as statistical sampling, which entails simulating only a mere 5% of the overall fault space. Thus, an FPGA-based fault emulation system emerges as a promising approach to expedite this process.

The novelty of this work was in designing a dedicated platform tailored for the evaluation of safety-critical systems for automotive applications such as Battery Management Systems (BMS). This platform can execute the safety sequences on the system to evaluate the safety mechanisms implemented in the design in the presence of random faults assuming the chip is in use in the car. Moreover, the fault emulation activity provides the evidence necessary for the certification of products with ASIL level. Furthermore, performing this activity during the development stage helps in designing the ICs with the highest level of safety. The proposed FPGA-based fault emulation system efficiently overcomes three key challenges: it decreases execution time dramatically provides a speed-up of 296x compared to the simulation method, optimizes resource utilization, eliminates the tool license cost, and removes the requirement for considerable fault space reduction. This platform can emulate a large fault population of up to one million faults in less than three hours.

### Acknowledgements

As I write this section, marking the final step of my journey at TU Delft, I feel nostalgic, recalling the very first day I arrived in the Netherlands. These two years have been filled with a wealth of learning and emotions, and I would like to take this opportunity to express my profound gratitude to all the individuals who have made this journey a memory to cherish for a lifetime.

First and foremost, I extend my heartfelt thanks to my supervisors at TU Delft, Prof. Dr. Ir. Said Hamdioui and Dr. Ir. Moritz Fieback. They not only assisted me in resolving my various doubts related to the subject matter during my thesis but also groomed me to become a better engineer, well-prepared to tackle real-world challenges beyond the university. Their constant encouragement to think critically has equipped me to explore beyond the confines of this work.

I would also like to express my deepest appreciation to my supervisors at Analog Devices, Dr. Ir. Caspar Van Vroonhoven and Alessandro Trevisan. Their curiosity and active involvement in my work not only facilitated the timely completion of my thesis but also provided me with insights that extend far beyond the academic realm, into the industrial domain. This experience has endowed me with a unique perspective, allowing me to approach problems from both academic and industrial viewpoints. Additionally, I am grateful to all my colleagues at Analog Devices, who not only welcomed me into their professional family but also generously shared their valuable experiences, contributing significantly to my learning curve.

I am thankful to all my peers and friends who have been a part of this remarkable journey. Their presence turned this academic adventure into a joyful and enriching process, without which it would have been an arduous path to traverse.

Lastly, I wish to express my heartfelt gratitude to my parents and all my friends back in my home country for their unwavering support and constant availability throughout this journey.

This Acknowledgment section of the master's thesis captures the essence of the beautiful journey it has been.

Nivedita Lohar Delft, September 2023

### Contents

| Al | stract                                                                                                                                                                                                                                                     | i                                    |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Ac | knowledgements                                                                                                                                                                                                                                             | ii                                   |

| Li | of Figures                                                                                                                                                                                                                                                 | ii                                   |

| Li | of Tables                                                                                                                                                                                                                                                  | ii                                   |

| 1  | 1.1 Motivation . 1.2 Automotive Functional Safety in IC design 1.3 State of the Art . 1.4 Thesis Contribution . 1.4.1 Research goal . 1.4.2 Scope of the work . 1.4.3 Thesis Contribution .                                                                | 1<br>2<br>4<br>5<br>6<br>7<br>7<br>8 |

| 2  | 2.1 Introduction to ISO26262                                                                                                                                                                                                                               | 9<br>10<br>12                        |

| 3  | 3.1 Methods of performing Fault Injection       2         3.1.1 Simulation-based Fault Injection       2         3.1.2 Digital Fault Injection Emulation       2         3.2 Selected method for Fault Emulation       3                                   | 21<br>22<br>23<br>24<br>31           |

| 4  | 4.1 Project Overview                                                                                                                                                                                                                                       | 32<br>32<br>33<br>33<br>34           |

| 5  | 5.1 Performing Gate-Level Synthesis 5.1.1 Simplifications during the Gate-Level Netlist 5.2 Skew between clock-trees 5.2.1 Artificial skew generation FPGA 5.3 Modifying the GL netlist 5.3.1 Design of Fault Saboteurs 5.3.2 Insertion of Fault Saboteurs | 36<br>36<br>37<br>38<br>40<br>41     |

| 6  | Design and Verification  6.1 Purely Programmable-based Architecture                                                                                                                                                                                        | <b>45</b><br>45<br>46<br>48          |

Contents

| Re | ferer | nces                                                      | 69 |

|----|-------|-----------------------------------------------------------|----|

| 8  | Con   | nclusion                                                  | 67 |

|    | 7.6   | Limitations of the Fault Emulation System and Future Work | 66 |

|    | 7.5   | Performance Results                                       | 65 |

|    | 7.4   | Fault Classification Results                              | 64 |

|    | 7.3   | 8                                                         | 63 |

|    | 7.2   | 9                                                         | 62 |

|    | 7.1   | Design Under Test                                         | 58 |

| 7  | Syst  | tem Evaluation                                            | 58 |

|    |       | 6.3.1 Inspection of signals in the Fault Emulation system | 56 |

|    | 6.3   | Verification methodology                                  | 55 |

|    |       | 6.2.4 Limitations                                         | 55 |

|    |       | 6.2.3 Advantages                                          | 54 |

|    |       | 6.2.2 Software Implementation                             | 52 |

|    |       | 6.2.1 Building blocks of the architecture                 | 50 |

|    | 6.2   | Architecture 2                                            | 48 |

|    |       | 6.1.3 Limitations                                         | 48 |

|    |       |                                                           |    |

## List of Figures

| 1.1  | Trends in sales of Electric cars, 2016-2023[20]                                          | 1  |

|------|------------------------------------------------------------------------------------------|----|

| 1.2  | Battery Monitoring and balancing circuit overview [8]                                    | 5  |

| 1.3  | Overview of Fault Injection Techniques                                                   | 5  |

| 2.1  | ISO26262 Framework for safety-related product development [66]                           | 10 |

| 2.2  | V-model shows the process of product development at system level [23]                    | 11 |

| 2.3  | Steps in ASIL determination[44]                                                          | 12 |

| 2.4  | ASIL determination metrics[31]                                                           | 13 |

| 2.5  | Example of how fault travels from sub-part level to system level[32]                     | 13 |

| 2.6  | Cascading failure[1]                                                                     | 14 |

| 2.7  | Common cause failure[1]                                                                  | 14 |

| 2.8  | Dependent failure                                                                        | 15 |

| 2.9  | Independent failure                                                                      | 15 |

|      | Dual point failure                                                                       | 15 |

|      | Semiconductor reliability curve[32]                                                      | 16 |

| 2.12 | Type of hardware faults                                                                  | 16 |

| 2.13 | Fault occurrences and detection[32]                                                      | 17 |

| 2.14 | Safety related time intervals[1]                                                         | 18 |

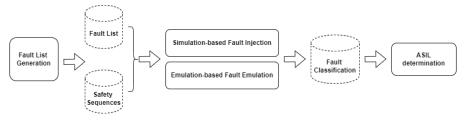

| 3.1  | Various methods used for performing Fault Injection                                      | 22 |

| 3.2  | An overview of a Fault Campaign                                                          | 22 |

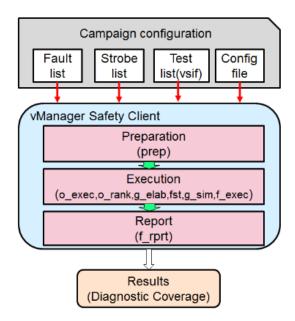

| 3.3  | Digital Fault Injection flow using vManager Safety Client                                | 23 |

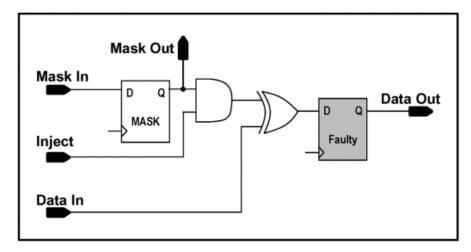

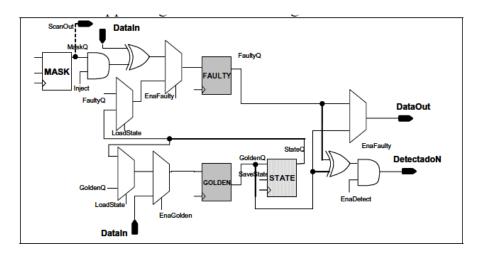

| 3.4  | Flip-flop replacement for the Mask-Scan emulation technique [40]                         | 26 |

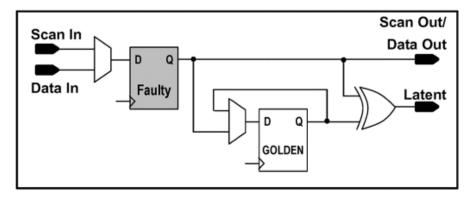

| 3.5  | Flip-flop replacement for the State-Scan emulation technique[40]                         | 26 |

| 3.6  | Instrument for time multiplexed [41]                                                     | 27 |

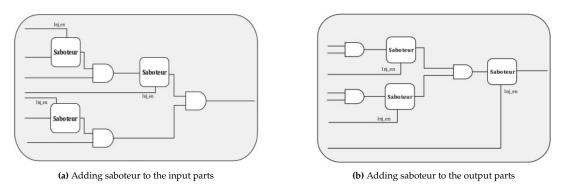

| 3.7  | Adding saboteurs at fault sites [21]                                                     | 27 |

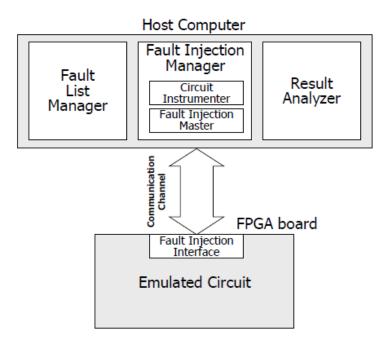

| 3.8  | Overview of Fault Injection environment [12]                                             | 28 |

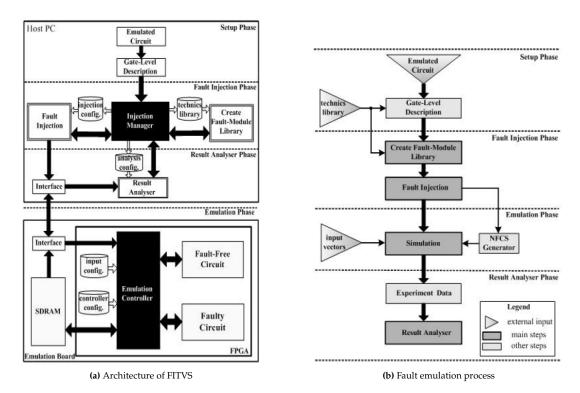

| 3.9  | Architecture of FITVS and Phases of Fault Emulation[68]                                  | 29 |

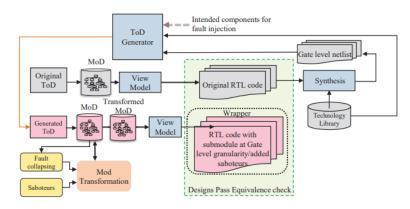

|      | Mixed register transfer/gate-level design generation flow [33]                           | 29 |

|      | Architecture at block-level[33]                                                          | 29 |

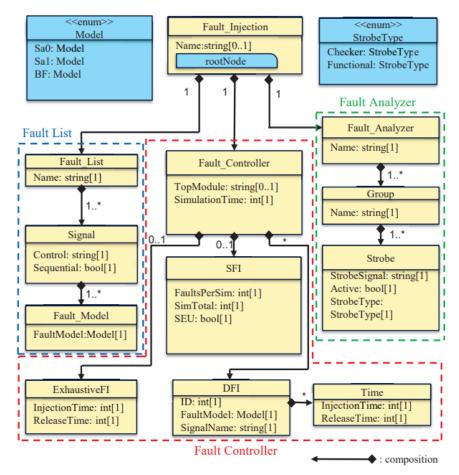

| 3.12 | Fault injection metamodel [33]                                                           | 30 |

| 4.1  | An overview of Fault Emulation using FPGA                                                | 33 |

| 4.2  | Process Flow                                                                             | 34 |

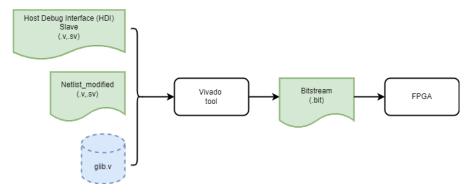

| 4.3  | The Hardware Design Flow                                                                 | 34 |

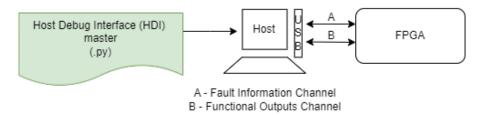

| 4.4  | The Software Flow                                                                        | 35 |

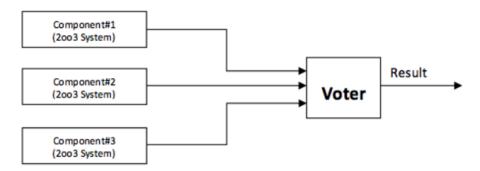

| 5.1  | Example for Triple Modular Redundancy (TMR)[19]                                          | 37 |

| 5.2  | Example for duplication for logic safety mechanism                                       | 38 |

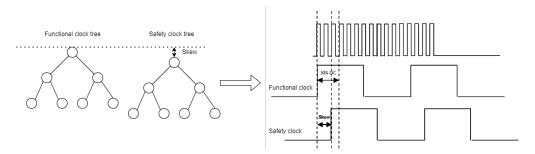

| 5.3  | Skew due to DFI avoidance in ASIC flow imitated in FPGA                                  | 38 |

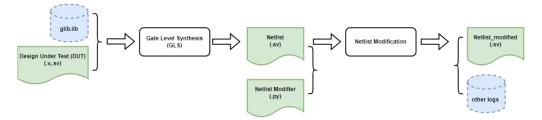

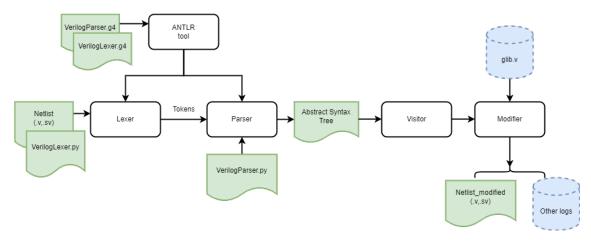

| 5.4  | Block diagram demonstrating the process of translation of the SystemVerilog netlist with |    |

|      | fault saboteurs                                                                          | 39 |

| 5.5  | Adding fault saboteur at every input of the gate in the netlist                          | 39 |

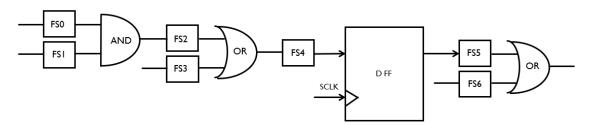

| 5.6  | All fault saboteurs form a fault chain pattern                                           | 40 |

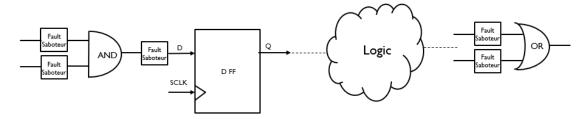

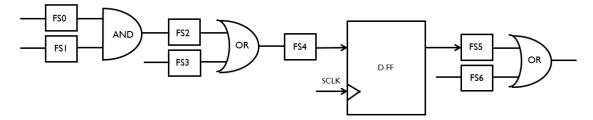

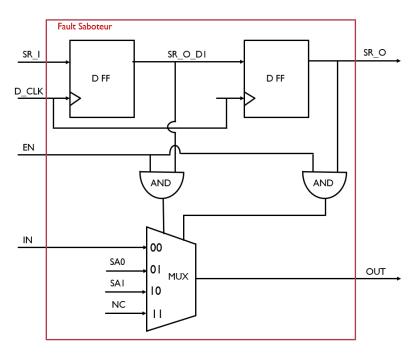

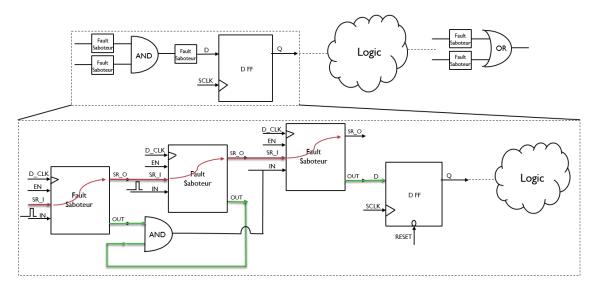

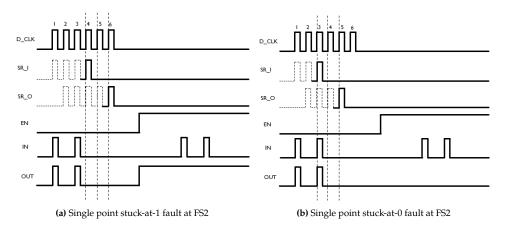

| 5.7  | Block diagram of Fault Saboteur                                                          | 40 |

| 5.8  | All fault saboteurs form a fault chain pattern                                           | 41 |

| 5.9  | All fault saboteurs form a fault chain pattern                                           | 41 |

| 5.13 | Logic Equivalence Check report for design vs modified netlist with fault saboteurs       | 44 |

|      | Logic Equivalence Check output for design vs modified netlist with fault saboteurs       | 44 |

List of Figures vi

| 6.1        | The initial architecture of HDI slave                                                              | 46       |

|------------|----------------------------------------------------------------------------------------------------|----------|

| 6.2<br>6.3 | Communication bus for fault campaign                                                               | 47<br>47 |

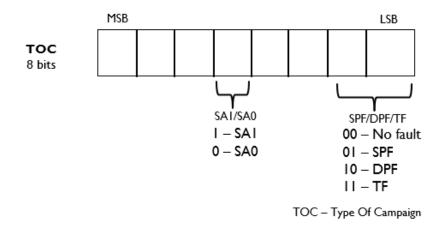

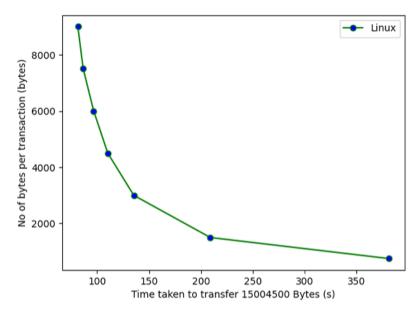

| 6.4        | Data transfer through UART using Python in Linux operating system                                  | 49       |

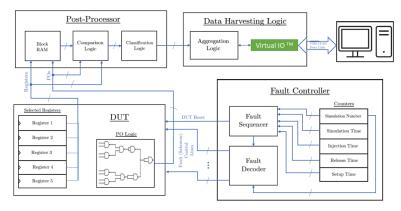

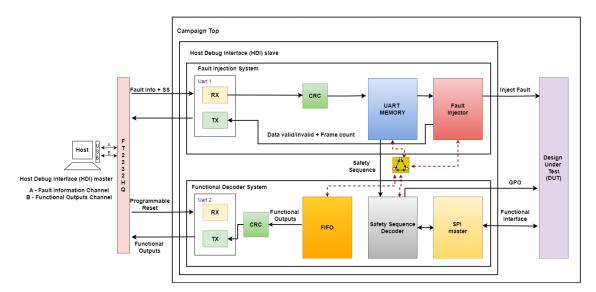

| 6.5        | Architecture 2 of the fault emulation system                                                       | 50       |

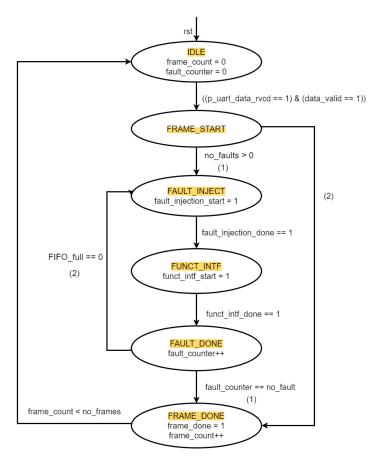

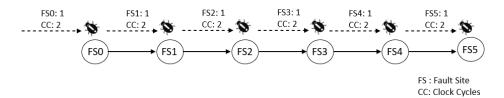

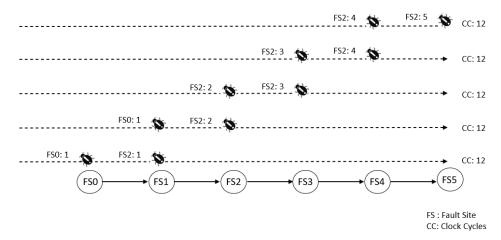

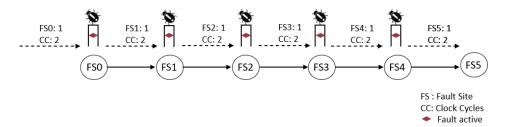

| 6.6        | Finite state machine illustrating the steps in executing the fault campaign                        | 51       |

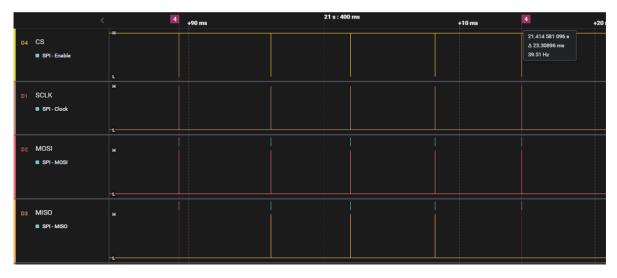

| 6.7        | Communication bus for architecture 2                                                               | 52       |

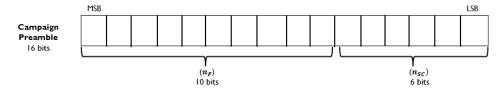

| 6.8        | Campaign preamble in the communication bus                                                         | 53       |

| 6.9        | Example for injecting single-point fault in the fault chain                                        | 53       |

| 6.10       | Example for injecting dual-point fault in the fault chain                                          | 54       |

|            | Example for injecting transient fault in the fault chain                                           | 54       |

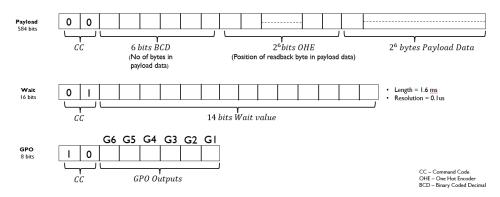

|            | Safety Commands: Payload, Wait and General purpose output (GPO)                                    | 54       |

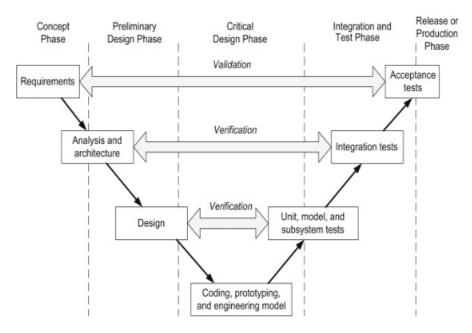

|            | V-model shows the process of product development at system level [23]                              | 55       |

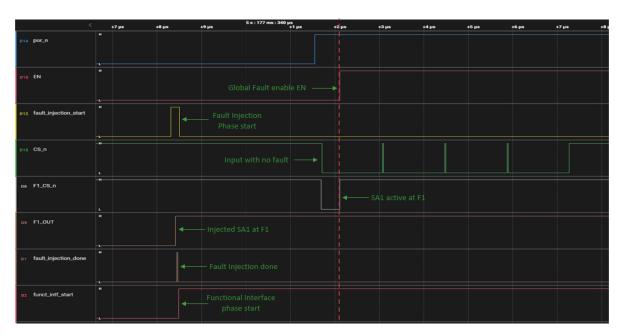

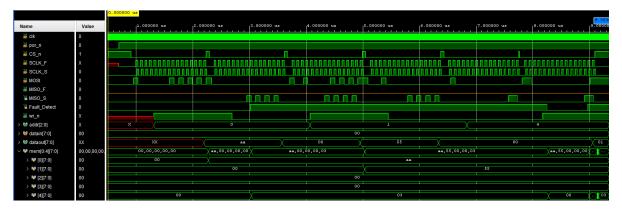

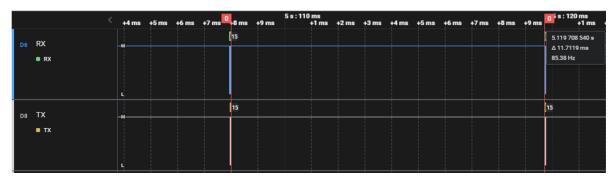

|            | Create of a Stuck-at-1 fault at fault site 1                                                       | 57       |

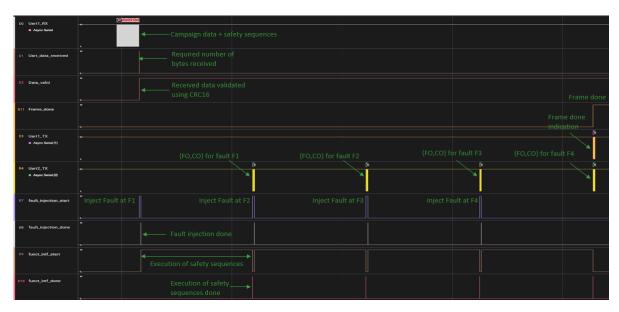

| 6.15       | Example: execution of fault campaign for a single transaction of UART containing four faults       | 57       |

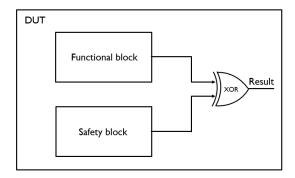

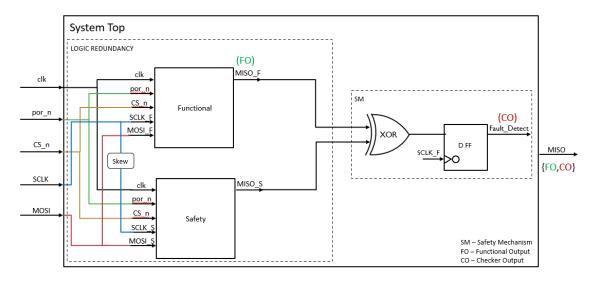

| 7.1        | Overview of DUT implementing the logic redundancy safety strategy and XOR-based                    |          |

|            | Safety Mechanism                                                                                   | 58       |

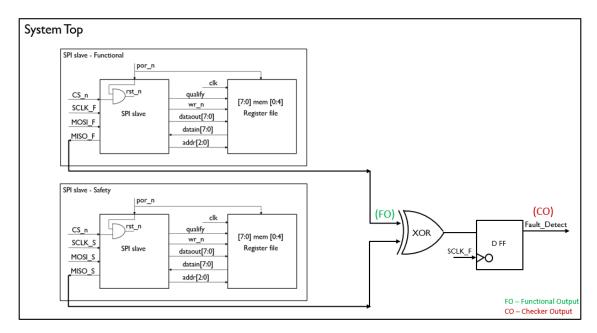

| 7.2        | Overview of the Design Under Test                                                                  | 59       |

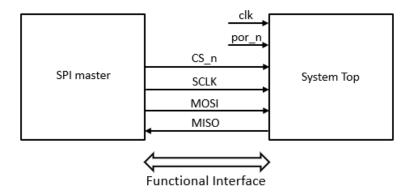

| 7.3        | Functional Interface to the DUT                                                                    | 59       |

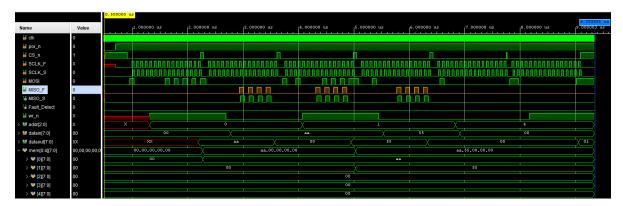

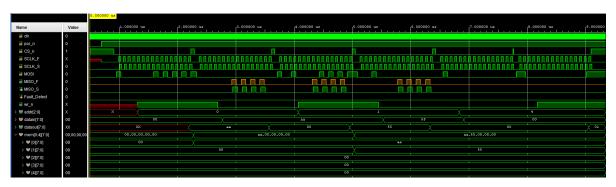

| 7.4        | Simulation output for golden run, FO1 = 8'hAA, FO2 = 8'h55, CO = 8'h00                             | 60       |

| 7.5        | Simulation output for fault type Undetected Non-Dangerous(UU), FO1 = 8'hAA, FO2 =                  |          |

|            | 8'h55, CO = 8'h00                                                                                  | 60       |

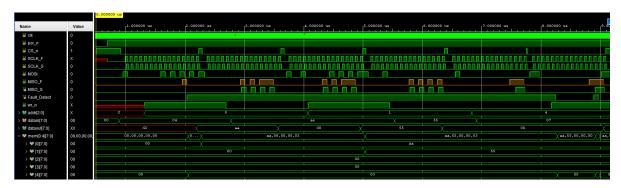

| 7.6        | Simulation output for fault type Detected Dangerous(DD), FO1 = 8'hAE, FO2 = 8'h55,                 |          |

|            | CO = 8'h03                                                                                         | 61       |

| 7.7        | Simulation output for fault type Detected Non-Dangerous (UD), FO1 = 8'hAA, FO2 = 8'h55, CO = 8'h03 | 61       |

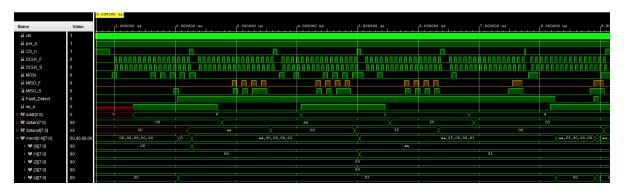

| 7.8        | Simulation output for fault type Undetected Dangerous (DU), FO1 = 8'h00, FO2 = 8'h00,              |          |

|            | CO = 8'h00                                                                                         | 61       |

| 7.9        | Software overhead during the transfer of fault information using the communication                 |          |

|            | interface                                                                                          | 62       |

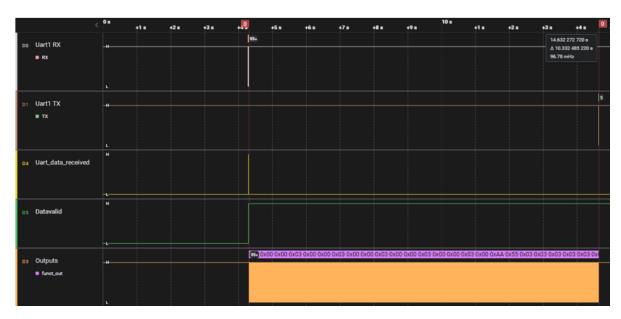

|            | Software Overhead during execution of the safety sequences                                         | 62       |

|            | Time taken to execute the single frame of Uart consisting of 1023 faults                           | 64       |

| 7.12       | Fault classification matrix                                                                        | 65       |

### List of Tables

| 2.1 | Minimum operation time without errors for ASIL classes[44]                                  | 11 |

|-----|---------------------------------------------------------------------------------------------|----|

| 2.2 | Random hardware Failure Rates (FR) in Failure in time (FIT) [44]                            | 11 |

| 2.3 | ISO26262 fault performance metrics [44]                                                     | 17 |

| 2.4 | HARA example for BMS system                                                                 | 19 |

| 2.5 |                                                                                             | 19 |

| 2.6 | FSRs for BMS system                                                                         | 20 |

| 3.1 | On-the-fly emulation technique runtime values [33]                                          | 30 |

| 3.2 | DFI performance of Battery Management System IC using Cadence Xcelium Fault Simulator       |    |

| 6.1 | Time taken to transfer 15M bytes of data through UART in varying chunk size per transaction | 49 |

| 6.2 | Configuration of parameters present in the communication bus                                | 52 |

| 7.1 | Classification of faults                                                                    | 62 |

| 7.2 | Campaign configuration parameters for Architecture 1                                        | 63 |

| 7.3 | Campaign configuration parameters for Architecture 2                                        | 63 |

| 7.4 | Fault Classification                                                                        | 65 |

| 7.5 | Performance comparison of Architecture 1 and 2 against the simulation benchmark             | 66 |

### Introduction

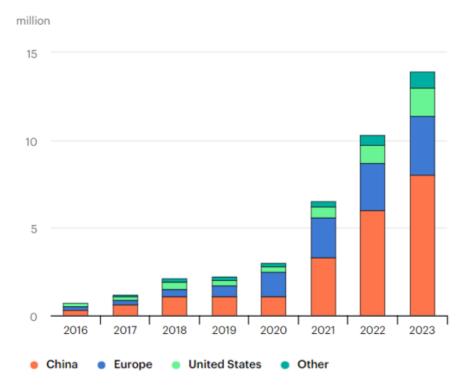

The Electric Vehicle was invented in 1834. However, due to the limitations associated with the batteries and the rapid advancement in Internal Combustion Engines vehicles, EVs almost vanished from the scene until the early 1970s. In the late 20th century due to the energy crisis, the interest in EVs was rekindling [10]. In the last 2 decades, the electric vehicle markets have expanded at an exponential rate, with sales exceeding 10 million in 2022. Electric vehicle sales have more than tripled in three years, from roughly 4% in 2020 to 14% in 2022. Figure 1.1 shows the trends in sales of Electric cars from 2016 to 2023. EV sales are predicted to remain sturdy through 2023. Over 2.3 million electric vehicles were sold in the first quarter, representing a 25% increase over the same period the previous year. Sales are projected to reach 14 million by the end of 2023, indicating a 35% growth year on year. As a consequence, electric vehicles account for 18% of overall vehicle sales [20].

Figure 1.1: Trends in sales of Electric cars, 2016-2023[20]

The electronics in these EVs must meet high functional safety and reliability requirements. Traditionally, automotive manufacturers and system suppliers were in charge of functional safety criteria. However, as

1.1. Motivation 2

the complexity of electronics grows, the responsibility for addressing functional safety is also spreading along the supply chain to semiconductor businesses and design tool suppliers. Functional Safety (FuSa) is the idea of ensuring that automobile functions work reliably, even when something unexpected or dangerous occurs, thus protecting individuals from unacceptable risk or damage.

In 2011, the International Organization for Standardization developed ISO26262, which provides guidelines on safety-related electronic and electrical systems in automobiles. This document [51] defines a set of regulations that automotive chip development companies must follow in order to certify their products for use in commercial vehicles. Furthermore, ISO26262 defines a fault classification system known as Automotive Safety Integrity Levels (ASIL) with the goal of reducing potential dangers caused by the faulty behavior of the electronics [50]. There are four levels of ASIL A, B, C, and D with D being the highest degree of safety level.

In order to certify the products with ASIL level, there is evidence required that the system developed for safety-related applications complies with all ISO26262 requirements. Currently, ISO26262 considers fault injection as one of the mandatory steps in system validation activities. The industry now uses a range of safety tools from EDA companies for Failure Modes, Effects, and Diagnostic Analysis (FMEDA). However, as designs get more sophisticated, the fault injection process using simulations might take days or even months.

The primary goal of this project is to accelerate fault injection by developing an FPGA-based emulation-based platform for testing system safety in the presence of random faults. The rationale for the need for such a platform is discussed in this chapter. Furthermore, various different techniques of testing a system are explored, and it is emphasized that fault injection is necessary for assessing a system, particularly for safety purposes. Following that, the significance of Functional Safety and the various processes used in the development of safety-critical ICs are demonstrated. Second, the most recent strategies in the field of fault injection are discussed. Finally, the project's purpose and obtained results are presented.

#### 1.1. Motivation

Design for Testability (DFT) is a critical aspect of modern integrated circuit (IC) design, aiming to ensure that electronic components and systems are easy to test and diagnose for faults or defects [17]. DFT emerged in the mid-20th century as semiconductor technology advanced and integrated circuits became increasingly complex. Engineers and designers recognized the need for efficient testing methods to identify manufacturing defects and ensure the reliability of electronic systems. As ICs grew in complexity, traditional testing techniques proved inadequate, leading to the development of DFT [42].

In the early days of DFT, designers mainly relied on manual techniques to improve testability. These included adding test points to the circuit layout, simplifying circuit structures to enhance observability and controllability, and ensuring that faults were more easily detectable [63]. These rudimentary approaches laid the foundation for more sophisticated DFT methodologies.

One of the seminal developments in DFT came with the introduction of scan design in the 1970s [65]. This method involved incorporating shift registers into the circuit to control the state of all flip-flops, allowing for easy access and control during testing. Scan design significantly improved testability and became a cornerstone of DFT. In the 1980s, the concept of Built-In Self-Test (BIST) gained prominence [27]. BIST techniques involve embedding test generators and response analyzers within the IC itself, enabling autonomous testing without external equipment. BIST reduced the reliance on external testers and contributed to cost-effective testing. The Joint Test Action Group (JTAG) standard, introduced in the 1990s [64], provided a standardized approach to testing and debugging PCBs and ICs. JTAG utilizes a boundary scan chain to access and test various components on a board, enhancing testability for complex systems. As ICs continued to grow in complexity, hierarchical DFT techniques emerged. These approaches involved dividing the design into smaller manageable blocks, each with its own DFT structures. Automatic Test Pattern Generation (ATPG) tools were developed to generate test patterns for these hierarchical structures, reducing the complexity of test generation.

In the realm of safety-critical integrated circuits (ICs) especially for automotive applications, the challenge lies not only in ensuring their functionality but also in verifying their performance under the most

1.1. Motivation 3

demanding real-world conditions where random failures could occur. Random faults are the ones that can arise unexpectedly throughout a hardware element's lifespan. When ICs are embedded in systems that must operate seamlessly in situations such as self-driving cars navigating busy streets delivering life-saving treatments, conventional Design for Testability (DFT) techniques face limitations. These traditional methods, primarily tailored for controlled lab environments or manufacturing testing, often fall short in simulating the dynamic and unpredictable scenarios encountered in operational use. Consequently, testing safety-critical ICs while they perform their normal functions presents a unique conundrum. In such cases, the most effective approach to guaranteeing their reliability and safety is through fault injection testing conducted in parallel to their standard operation [55]. This methodology allows for the rigorous assessment of ICs responses to random faults, ensuring they meet the stringent safety requirements of ISO26262.

Moreover, in safety-critical applications like autonomous vehicles, ICs must perform their functions while the system is in motion. Testing these ICs using DFT methods typically requires halting or isolating them from the operational system, which doesn't provide a realistic assessment of their performance under actual conditions. The battery management system ICs used in hybrid vehicles, for example, continually measure the voltage and current of the battery cells. To test this system for random single-point faults, safety procedures are run in tandem with battery readings to guarantee the system is not experiencing overvoltage or overcurrent [47].

To assure the functional safety of the products, several techniques for design known as Safety Mechanisms (SM) such as logic redundancy, multiple processing paths, triple modular redundancy, fail-safe mechanisms, and fault-tolerant patterns are incorporated in the safety-critical ICs [19]. These safety features must be examined for random faults assuming the vehicle is in motion in order to provide evidence for ASIL certification. Furthermore, this serves as proof of safety products to the OEMs, Tier 1 and Tier 2 customers. OEM stands for Original Equipment Manufacturer; these are the ultimate product makers who deal with the vehicle's final market release. Tier 1 suppliers create solutions that are tailored to the completed product without substantial changes. Tier 1 must, however, employ parts that allow for component manufacture. Tier 2 joins the picture here. These customers utilize these safety-critical ICs.

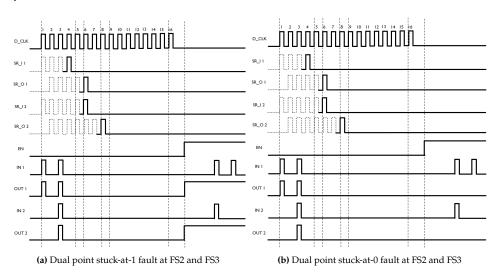

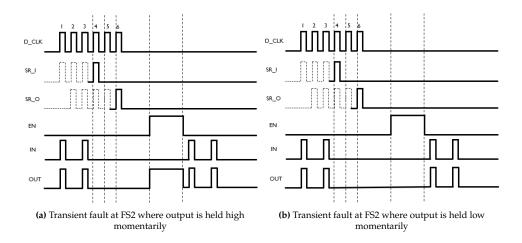

To assess the safety mechanisms (SMs), various sets of safety sequences are created [43]. These sequences are detailed in a document referred to as the Safety Manual, which is provided to the customers for monitoring the ICs. During the verification process, fault injection is performed to evaluate the Failure Modes, Effects, and Diagnostic Analysis (FMEDA). During fault injection, random faults such as single-point, dual-point, or transient faults are injected into the system and various safety routines are executed to examine the behavior at an application level [49][61].

Currently, the industry employs a variety of safety tools from EDA firms, such as Cadence's Xcelium Fault Simulator, a simulation tool used for executing Digital Fault Injection (DFI). Synopsys also offers a VC Functional Safety Manager, which is a single platform for doing FMEDA. However, fault Injection using a simulation tool becomes extremely time-consuming as the circuit complexity increases and the fault space grows a few hundred thousand. These simulations take weeks or even months for a fault space of 1M faults. As a result, there is a need to limit the amount of faults for simulations without affecting the quality of the results. Statistical sampling [59], fault collapse [62], and formal approaches [6][5] are some of the techniques used to reduce fault space. Statistical sampling, for example, aids in minimizing the fault space by simulating only 5-10% of the total fault population. Though this method guarantees that the results are unaffected, it is assumed that these defects represent the whole fault space.

Furthermore, most modern systems are mixed signal in nature, and as complexity rises, simulations using Analog Mixed Signal (AMS) Fault Injection and Digital Mixed Signal (DMS) Fault Injection become exceedingly cumbersome when compared to fully digital fault injection. This is because of the inherent complexity of analog and mixed-signal circuits, the need for continuous-time modeling, and convergence challenges that contribute to slower simulation times compared to fully digital designs. This necessitates the development of an environment that allows for hardware acceleration.

There are two ways of achieving hardware acceleration, one hardware emulators provided by the EDA companies and secondly, the FPGAs. This emulation platform should be capable of modeling the

Design Under Test, performing fault injection on the modeled hardware, and evaluating the system by running the functional and safety . From the literature study, it was observed that for fully digital circuits, the execution time grows almost linearly with the increase in the fault space. Secondly, the DMS simulations are faster than the AMS simulations because, in DMS, the analog circuits are accurately modeled using the SystemVerilog user-defined datatype EEnet and Real Number Modeling (RNM) which provides acceleration over the actual schematics used in AMS simulations.

In the emulation world, particularly with FPGAs, significant hardware acceleration has been accomplished. However, there is some non-recurring cost at the start of the campaign owing to transferring the design from ASIC flow to FPGA. Including additional logic to physically incorporate defects into the design. Moreover, as seen in the graph, there is significant latency involved even for smaller fault spaces. This is due to the campaign configuration on the FPGA before executing the fault injection. However, as the fault space grows, the achieved speedup outweighs the simulation methods. As a result, this project leverages the use of hardware acceleration gained using FPGAs. It focuses on developing a platform capable of doing fault injection in order to assess the system's safety by running the safety sequences and evaluating the system in the presence of random faults. The primary objective is to reduce the execution time of fault campaigns. Furthermore, this activity aids in resolving the limited availability of resources and allows emulation of the complete fault population. For this experiment, the performance assessment of the execution time for 1M fault space was considered.

In the next parts, the requirement of automotive functional safety in IC design is introduced. Following this, some of the prior work in performing fault injection is discussed. Lastly, the scope of this project and the expected outcome are presented.

#### 1.2. Automotive Functional Safety in IC design

Safety in technological development is not a novel notion. It was widely used in applications such as aerospace, military, and industrial machinery. As the technology progressed, the next-generation automobiles are increasingly becoming electrified, and the introduction of self-driving automobiles with Advanced Driver Assistance Systems (ADAS) drove the silicon designers towards creating even more sophisticated automotive integrated circuits. These chips must operate as intended, without any malfunctioning. This brings us to the realm of the Functional Safety (FuSa) concept. FuSa describes the detection of potentially hazardous situations and the activation of preventative procedures to mitigate them. For instance, if the car crashes in an accident, the sensors must detect the severity correctly and deploy the airbags within a few milliseconds. Even in case of malfunction, the system should return to a safe state where there is no unreasonable level of risk.

In 2011, the International Organization for Standardization (ISO) published ISO26262 [1], an international functional safety standard that protects the safety of a vehicle's electronics and electrical systems that are installed in series production passenger cars with a maximum gross vehicle mass up to 3500 kg. In 2018, the ISO26262 standard was amended to include all road vehicles, with new requirements reflecting current technological advancements.

ISO26262 specifies many procedures for determining how FuSa should be managed. One of these activities is determining the Automotive Safety Integrity Level (ASIL) that will be applied to the application. It assigns a grade from A to D, with D being the highest safety-critical level that must adhere to the most stringent testing. For example, Components like rear lights require merely an ASIL A rating. Whereas Headlights and brake lights are often ASIL B, whilst cruise control is typically ASIL C. And the airbags, anti-lock brakes, and power steering need an ASIL D grade, the highest level of rigor devoted to safety assurance because the hazards associated with their failure are the greatest.

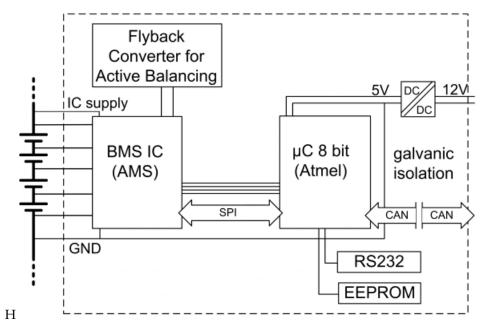

One of the example of ASIL D design is the Battery Management System (BMS) used in electric cars to monitor cell voltage and current. This is illustrated below. Figure 1.2 presents a circuit diagram of a battery monitoring unit. In this figure, the BMS IC is the core of the monitoring circuit. The 8-bit AMTEL microcontroller employs a SPI bus to communicate with this IC and the various digital IOs. The microcontroller's job is to enable Controller Area Network (CAN) bus connection between the monitoring IC and the Pack Management Unit (PMU), regulate cell data acquisition, and monitor the balancing process. The microcontroller executes different functional and safety sequences in regular time intervals to monitor the State of Health (SOH) and State of Charge (SOC) for the safety of the

1.3. State of the Art 5

Figure 1.2: Battery Monitoring and balancing circuit overview [8]

batteries.

#### 1.3. State of the Art

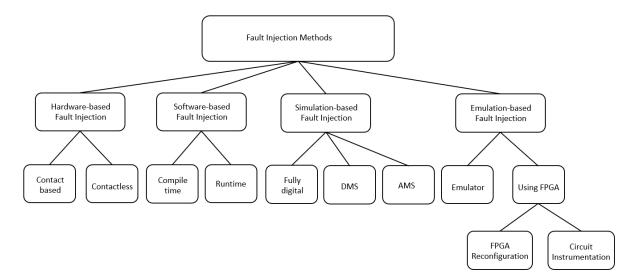

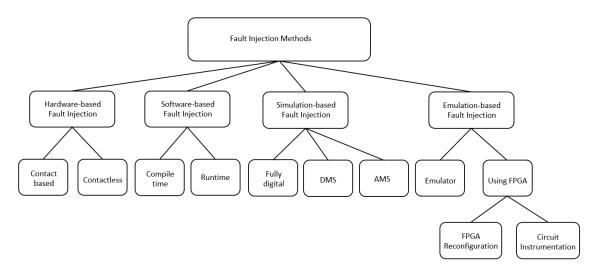

The fault injection technique goes back to the 1970s when it was initially employed to trigger hardware problems. Hardware Implemented Fault Injection (HWIFI) is a form of fault injection that seeks to replicate hardware breakdowns within a system. The initial hardware failure tests consisted of simply shorting connections on circuit boards and watching the effect on the system. Currently, there are four major categories of fault injection, namely, Hardware-based fault injection, Software-based fault injection, Simulation-based fault injection, and Emulation-based fault injection [29][69][36]. The overview of fault injection techniques is shown in Figure. 1.3.

Figure 1.3: Overview of Fault Injection Techniques

The purpose of **Hardware-based fault injection** is to generate disruptive signals or events, or to change the physical environment in which a device functions, in order to trigger incorrect behavior in electronic

1.4. Thesis Contribution 6

equipment. This can be accomplished through direct contact with the target chip's external pins or using contactless methods such as heavy ion radiation or electromagnetic interference.

To target software applications and operating systems, a **Software-based fault injection** method is employed. This approach is appealing since it is inexpensive and does not require any additional hardware. The method has two kinds, depending on the time when a fault is injected. The Compile-time fault injection method alters the source code or assembly code of the system before the start of execution of the program. Whereas the Run-time faults are injected using special trigger events like interrupts to activate faults.

The Simulation-based fault injection is carried out in three different ways,

- 1. Digital Fault Injection Simulation

- 2. Digital Mixed Signal (DMS) Simulation

- 3. Analog Mixed Signal (AMS) Simulation

To begin, the Digital Fault Injection approach involves building a simulation model of the system under examination and faults using HDLs such as Verilog and VHDL.[52]. Second, for mixed-signal architectures that include both digital and analog components, novel techniques for fault injection at the system level are required. To perform the Digital Mixed Signal (DMS) simulations, the analog circuits are accurately modeled using various methods like Verilog-A, Verilog-AMS, Real Number Modeling (RNM), and SystemVerilog-based datatype EEnet. Finally, Analog Mixed Signal (AMS) simulates the precise schematics of analog circuitry with digital interfaces and tests the system for different analog faults like open, short, changing clock frequency and duty cycle and voltage and current spikes.

The final category is **Emulation-based fault injection**. This can be done in two ways, using hardware emulators or employing FPGAs [22]. Various EDA vendors provide emulators like the Palladium emulation platform offered by Cadence, the Veloce by Mentor Graphics, Zebu Server by Synopsys. These platforms support the verification of designs up to several billion gates. Despite the high execution speed and scalability of these emulators, the high price is a significant drawback.

The second option is the emulation of faults using FPGAs. There are two categories to perform emulation of faults on FPGA based on the type of implementation [21].

- 1. **Reconfiguration-based** technique where one fault can be configured at a time using partial or full FPGA reconfiguration [3],[56].

- 2. **Instrumentation-based** technique where additional hardware is integrated with the design to enable fault activation from an external host [41],[40].

In this study, the instrumentation-based emulation approach is used, where a custom fault saboteur is created to inject the fault into the design's gate-level netlist. Previously, this approach was used to examine the system's functioning. This thesis applies the principles of fault injection on the FPGA and safety-related techniques used in simulation-based fault injection to develop a system that emulates random faults in order to evaluate the system's safety on the FPGA and establish ASIL levels, as mentioned in section 2.1.1. Chapter 3 delves further into the two forms of fault injection, simulation-based and emulation-based, as well as the numerous strategies employed.

#### 1.4. Thesis Contribution

The main goal of this thesis is to develop a fast and efficient platform to perform fault emulation on the FPGA for evaluating the designs for safety-related automotive applications to determine the ASIL level. There are several procedures involved throughout the development process of these ICs and even beyond once the chip is in the field. With the growing demand for faster chip time to market, there is a need to accelerate the development process. Furthermore, there are other factors such as labor cost, and resources available which impact the overall process. This endeavor aims to speed up the fault injection process in order to validate the functioning of Safety Mechanisms and provide diagnostics of fault classification to certify the product for ASIL.

#### 1.4.1. Research goal

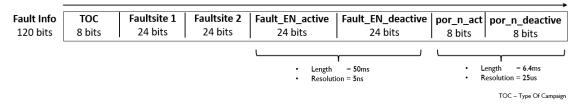

The primary goal of this research is to investigate the various techniques used in performing fault injection. Moreover, to evaluate these methods and formulate an architecture that helps to expedite this process. Currently, the fault injection activity is performed using extensive simulations which take days or even months. The main limitation of the simulation-based FI is the significant software overhead and availability of the resources. The simulation data provided by Analog Devices for one of their Battery Management Systems (IC) developed for ASIL D level showed the execution time for the fault injection activity to be 22 days. This is detailed in section 3.3. This work aims to bring this activity from simulation to the emulation world, building an architecture with minimal software overhead, and executing the fault campaign in less than 3 hours for a fault space of 1M.

#### 1.4.2. Scope of the work

The state of the art revealed that FPGA-based fault emulation is one of the most feasible and cost-effective ways of performing fault injection. The fault injection activity mainly serves two purposes, firstly the diagnostic metrics of the fault campaign activity are required to provide evidence in order to certify the product before releasing it in the market. Secondly, evaluating the system's behavior in the field well during the development stage helps in designing the systems with the highest level of safety.

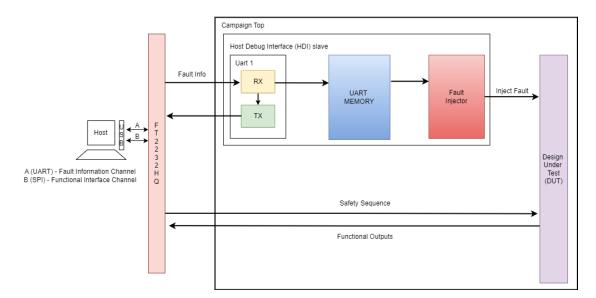

To perform the fault emulation on the FPGA requires three main components, firstly an automated flow that can map the design from ASIC to FPGA flow. Second, a hardware design that sits parallel to the Design Under Test (DUT) on the FPGA that can perform the fault injection and evaluation of the system on the FPGA, and lastly a software platform that can co-ordinate the fault campaign between the host PC and the FPGA. In this work, all these components are developed and tested. The motivation of the experiment is to evaluate the execution time of the fault campaign activity in comparison to the simulation-based method and achieve a minimum of 250x speed up.

#### 1.4.3. Thesis Contribution

The outcome of this work is to develop a fault emulation platform that is fast and universal to perform the fault injection for a mixed signal system. There are three main components of this project,

- 1. First, a compiler was built to transform the gate-level netlist with a modular design for fault injection. This was accomplished using a Python-based platform and the ANTLR tool, which automatically deconstructs the netlist and implements the necessary changes without any manual intervention.

- 2. Second, the architecture of the emulation platform to perform the testing on the targeted design on the FPGA was developed. This design required to be fast enough to execute the functional and safety sequences with minimum overhead. This activity was accomplished in two stages: first, a simple architecture was developed, but had significant software overhead and was able to achieve a speedup of 43.2x; second, the limitations of this architecture were realized and improved in a final architecture with minimal overhead, allowing the time taken to execute the functionality of the DUT to be the largest time factor in the calculation of the fault campaign's execution speed and a speedup of 296x was achieved.

- 3. Finally, a software platform to efficiently communicate the campaign configuration from the host PC to the campaign manager on the FPGA was implemented, as well as record the outputs and execute the final fault categorization, which is the final outcome of this effort.

#### 1.5. Report Organization

The rest of the report is divided into 9 chapters.

Chapter 2 describes the Functional Safety procedures used in the IC development process. It presents the ISO26262 standard for automotive applications and discusses the various ASIL requirements.

Chapter 3 discusses the various fault injection techniques used for evaluating the safety-critical integrated circuits. It discusses the various simulation-based methodologies and their limitations, as well as lays the groundwork for the emulation-based approach.

Chapter 4 introduces the FPGA-based Fault Emulation platform developed in this work. This chapter provides an overview of the system requirements and system specifications considered for this experiment as well as touches upon the flow of this project.

Chapter 5 establishes the preparation of the design for mapping onto the FPGA. It gives details about the gate-level synthesis and the netlist modifications with fault saboteurs.

Chapter 6 dives into the details of the two architectures experimented in this research. The various blocks of the system and their functions are explained. The main constraints of the first architecture's efficiency are underlined, and it is described how this is overcome in the second.

Chapter 7 focuses on the performance of the two architectures and a comparison of the two. It also provides the fault classification results for the second architecture which is the expected output of this project.

Chapter 8 summarizes the results of this work, discusses the simplifications made in order to expedite the activity without affecting the target goal of reducing the execution time of the fault injection activity, as well as mentions some of the limitations of the system.

Chapter 9 talks about the scope of future work. It illustrates how this project can be expanded in various areas.

# Background on Functional Safety (FuSa) in IC design

The primary goal of Functional Safety (FuSa) in automobiles is to ensure the safety of human lives. The idea is to build systems that are reliable even in the face of unforeseen events. Initially, the concept of FuSa was applied to the development of electronics at a system level. But with increasing complexity and growing heterogeneous systems, its relevance has been observed at the chip development level. Today, automotive Original Equipment Manufacturers (OEM)s require safety-certified semiconductors to manufacture cars with high safety standards that gain the trust of their customers. This prompted EDA firms to see the tool development process as embracing the safety aspect. EDA companies like Cadence provide state-of-the-art solutions that cover parts of the safety spectrum, such as FMEDA (Failure Modes Effects and Diagnostic Analysis).

Moreover, the applicability of FuSa extends even beyond the IC development process. Electric vehicles (EVs), for example, employ a large number of Li-ion battery cells to achieve battery pack voltages in the hundreds of volts and capacities in the tens of kWh. These ICs necessitate safety measures not only throughout the design phase but also during the lifespan of the device in which they are placed. This draws focus on FuSa in the system on the fly.

In the following parts, the various safety aspects of the system and the standard followed during the IC design process is illustrated.

#### 2.1. Introduction to ISO26262

Most of the cars today consist of complex technology, advanced software control, and mechatronics implementation. The risks posed by systematic and random hardware failures are also very high. Thus, to mitigate these risks, ISO26262 was introduced to provide universal guidelines for semiconductor development. The following are a series of standards provided by ISO26262 to achieve functional safety:

- 1. Offers a guide for the vehicle safety lifecycle and aids in designing tasks to be carried out during the lifecycle stages of development, manufacture, operation, service, and decommissioning.

- 2. Presents a risk-based strategy for determining integrity levels in the automobile industry [Automotive Safety Integrity Levels (ASILs)].

- 3. To eliminate unacceptable residual risk, ASILs are applied to identify which of the ISO26262 family of standards are relevant.

- 4. Specifies criteria for functional safety management, design, implementation, verification, validation, and confirmation measures

- 5. Describes the standards for customer-supplier relationships.

The process of developing a product is broken down into several stages, including the concept stage, product development at the system level, manufacture, operation, service, and decommissioning. Figure

2-5 Overall safety management 2-6 Project dependent safety management 3-5 Item definition 2-6 Impact analysis at the item level 3-6 Hazard analysis and risk assessment 3-7 Functional safety concept 4 Product development at the Allocation to Externa. system level1) Controllability other measures 2-6 Confirmation 5 Product measures development development at the hardware software level<sup>3)</sup> level<sup>2)</sup> 2-6 Release for production 2-7 Safety management regarding production, 7-5 Planning for operation, service and production, decommissioning 7-6 Production operation, service In the case of a modification, nd decommissioning back to the appropriate 7-7 Operation, service and lifecycle phase decomissioning

2.1 shows a framework illustrating different activities during safety-related product development.

Figure 2.1: ISO26262 Framework for safety-related product development [66]

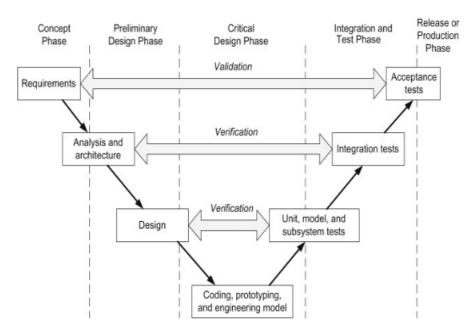

The first stage of the safety lifecycle is the item definition, during which a comprehensive description of an item's functioning and risks is established. This is followed by hazard analysis and risk assessment, which evaluates the possibility of controllability, exposure, and severity of hazardous occurrences in relation to the item. Then, based on the safety goals specified by the preliminary architectural assumptions, a functional safety concept is constructed. Then comes the product development process at the system level, this is explained using a V-model shown in Figure 2.2. Finally, throughout the operation, service, and decommissioning phases, all requirements' specifications are confirmed, and instructions are given to assure functional safety during production. This phase runs in parallel with the others.

#### 2.1.1. Automotive Safety Integrity Level

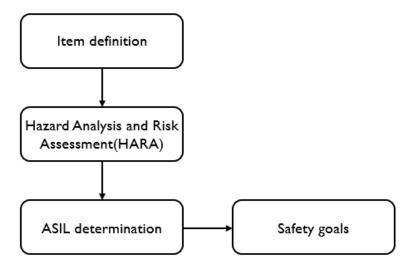

Automotive Safety Integrity Level (ASIL) is a risk categorization methodology based on the ISO 26262 standard for Functional Safety for Road Vehicles. The ASIL is determined in 4 steps as shown in Figure 2.3 The item definition of a function of component/block of a system is analysed using Hazard Analysis and Risk Assessment (HARA). This process requires the knowledge of ISO26262 framework and the teams's understanding of functional safety.

There are various activities performed in HARA such as,

- 1. Identify and categorize possible hazardous events, modes of operation, and environmental circumstances

- 2. Develop safety objectives in order to define a safe state

- 3. Indicate assumed safety goals and their associated ASIL

- 4. Summarize the customer's information on hazard analysis and risk assessment

- 5. To transform customer information in various formats into a standard format so that corresponding safety activities can be carried out

- 6. To provide a solid foundation for further safety operations for the product development

Figure 2.2: V-model shows the process of product development at system level [23]

HARA analyzes the three main criteria of ASIL, Severity, Controllability, and Exposure using the equation 2.1.

$$ASIL = Severity \ x \ (Exposure \ x \ Controllability)$$

(2.1)

Here, Severity is the measure of harm caused by the malfunction of the system to the people involved. Controllability determines the extent to which the vehicle is under control of the driver if certain operation of the system fails. The chance of a system failing or causing a dangerous condition is referred to as exposure. Figure 2.4¹ depicts the metrics used for determination. As shown in the figure, ASIL is classified into four classes: A, B, C, and D, with D being the highest safety level that demands more rigorous verification. Because there are no specific safety objectives, it is anticipated that hazards will be handled within the routine quality evaluation for the feature's functioning when a feature is classified as QM. The table 2.1 displays the minimum operating time (T) of a device "without faults" in relation to its ASIL level and table 2.2 defines the random hardware failure rates.

| ASIL | Minimum operation time (T) without errors (hour) |  |

|------|--------------------------------------------------|--|

| A    | $1.2 \times 10^7 h$                              |  |

| В    | $1.2 \times 10^8 h$                              |  |

| С    | $1.2 \times 10^8 h$                              |  |

| D    | $1.2 \times 10^9 h$                              |  |

Table 2.1: Minimum operation time without errors for ASIL classes[44]

| ASIL | Random Hardware Failure Rate (FR) | FR in Failure in Time (FIT)* |

|------|-----------------------------------|------------------------------|

| D    | 10 <sup>-8</sup> /hour            | 10 FIT                       |

| С    | 10 <sup>-7</sup> /hour            | 100 FIT                      |

| В    | 10 <sup>-7</sup> /hour            | 1000 FIT                     |

| A    | Irrelevant                        | Irrelevant                   |

\*

$$1FIT = 10^{-9} failuresperhour$$

Table 2.2: Random hardware Failure Rates (FR) in Failure in time (FIT) [44]

<sup>&</sup>lt;sup>1</sup>https://www.linkedin.com/pulse/asil-automotive-safety-integrity-levels-ratings-animesh-sarkar

Figure 2.3: Steps in ASIL determination[44]

#### 2.1.2. FuSa Verification process

The verification process followed under ISO26262 mainly defines the "WHAT", "HOW" and "RESULTS". The verification plan helps to define "WHAT" is the strategy of the process. Here the objective, method of verification, pass/fail criteria, tools to be used, resources available and the regression strategy is laid out. Secondly, the verification specification defines "HOW" the process is carried out. There are checklists documented, simulation scenarios listed, test cases and objects are detailed, how different versions of work-product will be maintained is discussed, and environment and configurations are defined. Finally, all the results of the verification activities are documented. There are 5 types of verification being performed throughout the cycle.

- 1. Design reviews through inspection/walk-through which is a formal review process

- 2. Verification through engineering judgement

- 3. Simulation of various test scenarios

- 4. Bench Testing

- 5. Fault Injection

This project focuses on fault injection type of verification. The major distinction between fault injection activity for functional safety devices and other products is the verification of the system's accurate reaction. In general, fault injection is used to validate functional correctness. For example, if a defect exists, the fault injection activity should report incorrect output of the system and identify the location of the error; this aids in the design's improvement through techniques such as fault tolerance. These flaws might be random or systematic. However, they are assessed at the moment  $t_0$  of the chip placement in the automobile.

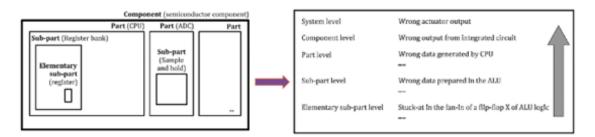

The purpose of fault injection for functional safety goods, on the other hand, is to analyze the behavior of the chip placed in the automobile when it is in operation. For instance, consider a component shown in Figure 2.5 is deployed in a hybrid car, while being driven, a stuck-at fault(random) occurs in the fan-in of a flipflop X of the ALU logic at the Elementary sub-part level. This fault travels to the sub-part level as wrong data is being prepared by the ALU. The fault further disrupts the data generated by the CPU which results in wrong output of the Integrated Circuit at component level. This causes the actuator output to deviate and cause harm at the system level. Thus, a safety mechanism for the component is designed, and a safe state for the system is specified, to avoid and reduce the dangers produced by random errors occurred in the system on the fly. This implies that if something goes wrong in the IC, the safety mechanism is activated, and the system returns to a safe condition. Thus, the fault injection activity for functional safety product development is used for following purposes:

1. To evaluate the diagnostic coverage of safety mechanism

Figure 2.4: ASIL determination metrics[31]

- 2. To evaluate the diagnostic time interval and the fault reaction time interval

- 3. Pre-silicon verification of safety mechanism with respect to the requirements, including its capacity to detect faults and control their effect (fault reaction)

Figure 2.5: Example of how fault travels from sub-part level to system level[32]

In the following parts of this section, certain terms defined in ISO26262 are explained.

#### Type of failures

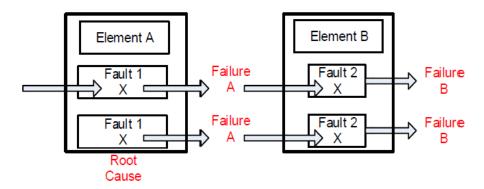

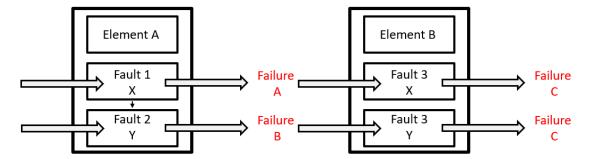

A **Cascading failure** happens when a failure in one element creates problems in another. The element that is producing the issue is referred to as the root element. Figure 2.6 shows an instance of the occurrence of cascading failure. As seen in the figure, if some random fault occurs in Element A, and this element serves some functions of Element B, then the fault in Element A will trigger a failure in Element B.

Figure 2.6: Cascading failure[1]

A **Common cause failure** occurs when two or more components of an item fail as a direct result of a single event that is either internal or external to all elements. Figure 2.7 shows an instance of common cause failure. Consider the two redundant blocks X depicted in the picture, and another Element B delivers some information to both of them. Consider that the output of both of these duplicate blocks has to be compared. Then, a failure in Element B will cause the identical fault in both the redundant blocks, and the outputs of both will be impacted equally.

Figure 2.7: Common cause failure[1]

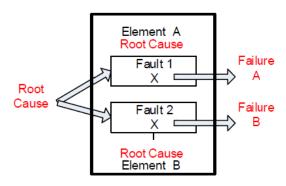

**Dependent failures**, as the name implies, are two or more failures that are dependent on one other. This does not imply that the product of all independent failures translates to the combined occurrences of dependent failures. The dependent failures have the capacity to exhibit themselves simultaneously or within a short time span to have a simultaneous impact. The common cause failures and cascading failures are also included in the dependent failures. Consider, Figure 2.8, blocks X and Y of Element A are dependent on each other, and in turn, facilitate the blocks X and Y of Element B. So any fault in blocks X and Y in Element A has the possibility to affect the blocks X and Y of Element B similarly even though these blocks are not connected to each other.

Figure 2.8: Dependent failure

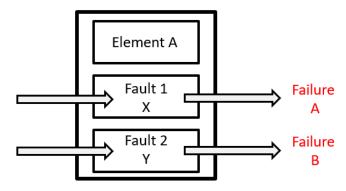

**Independent failure** also known as Single-Point fault occurs when each defect in the system is not reliant on other faults. This is displayed in Figure 2.9.

Figure 2.9: Independent failure

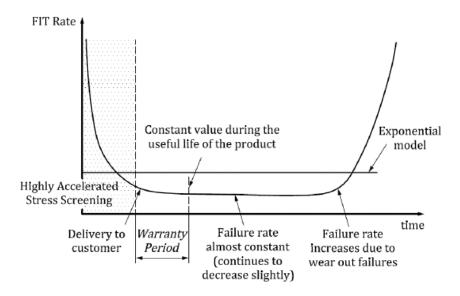

**Dual point failure** arises when two independent hardware faults exist in the system, resulting in a violation of the safety goal. Figure 2.10 illustrates this fault. Here the two blocks X and Y are independent of each other and cause two distinct faults in Element A.

Figure 2.10: Dual point failure

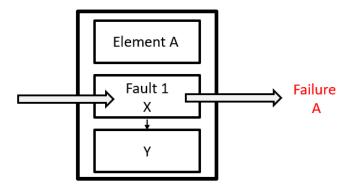

**Random failure** can individually occur unpredictably during the lifetime of a hardware element. However, these failures can be modeled probabilistically. Random defects can arise for a variety of reasons, including heat stress, ageing, corrosion, and interactions with subatomic particles. Figure 2.11 depicts the connection of random failure with time.

Figure 2.11: Semiconductor reliability curve[32]

**Systematic failures** occur during the product development process as a result of human error or error in the tool. These are deterministic faults that can be eliminated by enhancing the design and verification processes.

#### Type of faults

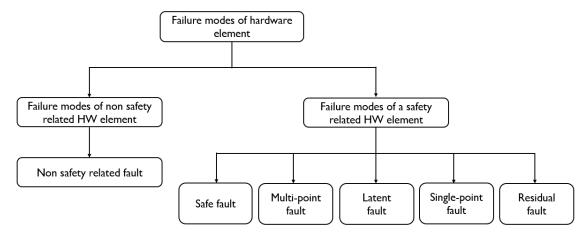

The diagram below depicts all of the different types of hardware failures that can occur in a system. There are two types of failure modes: Safety-related failure mode and Non-safety-related failure mode. Non-safety related flaws do not breach any safety goals. There are five types of failures within the safety related failure mode: safe fault, multi-point fault, latent fault, single-point fault, and residual fault.

Figure 2.12: Type of hardware faults

A **Safe fault** is one that has little to no impact on the system's operation. These failures create a variation in functioning that is within the system's tolerances. A **Single-point fault** is a hardware fault present in the element that leads to safety violation and there is no safety mechanism is place to detect it. **Latent fault** is one that occurs in the safety mechanism (SM). However, a safety mechanism by itself does not violate any safety goals; often, a defect in SM happens in conjunction with a single-point malfunction. The next type of fault, as the name indicates, a **Residual fault** is created by a portion of the system yet directly violates the safety goal. There is no safety mechanism in place to regulate this unpredictable malfunction. Lastly, the **Multi-point fault** is a combination of two or more single-point faults or a

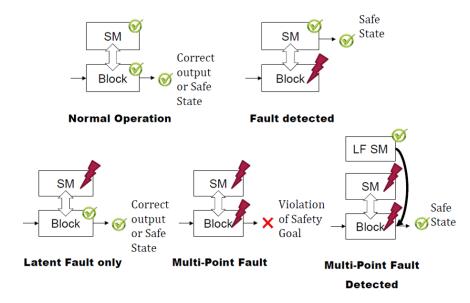

single-point fault and a fault in the safety mechanism. The latter type of multi-point fault detection requires duplication of the safety mechanism. Figure 2.13 illustrates the occurrences of different faults and how it is detected by the safety mechanism (SM). The last type of fault which is not mentioned in the above figure is **Transient fault**. This issue arises for a brief period of time. If the duration of this defect exceeds the fault tolerance, it causes damage.

Figure 2.13: Fault occurrences and detection[32]

The two important faults are single-point faults and latent faults that cause the major issues. The performance metrics required for these faults to qualify different ASIL classes is shown in table 2.3.

|                           | ASIL A     | ASIL B | ASIL C | ASIL D |

|---------------------------|------------|--------|--------|--------|

| Single-point fault metric | Irrelevant | ≥ 90%  | ≥ 97%  | ≥ 99%  |

| Latent fault metric       | Irrelevant | ≥ 60%  | ≥ 80%  | ≥ 90%  |

Table 2.3: ISO26262 fault performance metrics [44]

#### Failure mode and Safe mode

The **Failure mode** is simply the state where something goes wrong in the system. When a failure occurs, the system enters **Safe mode**. This is a state where unreasonable risks are mitigated.

#### **Safety Mechanism**

A random failure can occur at any moment in any aspect of the system owing to a multitude of factors such as environmental conditions such as light radiation flipping a memory fit or thermal stress changing the state in a key register. As a result, several safety mechanisms are developed to limit the impact of these unpredictable hardware errors. Some of these approaches are addressed in [44], including Error Correcting Codes (ECC), Dual and Triple Modular Redundancy (DMR/TMR), Lock step, DMR Hardened Flip-Flops, Built-in Self Test (BIST), and Cyclic Redundancy Checking.

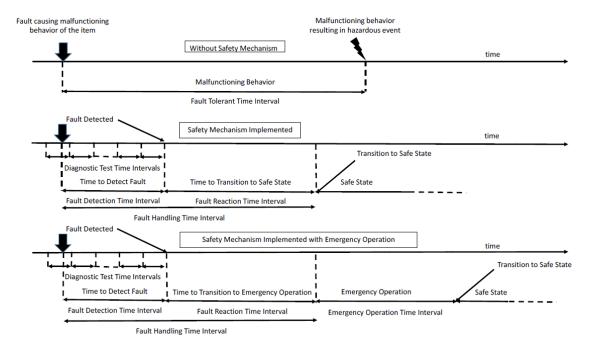

In Figure 2.14, the effect of faults with and without safety mechanisms is demonstrated. When an element/item fails, the system continues to function normally until the fault tolerance is reached. The fault is not detected for a specific time span known as the fault detection time interval. During this time, various safety sequences are executed regularly to capture the presence of fault. Once the fault is identified, the system returns to a safe state; the time necessary for this is referred to as the fault reaction time interval. The fault detection and reaction time are combined to form the fault handling time. In the absence of safety mechanisms, the minimal time span between the occurrence of a problem in an item to a potentially dangerous period is known as the fault tolerant time interval.

Figure 2.14: Safety related time intervals[1]

#### Fault classification

To evaluate the fault campaign, there are mainly two outputs observed, namely Functional Output (FO) and the Checker Output (CO). The functionality of the system can be determined from the functional output, and the checker output gives information about the faulty behaviour of the system. For instance, if the output of a temperature sensor is to be measured and the threshold of the system under test is set to a particular range. Now, if the sensor output deviates from the set range, the CO sets high and FO shows the amount of deviation. Using the two outputs FO and CO, any fault can be classified into four types:

- Unobserved Undetected (UU)

- Unobserved Detected (UD)

- Dangerous Undetected (DU)

- Dangerous Detected (DD)

When neither the functional nor the checker outputs are affected by the fault, the UU case occurs. UD indicates that the functional output is undetected but the tool output is set. This situation is not harmful since the user is aware that some functionality is not behaving properly. Thus, UU and UD can be categorised as safe faults. The following one, DU, is the most perilous since the functional output is detected whereas the checker output is not. In this test case, the user will be unaware that the system is failing and posing a risk. The verification engineer's purpose is to disclose the majority of DU situations and indeed provide proof that the design meets all the safety requirements. The last case DD is equally dangerous but it has been recognized, so any mishaps caused by it can be avoided.

The fault coverage can be calculated as:

$$Fault\ coverage = \frac{DU}{DD + DU + UD + UU} \tag{2.2}$$

#### 2.2. Example: Battery Monitoring System in Electric Vehicle

The transition to Electric Vehicles (EVs) in the automotive sector is accelerating. Lithium-Ion batteries are a main component of electric vehicles. The presence of a considerable number of these batteries is responsible for a range of risks such as electric shock, thermal events, and poisonous gas release, necessitating the implementation of a Battery Management System (BMS) system with high functional

safety standards. Furthermore, because lithium-ion batteries have changing performance depending on environmental conditions, active monitoring of voltage, current, and temperature is essential to operate the system efficiently. Due to the criticality of the BMS system, it requires a higher ASIL validation.

The BMS continuously monitors varying parameters in different operating modes and takes the necessary actions to prevent cell degradation. In [54], some of the BMS functions are mentioned below,

- 1. Cell voltage and temperature monitoring

- 2. Wake-up and sleep management

- 3. Cell balancing

- 4. Network management

- 5. Fault management and isolation detection

- 6. Battery charge monitoring

Once the functionality of the BMS system is known, the system is evaluated using HARA to identify all the critical points causing hazards. These hazards are categorized in terms of severity, exposure, and controllability. Consider the table below illustrating the HARA activity for battery charge monitoring.

| BMS Function                  | Battery charge monitoring                                |

|-------------------------------|----------------------------------------------------------|

| Possible failure modes        | Failure in the charge monitoring functionality           |

| Operational Scenarios         | Vehicle plugged in for charging while occupied           |

| Hazard Impact (Vehicle Level) | Toxic gas leak from parked car                           |

| Severity class (S)            | S3                                                       |

| Possible consequences         | Vehicle occupants lose consciousness and are             |

|                               | at risk of getting fatally intoxicated as a result       |

|                               | of the poisonous gas buildup within the passenger cabin. |

| Probability class (E)         | E4                                                       |

| Use cases                     | Travel on the highway and make a charging stop.          |

| Controllability class (C)     | C3                                                       |

| Controllability Assumptions   | Occupants are oblivious of the danger.                   |

|                               | They may abandon the car owing to tiredness,             |

|                               | but they are unlikely to be aware of the origin          |

|                               | of the problem and therefore the essential solution.     |

| ASIL                          | С                                                        |

Table 2.4: HARA example for BMS system

After determining the ASIL grade, safety goals for single or multiple hazardous incidents are developed. These safety goals signify the top-level safety standards. They result in functional safety standards for each hazardous event in order to avoid an erroneous risk. Table 2.5 presents the functional safety requirements,

| SG Description                                                   | ASIL |

|------------------------------------------------------------------|------|

| Avoid exposing humans to high voltage electrical energy (HV E/E) | В    |

| Avoid Vehicle Thermal event that cannot propagate                | С    |

| through the vehicle or damage to safety-critical components      |      |

| Prevent the hazardous emission of poisonous fumes                | С    |

| from the High Voltage Battery (when the car                      |      |

| is plugged in and charging).                                     |      |

Table 2.5: BMS Safety goals

Based on these requirements, the functional safety concept is drawn and the system architecture is developed considering the ASIL grading. Table 2.6 displays a few functional safety requirements for the BMS system.

| Functional Safety Requirement                         | ASIL |

|-------------------------------------------------------|------|

| Any cell voltage that falls below a certain           | С    |

| threshold is considered an undervoltage fault         |      |

| Any cell voltage beyond a certain threshold must      | С    |

| be identified as an overvoltage malfunction           |      |

| Any cell temperature that falls below a certain       | С    |

| threshold is considered a temperature defect          |      |

| Any cell temperature that exceeds a certain threshold | С    |

| is considered an excessive temperature malfunction    |      |

Table 2.6: FSRs for BMS system

Consider the above-mentioned first function of the Battery Management System (BMS) IC, which continually checks cell voltage and current. Consider the following system design: three ADC converters and an SPI serial protocol to convey digital voltage and current to the host. These ADCs are constructed utilizing majority voters logic, which requires that the majority of redundant blocks provide the same outcome. Random faults may be inserted into the ADCs and analyzed by performing multiple safety sequences to test this system. This safety check must occur concurrently with the routine monitoring of the battery cells' voltages and currents.

### State of the art in Fault Injection

Any electrical system may be examined for two types of behavior: positive and negative. Non-critical systems are often evaluated for positive behavior, which implies that the functionality is checked for correctness within the expected range of behavior. However, the risks associated with safety-critical ICs, such as the battery management system IC in electric vehicles, are so significant that these ICs also require negative testing. Furthermore, evaluating these chips solely before they are distributed to consumers is insufficient. They must be constantly monitored for their behavior. For example, if a random failure occurs in a system when the vehicle is in motion, it is important to determine how fast the system can detect the fault and react to a failure. In such a case, the system should identify the error before it causes excessive harm and return the system to safe mode, without affecting the functionality, in a controlled manner. As can be observed, the criticality of the system dictates the path of system verification throughout IC development. This leads us to the 'WHY' fault injection is required. Fault injection is an excellent strategy that allows the engineer to test the design at a system level in every possible scenario. This helps in evaluating system behavior when the chip is in operation. Performing fault injection activity at the development stage assists in gauging chip functioning in the field, estimating the severity of the hazard, and reflecting on architectural improvements if required that may be vital when designing ICs with high safety requirements.

The fault injection processes are performed in a variety of methods to target specific parts of the system and evaluate its capacity to detect, respond to, and recover from defects in a safe and controlled manner. The four types described in [57] explains 'WHAT' needs to be done during the fault injection activity,

- 1. **Stimulus-based fault injection**: This includes injecting faults into the system on purpose by modifying input data, changing internal state, or triggering error conditions.

- 2. **Structural fault injection**: This process involves introducing faults by restructuring the source code, changing the execution routes, or interfering with memory access.

- 3. **Environmental fault injection**: This type of FI entails exposing the system to situations that may create defects such as temperature extremes, voltage fluctuations, or electromagnetic interference.

- 4. **Timing fault injection**: This includes changing the timing of system events, such as introducing delays or race situations, in order to create failures.