#### Design and processing of silicon and silicon carbide sensors

el Mansouri, B.

10.4233/uuid:5b19a1ef-8c82-41f0-a6ee-c16402daa110

**Publication date**

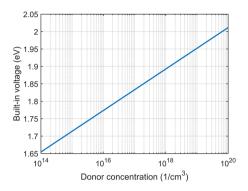

**Document Version** Final published version

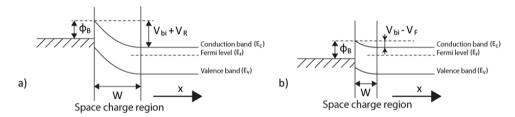

Citation (APA)

el Mansouri, B. (2021). Design and processing of silicon and silicon carbide sensors. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:5b19a1ef-8c82-41f0-a6eec16402daa110

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# DESIGN AND PROCESSING OF SILICON AND SILICON CARBIDE SENSORS

## DESIGN AND PROCESSING OF SILICON AND SILICON CARBIDE SENSORS

#### **Proefschrift**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus Prof.dr.ir. T.H.J.J. van der Hagen, voorzitter van het College voor Promoties, in het openbaar te verdedigen op dinsdag 22 juni 2021 om 12:30 uur

door

#### **Brahim EL MANSOURI**

Master of Science in Electrical Engineering, Technische Universiteit Delft, Nederland, geboren te Tirni, Marokko. Dit proefschrift is goedgekeurd door de promotor.

Samenstelling promotiecommissie:

Rector Magnificus, voorzitter, Technische Universiteit Delft Prof.dr. G.Q. Zhang Technische Universiteit Delft, promotor

Onafhankelijke leden:

Prof. S. Dimitrijev Griffith University, Australia Prof.dr. X.J. Fan Lamar University, VS Prof. Y.F. Qui Xiamen University, China

Prof. C.L. Zetterling KTH Royal Institute of Technology, Zweden

Prof.dr. P.I. French Technische Universiteit Delft

Prof. dr. ir. P.M. Sarro Technische Universiteit Delft, reservelid

Overig lid:

Dr.ir. H.W. van Zeijl Technische Universiteit Delft

Keywords: MEMS gravimeter, wide bandgap semiconductors, silicon carbide, ultraviolet sensing, MSM, APD, SiC temperature sensing, SiC CMOS

This work was supported by the European project "IoSense: Flexible FE/BE Sensor Pilot Line for the Internet of Everything". This project has received funding from the Electronic Component Systems for European Leadership Joint Undertaking under grant agreement No. 692480. This Joint Undertaking receives support from the European Union's Horizon 2020 research and innovation programme in Germany, Saxony, Austria, Belgium, Netherlands, Slovakia, Spain.

Printed by: Ipskamp printing Cover: Brahim el Mansouri

Copyright © 2021 by B. El Mansouri

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means without the prior written permission of the author.

An electronic version of this dissertation is available at <a href="http://repository.tudelft.nl/">http://repository.tudelft.nl/</a>.

## **CONTENTS**

| Sı | ımm  | ary                                            | ix |

|----|------|------------------------------------------------|----|

| Sa | ımen | vatting                                        | хi |

| 1  | INT  | RODUCTION                                      | 1  |

|    | 1.1  | Background                                     | 1  |

|    | 1.2  | Highly Sensitive Accelerometer                 | 2  |

|    | 1.3  | Wide Bandgap Semiconductor Technology          | 3  |

|    |      | 1.3.1 Temperature Sensing                      | 3  |

|    |      | 1.3.2 Ultraviolet Photodetection               | 4  |

|    |      | 1.3.3 Silicon Carbide                          | 4  |

|    | 1.4  | Project Objectives and Thesis Outline          | 6  |

|    | Refe | erences                                        | 7  |

| 2  | ΑH   | igh-resolution MEMS inertial sensor            | 11 |

|    | 2.1  | Introduction                                   | 12 |

|    | 2.2  | Background                                     | 13 |

|    |      | 2.2.1 Mechanical spring system                 | 13 |

|    |      | 2.2.2 Mechanical noise                         | 15 |

|    | 2.3  | Nonlinear Beam Design                          | 16 |

|    |      | 2.3.1 Design of a single nonlinear beam        | 16 |

|    | 2.4  | Design and Simulations of The Accelerometer    | 20 |

|    | 2.5  | Transducer design                              | 23 |

|    |      | 2.5.1 Parasitic capacitances                   | 25 |

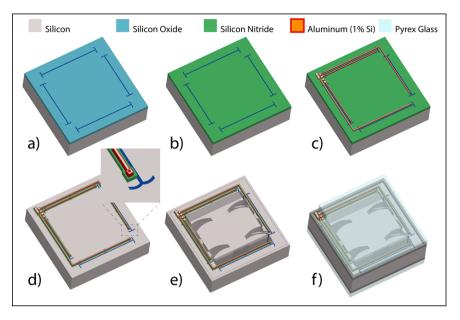

|    | 2.6  | Fabrication                                    | 26 |

|    |      | 2.6.1 Fabrication considerations and geometry  | 26 |

|    |      | 2.6.2 Processing                               | 28 |

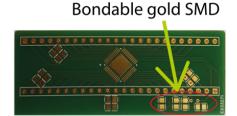

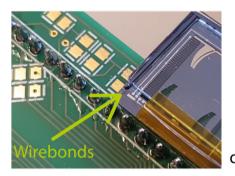

|    |      | 2.6.3 Packaging and ASIC integration           | 30 |

|    | 2.7  | Results and Discussion                         | 30 |

|    | 2.8  | Conclusion                                     | 35 |

|    | Refe | erences                                        | 36 |

| 3  | SIC  | UV DETECTOR AND KEY PROCESS STEPS              | 37 |

|    | 3.1  | UV Detection Background                        | 38 |

|    | 3.2  | Ultraviolet Detectors                          | 40 |

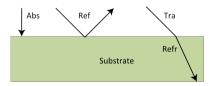

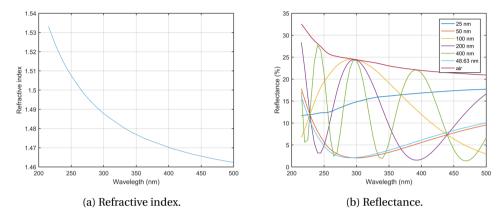

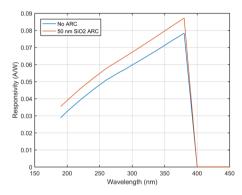

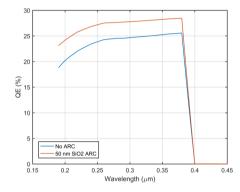

|    | 3.3  | Antireflective Coating                         | 43 |

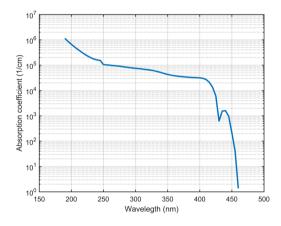

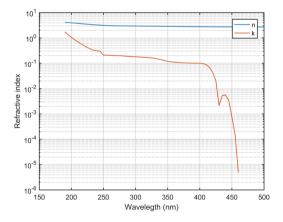

|    |      | 3.3.1 Absorption                               | 43 |

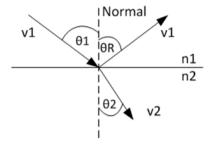

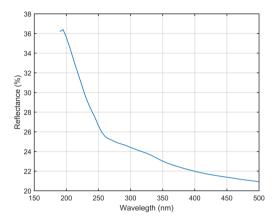

|    |      | 3.3.2 Refraction, Transmittance and Reflection |    |

vi Contents

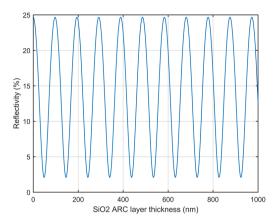

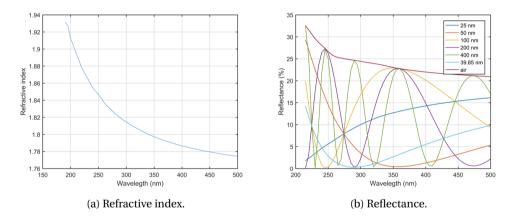

|   | 3.4  | Antireflective Coating for 4H-SiC                    |

|---|------|------------------------------------------------------|

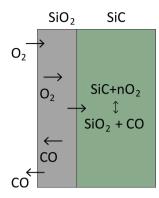

|   | 3.5  | Wet thermal oxidation of silicon carbide             |

|   |      | 3.5.1 Method                                         |

|   | 3.6  | Dry Etching of SiC                                   |

|   |      | 3.6.1 ICP Etching                                    |

|   |      | 3.6.2 RIE etching                                    |

|   | 3.7  | Chapter Summary                                      |

|   | Refe | rences                                               |

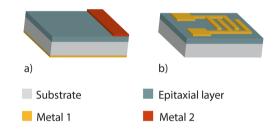

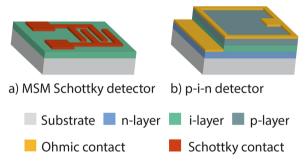

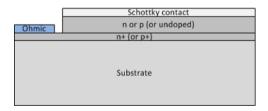

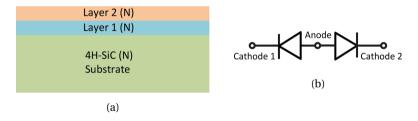

| 4 | MSI  | I SCHOTTKY SENSOR 67                                 |

|   | 4.1  | Introduction                                         |

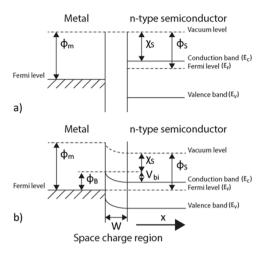

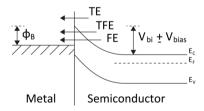

|   |      | 4.1.1 Metal semiconductor Schottky contact           |

|   |      | 4.1.2 MS Schottky contact current mechanisms         |

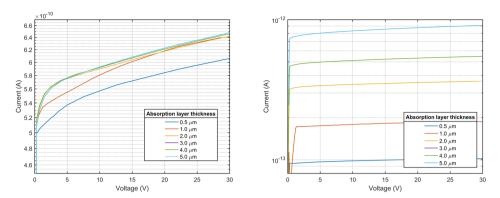

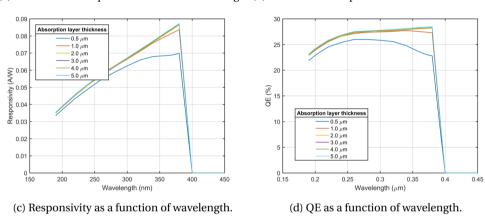

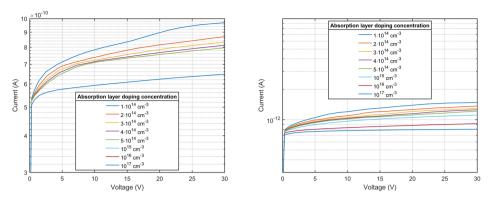

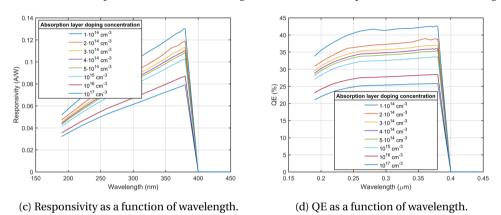

|   | 4.2  | Design for UV detection                              |

|   |      | 4.2.1 Absorption layer                               |

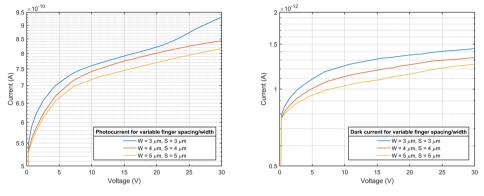

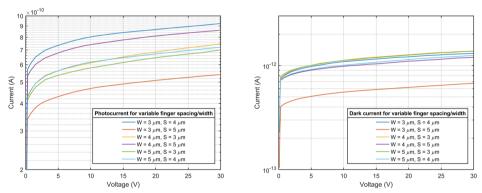

|   |      | 4.2.2 Electrodes finger sizes and spacing            |

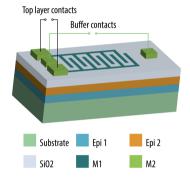

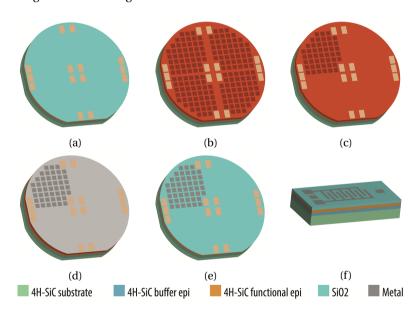

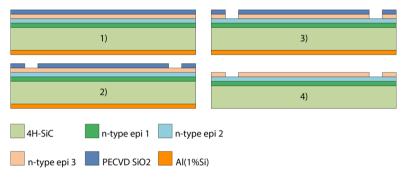

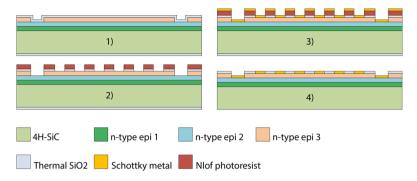

|   | 4.3  | Fabrication                                          |

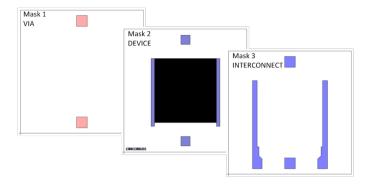

|   |      | 4.3.1 Processing steps                               |

|   | 4.4  | RESULTS AND DISCUSSION                               |

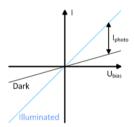

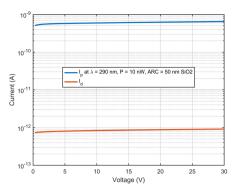

|   |      | 4.4.1 IV characteristics                             |

|   |      | 4.4.2 Schottky barrier height                        |

|   |      | 4.4.3 UV characterization                            |

|   |      | 4.4.4 PTAT MSM sensor                                |

|   |      | Chapter Summary                                      |

|   | Refe | rences                                               |

| 5 |      | SIC AVALANCHE PHOTODIODE 10                          |

|   | 5.1  | Introduction                                         |

|   |      | 5.1.1 State of The Art                               |

|   | 5.2  | Background                                           |

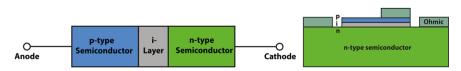

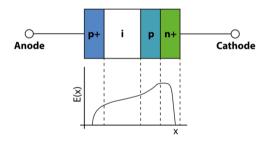

|   |      | 5.2.1 The pin- junction                              |

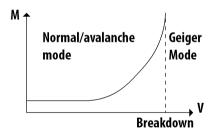

|   |      | 5.2.2 The avalanche photodiode                       |

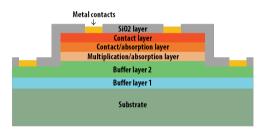

|   | 5.3  | DESIGN                                               |

|   |      | 5.3.1 Key parameters and factors                     |

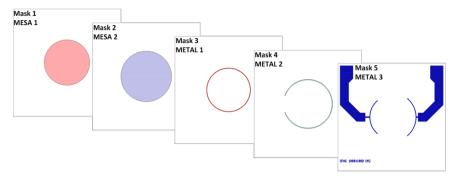

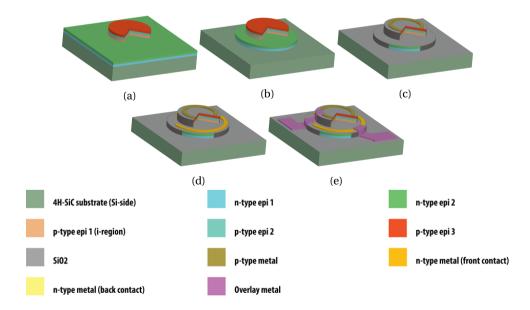

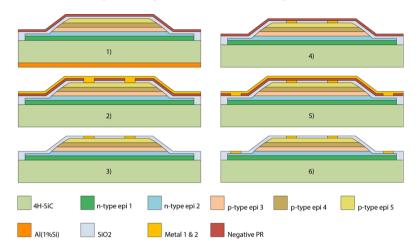

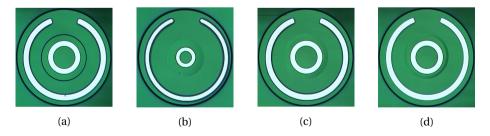

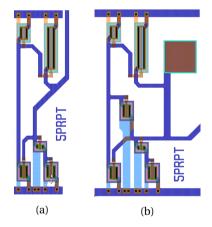

|   | 5.4  | Fabrication                                          |

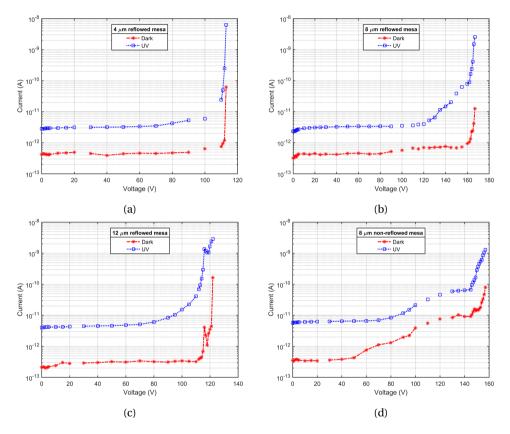

|   |      | Results and discussion                               |

|   |      | Chapter Summary                                      |

|   | Refe | rences                                               |

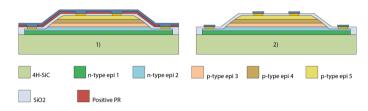

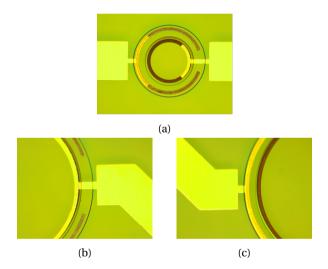

| 6 | Tow  | ards SiC CMOS sensors and electronics technology 123 |

|   | 6.1  | Introduction                                         |

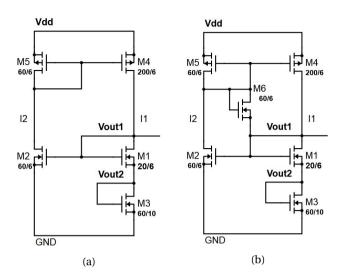

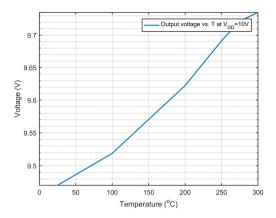

|   | 6.2  | Threshold voltage based temperature sensing          |

|   |      | Chapter Summary                                      |

|   | Refe | rences                                               |

| 7  | COI   | CLUSIONS AND RESEARCH OUTLOOK | 131 |

|----|-------|-------------------------------|-----|

| •  |       | Silicon Sensor                | -0- |

|    | 7.2   | Silicon Carbide Sensors       | 132 |

| Ac | knov  | rledgements                   | 135 |

| Li | st of | Publications                  | 136 |

### **SUMMARY**

Downscaling of transistors, also known as Moore's law, has been the main propelling force behind the microelectronics industry. This trend will eventually come to an end due to physical limitations, hence an alternative is required to further drive technological progress. This gave an incentive to evolve in other directions as well, also known as More than Moore (MtM). This concerns all technologies adding functionality to integrated circuits (IC), all packaged as a single system. This can be done by combining digital and non-digital elements, e.g. analog/RF, passives, microelectromechanical devices (MEMS), and so on. The non-digital elements are not necessarily scalable according to Moore's law. Therefore, in this thesis we investigated the possibilities of using silicon and silicon carbide (SiC) to fabricate a number of sensors, capable of measuring weak signals. This is done by having a multidisciplinary investigation spanning from electrical, to mechanical and optical domains.

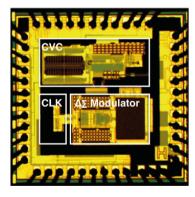

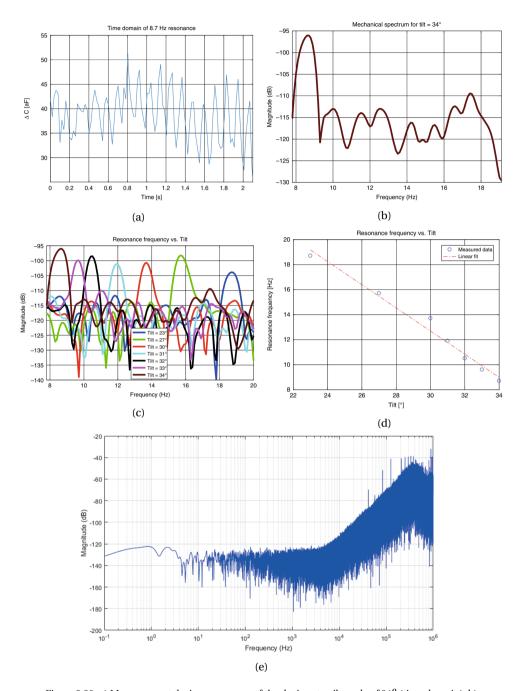

In Chapter 2, a bulk micro-machined high sensitivity accelerometer was designed, simulated, fabricated and characterized. By employing non-linear behaviour of four long slender beams to support a proof-mass, an operating point has been obtained where extremely low spring stiffness occurs. An integrated IDT capacitive transducer is used to readout the displacement of the proof-mass. The integration of the capacitive transducer was made possible using trench isolation technique to electrically isolate the electrodes of the capacitor, all fabricated in the same bulk silicon. The devices were capped using Pyrex glass dies. A PCB containing readout ASIC was used to readout the accelerometer. The PCB was then connected to a high-resolution impedance readout system, forming a measurement system. The device, at it its lowest resonance frequency of 8.7 Hz, the capacitive sensitivity and the experimentally characterised noise floor of the readout chip, the theoretically obtainable system resolution equals  $17.02\ ng/\sqrt{Hz}$ . This work shows that the proof of concept is promising for future iterations.

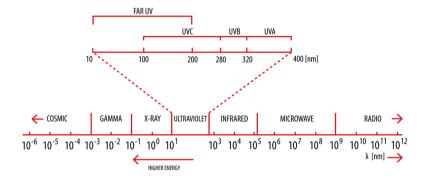

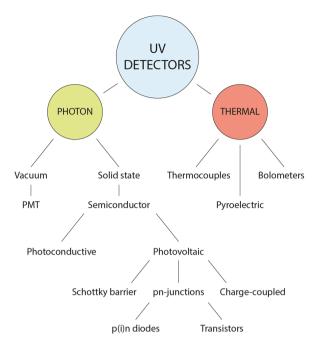

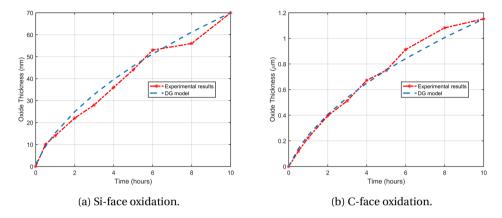

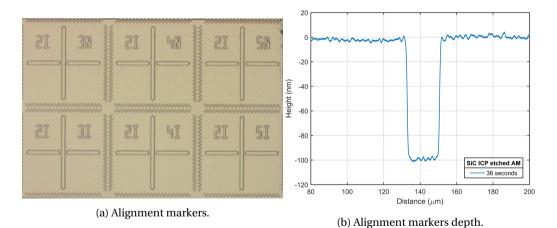

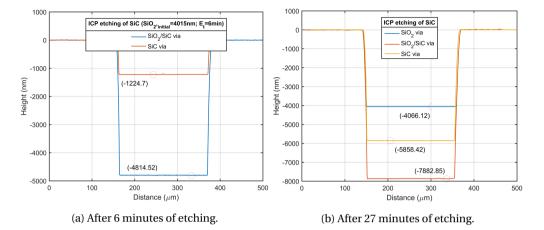

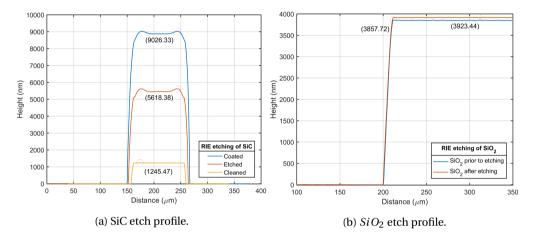

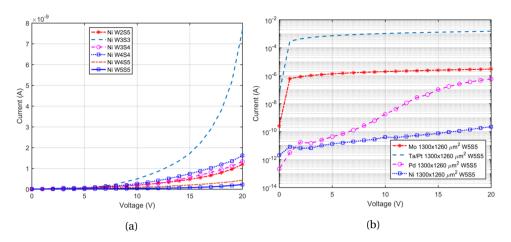

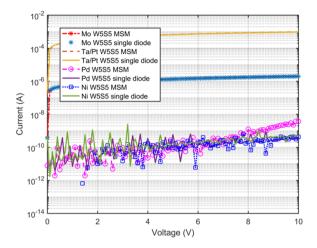

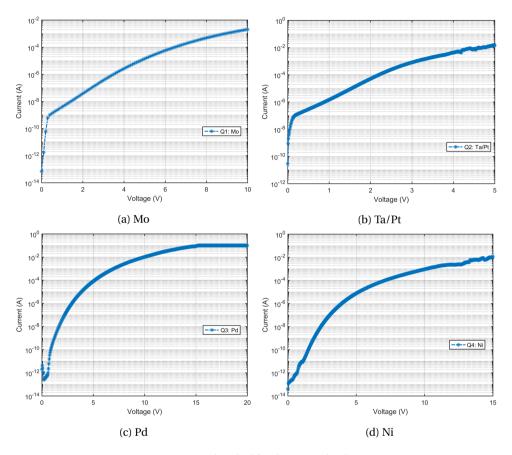

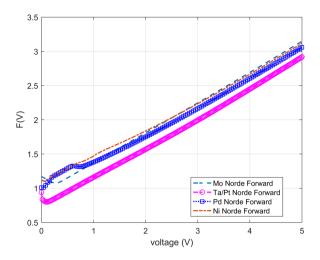

In Chapter 3, SiC ultraviolet (UV) photodetectors are introduced along with key SiC processing steps. 4H-SiC has a significant advantage over silicon when dealing with certain applications such as UV and harsh environments. Thermally growing  $SiO_2$  is one of the advantages of SiC over other wide bandgap (WBG) semiconductors. The oxidation of SiC was therefore investigated and characterized. The results showed a good fit with the DG-model but needs further investigation as to how the behaviour is in all crystal directions. Furthermore, 4H-SiC etching was also investigated by using the ICP and RIE processes. Subsequent chapters describe the devices which were fabricated using the findings in chapter 3 (except for CMOS devices). Thus these results from these experiments were used to fabricate MSM Schottky sensors for multi-sensing applications using various metallizations. The metals used are Mo, Ta/Pt, Pd, and Ni, where the last two showed the best dark current performance in the range of pA. The devices showed reasonable dark currents at 200 °C where Ni electrodes gave a dark current of  $\sim$  223 pA at 20V bias. Al-

x Summary

though Pt has a large metal workfunction, the dark current reached  $\sim 1.52~mA$  at 200 °C for the same bias. The tantalum adhesion layer has a lower metal workfunction at a value of 4.22 eV, hence a lower Schottky barrier height resulted, at around 0.6 eV. The reason for using Ta as an adhesion layer is because the Pt comes off when doing the Scotch tape test. It was assumed that due to metal stacking, the overall Schottky barrier would increase sufficiently high. The observed metal workfunction is  $\sim 0.8~eV$  which is higher than what would be expected for Ta/4H-SiC but is still lacking. Additionally, also the processing has an influence on the SBH. The ideality factors calculated using the standard IV method showed high values which means that the devices need improvement. This can be done for instance by annealing the devices at higher temperatures to improve the metal-semiconductor interface. Other alternatives may be the surface passivation prior to metallization which potentially can result in also lower leakage currents. An example of surface passivation can be done by inserting a dielectric such as aluminium oxide to passivate surface defects, but also preventing diffusion of metals. Although not characterized for its UV behaviour, the Mo metal, showed a Schottky barrier of about 1.2 eV which means that it can be used for optical detection. This metal is useful for high temperature applications and other harsh environments because it is a refractory metal. This allows the device to be used for high temperature applications where the device is used as a PTAT temperature sensor. The W5S5 devices with Mo electrodes were tested up to 200 °C and showed good temperature behaviour. The findings are encouraging to further investigate the device for multi-sensing applications targeted at harsh environments.

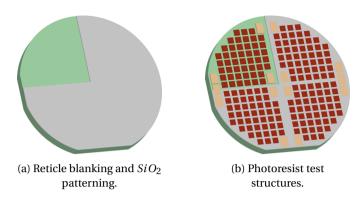

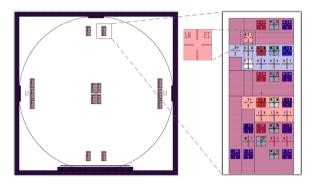

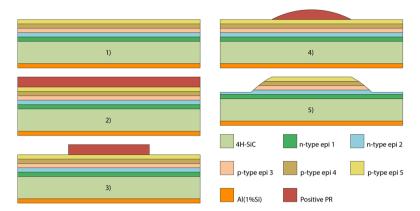

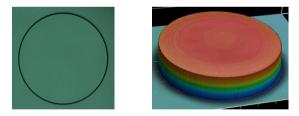

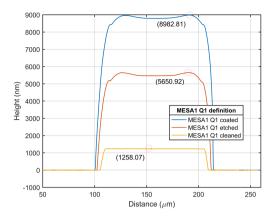

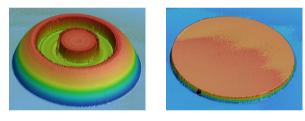

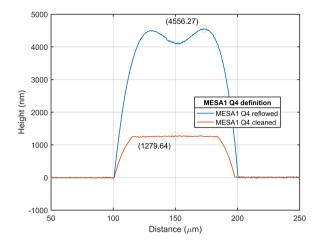

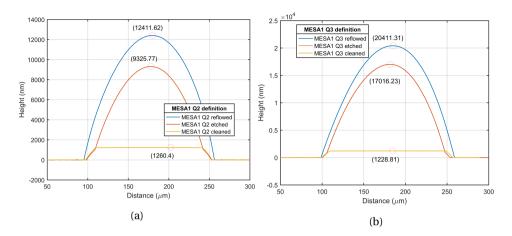

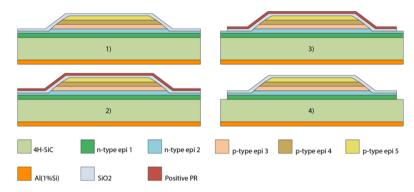

In addition to this device, dedicated devices for UV sensing and temperature sensing (SiC CMOS) were developed. The first is an avalanche photodiode which is advantageous for detecting weak ultraviolet signals thanks to its small size, low dark current, high multiplication gain, and high quantum efficiency. Such detectors can be used in a wide range of applications, e.g. corona discharge, flame detection, missile plume detection, UV astronomy, UV LIDAR, and biological and chemical detection. We discussed the design, fabrication, and characterization of a 4H-SiC APD. The devices are based on epitaxial technology to ease the fabrication constraints w.r.t. implantation, activation and etching. This allowed for device fabrication in our own cleanroom facilities. The bevel angles were etched by using the photoresist reflow technique to make lens shape structures, and transferring the side-angles into the SiC semiconductor. As for the temperature sensing, this is based on SiC CMOS technology. The devices are threshold voltage based temperature circuit sensors. The designs of the circuits relied on using LTspice simulations based on immature PMOS and NMOS models. Here channel length modulation was not taken into account. Nonetheless, this provided a starting point. The layout design was done in L-edit and verified for the design rules using K-layout. The fabrication was done at the Fraunhofer IISB Erlangen, Germany. For some of the wafers, we did the metallization at our own facilities, EKL. Basic measurements up to 200 °C have been done for the temperature sensor which showed good behaviour. Future work should include testing of the devices at high temperatures, well above 200 °C.

### **SAMENVATTING**

Het terugschalen van transistors, ook bekend als de wet van Moore, is de belangrijkste drijvende kracht geweest achter de micro-elektronica-industrie. Aan deze trend zal uiteindelijk een einde komen door fysische beperkingen, zodat een alternatief nodig is om de technologische vooruitgang verder te stuwen. Dit gaf een stimulans om ook in andere richtingen te evolueren, ook bekend als More than Moore (MtM). Hierbij gaat het om alle technologieën die functionaliteit toevoegen aan geïntegreerde schakelingen (IC), allemaal verpakt als één systeem. Dit kan gebeuren door digitale en niet-digitale elementen te combineren, b.v. analoog/RF, passieven, micro-elektromechanische apparaten (MEMS), enzovoort. De niet-digitale elementen zijn niet noodzakelijk schaalbaar volgens de wet van Moore. Daarom hebben we in dit proefschrift de mogelijkheden onderzocht om silicium en siliciumcarbide (SiC) te gebruiken om een aantal sensoren te fabriceren, die in staat zijn zwakke signalen te meten. Dit wordt gedaan door een multidisciplinair onderzoek dat zich uitstrekt van elektrische, tot mechanische en optische domeinen.

In hoofdstuk 2 werd een in bulk microbewerkte hooggevoelige versnellingsmeter ontworpen, gesimuleerd, gefabriceerd en gekarakteriseerd. Door gebruik te maken van het niet-lineaire gedrag van vier lange slanke balken om een proefmassa te ondersteunen, is een werkpunt verkregen waar een extreem lage veerstijfheid optreedt. Een geïntegreerde capacitieve IDT-transducer wordt gebruikt om de verplaatsing van de proefmassa af te lezen. De integratie van de capacitieve uitlezing werd mogelijk gemaakt door gebruik te maken van de sleufisolatietechniek om de elektroden van de condensator elektrisch te isoleren, welk helemaal in hetzelfde bulk silicium werden vervaardigd. De apparaten werden afgedekt met stukjes Pyrex-glas. Een PCB met uitlees-ASIC werd gebruikt om de versnellingsmeter uit te lezen. De PCB werd vervolgens aangesloten op een impedantieuitleessysteem met hoge resolutie, waardoor een meetsysteem ontstond. Met de laagste resonantiefrequentie van 8,7 Hz, de capacitieve gevoeligheid en de experimenteel gekarakteriseerde ruisvloer van de uitleeschip is de theoretisch haalbare systeemresolutie gelijk aan  $17,02 \ ng/\sqrt{Hz}$ . Dit werk toont aan dat de proof of concept veelbelovend is voor toekomstige iteraties.

In hoofdstuk 3 worden SiC ultraviolet (UV) fotodetectoren geïntroduceerd, samen met de belangrijkste fabricage-stappen voor SiC. 4H-SiC heeft een aanzienlijk voordeel ten opzichte van silicium bij bepaalde toepassingen zoals UV en barre omgevingen. De thermische groei van  $SiO_2$  is een van de voordelen van SiC ten opzichte van andere halfgeleiders met brede bandgap (WBG). De oxidatie van SiC werd daarom onderzocht en gekarakteriseerd. De resultaten bleken goed te passen in het DG-model, maar er moet verder worden onderzocht hoe het gedrag in alle kristalrichtingen is. Verder werd ook het etsen van 4H-SiC onderzocht met behulp van de ICP- en RIE-processen. De daaropvolgende hoofdstukken beschrijven de apparaten die werden gefabriceerd met ge-

xii Samenvatting

bruikmaking van de bevindingen in hoofdstuk 3 (behalve voor CMOS-apparaten). De resultaten van deze experimenten werden gebruikt om MSM Schottky sensoren te fabriceren voor multi-sensing toepassingen met behulp van verschillende metallizaties. De gebruikte metalen zijn Mo, Ta/Pt, Pd, en Ni, waarbij de laatste twee de beste donkerstroomprestaties vertoonden in het bereik van pA. De apparaten vertoonden redelijke donkere stromen bij 200 °C waarbij de nikkelelektroden een donkere stroom gaven van ~ 223 pA bij 20V bias. Hoewel Pt een grote metaalfunctie heeft, bereikte de donkere stroom  $\sim 1,52~mA$  bij 200 °C voor dezelfde spanning. De tantaal adhesielaag heeft een lagere metaalwerkfunctie met een waarde van 4,22 eV, vandaar een lagere Schottky barrièrehoogte, rond 0,6 eV. De reden om Ta als adhesielaag te gebruiken is dat de Pt loslaat bij het uitvoeren van de Scotch tape test. Aangenomen werd dat door metaalstapeling de totale Schottky-barrière voldoende hoog zou worden. De waargenomen metaalwerkfunctie is  $\sim 0.8 \ eV$  wat hoger is dan wat verwacht zou worden voor Ta/4H-SiC maar nog steeds onvoldoende is. Bovendien heeft ook de verwerking invloed op de SBH. De idealiteitsfactoren berekend met de standaard IV-methode vertoonden hoge waarden, wat betekent dat de apparaten moeten worden verbeterd. Dit kan bijvoorbeeld worden gedaan door de componenten bij hogere temperaturen te annealen om het metaal-halfgeleider interface te verbeteren. Een ander alternatief is de passivering van het oppervlak vóór de metallisering, die mogelijk ook kan leiden tot lagere lekstromen. Een voorbeeld van oppervlaktepassivering is het inbrengen van een diëlektricum zoals aluminiumoxide om oppervlaktedefecten te passiveren, maar ook om diffusie van metalen te voorkomen. Hoewel niet gekarakteriseerd voor zijn UV-gedrag, Mo-metaal vertoonde een Schottkybarrière van ongeveer 1,2 eV, hetgeen betekent dat het kan worden gebruikt voor optische detectie. Dit metaal is nuttig voor toepassingen bij hoge temperaturen en andere barre omgevingen omdat het een refractair metaal is. Hierdoor kan het apparaat worden gebruikt voor toepassingen bij hoge temperaturen waarbij het apparaat wordt gebruikt als een PTAT-temperatuursensor. De W5S5-apparaten met Mo-elektroden werden getest tot 200 °C en vertoonden een goed temperatuurgedrag. De bevindingen zijn bemoedigend om het apparaat verder te onderzoeken voor multi-sensing toepassingen gericht op barre omgevingen.

Naast dit apparaat werden specifieke apparaten voor UV-detectie en temperatuurdetectie (SiC CMOS) ontwikkeld. De eerste is een lawinefotodiode die gunstig is voor de detectie van zwakke ultraviolette signalen dankzij zijn kleine afmetingen, lage donkerstroom, hoge vermenigvuldigingsfactor en hoge kwantumefficiëntie. Dergelijke detectoren kunnen worden gebruikt in een breed scala van toepassingen, b.v. corona-ontlading, vlamdetectie, raketpluimdetectie, UV-astronomie, UV LIDAR, en biologische en chemische detectie. Wij behandelden het ontwerp, de fabricage en de karakterisering van een 4H-SiC APD. De apparaten zijn gebaseerd op epitaxiale technologie om de fabricagebeperkingen ten aanzien van implantatie, activering en etsen te verlichten. Hierdoor konden de apparaten in onze eigen cleanroomfaciliteiten worden vervaardigd. De schuine hoeken werden geëtst door gebruik te maken van de fotoresist-reflowtechniek om lensvormige structuren te maken, en de zijhoeken over te brengen in de SiC-halfgeleider. De temperatuursensoren zijn gebaseerd op SiC CMOS-technologie. De apparaten zijn drempelspanning-gebaseerde temperatuurschakelingsensoren. De ontwerpen van de schakelingen berustten op het gebruik van LT-spice simulaties op basis van onvolwas-

SAMENVATTING xiii

sen PMOS- en NMOS-modellen. Hierbij werd geen rekening gehouden met modulatie van de kanaallengte. Niettemin bood dit een uitgangspunt. Het layout-ontwerp werd gedaan in L-edit en geverifieerd op de ontwerpregels met behulp van K-layout. De fabricage vond plaats in het Fraunhofer IISB Erlangen, Duitsland. Voor sommige wafers hebben we de metallisatie gedaan in onze eigen faciliteiten, EKL. Voor de temperatuursensor zijn basismetingen tot 200 °C gedaan, die goed bleken te zijn. In de toekomst moeten de apparaten worden getest bij hoge temperaturen, ver boven 200 °C.

### INTRODUCTION

#### 1.1. BACKGROUND

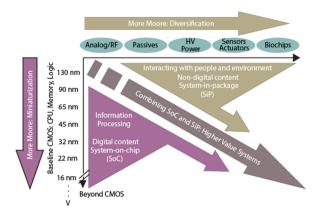

In the last century, physicists such as Richard Feynman have realized the importance of downscaling electronics as was evident from his speech "There's plenty of room at the bottom" [1]. Not long after this, the co-founder of Intel, Gordon E. Moore, has defined Moore's law which states that the number of devices in an integrated circuit (IC) will increase exponentially over time [2]. It is somehow counter-intuitive that the functionality of CMOS devices stays about the same while downscaling and keeping the W/L ratio constant. However, this miniaturization trend is coming to an end due to physical limitations, hence an alternative is required to further drive technological progress. The alternative is to combine the miniaturization of functionality and diversification of functional elements in integrated circuit (IC) devices. This can be done by combining digital and non-digital elements, e.g. analog/RF, Passives, microelectromechanical devices (MEMS), and so on. The non-digital elements are not necessarily scalable according to Moore's law. This is known as More than Moore (MtM) (Figure 1.1) [2–4].

The development of sensors capable of measuring extremely small signals and/or operating in harsh environments enable applications over large spans such as seen in the emerging field of internet of things (IoT) [5]. Here diversification is not only in the form of sensor types but also materials of choice to develop such devices. However, silicon technology is reaching its physical limits and has serious drawbacks in harsh environments, i.e. fails at high temperatures, high pressures, radiation, shock/ high vibration, harsh chemicals, humidity, and biology [6]. Various solutions have been proposed to make silicon technology compatible with harsh environments, e.g. packaging, material selection, additives by fabrication such as adhesion layers, etc. [6]. Furthermore, the solutions proposed in research and industry all have different effectiveness in different harsh environments where material selection and packaging are the best approaches [6]. However, sensor packaging is the most costly step in the realization of the devices where harsh environment compatibility further complicates packaging [7]. Sensors can be integrated into systems for monitoring and performance enhancement but are beneficial

Figure 1.1: The International Technology Roadmap for Semiconductors: Miniaturization and diversification [4].

up to the point where the added value is exceeded by the cost [7]. One way to still use silicon technology for harsh environments lies in how it is utilised. For example, measuring volcanic activity (vibrations/shocks) may be difficult due to large shocks and high temperatures. But if the devices were to be very sensitive, these can be applied at a safe distance. Such device has been fabricated in this work (MEMS accelerometer). Alternative solutions are possible, e.g. harsh environment compatible materials [7]. One very attractive material is silicon carbide (SiC) thanks to its electrical and mechanical properties [8]. The semiconductor material lends itself not only for power electronics but also for sensor and integrated circuit technologies, albeit with some limitations. By combining electronics and sensors, the performance of a system can be greatly enhanced w.r.t. effects such as noise, parasitics, and other unwanted effects. Therefore, in this work we will focus on four aspects. The first is to investigate the detection of extremely small signals associated with gravimetry. The second is to detect low ultraviolet (UV) light. Here we also investigate avalanche photodiodes which potentially can be used for single photon detection. The third is related to measuring high temperatures.

#### 1.2. HIGHLY SENSITIVE ACCELEROMETER

Silicon technology already proved to be the main propeller of today's electronics advancement. This also goes for MEMS devices which are applied in various fields, e.g. to measure acceleration, pressure, flow or actuation such as physical switching or even thrusters [9–11]. Therefore, the first aspect of this research is the development of an extremely sensitive accelerometer to sense small variations in local gravitational acceleration [12]. Its applications range from studying our planet's behaviour w.r.t. earth crust movement, volcanic eruptions, detection of earth tides, to water and oil pockets. Even though some applications may be harsh environments, i.e. high shocks/high temperatures, the devices can be applied at a safe distance thanks to their high sensitivity. Moreover, such sensing can be used to monitor vibrations in high end machinery where nanometre accuracy is required, e.g. lithography processing machines. Unlike the em-

ployment of large detection devices for gravimetry purposes, developing miniaturised silicon devices allows over large-area detection thanks to its low cost and high sensitivity when well designed. An application may be the internet of things (IoT) to collect data for studying earth activity. To this end, high sensitivity accelerometers can be designed by exploiting geometrical nonlinearity seen in long slender beams, also known as compliant mechanisms [9]. The required gravimeter sensitivities for detecting the smallest changes in gravitational acceleration are in the range of  $1-100\ ng/\sqrt{Hz}$  [13].

Figure 1.2: Going from large gravimeter devices to a small MEMS accelerometer (Source Large size gravimeter: [14]).

#### 1.3. WIDE BANDGAP SEMICONDUCTOR TECHNOLOGY

A harsh environment is any environment having certain characteristics impeding the normal operation of a sensor or actuation device [6]. One of the most discussed types is the high temperature  $> 200\,^{\circ}C$  where extrinsic silicon reverts to being intrinsic due to the high electron-hole carriers generation. Moreover, the useful mechanical properties are lost at higher temperatures which limits the working range of MEMS devices. Next to high temperatures, optical harsh conditions such as short wavelengths and high radiation conditions can significantly reduce the lifetime of devices [15, 16].

Other harsh environment types are high pressures  $(2000-3000\ bar)$  as seen in automotive and process industries, high shock/ high acceleration, high radiation, harsh chemical environment, and high humidity [6]. These challenges can be addressed depending on the type of environment through design considerations w.r.t. materials, technology, device fabrication, packaging, and system type [6]. The material aspect of the design can reduce the design constraints and reduce cost if it meets the requirements of specific applications which may include high-temperature capability, high electric breakdown for high power actuation, fast switching, and radiation hardness.

#### 1.3.1. TEMPERATURE SENSING

Temperature sensing using SiC technology can be applied up to  $600 \,^{\circ}C$  in many industrial applications, e.g. geothermal power generation, gas turbines, aerospace systems, etc. [17]. Furthermore, real-time monitoring can be enabled by this method allowing

for in-situ changes in processes such as solar panel production. Such sensors can be based on simple diodes or CMOS technology and can be monolithically integrated with SiC electronics [18]. In this work diode based and CMOS based temperature sensors are investigated up to a working temperature of  $200^{\circ}C$ .

#### 1.3.2. Ultraviolet Photodetection

There are various methods for detecting partial discharge, including pulse current method, optical detection in the infrared and ultraviolet spectral range, acoustic emission, temperature, and pressure changes in the area [19–22]. Gas sensing could also be used to measure chemical reactions occurring in oil-filled transformers [20, 23].

For example, ultraviolet (UV) detection in power grid applications is currently done using UV cameras such as the "UV-260 Corona Discharge Camera" and "DayCor Superb UV imager". Such cameras superimposes the detected UV light on a normal image to show the location [22]. The "DayCor Superb UV imager" has a UV sensitivity of  $2.2 \times 10^{-18} \ W/cm^2$  and a minimum visible light detection of  $0.1 \ Lux$ . The Minimum Discharge detection is  $1 \ pC$  at a distance of  $10 \ m$ . The spectral range is kept within  $240 - 280 \ nm$  as this corresponds to the solar-blind range allowing for daytime detection. The discharge severity can then be estimated based on the photon number [22]. However, even-though this camera has high specifications, this method is only used at close range while needing someone to operate it. This shows that developing sensors capable of employment over entire grids offer better monitoring of the power grid. Developing UV sensors is not limited to the application in power grids but can range from chemical, environmental, and biological analysis. Furthermore, it can be used for monitoring, e.g. flame and radiation detection, etc. [24]. In some cases such as flame detection, high-temperature thermally stable detectors with high performance are required [24].

Thanks to the wide bandgap of SiC, UV detectors made from it are visible blind ( $\approx 400~nm$ ), hence no filtering is required [16, 25–27]. Moreover, its high mechanical and chemical stability enable application in high radiation conditions. Such conditions may significantly reduce the lifetime of silicon devices [28–30]. The instability of photodetectors depends on the irradiation type, level of irradiation and its duration. The radiation effects result in changes in spectral responsivity, increase of leakage current, reduction of charge collection efficiency and removal of free carriers from the conductive regions of the device [31]. The swelling and mechanical properties of SiC are of interest in nuclear applications where devices and electronics undergo neutron irradiation [32]. On the other hand, SiC avalanche photodetectors can be sensitive to low UV light levels in the range of  $fW - aW/cm^2$  while having a clear distinction from the noise level and maintaining a reliable signal. SiC also has the advantage of good responsivity, high thermal stability, radiation hardness suited for nuclear applications, high response speed, and high-power [24]. Therefore, this work will focus on designing and fabricating SiC UV UV photodetectors.

#### 1.3.3. SILICON CARBIDE

To aid in the design of more robust sensors, wide bandgap technology offers an excellent alternative to silicon. One of the materials coming on top for this is SiC. Its wide bandgap

not only enables visible blind operation of photodetectors, but thanks to its mechanical and chemical stabilities, it also enables operation in harsh optical environments where short wavelengths affect the stability and lifetime of detectors. Furthermore, this property enables operation in high-temperature regimes where the intrinsic carrier concentration generation doesn't surpass the dopant concentration carriers [33]. However, such properties are also exhibited in other wide bandgap materials as well [33]. One major advantage of SiC over other wide bandgap materials is its oxidation being similar to that of silicon, namely silicon oxide  $(SiO_2)$ . This allows for growing gate oxide under similar conditions as seen for silicon technology, enabling CMOS compatibility.

Unlike silicon which is diamond-like, 4H-SiC comes in Wurtzite (hexagonal) unit cells. The SiC crystal structure occurs in many phases, also known as polytypism. That is, depending on the stacking sequence along one direction, up to 250 polytypes can be obtained [34, 35]. Each polytype can be envisioned as a corner-sharing tetrahedral where each tetrahedron consists of a silicon atom at the centre and four carbon atoms bonded to the silicon atom [36, 37]. Figure 1.3 illustrates a tetrahedron building block. The three popular polytypes are the 3C-SiC, 4H-SiC, and 6H-SiC. In this work, the focus is on the monocrystalline 4H-SiC. Table 1.1 summarized some of the properties where SiC shows both advantages and disadvantages compared to silicon.

Figure 1.3: SiC tetrahedron building block.

Four key properties of SiC come into play in the case of applications where silicon is not adequate. These are its wide bandgap, high electrical breakdown, high thermal conductivity and high temperature operation capability [27, 38-41]. Its wide bandgap is one of its most important attributes since this is related to photodetection, high temperature operation, and high electrical breakdown ability. The latter two attributes are important in power electronic applications. The energy bandgap represents the minimum energy required by an electron to be excited from the valence band to the conduction band [42]. The excitation can for instance take place for thermal energy or photon energy. The first is what makes SiC high temperature compatible where the intrinsic carrier concentration at 300 K is at  $8.2 \cdot 10^{-9}$  for 4H-SiC while this is  $1.5 \cdot 10^{10}$  for silicon (see Table 1.1). Thus, in silicon this is limited to operations at temperatures of  $\sim 125\,^{\circ}\text{C}$  where extrinsic silicon reverts to intrinsic silicon at temperatures nearing 200 °C [6] compared to 700 °C for 4H-SiC. The energy bandgap is also important for short-wavelength photodetection applications. In the case of silicon with its bandgap of  $\sim 1.12 eV$ , silicon devices require filtering for selective detection of ultraviolet radiation. Another advantage of SiC photodetectors is having a low dark current as this is directly proportional to the intrin-

Table 1.1: Comparison of silicon and SiC polytypes at room temperature [27, 38-41].

| Property                                             | Si                  | 3C-SiC         | 4H-SiC              | 6H-SiC              |

|------------------------------------------------------|---------------------|----------------|---------------------|---------------------|

| Bandgap (eV)                                         | 1.12                | 2.3            | 3.26                | 3                   |

| Thermal conductivity $(W/cm \cdot K)$                | 1.5                 | 4.5            | 4.5                 | 4.5                 |

| Intrinsic carrier concentration $(cm^{-3})$          | $1.5 \cdot 10^{10}$ | 6.9            | $8.2 \cdot 10^{-9}$ | $2.3 \cdot 10^{-6}$ |

| Electron mobility $(cm^2/V \cdot s)$                 | 1350                | 900            | 720*<br>650**       | 370*<br>50**        |

| Hole mobility $(cm^2/V \cdot s)$                     | 480                 | 40             | 120                 | 80                  |

| Breakdown field $(MV/cm)$                            | 0.3                 | 1.2            | 2                   | 2.4                 |

| Dielectric constant                                  | 11.9                | 9.7            | 9.7                 | 9.7                 |

| Saturated electron drift velocity ( <i>cm/s</i> )    | $1 \cdot 10^7$      | $2 \cdot 10^7$ | $2 \cdot 10^7$      | $2 \cdot 10^7$      |

| Intrinsic electrical resistivity $(\Omega \cdot cm)$ | $10^3 - 10^5$       | 150            | > 10 <sup>12</sup>  | $10^4 - 10^8$       |

<sup>\*</sup> Electron mobility of SiC along a-axis. \*\* Electron mobility of SiC along c-axis.

sic carrier concentration and since this is very low for SiC, extremely low dark current generation at room temperature can be obtained, thus allowing low levels of UV light detection. As for the high electric breakdown of SiC, this allows for high electrical fields without triggering an avalanche multiplication at low voltages. This ability is very important in power electronics as well as for avalanche photodetectors. This will be discussed further in Chapter 5.

#### 1.4. PROJECT OBJECTIVES AND THESIS OUTLINE

This research work will focus on designing and fabrication of various types of sensors as proof of concept. The work is multi-disciplinary where mechanical, electrical, and optical knowledge is used to fabricate devices which are harsh environment compatible, either thanks to their physical or structural properties. In Chapter 2 we focus on developing a highly sensitive accelerometer for applications requiring tilt and vibration sensing. Here, we design and fabricate a MEMS silicon device using high aspect ratio deep reactive ion etching to obtain a large mass supported by four long slender beams. The beams are non-linear allowing for high sensitivity. In Chapter 3 we will introduce ultraviolet detection, photodetectors, antireflective coating, 4H-SiC oxidation, and etching of 4H-SiC. In Chapter 4 we focus on the development of metal-semiconductor-metal (MSM) devices for UV and temperature sensing. In Chapter 5 we introduce a pin photodiode aimed at avalanche operation to detect small UV signals, up to single photons. In Chapter 6 we focus on a CMOS temperature sensor and briefly introduce a simple amplifier circuit in SiC as proof of concept. A conclusion and recommendations chapter is added to give future work outlook.

#### REFERENCES

- [1] R. P. Feynman, *There's plenty of room at the bottom,* California Institute of Technology, Engineering and Science magazine (1960).

- [2] G. Q. Zhang and A. V. Roosmalen, *More than moore Creating High Value Micro/Nanoelectronics Systems* (Springer, Boston, MA, 2009).

- [3] G. Zhang, M. Graef, and F. van Roosmalen, *The rationale and paradigm of "more than moore"*, 56th Electronic Components and Technology Conference 2006, , pp. 7 (2006).

- [4] W. Arden, M. Brillouët, P. Cogez, M. Graef, B. Huizing, and R. Mahnkopf, *More-than-moore white paper*, Version **2**, 14 (2010).

- [5] M. M. Waldrop, The chips are down for moore's law, Nature News 530, 144 (2016).

- [6] P. French, G. Krijnen, and F. Roozeboom, *Precision in harsh environments*, Microsystems & nanoengineering **2**, 1 (2016).

- [7] K. Dyrbye, T. R. Brown, and G. F. Eriksen, *Packaging of physical sensors for aggressive media applications*, Journal of Micromechanics and Microengineering 6, 187 (1996).

- [8] D. G. Senesky, B. Jamshidi, K. B. Cheng, and A. P. Pisano, *Harsh environment sili-con carbide sensors for health and performance monitoring of aerospace systems: A review*, IEEE Sensors Journal **9**, 1472 (2009).

- [9] B. El Mansouri, L. M. Middelburg, R. H. Poelma, G. Q. Zhang, H. W. van Zeijl, J. Wei, H. Jiang, J. G. Vogel, and W. D. van Driel, *High-resolution mems inertial sensor com*bining large-displacement buckling behaviour with integrated capacitive readout, Microsystems & Nanoengineering 5, 1 (2019).

- [10] L. M. Middelburg, H. van Zeijl, S. Vollebregt, B. Morana, and G. Zhang, *Toward a self-sensing piezoresistive pressure sensor for all-sic monolithic integration*, IEEE Sensors Journal **20**, 11265 (2020).

- [11] M. A. Silva, D. C. Guerrieri, H. van Zeijl, A. Cervone, and E. Gill, *Vaporizing liquid microthrusters with integrated heaters and temperature measurement,* Sensors and Actuators A: Physical **265**, 261 (2017).

- [12] R. Middlemiss, A. Samarelli, D. Paul, J. Hough, S. Rowan, and G. Hammond, *Measurement of the earth tides with a mems gravimeter*, Nature **531**, 614 (2016).

- [13] D. Crossley, J. Hinderer, and U. Riccardi, *The measurement of surface gravity*, Reports on Progress in Physics **76**, 046101 (2013).

- [14] C. Rothleitner, S. Svitlov, H. Mérimèche, H. Hu, and L. Wang, *Development of new free-fall absolute gravimeters*, Metrologia **46**, 283 (2009).

- [15] F. Scholze, R. Klein, and T. Bock, *Irradiation stability of silicon photodiodes for extreme-ultraviolet radiation*, Applied optics **42**, 5621 (2003).

- [16] D. Prasai, W. John, L. Weixelbaum, O. Krüger, G. Wagner, P. Sperfeld, S. Nowy, D. Friedrich, S. Winter, and T. Weiss, *Highly reliable silicon carbide photodiodes* for visible-blind ultraviolet detector applications, Journal of Materials Research 28, 33 (2013).

- [17] N. Zhang, C.-M. Lin, D. G. Senesky, and A. P. Pisano, *Temperature sensor based on 4h-silicon carbide pn diode operational from 20 c to 600 c*, Applied Physics Letters **104**, 073504 (2014).

- [18] J. He, C. Zhao, S.-H. Lee, K. Peterson, R. Geiger, and D. Chen, *Highly linear very compact untrimmed on-chip temperature sensor with second and third order temperature compensation*, in 2010 53rd IEEE International Midwest Symposium on Circuits and Systems (IEEE, 2010) pp. 288–291.

- [19] Z. Li, Y. Li, J. Du, J. Gao, X. Zhang, T. Liu, G. Wang, R. Li, Z. Liu, and J. Wang, *Classification of different types of partial discharge based on acoustic emission techniques*, in *Proceedings of 2013 2nd International Conference on Measurement, Information and Control*, Vol. 02 (2013) pp. 1118–1121.

- [20] F. Álvarez, F. Garnacho, J. Ortego, and M. Á. Sánchez-Urán, *Application of hfct and uhf sensors in on-line partial discharge measurements for insulation diagnosis of high voltage equipment*, Sensors **15**, 7360 (2015).

- [21] M. Muhr and R. Schwarz, *Experience with optical partial discharge detection*. Materials Science (0137-1339) **27** (2009).

- [22] Z. Zhang, W. Zhang, D. Zhang, Y. Xiao, J. Deng, and G. Xia, *Comparison of different characteristic parameters acquired by uv imager in detecting corona discharge*, IEEE Transactions on Dielectrics and Electrical Insulation **23**, 1597 (2016).

- [23] M. Wang, A. Vandermaar, and K. Srivastava, *Review of condition assessment of power transformers in service*, IEEE Electrical Insulation Magazine 18, 12 (2002).

- [24] L. Sang, M. Liao, and M. Sumiya, *A comprehensive review of semiconductor ultraviolet photodetectors: from thin film to one-dimensional nanostructures*, Sensors **13**, 10482 (2013).

- [25] Z. Alaie, S. M. Nejad, and M. Yousefi, *Recent advances in ultraviolet photodetectors*, Materials Science in Semiconductor Processing **29**, 16 (2015).

- [26] S. Yang, D. Zhou, X. Cai, W. Xu, H. Lu, D. Chen, F. Ren, R. Zhang, Y. Zheng, and R. Wang, *Analysis of dark count mechanisms of 4h-sic ultraviolet avalanche photodiodes working in geiger mode*, IEEE Transactions on Electron Devices **64**, 4532 (2017).

- [27] H. Abderrazak and E. Hmida, *Silicon carbide: synthesis and properties*, Properties and applications of Silicon Carbide, 361 (2011).

- [28] M. Mazzillo, A. Sciuto, F. Roccaforte, and V. Raineri, 4h-sic schottky photodiodes for ultraviolet light detection, in 2011 IEEE Nuclear Science Symposium Conference Record (IEEE, 2011) pp. 1642–1646.

- [29] L. Werner, Ultraviolet stability of silicon photodiodes, Metrologia 35, 407 (1998).

- [30] A. Aldalbahi, E. Li, M. Rivera, R. Velazquez, T. Altalhi, X. Peng, and P. X. Feng, *A new approach for fabrications of sic based photodetectors*, Scientific reports **6**, 23457 (2016).

- [31] P. Lenzi and S. Tudisco, How can we use sic? PoS, 008 (2016).

- [32] M. Mukherjee, *Silicon Carbide: Materials, Processing and Applications in Electronic Devices* (BoD–Books on Demand, 2011).

- [33] M. E. Levinshtein, S. L. Rumyantsev, and M. S. Shur, *Properties of Advanced Semi-conductor Materials: GaN, AIN, InN, BN, SiC, SiGe* (John Wiley & Sons, 2001).

- [34] G. Fisher and P. Barnes, *Towards a unified view of polytypism in silicon carbide*, Philosophical Magazine B **61**, 217 (1990).

- [35] S. Tanaka, R. S. Kern, and R. F. Davis, *Effects of gas flow ratio on silicon carbide thin film growth mode and polytype formation during gas-source molecular beam epitaxy*, Applied physics letters **65**, 2851 (1994).

- [36] F. Bechstedt, P. Käckell, A. Zywietz, K. Karch, B. Adolph, K. Tenelsen, and J. Furthmüller, *Polytypism and properties of silicon carbide*, physica status solidi (b) **202**, 35 (1997).

- [37] M. H. Hong, A. Samant, and P. Pirouz, *Stacking fault energy of 6h-sic and 4h-sic single crystals*, Philosophical Magazine A **80**, 919 (2000).

- [38] E. Monroy, F. Omnès, and F. Calle, *Wide-bandgap semiconductor ultraviolet pho-todetectors*, Semiconductor Science and Technology **18**, R33 (2003).

- [39] O. M. Rodríguez-Benítez, M. P. Silva, L. H. González, J. A. Aqui-Tapia, A. C. Sánchez, G. Calzada-Lara, and C. Cortés-García, *Recent advance and future progress of gan power semiconductor devices used in pv module integrated converters,* (2018).

- [40] M. A. Fraga, H. Furlan, R. Pessoa, and M. Massi, *Wide bandgap semiconductor thin films for piezoelectric and piezoresistive mems sensors applied at high temperatures: an overview, Microsystem technologies* **20**, 9 (2014).

- [41] A. Ong, J. Carr, J. Balda, and A. Mantooth, A comparison of silicon and silicon carbide mosfet switching characteristics, in 2007 IEEE Region 5 Technical Conference (IEEE, 2007) pp. 273–277.

- [42] B. V. Suresh, Solid State Devices and Technology (Pearson Education India, 2010).

# A HIGH-RESOLUTION MEMS INERTIAL SENSOR

This chapter discusses the design of a highly sensitive accelerometer capable of  $ng/\sqrt{Hz}$  sensitivity. The device can be used for tilt and vibration sensing and is also known as a MEMS gravimeter. First, the requirements for the sensor are defined followed by detailing the design, realisation and testing.

#### 2.1. Introduction

The research community is becoming exceedingly more interested in the behaviour of our planet regarding its weather condition, but also other geoscience studies such as earth plate movements, volcanic activity, underground water- and oil pockets [1] or any extremely small variations in local gravitational acceleration. Moreover, such sensing can also be used to monitor vibrations in high-end machines where nanometre accuracy is required, e.g. lithography processing machines. To sense vibrations, MEMS technology can be applied, e.g. highly sensitive accelerometers. Although MEMS devices do not have the high sensitivity seen in the traditional devices such as mechanical gravimeters, the MEMS devices are much smaller while being low cost when produced in high quantities. Moreover, such devices can be combined with the emerging Internet of Things (IoT) [2] to sense over large areas. Since the cost is much lower, the MEMS devices can be placed in a much higher density which may allow for a higher mapping of measured areas. A MEMS-based gravimeter should have a sensitivity in the range of  $1-100\ ng/\sqrt{Hz}$  to measure very small changes in gravitational acceleration at low frequencies [1].

Recently researchers have put focus on developing MEMS accelerometers for gravimetry applications. Middlemiss et. Al. designed a highly sensitive accelerometer exploiting nonlinear buckling behaviour observed in compliant mechanisms [3]. Thanks to this, a high mechanical sensitivity within the micromachined structure was obtained and reached a value of  $40~ng/\sqrt{Hz}$  at a resonance frequency of 2.3 Hz. However, this work didn't exploit the full potential of MEMS devices lacking the electrical component of MEMS technology. Instead, the read-out of motion was done using a shadow sensor which is comprised of a LED and a photodiode. Furthermore, the device is highly sensitive to temperature variations where 1~mK can result in an error of  $0.25~\mu Gal$ , or 0.25~ng. To account for this limitation, a servo-control was added for temperature control. An integrated electrical readout as seen in standard applications, i.e. capacitive transduction, would result to reduction in cost and facilitate miniaturization. This could be further enhanced by using onboard integrated ASIC to process the capacitive signal while significantly improving noise level performance [4].

Li, et. Al, have developed a linear spring-based accelerometer for gravimetry applications [5–7]. The device has a sensitivity of 30  $ng/\sqrt{Hz}$  at a resonance frequency of 13.2 Hz. The high sensitivity is obtained using a fine/coarse capacitive readout combined with linear springs. However, the realization of this device is complex as it requires wafer stacking and bonding to enable surface capacitive transduction. Furthermore, such configuration introduces fringe capacitances and large parasitic capacitances reducing noise level performance.

Unlike the work of Li, this work uses nonlinear near-zero stiffness springs for further improvement of resolution. By employing a capacitive readout ASIC with higher sensitivity, system resolutions beyond  $ng/\sqrt{Hz}$  could be feasible. Furthermore, using nonlinear springs, the dynamic range is not determined solely by the low spring stiffness, i.e. a measurable signal is still feasible even when the device is not in its operating point. It should be noted that both the stiffness and resonance frequency will increase.

Therefore, this work will focus on designing and realization of a compact MEMS ac-

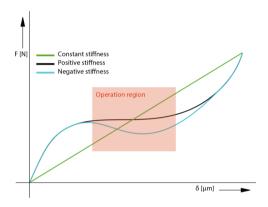

celerometer capable of  $ng/\sqrt{Hz}$  detection based on capacitive readout with an open-loop configuration. The beams holding the mass in place are nonlinear, theoretically capable of reaching near-zero stiffness. such behaviour is seen in compliant mechanisms having large elastic deformations by design which allow actuation with precision without having to deal with friction, wear, or backlashes [8]. The difference in this design is the absence of negative stiffness which prevents the device to buckle in a second motion or negative state. By designing the geometry of the four beams properly, the softening of the beams can result in a local region where the spring stiffness is near-zero for a range of displacement values, while an increase in stiffness is observed for displacements out of this range [9]. This is illustrated in Figure 2.1 as a local 'constant region' or 'positive stiffness region' in the force-displacement graph.

Figure 2.1: Behaviour of linear and nonlinear beams [4].

As mentioned earlier, it's necessary to design the beams such that negative stiffness is avoided. This not only limits the range of motion, hence, reducing the sensing range of the device, but also results in multiple operating points for the same applied force where a snap-through behaviour occurs as illustrated for the negative stiffness spring in Figure 2.1.

#### 2.2. BACKGROUND

#### 2.2.1. MECHANICAL SPRING SYSTEM

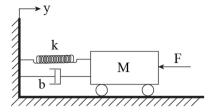

Before discussing the design, first relevant basic accelerometer theory will be introduced. This is true for linear behaviour but is used to convey the principle of the nonlinear device. The design will be aided using finite element modelling using COMSOL software. Consider Figure 2.2 where a mass-spring system is shown.

The operation principle of accelerometers is based on Newton's second law. A cantilever with a mass at its tip acts as an accelerometer where an external excitation force (F) such as a shock can be used to displace the mass. The cantilever acts as a spring with a stiff-

Figure 2.2: Mechanical representation of an open-loop accelerometer [10].

ness (k) while some damping (b) reduces the displacement. After the displacement, the mass will experience a restoring force due to the spring action of the cantilever.

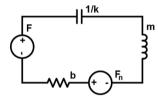

To analyse such systems, one can use the electrical equivalent circuit of the system as illustrated in Figure 2.3. For completion, a noise source is added to account for the Brownian motion noise (white) noise.

Figure 2.3: Electrical equivalent circuit of the accelerometer representation [11].

This results in the second-order equation (2.1).

$$F + F_n = m \cdot a = m \cdot \frac{d^2x}{dt^2} + b \cdot \frac{dx}{dt} + kx$$

(2.1)

Using Laplace transform for s-plane, this results in equation (2.2).

$$\frac{X(s)}{A(s)} = \frac{m}{ms^2 + bs + k} = \frac{1}{s^2 + \frac{b}{m}s + \frac{k}{m}} = \frac{1}{s^2 + 2\zeta\omega_n s + \omega_n^2}$$

(2.2)

The above leads to the formulation of the resonance frequency [10]

$$\omega_n = \sqrt{\frac{k}{m}}$$

and  $\zeta = \frac{b}{2m\omega_n}$  (2.3)

Where  $\omega_n$  is the natural resonance frequency and  $\zeta$  is the damping factor.

Here the damping coefficient (*b*) is determined by gas damping where this can be pressurized to a certain degree to obtain critical damping, provided packaging requirements

are met. The critical damping is important for achieving maximum bandwidth and minimum overshoot or ringing [10]. Moreover, the damping coefficient is temperature dependent which adds to the difficulty of obtaining linear behaviour due to compressibility of the gas in the case an open-loop configuration for the accelerometer is selected.

Both the bandwidth (BW) and sensitivity (S) can be determined using the resonance frequency. To measure it, the accelerometer can be dynamically resonating or statically measuring the displacement for a given acceleration. The displacement is related to natural resonance frequency by [10]

$$\omega_n^2 = \frac{k}{m} = \frac{a}{r} \quad with \quad x = \frac{F}{k} = \frac{m \cdot a}{k} = \frac{m \cdot g}{k}$$

(2.4)

Where g is the gravity constant. As for the sensitivity, this is determined by the inverse of the square of the natural resonance frequency and is obtained by taking equation (2.2) at s = 0 as shown by equation (2.5).

$$S = \frac{X(s)}{A(s)}\Big|_{s=0} = \frac{1}{\omega_n^2} = \frac{m}{k}$$

(2.5)

Equation (2.5) shows that the sensitivity can be high by reducing the bandwidth. This can be done by increasing the proof mass weight or by reducing the suspension beams stiffness.

The trade-off is made for an open-loop accelerometer are between the sensitivity, dynamic range, and bandwidth [10]. Therefore, the key design aspect of an open-loop accelerometer is its mechanical suspension design. Closed-loop control can be added to the design of an accelerometer where the output signal is used to generate a feedback force and apply this onto the proof mass. This counteracts the acceleration resulting in a stationary proof mass and negligible displacement [10]. This design has the advantage of being less sensitive to process variations and by adding temperature sensing one can further reduce the errors in the measurements.

#### 2.2.2. MECHANICAL NOISE

The fundamental detection limit of an accelerometer is determined by the noise of the total system including, the mechanical Brownian motion (white) noise and the electrical noise [12]. Consider equation (2.6).

$$X(s) = \frac{F + F_n}{ms^2 + bs + k} \quad \Rightarrow \quad \frac{X(s)}{A(s)} = \frac{1}{s^2 + \frac{b}{m}s + \frac{k}{m}} = \frac{1}{s^2 + \frac{\omega_n}{Q}s + \omega_n^2}$$

(2.6)

The damping shown in the equivalent circuit in Figure 2.3 accounts for the noise, similar to a resistor in an electrical circuit. Following this analogy, the noise spectral density is given by  $4k_BTb$ . Moreover, this can be related to the mechanical quality factor (Q) given by equation (2.7).

$$Q = \frac{m\omega_n}{b} \tag{2.7}$$

The noise can be interpreted as an error in the acceleration. Consider equation (2.8) at low frequency  $\omega \ll \omega_n$ .

$$a_{n,rms} = \sqrt{\frac{4k_B Tb}{m^2}} = \sqrt{\frac{4k_B Tb}{m \cdot \left(\frac{Q \cdot b}{\omega_n}\right)}} = \sqrt{\frac{4k_B T\omega_n}{m \cdot Q}} \qquad \left[ms^{-2} Hz^{-1/2}\right]$$

(2.8)

Using the above equations one can design an accelerometer that has minimum noise contribution for a given sensitivity. Furthermore, it can be seen that the resonance frequency is an important factor in reducing the noise. The minimum detectable acceleration is inversely proportional to the square-root of the accelerometer proof mass which is the fundamental limit for silicon accelerometers regardless of the sensing method [10]. The signal-to-noise ratio (SNR) is then given by equation (2.9).

$$S^2 = \frac{a^2}{a_n^2} = \frac{a_n^2 mQ}{4k_B T \omega_n}$$

(2.9)

From the above equation, it shows that the resonant frequency should be kept as minimum as possible while meeting the required bandwidth for the specific sensing application. This can be done by increasing the proof mass weight while reducing the spring constant or stiffness. The SNR equation also shows that the quality factor Q should be as large as possible for maximizing the SNR [10]. Next to mechanical noise there is also the electrical noise component. This is dependent on the capacitive interconnect and readout ASIC as will be explained in later text.

#### 2.3. NONLINEAR BEAM DESIGN

#### **2.3.1.** DESIGN OF A SINGLE NONLINEAR BEAM

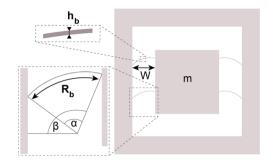

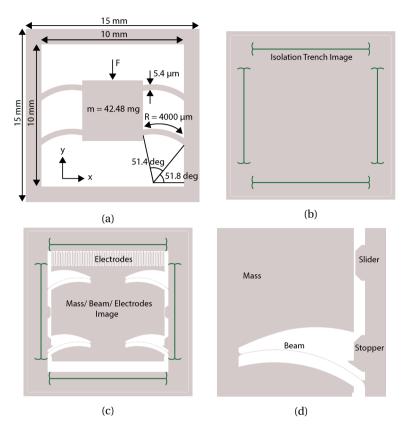

As shown in Figure 2.4, the accelerometer in our design uses four slender beams to suspend the mass in the centre of the frame. Here the beams are initially curved while both ends have inclination angles of  $\alpha$  and  $\beta$ . Finite Element Analysis (FEA) is employed for designing the device based on initial parameters such as the required mechanical sensitivity, the fabrication limitations, and any other general design rules for compliant mechanisms. The simulations were carried out using COMSOL for displacements in the y-direction, x-direction, and z-direction. The outcomes are the force-displacement curves, the mechanical stiffness and the resonance frequencies. The overall design of the mass-beam device was done modularly.

Consider Figure 2.4 showing the suspended mass and Table 2.1 listing the geometry design parameters used in the simulations. Here angles  $\alpha$  and  $\beta$  are defined as per Table 2.1.

Figure 2.4: Illustration of the mechanical structure and the geometry design parameters.

| Parameter                              | Symbol | Setting               |

|----------------------------------------|--------|-----------------------|

| Device thickness                       | t      | $300 \mu m$           |

| Mass weight                            | m      | 35 – 69.9 <i>mg</i>   |

| Beam height                            | $h_b$  | $4-6 \mu m$           |

| Beam radius                            | $R_b$  | $3000 - 4500 \ \mu m$ |

| Beam sector angle                      | α      | 51.4°                 |

| Beam inclination angle                 | β      | 103.2°                |

| Inner frame dimensions                 | $f_i$  | $10 \times 10 \ mm^2$ |

| Outer frame dimensions                 | $f_0$  | $15 \times 15 \ mm^2$ |

| Spacing W between mass and inner frame | W      | $3500 - 4500 \ \mu m$ |

A simple yet effective relation between the mass and the spring stiffness is given by equations (2.10) and (2.11).

$$F = m \cdot a = m \cdot g \qquad \Rightarrow \qquad m = \frac{F}{9.81} \tag{2.10}$$

$$f_0 = \frac{1}{2\pi} \sqrt{\frac{k}{m}} = 2 Hz$$

$\Rightarrow$   $\frac{k}{m} = 16\pi^2$   $\Rightarrow$   $m = \frac{k}{16\pi^2}$  (2.11)

The above relation is only useful at the operating point where a linearisation is done. This can be used as an indication for determining the stiffness at a given mass.

To obtain the nonlinear behaviour, the geometry design parameters are changed iteratively until the desired force-deflection behaviour is obtained. The aim is to design a device having a frame of  $15 \times 15 \ mm^2$  where the mass-beam structure is within  $10 \times 10 \ mm^2$ . This means that the beams can be about  $4-5 \ mm$  long to fit within these constraints. Moreover, the mass should have a minimum width (x-direction) to reduce deflections in unwanted directions. To further restrict unwanted deflections, the beams should be as straight as possible while still maintaining a low stiffness at the operating region. This means that the beams should have a large radius and be as close to a straight beam as

possible when the sector and inclination angles are adjusted for the beam to fit the required spacing (*W*) between mass and inner of the frame. By combining the radius, the inclination angle and the sector angle, the desired force-displacement behaviour and lower spring stiffness of the beam can be obtained. Other parameters are the beam thickness and length, where the latter is set by its radius and spacing W between mass and inner of the frame.

It should be noted that without design guidelines, the task becomes tedious due to a large number of degrees of freedom given by the geometrical parameters. Hence, the first objective is to formulate design guides to obtain the desired force-displacement behaviour.

#### SECTOR AND INCLINATION ANGLES

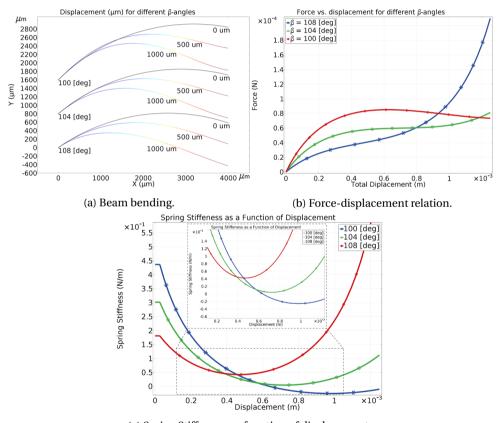

The first design parameters are the sector and inclination angles. Consider Figure 2.5.

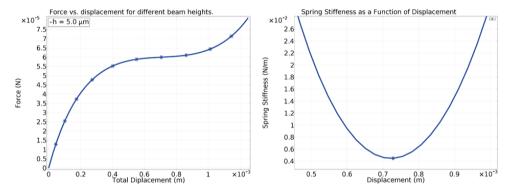

(c) Spring Stiffness as a function of displacement.

Figure 2.5: Single beam at different inclination angles.

Figure 2.5a shows three beams with increasing sector and inclination angles as defined in Figure 2.4. Here, the bent shapes of the beams for different deflections are shown.

Notice that the larger the inclination angle at the fixed tip, the larger this also becomes at the moving tip. Here the sector angle of the beams is increased to fit the beam within the available spacing W at 4000  $\mu m$  while maintaining the radius at a constant value of 4500  $\mu m$ . Furthermore, an indicative effect is the "S-shape" of the bent beam. It indicates a spring softening effect in the beams which becomes more apparent at higher inclination angles. However, as the inclination angle further increases at both sides, the S-shape from the bending becomes less prominent resulting in the bottom spring. Figure 2.5b shows the force-displacement behaviour indicating that the higher the inclination angle, the flatter the near-constant force region becomes. The low inclination angle shows that multiple operating points exist for the same applied force. The inclination angle at  $104^o$  shows the best behaviour but can further be improved. To do this a close look at the spring stiffness is needed. Figure 2.5c shows the spring stiffness, obtained by taking the derivative of the force-displacement relation (see equation (??) in Appendix A). The inclination angle of  $104^o$  indeed shows the lowest stiffness without becoming negative.

Another option for fitting the beam within the spacing W can be by adjusting the radius instead of the sector angle. By doing so the inclination angle at the moving tip of the beam can be kept relatively constant while the inclination angle at the fixed side may be changed. However, this method may be more complex to achieve the desired results but is nonetheless a useful method.

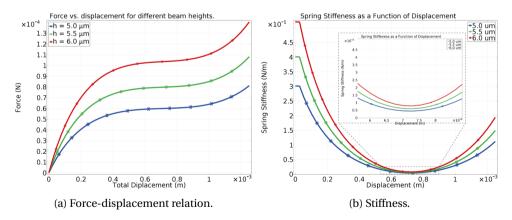

#### BEAM HEIGHT AND LENGTH

Once the desired force-displacement behaviour is achieved, the height of the beam and its length can be changed. These parameters are useful for determining both the size of the beams and the mechanical robustness during fabrication and application of the device. Moreover, the beam geometry also determines the mass size and with that, the size of the device. Consider Figure 2.6 showing the simulations for different beam heights.

Figure 2.6: Single beam at different beam heights.

Figures 2.6a-2.6b show that required force scales down with decreasing beam height (thickness). This enables smaller mass size, hence smaller devices. However, the thinner

the beams become, the more challenging the fabrication becomes. The devices will also be very fragile.

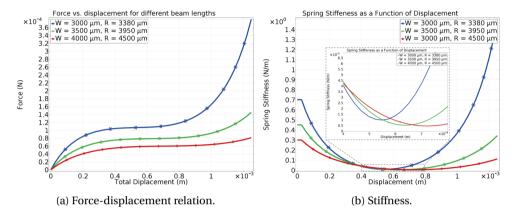

The length of the beam has a similar effect on the force-displacement behaviour and is set by the spacing W and the radius of the curved beam. Consider Figures 2.7. Here the beam length is varied using the curve radius while maintaining the sector and the inclination angles at constant values of  $54.31^o$  and  $104^o$ , respectively. The spacing W is varied in steps of  $500~\mu m$  from  $3000-4000~\mu m$ . As for the beam height, this is  $5~\mu m$ .

Figure 2.7: Single beam at different beam lengths (spacing W).

Figure 2.7a shows that not only the force decreases but also an increase in the displacement range is shown. This means that the beam length can be used to increase the dynamic range of the device and measure a larger range of acceleration. Figure 2.7b shows the stiffness as a function of the displacement. Similar to Figure 2.7a, a shift in the operating region is observed. However, the stiffness does not become negative which means that larger devices will have better performance.

#### **2.4.** DESIGN AND SIMULATIONS OF THE ACCELEROMETER

At this point, the design of the total accelerometer can be done. Recalling two basic requirements: the resonance frequency is targeted to be  $\sim 2~Hz$  while the mass-beam structure should fit within the given geometric constraints of  $10\times 10~mm^2$ . Recalling the relations given by equations (2.10) and (2.11), repeated here for ease. The equations give the minimum mass required for the mass deflection to reach the operating region of 1 g. Furthermore, the resonance frequency is also related to the minimum mass size. Both equations are useful at a linearised operating point.

$$F = m \cdot a = m \cdot g \quad \Rightarrow \quad m = \frac{F}{9.81}$$

(2.12)

$$f_0 = \frac{1}{2\pi} \sqrt{\frac{k(x)}{m}} = 2 Hz$$

$\Rightarrow$   $\frac{k(x)}{m} = 16\pi^2$   $\Rightarrow$   $m = \frac{k(x)}{16\pi^2}$  (2.13)

This means that by designing each beam, as described in the previous section, to have a certain stiffness, equations (2.12) and (2.13) can be used to define the mass required at the operating region. Since the geometrical size of  $10 \times 10~mm^2$  is known, a relation between the spring stiffness and the force generated by the gravitational acceleration can be plotted. The maximum mass which can be obtained within the geometrical constraints (simplified), is given by

$$m_{max} = \rho_{Si} \cdot \nu_m = 2330 \ [kg/m^3] \cdot [(10 \cdot 10^{-3}) \cdot (10 \cdot 10^{-3}) \cdot (300 \cdot 10^{-6})] = 69.9 \ mg$$

(2.14)

Where  $\rho_{Si}$  is the density of silicon and  $v_m$  is the volume of the mass having the units of  $kg/m^3$  and  $m^3$ , respectively. Through this method, the spring stiffness at the operating point can be designed while matching is done for the mass to reach the required force at the operating point. Consider Figures 2.8 showing the force-displacement relation and the spring stiffness of a single beam.

Figure 2.8: (a) Force and (b) stiffness behaviour as function of displacement of a single beam.

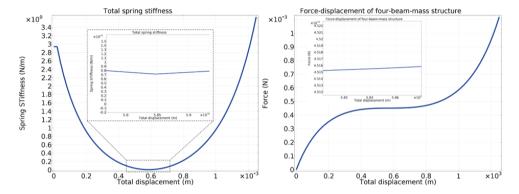

Knowing that spring stiffness can be summed, four beams at  $2\ Hz$  should have a mass of  $115\ mg$  which is far above the maximal attainable mass given the geometric constraints. Here the force should also be  $1.13\cdot 10^{-3}\ N$  to set the operating point at  $1\ g$  whereas Figure 2.8(a), it shows a force of approximately  $6\cdot 10^{-5}\ N$ . Summing this for four beams it gives  $2.4\cdot 10^{-4}\ N$  which corresponds to an acceleration of  $2.09\ ms^{-2}$ . This acceleration is far below  $1\ g$  and concludes that the beams have a stiffness that is too high. Using the design guides, the beam is redesigned to fit the requirements needed for  $1\ g$  operating point and a resonance frequency of  $2\ Hz$ . Table  $2.2\ sums$  the design parameters of the mass-beam structure.

Figures 2.9(a) 2.9(b) show the force- and spring stiffness as a function of displacement for the four-beam-mass structure.

The operating point of 1 g is at a displacement of 584  $\mu m$  in the above figure. The resonance frequency is determined at the operating point where the first mode is at 2 Hz. The second mode lies at 8487 Hz, thus sufficiently far from the first frequency mode.

| 0 1                                    |        |                       |  |  |

|----------------------------------------|--------|-----------------------|--|--|

| Parameter                              | Symbol | Setting               |  |  |

| Device thickness                       | t      | $300  \mu m$          |  |  |

| Mass weight                            | m      | 45.95 mg              |  |  |

| Beam height                            | $h_b$  | $5.55 \mu m$          |  |  |

| Beam radius                            | $R_b$  | $4000~\mu m$          |  |  |

| Beam sector angle                      | α      | 56.3°                 |  |  |

| Beam inclination angle                 | β      | 104.8°                |  |  |

| Inner frame dimensions                 | $f_i$  | $10 \times 10 \ mm^2$ |  |  |

| Outer frame dimensions                 | $f_0$  | $15 \times 15 \ mm^2$ |  |  |

| Spacing W between mass and inner frame | W      | 3570 μm               |  |  |

Table 2.2: MFour-beam-mass structure design parameters.

Figure 2.9: a) Force and b) spring stiffness vs. displacement of the four-beam-mass structure.

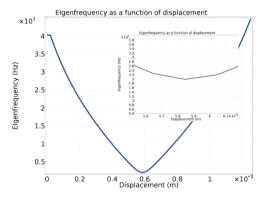

Figure 2.10: Eigenfrequency of the mass-beam structure as a function of displacement.

Recalling from equation (2.13), the spring stiffness is displacement dependent. Here the resonance frequency is the square root of the spring stiffness and mass ratio. Figure 2.10 is obtained from the spring stiffness relation.

The simulations were also done to obtain the spring stiffness in both the x- and z-directions in the same manner as for the y-direction. Here the direction of the prescribed displacement was changed to the unwanted directions. The proof mass was first set to the deflection corresponding to the operating point of 1 g in the y-direction by a prescribed displacement imposed on the mass. The resulting reaction forces and spring stiffness in these directions were then determined from the operating point with a deflection of  $\sim 800 \ \mu m$  The lowest stiffness at the 1 g operating point in the z-direction is  $2 \cdot 10^4$  times higher than in the y-direction. The estimated error caused by the out of plane displacement, a displacement of 50  $\mu m$  in the y-direction would result in a displacement of 3 nmat a tilting angle of  $34^{\circ}$ . The resulting capacitive error is then  $1 \cdot 10^{-3}$  %. As for the stiffness in the x-direction, this is initially similar to that in the y-direction and increases beyond a value of  $1.2 \cdot 10^5$  N/m after 20  $\mu m$  of displacement, owing to spring stiffening. A tilt with respect to the vertical axis can be applied to the device, resulting in a decreased ycomponent acting on the proof mass. By doing so, the operating point and stiffness are changed accordingly. Thanks to the high stiffness in the z-direction, the response of the sensor is not compromised by the out-of-plane force. The amount of deflection and thus the spring constant can be varied in this way, providing a trade-off between bandwidth and sensitivity.

# 2.5. Transducer design

Sensors in general can be classified according to transduction type for measuring the signal of interest. In this case, multiple read-out methods can be applied to convert the mechanical signal (displacement of the proof mass) to the electrical domain where data processing and communication takes place. The methods may include: piezoelectric, piezoresistive, optical, thermal, magnetic, and electrostatic. Each transaction type has its advantages and disadvantages. The transduction should be selected not only based on signal readout type, but also the best fitting method for fabrication. In this work, we selected the capacitive method based on its advantages for fabrication and readout. It is fairly easy to integrate into the device, can be directly used to translate the mechanical signal into an electrical one, and has low-temperature dependency.

The capacitive transducer used is a lateral comb drive structure where th electrode fingers slide into place after the release of the mass-beam structure. This helps in maximizing the number of electrode fingers which would otherwise be limited by the fabrication. Moreover, the structure helps in reducing the damping caused by air surrounding the fingers. This can be explained by the Couette flow, occurring for lateral motion, being much less dissipative compared with the squeeze film damping. Thanks to this and the main objective of measuring mechanical signals in the sub  $20\ Hz$  range, the fluid inside the gaps has enough time to displace. This also prevents the air to act like a spring, which stores and releases energy at higher frequencies [13]. The damping can be further reduced by using vacuum packaging.

The sensitivity of the capacitive transducer was maximised thanks to the number of IDT electrode fingers. For this analysis, a simplification of the capacitive change is used

where a linear addition of parallel plate equivalents is used. This is given by equation (2.15).

$$\Delta C_{tot} = \frac{2N\epsilon_0 \epsilon_r t(y_0 - y)}{d}$$

(2.15)

Where N is the number of fingers,  $\epsilon_0$  is the permittivity of vacuum,  $\epsilon_r$  is the relative permittivity, t is the thickness of the substrate,  $(y_0-y)$  is the displacement in the y-direction, and d is the gap between the IDT fingers. From this equation, it can be concluded that the change in capacitance is maximised by maximising the number of fingers within the geometrical constraints  $(10x10 \ mm^2)$  and by reducing the gap d between the IDT fingers.

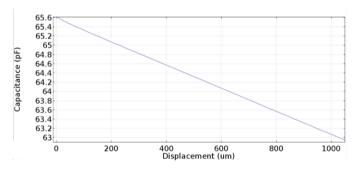

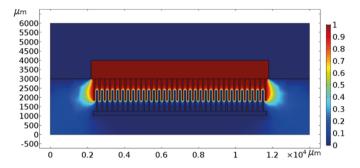

Capacitive simulations have been performed to investigate the electric field distribution and verify that the absolute value of the electric field does not exceed the dielectric strength of air. To simulate the capacitive response, an interdigitated (IDT) electrode was placed across a second moving electrode. The capacitance/displacement behaviour is included in Figure 2.11. As can be concluded from this result, the capacitance varied from 35.58 pF to 33.47 pF. The values on the y-axis however show larger values for the capacitance, because the trench for electric isolation is also included in this value. From this result, it can be concluded that the capacitive response as a function of deflection is highly linear with a large capacitive change per nm distance. Taking the first-order derivative of the capacitance versus displacement characteristic in the linear region yields a sensitivity of 2.55 aF/nm in the displacement region of interest.

Figure 2.11: Capacitance vs. displacement behaviour.

The high degree of linearity in the capacitive response is thanks to the large number of fingers. The non-linear effect of the fringing electric field on either side of the electrode array is suppressed by the large contribution to the total capacitance of the normal components of the field between the parallel electrode fingers. Figure 2.12 shows the electric field distribution, where the fringing electric field (boundary) effects are visible. Furthermore, it can be noted that the aspect ratio of the structure is high: The width of each finger equals only 70  $\mu m$ , whereas the thickness of the structure equals a wafer thickness of 300  $\mu m$ . The large width of each finger suppresses the non-linear effect caused by fringing fields at the beginning and end of the IDE finger array, while the large height of each IDE finger suppresses the fringing fields on front- and backside of the wafer.

Figure 2.12: Potential distribution of the IDT

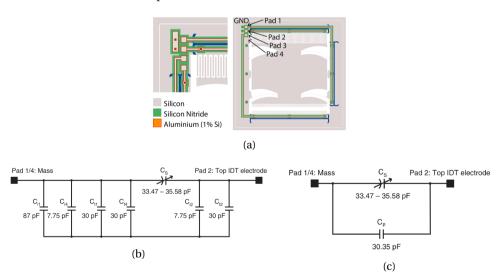

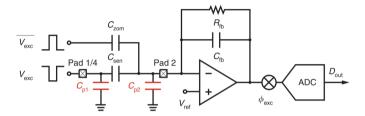

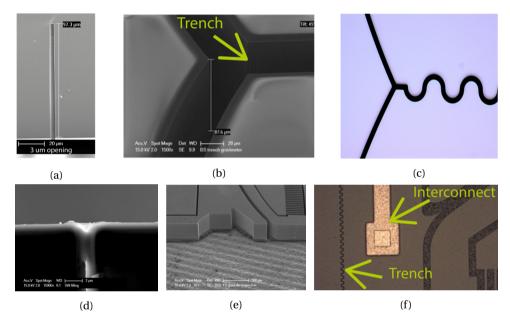

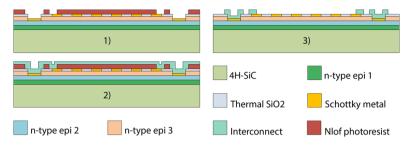

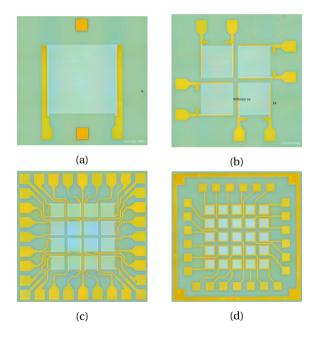

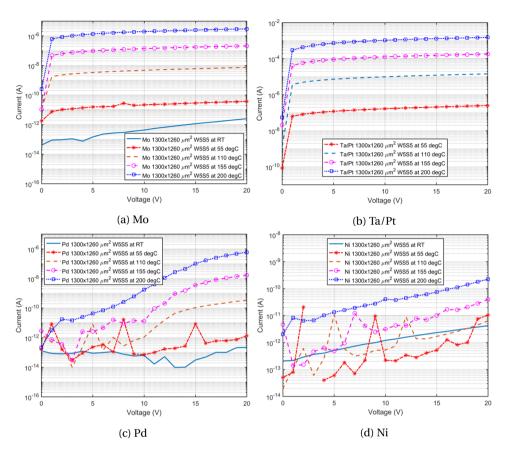

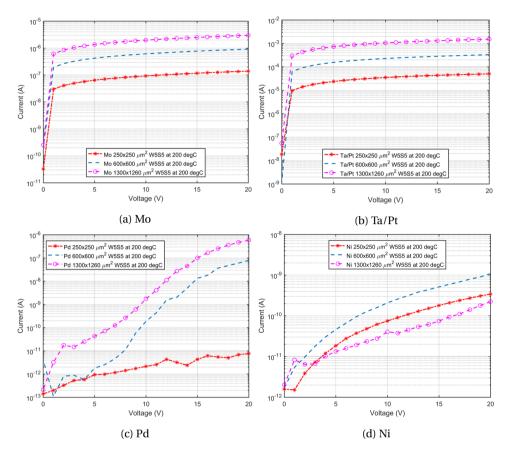

## 2.5.1. PARASITIC CAPACITANCES