### Digital Twin Technology for Microelectronics Reliability

Inamdar, A.S.

10.4233/uuid:e7e1054e-43aa-4f72-80c0-fbf6748537eb

**Publication date**

**Document Version** Final published version

Citation (APA)

Inamdar, A. S. (2025). Digital Twin Technology for Microelectronics Reliability. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:e7e1054e-43aa-4f72-80c0-fbf6748537eb

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# DIGITAL TWIN TECHNOLOGY

FOR MICROELECTRONICS RELIABILITY

**ADWAIT INAMDAR**

### **Invitation**

for the public defence of the doctoral thesis

Digital Twin

Technology for

Microelectronics

Reliability

## DIGITAL TWIN TECHNOLOGY FOR MICROELECTRONICS RELIABILITY

## DIGITAL TWIN TECHNOLOGY FOR MICROELECTRONICS RELIABILITY

### Dissertation

for the purpose of obtaining the degree of doctor at Delft University of Technology,

by the authority of the Rector Magnificus prof. dr. ir. T.H.J.J. van der Hagen, chair of the Board for Doctorates,

to be defended publicly on Wednesday, 10 September 2025, at 17:30

by

### **Adwait Sanjay INAMDAR**

Master of Science in Computational Engineering, Ruhr-University Bochum, Germany born in Thane, India This dissertation has been approved by the promotors.

Composition of the doctoral committee:

Rector Magnificus, Chairperson

Prof. dr. G.Q. Zhang, Delft University of Technology, promotor Prof. dr. ir. W.D. van Driel, Delft University of Technology, promotor

*Independent members:*

Prof. dr. ir. S. Hamdioui, Delft University of Technology, Netherlands Prof. dr. C.J. Bailey, Arizona State University, United States Prof. dr. S. Rzepka, Technische Universität Chemnitz, Germany

Dr. P.J. Gromala, Robert Bosch GmbH, Germany

Dr. A. Mavinkurve, NXP Semiconductors, Netherlands

Reserve member:

Em. prof. dr. ir. P.M. Sarro, Delft University of Technology, Netherlands

This work was supported by the European project *ArchitectECA2030* under the grant agreement №877539. The project is co-funded by grants from Germany, Netherlands, Czech Republic, Austria, Norway, and Electronic Component Systems for European Leadership Joint Undertaking (*ECSEL JU*).

Keywords: Digital Twin, Microelectronics Reliability, Physics of Degradation,

Epoxy Moulding Compounds, Thermomechanical Ageing, Finite Element Analysis, In-situ Monitoring, Piezoresistive Sensor, Design of Experiments, Reduced-order Models, Multi-point Constraints.

Printed by: Ipskamp drukkers

Cover by: Adwait Inamdar

Copyright © 2025 by A.S. Inamdar

ISBN: 978-94-6384-824-4

An electronic version of this dissertation is available at

https://repository.tudelft.nl.

Dedicated to my parents, teachers, friends & family

मला घडवणाऱ्या आणि सदैव पाठीशी असणाऱ्या आई, बाबा, दादा, आणि संपूर्ण कुटुंबाला, शिक्षक आणि मित्रपरिवाराला समर्पित!

## **CONTENTS**

| Li | st of A | Abbrevi | iations                                 | хi   |

|----|---------|---------|-----------------------------------------|------|

| Su | ımma    | ry      |                                         | xv   |

| Sa | menv    | atting  |                                         | xix  |

| 1  | Intr    | oductio | on                                      | 1    |

|    | 1.1     | Electro | onification of Industries               | . 2  |

|    | 1.2     | Degrae  | dation of Electronic Components         | . 4  |

|    | 1.3     | Micro   | electronics Reliability                 | . 6  |

|    | 1.4     | Progn   | ostics and Health Management            | . 8  |

|    | 1.5     | Monite  | oring Device                            | . 10 |

|    | 1.6     | Resear  | rch Objectives                          | . 11 |

|    | 1.7     | Outlin  | e of this Thesis                        | . 12 |

|    | Refe    | rences  |                                         | . 13 |

| 2  | Digi    | tal Twi | ns for Health Monitoring of Electronics | 19   |

|    | 2.1     | Introd  | uction                                  | . 20 |

|    | 2.2     | Digital | l Twin — Development                    | . 21 |

|    |         | 2.2.1   | History of Digitalisation               | . 22 |

|    |         | 2.2.2   | Review of Digital Twin Definitions      |      |

|    |         | 2.2.3   | Formal Definition of a Digital Twin     | . 27 |

|    | 2.3     | Digital | l Twin — Adoption                       |      |

|    |         | 2.3.1   | Industry 4.0 and Smart Manufacturing    |      |

|    |         | 2.3.2   | Health, Telecom, and Other Industries   |      |

|    |         | 2.3.3   | Reliability of Electronic Systems       | . 30 |

|    | 2.4     | Digital | l Twin — Architecture                   | . 30 |

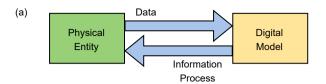

|    |         | 2.4.1   | Basic Structure                         | . 30 |

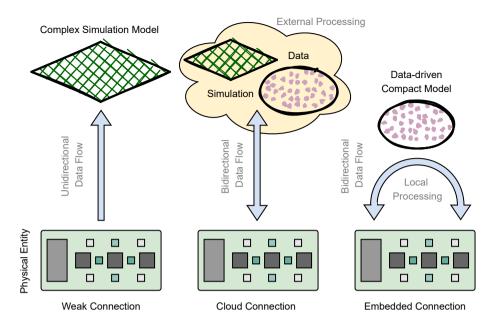

|    |         | 2.4.2   | Types of Connections                    | . 31 |

|    |         | 2.4.3   | Digital Twinning Approach               |      |

|    |         | 2.4.4   | What is <i>NOT</i> a Digital Twin?      |      |

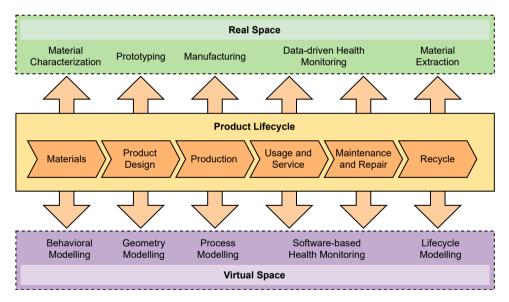

|    |         | 2.4.5   | Digital Twins and Product-Lifecycle     |      |

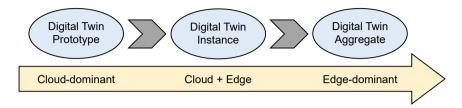

|    |         | 2.4.6   | Implementation Scales                   |      |

viii Contents

|   | 2.5  | Digital Twin — Models                                                                | 36 |

|---|------|--------------------------------------------------------------------------------------|----|

|   |      | 2.5.1 Three and Five-dimensional Models                                              | 36 |

|   |      | 2.5.2 Two-branched Model and PHM                                                     | 9  |

|   |      | 2.5.3 Advantages, Challenges, and Roadmap                                            | ŀ3 |

|   | Con  | lusion                                                                               | ŀ5 |

|   | Refe | rences                                                                               | ŀ6 |

| 3 | Elec | ronics Packaging and Physics-of-Degradation 5                                        | 3  |

|   | 3.1  | Packaging Technology                                                                 | 54 |

|   |      | 3.1.1 Encapsulating Materials                                                        | 54 |

|   |      | 3.1.2 Epoxy Moulding Compounds                                                       | 55 |

|   | 3.2  | Package-Associated Degradation                                                       | 6  |

|   |      | 3.2.1 Degradation Factors                                                            | 8  |

|   |      | 3.2.2 Failure Modes                                                                  | 9  |

|   | 3.3  | Hardware for Degradation Monitoring $\ldots \ldots \ldots \ldots \ldots $ $\epsilon$ | 51 |

|   |      | 3.3.1 Sensors and Measurements                                                       | 51 |

|   |      | 3.3.2 Processing and Communication 6                                                 | 52 |

|   |      | 3.3.3 Test-Board Reference Design 6                                                  | 53 |

|   | Con  | lusion                                                                               | 64 |

|   | Refe | rences                                                                               | 55 |

| 4 | Digi | al Twin Instance for Thermomechanical Ageing                                         | 71 |

|   | 4.1  | Introduction                                                                         | 72 |

|   | 4.2  |                                                                                      | 75 |

|   | 4.3  | \$                                                                                   | 7  |

|   | 4.4  |                                                                                      | 78 |

|   |      | 1                                                                                    | 79 |

|   |      |                                                                                      | 79 |

|   |      | •                                                                                    | 30 |

|   |      | 0                                                                                    | 32 |

|   |      | •                                                                                    | 3  |

|   |      | 4.4.6 A Continuous Material Model                                                    |    |

|   | 4.5  | 0 10                                                                                 | 0  |

|   | 4.6  | , 0                                                                                  | 2  |

|   | 4.7  |                                                                                      | 4  |

|   |      |                                                                                      | 8  |

|   | Refe | rences                                                                               | 0  |

| 5 | In-s | tu Monitoring for Data-driven Digital Twins                                          |    |

|   | 5.1  | Introduction                                                                         | 16 |

Contents ix

|     | 5.2             | Stress Sensing                                 | 107 |  |

|-----|-----------------|------------------------------------------------|-----|--|

|     |                 | 5.2.1 Sensor Readout Optimisation              | 108 |  |

|     |                 | 5.2.2 Sensor Data Processing                   | 109 |  |

|     | <b>5.</b> 3     | Temperature-Coupled Bend Test                  | 111 |  |

|     |                 | 5.3.1 Experimental Setup                       | 111 |  |

|     |                 | 5.3.2 Test Specimen                            | 112 |  |

|     |                 | 5.3.3 Loading Conditions                       | 113 |  |

|     |                 | 5.3.4 Data Processing and Analysis             | 114 |  |

|     | 5.4             | Mechanical Bend-Test until Failure             | 116 |  |

|     | Con             | clusion                                        | 119 |  |

|     | Refe            | erences                                        | 120 |  |

| 6   | Red             | uced-Order Modelling for Compact Digital Twins | 123 |  |

|     | 6.1             | Introduction                                   | 124 |  |

|     | 6.2             | Finite Element-based FOM                       | 126 |  |

|     | 6.3             | Substructure-based FEA (ROM)                   | 127 |  |

|     |                 | 6.3.1 Substructure Generation                  | 127 |  |

|     |                 | 6.3.2 ROM Integration and Load Vector          | 129 |  |

|     | 6.4             | Virtual Design of Experiments                  | 130 |  |

|     | 6.5             | ROM-FOM Interface for Complex Test Cases       | 135 |  |

|     |                 | 6.5.1 Accuracy Comparison                      | 136 |  |

|     |                 | 6.5.2 Efficiency Comparison                    | 138 |  |

|     | Con             | clusion                                        | 138 |  |

|     | Refe            | erences                                        | 139 |  |

| 7   | Con             | clusion and Future Outlook                     | 145 |  |

|     | <b>7.</b> 1     | Concluding Remarks                             | 145 |  |

|     | 7.2             | Recommendations                                | 147 |  |

| A   | App             | endix A: Supplemental Information to Chapter 3 | 149 |  |

| В   | App             | endix B: Supplemental Information to Chapter 6 | 155 |  |

| Ac  | knov            | vledgements                                    | 159 |  |

| Cu  | Curriculum Vitæ |                                                |     |  |

| Lie | st of I         | Publications                                   | 165 |  |

## **LIST OF ABBREVIATIONS**

| ISA        | Instruction Set Architecture            | 2  |

|------------|-----------------------------------------|----|

| IT         | Information Technology                  | 2  |

| IoT        | Internet of Things                      | 2  |

| AI         | Artificial Intelligence                 | 2  |

| ECA        | Electric Connected and Automated        | 3  |

| ECS        | Electronic Components and Systems       | 3  |

| SAE        | Society of Automobile Engineers         | 3  |

| ADAS       | Advanced Driver Assistance Systems      | 3  |

| ORAD       | On-Road Automated Driving               | 3  |

| V2X        | Vehicle to 'X'                          | 3  |

| V2V        | Vehicle to Vehicle                      | 3  |

| ABS        | Anti-lock Braking System                | 3  |

| IVI        | In-Vehicle Infotainment                 | 3  |

| EU         | European Union                          | 4  |

| MCE        | Mission Critical Electronics            | 4  |

| MEMS       | Micro-Electro-Mechanical Systems        | 4  |

| RUL        | Remaining Useful Life                   | 5  |

| TTF        | Time to Failure                         | 6  |

| PDF        | Probability Density Function            | 6  |

| ROCOF      | Rate of Occurrence of Failure           | 6  |

| MTTF       | Mean Time to Failure                    | 6  |

| MTBF       | Mean Time Between Failures              | 6  |

| <b>OEM</b> | Original Equipment Manufacturer         | 7  |

| PHM        | Prognostics and Health Management       | 8  |

| PoF        | Physics of Failure                      | 8  |

| PoD        | Physics of Degradation                  | 9  |

| PCB        | Printed Circuit Board                   | 10 |

| DC         | Direct Current                          | 10 |

| RF         | Radio Frequency                         | 10 |

| MSET       | Multivariate State Estimation Technique | 10 |

| SPRT       | Sequential Probability Ratio Test       | 10 |

| MonDev     |                                         | 11 |

| Digital Twin                                  | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Lifecycle Management                  | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| National Aeronautics and Space Administration | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Graphical User Interface                      | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Computer-Aided 'X'                            | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Computer-Aided Drawing                        | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Computer-Aided Engineering                    | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                               | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                               | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                               | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                               | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Building Information Model                    | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Machine Learning                              | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Micro-controller Unit                         | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Physics-Informed Neural Network               | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Digital Twin Prototype                        | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Digital Twin Instance                         | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Digital Twin Aggregate                        | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Integrated Circuits                           | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Outsourced Semiconductor Assembly and Test    | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Electronics System Design and Manufacturing   | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Assembly, Testing, Marking, and Packaging     | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Reference Architecture Model in Industry 4.0  | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Reduced-Order Model                           | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Molecular Dynamics                            | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Copper Nanoparticle                           | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Carbon Nanotube                               | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Light-Emitting Diode                          | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Dual In-line Package                          | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Quad Flat Package                             | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Small Outline Package                         | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Lead-less Chip Carrier                        | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Pin Grid Array                                | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Ball Grid Array                               | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Quad Flat No-leads                            | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Chip-Scale Package                            | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| System in Package                             | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Package on Package                            | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Wafer-Level Package                           | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                               | Product Lifecycle Management National Aeronautics and Space Administration Graphical User Interface Computer-Aided 'X' Computer-Aided Drawing Computer-Aided Engineering Computer-Aided Machining Three-Dimensional Heterogeneous Integration Roadmap Electronics Packaging Society Building Information Model Machine Learning Micro-controller Unit Physics-Informed Neural Network Digital Twin Prototype Digital Twin Instance Digital Twin Aggregate Integrated Circuits Outsourced Semiconductor Assembly and Test Electronics System Design and Manufacturing Assembly, Testing, Marking, and Packaging Reference Architecture Model in Industry 4.0 Reduced-Order Model Molecular Dynamics Copper Nanoparticle Carbon Nanotube Light-Emitting Diode Dual In-line Package Quad Flat Package Small Outline Package Lead-less Chip Carrier Pin Grid Array Ball Grid Array Quad Flat No-leads Chip-Scale Package System in Package System in Package Package on Package |

| EMC        | Epoxy Moulding Compound                             | 55  |

|------------|-----------------------------------------------------|-----|

| PEM        | Plastic-Encapsulated Microelectronics               | 55  |

| CTE        | Coefficient of Thermal Expansion                    | 56  |

| SEM        | Scanning Electron Microscope                        | 56  |

| WLCSP      | Wafer-Level Chip-Scale Package                      | 58  |

| <b>IMU</b> | Inertial Measurement Unit                           | 62  |

| BLE        | Bluetooth Low Energy                                | 63  |

| SPI        | Serial Peripheral Interface                         | 63  |

| I2C        | Inter-Integrated Circuit                            | 63  |

| USB        | Universal Serial Bus                                | 63  |

| AEC        | Automotive Electronic Council                       | 72  |

| FT-IR      | Fourier Transform Infrared                          | 72  |

| FE         | Finite Element                                      | 75  |

| HTS        | High-Temperature Storage                            | 75  |

| DUT        | Device Under Test                                   | 75  |

| DLO        | Diffusion-Limited Oxidation                         | 75  |

| TOL        | Thickness of Oxidation Layer                        | 75  |

| UV         | Ultraviolet                                         | 75  |

| <b>PMC</b> | Post Mould Cure                                     | 76  |

| DMA        | Dynamic Mechanical Analysis                         | 79  |

| TMA        | Thermal-Mechanical Analysis                         | 79  |

| KWW        | Kohlrausch-Williams-Watts                           | 80  |

| DOC        | Degree of Cure                                      | 85  |

| DoE        | Design of Experiments                               | 107 |

| SMT        | Surface Mount Technology                            | 107 |

| BEOL       | Back-End of Line                                    | 107 |

| BLR        | Board-Level Reliability                             | 108 |

| SMU        | Source Measurement Unit                             | 108 |

| SCPI       | Standard Commands for Programmable Instruments      | 109 |

| MOS        | Metal Oxide Semiconductor                           | 113 |

| MOR        | Model Order Reduction                               | 124 |

| LPM        | Lumped Parameter Model                              | 124 |

| SPICE      | Simulation Program with Integrated Circuit Emphasis | 124 |

| ANN        | Artificial Neural Network                           | 124 |

| FEM        | Finite Element Method                               | 125 |

| FEA        | Finite Element Analysis                             | 125 |

| IP         | Intellectual Property                               | 125 |

| FOM        | Full-Order Model                                    | 125 |

| SE         | Super Element                                       | 125 |

| VDoE | Virtual Design of Experiments | 126 |

|------|-------------------------------|-----|

| LF   | Lead-Frame                    | 126 |

| DoF  | Degrees of Freedom            | 128 |

| MPC  | Multi-Point Constraint        | 128 |

| HPC  | High-Performance Computer     | 138 |

| FMI  | Functional Mock-up Interface  | 139 |

| FMU  | Functional Mock-up Unit       | 139 |

| SBC  | Single-Board Computer         | 148 |

## **SUMMARY**

Electronic components are getting increasingly integrated into a diversity of applications, products, and industries and are becoming an essential part of them. In some cases, they are responsible for handling critical tasks (*e.g.*, the perception system in autonomous driving) and, in some, are exposed to harsh environmental conditions (*e.g.*, elevated temperatures). Thus, the reliable functioning of electronics has more significance than ever before. Traditional reliability qualification methods rely on the tests in specification manuals and handbooks. Although still commonly cited, they hold little significance in today's day and age.

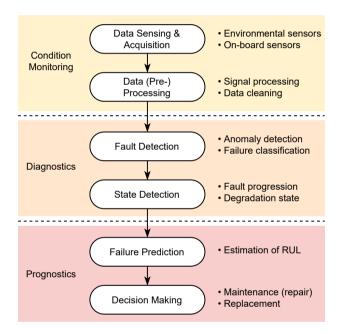

New methods of reliability estimation have emerged and evolved quite a lot over the past six decades. Yet, they face the limitation of getting only a collective overview of failures from batch-based experimental tests. In reality, it is often the case that identical electronic components experience non-identical operating conditions and environmental loads and, thus, have a variation in their lifetimes. Thus, obtaining individual, component-specific insights is crucial when moving from a physics-of-failure to a physics-of-degradation approach for reliability. Implementing Prognostics and Health Management (PHM) for electronic components is a promising way to address this challenge. Demonstrating this approach using a Digital Twin-based framework is the primary goal of this dissertation.

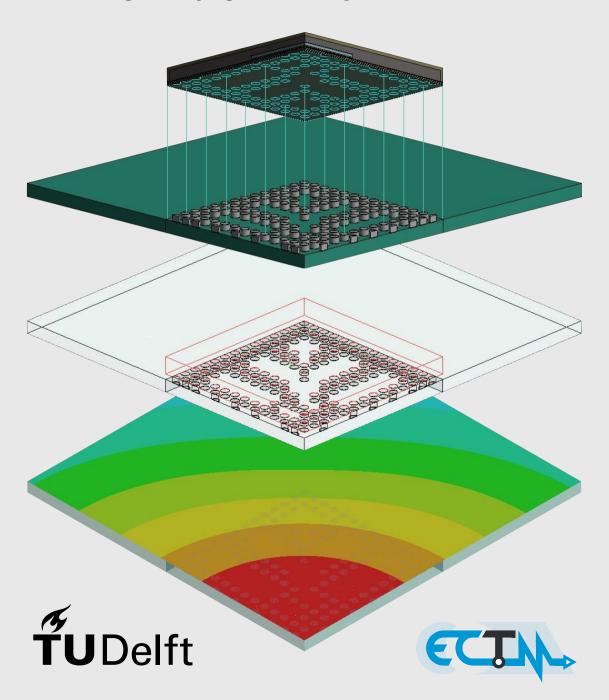

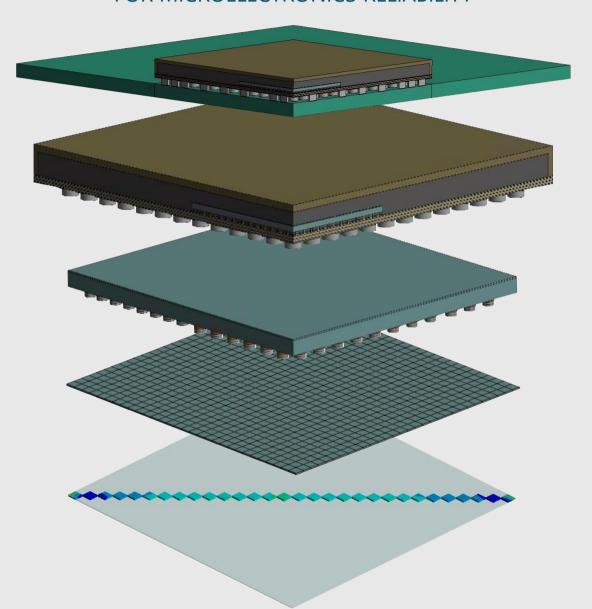

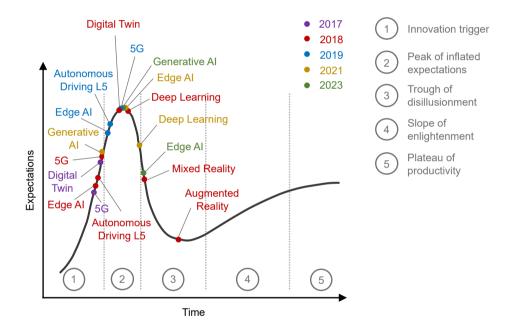

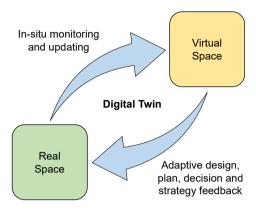

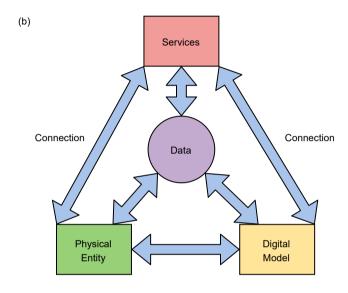

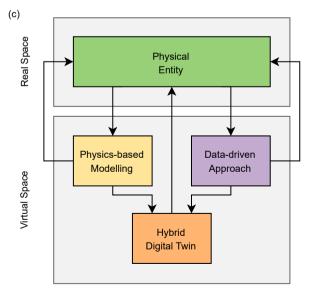

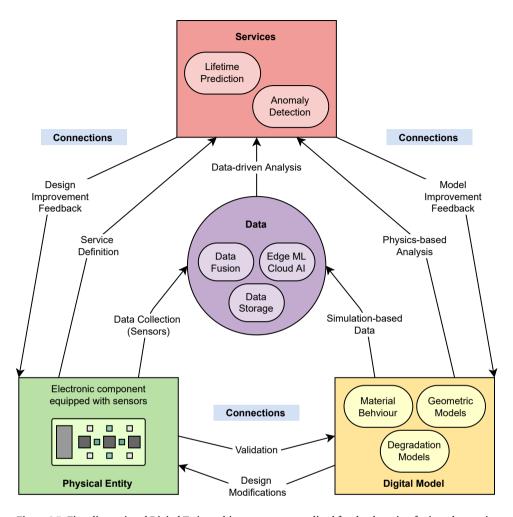

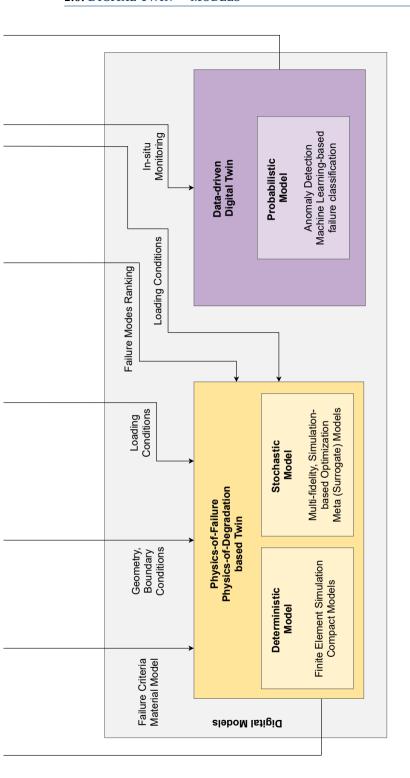

First, a generalised framework for PHM is laid out (Chapter 1), and its building blocks are discussed. Then a systematic review of the term 'Digital Twin' and its state of the art is presented (Chapter 2). A new, more comprehensive, and yet generalised definition of a Digital Twin (DT) is prepared. Existing DT architectural models are analysed, and a novel two-branched model is introduced, which incorporates two key techniques, *viz.*, physics-based and data-driven modelling. In a complete DT implementation including both modelling approaches, both a cloud-based (external) computing and an edge-based (localised) computing infrastructure can be utilised to varying capacities. There are three phases of implementing Digital Twins within a product's lifecycle — Digital Twin Prototype (DTP), Digital Twin Instance (DTI), and Digital Twin Aggregate (DTA) — which gradually shift from a cloud-dominant to edge-dominant implementation.

xvi Summary

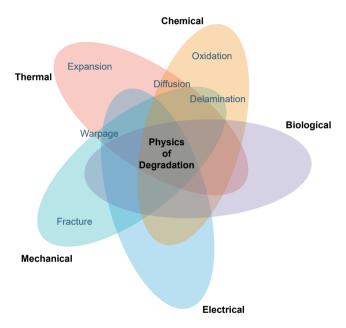

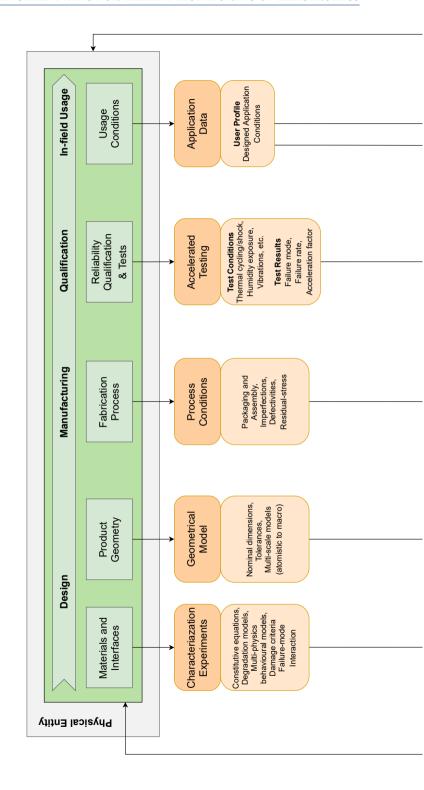

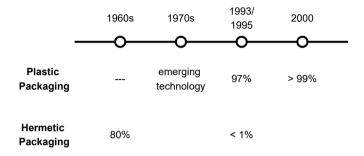

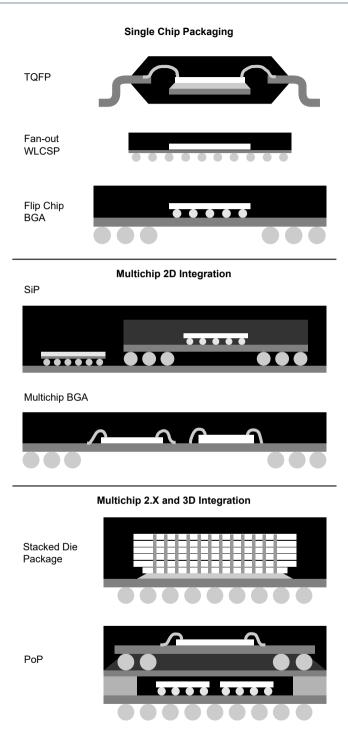

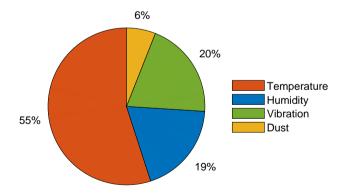

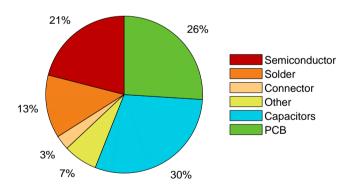

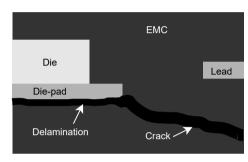

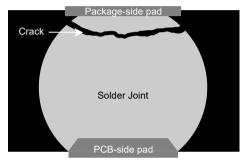

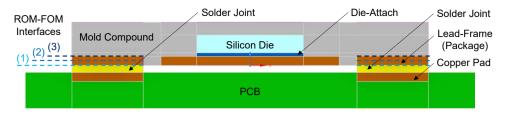

Next, the groundwork for the physics-based branch is laid (Chapter 3) by delving into electronics packaging materials and associated ageing effects and degradation mechanisms due to the three dominant stress-factors — temperature, humidity, and mechanical vibration. Two commonly observed package-associated mechanical failure mechanisms, *viz.*, delamination and solder fatigue are identified. Furthermore, specialised hardware requirements for an edge-based, data-driven DT implementation (*i.e.* a DTA) are explored. Each chapter after this is dedicated to demonstrating one or more puzzle pieces of the two-branched DT framework for PHM.

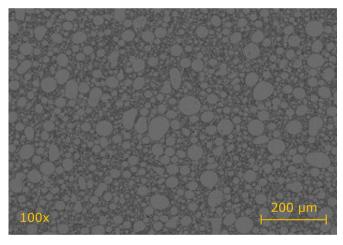

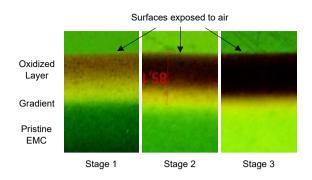

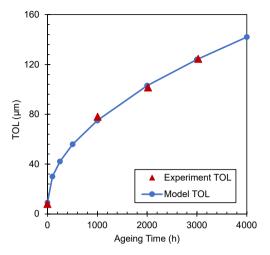

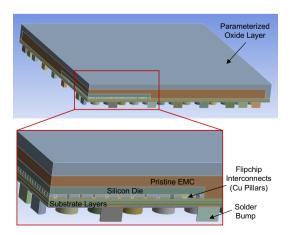

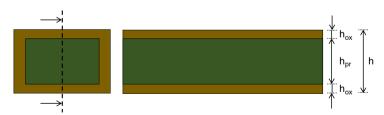

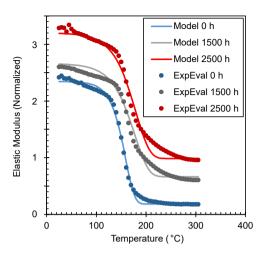

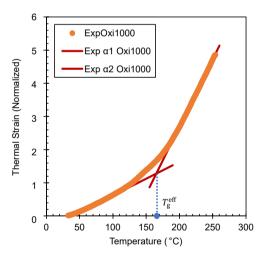

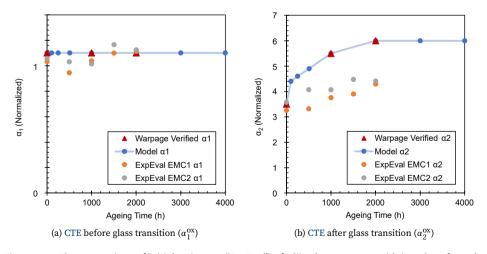

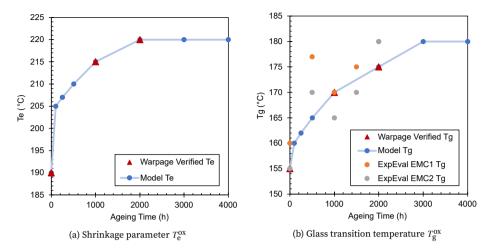

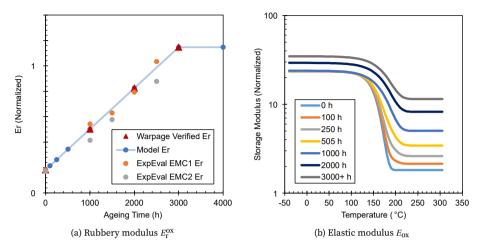

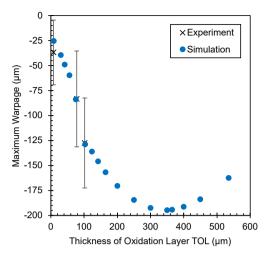

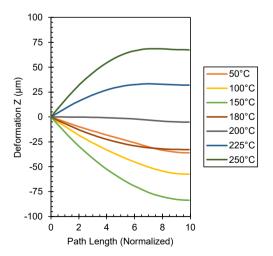

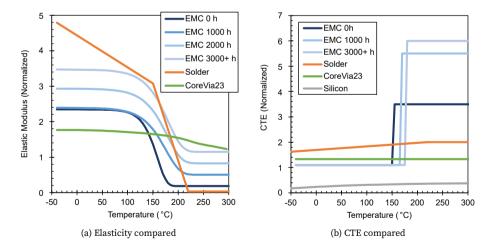

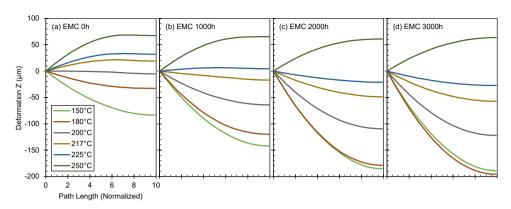

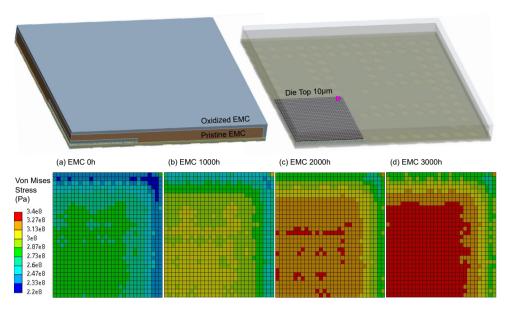

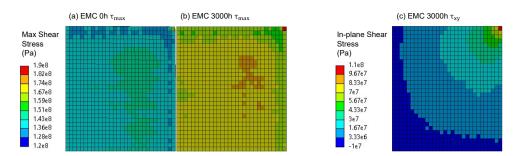

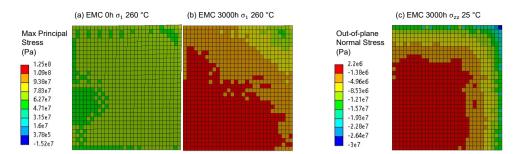

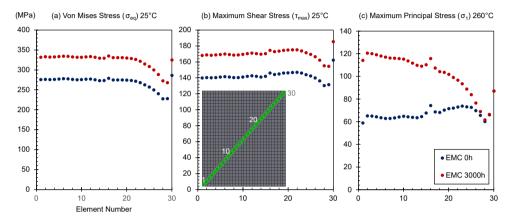

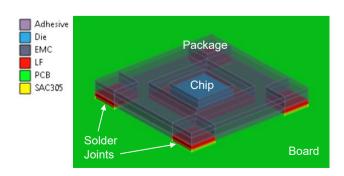

Starting with the physics-of-degradation, the thermo-oxidative ageing of Epoxy Moulding Compounds (EMC) is modelled to study its effects on the thermomechanical behaviour of an electronic package (Chapter 4). A combination of experimental characterisation and analytical methods is utilised to record the changes in linear elastic temperature-dependent mechanical properties of the oxidised EMC at different stages of thermal ageing. A six-parameter material model (viz.,  $\alpha_1^{ox}$ ,  $\alpha_2^{ox}$ ,  $T_g^{ox}$ ,  $T_g^{ox}$ ,  $E_g^{ox}$ ,  $E_r^{ox}$ ) is constructed to reflect the changes in between the known ageing stages, and a continuously updated Digital Twin Instance (DTI) of a Flipchip BGA package is prepared. The prepared DTI is utilised to predict mechanical stresses along the top surface of the silicon die, which showed up to 40% increase in the maximum principal stress ( $\sigma_1$ ) after 3000 h of ageing. The effect of thermomechanical degradation on the acceleration of EMC-die interface delamination is also discussed.

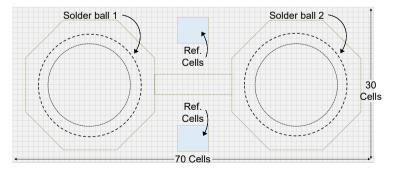

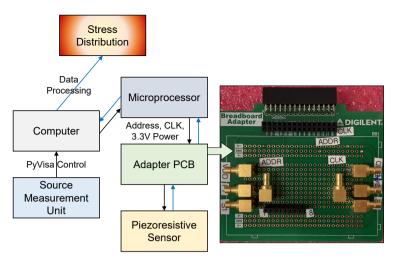

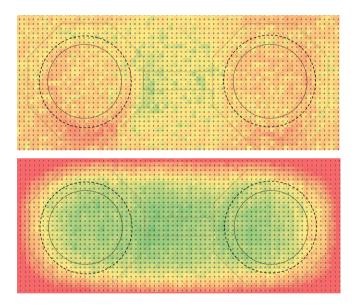

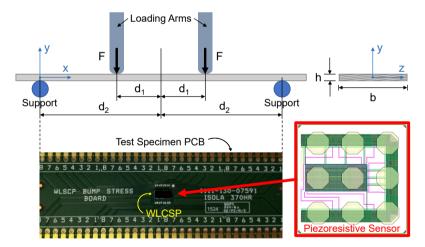

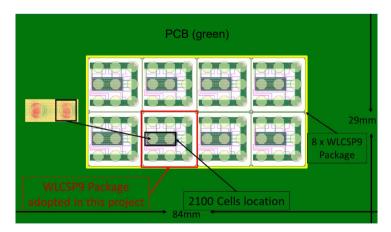

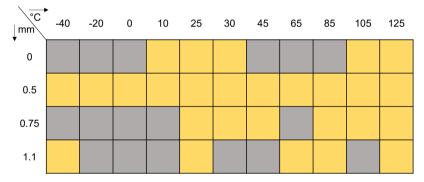

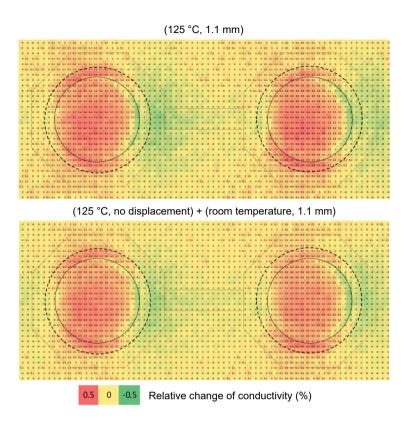

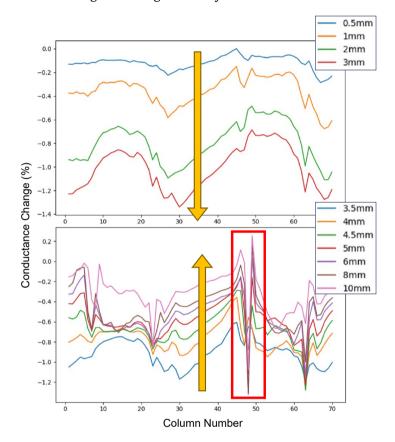

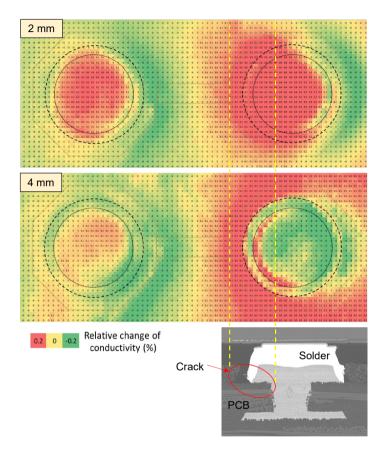

The in-situ monitoring aspect within the data-driven branch of the DT framework is demonstrated using a solder joint degradation monitoring setup (Chapter 5). A Wafer-Level Chip-Scale Package (WLCSP) housing a piezoresistive sensor with a high spatial resolution ( $70\times30$  cells of size  $10~\mu\text{m}\times10~\mu\text{m}$  each) is surface-mounted on a PCB. An efficient algorithm is developed to achieve a much faster full-readout under 5 min. A design of experiments involving static mechanical load with a four-point bending setup (maximum bending displacement of up to 1.1 mm) coupled with temperature variation (from -40~C to 125~C) is carried out to record piezoresistive data due to the deformation of the package-on-PCB assembly. The measured change in resistance is able to capture the concentrated stress patterns in the regions around the solder joints (*i.e.*, the potential location of failure). Moreover, the sensor is able to detect a crack (*i.e.*, the failure mode) resulting from the static mechanical load.

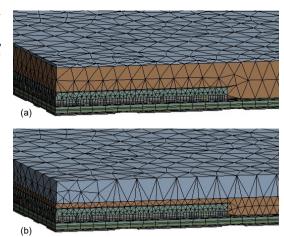

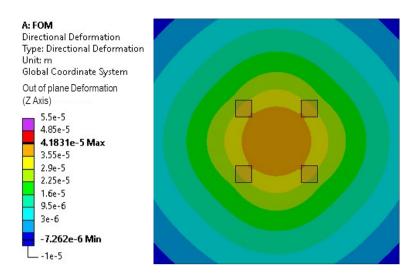

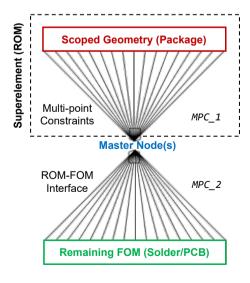

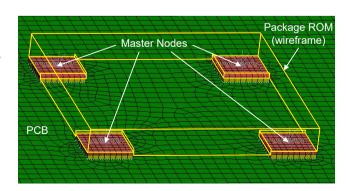

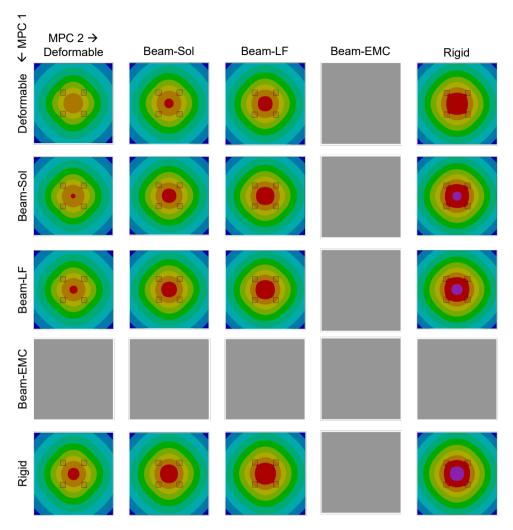

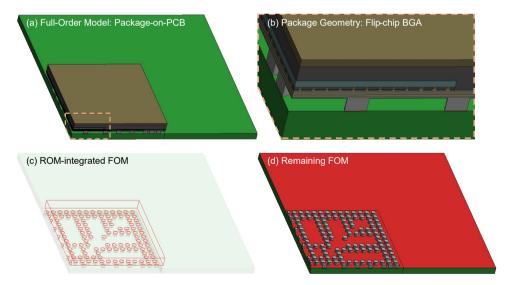

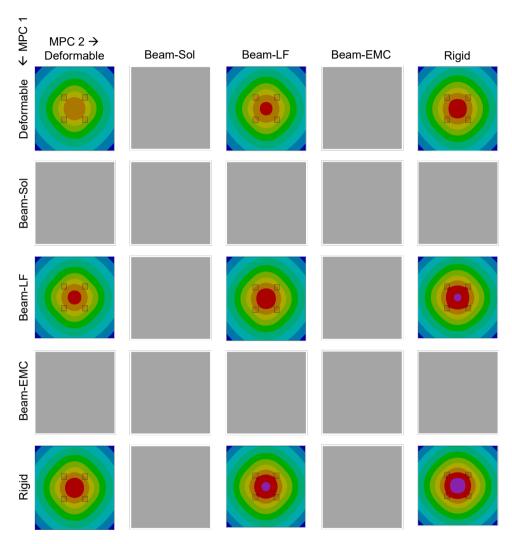

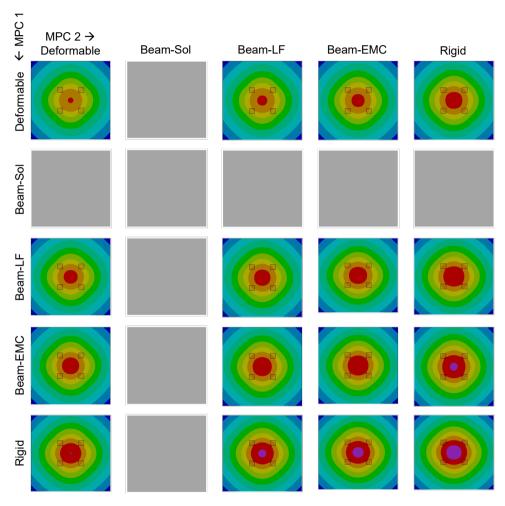

Another important aspect of the DT framework is hybrid modelling, which combines the physics-based and data-driven approaches. This is demonstrated by preparing thermomechanical Reduced-Order Models (ROM) using the physics-based Full-order Models (FOM) to be utilised in a data-driven approach (Chapter 6). A superelement (SE)-based ROM of a simpler test package (with 4 solder joints) is prepared and is used to study the effect of several combinations of the definitions and locations

Summary xvii

of the ROM-FOM interface. A benchmarking against the Finite Element-based FOM shows more than one optimal combination for the accuracy and computational efforts, as well as the dependency on the thermomechanical properties of the materials involved in the ROM-FOM interface. The SE-based approach is then utilised on the thermomechanically aged (3000 h) Flipchip BGA package with a much more complex geometry and a larger 27×27 solder joint array, and its implications on the accuracy and efficiency of the ROM-integrated FOM are studied.

In the end, conclusions are drawn based on the obtained results from the aforementioned demonstrators (Chapter 7). An outlook of the feasibility and complexity of implementing a fully functional Digital Twin framework for PHM of microelectronic components and systems is also discussed. Finally, recommendations are provided for further work in the future.

## SAMENVATTING

Elektronische componenten worden steeds meer geïntegreerd in een verscheidenheid aan toepassingen, producten en industrieën en worden er een essentieel onderdeel van. In sommige gevallen zijn ze verantwoordelijk voor het afhandelen van kritieke taken (e.g., het perceptiesysteem bij autonoom rijden) en in sommige worden ze blootgesteld aan moeilijke omgevingen (e.g., verhoogde temperaturen). Het betrouwbaar functioneren van elektronica is dus belangrijker dan ooit tevoren. Traditionele betrouwbaarheidskwalificatiemethoden zijn gebaseerd op de testen in specificatiehandleidingen en handboeken. Hoewel ze nog steeds vaak naar wordt verwezen, hebben ze weinig betekenis in deze tijd.

Nieuwe methoden voor betrouwbaarheidsschatting zijn ontstaan en zijn de afgelopen zes decennia behoorlijk geëvolueerd. Toch worden ze geconfronteerd met de beperking om alleen een collectief overzicht te krijgen van storingen van batchgebaseerde experimentele testen. In werkelijkheid is het vaak zo dat identieke elektronische componenten niet-identieke operatie-omstandigheden en omgevingsbelastingen ervaren en dus een variatie in hun levensduur hebben. Het verkrijgen van individuele, componentspecifieke inzichten is dus cruciaal bij de overgang van een fysica-van-falen (physics-of-failure) naar een fysica-van-degradatie (physics-of-degradation)-benadering voor betrouwbaarheid. Het implementeren van Prognostics and Health Management (PHM) voor elektronische componenten is een veelbelovende manier om deze uitdaging aan te gaan. Het aantonen van deze aanpak met behulp van een op Digital Twin gebaseerd werkwijze is het primaire doel van dit proefschrift.

Eerst wordt een algemeen kader voor PHM opgesteld (Chapter 1) en worden de bouwstenen daarvan besproken. Vervolgens wordt een systematisch overzicht gemaakt van de term 'Digital Twin' en de stand van de techniek ervan gepresenteerd (Chapter 2). Er wordt een nieuwe, uitgebreidere en toch algemenere definitie van een Digital Twin (DT) voorbereid. Bestaande DT-architectuurmodellen worden geanalyseerd en een nieuw model met twee takken wordt geïntroduceerd, dat twee belangrijke technieken bevat, viz., op fysica gebaseerde en datagestuurde modellering. In een volledige DT-implementatie die beide modelleringsbenaderingen omvat, kunnen zowel een cloud-gebaseerde (externe) computer als een edge-gebaseerde

XX SAMENVATTING

(gelokaliseerde) computerinfrastructuur met verschillende capaciteiten worden gebruikt. Er zijn drie fasen van het implementeren van Digital Twins binnen de levenscyclus van een product — Digital Twin Prototype (DTP), Digital Twin Instance (DTI) en Digital Twin Aggregate (DTA) — die geleidelijk verschuift van een *cloud*-dominante naar *edge*-dominante implementatie.

Vervolgens wordt de basis gelegd voor de op fysica gebaseerde tak (Chapter 3) door zich te verdiepen in verpakkingsmaterialen voor elektronica en bijbehorende verouderingseffecten en afbraakmechanismen als gevolg van de drie dominante stressfactoren — temperatuur, vochtigheid en mechanische trillingen. Twee veelgebruikte verpakkingsgeassocieerde mechanische faalmechanismen, *viz.*, delaminering en soldeervermoeidheid, worden geïdentificeerd. Verder worden gespecialiseerde hardwarevereisten voor een *edge*-gebaseerde, datagestuurde (*i.e.*, een DTA) DT-implementatie onderzocht. Elk hoofdstuk hierna is gewijd aan het demonstreren van een of meer puzzelstukjes van de twee vertakte DT-werkwijze voor PHM.

Beginnend met de *physics-of-degradation*, wordt de thermooxidatieve veroudering van Epoxy Moulding Compounds (EMC) gemodelleerd om de effecten ervan op het thermomechanische gedrag van een elektronisch pakket te bestuderen (Chapter 4). Een combinatie van experimentele karakterisering en analytische methoden wordt gebruikt om de veranderingen in lineaire elastische temperatuurafhankelijke mechanische eigenschappen van de geoxideerde EMC in verschillende stadia van thermische veroudering vast te leggen. Een materiaalmodel met zes parameters (viz.,  $\alpha_1^{ox}$ ,  $\alpha_2^{ox}$ ,  $T_g^{ox}$ ,  $T_g^{ox}$ ,  $E_g^{ox}$ ,  $E_r^{ox}$ ) is geconstrueerd om de veranderingen tussen de bekende verouderde stadia weer te geven, en een continu bijgewerkte Digital Twin Instance (DTI) van het Flipchip BGA-pakket wordt voorbereid. De voorbereide DTI wordt gebruikt om de mechanische spanningen langs het bovenoppervlak van de siliciumlaag ( $silicon\ die$ ) te voorspellen, die tot 40% toename van  $\sigma_1$  vertoonde na 3000 h veroudering. Het effect van thermomechanische afbraak op de versnelling van de EMC-die raakvlak-delaminering wordt ook besproken.

Het in-situ monitoren aspect binnen de datagestuurde tak van het DT-werkwijze wordt gedemonstreerd met behulp van een opstelling voor het monitoren van de degradatie van soldeerverbindingen (Chapter 5). Een Wafer-level Chip-scale Package (WLCSP) met een piëzoresistieve sensor met een hoge ruimtelijke resolutie ( $70\times30$  cellen van grootte  $10~\mu\text{m}\times10~\mu\text{m}$  elk) is gemonteerd op het oppervlak van een PCB. Een efficiënt algoritme is ontwikkeld om een veel snellere volledige uitlezing te bereiken binnen 5 min. Een ontwerp van experimenten met statische mechanische belasting met een vierpunts buigopstelling (maximale verplaatsing tot 1.1~mm) gekoppeld aan temperatuurvariatie (van -40~°C tot 125~°C) wordt uitgevoerd om piëzoresistieve gegevens op te nemen als gevolg van de vervorming van de

Samenvatting xxi

verpakking-op-PCB assemblage. De gemeten verandering in weerstand is in staat om de geconcentreerde spanningspatronen in het gebied rond de soldeerverbindingen (*i.e.*, de potentiële storingslocatie) vast te leggen. Bovendien kan de sensor een scheur (*i.e.*, de storingsmodus) detecteren als gevolg van de zuivere statische mechanische belasting.

Een ander belangrijk aspect van de DT-werkwijze is hybride modellering, die de op fysica gebaseerde en datagestuurde benaderingen combineert. Dit wordt aangetoond door het voorbereiden van thermomechanische Reduced-Order Models (ROM) met behulp van de op fysica gebaseerde Full-order Models (FOM) die worden gebruikt in een datagestuurde aanpak (Chapter 6). Een op superelement (SE) gebaseerde ROM van een eenvoudiger testpakket (met 4 soldeerverbindingen) wordt voorbereid en gebruikt om het effect van verschillende combinaties van de definities en locaties van de ROM-FOM-interface te bestuderen. Een vergelijking met de op Finite Element gebaseerde FOM toont meer dan één optimale combinatie voor de nauwkeurigheid en computationele inspanningen, evenals de afhankeliikheid van de thermomechanische eigenschappen van de materialen die betrokken zijn bij de ROM-FOM interface. De SE-gebaseerde aanpak wordt vervolgens gebruikt op het thermomechanisch verouderde (3000 h) Flipchip BGA-pakket met een veel complexere geometrie en een grotere 27×27 soldeerverbindingsreeks De implicaties van een complexere geometrie voor de nauwkeurigheid en efficiëntie van de ROM-geïntegreerde FOM worden ook bestudeerd.

Uiteindelijk worden conclusies getrokken op basis van de verkregen resultaten van de bovengenoemde demonstratoren (Chapter 7). Een vooruitblik op de haalbaarheid en complexiteit van het implementeren van een volledige functionele Digital Twinwerkwijze voor PHM van micro-elektronische componenten en systemen wordt ook besproken. Ten slotte worden aanbevelingen voor toekomstig werk verstrekt.

# 1

## **INTRODUCTION**

Parts of this chapter have been published in *Frontiers in Electronics* (2025) [1], in *MDPI Electronics* (2024) [2], in the proceedings of *ESREL Conference* (2023) [3], and submitted to *IEEE Transactions on Intelligent Vehicles* [4].

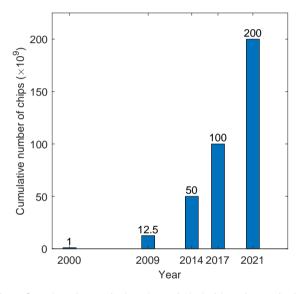

### 1.1. ELECTRONIFICATION OF INDUSTRIES

Electronics play a vital role in most modern devices and systems. During the second decade of the 21<sup>st</sup> century, the number of electronic devices used in various applications has seen tremendous growth. Figure 1.1 shows the number of chips made just based on the *ARM* architecture, which is a widely-used Instruction Set Architecture (ISA) for consumer electronic products [5]. By the year 2021, about 200 billion *ARM*-based chips in total were shipped, from which the first 1 billion during 1991-2002, about 100 billion cumulative by 2017, and an additional 100 billion in just the following five years [6–8].

Figure 1.1: Number of semiconductor devices (cumulative) shipped over the last 20 years [6–8]. The chart only includes *ARM*-based chips, which are primarily used in low-power consumer electronic applications. The exponential growth in the last few years indicates the trend of rapid electronification.

At the core of this phenomenon is the 'digitalisation' or 'electronification' of industries over the last few decades. This has been accelerated by newly emerging Information Technology (IT), the incorporation of more and more electronics (*e.g.*, sensors) into conventional products/systems, and the integration of computer-aided, software-based technologies into traditional industries. Internet of Things (IoT)-enabled smart-home products such as Artificial Intelligence (AI)-powered smart speakers, thermostats and home appliances, *etc.*, are classic examples of the latter. Other well-known examples are the daily-use gadgets such as laptop/tablet computers, smartphones, and smartwatches, which consist mostly of electronic components. In addition to consumer electronics, such growth is also reflected in several other industries, such as manufacturing, automotive, and healthcare [9, 10].

### **USE CASE: AUTOMOTIVE ELECTRONICS**

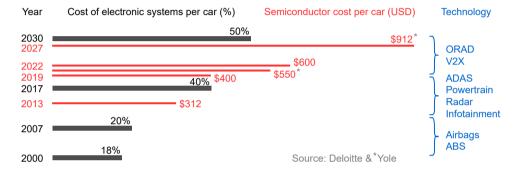

An automobile is no exception to the rapid adoption of electronics. According to a 2019 report by *Deloitte* [10], electronic systems in a modern car constitute about 35 % of its total cost, and it is expected to have close to 50 % share by the year 2030. Automotive electronics are responsible for primary functions such as engine control, transmission control, and suspension control, as well as advanced functions such as telematics (for location tracking and navigation) and cloud connectivity. Figure 1.2 gives an overview of the cost of automotive electronics and the technology deployment over time.

Figure 1.2: Overview of the cost of automotive electronics and the technology deployment over time. The grey bars represent the cost of electronic systems as a percentage (%) of total car cost. The red bars indicate the semiconductor cost per car in United States Dollars (\$). Values beyond the year 2022 are predictions. The recorded data and estimated values are sourced from [10] and [11]. The blue text lists the technology deployed in the past and on the roadmap of Society of Automobile Engineers (SAE) [12]. The abbreviations stand for On-Road Automated Driving (ORAD); Vehicle to 'X' (V2X) connectivity including Vehicle to Vehicle (V2V); Advanced Driver Assistance Systems (ADAS); Anti-lock Braking System (ABS).

The automotive industry is progressing towards developing a framework for Electric Connected and Automated (ECA) vehicles, and the development of necessary automotive Electronic Components and Systems (ECS) is driven by three major trends – electrification, connectivity, and automation [13]. The SAE defines six levels of autonomous driving vehicles (*i.e.*, SAE L0–L5), starting with 'level 0' with no automation capabilities and going up to 'level 5' with full automation [14]. The development of a homologation framework for levels 3 to 5 (*i.e.*, SAE L3–L5) is in progress, with a forecast for the number of SAE L3 and L4 vehicles to grow from 0.2 million newly-registered units in the year 2020 to 24 million in the year 2030 [15].

Every step towards a higher level of automation requires additional electronics (*e.g.*, sensors and control units) and their integration into various functions of a car. From the year 2016–2022, a sizeable growth is observed in the revenue of 2 subcategories of the automotive semiconductor revenue – Advanced Driver Assistance Systems (ADAS) and In-Vehicle Infotainment (IVI) system – aimed primarily at

providing safety and comforts. In terms of revenue, infotainment showed a jump from ~\$6 billion to ~\$9 billion, while ADAS from ~\$3 billion to ~\$12 billion [10]. According to *Yole Group* [11], the semiconductor cost per car is predicted to go from \$550 today to about \$912 by the year 2027. These trends are quite significant in terms of user safety, technological development, and economics.

Thus, automotive electronic systems are, and will remain, a crucial component of an automobile concerning its functionality, cost, and overall safety. To address this, many projects are created under multinational joint undertakings such as European Union (EU)-level funding programs for research and development. The project 'ArchitectECA2030' envisions providing "a harmonized pan European validation framework enabling mission oriented validation of ECS for ECA vehicles from SAE L3 to L5 to improve reliability, robustness, safety and traceability" [16].