#### **Graphene-Based Computing** Nanoribbon Logic Gates & Circuits

Jiang, Y.

10.4233/uuid:f5496a9d-cd10-4279-b5f0-052cd8a53fc6

**Publication date**

**Document Version** Final published version

Citation (APA)

Jiang, Y. (2020). Graphene-Based Computing: Nanoribbon Logic Gates & Circuits. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:f5496a9d-cd10-4279-b5f0-052cd8a53fc6

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

### Graphene-Based Computing: Nanoribbon Logic Gates & Circuits

#### Dissertation

for the purpose of obtaining the degree of doctor

at Delft University of Technology

by the authority of the Rector Magnificus prof.dr.ir. T.H.J.J. van der Hagen

chair of the Board for Doctorates

to be defended publicly on

Thursday 3 December 2020 at 18:00 o'clock by

#### Yande JIANG

Master of Engineering in Electronic Science and Technology, National University of Defense Technology, China born in Guilin, China This dissertation has been approved by the promotors:

promotor: dr. S.D. Cotofana copromotor: dr. ir. J.S.S.M. Wong,

#### Composition of the doctoral committee:

Rector Magnificus, chairman

Dr. S.D. Cotofana, Delft University of Technology, promotor Dr.ir. J.S.S.M. Wong, Delft University of Technology, copromotor

*Independent members:*

Prof.dr.ir. W.A. Serdijn Delft University of Technology

Prof.dr. K.G.W. Goossens Eindhoven University of Technology, The Netherlands

Prof. A. Rubio Polytechnic University of Catalonia, Spain Prof. G. Ch. Sirakoulis Democritus University of Thrace, Greece

Dr. Y. Chi

Prof.dr.ir. S. Hamdioui

National University of Defense Technology, China

Delft University of Technology, reserve member

This research was financially supported by China Scholarship Council (CSC)

Keywords: Graphene, Graphene Nanoribbon, Graphene-based Computing,

Carbon-Nanoelectronics, Graphene-based Gate, Graphene-based

Circuit

Printed by: Ipskamp Printing, the Netherlands

#### Copyright © 2020 by Yande JIANG

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without written permission of the author.

ISBN 978-94-6384-176-4

An electronic version of this dissertation is available at http://repository.tudelft.nl/.

#### Dedicated to

my supervisors, family and country

#### **Abstract**

As CMOS feature size is reaching atomic dimensions, unjustifiable static power, reliability, and economic implications are exacerbating, thus prompting for research on new materials, devices, and/or computation paradigms. Within this context, Graphene Nanoribbons (GNRs), owing to graphene's excellent electronic properties, may serve as basic structures for carbon-based nanoelectronics. However, the graphene intrinsic energy bandgap absence hinders GNR-based devices and circuits implementation. As a result, en route to graphene-based logic circuits, finding a way to open a sizable energy bandgap, externally control GNR's conduction, and construct reliable high-performance graphene-based gates are the main desideratum. To this end, first, we propose a GNR-based structure (building block) by extending it with additional top gates and back gate while considering five GNR shapes with zigzag edges in order to open a sizeable bandgap, and further investigate GNR geometry and contact topology influence on its conductance and current characteristics. Second, we present a methodology of encoding the desired Boolean logic transfer function into the GNR electrical characteristics, i.e., conduction maps, and then evaluate the effect of  $V_{\rm DD}$  variation on GNR conductance. Moreover, we find a proper external electric mean (e.g., top gates and back gates) to control the GNR behavior. Third, we develop a parameterized Verilog-A SPICEcompatible GNR model based on Non-Equilibrium Green's Function (NEGF)-Landauer formalism that builds upon an accurate physics formalization, which enables to symbiotically exploit accurate physics results from Matlab Simulink and optimized SPICE circuit solvers (e.g., Spectre, HSPICE). Subsequently, we construct graphene-based Boolean gates by means of two complementary GNRs, and design a GNR-based 1-bit Full Adder and a SRAM cell. Finally, we extend the NEGF-Landauer simulation framework with the self-consistent Born approximation while taking into account the temperature-induced phenomena in GNR electron transport, i.e., electron-phonon interactions for both optical and acoustic phonons, and further explore the graphene-based gates performance robustness under temperature variations.

# Table of Contents

| Ab  | stract                                  |                     | 5                                                                          |

|-----|-----------------------------------------|---------------------|----------------------------------------------------------------------------|

| Tal | ble of                                  | Contents            | i                                                                          |

| Lis | t of Ta                                 | ables               | iii                                                                        |

| Lis | t of Fi                                 | gures               | v                                                                          |

| Lis | t of A                                  | cronyms and Symbols | ix                                                                         |

| 1   | 1.1<br>1.2<br>1.3<br>1.4<br>1.5         |                     | 1<br>2<br>5<br>7<br>10<br>15                                               |

| 2   | Topo<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Introduction        | 17<br>18<br>20<br>22<br>24<br>25<br>27<br>28<br>30<br>31<br>34<br>36<br>38 |

| 3   | Grap 3.1 3.2 3.3 3.4                    | Introduction        | 44<br>46<br>49<br>49<br>50<br>52                                           |

|     |              | 3.4.1 Propagation Delay, Area, and Power                                                                                             | 53<br>57<br>59<br>62 |

|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|     | 3.5          | Conclusion                                                                                                                           | 66                   |

| 4   | Para<br>Mode | meterized Verilog-A SPICE-compatible Graphene Nanoribbon                                                                             | 67                   |

|     | 4.1<br>4.2   | Introduction                                                                                                                         | 67<br>68<br>69<br>69 |

|     | 4.3<br>4.4   | Simulation Results                                                                                                                   | 71<br>74             |

| 5   |              | -based Complementary Gates                                                                                                           | 75                   |

|     | 5.1          | Introduction                                                                                                                         | 76                   |

|     | 5.2<br>5.3   | Complementary GNR Pair-based Boolean Gates Simulation Setup                                                                          | 78<br>81             |

|     | 3.3          | 5.3.1 GNR Conduction Computation                                                                                                     | 81                   |

|     |              | 5.3.2 Mixed SPICE-Simulink Simulation                                                                                                | 82                   |

|     |              | 5.3.3 GNR Gates Simulation                                                                                                           | 82                   |

|     | 5.4          | GNR Boolean Gates                                                                                                                    | 83                   |

|     |              | 5.4.1 1- and 2-input GNR Gates                                                                                                       | 83                   |

|     |              | 5.4.2 3-input GNR Gates                                                                                                              | 87                   |

|     | 5.5          | Basic GNR Circuits                                                                                                                   | 91<br>91             |

|     |              | 5.5.2 SRAM Cell                                                                                                                      | 93                   |

|     | 5.6          | Conclusion                                                                                                                           | 95                   |

| 6   | CNB          | Gates Performance Robustness under Temperature Variations .                                                                          | 99                   |

| U   | 6.1          | Introduction                                                                                                                         | 99                   |

|     | 6.2          | Simulation Framework                                                                                                                 | 100                  |

|     |              | 6.2.1 Phonon Limited GNR Transport Computation Model .                                                                               | 100                  |

|     |              | 6.2.2 GNR Gate SPICE Simulation                                                                                                      | 104                  |

|     | 6.3          | Simulation Results                                                                                                                   | 104                  |

|     |              | <ul><li>6.3.1 GNR Dimensions and Topologies of Boolean Gates</li><li>6.3.2 GNR Gates Performance Robustness under Tempera-</li></ul> | 105                  |

|     | 6.4          | ture Variations                                                                                                                      | 105<br>108           |

| 7   | Cond         | clusions and Future Work                                                                                                             | 109                  |

|     | 7.1<br>7.2   | Summary                                                                                                                              | 109<br>112           |

| Bib | liogra       | aphy                                                                                                                                 | 115                  |

| Saı | menva        | atting                                                                                                                               | 123                  |

| Lis | t of P       | ublications                                                                                                                          | 125                  |

| Cu  | rriculı      | um Vitae                                                                                                                             | 127                  |

# List of Tables

| 2.1  | Feasible Constriction Angles                                        | 32  |

|------|---------------------------------------------------------------------|-----|

| 2.2  | Top Gate Voltage Contact Dimensions for the Best Current            |     |

|      | Characteristics at $V_d = 0.2 \mathrm{V}.$                          | 40  |

| 3.1  | 2-input Butterfly GNR Topologies                                    | 49  |

| 3.2  | 3-input Butterfly GNR Topologies                                    | 52  |

| 3.3  | 2-input GNRs and 7 nm CMOS Gates Propagation Delay,                 | 53  |

| 2.4  | Area, and Power.                                                    | 33  |

| 3.4  | 3-input GNRs and 7 nm CMOS Gates Propagation Delay, Area, and Power | 55  |

| 3.5  | 2-input GNR and pn-Junctions Gate Delays                            | 57  |

| 3.6  | 2-input AND GNR Topology vs $V_{\rm DD}$                            | 61  |

| 3.7  | 2-input NOR GNR Topology vs $V_{DD}$                                | 61  |

| 3.8  | Conductance of Ideal and Incomplete 2-input AND GNR                 | 65  |

| 5.1  | Complementary Boolean Gate GNR Dimensions                           | 84  |

| 5.2  | 1- and 2-input Gates Delay, Area, and Power                         | 86  |

| 5.3  | 3-input GNR Gate Dimensions                                         | 88  |

| 5.4  | 3-input GNR Back Gate Bias                                          | 89  |

| 5.5  | 3-input GNR Gates Propagation Delay, Area, and Power vs             |     |

|      | 7 nm FinFET CMOS                                                    | 89  |

| 5.6  | Extended DSE Delay, Area, and Power                                 | 90  |

| 5.7  | Dimensions of GNR 1-bit Full Adder Gates                            | 92  |

| 5.8  | FA Gates GNR Back Gate Bias                                         | 92  |

| 5.9  | FA Delay, Area and Power Consumption                                | 93  |

| 5.10 | GNR SRAM Component Dimensions                                       | 97  |

| 5.11 | SRAM Delay, Area and Power Consumption                              | 97  |

| 6.1  | Complementary Boolean gate GNR dimensions and topologies.           | 105 |

| 6.2  | GNR gates output voltage levels, delay, and power consump-          |     |

|      | tion variation (%) vs. temperature                                  | 106 |

|      |                                                                     |     |

$6.3 \quad GNR \ gates \ worst \ case \ propagation \ delay \ and \ power \ consumption \ vs. \ room \ temperature \ CMOS \ FinFET \ 7 \ nm \ counterparts. \ . \ 107$

# List of Figures

| 1.1  | Graphene Crystal and its Chemical Bonds                                                                     | 1  |

|------|-------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Graphene Zero Bandgap vs. Semiconductor Bandgap                                                             | 7  |

| 2.1  | Zig-Zag GNR Configuration                                                                                   | 20 |

| 2.2  | General Simulation Model                                                                                    | 21 |

| 2.3  | Rectangular GNR and Unit Cell                                                                               | 22 |

| 2.4  | Non-rectangular GNRs                                                                                        | 23 |

| 2.5  | 3D GNR Structure [1]                                                                                        | 24 |

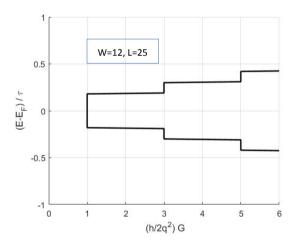

| 2.6  | R-GNR Conductance $G$ vs. Energy $E$                                                                        | 25 |

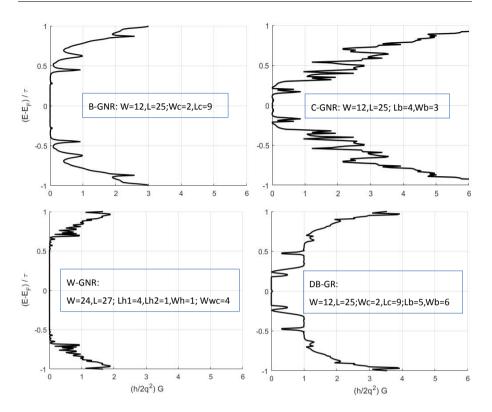

| 2.7  | GNR Conductance vs. Energy                                                                                  | 26 |

| 2.8  | Conductance vs. Energy for R-GNR with Geometry $W = 12$ ,                                                   |    |

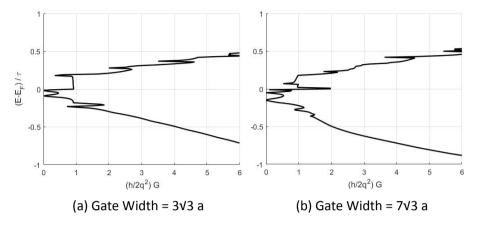

|      | $L=25,V_{ m g}=1{ m V},V_{ m back}=0{ m V}$ and Different Gate Widthes                                      | 27 |

| 2.9  | Conductance with Energy for R-GNR with Geometry $W =$                                                       |    |

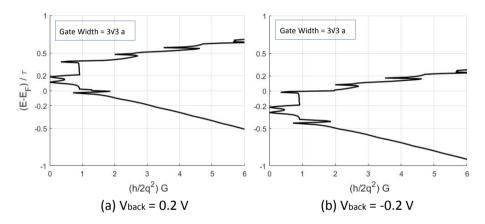

|      | $12, L=25$ and $V_{ m g}=1{ m V}, V_{ m back}=\pm 0.2{ m V}.$                                               | 27 |

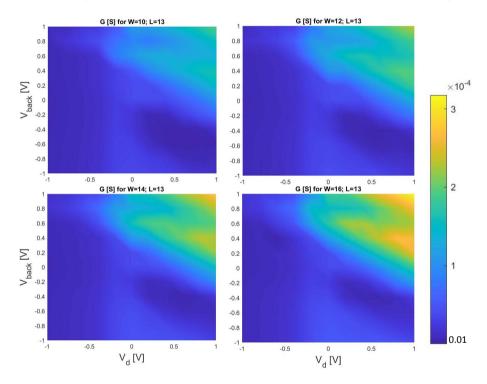

| 2.10 | G vs. $V_{\text{back}}$ vs. $V_{\text{d}}$ for $W = 10, 12, 14, 16. \dots$                                  | 28 |

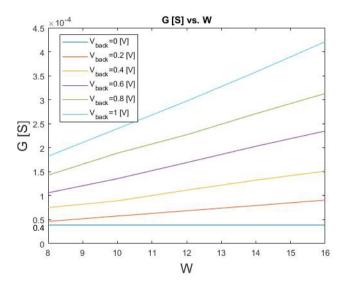

| 2.11 | $G$ vs. $W$ with Variable $V_{\text{back}}$                                                                 | 29 |

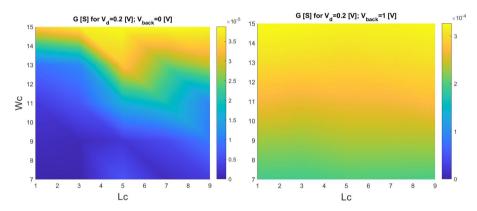

| 2.12 | $G$ vs. $L_{\rm c}$ and $W_{\rm c}$ for $V_{\rm d}=0.2{\rm V}, W=18$ at $V_{\rm back}=0{\rm V}$ and         |    |

|      | 1 V                                                                                                         | 30 |

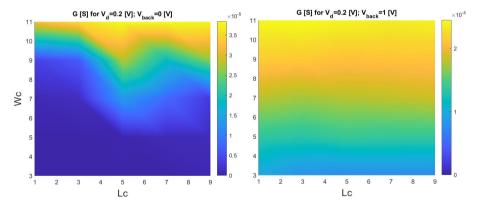

| 2.13 | $G$ vs. $L_{\rm c}$ and $W_{\rm c}$ for $V_{\rm d}=0.2{\rm V}$ , $W=14$ at $V_{\rm back}=0{\rm V}$ and      |    |

|      | 1 V                                                                                                         | 30 |

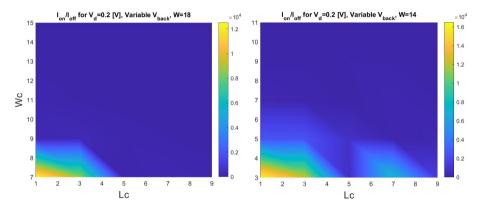

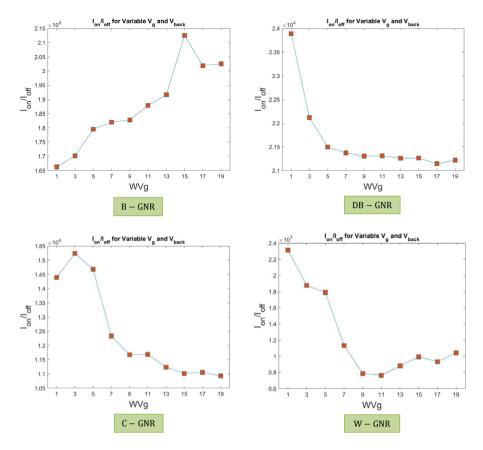

| 2.14 | $I_{\rm on}/I_{\rm off}$ vs. $L_{\rm c}$ and $W_{\rm c}$ for $V_{\rm d}=0.2{ m V}$ , Variable $V_{ m back}$ | 31 |

| 2.15 | B-GNR Oblique Line Realization                                                                              | 32 |

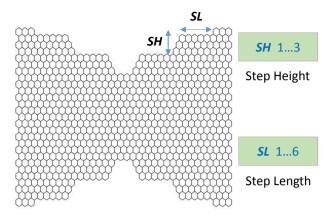

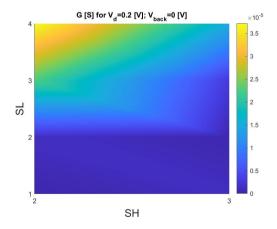

| 2.16 | $G$ vs. $SH$ and $SL$ for $V_{\rm d}=0.2{ m V},V_{ m back}=0{ m V}.$                                        | 32 |

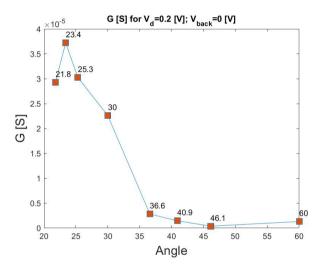

| 2.17 | $G$ vs. Constriction Angle for $V_{\rm d}=0.2{\rm V},V_{\rm back}=0{\rm V}.$                                | 33 |

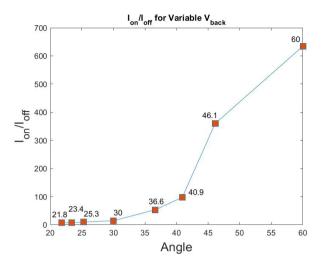

| 2.18 | $I_{\rm on}/I_{\rm off}$ vs. Angle for $V_{\rm d}=0.2{ m V}$ and Variable $V_{ m back}$                     | 34 |

| 2.19 | Initial Nanoribbon Configuration and Bump Dimensions                                                        | 34 |

| 2.20 | $G$ vs. Bump Dimensions for Different $V_{\text{back}}$                                                     | 35 |

| 2.21 | $I_{\rm on}/I_{\rm off}$ vs. Bump Dimensions for $V_{\rm d}=0.2{ m V.}$                                     | 35 |

| 2.22 | Initial Butterfly GNR Configurations                                                                        | 36 |

| 2.23 | DB-GNR Dimensions                                                                                           | 36 |

| 2.24 | G vs. $W_b$ vs. $L_b$ for $W = 14$ , $V_d = 0.2 \text{ V}$ and $V_{back} = 0 \text{ V}$ or                      |    |

|------|-----------------------------------------------------------------------------------------------------------------|----|

|      | 1V                                                                                                              | 37 |

| 2.25 | $G$ vs. $W_b$ vs. $L_b$ for $W = 18$ , $V_d = 0.2 \text{ V}$ and $V_{back} = 0 \text{ V}$ or                    | 27 |

| 2.26 | 1V                                                                                                              | 37 |

|      | $I_{\rm on}/I_{\rm off}$ vs. $W_{\rm b}$ vs. $L_{\rm b}$ for $V_{\rm d}=0.2{\rm V}$ and Variable $V_{\rm back}$ | 38 |

|      | Examples of Top Gate Contact Width                                                                              | 39 |

| 2.28 | Conductance vs. Top Gate and Back Gate Voltages for B-                                                          |    |

|      | GNR with $WV_g = 7$ and 13                                                                                      | 40 |

| 2.29 | $I_{ m on}/I_{ m off}$ vs. Top Gate Contact Width $WV_{ m g}$                                                   | 41 |

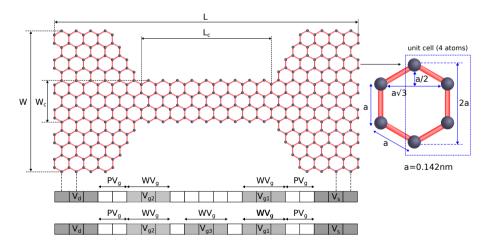

| 3.1  | Butterfly Graphene Nanoribbon (GNR)                                                                             | 46 |

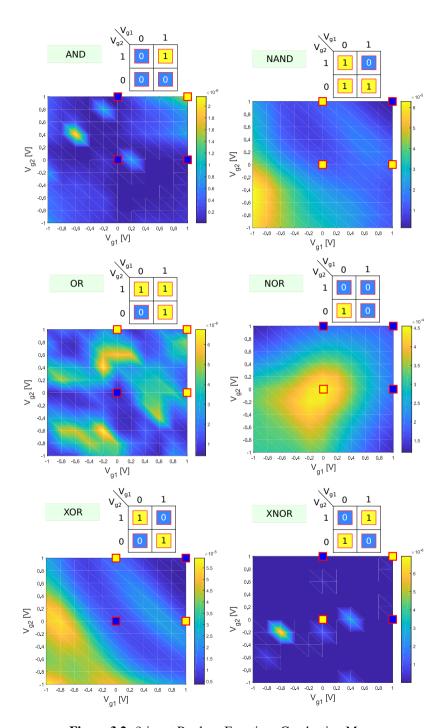

| 3.2  | 2-input Boolean Functions Conduction Maps                                                                       | 48 |

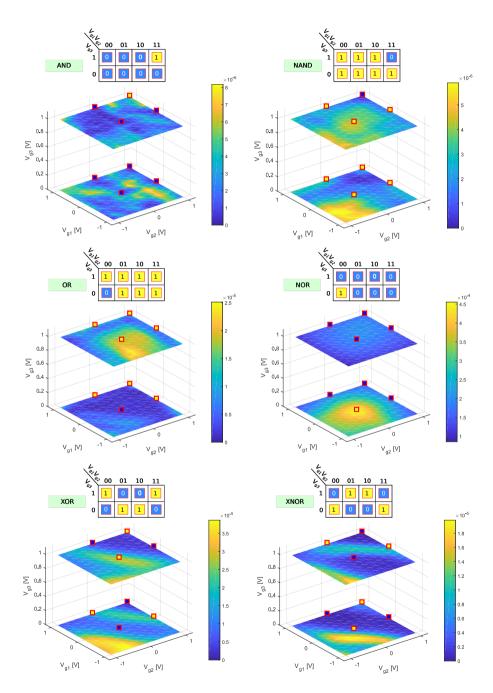

| 3.3  | 3-input Boolean Functions Conduction Maps                                                                       | 51 |

| 3.4  | Top Gate Capacitance                                                                                            | 54 |

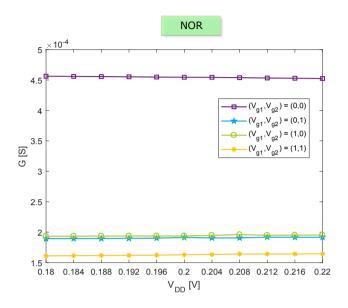

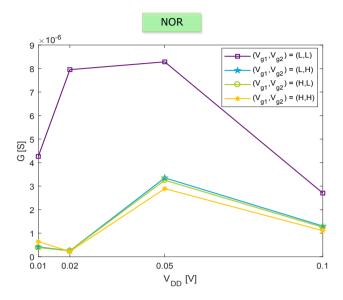

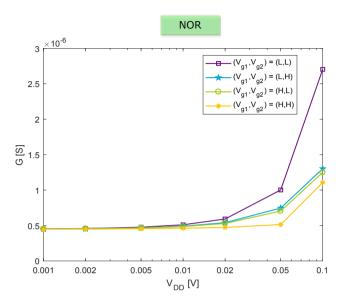

| 3.5  | 2-input NOR GNR $G$ Stability to $V_{\rm DD}$ Variations                                                        | 58 |

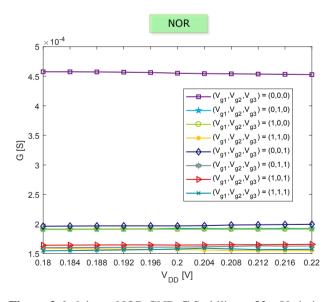

| 3.6  | 3-input NOR GNR $G$ Stability to $V_{\rm DD}$ Variations                                                        | 58 |

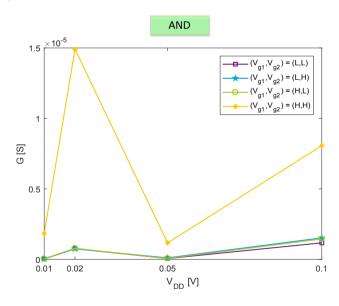

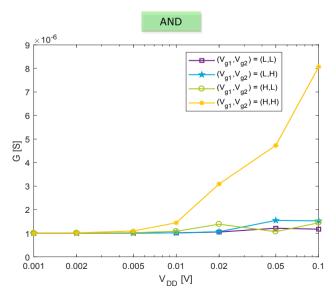

| 3.7  | 2-input AND GNR Conductance vs $V_{\rm DD}$                                                                     | 59 |

| 3.8  | 2-input NOR GNR Conductance vs $V_{\rm DD}$                                                                     | 60 |

| 3.9  | $0.1\mathrm{V}$ 2-input AND GNR Conductance vs $V_{DD}$                                                         | 61 |

| 3.10 | $0.1\mathrm{V}$ 2-input NOR GNR Conductance vs $V_{DD}$                                                         | 62 |

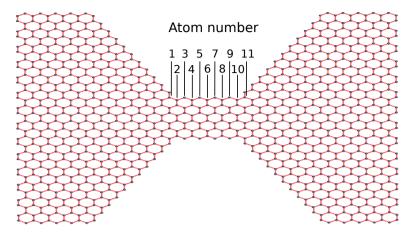

| 3.11 | Missing Atoms on the Constriction Upper Edge                                                                    | 64 |

| 4.1  | Trapezoidal QPC Topology and Associated SPICE Symbol                                                            | 69 |

| 4.2  | Cadence-Simulink-Based Verilog-A GNR Simulation Frame-                                                          |    |

|      | work                                                                                                            | 70 |

| 4.3  | One GNR-based Circuit Simulation Setup                                                                          | 71 |

| 4.4  | One GNR-based Circuit Simulation Results                                                                        | 72 |

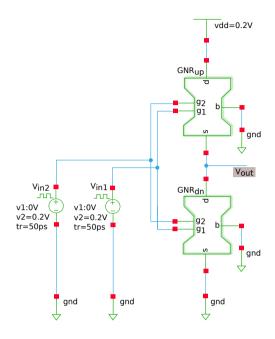

| 4.5  | GNR-based XOR Gate Simulation Setup                                                                             | 73 |

| 4.6  | GNR-based XOR Gate Simulation Results                                                                           | 73 |

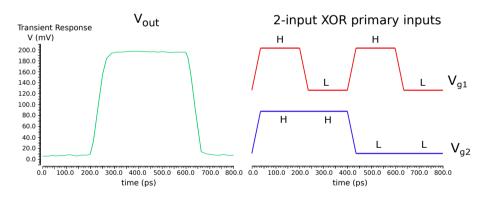

| 5.1  | 2-input XOR Conductance Map                                                                                     | 79 |

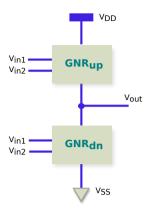

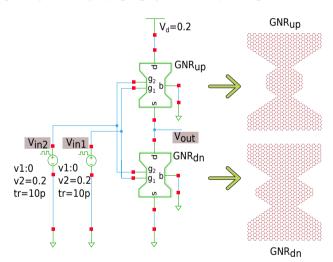

| 5.2  | GNR Boolean Gate with Complementary GNRs                                                                        | 80 |

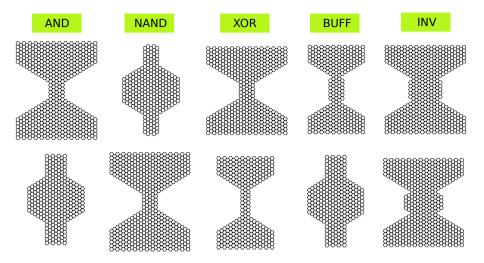

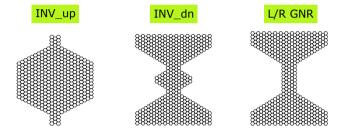

| 5.3  | GNR Shapes for Boolean Gates                                                                                    | 81 |

| 5.4  | $GNR_{up}$ (top row) and $GNR_{dn}$ (bottom row)                                                                | 83 |

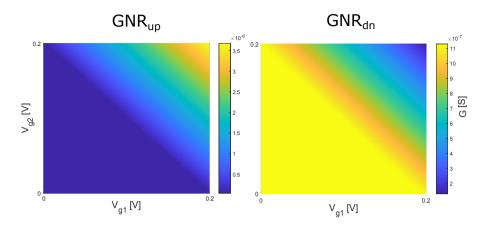

| 5.5  | AND Gate GNR Conductance Maps                                                                                   | 85 |

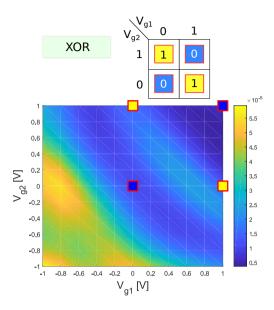

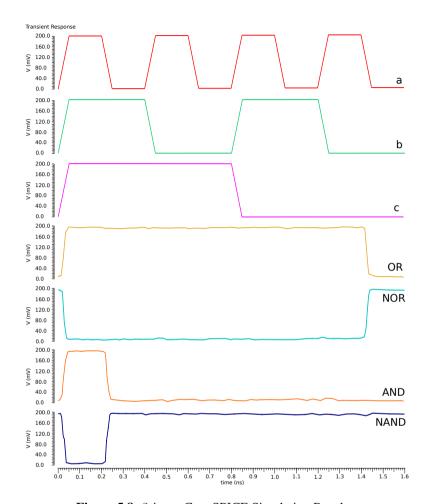

| 5.6  | GNR Gate SPICE Simulation Results                                                                               | 86 |

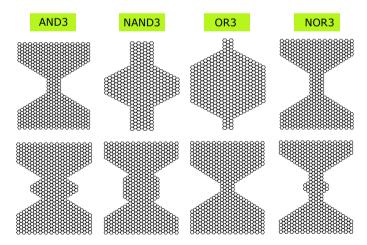

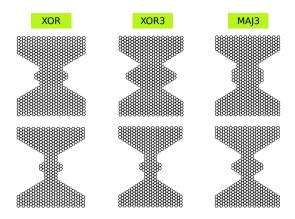

| 5.7  | 3-input Gate GNR Shapes                                                                                         | 87 |

| 5.8  | 3-input Gate SPICE Simulation Results                                                                           | 90 |

| 5.9  | 1-bit Full Adder                                                                                                | 92 |

| 5.10 | FA GNR <sub>up</sub> (top row) and GNR <sub>dn</sub> (bottom row)                                               | 93 |

| 5.11 | GNR FA SPICE Simulation Results                      | 94  |

|------|------------------------------------------------------|-----|

| 5.12 | SRAM Cell                                            | 95  |

| 5.13 | SRAM Cell GNR Topologies                             | 95  |

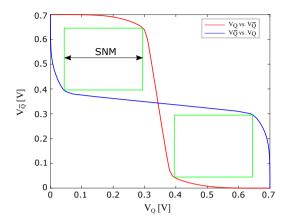

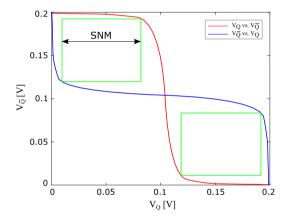

| 5.14 | 6T SRAM SNM Diagram                                  | 96  |

| 5.15 | GNR SRAM SNM Diagram                                 | 96  |

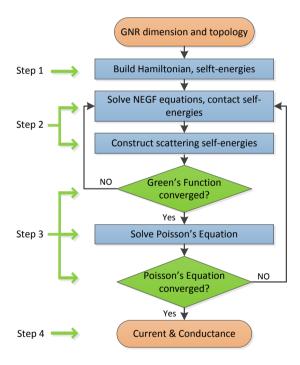

| 6.1  | GNR Simulation Flow based on NEGF-Landauer Formalism |     |

|      | with Phonon Scattering                               | 101 |

| 6.2  | Generic GNR Gate SPICE Circuit (left) and NAND2 GNRs |     |

|      | Dimensions (right)                                   | 104 |

| 6.3  | GNR NAND2 Gate Eye Diagram (% variations are between |     |

|      | min and max values)                                  | 107 |

### List of Acronyms and Symbols

HOPG Highly Ordered Pyrolytic Graphite

CVD Chemical Vapor Deposition

STT Spin-Transfer Torque SOT Spin-Orbit Torque GNR Graphene Nanoribbon GQD Graphene Quantum Dot

MOSFET Metal Oxide Semiconductor FET

FET Field Effect Transistor

G-FET Graphene based Field-effect Transistor

G-TFET Graphene Tunnel Field-effect Transistor

DSE Design Space Exploration

QPC Quantum Point Contact

FA Full Adder

NEGF Non-Equilibrium Green Function

R-GNR Rectangular Graphene Nanoribbon

B-GNR Butterfly Graphene Nanoribbon

C-GNR Camel Graphene Nanoribbon

W-GNR Waterfall Graphene Nanoribbon

DB-GNR Double Butterfly Graphene Nanoribbon

Z-GNR Zigzag Graphene Nanoribbon A-GNR Armchair Graphene Nanoribbon

TB Tight Binding DOS Density of State

GNRFET Graphene Nanoribbon Field-Effect Transistor

SB-GNRFET Schottky-Barrier-Type GNRFET

GNR-TFET Graphene Nanoribbon Tunnel Field-Effect Transistor

SRAM Static Random-Access Memory

ECC Error Correcting Code

LDPC Low Density Parity Code

RCA Ripple Carry Adder

SNM Static Noise Margin

3D Three-dimensional

TSV Through Silicon Via

MRAM Magnetic Random Access Memory

MTJ Magnetic Tunnel Junction TMR Tunnel Magnetoresistance

# 1

#### Introduction

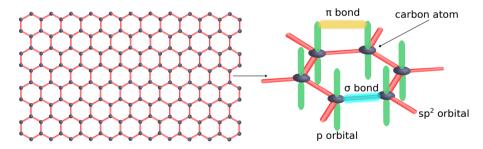

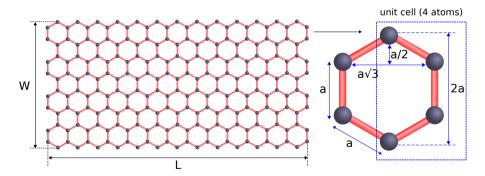

As CMOS scaling is approaching atomic feature size, the high power density and leakage, low reliability and yield, and increasing IC production costs are exacerbating, thus prompting for research and development on new materials, devices, architectures, and computation paradigms. One of the post Silicon front runners is graphene, which is a two-dimensional carbon allotrope where carbon atoms occupy the hexagon vertices and are arranged in a honeycomb lattice, as illustrated in Figure 1.1. The carbon atom forms a very strong  $\sigma$  bond

Figure 1.1: Graphene Crystal and its Chemical Bonds.

with its three neighbors via  $sp^2$  hybridization, and the remaining p orbital constructs a  $\pi$  bond with adjacent carbon atoms [2], [3]. As a result, on one hand, the formed extended  $\pi$ -electron system in the honeycomb lattice dominates graphene's electronic conduction, and determines its electrical properties, e.g., (i) very high electron mobility at room temperature  $(2 \times 10^5 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}, 200 \times \text{higher than Si})$  [4], (ii) high thermal conductivity  $(5.30 \times 10^3 \text{ W/mK}, 10 \times \text{larger than copper})$  [5], (iii) high electron velocity near the K (Dirac) points  $(1.1 \times 10^6 \text{ m/s})$  [6], (iv) high current density  $(10^8 \text{A/cm}^2, 5 \text{ orders})$  of magnitude larger than copper interconnects) [7], (v) ballistic carrier transport (> 1  $\mu$ m mean free paths) [8], (vi) good electrical conductivity, (vii)

tunable electronic properties, which makes it attractive for high-speed electronic circuit applications [9], [10], [11]. On the other hand, the strength of graphene  $sp^2$  bonds determine its chemical stability and mechanical properties, e.g., (i) thinness ( $< 10\,\mathrm{nm}$ ) [12], (ii) stiffness, strength, and toughness (a high Young's Modulus (or Elastic Modulus) of 1 Tpa [13], [14],  $2\times$  larger than silicon carbide), (iii) zero effective mass, (iv) stackable, (v) impermeable to gases [15], (vi) flexible [16], (vii) optically transparent [17], which make it a strong candidate for, e.g., electromechanical systems, strain sensors, supercapacitors, hydrogen storage, and flexible devices. These unique and outstanding electrical and mechanical properties of graphene have attracted tremendous academia and industry attention, and investigations on graphene fabrication methods and graphene-based applications have exponentially increased [18], [19], [20], [21], [22].

#### 1.1 Graphene Synthesis and Applications

Since graphene was first unambiguously produced, identified, and reported in the celebrated paper by K. S. Novoselov and A. K. Geim [23], its fabrication enjoyed a research popularity surge as mass high-quality graphene production techniques are crucial for graphene potential exploitation. Several methods have been developed to synthesize graphene, and generally speaking, there are three main monolayer graphene fabrication approaches. (i) Thermal decomposition of SiC wafers, also called this way epitaxial growth that can deliver large-area epitaxial graphene via Si sublimation and C atoms segregation on graphitic layers [24]. The advantage of epitaxially grown graphene for nanoscale electronic applications resides in its planar two-dimensional structure, which allows for traditional top-down lithography and processing technologies [25]. However, this method is complicated, time-consuming, and expensive, due to SiC processing difficulty. (ii) Mechanical exfoliation from, e.g., Highly Ordered Pyrolytic Graphite (HOPG), and transfer onto substrates, such as SiO2 [26]. Mechanical exfoliation generates high-quality pristine graphene via a repetitive stick and peel process, which avoids the long processing time, high temperature, and metal catalyst required the epitaxial growth method [27]. However, mechanical exfoliation is labor intensive and limited into small (micro-scale) areas, which makes it rather inappropriate for large-scale fabrication and processing. (iii) Chemical exfoliation, e.g., Chemical Vapor Deposition (CVD) of polycrystalline graphene [28], chemical reduction of fewlayered graphene oxide [29], [30], and wet-chemistry synthesis methods, e.g.,

electrochemical, graphite oxide, and liquid-phase exfoliation [31], [32], [33]. CVD and chemical reduction method offer high-quality graphene sheets in large quantity, and wet-chemistry has the advantage to produce graphene with excellent solubility that is fundamental for solution process device applications. In addition, liquid-phase exfoliation method makes graphene attractive for specific applications like printed and flexible electronics, supercapacitors, and electromagnetic shielding. However, the chemical exfoliation causes a permanent  $sp^2$  structural damage in graphene [34], which changes pristine graphene's electrochemical behavior and degrades graphene electrical properties [35], [36]. Although current graphene manufacturing methods have their own limitations, they laid manufacturing foundations of future graphene-based devices and applications and fundamental breakthrough are still expected due to graphene research community expected endeavours.

Due to its remarkable properties and vast carbon availability, a wide range of graphene-based applications, e.g., spintronics, photonics and optoelectronics, sensors, energy storage and conversion, biomedical applications, electronics, are starting to get momentum. Owing to its room-temperature spin transport property (long spin-diffusion lengths of µm scale), adjastable carrier concentration, and high electronic mobility, graphene has very good potential of serving as spin channel material of spintronic devices [37], [38]. Graphene spintronics attempts take advantage of the large electron spin freedom degree in order to create a novel form of information storage and associated logic gates for high-speed and low-power operations. While new graphene based spin-based memories, e.g., Spin-Transfer Torque (STT) and Spin-Orbit Torque (SOT) MRAMs, are appealing [39] further experimental and theoretical exploration of, e.g., spin injection and transport, spin orbit coupling and relaxation, defect-induced magnetic moments, in order to enable the practical ralization of graphene-based spin logic devices.

Moreover, its optical transparency, flexibility, and environmental stability, encouraged graphene-based photonics and optoelectronics application research, ranging from solar cells and light emitting devices, to photo-detectors, ultrafast lasers and touch screens [40], [41]. Specifically, an organic solar cell with solution-processed graphene transparent electrodes has been proposed with a film thickness smaller than 20 nm and optical transmittance bigger than 80% [42]. A graphene-based broadband optical modulator with high modulation speed, small area, and big optical bandwidth has been developed at Berkeley to provide support for on-chip optical communication [43]. A chipintegrated graphene-based photodetector with ultra-fast response and broad spectral bandwidth has been introduced, which achieves a photo-responsivity

of  $> 0.1 \, \mathrm{AW^{-1}}$  and a response rate of 20GHz [44].

Graphene is also quite attractive for the fabrication of various sensor types, e.g., chemical and electrochemical, mass and strain, optical, electric field [45], [46], and for the detection of toxic, explosive, and flammable gases, and oxygen depletion in industry and fire-fighting. A high-performance low-power carbon dioxide  $(CO_2)$  gas sensor has been reported [47], with high-sensitivity, fast response, and short recovery time. The sensing mechanism relies on the fact that graphene conductance linearly increases with the concentration of the  $CO_2$  adsorbed on the graphene surface. A real-time multi-channel graphene biosensor has been proposed [48], which enables reliable measurement of concentration-dependent DNA hybridization kinetics and affinity, and exhibits low cost and high throughput when compared to biosensors based on nanowire field-effect transistors. However, despite of its great promise, the road towards achieving commercial graphene-based sensors is still hindered by the limited availability of high quality and wafer-scale graphene.

Due to its ease of synthesis and functionalization graphene is also exhibiting promising potential in energy storage and conversion applications, e.g., lithium ion batteries, fuel cells, and supercapacitors. Specifically, [49] reported a novel graphene aerogel assisted method for the preparation of metal oxide nanoparticles with excellent capacitance and rate capability for supercapacitor implementations and [50] an advanced energy-storage system, "all-graphene battery", which can deliver a power density of  $6450\,\mathrm{W/kg}$  while retaining an energy density of  $225\,\mathrm{Wh/kg}$ . Again, several key issues, e.g., effectively increasing electrode conductivity and enlarging specific surface area, remain to be addressed en route to the realization of practical graphene-based devices able to outperform conventional counterparts.

Graphene has also captured an increasing interest for biomedical applications, including biosensing and tissue engineering through graphene-quenched fluorescence, gene and drug delivery, graphene-enhanced cell differentiation and cell growth control, cancer therapy, biological imaging, and graphene-assisted laser desorption/ionization for mass spectrometry [51], [52], [53]. A nanographene oxide for cellular imaging and drug delivery has been developed [54], owning promising properties of large specific surface area, low cost and noncovalent interactions with aromatic drug molecules. Moreover, [55] proposed an enhanced stem cell growth and differentiation method based on graphene and graphene oxide, which provides accelerated stem cell growing due to graphene's strong non-covalent binding abilities. Those initial but very significant contributions on graphene-based biomedical and biological devices

suggest a promising future for graphene utilization in clinical assays and advanced clinical tools.

Apart of the previously mentioned applications, graphene electronics is most likely the most attractive one due to graphene's unique and remarkable electrical properties, e.g., ballistic electron transport, which make it a strong Si challenger for digital logic implementations. Its excellent electrical properties make it a promising material for high-performance, low-power, nano-scale carbon-based circuits, which are expected to play an important role in the advancement of semiconductor technology [56], [57], [58], [59], [60].

Nevertheless, the road towards graphene based nanoelectronics development is not that straightforward, mostly due to its zero bandgap and semi-metallic behavior [61]. One way to alleviate this problem is to process graphene into Graphene Nanoribbons (GNRs) [62], or Graphene Quantum Dots (GQDs) [63] and to this end GNRs have been utilized as conduction channels into graphene based Metal Oxide Semiconductor FET (MOSFET) equivalents, e.g., Graphene based Field-effect Transistor (G-FET) [64], [65], Graphene Tunnel Field-effect Transistor (G-TFET) [66], [67]. The availability of graphene MOSFETs and interconnects (graphene can exhibit metallic behavior) potentially opens the avenue towards designing and implementing all-graphene integrated circuits based on the current CMOS Boolean algebra based paradigm. However, graphene-based electronic devices based on the traditional MOS-FET operation principle suffer from fundamental issues, e.g., low ON/OFF current ratio, high off-state current, high contact resistance, graphene rough edges (defects). Therefore, the development of commercial graphene-based devices and circuits requires breakthroughs for: (i) opening a distinct and welldefined graphene bandgap without degrading its electronic properties, (ii) enlarging device ON/OFF current ratios, and (iii) fabricating graphene ribbons with well-defined widths and clean edges.

#### 1.2 Graphene Nanoribbon Logic Circuit Challenges

Graphene Nanoribbons (GNRs) are narrow graphene strips exhibiting semiconducting behavior through quantum confinement. Moreover, if produced into quasi-one-dimensional structures with sub-10 nm narrow widths and welldefiend (atomically smooth) edges, they are predicted to present a nanoribbon width and edge structure adjustable band gap, which is essential for the design of graphene-based transistors operating at room-temperature with high electron mobility, outstanding switching speed, and ballistic transport [68], [69]. However, there are a number of design and manufacturing related issues that need to be addressed, en route to GNR-based logic circuits.

From manufacturing perspective the main hurdle is the unavailability of a cost-effective, reliable large-scale (wafer-scale) GNR fabrication method to allow the mass-production of graphene structures with well-defined edges and highly reproducible features. Over the past few years, graphene researchers focused on GNR fabrication and several approaches have been developed, such as top-down lithographic patterning [70], [71], chemical procedures [72], and high quality grown carbon nanotubes longitudinally unzipping [73], [74]. Specifically, a fast and inexpensive approach to fabricate GNRs as narrow as 9 nm with an ON/OFF current ratio of 70 at room temperature and carrier mobility of  $300~{\rm cm^2V^{-1}s^{-1}}$  is presented in [75] and a surface-assisted synthesis method to produce atomically precise, low-edge-defect GNRs, e.g., 3-Armchair GNRs (1 hexagon width) and 6-Zigzag GNRs (6 hexagon width) is described in [76]. Such developments clearly indicate that GNR structures with well-defined dimensions and geometries and clean defect free edges can be potentially fabricated in the close future.

From the design standpoint, there are several graphene specific problems, which solutions are essential for the realization of competitive graphene based circuits and systems as follows:

- Identify the appropriate external means (e.g., voltage, magnetic field) to enable GNR conductance/behaviour control.

- Obtain distinguishable "ON" and "OFF" states, by means of GNR's conductivity manipulation while not degrading the intrinsic highly advantageous properties of graphene (e.g., extremely high charge-carrier mobility).

- ullet Open a sizeable GNR energy bandgap and achieve an  $I_{ON}/I_{OFF}$  current ratio suitable for robust operation.

- Investigate alternative design styles able to take full advantage of GNR's conductance nonlinearities.

- Ensure GNR based logic structures' input output compatibility such that they can be straightforwardly connected to form larger circuits.

This thesis aims to address and provide solutions to the previously GNR-based logic circuits design related issues.

#### 1.3 Research Questions

In this section, we formulate the research question addressed by this thesis, which in its most general form can be stated as:

• Can graphene open alternative beyond CMOS avenues towards energy effective computing despite its band-gap opening lack?

To provide an answer to this fundamental question we pursue a rather complex investigation by addressing 6 related questions, which are essential with regard to the general one.

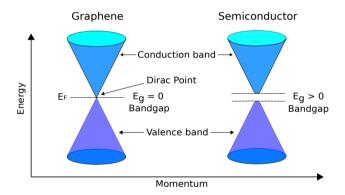

The first issue one is facing when considering graphene based computing is the fact that it is a semimetal with "zero" energy bandgap ( $E_g=0$ ) in the Fermi level ( $E_F$ ) proximity, as illustrated in Figure 1.2, which, essentially speaking, prohibits the OFF switching of graphene conduction channels in devices, such as Field Effect Transistors (FETs). Thus, a distinct bandgap ( $E_g>0$ )

**Figure 1.2:** Graphene Zero Bandgap vs. Semiconductor Bandgap.

is crucial for graphene-based devices conduction control. Generally speaking, three main avenues have been undertaken to induce graphene non-zero energy bandgap: (i) internal structure chemical modification via patterned hydrogenation [77], [78] or chemical doping [79], [80], (ii) exposure to external electro-magnetic fields by means of applying perpendicular electrical field via top gate electrodes [81], [82], and (iii) topology modifications by use of, e.g., straining [83], [84], patterning [85], [86], [24], [87], and topological imperfections [88], [89].

Nevertheless, while being able to provide an energy bandgap increase these methods negatively impact graphene charge-carrier mobility and by implication limit the achievable graphene device operation speed. Thus, on one hand, graphene high carrier mobility that potentially benefit device switching speed comes at the cost of diminished OFF switch capabilities, which results in high static power consumption, while on the other hand state-of-the-art bangap opening methods have detrimental impact on carrier mobility. This clearly indicates that in order to make graphene a strong CMOS contender in implementing Boolean algebra based digital logic (e.g., processors and computing platforms, which, to be competitive need to build upon fast and energy effective switches), further investigations on graphene electron transport and electrical properties are required. In this context, the first to be investigated question can be formulated as:

# Can we find a way to open GNR energy bandgap without compromising graphene excellent intrinsic properties, such as high carrier mobility?

Such a method ought to induce a sizeable bandgap of at least  $0.4\,\mathrm{eV}$  without degrading graphene intrinsic properties, and in the same time enable GNR conductance/behaviour control, in order to yield distinguishable "ON" and "OFF" states and an  $I_{ON}/I_{OFF}$  current ratio (in the order of  $10^6$ , which is typical for low power sub-10 nm CMOS) suitable for robust operation on GNR-based devices.

While graphene based FETs able to exhibit a certain switching behaviour have been proposed [90], [91], and can potentially be utilized to construct CMOS alike logic gates and circuits such an approach is not able to take full advantage of graphene conduction nonlinearity [92], [1]. Thus our next investigation step is focused on the investigation of GNRs' potential to provide more complex than simple switching behaviours. Thus, this gives shape to the following research question:

# Given a certain basic Boolean function can we identify a GNR topology, which conductance accurately mirrors its true table?

The basic idea behind such an approach is to embed more computation power, e.g., 2-input (N)AND, (N)OR, X(N)OR, in one single graphene device, which potentially benefits circuit area, delay, and power consumption.

One essential element for our investigations towards energy effective graphene gates and circuits is the availability of GNR circuit-level models and simulations tools able to accurately capture graphene related physical phenomena. Therefore, in order to bring graphene specific phenomena from the physics to the circuit-level and allow for graphene-based circuit design and optimizations, a fast and parameterized model appropriate for electrical, e.g., SPICE, simulations is required. Moreover, since GNRs behavior and potential benefit

in circuits are not fully comprehended, such a model should preserve the high accuracy of low-evel physical simulation methods. In view of the previous argument, the next research question formulates as:

Can we devise a model able to bring GNR specific phenomena from physics to circuit level, in such a way that accurate physics formalization and fast SPICE circuit solvers can be symbiotically exploited?

Such a model ought to build upon an accurate physical formalization and be able to symbiotically exploit accurate physics results and optimized SPICE circuit solvers (e.g., Spectre, HSPICE). Moreover, to allow for GNR gate and circuit design exploration it should be generic and has the ability to accommodate a wide range of GNR shapes and topologies as input parameters.

Equipped with bandgap opening, function mapping, and simulation methods the next investigation step focusses on the construction of energy effective GNR-based logic gates and circuits. Generally speaking, en route to such gates/circuits, there are multiple aspects which need to be taken into consideration, e.g., (i) how GNRs interact with each other when interconnected, (ii) how to combine GNRs and construct GNR-based gates/circuits which is able to perform fast and energy effective operations, (iii) how to make sure that digital GNR gates/circuits can be cascaded, i.e., achieve clean and compatible/matching gate inputs and outputs electric levels. Thus, the next to be addressed research question is:

Can GNRs be combined in order to construct fast and energy effective gates and circuits, e.g., Boolean gates, full adders, and memory cells?

The main goal inhere is to go beyond simple switching behaviour and seek gate and circuit structures able to take full advantage of the GNR potential (e.g., high electron mobility, and ballistic carrier transport) while being able to perform robust, fast, and energy effective computation.

As CMOS device dimensions are down-scaling into the sub-10nm range, temperature variations have a significant impact on devices and circuits reliability and performance, e.g., output signal integrity, propagation delay, and power consumption [93]. While for CMOS gates temperature effects have been largely investigated [94], for gates implemented with atomic-level GNRs, such effects have not been explored. Furthermore, the temperature-related electron-phonon scattering mechanisms have a significant impact on graphene electron transport behaviour and carrier mobility [95]. Moreover, even though new graphene fabrication technologies (e.g., scalable bottom-up approaches that

produce graphene by means of Chemical Vapour Deposition (CVD) [96], and on-surface synthesis methods [76]) are exceeding the precision limit of modern lithographic approach, and can manufacture atomically precise GNRs with well-defined width, e.g., 3-Armchair GNRs (1 hexagon width) and 6-Zigzag GNRs (6 hexagon width), GNR edge defects caused by non-ideal graphene fabrication process cannot be completely eliminated and may have a negative influence on GNR-based gates. In this context, we raise the following research question:

• Can we devise performance-wise, when subjected to reliability compromising conditions commonly affecting circuit operation, e.g., temperature variation and defects, GNR Boolean gates?

In answering the above research questions, this thesis explores and provides evidence related to graphene's potential in opening alternative beyond CMOS roads towards energy effective computing. Specifically, as presented in the next section, we investigate, propose, and evaluate techniques for GNR energy bandgap creation, GNR conductance modulation, GNR circuit-level modeling and simulation, and design of robust, fast, energy effective GNR-based gates and circuits.

#### 1.4 Thesis Contributions

Subsequently, we summarize the contributions we made in this thesis towards the topology-induced GNR electron transport, conductance modulation, simulation model, the design of the proposed complementary GNR-based gates and computing circuits, and investigations of GNR-based gates performance robustness under temperature variations and GNR edge defects, as follows.

• We propose a graphene structure (building block) which employs a GNR as the conducting channel, and extends it with source/drain contacts and additional top/back gates as means to modulate its conduction. Further, we explore the graphene structure's ability to open the GNR energy bandgap via GNR geometry change. The simulation results show that by means of GNR geometry carving, we are able to derive a sizeable energy bandgap, e.g., butterfly GNR and waterfall GNR obtain wider energy bandgap values of 0.4 eV and 0.7 eV, when compared to other methods such as periodic modulation of the graphene lattice via patterned adsorption of atomic hydrogen (i.e., an obtained bandgap is 0.4 eV) and molecular doping (i.e., this approach results in a bandgap from 0.19 eV

- to  $0.54\,\mathrm{eV}$ ). Thus, to some extent, we address the issue of GNR energy bandgap lack, which suggests GNR's potential as a basic building block for future carbon-based electronic circuits and applications.

- We investigate various GNR geometries and contact topologies influence on the GNR-based structure's conductance and current characteristics by means of the NEGF-Landauer formalism. The simulation results exhibit that the GNR width has a remarkable impact on GNR conductance, while length has little effect on conductance. For butterfly GNR configuration, the narrow and short constriction channel is more efficient to obtain a high current ratio, up to  $2.1 \times 10^4$ . To account for angle between constriction channel and Drain/Source contact for butterfly GNR, the bigger angle can achieve better current ratio. In addition, longer and wider bump structure provides better current ratio, up to  $1.5 \times 10^4$  for Camel GNRs, and the bump configurations improve the current related characteristics for Double butterfly GNRs, e.g., the current ratio is up to  $2.4 \times 10^4$ . Last, we explore the ability of gate bias, top gate  $V_g$  and back gate  $V_{\text{back}}$  to control GNR conduction. The simulation results suggest the top/back gate contacts are good enough ways to modulate the GNRbased device conduction, e.g., gate contact improves current ratio up to  $2.3 \times 10^7$  for Waterfall GNRs. Thus, we can derive higher current ratio for Non-rectangular GNR, up to  $10^7$ , when compared to  $10^2$  of rectangular GNRs and  $10^6$  of traditional low-power sub- $10 \,\mathrm{nm}$  Si process.

- We present a methodology of encoding the desired Boolean logic transfer function into the graphene electrical characteristics, e.g., conduction maps, by performing a Design Space Exploration (DSE) with regard to GNR topologies and geometries. In particular, we introduce a butterfly GNR structure by augmenting the trapezoidal Quantum Point Contact (QPC) topology with two top gates such that we can modulate its conductance via external voltages. Subsequently, we take into account the basic set of Boolean functions (INV, BUF, AND, NAND, OR, NOR, XOR, XNOR), and for each function we identify a GNR topology capable providing a conductance map (conductance G as output vs. two top gate voltages as inputs) mirroring the relative Boolean function truth table in which high G stands for logic output "1" and low G represents logic output "0". The simulation results indicate that the proposed 2input butterfly GNR-based structures operating at  $V_{\rm DD} = 0.2 \, {\rm V}$  surpass 7 nm FinFET CMOS counterparts running at  $V_{\rm DD} = 0.7 \, \rm V$  by up to 2, 2 and 4 orders of magnitude in terms of propagation delay, power consumption, and power-delay product, respectively, while requiring 2

orders of magnitude less active area. Particularly, for 3-input Boolean function, the proposed GNR-based approach proves to be even more effective, i.e., up to 3, 2, and 4 orders of magnitude in terms of propagation delay, power consumption, and power-delay product, respectively. Furthermore, the proposed method is less sensitive to gate fan-in scaling, as when incrementing it from 2 to 3, the GNR structures obtain 26% and 42% variation for area and delay, respectively, while CMOS area footprint and delay increase by up to 100% and 51%, respectively. Thus, this suggests that the GNR-based sructure's excellent potential of serving as a potent candidate to replace CMOS in the future high-performance energy-effective post-Si nanoelectronics.

- We evaluate the effect of V<sub>DD</sub> variation on the GNR-based structure's conductance and delay, and further to determine V<sub>DD</sub> lower bound for proper operation. The experiments indicate the proposed GNR-based structures have a strong robustness with respect to V<sub>DD</sub> variation, e.g., the GNR conductance and delay for butterfly GNR structure that reflects NOR function, change by no more than 2% and 6%, respectively. In addition, to account for V<sub>DD</sub> lower bound value, the NOR GNR structure is able to operate even at 10 mV. Further, we explore GNR edge defects influence on butterfly GNR conductance. The simulation results reveal that rather substantial even due to one missing atom in the constriction edge, and despite the performance degradation, the GNR-based structure is still able to deliver the expected Boolean functionality. This suggests the proposed GNR-based structure potential of performing robust operations related to V<sub>DD</sub> variation and GNR edge defects.

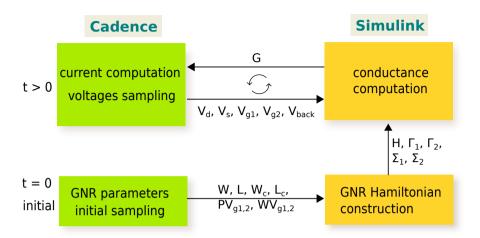

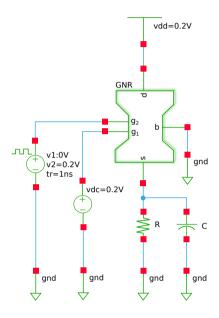

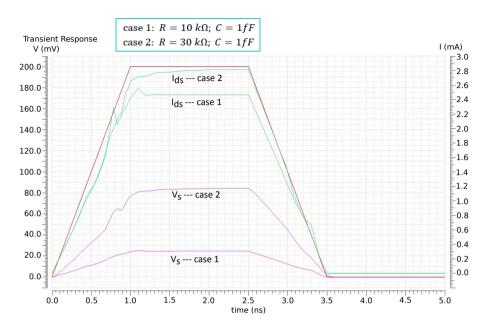

- We develop a parameterized Verilog-A SPICE-compatible generic model based on NEGF-Landauer formalism which builds upon an accurate physics formalization, by computing GNR specific variables, e.g., conductance, current, via internally called Simulink code. In this way, the proposed GNR model symbiotically exploits accurate physics results from Matlab Simulink and optimized SPICE circuit solvers (e.g., Spectre, HSPICE). This model enables parameterized electrical simulations for GNR-based structures, and preserves the physical simulation accuracy degree. In addition, the parameterized model allows for graphene-based circuit design and optimizations, which suggests the model potential of bringing GNR specific phenomena from the physics to the circuit-level by fully comprehending the GNRs behavior and potential benefit in the circuit context. In order to validate and evaluate the proposed model applicability, we take into account a simple test case circuit and

- the GNR-based 2-input XOR gate, and simulate the afferent I-V characteristic via Cadence Spectre and Matlab Simulink. The simulation results indicate that our proposed Verilog-A GNR model is accurate and enables the accurate evaluation of graphene-based circuits potential performance.

- We propose a methodology of constructing graphene-based Boolean gates and circuits. To this end, we make use of two complementary GNRs, i.e., a pull-up GNR performing the targeted Boolean function and a pull-down GNR operating its inverse Boolean function. Each GNR structure has a conduction channel made of a GNR with zigzag edges, which is situated between the drain and source contacts. The gate primary inputs voltages are applied via top gates. Subsequently, we conduct a special Design Space Exploration with regard to GNR dimensions (geometries) and gate contact topologies, while abiding to particular constraints: (i) gate output voltage values which are compatible with gate input voltage values, and (ii) high ratio between the high and low GNR conductance values, in order to identify the specific GNRs with desired functionalities. The proposed 1-, 2-, and 3-input complementary GNR gates are validated in Cadence by means of SPICE simulation which employs a Verilog-A model that calls internally a Simulink model. we obtain up to 2 orders of magnitude smaller propagation delay, 3 orders of magnitude lower power, and 2 orders of magnitude smaller active area footprint, when compared to 7nm FinFET CMOS counterparts. In addition, we prove that contrary to CMOS designs, the proposed GNR-based gates can yield effective power-delay trade-offs, at approximately the same area. We observe that this is because the graphene conductance main contributor is the nanoribbon geometry and its overall topology, rather than the effective area, thus the required active area is not proportional with gate's function complexity and fan-in. In particular, the proposed GNR gates provide clean and compatible/matching gate inputs and outputs electric levels. Therefore, the obtained results suggests the graphene-based gates surpass the CMOS counterparts in terms of delay, power and area, and have a promising potential of serving as the basic building blocks for future fast, energy-effective, high-dense carbon-based integrated circuits.

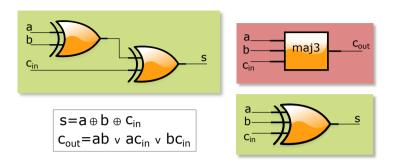

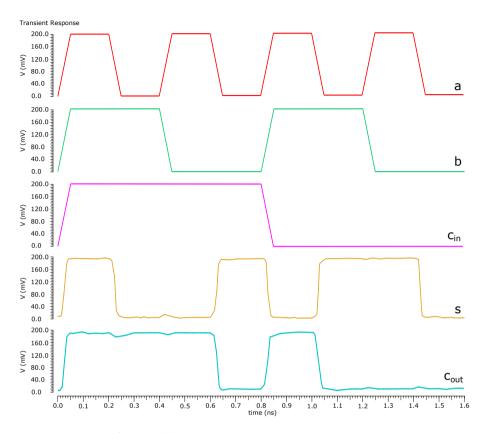

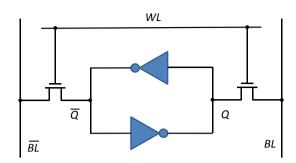

- We present a GNR-based 1-bit Full Adder (FA) and a SRAM cell, as they currently constitute the foundation for the construction of any computation system. In particular, we design a 3-input MAJORITY gate which apart of being able to directly compute FA's Carry-Out, which

surpasses the CMOS equivalent Carry-Out calculation circuit by up to 2 orders of magnitude smaller delay and 3 orders of magnitude lower power consumption, while requiring 2 orders of magnitude less area. The proposed FA design provides  $6 \times$  smaller delay, 3 orders of magnitude less power consumption, while requiring 2 orders of magnitude less area, when compared to 7nm FinFET CMOS counterpart. By consequence, a GNR-based *n*-bit Ripple Carry Adder, which performance is linear in the Carry-Out path, will be  $108 \times$  faster than a CMOS implementation. Particularly, the proposed GNR-based SRAM cell achieves a better resilience to DC noise characteristics than the CMOS equivalent, while obtaining 3.6× smaller delay, 2 orders of magnitude less power, and 1 order of magnitude less area. The proposed GNR FA and SRAM cell clearly reveal that GNR-based implementations can potentially outperform CMOS counterparts and that the proposed approach is opening a promising avenue towards future energy-effective carbon-based nanoelectronics.

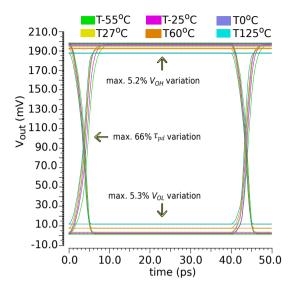

• We extend a NEGF-Landauer simulation framework with the selfconsistent Born approximation, while taking into account the temperature-induced phenomena, i.e., electron-phonon interactions for both optical and acoustic phonons, where NEGF calculations describe the electron-electron interaction and the Landauer formula provides the GNR device current and conductance. Subsequently, we evaluate the considered complementary graphene-based Boolean gates behavior under a set of temperatures from  $-55^{\circ}C$  to  $125^{\circ}C$  which covers the commercial, industrial and military ranges, and further investigate the temperature variation impact on GNR-based gates reliability and performance in terms of output signal integrity, input-to-output propagation delay, and power consumption by means of SPICE simulation in Cadence. We observe that the proposed GNR-based complementary gates are robust with respect to temperature variation, and even in the worst temperature condition (at  $125^{\circ}C$  ) outperform 7nm CMOS Fin-FET counterparts operating at room temperature, which suggesting the GNR-based gates' potential as basic building cells for future reliable, low-power, nanoscale carbon-based electronics and applications.

#### 1.5 Thesis Organization

The remainder of the thesis is structured in 6 chapters, as follows:

In **Chapter 2**, we present a graphene structure and explore its ability to open a sizeable energy bandgap via GNR geometry carving and applied top/back gate voltages. Moreover, we design five different GNR shapes with zig-zag edges, and investigate the GNR geometry influence on its conductance and current characteristics. Last, we explore the ability of gate bias (e.g., top gates and back gate) to control GNR conduction.

In Chapter 3, we consider a basic set of Boolean functions (e.g., INV, BUF, AND, NAND, OR, NOR, XOR, XNOR) and perform DSE with regard to GNR dimensions and topologies, such that for each function we find out a GNR structure which is able to provide a conductance density map reflecting the relative Boolean function truth table (e.g., high G for logic output 1, low G for logic output 0). Subsequently, we investigate the effect of  $V_{\rm DD}$  variation, and determine  $V_{\rm DD}$  lower bound value. Last, we discuss GNR fabrication status, difficulties and challenges, and investigate GNR edge defects influence on GNR conductance and performance figures of merit.

In **Chapter 4**, we develop a fast, accurate and parameterizable Verilog-A SPICE-compatible generic model for the GNR-based structure simulations, which computes the GNR conductance by means of NEGF-Landauer formalism called from within the Verilog-A code. We validate the model accuracy and versatility by utilizing Simulink assisted Cadence Spectre simulation of a simple test case GNR-based circuit and a GNR-based 2-input XOR gate.

In **Chapter 5**, we introduce a methodology of designing GNR Boolean gates by means of two complementary GNRs in which a pull-up GNR performs the targeted Boolean function and a pull-down GNR implements its inverse. Subsequently, we propose and evaluate the 1-, 2- and 3-input GNR gates via the proposed SPICE simulation. Further, we present GNR-based designs of 1-bit Full Adder (FA) and SRAM cell, as they currently constitute the foundation for the construction of any computation system.

In **Chapter 6**, we extend the NEGF-Landauer simulation framework with the self-consistent Born approximation in order to taking into account the temperature-induced phenomena, i.e., electron-phonon interactions for both optical and acoustic phonons. Next, we evaluate the graphene-based complementary Boolean gates behavior under a set of temperatures by means of SPICE simulation in Cadence, and further explore the temperature variation impact on their reliability and performance (e.g., output signal integrity, prop-

agation delay, and power consumption).

**Chapter 7** summarizes the thesis, and provides possible directions for future work.

# 2

# Topology Induced Graphene Nanoribbon Electron Transport

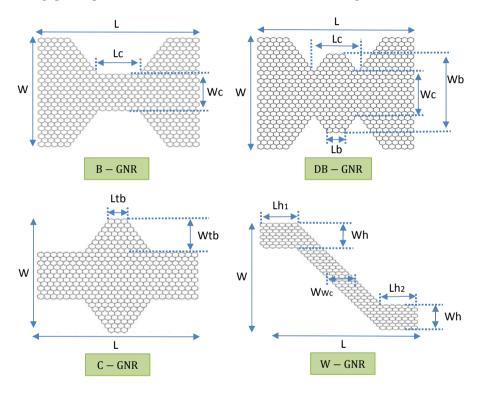

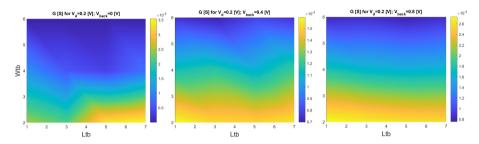

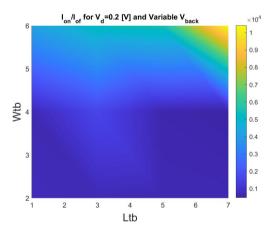

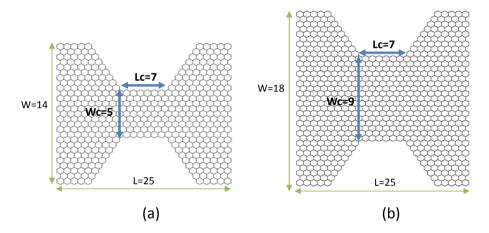

Graphene Nanoribbons (GNRs) owing to graphene's remarkable electronic properties may serve as basic blocks for post-Si nanoelectronics. En route to GNR-based logic circuits, finding a way to open GNR energy bandgap and to externally control GNR's conduction with a high current ratio  $I_{\rm on}/I_{\rm off}$  is the main desideratum. To this purpose, we design five different GNR shapes with zigzag edges (Rectangular, Butterfly, Double Butterfly, Camel, Waterfall GNRs) and build upon a GNR-based building block by extending it with additional top gate and back gate, and then investigate GNR geometry and contact topology influence on its conductance and current characteristics by means of the Non-Equilibrium Green Function (NEGF)-Landauer formalism with a 3D Poisson solver. The simulation results show that by means of GNR geometry carving, we are able to open GNR energy bandgap (e.g., Butterfly GNR and Waterfall GNR obtain wide energy bandgap 0.4 eV and 0.7 eV, respectively). For Butterfly GNR, the narrow and short constriction channel (small  $W_c$  and  $I_c$ ) is more helpful to obtain a high  $I_{on}/I_{off}$  (up to  $2.1 \times 10^4$ ). For Double Butterfly GNR and Camel GNR, the bump structures help improve  $I_{

m on}/I_{

m off}$  (up to  $2.4 \times 10^4$  and  $1.5 \times 10^4$ , respectively). Furthermore, our experiments suggest that top/back gates have a big influence on the GNR conductance and  $I_{\rm on}/I_{\rm off}$ (e.g., provide a high  $I_{\rm on}/I_{\rm off}=2.3\times10^7$  for Waterfall GNR), which suggests the applied top/back gate contacts are good methods for controlling the GNRbased device conduction, establishing GNR's potential as basic building block for future GNR-based logic circuits.

#### 2.1 Introduction

Graphene Nanoribbons(GNRs) are strong candidates for device conduction channel implementations with one caveat characteristic to pristine graphene, i.e., the absence of an intrinsic energy bandgap in the proximity of the Fermi level [97], [90], [98]. Such a bandgap is fundamental for conductivity control via electronic means (e.g., applied gate voltages), in order to create distinguishable "ON" and "OFF" states in digital electronics [99], [100], [101].

To induce a graphene energy bandgap, three main avenues have been typically undertaken: (i) chemical modification of graphene's internal structure by means of, e.g, patterned hydrogenation [77], [78], chemical doping [79], [80], (ii) multilayer graphene exposure to external electro-magnetic fields, e.g., applying perpendicular electrical field via top gate electrodes [81], [82], and (iii) topology modifications, e.g., straining [83], [84], patterning [86], [24], [87], generating topological imperfections, such as stone-wale defects [88], [89]. For example, it was demonstrated that: (i) periodic modulation of the graphene lattice via patterned adsorption of atomic hydrogen opens a bandgap of  $\approx 0.4 \text{ eV}$  [102], (ii) molecular doping results in a bandgap magnitude ranging from 0.19 eV to 0.54 eV [103], [104], [105] and (iii) bilayer graphene exhibits a non-zero bandgap, modulated by an external electric field applied perpendicularly to the graphene layers, while multilayer ( $\geq 3$  layers) graphene under electric field lacks any appreciable induced energy bandgap [106], [107].

All the above approaches with the exception of chemical modification have been proved unable to open an energy bandgap wider than 0.4 eV, which means that graphene based switches can have at most a current ratio  $I_{\rm on}/I_{\rm off}$ in the order of  $10^3$ , as opposed to  $10^6 - 10^7$  which is the typical ratio for low power nano-level Si process. Moreover, with the energy bandgap increase these methods negatively impact the charge carrier mobility. Thus, the high carrier mobility exhibited by graphene (which can greatly benefit the devices switching speed) comes at the expense of diminished ability to switch off the devices, which further results in high static power consumption figures (uncompetitive with low-power CMOS). This suggests that in order to make graphene a strong CMOS contender in implementing Boolean algebra based digital logic (e.g., processors and computing platforms, which to be competitive need to build upon fast and energy effective switches), further investigations are required. While finding a better way to open GNR's energy bandgap and to achieve a high  $I_{\rm on}/I_{\rm off}$  is the main desideratum, achieving it requires a better understanding of the relation between GNR's conduction and its shape (dimensions and geometries), which is the focus of the investigation presented

#### in this chaper.

In order to address the GNR zero energy bandgap and low current ratio problem, we build upon a graphene building block by extending it with source/drain contact and additional top/back gates as means to modulate its conduction. First, we explore the ability to open the GNR energy bandgap via GNR geometry change or through applied top/back gate voltages. The experimental results show that the method by GNR geometry change can make the GNR energy bandgap wider open (e.g., Butterfly GNR gets a wide bandgap  $0.4\,\mathrm{eV}$  and Waterfall GNR obtains a wider band gap  $0.7\,\mathrm{eV}$ ).

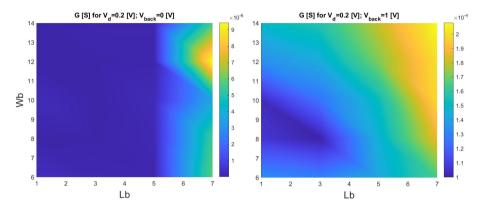

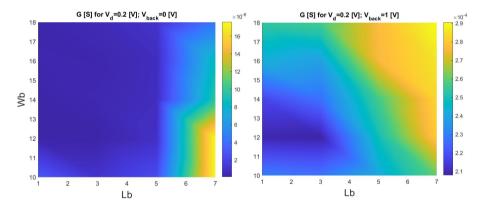

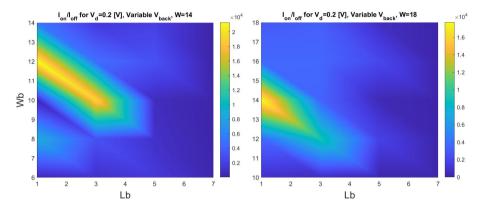

Second, we design five different GNR shapes with zig-zag edges Rectangular GNR (R-GNR), Butterfly GNR (B-GNR), Camel GNR (C-GNR), Waterfall GNR (W-GNR) and Double Butterfly GNR (DB-GNR) and investigate the GNR geometry influence on its conductance and current characteristics. To this end, we consider various GNR configurations by carving GNR geometries  $W, L, W_c, L_c, W_b, L_b$ , and derive GNR conductance and current by means of the NEGF-Landauer formalism. The experimental results suggest that W has a remarkable impact on GNR conductance G, while L has little effect on G. Normally, for B-GNR configuration, the narrow and short constriction channel (smaller  $W_c$  and  $L_c$ ) is more helpful to obtain a higher  $I_{on}/I_{off}$  (up to  $2.1 \times 10^4$ ). With respect to angle between constriction channel and Drain/Source contact for B-GNR, the bigger angle can achieve better  $I_{\rm on}/I_{\rm off}$  (e.g., GNR with  $60^{\circ}$ has  $92 \times$  bigger  $I_{\rm on}/I_{\rm off}$  than GNR with  $22^{\circ}$ ). However, for C-GNR case, longer and wider bump yields better  $I_{\rm on}/I_{\rm off}$  (up to  $1.5\times10^4$ ). Furthermore, for DB-GNR case, the bump configurations can help improve the current related characteristics (e.g.,  $I_{\rm on}/I_{\rm off}$  is up to  $2.4 \times 10^4$ ).

Last, we explore the ability of gate bias (e.g., top gate  $V_{\rm g}$  and back gate  $V_{\rm back}$ ) to control GNR conduction. The results show that  $V_{\rm back}$  modulates the Fermi level for the energy at the Dirac point, thus the back-gated GNR can enable a higher  $I_{\rm on}/I_{\rm off}$  ( $10\times$  bigger when compared to top-gate controlled GNR). In addition,  $V_{\rm g}$  has also a big impact on  $I_{\rm on}/I_{\rm off}$ . The experimental results suggest the top/back gate contacts are good methods to control the GNR-based device conduction (e.g., gate contact improves  $I_{\rm on}/I_{\rm off}$  up to  $2.3\times10^7$  for W-GNR).

The remaining of this chapter is structured as follows: Section 2.2 presents the theoretical formalism to compute the GNR electronic ballistic transport. Section 2.3 entails an overview of the GNR geometries and topologies in our experiments. Section 2.4 illustrates the means to open the energy bandgap: via GNR geometry change or through applied gate voltages. The simulation results are shown in Section 2.5. Finally, some concluding remarks are given

in Section 2.6.

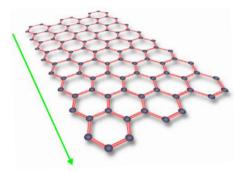

# 2.2 Graphene Nanoribbon Modelling & Simulation

Like the mythological Janus, graphene nanoribbons have two personae determined by the lattice orientation: (i) Zig-Zag graphene nanoribbon (Z-GNR), which is always metallic due to its near the Fermi level localized state and (ii) Armchair graphene nanoribbon (A-GNR), which is metallic or semiconducting depending on its ribbon width [108]. For the purpose of our investigation only Z-GNRs are relevant and as such in the sequel we study carrier transport properties inside single layer Z-GNRs, as the one depicted in Figure 2.1.

Figure 2.1: Zig-Zag GNR Configuration.

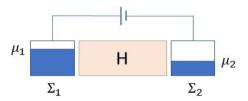

To capture the GNR specific electronic ballistic transport we make use of the Non-Equilibrium Green Function (NEGF) – Landauer formalism, which builds upon the NEGF quantum transport methodology, the tight-binding Hamiltonian model and the Landauer formula to compute GNR's conductance and current-voltage characteristics. In addition, we utilize a 3D Poisson solver to self-consistently calculate the GNR potential by means of finite difference method [109], [110]. As discussion vehicle we make use of a conduction channel formed by a GNR placed between two electrodes as depicted in Figure 2.2, which is described by a Hamiltonian matrix H incorporating all internal and external potentials. In our simulations, we construct H by using semi-empirical tight-binding model computations, as follows:

$$H = \sum_{i,j} t_{i,j} |i\rangle \langle j|, \qquad (2.1)$$

where  $t_{i,j}$  is computed as:

$$t_{i,j} = \begin{cases} \tau, & \text{if } i \text{ and } j \text{ atoms are adjacent,} \\ 0, & \text{otherwise.} \end{cases}$$

(2.2)

In general,  $\tau = -2.7\,\mathrm{eV}$  [110]. On the channel sides the two contacts with different electrochemical potentials  $u_1$  and  $u_2$ , sustain the channel conduction and their interaction with the channel is modelled via the left and right contact self-energy matrices  $\Sigma_1$  and  $\Sigma_2$ , respectively.

Figure 2.2: General Simulation Model.

After H,  $\Sigma_1$  and  $\Sigma_2$  are derived, T(E) which models the probability of one electron being transmitted between the two end contacts is computed as a function of energy E via:

$$T(E) = trace(\Gamma_1 G_R \Gamma_2 G_R^{\dagger}). \tag{2.3}$$

where  $G_R(E)$  is the retarded Green's function with energy E and  $G_R^{\dagger}$  is the transpose of  $G_R$ .  $\Gamma_{1,2}$  are the left and right contact broadening factors, which are numerically computed via:

$$G_R(E) = [EI - H - \Sigma_1 - \Sigma_2]^{-1},$$

(2.4)

$$\Gamma_{1,2} = i \cdot [\Sigma_{1,2} - \Sigma_{1,2}^{\dagger}],$$

(2.5)

respectively, where I is the identity matrix and H GNR's tight-binding Hamiltonian matrix.

The current to flow along the GNR is then derived based on the Landauer formula, as follows:

$$I = \frac{q}{h} \int_{-\infty}^{+\infty} T(E) \cdot (f_0(E - \mu_1) - f_0(E - \mu_2)) \, dE, \qquad (2.6)$$

where q and h are the electron charge and Planck's constant, respectively. Moreover,  $f_{1,2}(E)$  are the Fermi functions corresponding to the left and right contacts, respectively, computed via:

$$f_{1,2}(E) = \frac{1}{1 + \exp((E - u_{1,2})/(K_B T))},$$

(2.7)

where  $K_B$  and T are the Boltzmann constant and the experimental temperature.

Assuming that the end contacts are biased by  $V_{\rm d}$  and  $V_{\rm s}$ , the channel conductance is derived according to Ohm's law as follows:

$$G = \frac{I}{V_{\rm d} - V_{\rm s}}.\tag{2.8}$$

# 2.3 Graphene Nanoribbon Topologies

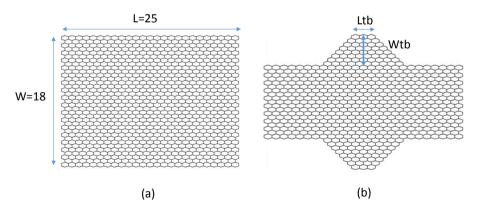

Figure 2.3 depicts on its left side a Rectangular GNR (R-GNR) with zig-zag edges, and on its right side the basic unit of the graphene lattice (a carbon atoms hexagon with  $a=0.142\,\mathrm{nm}$  side). The length and the width of one

Figure 2.3: Rectangular GNR and Unit Cell.

carbon hexagon are  $a\sqrt{3}$  nm and 2a nm. In our experiments, we define the right 4 atoms of a hexagon as a Unit Cell (UC). To express GNR's width/length we make use of Row/Column UC (RUC, CUC) as basic units, thus the GNR in Figure 2.3, has W=4 RUC and L=13 CUC.

The actual length or width of a GNR (unit is [nm]), is calculated as:

$$Length = L \cdot \sqrt{3} \cdot a \tag{2.9}$$

and

$$Width = (3 \cdot W - 1) \cdot a. \tag{2.10}$$

As nanoribbons can be patterned we consider in our investigation, besides rectangular GNR, we design and investigate four GNR shapes: Butterfly GNR (B-GNR), Camel GNR (C-GNR), Double Butterfly GNR (DB-GNR) and Waterfall GNR (W-GNR), as depicted in Figure 2.4, in order to address the zero bandgap and poor current ratio associated with the rectangular structure. As

Figure 2.4: Non-rectangular GNRs.

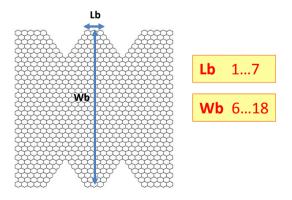

indicated in the Figure, each geometry is described by global Width W and Length L, and, when applicable, by Constriction Width  $W_{\rm c}$  and Length  $L_{\rm c}$ , Bump Width  $W_{\rm b}$  and Length  $L_{\rm b}$ , Top Bump Width  $W_{\rm tb}$  and Length  $L_{\rm tb}$ , or outer and inner boundary Head Length  $L_{\rm h1}$  and  $L_{\rm h2}$ , Head Width  $W_{\rm h}$  and Channel Width  $W_{\rm wc}$ .

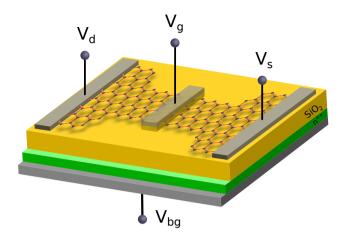

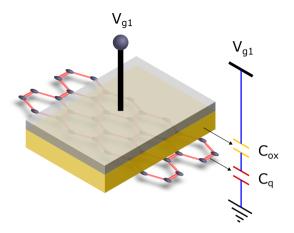

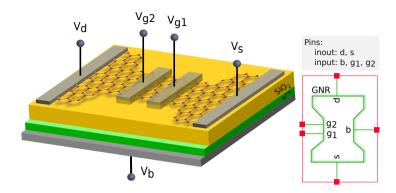

Apart of biasing the GNR by applying  $V_{\rm s}$  and  $V_{\rm d}$  on the source and drain contacts its conductance can be also modulated by means of electrostatic interaction (e.g., a top gate voltage  $V_{\rm g}$ ). As illustrated in Figure 2.5, we design

Figure 2.5: 3D GNR Structure [1].

a GNR-based building block and employ the butterfly GNR as its conduction channel, through which the current flow is induced by applying a bias voltage  $(V_{\rm d}-V_{\rm s})$  between the two end-point contacts, and is modulated by the top gate. In our experiment we set the width of action of each of these voltages to  $3\sqrt{3}a$  (3 unit cell width). In addition, a back bias voltage  $V_{\rm back}$  is applied beneath the GNR, which in manufactured devices is typically a small fraction of the back gate potential, i.e.,  $V_{\rm bg}$  (because of the significant potential drop on the dielectric layer - usually SiO<sub>2</sub> - residing underneath the graphene ribbon). For all the other shapes we use the same approach to apply the voltages on the GNRs.

In the next section we used the Non-Equilibrium Green Function - Landauer formalism described in Section 2.2, to simulate the previously described GNRs to investigate how their geometry influences their electronic transport properties (conductance and current), and demonstrate that geometry has a crucial role in shaping GNR's conduction and energy bandgap opening.

# 2.4 Energy Bandgap Opening

As Z-GNRs are always metallic, due to energy bandgap absence, one needs to find a way to create bandgap in order to design GNR-based devices/switches. In this section we investigate the potential effect of Z-GNR geometry change and/or external bias on bandgap formation and width.

#### 2.4.1 Via GNR Geometry Change