# **Hardware Acceleration of Bioinformatics Sequence Alignment Applications**

## **Proefschrift**

ter verkrijging van de graad van doctor

aan de Technische Universiteit Delft,

op gezag van de Rector Magnificus Prof. ir. K. C. A. M. Luyben,

voorzitter van het College voor Promoties,

in het openbaar te verdedigen op maandag 6 juni 2011 om 12.30 uur

door

**Laiq HASAN,**

Master of Science in Electrical Engineering

N-W.F.P. University of Engineering and Technology, Peshawar, Pakistan

geboren te Swabi, Pakistan.

Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. ir. H. J. Sips

Copromotor: Dr. ir. Z. Al-Ars

Samenstelling promotiecommissie:

Rector Magnificus

Prof. dr. ir. H. J. Sips

Dr. ir. Z. Al-Ars

Prof. dr. W. Anheier

Prof. dr. O. Nieto-Taladriz Garcia

Prof. dr. ir. C. Vuik

Prof. dr. ir. M. J. T. Reinders

Dr. ir. T. G. R. M. van Leuken

Prof. dr. ir. P. F. A. Van Mieghem

voorzitter

Technische Universiteit Delft, promotor

Technische Universiteit Delft, copromotor

Universität Bremen

Universidad Politecnica de Madrid

Technische Universiteit Delft

Technische Universiteit Delft

Technische Universiteit Delft

Technische Universiteit Delft, reservelid

This thesis has been completed in partial fulfillment of the requirements of Delft University of Technology (Delft, The Netherlands) for the award of the Ph.D. degree. The research described in this thesis was supported in parts by three institutions. (1) CE Lab. Delft University of Technology, (2) HEC Pakistan, (3) UET Peshawar, Pakistan.

Published and distributed by: Laiq Hasan, E-mail: [laiqhasan@gmail.com](mailto:laiqhasan@gmail.com)

ISBN: 978-90-72298-19-5

Keywords: Bioinformatics, Sequence Alignment, Hardware Acceleration, Systolic Arrays, Recursive Variable Expansion, FPGAs, GPUs, Performance Analysis.

Copyright © 2011 by Laiq Hasan

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without written permission of the author.

Printed in The Netherlands

Dedicated to:

**The Sunday morning Sun, cool breeze and clear blue skies.**

# Summary

Biological sequence alignment is an important and challenging task in bioinformatics. Alignment may be defined as an arrangement of two or more DNA or protein sequences to highlight the regions of their similarity. Sequence alignment is used to infer the evolutionary relationship between a set of protein or DNA sequences. An accurate alignment can provide valuable information for experimentation on the newly found sequences. It is indispensable in basic research as well as in practical applications such as pharmaceutical development, drug discovery, disease prevention and criminal forensics.

Many algorithms and methods, such as, dot plot, Needleman-Wunsch, Smith-Waterman, FASTA, BLAST, HMMER and ClustalW have been proposed to perform and accelerate sequence alignment activities. However, with the ever increasing volume of data in bioinformatics databases, the time needed for biological sequence alignment is always increasing. The main aim of the research presented in this thesis is to explore and analyze the existing sequence alignment methods and come up with better and optimized solutions. The following research goals have been achieved during the course of this thesis.

1. Classification and comparison of the available sequence alignment methods with the emphasis on identifying the most optimal but computationally expensive methods that are best suited for hardware acceleration.

2. Optimized systolic array implementations of the Smith-Waterman based sequence alignment on FPGAs.

3. A novel FPGA implementation of sequence alignment based on recursive variable expansion and its performance evaluation.

4. An optimized and high performance GPU-based protein sequence alignment and its comparison with the existing GPU solutions.

5. Detailed performance analysis and optimization of the hardware-based sequence alignment, considering the limiting factors like computational resources, memory bandwidth and power consumption.

6. Introduction of a technique based on hardware partitioning to improve performance by reducing the hardware overhead cost.

# Samenvatting

Biologische sequentie uitlijning is een belangrijke en uitdagende taak in bioinformatica. Uitlijning kan gedefinieerd worden als een rangschikking van twee of meer DNA- of eiwitsequenties om gelijkvormig delen te markeren. Sequentieuitlijning wordt gebruikt om de evolutionaire relatie tussen een set eiwitten of DNA-sequenties af te leiden. Een nauwkeurige uitlijning kan waardevolle informatie voor experimenten op nieuw ontdekte sequenties opleveren. Het is onontbeerlijk in basisonderzoeken evenals in praktische toepassingen zoals farmaceutische ontwikkelingen, medicijn onderzoek, ziekte preventie en forensisch onderzoek.

Vele algoritmes en methoden, zoals dot plot, Needleman-Wunsch, Smith-Waterman, FASTA, BLAST, HMMER en ClustalW zijn bedoeld om de sequentieuitlijning uit te voeren en te versnellen. Echter, met het alsmaar groeiende volume van de data in bio-informatica databanken, groeit ook alsmaar de tijd benodigd voor biologische sequentie uitlijning. Het voornaamste doel van het in dit proefschrift gepresenteerde onderzoek is het verkennen en analyseren van bestaande sequentieuitlijningsmethoden en het opzetten van een betere, optimalere oplossing. De volgende onderzoeksdoelen zijn voltooid in het kader van dit proefschrift.

1. Classificatie en vergelijking van beschikbare sequentieuitlijningsmethoden met nadruk op het identificeren van de meest optimale maar mathematisch kostbaarste methoden die het best passen bij hardwareversnelling.

2. Optimalisatie van systolic-array uitvoeringen van de op Smith-Waterman gebaseerde sequentieuitlijning in FPGAs.

3. Een nieuwe FPGA-implementatie van sequentieuitlijning gebaseerd op ‘recursive variable expansion’ en zijn performance evaluatie.

4. Een geoptimaliseerde en high performance GPU-gebaseerd eiwit sequentieuitlijning en de vergelijking met bestaande GPU-oplossingen.

5. Gedetailleerde performance evaluatie en optimalisatie van hardware gebonden sequentieuitlijning, met het oog op beperkende factoren zoals computer hulpbronnen, geheugenbandbreedte en energieverbruik.

6. Introductie van een werkwijze gebaseerd op hardware partitionering om de prestatie te verbeteren door het terugbrengen van de hardware overhead kosten.

# Acknowledgments

First and foremost, I would like to thank Allah SWT, as counting up His favors is inconceivable to categorize. “If you would count up the favors of Allah, never would you be able to number them: for Allah is Oft-Forgiving, Most Merciful.” (Quran, Surah Al-Nahl, Verse 18)

Next, I thank my family and friends back home, who continuously keep praying for my success, without expecting anything in return. Thanks are due to my friends and acquaintances, in The Netherlands in general and Delft in particular, whose support was necessary for my long stay here. Thanks are also due to my friends abroad, spread all over the world and whom I keep visiting from time to time. They really make me feel like a global citizen.

In the Computer Engineering Laboratory, my first thanks go to the late professor Stamatis Vassiliadis, who gave me the confidence and courage to continue with my Ph.D. God may rest his soul in peace. Next, thanks to prof. dr. ir. H. J. Sips for agreeing to be my promotor and approving the thesis. After Stamatis and H. J. Sips, the next thanks of course go to my co-supervisor, dr. ir. Zaid Al-Ars, who always remained patient and optimistic about my work and guided me to the best of his abilities throughout my Ph.D. Thanks are due to dr. Koen Bertels and dr. Georgi Gaydadjiev, who always helped and encouraged during the course of my Ph.D. Thanks to other faculty members in the laboratory, Said Hamdioui, Sorin Cotofana, Arjan van Genderen and Stephan Wong too, who have always been friendly and cooperative. Thanks are also due to my colleagues Ioannis Soudis and Blagomir Donchev for giving me a start in VHDL, Sebastian Isaza for his friendly discussions and improving the presentation for my first colloquium talk, Bogdan Spinean for helping me out during our travel to Rabat, Morocco for DTIS’07, soon after the major surgery on my left kidney at Erasmus Medical Center in Rotterdam. Bundles of thanks to my colleagues Yao Wang and Mottaqiallah Taouil for their handy advices about my work during the later part of my Ph.D. Thanks are also due to Marijn Kentie and Erik Vermij for their contributions in the practical part of the research while doing their M.Sc. projects with me and Zaid. I also thank all other colleagues at Computer Engineering Laboratory,

for providing a friendly and research conducive environment. It would be unfair if I do not mention the technical and administrative support provided by Bert Meijs, Erik de Vries, Eef Hartman, Lidwina Tromp and Monique Tromp. Their support gave me the luxury of focusing only on my work, without caring much about the related issues.

Outside the Computer Engineering Laboratory, thanks to Franca Post from CICAT (TU Delft), Loes Minkman from NUFFIC (The Netherlands), the concerned people from the Higher Education Commission of Pakistan and University of Engineering and Technology Peshawar Pakistan. They smoothly processed all my financial and 'study leave' related issues, thus making my life relatively easy. Thanks are due to my friends Wouter van der Sluis, Weiman Chim, Saleh Safiruddin, Johan Splinter and Serge Keyser for helping me in translating the summary of my thesis and propositions into Dutch. Also, my humble thanks to all my friends and their families for taking good care of me during my necessary treatment at Erasmus Medical Center in Rotterdam in August 2007. Special thanks go to Ahmad Jan, Saad Hassan Mirza and my dear friend Waqar who remained with me for around 10 days in the hospital, my friend Malik Aleem Ahmad for taking good care for more than a month during my post hospital rest period, Mehfooz, Hamayun, Hisham, Haleem Bangash, Aqeel, Ahson Jabbar, Ahsan Shabir, Haroon, Omer, Noman, Sant Paul, Jawad, Plamen Gonchosov, Blagormir Donchev and all other friends who visited me on regular basis and kept me away from loneliness, desperation and frustration.

For the leisure times, my first thanks go to the Computer Engineering Laboratory for organizing those enjoyable social events that are an integral part of life at the laboratory. Next, I thank Saleh, Marius, George, Mihai, Chunyang, my Belgian friend Glen and my Swedish friend Henrik for their company and playing my favorite sport (tennis) with me. I also thank all my Pakistani, Indian, Chinese, Iranian, Dutch and other friends for the cricket, volleyball, squash, swimming, cycling, going to cinemas and other amazing activities in which we participated together. These activities were the best part of my stay in The Netherlands. Thanks to all my friends in Delft and outside (specially Seyab, Faisal Nadeem, Faisal Kareem, Fakhar, Mehfooz, Cheema, Hamayun, Dev, Atif, Sandilo, Hanan, Zahid Shabbir, Nadeem, Zubair, Tariq, Hisham, Sharif Ullah, Husnul Amin, Saleem, Haider, Mazhar, Amir, Sarfaraz, Samad Khan, Shakir bhai, Niaz, Imran, Adeel, Zaidi, Mafalda and others), who made my stay in The Netherlands sociable, by inviting me in so many parties and gatherings that they kept organizing from time to time. I think, I should write a memoir at some point in time to elaborate all these activities and the people involved.

Finally, I thank members of the opposing committee for devoting some of their precious time to scrutinize my thesis, give their valuable feedback and above all travel to Delft for the public defense of this dissertation.

# Contents

|                                                            |            |

|------------------------------------------------------------|------------|

| <b>Summary</b>                                             | <b>v</b>   |

| <b>Samenvatting</b>                                        | <b>vii</b> |

| <b>Acknowledgments</b>                                     | <b>ix</b>  |

| <b>Abbreviations and Symbols</b>                           | <b>xxi</b> |

| <b>1 Introduction</b>                                      | <b>1</b>   |

| 1.1 Molecular biology - an overview . . . . .              | 1          |

| 1.1.1 Cells, amino acids and proteins . . . . .            | 2          |

| 1.1.2 Chromosomes and DNA . . . . .                        | 2          |

| 1.1.3 RNA and transcription . . . . .                      | 3          |

| 1.2 Bioinformatics . . . . .                               | 4          |

| 1.2.1 Fields of bioinformatics . . . . .                   | 5          |

| 1.2.2 Sequence alignment and its types . . . . .           | 6          |

| 1.2.3 Applications of sequence alignment . . . . .         | 9          |

| 1.3 Acceleration of sequence alignment . . . . .           | 11         |

| 1.3.1 Methods of acceleration . . . . .                    | 11         |

| 1.3.2 Thesis contribution . . . . .                        | 13         |

| 1.4 Thesis outline . . . . .                               | 14         |

| 1.5 Summary . . . . .                                      | 15         |

| <b>2 Sequence Alignment Methods</b>                        | <b>17</b>  |

| 2.1 Classification of sequence alignment methods . . . . . | 17         |

| 2.2 Global methods . . . . .                               | 18         |

| 2.2.1 Dot plot method . . . . .                            | 18         |

| 2.2.2 Needleman-Wunsch algorithm . . . . .                 | 19         |

| 2.3 Local methods . . . . .                                | 21         |

| 2.3.1 Smith-Waterman algorithm . . . . .                   | 21         |

|          |                                                     |           |

|----------|-----------------------------------------------------|-----------|

| 2.3.2    | FASTA algorithm . . . . .                           | 24        |

| 2.3.3    | BLAST: Basic Local Alignment Search Tool . . . . .  | 26        |

| 2.4      | Mutiple alignment methods . . . . .                 | 27        |

| 2.4.1    | HMMER . . . . .                                     | 27        |

| 2.4.2    | ClustalW . . . . .                                  | 28        |

| 2.5      | Comparison of sequence alignment methods . . . . .  | 29        |

| 2.6      | Summary . . . . .                                   | 31        |

| <b>3</b> | <b>Hardware Acceleration</b>                        | <b>33</b> |

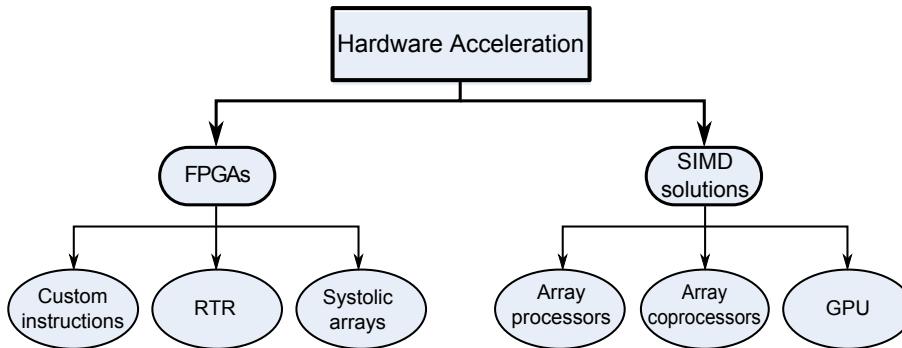

| 3.1      | Classification of acceleration methods . . . . .    | 33        |

| 3.1.1    | FPGAs . . . . .                                     | 34        |

| 3.1.2    | SIMD solutions . . . . .                            | 36        |

| 3.2      | Accurate acceleration evaluation approach . . . . . | 38        |

| 3.2.1    | MOLEN platform . . . . .                            | 38        |

| 3.2.2    | S-W implementation on MOLEN . . . . .               | 40        |

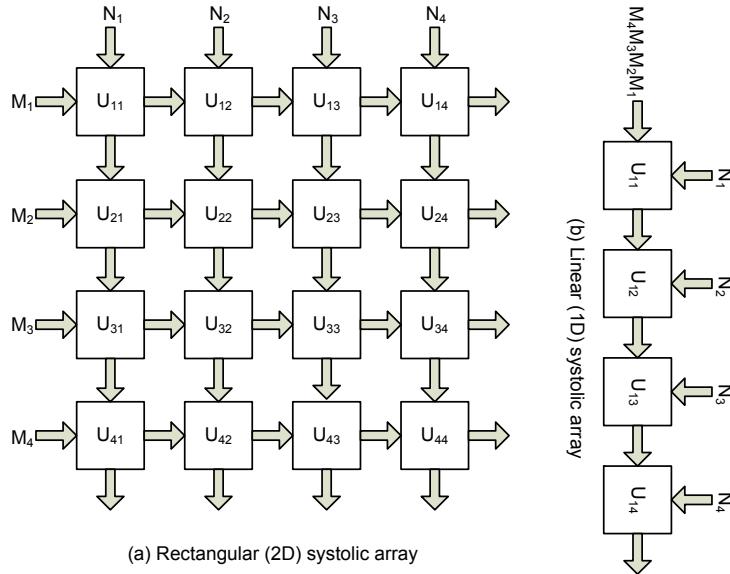

| 3.3      | Rectangular (2D) systolic implementation . . . . .  | 43        |

| 3.3.1    | Cell design . . . . .                               | 44        |

| 3.3.2    | System design . . . . .                             | 45        |

| 3.4      | Linear (1D) systolic implementation . . . . .       | 46        |

| 3.4.1    | Cell design . . . . .                               | 46        |

| 3.4.2    | System design . . . . .                             | 47        |

| 3.4.3    | Extended design with DDR RAM . . . . .              | 50        |

| 3.5      | Summary . . . . .                                   | 51        |

| <b>4</b> | <b>RVE-based FPGA Acceleration</b>                  | <b>53</b> |

| 4.1      | Introduction . . . . .                              | 53        |

| 4.1.1    | The RVE approach . . . . .                          | 53        |

| 4.1.2    | Sequence alignment using RVE approach . . . . .     | 54        |

| 4.2      | Rectangular (2D) RVE implementation . . . . .       | 56        |

| 4.2.1    | Building block description . . . . .                | 56        |

| 4.2.2    | System design . . . . .                             | 57        |

| 4.2.3    | Discussion of results . . . . .                     | 57        |

| 4.3      | Linear (1D) RVE implementation . . . . .            | 60        |

| 4.3.1    | Building block description . . . . .                | 60        |

| 4.3.2    | System design . . . . .                             | 61        |

| 4.3.3    | Discussion of results . . . . .                     | 61        |

| 4.4      | RVE performance evaluation . . . . .                | 63        |

| 4.5      | Summary . . . . .                                   | 67        |

| <b>5</b> | <b>GPU Acceleration</b>                             | <b>69</b> |

| 5.1      | GPU as a computational platform . . . . .           | 69        |

| 5.1.1    | CUDA framework . . . . .                            | 69        |

| 5.1.2    | Coalescing . . . . .                                | 71        |

| 5.1.3    | Previous implementations . . . . .                  | 72        |

---

|          |                                                              |            |

|----------|--------------------------------------------------------------|------------|

| 5.2      | Optimized GPU implementation . . . . .                       | 73         |

| 5.2.1    | General design . . . . .                                     | 73         |

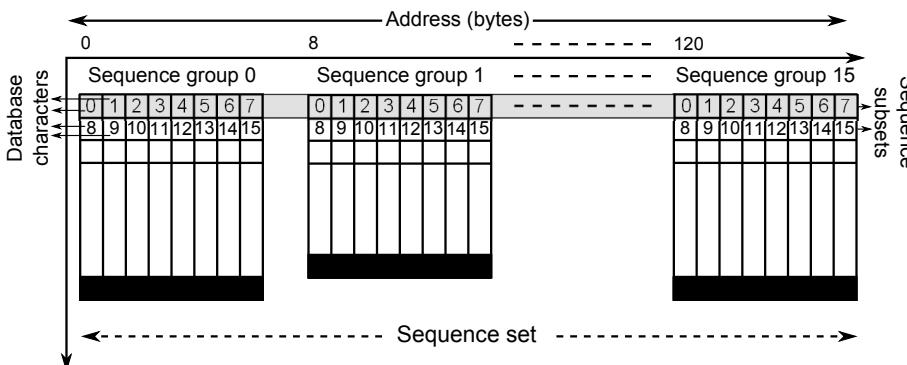

| 5.2.2    | Database conversion . . . . .                                | 74         |

| 5.2.3    | Temporary data reads and writes . . . . .                    | 77         |

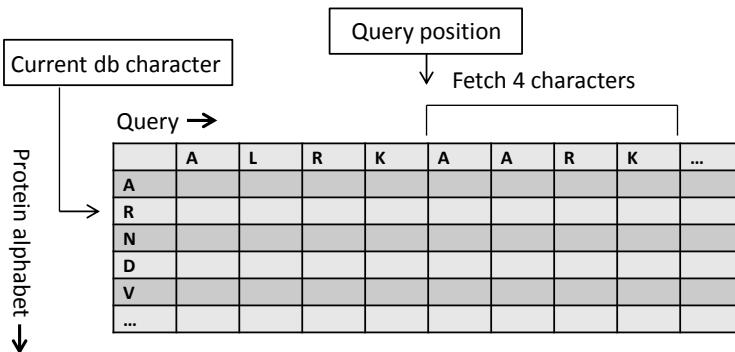

| 5.2.4    | Substitution matrix accesses . . . . .                       | 78         |

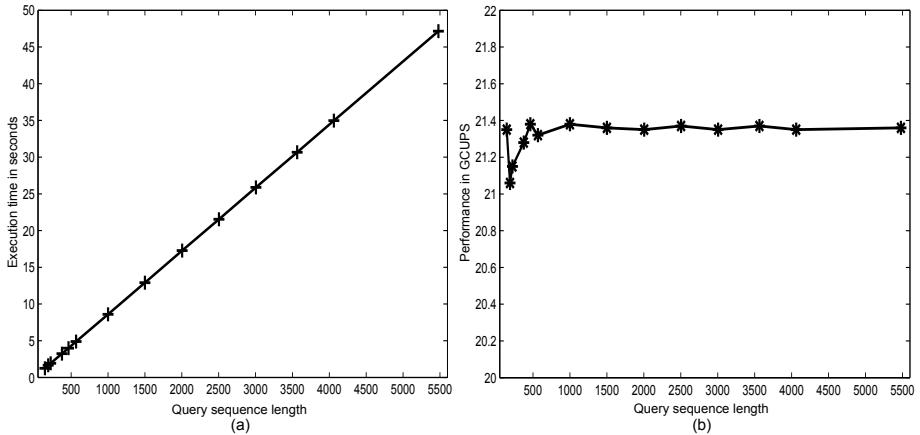

| 5.3      | Discussion of results . . . . .                              | 79         |

| 5.3.1    | Experimental setup . . . . .                                 | 79         |

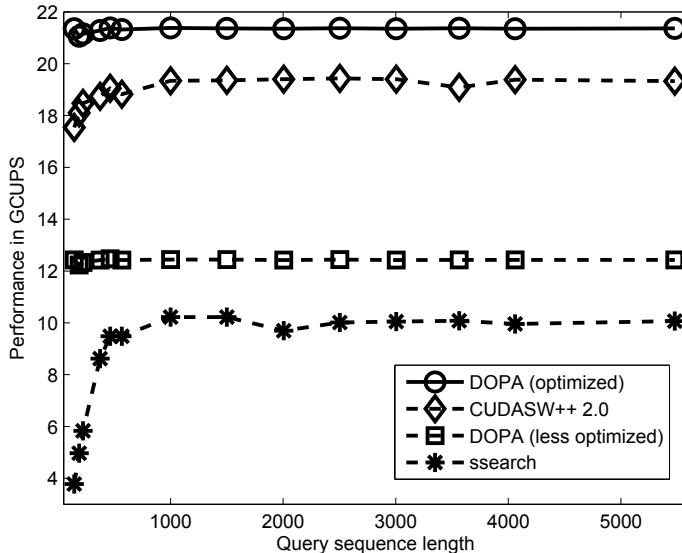

| 5.3.2    | Performance comparison . . . . .                             | 81         |

| 5.4      | Performance limits . . . . .                                 | 83         |

| 5.4.1    | Limits/bottlenecks . . . . .                                 | 83         |

| 5.4.2    | Scalability/future prospects . . . . .                       | 84         |

| 5.5      | Summary . . . . .                                            | 86         |

| <b>6</b> | <b>Performance Analysis</b>                                  | <b>87</b>  |

| 6.1      | Theoretical performance boundaries . . . . .                 | 87         |

| 6.2      | Performance limitations . . . . .                            | 90         |

| 6.2.1    | Performance limited by the computational resources . . . . . | 90         |

| 6.2.2    | Performance limited by the bandwidth . . . . .               | 94         |

| 6.3      | Performance and bandwidth optimization . . . . .             | 96         |

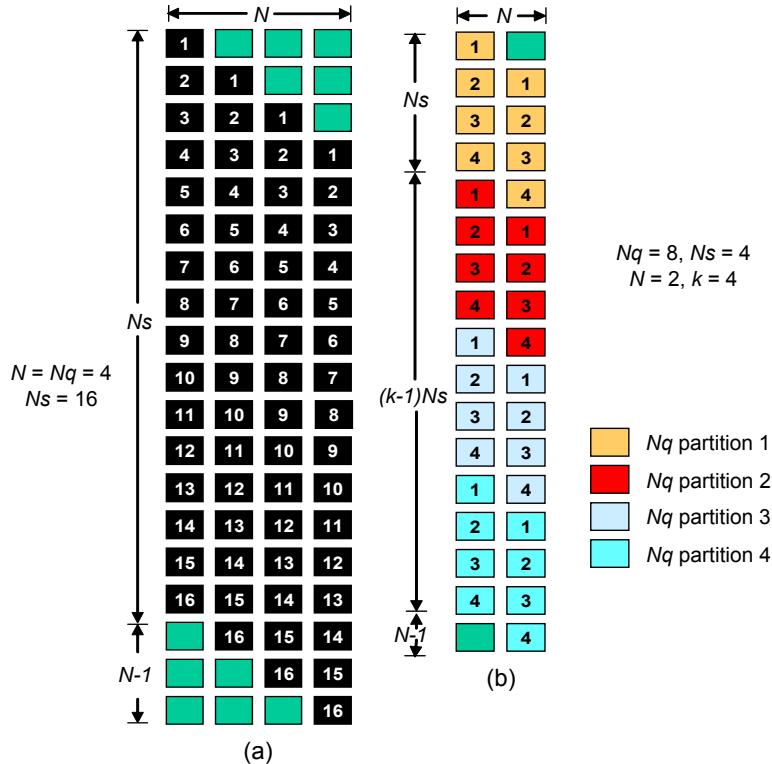

| 6.4      | Hardware partitioning . . . . .                              | 99         |

| 6.4.1    | Theoretical concept . . . . .                                | 99         |

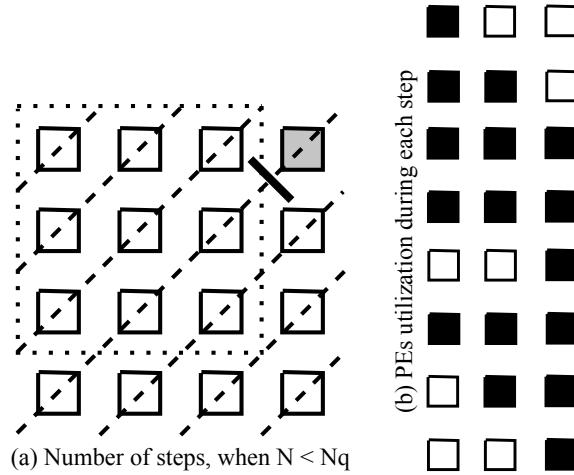

| 6.4.2    | Example of the process . . . . .                             | 100        |

| 6.5      | Generalizing the hardware partitioning method . . . . .      | 101        |

| 6.6      | Summary . . . . .                                            | 105        |

| <b>7</b> | <b>Conclusions and Future Research Directions</b>            | <b>107</b> |

| 7.1      | Conclusions . . . . .                                        | 107        |

| 7.2      | Future research directions . . . . .                         | 108        |

| <b>A</b> | <b>Important Terms in Bioinformatics</b>                     | <b>111</b> |

| <b>B</b> | <b>Dot Plot Implementation</b>                               | <b>113</b> |

| <b>C</b> | <b>N-W Examples</b>                                          | <b>115</b> |

| C.1      | Example 1 . . . . .                                          | 115        |

| C.2      | Example 2 . . . . .                                          | 118        |

| <b>D</b> | <b>S-W Examples</b>                                          | <b>123</b> |

| D.1      | Flow chart . . . . .                                         | 123        |

| D.2      | Example 1 . . . . .                                          | 123        |

| D.3      | Example 2 . . . . .                                          | 125        |

|                                                       |            |

|-------------------------------------------------------|------------|

| <b>E Power Consumption Evaluation</b>                 | <b>127</b> |

| E.1 Evaluation of dynamic power consumption . . . . . | 127        |

| E.2 Resource utilization . . . . .                    | 129        |

| E.3 Performance optimization . . . . .                | 130        |

| <b>Publications</b>                                   | <b>140</b> |

| <b>Curriculum Vitae</b>                               | <b>143</b> |

# List of Tables

|     |                                                                                           |     |

|-----|-------------------------------------------------------------------------------------------|-----|

| 1.1 | The 20 amino acids . . . . .                                                              | 6   |

| 1.2 | The BLOSUM62 amino acid substitution matrix . . . . .                                     | 9   |

| 2.1 | Dot plot matrix . . . . .                                                                 | 19  |

| 2.2 | Comparison of various sequence alignment methods . . . . .                                | 29  |

| 3.1 | Comparison of the work reviewed in Section 3.1 . . . . .                                  | 37  |

| 3.2 | Profiling results . . . . .                                                               | 41  |

| 3.3 | Performance in GCUPS and frequency in MHz for various number of PEs ( $N$ ) . . . . .     | 49  |

| 3.4 | $H$ matrix for aligning sequences of $m$ characters each . . . . .                        | 50  |

| 4.1 | Comparison between 2D systolic array and RVE implementations . .                          | 59  |

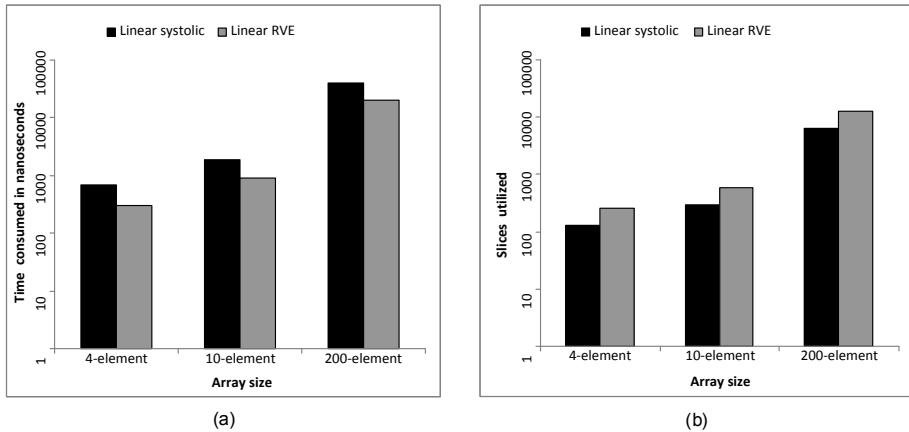

| 4.2 | Comparison between linear systolic array and linear RVE implementations . . . . .         | 62  |

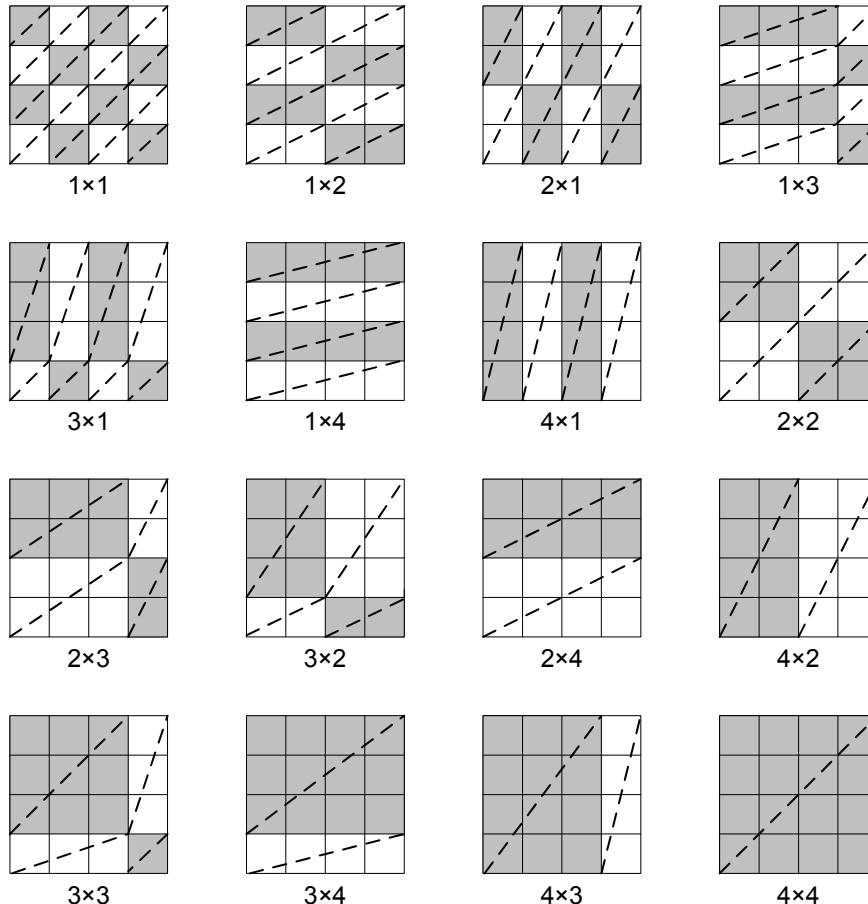

| 4.3 | Performance evaluation for various RVE implementations . . . . .                          | 65  |

| 5.1 | Performance results with Swiss-Prot . . . . .                                             | 80  |

| 5.2 | A comparison with CUDASW++ 2.0 . . . . .                                                  | 83  |

| 6.1 | Execution time ( $T_{exec}$ ) in $\mu$ sec for various combinations of $k$ and $N$ .      | 94  |

| 6.2 | Execution time ( $T_{exec}$ ) in $\mu$ sec for various combinations of $N$ and $B_{main}$ | 95  |

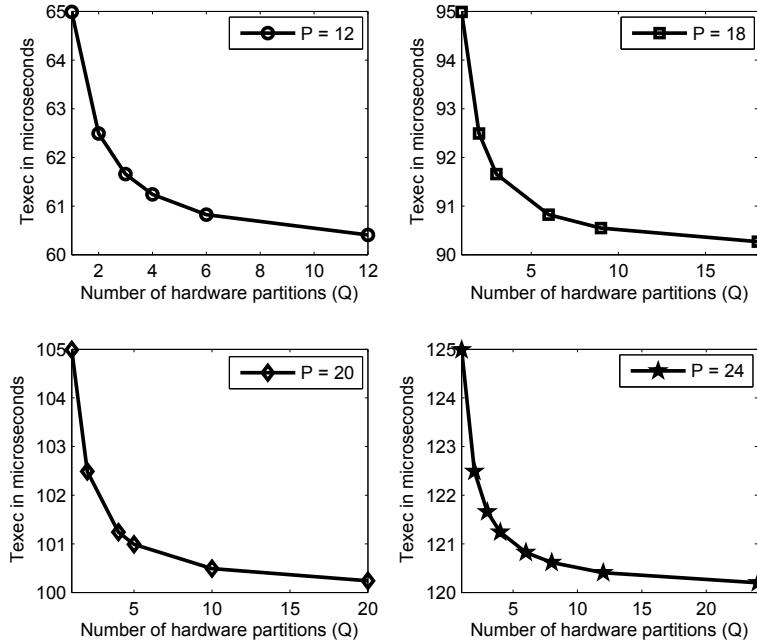

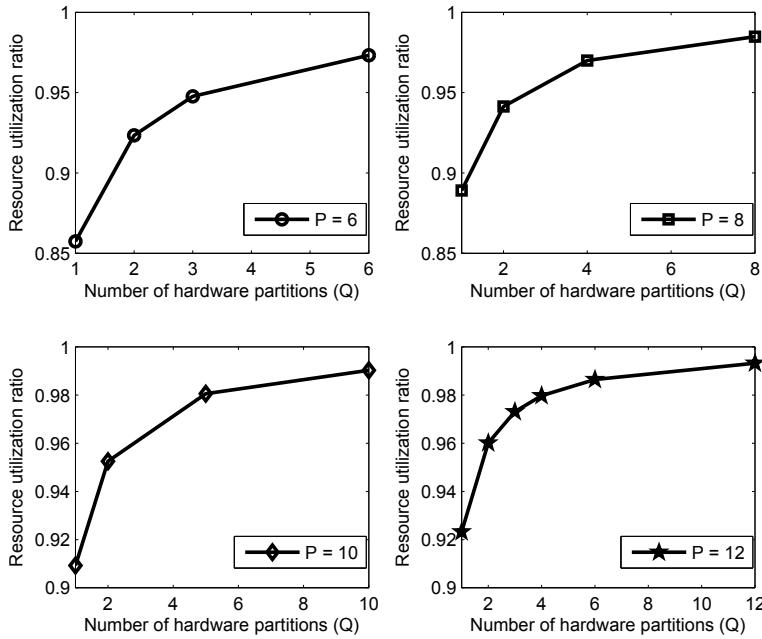

| 6.3 | Execution time ( $T_{exec}$ ) in $\mu$ sec for various ( $Ps$ ) and ( $Qs$ ) . . . . .    | 102 |

| 6.4 | Resource utilization ratio for various ( $Ps$ ) and ( $Qs$ ) . . . . .                    | 103 |

| B.1 | Example to prove our approach and its result . . . . .                                    | 114 |

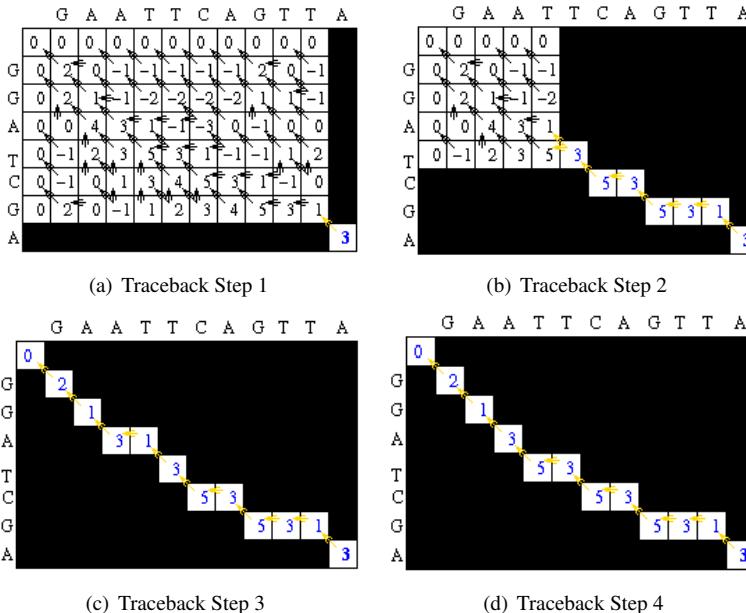

| D.1 | The dynamic programming matrix and the traceback path . . . . .                           | 125 |

| D.2 | Initialization for Example 2 with floating point values . . . . .                         | 125 |

|     |                                                                                                                                                       |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| D.3 | Calculation of first set diagonal similarity scores in the Smith-Waterman algorithm . . . . .                                                         | 126 |

| D.4 | The endpoint of the Smith-Waterman algorithm after calculation of all scoring parameters. A traceback from the highest score is highlighted . . . . . | 126 |

| E.1 | Dynamic power consumption in milliwatts ( <i>XC2VP30</i> ) . . . . .                                                                                  | 128 |

| E.2 | Dynamic power consumption in milliwatts ( <i>XC4VFX12</i> ) . . . . .                                                                                 | 129 |

| E.3 | Dynamic power consumption in milliwatts ( <i>XC5VTX240T</i> ) . . . . .                                                                               | 129 |

| E.4 | Device utilization and performance results ( <i>XC2VP30</i> ) . . . . .                                                                               | 130 |

| E.5 | Device utilization and performance results ( <i>XC4VFX12</i> ) . . . . .                                                                              | 130 |

| E.6 | Device utilization and performance results ( <i>XC5VTX240T</i> ) . . . . .                                                                            | 131 |

| E.7 | Modeling coefficients for various technologies . . . . .                                                                                              | 132 |

# List of Figures

|      |                                                                                                                                                                                 |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | The structure of DNA . . . . .                                                                                                                                                  | 3  |

| 1.2  | Classification of bioinformatics research areas . . . . .                                                                                                                       | 5  |

| 1.3  | Types of sequence alignment . . . . .                                                                                                                                           | 7  |

| 1.4  | Examples of sequence alignment applications . . . . .                                                                                                                           | 10 |

| 1.5  | Broad classification of sequence alignment acceleration . . . . .                                                                                                               | 11 |

| 2.1  | Various methods for sequence alignment . . . . .                                                                                                                                | 18 |

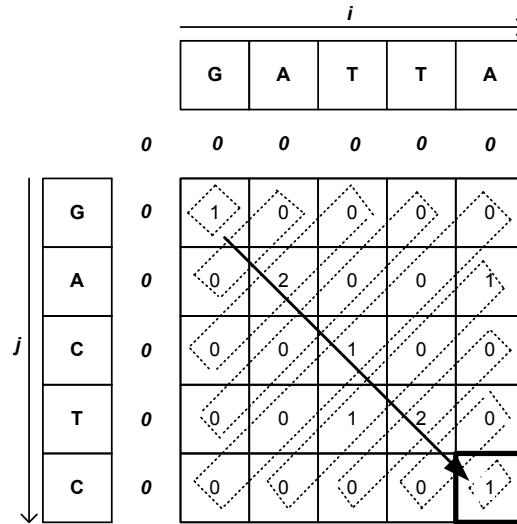

| 2.2  | Sample $H$ matrix, where the dotted rectangles show the elements that can be computed in parallel . . . . .                                                                     | 23 |

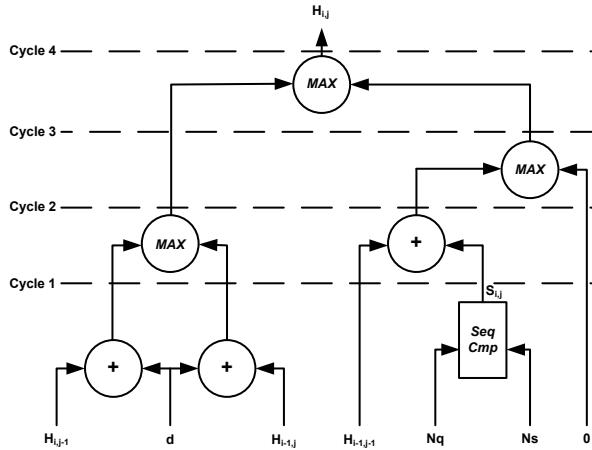

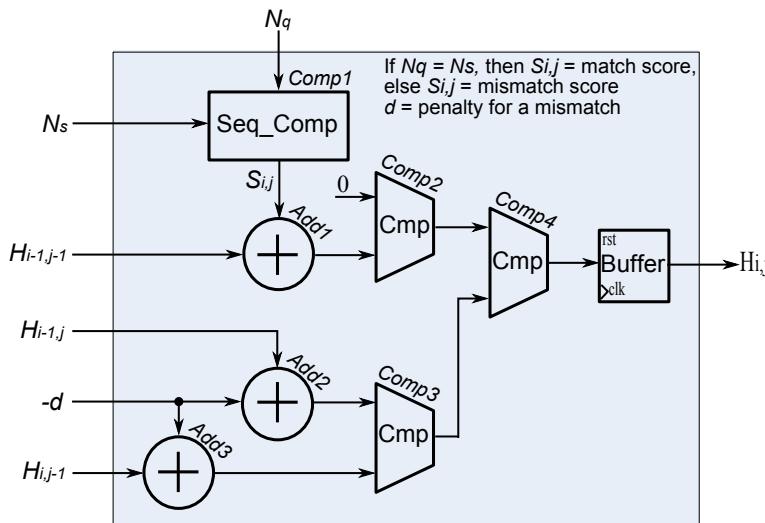

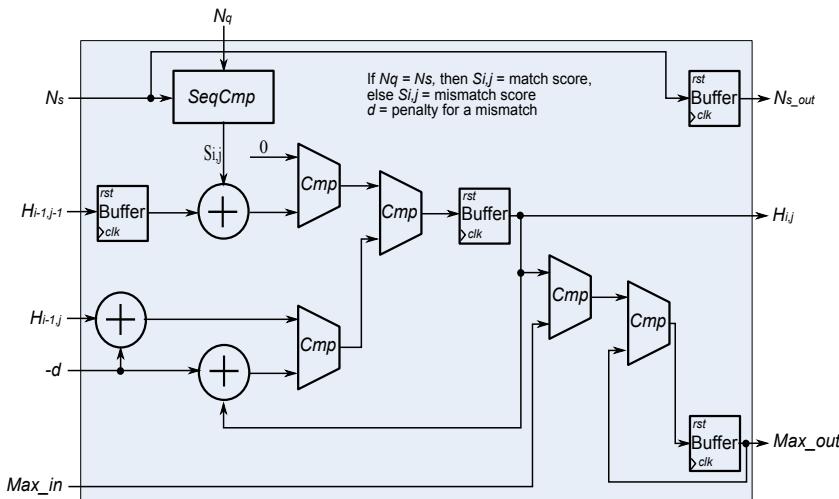

| 2.3  | Logic to compute cells in the $H$ matrix, where $+$ is an adder, $MAX$ is a max operator and $SeqCmp$ is the sequence comparator that generates match/mismatch scores . . . . . | 24 |

| 2.4  | Sample plot for FASTA . . . . .                                                                                                                                                 | 25 |

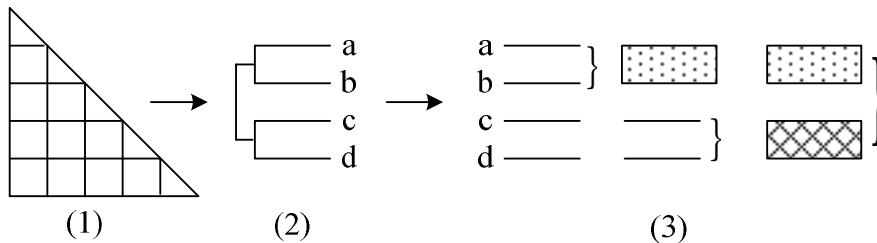

| 2.5  | Three stages of progressive alignment: (1) similarity matrix, (2) guided tree, (3) profile-profile progressive alignment . . . . .                                              | 28 |

| 3.1  | Hardware acceleration of sequence alignment methods . . . . .                                                                                                                   | 34 |

| 3.2  | Pictorial view of systolic array architectures . . . . .                                                                                                                        | 35 |

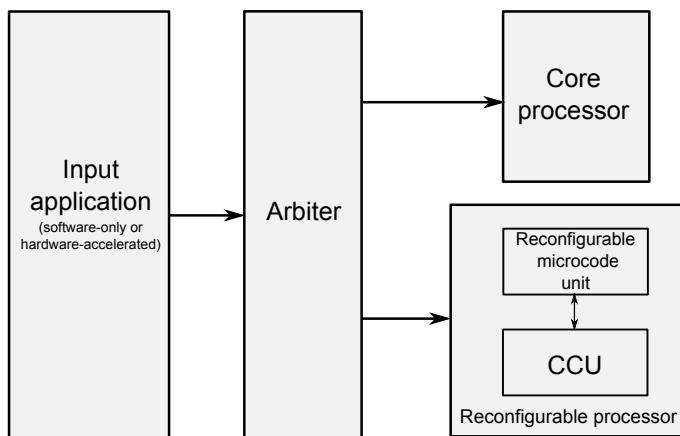

| 3.3  | Block diagram description of MOLEN platform . . . . .                                                                                                                           | 38 |

| 3.4  | Block diagram representation of MOLEN implementation approach .                                                                                                                 | 39 |

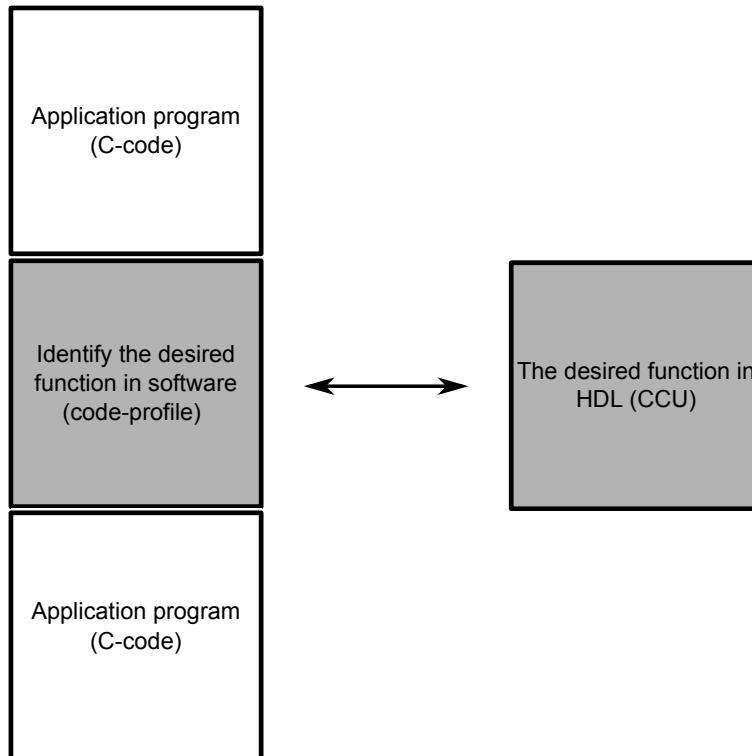

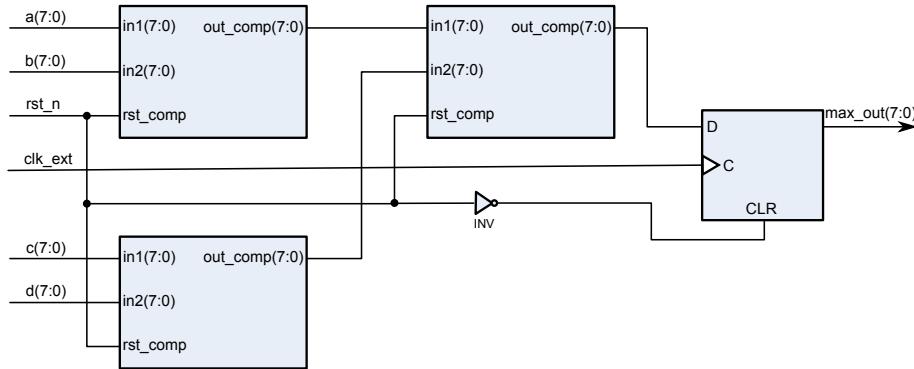

| 3.5  | Functional description of a software implementation of S-W algorithm                                                                                                            | 40 |

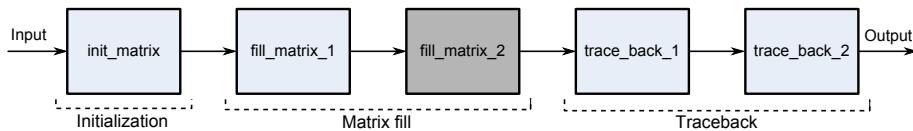

| 3.6  | RTL schematic of the CCU for the function <code>fill_matrix_2</code> . . . . .                                                                                                  | 42 |

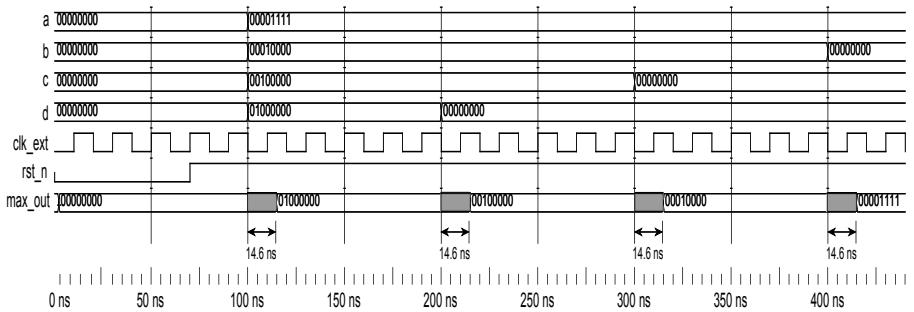

| 3.7  | Post place and route simulation results . . . . .                                                                                                                               | 42 |

| 3.8  | Cell design for rectangular systolic array implementation . . . . .                                                                                                             | 44 |

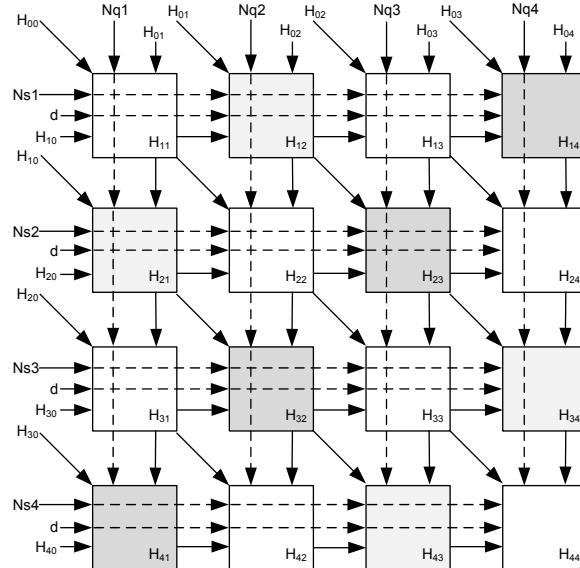

| 3.9  | Block diagram description of a $4 \times 4$ systolic array . . . . .                                                                                                            | 45 |

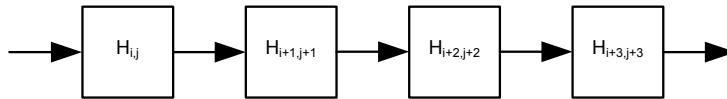

| 3.10 | Description of a 4-element linear systolic array . . . . .                                                                                                                      | 46 |

| 3.11 | Cell design for linear systolic array implementation . . . . .                                                                                                                  | 46 |

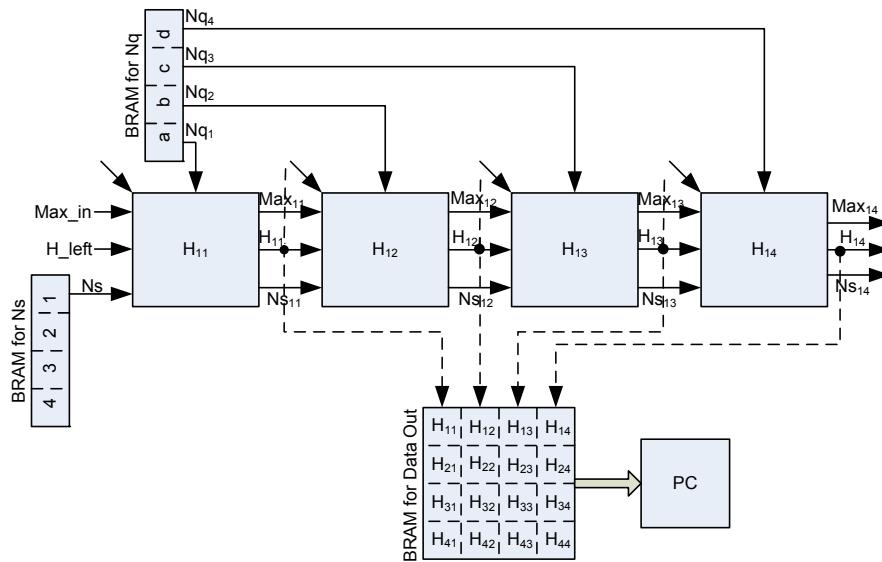

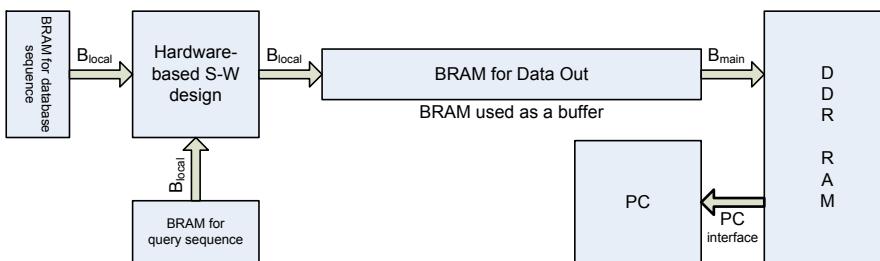

| 3.12 | Linear systolic array design using BRAM for intermediate data storage                                                                                                           | 48 |

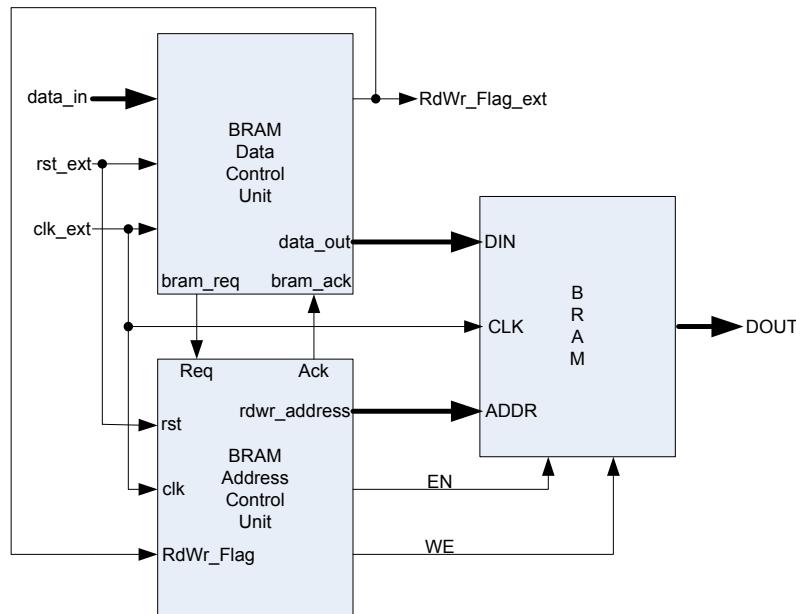

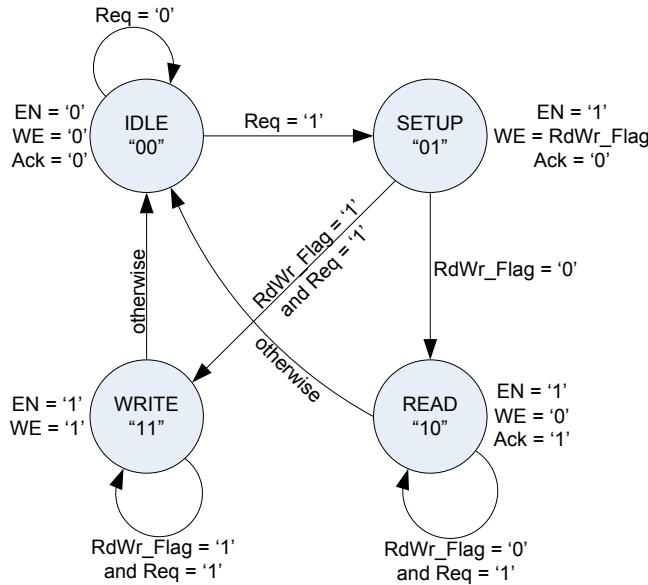

| 3.13 | Block diagram representation of BRAM control design . . . . .                                                                                                                   | 48 |

|      |                                                                                                                  |     |

|------|------------------------------------------------------------------------------------------------------------------|-----|

| 3.14 | State machine for BRAM address control unit . . . . .                                                            | 49  |

| 3.15 | Linear systolic array design using BRAM and DDR RAM . . . . .                                                    | 50  |

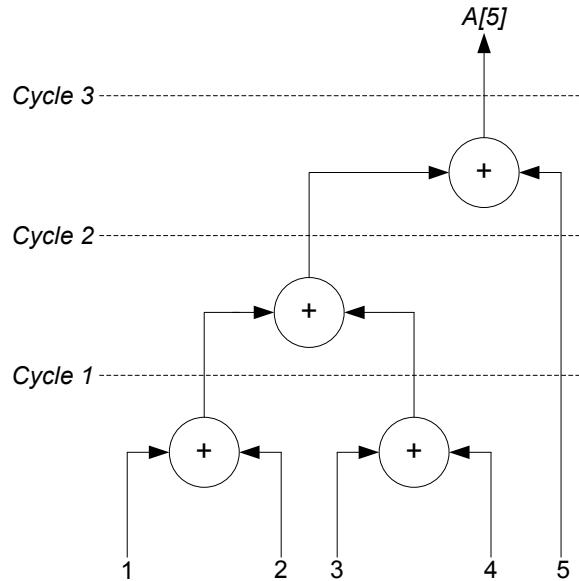

| 4.1  | Circuit for the Example 2 . . . . .                                                                              | 55  |

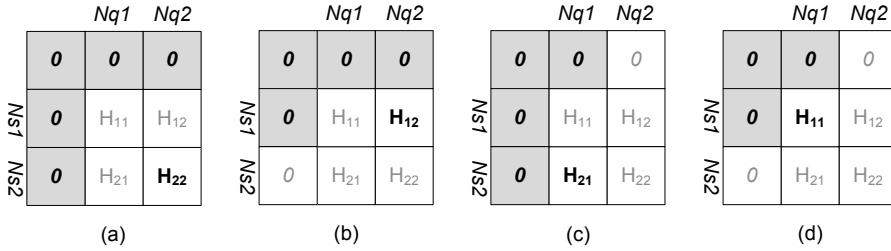

| 4.2  | Filling a $2 \times 2 H$ matrix using the RVE approach . . . . .                                                 | 56  |

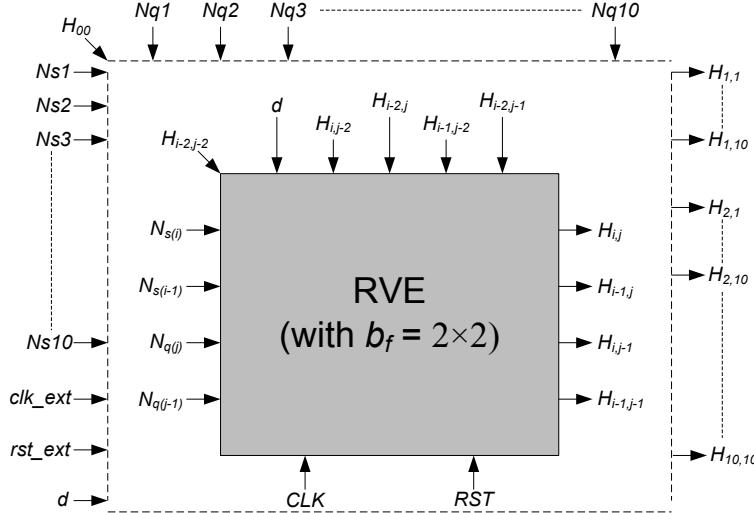

| 4.3  | Block diagram description of a 2D RVE design with $b_f = 2 \times 2$ . . . . .                                   | 56  |

| 4.4  | Block diagram representation of a $5 \times 5$ array using multiple RVE blocks with $b_f = 2 \times 2$ . . . . . | 57  |

| 4.5  | $5 \times 5$ array using RVE blocks with $b_f = 2 \times 2$ . . . . .                                            | 58  |

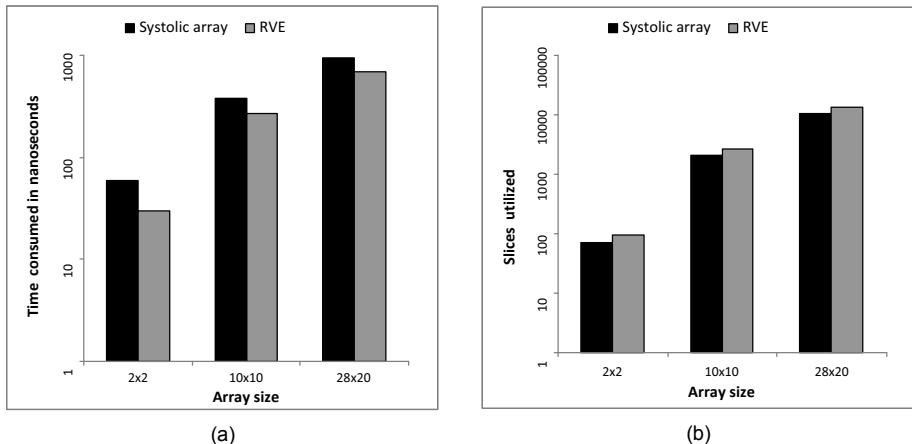

| 4.6  | Comparison between various 2D systolic array and 2D RVE implementations on a logarithmic scale . . . . .         | 59  |

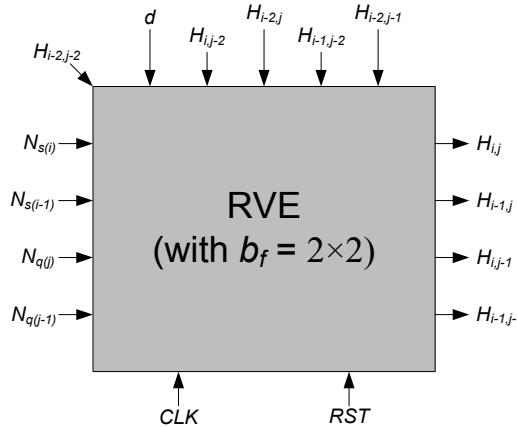

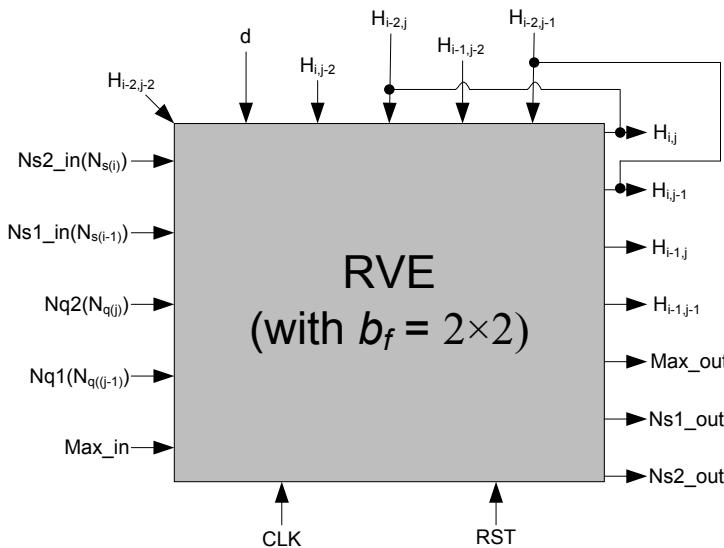

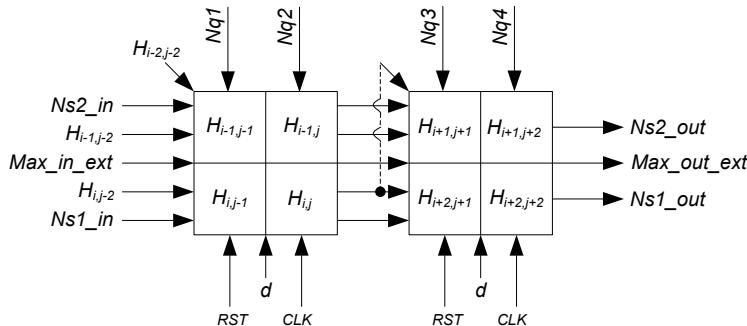

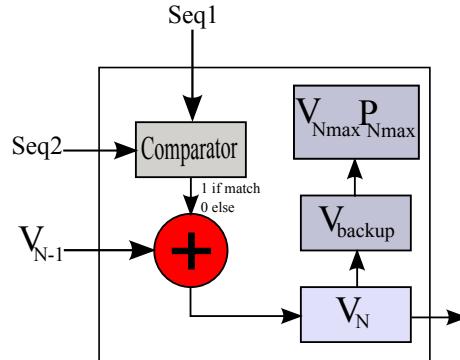

| 4.7  | Block diagram representation of the linear RVE design with $b_f = 2 \times 2$ . . . . .                          | 60  |

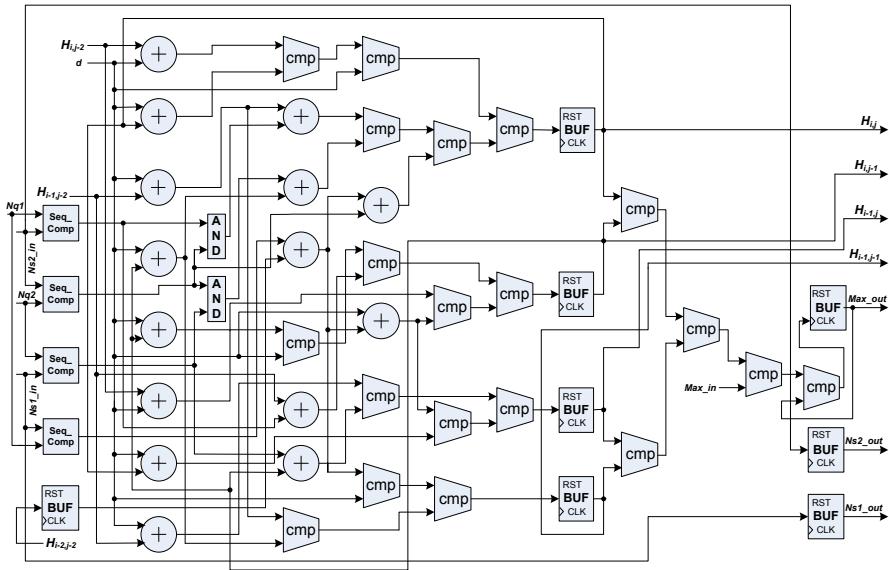

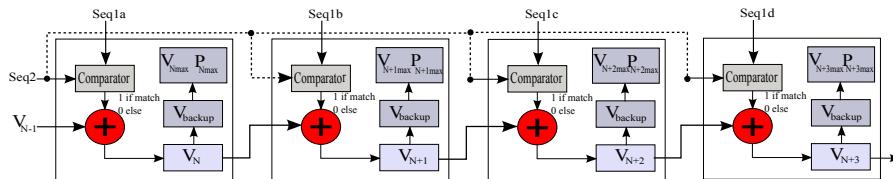

| 4.8  | Logical description of an RVE implementation with $b_f = 2 \times 2$ . . . . .                                   | 61  |

| 4.9  | 2-block linear RVE design . . . . .                                                                              | 62  |

| 4.10 | Comparison between various linear systolic array and linear RVE implementations on a logarithmic scale . . . . . | 63  |

| 4.11 | RVE designs with various blocking factors . . . . .                                                              | 64  |

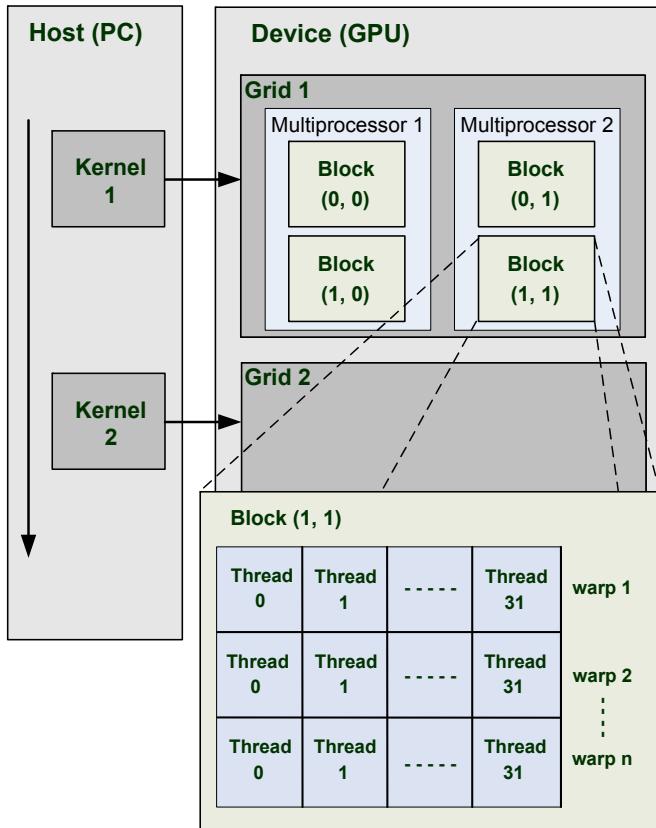

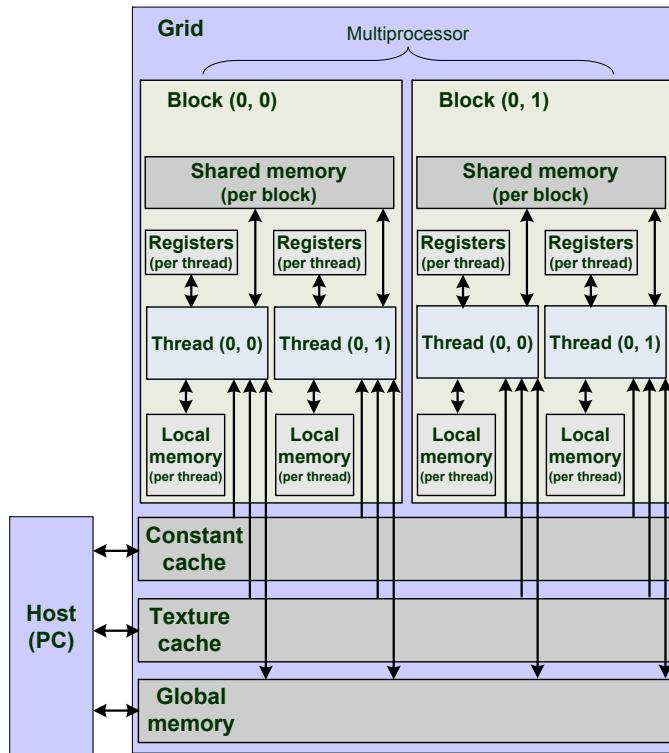

| 5.1  | CUDA hierarchy of threads, blocks and grids . . . . .                                                            | 70  |

| 5.2  | CUDA memory hierarchy . . . . .                                                                                  | 71  |

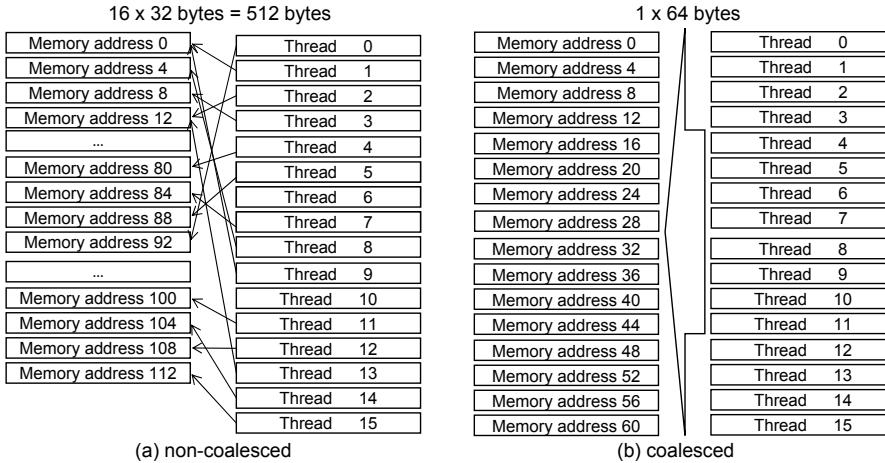

| 5.3  | The effect of coalescing on memory reads . . . . .                                                               | 72  |

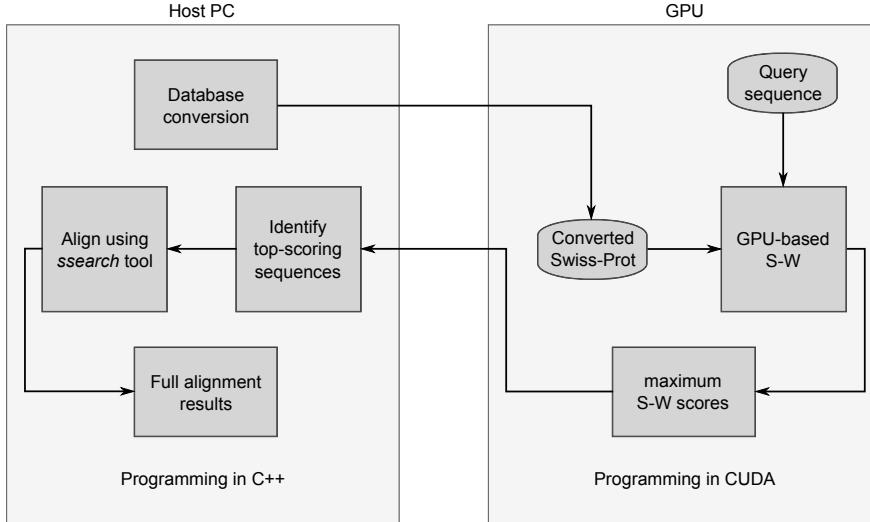

| 5.4  | Description of the GPU implementation . . . . .                                                                  | 74  |

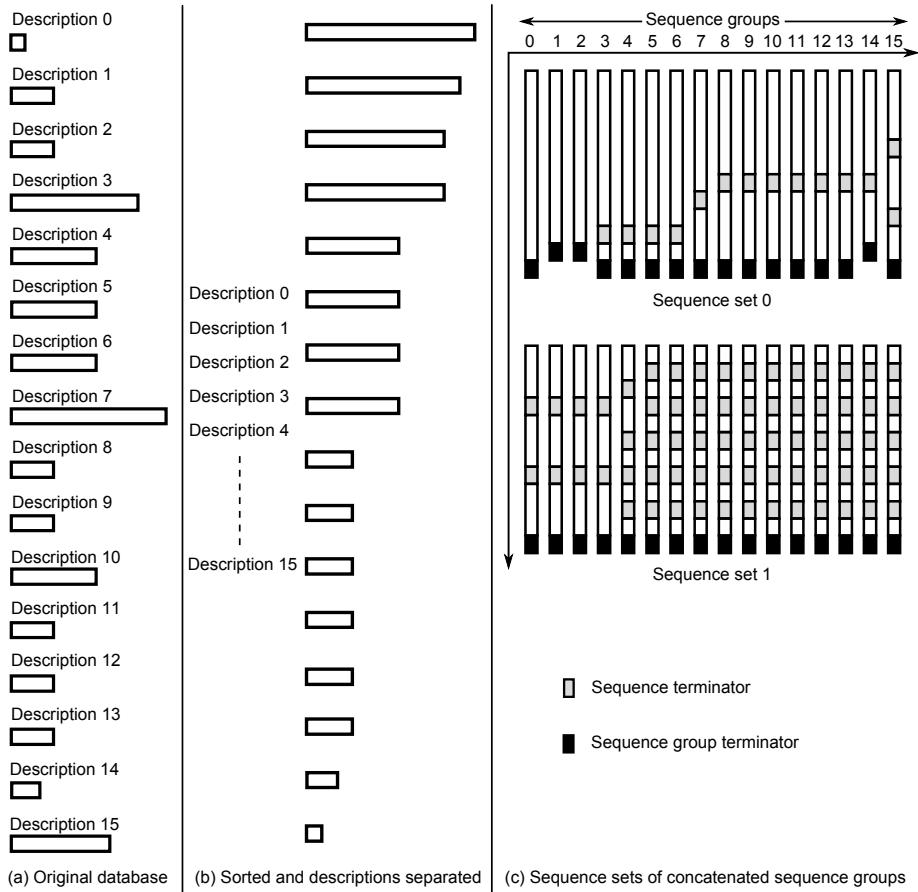

| 5.5  | The database conversion process . . . . .                                                                        | 75  |

| 5.6  | Sequence storing as interlaced subsets . . . . .                                                                 | 76  |

| 5.7  | Query profile . . . . .                                                                                          | 79  |

| 5.8  | (a) Execution time (b) Performance for query sequences of varying lengths . . . . .                              | 81  |

| 5.9  | Performance comparison . . . . .                                                                                 | 82  |

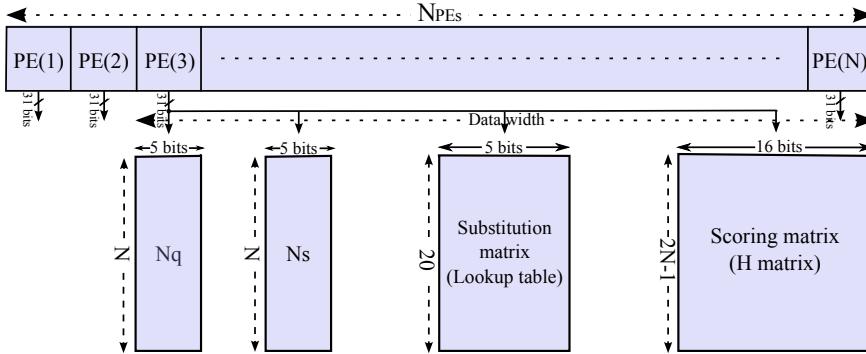

| 6.1  | System model for the S-W based sequence alignment . . . . .                                                      | 88  |

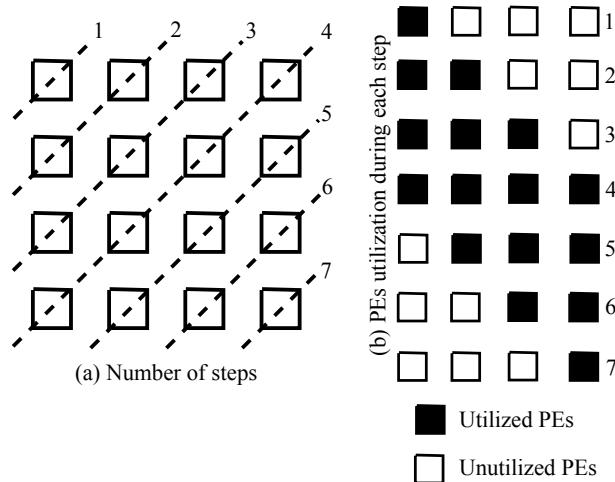

| 6.2  | Number of steps and PEs utilization during each step for $N = N_q = N_s$ . . . . .                               | 89  |

| 6.3  | Number of steps and PEs utilization during each step for $N < (N_q = N_s)$ . . . . .                             | 92  |

| 6.4  | Number of steps and PEs utilization (a) $N = N_q < N_s$ (b) $N < N_s < N_q$ . . . . .                            | 93  |

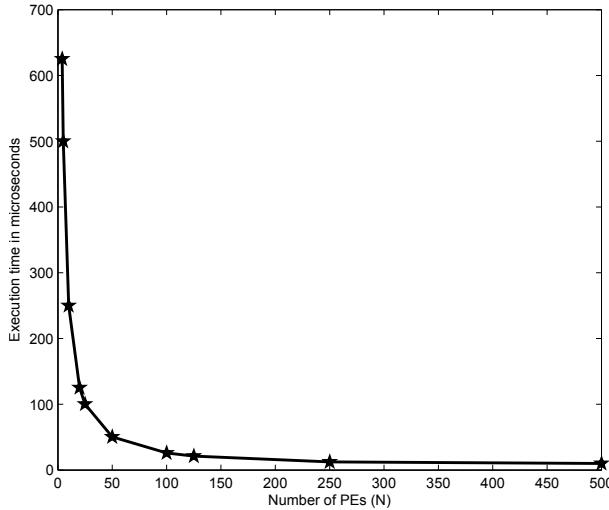

| 6.5  | $T_{exec}$ vs $N$ curve, limited by the computational resources . . . . .                                        | 95  |

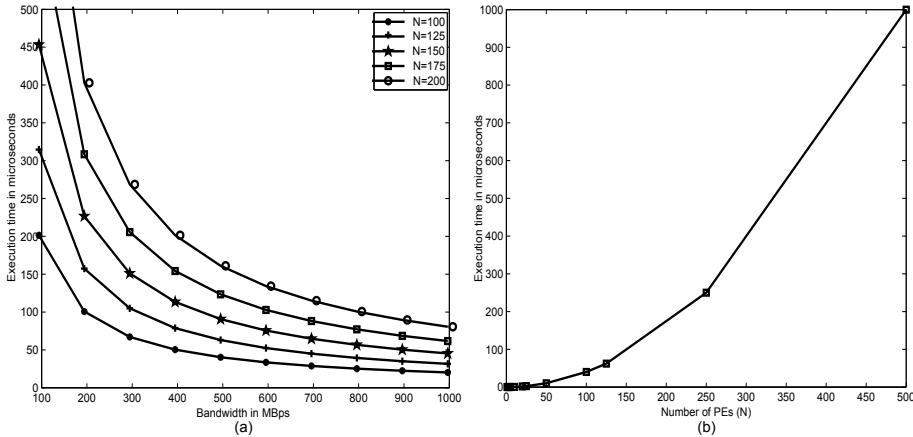

| 6.6  | Performance limited by bandwidth (a) $T_{exec}$ vs bandwidth (b) $T_{exec}$ vs $N$ . . . . .                     | 96  |

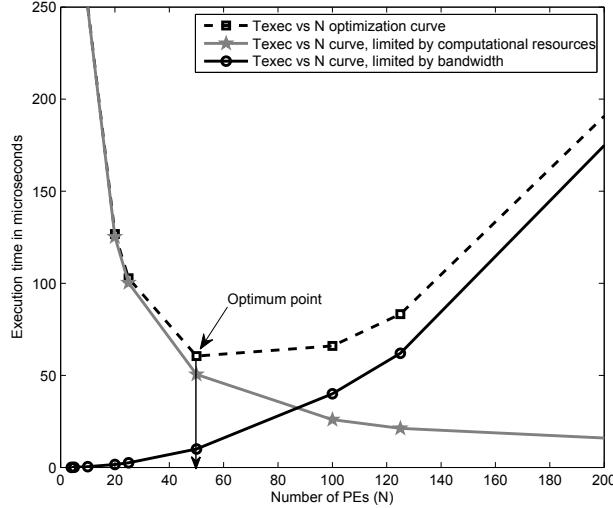

| 6.7  | $T_{exec}$ vs $N$ design trade off curves . . . . .                                                              | 97  |

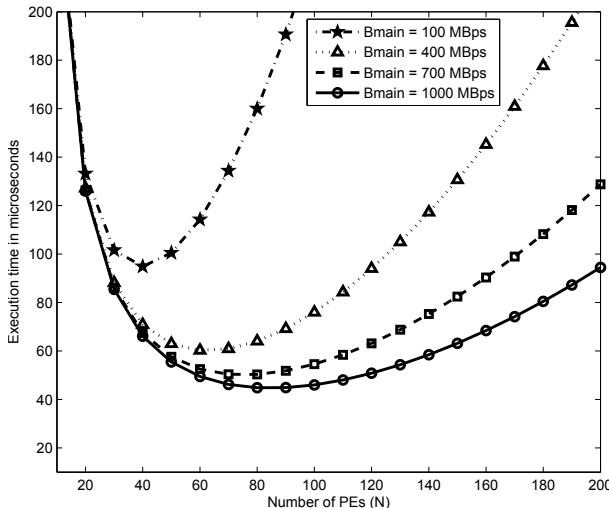

| 6.8  | $T_{exec}$ vs $N$ optimization curves . . . . .                                                                  | 98  |

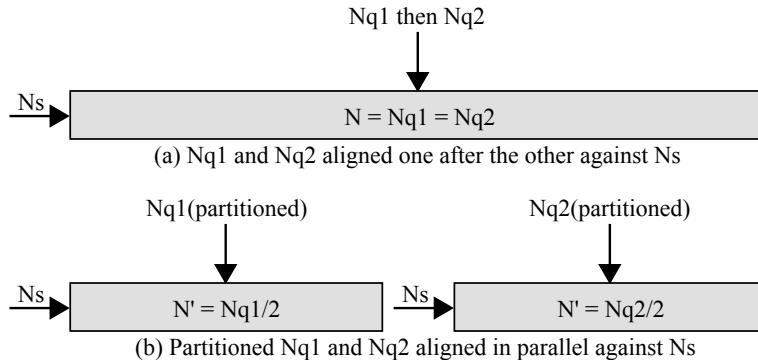

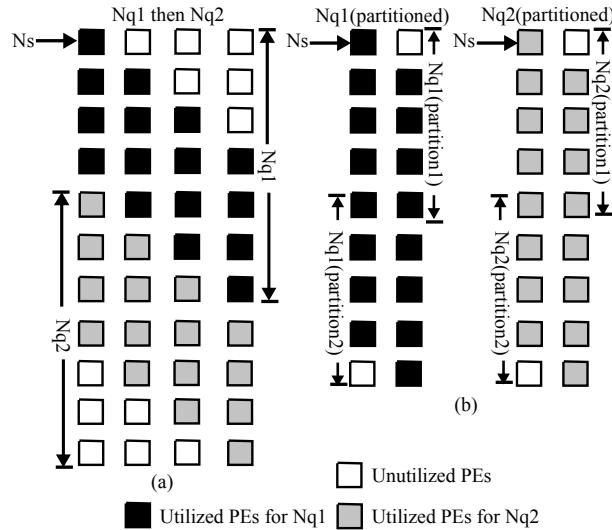

| 6.9  | 2-sequence alignment (a) Sequential (b) Partitioned and in parallel . . . . .                                    | 99  |

| 6.10 | 2-sequence alignment example . . . . .                                                                           | 101 |

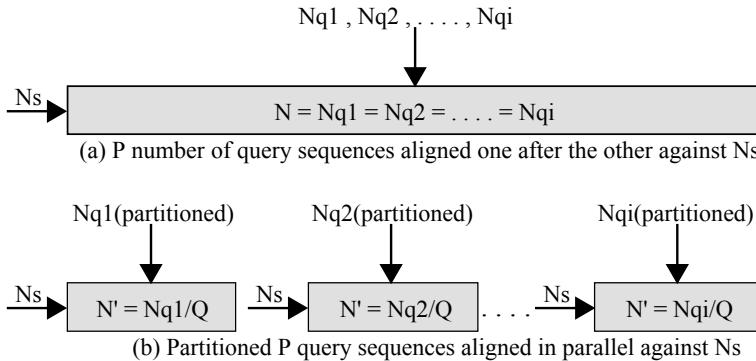

| 6.11 | $P$ -sequence alignment (a) Sequential (b) Partitioned and in parallel . . . . .                                 | 102 |

| 6.12 | Execution time reduction by hardware partitioning . . . . .                                                      | 103 |

| 6.13 | Resource utilization improvement by hardware partitioning . . . . .                                              | 104 |

| B.1  | Dot plot cell design . . . . .                                                                                   | 114 |

---

|     |                                                                         |     |

|-----|-------------------------------------------------------------------------|-----|

| B.2 | 4-element dot plot array . . . . .                                      | 114 |

| C.1 | Initialization step . . . . .                                           | 116 |

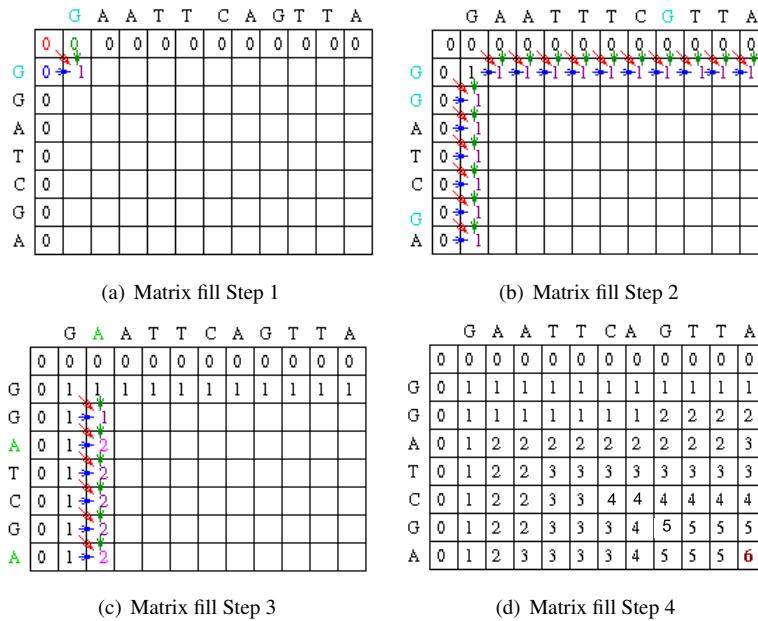

| C.2 | Matrix fill (a) Step 1, (b) Step 2, (c) Step 3 and (d) Step 4 . . . . . | 117 |

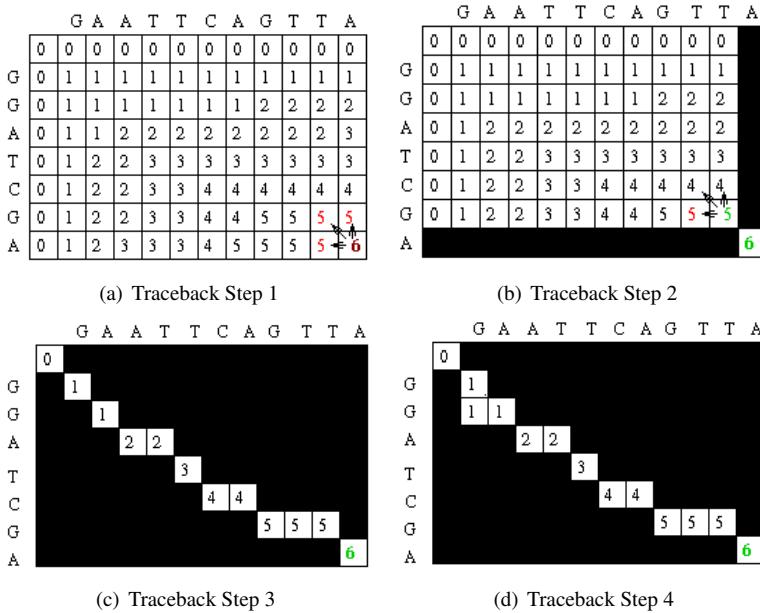

| C.3 | Traceback (a) Step 1, (b) Step 2, (c) Step 3 and (d) Step 4 . . . . .   | 118 |

| C.4 | Matrix fill for Example 2 . . . . .                                     | 120 |

| C.5 | Traceback for Example 2 . . . . .                                       | 121 |

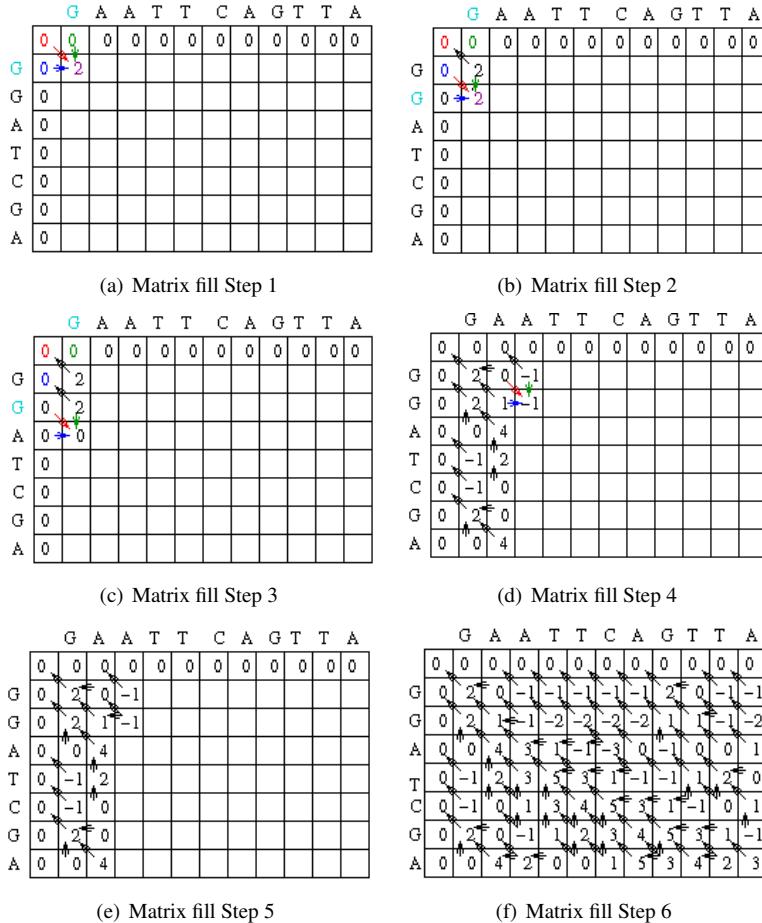

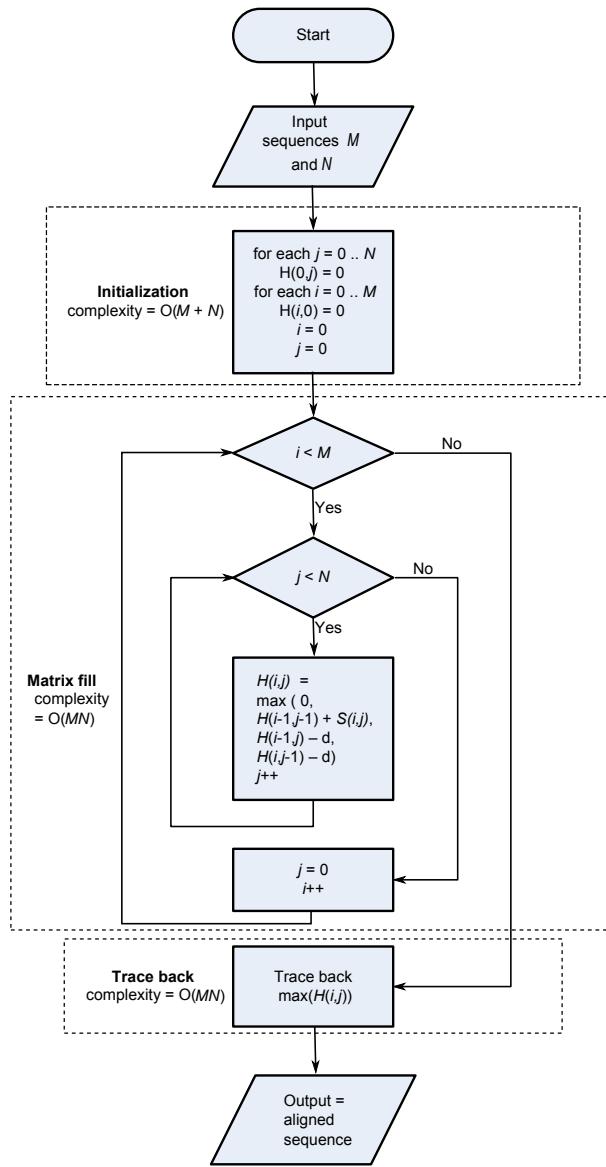

| D.1 | Smith-Waterman flow chart . . . . .                                     | 124 |

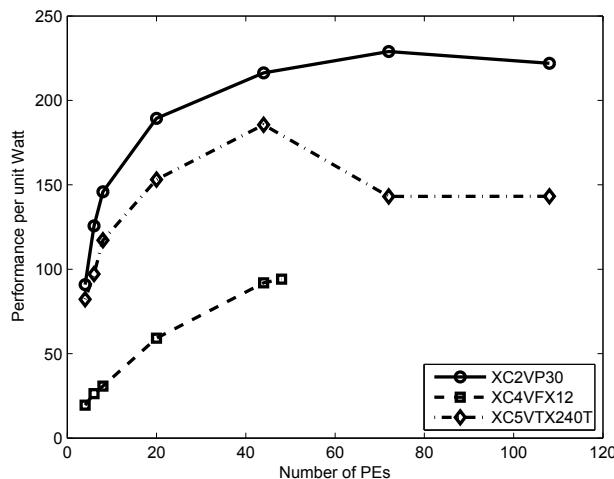

| E.1 | Performance per unit Watt for S-W based sequence alignment . . . . .    | 131 |

# Abbreviations and Symbols

|              |   |                                      |

|--------------|---|--------------------------------------|

| <b>1D</b>    | - | 1-dimensional or linear              |

| <b>2D</b>    | - | 2-dimensional                        |

| $b_f$        | - | blocking factor                      |

| <b>A</b>     | - | Adenine                              |

| <b>BLAST</b> | - | Basic Local Alignment Search Tool    |

| <b>BRAM</b>  | - | Block RAM                            |

| <b>C</b>     | - | Cytosine                             |

| <b>CCU</b>   | - | Custom Computing Unit                |

| <b>CUDA</b>  | - | Compute Unified Device Architecture  |

| <b>CUPS</b>  | - | Cell Updates Per Second              |

| <b>DDR</b>   | - | Double Data Rate                     |

| <b>DNA</b>   | - | Deoxyribonucleic Acid                |

| <b>DOPA</b>  | - | Database Optimized Protein Alignment |

| <b>DP</b>    | - | Dynamic Programming                  |

| <b>FASTA</b> | - | Fast Alignment Search Tools - All    |

| <b>FPGAs</b> | - | Field Programmable Gate Arrays       |

| <b>G</b>     | - | Guanine                              |

| <b>GPUs</b>  | - | Graphic Processing Units             |

| <b>gprof</b> | - | GNU profiler                         |

| <b>HGP</b>   | - | Human Genome Project                 |

| <b>HMMs</b>  | - | Hidden Morkov Models                 |

| <b>HSPs</b>  | - | High-scoring Segment Pairs           |

|                |                                                            |

|----------------|------------------------------------------------------------|

| <b>INSDC</b>   | - International Nucleotide Sequence Database Collaboration |

| <b>MGAP</b>    | - Micro Grained Array Processor                            |

| <b>NCBI</b>    | - National Center for Biotechnology Information            |

| <b>N-W</b>     | - Needleman-Wunsch                                         |

| <b>PE</b>      | - Processing Element                                       |

| <b>PIR</b>     | - Protein Information Resource                             |

| <b>QSP</b>     | - Query Sequence Partitioning                              |

| <b>RNA</b>     | - Ribonucleic Acid                                         |

| <b>RTR</b>     | - Run-time Reconfiguration                                 |

| <b>RVE</b>     | - Recursive Variable Expansion                             |

| <b>S-W</b>     | - Smith-Waterman                                           |

| <b>ssearch</b> | - Smith-Waterman search                                    |

| <b>SIMD</b>    | - Single-Instruction stream, Multiple-Data stream          |

| <b>T</b>       | - Thymine                                                  |

| <b>tRNA</b>    | - transfer-RNA                                             |

| <b>U</b>       | - Uracyl                                                   |

# Introduction

With the ever increasing volume of data in the bioinformatics databases, the time for comparing a query sequence with the pre-existing sequences in the databases is always increasing. Researchers in various communities are working on accelerating the available methods for comparing and aligning these sequences. This thesis presents one such work. This chapter provides a brief overview of bioinformatics in general with a particular emphasis on sequence alignment.

The chapter starts with an overview of molecular biology, presented in Section 1.1. It is followed by an introduction to bioinformatics, sequence alignment, its types and applications, presented in Section 1.2. Further, it presents the acceleration approaches for sequence alignment in Section 1.3 followed by an overview of the thesis contribution. An outline of the thesis is presented in Section 1.4. The chapter concludes with a summary, presented in Section 1.5.

## 1.1 Molecular biology - an overview

The field of bioinformatics is the application of computer science to biology in general and molecular biology in particular. This can involve the development of algorithms and software that can analyze huge amounts of data, the automation of previously labor intensive tasks, or the creation of tools, for example with which to view 3D models of biological structures. Although no in-depth knowledge of the chemical processes involved is required from the perspective of computer scientists and hardware design experts, subjects such as *Deoxyribonucleic Acid (DNA)* and protein construction are integral to understanding the relevance of research topics like sequence alignment. In the following subsections, a recap of the basics of molecular biology is presented.

### 1.1.1 Cells, amino acids and proteins

All living organisms consist of one, or many more, of a basic functional unit, the cell. Classified as being ‘alive’ (the smallest organisms consist of a single cell), cells can process and excrete molecules (metabolism), alter their electrical potential and procreate by cell division. Many of the processes inside cells are governed by proteins. Proteins are complex chains of molecules called amino acids. Some amino acids, the ‘non-essential’ ones, can be synthesized by the cell. The other, essential, amino acids must be procured through the ingestion and breakdown of proteins in foods such as meat. Again, this breaking down of food products is performed by proteins, this time existing outside of any cell.

Proteins exist for a wide array of functions, for instance *actin* aids in muscle contraction while the proteins of the cytoskeleton form a cell’s ‘skeleton’, giving it its shape and protection. Another important role of proteins is to act as a catalyst, where the proteins are called enzymes. Enzymes act as catalysts by binding to the reagents of a reaction and lowering the activation energy required for it to take place. Designed to only be compatible with those specific reagents due to their structure, enzymes are not consumed in the reaction and can be reused. Returning to the example of breaking down food into nutrients, there are enzymes that split proteins into their component amino acids, enzymes which break down fat molecules and enzymes that allow ingested nucleic acid to be reused for the construction of DNA.

### 1.1.2 Chromosomes and DNA

The cells require the presence of proteins, both internally and externally, to survive. In fact, the reproduction of cells relies heavily on proteins too, such as those of the aforementioned cytoskeleton facilitating the division of the cell membrane. Proteins are created, from scratch and to specification, within the cell itself. This is where the DNA comes in. DNA is stored in structures called chromosomes. Made up of the DNA molecules and a supporting protein packaging, chromosomes are ‘wadded up’ in the cell similar to a ball of string. Attached to these chromosomes, the DNA is protected and more compact; this way it is able to fit in the cell (nucleus). The structure and number of chromosomes varies on a per species bases, additionally the shape of chromosomes is also determined by what stage of its life cycle the cell currently resides in.

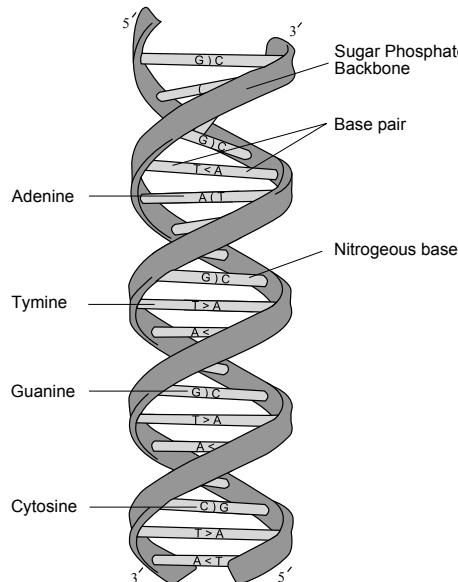

The DNA itself contains the genetic instructions that describe how the various proteins should be constructed. The structure of DNA is shown in Figure 1.1. Structurally, DNA consists of two long, coiled nucleotide polymer strands that take the well-known double-helix form. These polymers are strengthened by a skeleton of sugars and phosphate groups, connected to these sugars are the bases, pairs of molecules that specify the genetic code. Each strand of DNA has one end called the 3' end, the other end is called the 5' end. Due to the anti parallel nature of the strands, their ends are mirrored. When talking about DNA, these ends can be used to indicate in which direction a strand is being built/interpreted/etc.

Figure 1.1: The structure of DNA

Four different bases exist, i.e. *adenine (A)*, *cytosine (C)*, *guanine (G)* and *thymine (T)*. A base on one strand will be matched by its twin base on the other strand and connected to it using hydrogen bonds. Adenine is always paired with thymine whereas cytosine and guanine form the second combination. This duplication of the bases is central to the replication of DNA, and as such, to that of the cell and the survival of the host organism.

During the replication of DNA mutations can occur, altering the genes of a host organism. This ties into the theory of evolution and the field of phylogenetics, the study of relatedness among organisms by comparing their genetic makeup.

### 1.1.3 RNA and transcription

The bases of DNA can be seen as letters (A, C, G and T). These letters are interpreted in words of three, called codons. Each codon describes a single amino acid, the building blocks of proteins. A portion of DNA that codes for a protein is known as a gene. As there are four bases and they appear in words of three, there exist 43 possible codons. However, only 20 different amino acids are encoded. This means that some words code for the same amino acid. Additionally, some words have special functions: the start (ATG) and stop (TAG, TAA, TGA) codons function as markers to aid in the correct interpretation of the code at the RNA stage. A sequence of codons that starts with a start codon and ends with a stop codon is called an open reading frame. The process of interpreting the genetic code and using it to synthesize proteins

is called genetic expression. The first step is the generation of *ribonucleic acid (RNA)*, which will mirror the gene in question and be transported to the cell's 'protein factory'. Genes are transcribed to RNA by an enzyme called RNA polymerase. This is bound to the correct place on the DNA by means of a promoter, which is a sequence of codons that influences the binding of RNA polymerase directly or indirectly by means of proteins. The DNA strand, the RNA will be based on, is called the coding strand. When generating RNA, the strands are separated and the complementary strand, called the template strand, is walked in the 3' → 5' direction. The strand's bases are then paired with a new strand of again complementary bases (with thymine replaced by *uracyl (U)*). This is the RNA. This strand is separated from the DNA once transcription is complete, after which the DNA's structure is restored. In effect, the created RNA is a copy of the coding strand with T replaced by U.

Example: consider a strand of DNA coding a gene:

5' A T G G C C T G G A C T T C A ... 3' coding strand

3' T A C C G G A C C T G A A G T ... 5' template strand

The resultant RNA will then be:

5' A U G G C C U G G A C U U C A ... 3'

Note the start codon ATG (AUG for the RNA). This RNA is transported to the ribosomes, the cell components which assemble proteins by chaining together amino acids. Here the RNA is walked and interpreted from the start to the stop codon. The codons are interpreted by means of *transfer-RNA (tRNA)*. These molecules also contain a complementary codon to match with the RNA and carry an amino acid to link up to the protein. The ribosomes themselves again consist of proteins and ribosomal RNA.

This recap of genetic expression glosses over many things, including introns/exons, the various RNA types, DNA/RNA quality control and the roles of proteins such as repressors. Although the process is more involved than described here, especially in humans, more information is not required to understand the basics of bioinformatics and sequence alignment, presented in the next section. Readers interested in further details may refer to [1] and [2].

## 1.2 Bioinformatics

Biology is in the middle of a major paradigm shift, driven by computing technology. Two decades before the formal inauguration of the *Human Genome Project (HGP)*, a new hybrid field (partly molecular biology and partly computer science) began to emerge. The new field was called *computational molecular biology* or *bioinformatics*, which may be defined as a discipline that generates computational tools, databases, and methods to support genomic and post genomic research. Bioinformatics is the multidisciplinary research area aimed at organizing and classifying the immense rich-

ness of sequence data, where the sequence may refer to either DNA or protein.

Bioinformatics employs a digital language for representing its information using the four basic alphabets (A, C, G, T). All the DNA molecules in an organism's cell have been represented and being identified using these alphabets. The tools of computer science, statistics and mathematics are very critical for studying bioinformatics. Some of the recent advances happened include improved DNA sequencing methods, new approaches to identify protein structure and revolutionary methods to monitor the expression of many genes in parallel. The following subsection presents major fields of bioinformatics.

### 1.2.1 Fields of bioinformatics

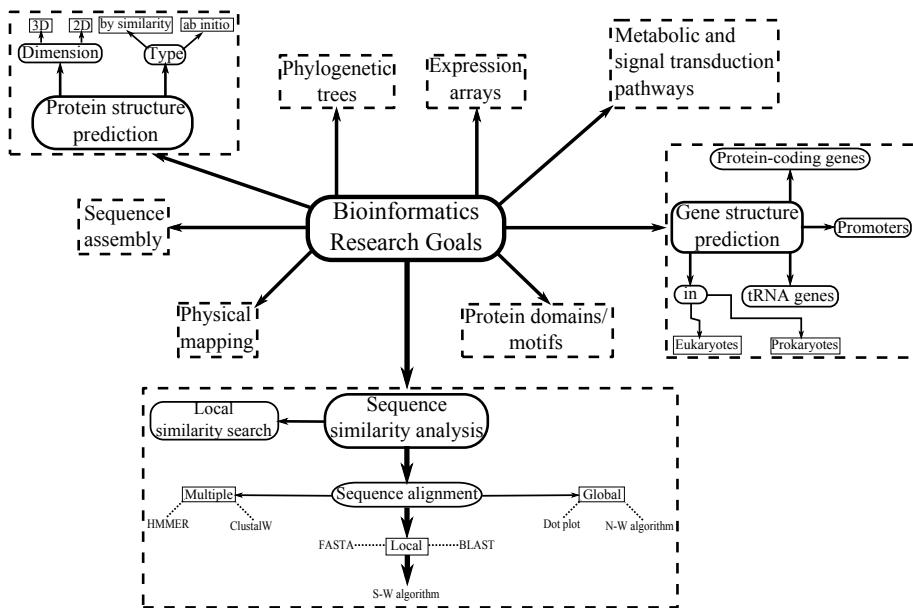

A wide variety of research topics are being explored by researchers in the diversified field of bioinformatics. Examples are, gene structure prediction, phylogenetic trees, protein structure prediction (2D, 3D), sequencing (i.e. mapping) genomes etc. Figure 1.2 gives a broad classification of major research areas in bioinformatics.

Figure 1.2: Classification of bioinformatics research areas

The relevant field among these to this thesis is the sequence similarity analysis or *sequence alignment*. A significant part of bioinformatics is the analysis of sequences, where the sequences of interest in molecular biology are those of DNA and proteins. As discussed before, DNA consists of the four bases A, C, G and T. One might say that DNA is a sequence, or string, of the alphabet {A,C,G,T}. Not surprisingly, RNA can

be looked at similarly, with the alphabet {A,C,G,U}. Whereas, proteins, too, can be viewed as strings of an alphabet [3]. In this case, the alphabet of the 20 amino acids is {A,C,D,E,F,G,H,I,K,L,M,N,P,Q,R,S,T,V,W,Y}. The amino acids corresponding to these letters are shown in Table 1.1.

Table 1.1: The 20 amino acids

| Letter | Amino acids   | Letter | Amino acids   | Letter | Amino acids   | Letter | Amino acids |

|--------|---------------|--------|---------------|--------|---------------|--------|-------------|

| A      | Alanine       | Q      | Glutamine     | L      | Leucine       | S      | Serine      |

| R      | Arginine      | E      | Glutamic acid | K      | Lycine        | T      | Threonine   |

| N      | Asparagine    | G      | Glycine       | M      | Methionine    | W      | Tryptophan  |

| D      | Aspartic acid | H      | Histidine     | F      | Phenylalanine | Y      | Tyrosine    |

| C      | Cysteine      | I      | Isoleucine    | P      | Proline       | V      | Valine      |

Numerous projects for sequencing the DNA of particular organisms constantly supply new amounts of data on an enormous scale [4], with a doubling time estimated to be 9-12 months. The bioinformatics industry has grown to keep up pace with this information explosion, growing at 25-50% a year. In 2000, the US market Research company, Oscar Gruss [5] estimated that the value of the bioinformatics industry would touch \$ 2 billion. With the ever increasing volume of sequence data in various bioinformatics databases from *International Nucleotide Sequence Database Collaboration (INSDC)* [6] (e.g. “public” repositories of gene data like GenBank from *National Center for Biotechnology Information (NCBI)* [7], *SwissProt* from the *Swiss Institute of Bioinformatics* [8] and *PIR* from the *Protein Information Resource* [9]), the time for comparing a query sequence with the available databases is always increasing. It could take weeks to months for a researcher to search sequences by hand in order to find related genes or proteins. Computer technology has provided the obvious solution to this problem. Not only can computers be used to store and organize sequence information into databases, but they can also be used to analyze sequence data rapidly. The evolution of computing power and storage capacity has, so far, been able to outpace the increase in sequence information being created. Theoretical scientists have derived new and sophisticated algorithms which allow sequences to be readily compared using probability theories. These comparisons become the basis for determining gene function, developing phylogenetic relationships and simulating protein models. On the other hand, hardware design experts have been working on designing and accelerating the more accurate methods of sequence alignment. In the following subsections, sequence alignment, its types and application are elaborated.

## 1.2.2 Sequence alignment and its types

In most common terms sequence alignment may be defined as an arrangement of two or more DNA or protein sequences to highlight the regions of their similarity. This, in turn indicates the genetic relatedness between the organisms. The similarity may be a consequence of functional, structural or evolutionary relationship between

the sequences [10]. New DNA, RNA and protein sequences develop from the pre-existing sequences rather than get invented by nature from the scratch. This fact is the foundation of any sequence analysis.

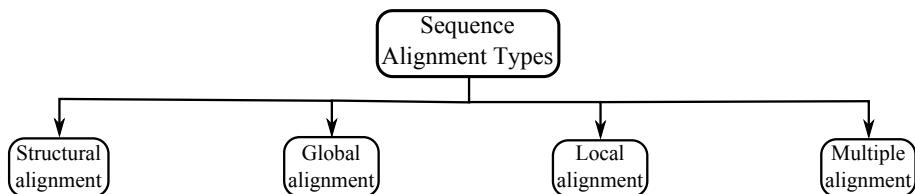

If two DNA, RNA or amino acid sequences are similar, there is a chance that they are homologous. Homologous sequences share a common ancestral sequence, their relative differences are the result of mutations. These mutations might manifest in various ways: substitutions, where one symbol is replaced by another, insertions where a new symbol is inserted into the sequence and deletions, the removal of a symbol. To establish the degree of homology, the sequences are aligned i.e. lined up in such a way that the degree of similarity is maximized. This process is known as sequence alignment, which can be classified into various types as shown in Figure 1.3. Following is a brief description of these types.

Figure 1.3: Types of sequence alignment

### Structural alignment

Structural alignment [11] is an approach of attempting to infer similarity between proteins by comparing their three dimensional shapes, or tertiary structures. As a protein's shape is determined by its amino acid makeup, which, in turn, determines its function, it is obvious that structural alignment is an attractive tool for homology research. In fact, different protein letter sequences might result in similar 3D structures, where protein structure is better evolutionary conserved than sequence [12]. Unfortunately, determining the tertiary structure of proteins requires costly, time consuming procedures such as X-ray crystallography and nuclear magnetic resonance imaging (bioinformatics databases contain much less protein structures than sequences) [2]. One field of bioinformatics, i.e. protein structure prediction concentrates on unraveling the mysteries behind protein folding, the process in which an unfolded random coil amino acid takes its characteristic tertiary structure. Using computational protein folding, any of the myriad available protein sequences could be converted to a 3D representation. Then, in turn, structural alignment could be used to infer homology. Currently, however, protein folding is still an open problem and current approaches have such high computational requirements that researchers have turned to super or distributed computing [13]. Although mainly used for proteins, structural alignment is also promising for strands of RNA [14]. It is not suitable for DNA as this always takes the double-helix structure.

## Global alignment

Global alignment methods operate directly on all sequence letters. The idea is to line up two (or more) sequences so that their degree of similarity is maximized. For DNA and RNA this means matching identical bases. In the case of proteins, amino acids are matched if they are identical or can be derived from one another through likely to occur substitutions [2]. Although matching two sequences directly will take into account substitution/mutations to handle insertions and deletions, the notion of *gaps* is introduced. Marked by the symbol ‘-’, a gap can be chosen to be inserted into any of the sequences to obtain a closer match. Following is an example with the base sequences TACCACT and CCCGTAA:

| No gaps |   |   |   |   |   |   |   |   |

|---------|---|---|---|---|---|---|---|---|

| T       | A | C | C | A | G | T |   |   |

| C       | C | C | G | T | A | A |   |   |

| Gaps    |   |   |   |   |   |   |   |   |

| T       | A | C | C | A | G | T | - | - |

| C       | - | C | C | - | G | T | A | A |

Clearly the alignment with gaps is more relevant and better exposes the similarities between both sequences. Note that other alignments are possible. An option would be:

|   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|

| T | A | C | C | A | G | T | - | - |

| - | - | C | C | C | G | T | A | A |

As multiple alignments are possible even in this simple case, it makes sense to devise a way to rate and then select the best alignment(s). A simple method to accomplish this is to assign scores to the alignment letters. A simple scheme is 1 for a match, -1 for a mismatch and -2 for a gap. Such a scheme is said to have a *linear gap penalty*. A more advanced method is to introduce an *affine gap penalty*, which assigns different scores to the starting of a new gap and the extension of a current one. Generally, starting a new gap is given the largest penalty as this is biologically the hardest [15]. Using the aforementioned scoring system, the first gapped alignment scores  $(-1-2+1+1-2+1+1-2-2) = -5$  and the second option does so as well with  $(-2-2+1+1-1+1+1-2-2) = -5$ . So in this case, both gapped alignments are ‘as good’ as one another. However, this does not automatically mean they both have the same biological relevance. To judge how relevant an alignment’s score is, probabilistic methods can be used. The idea is to check whether the probability of an alignment attaining the score in question is adequately small (Chapter 7 of [15]). In case of using an affine gap penalty, the second alignment would have the best score, as it contains two gaps instead of three. The same approach can be used for amino acids as opposed to DNA bases. Instead of working with fixed scores, amino acid substitutions have been rated by their evolutionary likeliness and are available as standard  $20 \times 20$  triangular substitution matrices. The two most well known matrices are the PAM and BLOSUM families. Table 1.2 shows the BLOSUM62 matrix. Example of global alignment is the *Needleman-Wunsch (N-W)* algorithm [16].

Table 1.2: The BLOSUM62 amino acid substitution matrix

## Local alignment

Local alignments are similar to global ones. The only difference is that instead of attempting to align the complete sequences to one another, portions of similarity are aligned. Following is an example with sequences GTGTACTCCAGAG and GTACC-CAAG:

## Global alignment

|   |   |   |   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| G | T | G | T | A | C | T | C | C | A | G | A | G |

| G | - | - | T | A | C | - | C | C | A | - | A | G |

## Local alignment

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| G | T | G | T | A | C | T | C | C | - | A | G | A | G |

| - | - | G | T | A | C | - | C | C | A | A | G | - | - |

Looking for a local alignment will better expose ‘patches’ of homology in two relatively dissimilar sequences. Thus it might lead to more biologically relevant results [15]. Example of local alignment is the *Smith-Waterman* (*S-W*) algorithm [17].

## Multiple alignment

The previous examples focused on aligning just two sequences, but in some cases it might be interesting to consider the similarities between a group of sequences. For example, if the structure of a protein is unknown, a similarity to a group of other proteins might give clues. Global and local alignment algorithms can be adapted to deal with multiple alignments, though this quickly becomes extremely computationally expensive. An alternative is to use specifically designed heuristic algorithms, for example *ClustalW* [18].

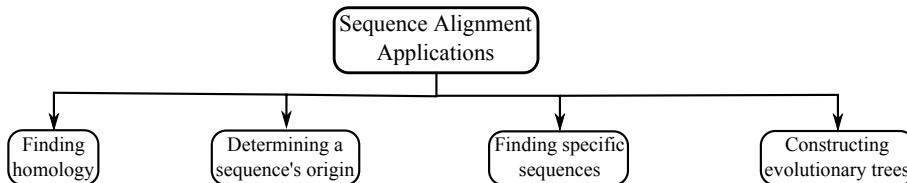

### 1.2.3 Applications of sequence alignment

Sequence alignment has many applications in bioinformatics. Figure 1.4 presents some examples. Following is a brief description of these applications.

Figure 1.4: Examples of sequence alignment applications

### Finding homology

One of the main uses for sequence alignment is to find homology. Homology means that two sequences share a common ancestor; evolution says that all cells must eventually trace back to the same ancestor. Finding homology between organisms might enable knowledge of one to be applied to the other, or to infer the function of one organism's gene from that of a related species.

### Determining the origin of a sequence

If a DNA or protein sample is recovered but its originating species are unknown, sequence alignment can be used to find likely sources, i.e. the known sequences most closely matching the sample.

### Finding specific sequences

Suppose we have discovered the function of a part of species  $X$ 's genetic code. Then it might be attractive to search species  $Y$ 's code for the sequence. If something similar is found, it might give clues as to the location of a similar gene in  $Y$ . Similarly, suppose that we might have found the piece of code that expresses a trait, such as a physical characteristic or the presence of a genetic disease, in one piece of genetic code. Searching other pieces known to either feature or lack this trait might help validate or disprove the theory.

### Constructing evolutionary trees

From homology data, evolutionary (phylogenetic) trees can be constructed [15]. These trees are built using the 'genetic distance' between species and give insight into species relationships and the course of evolution. Using the concept of an evolutionary rate, the species' sequence homology can be translated into the time they took to develop from ancestral species. The actual construction of the tree can be done in many ways; examples include maximum parsimony methods (building the tree such that the lowest amount of evolutionary change is required) and distance methods such as the UPGMA algorithm which builds the tree from the result matrix of a multiple alignment.

The information presented in this section is annexed by the definitions of some important bioinformatics terms given in Appendix A. In the next section, acceleration of sequence alignment is presented followed by an overview of the thesis contribution.

## 1.3 Acceleration of sequence alignment

This section presents a broad classification of the methods used for acceleration of sequence alignment applications. Furthermore, it provides an overview of the contributions of this thesis for acceleration, analysis and optimization of such applications.

### 1.3.1 Methods of acceleration

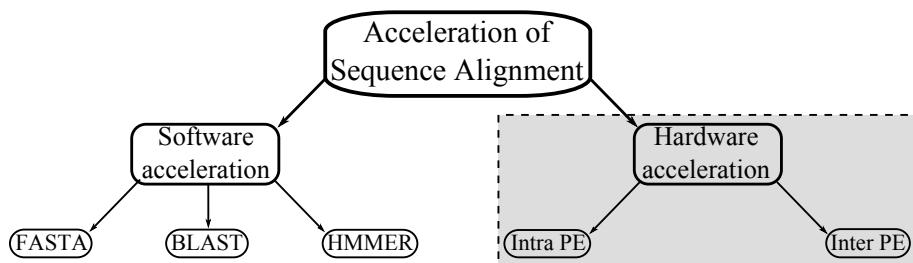

Figure 1.5 presents a broad classification for acceleration of sequence alignment applications. The figure shows that the acceleration of sequence alignment applications can either be in hardware or software. However, the main focus of the thesis is on hardware acceleration, as shaded in the figure.

Figure 1.5: Broad classification of sequence alignment acceleration

### Software acceleration

Heuristics based algorithmic modifications are done to achieve faster software implementations of the sequence alignment applications, as done in FASTA, BLAST and HMMER. These software implementations do not guarantee an optimal alignment though. Following is a brief description of such heuristics based software implementations.

**FASTA:** FASTA was developed in 1985 by Lipman and Pearson [19]. Unlike the N-W and S-W algorithms, FASTA approximates the optimal alignment by searching and matching k-tuples (i.e. subsequences of length k). The algorithm assumes that related proteins will have regions of identity. By searching with k-tuples, the FASTA algorithm allows small regions of local identity to be found quickly. For proteins, these k-tuples tend to be of length two.

**BLAST:** BLAST [20] is similar to the FASTA algorithm, however, it uses words ( $w$ ) instead of  $k$ -tuples. The computational complexity of both FASTA and BLAST comes out to be  $O(MN)$ . The space complexity for FASTA is  $O(MN)$ , whereas for BLAST, it is higher than all other algorithms and it comes out to be  $O(20^w + MN)$ , where  $w$  is the word size.

**HMMER:** HMMER uses *Hidden Markov Models (HMMs)* which are widely used in biological sequence analysis. HMMs are a probabilistic tool which can be used for sequence alignment [21], finding sequences in genetic code [2], inferring protein structure or building profiles of DNA and proteins [15]. Such profile HMMs can be used to determine whether a sequence is part of a family of DNAs or proteins. HMMs are based on the probability of a sequence adhering to certain characteristics. To determine these probabilities, machine learning principles are used. In the case of a profile HMM, the learning set is a multiple alignment. HMMs originated and still play a significant role in speech recognition [22].

## Hardware acceleration

The heuristics based software implementations just described improves the performance at the cost of loosing accuracy. In contrast methods like the S-W algorithm provides accurate and optimal solution. But based on exhaustive search, the limitation of such methods is that they become too slow in practical situations, particularly for long sequences. The focus of the thesis is on hardware acceleration of such accurate methods on platforms like *Field Programmable Gate Arrays (FPGAs)* and *Graphic Processing Units (GPUs)*, which can either be related to the design of the basic *Processing Element (PE)* called *intra PE level* or related to multiple PEs organization called *inter PE level*. Following is a description of the acceleration at both levels.

**Intra PE level:** At this level of hardware acceleration, a basic building block, called the PE is designed for a sequence alignment application. The PE is capable of performing comparison between individual characters of the query and database sequences and is optimized for high performance and/or efficient resource utilization. In the later chapters of the thesis, such designs and optimizations are presented in detail. More specifically, high performance PE designs for systolic array and *recursive variable expansion (RVE)* based implementations are presented.

**Inter PE level:** At the inter PE level, the organization and interconnection of the PEs is optimized for high performance, efficient resource and bandwidth utilization. In this thesis, the PEs organized in *2-dimensional (2D)* and *1-dimensional or linear (1D)* systolic array fashion are presented. Further, 2D and 1D RVE implementations are discussed and compared with the corresponding systolic array implementations. Additionally, high performance GPU-based sequence alignment is presented that eliminates the need for inter PE communication. Also,

the issues related to bandwidth requirement and hardware redundancy are discussed in detail and performance and bandwidth optimizations are presented. Furthermore, an approach for high performance and resource efficient biological sequence alignment is presented. The succeeding chapters of the thesis give an insight to such optimizations and analysis.

### 1.3.2 Thesis contribution

The research performed in the course of this thesis has contributed in a number of ways to the hardware acceleration, performance optimization and analysis of bioinformatics sequence alignment applications. Different ways and means have been explored to accelerate such applications. Further, detailed performance analysis has been carried out, considering the limiting factors like computational resources and memory bandwidth. Following are the details of the contribution.

- A review of hardware acceleration of sequence alignment applications and their comparisons based on various parameters [23] is presented Chapters 2 and 3.

- An accurate profiling and acceleration evaluation procedure has been proposed [24] and presented in Chapter 3.

- An efficient and high performance systolic array architecture for biological sequence alignment [25,26] is presented in Chapter 3.

- An implementation based on the RVE approach to reduce the execution time at the cost of additional hardware resource utilization [26,27] is presented in Chapter 4.

- An optimized and high performance GPU-based protein sequence alignment outperforming the existing GPU solutions [28] is presented in Chapter 5.

- A comprehensive and elaborate mathematical performance and bandwidth analysis and optimization for biological sequence alignment with particular emphasis on the S-W algorithm [29] is presented and maximum theoretical performance boundaries are investigated in Chapter 6.

- An approach based on hardware partitioning is proposed to achieve high performance and resource efficient biological sequence alignment [30]. This approach is presented in Chapter 6.

- Power consumption evaluation and its impact on performance [31] is presented in Appendix E.

## 1.4 Thesis outline

The rest of the thesis is organized as follows.

Chapter 2 presents a classification of various sequence alignment methods and continues with a discussion of global, local and multiple methods in detail. It describes exact methods like dot plot, Needleman-Wunsch and Smith-Waterman and approximate methods like FASTA, BLAST, HMMER and ClustalW. The chapter ends with a comparison of the presented methods followed by a brief summary of the chapter.

Chapter 3 presents a classification of the various available acceleration methods for sequence alignment applications and proposes an accurate profiling and acceleration evaluation method using the MOLEN platform. Further, it presents FPGA-based rectangular (2D) and linear (1D) systolic array implementations for sequence alignment. It continues with the discussion of an extended linear systolic array design and ends with a brief summary of the chapter.

Chapter 4 presents RVE-based approach for sequence alignment and its comparison with traditional systolic array based approaches. Further, it presents rectangular and linear FPGA-based RVE implementations for sequence alignment and a discussion of the corresponding results. It continues with the RVE performance evaluation before concluding with a brief summary of the chapter.

Chapter 5 provides an introduction to GPUs, *Compute Unified Device Architecture (CUDA)* and its programming and memory models. The chapter explores the parallelization capabilities of GPUs for sequence alignments and reviews the available GPU-based approaches. It presents an optimized GPU implementation for S-W based protein sequence alignment. Further, it evaluates the performance of the optimized GPU implementation and compares it with the fastest available similar design. The chapter concludes with a brief summary.

Chapter 6 presents a comprehensive and elaborate performance and bandwidth analysis for sequence alignment. It continues with evaluating theoretical performance boundaries for various cases and optimizing bandwidth requirement. Further, it presents a method based on hardware partitioning to carry out high performance and resource efficient biological sequence alignment. Additionally, it develops equations to show the general trend of execution time reduction, resource utilization improvement and hence performance enhancement. The chapter ends with a brief summary.

The thesis ends with Chapter 7, where chapter wise brief conclusions are given, followed by a number of recommendations intended to identify future research directions.

The main content of the thesis is annexed by five appendices organized as follows.

Appendix A defines some important terms used in bioinformatics. Appendix B provides a dot plot implementation. Appendix C gives a couple of examples to explain the N-W algorithm. Appendix D explains S-W algorithm with the help of a flow chart and two examples. Appendix E presents power consumption evaluation for sequence alignment and its impact on performance.

At the end, a list of publications related to the thesis and a brief curriculum vitae of the author are given.

## 1.5 Summary

This chapter served as a simple introduction to the concepts associated with molecular biology, bioinformatics and sequence alignment in general. Further, it presented the methods for acceleration of sequence alignment applications and provided an overview of the thesis contribution. The main topics discussed are as follows.

- An overview of molecular biology including a brief discussion about cells, amino acids, proteins, chromosomes, DNA, RNA and transcription.

- An introduction to bioinformatics including a discussion about its fields with a particular emphasis on sequence alignment, its types and applications.

- Classification of sequence alignment acceleration and a discussion about the acceleration methods.

- An overview of the thesis contribution with references to the papers published during the course of the thesis.

- An outline of the thesis glancing at the topics to be presented in the following chapters.

# Chapter 2

## Sequence Alignment Methods

This chapter introduces a taxonomy of the various sequence alignment methods found in the literature. It describes in detail, exact methods like dot plot, Needleman-Wunsch and Smith-Waterman and approximate methods like FASTA, BLAST, HMMER and ClustalW. Further, it compares the presented methods based on their complexities and parameters like alignment type and the search procedure used.

It starts with a classification of sequence alignment methods, presented in Section 2.1, followed by a discussion about global methods like dot plot and Needleman-Wunsch in Section 2.2. Section 2.3 presents local methods like Smith-Waterman, FASTA and BLAST, whereas Section 2.4 presents multiple alignment methods like HMMER and ClustalW. Section 2.5 presents a comparison of various sequence alignment methods discussed in the previous sections, whereas Section 2.6 summarizes the chapter.

### 2.1 Classification of sequence alignment methods

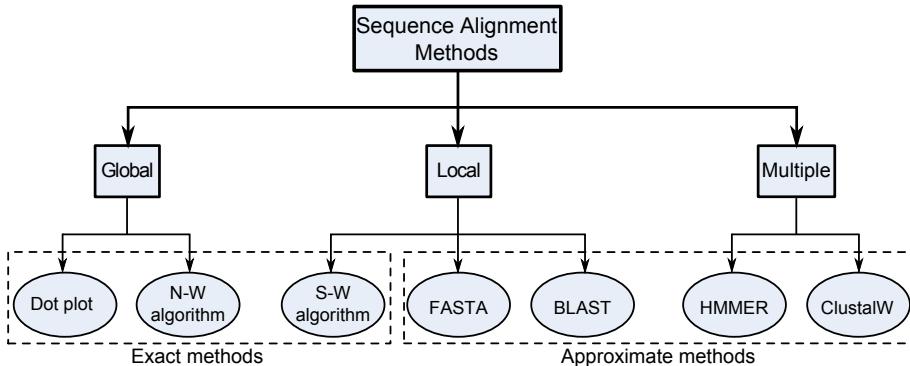

Sequence alignment aims at identifying regions of similarity between two DNA or protein sequences (the query sequence and the subject or database sequence). Traditionally, the methods of pairwise sequence alignment [32] are classified as either global or local, where pairwise means considering only two sequences at a time. Global methods [33] attempt to match as many characters as possible, from end to end, whereas local methods [34] aim at identifying short stretches of similarity between two sequences [35]. However, in some cases, it might also be needed to investigate the similarities between a group of sequences, hence multiple sequence alignment methods are introduced. Multiple sequence alignment [36] is an extension of pairwise alignment to incorporate more than two sequences at a time. Such methods try to align all of the sequences in a given query set simultaneously. Figure 2.1 gives a classifica-

tion of various available sequence alignment methods. These methods are categorized into three types, i.e. global, local and multiple, as shown in the figure. Further, the figure also identifies the exact methods and approximate methods. The methods shown in Figure 2.1 are further elaborated in the following sections.

Figure 2.1: Various methods for sequence alignment

## 2.2 Global methods

As described earlier, global methods aim at matching as many characters as possible, from end to end between two sequences i.e. the query sequence ( $N_q$ ) and the subject or database sequence ( $N_s$ ). Methods carrying out global alignment include dot plot and Needleman-Wunsch algorithm. Both are categorized as exact methods. The difference is that dot plot is based on a basic search method, whereas Needleman-Wunsch on dynamic programming, as discussed in the following subsections.

### 2.2.1 Dot plot method

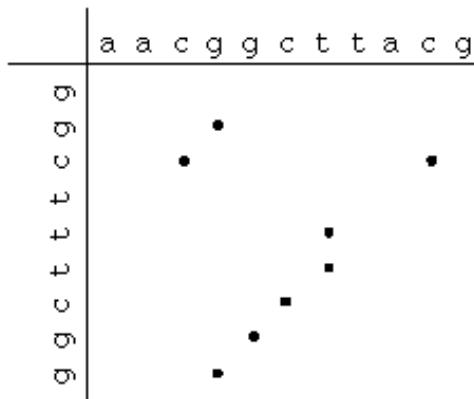

The most basic method of comparing two sequences is a visual approach known as a dot plot [37]. The sequences to be compared are arranged along the margins of a matrix. At every point in the matrix where the two sequences are identical, a dot is placed (i.e. at the intersection of every row and column that have the same letter in both sequences). A diagonal stretch of dots indicates regions where the two sequences are similar. Done in this fashion, a dot plot as shown in Table 2.1 is obtained (for clarity, dots are marked as  $\times$ s in the table).

In general two sequences are considered, i.e. the query sequence ( $N_q$ ) and the subject or database sequence ( $N_s$ ), whose lengths can be different, but in the ideal case are fairly similar. We proceed by creating a rectangular matrix in which the characters of  $N_q$  are mapped along the  $x$ -axis, and those of  $N_s$  along the  $y$ -axis. Initially, the

Table 2.1: Dot plot matrix