# Pitch-Matched Integrated Circuits for Ultrasound Transducer Arrays

Pertijs, Michiel; Hopf, Yannick; Guo, Peng

10.1007/978-3-031-71559-4 1

**Publication date**

**Document Version** Final published version

Published in

Imaging Sensors, Power Management, PLLs and Frequency Synthesizers

Citation (APA)

Pertijs, M., Hopf, Y., & Guo, P. (2024). Pitch-Matched Integrated Circuits for Ultrasound Transducer Arrays. In Imaging Sensors, Power Management, PLLs and Frequency Synthesizers (pp. 3-21). Springer Nature. https://doi.org/10.1007/978-3-031-71559-4\_1

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# Pitch-Matched Integrated Circuits for Ultrasound Transducer Arrays

Michiel Pertijs, Yannick Hopf, and Peng Guo

#### 1 Introduction

Ultrasound imaging is widely used in medical diagnosis and treatment. Recent advancements in technology have led to significant changes in the form factor of ultrasound devices, transitioning from traditional handheld probes to smaller and more portable devices, like pocket-sized handheld scanners [1], endoscopes [2], catheters [3], pills [4], and patches [5]. Additionally, 2D arrays capable of generating 3D images are becoming more common, not only in handheld probes but also in miniature probes like endoscopes and catheters [2, 3]. The increased demand for accessibility and ease of use have led to the development of ultrasound devices that are cost-effective and require minimal training. These advancements have the potential to revolutionize medical imaging and enable the early detection and treatment of diseases.

Integrated circuits play a key role in these developments. The electronics architecture of conventional imaging systems, which is based on commercial off-the-shelf components, is not scalable to the new form factors, particularly in terms of size and power consumption. Furthermore, the conventional architectures are not suitable for 3D imaging in terms of channel count. The integration of transceiver circuits with the ultrasound transducer array can address these issues [2, 6, 7]. Additionally, the move from bulk-piezoelectric transducer technology to micromachined transducers, combined with the integration of circuits, has the potential to significantly reduce the cost of ultrasound devices, making them more accessible for widespread use [1].

This chapter provides a review of the state-of-the-art in integrated circuits for next-generation ultrasound imaging devices. Section 2 starts by giving an overview of the electronics architecture of conventional ultrasound imaging systems and discusses the limitations of this architecture in terms of channel count and miniaturization. This motivates the use of in-probe integrated circuits. Section 3 focuses on the most commonly used channel-count reduction technique: sub-array beamforming. After discussing its basic operating principle, an overview is given of possible circuit implementations. Section 4 discusses full digitization of the echo signals in the probe, which can provide further channel-count reduction and paves the way to more advanced signal processing in the probe. Section 5 illustrates the use of these techniques in the context of a catheter-based 3D intracardiac probe. This chapter ends with conclusions and an outlook on future work.

#### 2 Ultrasound Electronics Architectures

## 2.1 Conventional Ultrasound Imaging Systems

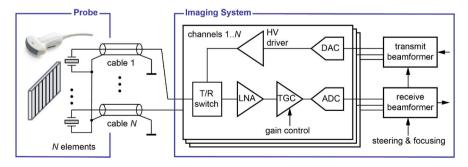

Figure 1 shows a schematic representation of a conventional ultrasound imaging system linked to a probe housing an array of *N* transducer elements, each of which performs the dual role of transmitting (TX) and receiving (RX) acoustic waves [8]. These transducer elements are connected via cables to transceiver channels within the imaging system.

In order to emit an acoustic wave for imaging purposes, these elements are driven by timed pulses, orchestrated by a TX beamformer, with the objective of achieving a desired spatial distribution of the acoustic wave. Typically, this involves focusing the acoustic wave at a selected point along a scan line. To ensure the acquisition of sufficiently strong echoes, even from the most distant points within the imaging region, where signal attenuation significantly reduces signal strength, high-voltage (HV) pulses are commonly utilized to drive the transducer elements. These HV pulses exhibit voltage levels ranging from tens of Volts to well over 100 V.

Fig. 1 Block diagram of a conventional ultrasound imaging system

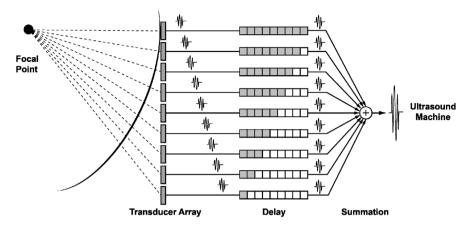

Fig. 2 Receive beamforming by means of a delay-and-sum operation

These pulses are conveyed to the transducer elements through transmit/receive (T/R) switches, which serve the critical role of protecting the low-voltage receive circuits during pulse transmission.

Following transmission, each transducer element receives the resulting echo signals, also referred to as the element-level RF signals, which are amplified by a low-noise amplifier (LNA). The first echo signals received, which come from scatters close to the probe, typically have higher amplitudes than the echoes arriving later, which come from deeper scatters and hence are subject to more propagation attenuation [9]. To compensate for this decrease in signal strength, a time-gain compensation (TGC) amplifier is used. This amplifier provides a gain that increases exponentially with time [8]. This significantly reduces the echo-signal dynamic range. Finally, the echo signals are digitized using an analog-to-digital converter (ADC), usually preceded by an anti-aliasing filter (not shown in Fig. 3).

The digitized echo signals are combined using an RX beamformer, in the simplest case using a delay-and-sum operation, as illustrated in Fig. 2. This process is aimed at constructively adding signals from a specific focal point while suppressing signals from other locations [8, 9]. The resulting beamformed RF signal undergoes additional processing to generate an image. For example, in the case of conventional brightness-mode (B-mode) imaging, both the TX and RX beamformers focus on a scan line within the medium. The beamformed RF signal is subjected to envelope detection and log-compression to obtain the brightness along the corresponding line in the image. To form the complete image, multiple scan lines are combined, each requiring a cycle of pulse transmission and echo reception [9].

In the architecture of Fig. 1, each transducer element is connected using a cable to a transceiver channel in the imaging system. As a result, the number of elements is limited by practical constraints, e.g. in cable count and system size, to a maximum of 256 for high-end imaging systems [10]. This implies that for the matrix transducers

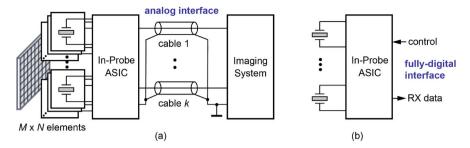

Fig. 3 Ultrasound probe with in-probe ASIC, employing (a) an analog interface to an imaging system; (b) a fully digital interface

needed for 3D imaging, which readily consist of thousands of elements, alternative solutions are needed, typically involving in-probe electronics.

#### 2.2 In-Probe Electronics

One of the main reasons for incorporating application-specific integrated circuits (ASICs) into ultrasound probes is to address the challenge of interfacing transducer arrays with many elements, as required for 3D imaging, with an imaging system with a much smaller number of channels (as depicted in Fig. 3a). Several strategies have been employed to address this challenge, including the use of multiplexing [11–13] and sub-array beamforming [2, 6, 14, 15], which will be discussed in more detail in Sect. 3. In these cases, the ASIC provides analog output signals to the imaging system. Moreover, in-probe ASICs contribute to enhancing the signal-tonoise ratio (SNR) by locally amplifying the echo signals received by the transducer elements. This local amplification helps prevent the signal loss associated with connecting the small, high-impedance elements of a matrix transducer to long cables [16–18].

To interface with the transducer elements, in-probe ASICs contain front-end transceiver circuits, including high-voltage transmitters, LNAs, and programmable-gain or TGC circuits. While functionally similar to the front-end circuits found in an imaging system (see Fig. 1), these building blocks typically need to meet stringent size and power-consumption constraints when integrated into the probe. Their optimization is therefore an important part of the design of in-probe ASICs. A detailed discussion of the front-end transceiver circuits is beyond the scope of this chapter. The interested reader is referred to [19] for a detailed review.

The potential role of ASICs integrated within the ultrasound probe extends beyond improving SNR and reducing the number of channels. They can offer additional capabilities, such as complete digitization (as shown in Fig. 3b) and additional processing of the echo signals [7, 15, 20–24]. This becomes particularly critical in the context of portable ultrasound probes, where traditional imaging

systems with analog front-ends and ADCs will be replaced by smartphones or tablets [1]. Consequently, the traditional data acquisition functions previously handled by the imaging system now shift to the ASIC, while the image-processing tasks are carried out through software. In-probe digitization will be discussed in detail in Sect. 4.

# 3 Sub-Array Beamforming

# 3.1 Operating Principle

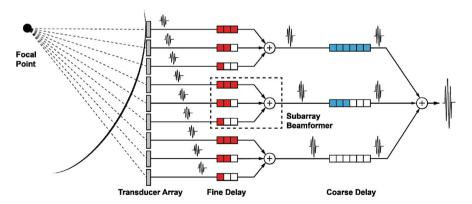

Full-array beamforming for large element-count arrays is challenging due to the large delay depth required for each element, which is typically a few microseconds. The sub-array beamforming scheme [14], also known as "microbeamforming," mitigates this issue by dividing the beamforming task into two steps (Fig. 4). A coarse delay that is common for all elements within one sub-array is applied in the external imaging system, while only fine delays for the individual elements (typically less than 1  $\mu s$ ) are applied by the sub-array beamformers in the ASIC, which significantly reduces the implementation complexity of the required on-chip delay lines.

Sub-array beamforming with a sub-array size of N elements reduces the number of channels by a factor of N, thus reducing the complexity of the remaining signal path. However, it does not provide the raw data of the full array and introduces focusing errors [25]. These result in increased grating and sidelobe levels as well as broadening of the main beam, all negatively impacting image quality. Narrower transmit beams can be used to mitigate these effects but require more acquisitions per volume, ultimately leading to a trade-off between sub-array size, with related channel-count reduction, and achievable frame rate [26].

Fig. 4 Subarray beamforming by means of two-step delay-and-sum

### 3.2 Circuit Implementation

Various RX beamformer topologies have been used to realize the delay-and-sum process. One option is to digitize the element-level RF signals and subsequently beamform these in the digital domain [22]. This solution, however, requires a relatively large die area and power consumption. Analog beamformer topologies can be broadly classified into three categories: beamformers based on phase rotation applied to I/Q demodulated RF signals [27]; beamformers based on continuous-time delay lines, in which the delays are tuned continuously [28, 29]; and beamformers based on discrete-time delay lines, in which the delays are discretized, conforming to a clock signal [2, 14, 15, 30–33].

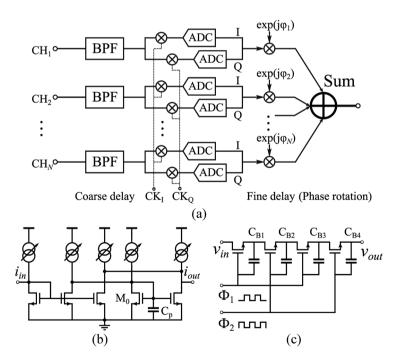

The phase-rotation-based beamformer as shown in Fig. 5a applies direct I/Q demodulation to bandpass-filtered RX signals followed by digitization. The digitized I/Q signals are fed to a series of phase rotators in the digital domain to approximate time delays before the summation takes place. In [27], a direct sampling I/Q demodulation is employed, and analog-to-digital conversion is required for each I/Q channel.

The solution is attractive for narrow-band ultrasound signals, for which phase shifting is a good approximation for delay, and which can be multiplexed on a

Fig. 5 Circuits for RX beamforming: (a) direct I/Q demodulation in conjunction with digital phase rotation [27]; (b) continuous-time delay cell [28]; (c) BBDs-based delay line [30]

high-speed ADC, thus saving area. However, echo signals in ultrasound imaging generally have a wide bandwidth, e.g., a fractional bandwidth of 80% around the transducer's resonance frequency, calling for many high-speed ADCs and making this solution less attractive.

As depicted in Fig. 5b, a continuous-time delay cell employs current mirror-based circuits to construct an all-pass filter, which is a first-order approximation of an ideal delay, tuned by the bias currents of the current mirror network. A delay line can be constructed by cascading a number of such delay cells [28]. The implementation has no passive devices and is potentially small. However, it suffers from non-linear phase response, resulting in different delays for different frequency components in a wide-band ultrasound signal and high sensitivity to temperature and process drift.

A discrete-time delay line using bucket-brigade devices (BBDs) [30] is shown in Fig. 5c. A series of bucket capacitors,  $C_{B1-4}$ , stores the information as charge packets transported by means of MOS transistors. The speed of the charge transportation is controlled by two complementary clock signals, making the delay step equal to the clock period. Although the BBD delay line uses a minimum number of transistors and occupies a small area, it suffers from poor charge-transfer linearity.

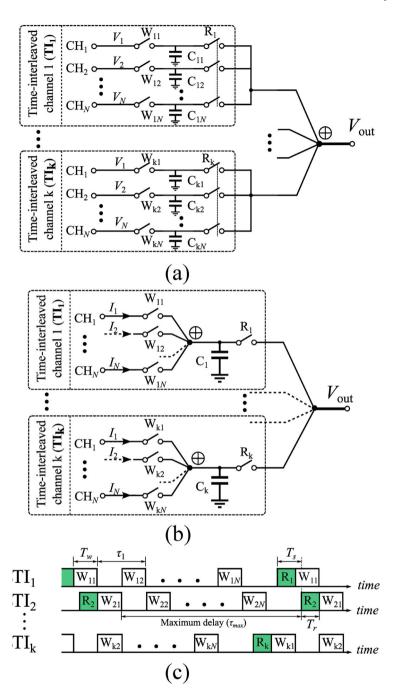

Other types of discrete-time beamformers are based on switched-capacitor [2, 14, 31] or switched-current delay lines [32]. Figure 6a shows a switched-capacitor implementation, in which every output sample of the beamformer is generated by combining delayed sampled-and-held versions of the input signals, stored on a bank of capacitors. To accommodate delays larger than the sampling interval  $T_s$ , k time-interleaved delay-and-sum channels are used, each of which contains N memory capacitors, one for each input channel. These k channels alternately generate the beamformer output, by the successive closing of read switches  $R_{1...k}$ , which connect the capacitors of one of the channels to the output, causing signal summation in the charge domain. The effective delay experienced by input signal  $V_j$  ( $1 \le j \le N$ ) is determined by the time delay between the opening of the write switches  $W_{ij}$  and the closing of the read switches  $R_i$ . Thus, the relative delays between adjacent channels are accurately defined by the falling edges of the write clock signals (e.g., the delay  $\tau_1$  between channels 1 and 2 is determined by the falling edges of  $W_{i1}$  and  $W_{i2}$ ).

While, in this example, summation takes place in the charge domain [2], it can also similarly be implemented in the voltage domain [31] or the current domain [32]. A disadvantage of these approaches is that a large number of memory capacitors, i.e.  $N \times k$  capacitors, is needed, along with the associated switches and interconnections.

To substantially reduce the number of required components, the delay-and-sum operation can be replaced by a sum-and-delay operation, as shown in Fig. 6b [15, 33]. Here, k time-interleaved channels are used to generate the beamformer output, but each channel only contains one memory capacitor, reducing the number of capacitors by a factor of N. This is enabled by applying the input signals to the beamformer in the current domain, rather than in the voltage domain, allowing the summation of the signals from different input channels to take place in the current domain at the input. The writing switches  $W_{ij}$  now determine during which

Fig. 6 Discrete-time RX beamformers based on (a) sample-and-hold delay lines [2, 14, 31]; (b) boxcar integration [15]

time interval the input current is integrated on the memory capacitors, rather than determining when the input signals are sampled-and-held, like in Fig. 6a. As before, the time delay between this interval and the closing of the corresponding read switch  $R_i$  determines the effective time delay that an input signal experiences. An added benefit of this solution is that the integration of the current-mode inputs on the memory capacitors forms a boxcar sampler, which provides inherent anti-aliasing for the sampling in the beamformer [15].

### 4 In-Probe Digitization

Most in-probe ASICs perform signal conditioning, sub-array beamforming, averaging, or multiplexing in the analog domain and provide analog output signals connecting to an imaging system, where digitization takes place. Nevertheless, there is a growing trend to move the analog-to-digital conversion into the probe as well, closer to the transducer. This offers many potential benefits, including further cable-count reduction by leveraging high-speed digital datalinks [21, 23, 34], and the integration of digital processing functions into the probe [1, 35]. Inprobe digitization can take place at the element-level, or after initial processing of the signals of multiple elements in the analog domain, e.g., after sub-array beamforming.

#### 4.1 Element-Level ADCs

Element-level digitization has the important advantage that it grants direct access to the RF data from all individual elements, eliminating any constraints imposed by analog pre-processing on the imaging algorithms. The main challenge associated with element-level digitization is the limited power and area budget typically available for element-level ADCs.

Various attempts have been made to tackle this challenge. In [36], a digital beamformer using element-level successive-approximation-register (SAR) ADCs following conventional analog front-ends was presented. The ADC employs a conventional charge-redistribution capacitive digital-to-analog converter (DAC), hence requiring substantial silicon area, preventing it from being pitch-matched integrated with the transducer array. In [22], this issue was addressed by leveraging a nanoscale CMOS process to integrate a  $\Delta\Sigma$  ADC along with an analog front-end within the area of a single transducer element, albeit at an energy efficiency that is not yet competitive with the analog approach.

Improvements in size and energy efficiency can be potentially obtained by exploiting specific characteristics of the ultrasound signals being digitized. For instance, in [37], a dynamic-bit-sharing technique was proposed based on the similarity of beamformed ultrasound signals, which allows adjacent element-level

Fig. 7 Beamforming SAR ADC [21]

SAR ADCs in a 2  $\times$  2 sub-array to share the most-significant bits, thus saving power. Another opportunity to save power and reduce size is to exploit specific characteristics of the transducer in the digitization process. An example is the use of the transducer as the electromechanical loop filter of a bandpass  $\Delta\Sigma$  ADC in [38].

# 4.2 Beamforming ADCs

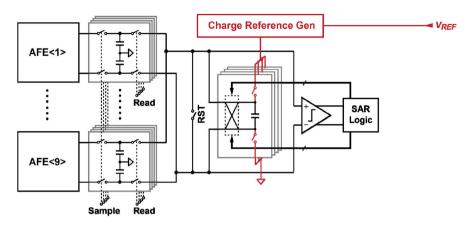

To avoid the large area and power impact of element-level digitization, several designs have employed converters that operate based on the output of a preceding sub-array beamformer. In [39], analog sub-array beamforming based on capacitive sample-and-hold cells precedes digitization with a SAR ADC. While this effectively reduces the required number of ADCs, the approach still requires an additional summing amplifier to realize the sub-array beamforming and a separate ADC driver.

To reduce these additional cost factors, [21] proposed the merging of subarray beamforming and digitization to a dedicated beamforming ADC, as shown in Fig. 7. Multiple element-level signals are provided via individual analog frontends to capacitive sample-and-hold cells to time-delay the element-level RF signals. To avoid the summing amplifier, summation is accomplished by passive charge redistribution when switching capacitive cells in parallel based on pre-determined timing. By employing a charge-sharing ADC, the combined charge can directly be used as the input for digitization. The converter operates by switching binary-scaled units of a pre-charged capacitive digital-to-analog converter (CDAC) in parallel or anti-parallel to the charge-domain input. The switching polarity is determined with an asynchronous comparator and SAR logic to successively approximate input signal. A low-bandwidth reference generator can be applied by using two CDACs and pre-charging one while the other is in operation.

Fig. 8 Hybrid Beamforming ADC [24]

This approach is particularly efficient in reducing the element-level power consumption, but still limits integration density due to the relatively large footprint. Two of the main challenges for the reduction of area are the requirement for a second CDAC and exponential scaling of the size of the SAR architecture with increased resolution.

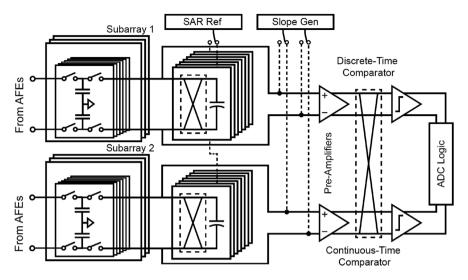

One way to mitigate the area impact of the converter is to transition to a hybrid beamforming ADC, as proposed in [24] and displayed in Fig. 8. While a slope ADC is typically too slow to efficiently convert ultrasound signals with center frequencies in the order of several MHz, it can be employed to convert the residue of a preceding SAR step. The SAR is again implemented as a charge-sharing topology for direct integration with the sub-array beamformer, but the overhead from exponential scaling is reduced due to its lower resolution requirement. Additionally, no second CDAC is required as the pre-charging can be performed during slope conversion. By letting the SAR and slope phase of two neighboring sub-array converters run in opposite phases, the design makes efficient use of the arrayed nature of ultrasound imaging with hardware sharing. One SAR reference generator and one slope generator are sufficient to serve two channels. While the slope ADC requires a continuous-time comparator and the SAR operation a discrete comparator, these can also be efficiently shared by switching them between two channels.

In conclusion, in-probe digitization can provide significant channel-count reduction and enable upcoming signal processing. Current developments in data converters tailored to ultrasound imaging have made the associated power and area requirement feasible and make the technique one of the major drivers of product miniaturization.

#### 4.3 Datalink Solutions

Once in-probe digitization is adopted, the conventional analog RX signal transmission from the probe to the imaging system is replaced by a digital datalink. To realize this at modest data rates, a solution is to multiplex the entire array onto a single ADC and data channel [20]. This implies that multiple transmit/receive cycles are needed to acquire a full RX data set, leading to a reduction in frame rate.

This problem can be mitigated, without increasing the cable count to the number of RX channels, by exploiting the fact that most cable connections between probes and imaging systems have bandwidths exceeding the bandwidth required by a single RX channel. Therefore, a single cable can be in principle shared by multiple RX channels. For analog signaling, this has been realized using time-division multiplexing (TDM) techniques [13, 40]. TDM is also possible in the digital domain [21] and provides the additional benefit of avoiding the susceptibility to crosstalk and interference associated with transmission of analog signals across non-ideal cable assemblies [40]. Together with potential benefits from upcoming in-probe data processing, this makes digital links especially promising.

To date, probes with digital interfaces typically employ conventional communication standards like low-voltage differential signaling (LVDS) [21, 24, 38]. While such standards ensure reliable communication with very low bit-error rates, they may be too power-hungry for power-constrained probes like imaging catheters. Power can be saved by exploiting the fact that bit error rates can be tolerated in digitized ultrasound RF data that are orders-of-magnitude higher than what is typically acceptable in datalinks, without noticeable impact on B-mode image quality [41]. To reduce the power consumption associated with data transmission and the cost of complex cable assemblies, [23] has investigated a custom datalink specifically for catheter-based ultrasound probes. An optimization of the channel bandwidth is achieved with multi-level signaling and a load modulation architecture shifts part of the associated power consumption from the probe to the imaging system in order to reduce heating of the catheter tip.

An alternative path is explored in optical communication [42]. With advances in the integration of optical modules, the larger bandwidth provided by optical fiber communication becomes more accessible and can potentially enable large channel-count reduction factors in the future.

# 5 Case Study: A 3D Intracardiac Probe

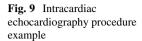

The following case study demonstrates the principles discussed in this chapter using the example of a 3D intracardiac echocardiography (ICE) probe as it reflects the challenges associated with upcoming miniaturized 3D ultrasound imaging devices. ICE is typically used in minimally-invasive cardiac procedures, such as catheter ablation used to treat cardiac arrhythmia [43]. The imaging catheter is inserted into

the heart via the vascular system as shown in Fig. 9 and provides guidance for the intervention. Due to the size constraints of the ICE catheter, with a diameter in the order of 3 mm, integration of circuitry at the catheter tip is challenging, and the number of cables that can be accommodated in the catheter shaft is limited. In addition, power consumption is tightly constrained in order to prevent excessive tissue heating. The presented design implements a high-frame-rate imaging scheme described in [25]. The design is described in detail in [23, 24].

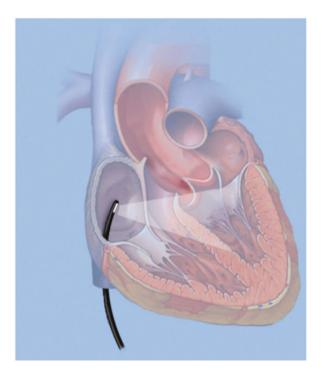

Figure 10 shows the global architecture of the implemented design. Each transducer element connects to element-level unipolar pulsers with an integrated transmit/receive (T/R) switch. On the receiver side, each transducer connects to a separate analog front-end, consisting of a first-stage low-noise amplifier (LNA) and a second-stage programmable-gain amplifier (PGA), which also performs conversion of the single-ended transducer signal to a differential output. Together, the two stages provide time-gain compensation (TGC) to limit the dynamic range of the signal for the following blocks. This is achieved by adjusting their gain along with the time-dependent attenuation of the ultrasound signal in the imaged medium.

Three element-level receiver outputs are subsequently combined in a subarray beamformer. By only combining three elements in one direction of the 2D transducer array, only few acquisitions have to be performed per reconstructed volume and a high frame rate can be achieved. The beamformer is realized using capacitive sample-and-hold cells. Two beamformers are merged with a hybrid ADC

Fig. 10 Architecture of a prototype ASIC for a high-frame-rate 3D ICE probe

Fig. 11 Chip micrograph and subgroup layout

in a subgroup. The ADC operates based on a SAR first stage and a single-slope (SS) second stage, as discussed in Sect. 4.2.

To maximize the available area for circuitry underneath the transducer array, the signals are forwarded to the periphery of the chip as soon as they are quantized. While the core area is quite constrained by the 160- $\mu$ m pitch of the transducer elements, there is more space available at the long ends of the catheter tip, and a digitally synthesized module is implemented at the periphery. This implements recombination of the hybrid ADC output, 8-bit/10-bit encoding, and serialization to LVDS drivers for data transmission.

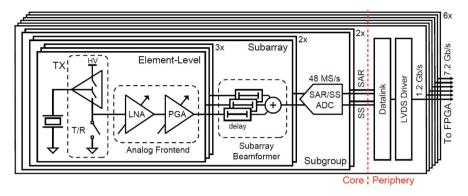

An overview of the implemented prototype is given in Fig. 11. It shows the fabricated chip with a transducer matrix manufactured on its surface. The chip was fabricated using a 180-nm BCD process, and the transducer array has a pitch of 160  $\times$  160  $\mu$ m with a center frequency of 6 MHz. There are a total of 72 active elements plus two rings of dummy transducers in order to reduce edge effects.

The first inset shows a micrograph of the electronics below the transducer array. The core area features circuitry pitch-matched to the transducers, and the datalinks are concentrated on one side in order to enable scalability to a full probe in the order of 1000 elements.

Fig. 12 Element-level power and area distribution

|                          | This<br>Work    | Lee et al.<br>JSSC'21 | Li et al.<br>VLSI'19 | Chen et al.<br>JSSC'18 | Wildes et al.<br>TUFFC'16 |

|--------------------------|-----------------|-----------------------|----------------------|------------------------|---------------------------|

| Process                  | 180 nm BCD      | 180 nm                | 180 nm               | 180 nm                 | N/A                       |

| Transducer               | 6 MHz 2D PZT    | 5 MHz 2D PMUT         | 5 MHz 2D PZT         | 5 MHz 2D PZT           | 5.6 MHz 2D PZT            |

| Array Size               | 8 x 9           | 6 x 6                 | 4 x 4                | 6 x 24                 | 60 x 14                   |

| Integrated<br>Transducer | <b>&gt;</b>     | Х                     | <b>✓</b>             | <b>✓</b>               | <b>√</b>                  |

| Pitch-Matched            | <b>✓</b>        | X                     | <b>✓</b>             | <b>✓</b>               | <                         |

| Element Pitch            | 160 μm x 160 μm | 250 μm x 250 μm       | 150 μm x 150 μm      | 150 μm x 150 μm        | 110 µm x 180 µm           |

| Integrated TX            | 65 V            | 13.2 V                | X                    | X                      | 40 V                      |

| Digitization             | <b>✓</b>        | <b>✓</b>              | <b>\</b>             | <b>✓</b>               | X                         |

| Chan. Reduction          | 12-fold         | N/A                   | N/A                  | 36-fold                | 15-to 20-fold             |

| Supported<br>Frame-Rate  | 1000 vol/s      | N/A                   | N/A                  | 200 vol/s              | 50 vol/s                  |

| RX Power / El.           | 1.23 mW         | 1.14 mW               | 1.54 mW              | 0.91 mW                | < 0.12 mW                 |

| Input DR                 | 91 dB           | N/A                   | N/A                  | 85 dB                  | N/A                       |

Fig. 13 Comparison to the prior art

The second inset shows the footprint of a single subgroup of six elements. Two sub-array beamformers are laid out together in order to make best use of the hardware sharing in the hybrid ADC. The subgroup is used as the lowest unit-cell and is replicated in order to achieve larger apertures.

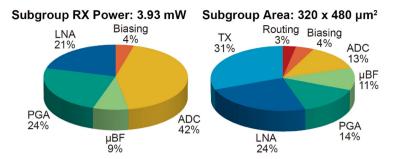

The distribution of RX power and area per elements is shown in Fig. 12. The power is fairly and evenly distributed between the analog front-end and the ADC. TX power consumption depends heavily on the applied imaging mode but has generally a fairly low contribution due to the heavy-duty cycling between transmit and receive in ultrasound imaging.

In the area overview, the effect of hardware sharing in the ADC in visible. With the sub-array beamformer included, the beamforming ADC only occupies 24% of the total subgroup space, and the transmitter is actually the largest contributor with almost one-third. This is due to the large spacing required for HV structures in junction-isolated technologies.

Figure 13 summarizes the system characteristics and compares the design to the prior art in catheter-based ultrasound systems. This is the first work to integrate HV transmitters, analog front-ends, sub-array beamforming, and in-probe digitization for scalable 3D imaging. A dedicated architecture enables the highest reported frame rate at a competitive power consumption.

#### 6 Conclusions

This chapter has reviewed pitch-matched circuit solutions for emerging ultrasound imaging devices, such as 3D imaging catheters, portable ultrasound scanners, and wearable ultrasound patches. It has focused on approaches for in-probe receive beamforming and digitization, which are crucial for the channel-count reduction needed in high-element-count probes for 3D imaging.

Currently, most in-probe ASICs act as an interface between the transducer and a conventional imaging system, providing amplification for improved SNR, and channel-count reduction for 3D imaging, by multiplexing or sub-array beamforming. An emerging trend is to move from analog outputs to full in-probe digitization, to provide a robust digital interface to the system. This will enable further data reduction by means of in-probe digital signal processing. Moreover, standardized digital interfaces could ease the integration with other tools supporting the physician. Eventually, this can lead to the disappearance of imaging systems, with all front-end electronics integrated on-chip in the probe, and image processing moved to software. Compared to PCB-based solutions [44], this is an essential step to reduce the size and cost of handheld ultrasound scanners. It is even more crucial for future wearable ultrasound devices, which can bring ultrasound technology to the home environment, for instance for long-term monitoring applications. Such devices will have to operate from a small battery and communicate wirelessly, for instance with a smart phone. This will come with many new challenges, such as the need for drastic data reduction and improvements in power efficiency, which call for further advances in integrated circuit design for ultrasound applications.

#### References

- J.M. Rothberg et al., Ultrasound-on-chip platform for medical imaging, analysis, and collective intelligence. Proc. Natl. Acad. Sci. USA 118(27), e2019339118 (2021). https://doi.org/ 10.1073/pnas.2019339118

- C. Chen et al., A front-end ASIC with receive sub-array beamforming integrated with a 32 x 32 PZT matrix transducer for 3-D transesophageal echocardiography. IEEE J. Solid State Circuits 52(4), 994–1006 (2017). https://doi.org/10.1109/JSSC.2016.2638433

- 3. D. Wildes et al., 4-D ICE: A 2-D Array transducer with integrated ASIC in a 10-Fr catheter for real-time 3-D Intracardiac echocardiography. IEEE Trans. Ultrason., Ferroelect., Freq. Contr. **63**(12), 2159–2173 (2016). https://doi.org/10.1109/TUFFC.2016.2615602

- H.S. Lay et al., Integrated Front End Circuitry for Microultrasound Capsule Endoscopy, in 2018 IEEE International Ultrasonics Symposium (IUS), (IEEE, Kobe, 2018), pp. 1–4. https://doi.org/10.1109/ULTSYM.2018.8579738

- C. Wang et al., Monitoring of the central blood pressure waveform via a conformal ultrasonic device. Nat. Biomed. Eng. 2(9), 687–695 (2018). https://doi.org/10.1038/s41551-018-0287-x

- Y. Igarashi et al., Single-chip 3072-element-channel transceiver/128-subarray-channel 2-D Array IC with analog RX and all-digital TX Beamformer for echocardiography. IEEE J. Solid State Circuits 54(9), 2555–2567 (2019). https://doi.org/10.1109/JSSC.2019.2921697

- N. Sanchez et al., An 8960-Element Ultrasound-on-Chip for Point-of-Care Ultrasound, in 2021 IEEE International Solid- State Circuits Conference (ISSCC), (IEEE, San Francisco, 2021), pp. 480–482. https://doi.org/10.1109/ISSCC42613.2021.9365808

- R. Wodnicki, B. Haider, K.E. Thomenius, Electronics for diagnostic ultrasound, in *Medical Imaging*, ed. by K. Iniewski, (John Wiley & Sons, Inc., Hoboken, 2009), pp. 165–220. https://doi.org/10.1002/9780470451816.ch7

- 9. T.L. Szabo, Diagnostic Ultrasound Imaging: Inside Out (Elsevier, 2014). https://doi.org/10.1016/C2011-0-07261-7

- E. Boni et al., ULA-OP 256: A 256-channel open scanner for development and real-time implementation of new ultrasound methods. IEEE Trans. Ultrason., Ferroelect., Freq. Contr. 63(10), 1488–1495 (2016). https://doi.org/10.1109/TUFFC.2016.2566920

- J.S. Kenji Hara, A New 80V 32x32ch Low Loss Multiplexer LSI for a 3D Ultrasound Imaging System, in *Proceedings. ISPSD '05. The 17th International Symposium on Power* Semiconductor Devices and ICs, 2005, (IEEE, Santa Barbara, 2005), pp. 359–362. https://doi.org/10.1109/ISPSD.2005.1488025

- 12. E. Kang et al., A reconfigurable ultrasound transceiver ASIC with 24 x 40 elements for 3-D carotid artery imaging. IEEE J. Solid State Circuits **53**(7), 2065–2075 (2018). https://doi.org/10.1109/JSSC.2018.2820156

- T.M. Carpenter, M.W. Rashid, M. Ghovanloo, D.M.J. Cowell, S. Freear, F.L. Degertekin, Direct digital demultiplexing of analog TDM signals for cable reduction in ultrasound imaging catheters. IEEE Trans. Ultrason., Ferroelect., Freq. Contr. 63(8), 1078–1085 (2016). https://doi.org/10.1109/TUFFC.2016.2557622

- B. Savord, R. Solomon, Fully sampled matrix transducer for real time 3D ultrasonic imaging, in IEEE Symposium on Ultrasonics, 2003, (IEEE, Honolulu, 2003), pp. 945–953. https://doi.org/ 10.1109/ULTSYM.2003.1293556

- P. Guo et al., A 1.2-mW/channel pitch-matched transceiver ASIC employing a boxcarintegration-based RX micro-beamformer for high-resolution 3-D ultrasound imaging. IEEE J. Solid State Circuits 58(9), 2607–2618 (2023). https://doi.org/10.1109/JSSC.2023.3271270

- E. Kang et al., A variable-gain low-noise transimpedance amplifier for miniature ultrasound probes. IEEE J. Solid State Circuits 55(12), 3157–3168 (2020). https://doi.org/10.1109/ JSSC.2020.3023618

- 17. P. Chatain, D. Voisin, M. Legros, G. Ferin, R. Dufait, Improving ultrasound imaging with integrated electronics, in *2009 IEEE International Ultrasonics Symposium*, (IEEE, Rome, 2009), pp. 2718–2721. https://doi.org/10.1109/ULTSYM.2009.5441470

- C. Chen et al., A single-cable PVDF transducer readout IC for intravascular photoacoustic imaging, in 2015 IEEE International Ultrasonics Symposium (IUS), (IEEE, Taipei, 2015), pp. 1–4. https://doi.org/10.1109/ULTSYM.2015.0142

- C. Chen, M.A.P. Pertijs, Integrated transceivers for emerging medical ultrasound imaging devices: A review. IEEE Open J. Solid-State Circuits Soc. 1, 104–114 (2021). https://doi.org/ 10.1109/OJSSCS.2021.3115398

- M. Tan et al., A front-end ASIC with high-voltage transmit switching and receive digitization for 3-D forward-looking intravascular ultrasound imaging. IEEE J. Solid State Circuits 53(8), 2284–2297 (2018). https://doi.org/10.1109/JSSC.2018.2828826

- C. Chen et al., A pitch-matched front-end ASIC with integrated subarray beamforming ADC for miniature 3-D ultrasound probes. IEEE J. Solid State Circuits 53(11), 3050–3064 (2018). https://doi.org/10.1109/JSSC.2018.2864295

- 22. M.-C. Chen et al., A pixel pitch-matched ultrasound receiver for 3-D photoacoustic imaging with integrated delta-sigma beamformer in 28-nm UTBB FD-SOI. IEEE J. Solid State Circuits, 1–14 (2017). https://doi.org/10.1109/JSSC.2017.2749425

- Y.M. Hopf et al., A pitch-matched high-frame-rate ultrasound imaging ASIC for catheter-based 3-D probes. IEEE J. Solid State Circuits, 59(2), 476–491 (2023). https://doi.org/10.1109/JSSC.2023.3299749

- Y.M. Hopf et al., A pitch-matched transceiver ASIC with shared hybrid beamforming ADC for high-frame-rate 3-D intracardiac echocardiography. IEEE J. Solid State Circuits 57(11), 3228–3242 (2022). https://doi.org/10.1109/JSSC.2022.3201758

- M. Soozande et al., Imaging scheme for 3-D high-frame-rate intracardiac echography: A simulation study. IEEE Trans. Ultrason., Ferroelect., Freq. Contr. 69(10), 2862–2874 (2022). https://doi.org/10.1109/TUFFC.2022.3186487

- P. Santos, G.U. Haugen, L. Lovstakken, E. Samset, J. D'hooge, Diverging wave volumetric imaging using subaperture beamforming. IEEE Trans. Ultrason., Ferroelect., Freq. Contr. 63(12), 2114–2124 (2016). https://doi.org/10.1109/TUFFC.2016.2616172

- K. Ranganathan, M.K. Santy, T.N. Blalock, J.A. Hossack, W.F. Walker, Direct sampled I/Q beamforming for compact and very low-cost ultrasound imaging. IEEE Trans. Ultrason., Ferroelect., Freq. Contr. 51(9), 1082–1094 (2004). https://doi.org/10.1109/TUFFC.2004.1334841

- G. Gurun, J.S. Zahorian, A. Sisman, M. Karaman, P.E. Hasler, F.L. Degertekin, An analog integrated circuit beamformer for high-frequency medical ultrasound imaging. IEEE Trans. Biomed. Circuits Syst. 6(5), 454–467 (2012). https://doi.org/10.1109/TBCAS.2012.2219532

- J.R. Talman, S.L. Garverick, G.R. Lockwood, Integrated circuit for high-frequency ultrasound annular array, in *Proceedings of the IEEE 2003 Custom Integrated Circuits Conference*, 2003, (IEEE, San Jose, 2003), pp. 477–480. https://doi.org/10.1109/CICC.2003.1249444

- T. Yaowu Mo, S. Tanaka, A. Arita, K.I. Tsuchitani, Y. Suzuki, Pipelined delay-sum architecture based on bucket-brigade devices for on-chip ultrasound beamforming. IEEE J. Solid State Circuits 38(10), 1754–1757 (2003). https://doi.org/10.1109/JSSC.2003.817603

- 31. J.-Y. Um et al., A single-Chip 32-channel analog beamformer with 4-ns delay resolution and 768-ns maximum delay range for ultrasound medical imaging with a linear array transducer. IEEE Trans. Biomed. Circuits Syst. 9(1), 138–151 (2015). https://doi.org/10.1109/ TBCAS.2014.2325851

- 32. B. Stefanelli, I. O'Connor, L. Quiquerez, A. Kaiser, D. Billet, An analog beam-forming circuit for ultrasound imaging using switched-current delay lines. IEEE J. Solid State Circuits 35(2), 202–211 (2000). https://doi.org/10.1109/4.823445

- J.-Y. Um, Current-mode ultrasound beamformer with multiple-input-sequential-output memory structure. Electron. Lett. 54(9), 545–546 (2018). https://doi.org/10.1049/el.2018.0133

- 34. P. Guo et al. A 125um-pitch-matched transceiver ASIC with micro-beamforming ADC and multi-level signaling for 3-D transfontanelle ultrasonography. IEEE J. Solid-State Circuits **59**(8), 2604–2617 (2024). https://doi.org/10.1109/JSSC.2024.3355854

- 35. B. Lam, M. Price, A.P. Chandrakasan, An ASIC for energy-scalable, low-power digital ultrasound beamforming, in 2016 IEEE International Workshop on Signal Processing Systems (SiPS), (IEEE, Dallas, 2016), pp. 57–62. https://doi.org/10.1109/SiPS.2016.18

- 36. Y.-J. Kim et al., A single-Chip 64-channel ultrasound RX-beamformer including analog frontend and an LUT for non-uniform ADC-sample-clock generation. IEEE Trans. Biomed. Circuits Syst. 11(1), 87–97 (2017). https://doi.org/10.1109/TBCAS.2016.2571739

- J. Lee et al., A 36-channel auto-calibrated front-end ASIC for a pMUT-based miniaturized 3-D ultrasound system. IEEE J. Solid State Circuits 56(6), 1910–1923 (2021). https://doi.org/ 10.1109/JSSC.2021.3049560

- M. D'Urbino et al., An element-matched electromechanical delta-sigma ADC for ultrasound imaging. IEEE J. Solid State Circuits 53(10), 2795–2805 (2018). https://doi.org/10.1109/ JSSC.2018.2859961

- 39. J.-Y. Um et al., "An analog-digital hybrid RX beamformer chip with non-uniform sampling for ultrasound medical imaging with 2D CMUT array," IEEE Trans. Biomed. Circuits Syst., vol. 8, no. 6, pp. 799–809, Dec. 2014, doi: https://doi.org/10.1109/TBCAS.2014.2375958

- Q. Liu, Z. Chao Chen, C.P. Chang, M.A.P. Pertijs, A mixed-signal multiplexing system for cable-count reduction in ultrasound probes, in 2015 IEEE International Ultrasonics Symposium (IUS), (IEEE, Taipei, Taiwan, Oct. 2015), pp. 1–4. https://doi.org/10.1109/ ULTSYM.2015.0141

- 41. Z. Chen *et al.*, "Impact of bit errors in digitized RF data on ultrasound image quality," IEEE Trans. Ultrason., Ferroelect., Freq. Contr., vol. 67, no. 1, pp. 13–24, Jan. 2020, doi: https://doi.org/10.1109/TUFFC.2019.2937462

- 42. J. Li et al., 25.8 Gb/s submillimeter optical data link module for smart catheters. J. Lightwave Technol. 40(8), 2456–2464 (2022). https://doi.org/10.1109/JLT.2021.3137981

- Z.M. Hijazi, K. Shivkumar, D.J. Sahn, Intracardiac echocardiography during interventional and electrophysiological cardiac catheterization. Circulation 119(4), 587–596 (2009). https:// doi.org/10.1161/CIRCULATIONAHA.107.753046

- P.A. Hager, L. Benini, LightProbe: A digital ultrasound probe for software-defined ultrafast imaging. IEEE Trans. Ultrason., Ferroelect., Freq. Contr. 66(4), 747–760 (2019). https://doi.org/10.1109/TUFFC.2019.2898007