Delft University of Technology

## Pressure-assisted CU sintering for SiC Die-attachment application

Liu, X.

**DOI**

[10.4233/uuid:291baefe-c4b9-46ea-b250-a6c8f4e6ece8](https://doi.org/10.4233/uuid:291baefe-c4b9-46ea-b250-a6c8f4e6ece8)

**Publication date**

2023

**Document Version**

Final published version

**Citation (APA)**

Liu, X. (2023). *Pressure-assisted CU sintering for SiC Die-attachment application*. [Dissertation (TU Delft), Delft University of Technology]. <https://doi.org/10.4233/uuid:291baefe-c4b9-46ea-b250-a6c8f4e6ece8>

**Important note**

To cite this publication, please use the final published version (if applicable).

Please check the document version above.

**Copyright**

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

**Takedown policy**

Please contact us and provide details if you believe this document breaches copyrights.

We will remove access to the work immediately and investigate your claim.

# **PRESSURE-ASSISTED Cu SINTERING FOR SiC DIE-ATTACHMENT APPLICATION**

# **PRESSURE-ASSISTED Cu SINTERING FOR SiC DIE-ATTACHMENT APPLICATION**

## **Dissertation**

for the purpose of obtaining the degree of doctor

at Delft University of Technology

by the authority of the Rector Magnificus prof. dr. ir. T.H.J.J. van der Hagen

chair of the Board for Doctorates

to be defended publicly on

Monday, 30 January 2023 at 12:30 o'clock

by

**Xu LIU**

Master of Science in Metallurgical Engineering,

RWTH Aachen University, Aachen, Germany,

born in Inner Mongolia, China.

This dissertation has been approved by

Promotor: prof. dr. G.Q. Zhang

Composition of the doctor committee:

|                       |                                                         |

|-----------------------|---------------------------------------------------------|

| Rector Magnificus,    | Chairperson                                             |

| Prof. dr. G.Q. Zhang, | Delft University of Technology, promotor                |

| Prof. dr. H.Y. Ye,    | Southern University of Science & Technology, copromotor |

*Independent members:*

|                               |                                                |

|-------------------------------|------------------------------------------------|

| Prof. dr. R. S. W. Lee,       | Hong Kong University of Science & Technology   |

| Prof. dr. ir. G. Rietveld,    | University of Twente                           |

| Prof. dr. R. Ross,            | Institute for Science & Development            |

| Prof. dr. ir. W.D. van Driel, | Delft University of Technology                 |

| Prof. dr. P. J. French,       | Delft University of Technology                 |

| Prof. dr. ir. P.M. Sarro,     | Delft University of Technology, reserve member |

*Keywords:* Nano Cu Sintering, Silicon Carbide Power Electronics Packaging, Shear Strength, Mechanical Reliability, Static and Dynamic Test, Thermal Conductivity, Nanoindentation, Molecular Dynamics

*Printed by:* Ipsonkamp printing

*Front & Back:* Cover art work of copper element, copper nanoparticles and Cu-sintered SiC die-attachment samples, by Xu Liu. Based on the "Trama A" artwork by Luis Medina©, under his permission.

Copyright © 2023 by X. Liu

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means without the prior permission in writing from the copyright owner. ISBN 978-94-6473-018-0

An electronic version of this dissertation is available at

<http://repository.tudelft.nl/>.

*To my parents and xiazi*

# CONTENTS

|                                                                                       |            |

|---------------------------------------------------------------------------------------|------------|

| <b>Summary</b>                                                                        | <b>xi</b>  |

| <b>Samenvatting</b>                                                                   | <b>xv</b>  |

| <b>List of Abbreviations</b>                                                          | <b>xix</b> |

| <b>1 Introduction</b>                                                                 | <b>1</b>   |

| 1.1 Merits of SiC Material and Device . . . . .                                       | 2          |

| 1.2 Die Attachment Technologies for Power Electronics Packaging Application . . . . . | 4          |

| 1.2.1 Reflow Soldering . . . . .                                                      | 4          |

| 1.2.2 Transient Liquid Phase Method . . . . .                                         | 5          |

| 1.2.3 Single-Metal Sintering . . . . .                                                | 6          |

| 1.3 Copper Sintering Technique . . . . .                                              | 8          |

| 1.3.1 Material Treatment . . . . .                                                    | 8          |

| 1.3.2 Paste Formulation and Sintering Process . . . . .                               | 10         |

| 1.4 Challenges and Research Objectives . . . . .                                      | 12         |

| 1.4.1 For Atomic-Scale Sintering Mechanism . . . . .                                  | 12         |

| 1.4.2 For Cu Particles Treatment Method and Sintering Process Effect . . . . .        | 13         |

| 1.4.3 For Mechanical, Thermal and Electrical Properties Evaluation . . . . .          | 13         |

| 1.4.4 For Die-attachment Application of SiC Devices . . . . .                         | 13         |

| 1.5 Thesis Outline . . . . .                                                          | 14         |

| References . . . . .                                                                  | 15         |

| <b>2 Molecular Dynamics Study of Cu NPs Sintering Between Substrates</b>              | <b>23</b>  |

| 2.1 Introduction . . . . .                                                            | 24         |

| 2.2 Methods . . . . .                                                                 | 25         |

| 2.2.1 Simulation Model . . . . .                                                      | 25         |

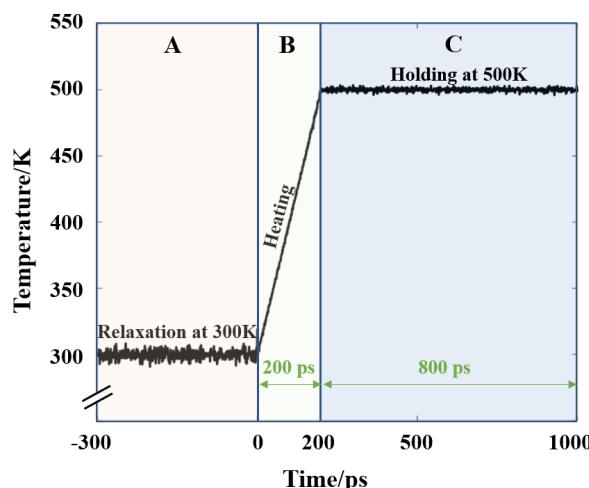

| 2.2.2 Temperature Profile . . . . .                                                   | 26         |

| 2.2.3 Data Recording and Analyzing Methods . . . . .                                  | 27         |

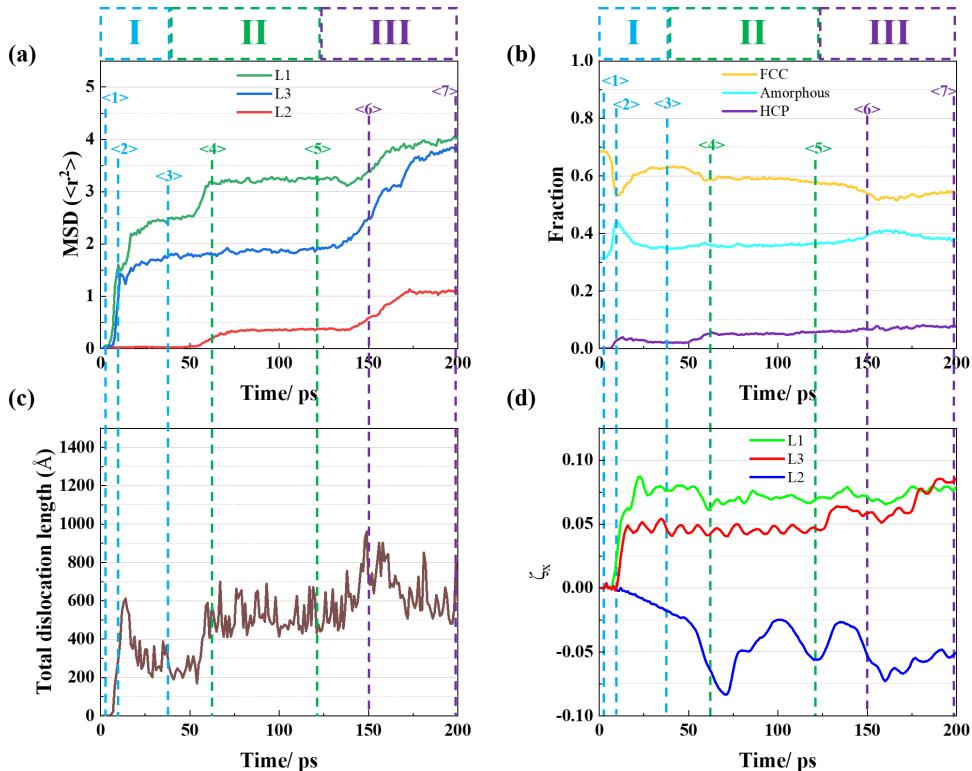

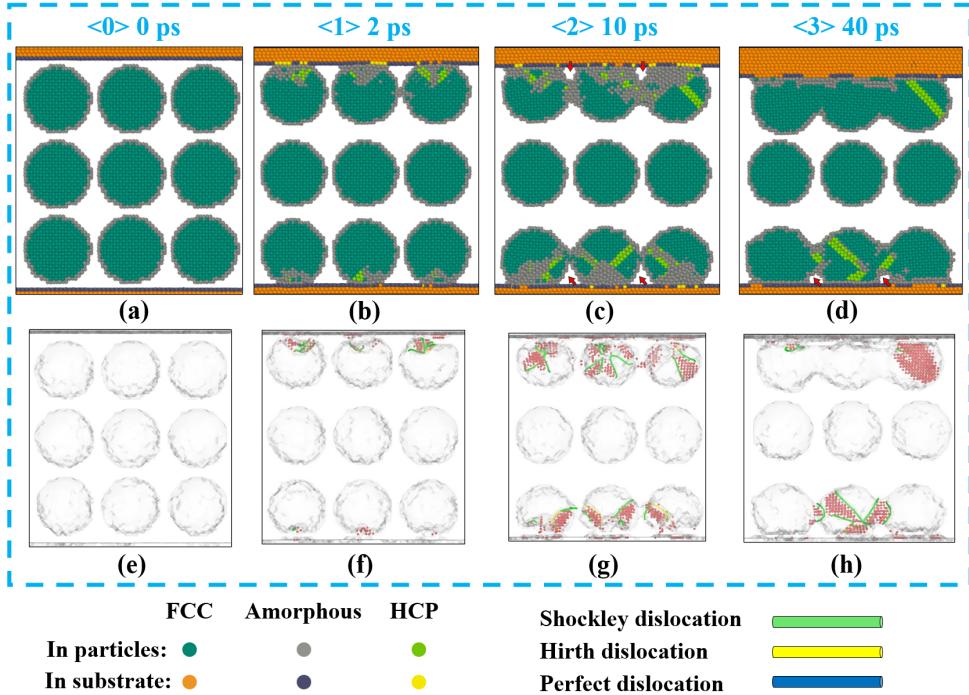

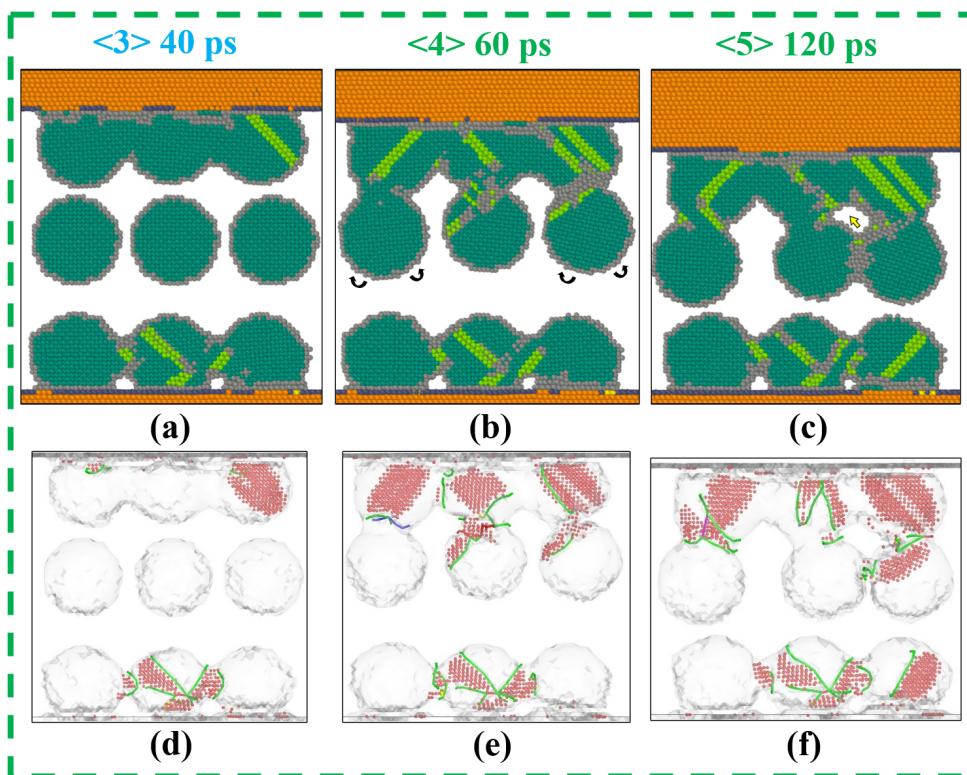

| 2.3 Coalescence Kinetics of NPs-Substrates Model . . . . .                            | 28         |

| 2.3.1 Stage I . . . . .                                                               | 29         |

| 2.3.2 Stage II . . . . .                                                              | 32         |

| 2.3.3 Stage III . . . . .                                                             | 33         |

| 2.4 Pores Evolution and Rotation Behavior . . . . .                                   | 35         |

| 2.4.1 Pores Evolution Between NPs and Substrates . . . . .                            | 35         |

| 2.4.2 Rotation Behavior of NPs Affected by the Substrate . . . . .                    | 35         |

| 2.5 Size Effect of NPs on the Sintering Mechanism . . . . .                           | 38         |

| 2.6 Conclusion . . . . .                                                              | 40         |

| References . . . . .                                                                  | 41         |

|                                                                                            |           |

|--------------------------------------------------------------------------------------------|-----------|

| <b>3 Die-attach Performance Evaluation and Mechanisms Study of Cu Sintering Technology</b> | <b>45</b> |

| 3.1 <b>Introduction</b>                                                                    | 46        |

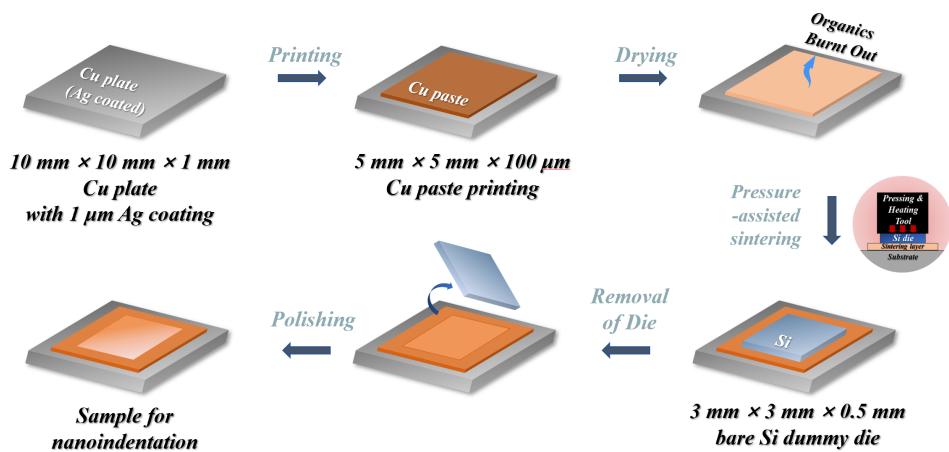

| 3.2 <b>Materials and Methodologies</b>                                                     | 46        |

| 3.2.1 Cu Particles and Other Materials                                                     | 46        |

| 3.2.2 Cu QNPs Treatment and Paste Formulation                                              | 47        |

| 3.2.3 The Die-attach Samples and Shear Strength Measurement                                | 47        |

| 3.2.4 Samples for Thermal and Electrical Properties Measurement                            | 49        |

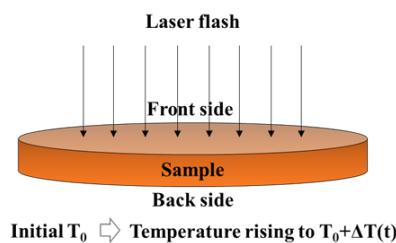

| 3.2.5 Thermal Conductivity Measurement Method                                              | 49        |

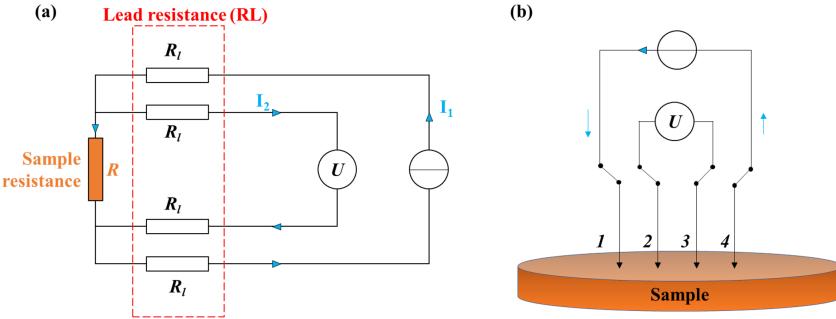

| 3.2.6 Electrical Resistivity Measurement Method                                            | 50        |

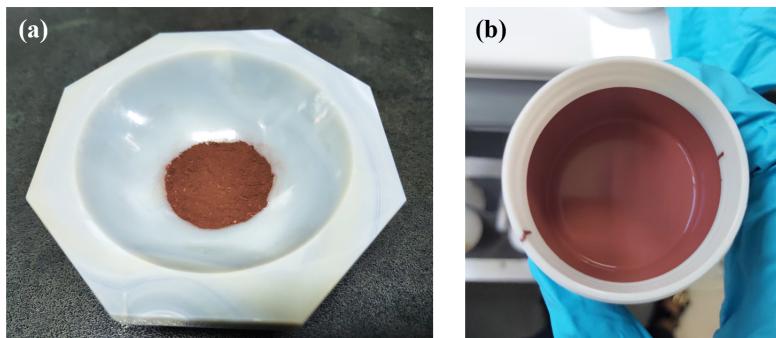

| 3.3 <b>Characterization of Cu QNPs and Cu Paste</b>                                        | 51        |

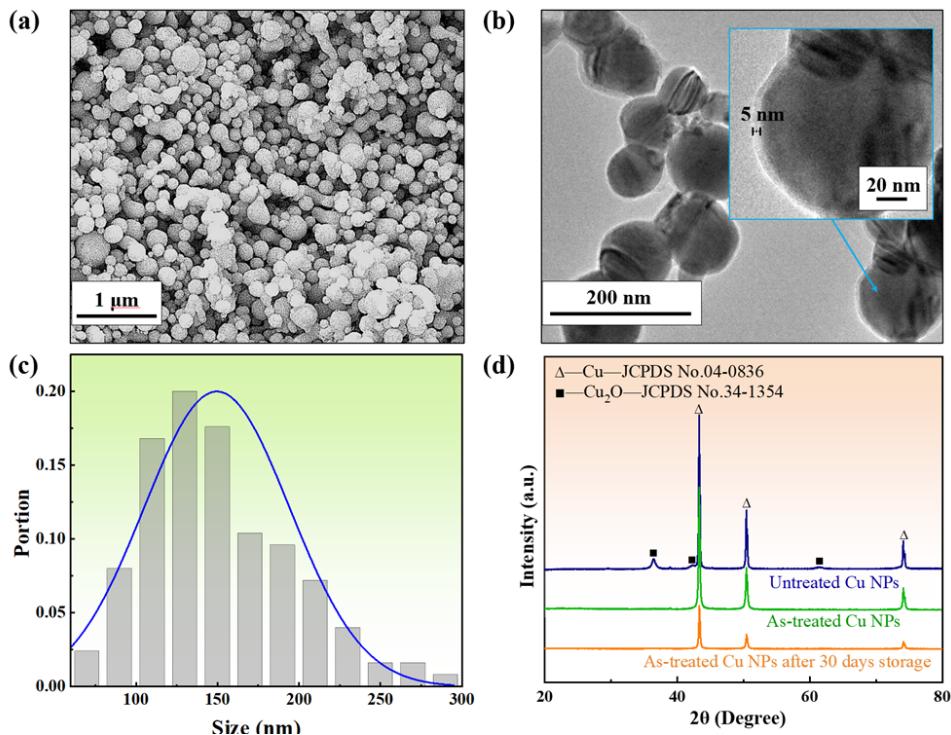

| 3.3.1 SEM, TEM and XRD Characterization of the Cu QNPs                                     | 51        |

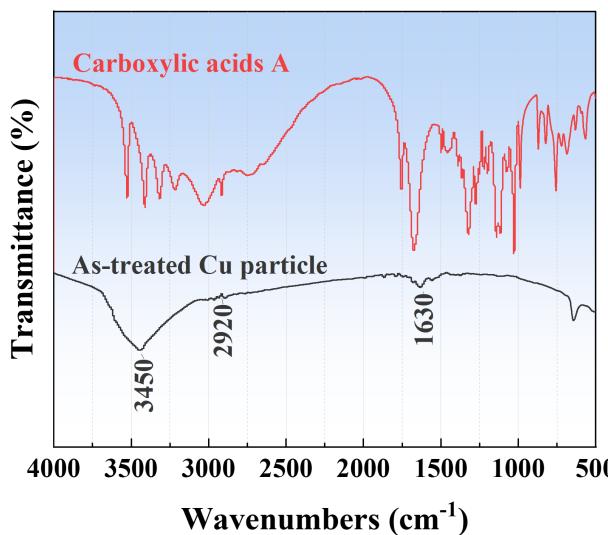

| 3.3.2 FT-IR Spectroscopy of the Cu QNPs                                                    | 53        |

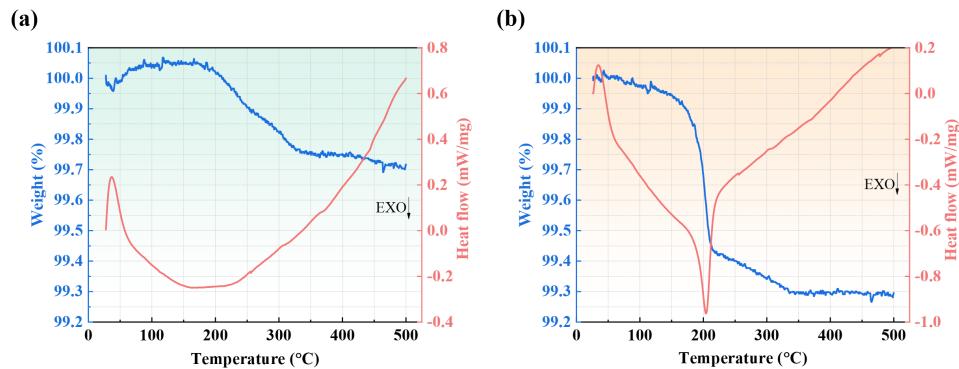

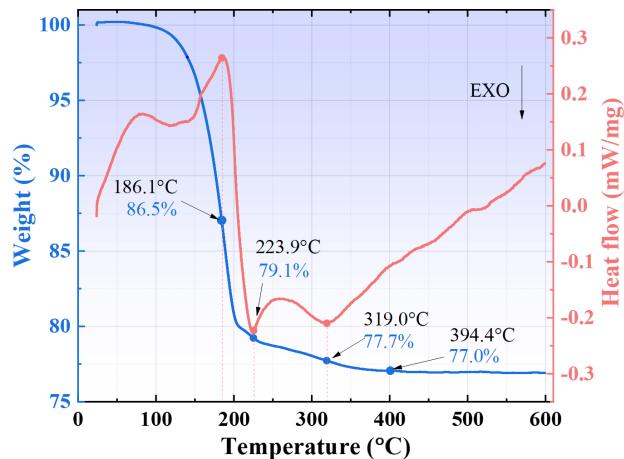

| 3.3.3 TG/DSC Characterization of the Cu NPs                                                | 53        |

| 3.3.4 TG/DSC Characterization of the Cu Paste                                              | 54        |

| 3.4 <b>Study on The Effects of Process Parameters on the Key Properties</b>                | 55        |

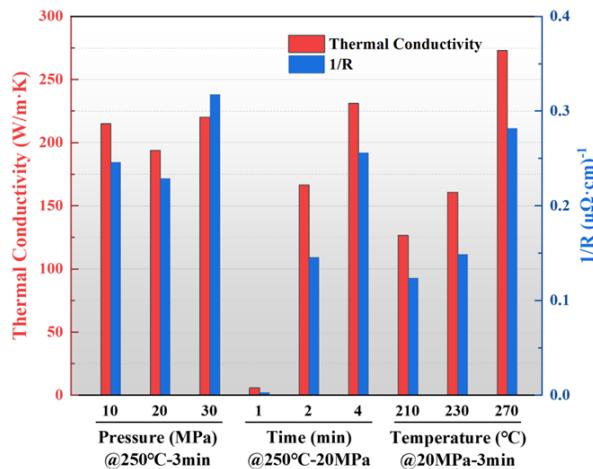

| 3.4.1 Thermal and Electrical Properties                                                    | 55        |

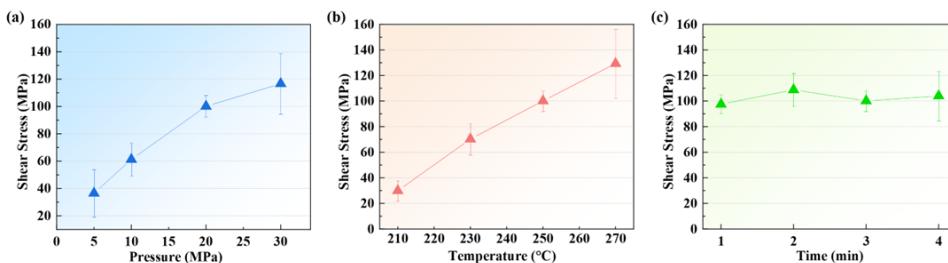

| 3.4.2 Shear Strength                                                                       | 56        |

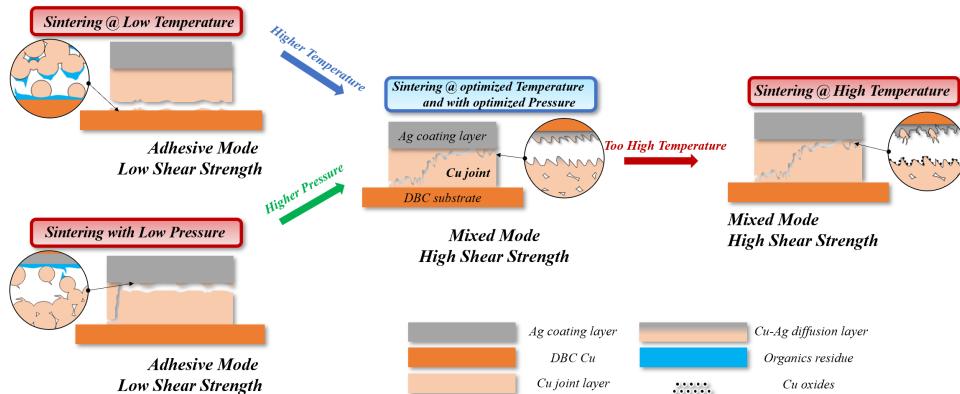

| 3.5 <b>Effects of Process Parameters on the Evolution of Microstructure</b>                | 58        |

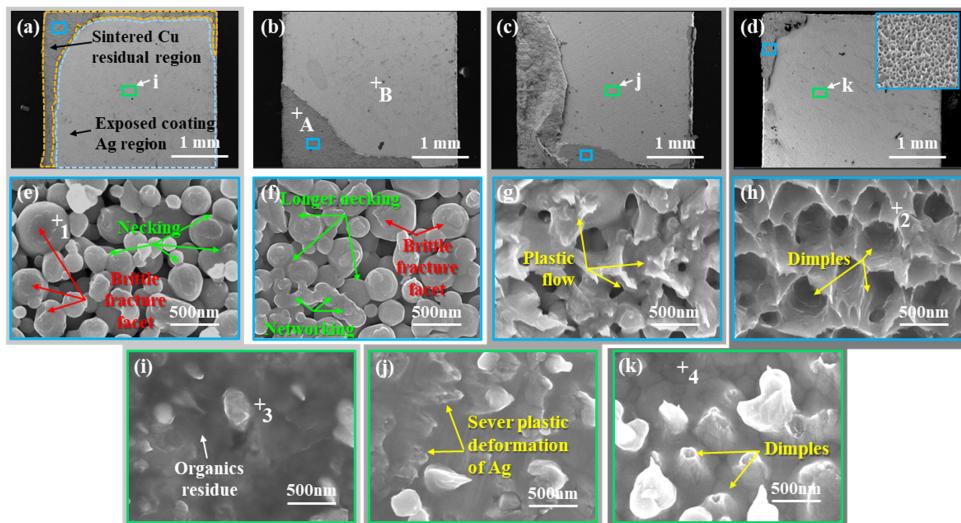

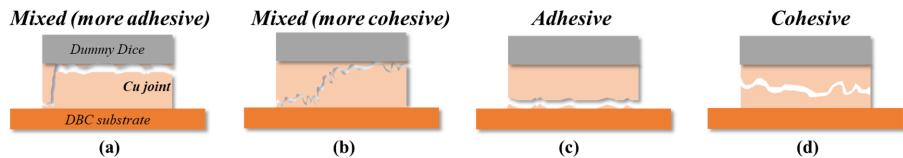

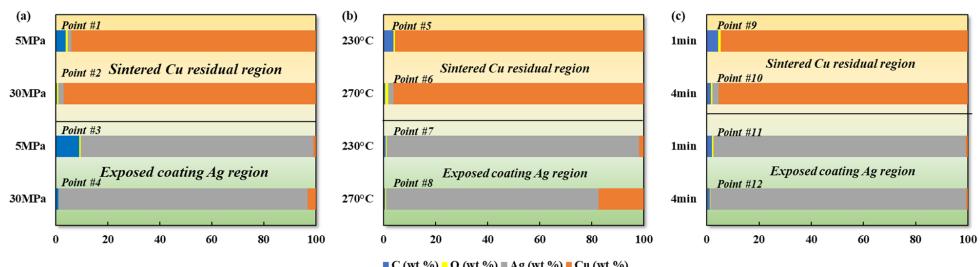

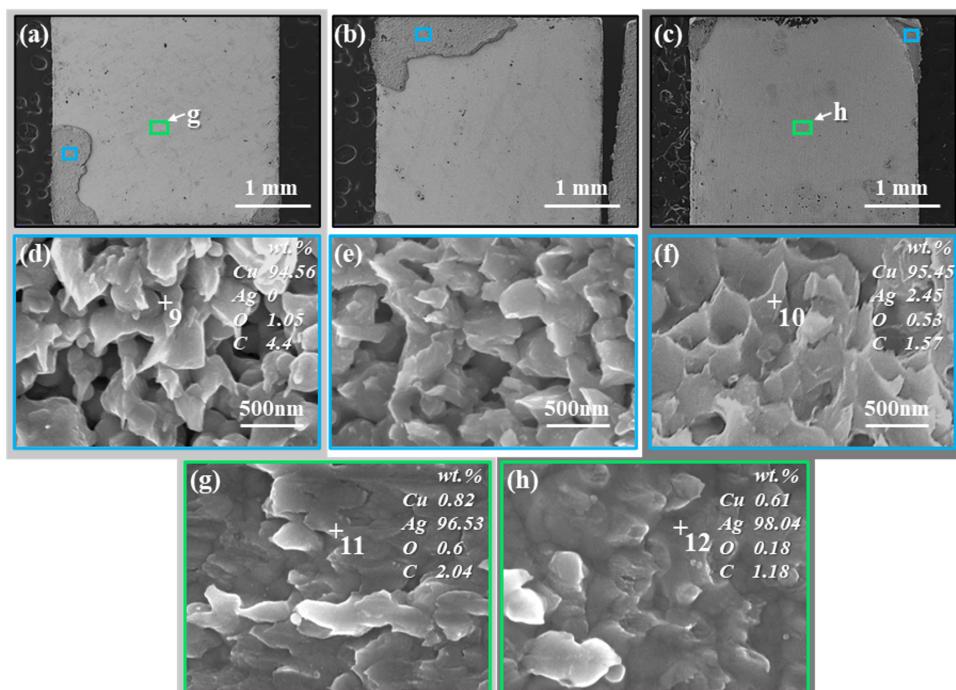

| 3.5.1 Fracture Mode                                                                        | 58        |

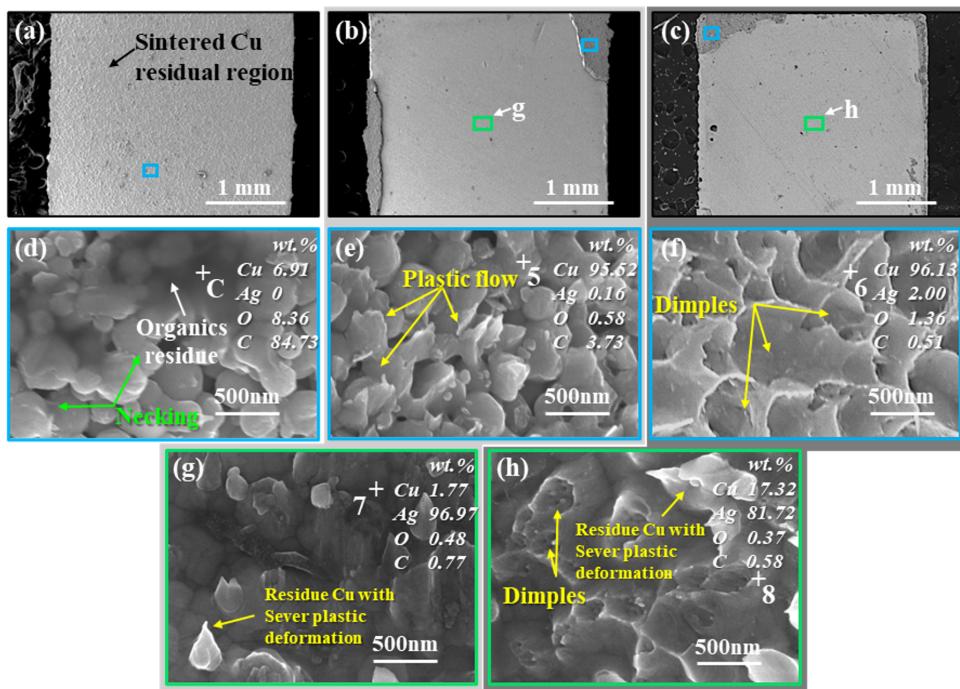

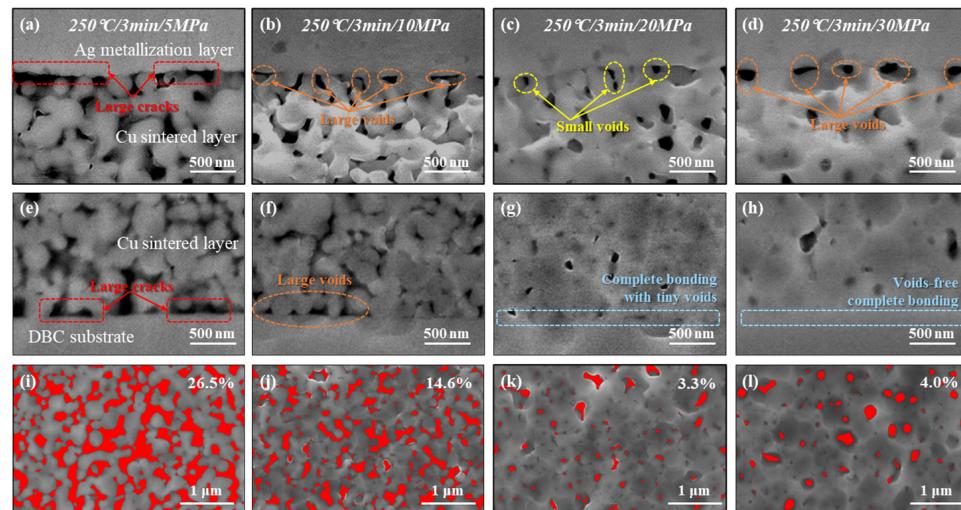

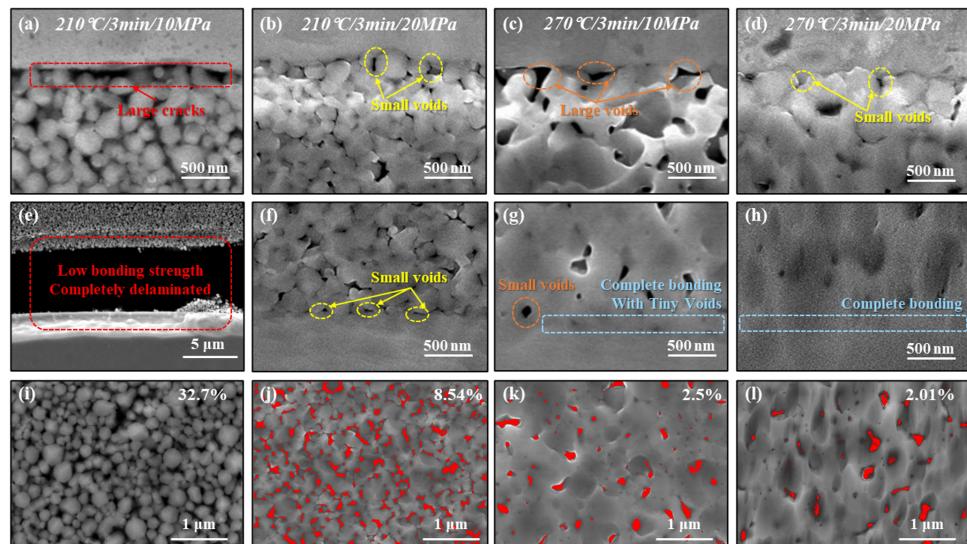

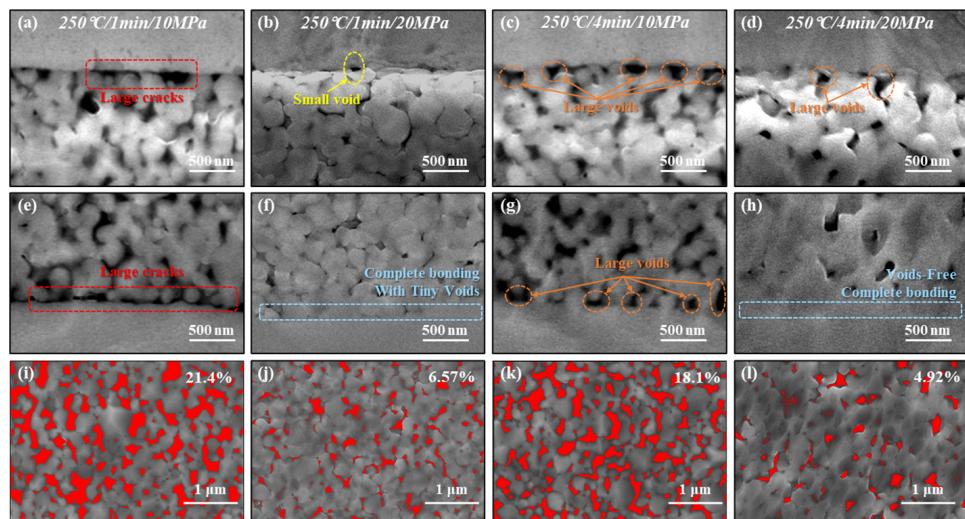

| 3.5.2 Interface Evolution                                                                  | 63        |

| 3.5.3 Bonding Mechanism                                                                    | 66        |

| 3.6 <b>Conclusion</b>                                                                      | 68        |

| References                                                                                 | 69        |

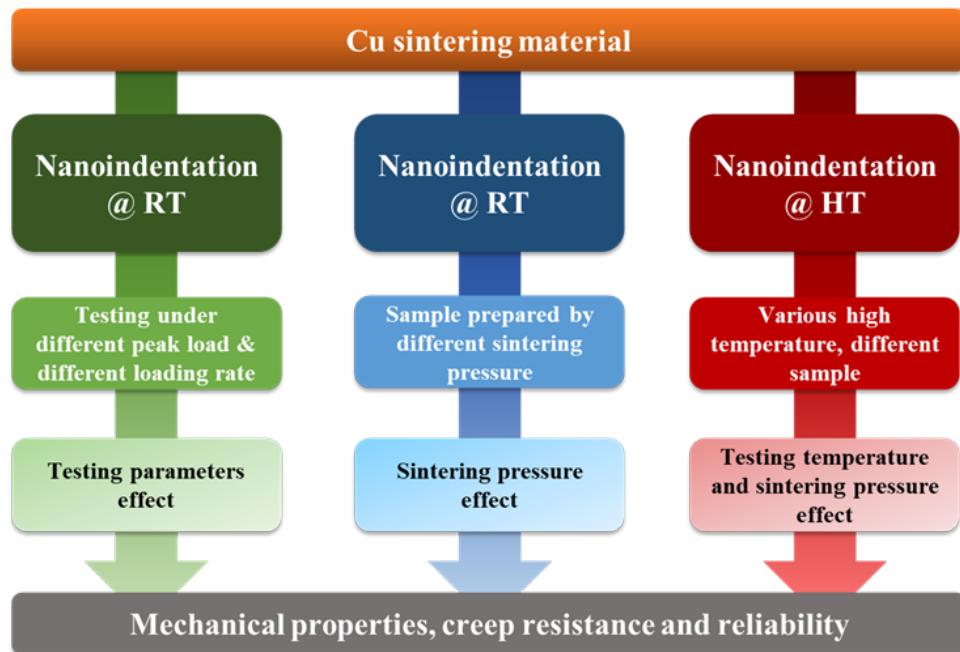

| <b>4 Mechanical Properties and Creep Behavior of Cu Sintered Material</b>                  | <b>73</b> |

| 4.1 <b>Introduction</b>                                                                    | 74        |

| 4.2 <b>Methodology</b>                                                                     | 75        |

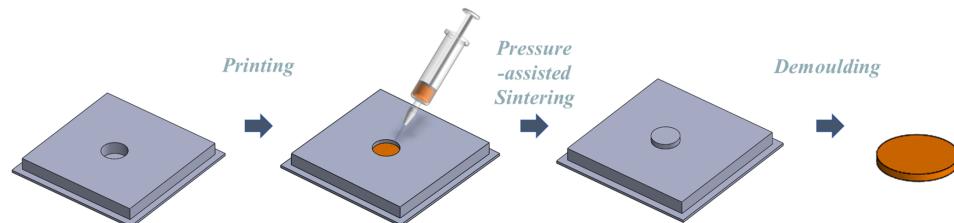

| 4.2.1 Sample Preparation                                                                   | 75        |

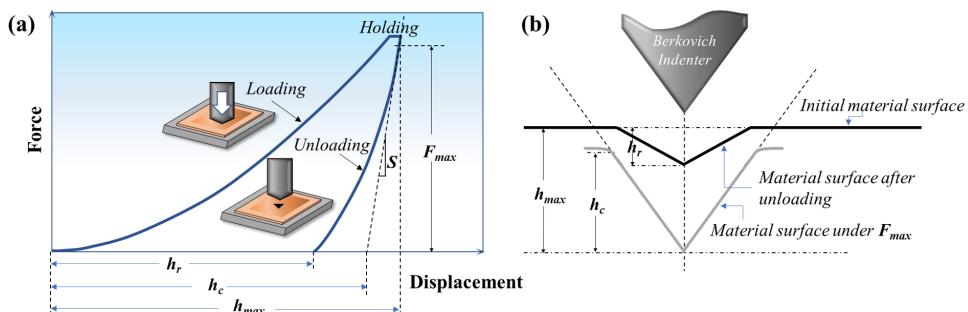

| 4.2.2 Nanoindentation Test and Displacement-load Curve                                     | 76        |

| 4.2.3 Indentation Hardness and Elastic Modulus Calculation                                 | 77        |

| 4.2.4 Constitutive Model                                                                   | 77        |

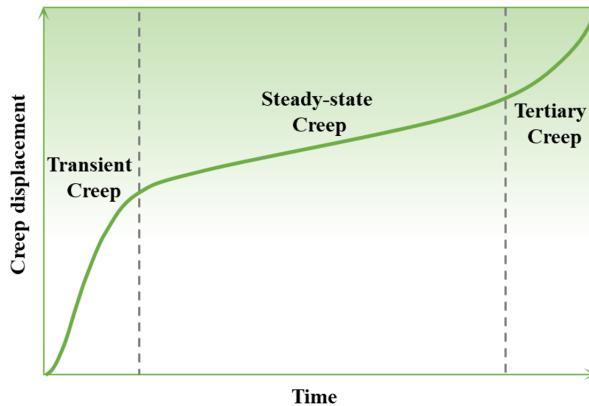

| 4.2.5 Creep Behavior                                                                       | 78        |

| 4.3 <b>Nanoindentation Study at Room Temperature</b>                                       | 79        |

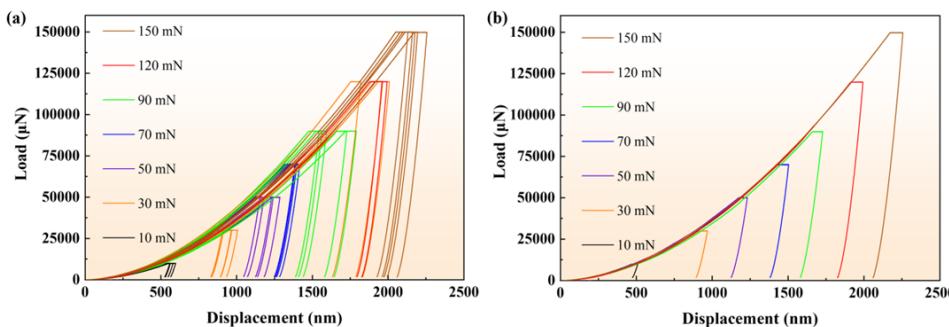

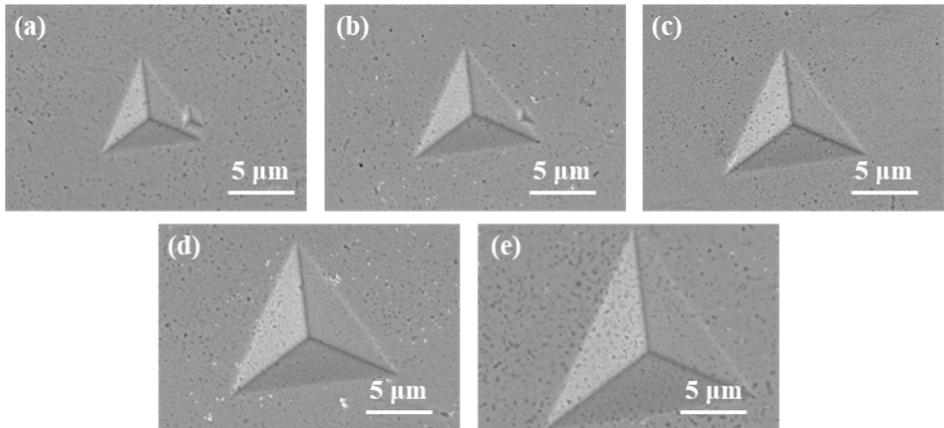

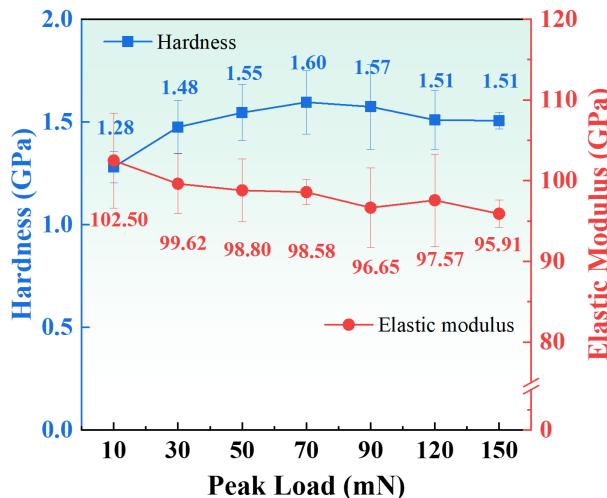

| 4.3.1 Effects of Peak Load at Room Temperature                                             | 79        |

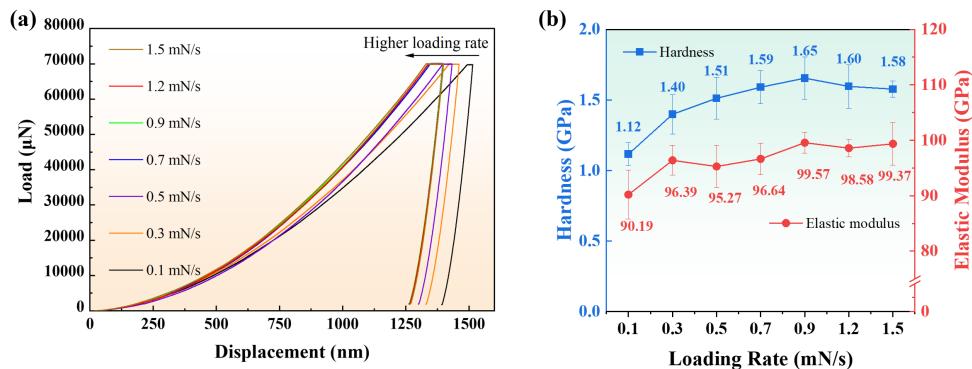

| 4.3.2 Effects of Loading Rate at Room Temperature                                          | 82        |

| 4.3.3 Effect of Sintering Pressure at Room Temperature                                     | 83        |

| 4.3.4 Constitutive Modeling Derivation                                                     | 83        |

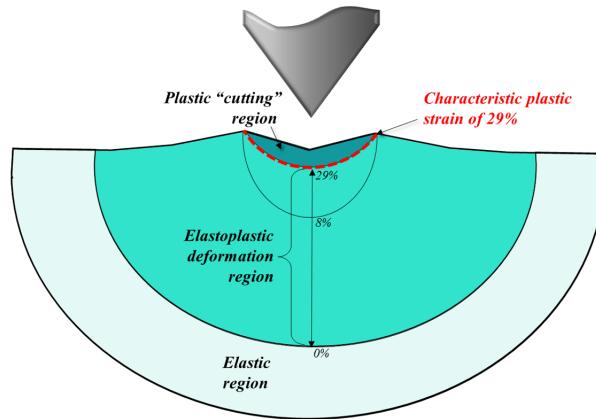

| 4.4 <b>Nanoindentation Study at High Temperature</b>                                       | 85        |

| 4.4.1 Displacement-load Curves at High Temperature                                         | 85        |

| 4.4.2 Hardness and Elastic Modulus at High Temperature                                     | 86        |

| 4.4.3 Creep Effect at High Temperature                                                     | 89        |

| 4.5 <b>Conclusion</b>                                                                      | 90        |

| References                                                                                 | 91        |

---

|                                                                            |            |

|----------------------------------------------------------------------------|------------|

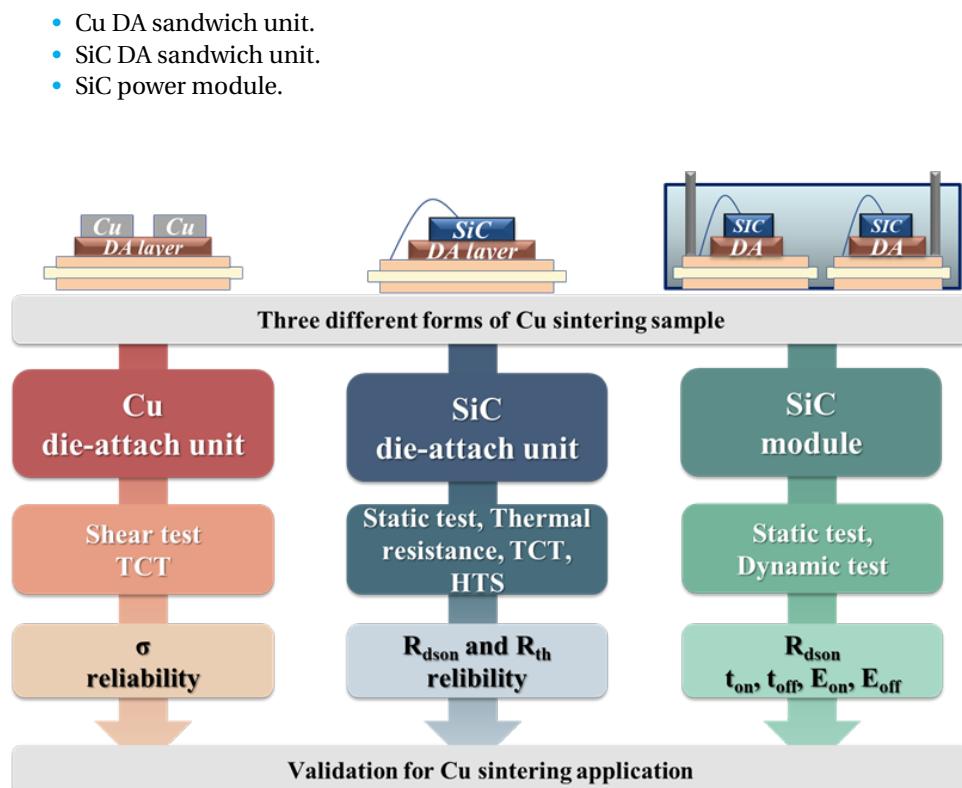

| <b>5 Application and Characterization of Cu Sintered SiC Power Modules</b> | <b>95</b>  |

| 5.1 Introduction . . . . .                                                 | 96         |

| 5.2 Methodology . . . . .                                                  | 97         |

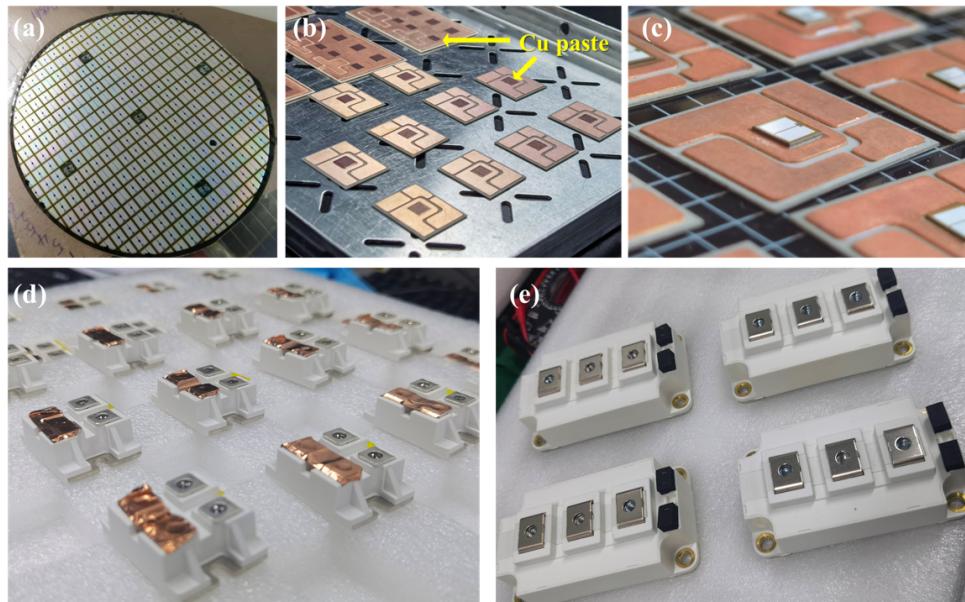

| 5.2.1 Cu-Sintered Cu DA Units . . . . .                                    | 98         |

| 5.2.2 Cu-Sintered SiC DA Units . . . . .                                   | 98         |

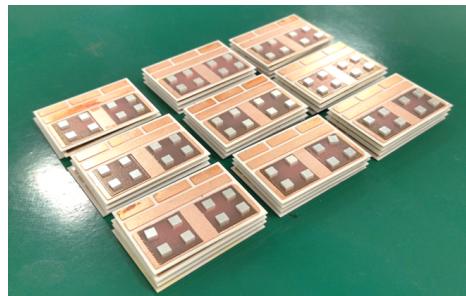

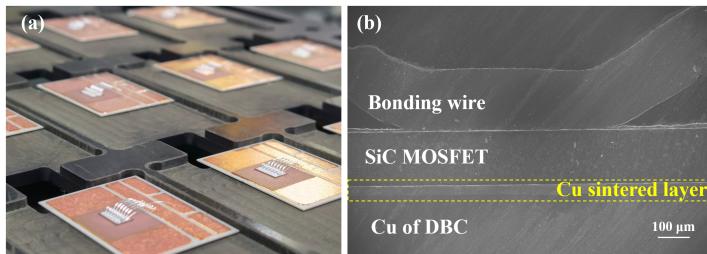

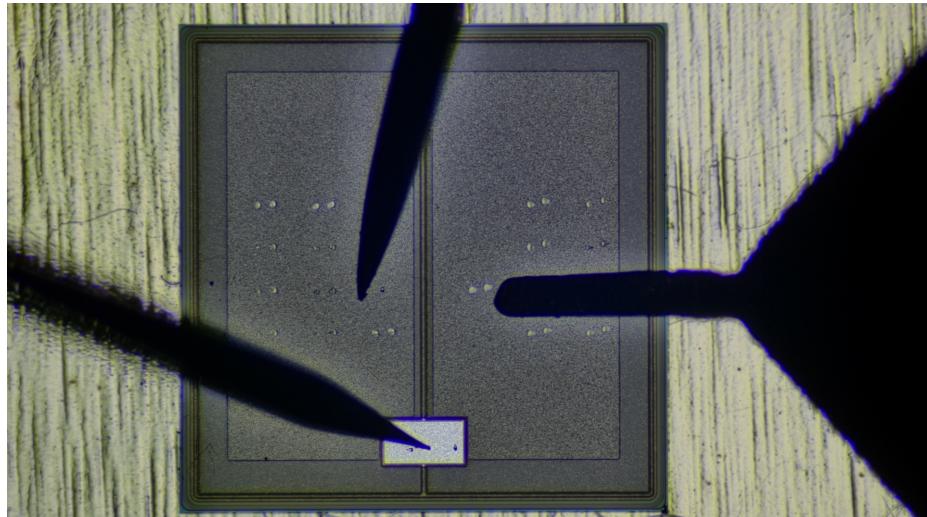

| 5.2.3 Cu-Sintered SiC Power Modules . . . . .                              | 99         |

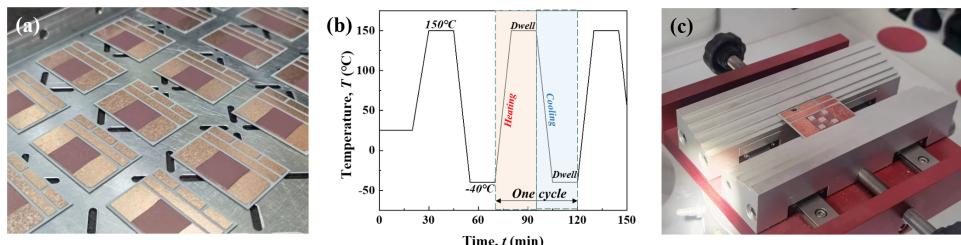

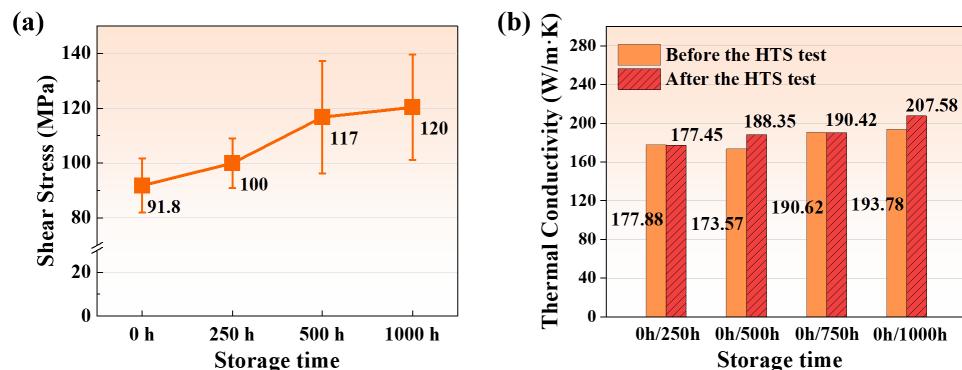

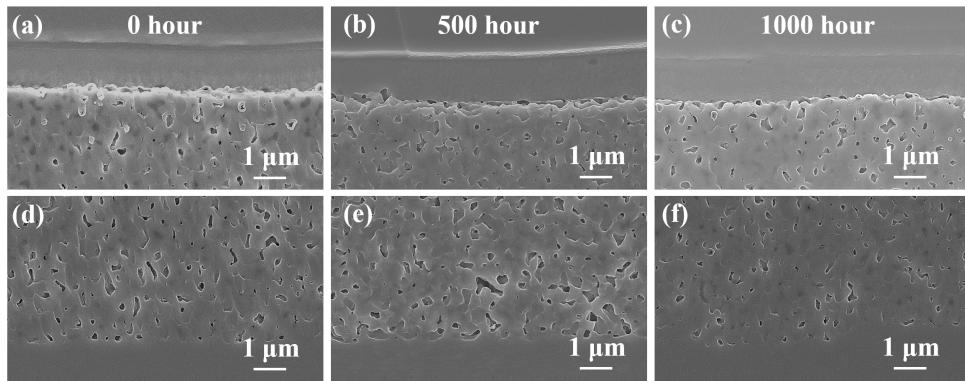

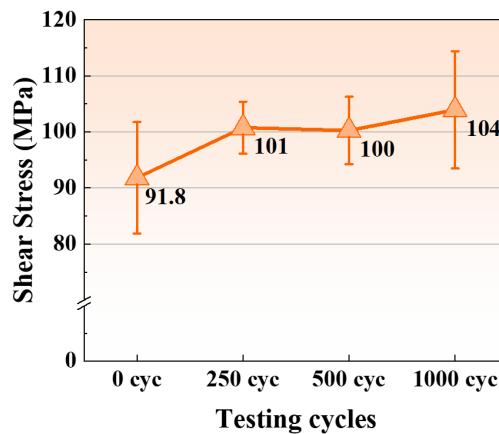

| 5.3 TCT and HTS Reliability of Shear Strength . . . . .                    | 100        |

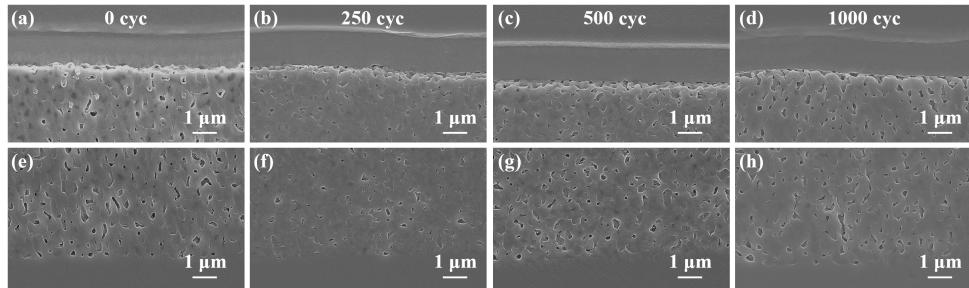

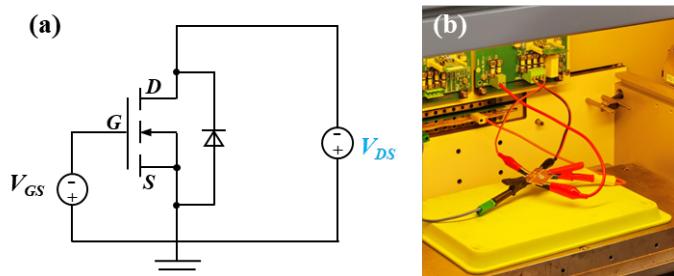

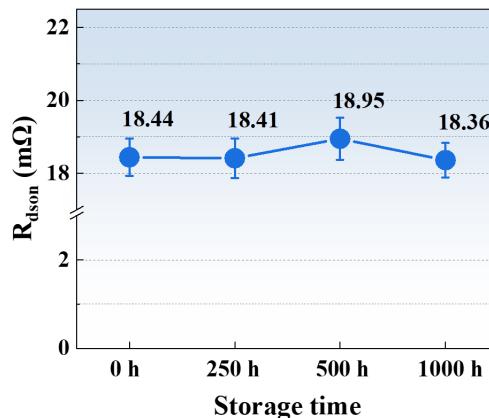

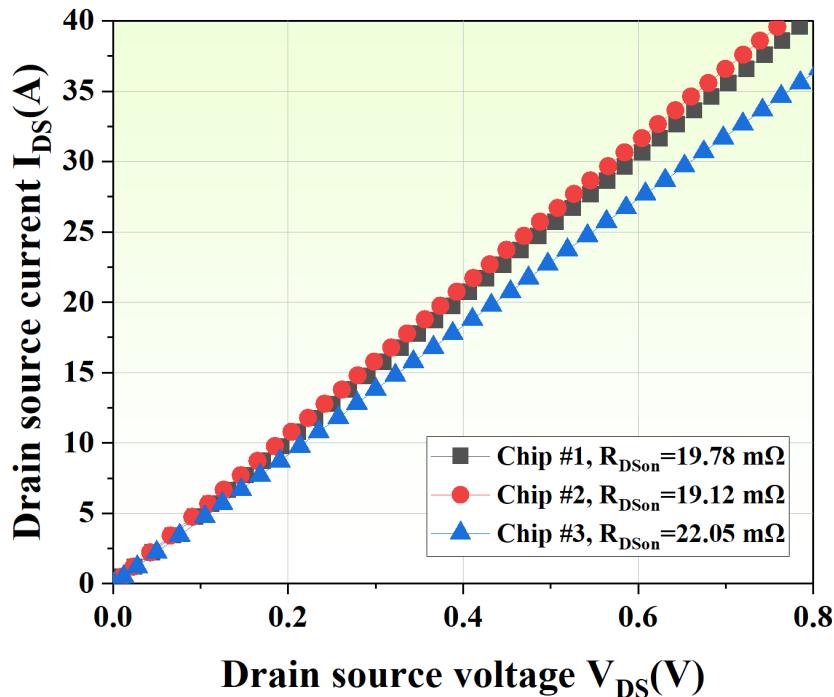

| 5.4 HTS Reliability of $R_{DSon}$ . . . . .                                | 102        |

| 5.5 TCT Reliability of $R_{th}$ . . . . .                                  | 103        |

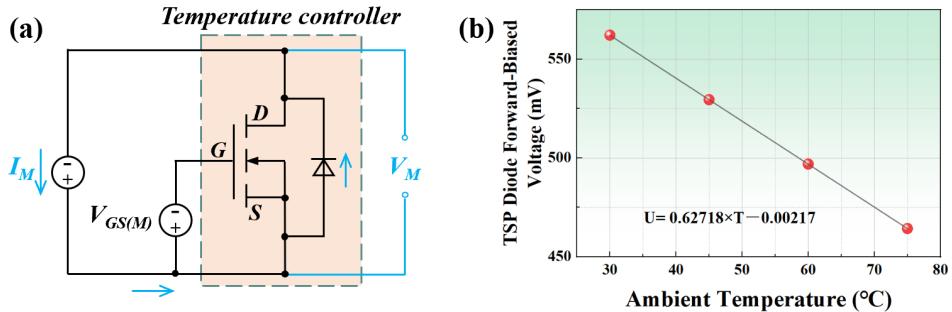

| 5.6 Static and Dynamic Test of SiC Power Modules . . . . .                 | 106        |

| 5.6.1 Static Test (I-V Characteristics) of SiC Power Modules . . . . .     | 106        |

| 5.6.2 Dynamic Test of SiC Power Modules . . . . .                          | 107        |

| 5.7 Conclusion . . . . .                                                   | 110        |

| References . . . . .                                                       | 110        |

| <b>6 Conclusions and Recommendations</b>                                   | <b>115</b> |

| 6.1 Conclusions . . . . .                                                  | 115        |

| 6.2 Recommendations in Future Works . . . . .                              | 118        |

| <b>A Supporting Information Chapter 2</b>                                  | <b>119</b> |

| References . . . . .                                                       | 122        |

| <b>B Supporting Information Chapter 3</b>                                  | <b>125</b> |

| <b>C Supporting Information Chapter 4</b>                                  | <b>129</b> |

| <b>D Supporting Information Chapter 5</b>                                  | <b>131</b> |

| <b>Acknowledgements</b>                                                    | <b>133</b> |

| <b>Curriculum Vitae</b>                                                    | <b>137</b> |

| <b>List of Publications</b>                                                | <b>139</b> |

# SUMMARY

Typical wide bandgap (WBG) semiconductor materials such as silicon carbide (SiC) and gallium nitride (GaN) contain larger bandgap, higher critical electric field and higher thermal conductivity than silicon (Si). These features ensure that power devices operate at much higher power levels ( $> 100\text{MW}$ ), faster switching speed ( $> 100\text{ kHz}$ ), and higher temperatures ( $> 300^\circ\text{C}$ ). However, the increased performance on the chip side has also led to higher requirements for package structures and materials. To support the stable performance of power chips under harsh conditions, the high-temperature reliability of die-attach materials is also critical. In recent years, copper sintering has emerged as one of the most promising solutions in the industry due to its excellent material properties. However, until now, academic and industrial research on copper sintering is still in its infancy. Therefore, a systematic study of copper sintering technology in combination with materials, processes, simulations, applications and tests is of great importance in promoting the industrial application of this technology.

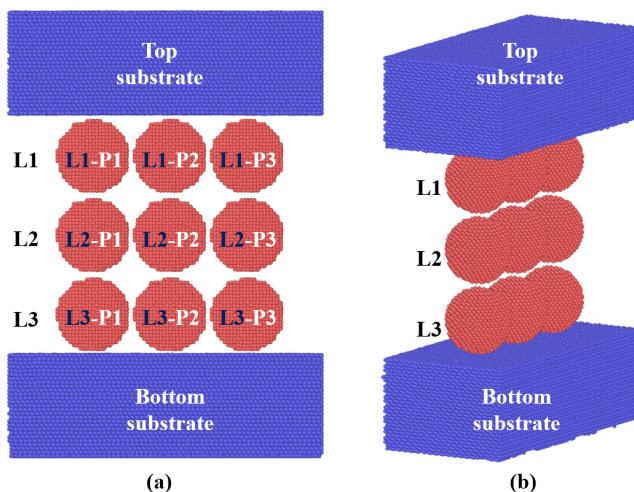

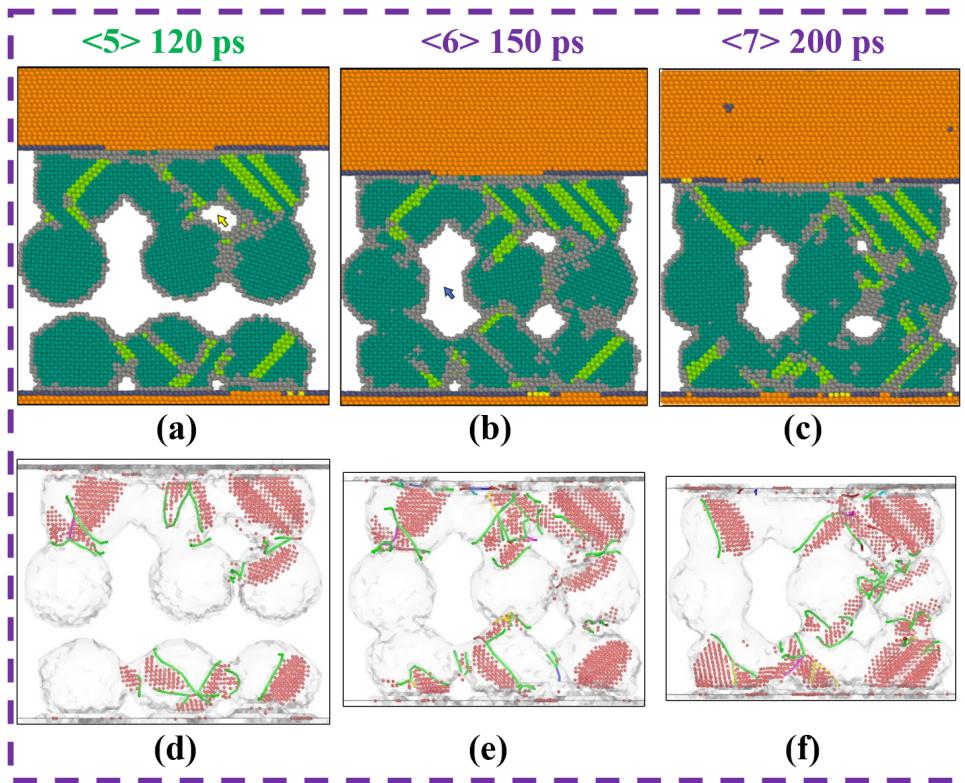

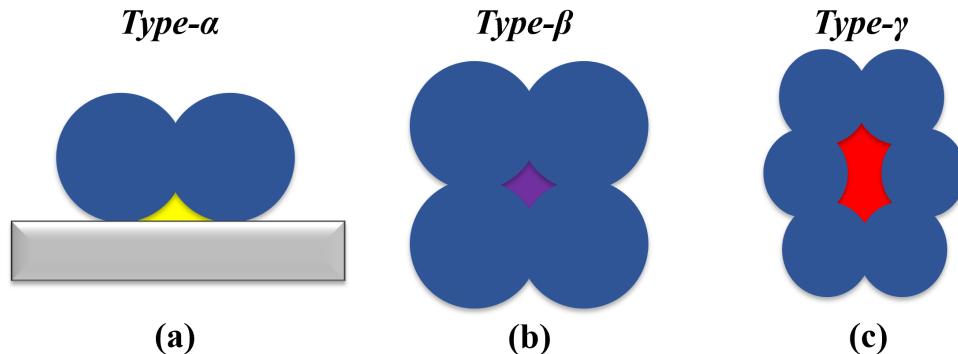

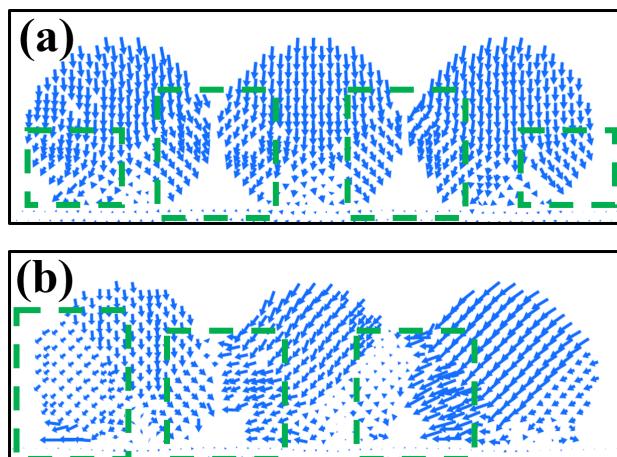

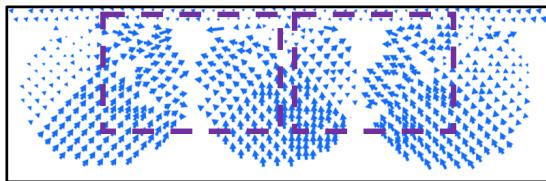

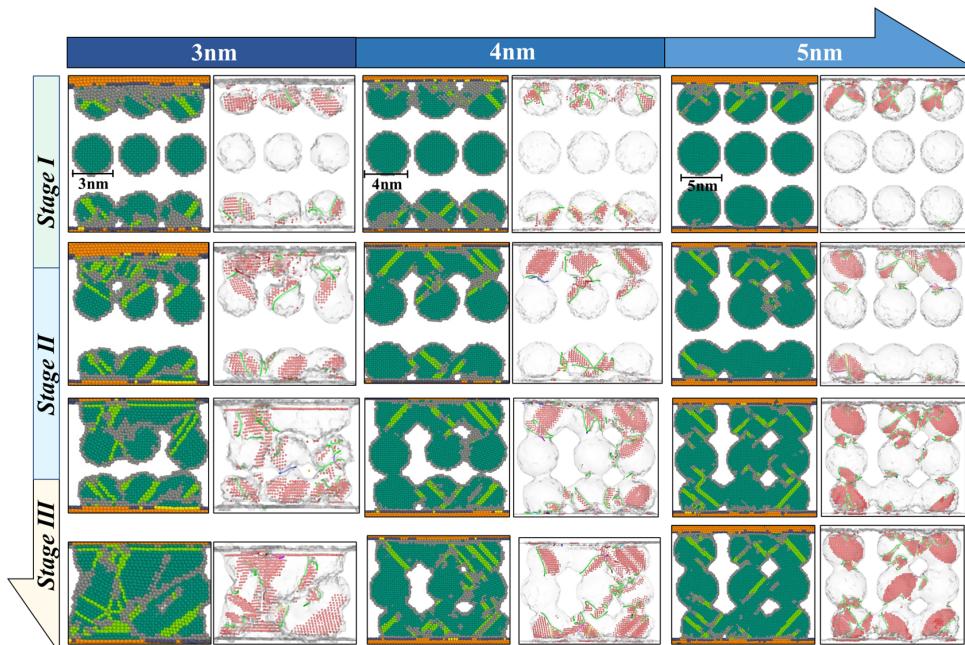

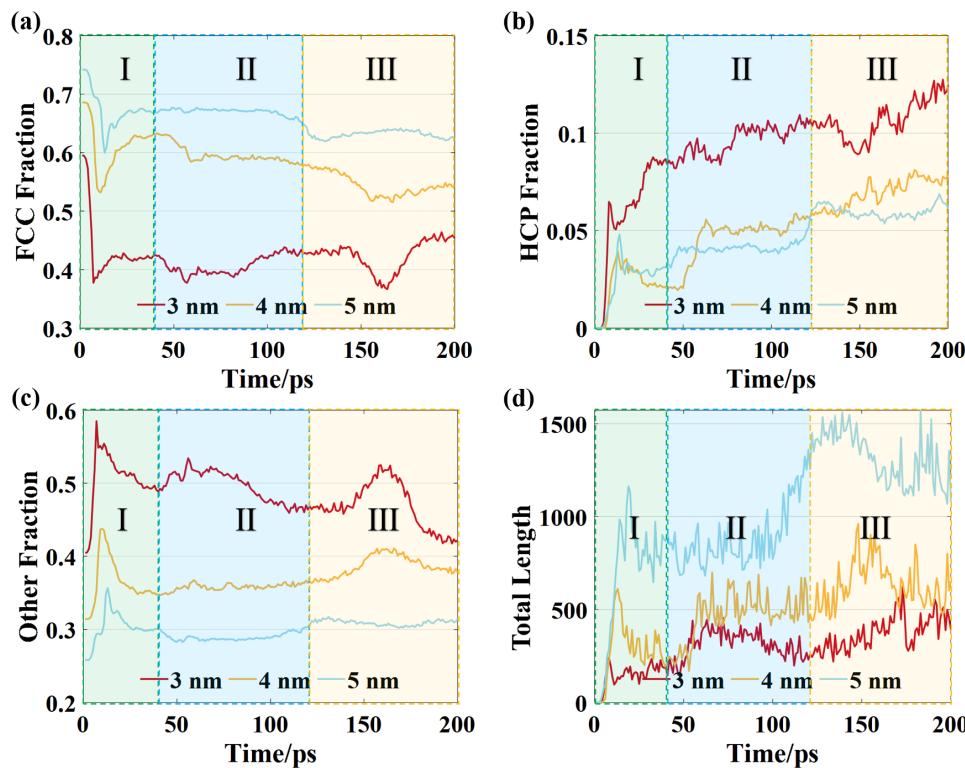

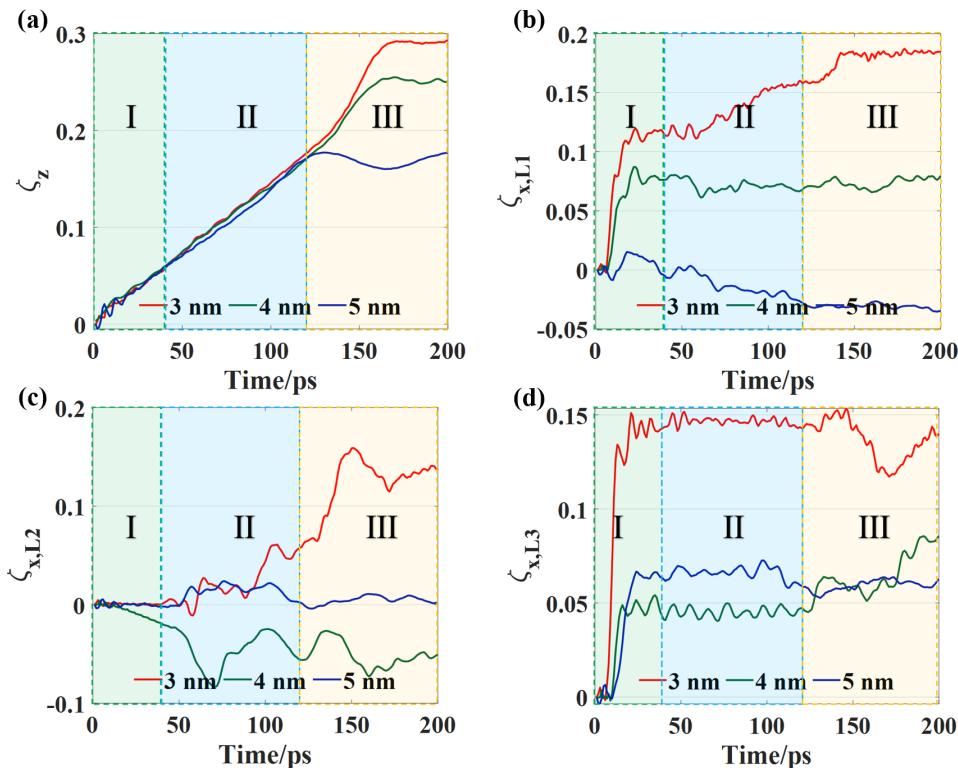

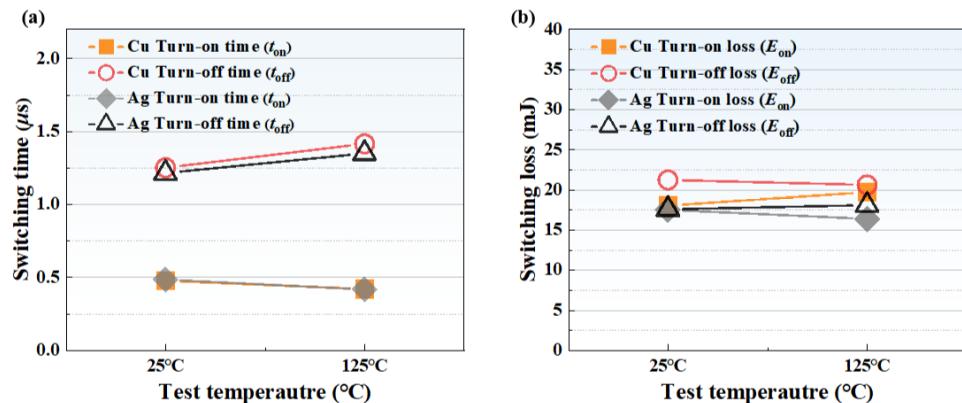

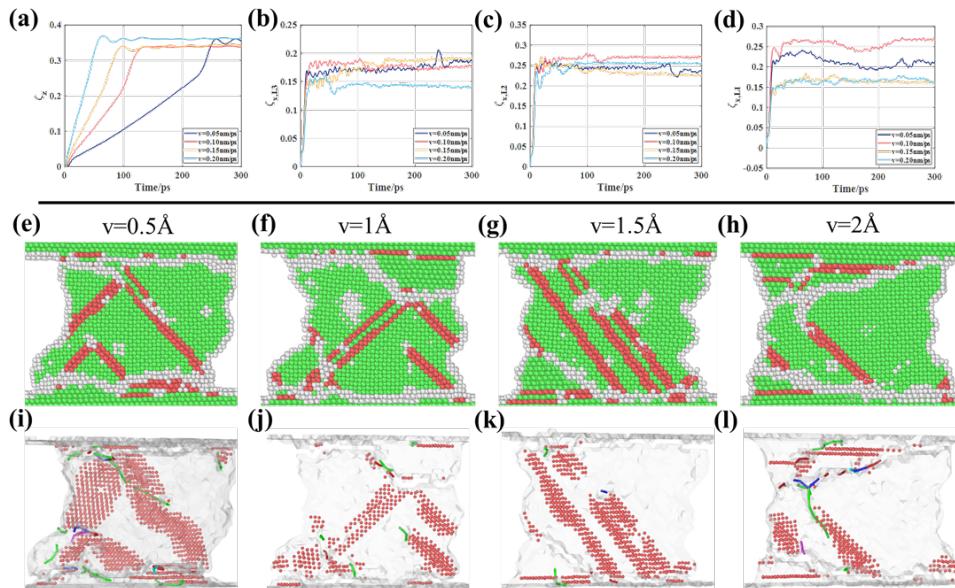

In this dissertation, firstly, a molecular dynamic (MD) simulation was carried out to study the coalescence kinetics and microstructure evolution of Cu nanoparticles sintering between two substrates at low temperatures. A sandwich structure model with two substrates and multiple particles in between was constructed to simulate the real die-attach structure. The crystal structure, atomic diffusion, dislocation behavior and porous defects were studied by using OVITO tools, MSD curves, CNA and DXA analysis. It was found that the dominant sintering mechanism for the particles without applied pressure, the sintering mechanism at low temperatures was mainly surface diffusion. However, when the pressure effect of the upper substrate on the particles was introduced, the dominant sintering mechanism of the particles changed to plastic flow induced by dislocation production and motion in the particles. In addition, the spontaneous rotation of particles occurred during the coalescence to eliminate the inter-particle lattice mismatch. Meanwhile, the passive rotation behavior of the bottom-layer particles also occurred due to the pinning effect of the substrate. Besides, the pinning effect of the substrate also caused giant pores between particles and substrates. Some of these pores can be filled via both plastic deformation and surface diffusion of atoms for the smaller particles. Finally, to investigate the size effect on the sintering kinetics, the atomic motion and microstructural evolution of 3 nm, 4 nm and 5 nm models were compared. It was found that the models of smaller size particles typically contained higher shrinkage ratios, larger sintering necks and smaller pores. More severe atomic motion and more drastic crystal structure transitions at each stage were found in smaller size particles. The research results show that the sintering densification and pores structure can be improved by using the applied pressure in the sintering process. Particle sintering progress is greatly accelerated by enhancing the plastic flow mechanism. However, attention should also be paid to the problems such as rotational residual stresses brought about by the pinning effect of the substrate, which may require further heat treatment to

eliminate.

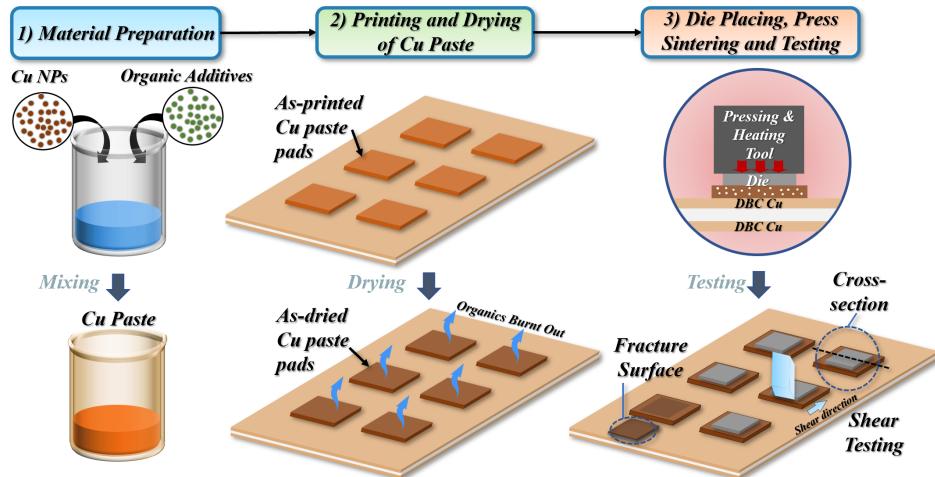

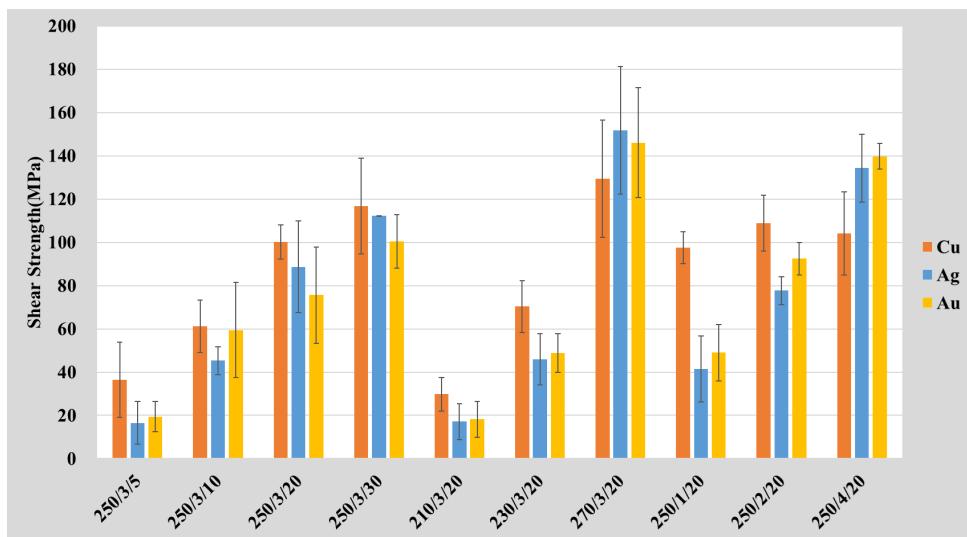

In the next chapter, a self-developed Cu paste was fabricated with predefined printing, and drying workability. A reductive pretreatment was conducted in advance to the raw Cu particles to remove the original oxidation. Then, laser flash measurements and four-probe measurements were carried out on the Cu sintered sample prepared by various temperatures, pressure and time, to evaluate the impact of the sintering process parameters on thermal and electrical properties. It was found that when the sintering process was at 250°C and 10 MPa with only 1 minute, the thermal (5.82 W/m·K) and electrical conductivity (0.003 /( $\mu\Omega\cdot\text{cm}$ )) of the sample is extremely small and cannot satisfy the semiconductor packaging requirements. Increasing the sintering time to 4 minutes can effectively improve the conductivity characteristics to 231.15 W/m·K and 0.255 /( $\mu\Omega\cdot\text{cm}$ ). There is a similar trend for the effect of temperature. From 210°C to 270°C, both properties are improved from 126.53 W/m·K and 0.124 /( $\mu\Omega\cdot\text{cm}$ ) to 272.87 W/m·K and 0.282 /( $\mu\Omega\cdot\text{cm}$ ). Among them, however, the effect of pressure is minimal. Then, in order to evaluate the impact of the Cu sintering process parameters on the joining performance and microstructure evolution of the die-attach samples, the shear test was conducted. It was also found that sintering temperature between 210°C and 230°C, or assisted pressure less than 10 MPa could provide bonding strength of around 30 MPa. Such low strength is due to both the partially burnt-out of organics and incomplete Cu particles sintering. By increasing pressure to 20 MPa and 30 MPa, it shows the enhanced die shear strength of 100.1 MPa and 116 MPa, accomplished with a sintering temperature of 250°C for 3 min. When increased temperature to 270°C, the shear strength was further enhanced to over 120 MPa. Moreover, time can insignificantly affect the microstructure and bonding strength in less than 4 min. Material microstructural characterization demonstrates that high bonding is coming from the positive effect of pressure and temperature on promoting the necking growth, sintering networking formation, pores isolation and brittle-ductile fracture transition. Considering the small improvement effect by further increasing of temperature and pressure, 250°C/3 min/20 MPa process recipe is well recommended for the application.

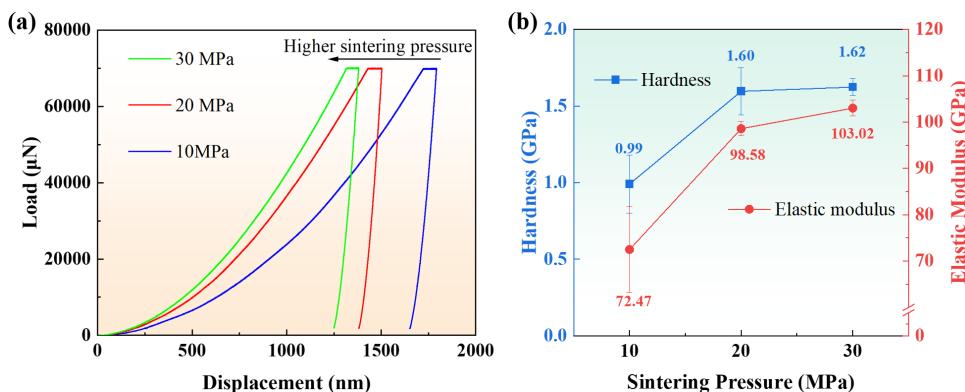

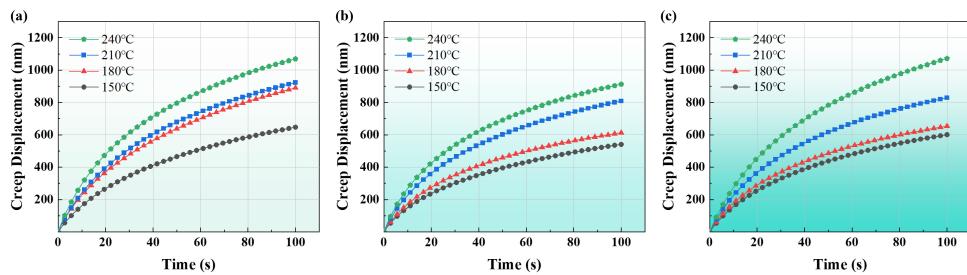

Next, in order to verify the robustness of this technique for application in die attachment processes, key mechanical properties such as indentation hardness, elastic modulus and creep behavior of Cu-sintered samples were evaluated separately. First of all, the peak load (from 10 mN to 150 mN) and loading rate (from 0.1 mN/s to 1.5 mN/s) effect on the indentation hardness and elastic modulus were investigated. The indentation size effect was found to be evident when the indentation depth was below 500 nm and the corresponding peak load was less than 10 mN. But after 70 mN of peak load (1500 nm of maximum depth), the changing trend was no more evident. Loading rate had a similar effect on these parameters. As it increased from 0.1 mN/s to 0.9 mN/s, both the indentation hardness and the elastic modulus gradually increased as well. But from 0.9 mN/s, the two properties started to become stable at around  $1.59 \pm 0.154$  GPa and  $99.5 \pm 0.86$  GPa. The potential causes were mainly work hardening effect, pores densification, and pile-up phenomena during the indentation test. Therefore, to ensure stable experimental results, an indentation depth of more than 1500 nm and a loading rate over 0.9 mN/s are necessary. By using the stable testing parameters, the constitutive models (yield stress, strain hardening exponent factors) for samples sintered via different

applied pressure were obtained, which can be used to describe the room-temperature mechanical properties of the Cu sintered joint. Next, the effects of temperature ranging from 150°C to 240°C on the indentation hardness and elastic modulus were investigated. The temperature dependence of both parameters was fitted to account for this effect. In addition, the creep behavior including the initial creep curves was studied and compared for samples sintered with different applied pressures. Higher testing temperatures were found to result in more severe creep deformations. However, higher sintering pressure can effectively improve the creep resistance against plastic deformation. But the increasing effect comes to a marginal over 20 MPa, which provides a hint to the selection of the sintering process parameters in practice.

Finally, a pressure-assisted Cu sintering die-attachment process (250°C/3 min/20 MPa) was adopted to prepare die-attach units and several SiC power modules. For the power module, the packaging process was conducted on an industrial standard packaging production line. The shear strength,  $R_{DSon}$  and thermal resistance reliability was investigated through 150°C/1000 hours high temperature storage test and -40°C~150°C /1000 cycles thermal cycling test. Then, the static and dynamic tests of the Cu-sintered SiC module were conducted. As a benchmark, the same SiC module that was die-attached by Ag sintering process was set in parallel. The experimental results indicated that both of the output characteristics switching performance of Cu-sintered SiC module are at the same level as Ag-sintered module did and consistent with the standard commercial one. Considering the comprehensive cost-performance balance, the presented Cu sintering technology is quite promising for WBG power electronics packaging application. At the end of the thesis, the main conclusions and contributions are summarized, and the outlook for future work in this field is proposed.

# SAMENVATTING

**T**YPISCHE Halfgeleidermaterialen met brede bandkloof (WBG) zoals siliciumcarbide (SiC) en galliumnitride (GaN) hebben een grotere bandkloof, een hoger kritisch elektrisch veld en een hoger warmtegeleidingsvermogen dan silicium (Si). Deze eigenschappen kunnen ervoor zorgen dat vermogensapparaten werken bij veel hogere vermogensniveaus ( $> 100\text{MW}$ ), een hogere schakelsnelheid ( $> 100\text{ kHz}$ ) en een hogere temperatuur ( $> 300^{\circ}\text{C}$ ). Om de stabiele prestaties van vermogenselektronica te ondersteunen in omstandigheden met een hoog vermogen, is de betrouwbaarheid bij hoge temperatuur van het materiaal van de matrijsbevestiging van cruciaal belang. In de afgelopen jaren is kopersintering naar voren gekomen als een van de meest veelbelovende oplossingen in de industrie vanwege de potentiële voordelen van hoge-temperatuureigenschappen. Tot nu toe stond de studie van kopersintering echter nog in de kinderschoenen in de academie en in de industrie. Daarom is een systematische studie van kopersinteringstechnieken in combinatie met materialen, proces, simulatie, toepassingen en testen van groot belang om de toepassing van deze techniek in industriële toepassingen te stimuleren.

In dit proefschrift werd eerst een moleculair dynamische (MD) simulatie uitgevoerd om de coalescentiekinetiek en microstructuurevolutie van Cu-nanopartikels die bij lage temperatuur tussen twee substraten sinteren te bestuderen. Een sandwichstructuurmodel met twee substraten en meerdere deeltjes ertussen werd geconstrueerd om de echte die-attach structuur te simuleren. De kristalstructuur, atoomdiffusie, dislocatiegedrag en poreuze defecten werden bestudeerd met behulp van OVITO, MSD-curen, CNA en DXA-analyse. Het bleek dat de dominante sintermechanismen voor de deeltjes zonder toegepaste druk, het sintermechanisme bij lage temperatuur voornamelijk oppervlaktediffusie was. Wanneer echter het drukkeffect van het bovenste substraat op de deeltjes werd ingevoerd, verandert het dominante sintermechanisme van de deeltjes in plastische stroming, veroorzaakt door dislocatieproductie en beweging in de deeltjes. Bovendien kwam de spontane rotatie van de deeltjes voor tijdens de coalescentie om de slechte afstemming tussen de deeltjesroosters te elimineren. Ondertussen kwam het passieve rotatiegedrag van de L3-deeltjes ook voor door het pinning-effect van het substraat. Bovendien veroorzaakte het pinning-effect van het substraat ook reusachtige poriën tussen de deeltjes en het substraat. Sommige van deze poriën kunnen worden gevuld via zowel plastische vervorming als oppervlaktediffusie van atomen voor de kleinere deeltjes. Om het grootte-effect op de sinterkinetiek te onderzoeken, werden ten slotte de atoombeweging en de microstructuurevolutie van modellen van 3 nm, 4 nm en 5 nm vergeleken. Het bleek dat de modellen van kleinere deeltjes doorgaans hogere krimpverhoudingen, grotere sinterhalzen en kleinere poriën bevatten. Bij kleinere deeltjes werd een sterkere atomaire beweging en drastischer kristalstructuurovergangen in elk stadium gevonden.

In het volgende hoofdstuk werd een zelfontwikkelde Cu-pasta gefabriceerd met vooraf gedefinieerde bedrukking, droging en sintering. Er werd vooraf een reductieve voorbe-

handeling uitgevoerd op de ruwe Cu-deeltjes om de oorspronkelijke oxidatie te verwijderen. Vervolgens werden laserflitsmetingen en metingen met vier sondes uitgevoerd op het Cu-gesinterde monster, bereid door verschillende temperaturen, druk en tijd, om de impact van de parameters van het sinterproces op thermische en elektrische eigenschappen te evalueren. Er werd vastgesteld dat met slechts 1 minuut sinterproces de thermische (5,82 W/m·K) en elektrische geleidbaarheid ( $0,003/(\mu\Omega\cdot\text{cm})$ ) van het monster extreem klein is en niet kan voldoen aan de eisen aan de verpakking van halfgeleiders. Door de sintertijd tot 4 minuten te verlengen, kunnen de geleidbaarheidskenmerken effectief worden verbeterd tot 231,15 W/m·K en  $0,255/(\mu\Omega\cdot\text{cm})$ . Er is een vergelijkbare trend voor het effect van temperatuur. Van 210°C tot 270°C zijn beide eigenschappen verbeterd van 126,53 W/m·K met  $0,124/(\mu\Omega\cdot\text{cm})$  tot 272,87 W/m·K met  $0,282/(\mu\Omega\cdot\text{cm})$ . Onder hen is het effect van druk echter minimaal. Om vervolgens de impact van de Cu-sinterprocesparameters op de verbindingsprestaties en microstructuurevololutie van de matrijs-attach-monsters te evalueren, werd de afschuiftest uitgevoerd met verschillende sintertemperaturen, druk en tijd. Er werd ook gevonden dat een sintertemperatuur tussen 210°C en 230°C, of een geassisteerde druk van minder dan 10 MPa, een hechtsterkte van ongeveer 30 MPa kon verschaffen. Een dergelijke lage sterkte is te wijten aan zowel het gedeeltelijk uitgebrande organische materiaal als het onvolledige sinteren van Cu-deeltjes. Door de druk te verhogen tot 20 MPa en 30 MPa, vertoont het de verbeterde afschuifsterkte van de matrijs van 100,1 MPa en 116 MPa, bereikt met een sintertemperatuur van 250°C gedurende 3 minuten. Wanneer de temperatuur werd verhoogd tot 270°C, werd de afschuifsterkte extreem verbeterd tot meer dan 120 MPa. Bovendien kan tijd de microstructuur en hechtsterkte in minder dan 4 minuten onbeduidend beïnvloeden. Microstructurele materiaalkarakterisering toont aan dat een hoge hechting het gevolg is van het positieve effect van druk en temperatuur op het bevorderen van de insnoeringsgroei, de vorming van sinternetwerken, poriënisolatie en bros-ductiele breukovergang. Gezien het kleine verbeteringseffect door verdere verhoging van temperatuur en druk, wordt het procesrecept van 250°C/3 min/20 MPa goed aanbevolen voor de toepassing.

Vervolgens worden de belangrijkste mechanische eigenschappen zoals indrukking-hardheid, elasticiteitsmodulus en kruipsnelheid van Cu gesinterde monsters afzonderlijk geëvalueerd om de haalbaarheid van deze techniek voor toepassing in matrijsbevestigingsprocessen te verifiëren. Eerst werd het effect van de piekbelasting (van 10 mN tot 150 mN) en de belastingssnelheid (van 0,1 mN/s tot 1,5 mN/s) op de indrukkinghardheid en de elasticiteitsmodulus onderzocht. De geteste verplaatsing-belastingskrommen werden gebruikt om de elastisch-plastische eigenschappen te analyseren en deze belangrijke mechanische parameters te berekenen. De ISE blijkt duidelijk wanneer de indrukkingdiepte minder dan 500 nm is en de overeenkomstige piekbelasting minder dan 10 mN bedraagt. Maar na 70 mN piekbelasting (1500 nm maximale diepte) is de veranderende trend niet meer duidelijk. De belastingssnelheid heeft een vergelijkbaar effect op deze parameters. Naarmate deze toeneemt van 0,1 mN/s tot 0,9 mN/s, nemen zowel de indrukkinghardheid als de elasticiteitsmodulus geleidelijk toe. Maar vanaf 0,9 mN/s beginnen de twee eigenschappen stabiel te worden rond  $1,59 \pm 0,154$  GPa en  $99,5 \pm 0,86$  GPa. De mogelijke oorzaken zijn voornamelijk het uithardingseffect, poriënverdichting en stapelverschijnselen tijdens de indrukkingstest. Om stabiele experimentele

resultaten te verkrijgen zijn daarom een indrukdiepte van meer dan 1500 nm en een belastingssnelheid van meer dan 0,9 mN/s noodzakelijk. Door gebruik te maken van de stabiele testparameters werden de constitutieve modellen (vloeispanning, de exponent van de deformatieharding) voor monsters die onder verschillende toegepaste druk werden gesinterd, verkregen, die kunnen worden gebruikt om de mechanische eigenschappen bij kamertemperatuur van de Cu-sinterverbinding te beschrijven. Vervolgens werden de effecten van de temperatuur van 150 tot 240°C op de indrukkinghardheid en de elasticiteitsmodulus onderzocht. De temperatuurafhankelijkheid van beide parameters werd aangepast om dit effect te verklaren. Bovendien werd het kruipgedrag, inclusief de kruipreksnelheid in stationaire toestand, bestudeerd en vergeleken voor monsters die werden gesinterd met verschillende toegepaste drukken. Hogere temperaturen bleken te resulteren in ernstigere kruipvervormingen. Een hogere sinterdruk kan echter de kruipweerstand tegen plastische vervorming effectief verbeteren. Het toenemende effect is echter marginaal boven 20 MPa, hetgeen een aanwijzing is voor de praktische keuze van de sinterprocesparameters.

Tenslotte werd een drukgesteund Cu-sinterproces (250°C/3 min/20 MPa) toegepast om die-attach-eenheden en verscheidene SiC-vermogensmodules te bereiden. Voor de vermogensmodule werd het verpakkingsproces uitgevoerd op een industriële standaard verpakkingslijn. De afschuifsterkte,  $R_{DSon}$  en de betrouwbaarheid van de thermische weerstand werden onderzocht aan de hand van een opslagtest bij hoge temperatuur van 150°C/1000 uur en een thermische cyclustest bij -40°C~150°C /1000 cycli. Dan, werden de statische en dynamische tests van Cu-gesinterde SiC module uitgevoerd. Als benchmark, werd een zelfde SiC module die door Ag-sintering proces werd die-vastgemaakt parallel geplaatst. De experimentele resultaten gaven aan dat zowel de uitgangskenmerken als de schakelprestaties van de Cu-sintered SiC module op hetzelfde niveau liggen als de Ag-sintered module en overeenkomen met de standaard commerciële module. Gezien de uitgebreide kosten-prestatie balans, de gepresenteerde Cu sinteren technologie is veelbelovend voor WBG vermogenselektronica verpakking toepassing. Aan het einde van het proefschrift worden de belangrijkste conclusies en bijdragen samengevat, en de vooruitzichten voor toekomstig werk op dit gebied worden voorgesteld.

# LIST OF ABBREVIATIONS

|           |                                                               |

|-----------|---------------------------------------------------------------|

| $\alpha$  | Thermal diffusion coefficient                                 |

| $A_C$     | Project area of the contact surface, for hardness measurement |

| $a_{fcc}$ | Lattice constant of the FCC (face-centered cubic)             |

| AMB       | Active metal brazing                                          |

| $B$       | Temperature sensitivity factor of hardness                    |

| C         | Indentation curvature                                         |

| CNA       | Common Neighbor Analysis                                      |

| $c_p$     | Specific heat capacity                                        |

| CTE       | Coefficient of thermal expansion                              |

| D         | Sample diameter, for resistivity measurement                  |

| DA        | Die-attachment                                                |

| DBC       | Direct bonded copper                                          |

| DPT       | Double pulse test                                             |

| DSC       | Differential scanning calorimetry                             |

| DUT       | Device under testing                                          |

| DXA       | Dislocation Extraction Algorithm                              |

| $e$       | Temperature sensitivity factor of elastic modulus             |

| E         | Elastic modulus                                               |

| EAM       | Embedded atom method                                          |

---

|             |                                                                     |

|-------------|---------------------------------------------------------------------|

| EDS         | Energy disperse spectroscopy                                        |

| $E_i$       | Elastic modulus for the Berkovich indenter, 1140 GPa                |

| EG          | Ethylene glycol                                                     |

| $E_{off}$   | Turn-OFF loss                                                       |

| $E_{on}$    | Turn-ON loss                                                        |

| $E_r$       | Reduced elastic modulus                                             |

| ETM         | Electrical test method                                              |

| FCC         | Face-centered cubic                                                 |

| $F_{(D/S)}$ | Sample diameter correction factor                                   |

| $F_{(W/S)}$ | Sample thickness correction factor                                  |

| $F_{max}$   | Peak load in the nanoindentation test                               |

| FT-IR       | Fourier transformed infrared                                        |

| GaN         | Gallium nitride                                                     |

| $H$         | Specimen thickness, for calculation                                 |

| $H$         | Indentation hardness                                                |

| HCP         | Hexagonal close-packed                                              |

| $h_c$       | Contact depth, for the indentation hardness measurement             |

| $h_{max}$   | Maximum indentation depth, for the indentation hardness measurement |

| $h_r$       | Residual depth, for the indentation hardness measurement            |

| HTP         | High melting-temperature phase                                      |

| HTS         | High temperature storage                                            |

| IGBT        | Insulated Gate Bipolar Transistor                                   |

| $I_H$       | Heating current                                                     |

| $I_M$       | Measurement current                                                 |

---

|              |                                                                           |

|--------------|---------------------------------------------------------------------------|

| $\lambda$    | Thermal conductivity                                                      |

| K factor     | Temperature sensitivity parameter, TSP                                    |

| LTP          | Low melting-temperature phase                                             |

| IMC          | Intermetallic compounds                                                   |

| LAMMPS       | Large-scale Atomic Molecular Massively Parallel Simulator                 |

| MD           | Molecular dynamics                                                        |

| MOSFET       | Metal-Oxide-Semiconductor Field-Effect Transistor                         |

| MSD          | Mean-squared displacement, $\langle d^2 \rangle$                          |

| N            | Number of atoms                                                           |

| $Nv$         | Number of vacancies                                                       |

| $\nu$        | Poisson ratio                                                             |

| $\nu_i$      | Poisson ratio for the Berkovich indenter, 0.07                            |

| n            | Work hardening coefficient                                                |

| NPs          | Nanoparticles                                                             |

| OFC          | Oxide-free copper                                                         |

| OM           | Optical microscope                                                        |

| $\rho$       | Density of the sample, g/cm <sup>3</sup> , for $\lambda$ measurement      |

| $\rho_0$     | Density of the liquid, g/cm <sup>3</sup> , for $\lambda$ measurement      |

| $\rho_{air}$ | Density of the air (0.0012 g/cm <sup>3</sup> ), for $\lambda$ measurement |

| PC           | Power cycling                                                             |

| PVD          | Physical vapor deposition                                                 |

| Q            | Activation energy required for vacancy generation                         |

| QNPs         | Quasi-nanoparticles                                                       |

| $r_{com}$    | Centroid coordinates of the particle                                      |

---

|                 |                                                                    |

|-----------------|--------------------------------------------------------------------|

| $r_{cut}$       | Cutoff radius                                                      |

| R               | Resistivity                                                        |

| R               | Universal gas constant                                             |

| $R_{DSon}$      | Drain-source on-state resistance                                   |

| $R_{th}$        | Thermal resistance                                                 |

| $R_{th(jc)}$    | Junction-to-case thermal resistance                                |

| <b>S</b>        | Probe spacing, for resistivity measurement                         |

| <b>S</b>        | Stiffness of the contact, the initial slope of the unloading curve |

| SAC             | Sn-Ag-Cu                                                           |

| SEM             | Scanning electron microscope                                       |

| SF              | Stacking fault                                                     |

| Si              | Silicon                                                            |

| SiC             | Silicon carbide                                                    |

| $\sigma$        | Shear strength                                                     |

| $\sigma$        | Stress                                                             |

| $\sigma_y$      | Yield strength                                                     |

| $\sigma_{0.29}$ | Characteristic stress when strain is 0.29                          |

| SLID            | Solid-liquid interdiffusion                                        |

| T               | Temperature                                                        |

| TCT             | Thermal cycling test                                               |

| TEM             | Transmission electron microscope                                   |

| TGA             | Thermogravimetric analysis                                         |

| TIM             | Thermal interface material                                         |

| $T_j$           | Junction temperature                                               |

|                   |                                                                                   |

|-------------------|-----------------------------------------------------------------------------------|

| TLPB              | Transient liquid phase bonding                                                    |

| TLPS              | Transient liquid phase sintering                                                  |

| $T_{melting}$     | Melting temperature                                                               |

| $T_{process}$     | Process temperature                                                               |

| TS                | Thermal shock                                                                     |

| TSP               | Temperature sensitivity parameter, K factor                                       |

| $t_0$             | Initial time                                                                      |

| $t_{1/2}$         | The time required for the backside temperature to reach half of the maximum value |

| $V_{DS}$          | Drain-source voltage                                                              |

| $V_{GS}$          | Gate-source voltage                                                               |

| $V_{GS(th)}$      | Threshold voltage                                                                 |

| W                 | Sample thickness, for resistivity measurement                                     |

| WB                | Wire bonding                                                                      |

| WBG               | Wide bandgap                                                                      |

| XRD               | X-ray diffraction                                                                 |

| XPS               | X-ray photoelectron spectroscopy                                                  |

| Y                 | Strength coefficient                                                              |

| $\epsilon$        | Total strain                                                                      |

| $\epsilon_p$      | Actual plastic strain                                                             |

| $\epsilon_y$      | Yield strain                                                                      |

| $\epsilon_{0.29}$ | Characteristic strain                                                             |

| $Z_{th}$          | Transient thermal resistance                                                      |

| $\zeta_x$         | Shrinkage ratio                                                                   |

# 1

## INTRODUCTION

**I**N recent centuries, excessive emission of greenhouse gases has been causing long-term, severe and pervasive influence on human beings and ecosystems [1]. It has been realized that shifting to a low-carbon economy on a global scale is necessary for sustainable development for each country[2]. Over the decades, the share of electricity in the world's final energy consumption has steadily risen with the development of electrification applications such as electric cars, high-speed rail, smart grids and photovoltaics. By 2040, Electrical energy is estimated to account for more than 40% of the rise in final energy consumption[3]. Therefore, improving the efficiency of electrical energy utilization and conversion is key in the economic transformation process. In this context, power electronics technology is becoming increasingly relevant. A power electronics device is a greatly integrated solid-state semiconductor electronics being employed to control and converse the high-power electric power to the demanding form for end user [4]. Thanks to the outstanding properties of wide bandgap (WBG) semiconductors, the performance and efficiency of power devices could be further expanded when the conventional Si-based device reaches its physical limits.

## 1.1. MERITS OF SiC MATERIAL AND DEVICE

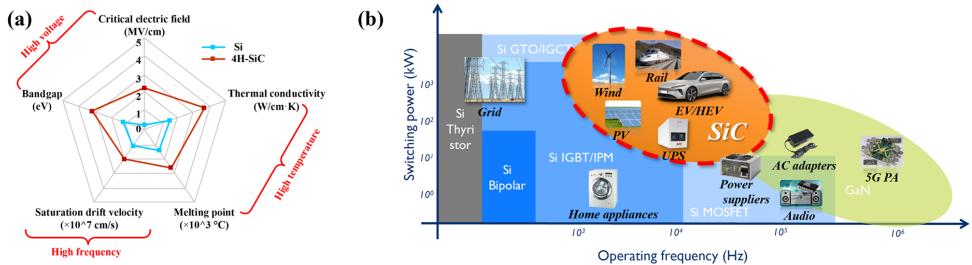

**A**s one of the most representative WBG semiconductor materials, silicon carbide (SiC) has larger band gap, higher critical electric field and higher thermal conductivity compared with silicon (Si)[5]. As shown in Fig.1.1a and b, these properties are particularly vital for allowing power devices to operate at considerably high-power levels and high-temperature conditions with high-efficiency [6]–[8]. Additionally, it can also help to reduce the size of the power module, which enables a more lightweight and low-cost system.

Figure 1.1: (a) Key properties comparison between Si and 4H SiC materials.[5] (b) Typical applications of different power devices. The highlighted region is where SiC power devices show advantages.[9]

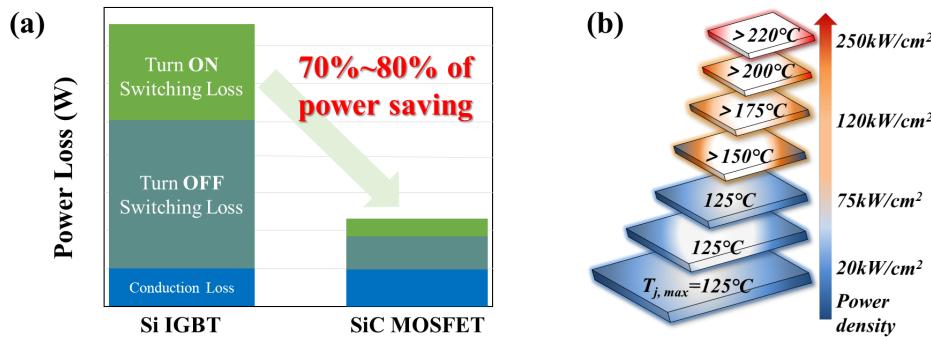

In the past, to lower down the driving current and output impedance for the device, the bipolar device Insulated Gate Bipolar Transistor (IGBT) was invented [10]. However, due to the bipolar characteristics, the switching loss during turning on ( $E_{on}$ ) and turning off ( $E_{off}$ ) is elevated at high switching speed. In contrast with IGBT modules, SiC Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) module can dramatically reduce the total loss by 70% due to its low-loss characteristics [11]–[13], as shown in Fig.1.2a. Such benefit is more pronounced at high temperatures [14], [15]. As a result, SiC MOSFET is more appropriate for medium and high voltage and frequency applica-

tions in high-temperature scenarios than Si.

Figure 1.2: (a) Performance advantages of SiC MOSFETs compared with IGBTs at high-speed switching conditions. (b) The schematic diagram for the evolution of chip size, junction temperature and power density for power electronics. [16]

However, as shown in Fig.1.2b, along with the excellent properties of SiC devices comes a reduction in chip size, an increase in power density, and an increase in junction temperature when replacing Si-based devices [17]. This will result in a greater challenge to the reliability of the entire module. Therefore, it is crucial to improve the current carrying and heat dissipation capabilities of the module to ensure superior performance of the SiC devices. This can be achieved through the innovation of packaging materials and technologies.

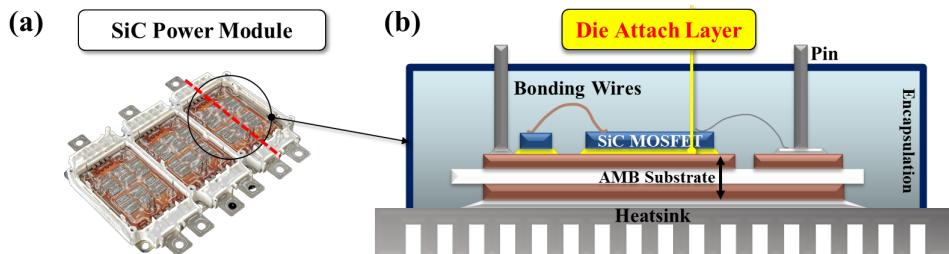

Figure 1.3: (a) A typical power module and (b) the schematic diagrams of the packaging internal structure.

Fig.1.3 shows a photo of a typical power module and a schematic of its internal structure. The materials and techniques used in these components are as follows:

- First, for mechanical supporting, heat dissipation and electricity carrying, the power die are attached onto the power substrate by a die-attachment (DA) layer, as highlighted in Fig.1.3b. Typical techniques applied in this region include reflow soldering, transient liquid phase bonding and sintering depending on the performance and cost requirement.

- The power substrate is a metal-ceramic substrate between the power chip and the heatsink (or sometimes baseplate) for realizing electrical insulation and heat dis-

sipation along the vertical direction. Normally, when considering the cost, the alumina Direct-Bonded-Copper (DBC) substrate is applied, whereas for better thermal conductivity and reliability, silicon nitride Active-Metal-Brazing (AMB) substrate with a thicker copper plate are adopted by the industry recently.

- Then, different power die are interconnected through wire bonds. In general, aluminum wires are used here. For higher reliability, copper wire bonding or clip bonding has also been proposed in recent years.

- Finally, the die-attached substrate is protected by a plastic housing case and encapsulated by silicon gel. There is a heatsink under the module for heat dissipation.

Among all package structures, the DA material is the first layer directly connected to the power chip and hence, it is one of the most critical components that directly affect the performance of the power module. Also, since the power module has to operate under high temperature and power fluctuation conditions, the DA layer will not only transmit a huge amount of heat and electrical signals, but also undergo large thermal stress brought by the power chip and the substrate. Therefore, an in-depth study of DA materials and processes is necessary for both the industry and the academy. In the next section, four of the most commonly used die attachment techniques are reviewed and compared.

## 1.2. DIE ATTACHMENT TECHNOLOGIES FOR POWER ELECTRONICS PACKAGING APPLICATION

### 1.2.1. REFLOW SOLDERING

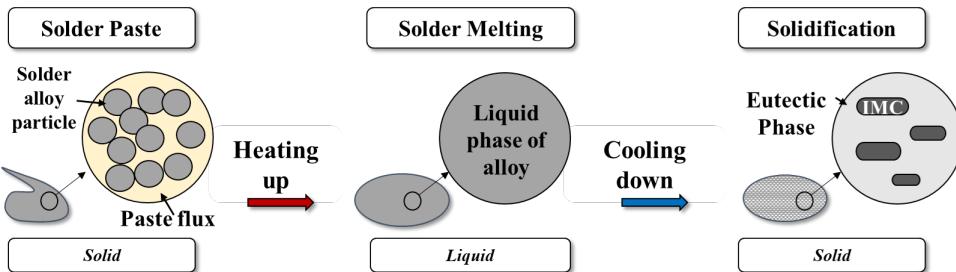

REFLOW soldering is the most widely used method for attaching power devices to substrates. During this process, the soldering paste undergoes melting, flow, and solidification to form metallurgical interconnects with the parts to be connected, as shown in Fig.1.4. The key ingredient for soldering paste is a metallic powder, which can contain different eutectic compositions and thus determine the solidus temperature. High-lead solders (Pb content >85 wt%, for example, 95Pb-5Sn) have been widely used for DA applications for decades due to their reasonably good thermal, electrical and mechanical performance. By the end of the last century, however, the toxicity of lead solder to humans and the environment was realized and investigated. Then from 2000 onwards, the application of lead-based soldering materials was scheduled to be gradually restricted, and lead-free solder alloys became popular as an alternative to electronic packaging.

Various lead-free solder alloys have been developed for different applications. Examples are the Sn-Bi eutectic alloy (139°C), the Sn-Ag eutectic alloy (221°C), and the Sn-Cu eutectic alloy (227°C). The most widely used one is Sn-Ag-Cu (SAC) alloy, which can provide outstanding performance (~60 W/mK) with a low-cost [18]. However, the relatively low remelting temperature limits its application for SiC power module which always operates at a temperature above 175°C, or even 200°C [19].

Au-Sn soldering alloys have higher reflowing temperatures which have been seen as the primary choice of DA materials for high-power LED applications [20]. However, the cost-benefit ratio is questionable given the high cost of eutectic Au-Sn soldering ma-

terials. In addition, for all reflow soldering materials, there are always stiff interfacial intermetallic compounds (IMCs). Such high brittleness phase precipitation can lead to inevitable reliability problems [21]. Therefore, in some cases, Ni, Pd, or Pt may be needed as diffusion barriers for preventing the formation of IMCs. Furthermore, Kirkendall voids may also form after the reaction between the liquefied solder and metalization surface, which would reduce the effective bonding area at the interface [22].

Figure 1.4: The schematic illustration of the reflow soldering process in a microscopic view.

### 1.2.2. TRANSIENT LIQUID PHASE METHOD

WHEN traditional solder alloys cannot meet the high-temperature reliability requirements for the WBG semiconductors, transient liquid phase bonding (TLPB) has been developed because of its "low processing temperature and high operating temperature" performance. The terms "transient liquid phase sintering" (TLPS), "liquid phase diffusion bonding" (LPDB), and "solid-liquid interdiffusion" (SLID) are also being applied to describe this method [23]. In this method, a low-melting temperature phase (LTP), such as Sn, and high-melting temperature phases (HTP) such as Cu, are utilized to form the metallurgical bonding. At temperatures above the liquidus line of the LTP, the melted LTP will diffuse into the solid state HTP and wet the particle surface to be joined. Along with the isothermal solidification, some IMC is formed in the joint to provide robust connection [24].

Figure 1.5: The schematic diagram of TLPB process.

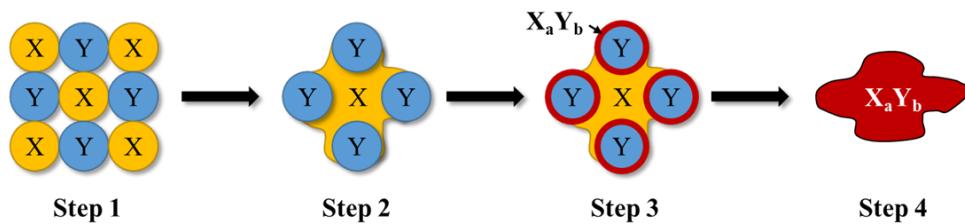

As shown in the Fig.1.5, the TLP method can be divided into four steps in general: heating, melting, interdiffusion and IMC formation [25]:

- In Step 1, the organics in the TLP paste are evaporated first. At the same time, the LTP (particles X) and HTP (particles Y) will approach each other with the temperature ramping up and solid-to-solid interdiffusion starts to occur.

- In Step 2, a liquid phase of X is formed when the temperature is above the melting temperature of X. The formation of the liquid phase is crucial at this point, as it will wet the surface of particle Y, accelerating mass transportation.

- Next in Step 3, the interdiffusion from the solid phase Y to the liquid phase X will occur. For better-joining performance, an auxiliary pressure and vacuum can be applied to guarantee the dense contact and promote interdiffusion of X and Y.

- Finally, at a certain point, when sufficient Y is diffused into X, IMC  $X_a Y_b$  in the joint will form via an isothermal solidification process. The newly formed  $X_a Y_b$  will provide robust bonding to the joint and contain a higher melting temperature than X.

As an example, the Cu-Sn binary system is a classical TLPB system. In this system, the LTP is Sn with a melting temperature of 232°C. After TLPB process, the remelting temperature of as-formed IMC  $Cu_6Sn_5$  is increased up to 415°C[26]. However, the TLPB technique suffers from various non-negligible problems that limit its wide range of applications [27]. The as-formed IMC  $Cu_6Sn_5$  is a brittle phase which will deteriorate the mechanical strength and reliability of the joint. Second, since TLPB is a reaction-based process, it is necessary to maintain accurate stoichiometry as well as long-lasting reaction times. This will increase the control difficulty of the process. In addition, pore formation and incomplete wetting of the LTP also occur from time to time, which may decrease the electrical and thermal conductivity.

### 1.2.3. SINGLE-METAL SINTERING

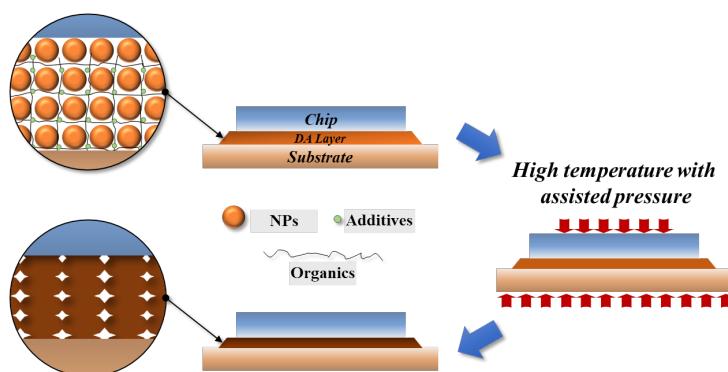

Figure 1.6: A schematic diagram of single metal sintering process.

As introduced in the previous section, WBG semiconductor devices have been extensively developed over the past decades and are gradually replacing Si-based devices in most high switching frequency, high power density and high temperature applications. However, the use of conventional lead-free solutions such as reflow soldering and

TLPB for WBG die attachment is limited due to their low melting point, low creep resistance, low thermal and electrical conductivity, and IMC precipitate problems [28]. To overcome these issues, low-temperature sintering techniques have been proposed and developed over the past two decades [29]–[33]. Here is a schematic diagram of the pressure-assisted sintering technique as shown in Fig.1.6.

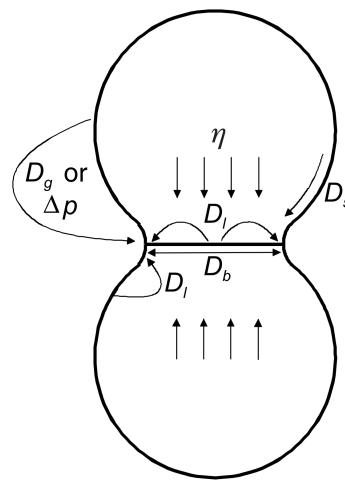

Generally speaking, sintering is the process of compacting and forming a powdery material into a solid bulk material by heat and pressure at temperatures well below the point of liquefaction [34]. After the formation and densification of the sintered body, it will obtain the excellent physical properties (melting temperature, thermal conductivity, mechanical strength) that is close to its corresponding bulk material. Therefore, sintering is also a technology with "low processing temperature and high operating temperature" advantage. The driving force for sintering is the reduction of the surface area and decreasing of the surface free energy during the densification process. On a microscopic scale, such process occurs through atomic transportation (mass transportation) at the contact area of particles [35], such as surface, grain boundary, and lattice diffusion. A schematic diagram of the material transport during the sintering process is illustrated in Fig.1.7.

Figure 1.7: A schematic diagram of the material transport during the sintering process.[35]

Silver and copper have excellent electrical and thermal conductivity and high melting points (960°C and 1083°C, respectively) and are very suitable materials for sintering technology in power semiconductor packaging [36], [37]. Nano-silver sintering has emerged as a promising technique to form the die-attach joint for power devices. However, there are two significant limitations of sintered Ag joint, namely high material costs [38] and electrochemical migration [39]. Recently, nano copper sintering is receiving great attentions because of its much lower material cost (about 1~10% of the Ag price), lower ion migration tendency, as well as sufficiently high thermal conductivity (398 W/mK for bulk material) [40]–[44]. The material properties can be easily found from the Table 1.1 below.

Table 1.1: Material properties of different die-attach techniques.

|                         | SAC        | $Au_{80}Sn_{20}$ | TLP Cu-Sn        | Ag Sintering | Cu Sintering |

|-------------------------|------------|------------------|------------------|--------------|--------------|

| $T_{process}$ (°C)      | 217–221    | 308 (278+30)     | 280, 30 min      | 250          | 250          |

| $T_{melting}$ (°C)      | 217        | 278              | 415              | 960          | 1084         |

| CTE ( $10^{-6}K^{-1}$ ) | 20         | 16               | /                | 18–23        | 16–21        |

| $\sigma$ * (MPa)        | ~45        | 65~130           | 20~40            | 20~80        | 20~80        |

| $\lambda$ ** (W/(mK))   | 60         | 57               | 34~70            | >100         | >100         |

| Cost                    | Lowest     | Highest          | Midium           | High         | Low          |

| Ref.                    | [18], [19] | [20], [45], [46] | [23], [47], [48] | [29]–[33]    | [40]–[44]    |

\*: shear strength

\*\*: thermal conductivity

### 1.3. COPPER SINTERING TECHNIQUE

**I**N this section, a comprehensive review of related studies on Cu sintering techniques is given. Firstly, the state-of-art Cu particles pretreatment methods are reviewed. Then typical sintering paste formulations and the important studies of Cu sintering process and sintering mechanisms are summarized. Finally, a brief review for MD simulation of the Cu NPs coalescence is given. For each topic, questions and challenges are summarized as well.

#### 1.3.1. MATERIAL TREATMENT

**D**IFFERENT synthesis methods of Cu particles were proposed to obtain small-size NPs with low-temperature sintering ability. Most of them were based on the modified polyol method applying different precursor and reducing agent. However, the biggest challenges that nano copper material encountered for the industrial application are the high oxidation risk, strong agglomeration tendency, and complex sintering process[49], [50]. Different approaches have been attempted to address these issues. First of all, the most effective way to avoid copper oxidation and to guarantee the good bonding performance was by injecting reducing atmosphere with specific concentration during sintering [51], [52]. The similar scheme also included by setting an intentional oxidation-reduction process of copper NPs during the sintering process [49], [53]–[55]. However, from an industrial/practical application point of view, the reduction gas and oxidation-reduction reactions may increase the cost as well as the complexity of the process.

For this reason, a protective treatment for Cu nano particles (NPs) in advance combined with applying of inert atmosphere during sintering can be a better way [56]. First of all, some groups have attempted to incorporate an in-situ coating process in addition to the copper particles producing process. These synthesis methods were also based on the modified polyol method with specific reducing agent, such as hydrazine [57], [58],

citric acid[57], PVP[59], [60], L-ascorbic acid[61], [62], formic acid[63].

Other groups preferred to develop the post-treatment process after the production of copper particles, in order to reduce the difficulties on the precise control of both the NPs preparation and the coating treatment at the same time. Gao et al.[64] used ascorbic acid to treat the as-produced NPs. After the treatment, the NPs obtained the self-reductive ability. Then by sintering at 250°C for 30 min with 0.4 MPa the joint showed over 15 MPa bonding strength. Zhao et al.[65] synthesized 30 nm mono-dispersed copper NPs and then did treatment process on the particles. The joint could have 17 MPa shear strength after sintering at 240°C. Mou et al.[56] reported that they used carboxylic acid (formic acid and oxalic acid) to modify the surface of Cu NPs(150~200 nm) and obtained over 20 MPa bonding performance by sintering at 250°C for 60 min in Ar-H<sub>2</sub> (5%H<sub>2</sub>) with 10 MPa assisted pressure.

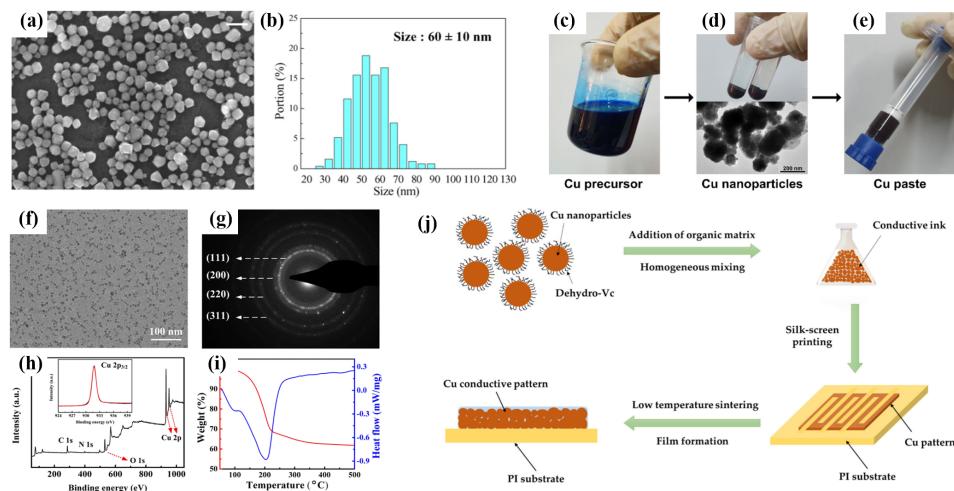

Figure 1.8: (a) The SEM photo and (b) the size distribution plot of the synthesized Cu NPs by using the modified polyol method in[66]. (c) to (e) The preparation process from Cu precursor to Cu NPs then to Cu paste[67]. (f) to (i) The SEM photo, TEM diffraction photo, XPS and DSC/TG results of the Cu NPs[68]. (j) The Cu NPs treatment and the corresponding sintering process[69].

It has also been found that the reduction of Ag and Cu particle size could effectively lower the sintering temperature to obtain the desired sintered joint[65], [70], [71]. However, smaller particle size can also increase the risk of particle spontaneous oxidation and agglomeration [72]. In our previous research[73], [74], it was found that, via proper particle treatment and sintering process, the particle with around 100 nm of size could already be sintered well. Therefore, applying Cu quasi-nanoparticles (QNPs, average diameter is between 100 nm and 200 nm) could be another option[56], [75], [76]. From the above discussion, the specific particle size, material treatment methods, and sintering conditions need to be comprehensively designed based on the sintering performance requirements.

### 1.3.2. PASTE FORMULATION AND SINTERING PROCESS

After the preparation of metallic particles, the organic components will be added and blended to form a viscous slurry that has specific viscosity, workability and preservation properties. The selection and the amount of organic components are crucial to modulate the performance of the paste. Normally, very small amounts of different functional additives can be added into the organic solvents to form the so-called vehicle, as shown in Fig.1.8j and Fig.1.9a. A common vehicle contains resins, solvents, thickeners and acid reductants. The resin mainly controls the rheology of the paste and greatly affects the printing performance. The solvent controls the evaporation of the vehicle and facilitates interparticle contact during printing and sintering. The thickener improves the rheological properties of the paste; and the acid reductant promotes sintering by reducing the oxides during the heating process. In the recent study[77], more than 50 different formulations were optimized: fluxes containing methyl ethyl ketone, isopropyl alcohol, methyl pyrrolidone, butyl fibrinolyte, pine alcohol, Tektros D85, Troy rheology additive, and malonic acid performed best. The prepared nanoparticles are then added to the as-prepared vehicle by stirring, three-roll milling and ultrasonic oscillation to formulate a homogeneous mixed copper paste.

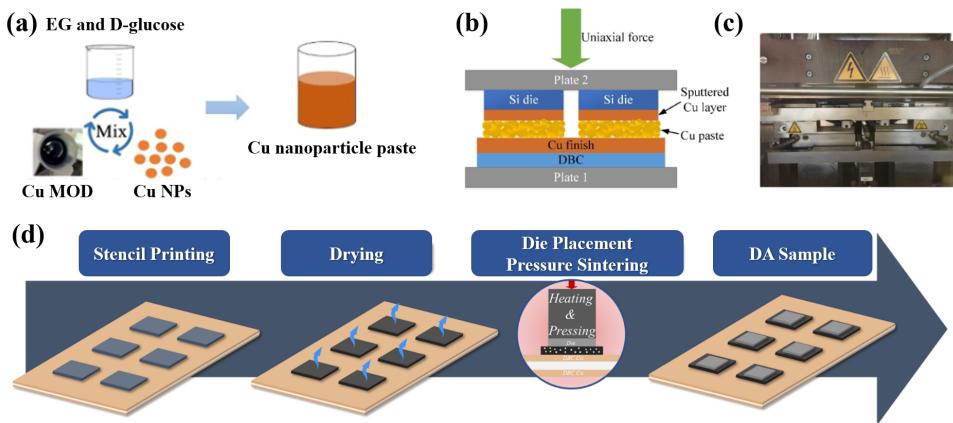

Figure 1.9: (a) The printing, drying and die-attach process flow[78]. (b) A schematic diagram and (c) a real sintering tool of the pressure-assisted sintering process[79]. (d) Schematic illustration of typical pressure-assisted sintering process.

Normally, the stencil printing process will be used to apply the paste. The substrate is loaded under the stencil, and a squeegee is used to move the paste on the stencil surface. Then the paste will be deposited through the stencil mask to form the designed pattern on the substrate. The paste volume is a function of the stencil, the printing process and equipment, paste properties. Next, the as-printed substrate needs to be delivered to a vacuum oven for a drying process, in which the organic solvent will be evaporated, as shown in Fig.1.9d. Then, the chip will be accurately placed on the as-dried pattern pad by the so-called pick & place process. Finally, the sample is sent into a nitrogen oven or a heat press sintering oven to conduct sintering process. To improve the performance and reliability of sintered joints, the pressure-assisted sintering method is developed in

the industry [80], [81]. By applying moderate external pressure to the die-attached samples, not only the metallic particles will be pushed together for better atomic diffusion, but also the porosity of the die-attach layer is reduced. Moreover, thanks to the development of advanced pressure-assisted sintering machine (or so-called sintering press) in the past few years, it is possible to provide precise pressure control to multiple samples simultaneously, as shown in Fig.1.9b and c. Therefore, fast sintering process (less than 5 min per batch) is achieved in the industry. As a result, copper materials will not be exposed to oxygen for too long, which considerably reduces the risk of oxidation during sintering[70], [82].

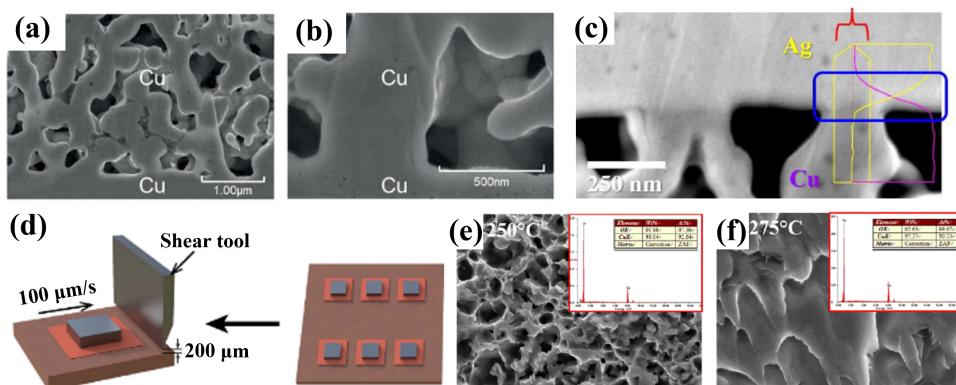

Figure 1.10: (a) and (b) Typical SEM images of the cross-section view of the die-attach region[83]. (c) The EDX analysis on the die-attach interface between the dice and the sintering layer[84]. (d) A schematic of die shear test[67]. (e) and (f) Typical SEM images of the sheared-off fracture surface of the die-attach sample[85].

For the evaluation of material properties, sintered joint performance and packaging device reliability, different methodologies have been applied from macroscopic to nanoscale. First, for material properties characterization, scanning electron microscope (SEM), transmission electron microscope (TEM), X-ray diffraction (XRD), Optical Microscope (OM), X-ray photoelectron spectroscopy (XPS) and Fourier transformed infrared (FTIR) spectroscopy are applied. OM, SEM and TEM are mostly used for observing the microstructural morphology of the NPs at different magnification levels, as shown in Fig.1.10a and b. Besides, energy disperse spectroscopy (EDS) can be further applied to analyze the elemental content at specific positions, as displayed in Fig.1.10c. XRD and XPS are used for checking oxidation condition at different thicknesses of the material. FTIR is used for investigation of the functional groups of organics present in a material system. Moreover, thermogravimetric analysis (TGA) and differential scanning calorimetry (DSC). can be used to study the phase transformation behavior of materials at different temperatures.

Then for sintered joints, the most important evaluation objects include: mechanical strength, failure modes, functional properties and reliability performance. The shear test is the most popular test applied both in the industry and academia for testing bonding strength, see Fig.1.10d. Then the SEM can be applied to observe the fracture surface as well as cross-section of the sintered joint, as displayed in . For functional material prop-

erties, four-point probe tester and laser-flash tester are always used for testing electrical resistivity and thermal conductivity of sintered bulk. Next, in order to test the reliability of the die-attached sample, there are hot temperature storage (HTS) test, thermal cycling test (TCT), thermal shock (TS) test and power cycling (PC) test. Normally the shear strength and thermal resistance are evaluated at the point before and after the reliability test to reveal the material properties degradation and failure modes.

When experimental method is difficult to conduct, the simulation method is also utilized for the fundamental investigation of the NPs coalescence mechanism at atomic-scale. One of the most applied simulation methods is Molecular Dynamics (MD), which can help to analyze the atomic movement and interaction of the material. By numerically solving Newton's equations of motion for the particles system, it allows us to obtain the microstructural evolution, dislocation behavior and diffusion process during the sintering[86]–[90]. Additionally, it can also help to analyze sintering mechanisms at various temperatures, including grain boundary diffusion, matrix diffusion, surface diffusion, plastic deformation mechanism [91]–[93].

## 1.4. CHALLENGES AND RESEARCH OBJECTIVES

THE previous introduction demonstrated that copper sintering technique has many potential advantages over silver sintering, TLPB technique, and reflow soldering regarding the performance, reliability, and cost for SiC power electronics packaging. However, a review of literature reveals that the research on copper sintering is still in its preliminary stages. Few studies and reports did comprehensive research on the raw materials, processes, microstructure evolution, sintering performance, reliability, and application validation. Therefore, it is important to study the copper sintering technique starting from a material point of view, in combination with the sintering process, microstructural mechanisms and packaging applications:

### 1.4.1. FOR ATOMIC-SCALE SINTERING MECHANISM

WHEN considering the sintering behavior of the nano-sized materials, it is a challenge to use experimental methods to study the nano-scale sintering mechanisms. In this context, MD simulation is often used to fundamentally investigate the NPs coalescence mechanism during the sintering process. However, most of the current MD research is based on two-particle or multi-particle models, which focus on neck formation and crystal rearrangement of the free-standing particles. In fact, in a practical semiconductor packaging scenario, nanoparticles need to be sintered between a backside metallization layer of the chip and a metallic surface of the substrate. Thus, the interaction between the NPs and the components around may not be negligible, which may significantly affect processes such as contact of particles, formation of the necks, distribution of stress, and generation of the pores. It was found that the interactions between different components at each sintering stage and the corresponding coalescence kinetics have not been discussed yet. Therefore, more simulation studies including these factors should be conducted in the future.

#### 1.4.2. FOR Cu PARTICLES TREATMENT METHOD AND SINTERING PROCESS EFFECT

THE in-situ treatment methods for Cu particles mentioned in the previous sections rely on the precise control of the additives amount in order to control the particle diameter and to prevent particle from aggregating in organic solvents simultaneously. Therefore, for industrial-scale applications such in-situ treatment method during the Cu NPs generation process is problematic. Correspondingly, creating protective capping after the synthesis of copper nanoparticle can be a more feasible solution. The effect of the post-treatment method on the oxidation removal and sintering performance enhancement need to be proved. Moreover, sintering temperature, pressure, and time are the three dominant factors that determine the sintering properties. In order to guarantee the performance of the sintering at short times, it is first necessary to investigate the effect of the process parameters on the microstructural evolution and bonding mechanism. In the field of Ag sintering, there has been a great deal of research on the effect of the parameters of the sintering process. However, few researchers have reported on the effect of sintering parameters while incorporating microstructural analysis for Cu sintering techniques.

#### 1.4.3. FOR MECHANICAL, THERMAL AND ELECTRICAL PROPERTIES EVALUATION

Mechanical strength, thermal conductivity and electrical resistivity are the three most important functional properties of the Cu-sintered joint, which can reflect the ability of DA layer on device bonding, heat dissipation and electrical signal transmission. In material science, hardness is the resistance to locally plastic deformation, and elastic modulus is the resistance to the elastic deformation. Both of them are important mechanical parameters to evaluate the mechanical properties of DA joints. However, up to now, the mechanical reliability of Cu-sintered DA material at various temperatures has yet to be thoroughly studied in the academy and industry. Apart from that, due to the porous microstructure, the resistivity of the sintered joints is several times higher than that of the corresponding metallic bulk material. Optimizing the sintering parameters to obtain lower resistivity is a viable way to improve the applicability of Cu sintering techniques. However, few researchers have reported on the effect of sintering parameters on these properties while incorporating microstructural analysis. Therefore, a comprehensive study of the mechanical strength, resistivity, and thermal conductivity of the microstructure of sintered samples with different process parameters is significantly necessary.

#### 1.4.4. FOR DIE-ATTACHMENT APPLICATION OF SiC DEVICES

NANO-silver sintering technology is relatively mature and has been applied to large-scale products. Considering the importance of efficiency-performance balance in industrial production, the use of inert-atmospheric conditions and pressure-assisted sintering can be a reasonable solution. In contrast, copper sintering technology research is still in the laboratory stage and there are very few demonstrations of nano Cu-sintering technology in functional packaging modules. In practical applications, in addition to the performance of the die-attachment material itself, it is also necessary to consider

the adaptability of the packaging material to the packaging process, the switching performance, the thermal performance and the reliability of the power module after the packaging process. Therefore, a systematic study of Cu-sintering techniques in combination with materials, process, simulation, and testing is of great importance to boost the application of such techniques to industrial applications.

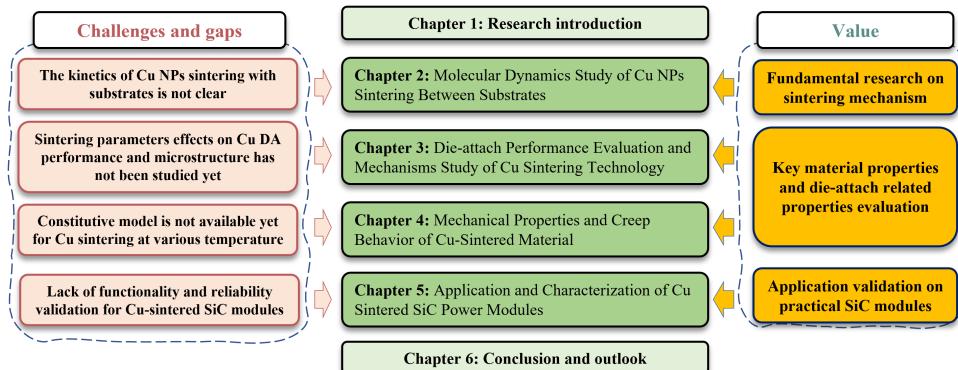

## 1.5. THESIS OUTLINE

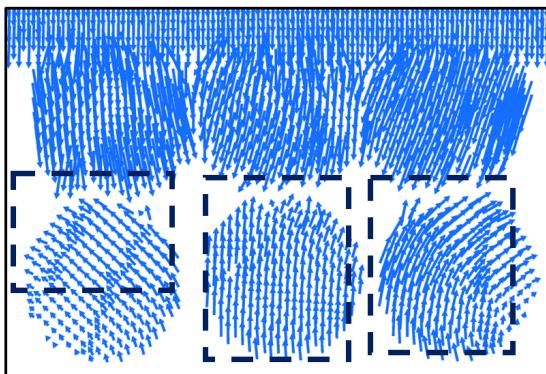

**T**HIS dissertation is divided into six chapters, as shown in Fig.1.11. In Chapter 2, a MD simulation was carried out to study the coalescence kinetics and microstructure evolution of Cu nanoparticles sintering at various temperatures. A sandwich structure model with two substrates and multiple particles in between was constructed to simulate the practical die-attach structure. The size effect of nanoparticles and pressure effect of the substrate at 500K low-temperature sintering process of this structure was thoroughly studied. Furthermore, the microstructure change, crystalline evolution, the dislocation generation and annihilation were monitored by carrying out Common Neighbor Analysis (CNA), and Dislocation Extraction Algorithm (DXA) analysis. Then the atomic diffusion activities were studied by analyzing the corresponding atomic Mean-Squared Displacement (MSD) diagrams. In addition, particle rotation phenomena and pore evolution during sintering have been extensively studied. Based on the studies in this chapter, the positive and negative effect of the substrate on the evolution of the nanoparticles sintering mechanism and the generation of the microscopic pores were deeply discussed.

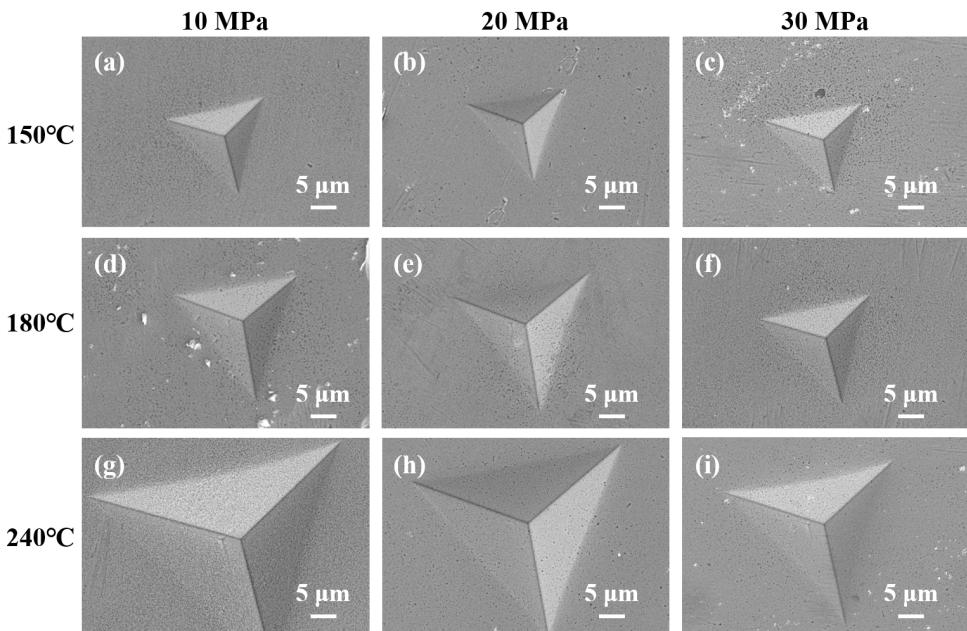

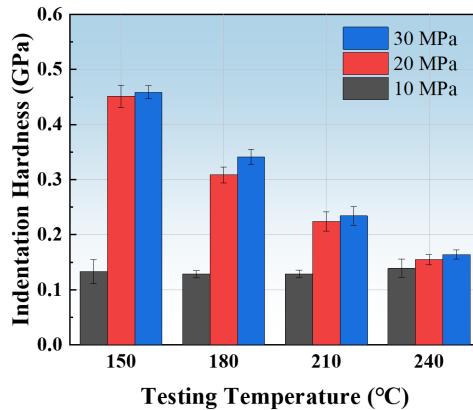

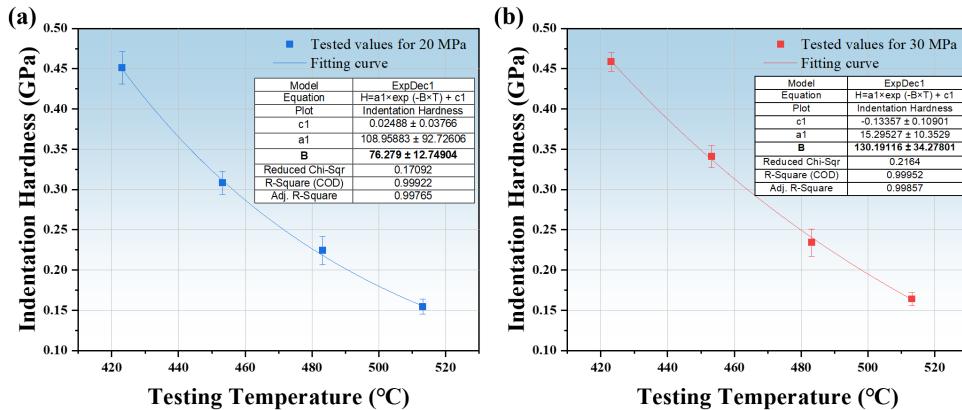

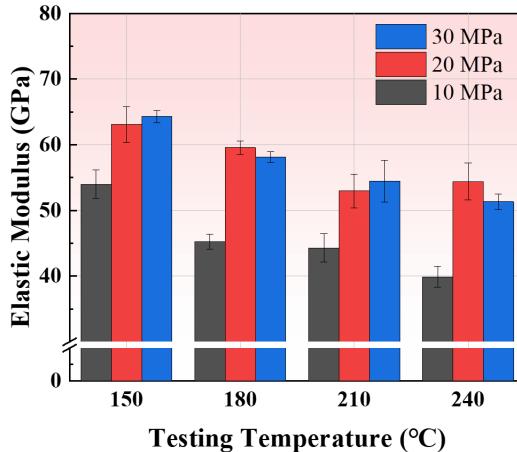

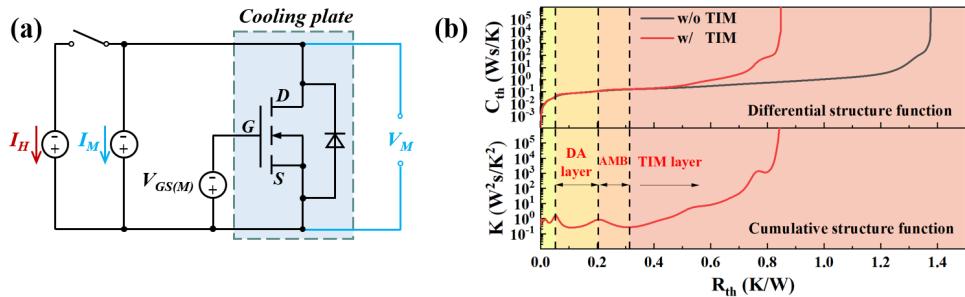

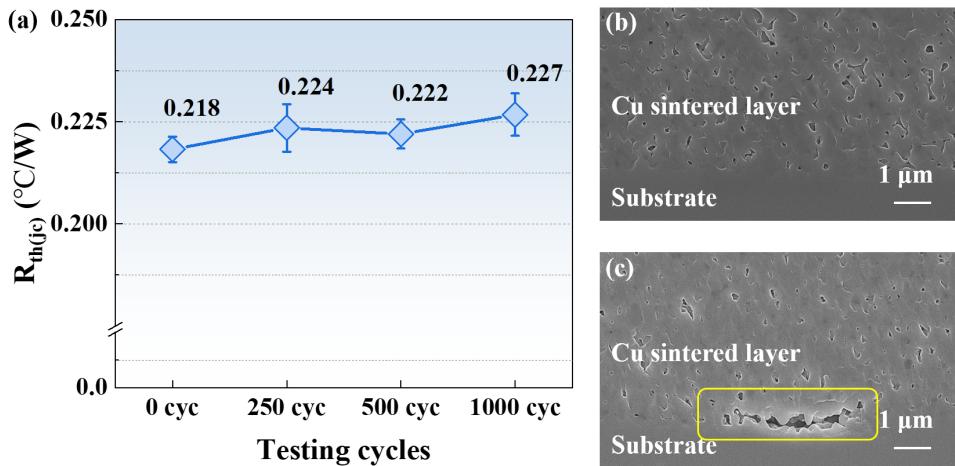

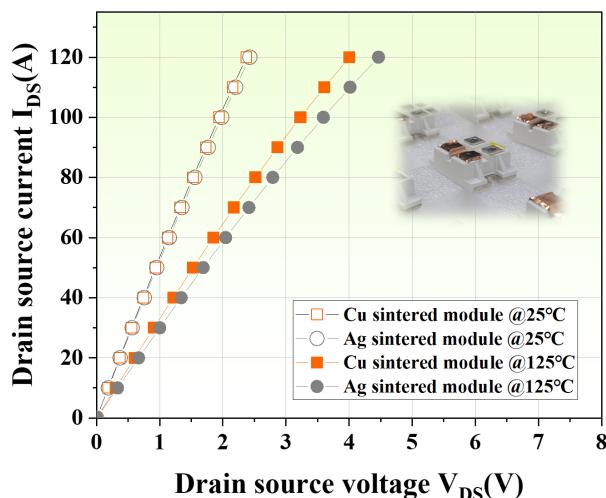

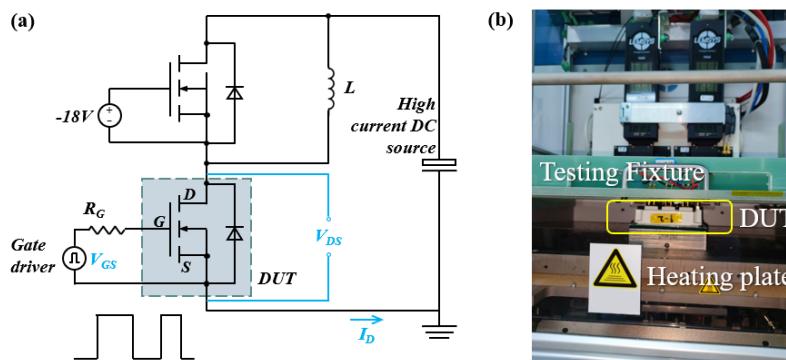

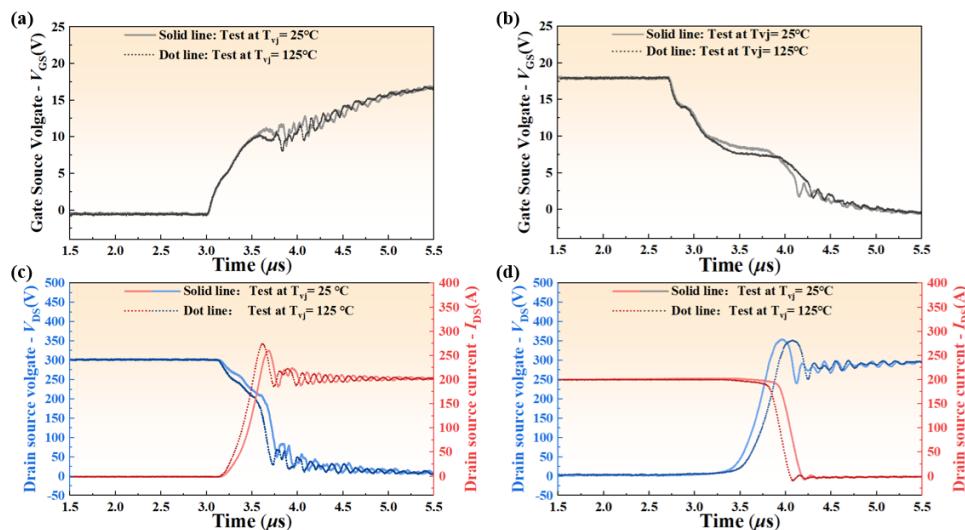

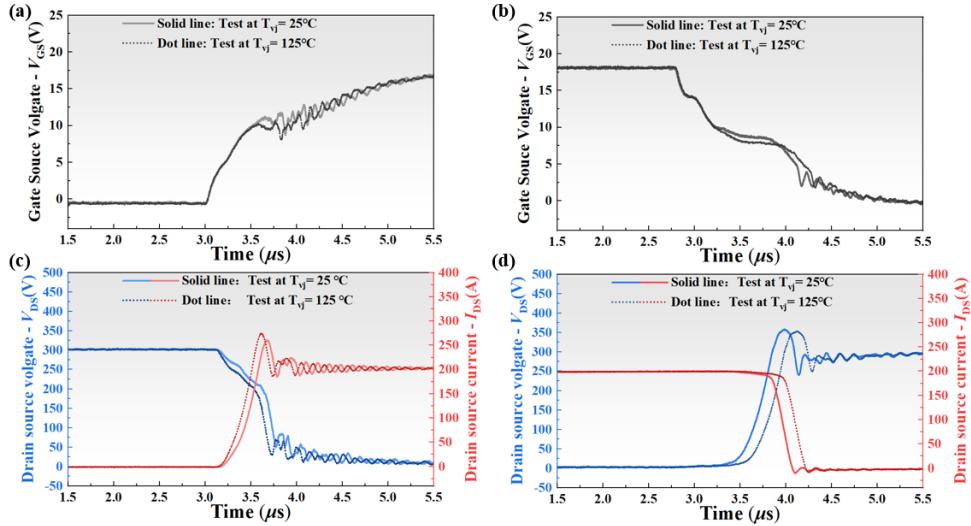

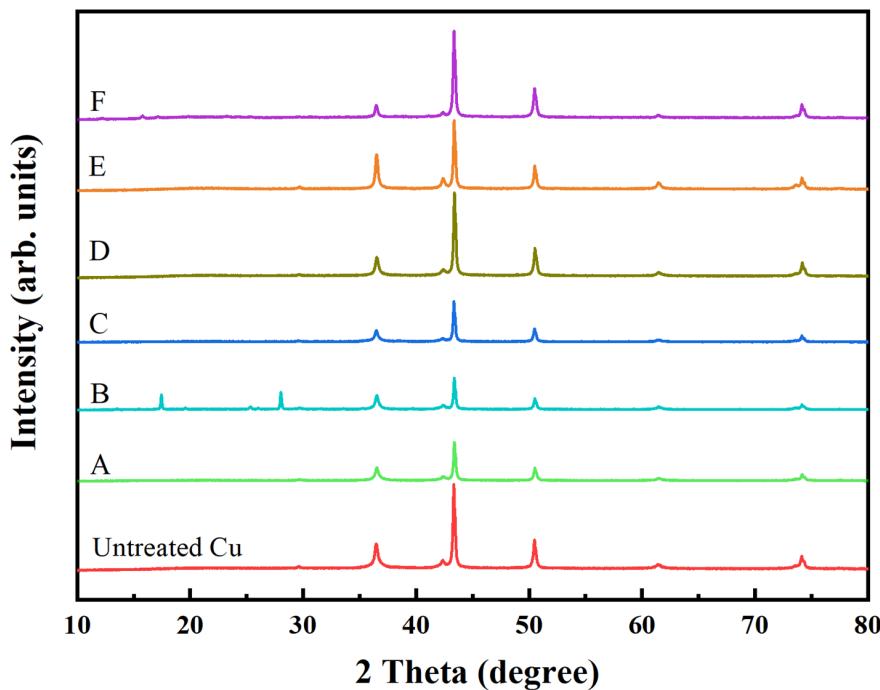

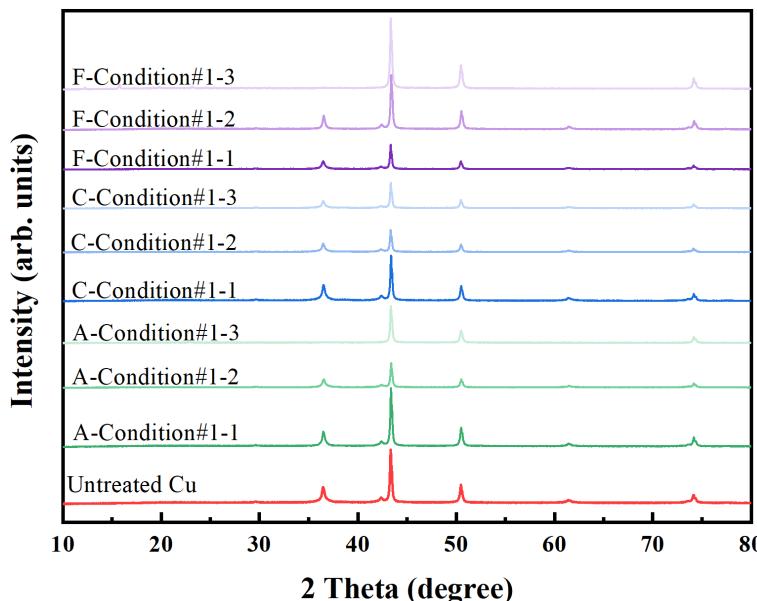

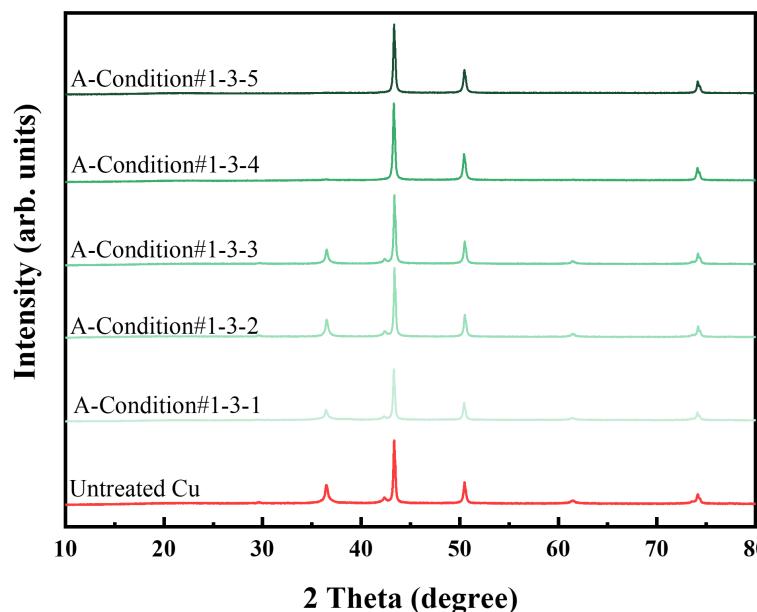

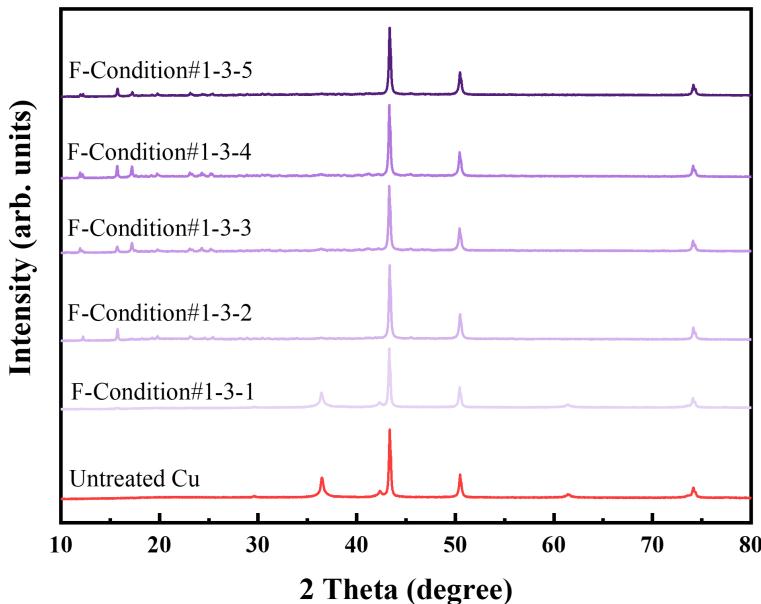

Figure 1.11: The outline of the thesis.