# DRAM Fault Analysis and Test Generation

# DRAM Fault Analysis and Test Generation

## Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof.dr.ir. J.T. Fokkema, voorzitter van het College voor Promoties, in het openbaar te verdedigen

op maandag 27 juni 2005 om 15.30 uur

$\operatorname{door}$

Zaid AL-ARS

elektrotechnisch ingenieur geboren te Bagdad, Irak Dit proefschrift is goedgekeurd door de promotor:

#### Prof.dr.ir. A.J. van de Goor

#### Samenstelling promotiecommissie:

Rector Magnificus, chair Prof.dr.ir. A.J. van de Goor Prof.dr.ing. E.J. Aas Prof.dr. C.I. Beenakker Prof.dr. H. Corporaal Dr. S. Mijalkovic Dr. G. Müller Prof.dr. L. Nanver Prof.dr. J.R. Long Delft University of Technology, Delft, The Netherlands Delft University of Technology, Delft, The Netherlands Norwegian Univ. of Sci. and Tech., Trondheim, Norway Delft University of Technology, Delft, The Netherlands Tech. Univ. of Eindhoven, Eindhoven, The Netherlands Delft University of Technology, Delft, The Netherlands Infineon Technologies, Munich, Germany Delft University of Technology, Delft, The Netherlands Delft University of Technology, Delft, The Netherlands

This work has been supported by Infineon Technologies, Munich, Germany, with a grant to the Delft University of Technology.

Graphical cover illustration by ATOC Designs (http://www.atocdesigns.com/)

ISBN-13: 978-90-9019612-1 ISBN-10: 90-9019612-9

NUR 959

### Copyright © 2005 Zaid Al-Ars

All rights reserved. No part of this publication, either text or image may be used for any purpose other than personal use. Reproduction, modification, storage in a retrieval system or retransmission, in any form or by any means, electronic, mechanical, or otherwise, for reasons other than personal use, is strictly prohibited without prior written permission from the author.

| To my father for teaching me how to have a dream, and to my mother for showing me how to make it a reality. |  |

|-------------------------------------------------------------------------------------------------------------|--|

|                                                                                                             |  |

|                                                                                                             |  |

|                                                                                                             |  |

|                                                                                                             |  |

|                                                                                                             |  |

|                                                                                                             |  |

# DRAM Fault Analysis and Test Generation

## Abstract

The dynamic random access memory (DRAM) is the most widely used type of memory in the market today, due to its important application as the main memory of the personal computer (PC). These memories are elaborately tested by their manufacturers to ensure a high quality product for the consumer. However, this testing process is responsible for a large portion of the cost of these memories, standing now at 40% and gradually rising with each new generation. Companies usually develop the required memory tests in an ad hoc manner, relying heavily on an expensive combination of experience and statistics to construct the best test approach, the price of which is ultimately paid by the end consumer.

In this thesis, we propose a new alternative approach to the development of industrial memory testing that is more systematic and less expensive than the currently prevalent test approaches. The new approach is based on the introduction of a number of fault analysis algorithms that enable the application of electrical Spice simulations to develop effective memory tests in a short amount of time. The new approach makes it possible to enhance memory tests in many different manufacturing stages, starting from the initial test application stage where silicon is manufactured, through the memory ramp-up stage where products are shipped to the customer, and ending with the test adaptation stage, based on memory failures in the field. The new test development approach has been implemented and evaluated at Infineon Technologies, a leading DRAM manufacturer, to develop tests for their DRAM products.

This thesis describes the details of the proposed test development algorithms, along with the way they are practically implemented for DRAM devices. Two different aspects necessary for DRAM tests are identified: test patterns and test stresses, then methods to generate and optimize both of them are proposed. In addition, the thesis discusses the results of applying the proposed approach to a large number of DRAM defects, modeled from known DRAM failures on the layout level. Finally, the thesis ends with an elaborate case study to generate and optimize tests for a specific DRAM problem for which the new test development approach has proven its effectiveness.

# Fout Analyseren en Test Genereren in DRAMs

# Samenvatting (Abstract in Dutch)

Het dynamic random access memory (DRAM) is heden het meest gebruikte type geheugen, wegens zijn belangrijke toepassing als het werkgeheugen van de personal computer (PC). Geheugen chips worden door geheugen fabrikanten uitvoerig getest om de hoge kwaliteit van hun producten te garanderen. Dit testproces is verantwoordelijk voor een groot gedeelte van de kosten van een geheugen, die nu rond 40% is, en geleidelijk met elke nieuwe geheugen generatie toeneemt. In het algemeen ontwikkelen bedrijven de vereiste geheugentests op een ad hoc manier, gebaseerd op een dure combinatie van ervaring en statistieken, om de beste tests te construeren. De prijs daarvan wordt uiteindelijk door de consument betaald.

In dit proefschrift, stellen wij een nieuwe en alternatieve benadering van industrieel test ontwikkeling voor, die systematischer en goedkoper is dan de huidige testmethoden. De nieuwe benadering is gebaseerd op de introductie van een aantal algoritmen om geheugenfouten door middel van elektronische Spice simulaties te analyseren. Dit maakt het mogelijk efficiënte geheugentests op korte termijn te ontwikkelen en om de tests in vele verschillende productiestadia te verbeteren. De nieuwe testontwikkeling methoden zijn bij Infineon Technologies, een belangrijke DRAM fabrikant, uitgevoerd en gevalueerd om tests voor hun DRAM producten te ontwikkelen.

Het proefschrift beschrijft de details van de voorgestelde testontwikkeling algoritmen, samen met de manier waarop zij praktisch voor DRAMs worden uitgevoerd. Twee belangrijke DRAM testaspecten worden geïdentificeerd (testpatronen, en teststress), en methoden om beide testaspecten te produceren en te optimaliseren worden voorgesteld. Bovendien bespreekt het proefschrift de toepassings resultaten van de voorgestelde testmethoden op een groot aantal bekende DRAM defecten, die belangrijk zijn op het layout-niveau. Tot slot eindigt het profschrift met een gedetailleerde casestudy, om tests voor een specifiek DRAM probleem te produceren en te optimaliseren. Hierin wordt het nut van de nieuwe benadering van testontwikkeling bewezen.

# Preface

From the bulky drum memory used in the early computer systems, through the relatively expensive core memory, to the semiconductor memory used extensively in most of today's integrated circuits (ICs), memory has played a vital, albeit quiet role in the history of computing. However, this important role is gradually becoming ever clearer, due to the exponentially increasing amount of memory used in ICs today, and because a constantly growing percentage of these ICs is being dedicated to implement memory devices. According to the International Technology Roadmap for Semiconductors (ITRS), a leading authority in the field of semiconductors, memory occupied 20% of the area of an IC in 1999, 52% in 2002, and is forecast to occupy up to 90% of the area by the year 2011. Due to this considerable usage of memory in many ICs, improvements in the design and fabrication process of memory devices have a considerable impact on the overall IC characteristics. Therefore, reducing the energy consumption, increasing the reliability or, most importantly, reducing the price of memories has a similar impact on the overall systems that contain them.

Furthermore, a large portion of the price of a memory today is incurred by the high costs of memory testing, which has to satisfy very high quality constraints ranging from 50 failing parts per million (ppm) for computer systems to less than 10 ppm for mission-critical applications (such as those in the automotive industry). Memory testing is expensive because of the high cost of the test equipment (a production memory tester costs more than \$500,000), a cost that has to be distributed over all of the produced chips, good and bad. As an example, a well-designed test of a typical 64 Mb DRAM comprises 39% of its total cost. The test cost of a 256 Mb DRAM is estimated to be more than 50% of the total cost, making the field of memory testing a rather significant and influential part of the whole memory production process.

Despite the huge current and future growth potential of the filed of memory testing, not much research has been dedicated to this important aspect of the IC industry. This lack of research is mainly due to the fact that memory testing is a relatively new and developing field, and to the unorthodox mathematical techniques it employs for fault modeling and test generation. Moreover, only a limited number of research projects exist in this field in the form of a collaboration between the industry and the academic world, due to the company-confidential nature of the memory test information.

#### A word on the project

The work in this thesis describes the results of a joint research project titled "Fault Analysis of DRAMs Using Defect Injection and Simulation" between Infineon Technologies, Munich, Germany, and the Delft University of Technology, Delft, The Netherlands, to analyze the faulty behavior of DRAMs produced by Infineon. It represents an example of a small number of projects between the memory industry and academia, meant to study the faulty behavior of memory devices and to suggest new, theoretically justified memory tests. The current project is a continuation of a previous joint project between Siemens Semiconductors (presently Infineon Technologies) and the Delft University of Technology, which supplied the material for the masters thesis "Analysis of the Space of Functional Fault Models and Its Application to Embedded DRAMs", by Zaid Al-Ars.

When we started out working on the project, the objective was to come up with a set of memory tests able to effectively detect the faults commonly encountered in DRAM chips. But soon it became clear that designing such a set of tests is not possible, because of the changing nature of the faulty behavior that takes place with every new technology or new design that comes into the market. As a result, the objective of the project rapidly shifted from generating a set of generic tests for all DRAMs to devising new test approaches and test methods that enable systematic and cost-effective generation and optimization of memory tests on a memory-specific basis.

As a result, the project includes research aspects that have not been investigated before by the memory testing research community. One example of the new aspects treated in this project is the theoretical analysis of memory test stresses as an integral part of the test process. This has commonly been considered a practical issue in memory test development, and has not been understood nor justified from a theoretical point of view.

Due to the extensive industrial input to the project, many practical aspects have been incorporated into the research, while the theoretical roots of the project ensured the rigorous nature of the performed analysis. In such an environment, where different aspects of theory and practice need to be taken into consideration, it is rather difficult to fulfill the requirements of both. However, we hope that in this research project we were able to strike a good tradeoff between the two, without compromising any important aspects on either side.

#### A word on the thesis

The information included in this thesis is fully self-contained and does not assume any prior knowledge of specific aspects of memory devices on the part of the reader. A reader with minimum understanding of memories should be able to read through the whole thesis with ease, and gradually build up the information necessary to understand the described concepts.

The thesis is organized as follows. Chapter 1 gives a general introduction to the

history and status of memory technology. It also provides an introduction to the main concepts and challenges of memory testing. Chapter 2 describes the external behavior and the internal architecture of modern DRAM devices in some detail. Chapter 3 builds on the information in Chapter 2 to give a detailed description of the buildup and behavior of internal electrical circuits, in addition to the possible layout implementations of DRAMs. Chapter 4 presents the theoretical bases used to model the faulty behavior of DRAMs. Chapter 5 presents the new simulationbased fault analysis methods, used to generate the memory test patterns and to optimize the needed memory test stresses. Chapter 6 discusses the concepts of coupling and crosstalk between internal memory lines, and the way these influence the faulty behavior of the memory. In Chapter 7, the faulty behavior of a large number of memory defects is evaluated, based on an electrical level simulation of the behavior. Chapter 8 shows how to use the theoretical analysis of DRAM faults performed in Chapter 4 to derive the required DRAM tests. Chapter 9 discusses an elaborate case study performed on a specific well-known DRAM defect, clearly showing the full test generation and optimization potential of the simulation-based fault analysis methods. Finally, Chapter 10 summarizes the thesis and ends with the conclusions and recommendations.

This thesis has a web site on the Internet at http://ce.et.tudelft.nl/~pazaid/ books/phd.html. This site contains the latest information regarding this thesis, updated errata and links to related work. The site also gives information about the performed fault analysis work that has been left out from this thesis. In addition, links are given to the raw fault analysis data generated in the course of the simulation-based analysis described in the thesis. Any questions, comments, suggestions or typos can be submitted using the e-mail link on the site, and will be greatly appreciated.

This thesis has been typeset using the LATEX  $2_{\varepsilon}$  package on a Linux machine. Most of the figures have been constructed using Xfig, the freeware vector graphics tool included with most Linux distributions. Simulations have been performed using Titan, the Siemens/Infineon in-house Spice-based circuit simulator, while figures of simulation output and figures of function plots have been produced using gnuplot, the freeware function plotting utility. The graphical cover illustration was designed by the media design company ATOC Designs (http://www.atocdesigns. com).

#### **Acknowledgments**

This thesis work has lasted for a period of more than four years, and in that period it received the kind support and encouragement of countless individuals, without whom this thesis would not have been realized. First and foremost, I wish to thank Prof. Ad van de Goor, my professor, from the Delft University of Technology, for his active involvement and continued support that helped shape many parts of the project. This thesis was only made possible with his guidance, meticulous reviews, and brilliant advice. My gratitude also goes to Detlev Richter, my manager at the product engineering group in Infineon Technologies, for his vision of merging the two worlds of theory and practice, and for the confidence he had in our work. I would further like to thank Jens Braun, my supervisor at Infineon for his valuable comments and for the countless hours he dedicated to discuss every step of the project. At its onset, the project was also supported by Michael Kund and Bernd Gauch from Infineon, who merit my gratitude as well.

Special thanks go to Georg Müller and Carsten Ohlhoff from Infineon for ensuring continued support to the project after the departure of Detlev Richter and Jens Braun. I wish to give my personal gratitude to Martin Herzog from the Technical University of Munich for creating some of the fault analysis programs and automation scripts used in this thesis, and for applying them to the defective memory models. The thesis also benefited greatly from the input and suggestions to improve the quality of the work contributed by Jörg Vollrath and Martin Versen from Infineon.

I also wish to thank the members of the product engineering department, my department at Infineon, for keeping up a great working atmosphere and making my stay among them cheerful and fun. From those, I would especially like to mention Martin Meier, Henno Harder and Christian Jaekel. Many thanks also go to the computer-aided design department, particularly Stefan Scholl, for their round-the-clock support of our work. Gratitude is also due to the members of the design department, most notably Eckehard Plaettner for setting up the memory design environment, and Udo Weber for performing kerf measurements of special wafer structures needed for defect modeling.

I would also like to thank Mirjam Nieman, the editor of technical English at the Delft University of Technology, for her review and commentary on the thesis. I further want to thank the members of the Laboratory of Computer Engineering in the Delft University of Technology, my group, for their moral support and help to finalize this thesis, many of whom I consider personal friends and colleagues. Special mention is due to Prof. Stamatis Vassiliadis for his support of the project, to Said Hamdioui for his continuous encouragement, to Bert Meijs for keeping up an excellent and flexible working environment, and finally to Lidwina Tromp, our group assistant, for her help and understanding during the long periods I spent away from the university.

And last but not least, my many thanks go to my family, and my parents in particular, for their love, unlimited support and patience along the years.

# Contents

|          | Abs  | stract                                    | vi |  |  |  |  |  |  |  |

|----------|------|-------------------------------------------|----|--|--|--|--|--|--|--|

|          | San  | Samenvatting (Abstract in Dutch)          |    |  |  |  |  |  |  |  |

|          | Pre  | face                                      | х  |  |  |  |  |  |  |  |

| 1        | Inti | roduction                                 |    |  |  |  |  |  |  |  |

|          | 1.1  | Semiconductor memories                    |    |  |  |  |  |  |  |  |

|          |      | 1.1.1 Definition and physical form        |    |  |  |  |  |  |  |  |

|          |      | 1.1.2 Types of semiconductor memories     |    |  |  |  |  |  |  |  |

|          | 1.2  | Memory testing                            |    |  |  |  |  |  |  |  |

|          |      | 1.2.1 Definition of memory testing        |    |  |  |  |  |  |  |  |

|          |      | 1.2.2 Manufacturing test flow             | 1  |  |  |  |  |  |  |  |

|          |      | 1.2.3 Frontend and backend testing        | 1  |  |  |  |  |  |  |  |

|          | 1.3  | Contribution of the project               | 1  |  |  |  |  |  |  |  |

|          |      | 1.3.1 Framework of the contribution       | 1  |  |  |  |  |  |  |  |

|          |      | 1.3.2 Details of the contribution         | 2  |  |  |  |  |  |  |  |

|          | 1.4  | Outline of the thesis                     | 2  |  |  |  |  |  |  |  |

|          | Sum  | nmary                                     | 2  |  |  |  |  |  |  |  |

| <b>2</b> | DR   | AM behavior and architecture              | 2  |  |  |  |  |  |  |  |

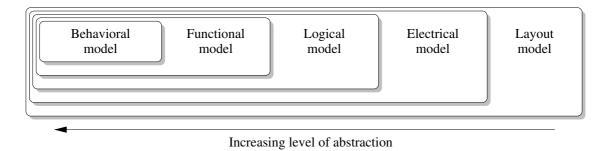

|          | 2.1  | Modeling of DRAMs                         | 2  |  |  |  |  |  |  |  |

|          | 2.2  | Behavioral DRAM model                     | 2  |  |  |  |  |  |  |  |

|          |      | 2.2.1 DRAM block diagram                  | 2  |  |  |  |  |  |  |  |

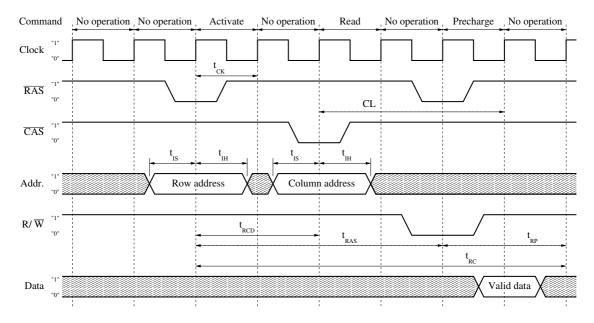

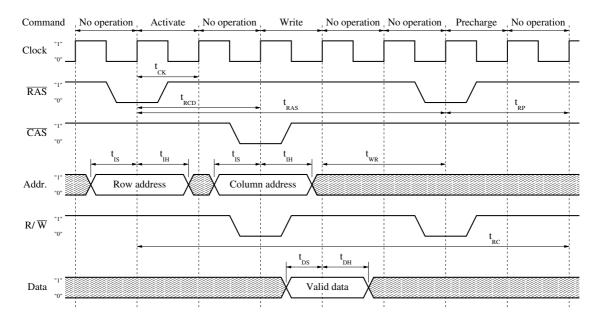

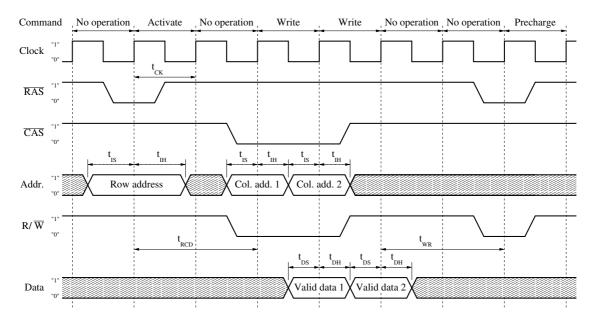

|          |      | 2.2.2 DRAM operations and timing diagrams | 3  |  |  |  |  |  |  |  |

|          | 2.3  | Functional DRAM model                     | 3  |  |  |  |  |  |  |  |

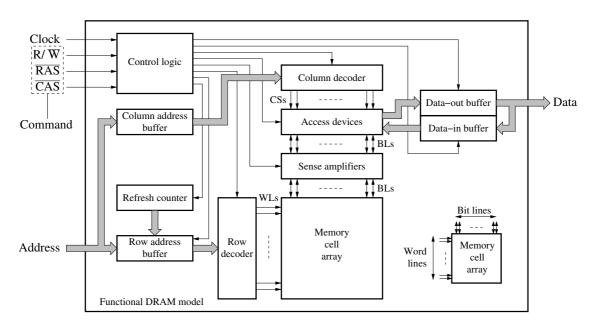

|          |      | 2.3.1 Functional block diagram            | 3  |  |  |  |  |  |  |  |

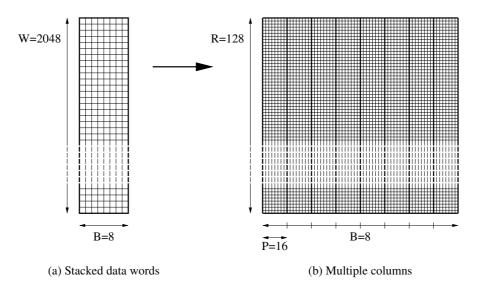

|          |      | 2.3.2 Cell array organization             | 3  |  |  |  |  |  |  |  |

|          |      | 2.3.3 Internal DRAM behavior              | 3  |  |  |  |  |  |  |  |

|          | Sum  | nmary                                     | 4  |  |  |  |  |  |  |  |

| 3        | DR   | AM design and implementation              | 4  |  |  |  |  |  |  |  |

|          | 3.1  | Basics of MOS transistors                 | 4  |  |  |  |  |  |  |  |

|          |      | 3.1.1 Physical transistor structure       | 4  |  |  |  |  |  |  |  |

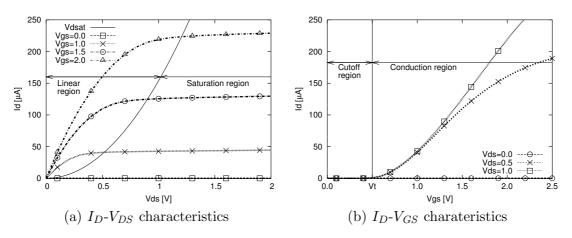

|   |     | 3.1.2 MOS transistor behavior          | 15            |

|---|-----|----------------------------------------|---------------|

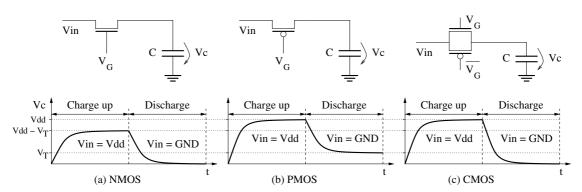

|   |     | 3.1.3 Transistor as a switch           | 18            |

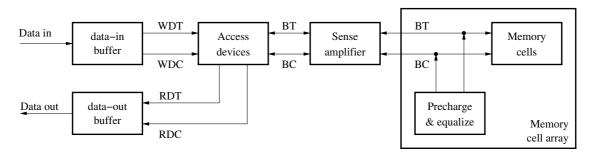

|   | 3.2 | Electrical DRAM model                  | 19            |

|   |     |                                        | 19            |

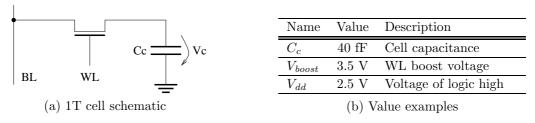

|   |     | 3.2.2 Memory cell                      | 50            |

|   |     | 3.2.3 Sense amplifier                  | 54            |

|   |     |                                        | 57            |

|   | 3.3 | DRAM layout model                      | 30            |

|   |     |                                        | 31            |

|   |     |                                        | 32            |

|   |     |                                        | 33            |

|   | Sum |                                        | 35            |

|   |     |                                        |               |

| 4 |     |                                        | <b>7</b>      |

|   | 4.1 |                                        | <sup>37</sup> |

|   |     |                                        | 38            |

|   |     | 1                                      | 39            |

|   | 4.2 | ±                                      | <sub>59</sub> |

|   |     | 1                                      | 39<br>-       |

|   |     |                                        | 71            |

|   |     |                                        | 76            |

|   |     | 1                                      | 77            |

|   | 4.3 | 1                                      | 78            |

|   |     | 0 1                                    | 79            |

|   |     | 1                                      | 32            |

|   |     | 1                                      | 36            |

|   | 4.4 | ±                                      | 39            |

|   |     |                                        | 39            |

|   |     | 1                                      | 91            |

|   |     | 1                                      | 94            |

|   | Sum | mary                                   | 96            |

| 5 | Fau | It analysis approximation methods      | 7             |

| • | 5.1 | J. T. T.                               | 97            |

|   |     | ·                                      | 98            |

|   |     |                                        | 99            |

|   |     | 5.1.3 Fault analysis time              |               |

|   | 5.2 | Approximate simulation                 |               |

|   | ٠   | 5.2.1 Example of 1D analysis           |               |

|   |     | 5.2.2 Fault analysis time              |               |

|   | 5.3 | Two dimensional analysis               |               |

|   | 5.4 | DRAM-specific simulation               |               |

|   |     | 5.4.1 Approximation with DRAM commands |               |

|   |     | 5.4.2 Stress optimization methodology  |               |

|   |     |                                        |               |

|   | Sum             | nary                                     |   | 116 |

|---|-----------------|------------------------------------------|---|-----|

| 6 | Effe            | ts of bit line coupling                  |   | 117 |

|   | 6.1             | Concept of BL coupling                   |   | 117 |

|   |                 | 3.1.1 Modeling BL coupling               |   | 118 |

|   |                 | 5.1.2 Effects of coupling                |   | 120 |

|   | 6.2             | Simulation of BL coupling                |   | 122 |

|   | 0.2             | 5.2.1 Fault analysis method              |   | 122 |

|   |                 | 3.2.2 Simulation results                 |   | 124 |

|   | 6.3             | Impact of BL twisting                    |   | 126 |

|   | 0.0             | 3.3.1 Theoretical evaluation of twisting |   | 126 |

|   |                 | 3.3.2 Simulation and analysis results    |   |     |

|   | Sum             | nary                                     |   | 132 |

|   |                 |                                          | • | 102 |

| 7 |                 | ication of the approximation method      |   | 133 |

|   | 7.1             | Memory simulation model                  |   | 134 |

|   |                 | 7.1.1 Simulated DRAM circuits            |   | 134 |

|   |                 | 7.1.2 Model reduction techniques         |   | 135 |

|   | 7.2             | Classification of defects                |   | 138 |

|   |                 | 7.2.1 Relations between injected defects |   | 139 |

|   |                 | 7.2.2 Definition of defects              |   | 140 |

|   | 7.3             | Application of 1D analysis               |   | 146 |

|   | 7.4             | Application of 2D analysis               |   | 153 |

|   | Sum             | nary                                     |   | 160 |

| 8 | Spa             | e of DRAM tests                          |   | 161 |

|   | 8.1             | Taxonomy of DRAM faults                  |   | 161 |

|   |                 | 8.1.1 Theoretical fault space            |   | 161 |

|   |                 | 8.1.2 Realistic fault space              |   | 165 |

|   | 8.2             | DRAM-specific tests                      |   | 166 |

|   |                 | 8.2.1 Detecting hard faults              |   | 167 |

|   |                 | 8.2.2 Detecting transient faults         |   | 171 |

|   |                 | 8.2.3 Detecting soft faults              |   | 176 |

|   | 8.3             | Customizing march tests                  |   | 181 |

|   | 0.0             | 8.3.1 Memory design considerations       |   | 181 |

|   |                 | 8.3.2 Memory layout implications         |   | 188 |

|   | Sum             | • •                                      |   | 191 |

| 9 | Cas             | study: the strap problem                 |   | 193 |

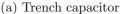

| J | 9.1             | Definition of strap problem              |   | 194 |

|   | $\mathcal{I}.1$ |                                          |   |     |

|   |                 |                                          |   | 194 |

|   |                 | 9.1.2 Simulation model                   |   | 195 |

|   | 0.2             | 9.1.3 Process variations                 |   | 196 |

|   | 9.2             | Analysis methodology                     |   | 198 |

# xviii | CONTENTS

|              |      | 9.2.1   | Simulated sequences       |  | 199 |

|--------------|------|---------|---------------------------|--|-----|

|              |      | 9.2.2   | Background 00             |  | 200 |

|              |      | 9.2.3   | Backgrounds 10, 11 and 01 |  | 203 |

|              | 9.3  | Result  | ts and tests              |  | 205 |

|              |      | 9.3.1   | Summary of results        |  | 205 |

|              |      | 9.3.2   | Test generation           |  | 207 |

|              | 9.4  | Optin   | nizing test stresses      |  | 210 |

|              |      | 9.4.1   | Optimizing $t_{cyc}$      |  | 211 |

|              |      | 9.4.2   | Optimizing temperature    |  | 215 |

|              | Sum  | mary    |                           |  | 219 |

| 10           | Con  | clusio  | ns and recommendations    |  | 221 |

|              | 10.1 | Concl   | usions                    |  | 221 |

|              | 10.2 | Contr   | ibutions                  |  | 226 |

|              | 10.3 | Recon   | nmendations               |  | 228 |

|              | Sum  | mary    |                           |  | 230 |

| $\mathbf{A}$ | List | of sy   | mbols                     |  | 231 |

| В            | List | of ab   | breviations               |  | 235 |

|              | Bibl | liograp | phy                       |  | 239 |

|              | Inde | ex      |                           |  | 247 |

|              | List | of pu   | blications                |  | 255 |

|              | Cur  | riculu  | m vitae                   |  | 259 |

|              | Stat | ement   | $\operatorname{ts}$       |  | 261 |

|              | Stel | lingen  | (Statements in Dutch)     |  | 263 |

# Contents of this chapter

- 1.1 Semiconductor memories

- 1.2 Memory testing

- 1.3 Contribution of the project

- 1.4 Outline of the thesis

Since the conception of the first electronic systems, memory components have always fulfilled the vital task of storing and retrieving system and user-specific data. Depending on the available technology and design requirements, memories have taken many different forms, ranging from the slow and bulky punch card storage prevalent in the early days of the computer industry to the fast and highly integrated semiconductor memories commonly found in today's leading-edge computer systems.

The fast development of memory devices and the strong market competition have increased the standards of these produced devices. The increased demand on reliability has, in turn, stressed the importance of failure analysis and memory testing techniques. More and more effort is being dedicated to the study of the faulty behavior of memory devices than ever before. This thesis describes one such study, made as a joint project between Infineon Technologies and the Delft University of Technology to study the faulty behavior of a number of memory designs, by utilizing electrical (or Spice) simulation models prepared during the design process to evaluate the faulty behavior of the memory.

This chapter gives an introduction to the topic of memory devices, the way they are tested, and to the Ph.D. project described in this thesis. Section 1.1 starts with an overview of semiconductor memory devices, presenting the different types of these devices along with the advantages and the disadvantages of each. Then, Section 1.2 discusses the test strategies used to test memories in the different stages of their production. Section 1.3 presents the contributions of this Ph.D. project to scientific knowledge and to industrial practices. Finally, an overview of the different chapters of this thesis is given in Section 1.4.

#### 1.1 Semiconductor memories

In their relatively short 30-year history, semiconductor memories have come from being an unknown and somewhat unproven technology to one of the most important memory technologies around. They provide an optimum combination of performance, price and density that gives them a central position in the computer industry. This section gives an overview of semiconductor memories, their different types and characteristics.

### 1.1.1 Definition and physical form

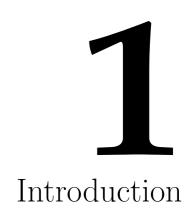

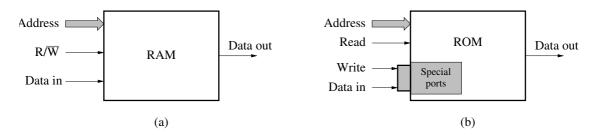

In very simple terms, a memory is a device used to store and retrieve information. Figure 1.1(a) shows a generic block diagram of a memory with the most basic input/output (I/O) interface possible, consisting of four inputs and one output. The address input identifies the memory cell of interest, on which memory operations are to be performed. The read input line signals a read operation performed to forward the data in the addressed cell to the data-out line. The write input line signals a write operation performed to store the data present on the data-in line into the addressed cell. Note that address input is represented in the figure as a wide arrow, which represents a so-called address bus, where a number of address lines are collected together into one single arrow. The terms "memory", "memory component", "memory device", and "memory part" all have the same meaning and are usually used interchangeably in the literature.

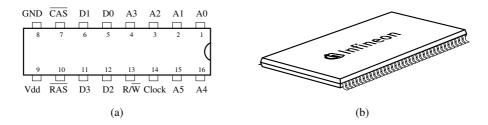

**Figure 1.1.** (a) Memory block diagram, (b) Infineon DRAM chip in TSOP, and (c) in TBGA package (source: Infineon Technologies).

One of the most well-known memory components in the industry is the **dynamic random access memory** ( $\mathbf{DRAM}$ ), primarily used as the main memory in personal computers (PCs), workstations and mainframes. The amount of DRAM found in a PC has a significant impact on its overall performance, and is considered an important parameter in PC specifications. DRAMs are usually produced in the form of an integrated circuit (IC) chip, which might be packaged in many different ways, depending on the specific application and the performance of the DRAM. Figure 1.1(b) shows an example of an Infineon memory packaged in a TSOP (thin small outline package), which is characterized by small size and low cost. This is a very common DRAM package suitable for memories of almost any size and density. It has an elongated rectangular shape with pins located on two sides of the package.

Figure 1.1(c) shows a 512 Mb (mega bit) DDR2 (double data rate 2) Infineon DRAM chip, packaged in a special high performance TBGA (tape ball grid array) package. It has a square shape with pins arranged in the form of a ball grid, located on the bottom surface of the chip. TBGA is a more expensive package to manufacture and to incorporate into a system, but it enables better performance and higher clock rates than TSOP by reducing internal die-to-pin path lengths and pin impedance. It also enables a much higher pin count, since it uses the whole bottom surface area of the package instead of only two sides of it.

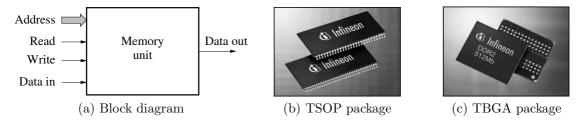

PC consumers are much more familiar with a DRAM module (also called DRAM card or DRAM stick) than with a single DRAM chip. A module basically consists of a printed circuit board (PCB) where a number of DRAM chips are connected together and made ready to be plugged into the system bus of the PC. Figure 1.2 gives an example of a 512 MB (mega byte) DDR2 Infineon DRAM module, where 8 TSOP 512 Mb chips of the type shown in Figure 1.1(b) are placed side by side and connected together on the PCB. There are two main types of DRAM modules: single in-line memory modules (SIMMs), and dual in-line memory modules (DIMMs), both of which have the same form shown in Figure 1.2. The main difference between the two lies in the fact that the data bus on a DIMM is twice as wide as that on a SIMM. The data bus width for a SIMM can range from 32 bits in small PCs up to 200 bits in a workstation, while twice this bus width applies for a DIMM [Prince99].

Figure 1.2. Infineon 512 MB DRAM module with chips in TSOP packages (source: Infineon Technologies).

#### 1.1.2 Types of semiconductor memories

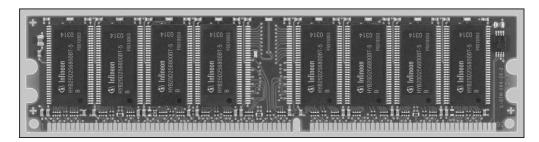

Figure 1.3 shows a common classification of the most important types of semiconductor memories, where two main classes are identified: random access memories (RAMs), and read-only memories (ROMs). The name RAM stands for a memory device in which cells may be accessed at random to perform a read or a write operation. Depending on the internal architecture and the actual memory cell structure, RAMs may be further divided into:

• dynamic RAMs (DRAMs), and

• static RAMs (SRAMs).

The name ROM, on the other hand, stands for a memory that can only be written a limited number of times but can be read indefinitely. The most important types of ROM are:

- programmable ROM (PROM),

- erasable PROM (EPROM),

- electrically erasable PROM (EEPROM), and

- flash memory.

As the manufacturing processes of ROMs improve, and device performance and number of possible write operations increase, the sharp boundary between RAM and ROM is gradually eroding [Waser03]. In the following, we will provide a general description of these architectures along with their advantages and disadvantages.

Figure 1.3. Classification of semiconductor memories.

#### **RAM** devices

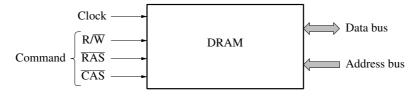

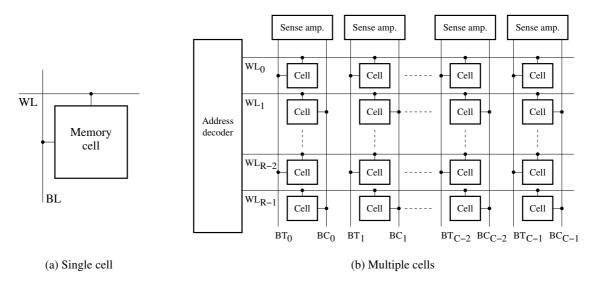

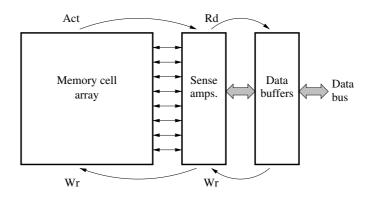

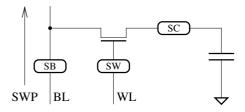

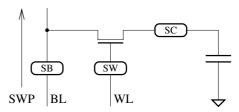

A simple block diagram of a RAM is given in Figure 1.4(a). Three main inputs are shown: a read/write  $(R/\overline{W})$  switch to signal the type of operation performed, an address input which identifies the cell to be accessed, and a data input line that supplies the data to be written in case of a write operation. A RAM also has a data output line to be used on a read operation to forward data from the addressed cell to the outside world. In principle, both DRAMs and SRAMs share this same general interface, but the specific implementation is different and mainly depends on the targeted application of the memory.

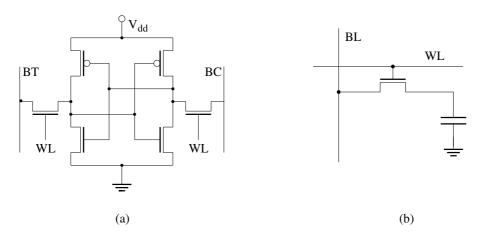

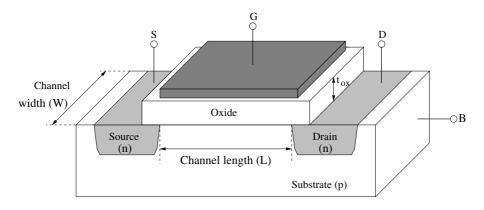

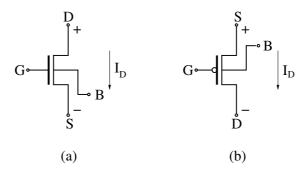

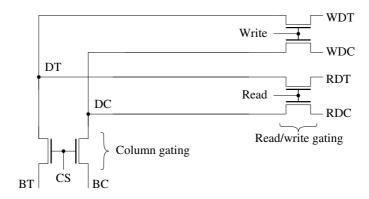

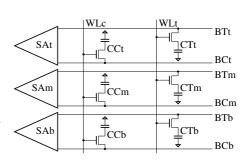

The electrical structure of an SRAM cell is shown in Figure 1.5(a). The cell is constructed using six transistors, four of which are of one transistor type (NMOS) while the other two are of another type (PMOS). The word line (WL) in the figure

Figure 1.4. Block diagrams of (a) RAMs and (b) ROMs.

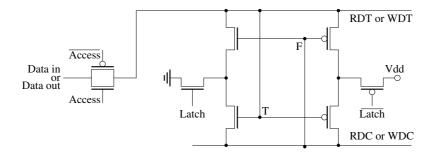

performs the address selection function for the cell. The  $true\ bit\ line\ (BT)$  and complement bit line (BC) serve both as the data input line and the data output line for the cell at the same time. The selection between performing a read or a write operation is fulfilled by other memory parts external to the cell. The operation of the cell in the figure is based on the fact that SRAM cells are bistable electrical elements (i.e., circuits that have two stable states). Each state is used to represent a given logical level. Once a cell is forced into one of the two states, it will stay in it as long as the memory is connected to the power supply; the name "static RAM" refers to this property.

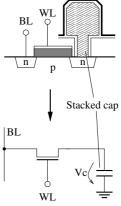

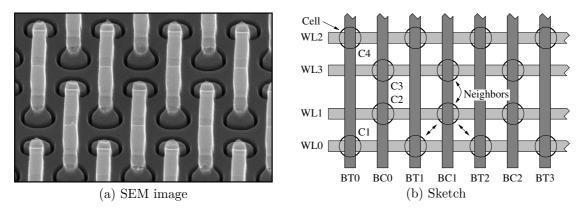

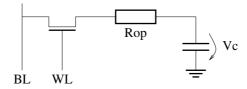

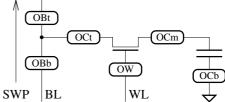

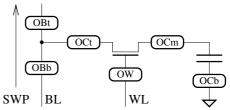

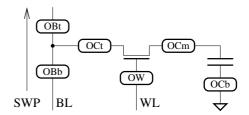

Figure 1.5. Electrical structure of (a) SRAM and (b) DRAM core cells.

The electrical structure of a DRAM cell is shown in Figure 1.5(b). The cell is constructed using one transistor and one capacitor. The WL performs the address selection, while the bit lines (BLs) are used as both the data input and data output lines. The selection between read and write operations is performed by other parts of the memory. As seen in the figure, DRAMs are constructed of simple capacitive elements that store electrical charges to represent a given logical level. Inherently, DRAM cells suffer from gradual charge loss, as a result of a phenomenon known as transistor leakage currents, which cause a cell to lose its charge gradually. In order to help cells keep their state, it is necessary for DRAMs to rewrite, or refresh, the already stored data bits from time to time before the cells lose their charge completely. The name "dynamic RAM" refers to the fact that the data stored in the DRAM cell may change spontaneously after a given period of time.

Both DRAMs and SRAMs are called **volatile memories** because they can only keep their data content if they stay connected to the power supply. A closer look at the two RAM structures reveals that SRAMs store their data actively by pulling their nodes to high or low voltage levels, while DRAMs store their data in capacitive elements that take time to charge up and discharge. Therefore, SRAMs have a much higher performance than DRAMs, and this is the reason they are used as the first level memory (or **cache memory**) directly supporting the *central processing unit* (*CPU*) in a microprocessor. Among other things, the main advantage that DRAMs have over SRAMs is in their density. Figure 1.5 clearly shows that DRAM cells are simple, compact elements that achieve much higher chip densities than their SRAM counterparts, which also makes them much cheaper. This cost difference is so important that it outweighs all other aspects in most applications [Al-Ars99].

#### **ROM devices**

The other architectural variation of semiconductor memories is the ROM, which is shown in Figure 1.4(b). ROMs are preprogrammed memory devices that permanently store information needed by the microprocessor for basic operation, information such as routines to interact with discs, keyboards and the display [Prince91]. The figure indicates that the write and data input lines are applied by special means, in accordance with the read-only functionality of ROMs. The most basic type of ROM, called **masked ROM** or simply ROM, can only be written once at the time of manufacturing, after which stored data cannot be changed. ROMs are non-volatile and, therefore, keep their stored data even when power is turned off.

**PROM** One variant of the ROM is the *programmable ROM*, or *PROM*, which is delivered unprogrammed to the consumer, who is then able to program it by writing an application-specific set of data only once. The stored information cannot be erased afterwards, a property that puts a limitation on the reusability of the PROM if the application for which the memory is used changes.

**EPROM** To tackle the limited reusability problem of PROMs, the *erasable PROM* (*EPROM*) was introduced. Once programmed, the EPROM acts like a normal ROM. However, if the need arises, the user is capable of erasing the contents of the EPROM and can reprogram it again. The disadvantage of the EPROM is that it cannot be reprogrammed while residing in the system; it must be removed from the system and erased with ultraviolet (UV) light first, and then reprogrammed using special equipment. Other disadvantages of the EPROM include a lower performance than ROMs, sensitivity to light, and expensive packaging with small quartz windows.

**EEPROM** The disadvantages of the EPROM have led to the introduction of the electrically erasable programmable ROM (EEPROM). The EEPROM can be electrically reprogrammed in the system, which eliminates the need of removing it, erasing it with UV light and reprogramming it using special equipment. EEP-ROMs have cheap packaging and are not sensitive to light. The main disadvantage here is the greater cell complexity as compared to the EPROM, and consequently the higher price. EEPROMs are only economically justified when non-volatility and in-system re-programmability are required.

**Flash memory** One variant of the EEPROM is the so-called flash memory, which combines the best features of the memory devices described thus far. Flash memories have high density, low cost, are non-volatile, fast (to read, but not to write), and electrically reprogrammable. These advantages are clearly overwhelming and, as a result, the market share of flash memory has increased dramatically in the past few years, especially in embedded systems and for mobile applications. From a software point of view, flash and EEPROM technologies are very similar. The major difference between them is that flash devices can only be erased in chunks, one sector at a time, and not on a byte-by-byte basis. Typical erasable sector sizes are in the range of 256 bytes to 16 KB. Despite this disadvantage, the flash memory combines an unbeatable set of advantages and is, therefore, becoming much more popular than the EEPROM. Flash is rapidly displacing other ROM devices as well, and in an increasing range of applications.

To summarize the discussion above, Table 1.1 lists the features of each type of semiconductor memory, and tries to quantify some aspects of memory operation. It is clear from the table that each memory type has its own strengths and weaknesses, which means that no one type can replace all others, but that each memory suits its own specific application [IBM02, Infineon04, Itoh01].

| Criterion                    | SRAM     | DRAM     | ROM      | EPROM    | EEPROM        | Flash                |

|------------------------------|----------|----------|----------|----------|---------------|----------------------|

| Relative cell size           | 4-6      | 1.5      | 1        | 1.5      | 3-4           | 1.5                  |

| Volatility                   | yes      | yes      | no       | no       | no            | no                   |

| Data retention               | $\infty$ | 64  ms   | $\infty$ | 10 years | 10 years      | 10 years             |

| In-system re-programmability | yes      | yes      | no       | no       | yes           | yes                  |

| In-system read speed         | 2.5 ns   | 55  ns   | 90 ns    | 90 ns    | 200 ns        | 60 ns                |

| In-system write speed        | 2.5 ns   | 55  ns   |          | _        | 2.5 s         | $6.4~\mu \mathrm{s}$ |

| Number of writes             | $\infty$ | $\infty$ | 1        | 100      | $10^4 - 10^5$ | $10^4 - 10^5$        |

Table 1.1. Summary of the characteristics of the different memory architectures.

# 1.2 Memory testing

The exponential increase in the integration density of memory components and the associated increase in the complexity of memory faulty behavior have made fault analysis and memory testing a significantly important, yet a difficult task to perform. This section serves as a global introduction to the topic of memory testing and the way it is usually performed in the industry.

## 1.2.1 Definition of memory testing

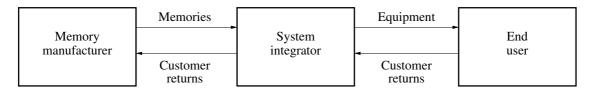

Memory testing means different things to different people. There are three major parties involved in the supply chain of memory devices, and each needs to test the memory in a different way:

- the memory chip manufacturer,

- the system integrator, and

- the end user.

Figure 1.6 graphically represents these three parties involved in the supply chain and the way they interact. A memory chip manufacturer is the party involved in defining the specifications of memory devices and subsequently designing and manufacturing raw memory devices of the form shown in Figure 1.1(b) and (c). The system integrator is the party that buys memory devices from a memory manufacturer and implements them into a system intended to solve a specific customer need, such as PCs, workstations or networking equipment. The end user is the party that acquires the equipment provided by the system integrator in order to deploy it for solving a specific problem.

Figure 1.6. Supply chain of memory devices.

The big burden of extensive testing and qualification of memory devices rests squarely on the shoulders of the memory chip manufacturer, the first party in the memory supply chain. The system integrator may perform simple tests on purchased memory devices to screen out defective parts before incorporating them into bigger systems. But this practice is gradually disappearing, as many companies expect the devices to be delivered just in time for use, and with very high quality levels. System integrators are expected, however, to test their systems extensively before delivery to the end user. During this testing process, if memory devices are

systematically found to cause equipment failure, these defective memories are sent back to the manufacturer in the form of customer returns. The manufacturer is then expected to investigate these returns and to try to screen them out before they are sold to the system integrator. Finally, the end user is not expected to perform any specific testing on acquired systems other than setting them up for regular operation. Here too, the end user sends back defective systems to the integrator in the form of customer returns for reparation or replacement.

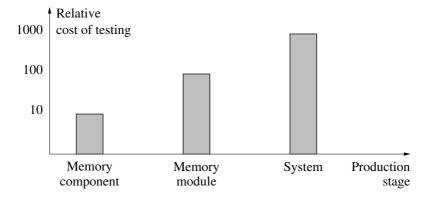

The fact that memory testing should mainly, and almost exclusively, be performed by memory manufacturers is due to the exponential increase in the cost of detecting a defective component after it gets incorporated into increasingly more complex systems, from chip to module to system. A well-known industrial rule of thumb (sometimes referred to as the "rule of tens") on the relative cost of system testing states that at each successive stage in production, it cost ten times as much to identify and repair a defective component than it would have cost at a previous production stage [Jha03]. Figure 1.7 gives a graphical representation of this rule.

$$Cost_{stage(i+1)} = 10 \cdot Cost_{stage(i)}$$

(1.1)

Figure 1.7. Relative cost of component testing at each stage in production.

This rule means that memory manufacturers have to elaborately test their memory chips in order to ensure the very high quality requirements expected from ICs in general and from memories in particular. Currently, manufacturers of high quality memories, such as those in the automotive industry, should supply chips with failure rates as low as 10 ppm (parts per million) to their customers [Majhi05].

Since memory testing is mainly performed by memory manufacturers, this thesis is only concerned with manufacturing tests, as it is the field where the biggest investment in testing is incurred, and where the highest possibility of payback on research is expected.

#### 1.2.2 Manufacturing test flow

A test flow is a description of the stages needed to test a specific device, along with the activities needed to set up and adapt these stages so that the device can be tested successfully. Different memory components require different test flows that fit the specific needs of each component. Despite the differences, all memories have lots of similarities and share the same general test flow structure.

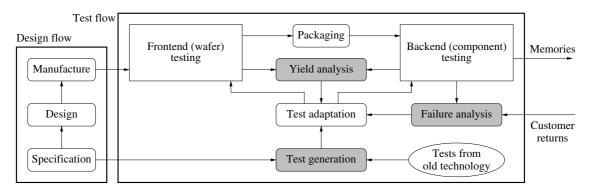

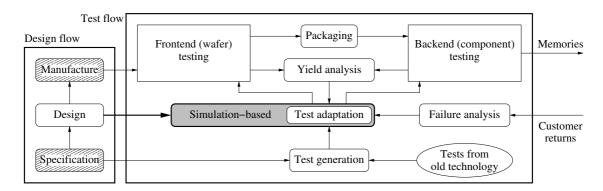

Figure 1.8 shows a simplified block diagram of a typical manufacturing test flow performed by a memory manufacturer [compare with Figure 1.6]. The figure also shows a three-stage representation of the design flow, starting with the specification of a new memory technology, followed by the design process and culminating with the actual chip manufacturing process [Nakamae03, Antonin91]. The design flow is included here for completeness, and to underscore the important interaction between the design and test flow. Within the test flow, the actual testing process takes place in only two blocks in the figure

- frontend (or wafer level) testing, and

- backend (or component level) testing,

drawn as two large rectangles. Frontend testing is performed before chip packaging so that only functional chips get to the packaging process, in order to reduce the costs of packaging. Backend testing ensures that packaged chips function properly before delivery to the customer. More details about the activities in these two test stages are given in the next section.

Figure 1.8. Block diagram of a manufacturing test flow for a memory manufacturer.

Figure 1.8 shows that in order to set up and maintain a proper testing process, three main activities need to be carried out (identified as three shaded blocks in the figure):

- test generation,

- yield analysis, and

- failure analysis.

**Test generation** For every new memory technology, an initial set of tests is needed to test the first manufactured components. This initial set is generated by adapting an existing set of tests used for the previous memory technology, so that the tests would fit the specifications of the new memory technology. Generating this initial set is the first step in setting up the memory testing process, and it starts even before the design is complete and before first silicon (a term used in the industry for the first wafers produced for the new technology) is manufactured.

**Yield analysis** Yield (Y) is defined as the fraction of functional memories relative to the total number of produced memories by a manufacturing process.

$$Y = \frac{\text{number of functional memories}}{\text{total number of memories}}$$

(1.2)

A successful manufacturing process is expected to result in high yield values. However, the actual manufacturing yield depends heavily on the quality of the testing process. A very stringent test process results in eliminating a large number of chips and allows only memories with the highest quality to pass to the customer, while a less restrictive test process allows a large number of high and low quality components to pass to the customer. Depending on the required memory quality and the effectiveness of the manufacturing process, a target yield is identified and tests should be modified to match it. For example, memories produced for mission-critical applications (such as life-support systems) demand very stringent test requirements, for which a lower yield (and a corresponding increase in price) is tolerated.

**Failure analysis** The ultimate arbitrator of a product's success is customer satisfaction. As long as the customer buys produced components and does not complain about equipment failures as a result of purchased memories, then the total manufacturing and testing process is considered to be functioning properly. But once the customer expresses dissatisfaction, and customer returns start coming back to the memory manufacturer, then failure analysis must be performed immediately on these customer returns to identify the defect causing the failure. Subsequently, the test process must be modified as soon as possible to prevent this type of defective devices from being shipped to the customer.

The next section discusses in more detail the actual manufacturing test process, which is performed within the frontend and backend stages of the test flow.

#### 1.2.3 Frontend and backend testing

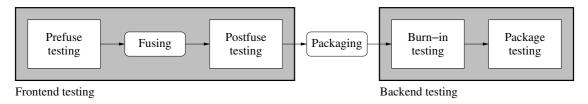

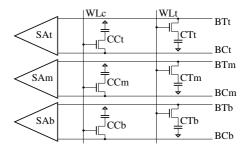

The frontend and backend test stages are the cornerstones of any memory test process. They are the test flow stages where the tests are actually performed on the memory, and the correctness of the memory behavior is inspected [Falter00]. Although the frontend and backend test stages are part of the test flow of most memory devices, the exact sequence of test steps (also called **test insertions**) that take place in each of these two stages vary significantly depending of the specific type of memory being tested. Still, the test process needed for DRAMs and SRAMs have a number of shared characteristics, and can be divided into four main test insertions [see Figure 1.9]:

- prefuse testing,

- postfuse testing,

- burn-in testing, and

- package testing.

In the following, these four test insertions are discussed, after which some of the differences in the test process of DRAMs and SRAMs are identified.

Figure 1.9. Typical test process of DRAM and SRAM devices.

Prefuse testing This is the first test insertion of frontend testing in the memory test process, with the main objective of identifying the failing cells and repairing them using redundant memory elements. In addition, the tests used here should be able to indicate the type of failure mechanism at play in case a failure does take place. This information is important as feedback to the manufacturing facility (fab) to modify the fabrication process, and to eliminate the failure in order to increase yield. One important characteristic of prefuse testing is that it is performed onwafer, using tiny needles (or probes) that are unable to conduct large amounts of current, thereby limiting the speed at which tests are performed in this test insertion. In other words, the high-speed operation of the memory cannot be inspected by prefuse tests. Such speed tests can only be performed after memory packaging, in the package testing stage, the final test insertion in the test flow [see package testing below].

**Postfuse testing** This is the second test insertion of frontend testing in the memory test process, with the main objective of checking that redundancy fusing and repair has been done in a proper way. Tests performed in this stage are rather simple and short sequences of write and read operations (so-called *scan tests*) used to check the basic functionality of repaired memory elements.

**Burn-in testing** This is the first test insertion of backend testing in the memory test process, and it takes place after wafer dicing and chip packaging. Burn-in is a well-known method to check the reliability of manufactured components by applying highly stressful operational conditions, called test stresses (such as high voltages, possibly combined with high temperature), which accelerate the aging process of the memory [vdGoor98]. Two different types of tests are done in this stage: those used merely to accelerate the aging process itself, and others used to check for proper functionality under test stresses. Tests performed to stimulate the aging process are simple scan tests or hammer tests (also called disturb tests, where a specific operation is repeated a multiple number of times on the same cell). The pass/fail information provided by these tests are generally neglected since they are not meant to test the actual functionality of the memory operation. The second type of tests is meant to ensure proper memory operation at high stresses. Most notably here are the data retention tests, which inspect the ability of memory cells to keep their data.

Package testing This is the second test insertion of backend testing and the last test insertion in the memory test process, with the main objective of validating the operation of the memory according to the specifications. In this test insertion, a set of memory tests is performed at high as well as at low temperature to ensure proper component functionality. Some tests performed in prefuse testing are repeated here, with a slightly lower level of stress on the memory compared to that applied during prefuse testing (using a so-called stress quard band). If such a test results in a relatively high fail count during package testing, then the corresponding prefuse test is not effective enough, and should be stressed further to identify failing cells during prefuse testing and to try to repair them during fusing.

The test process description above identifies the three necessary components of DRAM and SRAM tests, and the three different requirements a modern memory test should satisfy [see Figure 1.10].

#### • Test components

- 1. Operation sequence: a test should specify a memory operation sequence of writes and reads to be performed in a specific order on memory cells.

- 2. Data pattern (or data background): a test should also specify a pattern of 0s and 1s to be written into and read from accessed memory cells.

- 3. Stresses: a memory test should include a specification of different operational conditions or stresses (such as timing, temperature and voltage) that the test is supposed to be performed at. This component is important to test for proper functionality within the parameter range defined by the specifications. Stresses are also important (sometimes necessary) to increase the coverage of a test without increasing its length.

#### • Test requirements

- 1. Fault detection: a test that fulfills this requirement should result in a fail when applied on a memory that contains the fault. This is a basic requirement of any memory test designed to test for a specific type of faulty behavior.

- 2. Fault localization: a test that fulfills this requirement should be able to identify the specific memory cell (or group of cells) where the fault takes place. This requirement is associated with the need to identify and repair failing cells by fusing in order to increase yield.

- 3. Fault diagnosis: a test that fulfills this requirement should be able to indicate the physical root cause behind the observed faulty behavior. This requirement is associated with the need to give instant feedback to the fabrication process regarding possible fabrication causes of observed faults.

Figure 1.10 gives a summary of the components that DRAM and SRAM tests should have and the requirements these tests should satisfy. The three white blocks in the figure (data background, fault detection and fault localization) indicate those items that DRAM and SRAM tests have in common, while the three shaded blocks (operation sequence, stresses and fault diagnosis) indicate those items where DRAM and SRAM tests are different. In the following, the differences are discussed and the reasons for these differences are given [see summary in Table 1.2].

Figure 1.10. Components and requirements a memory test should satisfy.

**Differences in the operation sequence** SRAMs and DRAMs commonly suffer from different types of memory faults. The reason for this difference is the digital nature of SRAM cells (stored data are either logic 0 or logic 1) and the analog nature of DRAM cells (stored data can take any value within a range of voltages between 0 and 1). This aspect of DRAM operation is discussed in more detail in Chapter 4. The most common types of memory faults observed in SRAMs are the so-called *static faults*, where a fault is sensitized by performing at most one

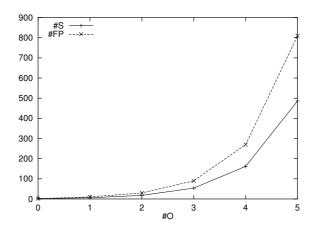

operation on the memory [Hamdioui00]. Therefore, the vast majority of SRAM tests are designed to target these static faults. Since the number of static faults is limited to 12 [see Chapter 4], each of which requires at most one operation for fault sensitization, this means that SRAM tests are rather short, limited in number, which in turn makes it feasible to perform a single test that is theoretically proven to detect all 12 static faults. In contrast, a relatively large portion of DRAM faults are the so-called *dynamic faults*, which are faults sensitized by performing two or more memory operations on the memory [see Chapter 7]. As a result, a large portion of DRAM tests are designed to target these dynamic faults. Since there is an unlimited number of dynamic faults, each of which requires a potentially large number of sensitizing operations, DRAM tests are rather complex and time consuming. Therefore, it is not possible to exhaustively analyze dynamic faults and derive general corresponding tests. The only way to derive DRAM tests is by analyzing the behavior of each DRAM design separately and deriving device-specific tests for each design.

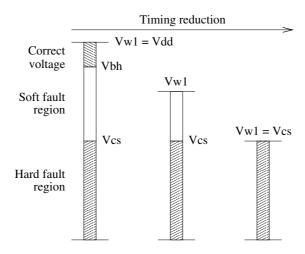

**Differences in stresses** Almost all memory tests designed for any type of memory include some kind of stress specification to perform the test at. For SRAM devices, stresses are most commonly used to inspect for proper functionality of the memory within the parameter range defined by the specifications. As a result, the specifications give a very good indication of the types of stresses and the values to be used for each stress in SRAM tests, even before the chips are manufactured. Small stress modifications are subsequently needed to ensure a specific quality level of the tests, which is not too relaxed nor too stressful. For DRAMs, on the other hand, stresses are needed not only to ensure proper functionality within the specifications, but also to identify the strength of the stored cell voltage and the amount of leakage current in the cell. DRAM cells suffer from leakage currents which gradually degrade any stored cell voltage, and eventually result in the total loss of stored values after a specific amount of time. To test for the ability of the cell to keep its voltage for a long enough amount of time, stresses are used to limit the maximum stored voltage level and to increase the amount of leakage current, so that the tests can identify failing cells in a short amount of time. Unlike SRAM stresses, DRAM stresses have no clear a priori indicators for the types and values to be used in the test. Therefore, an educated guess is attempted at first and, depending on yield feedback, these values are modified iteratively in a slow and costly process until acceptable final values are obtained. This thesis proposes an alternative, more cost-effective approach to optimize stresses, where it is possible to use Spice simulation to get a fairly good initial prediction for the required stresses. The issue of the importance of stresses for DRAMs is discussed in more detail in Chapter 4, while the Spice-based optimization method is discussed in Chapter 5.

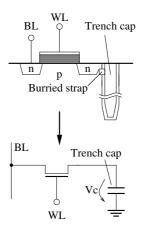

**Differences in fault diagnosis** A faulty fabrication process that systematically results in defective chips is very costly, and therefore feedback from the test process with regard to potential problems in the fabrication process is of prime importance. Therefore, it is common for many memory tests to have some kind of diagnostic capability. Tests designed with diagnostic capabilities are complex, since they should efficiently detect faults caused by a specific failure mechanism, while having minimal coverage of faults caused by other, unrelated failure mechanisms. As a result, the more complex and versatile the total faulty behavior of the memory is, the more complex each diagnostic test for a specific failure mechanism becomes, since a test must also avoid detecting faults resulting from other failure mechanisms. Usually, DRAMs lead the semiconductor industry by using the latest cutting-edge fabrication processes with the newest developments, where newly introduced failure mechanisms should be identified and dealt with. In addition, DRAMs need special, unconventional on-chip structures (such as trench or stack capacitors) that are difficult to manufacture and result in special, unconventional types of faults. SRAMs, on the other hand, are usually manufactured using an established manufacturing process, where the most common failure mechanisms are already known, and they mainly require conventional on-chip structures (transistors), similar to those commonly used for logic devices. As a consequence, DRAM test development is a gradual and slow process, where tests should be developed based on a close observation of the fabrication process, and where each test has a special relation to the fabrication process, to other tests in the test flow, and to the specific memory design being tested. This is a far cry from the world of SRAMs, where devices can be designed as macros and sold in the form of *intellectual property* (IP) structures, without having to care about the specifics of the fabrication process to be used.

# 1.3 Contribution of the project

The research performed in the course of this project has contributed in a number of ways to the development of a new methodology in DRAM testing on an industrial scale [Al-Ars05]. We start this section by identifying the global industrial framework of the contribution, followed by a detailed discussion of each of its aspects.

#### 1.3.1 Framework of the contribution

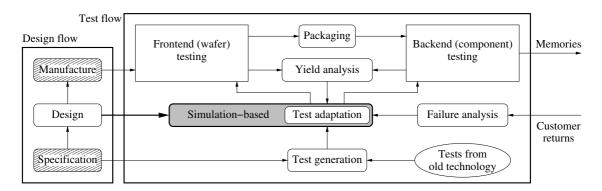

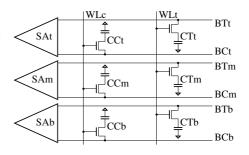

The high cost and complexity of the test process of DRAM devices calls for introducing new innovative ways to tackle the test development problem. As discussed in Section 1.2 and shown in Figure 1.11, the tests performed in the frontend and backend stages of the test flow are traditionally generated in two steps: 1. based on information from the specification stage of the design flow and, 2. based on feedback information from test application after the manufacture stage of the design flow. These two stages, shown shaded in Figure 1.11, are described next.

1. Specification stage—Every test flow for a new memory technology starts

Attribute Difference Cause Consequences Operation DRAMs: long DRAMs: analog cell DRAMs: sequence (possibly infinite) custom-made tests for operation sequences **SRAMs:** mostly each design **SRAMs:** short digital cell operation **SRAMs:** theoretically sequences (one derived tests for all operation) designs Stresses **DRAMs:** necessary to DRAMs: gradual **DRAMs:** needed types test functionality degradation of stored and values of stresses within specifications, voltage level due to are identified using a and to identify strength inherent leakage current time-consuming of voltage level and SRAMs: stored iterative process amount of leakage voltage level is fixed **SRAMs:** needed types current and leakage current is and values of stresses **SRAMs:** mainly compensated for are close to needed to test specifications and are functionality within easier to identify specifications **DRAMs:** necessary for Fault DRAMs: new, **DRAMs:** more diagnosis immediate feedback to unknown technology complex tests with fabrication process usually used and detection, localization SRAMs: not needed difficult structures and diagnosis abilities for a robust fabrication fabricated **SRAMs:** less complex process, minimal **SRAMs:** existing. tests with mainly feedback will suffice tested technology detection and usually used and typical localization abilities transistors fabricated

**Table 1.2.** Differences in the attributes of memory tests used for DRAMs and SRAMs.

with an analysis of the specifications of the new memory and an analysis of the tests used for the previous memory technology [see the block "Tests from old technology" in Figure 1.11. The specifications are used to generate a new set of tests by adapting the old tests to comply with specifications of the new memory [see the block "Test generation"].

2. Manufacture stage—After manufacturing the chips, the specifications-based tests generated by the previous step are applied to the memory in the frontend and backend stages of the test flow. For every new memory technology, the yield analysis stage [see block "Yield analysis"] identifies new, previously unknown, failure mechanisms for which additional (or modified) tests are needed. Furthermore, it is commonplace to have subtle fails that can only be identified after chips fail with the customer, who sends them back to the manufacturer as customer returns, where they get analyzed in the failure analysis stage of the test flow [see block "Failure analysis"]. The feedback from the yield analysis and the failure analysis stages is used to adapt the tests in the test adaptation stage [see block "Test adaptation"], so that a set of tests can

Figure 1.11. Manufacturing test flow, where the contribution of this thesis is shaded.

be attained that is more capable of detecting the previously unknown types of faulty behavior.

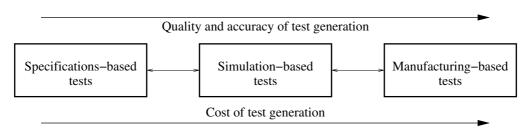

Therefore, a test set is developed in two steps: first using information from the specification stage and then adapting it based on information from the manufacture stage of the design flow. Each one of these two steps in test generation has advantages and disadvantages in terms of quality and cost, as shown in Figure 1.12.

Figure 1.12. Cost-quality tradeoff of test generation.

**Specifications-based test development** Tests generated based on the specifications of the memory have a relatively low cost since they can be derived analytically by adapting already known tests of previous memory designs. This style of test generation assumes that the faulty behavior of the memory does not change with changes in memory design and technology. This assumption might be valid for generic types of failure mechanisms, but for every new memory technology there are always some types of failure mechanisms that are specific to the memory under analysis. Therefore, specifications-based test generation, though relatively cheap, is not memory-specific enough to derive accurate tests for the memory under analysis.

**Manufacturing-based test development** Tests generated based on feedback from the manufacturing process are very accurate in describing the faulty behavior

of the memory under analysis, since the tests are generated by statistically analyzing feedback data from the manufacturing facility (fab) as tests are performed on real memory chips. This style of test generation assumes that there is a large volume of failing memory parts to enable a meaningful statistical analysis such that reliable tests can be derived. This assumption requires a rather expensive and time-consuming test adaptation loop of test application, yield analysis and test adaptation until a stable and a reliable set of tests can be generated. In Figure 1.11, two test adaptation loops are shown: 1. Frontend  $\rightarrow$  Yield analysis  $\rightarrow$  Test adaptation, and 2. Backend  $\rightarrow$  Yield analysis  $\rightarrow$  Test adaptation. If such expensive test adaptation loops are not properly implemented, the memory manufacturer runs the risk of delivering defective parts to the customer, which will most probably be sent back to the manufacturer in the form of defective customer returns, a situation that is bound to reduce customer satisfaction levels with the product. In conclusion, manufacture-based testing, though accurate and memory specific, has a high price tag associated with it, making it an expensive alternative for test generation.

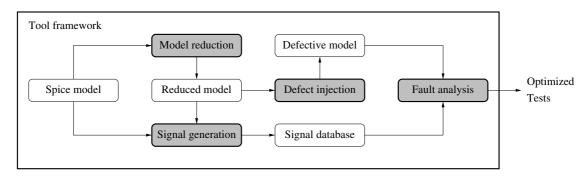

Thesis contribution: simulation-based test development This thesis proposes a simulation-based test generation approach, which strikes a tradeoff between specifications and manufacturing-based test generation, and provides an alternative that is both moderately cheap as well as device specific. As shown in the shaded "Simulation-based" block of Figure 1.11, simulation-based test generation uses information from the design stage of the design flow, where an electrical Spice model of the memory is generated to evaluate the expected memory behavior. The Spice model of the memory represents its internal design and behavior, in addition to an electrical description of the fabrication process to be used to manufacture the memory. This provides a fairly accurate representation of the specific behavior of the memory under analysis. At the same time, simulations can be directly related to a specific failure mechanism and, therefore, they can greatly accelerate the expensive and time-consuming feedback loop needed by manufacturing-based test generation. Furthermore, simulation-based test generation provides the following added advantages:

- It increases our understanding of the internal faulty behavior of the memory.

- It supports test adaptation activities after yield analysis of fab tests.

- It supports failure analysis activities for customer returns.

- It enables early identification of design bugs before tape out, which is the design stage where the design data is stored on tape and transported to the fab.

#### 1.3.2 Details of the contribution

In order to materialize the vision of simulation-based test development for DRAMs, a number of theoretical (scientific) as well as practical (industrial) hurdles have been tackled and solved in this thesis. It is worth noting here that this vision has been exclusively and completely carried out within the framework of this project, since there is no previously published work on employing electrical simulation for DRAM test development. First, the scientific contributions are listed, followed by the industrial contributions.

### Scientific contributions

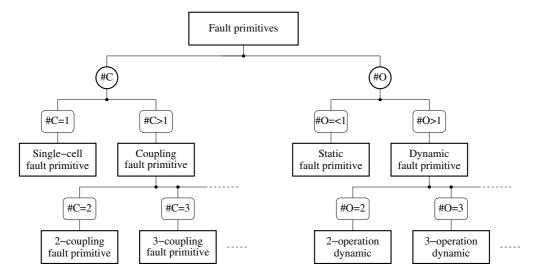

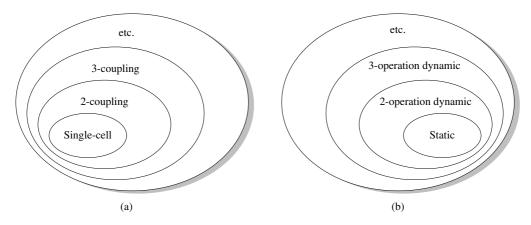

- The definition of a general space of memory faults in combination with a taxonomy that describes any possible faulty behavior exhibited by the memory [Al-Ars99, Al-Ars00, Al-Ars01a, Al-Ars03a, vdGoor00]. This general space is treated in Chapter 4.

- The identification of the specific fault classes needed to describe the faulty behavior of DRAMs, such that the rather complex general space of memory faults is reduced to a smaller, manageable size [Al-Ars01b, Al-Ars02a, Al-Ars04a]. These DRAM-specific fault classes are treated in Chapter 4.

- The inclusion of stresses (voltage, timing and temperature) as a theoretically fundamental part of memory testing, and devising a language to model it [Al-Ars01c, Al-Ars01d].

- The analysis of interactions between different memory faults in a way that may limit the ability of memory tests to detect them [Al-Ars04c, Hamdioui03b, Hamdioui04b].

- The theoretical derivation of a number of memory tests to effectively test special types of faulty behavior [Hamdioui02, Hamdioui03a, Hamdioui04c, vdGoor04a, vdGoor04b].

### Industrial contributions

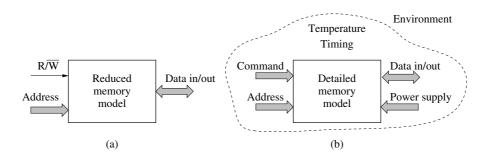

- Solving the problem of the long simulation time needed to simulate the faulty behavior of the memory by introducing the concept of a reduced memory model [Al-Ars01e]. This issue is treated in Chapter 7.

- Introducing simulation-based fault analysis methods to properly interpret the faulty behavior in the simulation results and to correctly map them into memory faults [Al-Ars02b, Al-Ars02c, Al-Ars03d, Al-Ars05]. This issue is treated in Chapter 5.

- Proposing a simulation-based stress optimization method to use circuit simulation to identify the most optimal stresses for a given defect [Al-Ars03c, Al-Ars03b].

- Dealing with simulation model inaccuracy and the issue of variations in the manufacturing process to ensure a high-quality fault analysis approach [Al-Ars02d, Al-Ars02e, Al-Ars03e].

- Evaluating the influence of parasitic capacitances in the simulation model, and analyzing the effect of bit line coupling on the simulated faulty behavior for a given defect [Al-Ars04b, Al-Ars04c].

#### 1.4 Outline of the thesis

This thesis is organized in 10 chapters of continuous material that gradually builds on the information presented as the thesis progresses. Unless one has previous knowledge of the presented topics, progression from chapter to chapter is important to gain the necessary understanding of the whole thesis.

Chapter 1 introduces the field of semiconductor memory devices, where a short description is given of a number of different types of semiconductor memories. The issue of manufacturing test development is discussed with some detail, in order to identify the position of this project in the big picture of industrial test development.

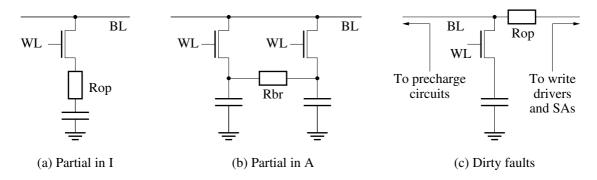

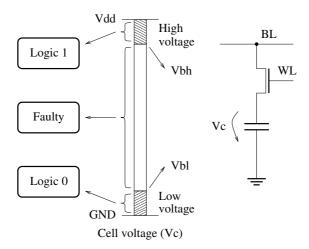

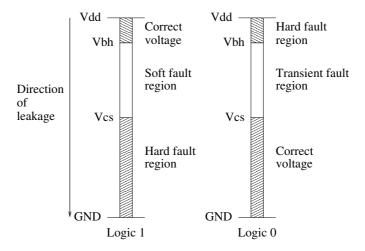

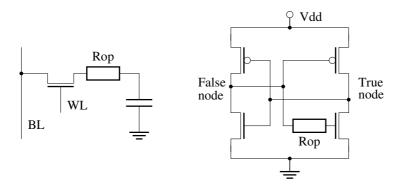

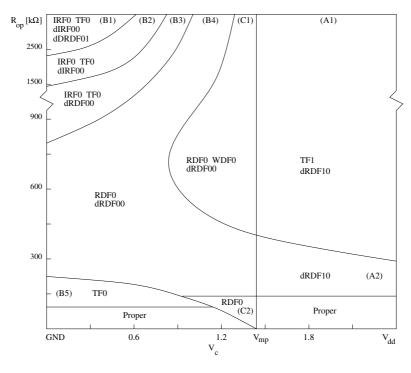

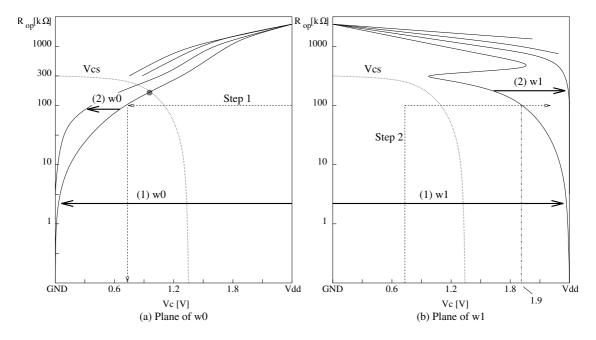

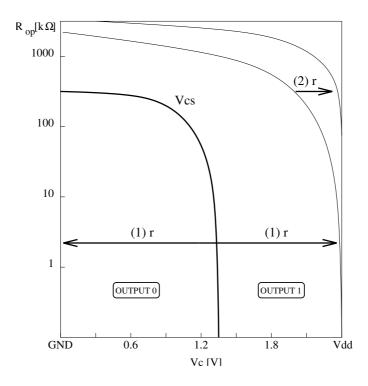

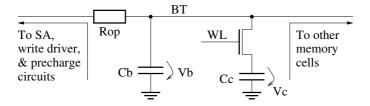

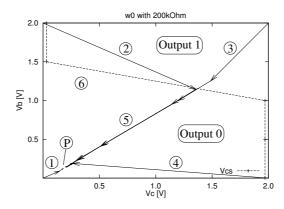

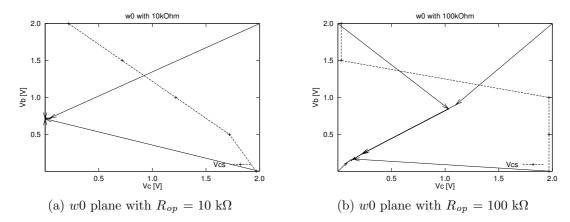

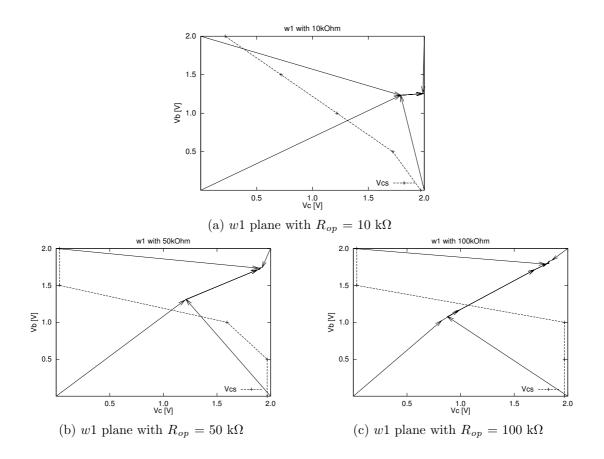

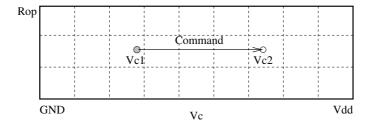

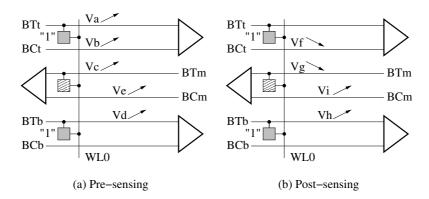

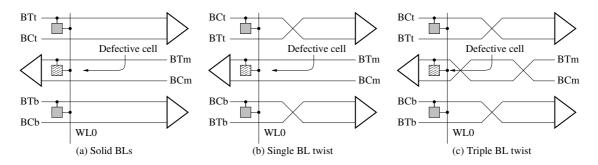

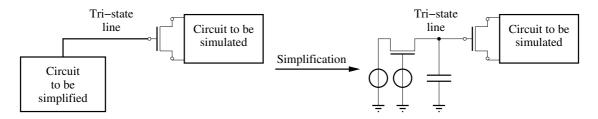

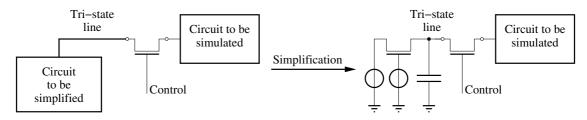

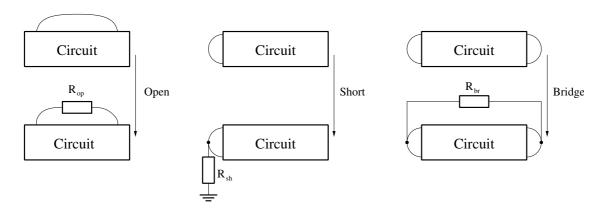

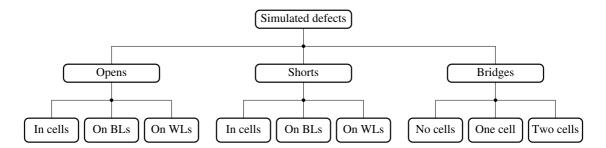

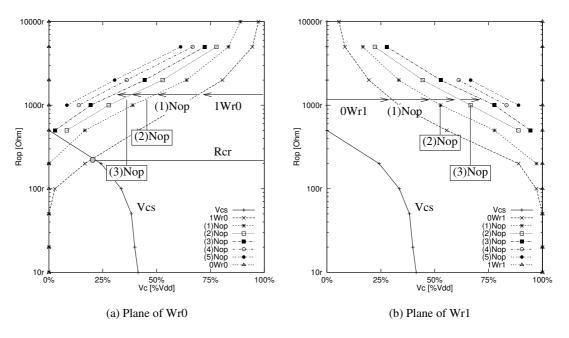

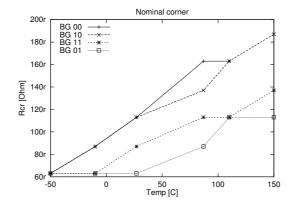

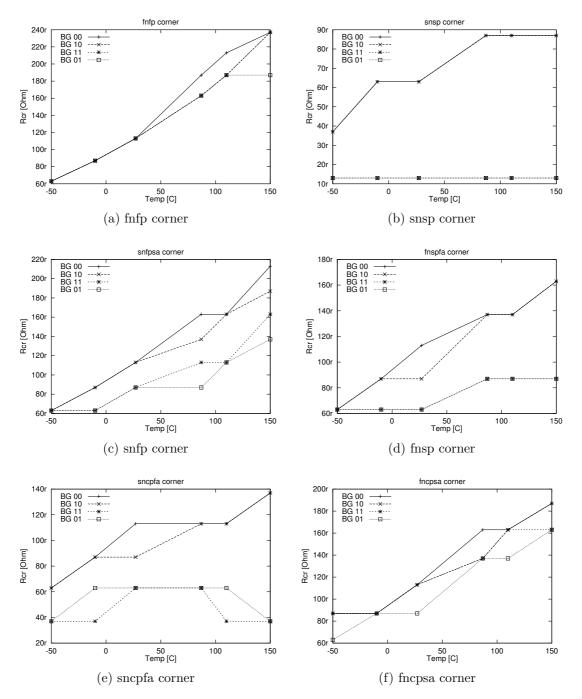

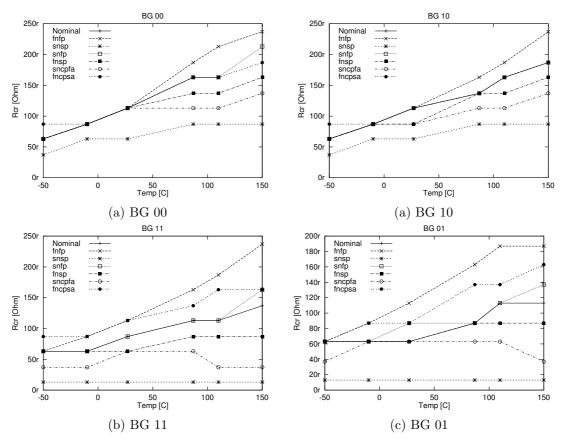

Chapter 2 gives a detailed discussion of the external behavior of DRAMs, represented by timing diagrams, as well as a description of the internal functional units a typical DRAM contains.