Circuits and Systems Mekelweg 4, 2628 CD Delft The Netherlands http://ens.ewi.tudelft.nl/

## M.Sc. Thesis

### Desynchronization Methods for Scheduled Circuits

Michael Simmonds B.ASc.

#### Abstract

Synchronous systems waste a lot of power in the clock tree, and must be designed based on the worst case scenario in terms of speed. Asynchronous circuits offer relief to these problems, by replacing clock signals with handshakes which only charge when data is being transferred, and delay signals which may adapt more easily to variance in speed compared to the clock period. Desynchronization is the process of turning a synchronous circuit into an asynchronous one. Scheduled circuits are a common way to provide a good compromise between conserving area of a circuit and increasing its speed. Desynchronizing such a system is made difficult because every functional unit in the circuit must respond to controls from the central state machine, which cannot easily handshake with all of them. This report demonstrates two related methods designed specifically for the conversion of a synchronous, scheduled circuit into an asynchronous, delay insensitive circuit. Decomposition of the central state machine into local, smaller ones is used to combat the problem of skew in the control signals, as well as to speed up the performance of the asynchronous circuit. The slack in the clock period can also be used for possible speedup. Conditions which threaten deadlock of the circuit are identified and rescheduling solutions are proposed. A tradeoff between the two methods of area conservation and hardware reusability versus speed is also explained.

THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

$\mathrm{in}$

Computer Engineering

by

Michael Simmonds B.ASc. born in North York, Canada

This work was performed in:

Circuits and Systems Group Department of Microelectronics & Computer Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

#### Delft University of Technology

Copyright © 2009 Circuits and Systems Group All rights reserved.

#### Delft University of Technology Department of Microelectronics & Computer Engineering

The undersigned hereby certify that they have read and recommend to the Faculty of Electrical Engineering, Mathematics and Computer Science for acceptance a thesis entitled "Desynchronization Methods for Scheduled Circuits" by Michael Simmonds B.ASc. in partial fulfillment of the requirements for the degree of Master of Science.

Dated: November 10th, 2009

Chairman:

prof.dr.ir. Alle-Jan van der Veen

Advisor:

dr.ir. Rene van Leuken

Committee Members:

dr. Ben Juurlink

dr.ir. Nick van der Meijs

## Abstract

Synchronous systems waste a lot of power in the clock tree, and must be designed based on the worst case scenario in terms of speed. Asynchronous circuits offer relief to these problems, by replacing clock signals with handshakes which only charge when data is being transferred, and delay signals which may adapt more easily to variance in speed compared to the clock period. Desynchronization is the process of turning a synchronous circuit into an asynchronous one. Scheduled circuits are a common way to provide a good compromise between conserving area of a circuit and increasing its speed. Desynchronizing such a system is made difficult because every functional unit in the circuit must respond to controls from the central state machine, which cannot easily handshake with all of them. This report demonstrates two related methods designed specifically for the conversion of a synchronous, scheduled circuit into an asynchronous, delay insensitive circuit. Decomposition of the central state machine into local, smaller ones is used to combat the problem of skew in the control signals, as well as to speed up the performance of the asynchronous circuit. The slack in the clock period can also be used for possible speedup. Conditions which threaten deadlock of the circuit are identified and rescheduling solutions are proposed. A tradeoff between the two methods of area conservation and hardware reusability versus speed is also explained.

## Acknowledgments

I would like to acknowledge my family, my girlfriend, and all of my friends for their support throughout the entire duration of my studies. Knowing I can count on them, and that they are counting on me is what keeps me going.

I would like to thank Alexander de Graaf, Huib Lincklaen Arriens, Tao Xu, and most of all my advisor Rene van Leuken, for their assistance and guidance during the formulation of the ideas that went into this thesis, their implementation and testing, and the writing of this report.

Michael Simmonds B.ASc. Delft, The Netherlands November 10th, 2009

# Contents

| A        | bstra | nct                                                             | v        |

|----------|-------|-----------------------------------------------------------------|----------|

| A        | ckno  | wledgments                                                      | vii      |

| 1        | Intr  | roduction                                                       | 1        |

|          | 1.1   | Motivation                                                      | 1        |

|          | 1.2   | Goals                                                           | 2        |

|          | 1.3   | Results                                                         | 3        |

|          | 1.4   | Thesis Outline                                                  | 3        |

| <b>2</b> | Bac   | kground                                                         | <b>5</b> |

|          | 2.1   | Synchronous Circuits                                            | 5        |

|          | 2.2   | Asynchronous Circuits                                           | 6        |

|          | 2.3   | A Method for Desynchronization                                  | 9        |

|          | 2.4   | Finite State Machines                                           | 12       |

|          | 2.5   | Asynchronous State Machines                                     | 12       |

|          | 2.6   | Scheduled Synchronous Filters                                   | 13       |

|          | 2.7   | Scheduled Asynchronous Circuits                                 | 16       |

| 3        | Exp   | periments                                                       | 17       |

|          | 3.1   | Desynchronization Tests                                         | 17       |

|          | 3.2   | Pipefitter Tests                                                | 17       |

|          | 3.3   | Summary                                                         | 20       |

| 4        | Des   | ynchronization Concepts and Solutions                           | 21       |

|          | 4.1   | Inefficiencies in a Scheduled Synchronous Circuit               | 21       |

|          | 4.2   | Desyncronization and Decentralization of a Finite State Machine | 22       |

|          | 4.3   | Modifications to the Latch Controller                           | 23       |

|          | 4.4   | Delay Elements and Bypassing                                    | 25       |

|          | 4.5   | Input Multiplexing Options                                      | 26       |

|          | 4.6   | Hazards, Deadlock, and Redesigning the Circuit to Avoid Them    | 27       |

|          | 4.7   | Separated Latch Pair Controller FSM Solution                    | 29       |

|          |       | 4.7.1 State Encodings                                           | 29       |

|          |       | 4.7.2 States and State Templates                                | 30       |

|          |       | 4.7.3 Connections and Communication Between Computational Units | 33       |

|          | 4.8   | Greater Handshakes and Dependency Between Computational Units   | 34       |

|          | 4.9   | Combined FSM Solution                                           | 35       |

|          |       | 4.9.1 Handshaking State Clusters                                | 36       |

|          |       | 4.9.2 State Encoding                                            | 37       |

|          |       | 4.9.3 Separating Greater Handshakes                             | 39       |

|          |       | 4.9.4 Further Expansion                                         | 39       |

| <b>5</b> | Imp | lementation of the Desynchronized Circuits                             | 41 |

|----------|-----|------------------------------------------------------------------------|----|

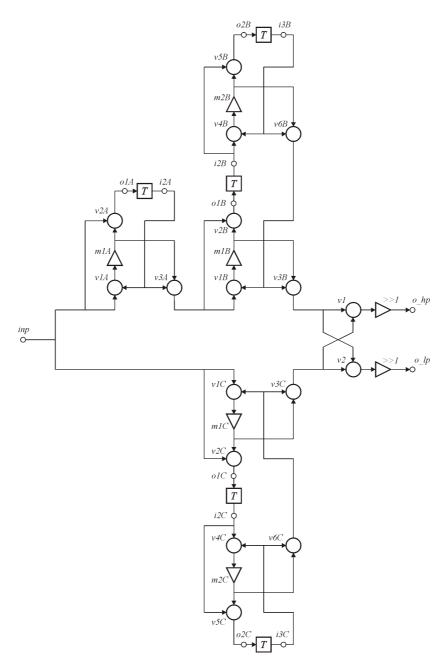

|          | 5.1 | Filter Specifics of Original Synchronous Implementation                | 41 |

|          | 5.2 | Two State Machine Implementation                                       | 44 |

|          | 5.3 | Process Overview for Desynchronizing and Decentralizing a Filter Using |    |

|          |     | the Dual State Machine Method                                          | 45 |

|          | 5.4 | The Combined State Machine Implementation                              | 46 |

|          | 5.5 | Process Overview for Desynchronizing and Decentralizing a Filter Using |    |

|          |     | the Combined State Machine Method                                      | 48 |

| 6        | Con | clusions                                                               | 51 |

|          | 6.1 | Simulations and Results                                                | 51 |

|          | 6.2 | Factors Affecting System Performance                                   | 53 |

|          | 6.3 | Impacts on Area Overhead, Power Usage, and Delay Variability           | 54 |

|          | 6.4 | Recommendations for Future Work                                        | 54 |

|          | 6.5 | Closing Remarks                                                        | 55 |

| A        | Mo  | re State Cluster Diagrams                                              | 57 |

| в        | Cod | le Samples                                                             | 63 |

|          | B.1 | Separated Latch Controller Implementation Code                         | 63 |

|          |     | B.1.1 The Latch Pair Controller State Machine                          | 63 |

|          |     | B.1.2 A Sample Instruction State Machine                               | 64 |

|          | B.2 | Combined FSM Implementation Code                                       | 67 |

|          |     | B.2.1 The Latch Pair Controller State Machine                          | 68 |

| С        | Way | veforms for Working Implementations                                    | 73 |

| $2.1 \\ 2.2 \\ 2.3 \\ 2.4 \\ 2.5 \\ 2.6 \\ 2.7$                             | Four Phase Handshaking                                                                                         | 8<br>10<br>10<br>11<br>13<br>13<br>15                                                        |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                      | Design of the Pipeline Circuit Before Desynchronization Design of the Pipeline Circuit After Desynchronization | 18<br>18<br>18<br>18<br>19<br>19                                                             |

| $\begin{array}{c} 4.11 \\ 4.12 \\ 4.13 \\ 4.14 \\ 4.15 \\ 4.16 \end{array}$ | A Sample Scheduled Synchronous System                                                                          | 23<br>24<br>25<br>26<br>28<br>29<br>30<br>31<br>31<br>32<br>32<br>33<br>35<br>36<br>37<br>38 |

| $5.1 \\ 5.2 \\ 5.3$                                                         | Circuit Diagram of the Synchronous Filter                                                                      | 43<br>47<br>48                                                                               |

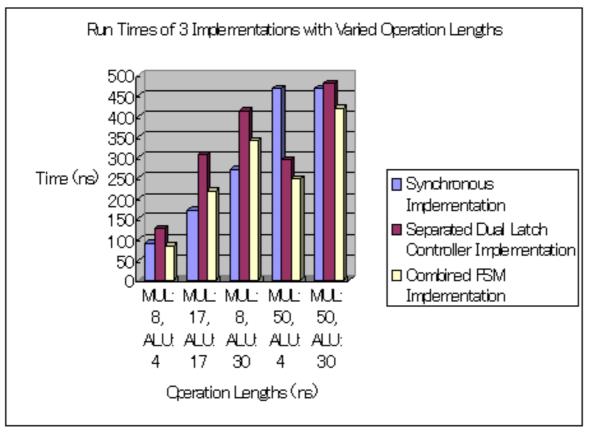

| 6.1                                                                         | Comparison of Speeds in the 3 Implementations                                                                  | 52                                                                                           |

| A.1<br>A.2                                                                  | A Standard 1-Input 1-Output State Cluster                                                                      | 57<br>58                                                                                     |

| A.3 | A Modified 1-Input 1-Output State Cluster                            | 58 |

|-----|----------------------------------------------------------------------|----|

| A.4 | A Modified 0-Input 2-Output State Cluster                            | 59 |

| A.5 | A Modified 2-Input 0-Output State Cluster                            | 60 |

| A.6 | A Modified 1-Input 2-Output State Cluster                            | 61 |

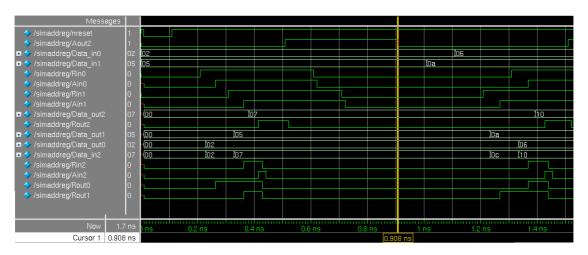

| C.1 | The Results of Running the Synchronous Implementation                | 73 |

| C.2 | The Results of Running the Separated Latch Pair Controller Implemen- |    |

|     | tation                                                               | 74 |

| C.3 | The Results of Running the Combined FSM Implementation               | 75 |

# List of Tables

| 2.1 | Muller C Element Truth Table                                      | 8  |

|-----|-------------------------------------------------------------------|----|

| 4.1 | Details of the Separated Latch Controller Solution                | 34 |

| 4.2 | Details of the Merged FSM Solution                                | 40 |

| 5.1 | Register States in the Synchronous Filter                         | 41 |

| 5.2 | ALU States in the Synchronous Filter                              | 42 |

| 5.3 | MUL States in the Synchronous Filter                              | 42 |

| 5.4 | Register States in the Two State Machine Asynchronous Filter      | 44 |

| 5.5 | ALU States in the Two State Machine Asynchronous Filter           | 45 |

| 5.6 | MUL States in the Two State Machine Asynchronous Filter           | 45 |

| 5.7 | Register States in the Combined State Machine Asynchronous Filter | 48 |

| 5.8 | ALU States in the Combined State Machine Asynchronous Filter      | 49 |

| 5.9 | MUL States in the Combined State Machine Asynchronous Filter      | 49 |

| 6.1 | Execution Times in the Three Implementations (ns)                 | 51 |

|     |                                                                   |    |

# 1

#### 1.1 Motivation

Transistor sizes continue to shrink, and engineers continue to search for new ways in which these exponential gains can be effectively used to increase computing power and decrease strain on the world's resources. Processing power is also so inexpensive that its use is being considered in all aspects of technology, society, and life. Engineers must look for new and better embedded solutions to meet the demands of the modern age, and sometimes must look outside of widely used and accepted digital hardware design methods.

Traditionally processor and digital electronic design is done in a synchronous fashion, using a clock signal which ideally rises and falls identically to every component and gives the circuit a sense of time. In general, this makes the design easier, but it has several drawbacks. Since a large portion of the circuit is occupied by wires carrying this falling and rising clock signal, and in most cycles most components are not changing, there is a lot of power used to drive these lines which is constantly wasted, often over 50 percent of the total power used in the circuit. In addition, the clock can only be as fast as the slowest register-to-register path in the circuit, which is a design constraint forcing engineers to make the gate delay of each component as similar in delay as possible, and limiting design possibilities. This also restricts the circuit from taking advantage of delay variability, that is, the phenomenon of the circuit's speed being dependent on operating conditions such as temperature. Circuits are also affected by clock skew, as in increasingly denser circuits it can take different amounts of time for the signal to propagate in different directions in a non-symmetrical circuit. In synchronous design processes, a great deal of effort is expended in ensuring the longest path is shorter than the clock period.

In traditional asynchronous design however, the entire synchronous circuit must be designed in a much more complicated process, which slows down time to market and makes new circuits incompatible with and unable to use most of the digital components designed up until now, since they employ clock signals. In this way we have to redesign all components that we want to use in an asynchronous circuit, and therefore lose backwards compatibility, as well as the ability to use experience in current design methods on future designs. Even so, its advantages are numerous and compelling enough that it has been used to create several processors [13].

Various efforts are being made to make asynchronous design more feasible for digital component design in both the academic and commercial sectors. There are increasingly more tools to aid in the design of asynchronous circuits[6, 3], but this pales in comparison to the amount of tools there are available for the design of synchronous systems. If there was an algorithm to systematically convert current and future synchronous designs to asynchronous designs, it could be a very attractive compromise with many benefits of both synchronous and asynchronous systems. The only real synchronous part of the synchronous circuit is the clock signal, so this means somehow the clock must be removed and communication between registers must be instead done in an asynchronous manner.

There are several methods for turning a synchronous circuit into an asynchronous one, using handshaking to replace the functions that originally are handled by the clock signal. For a pipelined circuit, these implementations are fairly straightforward, because all of the components have the same connections and perform the same tasks at any given step in the circuit.

If these methods are extended to circuits controlled with a central FSM, however, things are somewhat more difficult. There is one centralized control register which all the components read at every state. This means that if we are to guarantee the absence of skew in the control signals, all of the components must handshake with the state register or signals derived from it at each step. In a scheduled circuit, which uses an FSM as its control path, the structure is also much more complicated than a simple pipeline, and differs for each implementation. There should be a faster and more structured way to pass data between components than simply implementing handshaking for transfering data.

#### 1.2 Goals

- To find a method to convert a synchronous scheduled circuit to an asynchronous one with equivalent functionality and producing the same results

- This method should be systematic, repeatable, and suitable for future automation

- Determine if there are scheduling conditions which prevent this method from working, what they are, and how to get around them

- Execute this method on a simple scheduled filter, and demonstrate its results are equivalent to those in the original implementation using simulations

- Keep the circuit speed high, increase it if possible

- Circuit should be delay invariant to insure stability

- Determine the conditions for which this method is best suited and worst suited

Although part of the motivation for this project is minimizing power and taking advantage or delay variability, these are not the goals of this project. The project focuses on the development of a method to first desynchronize the system instead.

The method should be systematic and repeatable so that it can be used in further research and automation of the production of similar asynchronous circuits.

If there are conditions in the schedule which cause this method to produce incorrect results, they must be identified, as well as the reasons for their happening. If possible, solutions to fix these problems should be found and described in detail. In the same manner, conditions which adversely affect the performance of the circuit should be outlined and discussed.

#### 1.3 Results

- Two related methods which desynchronize such a circuit by decomposing the central FSM into local, smaller FSMs which communicate with each other to advance state and send data

- Clock and clock enable signals are replaced by a network of handshaking controllers

- Three separate scheduling hazards have been identified which cause deadlock in the system

- Rescheduling solutions to fix these hazards have also been identified

- Sample implementations have been performed using each method, with successful simulations

- Asynchronous circuits found to be faster than the synchronous implementation in certain cases

- Scheduling is a big factor in determining circuit speed in the desynchronized circuits, corrections meant to avoid hazards are especially slow

- Speed is also affected by the difference in the length of operations, frequency of operations, number of inputs and outputs, and size of the circuit

The first of the two methods uses less area, has more logic that is used without custom design, and takes less work to implement, but is much slower and more susceptible to hazards than the second method. The first was conceived more directly from Cortadella's desynchronization method, and the second created in order to deal with some weaknesses in the first design method.

Scheduling based on synchronous circuits prevents the desynchronization methods from reaching their full potential. This scheduling creates hazards, and can limit the concurrency obtained from an asynchronous implementation.

#### 1.4 Thesis Outline

The the following chapter will give a thorough background on all of the concepts used in this report which derive from the work of others, and explain how they relate to the project. If the reader is unfamiliar with any of the terms discussed in the introduction, they will all be thoroughly explained.

The third chapter is about two short experiments which were done on previously developed methods for desynchronization, the first manual, and the second method automated.

The fourth chapter focuses on the theory behind the solutions for desynchronization and the concepts developed in during this project.

The fifth chapter goes into detail about the implementations of the two different methods on the same synchronous circuit, how these implementations are different from each other and the synchronous circuit, and deviations from the theory in the fourth chapter.

The sixth and final chapter explains the results of the simulations and the conclusions derived thereof. The previous chapter provided a reasoning for the undertaking of this thesis, the goals set and results obtained, as well as an overview of the entire report.

The chapter will explain the following concepts:

- Synchronous circuits, clock signals, latches, registers, clock skew, and timing closure

- Asynchronous circuits, handshaking, Muller elements, Muller pipelines, and delay sensitivity

- Finite state machines and state variables

- Asynchronous finite state machines, bundled inputs, and the Aghdasi style state machine

- Scheduled circuits, scheduling, scheduling algorithms with and without constraints

- Scheduling for asynchronous circuits

#### 2.1 Synchronous Circuits

The following section will explain some background about synchronous circuits, concepts, and design methodology. Synchronous circuits are the industry standard in digital circuit design. They use a special signal global to all components called the *clock signal*, which is used to synchronize all components in the circuit. This ensures that the data in the system is valid and that the different parts of the circuit receive the correct control signals at the same time. The clock signal has a cycle in which it charges and discharges and usually the components in the circuit are activated on the *rising edge*, which the clock signal charges from a logical 0 to a logical 1 although sometimes this happens on the *falling edge* instead, when the signal discharges, changing its logical value from 1 to 0.

A *latch* is a hardware component used to be sometimes *transparent*, having the output match the input, sometimes *opaque*, where output stays at its previous value. When the input cannot affect the output, the value stored in the latch is said to be *latched* or *clocked*. *D-Latches* have two inputs, a clock signal and a data signal. These latches are designed so that the output is held when the clock signal is low, and changed to match the data signal when the clock is high.

In order to store data temporarily, until the following clock cycle, synchronous circuits use a hardware component known as a *register* or *flipflop*. A flipflop is composed of two D-latches back to back with the second clock signal inverted, a fact which is

used to an advantage later in this project. This ensures that the two latches will be transparent and opaque at complementary times. If the clock cycle is first high and then low, the input will be first transmitted to the output of the first latch when the first output has a high clock. Then the clocked output of the first latch will be will then become transparent through the second latch, and by the next rising edge will be clocked in.

This means that the flipflop is made to only allow the input which is to be stored in for a very short time, ideally as short as possible. This time is simultaneous with the rising or falling edge of the clock signal. While the electrical signals are propagating through the circuit, the input should be kept constant. When it has finished propagating and the circuit is stable, the next input can be clocked in and the process begun anew. This is how all of the circuit's parts can keep their data synchronized and valid. If not for using registers and a clock signal, design becomes much harder, because the designer must ensure the data is valid at any point in the system.

There are however, some resulting disadvantages to the synchronous approach to circuit design. These are mostly due to speed, power, and distribution.

The clock is calibrated for the longest possible delay path between any two latches in the system. All of the other paths in the system are not being traversed as quickly as is possible, and parts of the circuit are held up for extra amounts of time. Compared to the ideal solution, they are being used for some amount of extra time during which they could be used for another operation, or finished early. Any operations which are dependent on the output of a previous operation must stall until the end of the clock cycle, if all of their data is ready.

Having a universally distributed clock signal means that there is a lot of activity in the circuit. The clock must be charged and discharged at every component at every cycle. This requires a lot of unneeded power because some of the components are not actually in use at any given time.

A global clock can also cause *skew* in the circuit, which is the difference between arrival times of the clock signal to different components. This can affect the timing, and make it very difficult to ensure circuit data is valid in every situation.

Setup time is the name for the amount of time a value must stay at the desired value before a clock edge, and *hold time* is the amount of time it must stay at the required value after the edge. *Timing closure* is the term given to the state of a synchronous circuit where the delay in all paths added to the setup and hold times is less than the clock period. This takes a great deal of design effort, and is absolutely critical for the circuit to work correctly.

#### 2.2 Asynchronous Circuits

This section will go over some of the basics of asynchronous circuits. Asynchronous circuits are those which do not use a clock signal to synchronize their components. This means that the delay between a change in the input and the subsequent delay of the change in the output of the system is dependent only on the intrinsic logic delay of the circuit. This means that in general, an asynchronous system will be faster than a synchronous system because fast components are not waiting for the end of the clock

period to continue with their execution. Since a clock signal which runs through the entire circuit is not being charged and discharged at every cycle, there is also usually a large reduction in power. The downside of asynchronous circuits is that stability can arise in asynchronous circuits that are not designed properly and this can be simply solved with a clock signal. This makes the design more difficult and tedious. Also, designers are more used to the problems and design process of synchronous systems because they are the standard. Problems and design of asynchronous systems are less well explored.

Asynchronous circuits can be divided into different classes based on their sensitivity to delay. Speed independent circuits are those which will always function correctly regardless of timing. These are therefore the most robust and ideal, but their design is often very difficult, because for any input or bit that can change, the entire circuit must always be valid. Delay insensitive circuits are those which operate correctly due to delays that are bounded and greater than zero. These circuits are likewise extremely robust, because the delays keep data in the circuit from becoming invalid. Delay sensitive circuits are those which do not fall under either of these two categories. They must receive the correct inputs at the right times, or their data will become invalid. For this reason, they are not very robust, but they are usually the easiest to design and implement [14].

Handshaking is a method by which components with different timings, whether synchronous or asynchronous, can communicate with each other. The component sending data is known as the *master* and the one receiving data is the *slave*. The data which is communicated in this way is called *bundled-data* because it is sent and received in all data wires simultaneously. Two lines in addition to the data lines are used for the handshaking protocol, one controlled by the master called the *request* showing that it wants to send data. The other line is controlled by the slave and called the *acknowledgement*, showing that it has received data. There are two major methods of handshaking: *two phase* and *four phase*.

Two phased handshaking consists, as is implied of two phases. The first is the transmission of the request and the second is the transmission of the acknowledgement. Because there are only two phases, the lines alternate between going from 0 to 1 and from 1 to 0 in every other handshake. This method is faster, but since the master does not wait for the slave to receive data, problems can arise in the circuit if timings are not handled carefully.

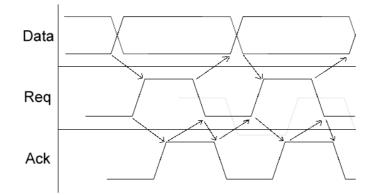

Four phased handshaking is more commonly used, and likewise composed of four phases. The request and acknowledgement lines are both initialized to 0. When data is ready to be passed the first component sets the request line high, which is the first phase. Then when data is received, the acknowledgement line goes high, which is the second phase. When the first component sees this, it discontinues its request, that is the third phase. When the second component sees that, it likewise discontinues its acknowledgement in the fourth and final phase. This is illustrated in Figure 2.1[14].

The *muller* C *element* is a piece of hardware used extensively in asynchronous circuits. A Muller C element holds the value of its output, until all inputs are the same value, at which point the output becomes that value, as seen in Table 2.1. Using a Muller C element, handshakes with more than one input or output can be performed,

Figure 2.1: Four Phase Handshaking

because the element will wait until all handshaking components are ready for the next phase of the handshake. It can also be used in another way, to create dual rail asynchronous circuits. Since the output will wait until both inputs have changed to make a change, the system can be made stable until all data is valid[14].

| А | В | Y | У |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Table 2.1: Muller C Element Truth Table

A *Muller pipeline* is a way to create an asynchronous pipeline of data using Muller C elements as a memory component. Data is passed to the next element of the pipeline using handshaking. The request of the previous element is put into a C element with the inverse of the acknowledgement from the next component, which means that the previous component has data ready and the next component is free. The output of the Muller C is then used as the request to the next component and acknowledgement back to the previous component. This frees the previous element and prepares the next element to accept the handshake, and in this way, the control signals are passed along the pipeline.

An asynchronous circuit's sensitivity to delay, handshaking, and Muller C elements and pipelines are concepts that are all used extensively in this project.

#### 2.3 A Method for Desynchronization

This section will discuss methods of conversion from a synchronous circuit to an asynchronus one, and discuss in detail the method that is the inspiration for this project.

*Desynchronization* is the process of eliminating the clock of a synchronous circuit, and in so doing making it asynchronous. In order to make this conversion there are two principle implementations: *dual rail*, *bundled data*.

Dual rail systems use a *dual rail Muller pipeline*. Throughout the design, all of the signals in the design are implemented using two lines where there would be only one in an equivalent synchronous system. One of these lines signifies true, and the other signifies false. If both lines are zero, the data is invalid. If the true line is 1, then this is the equivalent of a logical one, and if the false line is 1, this is equivalent of a logical 0. Both lines being set to true is an error that should not occur. Every operation is performed on both signals, and is equivalent to something in the synchronous implementation. For instance, an OR gate will produce a 1 in the false line if the false signals of both two rail inputs are 1, and does this with a Muller C element. An or gate is used to test if the signal is valid, in order to send an acknowledgement, which similar to in a Muller pipeline, allows the transmission of new data into the pipeline stage. There is no request line but valid data in the two rails is the equivalent of having an active request and invalid data is the equivalent of having an inactive request. Effectively, this combines the control and data of the implementation. It takes a lot of time to redesign all of the components and it takes up a lot of area since the wires and logic have effectively doubled, but to its credit it is speed independent and does not require delay elements.

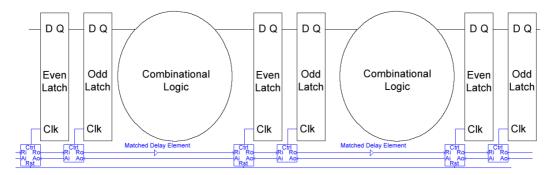

Bundled data implementations separate the data from the control lines. The data is passed through the pipeline through latches, which are controlled by a Muller pipeline. This is the basic version of the Muller pipeline, with two small additions. The output of the C element in every pipeline stage is also used as the clock input to a latch, which means that when a pipeline stage is "active", the latch is transparent. This allows data to be transmitted as the handshake moves through the pipeline. Also, a delay element must be used to match the combinational logic delay in the datapath between two latches [8]. This ensures the data is valid when it reaches the latch and classifies this circuit as delay insensitive. This delay element is difficult to implement, but this type of circuit is much more easily converted from a synchronous implementation and takes less area than the dual rail implementation.

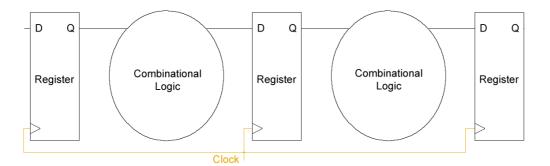

The method used in this paper to desynchronize the circuit was devised by Cortadella et al.[5, 4, 2], and its results can be seen from comparing Figure 2.2 and Figure 2.3. One goal of this method is to minimise the amount of design effort in the desynchronization process. It is similar to the bundled data method, but it does not use C elements in the pipeline stages. The main advantage over the Muller pipeline is that the circuit has an asynchronous reset signal. Since the datapath logic is left intact, the simplicity of the synchronous design process can be retained, and since it is unrestrained by the clock, the speed and power advantages of an asynchronous circuit can also be acquired, all in the same circuit.

Starting with the synchronous implementation, which typically uses D flip-flops as

Figure 2.2: A Simple Pipeline Prior to Desynchronization. From [5]

Figure 2.3: A Simple Pipeline Following Desynchronization. From [5]

registers which store information in a circuit, all of the flip flops in the design are split into two latches (a master and a slave), and the clock signals of all of these latches are replaced by control signals. Using this method, an asynchronous, open-source, high end processor known as ASPIDA was generated from the open source DLX processor.

Each latch has a controller as can be seen in Figure 2.4, to determine when this control signal should be high or low, which is analogous to the clock signal in the original circuit. The inputs and outputs to the controller are dual handshaking lines in and out and a reset signal. The controllers are slightly different between master and slave latches, so that the control signals into these latches are the complement of each other, ensuring that the latches are not both transparent at any one time. They are also designed such that only the master controllers need a reset signal. The circuits of both the master and slave controllers are shown in Figure 2.4.

The pairs of controllers are arranged so that every latch pair is handshaking with the latches to and from which it receives data. This creates a sort of handshaking network which mirrors the flow of data in the system.

When information is multiplexed from two or more registers into one, a Muller C element is used to group together all of the preceding adjacent request signals, because the system must wait for all of them to be ready to change the input to the next controller. The acknowledge signal can simply fan back out to all preceding acknowledge out ports. If we have a register that sends input to multiple adjacent registers, we do

Figure 2.4: Cortadella Style Latch Controllers. From [5]

the opposite, fanning out the request signal and using a C element for the acknowledge signals.

It is critical to ensure that the control signal for a request does not arrive at the next latch faster than the data from the corresponding combinational logic, because then the next register could be clocking invalid data. A delay is inserted between the request out and request in of the next controller, equal to or longer than the slowest path through the combinational logic between the two latches. This is the delay seen in Figure 2.4 and Figure 2.3. The major perceived disadvantage to this method is the difficulty of calculation of the delay, the complications of realising that delay accurately in real hardware, and an inability to port the logic for the delay between various hardware mappings, routings, and technologies.

The handshaking protocol is of the four phased variety, very standard, simple, and straightforward. When a controller receives a request in, it sends a request out to controllers after itself, and an acknowledge in signal back to preceding controllers. When the request in goes low, acknowledge in can go low, and when acknowledge out goes high, request out goes low. The system then only has to wait for acknowledge out to be low before it can respond to another request in.

The logic of the latch controllers are often described using *Petri Nets*, which are a graph used to verify the correctness of asynchronous systems. These are diagrams which demonstrate the impact on the current values of a circuit of the change in one or more of the inputs, and the flow of data, by way of showing which handshakes need to be be completed in order to start a given handshake in the diagram. They are different from a state diagram in that branching indicates not a choice, but two separate dataflows. An arrow indicates a transition between these states, and a "+" in the transition variable indicates a rising edge, and a "-" indicates a falling edge. Dots are also sometimes used to indicate the starting position of data in the circuit [16].

#### 2.4 Finite State Machines

This section will explain some basic concepts about finite state machines. Finite state machines are a method of controlling a circuit which performs different tasks at different points in time. A machine is split up into various states, which along with the inputs determine what the values of outputs are, and which state to move to at the end of the current one. When one state is over, the system moves to a new state, and in this way all of the states are connected in a network. The state machine moves to the next state with a trigger, which in a synchronous FSM is the clock signal, and in an asynchronous one more complicated and discussed in the next section. The machine uses a bitwise encoding, called a state variable from which it can identify which state it is currently in. A combinational logic network uses these and the system inputs to calculate an output, as well as the encoding for the next state, which becomes the new value of the memory element containing the current state at the trigger.

#### 2.5 Asynchronous State Machines

Finite state machines are most commonly implemented synchronously, but it is possible to implement them asynchronously. Memories are used instead of flipflops to hold the current state. The relative security of the clock is not present, and thus there can possibly be critical races, oscillations, and static hazards. If these things are allowed to happen they can cause the state machine to function incorrectly [14, 10, 15].

There are however, several methods of transforming the circuit to work around these timing errors. One of these is to make a speed independent circuit. With this method, one must make sure all state transitions only change one bit in the state encoding. This ensures that there are only two possibilities for state while the transition is happening. The inputs also cannot change during the transition between states. Therefore inputs are only changed in bursts [14].

There have been several ideas which attempt to retain as many advantages as possible from both synchronous and asynchronous finite state machines. Some of these ideas include using delays in the clock path(similar to what is done in the desynchronization method described above), and using inertial delay elements, in which the output is only changed if it is held for a certain amount of time. These can make the state encoding problem less difficult and desensitize the state machine against changing inputs, but they suffer from other problems, notably increased risk of metastability, slower circuits (when the delays are unnecessary), and the difficulty in calculating accurate delays [1].

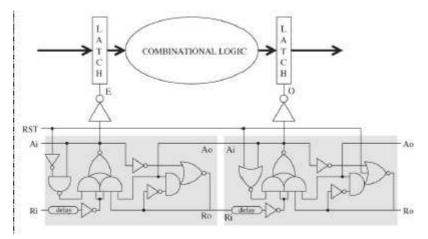

There is another way to implement state machines however, which is not sensitive to changing inputs and does not use delay elements, the structure of which is shown in Figure 2.6. Clock signals are generated for the memory elements using a sum of products equation of which input and current state combinations cause a  $0 \rightarrow 1$  and  $1 \rightarrow 0$  transition for outputs and the state variable. Each output and state variable bit has a latch pair. When a change has been made to the input or state, the change is clocked in the first latch. When the information is safely inside, the first latch becomes opaque, and the second latch transparent. The system then waits until the input has settled. The second latch is again made opaque and the first latch transparent, waiting

Figure 2.5: Output Latching in Aghdasi Style AFSM. From [1]

Figure 2.6: Next State Latching in Aghdasi Style AFSM. From [1]

for a change to state or input. When a state variable is wider than one bit, the system will wait until all bits are clocked into the second latch to reset the latch pair, by way of a common and gate. This will ensure that the machine does not move to a state to which it did not intend to go [1].

#### 2.6 Scheduled Synchronous Filters

The circuit of focus in this project is a scheduled filter. A *digital filter* is a circuit which applies a mathematical calculation on a sampled signal and previous outputs, which amplify or attenuate the different frequency components in the signal. They are used in any kind of circuits that do signal processing and can be found in devices such as

radios, DVD players, and cellular phones.

Scheduling is a process by which resources are allocated in a circuit to be used efficiently. A scheduled circuit is one which has been created in this way.

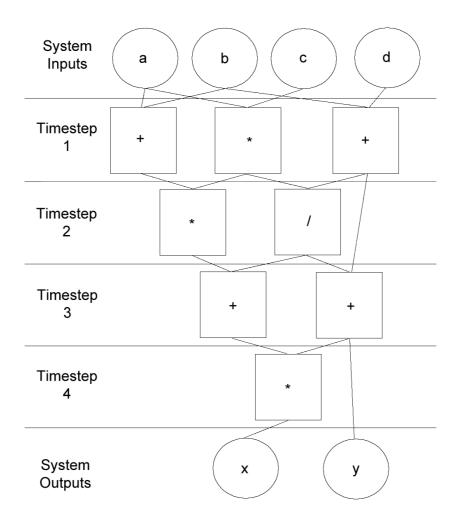

Every digital circuit takes some set of inputs, performs a function on them, and produces outputs. This function can be split into a set of smaller operations which when executed in a defined order, produce the same outputs. An common example of this is a mathematical function which can be split into additions, subtractions, multiplications, and divisions, but the method can be applied for any types of operations. The arrangement of inputs, operations, connections, orderings and outputs of the circuit is known as a dataflow [9].

If the same operations can be performed multiple times on different data within the dataflow, the hardware performing the operation can be shared, and ideally not much hardware needs to be added to multiplex between them and there will not be much contention and extra delay. If the dataflow is scheduled correctly, a circuit can be very quick and save a lot of area.

These shared, scheduled, hardware units which perform a defined operation are known as *computational units* (CUs) or *functional units*. Commonly they are ALU units which perform additions or subtractions, MUL units which perform multiplications, DIV units which perform divisions, shift registers, or simple registers.

*Timesteps* are used to separate each use of the computational units. A clock is used to set the length of a timestep in the circuit, and the cycle time is the length of the delay of slowest computational unit. A central finite state machine is used to send control signals enabling the different functional units in the circuit and multiplexing between the various data at the different states. The result is that at each state some of the computational units will be working, some will be off, and inputs and outputs will be routed in order to produce the correct data.

Calculating the optimal schedule is an NP problem, so heuristics must be used to find a circuit which has a low overall delay and/or a small die area, with a reasonable compilation time, depending on the priorities of the designer. Scheduling every operation to finish as early or as late as possible are two simple alternatives, and these are relatively easy to compute so they are sometimes used as bounds for the heuristic algorithm [9].

Some more complicated algorithms include list based scheduling and path based scheduling. List based scheduling assigns different operations different priority based on how many other operations are dependent on them, and how precious the resources they use are. Path based scheduling seeks to find the critical path in the circuit by determining what the longest string of operations is, and minimize the path in the circuit, by giving its operations first priority, and then scheduling the other operations [9].

There are other algorithms which work using constraints which limit the amount of each computational unit which can be used, such as integer linear programming, and force directed scheduling. Integer linear programming creates bounds using ASAP and ALAP times and the hardware constraints of the system. Then it uses algebraic substitution to satisfy all of these conditions and find an optimal schedule. Force directed scheduling seeks to balance the concurrency in the circuit to make all steps as

Figure 2.7: Sample Scheduled Dataflow with 2 ALU, 1 MUL, and 1 DIV units

concurrent as possible. First ASAP and ALAP are calculated to establish bounds, and then earliest and latest times are calculated for each component. Distribution graphs are taken to see how many of the different operations could used at different timesteps, and probabilities are established based on how many other options for scheduling that operation has. Every operation has a "force" calculated at every step within its bounds, calculated by the probability multiplied by the distribution. If all the forces in the circuit are added, the lowest total will be a circuit with the most concurrency. This is the solution that will be selected by the algorithm [9].

Scheduling is an important process for generating a large synchronous circuit that is run efficiently in terms of both time and hardware. There are many algorithms for scheduling, including as soon as possible, as late as possible, list based scheduling, path based scheduling, integer linear programming, and force directed scheduling.

#### 2.7 Scheduled Asynchronous Circuits

There are also a few published papers about asynchronous circuits and how to schedule them effectively to reduce total time and chip area. This is somewhat more difficult to do since the timing intervals are completely continuous, compared to the discrete intervals in synchronous scheduling.

In a method published by researchers at the University of Aizu, two algorithms are used that are based on force directed scheduling and force directed list scheduling in synchronous scheduling. The starting times of the different operation instances are estimated, and this is used at every iteration of these algorithms to scheduling operations which communicate asynchronously. States are also separated into the periods of time in between the start times of all operations in the system [7, 12]. This approach is different than the one used in this project, and they could possibly be combined in the future to great effect.

The reader should now be familiar with all of the background information required to understand the methods of desynchonization and decentralization explained and implemented in the following chapters.

The next chapter will discuss two experiments which show the functionality of the desynchronization method explained in this chapter and its automation using a language constructed specifically for that purpose.

In order to verify the feasibility of the desynchronization method, first some preliminary experiments were conducted. The first of these is a simple pipeline which is refitted with the latch controllers described in the desynchronization method above, in order to test the effectiveness of the method. The second test was using a tool, called Pipefitter, which can be used to describe asynchronous logic in a subset of Verilog.

#### 3.1 Desynchronization Tests

The even and odd latches specified in [5] were coded in VHDL and simulated functionally using ModelSim, a tool to simulate the functionality of a circuit with user specified test inputs. An 'after' statement was inserted in place of the delay element. Even though there is no delay in the corresponding combinational logic, the circuit needs at least some delay to function, because there are circular dependencies. In a physical circuit, there is some propogatation delay so this is taken care of, but in a virtual circuit without a sense of timing, there will be a logical loop which ModelSim cannot resolve.

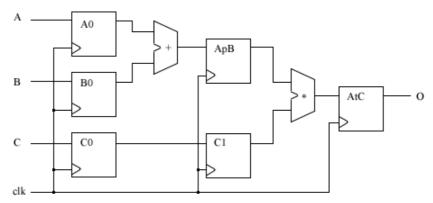

The pipelined circuit was coded with a simple  $(A+B)^*C$  operation. In the first stage taking three input values A, B, and C, in the second stage adding A and B and carrying C, and in the last stage multiplying the values (A+B) and C and writing to an output register. The circuit is used to demonstrate that the asynchronous circuit will produce the same results as the synchronous circuit even with pipeline stages of varying lengths, as well as to allow easy verification of the correctness of the results in both implementations since the operations are arithmetic.

The pipeline was first tested in its synchronous implementation for correctness with a variety of inputs based on corner cases. Then it was desynchronized in the manner described earlier, replacing each flip-flop with two latches and implementing the odd and even controllers for each latch pair, which handshake with the controllers of the adjacent latch pairs, the last pair also handshaking with the first. Diagrams of the synchronous and asynchronous implementations can be found in Figure 3.1 and Figure 3.2.

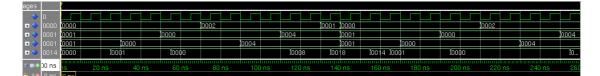

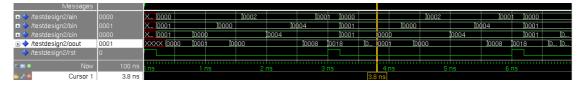

After being desynchronized, the circuit was tested again. The output results of the synchronous and desynchronized circuits were observed to be equivalent (as well as correct arithmetically), indicating a successful application of desynchronization in this experiment. The results of the simulations can be seen in the figures Figure 3.3 and Figure 3.4.

#### **3.2** Pipefitter Tests

In addition, the Pipefitter tool[3], which was developed at the University of Torino for use in the ASPIDA project, was tested with some examples to determine whether

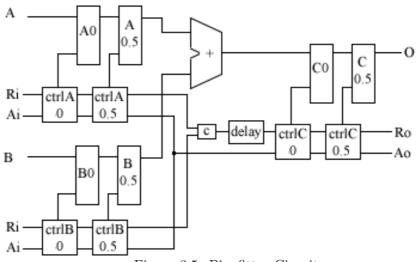

Figure 3.1: Design of the Pipeline Circuit Before Desynchronization

Figure 3.2: Design of the Pipeline Circuit After Desynchronization

Figure 3.3: Results from the Pipeline Circuit Before Desynchronization

Figure 3.4: Results from the Pipeline Circuit After Desynchronization

it was suitable for generating asynchronous control blocks for use in desynchronized systems. Pipefitter has the ability to add timing information to the models which allows the designer to check the timing of the handshaking protocol in addition to the

Figure 3.5: Pipefitter Circuit

Figure 3.6: Pipefitter Circuit Results

#### functionality.

First the examples provided with the source code of a sequential register, an adder/subtractor, and a concurrent register (which corresponds to the one we coded earlier in VHDL) were verified for correctness. Next a simple circuit was designed using instances of the concurrent registers connected in series, to test interactivity and interconnection of different registers. Lastly, an example with two registers which add their values was tested, to show the ability of the system to merge different asynchronous signals, but with the addition done functionally, without delay necessitating the calculated delay elements shown in Figure 3.5. All of these tests were successful, as seen in Figure 3.6, but logic for intercommunication between components had to be coded by hand.

#### 3.3 Summary

- Verification that the desynchronization method works as described

- Verification that Pipefitter works as described

- Better to perform manual desynchronizations than to use an automated desynchronization process for the task ahead

Having performed these experiments, we can see that the desynchronization method does what it is supposed to and is powerful and straightforward for making asynchronous implementations of of existing circuits. Now we are ready to explore how to apply this technique in real, complicated circuits, and produce observable changes and results. As for the pipefitter tool, it proved to be not useful for applications in this project, since similar results can be achieved without the tool, and all of the base circuits in this project are currently implemented in vhdl, while the tool uses verilog, which requires rewriting. Since there is more freedom in devising a method by hand and something must be written by hand in any event, the decision was made to use manual conversion to realise the methods.

The next chapter will delve into the ways in which the synchronous circuit can be improved by desynchronization, ways in which to perform that desynchronization, adjustments to the Cortadella style desynchronization process, and the inner workings of the control network and state machines used in these methods. The previous chapter discussed experiments and the validation of the desynchronization method presented in the background chapter.

This chapter will focus on:

- The ways in which desynchronization can benefit scheduled circuits

- Control skew from a central state machine, and how localization can solve this and further improve the circuit

- Required modifications to the latch controller to deal with logical changes, and to the delay element in order to keep the circuit fast

- Hazards that result in deadlock caused by conversion of a synchronous circuit to an asynchronous circuit, and how to avoid them

- Greater handshakes and how they create delays in the system

- The first solution, its approach to states, state templates, and handshaking, and connections between computational units

- The second solution, state clusters, and the way it removes dependencies between computational units

# 4.1 Inefficiencies in a Scheduled Synchronous Circuit

There are several ways in which a scheduled synchronous circuit is inefficient in using time and hardware resources. These are mainly due to the fact that it is synchronous.

Firstly, the clock is calibrated for the longest possible delay path between any two latches in the system. Faster parts of the circuit must operate at the speed of the slowest parts, due to the global clock signal. If all operations and all paths in the circuit are similar, the amount of wasted time can be negligible, but if there are large differences, the amount of wasted time can be a large percentage of the total time. In a standard ripple carry addition operation, there are N propagations through full adders, where N is the number of bits in the addition, and in an array multiplier, there are 2N propagations [11], meaning that the approximate delay difference of these two operations is the size of the addition. There are also many other common ways to implement the operations, so these differences can be more or less but are usually quite large. The delay for a division is even larger, and for bitwise operations smaller, and these are some of the most common operations in scheduled circuits.

The circuit, as all synchronous circuits also suffers from clock skew and excessive power dissipation by universal charging and discharging of the clock. An optimal solution to the scheduling problem is not solvable, to our knowledge, in a polynomial amount of time. Therefore we must use heuristics, and while they usually find an efficient solution, it is also usually suboptimal, and can even be quite inefficient in some cases.

Also, all of the control signals must travel to all of the computational units in the circuit. If there are enough of them, they could be located far away from the central controller, and this can cause some skew.

# 4.2 Desyncronization and Decentralization of a Finite State Machine

The goal is to apply the desyncronization method to a generic scheduled digital filter which has a central state machine that is linear in nature, and can be run in iterations from start to finish. There are some static inputs which can are constant throughout an iteration of the circuit. There is also some number of reusable computational units suitable for scheduling which perform different or similar operations on inputs and generating outputs for use as inputs in other functional components. Every computational unit has in it a register which stores the result of the function's combinatorial logic.

In a centralized, synchronous finite state machine, each functional unit in the design is communicating at every step with the state register. Making the FSM asynchronous, using method described in [5] to change all registers into a network of handshaking latches, can only serve to make the system the same speed or slower than the optimized synchronous system, because the entire system is waiting for the state register to handshake with the computational unit with the slowest path as well as for all of the other units. Also, at every state these lines must be charged and discharged, which will dissipate a lot of power and counteract the benefits of using the method. These observations provide motivation to change this desynchronization method in such a way that there is less of a negative impact on circuit speed and power usage.

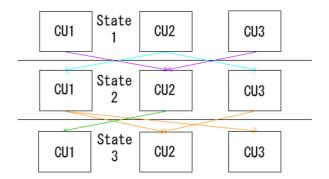

In order to have the chance of speedup in the circuit, one option is to separate the state machine into multiple independently clocked state machines which send requests and acknowledgements to each other and the functional units. The requests and acknowledgements will advance the states in this interdependent "state machine network". By separating the state machine into these smaller state machines, we do not have to wait for the entire clock period in the faster components, which corresponds to the combinational delay of the slowest functional units. Thus we can theoretically trim the difference in time between the longest path for the current component, and the longest path of the slowest component, each time an operation is performed.

In a software design, this is somewhat analogous to the procedure of separating a program into different parallel pieces which depend on information from each other, and will run simultaneously on different CPUs, interacting with each other using message passing. This is a common practice in embedded systems in order to effectively use multiple and often heterogeneous processors for separate tasks, in order to gain some speed up the entire system.

These smaller state machines do not have any knowledge about the execution of the others, and their only communication with the other FSMs is through handshaking.

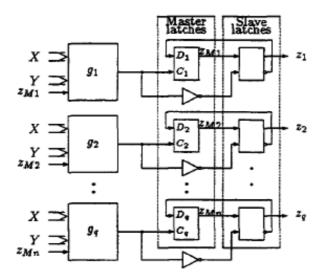

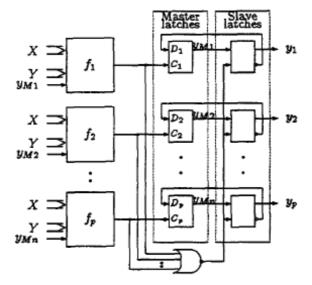

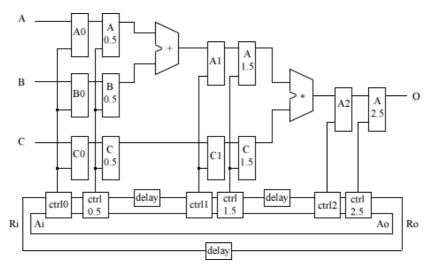

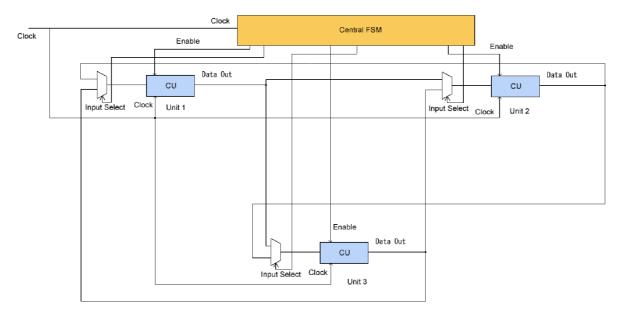

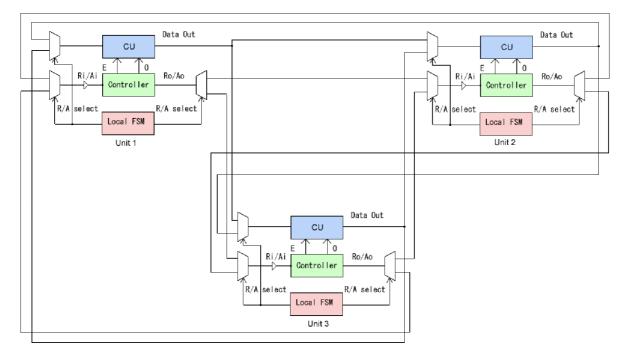

Figure 4.1: A Sample Scheduled Synchronous System

This is not a problem, because the global execution of the system is designed and determined at compile time, and there are no variations on execution. If the system is run once without error, it should run in the same way, without error, for every execution.

When splitting the state machines into smaller ones, how many is too much, and how many are too few? Which state machines will control which of the computational units in the circuit, and at which times? The most immediately obvious way to determine the number of state machines and allocate them responsibility for different functional units, is to create a separate state machine for every functional unit. Since they are asynchronous states, there is no clock to determine when one state is finished and the next state begins. Thus state transitions must happen asynchronously, as well. There is a method of doing this, mentioned in [1] which circumvents two major problems, namely, instability in the state machine due to input during a transition, and timed or significant delay. This method does, however, provide a sort of buffer for the input. That means that all possible combinations of inputs must be handled by the state machine, similar to a synchronous solution.

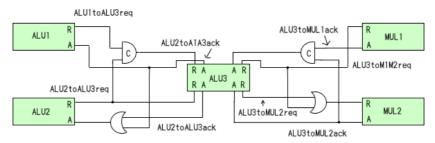

A diagram which shows the simplified structure of a scheduled circuit with three functional units can be seen in Figure 4.1. There is a central FSM, and this FSM controls the clock enable signals and selects which data to input to each CU at any given state. There is also a global clock signal which is seen by all components in the system.

# 4.3 Modifications to the Latch Controller

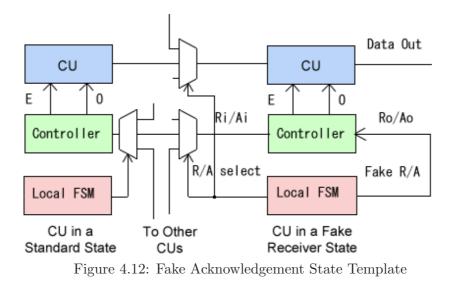

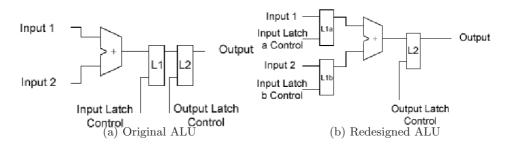

Both of the solutions presented in the following chapters make use of latch controllers, In the first solution, each functional unit in the circuit has an independent instruction state

Figure 4.2: Petri Nets for Original Desynchronized Even and Odd Latch Controllers. From [5]

machine and a separate latch-pair controller based on the latch controller introduced in the background chapter. In the second solution, this latch-pair controller is embedded in the logic of the instruction state machine, but the functionality is the same.

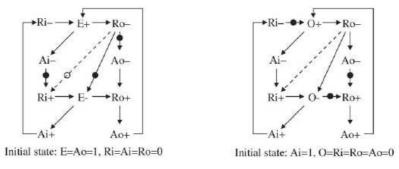

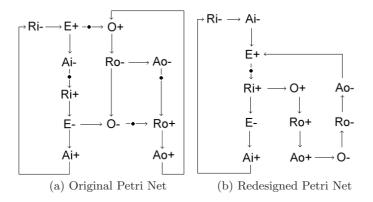

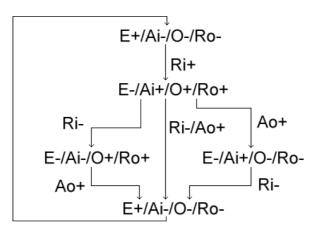

The controller is slightly modified from the [5] design. The Petri nets for the original latch controllers are given in Figure 4.2. The controllers for both latches are combined into a single unit called a *latch pair controller* for ease of use, since they are always used together throughout the circuit. In Figure 4.3a is the combined and simplified Petri nets from Figure 4.2, and in Figure 4.3b is the version used in this project. E stands for the control signal of the even latch or master latch, and O stands for the control of the odd or slave latch. The handshaking outputs consist of: Ai, the acknowledgement in signal which confirms the capture of data from the sender latch pair controller, and Ro, the request out of the controller to the receiving controller. The inputs are: Ri, which is the request into the controller, and Ao, the acknowledgement to the CU when its request is seen by another. A "+" in the diagram represents a rising edge, and a "-" represents a falling edge.

The modifications are mostly to allow the latch pair controller to signal an FSM that is keeping track of an overall state when it should advance its state. In the original latch controller, the state of the input and output is only loosely connected because both handshakes are happening as soon as the other is finished, which there is no common point for the Petri nets to pass through where the state of the controlling FSM can be changed. Therefore in the modified latch pair controller there is a common entry and exit point in the Petri net in the E+ stage where the controlling state machine ends and begins states. The rest of the latch controller logic is adapted to account for this change.

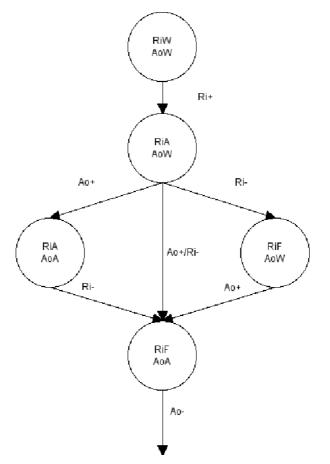

A perhaps easier way to see the logic for the latch pair controller is displayed in Figure 4.4. If the latch pair controller is used as a separate entity, this acts as a state machine diagram for the controller. If it is not explicitly separate from other hardware, the logic controlling the latches still follows this scheme. The edges of the graph, which represent the transitions between phases in the handshaking, are influenced by the positive or negative changes in the two handshaking inputs to the CU and its pair of latches. The final state is necessary if there is a another controlling state machine. It must be visited because its controlling state machine must see both handshakes are completed to advance to the next state, and as soon as it advances, the latch pair

Figure 4.3: Petri Nets for Original and Redesigned Latch Pair Controllers

Figure 4.4: Modified Latch Controller Logic

controller will also be told to advance.

# 4.4 Delay Elements and Bypassing

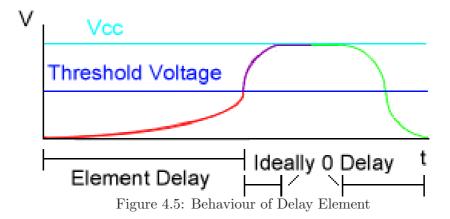

In the original desynchronization method, the delay elements in the circuit are placed in the request in line of all latch pair controllers which in turn serve all of the computational units. This ensures that the request is delayed and unseen, to allow the combinatorial logic of the receiving CU to saturate before the result is saved in the latch.

The delay while the circuit is waiting for its input request to go through the delay element is given the term *input delay* by this report, and the delay of a sending CU while this request is going through the receiver's delay is known as the *output delay*. The output delay can usually be alleviated, because the logic can begin to saturate with its new inputs and request as soon as the input handshake is complete (see the section on input multiplexing options). The input delay on the other hand is necessary for the logic to saturate and data validity.

When the acknowledgement is sent by the receiver back to the sender, and the CU waits for the request to end, since the lowering of the request also travels through the delay element. This delay, prior to the falling edge of the request in, is no longer needed, because the logic has already saturated and the result is secure in the latch pair, and the sender can safely finish the handshake as quickly as is possible.

If this extra time is added, the circuit can be up to two times slower, since every handshake has twice the input delay and output delay. Thus in order to save time, we should use a delay element which has delay only until the threshold voltage on the rising edge. When the request is rising past the threshold voltage or falling, ideally there should be zero delay in the element. This ideal behaviour can be seen in the curve in Figure 4.5. The further from this ideal the delay element is, the slower the circuit will be.

### 4.5 Input Multiplexing Options

There are two separate ways to multiplex the inputs to each FSM in the circuit. The first way is simpler and takes less area, the second way is faster and takes more area.

The simpler option is to change the inputs which are being passed into the functional unit at each state transition. This solution is more stable, but it wastes more time than the alternative. This is due do the logic only propagating through the computational unit's logic after the state has started. The unit will have to wait for the delay of itself between the start of every state and the input handshake. On the other hand the logic for multiplexing the inputs into the computational unit is simpler.

The more sophisticated option is to feed the input for the next state into the functional unit as soon as the input handshake is finished, locking the computed data into the first latch, so that we can cut down on the time it takes between the start of the next state and sending acknowledgements to the input units. If all of the inputs have propagated through the logic by the time the next state starts, this unit can save time equal to its own delay. In general it will save the difference in time from when it has finished the input handshake and inputs are ready until when the output handshake is finished and the next state starts. This is the method used for this project because the increase in speed is quite significant over the simple method.

# 4.6 Hazards, Deadlock, and Redesigning the Circuit to Avoid Them

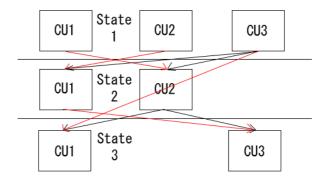

Depending on the synchronous design, situations can arise after the simple desynchronization which cause deadlock. This is due to the fact that in the synchronous implementation, these situations do not cause deadlock, and are not known to be avoided. Therefore, the asynchronous system must be slightly altered to avoid these situations and the ensuing deadlock. A properly designed system will never deadlock if as long as the components function correctly, since its execution path is predetermined, and the same every time. The fundamental cause of this deadlock is that there are one or more state machines which are involved in the same greater handshake in two different states. Since the transition from one state to the other is dependent on the handshake being completed, and every handshake in the greater handshake must complete before it will finish, there is a paradox. This happens in three different ways in a desynchronized circuit. In this report they are refered to as *crossover hazards*, *self-handshake hazards*, and *triangle hazards*.

If two or more functional units are in the synchronous design sending each other output over the same time boundary, it will create an interdependency between the output handshakes, and thus deadlock in the circuit. This phenomenon is referred to in this report as a crossover hazard and shown in Figure 4.6. The CUs are represented by squares, states and time are represented by the horizontal lines, and handshakes are represented by arrows between CUs. The handshakes causing a crossover hazard are coloured in red.

The simplest two CU problem lies in the fact that both of the units are at the end of their respective states, where they are trying to send their output, and need to finish before they can start a new state and accept new input. In a crossover deadlock involving more than two CUs, they will be connected in a circle, all of them trying to send requests to each other. A will be sending a request to B, B will be sending one to C, and C sending one to A.

One of the CUs will have to somehow finish first and accept input from the other CU in order to break the deadlock. One solution is to somehow reroute the output from the first unit to another computational unit. In the case of this implementation, there are CUs which are simple latch pairs with no other logic. We can use a latch pair which is not in use, or add one to the design in order to prevent the crossover deadlock. We can also potentially switch the operation in one of the computational units causing the deadlock to another which performs the same task and does not create a deadlock hazard with the other component.

Rerouting is however often a very unfavourable solution in terms of speed. The element through which the data is rerouted is often a simple latch pair, and fast, but the process destroys the concurrency of the scheduled circuit. The circuits which are rerouted all execute at the same time in the synchronous implementation, but in a rerouted implementation, they execute in a chain; first the one which has its output rerouted begins to execute and its sender is freed and begins to execute and so on.

Figure 4.6: Deadlock due to Crossover Hazards

This is very costly in a hardware system designed to be concurrent. Therefore if it's possible, it is much better to switch the operation with that in another functional unit with no dependency.

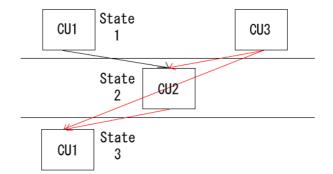

Another problem arises when in the synchronous solution a functional unit sends output to itself. This is impossible in the asynchronous solution because the output handshake is at the end of one state, and the input handshake is at the beginning of the next, these two need to handshake with each other, and the machine cannot be in two states at once. This is called a self-handshake hazard in the scope of this thesis. As with a crossover hazard the data has to either be rerouted or another equivalent functional unit that eliminates this problem must be used.

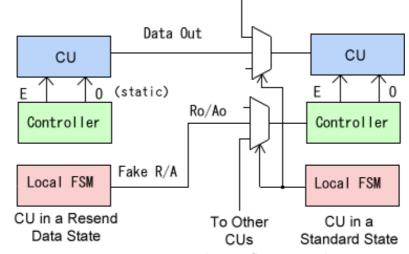

A third potential deadlock problem happens when there are two or more components receiving an output handshake, and one of those is also receiving an input handshake dependent on the other. This is called a triangle hazard by this report and illustrated in Figure 4.7, with the handshakes between CUs represented by arrows, and those causing the hazard represented by red arrows. This will cause deadlock because the first handshake can never complete. One or more of the signals in the greater handshake is dependent on the completion of the same greater handshake. This means that one of the computational units is part of the greater handshake in more than one state, which is impossible. This problem can be solved by separating the output handshakes in the first state. This is performed by adding a resend data state in the first computational unit. This splits the greater handshake into two parts, and the CU which previously had two states in the greater handshake will now have one state in each, and the deadlock is avoided.

All of these hazards can be intertwined and combined with each other, and their manual correction and elimination can be very complicated and time consuming. The resulting fixes are often more linear in execution than the synchronous implementation, and this may lead to slow down the circuit. This is akin to fixing mistakes in a factory made circuit board by soldering it by hand. It is somewhat less elegant than a circuit which has been scheduled to be executed asynchronously in this manner.

Figure 4.7: Deadlock due to Triangle Hazards

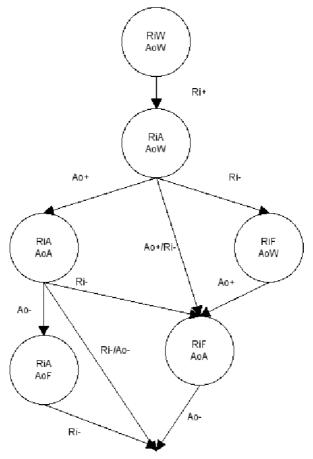

## 4.7 Separated Latch Pair Controller FSM Solution

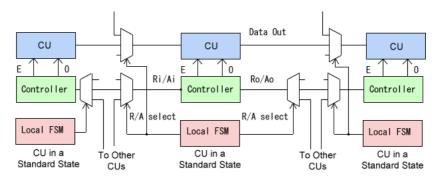

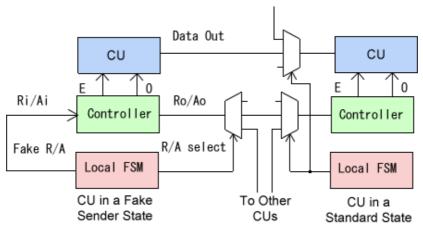

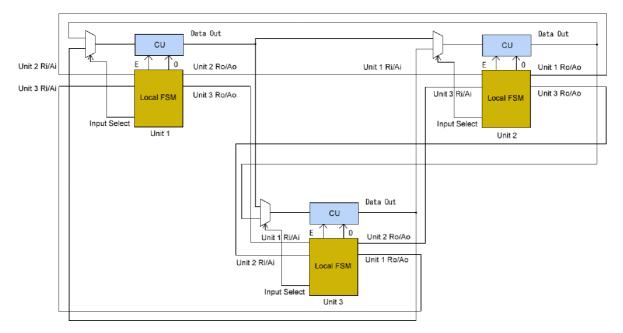

In this solution, each computational unit has a *latch pair controller*, a separated asynchronous FSM which controls the handshake cycle at every state, and a likewise asynchronous *instruction state machine*, which has states corresponding with the states that the functional unit is active in the synchronous implementation. This instruction state machine must interface with the latch pair controller at every state, and multiplex the correct inputs and outputs.

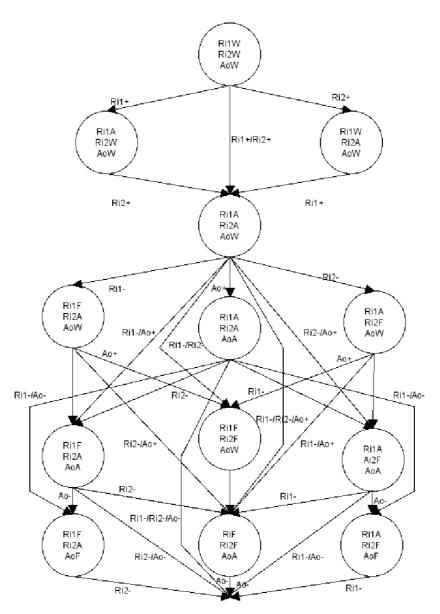

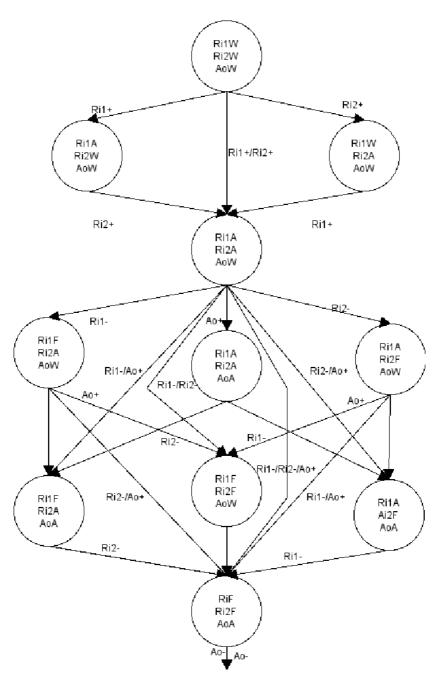

Every state in the instruction FSM is a complete handshaking cycle of a pair of latch controllers. They each have one input handshake and one output handshake with all of the functional units' inputs and outputs at the state in question, although handshakes to outputs can potentially be separated (refer to the section on state templates). The FSM will move to a subsequent state when both the input and output handshakes in the current state are completed.

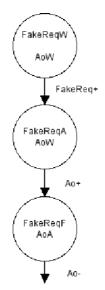

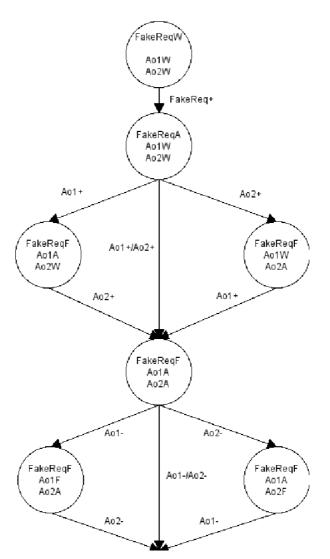

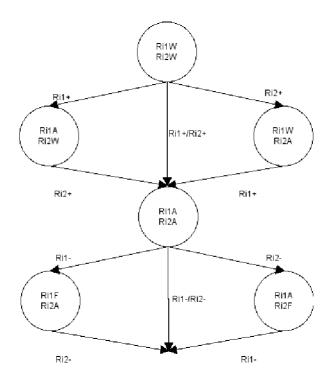

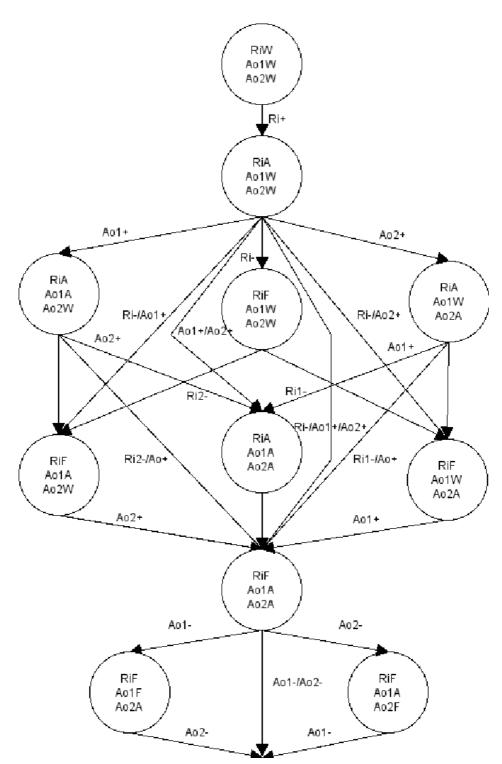

As for the latch pair controller, each cycle of states corresponds to one state in the instruction FSM. Each state in the latch controller corresponds with a possible phase in the input and output handshakes, and the state diagram is equivalent to the Petri Net in Figure 4.4. All of the inputs and outputs are multiplexed into and out of the latch controller with controls coming from the instruction FSM.