## Profiling quantum circuits for their efficient execution on single- and multi-core architectures

Bandic, M.; le Henaff, P.; Ovide, Anabel; Escofet, Pau ; Ben Rached, Sahar ; Rodrigo, Santiago; van Someren, J.; Abadal, Sergi; Feld, S.; More Authors

**DOI**

[10.1088/2058-9565/ada180](https://doi.org/10.1088/2058-9565/ada180)

**Licence**

CC BY

**Publication date**

2025

**Document Version**

Final published version

**Published in**

Quantum Science and Technology

**Citation (APA)**

Bandic, M., le Henaff, P., Ovide, A., Escofet, P., Ben Rached, S., Rodrigo, S., van Someren, J., Abadal, S., Feld, S., & More Authors (2025). Profiling quantum circuits for their efficient execution on single- and multi-core architectures. *Quantum Science and Technology*, 10(1), Article 015060. <https://doi.org/10.1088/2058-9565/ada180>

**Important note**

To cite this publication, please use the final published version (if applicable).

Please check the document version above.

**Copyright**

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

**Takedown policy**

Please contact us and provide details if you believe this document breaches copyrights.

We will remove access to the work immediately and investigate your claim.

PAPER • OPEN ACCESS

## Profiling quantum circuits for their efficient execution on single- and multi-core architectures

To cite this article: Medina Bandic *et al* 2025 *Quantum Sci. Technol.* **10** 015060

View the [article online](#) for updates and enhancements.

You may also like

- [Quantum information processing with superconducting circuits: a review](#)

G Wendl

- [Universal and holistic privacy protection in quantum computing: a novel approach through quantum circuit equivalence homomorphic encryption](#)

Xuejian Zhang, Yan Chang, Lin Zeng et al.

- [Variational quantum compiling with double Q-learning](#)

Zhimin He, Lvzhou Li, Shenggen Zheng et al.

**OPEN ACCESS****RECEIVED**

17 July 2024**REVISED**

7 October 2024**ACCEPTED FOR PUBLICATION**

19 December 2024**PUBLISHED**

6 January 2025

Original Content from

this work may be used

under the terms of the

[Creative Commons

Attribution 4.0 licence](#).

Any further distribution

of this work must

maintain attribution to

the author(s) and the title

of the work, journal

citation and DOI.

**PAPER**

## Profiling quantum circuits for their efficient execution on single- and multi-core architectures

Medina Bandic<sup>1,3,\*</sup> , Pablo le Henaff<sup>1,3</sup>, Anabel Ovide<sup>2</sup>, Pau Escofet<sup>4</sup> , Sahar Ben Rached<sup>4</sup> , Santiago Rodrigo<sup>4</sup> , Hans van Someren<sup>1</sup>, Sergi Abadal<sup>4</sup>, Eduard Alarcón<sup>4</sup>, Carmen G Almudever<sup>2</sup> and Sebastian Feld<sup>1,3</sup>

<sup>1</sup> Delft University of Technology, Delft, The Netherlands

<sup>2</sup> Universitat Politècnica de València, Valencia, Spain

<sup>3</sup> QuTech, Delft, The Netherlands

<sup>4</sup> Universitat Politècnica de Catalunya, Barcelona, Spain

\* Author to whom any correspondence should be addressed.

E-mail: [m.bandic@tudelft.nl](mailto:m.bandic@tudelft.nl)

**Keywords:** quantum circuit mapping, multi-core quantum computers, modular architectures, quantum communication, interaction graphs, quantum benchmarks, gate-dependency graphs

### Abstract

Application-specific quantum computers offer the most efficient means to tackle problems intractable by classical computers. Realizing these architectures necessitates a deep understanding of quantum circuit properties and their relationship to execution outcomes on quantum devices. Our study aims to perform for the first time a rigorous examination of quantum circuits by introducing graph theory-based metrics extracted from their qubit interaction graph and gate dependency graph (GDG) alongside conventional parameters describing the circuit itself. This methodology facilitates a comprehensive analysis and clustering of quantum circuits. Furthermore, it uncovers a connection between parameters rooted in both qubit interaction and GDGs, and the performance metrics for quantum circuit mapping, across a range of established quantum device and mapping configurations. Among the various device configurations, we particularly emphasize modular (i.e. multi-core) quantum computing architectures due to their high potential as a viable solution for quantum device scalability. This thorough analysis will help us to: i) identify key attributes of quantum circuits that affect the quantum circuit mapping performance metrics; ii) predict the performance on a specific chip for similar circuit structures; iii) determine preferable combinations of mapping techniques and hardware setups for specific circuits; and iv) define representative benchmark sets by clustering similarly structured circuits.

### 1. Introduction

In recent decades, the realm of quantum technology has witnessed remarkable progress, holding the potential to tackle problems that were once deemed insurmountable using classical means. Although these advancements are impressive, we are still in the early stages of understanding its full potential. The current generation of quantum devices, referred to as noisy intermediate-scale quantum (NISQ) devices [1], present severe limitations due to their size and susceptibility to noise. As a result, they are currently adept at handling only simple and modestly-sized circuits (i.e. executable descriptions of algorithms). These devices also face other hurdles, including restricted qubit connectivity, a narrow set of supported operations, and challenges pertaining to classical control resources [2, 3]. These collective constraints make the successful execution of a quantum circuit on such processors an intricate endeavor. Furthermore, NISQ devices often adhere to a ‘one-size-fits-all’ approach, which can lead to architectures ill-suited for certain quantum algorithms, resulting in lower success rates and fidelity. This is already well showcased in classical computing, where devices are often tailored for the purpose of usage (e.g. GPUs for gaming).

Most current quantum computers operate as single-processor devices, containing all qubits on a single chip. Scaling these designs proves challenging due to issues like crosstalk and limitations in control

electronics [4]. An alternative approach, akin to classical computing, involves multi-processor (or multi-core (MC)) architectures, which are proposed by various quantum processor manufacturers [5–10]. These new designs facilitate distributed quantum computing that enables the execution of large algorithms across multiple cores to accommodate more qubits than a single processor can handle, and represent a feasible avenue for achieving scalability in quantum computing.

For both NISQ and MC architectures, the quantum circuit mapping process [11, 12] is necessary to efficiently run the circuits and maximize the usage of hardware resources. Quantum circuit mapping essentially represents adapting quantum circuits to quantum devices to adhere to all hardware constraints, forming a vital component of a full-stack quantum computing system [13].

Several studies emphasize the importance of considering a broader range of circuit features during the process of mapping [14–17]. A comprehensive profiling or characterization of quantum circuits offers several advantages, including gaining a better understanding of why certain algorithms achieve higher fidelity with specific processors and mapping techniques [18]. Additionally, it enables the classification and prediction of the performance of similar circuits based on the circuits' attributes (like in [19]), all without the need for actual hardware execution. Moreover, this approach facilitates the development of mapping techniques and overall quantum systems customized for specific applications, respecting both the requirements (i.e. characteristics) of those particular circuits and the limitations of the hardware [13, 20, 21]; this consequently leads to an improvement in quality and execution time of solving currently intractable problems. It is important to note that this exhaustive characterization of quantum circuits is not only the key for formulating meaningful and representative sets of quantum benchmarks that evaluate quantum circuit mapping techniques and entire quantum computing systems [22, 23], but also for establishing a suite of algorithm-level metrics to measure system performance [24].

The state-of-the-art characterization of quantum circuits proposed in [18] extends beyond conventional metrics such as qubit and gate counts. In addition to these standard attributes, their approach includes an examination of qubit interaction graphs (IG), drawing insights from graph theory and machine learning to clarify the circuit's two-qubit gate connections (qubit interactions). They performed an analysis of how these circuit parameters affect the performance of a specific quantum circuit technique when considering three different single-core (SC) devices.

In this paper, we extend the results of [18] by additionally encompassing metrics extracted from GDGs (which portray inter-dependencies among gates within the circuit), as well as parameters that describe the *density of the circuit* and its *repetitive oracles*. Furthermore, we not only consider parameters that are relevant for SC processor devices but also identify those that are of special interest for the next generation of MC architectures. Within our approach, we also experiment with *diverse quantum circuit mapping configurations* (four for SC and three for MC quantum architectures). This intricate exploration allows us to: i) discern the most influential quantum circuit attributes that impact the performance of circuit mapping; ii) predict the mapping performance of similarly structured quantum circuits on a specific chip; iii) identify the most adequate combination of mapping technique and quantum hardware for a given quantum circuit or set of circuits; and iv) define a representative benchmark set [24], by specifying a finite amount of groups of similarly-structured circuits. This thorough analysis, therefore, holds the potential to contribute to the future co-design of compilation methodologies driven by algorithms and the evolution of quantum hardware.

In summary, the main contributions of this paper are:

- (i) performing the most comprehensive profiling of quantum circuits by extracting: (a) standard parameters (i.e. number of qubits and gates, two-qubit gate percentage and depth), metrics from the (b) IG (e.g. average node degree), and (c) GDG (e.g. critical path length), (d) gate density related parameters (e.g. amount of idling) and (e) characteristics related to repetitive sub-circuits. We believe that this list of parameters encompasses all relevant aspects of a quantum circuit. It helps us gain insights into why certain circuits excel or falter on particular architectures, potentially revealing correlations between circuit structure and performance across different quantum setups. Leveraging these parameters, we can adapt existing or craft new full-stack quantum systems with higher precision.

- (ii) Identifying, for the first time, circuit parameters that are key for scalable modular quantum computing architectures. Those architectures demand a unique parameter set due to their intricate quantum circuit mapping requirements, as elaborated in detail in section 2.

- (iii) Finding a correlation between extracted circuit features and compilation performance across various mapper-device combinations for SC and MC architectures (totaling in seven mappers and six devices). Utilizing the Pearson correlation score [25], we rank parameters from most positively correlated to most negatively correlated for each combination. This analysis shows the significance of selecting suitable device topologies and mapping techniques for quantum circuits with specific structural parameters. It also highlights the key circuit parameters crucial for designing application-aware

quantum systems. Identifying these influential circuit parameters marks the initial stride towards crafting such systems.

(iv) Clustering similarly structured circuits and determining the most effective mapper-device setups for them. We illustrate how these clusters also correspond to circuit origin groups found in qbench (i.e. random, QUEKO, real algorithms) [22]. This discovery of distinct groups of quantum circuits allows us to establish representative sets of quantum benchmarks without the need for an exhaustive list, which also facilitates the design of application-specific quantum systems tailored to each group, rather than a separate system for each benchmark.

The paper is organized as follows: section 2 introduces SC and MC computation and quantum circuit mapping, as well as the previous work on quantum circuit characterization. Section 3 showcases our novel circuit parameters and profiling process in this work, done for SC and MC quantum computation separately. In section 4, we dive into methodology and performance metrics. We show and discuss results in section 5 and finally conclude our work in section 6.

## 2. Background and previous research

### 2.1. MC quantum computation

Just like for classical computing, modular architectures are envisioned as a solution for the scalability of quantum devices and they are expected to accommodate thousands to millions of qubits within a single system. For dealing with problems regarding crosstalk, classical control electronics, and wiring complexity, qubits are distributed over multiple cores or processors. This strategy capitalizes on quantum parallelization while addressing qubit control demands and improving qubit isolation [26]. Nevertheless, constructing MC processors introduces new challenges, mainly due to latency-prone quantum communications that introduce inefficiencies. Quantum state transfer across chip-scale networks represents an alternative to conventional communication technologies, which prove impractical for modular architectures. Communication latencies heighten the risk of data loss during qubit transmission due to state decoherence [2]. Several strategies have emerged to create inter-core communication networks for modular quantum computing architectures, accommodating varying technology platforms. These include quantum links for superconducting chips [5], ion-shuttling for ion-trapped quantum computers [27], and photonic networks [28]. Modularity requirements extend beyond the qubit layer, imposing constraints on networking, control, and compilation layers, necessitating a comprehensive software–hardware stack [26].

### 2.2. The quantum circuit mapping problem

As previously stated, running a quantum circuit on any device is not a straightforward task. Given the constraints of current NISQ devices (e.g. highly error-prone and limited size and qubit connectivity), the execution of quantum circuits often requires making some modifications within the circuit. This process, referred to as quantum circuit mapping, is pivotal in adapting algorithms to quantum devices, and it forms a vital component of a full-stack quantum computing system [29]. Limited connectivity is the main challenge addressed by quantum circuit mapping because, during the execution of circuits, all interacting logical/virtual qubits (of the circuit) must be adjacent. This problem is solved by finding the most suitable allocation of logical qubits to physical qubits on the chip, and repositioning those logical qubits on the chip to make them adjacent when necessary, which is usually done by inserting additional gates (e.g. SWAPs or shuttle operations). The specifics of quantum circuit mapping can differ from one device to another due to technology disparities and qubit connectivity. Ensuring effective utilization of limited hardware resources and minimizing errors during quantum operation execution by reducing additional gates and circuit latency necessitates this process. Yet, solving the quantum circuit mapping problem as the qubit count increases is computationally challenging, even for current monolithic (or SC) devices. To address this, diverse quantum circuit mapping algorithms have been introduced, ranging from heuristic and brute-force strategies to graph-theoretical techniques, dynamic programming algorithms, and machine learning-based approaches [17, 30–53], relying on different performance metrics like gate count, circuit depth (i.e. number of layers of gates where gates can run in parallel), fidelity [38, 39, 54] or the circuit success rate [35, 55].

However, mapping techniques designed for SC-processor NISQ devices do not readily apply to modular MC (or multi-node) quantum computing architectures, which offer a promising path for quantum computing scalability [2]. This architectural approach involves cores (quantum processing units, or QPUs) interconnected via classical and, ultimately, quantum communication channels. Quantum links facilitate the transfer of quantum states among processors or the execution of inter-core quantum gates depending on the technology, while classical links ensure the coordination of quantum communication [56]. The intricate communication channels and traffic patterns in MC architectures add complexity to quantum circuit

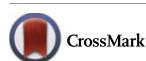

mapping compared to SC devices [3, 57, 58]. In response, novel techniques have emerged for modular architectures, aiming to minimize the costly (in terms of time and effort overhead or reduced fidelity) long-distance inter-core operations. To reduce the amount of inter-core operations, it is essential to efficiently allocate logical qubits across the physical qubits of the given cores. While the literature in this emerging domain is limited, some approaches have concentrated on quantum compilation and mapping for modular quantum computing [59–62]. In these approaches, the quantum circuit is divided into smaller partitions, and IGs reflecting operations within a circuit segment are mapped onto cores by grouping qubits with high interaction levels (see figure 1).

All previously stated strategies within both SC and MC quantum computation share a common goal: tailoring quantum circuits to device-specific attributes and constraints, while minimizing the communication overhead. However, they often only focus on a limited set of circuit features, such as gate and qubit counts, and qubit interactions. What is missing is a more comprehensive quantum circuit characterization that goes into deeper aspects. For example, one can explore the characteristics of the qubit IG, such as the frequency of interactions between qubit pairs [18] and the distribution of these interactions among qubits, as well as the quantum instruction dependency graph (representing gate dependencies for scheduling).

Some researchers have already highlighted the significance of incorporating application-specific properties [13, 15–18, 36] to enhance quantum circuit mapping and overall quantum system performance. Even in classical computing, the allocation of computing resources depends on the intended applications and processes. In a similar vein, thorough profiling aids in identifying the essential circuit features for successful execution on a particular device and vice versa. Yet, as we explore the intricacies of running algorithms on modular architectures, it becomes evident that this realm demands a distinct approach when compared to conventional monolithic NISQ devices. Consequently, profiling quantum circuits in the context of modular architectures should adopt a tailored strategy and select parameters that align with the nuances of this scenario.

In conclusion, understanding the structural attributes of quantum circuits sheds light on why and which groups of algorithms perform better on specific processors with designated mapping techniques than on others. This holistic understanding not only guides mapping but also opens avenues for improving the overall performance of quantum circuits on quantum hardware and represents a first step towards application-based quantum computers.

### 2.3. On the importance of qubit interaction and GDGs

Quantum circuits so far have mostly been characterized in terms of size, i.e. the number of qubits, gates, two-qubit gates, and depth, which are blind to the circuit's structure. Considering that the main quantum hardware constraints are low fidelity and limited qubit connectivity, it is important to extract more information about the qubit interaction distribution as well as gate dependencies as they directly relate to gate and depth overhead that results from the compilation process. Previous works have emphasized the significance of deriving additional circuit parameters based on qubit interaction and quantum instruction dependency graphs for the development of mapping techniques [12, 31, 32, 61]. While GDGs have been utilized for operation scheduling optimization and look-ahead techniques, IGs have typically been employed for the initial qubit placement and routing procedure. In this work, we utilize these two graphs and their graph-theory-based attributes for characterizing circuits targeting both SC and MC architectures. In the next paragraphs, we will introduce these two graph representations of the quantum circuit.

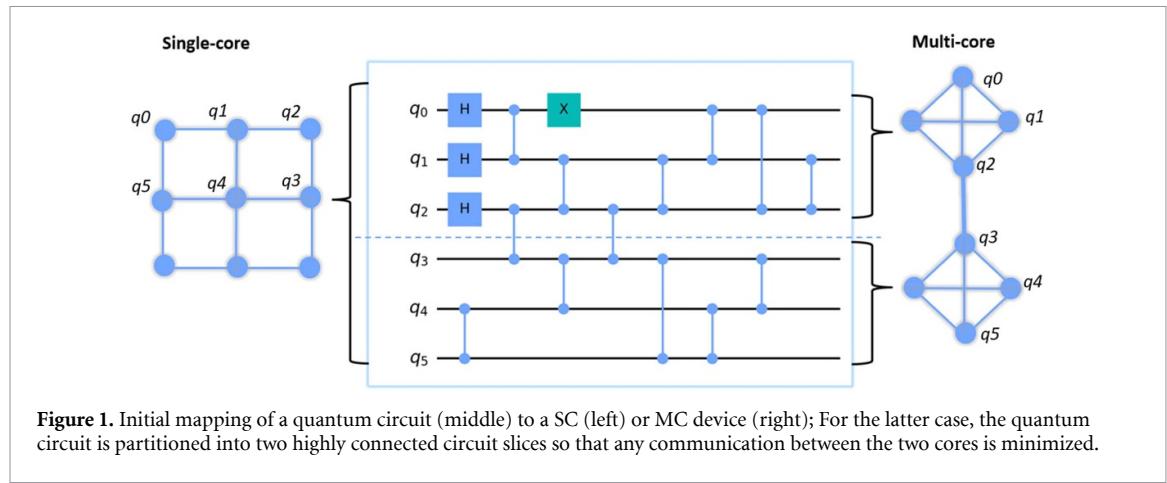

Figure 2. An exemplary quantum circuit (a) and its corresponding qubit interaction graph (b) and GDG (c).

The IG  $G_i(V_i, E_i)$  offers a visual representation of the spatial distribution of two-qubit gates for a given quantum circuit. Typically, this is an undirected and connected graph (see figure 2(b)), with edges denoted as  $e(v_i, v_j) \in E_i$  representing the two-qubit gates and nodes labeled as  $v_i \in V_i$  representing the qubits engaged in these gates [18, 61]. Previous research [18] has demonstrated that different categories of circuits (e.g. real algorithms and random circuits) exhibit varying compilation performance in terms of gate and depth overhead as well as fidelity decrease when executed on different physical-qubit topologies (see figures 5 and 14 of [18]). To understand the underlying reasons for these differences, prior studies have explored the structural disparities between various quantum circuit groups based on their IGs. The quantum circuit mapping problem can be conceptualized as a graph problem, in which the comparison between the IGs of a circuit and the coupling graph of the device is crucial [53]. Therefore, the parameters of the IG can significantly influence the outcome. Studies such as [18, 24] have illustrated how the IG and size parameters of quantum circuits directly correlate to their performance on different chips when employing the same mapping technique. For example, circuits with fully connected IGs are expected to incur higher overhead, unless the processor's coupling graph is fully or almost fully connected. Moreover, research such as [18] has further clustered the circuits based on these extracted parameters and identified performance discrepancies among the groups based on the aforementioned mapping metrics.

IGs play an even more significant role in the compilation of circuits for MC systems [63]. Mapping to MC devices involves minimizing inter-core communication by partitioning the IGs and effectively allocating the logical qubits (IG nodes) onto the physical qubits of different cores. This is achieved by aiming to map highly interacting qubits (with high IG weights) onto the same core. Given the importance of IG partitioning in modular compilation and its distinct approach compared to SC systems, it is essential to use different IG metrics. These metrics should focus on identifying local clusters and cliques to effectively describe how 'partitionable' a circuit is.

Besides that, the GDG  $G_{\text{gd}}(V_{\text{GD}}, E_{\text{GD}})$  is a directed and connected graph illustrating the interrelations between the gates in the circuit. Each gate in the circuit is represented by a node  $v_j \in V_{\text{GD}}$ , and the dependency between gates is depicted as a directed edge  $e(v_j, v_k) \in E_{\text{GD}}$ . An illustrative example of this concept is shown in figure 2, where a quantum circuit consisting of 6 qubits and 8 two-qubit gates is displayed alongside its corresponding IG and GDG [42]. It is worth noting that both graphs can also be represented as weighted graphs: the IG becomes weighted when multiple two-qubit operations occur between the same pairs of qubits, while the GDG becomes weighted when considering, for instance, gate duration (i.e. time). For the purpose of this paper, we focus on the simplified, unweighted version of GDG, where all gates take one time step.

In this paper, we aim to examine quantum circuits by analyzing parameters extracted from IGs that are relevant for SC and multi-processor architectures, from GDGs (e.g. path distribution and critical path length), parameters related to repeating sub-circuits/oracles within the circuit, and circuit density-related parameters, followed by a clustering of the circuits. Our focus is to identify and quantify the relationships between circuit parameters, clusters, and various compilation techniques across different quantum topologies. That is only possible if we observe the circuit as a whole and utilize all its complementary properties like those of IG (spatial) and GDG (temporal). Gaining a comprehensive understanding of circuit structures can aid in designing and evaluating quantum systems optimized for the highest success rates for specific circuit groups and help define a finite set of representative benchmarks.

In the subsequent sections, we will provide a detailed overview of the entire quantum circuit profiling process.

### 3. Characterizing quantum circuits—definition and profiling

#### 3.1. Parameter selection

Table 1 illustrates the five groups of circuit parameters we consider in this work. The process selection of the **parameters of interest** involved two steps: (1) selecting parameters within these groups relevant to SC and MC architectures considering their main constraints. For instance, the clustering coefficient [64] is important for the execution of circuits in MC devices but not in SC devices, as it requires graph partitioning. Conversely, node degree is relevant to both scenarios: a higher average degree in the IG makes mapping more challenging; and (2) reducing the number of parameters by identifying highly correlated ones using the Pearson correlation matrix [25], like in [18].

The resulting reduced set of parameters is as follows [18, 64]:

##### 3.1.1. Size

Standard parameters used for circuits description in previous works:

- *Number of qubits:  $n_q$*

- *Number of gates:  $n_g$*

- *Two-qubit gate percentage:  $\frac{n_{2qg}}{n_g}$* , where  $n_{2qg}$  is the number of two-qubit gates.

- *Decomposed circuit depth:  $d$*

##### 3.1.2. IG (definitions taken from [18])

- *Average shortest path length*: average hopcount between all nodes [64]. The larger the average hopcount between the nodes, the less connected the graph is. It also means that a simpler IG is easier to map.

- *Standard deviation of adjacency matrix  $\sigma(A)$* : an adjacency matrix  $A$  is a square matrix used for representing a graph whose elements are  $a_{ij} = a_{ji}$  represent the number of connections between nodes  $n_i$  and  $n_j$ . It shows which nodes are connected and with how many edges. A large  $\sigma$  value means some specific pairs of qubits interact much more than others and that there is less additional routing required.

- *Diameter*: longest shortest path in the circuit,

$$dm = \max_{n_i \in \mathcal{N}} (\epsilon_i),$$

where  $\epsilon_i$  is the longest hopcount between node  $n_i$  and any other node among the total of  $N$  nodes. The larger the diameter, the simpler the IG and, therefore, easier to map onto a device.

- *Central point of dominance*: maximal betweenness of any node in the graph, where betweenness is the number of shortest paths between nodes that traverse some node or edge [64]. A value of 0 results for complete graphs, and 1 for star-shaped graphs. Values approaching 0 or 1 are undesirable from the perspective of quantum circuit mapping, as 0 reports a graph that is too much connected, and 1 indicates that one qubit is involved in all gates, making the circuit hard to parallelize.

- *Average degree*: average degree of neighbor nodes, where the degree is the number of nodes to which one node is connected and defined as

$$\deg_i = \sum_{j=1}^N a_{ij}.$$

The lower the value of the average degree, the less connected the IG is, and the easier it is to map.

- *Number of maximal cliques*: the total number of the largest all-to-all connected subgraphs. This metric also depends on the size of the maximal clique. The smaller the largest clique, the less connected the graph and, therefore, easier to map.

Another cliques-related graph metric is *clustering coefficient* which measures the cliquishness of a neighborhood. The values range between 0 and 1, where 1 represents a fully connected graph, which is always the worst-case scenario for the quantum circuit mapping:

$$c_i = \frac{\gamma_i}{\binom{\deg_i}{2}},$$

where  $\gamma_i$  is the number of links between neighbors of node  $n_i$ . These two metrics are of high importance for MC computation as they show the presence of highly connected clusters of nodes within the graph, which is related to the IG partitioning part of MC quantum circuit mapping.

**Table 1.** Selected metrics for the characterization of quantum circuits.

| Metric                                      | Metric type             | SC or MC |

|---------------------------------------------|-------------------------|----------|

| Num. of qubits                              | Size                    | Both     |

| Num. of gates                               | Size                    | Both     |

| Two-qubit gate %                            | Size                    | Both     |

| Circuit depth                               | Size                    | Both     |

| Avg. shortest path                          | IG                      | SC       |

| Standard deviation of adjacency matrix      | IG                      | SC       |

| Diameter                                    | IG                      | MC       |

| Central point of dominance                  | IG                      | MC       |

| Maximal cliques and num. of maximal cliques | IG                      | MC       |

| Clustering coefficient                      | IG                      | MC       |

| Avg. degree                                 | IG                      | Both     |

| Vertex/edge reliability                     | IG                      | MC       |

| Coreness                                    | IG                      | MC       |

| Pagerank                                    | IG                      | MC       |

| Critical path length                        | GDG                     | Both     |

| Num. of critical paths                      | GDG                     | Both     |

| GDG path length distribution metrics        | GDG                     | Both     |

| % of gates in critical path                 | GDG                     | Both     |

| Density score                               | Circuit density         | Both     |

| Idling score                                | Circuit density         | Both     |

| Num. of largest rep. sub-circuit            | Sub-circuit repetitions | Both     |

| Size of largest rep. sub-circuit            | Sub-circuit repetitions | Both     |

- *Vertex/edge reliability*: the minimal number of nodes/edges whose removal can disconnect the graph. The lower the reliability, the easier it is to partition the graph for MC mapping.

- *Coreness*: maximal  $k$  for specific node  $i$  such that  $i$  is present in  $k$ -core graph but removed from  $(k+1)$ -core ( $k$ -core is a subgraph of some graph made by removing all the nodes of degree  $\leq k$ ). Coreness as the local metrics also relates to IG partitioning and modular computing.

- *Pagerank*: ranking of the importance of each node in the graph [65] based on the number and weights of the links with other nodes and the rank of those nodes. This graph metric emphasizes which nodes should be mapped to the most connected part of the chip.

### 3.1.3. GDG

One of the main disadvantages of current QPUs is the short lifetime of qubits, i.e. their decoherence. That makes the circuit *scheduling* one of the crucial segments of the quantum circuit compilation. The goal during scheduling is to make the gates run as parallel as possible. However, not every circuit is parallelizable. GDG and especially its *critical path* (longest path in GDG) showcases the minimal necessary duration of the circuit and represents its longest inter-dependent gate sequence. Therefore, this sequence of gates should be scheduled to run as soon as possible in order to shorten the circuit duration and prevent qubit decoherence. Metrics related to critical and other paths of GDG can also tell us how sequential the circuit is and, therefore, how easy it is to map to a single or to multiple cores. Qubits participating in the inter-dependent gates (gates of the same common paths) should be placed nearby on a chip or within the same core during the mapping process. Furthermore, the higher the percentage of the circuit gates included in the critical path, the more sequential the circuit is and, therefore, less parallelizable. Metrics that describe the GDG paths include:

- *critical path length* or number of gates in the critical path;

- *number of critical paths*;

- *path length distribution* and its mean and standard deviation; and

- *percentage of gates included in the critical path*.

These metrics' implementation and detailed definitions are shown in appendix B.

### 3.1.4. Circuit density

This set of metrics evaluates the degree of parallelization of the circuit gates before any optimizations. It indicates the number of gates executed in each layer (time-step) of the circuit relative to the maximum number of gates that could be executed if the circuit were fully parallelized (similar to quantum volume circuits [55]). A denser circuit implies greater difficulty in further optimization and execution. This paper utilizes two metrics to describe this behavior:

- Density score: parallelization level of the circuit;

$$D = \frac{\frac{2*n_{2qg} + n_{1qg}}{d} - 1}{n_q - 1},$$

where  $n_{2qg}$  and  $n_{1qg}$  are number of two- and SC-qubit gates, respectively. This is an extended version of the parallelism metric from [24]: we made a distinction between the SC and two-qubit gates for better preciseness, where  $D$  can actually reach all the values in the range between 0 and 1, (1 is maximal density); and

- Idling score: average amount of qubit idling in the circuit;

$$I = \frac{\sum_{i=1}^{n_q} d - q_i}{n_q * d},$$

where  $q_i$  signifies the number of layers of the circuit in which the qubit is used; range between 0 and 1, with 0 meaning no idling and 1 meaning no scheduled gates.

### 3.1.5. Longest sub-circuit repetitions

In circuits that are based on real algorithms, there are always patterns in terms of gate order and repetitions. In contrast, completely random circuits show, on average, no such patterns. In order to express the randomness of the gates and groups of gates in circuits, we have defined the following metrics

- the number of occurrences of the largest repetitive sub-circuit; and

- the size of this largest repetitive sub-circuit.

The extraction of these two metrics relies on existing algorithms used for strings of characters. The problem of finding the longest repeating sub-string in a text and the length thereof is efficiently solved by filling a data structure called a *suffix tree*[66]. We used the same implementation by identifying characters and quantum gates. The significance of gate randomness on circuit performance is closely tied to the type of mapper employed. Some mappers are expected to exhibit a high correlation, where the routing algorithm is designed to identify gate patterns in advance. In contrast, more stochastic approaches do not benefit from recognizing these patterns.

The IG parameters reveal patterns necessary for initial placement algorithms, whereas GDG parameters indicate the length and sequential nature of the circuit, crucial for mitigating decoherence and enhancing scheduling and routing. Parameters related to circuit density illustrate the extent of parallelization in the circuit before optimization, influencing the complexity of all stages of quantum circuit mapping. Additionally, identifying recurring gate patterns in the circuits assists in refining scheduling and look-ahead routing techniques. For the complete list of metrics, please refer to [11] (IG-based) and appendices D and C.

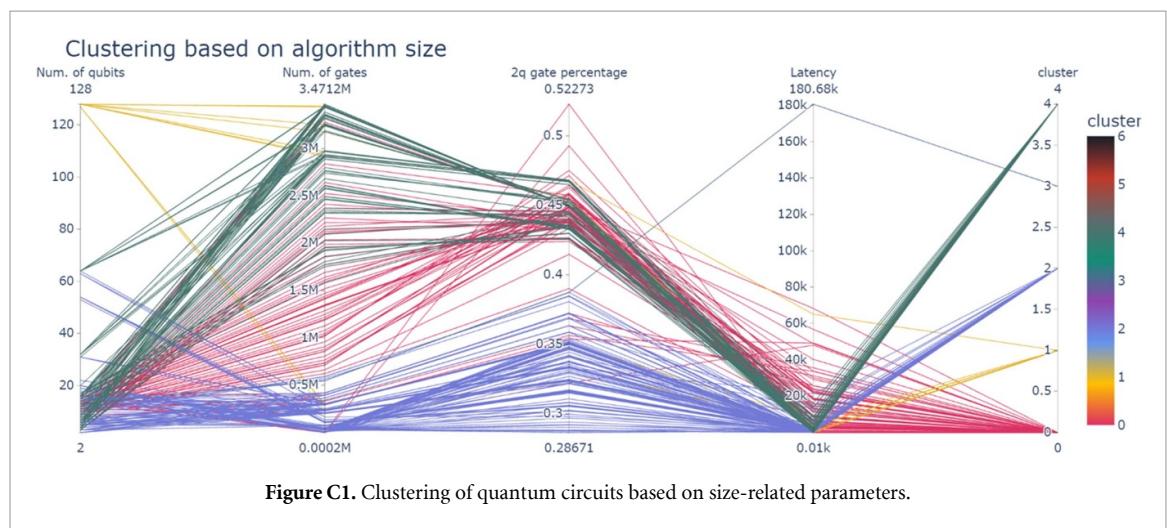

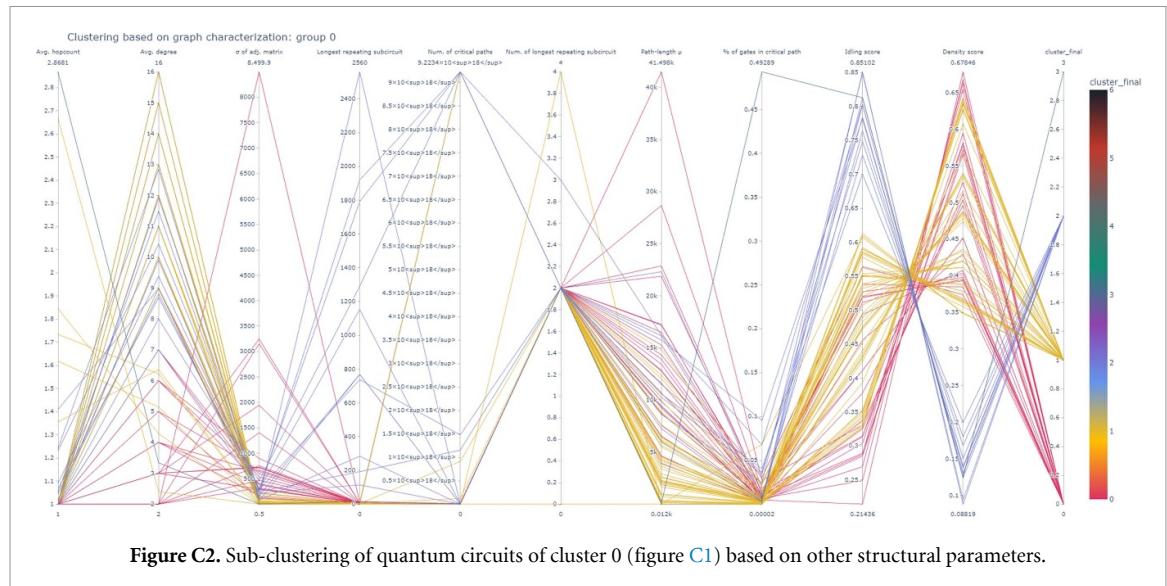

## 3.2. Quantum circuit clustering

As previously stated, one of our objectives is to identify structural similarities among quantum circuits and establish ‘circuit families’, wherein the constituent elements (i.e. the quantum circuits) exhibit similar compilation behavior and require comparable hardware resources. For this purpose, we employed a two-step clustering approach: an initial clustering of circuits based on size parameters (Group 1), followed by clustering based on the remaining parameters. This strategy was implemented to prevent size parameters from exerting undue influence on the clustering algorithm. Consequently, we initially categorized the set of 341 selected benchmarks (see section 4) into five clusters using the K-means clustering algorithm [67]. Subsequently, each of the five size-related clusters could be further subdivided into sub-clusters based on the previously described structural circuit parameters (groups 2-5). In this regard, we once again opted for the K-means algorithm after evaluating various methods and parameter configurations using the silhouette coefficient method [68]. The specific settings for clustering SC and MC devices, as well as the clusters themselves, are detailed or referred to in appendices C and D, respectively. It is expected that circuits assigned to the same sub-cluster will exhibit similar fidelity and gate overhead outcomes. The correlation between our circuit groups and mapping performance metrics, as well as potential explanations for these relationships, will be discussed in the subsequent sections.

## 4. Methodology

In our research, the quantum circuit profiling process encompasses the following four steps:

- (i) **Benchmark collection**—we gather benchmarks (i.e. quantum circuits) from diverse sources, translate them into the same quantum language (in our case cQASM [69]), and extract their interaction and GDGs [18].

- (ii) **Parameter selection and extraction**—we select and extract graph-theory-based parameters from the qubit IG and GDG, focusing on parameters relevant to mapping quantum circuits to SC and MC devices. Additionally, we extract supplementary circuit parameters to enhance the characterization related to circuit density.

- (iii) **Benchmark clustering**—we cluster benchmarks based on their size-related (number of qubits and gates, two-qubit gate percentage, and circuit depth) and structure-related parameters.

- (iv) **Compilation**—we compile the quantum circuits using Qiskit [70], OpenQl [71], and additional MC compilation solutions [61, 62], and analyze the relationship between their performance and the extracted parameters, as well as their cluster affiliation (see section 5).

### 4.1. Quantum benchmarks selection

In this paper, we employed the qbench benchmark set [18, 22], which offers a comprehensive collection of quantum circuits sourced from various platforms and written in different programming languages. This set encompasses a range of circuit types categorized based on their origin, including circuits derived from real quantum algorithms (e.g. QFT), simpler algorithm-based circuits (such as arithmetic circuits), QUEKO circuits optimized for specific devices [72], and randomly generated circuits produced by randomly selecting SC and two-qubit gates from a predefined set and applying them to arbitrarily chosen qubits or qubit pairs [73]. This category also includes highly parallelized quantum volume circuits used for device benchmarking [74].

Given the inclusion of MC architectures in our study, we also incorporated benchmarks used so far for MC computations [3, 12, 58, 61]. These benchmarks comprise a variety of circuit instances, ranging from 16 to 128 qubits, such as the Cuccaro Adder [75], Grover's main routine, GHZ state preparation [76], QFT, QAOA, and VQE [77]. To accommodate this aspect, we expanded our synthetic circuit set to include instances with up to 128 qubits. The complete list of 341 quantum circuits utilized in our study is detailed in appendix A, with accompanying code available at [22].

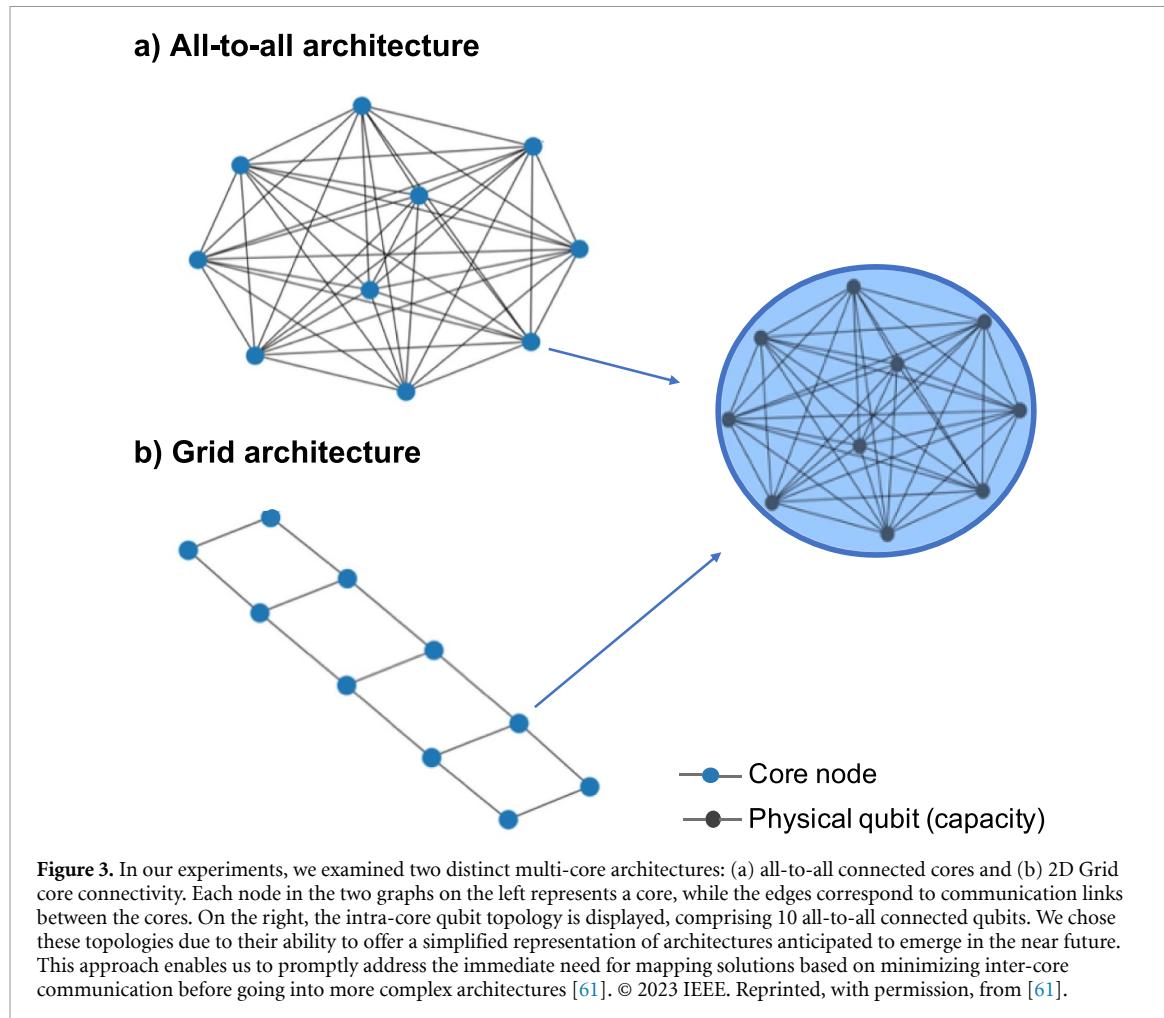

### 4.2. Hardware configuration

To investigate the relationship between the previously identified circuit clusters (see section 3) and the mapping outcomes, we compiled the selected quantum circuits using various target SC and MC quantum architectures. For SC architectures, we utilized the Rigetti Aspen-1, Surface-17 [32], IBM Rochester, and Google Bristlecone devices, as depicted in [32, 78–80]. Regarding modular architectures, we adopted the same configuration as detailed in [61]: all-to-all connected qubits within the cores, while the cores themselves are interconnected either in an all-to-all manner or in a grid-like fashion, as illustrated in figure 3. These device configurations were selected because they are commonly employed in quantum circuit mapping research and offer realistic and diverse connectivity patterns in their coupling graphs. Note, that we did not execute the quantum circuits on actual devices; instead, the hardware constraints of the devices were considered during the compilation process alone.

### 4.3. Quantum compilers

In this study, we investigate not only the relationship between different quantum circuit groups, parameters, and quantum devices but also explore the connection between quantum circuits and mapping techniques. The goal is to gain insights into developing and selecting mapping techniques tailored to circuits with specific common properties.

For SC devices, we utilize the widely used Qiskit compiler and test four combinations of compilation settings by pairing two routers with two optimization levels. Specifically, we employ the Stochastic and Sabre routers, along with optimization levels 1 and 2. The key distinction between the Stochastic and Sabre approaches lies in their routing path selection: Sabre utilizes a more deterministic approach, whereas Stochastic employs a more randomized strategy. Optimization level 1 involves simplistic mapping with minimal circuit optimization but short runtime, while optimization level 2 employs more aggressive gate

cancellation and commutation techniques to minimize qubit crosstalk and increase parallelism. Level 2 is suitable for complex circuits or cases in which circuit optimization is crucial despite requiring more computational resources and time during compilation. For simplicity, we will refer to these four method combinations as *Stochastic1*, *Stochastic2*, *Sabre1*, and *Sabre2*.

In the modular regime, we explore three techniques:

- The *time-sliced circuit partitioning rOEE* method [12], which leverages qubit clustering to create tractable partitioning heuristics for mapping quantum circuits to modular physical machines one slice at a time. This method also uses a tunable lookahead scheme to reduce the cost of moving to future time slices. Note that even though this method is mainly focused on reducing the number of inter-core operations, the gates in the time-slices are scheduled to run as concurrently as possible in order to reduce the circuit depth as well.

- The Hungarian qubit assignment (HQA) algorithm [62], which employs the Hungarian algorithm [81] to enhance qubit-to-core assignment by considering interactions between qubits across the entire circuit, and enabling fine-grained partitioning and enhanced qubit utilization.

- A QUBO-based approach [82], which encodes qubit allocation and inter-core communication costs in binary decision variables [61]. This method splits the quantum circuit into slices and formulates the qubit assignment as a graph partitioning problem for each slice, reducing costly inter-core communication by penalizing that. The final solution minimizes the overall cost across all circuit slices. It is important to note that unlike the rOEE method, this method includes different type of time-slicing, where gates are scheduled within the same time-layer as long as they can be run without imposing new inter-core operations, sometimes resulting in multiple gates run on the same qubits.

#### 4.4. Performance metrics

**Quantum circuit mapping performance** metrics are defined as follows:

- (i) **Gate overhead** is calculated using the formula:  $G_{\text{overhead}} = \frac{(G_{\text{after}} - G_{\text{before}})}{G_{\text{before}}}$ . Here,  $G_{\text{before}}$  and  $G_{\text{after}}$  denote the number of gates before and after compilation, respectively.

- (ii) **Depth overhead** is determined by:  $D_{\text{overhead}} = \frac{(D_{\text{after}} - D_{\text{before}})}{D_{\text{before}}}$ , where  $D_{\text{before}}$  and  $D_{\text{after}}$  represent the circuit depth before and after compilation. Depth refers to the number of cycles or layers of simultaneously running gates in the circuit.

- (iii) **Fidelity decrease** is computed as:  $F_{\text{decrease}} = \frac{(F_{\text{before}} - F_{\text{after}})}{F_{\text{before}}}$ . Here,  $F_{\text{before}}$  and  $F_{\text{after}}$  represent the circuit fidelity before and after compilation, respectively. *Circuit fidelity* is a product of the error rates of the gates in the circuit. The primary objective during circuit mapping is to maximize this metric. We assumed uniform error rates for all one-qubit and two-qubit gates, using average values from the Starmon-5 chip [69, 83, 84].

- (iv) **Number of non-local (inter-core) communications** is the number of qubit moves from one core to another within modular quantum architectures. Entanglement-based quantum communication protocols are employed that require bell-pair generations that enable the teleportation of quantum states. However, generating entangled pairs results in a resource overhead, and the process itself is non-deterministic, adding complexity to scheduling tasks [3].

In the following section, we will discuss the relation of the structural parameters of circuits from section 4.1 with the above-stated obtained metrics after mapping them into different combinations of quantum system setups mentioned in sections 4.2 and 4.3.

## 5. Results and discussion

In this section, we assess and contrast the mapping results of our chosen circuits while examining the influence of circuit parameters on the outcomes. Furthermore, we juxtapose the performance of various circuit clusters using different mapping techniques and processor designs.

### 5.1. Mapping to SC devices

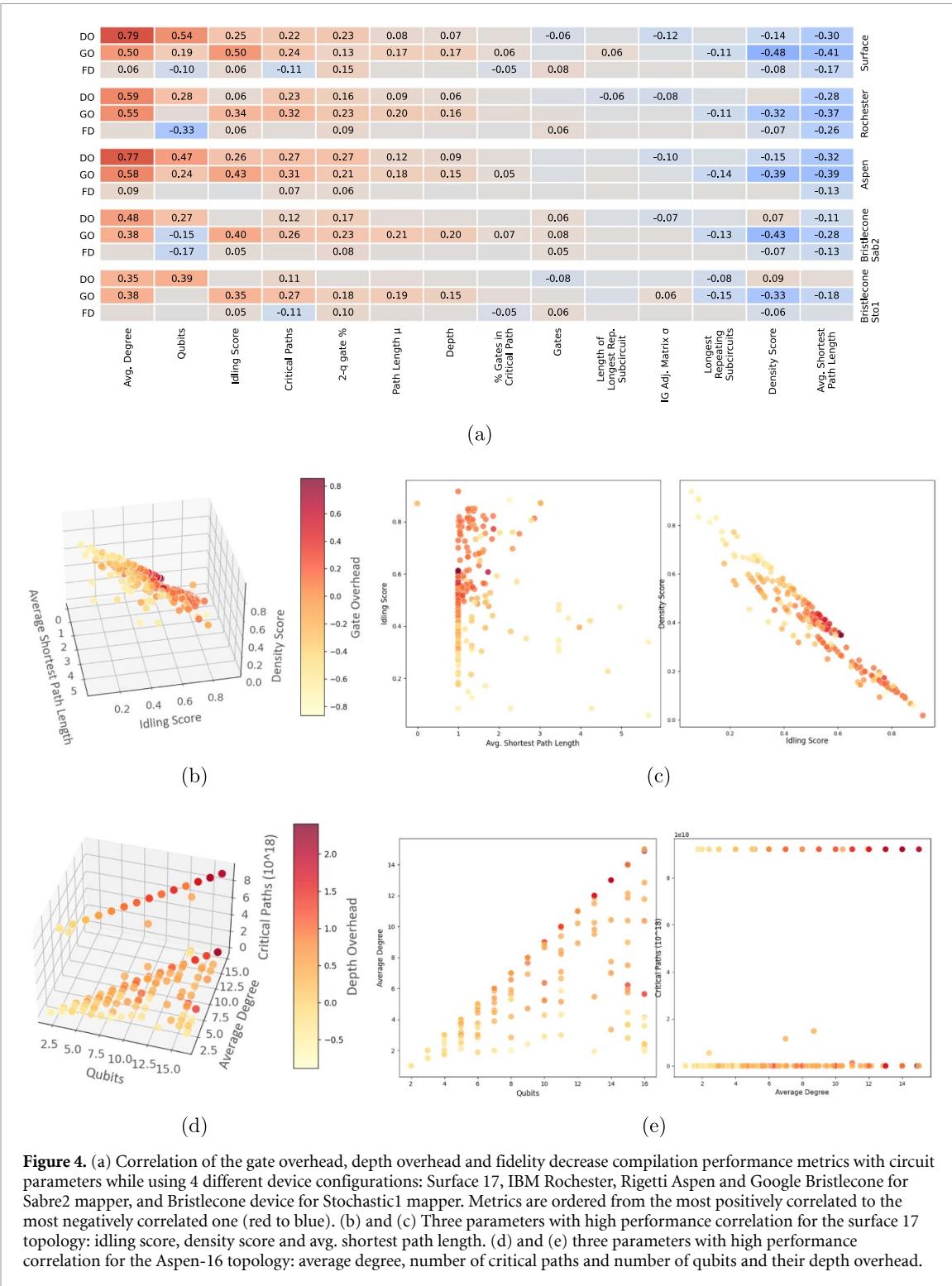

We begin our analysis by examining the correlation between the circuit parameters introduced in section 3 and the three quantum circuit mapping performance metrics across four different SC architectures: Surface 17, IBM Rochester, Rigetti Aspen, and Google Bristlecone (see [32, 78–80]). The correlations are visualized in figure 4(a) using a Pearson correlation map, where the correlation values range from dark red for the highest positive correlation to dark blue for the highest negative correlation. A positive correlation means that if values of one parameter increase, then so do of the other, and a negative is vice versa. White color, and correlation factors around zero indicate no significant correlation. The parameters are sorted to facilitate the identification of the most correlated ones. Notably, while some parameters are consistently important across all devices and metrics, others are not significant (e.g. the number of gates), and some vary in importance depending on the metrics and devices (e.g. the number of qubits has a high negative correlation factor only for the fidelity decrease in the IBM Rochester device). In addition to the analysis of the four devices using the same mapping technique (Sabre2), figure 4(a) also includes results for two different mapping configurations, namely Stochastic1 and Sabre2 (see section 4.3), for the Google Bristlecone device. The configurations Stochastic2 and Sabre1 are not shown, as their correlation results are similar to Stochastic1 and Sabre2, respectively. This suggests that the routing technique is more significant than other optimization passes concerning different circuit parameters. For the same reason, we opted to use Sabre2 and Stochastic1 for the rest of the experiments explained in this section.

To investigate the meaning of these correlations, we plotted 3D graphs of some of the highest-correlated parameters. As examples, we selected: (1) the gate overhead metric for the Surface 17 device with parameters: average shortest path length, density score, and idling score, shown in figure 4(b), and (2) the depth overhead metric for the Rigetti Aspen device with circuit parameters: number of qubits, average IG degree, and number of critical paths, shown in figure 4(d). In figure 4(b), we observe that the average shortest path length and density score metrics are negatively correlated with the gate overhead, meaning that higher values of these metrics correspond to a lower gate overhead. Conversely, the idling score shows a positive correlation. This implies that a higher average shortest path length simplifies running the circuit due to a simpler IG, confirming our hypotheses in section 3.1.2. In figure 4(d), the average degree of the IG is shown

**Figure 4.** (a) Correlation of the gate overhead, depth overhead and fidelity decrease compilation performance metrics with circuit parameters while using 4 different device configurations: Surface 17, IBM Rochester, Rigetti Aspen and Google Bristlecone for Sabre2 mapper, and Bristlecone device for Stochastic1 mapper. Metrics are ordered from the most positively correlated to the most negatively correlated one (red to blue). (b) and (c) Three parameters with high performance correlation for the surface 17 topology: idling score, density score and avg. shortest path length. (d) and (e) three parameters with high performance correlation for the Aspen-16 topology: average degree, number of critical paths and number of qubits and their depth overhead.

to be highly influential for the depth overhead: a higher degree indicates a denser IG, leading to a larger depth overhead. The number of qubits and the number of critical paths also exhibit positive correlations.

The reasoning behind these results can be summarized as follows:

- **Average shortest path length (hop count) and gate overhead:** a negative correlation is observed between the average shortest path length (or hop count) and the gate overhead, particularly in the case of the surface-17 device. This stems from the fact that a higher number of hops in the IG indicates poor connectivity. A poorly connected IG is easier to map onto grid-like architectures such as the Surface-17, as discussed in [18], resulting in fewer additional SWAP gates required to run the algorithm and, consequently, lower gate overhead.

- **Idling score and gate overhead:** a positive correlation is found between the idling score and gate overhead across all devices, especially with Surface-17. As described in section 3, the idling score ranges from 0 (no idling) to 1 (maximum average qubit idling). This correlation arises from both the limited connectivity of the device and the mapping techniques that employ lookahead strategies to minimize the number of SWAP gates for the immediate portion of the circuit. In circuits with higher idling, gates are spread across more time slices, reducing the effectiveness of such optimizations.

- **Density score and gate overhead:** the density score, which measures the degree of parallelization in the circuit, is negatively correlated with gate overhead. This is essentially the inverse of the idling score: circuits with higher parallelization tend to have lower gate overhead due to better optimization opportunities.

- **Average degree of the IG and overhead:** the average degree of the IG is positively correlated with both gate and depth overhead. As outlined in section 3, the average degree reflects the connectivity of the IG. Highly connected qubits in the IG make it difficult to map onto weakly connected architectures like Aspen-16, naturally leading to increased overhead for circuits with more complex topologies.

- **Number of qubits and depth overhead:** a positive correlation exists between the number of qubits and the depth overhead. This is due to both the device topology and the challenges of the mapping technique itself. With higher qubit counts, routing becomes more complex, as fewer ancillary qubits are available for routing, and the options for optimal initial placement decrease. These factors lead to more qubit idling during routing, which increases the circuit depth.

- **Number of critical paths and depth overhead:** the number of critical paths also shows a positive correlation with depth overhead. In all experiments, circuits with more critical paths (where many paths in the GDG are of equal largest length) create scheduling and gate prioritization challenges for the compilation algorithms, reducing their ability to optimize the circuit's overall latency.

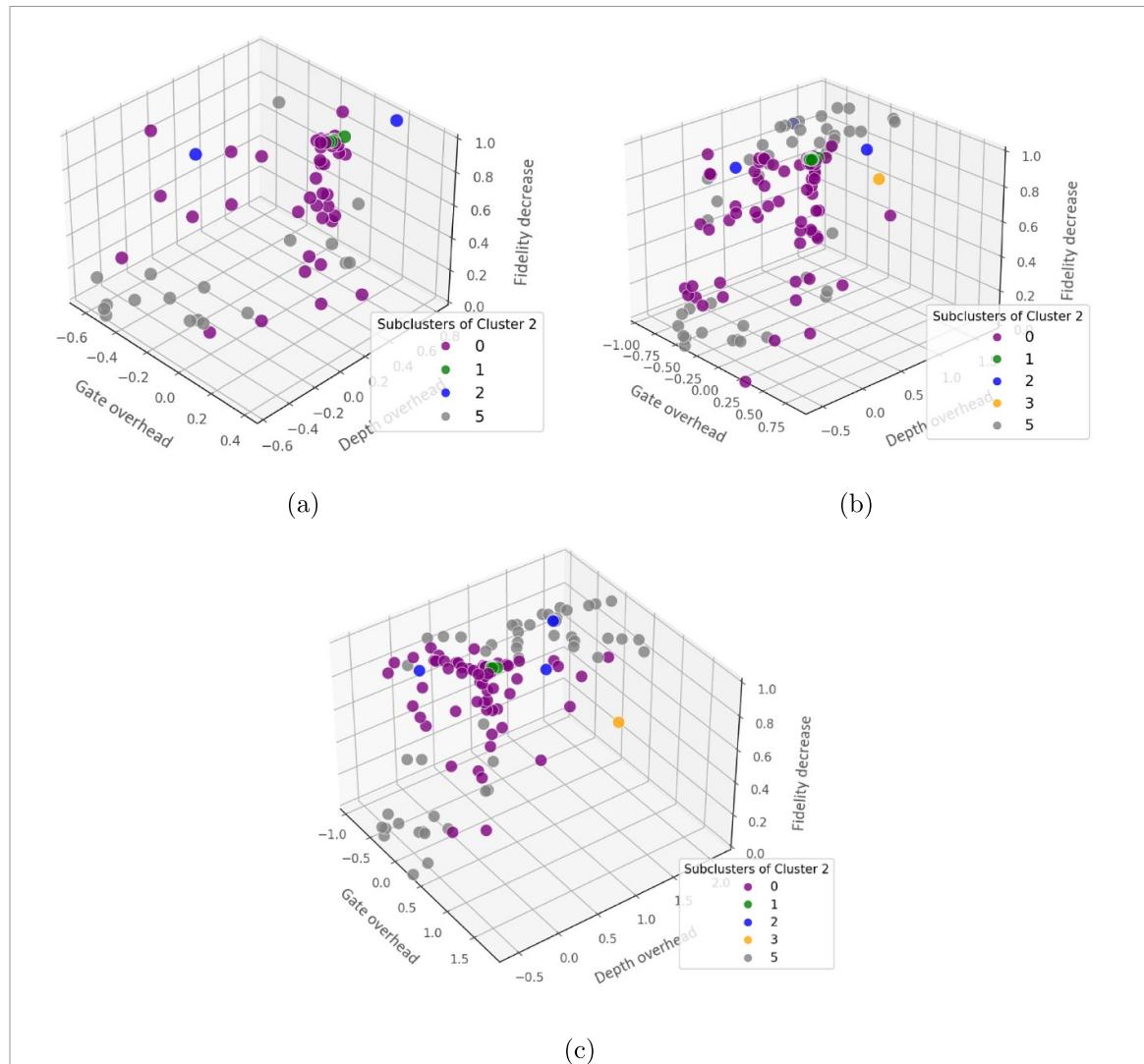

In the next part of our work, we created ‘circuit families’ containing circuits of similar structure based on extracted features. The two-level clustering approach used to achieve this is explained in section 3.2. Figure 5 presents examples of these created families and their results concerning the three compilation metrics. Figures 5(a)–(c) illustrate performance differences when targeting Surface 17, Bristlecone using Sabre2 mapper, and Bristlecone using the Stochastic1 mapper, respectively. Notably, the group of circuits marked in purple (Group 0) performed better on average with Bristlecone than on Surface 17, exhibiting approximately 20% fewer gates. Conversely, the group noted in grey (Group 5) performed better on Surface 17, particularly in terms of fidelity decrease, which remained below 40% except for one outlier. In contrast, for the Bristlecone device, the majority of benchmarks for this group ranged between 60% and 100%. The Stochastic1 mapper generally performed worse than Sabre2, as expected due to its simplicity. For example, Group 3 (yellow) reached 150% in gate overhead, and Group 5 reached 200% in depth overhead, whereas these metrics for Sabre2 were 75% and 150%, respectively. However, Group 0 did not show significant performance differences between the two mappers, with benchmarks performing within the same ranges (mostly between  $\sim 50\%$  and  $\sim 50\%$ ) regarding gate and depth overhead. In this case, it would be preferable to use the simpler and faster Stochastic1 method. It is important to note that the majority of circuits in Group 0 are real-algorithm-based circuits, including many instances of Grover’s algorithm [77], Cuccaro adder [75] and RevLib [85] algorithms. On the other hand, most circuits in Group 5 are QUEKO circuits [72]. This analysis provides guidance on which types of circuits work better with specific device/mapper configurations.

The Aspen and Rochester device configurations exhibited patterns very similar to Surface 17 and Bristlecone, respectively, for these particular circuit families. Therefore, they were not showcased in this paper. For the rest of the results, refer to appendix D.

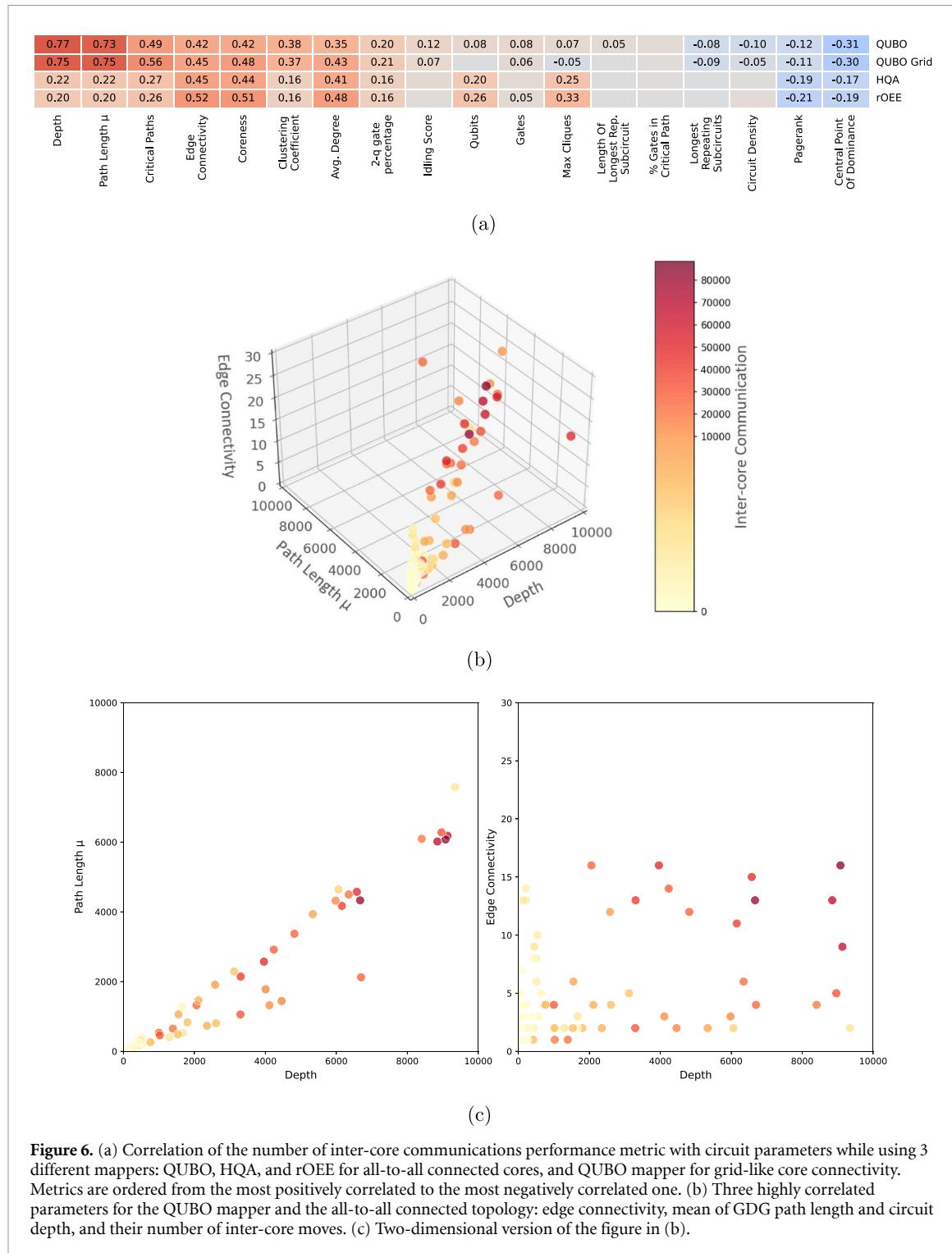

## 5.2. From SC to MC architectures

Our analysis continues by examining the correlations between the number of inter-core communications and circuit parameters using three different mapping configurations for all-to-all connected MC devices: QUBO, HQA, and rOEE, as introduced in section 4. (see figure 6). Notably, the importance of circuit parameters differs among the mapping techniques. For instance, the number of qubits and maximal cliques is positively correlated with the performance when using HQA, but not with other techniques. Circuit depth and GDG path length mean exhibit a high correlation score (approximately 0.75) with QUBO, while the scores are only 0.2 and 0.4 for the other two mappers. Edge connectivity is not influential when using rOEE, but it is for the other two mappers. Additionally, we explored two different core topologies with the QUBO mapper: all-to-all and grid. Generally, the parameter correlations between these topologies are similar, though some differences exist. For example, the average degree circuit parameter is significantly more important for grid connectivity due to the less connected device connectivity graph, emphasizing the importance of IG connectivity of the circuit, as expected in section 3. We anticipate a larger difference when also reducing the connectivity within the cores, an experiment we leave for future work.

**Figure 5.** Relation of circuit families (sub-clusters) of cluster 2 with their compilation metrics when targeting: (a) Surface 17, (b) bristlecone for Sabre2 mapper, and (c) bristlecone for Stochastic1 mapper.

Figure 6(b) shows an example of the correlation between parameters: edge connectivity, GDG path length mean, and circuit depth, with the number of inter-core communications when using the QUBO mapper. A trend is observed where overhead increases with higher metrics values, confirming the high positive correlation shown by their correlation factors in figure 6(a).

The reasoning behind this can be summarized as follows:

- **Initial circuit depth and inter-core communications:** there is a positive correlation between the initial circuit depth and the number of inter-core moves (communications). For methods like QUBO, which aim to minimize inter-core moves by optimizing each time-slice globally, mapping a circuit with significant depth onto a MC architecture is highly challenging and requires substantial computational resources. This difficulty leads to increased overhead. Leveraging quantum devices like D-Wave could potentially alleviate this issue [86].

- **Average GDG path length and inter-core moves:** a positive correlation is observed between the average GDG path length and the number of inter-core moves. Longer GDG paths result in greater circuit depth, which, as mentioned earlier, is correlated with higher overhead. Additionally, longer GDG paths complicate scheduling and partitioning for mapping techniques like QUBO, further contributing to the difficulty of optimizing these circuits.

- **IG edge connectivity and inter-core moves:** The number of inter-core moves also positively correlates with the edge connectivity of the IG. High edge connectivity makes it challenging to divide the graph into independent subgraphs, making it difficult to map the IG across multiple cores in a MC architecture. As a result, more inter-core communications are required to facilitate interactions between qubits, increasing the overhead.

**Figure 6.** (a) Correlation of the number of inter-core communications performance metric with circuit parameters while using 3 different mappers: QUBO, HQA, and rOEE for all-to-all connected cores, and QUBO mapper for grid-like core connectivity. Metrics are ordered from the most positively correlated to the most negatively correlated one. (b) Three highly correlated parameters for the QUBO mapper and the all-to-all connected topology: edge connectivity, mean of GDG path length and circuit depth, and their number of inter-core moves. (c) Two-dimensional version of the figure in (b).

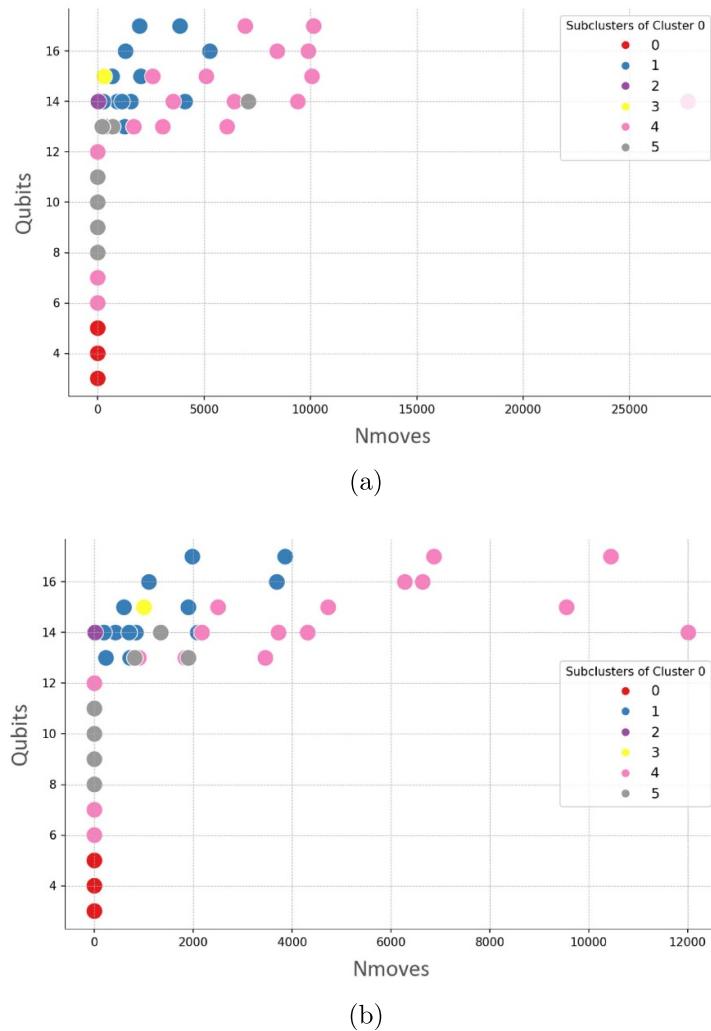

Similar to SC devices, we also analyze circuit families and their performance patterns for modular architecture. Figure 7 shows the groups of circuits that are part of size cluster 0 and their number of moves (inter-core communications) for the two mappers, HQA (a) and rOEE (b). Overall, the HQA mapper performed better, scaling up to 10 000 moves (with only one outlier with 25 000) compared to 12 000 for rOEE. rOEE reached that number only for group 4 (pink), making HQA a better choice for this group. Group 0 performed particularly well with both mappers, with all benchmarks having up to 100 moves. Group 4 showcased the worst performance for HQA, reaching up to 10 000 moves, but still significantly better than rOEE. Groups 1 and 5 (blue and grey, respectively), on the other hand, showed, on average, a better performance with rOEE, where group 5 outperformed most other groups, despite the higher qubit count. Note that here we do not showcase QUBO results due to lower amount of successfully compiled instances, which would lead to unfair comparison. The results are however available at location shown in appendix D.

**Figure 7.** Relation of circuit families (sub-clusters) of cluster 0 with the number of inter-core communications when using all-to-all core connectivity and (a) HQA mapper and (b) rOEE mapper.

The main insights are as follows:

- there is an evident correlation between the structural parameters of the circuits and their performance, which varies with different compilation and device configurations. This confirms that adapting the quantum system layers to the circuit properties and employing hardware-software co-design is key to successful quantum circuit execution.

- It is possible to make appropriate compilation/device choices per circuit family instead of per single circuit, as there are preferred combinations of device and compilation for each group of similar circuits.

- IG parameters are most important for less connected device topologies.

- Idling and density scores are always of high importance for SC devices.

- GDG-related parameters and circuit depth are the most relevant metrics for modular architectures, and they are more significant than for SC architectures.

- Contrary to our expectations, standard parameters like the number of gates, qubits, and the percentage of two-qubit gates, as well as repetitive sub-circuit metrics, are not that significant for circuit success rates.

### 5.3. Evaluating clusters based on circuit origin

The final part of this section showcases the types of clusters created based on the origin of the circuits. We aim to validate that circuits within the same families exhibit similarities not only in their extracted structural parameters but also in their origin. For instance, it stands to reason that randomly generated circuits would share similar structural parameters. This validation would also support the comprehensiveness of the parameter set we used to describe the circuits.

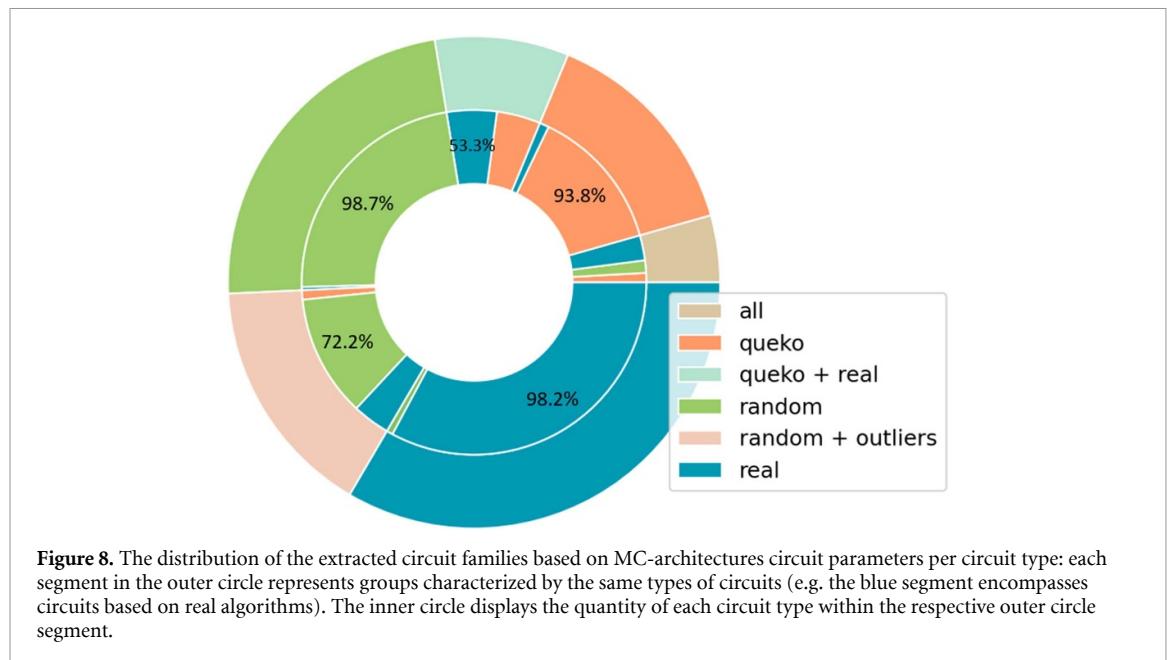

For this purpose, we labeled three groups: real algorithms (based on actual quantum algorithms like Grover's or arithmetic circuits), randomly generated circuits, and QUEKO circuits (synthetic circuits with predefined depth and gate count)[72]. The circuits were sourced from [22]. Figure 8 shows the distribution of the existing sub-circuits after a two-level clustering for the modular-architecture-related metrics. We observe that circuits with the same origin generally belong to the same group, with a few outliers. The exceptions are a very small percentage of mixed benchmarks (noted in light brown) and sub-clusters containing both QUEKO and real benchmarks (in mint-green). Since QUEKO circuits aim to mimic realistic behavior more closely than classical random circuits [72], the existence of these mixed groups is expected. The mixed benchmarks group comprises those circuits that are structurally unique compared to other circuits of the same type. This figure confirms that our defined circuit parameters effectively identify structural similarities between circuits, especially highlighting the distinction of randomly generated circuits (green) compared to the other two types that contain logical patterns and oracles.

The complete set of results (for all benchmarks, clusters, compilers and devices) can be found at <https://github.com/QML-Group/QuantumCircuitProfiling>.

## 6. Conclusion

To advance the development of future quantum computers and increase the probability of successfully executing algorithms that are currently unfeasible on classical computers, it is crucial to understand their structure. Quantum circuits (i.e. executable versions of quantum algorithms) will yield the highest success rates when run on a quantum system tailored for it. In classical computing, we see two trends that could also shape the future of quantum computers: a) application-specific devices optimized for particular tasks, and b) MC computation as a solution for current scalability problems.

In this paper, we explored these aspects within the quantum computing field by introducing the most comprehensive characterization of quantum circuit structures to date. This characterization addresses all facets of quantum circuits: circuit size, qubit interactions, gate density and dependencies, and repetitive patterns. For this purpose, we defined 15 and 19 circuit features of importance for SC and MC quantum devices, respectively. We made special emphasis on modular (i.e. MC) architectures, which represent the future of quantum computing and a solution to the scalability challenge of current NISQ devices. MC architecture and related compilation techniques function differently than current quantum systems, because the focus is primarily on reducing the expensive communication between cores. Consequently, extra circuit parameters should be considered for MC architectures.

The extracted parameters were used to create families of similarly structured circuits by utilizing the k-means clustering technique. Identifying circuit families simplifies the development of high-performance architectures (by optimizing for families instead of individual circuits), helps to create a representative set of circuits (using cluster representatives), and aids in approximating the performance of future circuits without running them. We also analyzed the types of circuits within the clusters and found that similarly created

circuits (real-algorithms, QUEKO, uniformly random) are mostly grouped together. This confirms that our characterization can comprehensively describe a circuit and identify structural similarities between different ones.

Furthermore, we conducted experiments with six different devices and seven mapping configurations to showcase varying correlation levels and performance patterns in terms of gate overhead, depth overhead, fidelity decrease, and number of inter-core communications metrics. These experiments revealed which parameters influence circuit success rates the most, and how these correlations change with different devices or compilers. We could also see that some mappers scale better with the same circuit families than others (e.g. HQA vs. rOEE mapper). Therefore, the patterns observed in clustered circuits can help identify the best existing mapper and device to use, particularly for higher numbers of qubits.

In our future work we plan to:

- **expand the set of benchmarks used in the clustering procedure:** the current set of benchmarks is limited in terms of the number of instances per algorithm. We aim to achieve more precisely defined clusters of algorithms by using a more balanced number of instances for each algorithm, covering a wider range of qubit counts. Additionally, we intend to incorporate synthetically-generated real algorithm-like circuits, described in [87].

- **broaden the range of technologies and mapping techniques:** we plan to explore how different circuit properties impact results across a broader set of quantum technologies and corresponding mapping techniques. This will provide a comparative analysis to the findings of our current research;

- **incorporate inter-core traffic parameters for modular architectures:** we aim to integrate inter-core traffic parameters for modular quantum architectures, as introduced in [58], to investigate how these parameters are influenced by circuit characteristics;

- **conduct design space exploration of full-stack quantum computing systems:** we will perform an exploration of the full design space, including circuit properties, compiler options, and a variety of quantum devices. This will allow us to develop architectural design guidelines for future quantum systems;

- **leverage circuit parameters for performance prediction:** finally, we aim to utilize circuit parameters to predict the performance of different mapper-device setups, providing insights into optimizing performance across various quantum computing configurations.

Overall, the proposed method and current findings can aid in the development of quantum systems by incorporating information about circuit structure and providing deeper insights into the variability of outcomes when executing different quantum circuits. Structural parameters of circuits can also be used to predict fidelity decrease, gate overhead, and depth overhead for specific processors and compilation techniques without executing them on actual devices. This can facilitate the co-design of quantum compilers, processors, and applications, ultimately contributing to the development of high-performance application-specific quantum systems. An in-depth analysis of quantum circuits used for benchmarking quantum computing systems is a systematic approach that directly contributes to assessing current devices and lays the foundation for designing future scalable architectures.

## Data availability statement

The data that support the findings of this study is openly available following an embargo at the following URL/DOI: <https://github.com/QML-Group/QuantumCircuitProfiling> [88].

## Acknowledgment

S F and M B acknowledge funding of Intel Corporation. CGA acknowledges funding from the Spanish Ministry of Science, Innovation and Universities through the Beatriz Galindo program 2020 (BG20-00023), from project PCI2022-133004 funded by MCIN/AEI/10.13039/501100011033 and by the European Union NextGenerationEU/PRTR, and from the Ministry for Digital Transformation and of Civil Service of the Spanish Government through the QUANTUM ENIA project call—Quantum Spain project, and by the European Union through the Recovery, Transformation and Resilience Plan—NextGenerationEU within the framework of the Digital Spain 2026 Agenda. C G A, E A and S A also acknowledge support from the E U, grant HORIZON-EIC-2022-PATHFINDEROPEN-01-101099697. Finally, S A acknowledges support from the E U, Grant ERC-StG-2021-WINC-101042080.

## Appendix A. Selected quantum benchmarks

**Table A1.** Benchmarks used for the experiments.

| Benchmark             | Qubits | Gates  | Two-qubit gate percentage |

|-----------------------|--------|--------|---------------------------|

| 0410 184_169          | 14     | 211    | 0.49 289 0995             |

| 15_enc                | 15     | 264    | 0.52 272 7273             |

| 16QBT_100CYC_QSE_1    | 16     | 1400   | 0.327 142 857             |

| 16QBT_10CYC_TFL_1     | 16     | 1473   | 0.330 617 787             |

| 16QBT_15CYC_TFL_2     | 16     | 1582   | 0.335 651 075             |

| 16QBT_20CYC_TFL_3     | 16     | 1727   | 0.341 053 851             |

| 16QBT_35CYC_TFL_6     | 16     | 1980   | 0.348 484 848             |

| 16QBT_40CYC_TFL_7     | 16     | 2269   | 0.355 222 565             |

| 16QBT_500CYC_QSE_3    | 16     | 7949   | 0.302 679 582             |

| 16QBT_700CYC_QSE_5    | 16     | 15 901 | 0.292 182 882             |

| 16QBT_900CYC_QSE_7    | 16     | 26 125 | 0.288 076 555             |

| 20QBT_100CYC_QSE_8    | 20     | 27 545 | 0.287 747 323             |

| 20QBT_400CYC_QSE_8    | 20     | 33 225 | 0.286 711 813             |

| 20QBT_45CYC_0D1_1D2_0 | 15     | 33 270 | 0.287 676 586             |

| 20QBT_45CYC_0D1_1D2_5 | 13     | 33 315 | 0.288 638 751             |

| 20QBT_45CYC_0D1_2D2_0 | 20     | 33 405 | 0.290 555 306             |

| 20QBT_45CYC_0D1_2D2_5 | 20     | 33 495 | 0.292 461 561             |

| 20QBT_45CYC_0D1_2D2_9 | 20     | 33 585 | 0.294 3576                |

| 20QBT_45CYC_0D1_3D2_0 | 20     | 33 720 | 0.297 182 681             |

| 20QBT_45CYC_0D1_3D2_5 | 20     | 33 855 | 0.299 985 231             |

| 20QBT_45CYC_0D1_3D2_9 | 20     | 33 990 | 0.302 765 519             |

| 20QBT_45CYC_0D1_4D2_0 | 20     | 34 170 | 0.306 438 396             |

| 20QBT_45CYC_0D1_5D2_1 | 20     | 34 395 | 0.310 975 432             |

| 20QBT_45CYC_0D1_6D2_2 | 20     | 34 665 | 0.316 342 132             |

| 20QBT_45CYC_0D1_7D2_3 | 20     | 34 980 | 0.322 498 571             |

| 20QBT_45CYC_0D1_8D2_4 | 20     | 35 340 | 0.329 400 113             |

| 20QBT_45CYC_1D1_1D2_5 | 20     | 35 475 | 0.329 415 081             |

| 20QBT_45CYC_1D1_2D2_6 | 20     | 35 655 | 0.330 276 259             |

| 20QBT_45CYC_1D1_3D2_7 | 20     | 35 880 | 0.331 967 67              |

| 20QBT_45CYC_1D1_4D2_8 | 20     | 36 150 | 0.334 467 497             |

| 20QBT_45CYC_1D1_5D2_9 | 20     | 36 465 | 0.337 748 526             |

| 20QBT_45CYC_1D1_6D2_0 | 20     | 36 825 | 0.341 778 683             |

| 20QBT_45CYC_1D1_7D2_1 | 20     | 37 230 | 0.346 521 622             |

| 20QBT_45CYC_2D1_2D2_3 | 20     | 37 500 | 0.346 426 667             |

| 20QBT_45CYC_2D1_3D2_4 | 20     | 37 815 | 0.347 110 935             |

| 20QBT_45CYC_2D1_4D2_5 | 20     | 38 175 | 0.348 552 718             |

| 20QBT_45CYC_2D1_5D2_6 | 20     | 38 580 | 0.350 725 765             |

| 20QBT_45CYC_2D1_6D2_7 | 20     | 39 030 | 0.353 599 795             |

| 20QBT_45CYC_3D1_1D2_8 | 17     | 39 345 | 0.351 912 568             |

| 20QBT_45CYC_3D1_2D2_9 | 20     | 39 705 | 0.350 988 54              |

| 20QBT_45CYC_3D1_3D2_0 | 20     | 40 110 | 0.350 810 272             |

| 20QBT_45CYC_3D1_4D2_1 | 20     | 40 560 | 0.351 356 016             |

| 20QBT_45CYC_3D1_5D2_2 | 20     | 41 055 | 0.352 600 171             |

| 20QBT_45CYC_4D1_1D2_3 | 19     | 41 460 | 0.350 241 196             |

| 20QBT_45CYC_4D1_2D2_4 | 20     | 41 910 | 0.348 628 012             |

| 20QBT_45CYC_4D1_3D2_5 | 20     | 42 405 | 0.347 742 012             |

| 20QBT_45CYC_4D1_4D2_6 | 20     | 42 945 | 0.347 560 834             |

| 20QBT_45CYC_5D1_1D2_7 | 20     | 43 440 | 0.344 636 28              |

| 20QBT_45CYC_5D1_2D2_8 | 20     | 43 980 | 0.342 451 114             |

| 20QBT_45CYC_5D1_3D2_9 | 20     | 44 565 | 0.340 985 078             |

| 20QBT_45CYC_6D1_2D2_1 | 20     | 45 195 | 0.338 223 255             |

| 20QBT_500CYC_QSE_7    | 20     | 52 295 | 0.330 547 854             |

| 20QBT_800CYC_QSE_4    | 20     | 63 655 | 0.321 828 607             |

| 20QBT_900CYC_QSE_3    | 20     | 76 435 | 0.315 117 42              |

| 3_17_13               | 3      | 76 471 | 0.315 191 38              |

(Continued.)

Table A1. (Continued.)

| Benchmark                       | Qubits | Gates   | Two-qubit gate percentage |

|---------------------------------|--------|---------|---------------------------|

| 4gt10-v1_81                     | 5      | 76 619  | 0.315 443 95              |

| 4gt11_82                        | 5      | 76 646  | 0.315 567 675             |

| 4gt12-v0_87                     | 6      | 76 893  | 0.316 010 56              |

| 4gt13_92                        | 5      | 76 959  | 0.316 129 368             |

| 4gt4-v0_72                      | 6      | 77 217  | 0.316 536 514             |

| 4gt5_75                         | 5      | 77 300  | 0.316 688 228             |

| 4mod5-bdd_287                   | 7      | 77 370  | 0.316 802 378             |

| 4mod7-v0_94                     | 5      | 77 532  | 0.317 069 081             |

| 4_49_16                         | 5      | 77 749  | 0.317 457 459             |

| 53QBT_700CYC_QSE_3              | 53     | 104 091 | 0.308 412 831             |

| 54QBT_10CYC_QSE_9               | 54     | 104 475 | 0.308 312 994             |

| 54QBT_15CYC_QSE_8               | 54     | 105 051 | 0.308 164 606             |

| 54QBT_200CYC_QSE_7              | 54     | 112 719 | 0.306 363 612             |

| 54QBT_25CYC_QSE_6               | 54     | 113 678 | 0.306 154 225             |

| 54QBT_35CYC_QSE_4               | 54     | 115 020 | 0.305 868 545             |

| 54QBT_40CYC_QSE_3               | 54     | 116 554 | 0.305 549 359             |

| 54QBT_500CYC_QSE_0              | 54     | 135 724 | 0.302 179 423             |

| 54QBT_800CYC_QSE_7              | 54     | 166 396 | 0.298 402 606             |

| 9symml_195                      | 11     | 201 277 | 0.322 366 689             |

| adder_n10                       | 10     | 201 571 | 0.322 218 97              |

| adder_n4                        | 4      | 201 594 | 0.322 231 812             |

| adr4_197                        | 13     | 205 033 | 0.324 133 188             |

| aj-e11_165                      | 5      | 205 184 | 0.324 230 934             |

| alu-bdd_288                     | 7      | 205 268 | 0.324 283 376             |

| alu-v0_26                       | 5      | 205 352 | 0.324 335 775             |

| alu-v1_28                       | 5      | 205 389 | 0.324 364 985             |

| alu-v2_30                       | 6      | 205 893 | 0.324 654 068             |

| alu-v2_31                       | 5      | 206 344 | 0.324 904 044             |

| alu-v3_34                       | 5      | 206 396 | 0.324 938 468             |

| alu-v4_36                       | 5      | 206 511 | 0.325 004 479             |