High energy yield Bifacial-IBC solar cells enabled by poly-SiO<sub>x</sub> carrier selective passivating contacts

Zakaria Asalieh TU Delft

# High energy yield Bifacial-IBC solar cells enabled by poly-SiO<sub>X</sub> carrier selective passivating contacts

Ву

## Zakaria Asalieh

in partial fulfilment of the requirements for the degree of

#### **Master of Science**

at the Delft University of Technology,

to be defended publicly on Thursday April 1, 2021 at 15:00

Supervisor: Asso. Prof. dr. Olindo Isabella

Dr. Guangtao Yang

Thesis committee: Assoc. Prof. dr. Olindo Isabella, TU Delft (ESE-PVMD)

Prof. dr. Miro Zeman, TU Delft (ESE-PVMD)

Dr. Massimo Mastrangeli, TU Delft (ECTM)

Dr. Guangtao Yang, TU Delft (ESE,PVMD)

# **Conference Abstract**

Evaluation and demonstration of bifacial-IBC solar cells featuring poly-Si alloy passivating contacts- Guangtao Yang, Zakaria Asalieh, Paul Procel, YiFeng Zhao, Can Han, Luana Mazzarella, Miro Zeman, Olindo Isabella – *EUPVSEC 2021*

# Acknowledgement

First, I would like to express my gratitude to Dr Olindo Isabella for giving me the opportunity to work with his group. He is one of the main reasons why I chose to do my master thesis in the PVMD group. After finishing my internship on solar cells, he recommended me to join the thesis projects event where I decided to work on this interesting thesis topic. I cannot forget his support when my family and I had the Covid-19 virus.

Second, I'd like to thank my daily supervisor Dr Guangtao Yang, despite supervising multiple MSc students, was able to provide me with all of the necessary guidance during this work. During the machine's downtime, he always tried to figure out an alternative solution to complete my process. His effective prioritization and guidance were truly inspiring.

I also want to thank the rest of the research team and my fellow cleanroom users. It was a pleasure to be a part of such a welcoming group of thinkers. I am grateful for the help that each of you was able to give me, and I will appreciate the time I spent here.

I would like to thank my family back home in Syria and my friends in the Netherlands. You provided me with a lot of encouragement and motivation to reach my goals. Again, thank you for being there for me and for your unconditional love.

Finally, I would like to thank my wife, Zahraa. Thank you for putting up with my late-night studying and early mornings. Thank you for being by my side every step of the way and taking care of me and our son. Thank you for being a source of inspiration when was feeling hopeless during tough times. Most importantly, thank you for being my best friend and my perfect life partner.

Zakaria Asalieh

Delft, April 2021

# **Abstract**

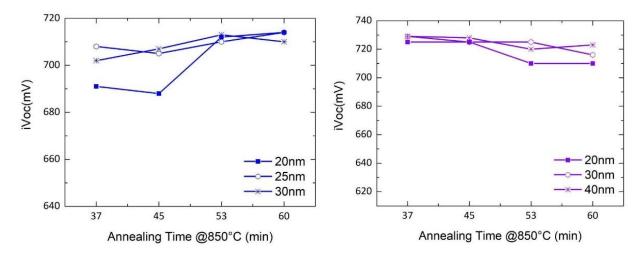

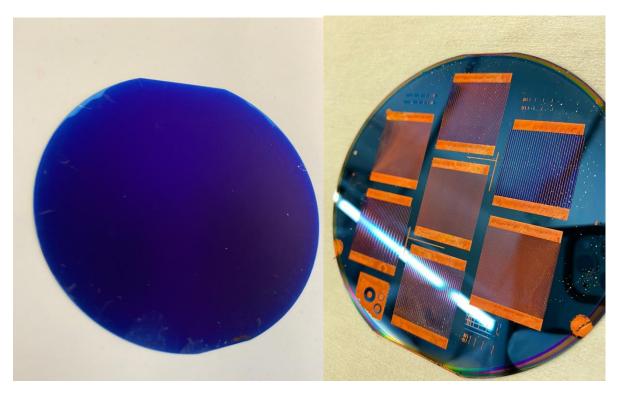

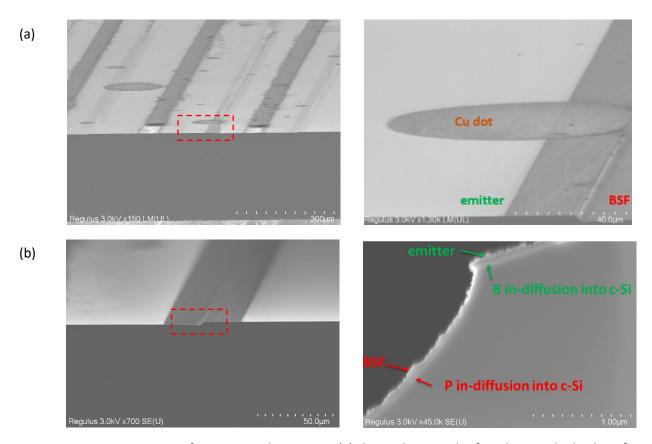

Carrier selective passivating contacts (CSPC) are promising contact structures for high efficiency silicon solar cells. They provide silicon surface passivation as well as high carrier selectivity. In this thesis, the bifacial interdigitate back contacted cell concept (bifacial IBC) is combined with the interdigitated backcontacted (IBC) structure with the bifacial concept for the purpose of further improve the solar cell output. It is enabled by poly-SiO $_X$  as CSPCs. The main aim of this thesis project is the preparation of proof of concept bifacial IBC cells. In this work, two process flowcharts for bifacial IBC solar cell fabrication are presented: (1) poly-SiO<sub>X</sub> fingers patterned by ion-implantation through photoresist masking layer, (2) wet chemical patterning of in-situ doped poly-SiO<sub>x</sub>. In the first process, the optimization of poly-SiO<sub>x</sub> passivating contact was performed by varying the intrinsic a-SiOx:H layer thickness. The best passivation results obtained from this approach was 646 mV, and 623 mV for the  $n^+$  and  $p^+$  layer, respectively. In the second process, the thickness of doped  $p^+$  and  $n^+$  poly-SiO<sub>x</sub> layers was also optimized for the symmetrical test samples based on the requirement of bifacial IBC solar cell flowchart. As a consequence, a 25 nm thick  $p^+$  poly-SiO<sub>x</sub> layer and a 40 nm thick  $n^+$  poly-SiO<sub>x</sub> layer recorded highest iV<sub>OC</sub> performance. Next, the hydrogenation treatment is applied to further optimize the samples passivation quality. This results in an overall passivation of 714 and 730 mV for  $p^+$  and  $n^+$  poly-SiO<sub>X</sub> symmetrical samples, owed to the fact that the high hydrogen content in  $SiN_X$  layer boosting the passivation properties of the poly- $SiO_X$  passivating contacts. These findings of the optimized poly- $SiO_X$  passivation contacts are used to fabricate the bifacial-IBC solar cell. As a result, using the wet-etching patterning of in-situ poly-SiO<sub>x</sub> CSPC flow chart, a demonstration proof of this cell principle is obtained with V<sub>OC</sub> of 649 mV, FF of 44,3 %, J<sub>SC</sub> of 40,7 mA/cm<sup>2</sup>, and efficiency of 12% for the best solar cell. The losses analysis of such cell performance was also conducted.

# Contents

| Abstract                                                                       | viii |

|--------------------------------------------------------------------------------|------|

| 1 Introduction                                                                 | 1    |

| 1.1 Solar cell working principle                                               | 3    |

| 1.2 Losses Mechanisms                                                          | 4    |

| 1.2.1 Optical losses                                                           | 4    |

| 1.2.2 Electrical losses                                                        | 5    |

| 1.3 External solar cell parameters                                             | 6    |

| 1.4 Surface passivation                                                        | 7    |

| 1.5 Carrier selective passivating contacts definition and techniques           | 9    |

| 1.6 Thesis objectives                                                          | 12   |

| 1.7 Thesis outline                                                             | 12   |

| 2 Experimental methods                                                         | 14   |

| 2.1 Fabrication process                                                        | 14   |

| 2.2 Characterization techniques                                                | 24   |

| 3 Ion-implantion for bifacial-IBC solar cell                                   | 29   |

| 3.1 Requirements for poly-SiO <sub>x</sub> passivation contacts                | 29   |

| 3.2 Sample preparation                                                         | 31   |

| 3.3 Optimization of PECVD intrinsic a-SiO <sub>X</sub> :H thickness            | 34   |

| 3.4 Hydrogenation effect                                                       | 37   |

| 3.5 Conclusion                                                                 | 38   |

| 4 in-situ doped poly-SiO $_X$ passivating contacts for bifacial-IBC solar cell | 40   |

| 4.1 Solar cell fabrication                                                     | 40   |

| 4.2 Experimental details                                                       | 42   |

| 4.3 Optimization of the $(p^+)$ poly-SiO <sub>X</sub> layer thickness          | 44   |

| 4.3.1 PECVD intrinsic a-SiO <sub>X</sub> :H layer                              | 45   |

| 4.3.2 LPCVD intrinsic a-SiO <sub>X</sub> :H layer                              | 47   |

| 4.4 Optimization of the $(n^+)$ poly-SiO <sub>X</sub> layer thickness          | 48   |

| 4.5 Hydrogenation optimization                                                 | 50   |

| 4.6 Front surface field (FSF) passivation test                                 | 51   |

| 4.7 TCO laver (ITO) pattering test                                             | 52   |

| 4.8 Solar cell results  | . 53 |

|-------------------------|------|

| 4.9 Conclusion          | . 56 |

| Conclusions and Outlook |      |

| 5.1 Conclusions         |      |

|                         |      |

| 5.2 Outlook             | . 60 |

# Nomenclature

Poly-SiO<sub>X</sub> Oxygen Alloyed Polycrystalline Silicon

Poly-Si Polycrystalline Silicon

τeff Minority Carrier Lifetime

Eg Bandgap

η Conversion efficiency

EC Conduction Band

ρ<sub>C</sub> Specific Contact resistance

EV Valance Band

a-Si Amorphous Silicon

FBC Front and Back Contacted

Ag Silver

FF Fill Factor

Al Aluminum

FG Forming Gas

ALD Atomic Layer Deposition

FZ Float Zone

ARC Anti-reflection Coating

HF Hydrofluoric Acid

B Boron

HNO<sub>3</sub> Nitric Acid

BHF Buffer Hydrofluoric Acid

iV<sub>OC</sub> Implied open-circuit voltage

c-Si Crystalline Silicon

IBC Interdigitated Back Contact

CSPC Carrier Selective Passivating Contacts

ITO Indium Tin Oxide

TMAH Tetramethylammonium Hydroxide

J<sub>0</sub> Recombination Current Density

VOC Open-Circuit Voltage

JSC Short-circuit Current density

PECVD Plasma Enhanced Chemical Layer Deposition

LPCVD Low Pressure Chemical Vapor Deposition

PV Photovoltaics

NAOS Nitric Acid Oxidation of Silicon

Rs Series Resistance

N<sub>2</sub> Nitrogen

Rshunt Shunt Resistance

O<sub>2</sub> Oxygen

Cu Copper

P Phosphorous

ITO Indium Tin Oxide

SEM Scanning Electron Microscopy

J<sub>0</sub> Recombination Current Density

SRH Shockley-Read-Hall

JSC Short-circuit Current density

STC Standard Test Conditions

SiH4 Silane

SiN<sub>X</sub> Silicon Nitride

TCO Transparent Conducting Oxide

# 1 Introduction

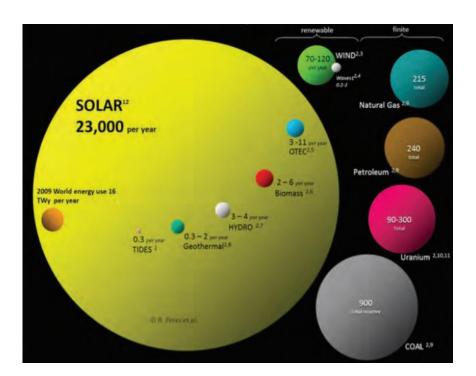

One of the most significant challenges that Humanity has to face nowadays, with the increasing population, is growing worldwide demand for energy. EIA projects that world energy consumption will increase by almost 50% by 2050 led by Asia [1]. The loss of traditional energy sources such as coal, oil and natural gas is increasing which will arise the problem of the scarcity and environmental impact. All previous reasons will place the human beings against the predicated energy crisis in the next decades [2]. Despite the increasing of energy demand, approximately 1.1 billion people are still living without having access to these goods [3]. These circumstances indicate the importance of shifting from conventional energy to a more renewable and abundant source. Comparing all energy resources, solar energy represents one of these alternatives and play a vital role in this energy transition. Figure 1 indicates the approximate of finite and renewables planetary energy reserves by International Energy Agency (IEA) [4]. Analyzing solar energy sources, it is very clear that it has gained so much attention in recent years because of its abundance relative to other energy sources. Theoretically, solar energy can produce 10,000 times more energy in comparation with current energy demand [5].

Figure 1.1: Energy sources power availability [4].

The French physicist Alexandre Edmond Becquerel discovered the photovoltaic effect in 1839. He Analyzed that conductance increases with illumination during his experiment with metal electrodes and electrolyte. Daryl Chapin, Calvin Fuller, and Gerald Pearson invented the first silicon solar cell at Bell Labs in 1954, with 4% efficiency. [6]. Addressing the current state of this technology, photovoltaic (PV) based on silicon have ruled the PV market over the last years. It worth to mention that silicon has significant advantages over other technologies since it is an abundant, cheap and non-toxic material [7]. The silicon solar cell was governed in the early years by multi-crystalline solar cells , however in the recent years mono-crystalline silicon solar cells dominate the market by 39.6 and 89.7 GWp, respectively [8].

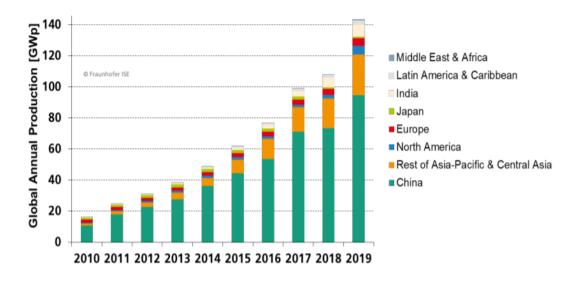

To harvest solar energy, photovoltaic (PV) system can directly convert the solar irradiance to electricity. The annual PV module global production from 2010 to 2019 are shown in Figure 2. The number of the annual PV module production increased from lower than 18 GW in 2010 to over 140 GW in 2019. The increase in PV production indicates that countries all over the world pay more attention to solar energy development. The Asian countries, especially China and Japan, contributes the most in the increment in PV market in last ten years [8].

Figure 1.2 Global annual production [8]

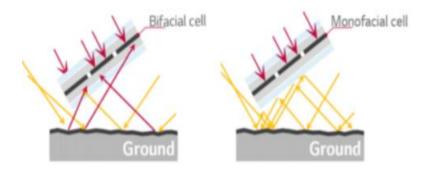

Bifacial solar cell gains more attention in the solar cells research field because it not only captures the incident light on the solar cell front side but also the diffused and scattered light on the rear side as shown in figure 1.3. Therefore, in contrast to monofacial cells, bifacial solar cells will significantly increase power generation [5]. The last Research shows that the same active area can be expected to harvest 50 percent more electricity than the traditional monofacial solar cells [61]. However, this improvement can vary depending on the local albedo and the nonuniform shading conditions. A further advantage is that the solar cell working temperature is reduced due to the infrared absorption reduction in the rear metallization [62] which will enhance the solar cell performance.

Figure 1.3: Comparison between the monofacial and bifacial solar cell [63].

# 1.1 Solar cell working principle

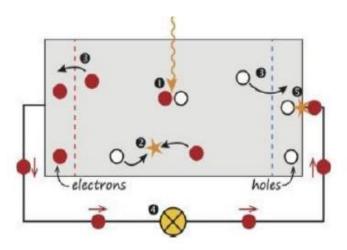

Photovoltaic (PV) effect is the core concept of the solar cell operation in which the light beams is converted into electricity using a solar cell. The photovoltaic effect provides a difference in the potential between two different materials due to the incident radiation. If the previous two materials were connected to an external circuit, it can be used to power a load. A solar cell's fundamental operating theory includes three main processes:

- Charge carrier generation occurs when an incident photon with a specific energy is absorbed by a semiconductor material. This results in an excitation of an electron from the valence band to the conduction band leaving a hole behind in the valence band. Thus, an electron-hole pairs are created within the material. The difference in energy between the valence band (Ev) and the conduction band (Ec) of the material is known as the band gab (Eg). It is worth noting that the electron-hole pair is produced only for absorption with energy equal to the material band gab e.g. Eg for crystalline silicon is 1.12 eV.

- Charge carrier separation this subsequent step is to prevent the generated charge carriers from recombining. This separation can be represented as the membrane that allows the passage of one form of charge carrier. This membrane is called the p-n junction in solar cells, which is created when semiconductors of the p-type and n-type are placed in contact.

- Collection of charge carriers is the last step which take place at the electrodes to extract the separated charge carriers from the solar cell. Electrons are passing through the external circuit, to utilize the electron energy, and recombine at the metal side with holes. In this particular step, the chemical energy is converted to useable electrical energy.

Figure 1.3 solar cell under the operation [5]

## 1.2 Loss Mechanisms

The losses in the solar cell are discussed in this section. There are two different losses categories optical and electrical losses. The spectral mismatch concerns a single-junction solar cell while optical and electrical represents the unsuccessful generation and absorption of the electron-hole pair.

## 1.2.1 Optical losses

The spectral mismatch is considered the largest optical loss mechanism. The spectral mismatch considers two important losses that suppress the efficiency of a solar cell. There other forms of optical losses that occur in the solar cell such as parasitic absorption, reflection and shading losses which can be explained as follow:

**Thermalization**: Photons with energy higher than material band gap is able to produce an electron-hole pair while excess energy of the photons will be lost and released as a heat in the semiconductor material. **Non-absorption**: On the other hand, the absorption for photons with energy lower than the semiconductor band gap will not be possible. Due to this unsuccessful absorption, these photons do not produce electron-hole pairs and will pass through the semiconductor.

**Parasitic absorption**: The semiconductor material will absorb photons with energy equal to the semiconductor band gap and these photons will travel through the semiconductor material. However, these photons can be absorbed in non-photoactive areas such as ARC and TCO layers and do not contribute to charge carrier generation; this is called parasitic absorption.

**Reflection losses**: is the next main loss mechanism where the incidents photons can be reflected before reaching the absorber layer. These losses can be minimized by introducing ARC layer or by using a transparent conducting oxide (TCO) layer. Additionally, to achieve a better light trapping in the cell, surface texturing is applied to increase the photons path length through the cell.

**Shading losses**: These losses are mainly due to the metallization fingers at the solar cell front side that blocks the incident light on the surface reducing the short circuit current. Therefore, the metal contacts geometry should be optimized to reduce the shading effect. These losses can be fully eliminated by introducing the IBC solar cell topology, in which all the contacts are located at the solar cell rear side.

#### 1.2.2 Flectrical losses

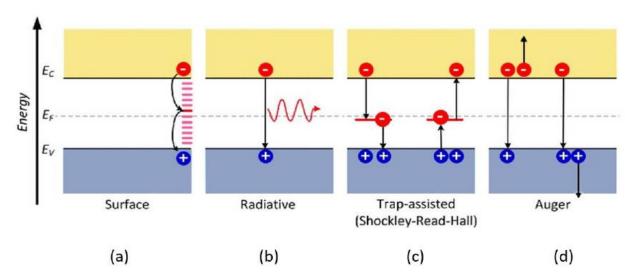

Electrical losses take place within the absorber material due to the ineffective utilization of excited electrons. This can be attributed to the recombination of the electrons before being collected which results in the reduction of the available charge carriers and eventually undermine the solar cell performance. It is possible to separate these recombination losses into two main mechanisms: surface and bulk recombination. The bulk recombination was categorized into Radiative recombination, Auger recombination and Shockley-Read-Hall (SRH), Figure 1.4.

#### Surface recombination

Thanks to the progress made by the silicon manufactures, the material quality has improved and thus the bulk recombination suppressed significantly. Therefore, the major recombination mechanism for most c-Si solar cells is surface recombination. Surface recombination occurs due to the presence of dangling bonds on the semiconductor surface that acts as a defect state. These defects state later capture the charge carriers which boost the SRH recombination rate. In a p-type semiconductor, the surface recombination rate can be described by equations (1.1)

$$R_s \approx v_{th} \sigma_p N_{sT} (p_s - p_0) \tag{1.1}$$

Where vth represents the surface recombination velocity, NsT the trap density at the surface  $\sigma p$  is the holes capture cross section. According to the above equation, the surface recombination can be minimized in two ways. The first method is to reduce the number of dangling bonds (trap state) as the higher the trap density the higher probability of electron-hole recombination. On the other hand, increasing the doping concentration at the semiconductor surface can decrease minority carriers on the material surface. This creates a barrier that prevents minority charge carriers from being transmitted to the semiconductor material surface.

Figure 1.4: Diagram demonstrate the recombination mechanisms [5].

#### Radiative recombination

Radiative recombination is the reverse action of photon absorption, where an excited photon relaxed back to the original energy state and emit a photon with energy equal to the band gap. For the direct bandgap semiconductor materials, the radiative recombination is dominant such as gallium arsenide (GaAs). Therefore, it does not play a vital role in the c-Si solar cells and the excited electron will not easily relax back to the initial state of energy.

#### **Auger recombination**

This type of recombination in contrast is dominant in the direct materials. Auger recombination is a process that needs three particles where the excess energy is transferred to a third particle(hole/electron). This third charge is therefore excited to a higher energy level and relax back again to semiconductor edge by thermalization. As Auger recombination requires three particles, it represents a dominant recombination mechanism in the highly doped regions and depletion region due to the large number of free carriers.

#### **Shockley Read hall Recombination**

SRH recombination occurs due the presence of an intermediate energy level between the valence and conduction bands in the c-Si band gap. This trap state can be induced by the existence of a structural defects or material impurities. The charge carrier is trapped in the introduced energy level which introduce a path to move the electron down to the valence bard. Therefore, SRH decreases with increasing the material quality.

#### **Resistive losses**

It worth to mention that there are other types of losses in the c-Si solar cell. Charge carriers encounter different layers within the solar cell to reach the metal electrode. This is known as a series resistance experienced by the charge carrier. For better charge carrier collection at the electrode side, this value should be kept at low level to maximize the cell performance. Additionally, the leakage current through the p-n junction corresponds to the shunt resistance. For better performance, this value has to be as high as possible.

# 1.3 External Solar cell parameters

Solar cell parameters help to identify the properties and performance of the solar cell. These parameters are defined in this section, since they will be used in this thesis.

#### Short circuit current density

The short circuit current, Isc, is the current that run in the cell when the voltage across the solar cell is zero [5]. It depends on several factors such as the cell area, photon numbers and other optical properties (absorption and reflection). To neglect the dependency on area of the solar cell, the sort circuit current density is used rather than short circuit current.

#### Open circuit voltage

The open circuit voltage, Voc, is the maximum voltage that can be produce by the solar cell and it occurs when the current of the solar cell is zero [5]. Looking at Equation (1.2), it shows that Voc is related to 10 which depends on recombination in the solar cell. Therefore, it is used as a measure of the solar cell quality.

$$V_{OC} = \frac{k_B.T}{q} \ln \left( \frac{J_{ph}}{J_0} \right) \tag{1.2}$$

#### Fill factor

As shown above the short circuit current and open circuit voltage represent the maximum current and voltage respectively of the solar cell, but at these both points the power delivered by the device is zero [5]. Therefore, the maximum power of the solar cell is indicated by the fill factor, FF, as it is a key indicator of the cell performance. The FF can be calculated by the equation (1.3)

$$FF = \frac{P_{mpp}}{V_{oc}J_{sc}} \tag{1.3}$$

## **Conversion efficiency**

The conversion efficiency of the solar cell is defined as the ratio of the energy out of the solar cell to the incident energy from the sun under standard test conditions (STC) [5]. STC conditions are at power available from the sun 1000 [W/m2] with the irradiance spectrum equal to AM1.5 spectrum and at a temperature of 25°C. The open circuit voltage (VOC) is calculated from Equation 1.4

$$\eta = \frac{P_{max}}{P_{in}} = \frac{J_{SC}.V_{OC}.FF}{P_{in}}$$

(1.4)

#### 1.4 Surface Passivation

As described above in section, solar cell influenced severely by surface recombination and it represent the major loss mechanism. In this section two treatment process namely chemical passivation and field-effect passivation are described which can be used to overcome this problem. A combination of these two techniques helps in creating a carrier selective passivating contact (CSPC) which results in a high passivation quality and it is discussed in detail later in the following section.

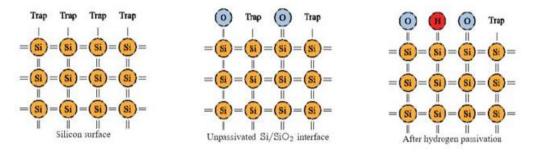

#### **Chemical passivation**

As discussed in section 1.2.2, to minimize the density of defects on the surface of the semiconductor material passivation techniques are used. Chemical passivation is done by introducing an ultra-thin layer which acts as insulation material on surface of the semiconductor material. The thin insulation layer will saturate the dangling bond at surface and usually also provide hydrogenation effect Figure 1.5. Common chemical passivation layers are silicon oxides ( $SiO_X$ ), hydrogenated amorphous silicon (a-Si:H) and hydrogenated amorphous silicon nitride (a-SiNx:H) [9][10].  $SiO_2$  can be grown chemically, deposited by plasma enhanced chemical vapor deposition (PECVD) or thermally formed [11].

Next, silicon nitride is a hydrogen rich material and used to saturate the dangling bonds with the help of hydrogen. This process called hydrogenation and it explained in detail in section. Silicon nitride can also be deposited by PECVD and it used as anti-reflection coating material [10][11]. Finally, Aluminum oxide (Al2O3) is applied to provide good passivation property deposited by atomic layer deposition (ALD) [12].

Figure 1.5: Chemical passivation of the silico surface using SiO₂ and hydrogen atoms [5].

#### Field-effect passivation

Another method to reduce the surface recombination is to reduce one type of carrier concentration by introducing a highly doped layer, which is known as field-effect passivation. The electric field repels the minority carrier from the highly doped region. Figure 1.6 demonstrate this technique of an n-type c-Si solar cell, in which the emitter is a highly boron-doped region, it rejects electrons and only accept holes to pass through. In this way, the surface recombination reduced significantly. However, a too high doping level will cause a poor passivation quality and the Auger passivation becomes dominant [13].

Figure 1.6: Selective passivation layers of the hole and the electron on the solar cell rear side [12].

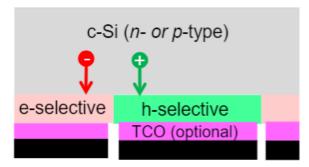

# 1.5 Carrier selective passivation contacts definition and techniques

As mentioned before, the implantation of carrier selective passivating contact (CSPC) brings a major improvement in solar cell design. An explanation of definition with some important examples is given in this section.

Thanks to the constant improvement in c-Si resulted in a substantial reduction of recombination losses at both bulk and surface level [11]. However, recombination at the metal/semiconductor interface is currently the controlling factor for to have high efficiency solar cells. Therefore, CSPC used to overcome this limitation factor. To present a better understanding of CSPC, two main parameters should be considered to achieve high solar cell quality which are the recombination current density,  $J_0$ , (non-collected charge carriers) and contact resistivity,  $\rho c$ , (collected charge carriers). These values have to be minimized to realize a highly selective contacts [14]. An ideal CSPC enables the following:

Firstly, implementing a passivating layer between the metal/c-Si interface. This facilitate an efficient interface passivation (minimize the defect density) and surface passivation. The high passivation quality result in lowering the  $J_0$  which enable higher Voc values. Next, a good field effect passivation by introducing a doped  $p^+$  or  $n^+$  layer. The excellent charge carrier selectivity enables the conductivity for majority charge carrier type (elections/holes) must be higher. In other words, it passes one type of charge carrier and block the other [15]. This good selectivity reduces the contact resistivity  $p_0$  significantly. The carrier selectivity can be achieved by many ways and the major forms of the passivation techniques are tunnel oxide passivation contact (TOPCon), silicon-heterojunction (SHJ), and doped poly-Si interdigitated back contacted (IBC) cell and explained in detail in this section.

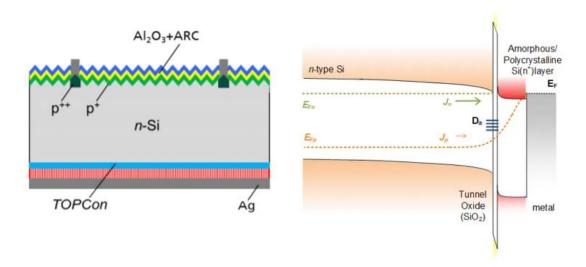

#### Tunnel oxide passivating contact solar cells

The TOPCon technology is a selective contact structure can be formed by an ultrathin tunnel oxide layer (typically <1.5nm) together with doped poly-Si layer [24]. The basic working principle of this passivating contact structure is based on two aspects: First, the ultrathin oxide which is typically grown by thermal or chemical oxidation, provides chemical passivation at the oxide/c-Si interface. It allows charge transfer from c-Si to poly-Si, while it repels the dopant movement from poly-Si to c-Si [24], figure 1.7 right. Next, the doping in the poly-Si layer increase the transmission possibility for electrons (in this case) while reducing the conductivity of the other charge carrier type (holes) [17]. Figure. 1.7 left is an example of TOPCon where the back-surface field (BSF) at the solar cell rear side replaced with tunnel oxide passivated contacts.

Figure 1.7: left: TOPCon cell structure with tunnel oxide at the rear side. Right: Band bending diagram at the tunnel oxide layer [19].

This technology is considered relatively thermally stable; however, the main advantage of this specific topology is the simple manufacture steps. This is realized by the fact that the metal on the rear side can be performed in on step rather than the complex pattering techniques for the back contact. The maximum achieved efficiency is 25.7[%] using this design [20]. On the other hand, this technique has some drawbacks because the doped poly-Si on the front side results in large parasitic absorption and on the rear side the heavily doped poly-Si, needed to obtain good carrier selectivity, increases the free-carrier absorption (FCA) [21].

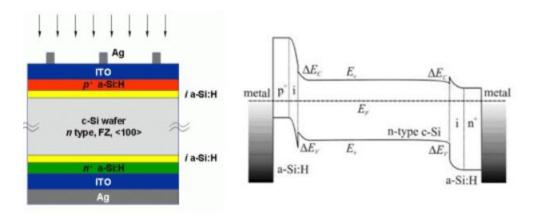

#### Silicon heterojunction solar cell

The silicon heterojunction (SHJ) was fabricated in the early 1990s and has been trademarked under the name of HIT (heterojunction with intrinsic thin layer). When two material are connected to each other it is called heterojunction. Applying this concept, Kaneka Corp. has reached SHJ cells with an outstanding conversion efficiency of 26.7 % [22]. The diagram of this cell is presented in figure 1.8 left.

The silicon heterojunction working mechanism is based on two passivation approaches mentioned in previously. Firstly, it comprises a thin intrinsic hydrogenated amorphous silicon a-Si: H layer on the silicon surface to provide high surface passivation (chemical passivation) [23]. Secondly, the doped a-Si:H layers (p/n type) are applied on top of it to enhance charge carrier selectivity by introducing band bending in the c-Si [see Fig. 1.8 right]. Additionally, the heavy doping layer increase the conduction of electrons and holes, which is further aided by the fact that a-Si:H has a wider bandgap than c-Si [24]. Finally, between the metal and a-Si layers, transparent conductive oxide (TCO) layers are introduced to promote the lateral conductivity, giving the fact that a-Si has a poor conductivity. Moreover, TCO acts as an antireflection coating which results in enhanced optical performance [5].

Utilizing these advances, leads to the fact that SHJ cells have very high Voc, which can reach a value of 750 mV [25]. Furthermore, one of the main advantages of SHJ cell is because it has a low thermal budget as a-Si doping is applied with low temperature processing. Additionally, the disadvantages are the a-Si:H layers introduce a significant optical absorption loss (parasitic absorption) and requires a TCO layer due to the poor conductivity [24].

Figure 1.8: left: schematic of the SHJ cell structure. Right: SHJ cell band diagram [26]

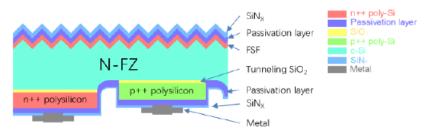

#### Poly silicon interdigitated back contacted solar cells

All previously mentioned solar cells technologies have both front and rear metal contacts, thus metal contacts at the front side induces optical losses caused by the shading effect, the interdigitated back contact (IBC) solar cells is developed to overcome the shading effect by moving all metal contacts to the solar cell rear side [59]. It is a successful structure with growing importance for high performance devices to be obtained. The world record holder efficiency is 26.1% for IBC cells designed by ISFH using this structure [27].

As shown previously in Figure 1.7 right which depict the band diagram of the poly-Si passivating contact. Looking to the diagram, it consists of a highly doped poly-Si layer and a SiOx layer. The dissimilarity of the work function between the n-Si bulk and the heavily doped n-type Si results in the band bending. This means that electrons can tunnel through oxide layer (green arrow) to the poly-Si layer, however holes will be repelled from the oxide layer. The oxide layer should be thin enough typically around 1.1 nm allowing electron tunneling [28].

Figure 1.9 left demonstrates an IBC solar cell, where all the metal contacts are on the back side. First the front side,  $SiN_x$  layer that acts as passivation and anti-reflecting coating. Next, another passivation material such as  $SiO_2$  or a-Si is added to improve the passivation quality. The  $n^+$  front diffusion region is called front surface field (FSF), which minimize front surface recombination through field-effect passivation. Moving to the rear side, an ultra-thin oxide layer is deposited on the Si bulk material. Below the oxide layer, the  $p^+$  and  $n^+$  regions are formed. Finally, another locally opened  $SiN_x$  layer to enhance the passivation with the metal electrodes.

Figure 1.9: Structure of Poly-Si IBC formed by PVMD group [29].

This structure can obtain high efficiencies as it combines the best aspects of the IBC and TOPCon topologies. Utilizing this with optical changes by eliminating front metal contacts and the ability to design the rear metal leads to excellent performance. Consequently, as seen in other high-performance structures, compared with a-Si, the use of poly-Si provides greater adaptability in the design process. As poly-Si has a higher thermal budget, it can withstand more intensive steps such as high temperature annealing.

The primary downside of this structure is the complexity needed for manufacturing process. For IBC solar cell fabrication, there are already several steps to perform. Thus, adding a tunnel oxide layer will further complicate the process. Therefore, despite the high thermal stability, it is not optimal for industry [31]. The other drawback of this topology is parasitic absorption in the highly doped layers (at both front and rear) mostly due to FCA in these layers. Parasitic absorption can be decreased by using other doping methods for example in situ doping or reducing the doped layer thickness [31]. This thesis focuses mainly on this side to minimize these losses by varying the thickness of the doped layer in terms by using plasma enhanced chemical vapor deposition (PECVD) rather than ion implanting.

# 1.6 Thesis objectives

The purpose of this thesis project is for the preparation of proof of concept (PoC) bifacial IBC solar cells through the implantation of poly-SiOx passivating contacts, to produce a highly efficient, high energy yield c-Si solar cell. Many experiments must be carried out to successfully produce the solar cell. The main objectives are (1) to study the most suitable approaches to pattern the poly-SiOx fingers, which could deliver/maintain the highest passivation qualities of the passivating contacts; (2) applying the ultimate patterning approach to the solar cell process flowchart to fabricate the proof of concept cell. Different manufacturing parameters must also be tested in order to achieve acceptable results namely annealing time, annealing temperature and other checks for material etching methods. In addition, the effect of hydrogenation mechanism was also checked, which has crucial importance on the cell parameters. Bifacial-IBC solar cells with poly-SiOx passivating contacts have been developed by seeking a compromise between several decision variables of the production process. The main research objectives of this thesis are:

- Compare masked ion-implantation and wet-etching approaches for patterning of BSF and emitter fingers.

- Optimize the passivation of the patterned BSF and emitter fingers at the solar cell rear side.

- Investigating best Bifacial-IBC solar cells flow chart.

- The optimal patterning approach for ITO fingers.

#### 1.7 Thesis outline

This work consists of 5 chapters. The fabrication and measurement techniques used in this thesis are described in Chapter 2. In chapter 3, the ion-implantation of poly-SiO<sub>X</sub> as patterning step of proposed flow chart is tested and evaluated. The passivation tests for fabrication of the bifacial-IBC solar cell using wet etching of in-situ doped poly-SiO<sub>X</sub> as patterning approach is introduced and evaluated in chapter 4. Also, in this chapter, the results of PoC bifacial IBC solar cell and the losses analysis are discussed. Finally, in chapter 5, the thesis concludes with a discussion of the findings and recommendations for further studies.

# 2 Experimental methods

This chapter is separated into two major sections: Firstly, the fabrication processes to manufacture the test samples and solar cell are introduced. Next, it explains how the measurements are conducted with the aid of characterization equipment.

# 2.1 Fabrication process

The various manufacturing processes involved in the processing of bifacial-IBC solar cells are presented in this section. Starting from wafer cleaning step and finishing up with metallization step. These processes are not only applied to manufacture bifacial-IBC solar cells, but also for symmetrical samples which are crucial to analyze the carrier selectivity and passivation quality.

## Wafer qualification

In this project, phosphorous (n-type) doped crystalline silicon (c-Si) wafers manufactured by TOP-SIL are used. The wafer material properties are presented in table 2.1. The reason behind the choice on n-type wafer is motivated by two crucial properties. First, n-type have higher bulk minority carrier lifetime because it has lower sensitivity to recombination. Second, p-type material suffers from oxygen impurities due to wafer fabrication, therefore n-type are more used to avoid the boron-oxygen related light-induced [32].

Table 2.1 c-Si material properties.

| Parameter             | Value    |  |

|-----------------------|----------|--|

| Diameter [mm]         | 100 +/-2 |  |

| Thickness [μm]        | 260~300  |  |

| Doping                | n-type   |  |

| Finish                | Polished |  |

| Resistivity [ ohm.cm] | 1-5      |  |

| Orientation           | <100>    |  |

#### Standard cleaning

Before starting any process, silicon wafers must first be properly cleaned to remove any organic or inorganic contaminants. The standard cleaning technique, used in Else Kooi Laboratory (EKL), consists of 5 main steps. First, to eliminate the organic contamination of the wafers it is immersed for 10 minutes in

a 99% HNO3 solution. After that, the wafers are rinsed for 5 minutes in deionized water (DI water). Next, Inorganic contamination is removed at 110 °C in a 68 % HNO3 solution for 10 minutes, also followed by a 5 minutes rinse in a DI water solution for 10 minutes. The final step is to dry the wafers in a Spin Rinse Dryer (SRD).

It is important to mention that, a native oxide layer is created at the surface of the wafer after different process such as standard cleaning although the wafer is kept in the cleanroom atmosphere. Therefore, this native oxide should be removed right before the next step this is done by immersing wafers in hydrofluoric acid (HF) 0.55% solution for 4 minutes until the entire surface become hydrophobic. Next, the wafer is rinsed with DI water for 4 minutes, with additional 1 minute of isopropyl alcohol (IPA) to dry the wafer.

#### Chemical silicon oxide growth

The growth of a thin silicon layer  $SiO_x$  layer is the next step of the manufacturing process. The goal of this step is to establish the best passivation ultra-thin  $SiO_x$  layer thickness typically 1.5 [nm] [33]. In this thesis work, the so-called Nitric Acid Oxidation of Silicon (NAOS) via the chemical oxidation method is used to develop this layer. Thus, the wafer is immersed for 60 minutes in a 69.5% HNO3 solution at room temperature to achieve this ultra-thin oxide layer. As mention previously, this step is carried out directly after removing the native oxide layer by Marangoni (0.55% HF). Finally, wafers should wash out in DI water for 5 minutes after NAOS oxidation.

The major benefit of chemically generated oxide is that it creates a homogenous layer thickness, thus it has a very low leakage current. Additionally, NAOS is easy to apply, and it is a very low thermal budget process compared with thermal oxidation which required a temperature 600 to 700°C [34]. However, the only downside of this method is that it is less thermally stable in comparation with other oxidation methods. Therefore, the oxide layer may not withstand the followed high temperature process [35].

#### Low Pressure chemical Vapor Deposition (LPCVD)

Low Pressure chemical Vapor Deposition (LPCVD) is one of many deposition methods used to deposit Si based layers (figure 2.2). This method allows layers with a thickness between a few nanometers and a few micrometers to be deposited.

The key advantage of this method is the high homogeneity and purity of the layers deposited by LPCVD, which is essential for the conducted experiments. Further, LPCVD deposited layer are pin-hole-free [36]. This ensures the safety of the ultra-thin oxide layer in the subsequent deposition and chemical steps.

## Horizontal LPCVD reactor N2 to open Pressure gauge 3 - zone resistive heater Exhaust Mixer Wafer holder Vacuum brake valve Particulate filter Flux Gas diffuser controller system Mechanical pump

Figure 2.2: Schematic of LPCVD system [37]

The LPCVD tube furnace developed by TEMPRESS SYSTEMS is used during the described thesis project. This system applied in order to deposit an intrinsic amorphous silicon layers [(i)a-Si] on both the symmetrical and bifacial-IBC cells. The (i)a-Si layer was deposited using an optimized recipe with the following parameters: Silane (SiH<sub>4</sub>) is the used gas with a constant flow rate at 45 sccm during the deposition. The temperature and pressure in the system in kept at 580°C, 20 Pa, respectively. Using these parameters, the a-Si deposition rate occurs on both side of the wafer was 2.2 nm/min. The furnace implements a post annealing at 600°C for 60 minutes. After the deposition step to remove stress from the sheet. This layer will be annealed later to formulate doped poly-Si layer at rear side of the solar cell. It should be noted that the sample must be dipped in 0.55% solution directly before performing the next process. This is done to remove the easily formed native oxide layer on the amorphous silicon surface.

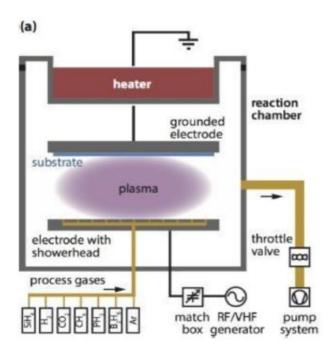

#### Plasma enhanced chemical vapor deposition (PECVD)

Next deposition method used in this project is plasma enhanced chemical vapor deposition (PECVD). It is used in the deposition of a large variety of materials in solar cell research. This machine runs only at low temperature typically between 200-400. This is due the presence of plasma that deliver ions and energetic free electrons that capable of breaking the gases' chemical bonds [38]. By applying a highly energetic field on each side of the chamber across the electrodes, plasma is ignited. The PECVD layers can be formed with high levels of uniformity, quality and at desirable thicknesses [39]. Figure 2.3 illustrates the PECVD machine.

Figure 2.3: PECVD chamber configuration [40].

In this thesis project three different PECVD machines are used. First, Novellus was used to deposit a thick  $SiN_x$  in the form of capping layer on the bifacial-IBC solar cell rear side. The function of this layer is to protect the doped region (p/n type) on the rear side during the front side texturing. The next PECVD is Plasmalap system 100 manufactured by Oxford instruments. This instrument is used first for hydrogenation step on the rear side to deposit SiNx at 400°C with 12 [nm/min] as deposition rate. Next, it is also used to form the front side passivation layers mainly a-Si at 250°C with deposition rate 45[nm/min] and again SiNx as ARC layer.

Finally, AMOR manufactured by Elettrorava is the last PECVD tool used in this project in order to deposit intrinsic, p doped and n-doped materials. The deposition using this device is done in four different chambers dedicated to particular material to avoid contamination of the deposited layers. To process the wafer both sides without breaking the vacuum an additional chamber is added. The descriptions of the deposited layers with deposition parameters are given in table 2.2.

Table 2.2 Deposited layers using PECVD.

| Layer     | Gas              | Gas flow rate[sccm] | Pressure[mbar] | Temperature[°C] |

|-----------|------------------|---------------------|----------------|-----------------|

| Intrinsic | SiH <sub>4</sub> | 45                  | 1-2            | 180             |

|           | SiH <sub>4</sub> | 110                 |                |                 |

| р         | $CO_2$           |                     | 1              | 180             |

|           | B2H6             | 115                 |                |                 |

|           | SiH <sub>4</sub> | 39                  |                |                 |

| n         | $CO_2$           |                     | 2              | 180             |

|           | PH <sub>3</sub>  | 43.8                |                |                 |

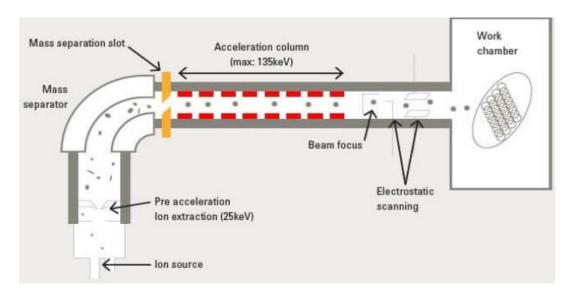

#### Ion implantation

In solar cell processing, Varian ion implanter is used to form  $n^+$  and  $p^+$  doped poly-Si layers using Phosphorous and Boron dopants, respectively. Figure 2.4 demonstrates the schematic of such an implanter. Using plasma, the dopant ions are formed and guided with the aid of a magnetic field into the accelerator. In order to filter the desired ions before entering the accelerator, a mass separation slot is used. Next, the ion beams are concentrated, with the help of magnetic lenses, on the target surface.

Figure 2.4: Schematic of ion implantation system [41].

One of key advantages of ion implantation that there is a large amount of control on the degree to which the ions would penetrate inside the substrate. This is done by varying the implantation energy, dopant species and ion dosage. However, this method may cause damage the target surface. The used ion dosage and energy for the formed FSF, BSF and emitter regions used in this thesis project are outlined in table 2.3.

Table 2.3: Ion implantation parameters

| Region  | Ion dopants | Energy [keV] | Dose [ions-cm <sup>-2</sup> ] |

|---------|-------------|--------------|-------------------------------|

| FSF     | Р           | 10           | 1e14                          |

| BSF     | Р           | 20           | 5e15                          |

| Emitter | В           | 20           | 6e15                          |

## **Photolithography**

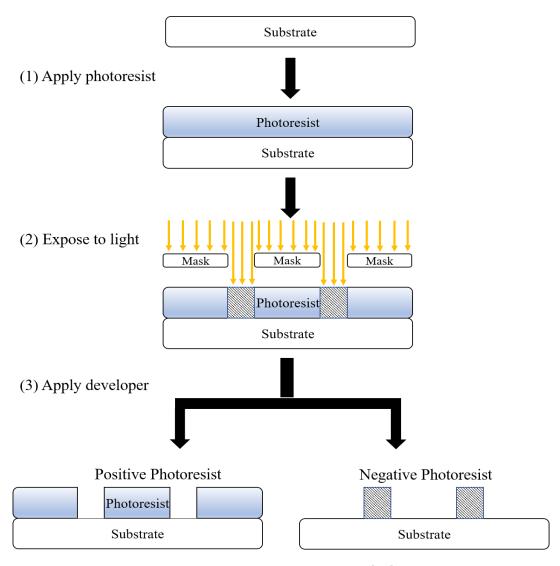

Photolithography is the most common used method to perform complex pattering of the p and n type contacts on the silicon wafer same surface. The key advantage of this technology its low typical feature size < 1 micrometer compared to other technologies; thus, it can be used for the most precise classification of structure. However, the downside of photolithography is the high equipment and process cost [42]. The brief explanation of photolithography process is as follow:

First, a photoresist layer is formed on the clean solar cell surface. The photoresist (PR) is an organic polymer substrate sensitive to ultraviolet radiation [43]. It has two different types positive photoresist and negative photoresist. The coating is done using EVG 120 tool from EV Group and the thickness of the PR layer depends on the chosen PR viscosity, the spin rotating speed and time. After the PR has been uniformly spread on the substrate, the wafer is pre-baked properly in the same machine. Next the exposure stage where the photoresist is subjected to intense light through chromic patterned mask. The light source illuminates the coated wafers with an ultraviolet (UV) light. The light exposure of the PR induces a chemical sift that ultimately enables the PR to be extracted. Exposure is applied with EVG 420 contact aligner manufactured by EV Group. The final step is development which is done again using EVG 120 tool from EV Group. In this process, the exposed/non-exposed areas differ chemically as one of the areas stay or dissolve during the development. The exposed region, in the case of a positive PR, is dissolved. However, this is not the case when negative PR is used where the exposed area remains. Figure 2.5 depicts the photolithography steps.

Photolithography process is applied a lot during this thesis work to process the solar cell. First, three photolithography steps are used to form the emitter and back surface field (BSF) regions on the rear side of the bifacial-IBC solar cell using PN mask. Next, it is also used to pattern the ITO layer using wide opening mask. Finally, two steps are applied to form the metal fingers on top of the TCO layer using narrow metal mask.

Figure 2.5: Photolithography steps [44].

#### High temperature annealing

After the deposition of the highly doped amorphous oxide layer, high temperature annealing is applied. There are several goals for this annealing step in order to activate the dopants and transform the a-Si layer into poly-Si layer [45]. Also, the diffusion of the dopants can also be enhanced through high temperature annealing. In other words, the deposited dopants will be activated and transferred. However, some of the dopants can be diffused into the bulk material which minimize the passivation quality. Additionally, the structure of the tunnel oxide layer will also be influenced by this step, Inducing pinhole formation at long annealing time and most possibly the layer breakdown. Samples are placed inside a Tempress furnace and annealing is performed on various time periods at high temperature between 850-950°C with pure N2 atmosphere to fabricate the bifacial-IBC solar cells.

#### Hydrogenation

One of the passivation methods used in this thesis is hydrogenation. It is one of the chemical passivation methods as it saturates, with the help of hydrogen atoms, the surface silicon atom dangling bonds. Two steps are involved in hydrogenation: the hydrogen rich capping layer  $(SiN_x)$  deposition, which is followed by forming gas annealing (FGA).

The  $SiN_x$  layer was deposited using PECVD method using the Oxford supplied instrument Plasmalab80plus. It is important to note that for this process ammonia (NH<sub>3</sub>) and Silane (SiH<sub>4</sub>) gasses are used, and it is performed under optimized conditions: a pressure of 87 [Pa] at 400°C as temperature.

The forming gas annealing is carried out to release H atoms embedded in the hydrogen rich  $SiN_x$  layer and to deliver additional hydrogen needed to passivate defects at the  $SiO_2$ /poly- $SiO_X$  interface [46]. In this thesis, the furnace developed by TEMPRESS SYSTEMS is the machine used for FGA. It was carried out for 30 minutes at a temperature of 400°C in the mixture of  $H_2$  and  $N_2$  atmosphere.

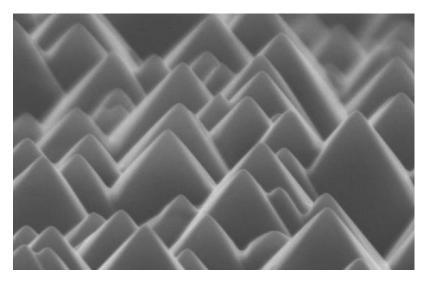

#### **Texturing**

Texturing is used in solar cells to maximize light absorption. This is accomplished by etching the cell surface by an alkaline solution. Two orientations can be represented in the c-Si lattice: <100> and <111>. The <100> crystal lattice orientation has an etching rate 50 times higher than that for the <111> orientation when it is exposed to this solution [47]. This is done until the lattice structure becomes <111> which means that the flat surface of the cell changes into a sequence of random pyramids [48]. The textured surface is shown in figure 2.6.

Figure 2.6: c-Si textured surface [49].

In this thesis, texturing is performed on the solar cell front surface to minimize the reflection losses. The used alkaline solution is held at high temperature 80°C prepared using a 4:1 ratio mixture of water and tetramethylammonium hydroxide (TMAH) with an additional 120 ml solution of ALKA-TEX.

#### Transparent conductive oxide (TCO) layer

The Transparent conductive oxide (TCO) layer is used in this thesis project for two main reasons: First, doped poly-SiOx layers are used as rear contacts in the bifacial-IBC solar cell. Compared to poly-Si, the poly-SiOx has relatively low conductivity. In other words, TCO layer serves as an electrical contact for solar cell operation as the transport of charge carriers may be inefficient at the poly-SiOx/metal interface. Second, for better light It may also function in the cell as an anti-reflection coating (ARC) film. Thus, to maximize the solar cell performance in the active wavelength range, this layer should be highly transparent by optimizing the refractive index and highly conductive by increasing the charge carrier's mobility [81].

Typical TCO layers are formed from fluor-doped tin oxide ( $SnO_2$ : F), aluminum-doped zinc oxide (ZnO:AI), boron-doped zinc oxide (ZnO:BI), hydrogen-doped (hydrogenated) indium oxide ( $In_2O_3:HI$ ) [50]. For this thesis, the Indium Thin Oxide optimized with PVMD group was chosen, which is a mixture of about 90% indium oxide ( $In_2O_3$ ) and 10% tin oxide ( $SnO_2$ ). It is chosen because it provides the trade-off between transparency and conductivity [51]. It can be applied using physical vapor deposition, namely sputtering method which results in a layer with high mobility as well as a proper work function without causing serious damage for both the semiconductor and metal contact [5]. The deposition of the ITO layer was performed with patterned structure at the rear side of the bifacial-IBC solar cell with a target thickness around 80 nm. This thickness maintains appropriate light trapping and charge carrier's transport.

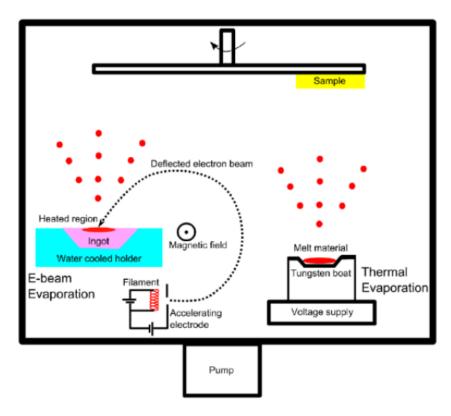

#### Metallization

Metallization is the last step in the solar cell fabrication. This process plays a vital role is the solar cell output optimization. First, optically by the means of metal gridlines, as the gridlines width increases it introduces more shading effect which ultimately affects the short circuit current. Second electrically, the metal fingers on the surface add more series resistance to the solar cells, which influences the fill factor [52]. For this project, the first used metal deposition method is the metal evaporation. It used to deposit both silver and aluminum or the solar cell rear side. Figure 2.7 shows a schematic drawing of the process. Typically, in this process either resistive evaporation or electron beams are applied to warm the metal ingots above the material melting point. The substance that has been evaporated would uniformly fill the deposition chamber, which subsequently cover the target surface. The metal evaporation is executed at high vacuum 10<sup>5</sup>, which means that the material oxidation and deposition thickness is well controlled [53]. After deposition, the target cools down and the metal condense back into a solid.

The used machine in this project is Provac evaporation machine at PVMD group. It worth to mention that to pattern the metal on the bifacial IBC solar cell rear side, a thick a uniform three photoresist layers is first applied to cover the wafer surface. This is done to accomplish a well patterned and thick metal layer. Next, a full area metal deposition is performed and the undesirable metal region on the solar cell surface is extracted by a metal lift-off step using acetone or by etching the metal seed layers after performing cupper plating process.

Figure 2.7: Schematic of metal evaporation process [53].

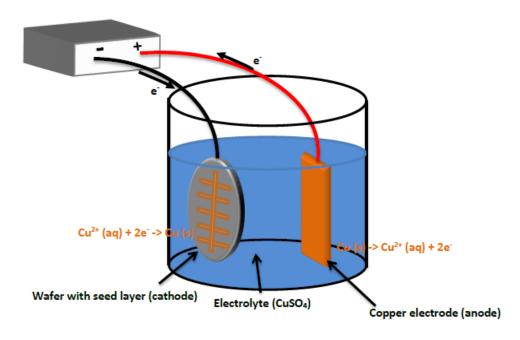

## Cu electroplating

Cu electroplating is an electrochemical (redox) reaction. This reaction requires the presence of two electrodes anode and cathode and electrolyte solution. The basic working principle is done as follow the wafer is placed at the cathode and the cupper source material at the cathode with CuSO<sub>4</sub> as an electrolyte solution. When the reaction takes place, the cupper at the cathode is dissolved in the solution and transported to the anode in our case is the solar cell. A schematic overview of copper plating process is shown in figure 2.8.

Figure 2.8: schematic of Cu plating.

The used machine during this thesis is an inhouse built-in machine in the MEMS lab. The wafer is placed horizontally on the holder and fixed with four clamps at the wafer edge. Next, the wafer holder is immersed in the plating bath at 28°C and the anode (copper plate) is fixed above facing the wafer holder. Bothe the copper plate and the wafer holder is connected to a power booster (10A) where the copper plate is connected to the negative side and the wafer holder to positive resulting in a negative current which is important to perform the reaction. During this process, the current is kept constant however the voltage is cannot be controlled, and it keeps changing during the process.

It is worth to mention that this process is very critical because copper diffusion to the silicon layer occurs at high speed levels leading to a serious impurities which will act as a recombination centers leading eventually to lower the carriers lifetime and the overall cell performance. Therefore, the silicon layer should be protected against the copper diffusion. This is done by adding a metal seed layer which acts as a barrier for the copper and as s a seed layer for the used current during the process. For our process, an added two metal seed layer a 200 nm aluminum and a 200 nm silver which will be etched away after performing the cupper plating process.

## 2.2 Characterization techniques

The characterization method and techniques used to assess the material quality for the optimization of the manufacturing process and the performance of the devices are described in this section. It is performed on different sample types: the symmetrical samples used to test the passivation quality and the full fabricated solar cells.

#### Photo-conductance lifetime measurement

The passivation quality of a silicon wafer can be specified through the effective lifetime (eff) of the minority charge carriers. The lifetime of the minority carrier is determined by the average time that the excess minority carrier need before it recombines. The effective lifetime of the carrier largely depends on the recombination process on both the wafer bulk and surface. Having the carrier density and lifetime, the recombination current density (J<sub>0</sub>) also can be calculated [55].

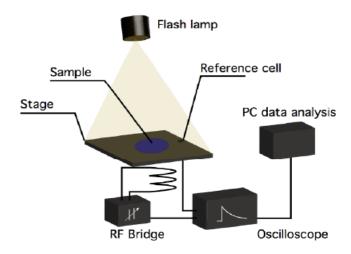

For the detection of the minority carrier lifetime (eff) and implied voltage ( $iV_{oc}$ ), the Sinton WCT-120 lifetime tester (Figure 2.98) was used. This unit is fitted with a filtered xenon flash lamp that provides a red range red color light. In the wafer bulk, the light flash requires the production of excess charge carriers which it will subsequently recombine until the balance is achieved. Next, the eddy-current conductance sensor is another unit that is used in the Sinton WCT-120. It tests the intensity of the light given by the lamb described above and the photoconductance of the wafer.

Figure 2.9: Measurement setup of photoconductance lifetime tester [55].

## Ellipsometry

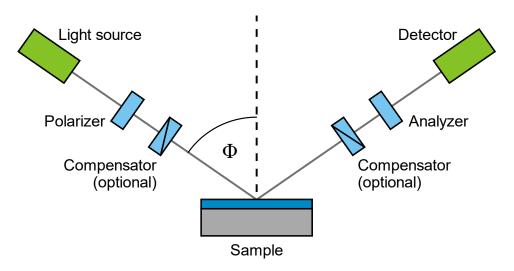

Ellipsometry is primarily used to measure the thickness of the examined layer and its optical constant. The measurements of the layers thickness should be accurate, because it plays a vital role in the solar cell designing. Ellipsometry tests the difference in incident light polarization relative to the light detector of the reflected light from the sample. Figure 2.10 shows the ellipsometry setup.

Figure 2.10: Ellipsometry setup [56].

The EC-400 manufactured by J.A Woolam Co. is the tool used in this project. Measurements were predominantly carried out on layers deposited on a wafer substrate. This allowed the thickness of the deposited layers to be found and further optimized for the best possible cell outcomes.

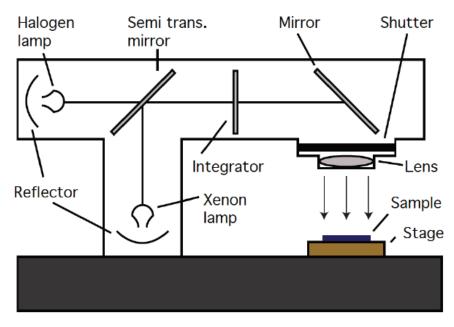

#### **Current-Voltage measurements**

Current and voltage characterization are the most significant parameters to describe the bifacial-IBC solar cells. Current-voltage measurements can be used to obtain these parameters. The typical test conditions are simulated with a AAA class Wacom WXS-156SL2 solar simulator [57] with the following setup: First a Halogen and a Xenon lamp are combined to correctly simulate the illumination of one sun using AM 1.5 spectrum and irradiance equal to 1000 W/m². Next, a temperature controller is mounted on the test stage where the solar cells are positioned to ensure that the temperature of the solar cell is kept constant at 25°C. Figure 2.11 shows the current-voltage measurements setup.

Figure 2.11: Current-voltage measurements setup [57].

## **Profile analyzing Laser Microscope**

The profile analyzing laser microscope can be used to measure the film thickness and roughness in addition to the ability to take an optical image of the material surface with nanometer resolution. This microscope is even able to measure any object with bumpy surface. The basic working principle of this microscope is by incorporating the laser light with a white light and observing the reflected laser light from the material surface [58].

During this thesis, the used microscope was VK-X250K manufactured by KEYENCE. It is used to take an optical image of the tested samples to compare the blistering effect. This is performed by simply placing the sample test on the device stage and it will automatically scan the sample. Figure 2.12 shows an image of the used microscope.

Figure 2.12: Profile analyzing laser microscope device [60]

# 3 Ion-implantation for bifacial-IBC solar cell

The aim of this chapter is to test the feasibility of the ion-implantation as doping and patterning approach for the fabrication of bifacial IBC solar cells. Therefore, the optimization of ion-implanted poly- $SiO_X$  carrier selective passivation was conducted. In section 3.1, it is aimed to discuss the crucial requirements for optimizing the passivation quality. The proposed process for bifacial-IBC solar cell and the necessary passivation tests were discussed in the section 3.2. Next in section 3.3, the thickness of the intrinsic a- $SiO_X$ :H layer deposited by PECVD at different annealing conditions is optimized. This is done to have a sufficiently crystallized structure and a desirable doping profile. Finally, the essential hydrogenation process is also examined to minimize defects, dangling bonds, at the interface between the c-Si bulk surface and poly- $SiO_X$  layer.

## 3.1 Requirements for poly-SiO<sub>x</sub> passivation contact

As mentioned in chapter 2, the tunnel oxide carrier selective passivation contact for poly- $SiO_x$  required the presence of an ultra-thin  $SiO_x$  layer formed on a doped poly- $SiO_x$  layer. This section discusses the requirements and factors needed to optimize the carrier selectivity of the **ion-implanted** poly- $SiO_x$  CSPCs which can be summarized as follow:

#### Silicon oxide layer

Tunnel oxide layer provides the chemical passivation of the c-Si surface by bonding with the Si dangling bonds. It should be thin enough to facilitate the charge carrier tunneling through it to the doped poly- $SiO_x$  layer. To obtain a better passivation quality of the CSPC, the integrity and the thickness of the formed tunnel oxide layer should be optimized.

First, the integrity of the tunnel oxide layer is crucial to provide the high passivation and it should be strong enough to stand the following high temperature processes. For example, the chemical oxidation NAOS used during in our thesis has low thermal stability which means the high temperature process may damage the tunneling oxide layer and might generate a local pin hole. These pin holes' increased with increasing the annealing thermal budget. Increasing the pin holes density reduces the contact resistivity and thus enhancing the charge carrier collection, however this brings an increasing in the recombination current density. Therefore, this layer must be optimized to provide an excellent passivation.

Second, the thickness of the tunneling oxide layer should be optimized to obtain the sufficient thickness required for the charge carrier tunneling to the doped poly-SiO<sub>x</sub> layer to provide the field effect passivation. According to previous PVMD group research, the best passivation effect for both contacts

were obtained with an oxide layer thickness of  $\sim$ 1.4 nm prepared by keeping the wafer in 69.5% HNO<sub>3</sub> solution for 60 minutes [9]. Therefore, we followed the findings of the previous work in our research.

#### Doped poly-SiO<sub>X</sub> layer

The doped poly-SiO<sub>x</sub> layer plays a vital role in providing a good performance of the passivating contact by providing field effect passivation through introducing a sufficient band bending at the poly-SiO<sub>x</sub>/SiO<sub>2</sub>/c-Si interferences. To obtain a better optical and electrical properties, the doping concentration, and the thickness of the doped poly-SiO<sub>x</sub> layer should be optimized.

First, the doping concentration play a vital role in the passivation quality of the doped poly-SiO<sub>x</sub> layer. The ideal doping profile is the one which provides the field effect passivation without passing the limit where the Auger recombination in the c-Si surface becomes dominant. In addition, if the doping concentration is too high, this may reduce the field effect passivation due to the increasing doping level and depth of the in-diffusion area of the dopants in the c-Si bulk material during the following high temperature process [64]. On the other hand, if the doping concentration was too shallow in the poly-SiO<sub>x</sub> layer the field effect passivation will be very poor, due to the non-sufficient filed effect passivation. By adjusting the implantation dose, the doping concentration of the poly-SiO<sub>x</sub> layer can be controlled. There is a wide variety to choose the implantation dose, however, the implantation energy is limited to 5 keV by the implanter. It is worth to mention that, it is suggested that a higher impanation energy for Phosphorous implantation than that for Boron implantation can be accepted. The low energy is requited due to the smaller size of boron atoms and their high diffusivity in silicon relative to Phosphorous atoms [65].

Second, optimizing the doped poly- $SiO_X$  layer thickness is also very important to achieve a high-quality passivation. On one hand, controlling the doped layer thickness using an optimized doping concentration and annealing conditions will results in a good electrical performance [66]. On the other hand, using a thinner layer thickness can reduce the optical losses (parasitic absorption) [67] induced by the doped layer significantly. The using of the thick poly-Si layers in the IBC solar cells is a not serious problem because both contacts are located at the solar cell rear side [31]. However, this is not an option for our bifacial-IBC solar cell because it benefits from the incident light on both the front and rear side of the solar cell.

Finally, the doped layer can be further optimized by increasing its transparency to limit the light absorption within this layer which will results in high optical performance. This can be achieved by controlling the layer oxygen content during the PECVD deposition process [68]. The absorption coefficient is shown to be decreasing with increasing the oxygen content, especially at long wavelength region, indicating that the material becomes more transparent [69].

#### High temperature annealing conditions

During the high temperature annealing step, three key occurrences take place. First, the dopant atoms (Phosphorous and Boron) are being activated and diffused within the poly- $SiO_X$  layers, therefore the intrinsic buffer layer (a- $SiO_X$ :H) becomes doped. Second, the used thermal budget crystallizes the a- $SiO_X$  layer into poly- $SiO_X$ . Third, some of the dopants diffused into the bulk material (in-diffused area), which is not preferred.

As mentioned previously, if most of the ion-implanted dopants are confined inside the poly- $SiO_X$  layer, a high passivation quality can be obtained. However, this is a tricky process and required multiple tests to be optimized due to the difference in the diffusion properties of the Phosphorous and Boron atoms. In

other words, the energy required to activate and diffuse the Boron atoms is higher than the energy needed for Phosphorous atoms [70]. Additionally, the high mobility of boron atoms distribution in the silicon material relative to the Phosphorous atoms since the Boron atoms have a smaller size than Phosphorous atoms which means that Boron atoms are easily implanted much deeper into the poly-SiO<sub>X</sub> materials [71]. Therefore, the higher thermal budget process enhances the dopants activation on the  $p^+$  contact, however it may rise the Boron atoms diffusion into bulk material resulting in a weak field effect passivation, and enhanced Auger recombination.

Previous studies executed at PVMD group, claimed that a high passivation quality can be obtained at high temperature and short annealing time for both contacts [33]. Therefore, the annealing conditions used during this thesis project are decided to vary between 850°C and 1000°C as an annealing temperature with different annealing duration. It is worth to note that applying a hydrogenation treatment after the high temperature annealing process can further enhance the passivation quality through reducing the defect density at the c-Si/SiO<sub>2</sub> /poly-SiO<sub>3</sub> interfaces.

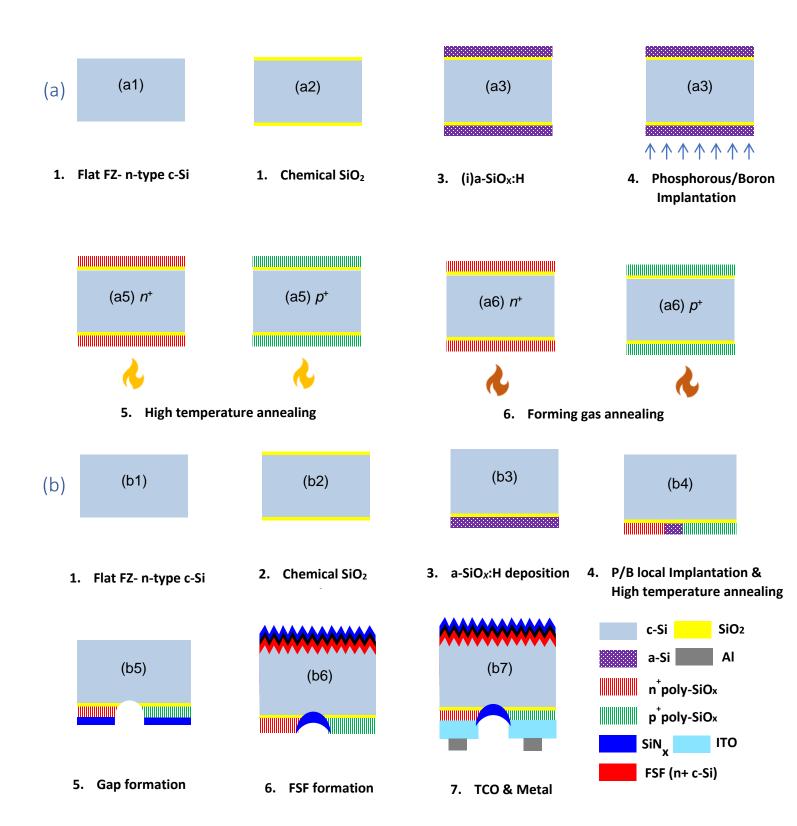

## 3.2 Sample preparation

In this section, the various manufacturing process that were implemented in order to obtain a good passivation quality are explained. On various passivation structure, passivation tests are conducted on symmetrical double side flat and textured samples. The test samples are fabricated at nearly the same conditions but the examined one to have a superior comparison between the expected results. In arrange to make the fabrication process clearer, a schematic sketch of all fabrication steps and deposited layers are indicated in figure 3.1 including the symmetrical test samples (a) and the ion-implanted bifacial-IBC solar cell (b).

Figure 3.1: (a) process flow for symmetrical samples preparation for passivation tests. (b) proposed flow chart of the Bifacial-IBC solar cell when deploying ion-implantation as doping and patterning approach.

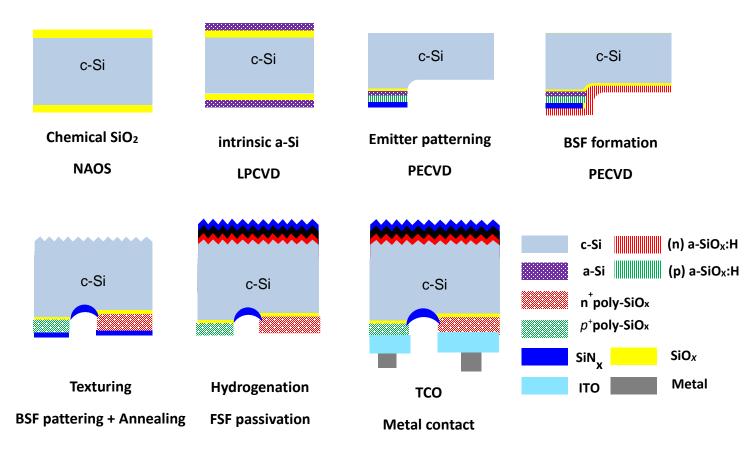

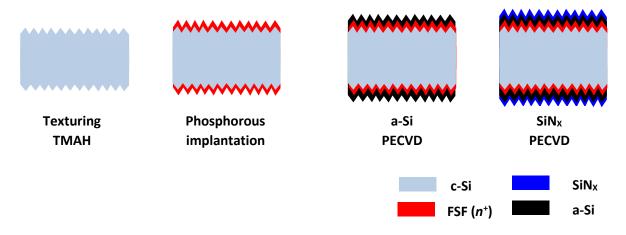

Figure 3.1(b) indicates the proposed bifacial-IBC solar cell flow chart using ion-implantation. First, the oxide layer is formed chemically by immersing the wafer in 69.5% solution for 1 hour. Next, the a-SiO $_X$ :H layer is deposited via PECVD at the rear side. Then, the boron and the phosphorous regions are locally implanted into the intrinsic a-SiO $_X$  layer by applying a lithography process. Next, an etching step is used to separate the BSF and the emitter fingers through lithography process followed by wet etching. Further, the textured front surface field on the front side formed chemically by TMAH with a lightly doped FSF implantation and SiNx as a passivation and ARC layer. Finally, on the rear side the ITO layer is formed by sputtering with the metal contact using copper plating.

The passivation properties need to be tested before the IBC cell process, in order to see the feasibility of ion-implantation for such IBC cell processes. Therefore, same processes, applied on the solar cell rear side Figure 3.1(b1-b3), are performed at the symmetrical test sample both sides.

As mentioned previously in section 2, the fabrication process starts using an n-type double side polished Float Zone (FZ) Si wafer with <100> surface orientation and an initial thickness of 280  $\pm$  20  $\mu$ m. Below, details for only the most important manufacturing steps are mentioned. However, some required steps, like standard wafer cleaning, are not listed below to provide clarity to the examined process. Furthermore, other layers with a protective feature such as SiN<sub>X</sub> and photolithography steps are not shown in figure 3.1, as they are etched away before conducting the measurements. The symmetrical test samples based on poly-SiO<sub>X</sub> carrier selective passivating contacts are fabricated as follow:

- 1. The starting point of preparing the symmetrical test samples was using a flat polished surface, Figure 3.1(a). However, it is worth to mention that textured surface can also chemically formed on the front surface by immersing the wafer in Tetramethylammonium Hydroxide (TMAH) solution for approximately 12 minutes at 80°C temperature to obtain a randomly textures silicon surface Figure 3.1(b5). Then, the wafers are dipped for 2 minutes in  $HNO_3/40\%$  HF to obtain a slightly rounding of the pyramid to minimize the defects centers. It is important to note that the other side of the wafer (rear side) should be protected during the texturing process using a  $SiN_X$  layer which can easily be removed afterwards during an etching step in BHF solution.

- 2. Next, after removing the SiNx on the other side, the tunneling oxide layer is formed chemically by immersing the silicon wafer in the 69.5% solution for 60 minutes at the room temperature. The resulting ultra-thin oxide layer has a thickness of approximately 1.4-1.5 nm [24].

- 3. Then, samples are processed in the PECVD chamber to deposit an intrinsic a-SiO<sub>X</sub>:H layer on the oxide layer. To obtain the intrinsic layer, the doping gases (PH<sub>3</sub> and B<sub>2</sub>H<sub>6</sub>) were set to zero, during the deposition.

- 4. After the intrinsic layer deposition, an implantation step is performed using Varian ion implanter E500HP where Phosphorous and Boron atoms, at certain implantation dosage and energy, are used to form the  $n^+$  and  $p^+$  regions, respectively.

- 5. Further, a post implantation high temperature annealing is performed at multiple temperature and duration to activate the dopants and to crystalize the amorphous silicon oxide layers and transforming to poly- $SiO_X$  layer. The annealing time and temperature are changed to identify the optimal passivation conditions.

6. Finally, to further enhance the chemical passivation at the interfaces a forming gas (10% H<sub>2</sub> in N<sub>2</sub>) annealing treatment is carried out in a tube furnace at constant temperature of 400°C for 30 minutes.

## 3.3 Optimization of PECVD intrinsic a-SiO<sub>x</sub>:H thickness

This section presents the influence of the intrinsic a-SiO<sub>X</sub>:H layer on the passivation quality of the carrier selective passivation contact enabled by poly-SiO<sub>X</sub>, prepared with **ion-implantation** as doping approach. As previously introduced in section 3.1, combining both the optimum interlayer thickness and the doping concentration using a proper annealing conditions can boost the passivation, corresponding to the improvement in the electrical and optical properties of the tested wafer. The tested intrinsic layer deposited in PECVD chamber studied at different thicknesses (30, 50, 75 nm, respectively). The main aim of varying the thickness of the a-SiO<sub>X</sub>:H layer is to check whether the **ion-implantation** energy was already sufficient for dopants to be implanted through this layer. The deposition is performed using an optimized recipe taken from a previously conducted study at PVMD group [72]. This study claims that the best deposition parameters are SiH<sub>4</sub> flow of 45 sscm, (1-2) mbar deposition pressure and 180°C as deposition substrate temperature. The studied symmetrical samples are depicted in figure 3.1(a). The doping concentrations of these samples is kept constant during the experiment. The ion implantation energy and dosage for the  $n^+$  and  $p^+$  regions are 20keV 5e15 ion/cm<sup>2</sup> and 20keV 6e15 ion/cm<sup>2</sup>, respectively.

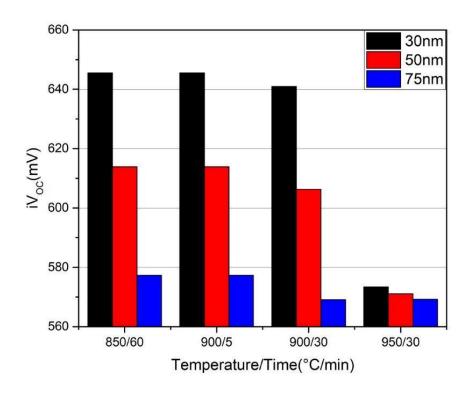

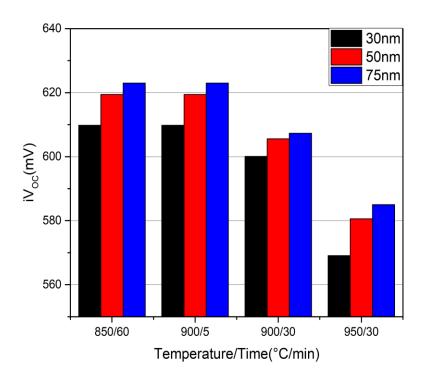

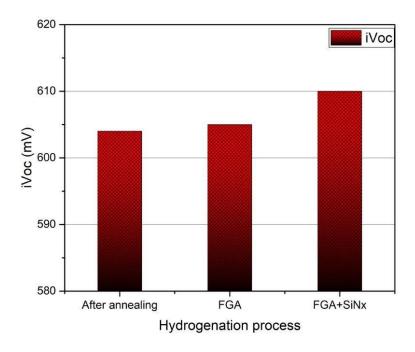

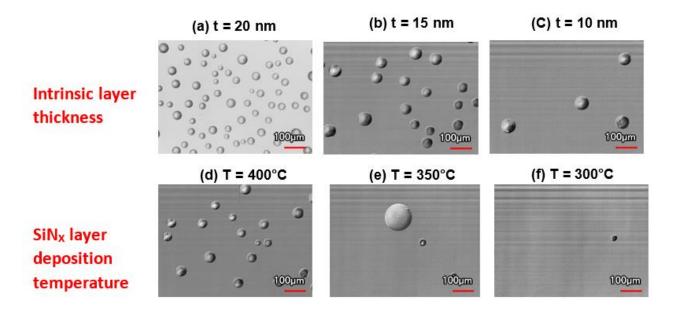

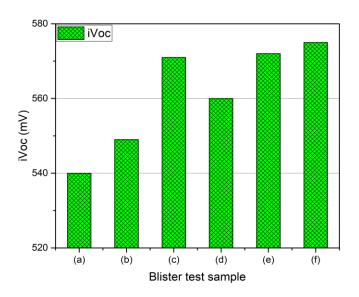

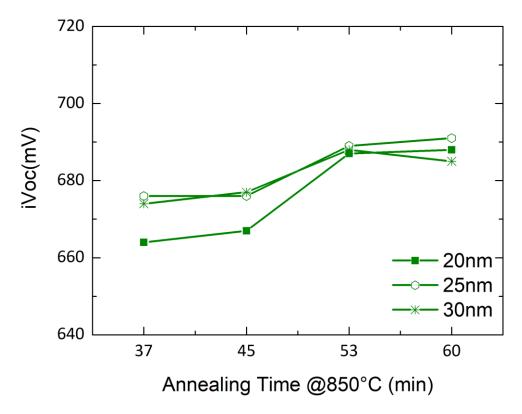

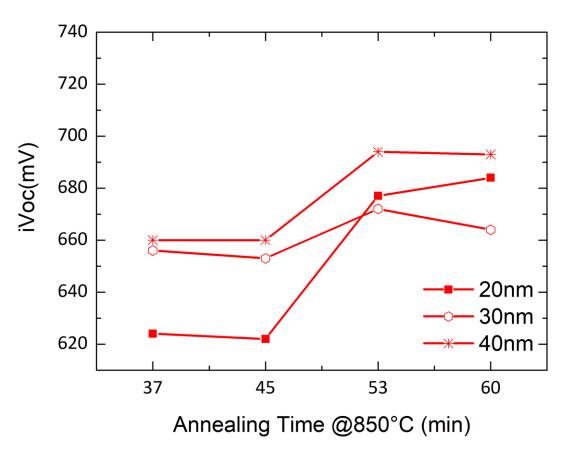

The a-SiO<sub>X</sub>:H layer thickness tests were initially performed using flat symmetrical ( $n^+$ ) poly-SiO<sub>X</sub> samples as shown in figure 3.1(a). Figure 3.2 shows the iV<sub>OC</sub> as a function of intrinsic layer thickness at different annealing time and temperature. Looking at the figure, we notice that all studied intrinsic layer thickness follow the same trend where the passivation quality decreases with increasing the temperature and annealing time. The optimum annealing temperature for the studied samples is obtained at lower temperature with a slightly higher iV<sub>OC</sub> at 900°C. Analyzing the different thicknesses in the annealed state, the best results have been obtained for the intrinsic a-SiO<sub>X</sub>:H layer with a thickness of 30 nm annealed at 900°C/5min with iV<sub>OC</sub> value of 646 mV and teff of 312  $\mu$ s .