### Computer Engineering Mekelweg 4, 2628 CD Delft The Netherlands

http://ce.et.tudelft.nl/

# MSc THESIS

# Task Scheduling for Adaptive Reconfigurable VLIW Multicore Processors

Georgios Andronikidis

#### Abstract

CE-MS-2014-16

Embedded Reconfigurable Architectures (ERA) is a project with the objective to design a platform that combines reconfigurable computing and network elements which can adapt on-the-fly their composition, organization and even instruction-set architectures in an effort to provide the best possible trade-offs in performance and power for the given application(s). Although some of this adaptiveness is controlled by software (mainly the operating system), the goal of the ERA project is that great deal of this control actually takes place automatically at hardware level, by the Hardware scheduler. This thesis deals specifically with the problem of hardware task scheduling. We studied a variety of possible implementations for the task scheduling in the ERA platform. After getting an inside look of the Processing component of the ERA platform and understanding the particularities of it, as well as of its main building block, the  $\rho$ -VEX core, we tried to find scheduling algorithms available in the bibliography to implement as the Hardware scheduler of ERA. This literature research did not yield any results, both because of the complexity of the problem, as well as the pioneer characteristics of ERA that we would like to take advantage of. We designed some simple scheduling algorithms, especially tailored for the ERA platform and tested

them. The most important of them were Basic, which simply stalls the tasks until there are enough resources for them, Versioning, which brings a different binary from the memory which is compiled to run on a smaller core and Generic Binary which uses a binary that is especially compiled to run on any core, so downgrading a task does not lead to the communication cost that Versioning suffers and upgrading a task becomes possible. We present the most important of the experiments that took place within this thesis and show that GB++ (a version of GB that supports forced priorities, interrupts and upgrading by default) is the most promising algorithm that can take advantage of all the characteristics and the abilities of ERA, without being the fastest one, which is Versioning. Finally, we researched and defined the minimum requirements of GB++ in order to become apart from the rest also the fastest algorithm for ERA.

# Task Scheduling for Adaptive Reconfigurable VLIW Multicore Processors

#### THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

COMPUTER ENGINEERING

by

Georgios Andronikidis born in Ptolemais, West Macedonia, Greece

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

# Task Scheduling for Adaptive Reconfigurable VLIW Multicore Processors

#### by Georgios Andronikidis

#### Abstract

Embedded Reconfigurable Architectures (ERA) is a project with the objective to design a platform that combines reconfigurable computing and network elements which can adapt on-thefly their composition, organization and even instruction-set architectures in an effort to provide the best possible trade-offs in performance and power for the given application(s). Although some of this adaptiveness is controlled by software (mainly the operating system), the goal of the ERA project is that great deal of this control actually takes place automatically at hardware level, by the Hardware scheduler. This thesis deals specifically with the problem of hardware task scheduling. We studied a variety of possible implementations for the task scheduling in the ERA platform. After getting an inside look of the Processing component of the ERA platform and understanding the particularities of it, as well as of its main building block, the  $\rho$ -VEX core, we tried to find scheduling algorithms available in the bibliography to implement as the Hardware scheduler of ERA. This literature research did not yield any results, both because of the complexity of the problem, as well as the pioneer characteristics of ERA that we would like to take advantage of. We designed some simple scheduling algorithms, especially tailored for the ERA platform and tested them. The most important of them were Basic, which simply stalls the tasks until there are enough resources for them, Versioning, which brings a different binary from the memory which is compiled to run on a smaller core and Generic Binary which uses a binary that is especially compiled to run on any core, so downgrading a task does not lead to the communication cost that Versioning suffers and upgrading a task becomes possible. We present the most important of the experiments that took place within this thesis and show that GB++ (a version of GB that supports forced priorities, interrupts and upgrading by default) is the most promising algorithm that can take advantage of all the characteristics and the abilities of ERA, without being the fastest one, which is Versioning. Finally, we researched and defined the minimum requirements of GB++ in order to become apart from the rest also the fastest algorithm for ERA.

**Laboratory** : Computer Engineering

Codenumber : CE-MS-2014-16

Committee Members :

Advisor: Dr. ir. Stephan S. Wong, CE, TU Delft

Chairperson: Dr. ir. Stephan S. Wong, CE, TU Delft

Member: Dr. Zaid Al-Ars, CE, TU Delft

Member: Dr. ir. T.G.R.M van Leuken, CE, TU Delft

To my beloved parents and in memory of Vasiliki Theodoridou:

«Της Βάσως τα εγγόνια να λένε...» ("So that people talk about Vaso's grandchildren...")

# Contents

| Li | st of | Figure       | es                                                             | viii |

|----|-------|--------------|----------------------------------------------------------------|------|

| Li | st of | Tables       | 5                                                              | ix   |

| Li | st of | Acron        | yms                                                            | xi   |

| Li | st of | Algori       | ithms                                                          | xiii |

| A  | cknov | wledge       | ments                                                          | xv   |

| 1  | Intr  | oducti       | ion                                                            | 1    |

|    | 1.1   | The E        | RA project                                                     | . 1  |

|    | 1.2   |              | ation                                                          |      |

|    | 1.3   |              |                                                                |      |

|    | 1.4   |              | $\operatorname{pdology}$                                       |      |

|    | 1.5   | Overvi       | iew                                                            | . 3  |

| 2  | Bac   | kgrour       | nd                                                             | 5    |

|    | 2.1   | The $\rho$ - | -VEX VLIW processor                                            | . 5  |

|    | 2.2   | The V        | LIW approach                                                   | . 9  |

|    | 2.3   | Paralle      | el algorithms                                                  | . 9  |

|    | 2.4   | Relate       | ${ m ed}$ work                                                 | . 12 |

|    |       | 2.4.1        | Grid Computers                                                 | . 12 |

|    |       | 2.4.2        | Homogeneous Multicore Processors                               |      |

|    |       | 2.4.3        | Heterogeneous Multicore Processors and Multiprocessor Computer |      |

|    | 2.5   | Conclu       | usion of Chapter 2                                             | . 14 |

| 3  | Imr   | lemen        | tation                                                         | 15   |

|    | 3.1   |              | ic scheduling algorithm                                        |      |

|    |       | 3.1.1        | The naive approach                                             |      |

|    |       | 3.1.2        | Time complexity analysis                                       |      |

|    |       | 3.1.3        | A realistic basic algorithm                                    |      |

|    | 3.2   | Version      | ning                                                           | . 18 |

|    |       | 3.2.1        | Communication Penalty                                          | . 18 |

|    |       | 3.2.2        | Time Complexity                                                | . 20 |

|    | 3.3   | The G        | leneric Binary                                                 | . 21 |

|    |       | 3.3.1        | Benefits and disadvantages                                     | . 21 |

|    |       | 3.3.2        | Priority tasks                                                 |      |

|    |       | 3.3.3        | Interrupts                                                     |      |

|    |       | 3.3.4        | Time complexity                                                | . 25 |

|                |     | 3.3.5 GB++                                    | 26        |

|----------------|-----|-----------------------------------------------|-----------|

|                | 3.4 | AlgD and AlgBall8                             | 27        |

|                | 3.5 | Conclusion of Chapter 3                       | 27        |

| 4              | Sim | ulator and benchmarks                         | 29        |

|                | 4.1 | The simulator                                 | 29        |

|                |     | 4.1.1 Task list generator                     | 29        |

|                |     | 4.1.2 Priority scenario generator             | 30        |

|                |     | 4.1.3 Algorithm simulator                     | 30        |

|                |     | 4.1.4 Small scripts                           | 31        |

|                |     | 4.1.5 Outputs                                 | 31        |

|                | 4.2 | Testing methodology                           | 31        |

|                |     | 4.2.1 Specific microtests                     | 32        |

|                |     | 4.2.2 Short-run testing                       | 32        |

|                |     | 4.2.3 Long-run testing                        | 33        |

|                | 4.3 | Conclusion of Chapter 4                       | 33        |

| 5              | Res | ults                                          | 35        |

|                | 5.1 | Crosspoints                                   | 35        |

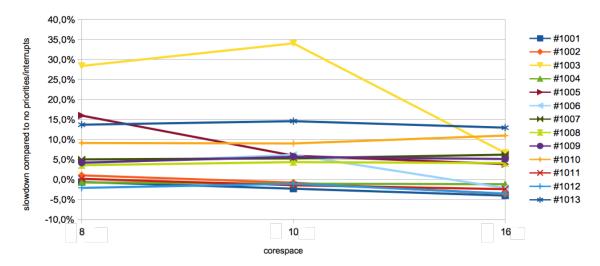

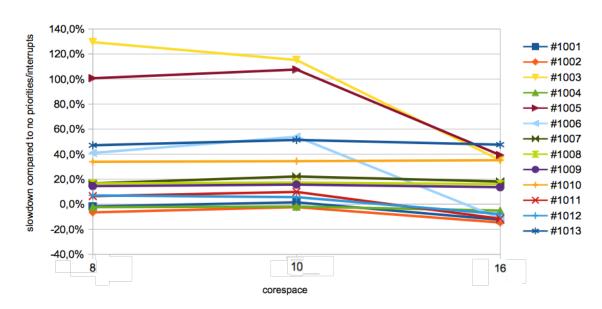

|                |     | 5.1.1 Corespace                               | 36        |

|                |     | 5.1.2 Task list window                        | 37        |

|                |     | 5.1.3 Reloading penalty                       | 39        |

|                |     | 5.1.4 GB execution times                      | 40        |

|                |     | 5.1.5 Priorities and interrupts               | 42        |

|                |     | 5.1.6 The effect on total execution times     | 42        |

|                | 5.2 | Task latency                                  | 44        |

|                |     | 5.2.1 The nature of the tasks                 | 44        |

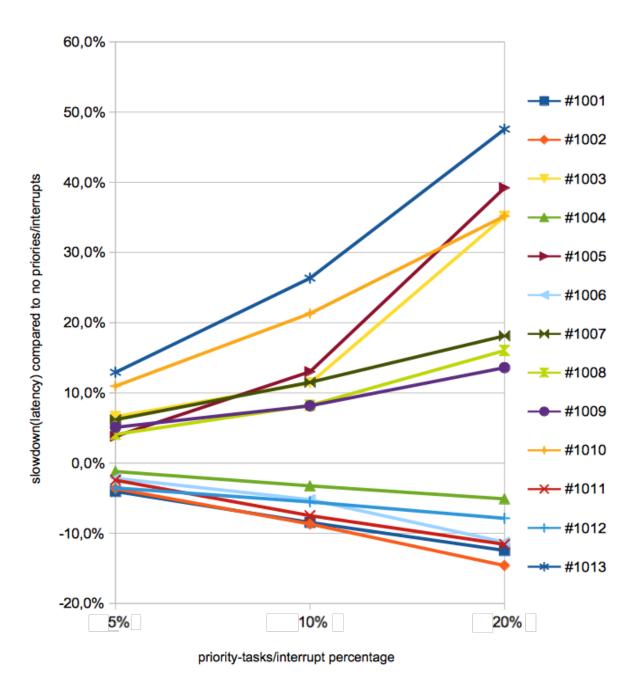

|                |     | 5.2.2 Latency and priorities/interrupts       | 47        |

|                | 5.3 | GB vs Versioning                              | 60        |

|                | 0.0 | 5.3.1 GB vs GB++                              | 60        |

|                |     | 5.3.2 GB++ with Versioning execution times    | 60        |

|                | 5.4 | Conclusion of Chapter 5                       | 62        |

|                | 0.1 | 5.4.1 The upgrading paradox and 2D scheduling | 62        |

|                |     | 5.4.2 Summing up the results                  | 64        |

|                |     |                                               |           |

| 6              |     | nclusions                                     | 67        |

|                | 6.1 | Summary                                       | 67        |

|                | 6.2 | Main problem statement & contributions        | 68        |

|                | 6.3 | Future work                                   | 69        |

| Bibliography 7 |     |                                               |           |

| A              | App | pendix A                                      | <b>75</b> |

# List of Figures

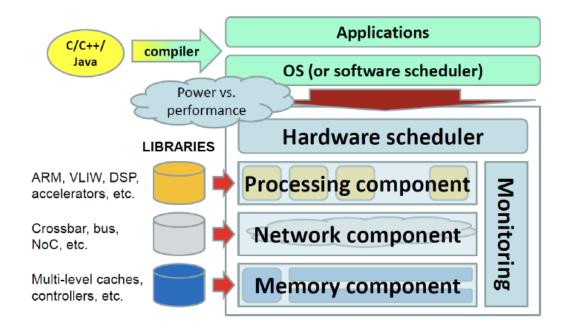

| 1.1  | The ERA platform                                                                                                                        | 2              |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1.2  | Flow chart showing of methodology for every goal                                                                                        | 3              |

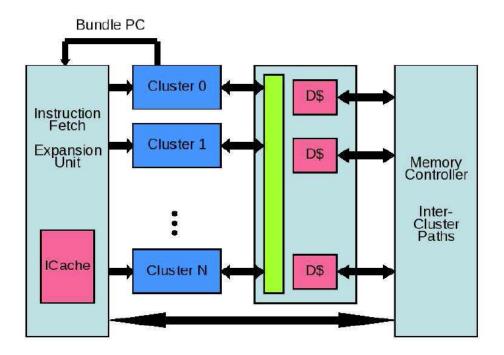

| 2.1  | The block diagramme of a VEX Multicore Processor                                                                                        | 5              |

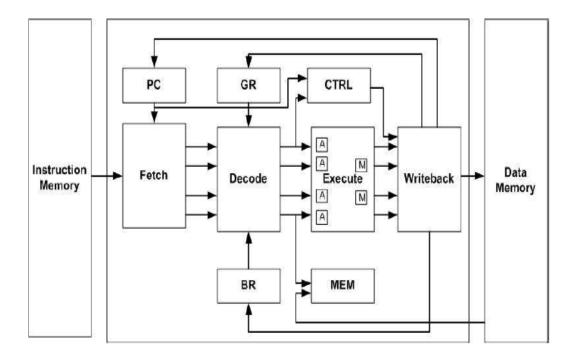

| 2.2  | The block diagramme of a 4-issue $\rho$ -VEX                                                                                            | 6              |

| 2.3  | How $\rho$ -VEX cores can be combined to form bigger ones                                                                               | 7              |

| 2.4  | Datapath sharing in $\rho$ -VEX cores                                                                                                   | 8              |

| 2.5  | A NOP in the 2nd position (bit-31 to bit-16) of a 4-issue VLIW                                                                          | 9              |

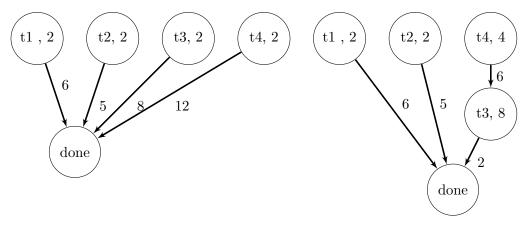

| 2.6  | Two of the many scheduling possibilities of just 4 tasks in ERA                                                                         | 10             |

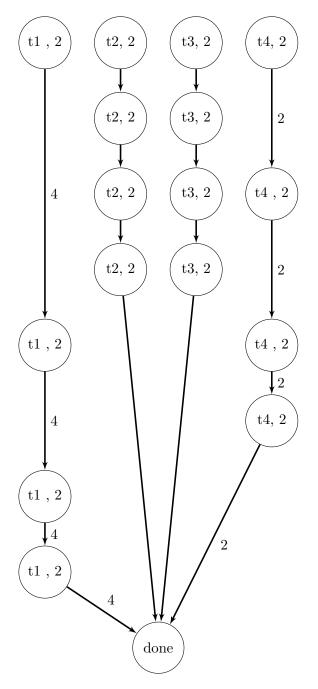

| 2.7  | A scheduling graph with only 2-issue nodes                                                                                              | 11             |

| 2.8  | Homogeneous multicore system                                                                                                            | 13             |

| 2.9  | Scheduling graph for a homogeneous multicore system                                                                                     | 13             |

| 3.1  | A 2-issue and a 4-issue task running in an ERA MCP                                                                                      | 15             |

| 3.2  | A bubble created in the execution timeline                                                                                              | 16             |

| 3.3  | The logic that detects available cores of any size (2,4,8,16) on an ERA MCP of corespace 16. Output Low means available, whereas output |                |

|      | High means unavailable                                                                                                                  | 17             |

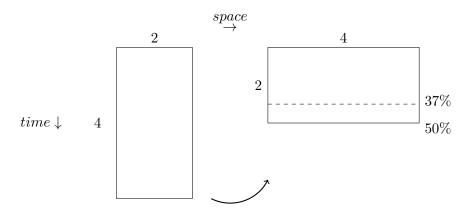

| 3.4  | A scenario on AlgA (left) and on Versioning(right)                                                                                      | 19             |

| 3.5  | Parallelising downgrading                                                                                                               | 20             |

| 3.6  | GB (left) and Versioning (right) handling a new 4-issue task                                                                            | $\frac{1}{22}$ |

| 3.7  | GB stealing resources from a task(left) or freezing it (right)                                                                          | 23             |

| 3.8  | A 4-issue forced priority task in an ERA MCP of corespace 8                                                                             | 24             |

| 3.9  | A task suddenly gains priority.                                                                                                         | 25             |

| 3.10 | Logic for parallelising default upgrading of core i                                                                                     | 26             |

| 4.1  | An abstract diagramme of the simulator                                                                                                  | 29             |

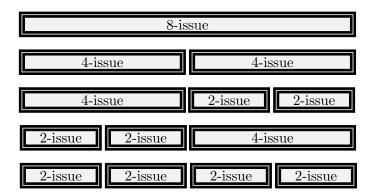

| 5.1  | The 5 different situations in which a corespace 8 ERA MCP can be found.                                                                 | 36             |

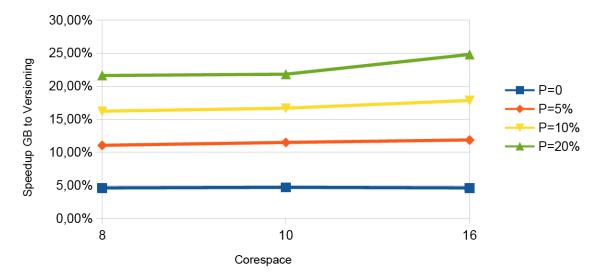

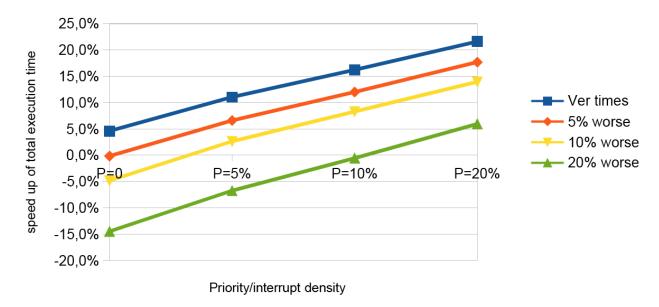

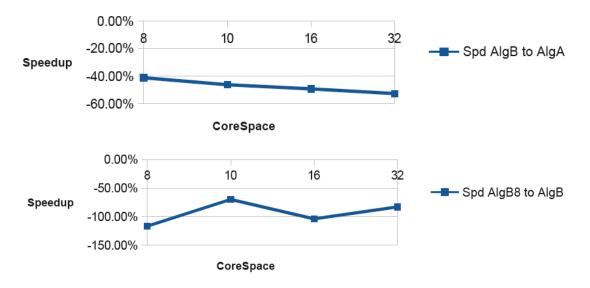

| 5.2  | The effect of the corespace in the performance of the algorithms                                                                        | 36             |

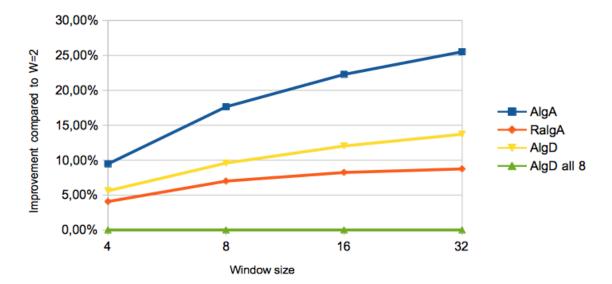

| 5.3  | Total execution times normalized to W=2                                                                                                 | 38             |

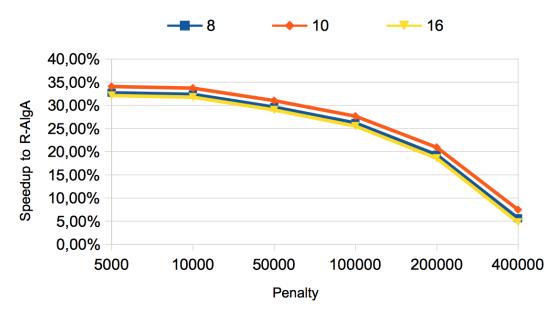

| 5.4  | Performance drop of Versioning as the penalty increases                                                                                 | 40             |

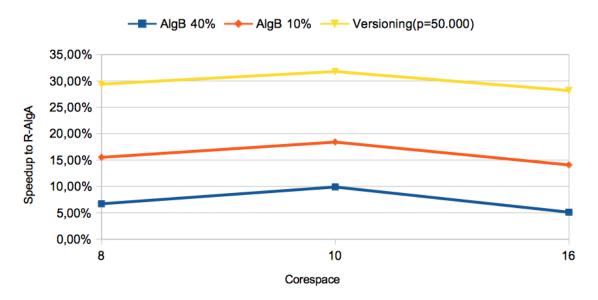

| 5.5  | Comparison of GB 40% and 10% times and Versioning                                                                                       | 41             |

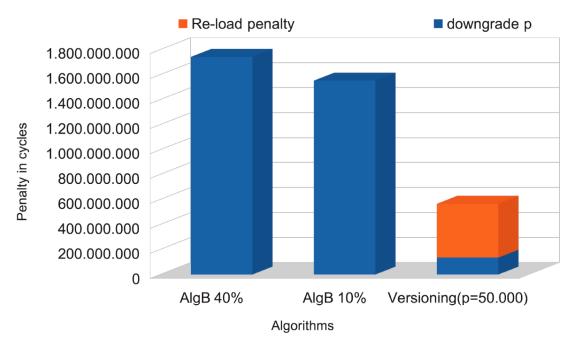

| 5.6  | Penalty analysis for GB and Versioning                                                                                                  | 42             |

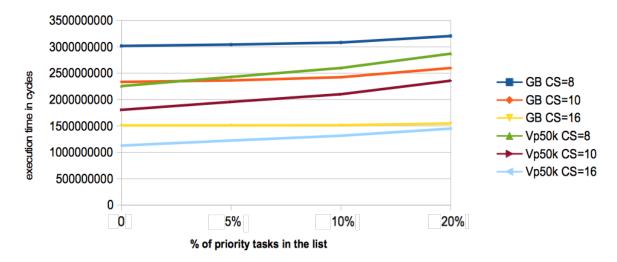

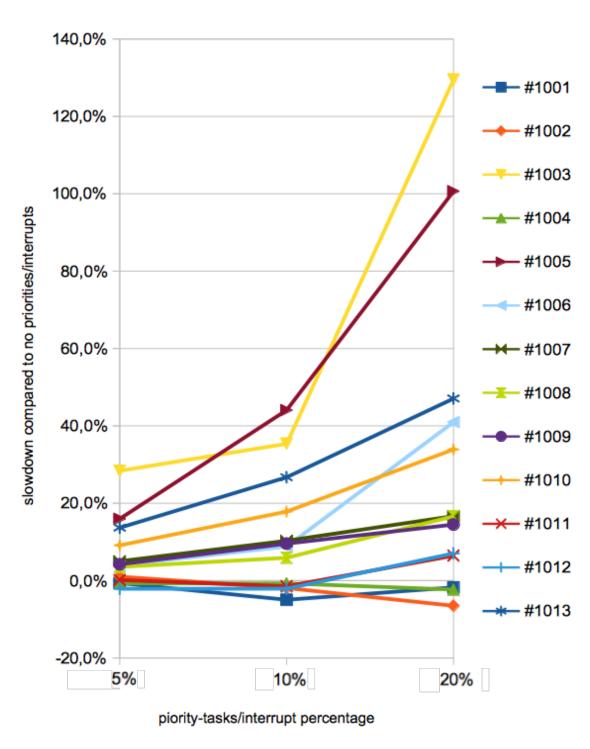

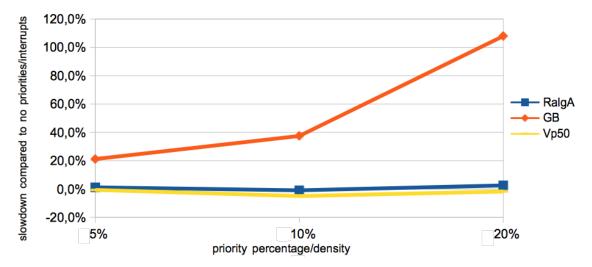

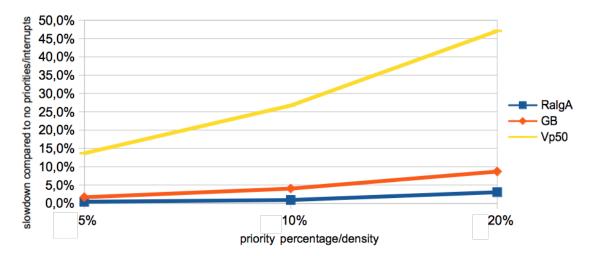

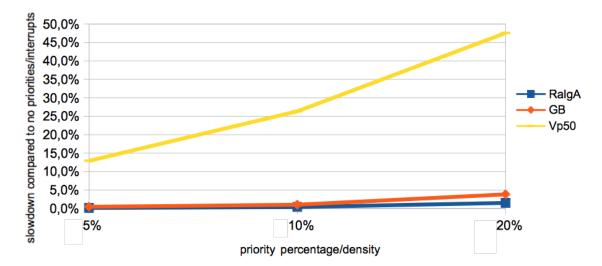

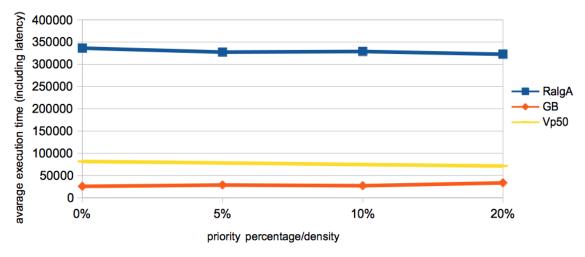

| 5.7  | The effect of priority density on total execution time of the task list                                                                 | 43             |

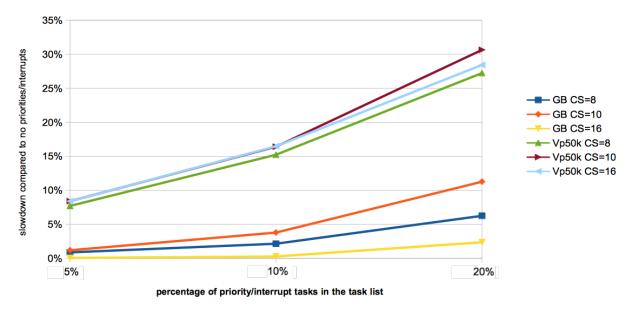

| 5.8  | Same as Figure 5.7 normalised to no priority execution times                                                                            | 43             |

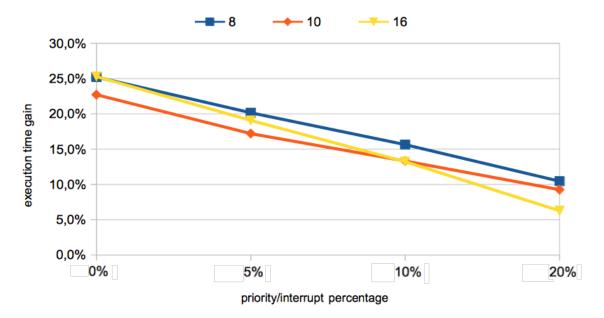

| 5.9  | Versioning losing its speedup to GB as priority density increases                                                                       | 44             |

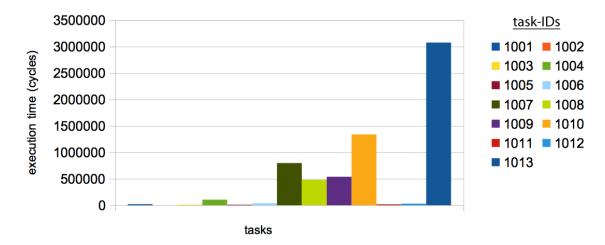

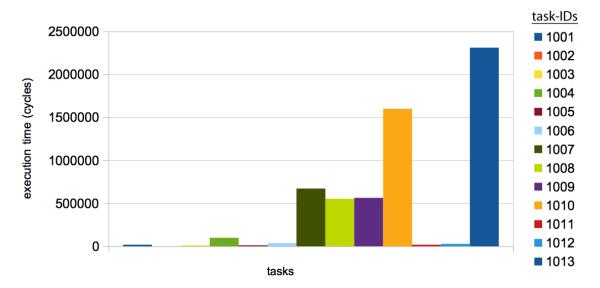

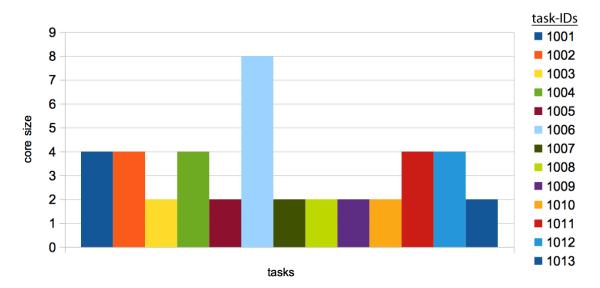

| 5.10 | The GB preferred execution times                                                                                                        | 45             |

| 5.11 | The Versioning/Basic preferred execution times                                                                                          | 45             |

| 5.12 | Preferred core sizes per task in GB                                                                                                     | 46             |

| 5.13 | Preferred core sizes per task in Versioning/Basic                                                                                       | 46             |

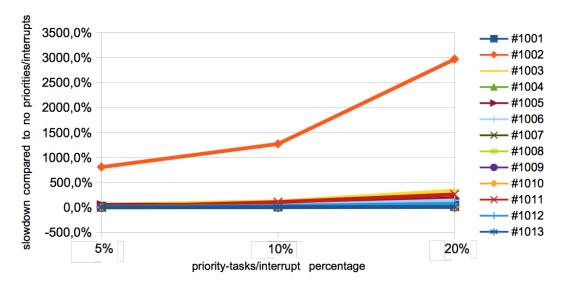

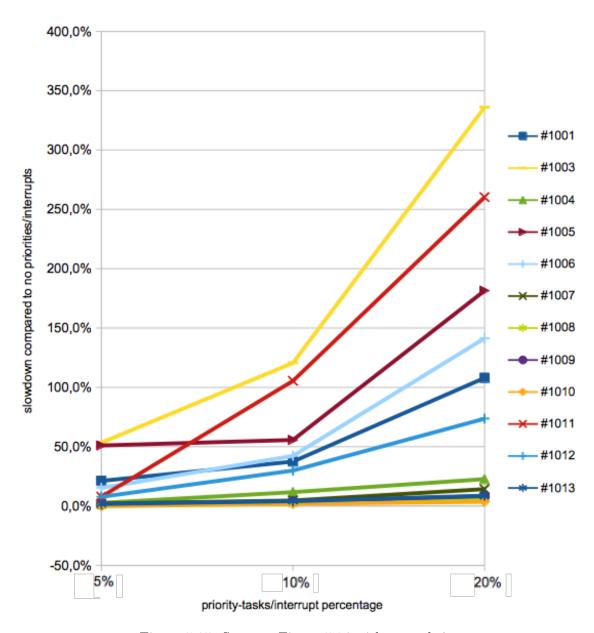

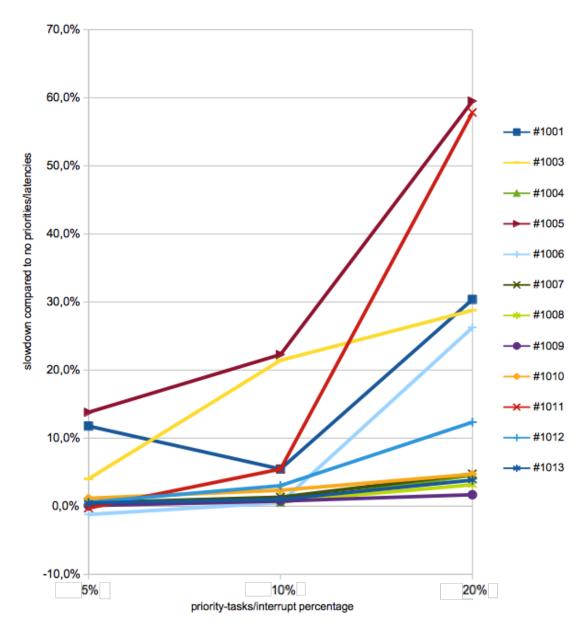

| 5.14 | GB execution time + latency slowdown to 0%-priorities for corespace 8.                                                                  | 47             |

| 5.15 | Same as Figure 5.14 without task 2                                                                                                      | 48             |

| 5.16 | Same as Figure 5.15 for corespace 16                                                                       | 49 |

|------|------------------------------------------------------------------------------------------------------------|----|

| 5.17 | GB execution time + latency slowdown to 0%-priorities for priority density 5%                              | 50 |

| 5.18 | Same as Figure 5.17 without task 2                                                                         | 50 |

| 5.19 | Same as Figure 5.18 for priority percentage 20%                                                            | 51 |

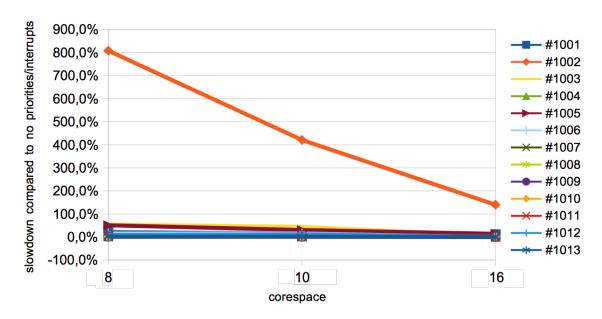

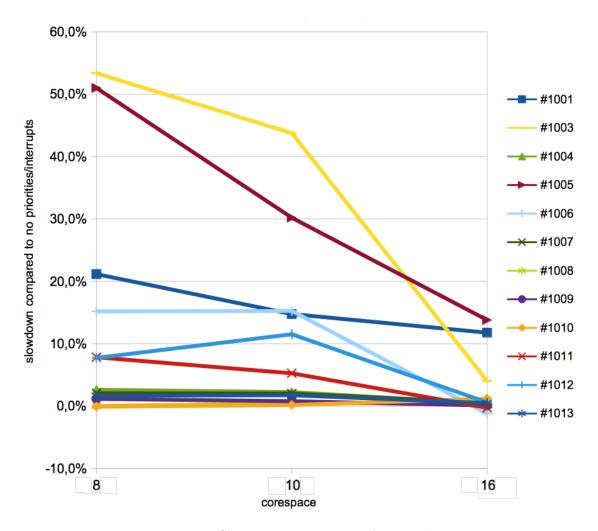

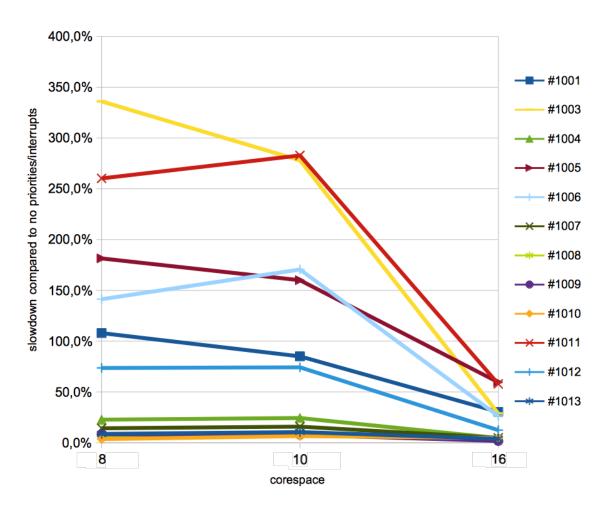

| 5.20 | Versioning execution time + task latency slowdown to 0%-priorities for corespace 8                         | 52 |

| 5.21 | Same as Figure 5.20 for corespace 16                                                                       | 53 |

| 5.22 | Versioning execution time + latency slowdown to 0%-priorities for priority density 5%                      | 55 |

| 5.23 | Same as Figure 5.22 for priority density 20%                                                               | 55 |

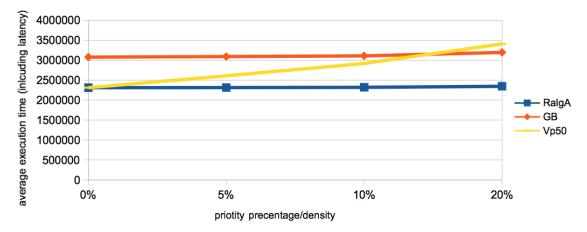

| 5.24 | Execution time + latency slowdown of task 1 for all algorithms compared to no priority times (corespace 8) | 56 |

| 5.25 | Same as Figure 5.24 for corespace 16                                                                       | 56 |

| 5.26 | Execution time + latency slowdown of task 13 for all algorithms com-                                       |    |

|      | pared to no priority times (corespace 8)                                                                   | 57 |

| 5.27 | Same as Figure 5.26 for corespace 16                                                                       | 57 |

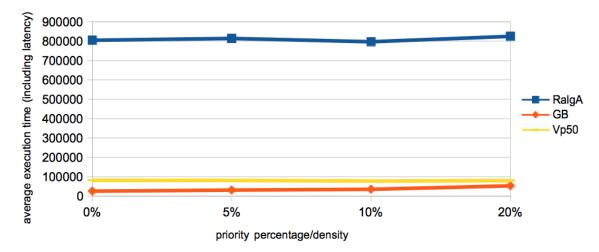

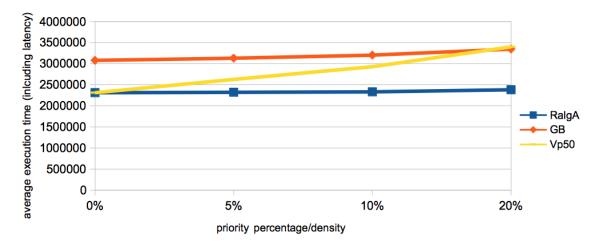

| 5.28 | Task 1 average execution time (incl. latency) for each algorithm for corespace 8                           | 58 |

| 5.29 | Task 1 average execution time (incl. latency) for each algorithm for corespace 16                          | 58 |

| 5.30 | Task 13 average execution time (incl. latency) for each algorithm for corespace 8                          | 59 |

| 5.31 | Task 13 average execution time (incl. latency) for each algorithm for                                      | 00 |

| 0.01 | corespace 8                                                                                                | 59 |

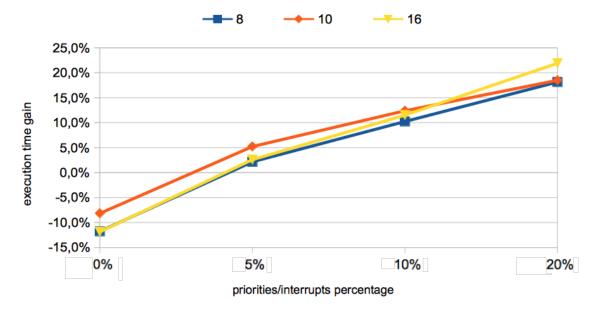

| 5.32 | Speedup of GB++ to GB                                                                                      | 60 |

| 5.33 | Running GB with Versioning execution times                                                                 | 61 |

| 5.34 | Speedup GB to Versioning for corespace 8                                                                   | 62 |

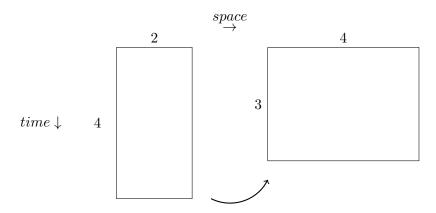

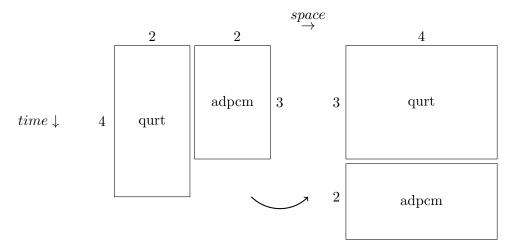

| 5.35 | The execution space of qurt for 2-issue (left) and 4-issue (right)                                         | 63 |

| 5.36 | The execution space of qurt for 2-issue (left) and 4-issue (right)                                         | 63 |

| 5.37 | Theoretical prerequisite in order to have speedup by upgrading                                             | 64 |

| A.1  | Some early test results actually showed slowdown instead of speedup                                        | 75 |

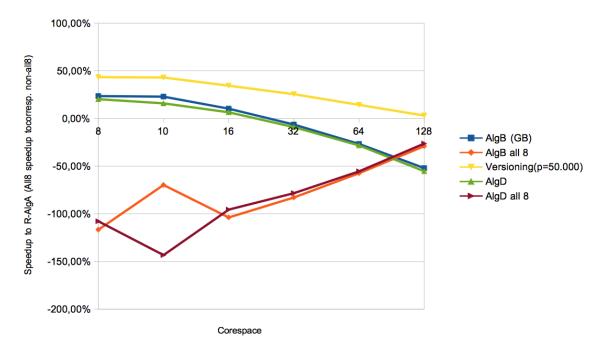

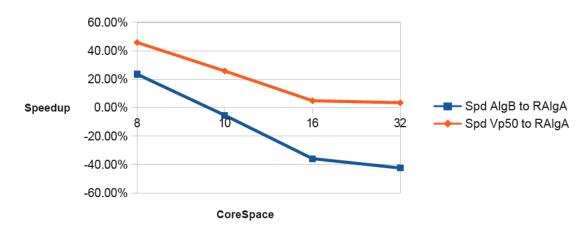

| A.2  | Some early test results of the total execution time speedup of GB and Versioning (penalty=50) to RAlgA     | 76 |

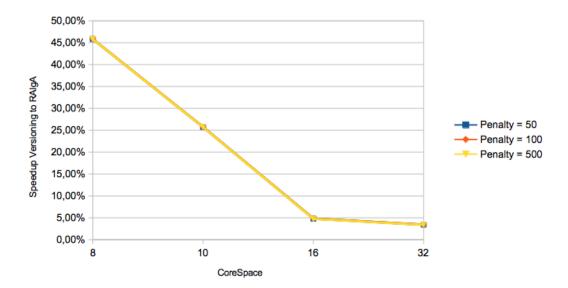

| A.3  | Early arbitrary Versioning penalty tests                                                                   | 76 |

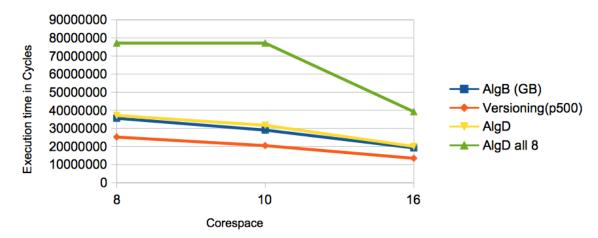

| A.4  | Early results from AlgD: total task list execution time                                                    | 77 |

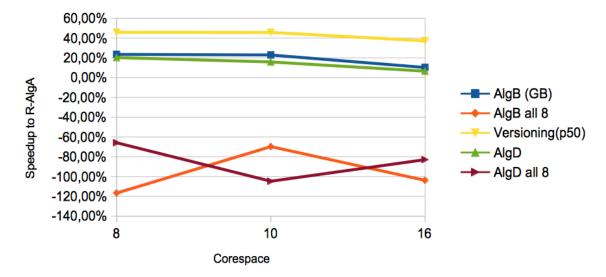

| A.5  | Early results from AlgD: speedup to RAlgA                                                                  | 77 |

# List of Tables

| 3.1 | Execution times (in cycles) and GB slowdown to Versioning/Basic              | 21 |

|-----|------------------------------------------------------------------------------|----|

| 3.2 | Execution-time gain from upgrading (8-issue times common for all algorithms) | 2/ |

| 3.3 | Overview of the developed algorithms.                                        |    |

| 4.1 | The benchmarks used to create the testing task lists                         | 32 |

| 5.1 | Utilisation of AlgA and RAlgA with and without Window                        | 39 |

| 5.2 | Binary sizes in bytes for each task and core size                            | 41 |

# List of Acronyms

FPGA Field-Programmable Gate Array

**ERA** Embedded Reconfigurable Architectures

VLIW Very Long Instruction Word

MCP Multicore Processor

**VEX** VLIW Example

**ISA** Instruction Set Architecture

ILP Instruction Level Parallelism

**DLP** Data Level Parallelism

NOP No Operation

NOC Network on Chip

FIFO First In First Out

**OS** Operating System

AlgA Algorithm A

RAlgA Realistic Algorithm A

RAlgAW8 Realist Algorithm A, Window=8

**GB** Generic Binary

AlgB Algorithm B (Generic Binary)

AlgBall8 Algorithm B, all tasks are 8-issue

AlgD Alogirthm D

AlgDall8 Alogirthm D, all tasks are 8-issue

# List of Algorithms

| 1 | Basic or Algorithm A          | 16 |

|---|-------------------------------|----|

| 2 | Versioning                    | 19 |

| 3 | Generic Binary or Algorithm B | 25 |

| 4 | Generic Binary++ or GB++      | 26 |

# Acknowledgements

First of all, I would like to thank my supervisor, Stephan Wong, for the opportunity he gave me to be a small part of the ERA project and his guidance throughout the whole thesis. For his patience and his understanding as well as the way he handled my particular character. The only thing I will never forgive him for, is making me learn and use LATEX.

Of course Fakhar Anjam and Anthony Brandon for their unconditional help and support. TU Delft is only lucky having such helpful and exceptional researchers.

Especially I want to thank my family, who stood by my side during the whole period of my studies, in its goods and its bads, as well as Bram Masseur and Massimiliano Marass, who did their best to keep all my distractions away during the period of this thesis and generally all my friends who tried to give me courage and energy.

I am also very grateful to Inge Verhoeven and John Stals, without the support of whom I might have never undertaken this project.

Finally, although he can't read these lines any more, I want to thank Stamatis Vassiliadis, for making everything he could for me to come to TU Delft.

A very special thanks to all those small and big scientists that doubt, question and challenge "reality" and "truth" constantly; for they are the true pioneers of science and my inspiration.

Georgios Andronikidis Delft, The Netherlands November 5, 2014

Introduction

When reconfigurable hardware was invented (especially Field-Programmable Gate Arrays - FPGAs) a new era began for Computer Engineering. Custom solutions could be designed for specific customers without the need of ordering millions of copies to make each solution affordable, as is the case with wafer solutions. Research in small scale and budget also became possible, spin-off companies' pop-up boosted. What made reconfigurable hardware even more attractive was the possibility of an upgrade. A better version of the hardware without making the old purchase useless, incredibly handy both for research and industry.

Adaptive hardware changed the rules of hardware design for good; it was a great innovation. But even more amazing opportunities arise the last years that technologies are invented which allow more and more the hardware to adapt on-the-fly. No need to switch off the system, re-arrange the hardware and switch it back on. Designers naturally start thinking of the possibilities that arise when you can design a platform the hardware of which can change any moment one wants, without putting the system down. This is how the ERA project was born.

## 1.1 The ERA project

The idea behind ERA (Embedded Reconfigurable Architectures) is to design a platform that combines reconfigurable computing and network elements which can adapt on-the-fly their composition, organization and even instruction-set architectures in an effort to provide the best possible trade-offs in performance and power for the given application(s). On ERA, network elements and topologies as well as memory hierarchy organization can be selected both statically at design time and dynamically at run-time [1]. That last one is what makes ERA special, because the hardware adapts to the software that runs on it on every cycle. All three basic hardware components of the ERA platform (Processing component, Network component and Memory component) shown in Figure 1.1 are actually dynamically adaptable. Although some of this adaptiveness is controlled by the software (mainly the operating system), the goal of the ERA project is that great deal of this control actually takes place automatically on hardware level, by the Hardware scheduler.

#### 1.2 Motivation

This thesis deals with the problem of task scheduling. The Task scheduler is the part of the Hardware scheduler seen on Figure 1.1 which with help by the Monitoring hardware is responsible for the reconfiguration of the Processing components. We will try to explore

Figure 1.1: The ERA platform.

possible implementations/algorithms for the task scheduling in the ERA platform. That is, we will try to find or invent algorithms that can look at the several tasks which are being executed every moment and try to map them on hardware within one or in any case finite number of cycles. This is the core idea of the ERA project. If this is not feasible, then the ERA platform would just be yet another VLIW system.

#### 1.3 Goals

The main goal of this thesis is to explore and compare the several possibilities/algorithms for task scheduling on the ERA platform. If no appropriate algorithms are available in the literature, we will have to invent some. Those algorithms, wherever they come from eventually, will have to be tested and compete with each other. The results should be analysed and if there is time, the chosen algorithm could be implemented inside ERA to see if it confirms the results of the research.

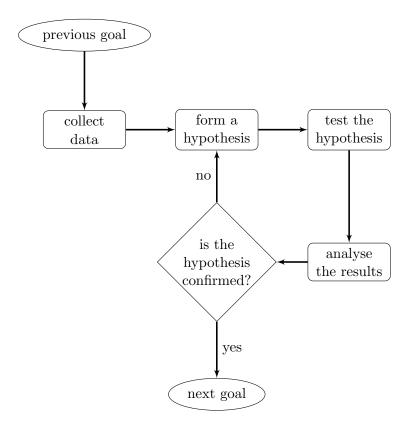

# 1.4 Methodology

In the most abstract level the methodology that will be followed is described by the following steps:

- Define the problem.

- Set the scope of the research.

1.5. OVERVIEW 3

- Look in the bibliography for solutions.

- Invent own/custom solutions if necessary.

- Test solutions.

- Analyse the results and draw conclusions.

More specifically the methodology in every step is described by the Figure 1.2 below.

#### 1.5 Overview

This thesis will be structured as follows. First, in Chapter 2 we are going to give some background information necessary for the understanding of the problem and the way we tried to tackle it, including the preliminary literature research performed. Then, in Chapter 3, the several algorithms will be presented and in Chapter 4 the simulator that we had to build to perform the research. In Chapter 5 the results of the research will follow and Chapter 6 concludes the thesis with a summary of all the conclusions drawn in the previous chapters, as well as some proposals for future work.

Figure 1.2: Flow chart showing of methodology for every goal.

Background

In this chapter we provide some background information about the ERA project as well as the literature research that took place in order to find out whether a solution that can be implemented in ERA and makes use of its special characteristics already exists.

## 2.1 The $\rho$ -VEX VLIW processor

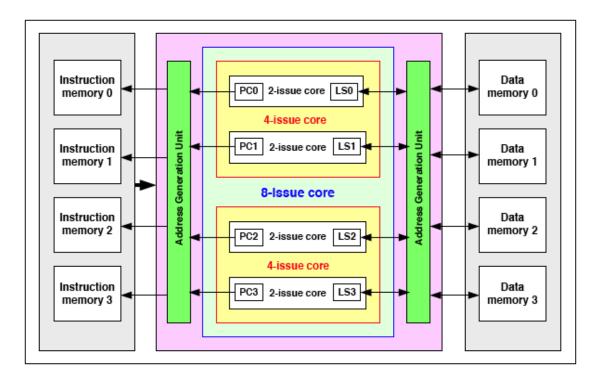

In the previous chapter, specifically on Figure 1.1, we saw an abstract block diagramme of the ERA platform. Since the focus of this thesis is on the Processing component seen in the figure, it is important to look inside that box more carefully. The goal is that the Processing component will be adapted constantly on the software running on the platform on any moment. That is why a Multicore Processor (MCP) described in [2] is implementing it, an abstract block diagramme of which is depicted in Figure 2.1 below. The originality lays on the fact that the core/cluster size and the number of cores/clusters can be adapted on-the-run.

Figure 2.1: The block diagramme of a VEX Multicore Processor.

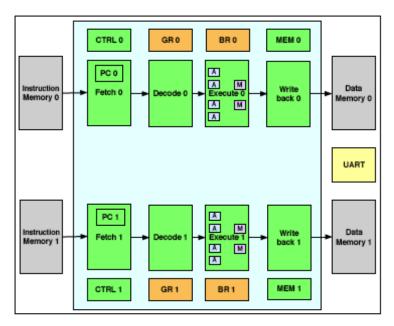

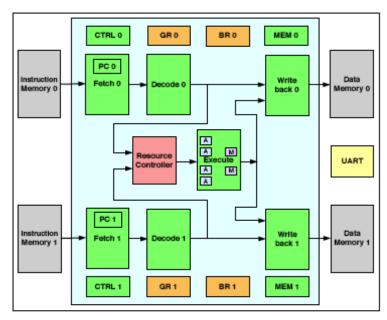

Figure 2.2: The block diagramme of a 4-issue  $\rho$ -VEX.

The smallest core of this Multicore Processor is a 2-issue  $\rho$ -VEX VLIW processor[3].  $\rho$ -VEX is a VLIW processor that implements the VEX ISA[4]. It is a reconfigurable and parameterized processor[5], the most relevant parameter of which is the issue width. A 4-issue  $\rho$ -VEX for example is depicted in Figure 2.2 above.

Two clusters can be combined to form a bigger one. For example two 2-issue cores can be combined to form one 4-issue core/cluster or two 4-issue cores can be combined to form one 8-issue core or two 8-issue cores can be combined to form one 16-issue core and so on. Theoretically there is no limit, but practically (and especially on FPGAs) the resources are limited and so is the parallelism VLIW processors can exploit. There is no meaning in using a 16-issue core when we hardly ever can find 16 operations that can be executed simultaneously. In that case it would be wiser to use two 8-issue cores and let 2 tasks run simultaneously, which is what ERA does.

The clusters do not necessarily have to be homogeneous. For a example if we have eight 2-issue cores available we can form four 2-issue clusters or two 2-issue and one 4-issue or two 4-issue or one 8-issue (core/cluster). Figure 2.3 summarises that.

Figure 2.3: How  $\rho$ -VEX cores can be combined to form bigger ones.

It has to be noted here that not just any two cores can be combined. For example assuming that N=4 in Figure 2.1 and that every cluster is a 2-issue core, in order to form a 4-issue core we could combine cluster-0 and cluster-1 or cluster-2 with cluster-3, but not cluster-1 and cluster-2. To imagine all the possible combinations, thus, we can imagine the clusters as the leaves of a binary tree, where the 2nd and the 3rd leaf cannot be combined since they belong to different branches.

We owe this limitation to the fact that ERA applies a datapath sharing method by Anjam et al. [6] depicted in Figure 2.4. Without getting too much into the details of the method, we can mention that Anjam et al. manage to halve the resources needed for the execution units, by sharing resources. While one operation is writing back (WB) results to the data memory, another operation can make use of the execution units. Apart from the obvious benefits in resources, Anjam et al. report benefits in power consumption, an important element in Embedded Architectures. The limitation brings some performance drop for the Multicore Processor as we will show in Chapter 5, but that is not tragic and it gets compensated by first of the core speedup which [6] reports by getting rid of the inter-cluster communication delay and secondly the fact that this binary-tree topology quite simplifies the design of the hardware scheduler, which brings benefits both in terms of resources as well as clock speed.

Apart from the ability of the MCP to switch off cores to save energy [7], this design can allow the ERA MCP extend its fault tolerant support (such as on-the-fly switching on and off of fault-tolerance support to save energy [8]) by permanently deactivating

cores that give errors constantly and proceed with task scheduling by ignoring them and using only the rest of the computing resources.

# (a) Non-shared datapath

# (b) Shared datapath

Figure 2.4: Datapath sharing in  $\rho$ -VEX cores.

## 2.2 The VLIW approach

It has already been mentioned that  $\rho$ -VEX is a VLIW processor. A VLIW processor takes advantage of Instruction Level Parallelism (ILP)[9] to execute independent operations simultaneously next to each other utilising extra hardware that is available[10]. For example if we have two processing units, an adder and a multiplier, there is no reason to leave the adder idle, while the multiplier is busy. Thus we feed the adder (already during compilation) with another operation which has no dependency to the operation being executed in the multiplier.

The way superscalars do that, is to look further in the code to find independent operations. Most of the times they need to perform out-of-order execution of the operations to reach high performance. To implement that, as well as to make sure that the final result is equivalent to in-order execution, out-of-order superscalar processors make use of a lot of extra control logic. Not ideal for Embedded applications, where less hardware is not only cheaper and faster (also faster to build), but also less energy consuming. VLIW architectures move that workload to the compiler. The compiler looks for independent operations that can be executed simultaneously and packs them together into Very Long Instruction Words (VLIW). This way VLIW hardware is much simpler and does not have to support out-of-order execution.

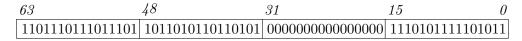

The cost we pay with VLIW architectures is that not always is there enough instruction level parallelism to exploit. If we have a 4-issue VLIW processor for example, we need to feed it 4 operations on every single cycle. That is not always possible. So often we end up with No Operations (NOPs) in the code[11]. NOPs are zeros filling up the gap of the operations we could not find to make a full Very Long Instruction Word. Figure 2.5 depicts a NOP inside a 4-issue instruction word of a 16-bit operation width VLIW architecture. A NOP means that the execution unit that will receive it, will do nothing. Most VLIW research goes around the problem of minimising NOPs.

## 2.3 Parallel algorithms

ERA not only exploits ILP by using VLIW architecture, but in the same time the clustering system tries to exploit Data Level Parallelism (DLP). Some applications could benefit from splitting the data into blocks that can be processed in parallel and calling the task independently for each block. Although the latter is not the job of the hardware scheduler, making idle resources available for another programme or task sent to  $\rho$ -VEX by the operating system for execution is.

Parallel algorithms theory has a lot to offer for exploitation of intro-task parallelism, but not much when we are trying to map to hardware tasks totally independent from each other, as this is considered an NP-hard problem [17]. For example it offers useful

Figure 2.5: A NOP in the 2nd position (bit-31 to bit-16) of a 4-issue VLIW.

tools for problems including communication (like Networks on Chip - NOCs), tasks with dependencies or communication with each other as well as divide and conquer methods for solving matrix problems [12], but nothing when it comes to completely independent tasks with no communication with each other competing for resources. Then the only fair solution in that case seems to be simply a FIFO and strict in-order execution.

However, there is a difference in ERA platform. The tasks can run in cores of several sizes, which creates some dependency between the tasks, cause some task B cannot use the resources allocated to some task A, till task A finishes. That would be a simple problem of balancing a tree graph, as painful as the word "simple" may sound in the the limited world of FPGAs and Embedded System. Figure 2.6 depicts such a weighted graph, where the nodes are the tasks and labeled by the name/number of the task and the size of the core (2-issue, 4-issue, etc) and the edge is the cycles it takes to execute this task in such a core. It is obvious that the bigger the core (thus the more resources we dedicate to this task) the shorter the edge (the faster the task is executed that is). On every level the sum of the core sizes is equal to the maximum resources we have. Let's say we have resources to build one 8-issue core or two 4-issue and so on as in the example of Section 2.1. Then 8 would be the sum of all the core sizes on each level (we let aside deactivating resources to save energy for now).

Since the maximum number of tasks we would be able to issue at such processor on one cycle is 4, we only take into consideration the next 4 tasks in the task queue. If all 4 can run simultaneously (Figure 2.6 left graph), obviously there is no need for balancing. The slowest task is giving us the height of the tree. If we dedicate double amount of resources though to the slowest task and let another task run only after this one or another one finishes, then we can shorten the tree's height. We managed to shorten the total execution of those tasks from 12 to 8 cycles. But then, what if we had made a different choice? Every task has 3 different versions (2-issue, 4-issue and 8-issue) and there are 4 different tasks. That means the task scheduler would have to construct  $3^4 = 81$  possible trees (even though some of them are equivalent to others), calculate their heights and choose the shortest one. That would demand a whole Multicore Processor only for the scheduling, so it is out of option.

Figure 2.6: Two of the many scheduling possibilities of just 4 tasks in ERA.

Another option is to consider all nodes as 2-issue tasks and represent an 8-issue task as four 2-issue tasks with a line dependency. Then we we would end up with only one tree/graph like that in Figure 2.7 which has to be balanced. Apart from the fact that such a problem would still need a whole MCP on its own every time we would want to

Figure 2.7: A scheduling graph with only 2-issue nodes.

reschedule the tasks, it is also not that accurate. In a perfect world the execution time of a task in a 4-issue core would be half the execution time of the same task in a 2-issue core. That means that we would manage to wrap all the operations of the 2-issue version into half the amount of instruction words we had in the 2-issue version without creating any new NOPs. Well, that is theoretically possible, but practically impossible, since no programme has such a great amount of instruction level parallelism. With other words pushing t1 up to execute it as a 4-issue task would not necessarily mean that the task would have been executed within 8 cycles.

Theory of Parallel algorithms and Parallel processing or Graph theory did not offer any solutions. However some investigation in the literature did take place, in case some algorithms have already been developed for similar to ERA platforms or conditions.

#### 2.4 Related work

Natural research domains that can be related to the hardware scheduling of ERA are Grid Computers, heterogeneous multicore computers and homogeneous multicore computers. Each of which failed to supply us with an algorithm relevant to ERA; each for its own reasons. We present one typical research/case per cluster below.

#### 2.4.1 Grid Computers

A Grid computer is a network of computers linked by software in such a way that they function as a single computer. The computational power of all those computers is combined to form a super computer[13]. The linking software has to perform task scheduling. The computational power of each computer in the grid is different, which could be related to the several  $\rho$ -VEX cores of different issue-widths inside the ERA multicore processor, but those computers are not next to each other, like the  $\rho$ -VEX cores, but they can even be at the other side of the planet. Thus most research on Grid task scheduling [14, 15, 16], for example that of Keqin Li in [14], focuses on minimising the communication costs between the different computer elements. If the communication cost is not the only factor of those specialised task scheduling algorithms (for example in cases that all computers members of the gird are the same or quite similar) it is at least the most important one. But in case of ERA the communication cost is irrelevant, because it is the same, no matter what kind of core we are going to select.

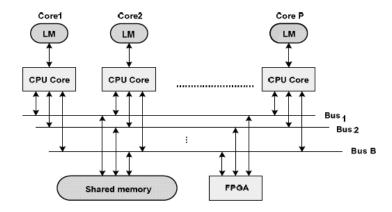

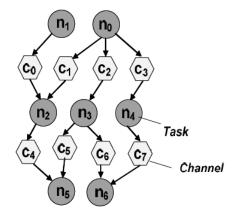

#### 2.4.2 Homogeneous Multicore Processors

Another cluster of research efforts is for scheduling on homogeneous multicore systems [17, 18, 19, 20]. Despite the fact that the geographical distances of the previous category of systems is not there, communication still is an important issue in Youness et al. [17], as the cores communicate with a shared memory through a bus as shown in Figure 2.8. Thus the algorithm is making a graph with dependencies (Figure 2.9) where round nodes is the execution time and hexagon nodes are communication costs. The algorithm is worrying mostly about queuing up tasks with dependencies after each other on the same core, in order for the next task to find the data ready in the core through

Figure 2.8: Homogeneous multicore system

Figure 2.9: Scheduling graph for a homogeneous multicore system

port-forwarding or core cache instead of having to use the bus to access the main memory. Such a scheme does not match the specifications of ERA, since we assume that tasks are totally independent, but could be used later as an improvement. For now the ability to run a task on a bigger core than the others and wether a scheduling that takes advantage of that is possible is a much more interesting question and most likely not to be answered by research efforts concerning homogeneous systems. Even in publications where tasks are independent (as in [20], since the system is homogeneous, the algorithms target mainly on workload balance which is core-oriented rather than task-oriented.

### 2.4.3 Heterogeneous Multicore Processors and Multiprocessor Computers

With the exception of some moments that only cores of the same size are used, ERA MCP can be considered a heterogeneous multicore system. Scheduling in heterogeneous has also not been very impressive[21, 22, 23, 24, 25], most authors claiming simply effective or efficient scheduling, but none of them optimal. The most interesting case is

that of Tang et al. [21]. The authors use estimated execution time of the task for every core in order to decide on which core the task will be assigned, but important role on the decision takes the deadline, since this is research for, not just Embedded Systems, but Real-Time Embedded Systems. Deadline miss rate is also the only criterium on which they compare the different versions of their algorithm. Moreover it is a software scheduler, although not that hard to implement in hardware. This could be a future add-on for the ERA hardware scheduler in order to support real-time systems, but it cannot be used as the basic scheduling algorithm.

## 2.5 Conclusion of Chapter 2

After getting an inside look of the Processing component of the ERA platform and understanding the particularities of it, as well as of its main building block, the  $\rho$ -VEX core, we tried to find in the bibliography an available scheduling algorithm to implement as the Hardware scheduler of ERA. This literature research did not yield any results, both because of the complexity of the problem, as well as the pioneer characteristics of ERA that we would like to take advantage of. Thus, we will try to design simple scheduling algorithms, especially tailored for the ERA platform and see how they perform.

Implementation

From the Introduction (Chapter 1) and the flow chart of Figure 1.2 the reader should probably have imagined already that the evolution of this research would be nothing like linear, which makes it rather difficult to lay on a book. However, this chapter and the next one will attempt to present the research in a linear way.

We saw in the previous chapter that the relevant literature could not supply us with the appropriate algorithm for the Hardware scheduler of the ERA platform. Thus, we went on and designed 4 simple scheduling algorithms. Some of them were part of the initial planning, whereas others came up or were abandoned during the course of the research. In this chapter we present those algorithms, their characteristics and their differences.

Imagine that our ERA Multicore Processor of Figure 2.1 is a co-processor in an embedded system and the main processor sends to the MCP only the hardest tasks for execution. The Hardware scheduler receives a task in a task list (FIFO) and tries to decide what percentage of the resources it should allocate to this task.

The Monitoring hardware (Figure 1.1) supplies the Hardware scheduler with information about the task. Information on how fast it has run in the past on every core-size available, so that the Hardware scheduler can make a smarter decision. Smarter meaning we do not have to offer an 8-issue core to a task if the execution-time gain compared to this task run in a 4-issue core is just 5% or 10%. That means that there is not much of Instruction Level Parallelism (ILP) to exploit in this task and that the 8-issue version is full of NOPs. This information can also come from the Operating System (OS) accompanying each task in order to save on hardware resources.

# 3.1 A basic scheduling algorithm

#### 3.1.1 The naive approach

Assuming we have a MCP of corespace 8. That means that we have resources to implement one 8-issue core or two 4-issue cores and so on, just like in the example of Section 2.1. There are 2 tasks running, one on a 4-issue core and one on a 2-issue core. That means that our only free resources is a 2-issue core. The situation is depicted in Figure 3.1 below.

Figure 3.1: A 2-issue and a 4-issue task running in an ERA MCP.

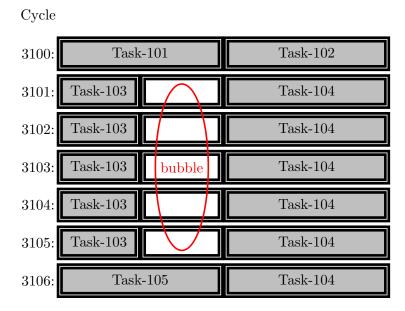

Figure 3.2: A bubble created in the execution timeline.

If the first task in the task list, waiting for execution, comes with the indication of preferably running on a 2-issue core, we got lucky. But if the task would prefer to run on a 4-issue or 8-issue core, then the Hardware scheduler has a decision to make. The simplest thing the Hardware scheduler can do is to wait until resources become available. But that means a NOP would have to be added in the 2nd cluster till one of the two tasks is finished. That creates a bubble in the execution timeline as seen in Figure 3.2. Such bubbles cause the utilisation percentage to drop, increase the task latency, which is the time from the moment a task arrives at the task list till the time its execution is completed, and the total execution time for any chosen amount of tasks.

In order to minimize the number of the bubbles, we can allow the algorithm to look further in the task list for smaller tasks that can be executed inside those bubbles. As in hardware the resources are not infinite there should be a maximum window in the task list that the algorithm can search for smaller tasks. This is the simplest algorithm we can implement, it is called 'Basic' (or 'Algorithm A' or just 'AlgA' for short), and it is depicted in Algorithm-figure 1 below.

### **Algorithm 1** Basic or Algorithm A

```

1: for i = 1 \rightarrow 10 do

2: find space p where task(i) fits

3: if p \neq NULL then

4: allocate p to task(i)

5: end if

6: end for

```

#### 3.1.2 Time complexity analysis

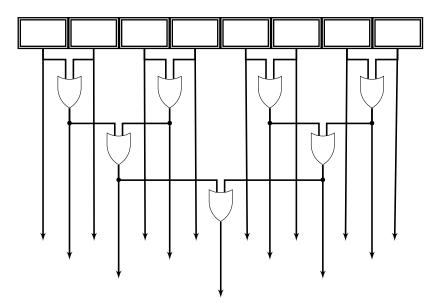

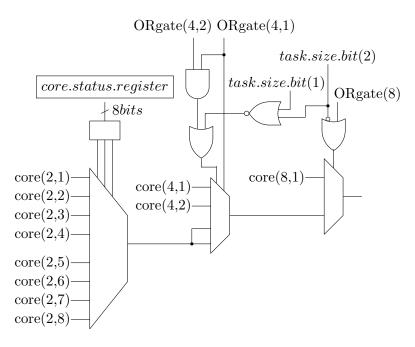

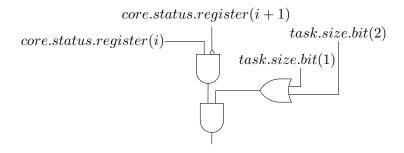

With the first look, one would estimate the time complexity of this algorithm to be  $O(m \times n)$ , m being the window size and n being the maximum number of 2-issue cores that the platform can offer to the tasks, or half the 'corespace', which can be defined as the maximum ops that can be running on a specific ERA MCP at the same time. The hardware world however has limitations and advantages that work on the benefit of our algorithms. First of all, we do not expect the window to be too large because, as we know from superscalars, that would seriously increase the complexity of the hardware design. Even if the window-size is adaptable on-the-fly (instead of decided on designtime) it would never exceed 10. That drops the time complexity to O(n). In the world of software it is difficult to overcome the O(n) time complexity, which comes from the search for an available core of the size that task(i) optimally runs (unless we use parallel computing which still has its limitations), but in the world of hardware we can turn the time complexity O(n) into workload complexity W(n) or any other W(). By means of logic gate design we can come up with a circuit of OR gates, like the one in Figure 3.3 that manages to detect a suitable free core within 1 cycle, thus time complexity O(1).

#### 3.1.3 A realistic basic algorithm

As we will see in Chapter 5, the Basic algorithm has a very important disadvantage that makes it unusable. The algorithm tends to execute all 2-issue tasks in the list first, then the 4-issue tasks and finally the 8-issue tasks. Even if we are not talking about real-time systems, where tasks have deadlines, this is still a problem, because in the real world that tasks keep coming constantly, it means that bigger tasks will never be executed. They will be waiting forever for execution because 2-issue tasks will be

Figure 3.3: The logic that detects available cores of any size (2,4,8,16) on an ERA MCP of corespace 16. Output Low means available, whereas output High means unavailable.

coming just on time to grab small cores immediately as soon as they become available. For this reason a modification is necessary. One modification could be that we first execute all tasks within the window-buffer before we start filling it up again with new coming tasks. But that would cause bubbles again and thus the utilisation would drop. Another similar modification is to introduce barriers/checkpoints wherever we meet an 8-issue task. That means that as soon as the algorithm detects an 8-issue task it will stop feeding the window-buffer with new tasks, until it is empty. Until that 8-issue task has been executed, that is. The 4-issue tasks are much more frequent than 8-issue ones. So the window-buffer often gets full of them and eventually it is forced to run them. That is sufficient so that they do not get postponed forever and works almost like the barrier function. Introducing a barrier-function also for 4-issue tasks would create too many bubbles. We call this version 'Realistic Basic Algorithm' or 'Realistic Algorithm A' or 'RAlgA' for short.

# 3.2 Versioning

Some 4-issue (and above) tasks though are not that large, meaning, they do not take that long to execute. Making them wait for several hundreds of thousands of cycles for free resources, while they take several hundreds of cycles to execute, even in the smallest cores, would be criminal. For those tasks it might be smarter to do the effort to bring another version of the task, compiled to run on a smaller core and allocate to them on such a smaller core which is available immediately. This algorithm is called 'Versioning'.

#### 3.2.1 Communication Penalty

We will suffer a communication penalty in that case, however, since we do not expect the Instruction Memory (cache) to be big enough to hold 3 versions of every task in the task list. Thus communication with the main memory is expected and that will bring penalty to the execution time of the task. We hope this way that the overload from the slower execution plus the penalty will be in total less than the time latency of the task if it would be waiting for free resources as is the case with RAlgA. The size of the penalty depends on the design of the platform, thus will be a subject of research.

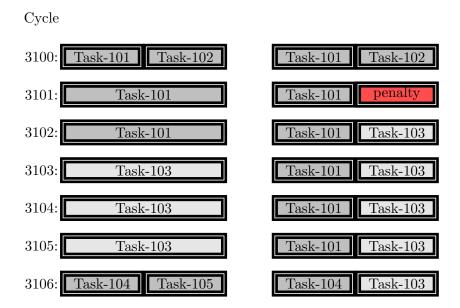

An example is shown in Figure 3.4. Task 101, a 2-issue task is already running on this MCP of corespace 4, when the 4-issue Task-102 arrives. AlgA would make Task-102 wait until Task-101 is done and thus enough resources are available. That would create a bubble of 5 cycles and Task-102 would only start running at cycle 3106. RAlgA might have done the same, unless it could find another 2-issue task to cover the bubble, but if that task took more than 5 cycles to execute, that would be even worse for Task-102 because that would mean it would have to wait even more to start running. Assuming that Task-102 takes 2 cycles to execute in a 4-issue core and 4 cycles in a 2-issue core and that the penalty to bring the 2-issue version is 2 cycles, we see that the task would finish 1 cycle earlier in Versioning, letting Task-103 also start earlier. Although 2 cycles

3.2. VERSIONING 19

Figure 3.4: A scenario on AlgA (left) and on Versioning(right).

reload penalty looks quite a heavy cost for a 2-cycle task, plus 2 cycles extra executional penalty (since 2-issue cores are slower than 4-issue cores) a total of 4 cycles penalty, the execution time of the 4-issue task is not what the Versioning penalty is competing with, but the task latency in the Basic Algorithm. Thus, as long as the following is true

$$T(i, rest) + T(j, 2 \times s) > P(j, s) + T(j, s)$$

$$(3.1)$$

(T being the execution time and P being the reload penalty, i being a task already running (like Task-101 in Figure 3.4) and j being a new task coming (like Task-102 in the same figure) and s being a core size) Versioning is better than the Basic algorithm.

#### Algorithm 2 Versioning

```

1: for s = task(i).size \rightarrow 2 do

find space p where task(i) fits

2:

if p \neq NULL then

3:

if s \neq task(i).size then

4:

bring the right version of the task

5:

end if

6:

7:

allocate p to task(i)

end if

8:

9: end for

```

Trying to include (in)equation 3.1 in the Versioning algorithm would demand extra resources (especially if we want to implement it within 1 cycle we would have to calculate the T(i, rest) for every i, for every task running at the moment that is) and the benefit would not be certain, since how long a task takes to run is not only dependent on the size of the core it is running on, but also on the amount of data it has to process. The algorithm would obviously fail if it let the new task wait, thinking a task would soon finish, while the task running actually has to process this time double or triple the amount of date it had to process last time.

Thus Versioning shall *always* schedule a task on every cycle (by reloading its binary to a version that fits) provided that there is an idle core. That means that the hardware utilization will be 100%, contrary to AlgA and RAlgA which produce task bubbles.

#### 3.2.2 Time Complexity

The Versioning algorithm (seen in Algorithm-figure 2) has the same time complexity as Basic, O(1). The number of the iterations of For cannot exceed logm, where m is the size of the biggest core which that specific ERA design supports. If, for example, the decision taken on design time is that the maximum core size is 8, then that For will have to run once for s = 8, once for s = 4 and once for s = 2. A time complexity of O(logm). Taking advantage of the logic circuit of Figure 3.3 (the output of which can be controlling some multiplexers as shown in Figure 3.5) we can even perform all three iterations in 1 cycle. That means the hardware version of the algorithm will have O(1) time complexity.

Figure 3.5: Parallelising downgrading.

| task | GB        |           | Ver./     | Basic     | slowdown |         |

|------|-----------|-----------|-----------|-----------|----------|---------|

| task | 2-issue   | 4-issue   | 2-issue   | 4-issue   | 2-issue  | 4-issue |

| 1001 | 29.750    | 20.229    | 31.546    | 18.376    | -6%      | 10%     |

| 1002 | 1.003     | 614       | 807       | 516       | 24%      | 19%     |

| 1003 | 11.202    | 10.337    | 10.488    | 10.335    | 7%       | 0%      |

| 1004 | 143.178   | 105.316   | 128.600   | 98.526    | 11%      | 7%      |

| 1005 | 14.054    | 10.056    | 11.037    | 9.208     | 27%      | 9%      |

| 1006 | 80.272    | 50.562    | 73.550    | 45.248    | 9%       | 12%     |

| 1007 | 798.108   | 626.721   | 671.589   | 572.852   | 19%      | 9%      |

| 1008 | 640.728   | 481.976   | 552.000   | 448.218   | 16%      | 8%      |

| 1009 | 788.241   | 538.547   | 562.866   | 469.166   | 40%      | 15%     |

| 1010 | 1.897.159 | 1.339.742 | 1.599.351 | 1.220.330 | 19%      | 10%     |

| 1011 | 34.910    | 22.605    | 24.845    | 18.018    | 41%      | 25%     |

| 1012 | 39.644    | 29.880    | 35.334    | 27.781    | 12%      | 8%      |

| 1013 | 3.077.053 | 2.285.802 | 2.310.467 | 2.026.995 | 33%      | 13%     |

Table 3.1: Execution times (in cycles) and GB slowdown to Versioning/Basic.

# 3.3 The Generic Binary

A great innovation would be if we could change to another core size than the one that task prefers, either from the beginning or in the middle of the execution of a task, without paying that penalty. Brandon and Wong [26] achieved to compile any task to a binary that can run on any core, even migrate to another core on-the-fly with a mere penalty of 155 cycles[27] and still run correctly. It is called generic binary and it makes the ERA  $\rho$ -VEX the first reconfigurable VLIW processor that can do that[28]. The algorithm takes the name from that special binary too, so for the rest of the thesis the term 'Generic Binary' (GB) will refer to the algorithm, not the binary.

## 3.3.1 Benefits and disadvantages

The penalty of 155 cycles is not the only one, though. A task compiled for the Generic Binary algorithm will not run as fast as if it were compiled specifically for a 2-issue or a 4-issue core (8-issue cores have no difference compiled to GB or not) for use in Versioning and AlgA. A task compiled for GB will usually take about 10% to 40% more time to execute than the same task specifically compiled for 2-issue or 4-issue (Table 3.1), depending on the task. However being able to downgrade or upgrade will give us the opportunity to support priority tasks, interrupts and save on energy, because downgrading with GB consumes less energy than reloading with Versioning and generally running a task on a smaller core also saves energy (assuming no other task comes to use the resources the downgraded task left idle)[28].

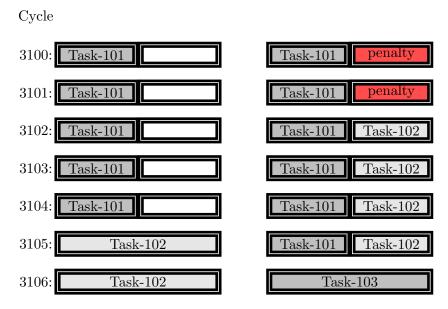

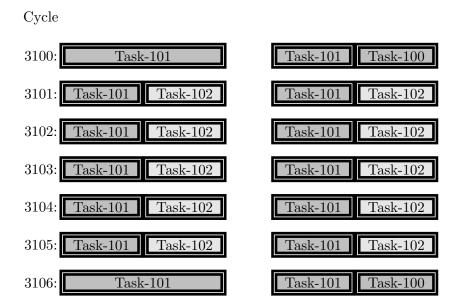

Figure 3.6: GB (left) and Versioning (right) handling a new 4-issue task.

## 3.3.2 Priority tasks

Priority tasks are tasks that:

- either have a deadline, so they need to use more resources to finish on time(Figure 3.6),

- or tasks that just came in and need to run now (Figure 3.7 and 3.8), even if it appears there are no available resources

- or that tasks that the operating system for any reason decided that they are more important than the rest(Figure 3.9).

Versioning cannot support those tasks. Switching to a bigger core to catch a deadline or downgrade to a smaller core to let a priority task run would mean that we would have to start running the task all the way from the beginning again. The only thing Versioning could do and only for tasks that come in and have to run now (not tasks that are already running and suddenly they acquire high priority) is freeze a (non-priority) task that is running, store its context and let the priority task run in its place. As soon as it is finished, the old task can be loaded again and start from where it had stopped.

GB on the other hand can handle all three kind of tasks described above. Tasks with a deadline can be given priority, either they are running now or they just came in. If the operating system (or the Hardware monitor) is afraid a task can lose a deadline, it can upgrade it by letting the task take over adjacent resources instead of bringing in a new task. At this moment the algorithm only looks for available recourses in adjacent resources. But total relocation of the resources on every cycle is feasible with some modifications. That means that the algorithm will switch location of two tasks, say A

Figure 3.7: GB stealing resources from a task(left) or freezing it (right).

and B, if it sees task A can take advantage also of adjacent idle resources of task B, if task B cannot or simply would really benefit as much.

When a priority task comes in and no resources are available the algorithm can either steal resources from another task. That could mean that the other task either has to downgrade or that it should or freeze and be taken out of the MCP to give its resources to the priority task. If victim-task is a non-priority task the choice is obvious. If it is also a priority task the question what to do rises. For the time being the algorithm supports only 1 level of priority. But it can easily be modified to support multiple levels of priority. The task with the smallest priority obviously becomes the victim-task.

There is a figure exhibiting every one of those cases. In Figure 3.6 Task-101 and Task-102 are running. Task-102 is done and the next task is Task-103, a task that preferably runs on a 4-issue core. GB also notices that Task-101 is a 4-issue task which has been downgraded. It upgrades to run in 4-issue so that it runs the 4 remaining words (8 operations) in 2 cycles instead of bringing Task-103. Then there is enough space for Task-103 to run on a 4-issue core, no need to downgrade. This way Task-103 finishes within 3 cycles instead of 6. Versioning followed a different pattern. It cannot upgrade Task-101, since it would have to make it run all the way from the beginning. So it has to downgrade Task-103. Task-103 runs 15% faster on Versioning since it is compiled especially for 2-issue, but it has to pay the re-loading penalty of at least 1 cycle. Both tasks finish later in Versioning than in GB. Even in the case that the GB overload for Task-103 was higher and thus Task-103 would also end on cycle 3105, there would still be the benefit of Task-101 finishing earlier.

In the case that a new priority comes in and there is no place for it to run is depicted in Figure 3.7. In the left scenario Task-101 is non-priority task (or a task with lower priority) running already on a 4 issue core. Task-102 is a (high) priority task that comes in and needs to run immediately. In that case Task-101 will be downgraded to a 2-issue

|        | GB              |         |         |          |                   | Versioning/Basic |         |          |             |

|--------|-----------------|---------|---------|----------|-------------------|------------------|---------|----------|-------------|

| task   | execution times |         |         | gain     |                   | execution times  |         | gain     |             |

|        | 2-issue         | 4-issue | 8-issue | $2{	o}4$ | $4 \rightarrow 8$ | 2-issue          | 4-issue | $2{	o}4$ | <b>4</b> →8 |

| adpcm  | 29750           | 20229   | 17025   | 32%      | 16%               | 31546            | 18376   | 42%      | 7%          |

| bent   | 1003            | 614     | 515     | 39%      | 16%               | 807              | 516     | 36%      | 0%          |

| blit   | 11202           | 10337   | 10334   | 8%       | 0%                | 10488            | 10335   | 1%       | 0%          |

| compr. | 143178          | 105316  | 95697   | 26%      | 9%                | 128600           | 98526   | 23%      | 3%          |

| crc    | 14054           | 10056   | 9209    | 28%      | 8%                | 11037            | 9208    | 17%      | 0%          |

| des    | 80272           | 50562   | 37729   | 37%      | 25%               | 73550            | 45248   | 38%      | 17%         |

| engine | 798108          | 626721  | 583252  | 21%      | 7%                | 671589           | 572852  | 15%      | -2%         |

| fir    | 640728          | 481976  | 421147  | 25%      | 13%               | 552000           | 448218  | 19%      | 6%          |

| g3fax  | 788241          | 538547  | 464712  | 32%      | 14%               | 562866           | 469166  | 17%      | 1%          |

| jpeg   | 1897159         | 1339742 | 1130842 | 29%      | 16%               | 1599351          | 1220330 | 24%      | 7%          |

| pocsag | 34910           | 22605   | 17024   | 35%      | 25%               | 24845            | 18018   | 27%      | 6%          |

| qurt   | 39644           | 29880   | 26053   | 21%      | 25%               | 35334            | 27781   | 13%      | 6%          |

| v42    | 3077053         | 2285802 | 2006688 | 12%      | 26%               | 2310467          | 2026995 | 12%      | 1%          |

Table 3.2: Execution-time gain from upgrading (8-issue times common for all algorithms)

core to leave some resources available for Task-102. If Task-101 still running when Task-102 finishes it can be upgraded again to a 4-issue core. On the right side, there are two tasks running when (high) priority Task-102 comes in, specifically the (low) priority Task-101 and the non-priority Task-100. GB will stall Task-100, store its context to the memory and let Task-102 run. When Task-102 is done, Task-100 can come back for execution. The scenario on the right side is what the other algorithms would do too, even if there was a 4-issue task running that moment. The benefit of GB is that it lets Task-101 keep running while the priority task is also running. That could be compensated in the other algorithms by letting the priority task use as many resources as possible. But not all tasks benefit significantly from bigger cores as we can see in Table 3.2. The execution times as those of Table 3.1 are supplied by [26].

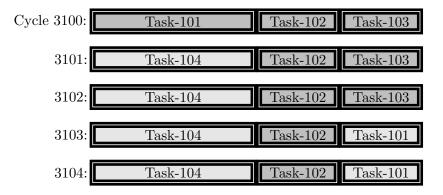

Figure 3.8: A 4-issue forced priority task in an ERA MCP of corespace 8.

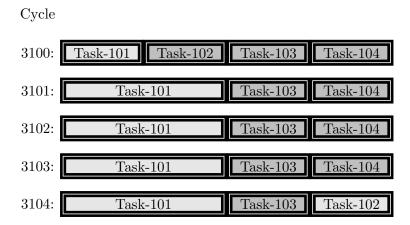

Figure 3.9: A task suddenly gains priority.

Figure 3.8 presents the case of a forced priority task. That is a task that not only has to run now, but it also has to run in the preferred core size, by all means. In that case Task-101 is taken out of the processor and comes back after resources are available. In this scenario one of the smaller tasks happens to finish before the forced priority task, so Task-101 is downgraded and brought back to a smaller core instead of keep waiting for the forced priority Task-104 to finish.

And finally Figure 3.9 depicts the case of a task that suddenly required priority and needs to take over resources around it. In this case this is Task-101 and Task-102 has to be taken out of execution. If another task is done in the meantime, like in this case Task-104, then Task-102 can come back to execution. Otherwise it has to wait for Task-101 to finish.

#### 3.3.3 Interrupts

A big advantage of GB is that it can handle interrupts without having to freeze all the tasks running. Given that there is at least one 4-issue or higher task running at the moment, we can downgrade it and let the interrupt be handled in the core that will be set free. Interrupts are identical with priority tasks of the cases depicted in Figure 3.7.

#### 3.3.4 Time complexity

GB can be represented in algorithmic form as seen in Algorithm-figure 3 below:

# Algorithm 3 Generic Binary or Algorithm B 1: $\mathbf{for} \ s = task(i).size \to 2 \ \mathbf{do}$ 2: find space p where task(i) fits 3: $\mathbf{if} \ p \neq NULL \ \mathbf{then}$ 4: allocate p to task(i)5: $\mathbf{end} \ \mathbf{if}$ 6: $\mathbf{end} \ \mathbf{for}$

It looks exactly like versioning, but the reloading logic is missing. Thus, O(1) complexity also for GB. Priorities could be implemented in parallel, in a similar way as the logic in Figure 3.3 and 3.5 but using the information from the priority bit instead of the allocated bit of the core-status register and using the size-check only if the task has a forced priority. With a priority task we do not care if there is another task running on the core or not, but only if it has a priority. After it is decided on which core the priority task is going to run the core-status bit simply tells us if we have to freeze or downgrade the running task before we bring the priority task.

#### 3.3.5 GB++

Generic Binary with default upgrading can be implemented by adding a preliminary step before the for as showed in Algorithm-figure 4 below:

#### Algorithm 4 Generic Binary++ or GB++

```

1: find task t such that p(t).size < task(i)size &&(p(t-1) = NULL)|p(t+1) = NULL)

2: if t = NULL then

for s = task(i).size \rightarrow 2 do

3:

find space p where task(i) fits

4:

if p \neq NULL then

5:

6:

allocate p to task(i)

7:

end if

end for

8:

9: else

upgrade

10:

11: end if

```

To sustain O(1) complexity we have to add logic to the circuits of Figure 3.3 and 3.5 but that would be only a couple of AND/OR gates of this kind:

Figure 3.10: Logic for parallelising default upgrading of core i.

This would be the logic per implementable core, which means also cores of 4-issue and 8 issue. The only difference for the bigger cores is that the core.status.register(i+1) in Figure 3.10 is replaced by the outputs of the ORgates of Figure 3.3. Thus for corespace 8 we would need 8+2+1=11 times the circuit above. We pay W(n) complexity to preserve O(1) time complexity.

# 3.4 AlgD and AlgBall8

If one looks at the scheduling historic of GB they will notice that the algorithm is downgrading too much. Sooner or later 2-issue execution dominates and the chance that two 2-issue tasks finish in the same time so that enough resources for a 4-issue task are available is rather small. In an effort of preventing too much downgrading we tried to switch the preferred core of all tasks to the biggest possible core (for this research that is 8) in AlgB/GB ending up with 'AlgBall8'. This is not really exactly a new algorithm, it is still AlgB/GB, but the input is altered so that it appears that the preferred core of every task is 8-issue. The results were not better as we will see in Chapter 5.

Another way of avoiding too much downgrading was to combine GB and AlgA, creating AlgD. This algorithm downgrades the tasks only one level down. If there is still no space to run the task it looks for another task in the window and tries again later on. Unfortunately this algorithm showed worse results than GB, probably because it combines the disadvantages of both algorithms, with most important the disadvantage of AlgA to create bubbles.

# 3.5 Conclusion of Chapter 3

In this chapter we presented the several algorithms that were developed and tested during this thesis, starting from a very Basic task scheduling algorithm, moving to algorithms more specific to the ERA platform. Such as Versioning that downgrades the task by scheduling it to run on a smaller core to avoid creating bubbles that Basic does. Running in a smaller task means bringing from the memory a different binary of the task, compiled especially for that core. That takes time, which is called the 'reloading penalty'. To deal with the reloading penalty Generic Binary was invented creating a binary of a task that can run on any core. That also created the ability to downgrade tasks on-the-fly to make space for new tasks, support priorities and handle interrupts without big delays for the tasks already running. All these lead to a new algorithm, AlgB or GB. But it also brought the idea of upgrading a task when resources become available. instead of bringing immediately a new task for execution. That is GB++. Finally some very unsuccessful algorithms like AlgBall8 and AlgD were mentioned. In Table 3.3 there is an overview of all the algorithms that were developed, their characteristics and their differences. It is time now to see how those algorithms performed and how they compare to each other.

| character.           | algorithms                          |                                     |                                    |                                    |                                   |                                                          |

|----------------------|-------------------------------------|-------------------------------------|------------------------------------|------------------------------------|-----------------------------------|----------------------------------------------------------|

| /situation           | AlgA                                | RAlgA                               | GB                                 | GB++                               | Versioning                        | AlgD                                                     |

| task does<br>not fit | stall task                          | stall task<br>unless<br>8-issue     | downgrade<br>task till it<br>fits  | downgrade<br>task till it<br>fits  | downgrade<br>task till it<br>fits | downgrade<br>once then<br>stall if still<br>does not fit |

| window               | yes                                 | yes                                 | no                                 | no                                 | no                                | yes                                                      |

| downgrad.            | no                                  | no                                  | yes                                | yes                                | only before execution             | only once                                                |

| upgrading            | no                                  | no                                  | no                                 | yes                                | no                                | no                                                       |

| penalty              | no                                  | no                                  | practically<br>not (155<br>cycles) | practically<br>not (155<br>cycles) | yes                               | practically<br>not (155<br>cycles)                       |

| interrupts           | replacing<br>bubbles or<br>stalling | replacing<br>bubbles or<br>stalling | downgrading or stalling            | downgrading<br>or stalling         |                                   | 12%                                                      |

| priorities           | only static                         | only static                         | only static                        | all<br>priorities                  | only static                       | no                                                       |

| forced priorities    | only by stalling                    | only by<br>stalling                 | yes (without upgrading)            | yes                                | only by stalling                  | no                                                       |

| binaries<br>per task | 3                                   | 3                                   | 1                                  | 1                                  | 3                                 | 1                                                        |

Table 3.3: Overview of the developed algorithms.

Simulator and benchmarks

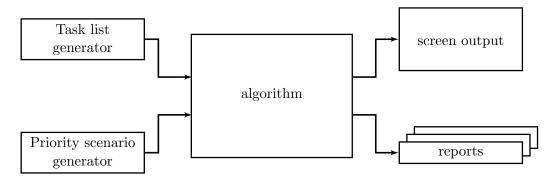

#### 4.1 The simulator