# A Multi-Path Sigma Delta ADC

For use in battery management systems

# L.A. Loopik

**Challenge the future**

# A Multi-Path Sigma Delta ADC

# For use in battery management systems

by

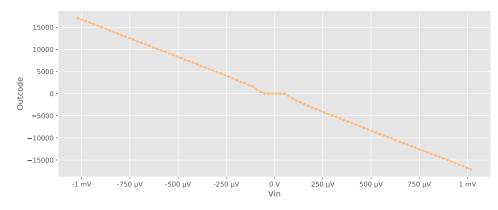

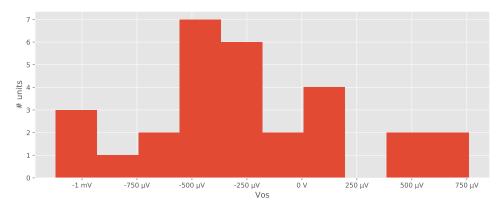

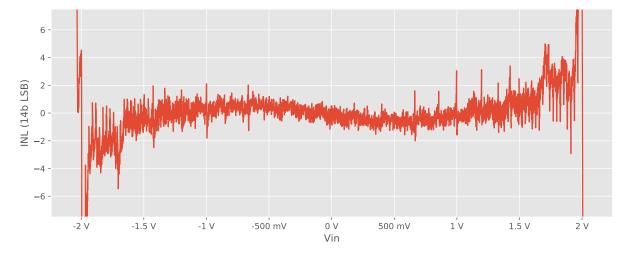

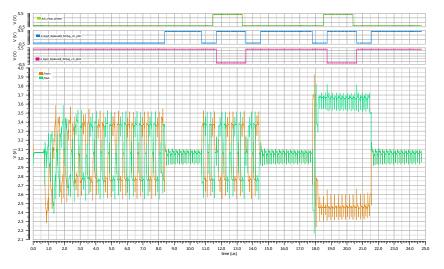

# L.A. Loopik

in partial fulfillment of the requirements for the degree of

#### Master of Science in Electrical Engineering

at the Delft University of Technology, to be defended publicly on Monday December 18, 2017 at 14:00.

Thesis committee:Prof. dr. ir. K.A.A. Makinwa,<br/>Dr. F. Sebastiano,TU Delft, supervisor<br/>TU DelftDr. C. P. L. van Vroonhoven,Analog Devices

This thesis is confidential and cannot be made public until December 18, 2020

An electronic version of this thesis is available at http://repository.tudelft.nl/.

# Abstract

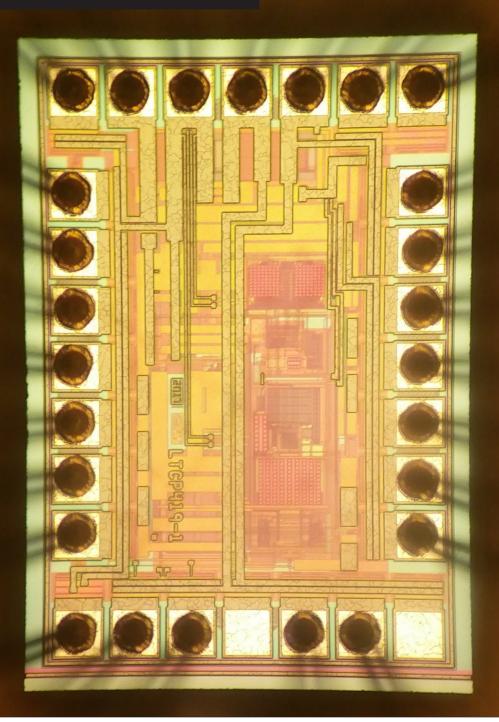

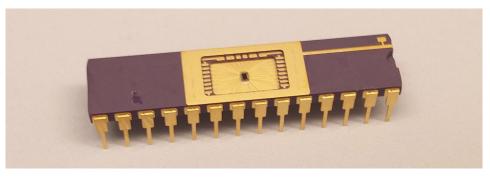

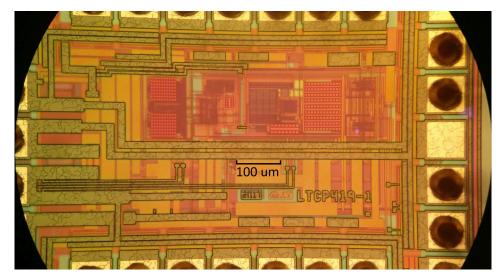

This thesis presents the design and testing of a multi-path analog-to-digital converter for current sensing in battery management systems. The specifications of this converter are (1) continuously integrate and convert a signal at 125 Hz with a resolution of 20 bit and (2) perform on demand fast conversions of 20 µs at a resolution of 14 bit. Both conversions should be done with a maximum 1 LSB offset and 0.1% gain error. The realized system consists of a discrete time 1st order sigma delta converter, followed by a 10 bit charge redistribution extended counting ADC. This design uses the same analog front end for both conversions, thereby saving both power and chip area. To achieve the lowest offset possible, a system level chopping scheme is implemented. A working prototype has been made in TSMC 0.18 BCD technology, using an area of  $570 \,\mu\text{m} \times 150 \,\mu\text{m}$  with a 5 V supply voltage. The realized chip proves that the concept of combining the analog front end works and achieves a 15 bit linearity. At the 20 bit level, there are still significant issues and despite serious efforts the root cause of those issues has not yet been isolated. Next design and testing steps have however been identified.

# Acknowledgements

Let me start by thanking everyone from the TU Delft and Linear Technology/Analog Devices for making it possible for me to reach this point in my life. First of all, many thanks to Prof. Kofi Makinwa for creating the opportunity for me to do my master thesis project with Linear Technology on this interesting and relevant topic. This way I was able to spend a fruitful year in Munich, learn a lot, both professionally and personally.

At Linear Technology, now merged with Analog Devices, my special thanks goes out to Christoph Schwoerer for inviting me and supporting me throughout my project and for making me a job offer! My biggest thanks goes to Caspar van Vroonhoven, my daily supervisor for his continuous support. He was always available to help me on any topic: anywhere from housing to the most detailed technical issues. I greatly enjoyed our technical conversations and thank you for your trust in me.

I also received great help and advice from Gerd Trampitsch on circuit design and from Axel Klein on my test setup and python. I thoroughly enjoyed being a part of the Munich design team. You are all great colleagues to work with! Jiri Dak, thank you for all your amazing layout work, and your help with all our tape-out troubles. Andreas Beermann, thank you for your help with the test PCB and Patrick Wilhelm, for your support with the FPGA's.

Further, I would like to thank my parents for their constant support throughout my study and their never ending trust in me. My fellow students Electrical Engineering and the Electrotechnische Vereeniging for our times together. My housemates at JvB 163 for always being there for me. And last but not least my student association DSB, especialy my friends from Schranz, for all the fun we had.

Let me finish by saying that I am very excited to be returning to Munich for a permanent position as Design Engineer with Analog Devices in January.

L.A. Loopik Rijswijk, December 2017

# Contents

| 1 | Introduction |                                                                   |    |  |  |  |  |

|---|--------------|-------------------------------------------------------------------|----|--|--|--|--|

|   | 1.1          | Battery Management Systems                                        | 1  |  |  |  |  |

|   |              | 1.1.1 System overview                                             | 1  |  |  |  |  |

|   |              | 1.1.2 Impedance measurement                                       | 1  |  |  |  |  |

|   |              | 1.1.3 Coulomb counting                                            | 2  |  |  |  |  |

|   |              | 1.1.4 Current-sensing techniques                                  |    |  |  |  |  |

|   | 1.2          | The multi-path current ADC                                        |    |  |  |  |  |

|   | 1.3          | Thesis outline                                                    | 3  |  |  |  |  |

| 2 | Svs          | tem requirements                                                  | 5  |  |  |  |  |

|   | -            | Requirements specification                                        | 5  |  |  |  |  |

|   |              |                                                                   |    |  |  |  |  |

|   |              | 2.2.1 Offset and Gain stability                                   |    |  |  |  |  |

|   |              | 2.2.2 Continuous measurement                                      |    |  |  |  |  |

|   |              | 2.2.3 Windowing                                                   |    |  |  |  |  |

|   | 2.3          | On demand current measurement                                     | 6  |  |  |  |  |

|   |              | 2.3.1 Timing constraints                                          |    |  |  |  |  |

|   |              | 2.3.2 Interference with coulomb counting                          |    |  |  |  |  |

| 3 | <b>C</b>     |                                                                   | 9  |  |  |  |  |

| 3 |              | rent-to-Digital converters and their front ends<br>Converter type | -  |  |  |  |  |

|   |              |                                                                   |    |  |  |  |  |

|   | 5.4          | 3.2.1 CT/DT sigma-delta converters                                |    |  |  |  |  |

|   | 2 2          | Direct input sampling                                             |    |  |  |  |  |

|   |              | Pre-amplifier                                                     |    |  |  |  |  |

|   | Ј.т          | 3.4.1 Noise/Bandwidth                                             |    |  |  |  |  |

|   |              | 3.4.2 Boxcar pre-amplifier                                        |    |  |  |  |  |

|   | 35           | Front-end choice                                                  |    |  |  |  |  |

|   |              |                                                                   |    |  |  |  |  |

| 4 | -            |                                                                   | 13 |  |  |  |  |

|   | 4.1          | Sigma delta analog to digital conversion                          |    |  |  |  |  |

|   |              | 4.1.1 Combining coulomb counting and current measurement          |    |  |  |  |  |

|   | 4.2          |                                                                   |    |  |  |  |  |

|   |              | 4.2.1 State-holding elements                                      |    |  |  |  |  |

|   |              | 4.2.2 Incremental conversions                                     |    |  |  |  |  |

|   | 4.0          | 4.2.3 Correct integration                                         |    |  |  |  |  |

|   | 4.3          | Extended counting.                                                |    |  |  |  |  |

|   |              | 4.3.1 Timing                                                      |    |  |  |  |  |

|   |              | 4.3.2 Gain matching                                               |    |  |  |  |  |

|   | 1 1          | 4.3.3 Resolution requirements secondary ADC                       |    |  |  |  |  |

|   | 4.4          | Adding the current measurement                                    |    |  |  |  |  |

|   | 4 -          | 4.4.1 Combined timing                                             |    |  |  |  |  |

|   | 4.5          | Other considerations.                                             |    |  |  |  |  |

|   |              | 4.5.1 Current conversion quantization noise                       |    |  |  |  |  |

|   |              | 4.5.2 Digital decimation filter and gain matching                 |    |  |  |  |  |

|   |              | 4.5.3 Speed                                                       |    |  |  |  |  |

|   | 10           | 4.5.4 Integrator leakage                                          |    |  |  |  |  |

|   | 4.6          | Oversampling rate                                                 | 22 |  |  |  |  |

| 5  |            | cuit level Design 25                 |

|----|------------|--------------------------------------|

|    | 5.1        | Sigma delta modulator                |

|    |            | 5.1.1 Integrator switching scheme    |

|    |            | 5.1.2 Thermal noise                  |

|    |            | 5.1.3 OTA design                     |

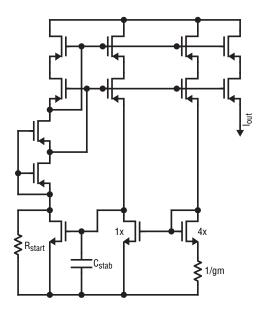

|    |            | 5.1.4 Constant gm current biasing    |

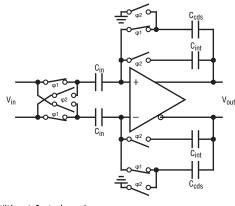

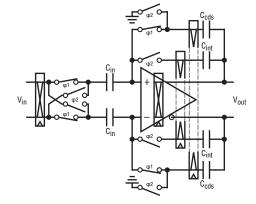

|    |            | 5.1.5 Fast chopping                  |

|    |            | 5.1.6 Comparator design              |

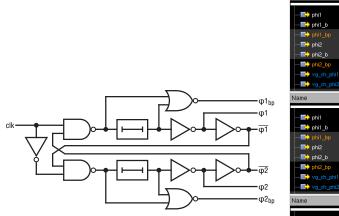

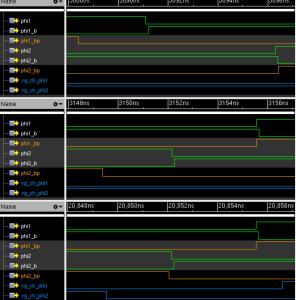

|    |            | 5.1.7 Timing generation              |

|    | 5.2        | Extended Counting ADC                |

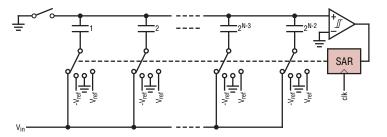

|    |            | 5.2.1 Architecture                   |

|    |            | 5.2.2 SAR Buffer                     |

|    |            | 5.2.3 Bridge capacitor               |

|    |            | 5.2.4 Further optimization's         |

|    |            | 5.2.5 Comparator                     |

|    |            | 5.2.6 SAR and SAR buffer timing      |

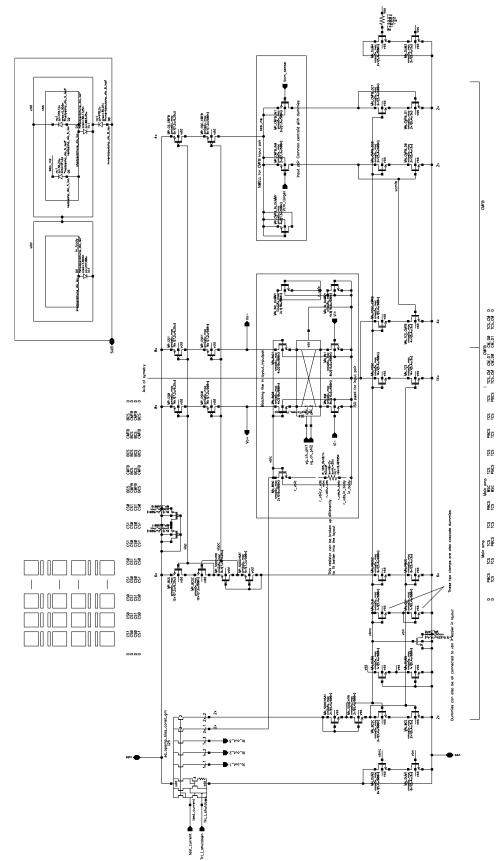

|    | 5.3        | Complete design                      |

|    |            | Test modes                           |

|    | 5.5        | Digital back-end                     |

| ~  |            |                                      |

| 0  | Lay        |                                      |

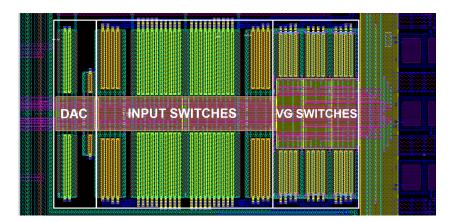

|    | 0.1        | Sigma delta modulator                |

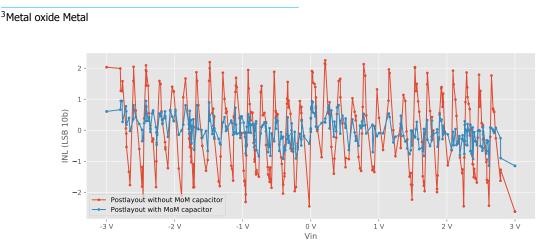

|    | <b>c</b> 0 | 6.1.1 Post-layout simulation         |

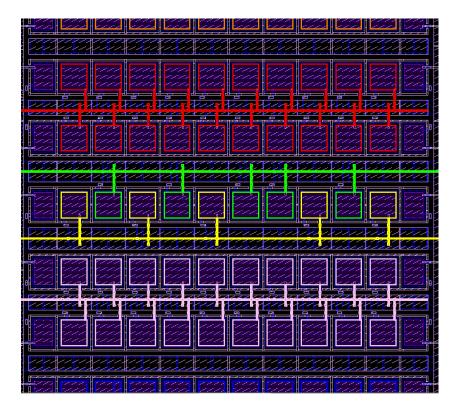

|    | 6.2        | SAR                                  |

|    |            | 6.2.1 SAR Capacitor array            |

| 7  | Mea        | asurement Results 43                 |

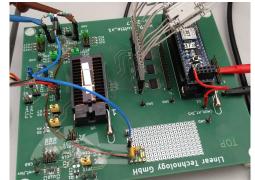

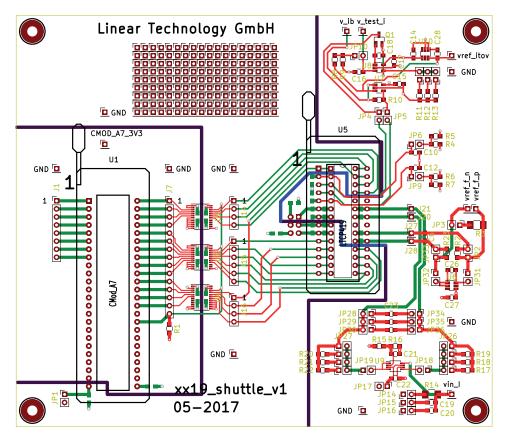

|    | 7.1        | Measurement setup                    |

|    |            | 7.1.1 Analog test system             |

|    |            | 7.1.2 Digital test system            |

|    |            | 7.1.3 Mixed signal design            |

|    |            | 7.1.4 Measurement instruments        |

|    | 7.2        | General functioning                  |

|    | 7.3        | SAR and SAR buffer                   |

|    | 7.4        | Sigma delta converter                |

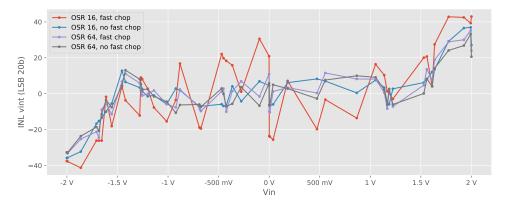

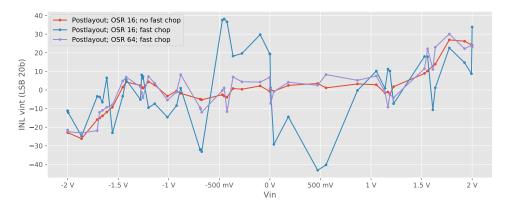

|    |            | 7.4.1 Linearity                      |

|    |            | 7.4.2 Dead-zone                      |

|    |            | 7.4.3 Offset                         |

|    | 7.5        | SAR to SD matching                   |

|    | 7.6        | Timing                               |

| 0  | Com        | clusions and Recommendations 53      |

| 0  |            | Conclusions                          |

|    |            | Future research                      |

|    |            | Known improvements                   |

|    | 0.5        |                                      |

| Bi | bliog      | sraphy 57                            |

| Δ  | Ton        | level simulations LTCP419 shuttle 61 |

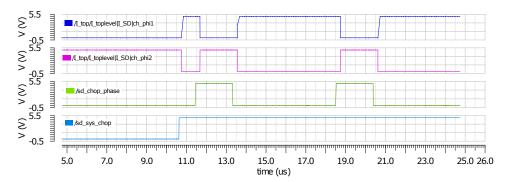

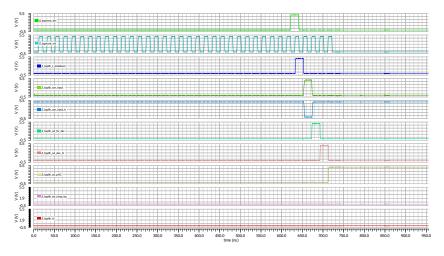

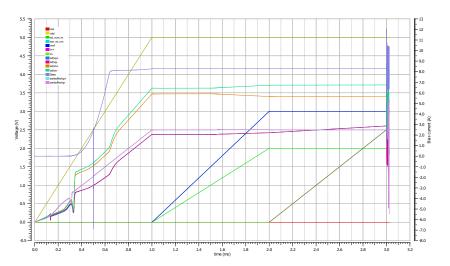

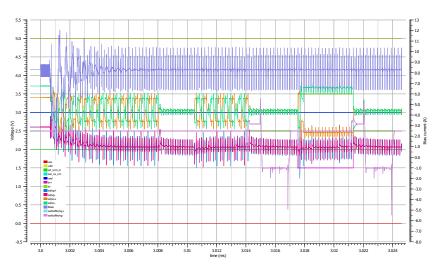

| А  |            | Sigma Delta operation                |

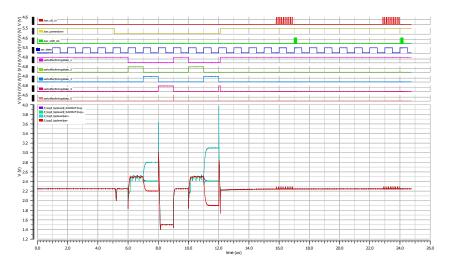

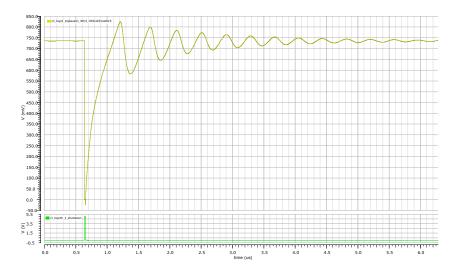

|    |            | SAR operation                        |

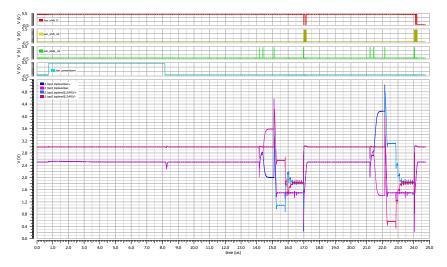

|    |            | Test mode operation                  |

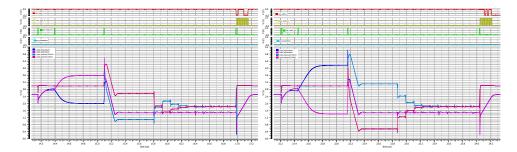

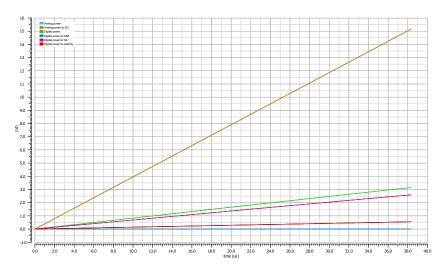

|    |            | Power consumption                    |

|    |            | •                                    |

|    | А.Э        | Power on                             |

| В  |            | CP419-x version information67        |

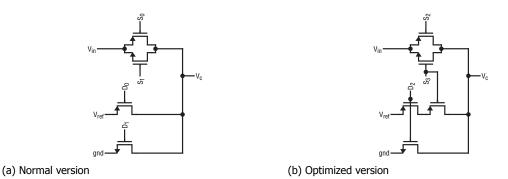

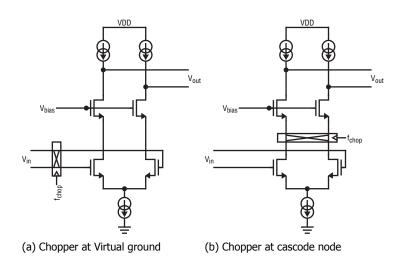

|    |            | Cascode chopping                     |

|    |            | Small capacitors                     |

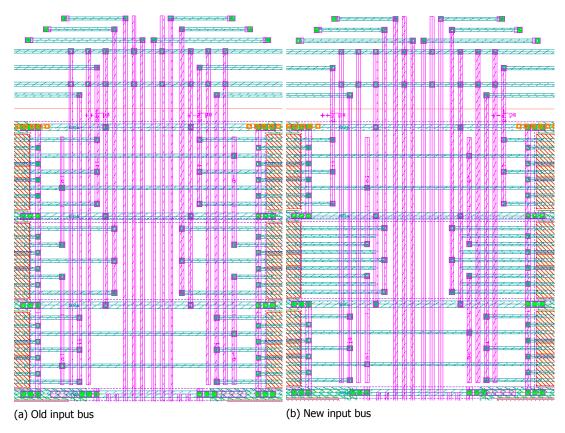

|    |            | Improved input bus                   |

| С | Switched Capacitor Integrator Circuits                  | 71   |

|---|---------------------------------------------------------|------|

|   | C.1 Used Python code                                    | . 71 |

|   | C.2 Simple SC integrator.                               | . 74 |

|   | C.3 SC integrator with autozeroing.                     | . 75 |

|   | C.4 SC integrator with auto-zeroing and double sampling | . 76 |

|   | C.5 Finite gain compensated integrator                  | . 77 |

|   | C.6 Finite gain compensation with non-constant gain     | . 78 |

| D | OTA Schematic                                           | 81   |

1

# Introduction

This thesis describes the design and testing of a Multi Path Analog to Digital Converter (MP-ADC). The aim of this MP-ADC is to explore the possibility of measuring two different quantities (electrical current and electrical charge) over two different time intervals with the same chip. If this succeeds it opens up the possibility to make smaller (die area) Battery Management System (BMS) chips with lower power consumption.

## **1.1.** Battery Management Systems

The world is using more and more batteries every day. Every day, more appliances and machines are battery powered. This change is going hand in hand with improvements in battery technology. And while battery technology is getting better, it is also getting more complicated. In the past, it was quite easy to determine the state of charge of a battery by measuring the cell voltage. But as battery technology improves, side effects such as dropping cell voltage, are getting smaller and smaller. Also, more complicated batteries require more control circuitry to prevent overcharging, undercharging, overheating and to determine the state of charge and state of health of a battery. This control circuitry is called the Battery Management System, or BMS. Because batteries are expensive it is important to maximize their lifetime. Being able to measure the behaviour of the battery and controlling it based on these measurements can increase the lifetime of the battery, and as such, give a significant competitive edge.

#### 1.1.1. System overview

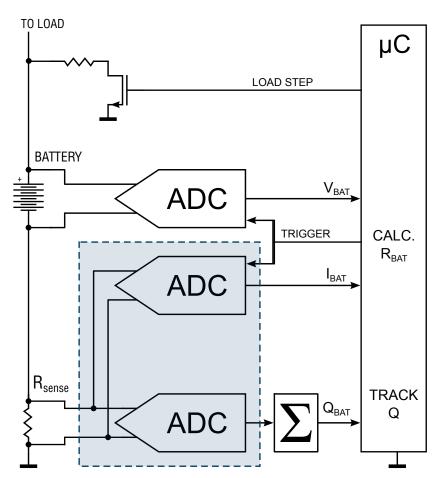

A modern battery system must measure and keep track of many different properties of the battery it is monitoring. In this thesis, we will focus on two main properties used to determine the state of charge and state of health of a battery: cell impedance and delta charge.

The cell impedance is the internal resistance of the battery, this quantity changes as the battery is charged and discharged, as well as over the lifetime of a battery. Because of this it can be used to determine the state of health, as well as give an estimate for the remaining state of charge.

Another method of determining the state of charge, is to use the delta charge of the battery. This quantity gives an good basis for determining the state of charge of the battery, by essentially measuring all charge going into, and going out of the battery. Of course, this measurement is also not perfect, as it does not include, for example, self discharge of the battery.

#### **1.1.2.** Impedance measurement

To measure the cell impedance, both the cell voltage and current are measured. The measured cell voltage is now a combination of the internal cell voltage and the voltage drop over the internal resistance of the cell. When this measurement is done with (at least) two distinct current levels, the internal cell voltage can be cancelled out, and the cell impedance can be calculated.

There are multiple techniques available to measure at two distinct current levels. The easiest method is to modulate the load of the battery (connect an extra load resistance) for a short time during the second measurement. Another option is to make use of the natural variations of the current when

the battery is connected to a non-constant load. It is important that these measurements are done with minimal energy use and minimal interference with normal operation. Therefore, these measurements need to be done as quickly and energy efficiently as possible.

#### Importance of synchronous V and I measurements for impedance measurement

Because in most situations, the load of the battery is not constant. It is very important to make sure that the voltage and current measurements used for the impedance calculation are done at the exact same time.

#### 1.1.3. Coulomb counting

For measuring the delta charge of the battery, a technique called Coulomb Counting is used. The total charge entering and exiting the battery is measured by continuously integrating the battery current. For this integration to be accurate, the current measurement should be done with a very low offset and gain error. Additionally, an accurate time reference is required for accurate integration. For BMS's, this time reference is usually available in the form of a crystal oscillator clock. In order to correctly integrate the signal, it is important that current is continuously measured, without any gaps between the time windows. The speed of these measurements is less important, as they are mostly used to track the status of the battery over a longer time.

#### **1.1.4.** Current-sensing techniques

For both the impedance measurement and the coulomb counting, a current measurement needs to be done. There are multiple techniques in use to measure currents. The most used ones are based on either magnetic sensing or shunt-based sensing.

#### Magnetic

Magnetic current sensing devices use the fact that an electric current produces an magnetic field proportional to the current (Ampère's law) to measure this current<sup>1</sup>[1]. Measuring this magnetic field can be done in multiple ways, ranging from using Hall-effect sensors to current transformers. This technique has the advantage that there is no device in series with the current to be measured. This also means that there is a galvanic isolation between the battery and the measurement circuit. The main disadvantage of this technique is that it is hard to do low offset, high precision measurements due to interference with external magnetic fields.

#### Shunt-based

The other commonly used technique to measure current is to use a shunt resistor in the current path. This can be either an external shunt<sup>2</sup>, or a internal shunt<sup>3</sup>[2]. The current will now produce a voltage proportional to the current over the shunt (Ohm's law), which can be measured using conventional ADC techniques. In order to have an accurate measurement, the shunt has to be very accurate as well. This means having a well known resistor value, but also a low temperature coefficient (as the shunt heats up during use). The main advantage of using this technique is the high precision measurements it allows. The main disadvantage is the use of an (expensive) shunt resistor that needs to be in the main current path of the battery.

## **1.2.** The multi-path current ADC

As described above, in a BMS needs to do two types of current measurements: a fast, on demand, medium-precision measurement for use in impedance measurements, and a slower, continuous, high precision measurement, for use in coulomb counting. Existing BMS's have two parallel converters that measure the same shunt voltage to fit both those requirements. In order to save chip area (and thus costs), a investigation is done to combine the two types of measurements into one, multi-path, analog to digital converter. This converter should continuously measure and integrate the current through the shunt. In addition to this it should be able to do a quick conversion of the instantaneous current

<sup>&</sup>lt;sup>1</sup>Open loop: MLX91206 https://www.melexis.com/en/product/MLX91206

Closed loop: DRV411: http://www.ti.com/product/DRV411

<sup>&</sup>lt;sup>2</sup>LTC2944http://www.linear.com/product/LTC2944

<sup>&</sup>lt;sup>3</sup>LTC2947: http://www.linear.com/product/LTC2947

Figure 1.1: A simplified view of the BMS showing the intended combination of converters.

through the shunt, whenever triggered to do so by an external controller. Furthermore, the on demand current measurement should not interfere with the continuous measurements, as to not negatively affect the continuous integration. The targeted combination of converters is shown in figure 1.1.

# 1.3. Thesis outline

The main research done in this thesis is to design such a converter for use in future BMS's. Chapter 2 will describe the requirements needed for such a converter. Next, chapter 3 looks into different aspects of current-to-digital conversion. With that knowledge, it will be possible to make a system level design, this is discussed in chapter 4. Next the circuit level design is documented in chapter 5. As the final result of this research is produced in silicon, the layout process is described in chapter 6. Chapter 7 describes the testing of the silicon and its results. Finally, in chapter 8 conclusions are drawn and recommendations for further research are made.

2

# System requirements

As documented in chapter 1, by combining a continuously integrating converter with a fast, on demand converter, their separate requirements need to be combined. In this chapter the requirements of the two different measurements will be discussed separately.

## **2.1.** Requirements specification

The MP-ADC need to fulfill the requirements in tables 2.1 and 2.2, as given by the sponsor of this project.

In the sections below, some background to the requirements will be discussed

# **2.2.** Coulomb counting

In order to correctly integrate the current through the shunt resistor, and be able to accurately calculate the charge that flowed through the shunt, it is important that the charge measurement is as accurate as possible. There are a few requirements that make a coulomb counting measurement stand out from a usual current measurement. These requirements are: offset and gain stability, continuous measurement and windowing.

## 2.2.1. Offset and Gain stability

Because the resulting measurements will be integrated indefinitely, it is important to have a very low offset, as an offset in the measurement will result in charge drift in the integrated charge. A gain error will translate directly to a gain error in the calculated charge, so it is also important to keep the gain stable. Linearity of the measurement will also translate to a non-linear error in the charge, but as long as this error is lower then the instability of the gain, this error will not substantially increase the total charge error.

#### 2.2.2. Continuous measurement

To calculate the total amount of charge correctly, even when the current through the shunt is not constant, it is necessary to continuously measure the current trough the shunt, and not to have any "gaps" in the measured data. In other words: as soon as one measurement is complete, the next one has to start, without any delay. This has the effect that the input stage is always busy sampling the input signal, and cannot be time-multiplexed, unless the whole input stage is implemented twice.

#### 2.2.3. Windowing

The final special requirement for coulomb counting is also imposed by the integration. To have a correct integration of the input signal, all input samples need to be weighted equally. This is another way of saying that if you apply a current pulse to the converter, it should always integrate to the same charge (if it is the same pulse), no matter when in the conversion cycle the current pulse is applied to the converter.

|                                 | Condition | Min | Тур     | Max  |       |

|---------------------------------|-----------|-----|---------|------|-------|

| Resolution (No missing codes)   | 2ms Mode  | 18  |         |      | Bits  |

|                                 | 8ms Mode  | 20  |         |      | Bits  |

| Full Scale Input Voltage        |           |     | ±2      |      | V     |

| LSB Voltage of Charge Sense     | 2ms Mode  |     | 15.625  |      | μV    |

|                                 | 8ms Mode  |     | 3.90625 |      | μV    |

| Noise                           | 2ms Mode  |     | 6       |      | μVrms |

|                                 | 8ms Mode  |     | 3       |      | μVrms |

| Gain Error                      | 90% FS    |     |         | ±0.1 | %     |

| Offset Voltage                  | IP=IM=0V  |     |         | ±1   | LSB   |

| Integral Non-linearity          |           |     |         | ±3   | LSB   |

| Supply Voltage                  |           |     | 5       |      | V     |

| Input Voltage Common Mode Range |           |     | 2.5     |      | V     |

| Conversion Time                 | 8ms Mode  |     | 8       |      | ms    |

|                                 | 2ms Mode  |     | 2       |      | ms    |

Table 2.1: The specifications for the coulomb counter

Table 2.2: The specifications for the on demand current measurement

|                               | Condition  | Min | Тур  | Max  |       |

|-------------------------------|------------|-----|------|------|-------|

| Resolution (No missing codes) | 125µs Mode | 16  |      |      | Bits  |

|                               | 30µs Mode  | 14  |      |      | Bits  |

| Full Scale Input Voltage      | •          |     | ±2   |      | V     |

| LSB Voltage of Charge Sense   | 125µs Mode |     | 62,5 |      | μV    |

|                               | 30µs Mode  |     | 250  |      | μV    |

| Noise                         | 125µs Mode |     | 40   |      | μVrms |

|                               | 30µs Mode  |     | 80   |      | μVrms |

| Gain Error                    | 90% FS     |     |      | ±0.1 | %     |

| Offset Voltage                | IP=IM=0V   |     |      | ±1   | LSB   |

| Integral Nonlinearity         |            |     |      | ±3   | LSB   |

| Conversion Time               | 125µs Mode |     | 125  |      | μs    |

|                               | 30µs Mode  |     | 31   |      | μs    |

| Trigger to measurement delay  | -          |     |      | 1    | μs    |

# 2.3. On demand current measurement

The requirements for the asynchronous current measurement are different from the requirements for coulomb counting, as it is a single shot measurement. This means it is not constrained by requirements as continuous integration. The main challenge for the asynchronous current measurement is however, to integrate it with the coulomb counter in such a way, that it is almost indistinguishable from two separate ADC's.

#### 2.3.1. Timing constraints

The main purpose of the single shot current measurement is to combine the measurement with a simultaneous cell voltage measurement, to calculate cell impedance. For this calculation to be accurate, the current measurement must be done in the same time frame as the cell voltage measurement, as also explained in chapter 1. Because the voltage measurement is done by a different converter, which is not necessarily synchronized with the multi-path current ADC, the current measurement must be able to start at any time, started by an external trigger signal. This essentially means that the current measurement must be completely independent (in the timing aspect) from the coulomb counter.

**2.3.2.** Interference with coulomb counting Apart from being independent of the timing of the coulomb counter, the asynchronous current measurement must also not interfere with the coulomb counter. This is important, as it is important that the charge measured by the coulomb counter should be as accurate as possible, and should not be disturbed by intermediate current measurements.

# 3

# Current-to-Digital converters and their front ends

In this chapter, possible front ends for the ADC's will be discussed. In order to do this, it is first necessary to decide on a converter type. Next, it is then possible to look at different front end designs, and choose the one which best matches the characteristics of this design.

## **3.1.** Converter type

By specification both converters are high precision converters with a low to medium bandwidth and very low offset. To decide what type of converter is best for this type of measurements, a couple of converters are considered.

#### Flash ADC

The simplest type of ADC is the flash ADC. A flash ADC consists of a way to split the reference into N equal parts, which are then used to compare to the input voltage by using N comparators. Because there is only one thing happening at the moment of conversion (the comparators making their decision), a flash ADC can be incredibly fast. For an n bit converter, however,  $2^n$  comparators are needed, which, at high resolutions, is not a realistic solution. Apart from the sheer number of comparators, the offset and matching of requirements of the comparators become exponentially more challenging with higher resolutions. Because of these properties, a flash ADC is not a realistic ADC type for this system.

#### Dual slope ADC

Another type of ADC is the dual slope ADC. Here the input signal is first integrated for a fixed amount of time, after which the reference signal with the opposite polarity is integrated until the output of the integrator is back to zero. The time it takes to bring the output of the integrator back to zero is proportional to the input signal. The advantage of this technique is that it integrates the input signal, which suppresses noise. The disadvantage is that during the discharge time, the input signal is not measured. Because the charge conversion requires a continuous input measurement, this is not a viable option for this design.

#### Successive approximation ADC

The next option are successive approximation ADC's[3], which by trying to match the output of a DAC with the input signal. This is done by trial-and-error for every bit from the MSB to the LSB as follows: First set all bits to 0, then first flip the MSB, if the signal is to high, flip the MSB back and keep it 0, if the signal is still to low, keep the bit 1. When this is continued for every bit, the final DAC value will represent the input signal as close as possible. This means that there is a digital representation of the input signal, and the signal is digitized. The maximum resolution and linearity of a successive approximation ADC is usually limited by matching, and can be increased by extensive trimming and calibration. As extensive trimming is not desired, and getting to 20 bit accuracy with component matching is not possible, the successive approximation ADC is also not a good option for this design.

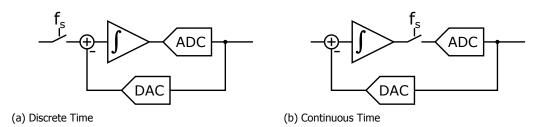

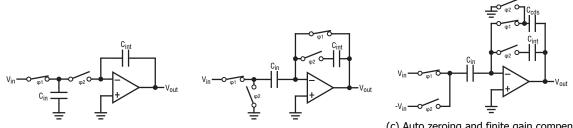

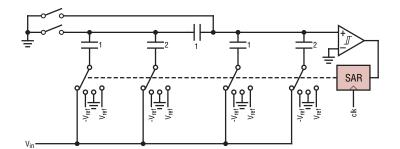

Figure 3.1: The two main Sigma-Delta sampling architectures

#### Sigma delta ADC

Finally, there is the option of sigma delta ADC's[4], these work by oversampling and noise-shaping. This means that the ADC samples at a higher frequency than the output frequency. This is done by putting a low resolution ADC and DAC in a feedback loop. While oversampling can be done with any type of ADC, in a sigma delta ADC the feedback loop 'shapes' the quantization noise with a high pass response. Since most of the quantization noise energy is now at higher frequencies, it is possible to remove most of it by passing the signal through a low-pass filter. This way, a low resolution ADC and DAC combination can be used to create a very high resolution ADC without extreme matching requirements. And while the resulting output sample rate is still quite low, the conversions can be combined back to back, without any dead time in between, which is important for the charge conversions. Because of these advantages a sigma delta ADC is thus the ADC type of choice for this project.

## 3.2. Sampling

A crucial part of any analog to digital converter is sampling. Somewhere in the signal path, the timecontinuous analog signal needs to be converted in a time-discrete signal. Especially for sigma-delta converters, there are multiple places in the signal path where this conversion can be done.

#### 3.2.1. CT/DT sigma-delta converters

In a sigma-delta converter there are two conventional places to do sampling: before or after the integrator. This results in two different types of sigma-delta converters: a Continuous Time (CT) sigma-delta converter (see figure 3.1b) and a Discrete Time (DT) sigma-delta converter (see figure 3.1a). The two types vary greatly in implementation and behaviour, but the two most important differences are frequency folding and integrator design.

When using the DT solution, sampling is done at the beginning of the signal path of the converter. This means the input signal (and noise) should already be band-limited to prevent aliasing (and noise folding). This is one of the disadvantages of using a DT system. Another disadvantage is that DT systems will use more power then equivalent CT systems. An advantage of DT systems is that chopping is easier to implement and that a DT integrator is used. DT integrators have as advantage that they can use techniques as auto zeroing (AZ) and finite gain compensation relatively easily. Also the design of a DT DAC is easier then the design of a CT DAC.

A CT solution instead has different advantages and disadvantages. By moving the sampling point behind the integrator, a low pass filtering is applied to the input signal. This means that there is an implicit anti-aliasing filter in a CT system. Another big advantage is that, as mentioned before, CT systems generally use less power for equivalent performance. Disadvantages of a CT system are that chopping becomes more complex, and that a CT (sample-and-hold) DAC needs to be implemented. Also jitter, and other timing inaccuracies become important. And while CT integrators are more power efficient than DT integrators, it is also much harder to get to the same level of precision using techniques like auto zeroing or finite gain compensation.

## **3.3.** Direct input sampling

With a DT system the sampling switch is the input of the system, as long as the input is already band-limited. The easiest way to connect the shunt to the system is thus to add an analog low pass filter to the shunt, and directly sample the voltage. By sampling the shunt directly like this, the input system of the converter is very simple, and chopping can be implemented in a straightforward manner.

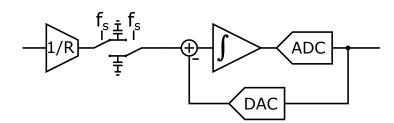

Figure 3.2: The boxcar pre-amplifier scheme

The disadvantages, however, are noise and input impedance. Noise because the shunt voltage will be relatively low (mV levels), and a big sampling capacitor is needed to have low enough kT/C noise. This big sampling capacitor will then lower the input impedance of the converter, unless a pre-charging scheme is used. Depending on the shunt and filter design, a too low input impedance can be a problem.

# 3.4. Pre-amplifier

The alternative to a direct input sampling system, is to use a pre-amplifier. Using a low noise preamplifier, can improve the SNR of the system and thus lower the noise requirements of the rest of the system. Another advantage of using a pre-amplifier is a higher input impedance.

#### 3.4.1. Noise/Bandwidth

When using a DT sigma-delta system, the output of the pre-amplifier will be sampled. Because this causes frequency folding, the bandwidth of the amplifier should be less then the Nyquist frequency of the sigma-delta. But even if this is the case, the output noise of the pre-amplifier will be folded down to frequencies of interest. To prevent this, a low pass filter should be added behind the pre-amplifier.

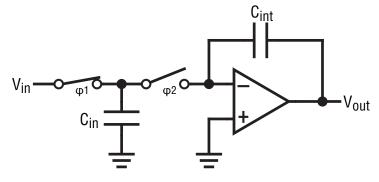

#### 3.4.2. Boxcar pre-amplifier

Another interesting concept, that can be exploited with the help of the pre-amplifier, is to use a boxcar pre-amplifier. This concept is based on using a linear transconductance amplifier as pre-amplifier[5][6], which then charges a capacitor with it's output current. This capacitor is then used in the switched capacitor DT integrator (see figure 3.2). Because this also produces a low pass response, it makes it possible to combine the inherent anti aliasing filter of the CT system with the precision advantages of using a DT integrator.

# **3.5.** Front-end choice

After having discussed the different possibilities for a front end for the ADC, a front end can be picked. The first important choice is whether or not to use a continuous time or a discrete time integrator. Because a high precision system is designed, and techniques like auto-zeroing are significantly easier to use with discrete time integrators, the discrete time system will be used. Especially because a continuous time system is more error prone, and the limited design time was important factor. The choice for a discrete time system has the disadvantage that it will consume more power then a continuous time system, and it will need an anti-aliasing filter.

In order to keep the sampling capacitor size reasonable and the input impedance high, it was decided to make use of a pre-amplifier. This pre-amplifier will amplify the input voltage  $20 \times$  from  $\pm 100 \text{ mV}$  to  $\pm 2 \text{ V}$ . To be able to fit within the available time, it is decided to keep the pre-amplifier out of the scope of this thesis. The decision is made to assume a band-limited, 2 V peak to peak input voltage, and design the rest of the ADC based on this assumption. Further research can be done later to design a fitting (boxcar) pre-amplifier.

4

# System level design

In this chapter the design of the charge and the current ADC's are discussed. Both converters are high precision converters with a low to medium bandwidth. As explained in the previous chapter, in such applications sigma delta converters are a good choice. In this chapter the design of the delta sigma converter and the rest of the system will be done on block level.

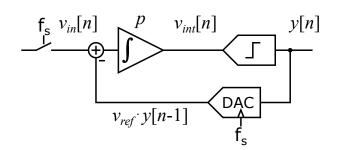

#### **4.1.** Sigma delta analog to digital conversion

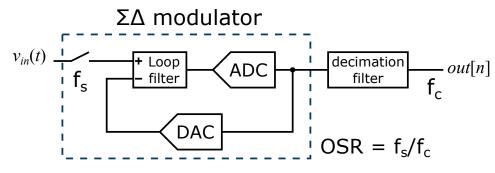

Sigma delta ADC's are best known for their ability to achieve high resolution conversions of signals with a low to medium bandwidth.[4] Sigma delta ADC's are composed of two parts, the sigma delta modulator, and the decimation filter. The sigma delta modulator uses oversampling of a low resolution ADC/DAC combination in a feedback configuration with a loop filter to generate a modulated signal. In this signal, the quantization noise of the ADC/DAC is noise-shaped to high frequencies, away from the frequencies of interest. Subsequently, the high frequencies can be filtered out by the decimation filter, leaving a high resolution reproduction of the input signal. This decimation filter will consist of a digital low-pass filter, usually of the SINC<sup>n</sup> family. The decimation filter will also down-sample the sample rate ( $f_s$ ) to the conversion rate ( $f_c$ ). A block diagram of a sigma delta ADC is shown in figure 4.1.

The ratio between the sampling rate of the sigma delta modulator and the conversion rate is called the oversampling ratio (OSR). Together with the order of the modulator the OSR determines how strongly the quantization noise is suppressed in the overall conversion. The order of the modulator is determined by the number of integrators in the loop-filter. Higher order modulators have higher noise-shaping capabilities, so the quantization noise can be filtered out more effectively.

In order to effectively filter out this more strongly shaped quantization noise, also a higher order decimation filter is needed. In general, the order of the decimation filter should match the order of the modulator. In this case the slope of shaped quantization noise will match the slope of the filter, resulting in a flat quantization noise over frequency.

The disadvantage of using a higher order sigma delta modulators is that these modulators are more sensitive to instability. To compensate for this effect, the ratio between the maximum input voltage

Figure 4.1: The generic block diagram of a discrete time sigma delta converter, with the two different sampling frequencies.

and the reference voltage is reduced.

Sigma delta modulation is based on negative feed-back, which means that as long as the forward gain of the loop is high and the loop is stable, the transfer function of the loop is determined by the feedback path. In the case of the sigma delta modulator, the high forward gain is assured by using integrators in the loop filter.

Because the transfer function of the system is determined by the feedback path, which exists of the internal DAC of the sigma delta modulator, this DAC determines the linearity of the modulator. The resolution of this DAC will need to match the resolution of the internal ADC that produces the quantization noise. While the quantization noise can be dealt with, the linearity of the internal DAC will directly determine the linearity of the system.

While multi-bit ADC's combinations produce less quantization noise, and thus require a lower OSR, realizing very linear multi-bit DAC's is not easy. While techniques exist for creating very linear multi-bit DAC's, most of them rely on complicated extra hardware or complicated switching schemes, such as dynamic element matching (DEM). Because of the added complexity of such techniques, a simpler design has been selected.

This is the use of a single bit ADC followed by a single bit DAC. This has the advantage that a single bit DAC is inherently linear due to having only two possible outputs<sup>1</sup>. Because of this, the overall converter will also be linear, as long as the forward gain of the loop is high enough.

The major disadvantage of using a single bit ADC, however, is that it has very high quantization noise. Which results in higher requirements for the OSR or modulator order in order to push the quantization noise back down to to a low enough level.

Because there are solutions to resolve this disadvantage (see section 4.3), and the specifications ask for a 20 bit linear ADC, a single bit ADC/DAC combination is the best option for this design.

#### **4.1.1.** Combining coulomb counting and current measurement

Because the final resolution of the sigma delta ADC is determined by the OSR, and the OSR is only determined at the decimation filter, it is possible to have a system which combines the two sigma delta ADC's into one, with a single sigma delta modulator, and two (digital) decimation filters. The first one needs to have a high OSR to be used for the high resolution, slow charge measurements. The second one needs to have a lower OSR and can be used for the faster, lower resolution current measurements.

Because the split between two converters happens so late in the signal chain and the analog part is the same for both converters, it is possible to first design the converter with the stricter requirements and later fit in the requirements of the second converter. As discussed before, the most important converter is the one used for the charge measurement, because it has the most strict offset and timing specifications. Consequently, in the following sections the main focus will lie on the design of the charge converter.

#### **4.2.** Sigma delta design for low offset

Because the result of the charge conversion will be integrated indefinitely, it is very important for the conversion to have extremely low offset, as any offset will result in a increasing error in the integral.

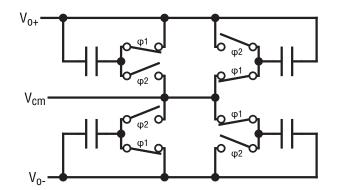

The easiest way to achieve very a low offset circuit is to make use of a switched capacitor circuit in combination with offset cancellation techniques like correlated double sampling (CDS) and block level chopping. These techniques alone are not enough to meet the extreme requirements targeted in this design (section 2.2.1). This is because of residual charge injection. By using system level chopping, however, a sufficiently low offset can be achieved.[7, section III.F]

System level chopping is the technique of chopping the complete circuit from input to output. This is done in a sigma delta converter by doing two complete conversions with opposite input polarity, while also reversing the input of the decimation filter. This is done by including choppers, one directly at the input of the system, and also around all state-holding circuit elements [8][9], like shown in figure 4.2.

#### **4.2.1.** State-holding elements

State-holding circuit elements are elements in the circuit that hold a state. In case of the sigma delta ADC, these elements are the capacitors that hold the analog values of the integrators and the digital

<sup>&</sup>lt;sup>1</sup>The line between two point's is always perfectly linear

Figure 4.2: An example of system level chopping where all state holding elements are chopped.

Figure 4.3: The quantization and thermal noise of a n<sup>th</sup> order sigma delta ADC with an assumed  $f_s$  of 4 MHz.

state of the decimation filter. It is not possible to flip the integrator as a whole circuit element, because by doing so the offset of the integrator itself is not canceled. Because of this, only switches around the state holding elements themselves should be added.

Adding these extra switches in the signal path has the unavoidable side-effect that the two conversions, that should be identical (except for their sign), will have slightly different signal paths. The effect of this is that adding more choppers will increase the residual offset. This effect, combined with the fact that flipping around all state holding capacitors will lead to very complex hardware, drives the search for a different solution to implement system level chopping.

#### **4.2.2.** Incremental conversions

This different solution has been found by resetting all state-holding elements in the converter between input windows, and completely decouple the different input windows from each other. This mode of operation, also known as incremental conversion[10][11][12], ensures a one-to-one input-output relationship between the input windows and the output samples. This means that every input sample only ever effects one output sample. Because the input windows are now completely independent, converting two input windows while flipping the input chopper in between, will result in two output samples which can be subtracted to produce a single output value with a offset only limited by the resolution of the converter[7, section III.F]. When using incremental conversions, however, equally weighting samples gets more challenging.

#### **4.2.3.** Correct integration

In order for the charge measurement to be useful, it should perform correct integration of the input samples (section 2.2.3), meaning all input samples have to be equally weighted. This can be achieved by a very slow anti aliasing filter, by filtering all frequencies higher then half the output sample rate. This filter will, however, interfere with the current measurements, which need to be done at a higher bandwidth.

Another option is to only filter out frequencies higher then half the sampling frequency, and equally

(a) Schematic

(b) Wave forms

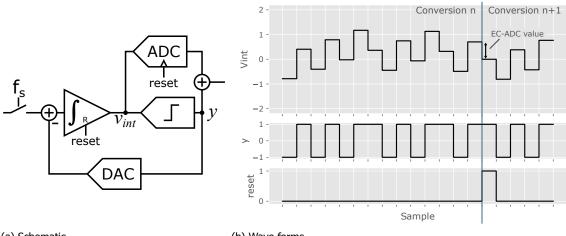

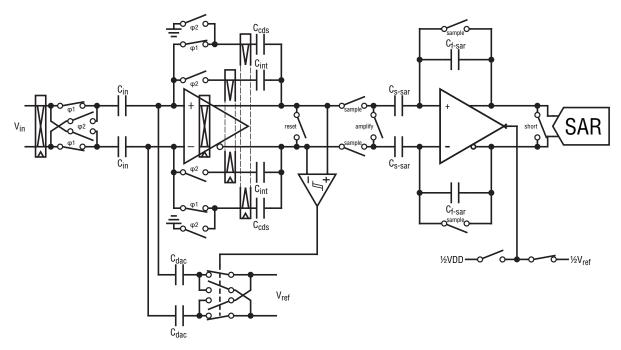

Figure 4.4: Discrete time 1<sup>st</sup> order sigma delta modulator with Extended Counting

*weighting* all samples in constructing the output value. In this way, the integration is partially done by the converter.

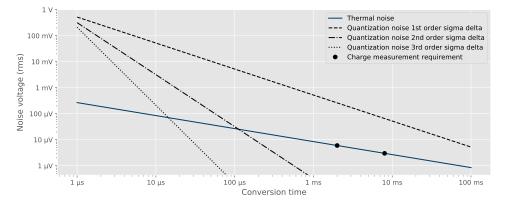

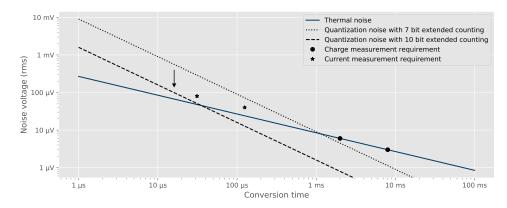

By looking at figure 4.3, it can be concluded that a 2<sup>nd</sup> order sigma delta ADC is necessary, in order reach a thermal noise limited ADC with low enough quantization noise (see table 2.1). Equally weighting samples while doing non-stop incremental conversions however, can only be done by using a first order sigma delta ADC. The reason for this is that higher order sigma delta modulators are only useful in combination with higher order decimation filters. And these higher order decimation filters don't have flat (time domain) responses (like a SINC<sup>1</sup> filter has). This in itself is not a problem, because as long as the higher order SINC filters partially overlap, the overall response will be flat. When using incremental conversions however, it is not possible to partially overlap the samples just before and just after the reset, because they do not share the same integrator states.

So, a incremental sigma delta ADC, with a input bandwidth of half the sampling frequency, can only perform correct integration of the input signal, when using a first order design. This means that 2<sup>nd</sup> order modulator cannot be used in this application, and so, as visible from figure 4.3, another technique is needed to reach the quantization noise level required.

## 4.3. Extended counting

Because a lower level of quantization noise is required, than a first order sigma delta produces, another technique is needed. Looking at the existing circuit, it can be noted that the quantization noise produced by the system is continuously integrated in the integrator. This means that the value in the integrator at the end of a conversion is exactly the quantization error made by the sigma delta ADC!

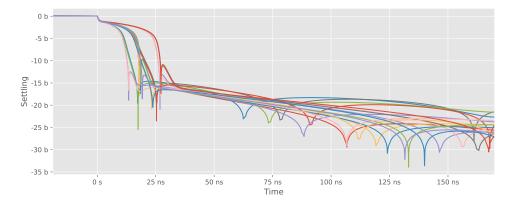

Measuring this integrator value, and using it to correct the output of the sigma delta is known as extended counting (EC)[13][14]. The measurement of the final integrator value just before reset is done by using a secondary ADC (see figure 4.4). With this value measured, it is possible to subtract it from the final result. Accordingly, the quantization noise of the converter can be improved by the difference of resolution between the secondary ADC and the quantizer in the sigma delta modulator.

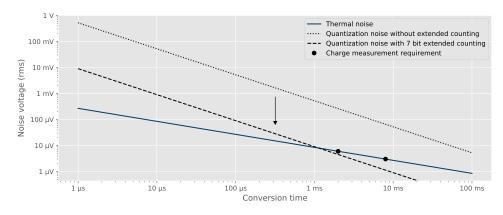

As long as the converter is not yet thermal noise limited, extended counting can thus be used to improve the resolution of the ADC. The effect of adding the extended counting to a first order sigma delta ADC can be seen in figure 4.5.

It should be noted that this technique gives similar improvements to using a multi-bit ADC/DAC combination inside of the sigma-delta modulator, without the challenges of building a linear multi-bit DAC.

In some cases, it is beneficial to combine the circuitry used for the sigma delta modulator for the extended counting ADC[15][16]. This technique cannot be used in this case, however, as the charge measurement must be done continuous. Due to this, the sigma delta circuitry cannot be time multiplexed for secondary use as a extended counting ADC.

#### **4.3.1.** Timing

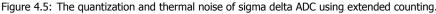

With the introduction of a first order sigma delta modulator, system level chopping and extended counting, it becomes possible to define a timing scheme. The converter runs two consecutive conversions with flipped input polarity to implement system level chopping. Between every conversion, the EC-ADC measures the integrator voltage and the integrator is reset. After these two conversions, the results are subtracted, and the charge measurement is complete. A simple timing diagram of these actions can be found in figure 4.6.

#### 4.3.2. Gain matching

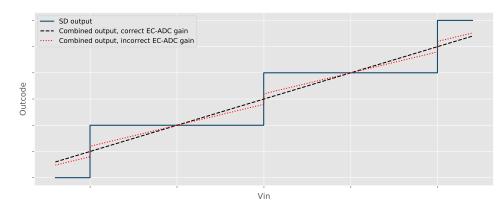

When using extended counting, like shown in figure 4.4a, the output of the total converter will be given by equation (4.1). Here is  $A_{\text{EC-ADC}}$  the relative gain of the EC-ADC. In order to prevent steps in the transfer function around the hand-off of the sigma delta ADC and the EC-ADC, this gain should be well defined. Because  $A_{\text{EC-ADC}}$  might be process dependent (depends on EC-ADC implementation), there can be variations in this factor. because of these variations, a gain trim should be implemented to match the sigma delta ADC and the EC-ADC.

In order to implement a gain trim, it should be taken into account that the resolution of the EC-ADC will also be affected by the gain trim. In order to compensate this, the resolution of the EC-ADC should be around 0.5 bit higher then required by the specifications.

$$ADC(v_{in}) = \sum_{i=-1}^{OSR-1} y[i] + A_{EC-ADC} \cdot EC-ADC(v_{int}[OSR])$$

(4.1)

#### **4.3.3.** Resolution requirements secondary ADC

In order to find the requirements for the secondary ADC that implements the extended counting, the resolution of the sigma delta ADC needs to be known. This is the case because the EC-ADC essentially provides the extra bits of resolution that the sigma delta ADC `misses'.

To calculate what the resolution of the EC-ADC should be with a given OSR, a few effects need to be considered:

1. When using a EC-ADC with the same resolution as the ADC/DAC in the sigma delta ADC, no

Figure 4.7: The hand-off between the sigma delta LSB and the EC-ADC

improvement will be made, only extra bits help. Because the ADC/DAC combination of the sigma delta modulator is 1b, 1b of the EC-ADC is used to match this.

- 2. Every charge conversion requires 2 conversions because of system level chopping (see section 4.3.1). Because of this, the EC-ADC needs another 0.5 bit of resolution.

- Because of the trimming necessity of the gain matching (see section 4.3.2) another 0.5 bits is needed.

In total the resolution of the EC-ADC required by the charge conversion is given by equation (4.2).

## **4.4.** Adding the current measurement

With the addition of the EC-ADC, a feasible system for the charge measurement is conceived. This can be seen as taking a single point measurement on the combined thermal-noise and quantization noise line from figure 4.5. The next step in the design of the multi-path ADC is to add in the current conversion. This is equivalent to making a second single point measurement on the same line simultaneously. Theoretically this should be possible just by adding a second decimation filter with a different OSR. The difficult question however, is how to do this in a system with extended counting and system level copping.

The first step is to match the extended counting technique to the current measurement, where the OSR is reduced. Additional to the reduced OSR, there is another difference with the charge measurement: in the case of the current measurement, the state of the integrator is unknown at the start and the end of the measurement, because the fast measurement starts in the middle of a charge measurement. To resolve this, the EC-ADC is run twice, once at the start, and once at the end of the current conversion. The transfer of this current conversion started at sample n is now given by equation (4.3).

$$I-ADC(v_{in},n) = \sum_{i=n}^{n+I-OSR} y[i] + A_{EC-ADC} [EC-ADC(v_{int}[n+I-OSR+1]) - EC-ADC(v_{int}[n])]$$

(4.3)

#### 4.4.1. Combined timing

In order to assure that the current measurement does not interfere with the charge measurement, but still can start at any moment in the charge conversion cycle, a more complicated timing scheme is needed.

Starting from figure 4.6, adding the fast current measurement seems quite simple: add a EC-ADC measurement to the begin and end of the current measurement. But because the current conversion is asynchronous with the charge conversion, there are four possible scenarios for the current measurement (also shown graphically in figures 4.8a to 4.8d):

#### 4.5. Other considerations

| System level chop                                | System level chop                                |

|--------------------------------------------------|--------------------------------------------------|

| IΣΔ reset                                        | ΙΣΔ reset                                        |

| EC-ADC running                                   | EC-ADC running                                   |

| Charge conversion complete                       | Charge conversion                                |

| Current measurement                              | <br>Current measurement                          |

| (a) The timing of a current measurement (case 1) | (b) The timing of a current measurement (case 2) |

| System level chop                                | System level chop                                |

| IΣΔ reset                                        | IΣΔ reset                                        |

| EC-ADC running                                   | EC-ADC running                                   |

| Charge conversion complete                       | Charge conversion                                |

| Current measurement                              | <br>Current measurement                          |

| (c) The timing of a current measurement (case 3) | (d) The timing of a current measurement (case 4) |

Figure 4.8: Timing diagrams showing the possible different cases for the current measurement

- 1. The current conversion occurs in the middle of a charge conversion.

- 2. The end of the current conversion overlaps with the reset of the integrator.

- 3. The current conversion starts just after the reset of the integrator.

- 4. The current conversion overlaps with the reset of the integrator.

In the first case the only thing that needs to happen is to add the EC-ADC measurements at the beginning and the end of the current conversion. In the second case, the second EC-ADC measurement overlaps with the measurement that was going to be done for the charge measurement. Because there is nothing different between the two measurements, the result can just be shared. The third case seems the easiest case: the integrator starts from a known (reset) state, so only the EC-ADC measurement at the end of the conversion is needed. While this is correct, any offset in the EC-ADC will not be canceled in this case, to fix this, a shorted input measurement of the EC-ADC is subtracted from the result. The forth case is quite clearly the most complicated case. In order to correctly measure the current when a integrator reset is taking place, the conversion is broken up into two pieces. The first part of the conversion is done as in case 2, and the second part of the conversion is done as case 3. Because of this, there will be 4 EC-ADC <sup>2</sup> conversions done in this case, this means the quantization noise of this case will be  $\sqrt{2} \times$  higher than in the other three cases.

## 4.5. Other considerations

There are a couple of other considerations to look into.

#### 4.5.1. Current conversion quantization noise

After adding the current conversion to the ADC, its resolution will be quantization noise limited. This means that it is relatively power efficient to increase the resolution. In this case, this even needs to be done in order to meet the requirements from table 2.2. To decrease the quantization noise the required amount, the resolution of the EC-ADC is increased. This is shown in figure 4.9.

#### 4.5.2. Digital decimation filter and gain matching

In order to calculate the out-code for a conversion, the gain of the EC-ADC needs to be matched to the gain of the sigma delta ADC to avoid DNL errors (see section 4.3.2). In order to match the two results, there are two possibilities.

<sup>&</sup>lt;sup>2</sup>the 3 from figure 4.8d plus a shorted input measurement

Figure 4.9: The quantization and thermal noise of sigma delta ADC, including the current conversion specifications

- 1. Adjust the gain of the EC-ADC to the gain of the sigma delta ADC by multiplying the result of the EC-ADC by  $A_{\text{EC-ADC}}$ . This approach is taken in equations (4.1) and (4.3).

- 2. Adjust the gain of the sigma delta ADC to the gain of the EC-ADC by changing the weights of the bit-stream from 1 to  $\frac{1}{A_{\rm EC-ADC}}$ .

Option 1 requires a (expensive) digital multiplier, while option 2 only needs an adder. But, option 2 adjusts the gain of the complete system (which is very stable due to the 1 bit DAC) to the gain of the EC-ADC.

In the intended application, however, the gain of the total system will need to be trimmed anyway, because the value of the sense resistor can vary. This trim will be done by adjusting the reference voltage going to the ADC. This affects both the sigma-delta ADC as the EC-ADC. When this is the case, it is not a problem anymore to adjust the gain of the system to the gain of the EC-ADC. Because of this, option 2 is the better option for this design. Equation (4.4) shows the transfer of the ADC using option 2.

$$ADC'(v_{in}) = \sum_{i=-1}^{OSR-1} \left( \frac{1}{A_{EC-ADC}} \cdot y[i] \right) + EC-ADC(v_{int}[OSR])$$

(4.4)

#### 4.5.3. Speed

The speed of the EC-ADC can be split into two independent requirements: the sampling speed and the conversion speed.

The requirement for the sampling speed is set by the speed of the sigma delta modulator. This is because the EC-ADC needs to sample the integrator signal of the sigma delta modulator, at one specific sample. In order for this sampling to be correct, the sampling speed of the EC-ADC should match the sampling speed of the sigma delta loop.

The conversion time of the EC-ADC however, determines the maximum delay time between the external trigger and the start of the current conversion. This is because the EC-ADC can not run two conversions at the same time. This means that the current conversion cannot be started if it would cause two EC-ADC conversions of the charge and current conversion to partially overlap. If they fully overlap, there is no problem, as the conversion result can be shared (case 2 in section 4.4.1). Because all EC-ADC conversions for the charge conversion are done according to a pre-determined schedule, it is possible to schedule all current conversions with a maximum delay of  $T_{conv,EC-ADC}$  without any EC-ADC collisions. As the maximum variation in conversion start is 1 µs (see table 2.2), the maximum conversion time of the EC-ADC is 1 µs.

#### **4.5.4.** Integrator leakage

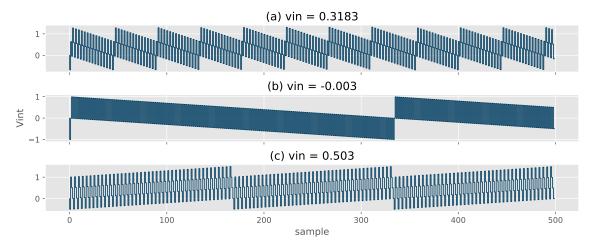

One of the main weaknesses of first order sigma delta ADC's is their sensitivity to integrator leakage, especially when using a single bit DAC. This is caused by the fact that in a first order sigma delta ADC with a single bit DAC, the quantization noise cannot be seen as random, because it is heavily correlated

Figure 4.10: The sigma delta modulator as described by equations (4.5) and (4.6)

with the signal. With integrator leakage, this correlation can cause so called limit cycles. Limit cycles are cycles in which a relatively short pattern in the bit-stream is repeated continuously, caused by (near) integer relations between the input voltage and the reference voltage.

In other applications (for example audio), the main problem of these limit cycles is that they cause spurious tones that must be suppressed by the decimation filter. In this application, however, spurious tones are not a problem, because the signal gets integrated, and the integral of the signal stays the same, regardless of the spurious tones.

Limit cycles do have another effect, however: because the same signal continuously repeats, and the quantization noise is correlated with the input signal, the quantization noise in the loop is no longer zero on average. While this quantization error slowly accumulates, it leaks away through the integrator, which causes dead-zones. This effect can been seen from equation (4.5), the main equation of the 1<sup>st</sup> order sigma delta modulator. In this equation  $v_{in}$  is the modulator input voltage,  $v_{int}$  is the integrator output voltage, y[n] is the bit stream at sample n and p is the leakage factor of the integrator (see figure 4.10).

$$v_{int}[n] = \sum_{i=0}^{n} \left( v_{in}[i] - v_{ref} \cdot y[i-1] - p \cdot v_{int}[i-1] \right)$$

(4.5)

When rewritten as equation (4.7), it is clear how the modulator works as converter. As long as  $v_{int}[n]$  is bounded (which it is for a stable converter), and p is very small (near perfect integrator), the sum of the bit stream is a good approximation of the sum of the input voltage. It is also important to note the value's y[-1] and  $v_{int}[-1]$  are the reset values of y and  $v_{int}$ .

$$v_{ref} \sum_{i=-1}^{n-1} y[i] = \sum_{i=0}^{n} v_{in}[i] - p \sum_{i=-1}^{n-1} v_{int}[i] - v_{int}[n]$$

(4.6)

$$\underbrace{v_{ref} \sum_{i=-1}^{\text{OSR}-1} y[i]}_{\text{SD result}} + \underbrace{v_{int}[\text{OSR}]}_{\text{EC result}} = \overline{v_{in}} - p \cdot \overline{v_{int}}$$

(4.7)

If the leakage factor of the integrator is not zero, the output of the integrator will be a term in the equation. As long as the modulator is not in a limit cycle, the output of the integrator will be the input signal plus a noise shaped high frequency signal. This means the mean value of the signal is proportional to the input voltage. Because of this, leakage will cause a gain error as long as the modulator does not hit any limit cycles. When the modulator approaches a limit cycle, however, there can be a low frequency component in  $v_{int}$ , as shown in figure 4.11. If the leakage of the integrator will 'snap' to simple fractions  $(\frac{1}{2}, \frac{1}{4}, \text{ etc.})$  of the full scale, causing the limit cycle. Because the output of the modulator will snap to these fractions as well, it causes non-linearity's known as dead-zones around simple fractions of the full scale.

To prevent this issue, the leakage of the integrator should be small. The maximum leakage is determined by the maximum permitted dead-zone. For the case of a 20b ADC (table 2.1) without a visible dead-zone, the maximum permissible leakage is calculated by equations (4.8) to (4.10). The

Figure 4.11: The effect of limit cycles on the integrator voltage.

Table 4.1: A table comparing the different possible sampling frequencies and their corresponding OSR, minimum resolution EC-ADC for the Charge ADC and the Current ADC

|                      | Char            | ge ADC                   | Current ADC     |                          |  |

|----------------------|-----------------|--------------------------|-----------------|--------------------------|--|

| Fs<br>[ <i>MHz</i> ] | OSR             | EC-ADC<br>[ <i>bit</i> ] | OSR             | EC-ADC<br>[ <i>bit</i> ] |  |

| 0.256                | 211             | 11                       | 2 <sup>5</sup>  | 13.5                     |  |

| 0.512                | 2 <sup>12</sup> | 10                       | 2 <sup>6</sup>  | 12.5                     |  |

| 1.02                 | 2 <sup>13</sup> | 9                        | 2 <sup>7</sup>  | 11.5                     |  |

| 2.05                 | 2 <sup>14</sup> | 8                        | 2 <sup>8</sup>  | 10.5                     |  |

| 4.10                 | 2 <sup>15</sup> | 7                        | 2 <sup>9</sup>  | 9.5                      |  |

| 8.19                 | 2 <sup>16</sup> | 6                        | 2 <sup>10</sup> | 8.5                      |  |

| 16.4                 | 2 <sup>17</sup> | 5                        | 2 <sup>11</sup> | 7.5                      |  |

| 32.8                 | 2 <sup>18</sup> | 4                        | 2 <sup>12</sup> | 6.5                      |  |

| 65.5                 | 2 <sup>19</sup> | 3                        | 2 <sup>13</sup> | 5.5                      |  |

maximum value of  $e_{mean}$ , the difference between  $\overline{v_{in}}$  and  $\overline{v_{int}}$  is  $\frac{1}{2}$  of the input full scale. This is the case at 0 input, when the  $v_{int}$  swings between plus and minus  $v_{ref}^{3}$ .

$$e_{leak} = p \cdot \overline{v_{int}} = p \cdot (\overbrace{v_{in}}^{\text{gain error}} + \overbrace{e_{mean}}^{\text{non-linear}}) \le p \cdot (\overline{v_{in}} \pm \frac{1}{2}v_{fs})$$

(4.8)

$$e_{leak,non-linear} = p \cdot \frac{1}{2} v_{fs} \le \frac{1}{2} \text{LSB} = \frac{1}{2} \cdot 2^{-20} \cdot v_{fs}$$

(4.9)

$$p \le 2^{-20}$$

(4.10)

### **4.6.** Oversampling rate

With the architecture of the converter determined, the oversampling rate (OSR) can be determined. The OSR is the ratio between the sampling rate of the sigma delta modulator, and the output sample rate. Because the output sample rate is fixed by the specifications, the OSR is completely determined by the sampling rate of the sigma delta.

A main factor in determining the OSR is the distribution of quantization noise between the sigma delta converter and the EC-ADC. In order to determine the optimal OSR, different sampling rates are compared. With the information from tables 2.1 and 2.2, it is possible to generate table 4.1.

<sup>&</sup>lt;sup>3</sup>All these calculations are done with an integrator and a DAC gain of 1, this means the input full scale  $v_{fs} = v_{ref}$ . The conclusion of these equations is, however, independent of these gains.

From table 4.1 it is now possible to select an appropriate sampling frequency. In order to choose between the different versions, a few selection criteria are chosen.

- 1. Because a very high speed design is not desired, the maximum sampling frequency is chosen to be 10 MHz.

- 2. In order to not go to extremes for the EC-ADC, the maximum EC-ADC resolution is chosen to be 10 bit, as it is relatively straightforward to achieve this level of linearity by only relying on capacitor matching, and not on trimming, calibration or other error correction schemes.

After applying these selection criteria, two possible sampling frequencies remain: 4.1 MHz and 8.2 MHz. Initially, a sampling rate of 8.2 MHz was chosen, but due to process options, the final sampling rate of the system is 4.1 MHz (for more information see appendix B.2). For the EC-ADC, a resolution of 10 bit is chosen.

5

# Circuit level Design

In this chapter, a circuit level design, based on the system level design in chapter 4 and the specifications from chapter 2, will be made. First, the sigma delta modulator will be designed, after which the EC-ADC is designed, and finally some timing generation circuitry is discussed.

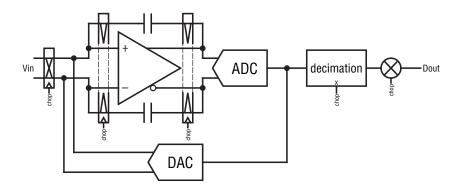

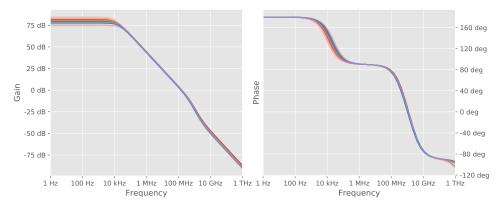

## **5.1.** Sigma delta modulator

The block level of the sigma delta modulator as described in chapter 4, will be implemented using a switched capacitor integration scheme. The goal of this section is to design a delta sigma modulator which is as small and power efficient as possible, while still meeting the noise, leakage and offset requirements. The first thing to look at is the switching scheme of the integrator, as this determines many of the other factors of the design.

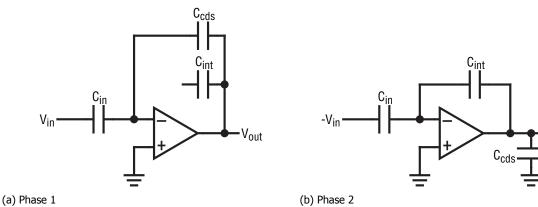

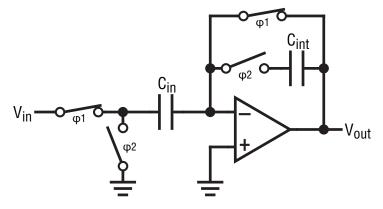

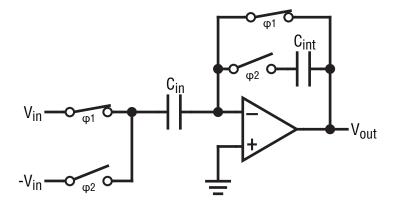

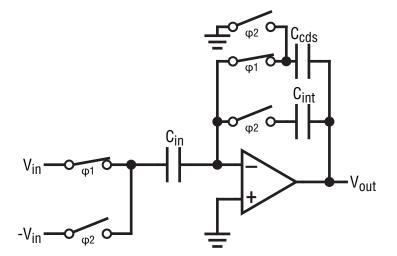

## **5.1.1.** Integrator switching scheme

One of the most strict requirements that need to be fulfilled is the leakage requirement of the integrator calculated in section 4.5.4, equation (4.10). Consider the case of a typical switched-capacitor integrator, as depicted in figure 5.1a. In this system, the DC gain of the amplifier used needs to be quite high, as shown by equation (5.3), in which *G* is the gain of the integrator<sup>1</sup>, *A* is the DC gain of the amplifier used to implement the integrator and  $V_{os}$  is the offset voltage of the amplifier.

$$V_{int}[n] \approx G\left(-V_{os} + V_{in}[n] + \frac{V_{out}[n-1]}{A}\right) + V_{int}[n-1]$$

(App. C.2) (5.1)

$$p \approx \frac{G}{A} \tag{A \gg 1} \tag{5.2}$$

$$A \ge \frac{G}{p} = \frac{G}{2^{-20}} = G_{dB} + 120.4 \, dB \tag{5.3}$$

The first issue with this basic switching scheme is that the offset voltage of the amplifier is directly integrated. And while system level chopping is implemented for the charge measurement, it is not helping to reduce the offset in the current measurement. In order to prevent this, a auto zeroing switching scheme can be used, as shown in figure 5.1b. In this switching scheme, the sampling capacitor samples the offset voltage in both phases, and in this manner, prevent the offset from getting integrated.

Another issue is that with reasonable values for G (-15 - 0dB), a DC gain of at least 105 dB is needed. To get to this level of DC gain, either a two stage amplifier or gain-boosting is required. While this is not a big issue, a solution is available.

To improve the leakage characteristics of the integrator, the scheme shown in figure 5.1c is used. This is a variation on the finite gain compensation scheme in [17, figures 30 and 31]. The main advantage of using this switching scheme is that the leakage of the integrator is now proportional to the squared gain of the op-amp (appendix C.5).

$${}^{1}V_{int}[n] = V_{int}[n-1] + G \cdot V_{in}[n]$$

Vout

(a) Simple switching scheme

(b) Simple auto zeroing switching scheme (c) Auto zeroing and finite gain compensation with double sampling

Figure 5.1: Switched capacitor integrators

Figure 5.2: The two phases of the finite gain compensating integrator.

## Finite gain compensation scheme

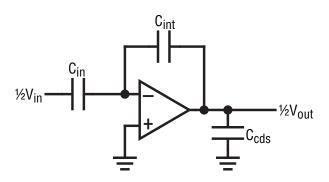

The working of the finite gain compensation scheme from figure 5.1c is based on first stepping the output of the integrator in the opposite direction using  $C_{cds}$  in  $\phi_1$ , and sampling the step at the virtual ground produced by this output step. After this, in  $\phi_2$ ,  $C_{int}$  is connected again, and this time, the output steps in the correct direction. Because the step produced at the virtual ground is already added to the signal in  $\phi_1$ , the overall effect is that the error produced by the finite gain of the amplifier is suppressed by another factor *A*. This can also been seen in mathematical form in equations (5.4) to (5.28).

$\phi_0$  is defined as the final state of the previous  $\phi_2$  phase:

$$V_{vg}[\phi_0] = -\frac{V_{out}[\phi_0]}{A} + V_{os}$$

(5.4)

$$V_{C_{in}}[\phi_0] = V_{vg}[\phi_0] + V_{in}[\phi_0]$$

(5.5)

$$V_{C_{int}}[\phi_0] = V_{vg}[\phi_0] + V_{in}[\phi_0]$$

(5.6)

$$V_{C_{cds}}[\phi_0] = V_{out}[\phi_0]$$

(5.7)

Now the equations for the transition to  $\phi_1$  can be set up (see figure 5.2a):

$$V_{vg}[\phi_1] = -\frac{V_{out}[\phi_1]}{A} + V_{os}$$

(5.8)

$$V_{C_{in}}[\phi_1] = V_{vg}[\phi_1] - V_{in}[\phi_1]$$

(5.9)

$$V_{C_{int}}[\phi_1] = V_{C_{int}}[\phi_0]$$

(5.10)

$$V_{C_{cds}}[\phi_1] = V_{out}[\phi_1] - V_{vg}[\phi_1]$$

(5.11)

$$C_{in}(V_{c_{in}}[\phi_1] - V_{c_{in}}[\phi_0]) = C_{cds}(V_{c_{cds}}[\phi_1] - V_{c_{cds}}[\phi_0])$$

(5.12)

Solving for  $V_{out}[\phi_1]$  gives the output voltage at the end of  $\phi_1$ :

$$V_{out}[\phi_1] = \frac{A(C_{cds}(V_{os} + V_{out}[\phi_0]) - C_{in}(V_{in}[\phi_0] + V_{in}[\phi_1])) + C_{in}V_{out}[\phi_0]}{C_{cds}(A+1) + C_{in}}$$

(5.13)

$$V_{out}[\phi_1] \approx V_{out}[\phi_0] + V_{os} - \frac{C_{in}}{C_{cds}}(V_{in}[\phi_0] + V_{in}[\phi_1]) + \frac{C_{in}}{C_{cds}A}V_{out}[\phi_0]$$

(A » 1) (5.14)

As the output voltage changes due to the sampling of the input voltage on  $C_{in}$ , two things happen in equation (5.14): first, the offset voltage is added to the output, such that it will not be sampled when  $C_{int}$  is connected; and second, the leakage from  $\phi_0$  due to the difference in output voltage is added to the output. This means that when  $C_{int}$  is connected again, this leakage will be sampled by  $C_{int}$ , but because the step in  $\phi_1$  is of opposite polarity as in  $\phi_2$ , the leakage component will be canceled out.

Similarly  $\phi_2$  looks as follows (see figure 5.2b):

$$V_{vg}[\phi_2] = -\frac{V_{out}[\phi_2]}{A} + V_{os}$$

(5.15)

$$V_{C_{in}}[\phi_2] = V_{vg}[\phi_2] + V_{in}[\phi_2]$$

(5.16)

$$V_{C_{int}}[\phi_2] = V_{out}[\phi_2] - V_{vg}[\phi_2]$$

(5.17)

$$V_{C_{ods}}[\phi_2] = V_{out}[\phi_2] \tag{5.18}$$

$$C_{in}(V_{C_{in}}[\phi_2] - V_{C_{in}}[\phi_1]) = C_{int}(V_{C_{int}}[\phi_2] - V_{C_{int}}[\phi_1])$$

(5.19)

Next, the equations are rewritten in terms of the samples n - 1 and n:

$$V_{C_{int}}[\phi_0] = V_{int}[n-1]$$

(5.20)

$$V_{C_{int}}[\phi_2] = V_{int}[n]$$

(5.21)

$$V_{in}[\phi_0] = V_{in}[n-1]$$

(5.22)

$$V_{in}[\phi_1] = V_{in}[\phi_2] = V_{in}[n]$$

(5.23)

Now the integrated voltage can be calculated (see also appendix C.5):

$$V_{int}[n] = G'\left(V_{in}[n] + \frac{1}{A}\left(\frac{V_{os}}{2} + V_{in}[n] - \frac{C_{in}V_{in}[n-1]}{2C_{cds}} + \frac{C_{in}V_{in}[n]}{2C_{cds}}\right) - \frac{V_{out}[n-1]}{2A^2}\right) + V_{int}[n-1]$$

(5.24)

$$G' \approx 2 \frac{C_{in}}{C_{int}}$$

(A >> 1) (5.25)

$$p \approx \frac{G}{2A^2} \qquad (A \gg 1) \quad (5.26)$$

$$A \ge \sqrt{\frac{G'}{2p}} = \sqrt{\frac{G'}{2 \cdot 2^{-20}}} = \frac{1}{2}G'_{dB} + 57.2 \, dB \tag{5.27}$$

$$V_{os} = \frac{V_{os,amp}}{2A}$$

(5.28)

From the resulting equation (5.24) is is visible that indeed the leakage ( $V_{out}[n-1]$ ) is suppressed by a factor  $\frac{1}{A^2}$ . Note that these equations assume *A* is constant over both phases. The consequences of this assumption will be discussed further in section 7.4.2.

## Double sampling

Another technique that is added to this switching scheme is double sampling[18]. This technique works by connecting the input capacitor to  $-V_{in}$  instead of to signal ground in  $\phi_2$ . This is easy to accomplish in a fully differential implementation. The effect of this double sampling is that the signal charge going into the integrator is doubled for the same amount of noise. This technique thus improves the signal to noise ratio for a given  $C_{in}$  (or gives a smaller  $C_{in}$  for a given SNR).

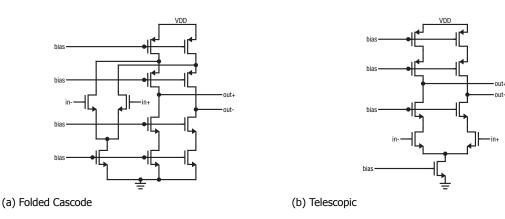

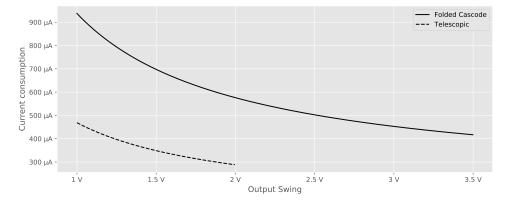

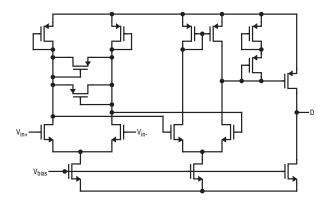

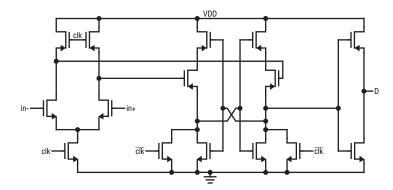

Figure 5.3: Two common OTA architectures

## 5.1.2. Thermal noise

With the OSR and the switching scheme determined, it is possible to calculate the capacitor sizes needed to achieve low enough thermal noise levels. A main factor in determining the capacitor size requirements is the OSR. This is important because bigger OSR's reduce the thermal noise by integrating. Taking this into account, the thermal noise produced by the switching scheme shown from section 5.1.1, can be estimated.