# **Conducted EMI in Inverters** with SiC Transistors

# **Conducted EMI in Inverters** with SiC Transistors

Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen op maandag 11 maart 2013 om 15.00 uur door

Xun GONG

Control Theory and Control Engineering Dalian University of Technology, China geboren te Panjin City, China. Dit proefschrift is goedgekeurd door de promotor: Prof. dr. J.A. Ferreira

Samenstelling promotiecommissie:

| Rector Magnificus             | voorzitter, Technische Universiteit Delft |

|-------------------------------|-------------------------------------------|

| Prof. dr. J.A. Ferreira       | Technische Universiteit Delft, promotor   |

| Prof. dr. ing. P. Mattavelli  | University of Padova                      |

| Prof. dr. M. Zeman            | Technische Universiteit Delft             |

| Prof. dr. ir. F.B.J. Leferink | Universiteit Twente                       |

| Prof. ir. L. Van der Sluis    | Technische Universiteit Delft             |

| Ir. S.W.H. de Haan            | Technische Universiteit Delft             |

| Prof. dr. A. Neto             | Technische Universiteit Delft             |

|                               |                                           |

Cover designed by Xiangxiang Dang Cover photo by CNPENTAX

Copyright © 2013 by Xun Gong

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without the prior permission of the author.

ISBN 978-90-6562-317-1

To my parents: Zhenju Gong and Liangjun Yi

# Abbreviations

| 2D      | Two Dimensional                                          |

|---------|----------------------------------------------------------|

| 3D      | Three Dimensional                                        |

| AC      | Alternating Current                                      |

| Av      | Average detector                                         |

| AMN     | Artificial Mains Network                                 |

| AZSPWM  | Active Zero State Pulse Width Modulation                 |

| CENELEC | European Committee for Electro-technical Standardization |

| CISPR   | International Special Committee on Radio Interference    |

| СМ      | Common mode                                              |

| СМС     | Common Mode Choke                                        |

| CSI     | Current Source Inverter                                  |

| DC      | Direct Current                                           |

| DM      | Differential Mode                                        |

| DPWM    | Discontinuous Pulse Width Modulation                     |

| DSP     | Digital Signal Processor                                 |

| EMC     | Electromagnetic Compatibility                            |

| EMI     | Electromagnetic Interference                             |

| EPC     | Equivalent Parallel Capacitance                          |

| EPR     | Equivalent Parallel Resistance                           |

| ESL     | Equivalent Series Inductance                             |

| ESR     | Equivalent Series Resistance                             |

| ETSI    | European Telecommunications Standards Institute          |

| EUT     | Equipment Under Test                                     |

| FCC     | Federal Communications Commission                        |

| FFT     | Fast Fourier Transform                                   |

|         |                                                          |

| GaN    | Gallium Nitride                                   |

|--------|---------------------------------------------------|

| IC     | Integrated Circuit                                |

| IEC    | International Electromechanical Commission        |

| IGBT   | Insulated Gate Bipolar Transistor                 |

| IMS    | Insulated Metal Substrate                         |

| JFET   | Junction Field Effect Transistor                  |

| JBS    | Junction Barrier Schottky                         |

| LISN   | Line Impedance Stabilization Network              |

| MM     | Mixed Mode                                        |

| MOSFET | Metal oxide Semiconductor Field Effect Transistor |

| NSPWM  | Near State Pulse Width Modulation                 |

| РСВ    | Printed Circuit Board                             |

| PE     | Protective Earth                                  |

| PFC    | Power Factor Corrector                            |

| Pk     | Peak Detector                                     |

| PWM    | Pulse Width Modulation                            |

| RFI    | Radio Frequency Interference                      |

| Si     | Silicon                                           |

| SiC    | Silicon Carbide                                   |

| SMT    | Surface Mount Technology                          |

| PWM    | Pulse Width Modulation                            |

| TDR    | Time Domain Refectometry                          |

| THD    | Total Harmonic Distortion                         |

| THT    | Through Hole Technology                           |

| VSD    | Variable Speed Drive                              |

| VSI    | Voltage Source Inverter                           |

# Acknowledgments

Actually I had never expected to own a doctoral degree during the 19 years of study. In February, 2008 I was accepted as a PhD student by Electrical Power Processing (EPP) group of TU Delft, the Netherlands. It was such a surprise to me that I can not wait to share this news with my parents. In my childhood, my parents were always alerting me: be diligent, save time and study hard, otherwise I can not even pass the entrance examination to the universities. Looking back upon, although it was a painful experience that I started studying when I was very little, all these efforts become the foundation stone to my success. My parents' words that were used to making me anxious become the encouragements and motivations, driving me forward all the time.

Today, looking back the last four years that enriched me the most significant than any other period of my life, I would like to express my deeply gratitude to many people that I was fortunate to be acquainted with, to be accompanied and to be cooperated. Thanks to god's favor and diligent arrangement, without them I could never make any of these things happen.

Firstly, I would like to thank my promoter, Professor Braham Ferreira, who trusted me and gave me this change to do my Ph.D. It is my great honor and fortune to have him as both of my promoter and weekly supervisor. His brilliant guidance, broad horizon, precise attitude, excellent humor sense, the spirit of self-sacrifice, profound knowledge, support and encourage me to be able to continue and finish my Ph.D.

To my senior college, Dongsheng Zhao, I am so grateful for helping me with any kind of problem at the beginning stage of my research, from teaching me every aspect of EMC knowledge, doing all kinds of EMC tests in EPP lab, to showing me where to go to repair my broken bicycle.

I would like to thank Xuefei Mei, who is my wife now and Mingliang Li, my true friend. I was so lucky to travel with them with the same plane when coming to the Netherlands. Without their accompanist and encouragement, my starting stage would be very difficult. They took care of me like a family therefore I can adapt quickly and enjoy life in this very new environment.

I would like to thank Rob Schoevaars, who taught me how to design and build hardware of my setups. Without his help, it would be difficult to make any experiments happen.

I would like to thank Frans Pansier, who gave me very valuable ideas to guide and analyze my experimental results. His profound knowledge, great tolerance and encouraging smiles have always been me driving force.

I would like to thank Ivan Josifovic, who improved my power electronics skills greatly and spent many weeks in the lab to do EMC measurements with me. Without his great ideas and technical discussions, I would have never been able to achieve valuable experimental results and such number of scientific publications.

I would like to thank my officemates Rodrigo Teixeira Pinto, Todor Todorcevic and Dr. Yi Zhou. It was so great to share an office with them. Their sharing, e.g. stories in daily life, news, philosophies, was always interesting and inspiring.

I would like to thank Dr. Bart Roodenburg for translating the propositions and summary into Dutch.

I would like to thank staff members in the EPP group, Professor dr. Paul Bauer, Ir. Sjoerd de Haan, Dr. Henk Polinder, and Dr. Jelena Popovic, for sharing their technical knowledge and lectures.

I would like to thank my doctoral examination committee, Prof. Paolo Mattavelli, Prof. Frank Leferink, Prof. Van der Sluis, Prof. Miro Zeman, Prof. Andrea Neto and Ir. Sjoerd de Haan for spending long time in reading my draft thesis and giving valuable comments and suggestions.

I would like to thank other Chinese colleges in my group, Dr. Zhihui Yuan, Yi Wang, Wenbo Wang, Yeh Ting, Jianing Wang, Jinku Hu, and Dong liu, for helping me overcome any kind of problem in my daily life. In addition, it was super enjoyable to do sports, having lunch, and dining out with them.

Thanks so much to my colleges and ex-colleges in the EPP group. It was my great honor to work with such many talented and diligent young researchers: Deok-Je Bang, Aleksandar Borisavljevic, Balazs Czech, Frank van der Pijl, Rick van Kessel, Johan Wolmarans, Milos Acanski, Silvio Fragoso Rodrigues, Ghanshyam Shrestha, Anoop Jassal, Martin van der Geest, Samuel Ani, Hung Vu Xuan, Prasanth Venugopal, Marcelo Gutierrez-Alcaraz, Dalibor Cvoric, Swagat Chopra, Wim van der Merwe, Emile Brink, and Ilija Pecelj. We were meeting and talking during lunch, coffee time, in the office and corridor, going out for BBQs, Carting and many group activities. Thanks for giving me so much support and making my Ph.D. time so enjoyable.

I would like to thank Xiangxiang Dang for designing such a beautiful thesis cover under the tight schedule.

I would like to thank many friends for their great friendship and support, especially to Zhan Zhang, Xu Jiang, Xuhong Qiang, Zhichao Tan, Yue Xiao, Lin Liu, Mingzhong Zhang, Haiyang Cui, Ran An, Tingting Jiang, Fan Li, Hua Zhong, Junchao Shi, Qian Ke, Zijin Xu, Lu Wang, Wei Meng, Shuzheng Wang, Yunqian Wang, Huayang Cai, Bishuang Chen, Xiaoyu Zhang, and Haiqiang Wang.

Finally yet importantly, I would like to thank my wife Xuefei Mei and my parents, Zhenju Gong and Liangjun Yi, for their diligent taking care and strong-minded support of my life. Their magnanimity, dedication and tolerance are always my motivation and driving me forward.

Xun Gong

# Contents

| Abbrevia | ations                                                              | i   |

|----------|---------------------------------------------------------------------|-----|

| Acknowl  | edgments                                                            | iii |

| Contents | 3                                                                   | i   |

| -        | 1<br>uction                                                         |     |

| 1.1      | Background                                                          | 1   |

| 1.2      | Research target and EMC challenges                                  |     |

| 1.2      |                                                                     |     |

| 1.2.2    |                                                                     |     |

| 1.2.3    | •                                                                   |     |

| 1.2.     |                                                                     |     |

| Si       | iC power devices – faster switching but increased EMI               |     |

|          | igher integration levels – small filters and increased EMI coupling |     |

| 1.3      | Problem description and thesis objectives                           |     |

| 1.3.1    | 1 5                                                                 |     |

| In       | creased EMI due to the use of SiC devices                           |     |

|          | omplicated coupling paths and the role of parasitics                |     |

|          | Iore sensitive EMI receptors                                        |     |

| 1.3.2    | 1                                                                   |     |

| 1.4      | Research method                                                     |     |

| 1.5      | Thesis layout                                                       |     |

| -        | 2                                                                   |     |

| Condu    | icted EMC Strategies for Variable Speed Drive Systems               | 11  |

| 2.1      | Introduction                                                        | 11  |

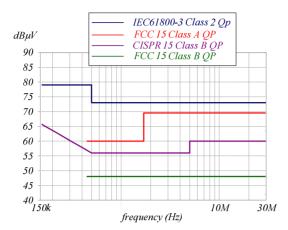

| 2.2      | Standards for conducted emission                                    | 12  |

| St       | tandard for VSD                                                     | 12  |

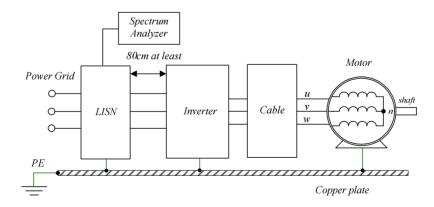

| Μ        | leasurement for VSD                                                 | 13  |

| 2.3                                                                                                                                                            | EMI generation and propagation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 2.3.1.                                                                                                                                                         | EMI propagation mechanisms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14                                                                                           |

| 2.3.2.                                                                                                                                                         | Noise emission at input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16                                                                                           |

| 2.3.3.                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

| DN                                                                                                                                                             | 1 propagation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18                                                                                           |

|                                                                                                                                                                | I propagation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

| 2.4                                                                                                                                                            | Review of suppression strategies along noise coupling path                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |

| 2.4.1.                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

|                                                                                                                                                                | nt stage filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

|                                                                                                                                                                | put filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |

| 2.4.2.                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

|                                                                                                                                                                | utral grounding configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

|                                                                                                                                                                | ounding of VSDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 2.4.3.                                                                                                                                                         | 1 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                              |

| 2.5                                                                                                                                                            | Review of suppression techniques at the EMI source                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                              |

| 2.5.1.                                                                                                                                                         | Optimization of circuit design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

| 2.5.2.                                                                                                                                                         | 6 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| 2.5.3.                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

| 2.5.4.                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 2.5.5.                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 2.5.6.                                                                                                                                                         | Other methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

| 2.6                                                                                                                                                            | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37                                                                                           |

|                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20                                                                                           |

| -                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

|                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| System                                                                                                                                                         | Equivalent Circuit Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39                                                                                           |

| -                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 3.1                                                                                                                                                            | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39                                                                                           |

| 3.1<br>3.2                                                                                                                                                     | Introduction<br>Modeling of Conducted Emission Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39<br>40                                                                                     |

| 3.1<br>3.2<br>3.2.1                                                                                                                                            | Introduction<br>Modeling of Conducted Emission Environment<br>LISN                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 39<br>40<br>40                                                                               |

| 3.1<br>3.2<br>3.2.1<br>3.2.2                                                                                                                                   | Introduction<br>Modeling of Conducted Emission Environment<br>LISN<br>Power Cables                                                                                                                                                                                                                                                                                                                                                                                                                                     | 39<br>40<br>40<br>42                                                                         |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3                                                                                                                          | Introduction<br>Modeling of Conducted Emission Environment<br>LISN<br>Power Cables<br>Electric Machine                                                                                                                                                                                                                                                                                                                                                                                                                 | 39<br>40<br>40<br>42<br>47                                                                   |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3                                                                                                                   | Introduction<br>Modeling of Conducted Emission Environment<br>LISN<br>Power Cables<br>Electric Machine<br>VSD system equivalent circuit modeling                                                                                                                                                                                                                                                                                                                                                                       | 39<br>40<br>40<br>42<br>47<br>52                                                             |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3<br>Par                                                                                                            | Introduction<br>Modeling of Conducted Emission Environment<br>LISN<br>Power Cables<br>Electric Machine<br>VSD system equivalent circuit modeling<br>ameters extraction through direct measurements                                                                                                                                                                                                                                                                                                                     | 39<br>40<br>42<br>42<br>47<br>52<br>54                                                       |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3<br>Par<br>Par                                                                                                     | Introduction<br>Modeling of Conducted Emission Environment<br>LISN<br>Power Cables<br>Electric Machine<br>VSD system equivalent circuit modeling<br>ameters extraction through direct measurements<br>ameters extraction through open- and short-circuit measurements                                                                                                                                                                                                                                                  | 39<br>40<br>40<br>42<br>47<br>52<br>54<br>59                                                 |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3<br>Par<br>Par<br>Ver                                                                                              | Introduction<br>Modeling of Conducted Emission Environment<br>LISN<br>Power Cables<br>Electric Machine<br>VSD system equivalent circuit modeling<br>ameters extraction through direct measurements                                                                                                                                                                                                                                                                                                                     | 39<br>40<br>40<br>42<br>47<br>52<br>54<br>59<br>64                                           |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3<br>Par<br>Par                                                                                                     | Introduction<br>Modeling of Conducted Emission Environment<br>LISN<br>Power Cables<br>Electric Machine<br>VSD system equivalent circuit modeling<br>ameters extraction through direct measurements<br>ameters extraction through open- and short-circuit measurements                                                                                                                                                                                                                                                  | 39<br>40<br>40<br>42<br>47<br>52<br>54<br>59<br>64                                           |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3<br>Par<br>Ver<br>3.4                                                                                              | Introduction<br>Modeling of Conducted Emission Environment<br>LISN<br>Power Cables<br>Electric Machine<br>VSD system equivalent circuit modeling                                                                                                                                                                                                                                                                                                                                                                       |                                                                                              |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3<br>Par<br>Par<br>Ver<br>3.4<br><b>Chapter 4</b>                                                                   | Introduction<br>Modeling of Conducted Emission Environment<br>LISN<br>Power Cables<br>Electric Machine<br>VSD system equivalent circuit modeling<br>ameters extraction through direct measurements<br>ameters extraction through open- and short-circuit measurements<br>ification in large signal condition<br>Conclusion                                                                                                                                                                                             | 39<br>40<br>40<br>42<br>52<br>54<br>59<br>64<br>66                                           |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3<br>Par<br>Par<br>Ver<br>3.4<br><b>Chapter 4</b>                                                                   | Introduction<br>Modeling of Conducted Emission Environment<br>LISN<br>Power Cables<br>Electric Machine<br>VSD system equivalent circuit modeling                                                                                                                                                                                                                                                                                                                                                                       | 39<br>40<br>40<br>42<br>52<br>54<br>59<br>64<br>66                                           |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3<br>Par<br>Par<br>Ver<br>3.4<br><b>Chapter 4</b><br><b>3D Para</b>                                                 | Introduction<br>Modeling of Conducted Emission Environment<br>LISN<br>Power Cables<br>Electric Machine<br>VSD system equivalent circuit modeling<br>ameters extraction through direct measurements<br>ameters extraction through open- and short-circuit measurements<br>ification in large signal condition<br>Conclusion                                                                                                                                                                                             | 39<br>40<br>42<br>52<br>54<br>59<br>64<br>66<br>69<br>69                                     |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3<br>Par<br>Par<br>Ver<br>3.4<br><b>Chapter 4</b>                                                                   | Introduction<br>Modeling of Conducted Emission Environment<br>LISN<br>Power Cables<br>Electric Machine<br>VSD system equivalent circuit modeling<br>ameters extraction through direct measurements<br>ameters extraction through open- and short-circuit measurements<br>ification in large signal condition<br>Conclusion<br>Introduction                                                                                                                                                                             |                                                                                              |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3<br>Par<br>Par<br>Ver<br>3.4<br><b>Chapter 4</b><br><b>3D Para</b><br>4.1                                          | Introduction<br>Modeling of Conducted Emission Environment<br>LISN                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                              |

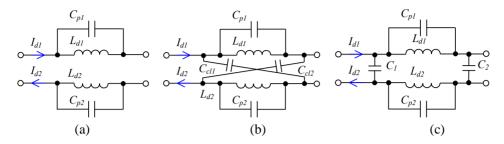

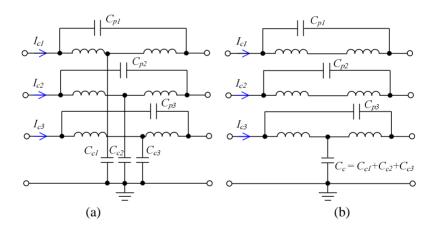

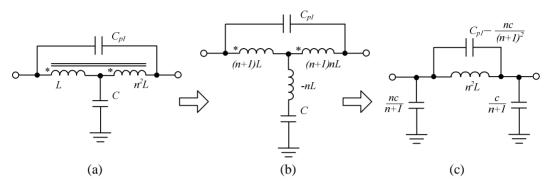

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3<br>Par<br>Par<br>Ver<br>3.4<br><b>Chapter 4</b><br><b>3D Para</b><br>4.1<br>4.2                                   | Introduction<br>Modeling of Conducted Emission Environment<br>LISN<br>Power Cables<br>Electric Machine<br>VSD system equivalent circuit modeling<br>ameters extraction through direct measurements<br>ameters extraction through open- and short-circuit measurements<br>ification in large signal condition<br>Conclusion<br><b>sitics Cancellation</b><br>Present filter parasitics cancellation techniques<br>EPC cancellation techniques                                                                           |                                                                                              |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3<br>Par<br>Ver<br>3.4<br><b>Chapter 4</b><br><b>3D Para</b><br>4.1<br>4.2<br>4.2.1                                 | Introduction<br>Modeling of Conducted Emission Environment<br>LISN<br>Power Cables<br>Electric Machine<br>VSD system equivalent circuit modeling<br>ameters extraction through direct measurements<br>ameters extraction through open- and short-circuit measurements<br>ification in large signal condition<br>Conclusion<br>sitics Cancellation<br>Present filter parasitics cancellation techniques<br>EPC cancellation techniques<br>ESL cancellation techniques                                                   | 39<br>40<br>40<br>42<br>52<br>54<br>64<br>66<br>69<br>69<br>69<br>70<br>70                   |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3<br>Par<br>Ver<br>3.4<br><b>Chapter 4</b><br><b>3D Para</b><br>4.1<br>4.2<br>4.2.1<br>4.2.2                        | Introduction<br>Modeling of Conducted Emission Environment<br>LISN<br>Power Cables<br>Electric Machine<br>VSD system equivalent circuit modeling<br>ameters extraction through direct measurements<br>ameters extraction through open- and short-circuit measurements<br>ification in large signal condition<br>Conclusion<br><b>sitics Cancellation</b><br>Present filter parasitics cancellation techniques<br>EPC cancellation techniques<br>ESL cancellation techniques<br>Mutual coupling cancellation techniques | 39<br>40<br>40<br>42<br>52<br>54<br>59<br>64<br>66<br>69<br>69<br>70<br>70<br>72<br>73       |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3<br>Par<br>Par<br>Ver<br>3.4<br><b>Chapter 4</b><br><b>3D Para</b><br>4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3        | Introduction<br>Modeling of Conducted Emission Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39<br>40<br>40<br>42<br>52<br>54<br>59<br>64<br>66<br>69<br>69<br>69<br>70<br>72<br>73<br>73 |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3<br>Par<br>Par<br>Ver<br>3.4<br><b>Chapter 4</b><br><b>3D Para</b><br>4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3 | Introduction<br>Modeling of Conducted Emission Environment<br>LISN<br>Power Cables<br>Electric Machine<br>VSD system equivalent circuit modeling<br>ameters extraction through direct measurements<br>ameters extraction through open- and short-circuit measurements<br>ification in large signal condition<br>Conclusion<br><b>sitics Cancellation</b><br>Present filter parasitics cancellation techniques<br>EPC cancellation techniques<br>ESL cancellation techniques<br>Mutual coupling cancellation techniques | 39<br>40<br>42<br>52<br>54<br>59<br>64<br>66<br>69<br>69<br>69<br>70<br>70<br>73<br>73<br>75 |

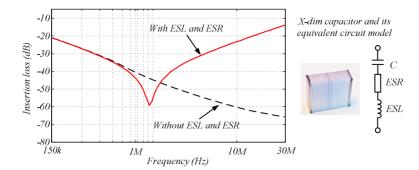

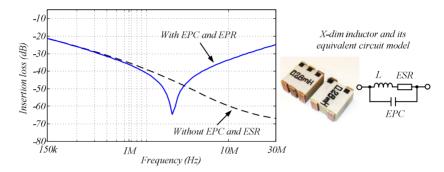

| 4.4.2     | Parasitic effects in LC filters                                 |     |

|-----------|-----------------------------------------------------------------|-----|

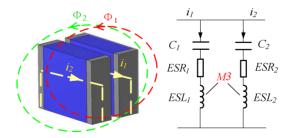

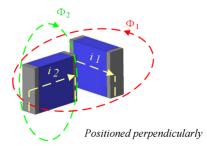

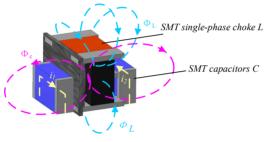

| 4.4.3     | Reduction of mutual inductive coupling                          |     |

| Rec       | duction of mutual coupling between SMT capacitors               |     |

|           | duction of mutual coupling between SMT equations and capacitors |     |

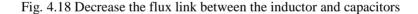

|           | ermediate substrate as shield                                   |     |

| 4.4.4     | Design of ESL cancellation winding for SMT capacitors           |     |

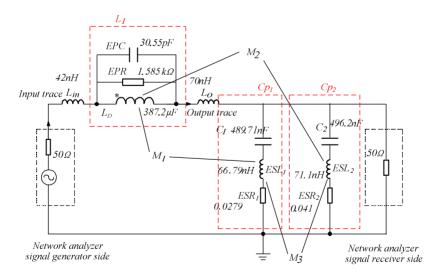

| 4.5       | Experimental verification through network analyzer and LISN     |     |

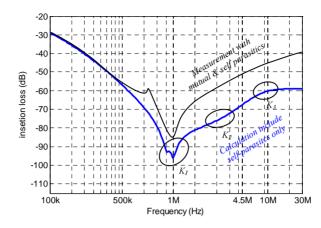

| 4.5.1     | Insertion losses measured from network analyzer and Dist        |     |

| 4.5.2     | Noise spectra measured from LISN                                |     |

| 4.6       | Conclusion                                                      |     |

| 4.0       | Conclusion                                                      |     |

|           |                                                                 |     |

| Compar    | ring and Improving EMC Performance in Si IGBT and SiC JFET N    |     |

|           |                                                                 |     |

| 5.1       | Introduction                                                    | 89  |

| 5.2       | Comparison in inverter legs                                     |     |

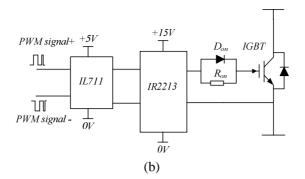

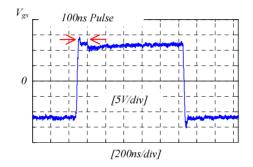

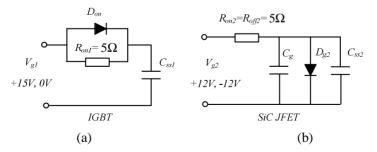

| 5.2.1     | Configuration of gate drivers                                   |     |

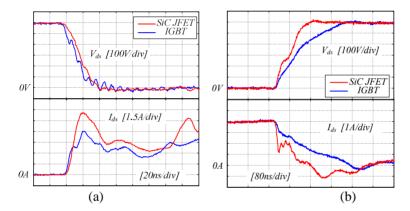

| 5.2.2     | Turn-on of transistors                                          |     |

| 5.2.3     | Turn-off of transistors                                         |     |

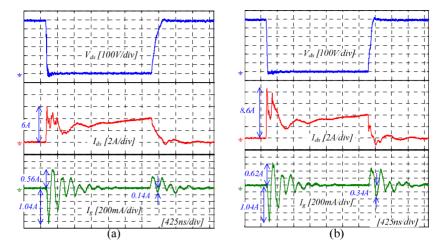

| 5.2.4     | Inductive switching waveforms                                   |     |

| 5.2.5     | Noise source analysis                                           |     |

| 5.3       | EMI Comparison and analysis in three phase systems              |     |

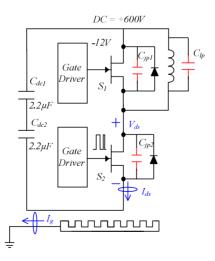

| 5.3.1     | Experiment configuration                                        |     |

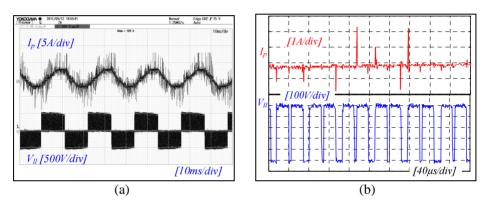

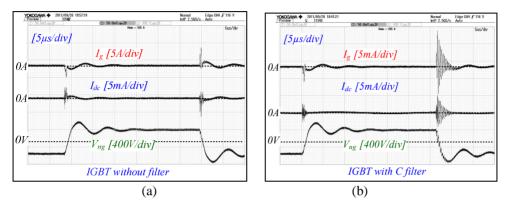

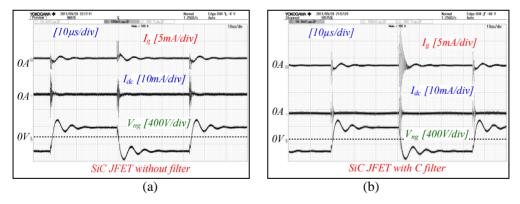

| 5.3.2     | Waveforms without filter                                        |     |

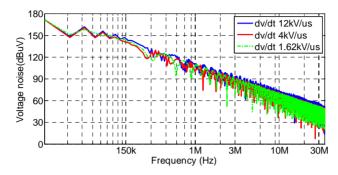

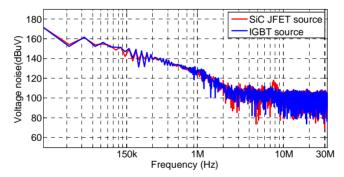

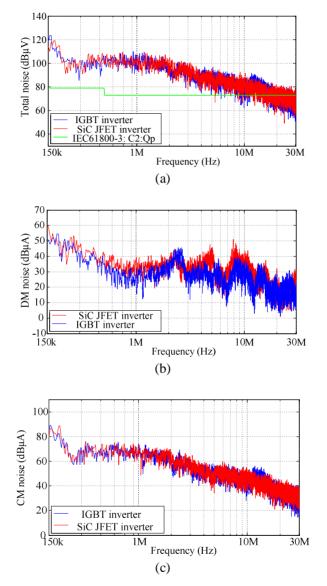

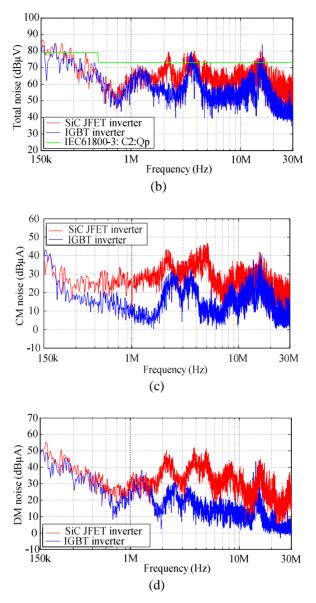

| 5.3.3     | Measured EMI without filter                                     |     |

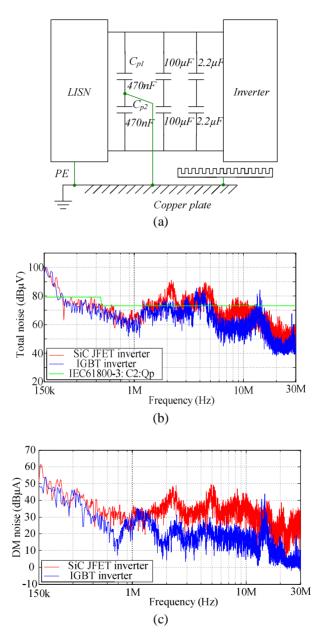

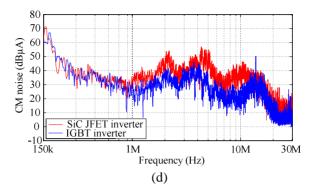

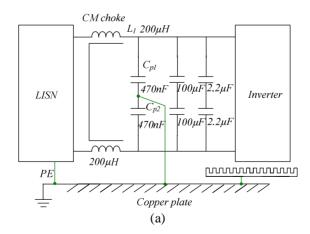

| 5.3.4     | Measured EMI with CM filters                                    |     |

| 5.4       | Filtering performance analysis and verification                 |     |

| 5.4.1     | Inverter CM test mode                                           |     |

| 5.4.2     | Parasitic oscillations                                          |     |

| 5.4.3     | Increased parasitic oscillations                                |     |

| 5.4.4     | CM superimposed on DM                                           |     |

| 5.4.5     | Measured EMI spectra of CM test mode                            |     |

| 5.4.6     | Other causes                                                    |     |

| 5.5       | Suppression of the parasitic oscillations                       |     |

| 5.5.1     | Modeling of CM current spectra                                  |     |

| 5.5.2     | Suppression of parasitic oscillations                           |     |

| 5.5.3     | Selection of ferrite beads                                      |     |

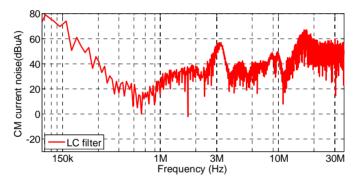

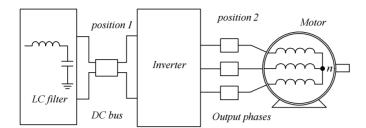

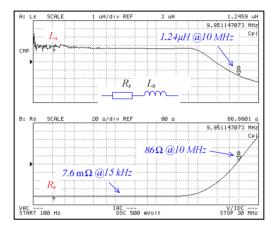

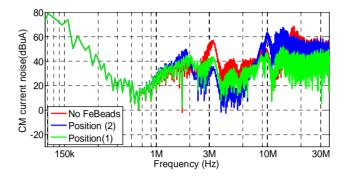

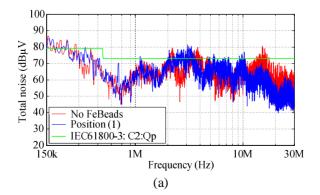

| 5.5.4     | Validation of suppression effects                               | 117 |

| 5.6       | Conclusion                                                      | 118 |

| Chantor 6 |                                                                 | 110 |

| -         |                                                                 |     |

| SIC INOI  | se Reduction Due to Substrate Capacitive Coupling               |     |

| 6.1       | Introduction                                                    | 119 |

| 6.2       | Capacitive coupling influence and minimizations                 |     |

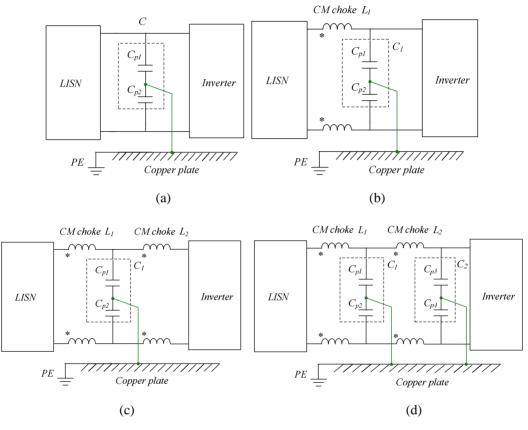

| 6.2.1     | Influences and Solutions                                        |     |

| Inf       | luence on DM                                                    |     |

|     | Solutions for DM                                                                                  | 123 |

|-----|---------------------------------------------------------------------------------------------------|-----|

|     | Influence on CM                                                                                   | 123 |

|     | Solutions for CM                                                                                  | 125 |

| 6.  | 2.2 Circuit parasitics and extraction                                                             |     |

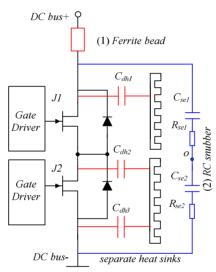

| 6.  | 2.3 DM Oscillation Damping Methods – Simulation and Implementation                                |     |

|     | Simulations                                                                                       |     |

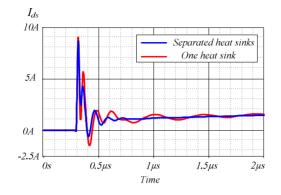

|     | Inductive switching waveforms                                                                     | 129 |

| 6.  | 2.4 CM Oscillation Damping Methods – Simulation and Implementation                                | 130 |

|     | The grounding of high side heat sink                                                              | 130 |

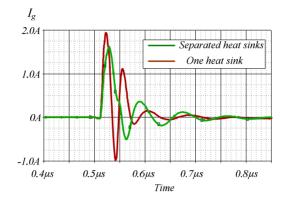

|     | Inductive switching waveforms                                                                     | 131 |

| 6.3 | Comparisons between IMS and one heat sink inverters                                               |     |

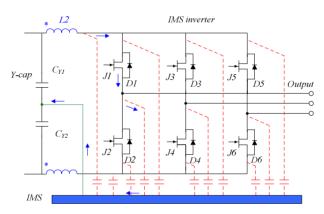

| 6.  | 3.1 Experiment configuration                                                                      |     |

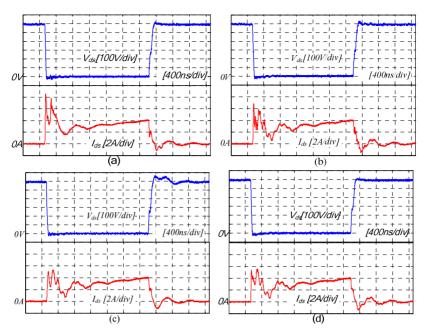

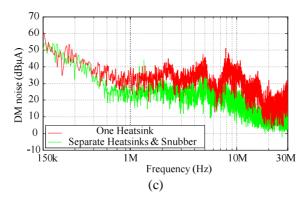

| 6.  | 3.2 Comparisons without filter                                                                    |     |

| 6.  | 3.3 Comparisons with purely capacitive filter                                                     |     |

| 6.4 | Comparisons between one heat sink and separated heat sink inverters                               |     |

|     | 4.1 Experiment configuration                                                                      |     |

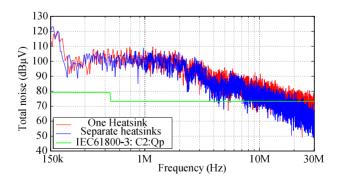

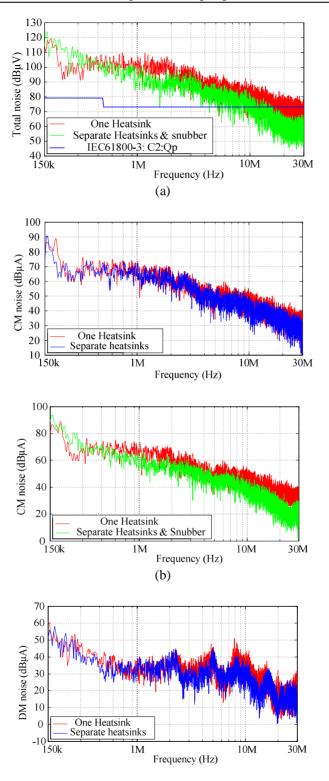

| 6.  | 4.2 Spectra Comparisons                                                                           |     |

| 6.5 |                                                                                                   |     |

|     | 5.1 Filtering solutions                                                                           |     |

|     | 5.2 Implementation for heat sink inverter                                                         |     |

|     | 5.3 Implementation for IMS inverter                                                               |     |

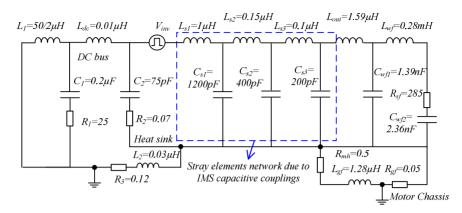

| 6.6 | Modeling for IMS Inverter                                                                         |     |

| 0.  | 6.1 A Broadband modeling procedure                                                                |     |

| 0.  | 6.2 Creation of the modeling bases                                                                |     |

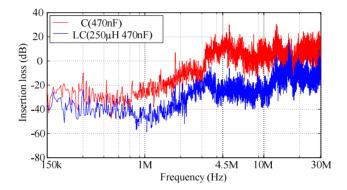

|     | 6.3 Final model for insertion losses                                                              |     |

|     | 6.4 Elements Extraction                                                                           |     |

|     | 6.5 Evaluation of different filter topologies                                                     |     |

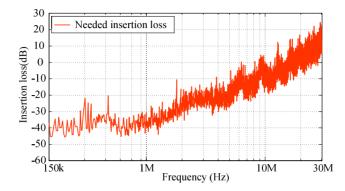

| 6.7 | Towards The Standard Compliance                                                                   |     |

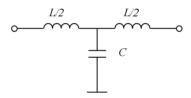

|     | 7.1 LCL filter as the selection                                                                   |     |

|     | 7.2 Optimization                                                                                  |     |

| 6.8 | Conclusion                                                                                        | 155 |

| ~   | _                                                                                                 |     |

| -   | er 7                                                                                              |     |

| Con | clusions and Recommendations                                                                      | 157 |

| 7 1 |                                                                                                   | 1   |

| 7.1 | Conclusions                                                                                       |     |

|     | Equivalent circuit modeling (Chapter 3)                                                           |     |

|     | 3D parasitics cancellation techniques (Chapter 4)                                                 |     |

|     | Dominant parameters influencing EMI magnitude (Chapter 5)                                         |     |

|     | Significantly higher DM noise emitted from SiC JFET system (Chapter 5)                            |     |

|     | Influence of circuit parasitics (Chapter 5)<br>High frequency performance improvement (Chapter 5) |     |

|     |                                                                                                   |     |

|     | Attachment of power device drain plate to substrate (Chapter 6)                                   |     |

| 7.2 | IMS cooling and increased EMI (Chapter 6)<br>Recommendations for further research                 |     |

| 1.2 | Equivalent circuit modeling                                                                       |     |

|     | 3D parasitics cancellation                                                                        |     |

|     | EMI comparison between Si IGBT and SiC JFET based motor drive systems                             |     |

|     | En comparison between of 10D1 and bre of D1 based motor drive systems                             | 100 |

| Separation of the substrates |  |

|------------------------------|--|

| References                   |  |

| List of Publications         |  |

| Summary                      |  |

| Samenvatting                 |  |

| Curriculum Vitae             |  |

# Chapter 1

# Introduction

### 1.1 Background

Electromagnetic Interference (EMI) is defined as any electromagnetic disturbance that interrupts, obstructs, degrades or limits the effective performance of electronic or electrical equipment [Pau06]. Adopting the practice of meeting EMI standards is defined as Electromagnetic compatibility (EMC), which is the ability of a device, unit of equipment or system to function satisfactorily with other electronic systems, and not produce or be susceptible to interference. Before being placed on the market, any power electronics product must be not only functionally compatible with other systems but must also meet legal requirements in virtually all countries of the world.

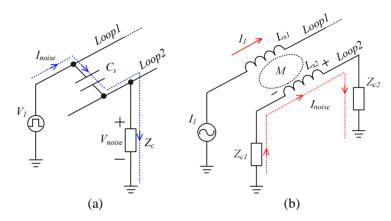

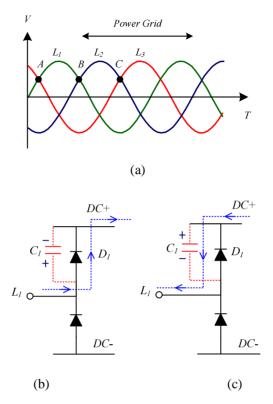

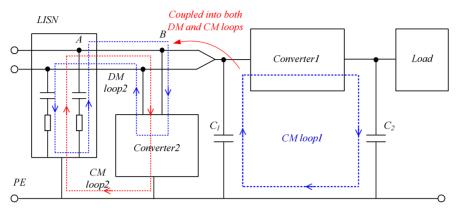

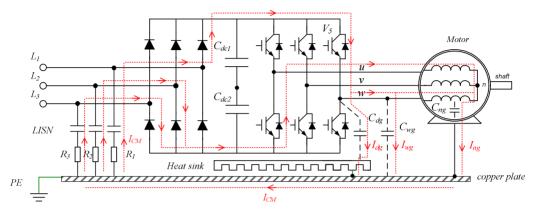

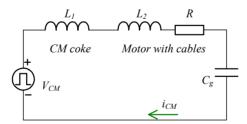

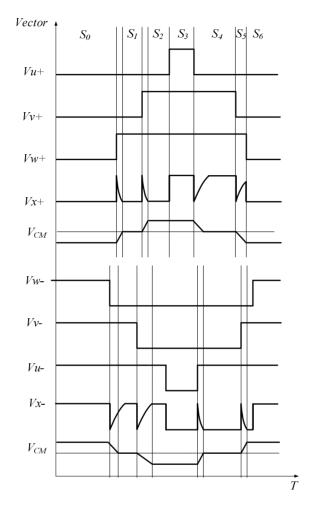

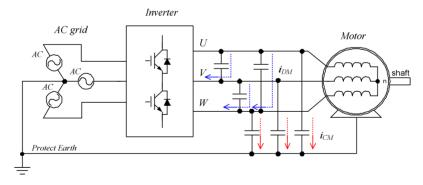

The switched mode power conversion systems generate EMI noise at each switching transient. Usually the noise is separated into two modes: differential mode (DM) and common mode (CM). The CM noise is defined as the type of EMI noise induced on signals with respect to a reference ground [Ski99]. The DM noise is defined as the type of noise flowing between power supplying cables. As the application of switched power converters increases, concerns about EMC strategies grow for both power electronics system designers and users.

EMI can be categorized into two groups of conducted and radiated emissions [Pau06]. Conducted emission mainly concerns electromagnetic energy that is propagated through cables connecting the system to the grid or interconnecting subsystems. These interference signals pass together with the functional signals. The frequency range where conducted emissions are regulated is generally up to 30 MHz. Radiated emission mainly concerns electromagnetic energy the frequency of which is higher than 30 MHz. In this frequency range the energy is generally propagated in the form of electromagnetic waves through air rather than by direct conduction through cables. In power electronics systems a conducted emission can produce a radiated emission and vice versa.

### **1.2 Research target and EMC challenges**

#### **1.2.1 Research target**

As power electronic technology grows, power converters are present everywhere and modify the form of electrical energy in industrial, commercial, and residential environments. As a result, frequency converters have become the main EMI sources and design efforts are needed to ensure an electromagnetic friendly environment.

In this thesis Variable Speed Drives (VSDs) are investigated, and for the following reasons:

1. VSD for speed control of motors provides energy savings and ease in control. Nowadays it is estimated that 60% ~ 65% of electricity generated in the United States is consumed by motor drives. [Asa93].

2. The switching frequencies of VSDs are in the range of  $10 \sim 20$  kHz when Insulate Gate Bipolar Transistors (IGBTs) are used. It is possible to increase switching frequencies of existing motor drives by employing new Silicon Carbide (SiC) or Gallium Nitride (GaN) devices.

#### **1.2.2 EMC design in motor drives**

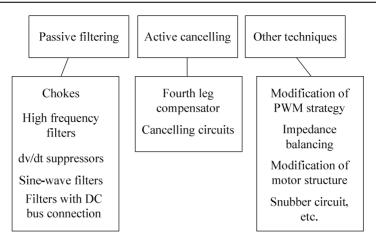

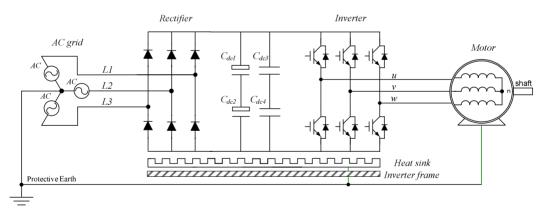

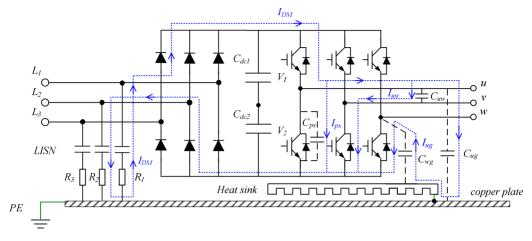

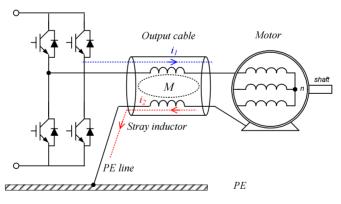

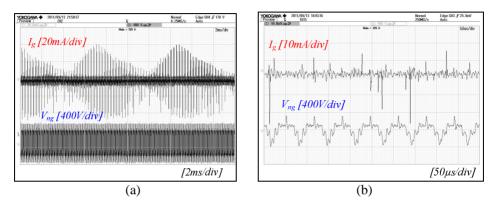

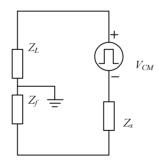

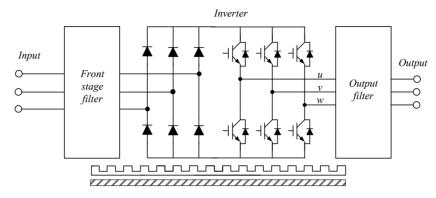

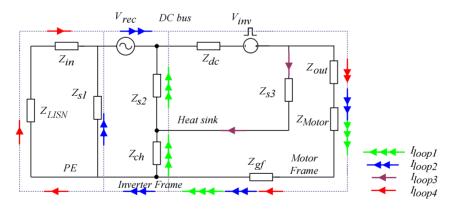

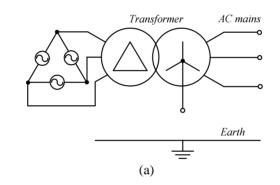

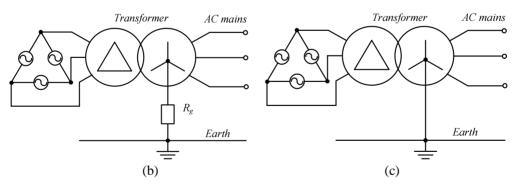

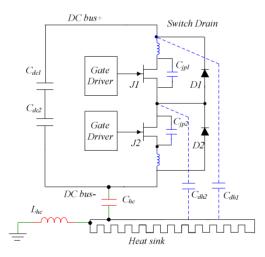

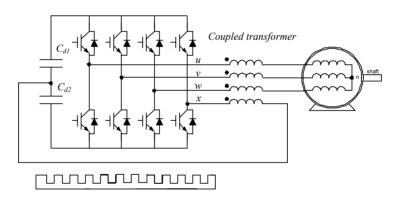

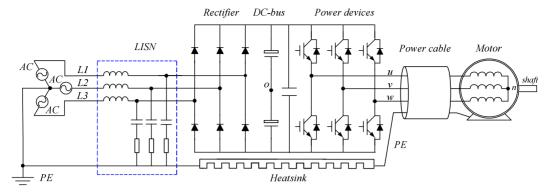

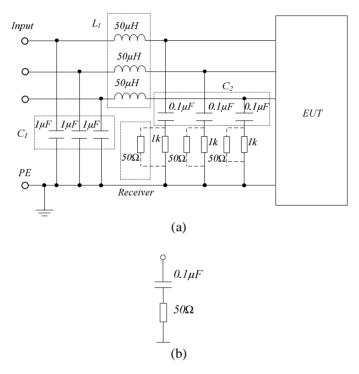

The standard industrial solution for VSDs uses induction motors fed by voltage source inverters (VSI). The inverter generates Pulse Width Modulated (PWM) voltages, with dv/dt values of  $10kV/\mu s$  or more. Consequently, both conducted and radiated EMI have become major problems which make EMC design essential. Many conducted EMC strategies have been developed in the past decades for motor drive systems. They can be categorized into three groups: passive filtering, active cancelling, and other techniques, as shown in Fig. 1.1.

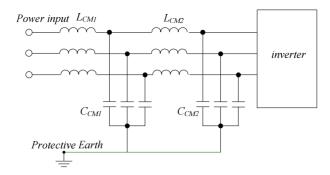

Traditionally, passive filtering methods especially power line filters have mostly been used to suppress conduced EMI. Filter solutions include chokes, high frequency filters, dv/dt suppressors, sine-wave filters, and filters with DC bus connection [Han06; Han07].

Methods of active cancelling usually apply active devices and control to compensate for the dv/dt transients generated by the PWM switching scheme[Jul99; Pia09]. Generally an extra winding is needed to form a coupled transformer which generates the opposite voltage to the other three inverter phases.

The other techniques include: modification of PWM strategy, impedance balancing, modification of motor structure, etc. Detailed reviews on various EMC design strategies will be given in Chapter 2.

Fig. 1.1 Summary of EMC strategies for motor drives

# **1.2.3** Technological advances in power electronics and relevance to EMC challenges

Two important technology developments that will affect EMC are SiC power devices and increased integration of inverters.

#### SiC power devices - faster switching but increased EMI

After 30 years of development, wide band-gap material SiC now has great potential to replace Si as the dominant transistor technology because of its having a number of superior qualities [Ozp10]:

- SiC material's critical breakdown field is approximately 10 times that of silicon, which enables the development of a thinner structure of a stated breakdown voltage, which in turn reduces the channel on-resistance [Cal08].

- SiC has a thermal conductivity of 2.8 times higher than that of Si, providing a much higher current density at a given junction temperature.

- With a band-gap of approximately 3 times wider than Si, the SiC devices also exhibit significantly lower leakage current at high temperature operation [Onl11b].

Although the advantages of SiC material have been recognized since 1980s, immature technology that limited the breakdown performance became the main barrier for the introduction of SiC devices. In 2004, the first successful commercial adoption of SiC Junction Barrier Schottky (JBS) diodes and power switch product – 1200V,  $80m\Omega$  SiC MOSFET from Cree - was reported [Das11]. In 2008, the enhanced mode SiC Junction Field Effect Transistor (JFET) that can be used as a direct replacement for Si MOSFETs and IGBTs was announced by the SemiSouth Laboratories, Tennessee, USA. They were applied on an off-the-shelf solar inverter, whose energy loss is effectively reduced by as much as 50% [On108]. In this research

the normally-OFF trench SiC power JFETs have been chosen because of the good match of their blocking voltage and current levels with the traditional Si IGBT.

Over the last couple of years, the SiC devices have been subjected to extensive research in an attempt to exploit the above properties. For example, in [Kra09; Fun07], very high converter efficiencies were reported under high temperature and low switching frequency conditions. A comparative study shows that the losses of SiC MOSFETS can be reduced by a factor ranging from two to five, compared to normal Si MOSFETS [Gla11]. The enhanced switching performance of the SiC switches, allowing for increased switching frequencies and lower losses, leads to increased power density by size reduction of magnetic components and heat sinks [Jos11b]. At the same time, EMI emissions are increasing due to the SiC transistors' faster switching speed. Nowadays, with a more stringent EMC environment due to the fast growing power electronics applications, smart EMI filter development that has better filtering abilities becomes essential for the acceptance of SiC power converters.

#### Higher integration levels - small filters and increased EMI coupling

Increasing the power density is one of the main objectives. Therefore a compact EMI filter design is essential. Nowadays, EMI filters are still most commonly composed of passive components that can make up more than 50% of the volume of the entire system. Numerous techniques, such as topology optimization, components packaging and manufacturing have been developed to reduce the size of EMI filters, while maintaining high filter performances, for example:

• Filter topology optimization

This technique optimizes filter design to fulfill noise attenuations while avoiding over sizing and large components. Usually the focus is on advanced measuring techniques and elements extraction methodology in order to develop an accurate model [Har10; Tar10].

Integration technology

Integration technology is mostly realized through new component material [Wu11], and reshaping or unifying the component profiles [Jos09; Che03]. Hence optimized spatial design and packaging are achieved.

• Parasitic cancellations

This technique aims to make EMI coupling effects as low as possible [Neu04a; Hel08; Wan06a; Wan08b]. It improves the filter high frequency performance. Generally additional components are added to cancel high influence parasitics such as those in CM capacitors [Wan10; Tao 11].

• Thermally enhanced passives

This technique aims to enhance the components thermal performance of the components in order to operate under high temperature and high power conditions. Examples such as [Wyk03] where the inductor is encapsulated into a heat sink, and [Dir05] the heat extractors are integrated into power passive modules to improve the thermal performance.

## 1.3 Problem description and thesis objectives

#### 1.3.1 Problem description

EMC problems addressed in this thesis are:

#### Increased EMI due to the use of SiC devices

The first problem is increased noise emissions due to the employment of SiC transistors. Depending on the circuit configurations, the switching speed of a SiC JFET can be two to six times higher than a traditional Si IGBT [Hor06], which leads to degraded EMC performances. To accommodate SiC switches in motor drives, investigations are necessary to improve filter designs. The questions that need to be answered are: 1. How much would the spectral contents would be increased? 2. How would the filter design be influenced?

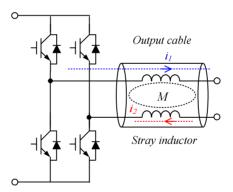

#### Complicated coupling paths and the role of parasitics

Circuit parasitics that were previously neglected start to play a role in EMI production due to the faster switching transients. The capacitive coupling existing in the circuits become more prominent, because they create loops for high frequency noise propagation generated with fast switching due to SiC devices. Hence EMC designs that have high frequency attenuation abilities are essential. Traditional filter designs targeting a too low frequency range may become inadequate.

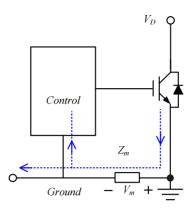

#### More sensitive EMI receptors

The third problem is that EMI receptors have become more sensitive due to the reduced logical and threshold levels of the electronic devices. It is necessary to put more effort into limiting the emitted noise in the source or decreasing the coupling effects. For example, the gate threshold the SiC JFET has been reduced to 1.5V which is half of the 3.0V threshold voltage of a traditional Si IGBT. For embedded logical devices as the controller part, the general power supplying voltage has been dramatically reduced from 5V to 3.3V in order to reduce power consumptions, for example, DSP TMS320F2808 which is 3.3V as opposed to classic ADMCF328 from Texas Instruments for motor control. Innovative methods rather than traditional methods, e.g. shielding, insert of the chokes, are preferred in order to lower the system cost and the volume.

#### **1.3.2** Thesis objectives

Based on the problems listed above, the objectives of this thesis are:

- To improve filter performances without increasing volume and cost.

- To provide quantitative understanding on EMC differences when using SiC JFETs and Si IGBTs in motor drive systems.

- To accommodate SiC JFETs in motor drives from EMC point of view.

• To develop a systematic EMI Filter design procedure.

In this thesis the focus is on the remedies and techniques to suppress the conducted EMI of inverters in VSD systems, using wide band-gap SiC JFETs as the switches, within the frequency range of interest from 9 kHz to 30 MHz.

### 1.4 Research method

In this thesis, the following approaches are developed in order to achieve the aforementioned objectives.

1. System modeling using equivalent circuits.

It is proposed that equivalent circuits be used to analyze and predict EMI levels in VSD systems. The predictable frequency range is up to 30 MHz of conducted EMI range.

#### The state of the art approach and significance of the approach:

Elements extraction is traditionally used for modeling the behavior of discrete components. Depending on the investigation purpose and prediction at concerned frequencies, the model can be adjusted by including elements that cause the corresponding influences, thereby extending the predictable frequency range.

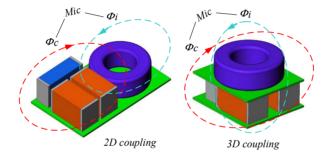

2. Parasitic cancellations in 3D spatial layout.

The filtering performance is enhanced by applying parasitics cancellation techniques which are implemented in 3D spatial layout.

#### The state of the art approach and significance of the approach:

Previous techniques in this field are implemented in 2D and limited by space and spatial constrains. With the generation of innovative passive components a new concept named 3D parasitic cancellations is proposed. Compared to traditional 2D methods it is more effective in obtaining cancellations while without lowering power density and increasing parasitic loops.

3. EMC comparison between SiC JFETs and Si IGBTs based drive systems.

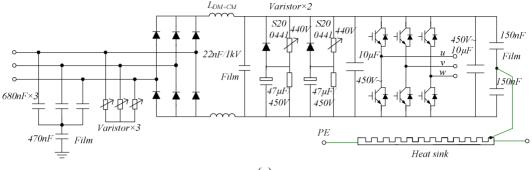

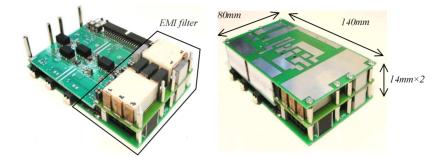

For comparative EMC studies, two 2.2 kW inverter prototypes which are IGBTs and SiC JFETs based respectively are built using the same layout. Their switching waveforms and spectra are compared in order to identify their EMC differences.

#### The state of the art approach and significance of the approach:

Nowadays the EMC remedies are mostly applied on the conventional Si IGBT based inverter systems. Even though the previous research unanimously concludes that the use of new SiC power devices increases the level of EMI noise, a quantitative understanding of the differences compared to Si devices is still elusive.

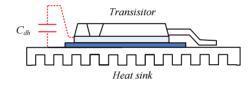

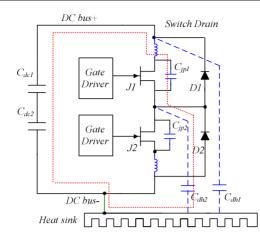

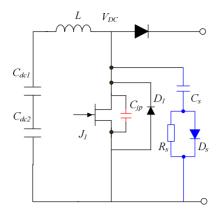

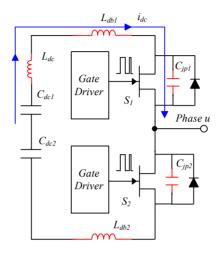

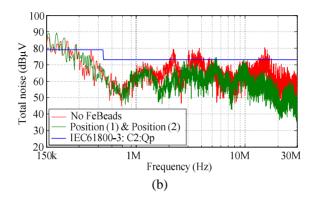

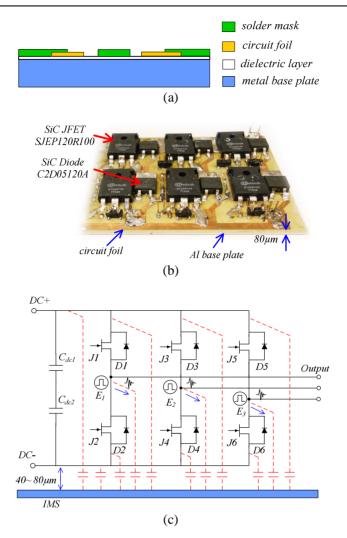

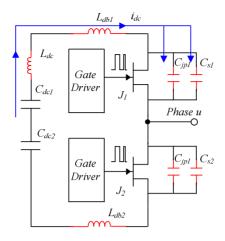

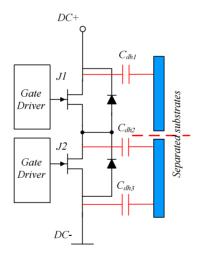

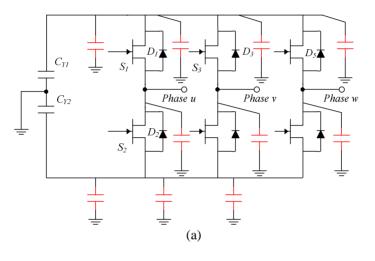

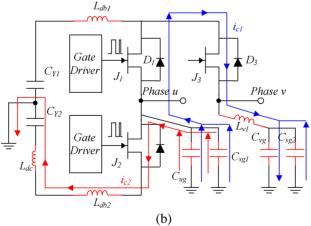

4. SiC noise source suppression.

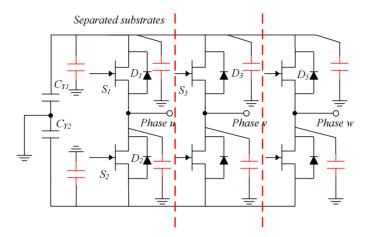

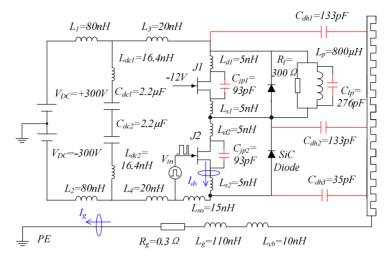

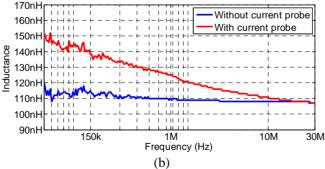

The implementation of the discrete SiC JFET with external free wheeling diode on top of the substrate creates capacitive coupling that close loops with considerable high frequency EMI propagations. Two substrates of insulated metal substrates (IMS) and heat sinks are employed. The proposed methods include using separated substrates layout, damping circuits, and insert of ferrite beads at difference positions.

#### The state of the art approach and significance of the approach:

During recent investigations the influence of substrate layout was ignored because the influence is not evident in IGBTs based inverters where dv/dts values are relatively low. Minimization on substrate influences thus becomes critical when SiC power devices are directly attached on top of substrates. The proposed approaches suppress the SiC noise at its source.

5. The procedure of systematic filter design.

Equivalent circuit modeling as introduced in Chapter 3 is used to develop the procedure. The designed filter is applied to the IMS inverter.

#### The state of the art approach and significance of the approach:

Nowadays, the trail-and-error process is still usually involved when designing EMI filters. The proposed procedure adopts the filter insertion losses as the modeling target, which avoids the onerous tasks of noise source analysis. The model is able to evaluate insertion losses of various filter topologies over a broad conducted EMI frequency range, which is essential in order to achieve an optimized filter design balanced between performance and cost.

## 1.5 Thesis layout

The layout of this thesis is illustrated in Fig. 1.2.

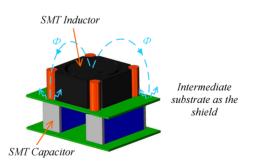

- Chapter 2 reviews the EMC strategies for VSD systems. Mechanism of EMI generation and propagation is investigated. The reviewed filter strategies include active and passive ones.

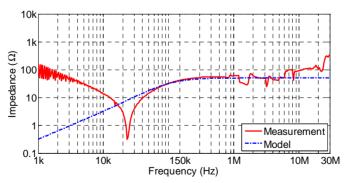

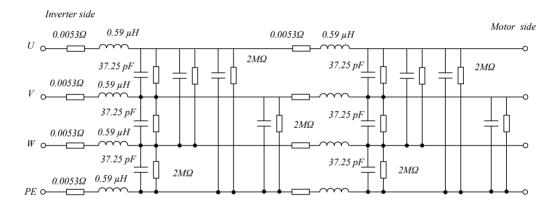

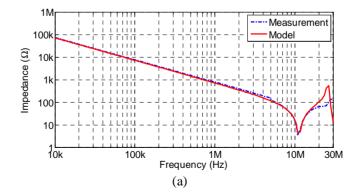

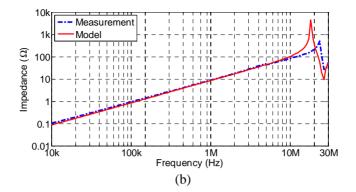

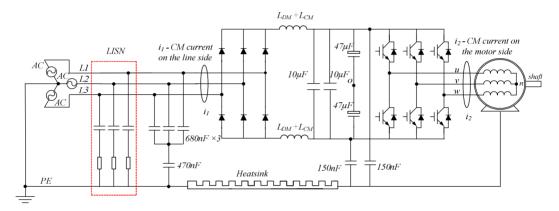

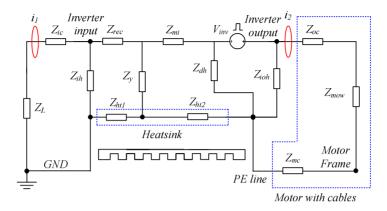

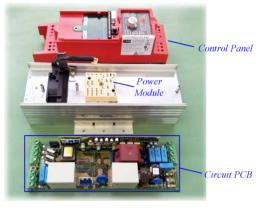

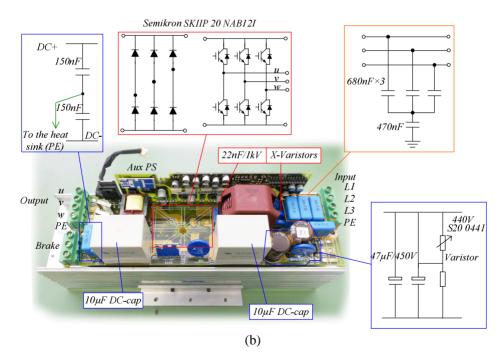

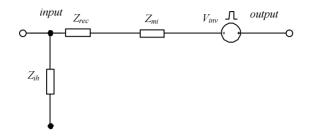

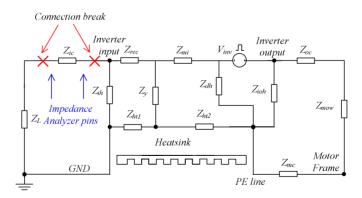

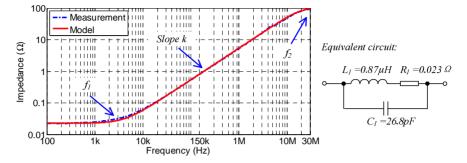

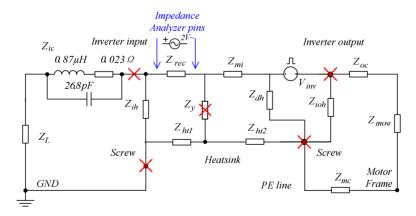

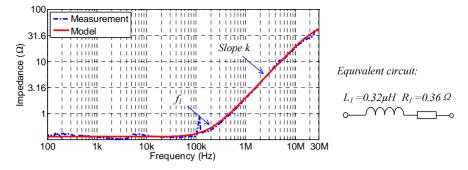

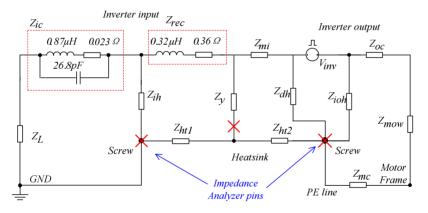

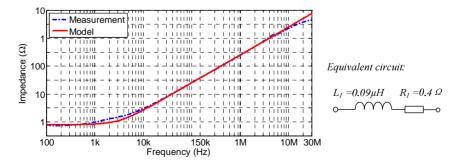

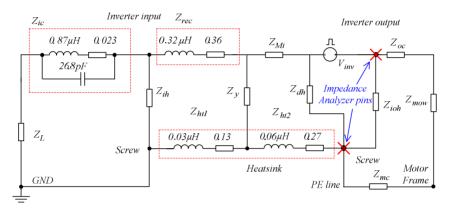

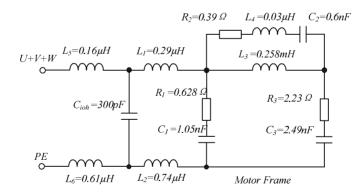

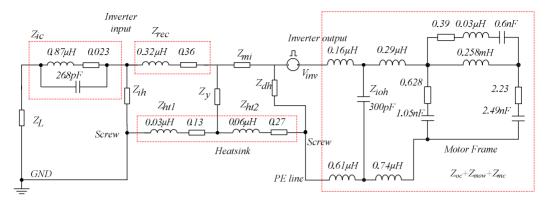

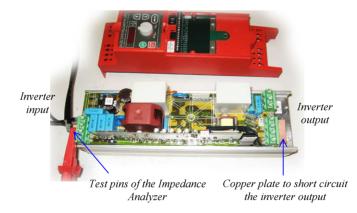

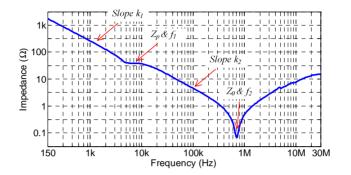

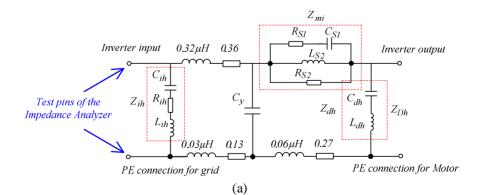

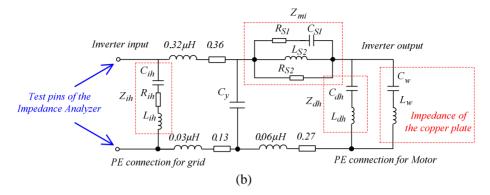

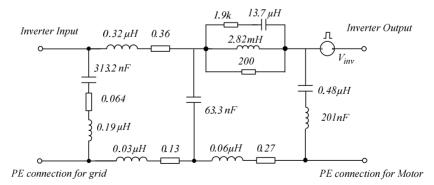

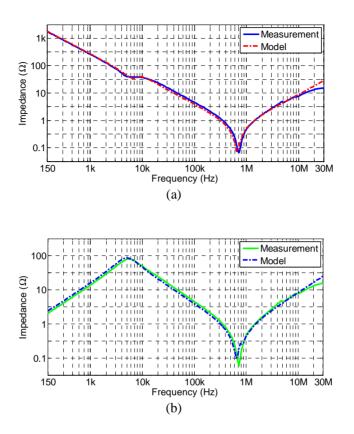

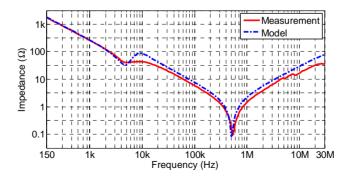

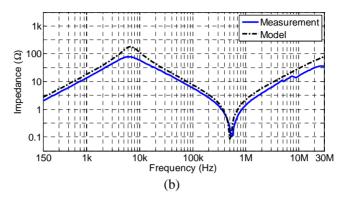

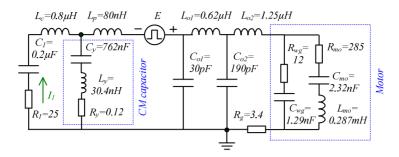

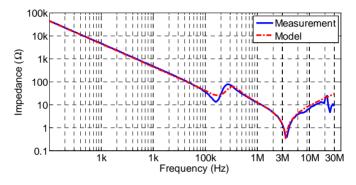

- Chapter 3 proposes the equivalent circuit modeling method for EMC performance predictions. A commercial industrial drive is taken as the case study. The parasitic elements are characterized by curve-fitting of impedance-frequency characteristics with the aid of inverter hardware disassembling.

- Chapter 4 presents parasitic cancellation techniques for EMI filters. A new concept named 3D parasitic cancellations for better filter performance is presented.

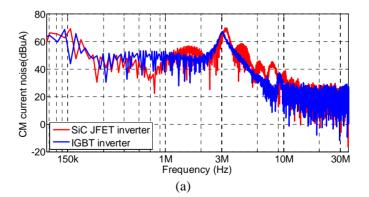

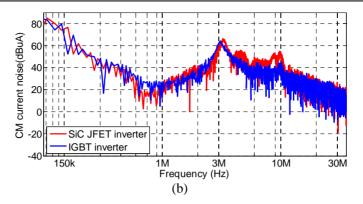

- Chapter 5 investigates the EMC differences, causes and approaches to improve filter design for SiC JFETs based motor drives, with a comparative Si IGBT based drive as the reference. The inverter prototypes are built using the same layout. Comparisons include switching waveforms and spectra measured by the LISN. The equivalent circuit modeling method is used for analyzing their spectral differences.

- Chapter 6 presents two methods namely the use of separated substrates and a broadband modeling procedure to suppress EMI under the influence of substrate capacitive coupling. The implemented substrates include Insulated Metal Substrate and Heat sink.

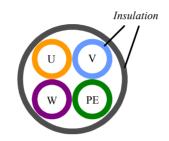

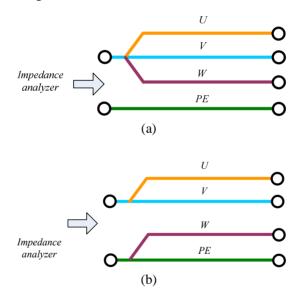

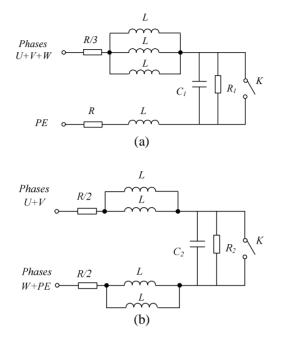

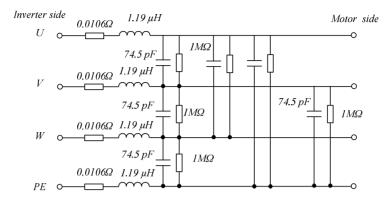

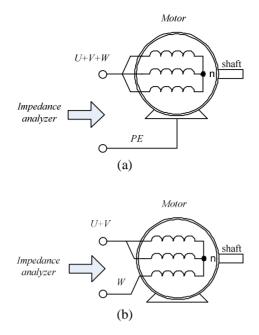

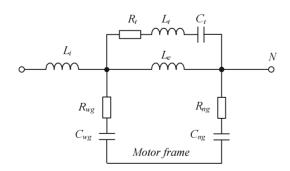

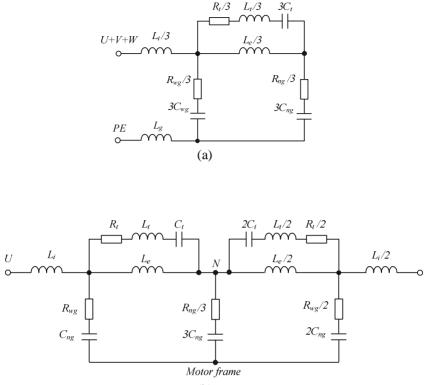

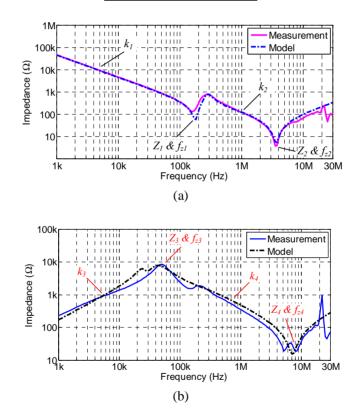

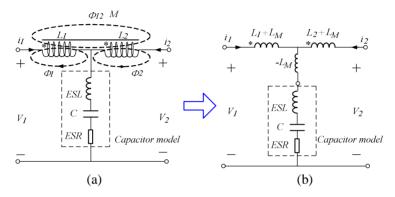

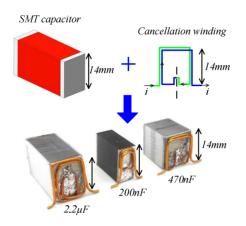

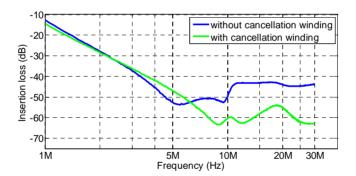

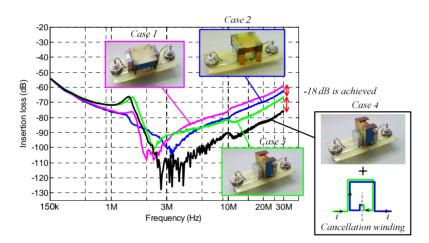

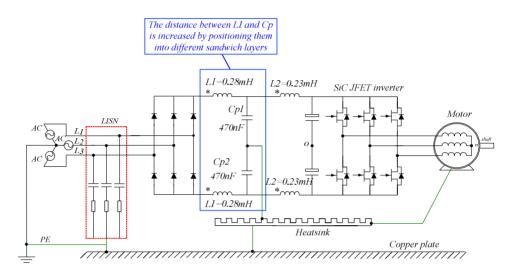

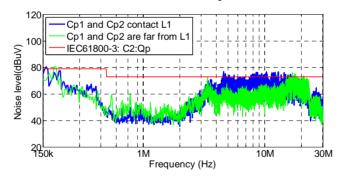

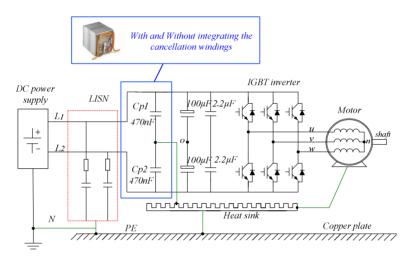

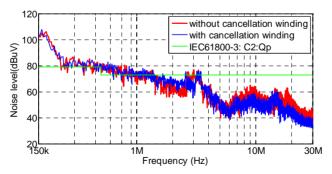

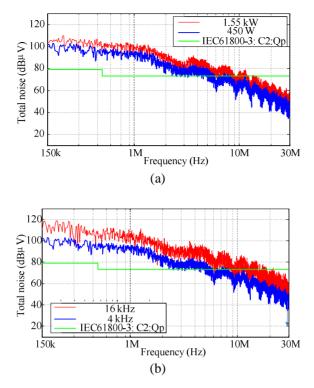

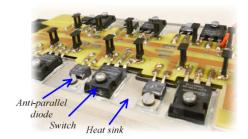

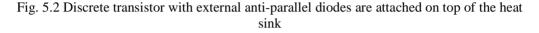

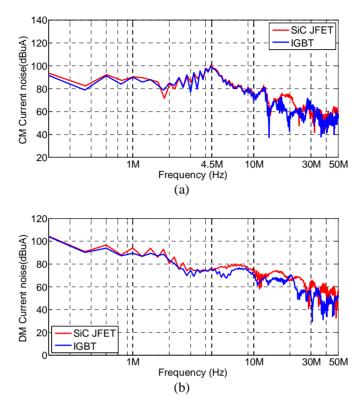

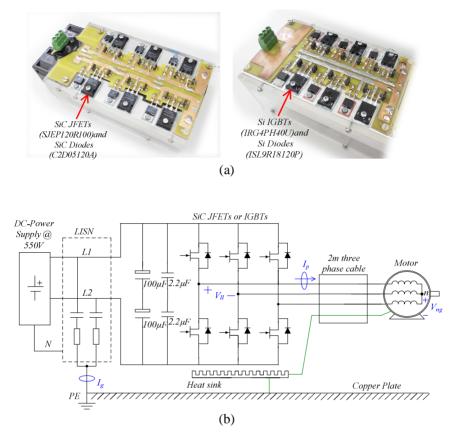

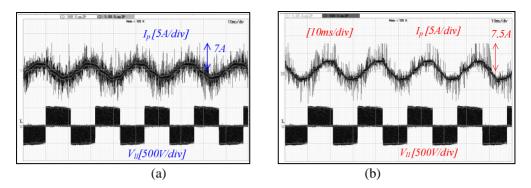

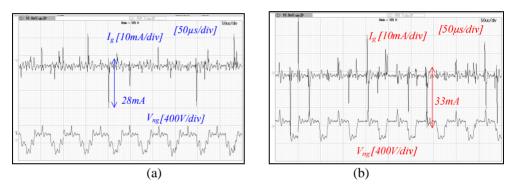

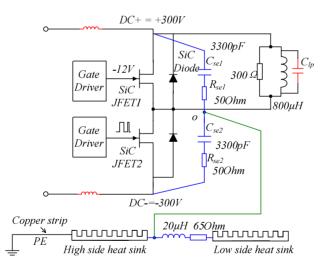

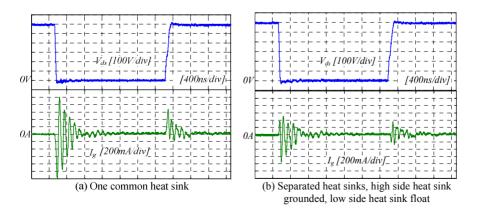

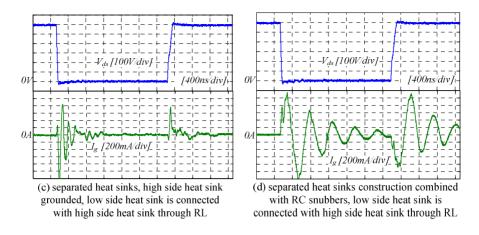

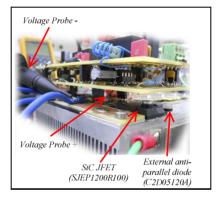

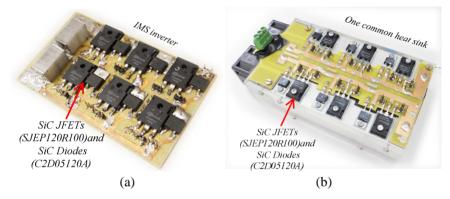

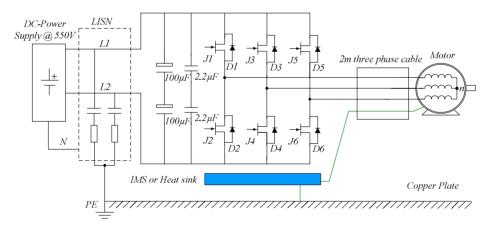

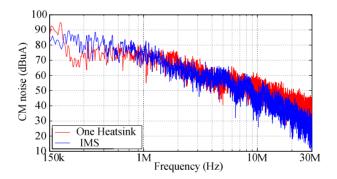

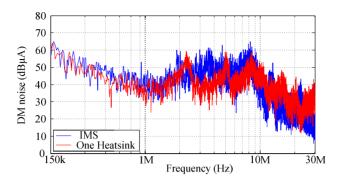

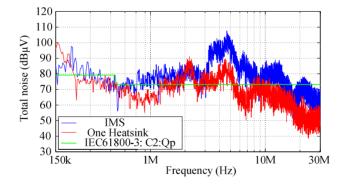

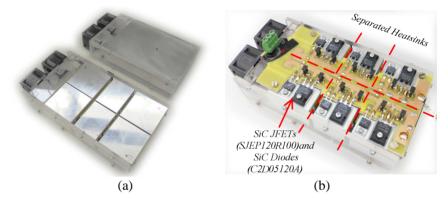

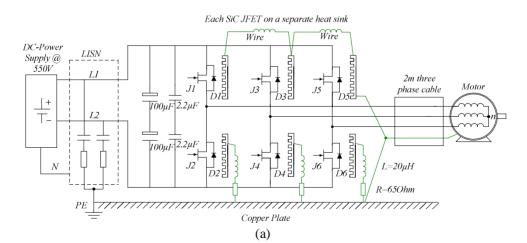

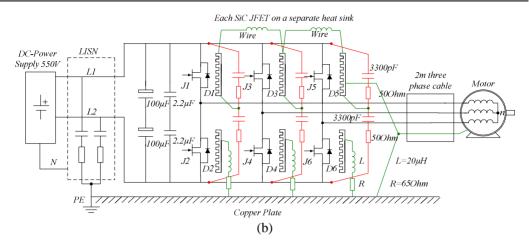

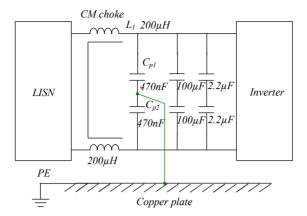

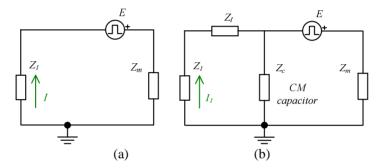

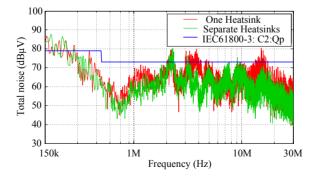

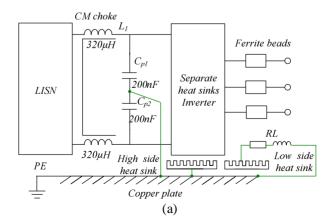

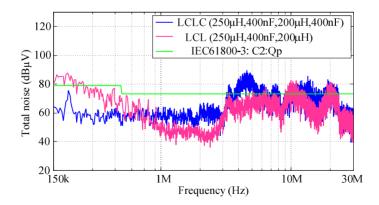

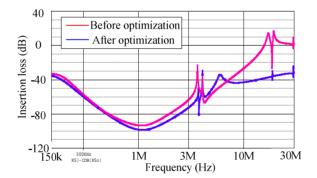

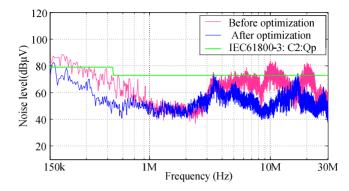

- Chapter 7 concludes the achievements and recommends for future research of this thesis.