# Silicon-Based Integration of Groups III, IV, V Chemical Vapor Depositions in High-Quality Photodiodes

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus Prof. ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen op donderdag 20 december 2012 om 10:00 uur

## door Amir SAMMAK

Master of Science (M.Sc) in Electrical Engineering, Electronics University of Tehran, Tehran, Iran geboren te Tehran, Iran Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. L. K. Nanver

#### Samenstelling promotiecommissie:

Rector Magnificus voorzitter

Prof. dr. L. K. Nanver Technische Universiteit Delft, promotor

Prof. dr. ir. E. Charbon Technische Universiteit Delft

Prof. dr. J. Schmitz Universiteit Twente

Prof. dr. H. W. M. Salemink Radboud Universiteit Nijmegen

Prof. L. Miglio Università degli Studi di Milano-Bicocca, Italië

Prof. J. Grahn Chalmers tekniska högskola, Zweden

Dr. ir. A. Pruijmboom Philips Lighting

Amir Sammak, Ph.D. thesis Delft University of Technology, with summary in Dutch.

The work described in this thesis was financially supported by Smart Mix Memphis project.

Keywords: Chemical Vapor Deposition (CVD), Epitaxial growth, Silicon-based integration, GaAs epitaxy, Ge-on-Si crystal growth, Boron (B), Gallium (Ga), PureB, PureGa, PureGaB, p<sup>+</sup>n diode, Ultrashallow junction diode, Avalanche photodiode, Photon counter.

ISBN: 978-94-6203-270-5

Copyright © 2012 by Amir Sammak

All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the prior written permission of the copyright owner.

## **Contents**

| 1 | Intr                               | Introduction                           |    |  |  |  |  |

|---|------------------------------------|----------------------------------------|----|--|--|--|--|

|   | 1.1 Fundamentals of photodetection |                                        |    |  |  |  |  |

|   |                                    | 1.1.1 Photonic semiconductor materials | 5  |  |  |  |  |

|   |                                    | 1.1.2 p-i-n photodiodes                | 9  |  |  |  |  |

|   |                                    |                                        | 11 |  |  |  |  |

|   |                                    | 1.1.4 Avalanche photodiodes            | 13 |  |  |  |  |

|   |                                    |                                        | 16 |  |  |  |  |

|   | 1.2                                | Properties of germanium                | 18 |  |  |  |  |

|   |                                    | 1.2.1 Infrared detection               | 20 |  |  |  |  |

|   |                                    | 1.2.2 Dopants in Ge                    | 20 |  |  |  |  |

|   |                                    | 1.2.3 Ge as III-V epitaxy template     | 23 |  |  |  |  |

|   | 1.3                                | Outline of this thesis                 | 25 |  |  |  |  |

| 2 | Gall                               | um arsenide epitaxial growth           | 27 |  |  |  |  |

|   | 2.1                                | Introduction                           | 27 |  |  |  |  |

|   | 2.2                                |                                        | 28 |  |  |  |  |

|   | 2.3                                | GaAs epitaxy                           | 30 |  |  |  |  |

|   |                                    | 2.3.1 Characterization                 | 31 |  |  |  |  |

|   |                                    | 2.3.2 Doping profiles                  | 32 |  |  |  |  |

|   | 2.4                                | GaAs on Si substrates                  | 36 |  |  |  |  |

|   | 2.5                                | Conclusions                            | 38 |  |  |  |  |

| 3 | Cry                                | talline germanium growth on silicon    | 41 |  |  |  |  |

|   | 3.1                                | Introduction                           | 42 |  |  |  |  |

|   | 3.2                                | Experimental procedures and analysis   |    |  |  |  |  |

|   |                                    |                                        | 44 |  |  |  |  |

|   |                                    |                                        | 46 |  |  |  |  |

|   |                                    | 3.2.3 Ge lateral overgrowth            | 47 |  |  |  |  |

vi CONTENTS

|   | 3.3  | Doping profiles                                   | 50  |

|---|------|---------------------------------------------------|-----|

|   | 3.4  | Conclusions                                       | 52  |

| 4 | Pur  | e dopant deposition for ultrashallow Si junctions | 55  |

|   | 4.1  | Introduction                                      | 56  |

|   | 4.2  | Pure dopant vs. conventional pn junctions         | 57  |

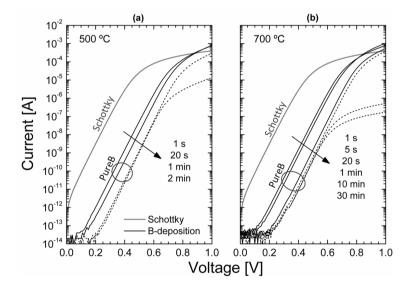

|   | 4.3  | PureB on Si                                       | 59  |

|   |      | 4.3.1 Deposition conditions                       | 59  |

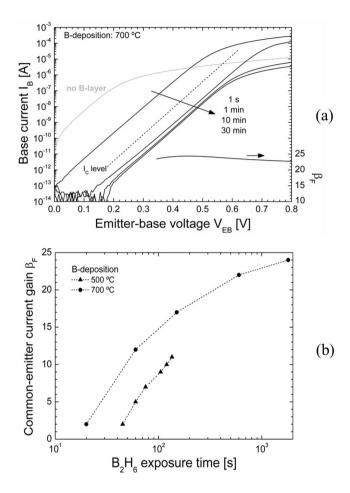

|   |      | 4.3.2 Electrical behavior                         | 60  |

|   | 4.4  | PureGa on Si                                      | 63  |

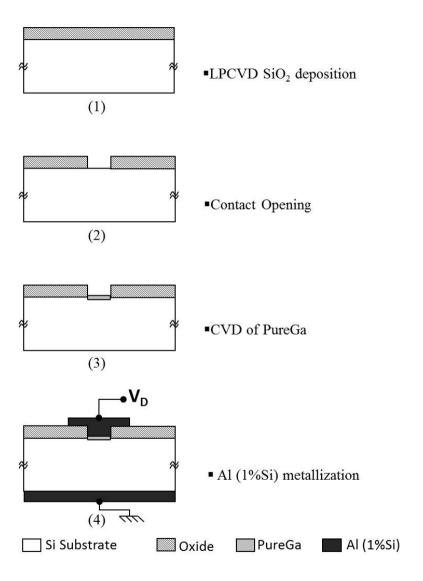

|   |      | 4.4.1 Fabrication process                         | 64  |

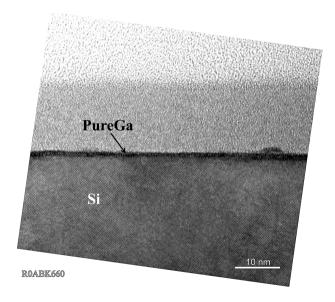

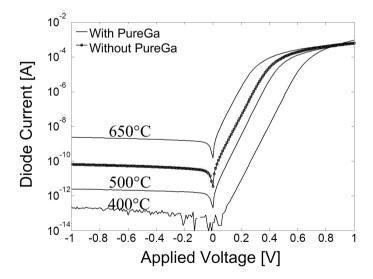

|   |      | 4.4.2 Electrical behavior                         | 66  |

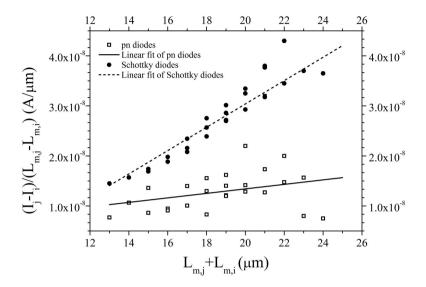

|   |      | 4.4.3 Perimeter and area current analysis         | 68  |

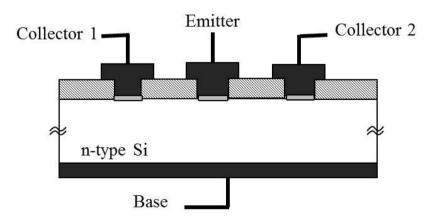

|   |      | 4.4.4 PureGa lateral pnp transistor               | 68  |

|   | 4.5  | Conclusions                                       | 71  |

| 5 | Ge-c | on-Si photodiodes                                 | 73  |

|   | 5.1  | Introduction                                      | 74  |

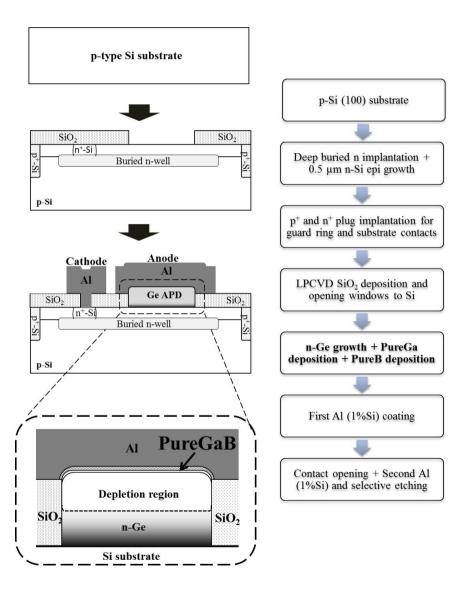

|   | 5.2  | PureGaB on Ge                                     | 75  |

|   |      | 5.2.1 Device fabrication                          | 75  |

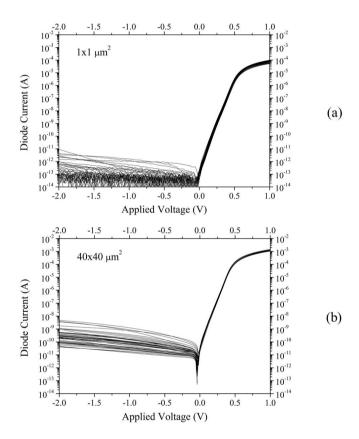

|   |      | 5.2.2 Electrical behavior                         | 77  |

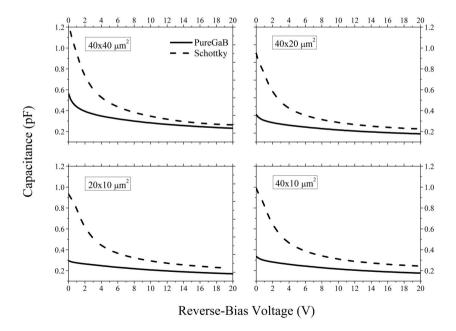

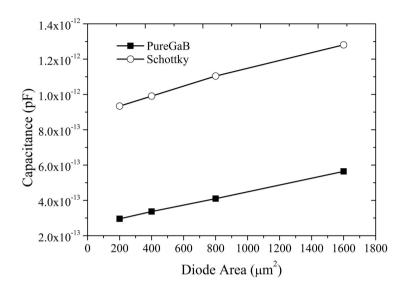

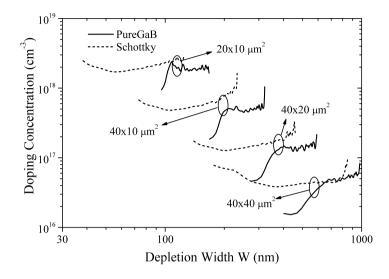

|   |      | 5.2.3 Perimeter and area current analysis         | 83  |

|   | 5.3  | Ge-on-Si APDs by PureGaB                          | 85  |

|   |      | 5.3.1 Fabrication process                         | 85  |

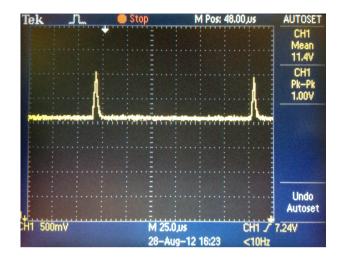

|   |      | 5.3.2 Optical/Electrical behavior                 | 85  |

|   | 5.4  | Conclusions                                       | 91  |

| 6 | Con  | clusions and recommendations                      | 95  |

|   | 6.1  | Conclusions                                       | 95  |

|   | 6.2  | Recommendations for future work                   | 97  |

|   | Bibl | iography                                          | 99  |

|   | List | of abbreviations                                  | 111 |

|   | Sum  | nmary                                             | 113 |

|   | Sam  | nenvatting                                        | 117 |

|   |      | of Publications                                   | 121 |

| CO | ONTENTS | Vii |

|----|---------|-----|

|    |         |     |

Acknowledgement 125

viii CONTENTS

## Chapter 1

## Introduction

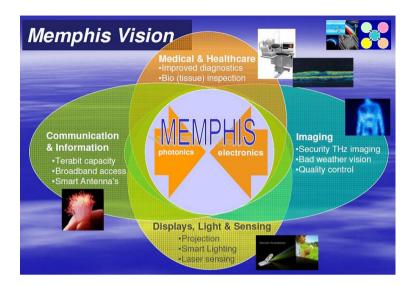

While the backbone of the semiconductor industry is silicon technology with a clear CMOS dominance, III-V semiconductors are playing an increasing role as suppliers of optical functions and high-speed electronics. While the latter application is holding ground but must constantly compete with the continual speed advances made in CMOS, the photonic industry is one of today's fastest growing industries driven by a very wide range of potential applications. It is therefore not surprising that there is a vibrant interest in merging photonics with electronics. In Holland, this endeavor crystallized in 2006 in the large SmartMix program MEMPHIS "Merging Electronics and Micro and nano Photonics in Integrated Systems". This program supported the view that "our future lives will be changed by an ambient, intelligent, comfortable and safe environment, by continuous health monitoring, by personal communication and by early detection of threats from nature, technical failure and human activities". These developments require new complex miniaturized devices with vastly increasing functionalities against the lowest possible cost price which cannot be fulfilled with present micro-electronic technology alone. The limitations of present electronics require a new massive converging technology based on complementary characteristics of micro- and nano-electronics and micro- and nano-photonics, utilizing the best of both technology worlds. A low cost combination of the processing power of classical CMOS IC technology, the high frequency capabilities of modern High Frequency (HF) electronics and the large bandwidth offered by integrated photonics creates the technology for novel broadband miniaturized "electronic-photonic devices". This will open the way to major new applications for the use of light: in medical diagnostics, for healthcare, entertainment, telecommunications, tracking and positioning. The MEMPHIS vision is illustrated in Figure 1.1.

Figure 1.1: The MEMPHIS vision of the impact of merging electronics with photonics.

The work presented in this thesis has formed the part of the technology developments promoted in the MEMPHIS program. The focus was placed on the merging of III-V semiconductor technology with Si technology. It by no means represents the first attempts in this direction; on the contrary, since the early days of integrated circuits it has been one of the holy grails for the semiconductor industry to grow high-quality III-V materials on Si. Nevertheless, in many ways it remains an elusive goal towards which this thesis has made its own specific contributions. The experimental basis was the development of a new tool for chemical vapour deposition (CVD) of III-V materials with an initial focus on gallium arsenide (GaAs). Conventionally, CVD of these materials is achieved from high concentrations of gases, including metal-organics, in equipment referred to as Metal-Organic CVD (MOCVD) epitaxy systems. The high gas concentrations, particularly of the highly toxic gases arsine (AsH<sub>3</sub>) and phosphine (PH<sub>3</sub>), mean that severe safety precautions must be implemented when running MOCVD. For this reason, most MOCVD III-V materials fabricated today are produced in dedicated laboratories not directly connected to Si cleanroom facilities.

In the MEMPHIS project the growth of both III-V compounds and Si/SiGe was combined in one and the same CVD system: the ASMI Epsilon 2000, a commercial CVD system designed for Si and SiGe epitaxy. The tool was especially equipped for the growth of III-V compounds in a manner that did not exclude

the use of the system also for Si-based depositions. For this purpose, the system was extended with a TriMethylGallium (TMGa) bubbler and extra tubing to allow the deposition of GaAs as well as the standard Si and SiGe depositions. Good results were achieved for epitaxial growth of GaAs with a very low AsH<sub>3</sub> concentration: 0.7% as compared to the at least ten times higher values normally used in MOCVDs. The correspondingly low concentration of TMGa means that the contamination of the reactor chamber with gallium or arsenic is so low that standard high-quality low-doped Si and SiGe depositions can still be performed in the same chamber. Moreover, the low gas concentrations permit the system to be run with the same safety precautions that apply to a normal Si/SiGe reactor. Thus there is no issue with respect to adding this equipment to a CMOS cleanroom environment.

The crucial feature that made it possible to reach the results presented in this thesis was the new availability of gallium (Ga), boron (B), germanium (Ge), silicon (Si), arsenic (As) and phosphorus (P) in one and the same epitaxial reactor. Deposition cycles containing layers of different combinations of these III, IV, V elements could then be performed without vacuum break. This proved important not only for the growth of good quality Ge and GaAs but also for the formation of junction diodes in these materials. In particular, the formation of p<sup>+</sup>n Ge-on-Si diodes of exceptional quality was facilitated by deposition of pure gallium (PureGa) and pure boron (PureB) to create the p<sup>+</sup>-region. The ideas leading to this solution leaned strongly on the success of PureB depositions to form nanometer-shallow p<sup>+</sup>n Si diodes. These are now extensively used as photodiodes for detecting beams that only penetrate a few nanometer into the Si such as vacuum-ultraviolet (VUV) light and electrons with energies below 1 keV [1, 2]. In the present work, similarly good results were achieved with PureGa deposition on Si to form p<sup>+</sup>n Si diodes. In all these diodes formed by pure dopant deposition, PureB/Ga for Si diodes and PureGa plus PureB (PureGaB) for Ge-on-Si diodes, the excellent electrical characteristics have been ascribed to the creation of a very high hole concentration at the interface between the semiconductor and the bulk dopant material. This is not seen in other ultrashallow diodes produced by techniques that only aim at damage-free doping of the semiconductor, for example, epitaxy of doped Si or Ge, or doping from a gas [3]. Therefore the terms PureB/PureGa/PureGaB have been introduced to underline that a solid layer of pure dopant material has been deposited.

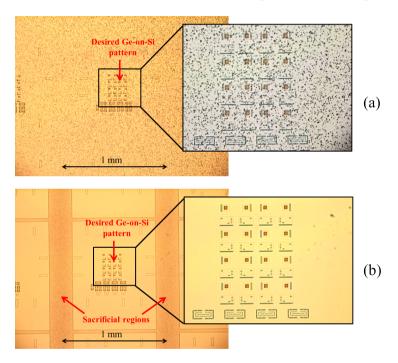

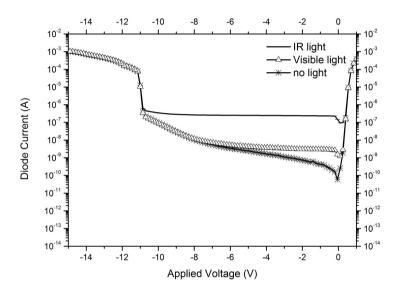

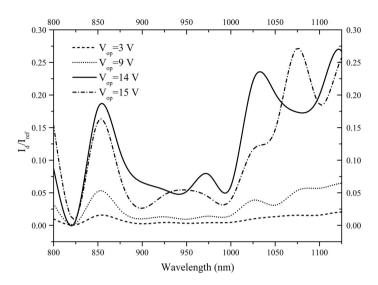

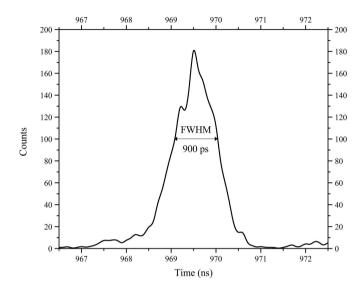

On the applications side, this thesis work has been directed towards the very challenging feat of fabricating Ge avalanche photodiodes (Ge APDs) on Si substrates. This was motivated by the good I-V characteristics obtained for the first

PureGaB Ge-on-Si diodes. Besides having a low dark current, they also displayed a clear breakdown curve that was proven to be suitable for infrared (IR) photon counting in Geiger mode. Compared to the PureB Si photodiodes, these Ge photodiodes are many times more complex to optimize. A new method was developed to grow high-quality, As-doped crystalline Ge in tens-of-micron large windows to the Si with only a 200 nm transition region to localize the misfit dislocations. However, both the Ge growth and the As-doping are subjected to strong CVD loading effects, i.e., the circuit layout will influence the geometry and doping distribution of the Ge-islands, which are factors that are decisive for the breakdown mechanism. Nevertheless, in view of the multitude of applications of sensitive infared detectors and imagers, gaining control of the Ge-on-Si growth is a very worthwhile endeavor and this thesis offers solutions to a number of the issues.

In the following, an overview on photonic materials and basics of semiconductor photodetectors is provided. Different photodiode technologies are reviewed with focus on their characteristics and special qualities. Also some of the unique properties and applications of Ge, which became the main vehicle for the work in this thesis, is studied with the focus on the processing and technological issues.

#### 1.1 Fundamentals of photodetection

The science of photonics includes the generation, emission, transmission, modulation, signal processing, switching, amplification and detection/sensing of light and it covers the whole light spectrum from ultraviolet over the visible to the near-, mid- and far-infrared. A variety of applications from telecommunications to displays involves photonic semiconductors. Photodetection and light emission, however, have always been two of the largest and most interesting application areas. Both photodetection and light emission in semiconductors work on the general principle of the creation or recombination of electron-hole pairs upon exposure to light. According to Albert Einstein, who won a Nobel prize for the discovery of the photoelectric effect [4], anytime a photon hits a conductor it can excite electrons. The same phenomena happens in a semiconductor. When a semiconductor material is illuminated by photons of an energy greater than or equal to its bandgap, the absorbed photons promote electrons from the valence band into excited states in the conduction band, where they behave like free electrons able to produce electrical current in the crystal structure under the influence of an intrinsic or externally-applied electric field. In addition, the positively-charged holes left in the valence band contribute to electrical conduction by moving from one atomic site to another under the effect of the electric field. In this way the separation of electron-hole pairs generated by the absorption of light gives rise to a photocurrent, which refers by definition to the fraction of the photo-generated free charge-carriers collected at the edges of the material by the electrodes of the photodetecting structure. The intensity of such a photocurrent at a given wavelength increases with the intensity of incident light.

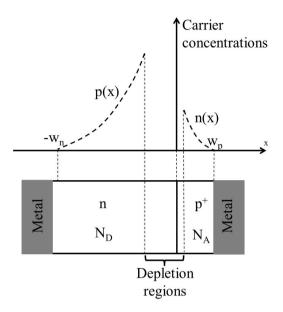

On this level we can distinguish between two large categories of photodetectors based on the nature of the electric field, which causes the charge separation of photogenerated electron-hole pairs: (i) photoconductors, which consist of a simple layer of semiconductor simply with two ohmic contacts, where the electric field leading to the collection of the charge-carriers is provided by applying a bias voltage between the contacts at either end, and (ii) photovoltaic photodetectors, which use the internal electric field of a pn or Schottky (metal-semiconductor) diode to achieve the charge separation. This last term covers pn junction photodetectors (photovoltaic structures consisting of a simple pn junction, and pin photodetectors which include a thin layer of semiconductor material between the p- and n-regions which is not deliberately doped), as well as all Schottky junction photodetectors (Schottky barrier photodiodes and metal-semiconductor-metal (MSM) photodiodes) [5].

Other optical devices similar to photodetectors are solar cells which also absorb the energy of light and turn it into electricity by generation of electrical carriers; and light emitting diodes (LEDs) which are basically the inverse of photodiodes, instead of converting light to a voltage or current, it converts a voltage or current to light. In the following, some properties of photonic semiconductors are presented and then details of some well-known types of photodiodes are given.

#### 1.1.1 Photonic semiconductor materials

The minimum energy of a photon that is required to generate an electron-hole pair in a semiconductor is defined as the work function and the number of electrons generated is proportional to the intensity of the light. The semiconductor photodetectors are made from different semiconductor materials such as Si, Ge and InGaAs. Each material has a characteristic bandgap energy  $E_g$  which determines its capability to absorb photons. The equation between  $E_g$  and cut-off wavelength  $\lambda_c$  is:

$$\lambda_c = \frac{1.24 \times 10^3 (nm)}{E_q(eV)} \tag{1.1}$$

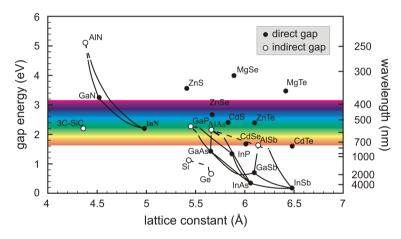

Semiconductors with smaller bandgaps can absorb larger wavelenghts of light. Figure 1.2 shows the bandgaps of different semiconductors with their corresponding wavelengths with respect to the visible light. The information in Figure 1.2 is summarized in Table 1.1 for some prominent photonic materials, their bandgaps , and cut-off wavelengths  $\lambda_c$  at room temperature (300 K).

Figure 1.2: Bandgaps as a function of lattice constant and corresponding wavelengths of different semiconductors.

Table 1.1: Important photodetector semiconductors, the bandgaps and corresponding photon wavelengths [6].

| Type   | $\mathbf{E}_g(\mathbf{eV})$ | $\lambda_c$ (nm) | Band                 |

|--------|-----------------------------|------------------|----------------------|

| Si     | 1.12                        | 1100             | Visible              |

| Ge     | 0.66                        | 1800             | Near-Infrared        |

| GaAs   | 1.42                        | 875              | Visible              |

| InGaAs | 0.73 - 0.47                 | 1700 - 2600      | Near-Infrared        |

| InAs   | 0.36                        | 3400             | Near-Infrared        |

| InSb   | 0.17                        | 5700             | Medium-Infrared      |

| HgCd   | 0.7 - 0.1                   | 1700 - 12500     | Near to Far-Infrared |

One of the important terms in qualification of a photonic semiconductor is

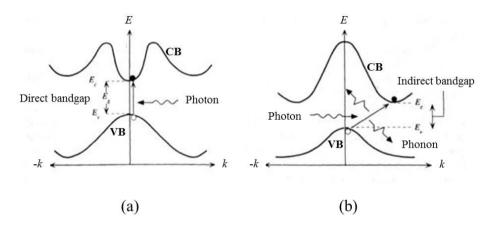

the light absorption coefficient. In order to have a good photonic device with high quantum efficiency (QE), the absorption coefficient of the semiconductor should be high enough for the majority of the photons to be absorbed in the active detector region. Above the bandgap (or below the corresponding cut-off wavelength) the absorption increases rapidly. For semiconductors with direct bandgaps such as GaAs and InGaAs this is rather easily obtained. The difference between direct bandgap and indirect bandgap semiconductors is shown in Figure 1.3. Light induced electron-hole pair generation in semiconductors with indirect bandgap requires both photon and phonon assisted transitions [7].

Figure 1.3: Photon absorption in semiconductors with a) direct and b) indirect bandgaps. Photon absorption in a semiconductor with an indirect bandgap requires phonon assisted transition.

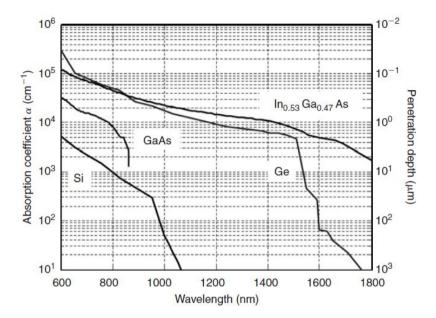

Figure 1.4 shows the absorption coefficient and penetration depth of photons with different wavelengths for four different semiconductors. For GaAs and In-GaAs, a penetration depth of 1  $\mu$ m is obtained for wavelengths below 800 nm and 1400 nm, respectively. A penetration depth of 10  $\mu$ m is found at 855 nm and 1850 nm, respectively.

Both Si and Ge are indirect semiconductors with a much weaker absorption directly above the bandgap. The corresponding cut-off wavelength for Si is 1100 nm. The  $10 \, \mu m$  penetration depth is only reached in the red ( $800 \, nm$ ) and the  $1 \, \mu m$  penetration depth in the visible ( $550 \, nm$ ). Despite this, Si detectors with good QE in the red and very near-infrared are fabricated with a large detector region and diffusion controlled carrier movement, but these detectors are inherently slower than III-Vs counterparts -depending on the design- and lack good responsivity in

Figure 1.4: Absorption versus wavelength for two direct bandgap (GaAs, In-GaAs) and two indirect bandgap (Si, Ge) semiconductors. [8]

the near-infrared wavelengths. Although Ge is also an indirect semiconductor its absorption curve looks very different. Below the cut-off at about 1800 nm a slight increase in absorption is seen as typical for the indirect bandgap but below 1600 nm a steep increase follows. This is a consequence of the lowest direct transition in Ge being slightly above (0.2 eV) the indirect transition (0.66 eV) whereas in Si the lowest direct transition (3.4 eV) is far above the indirect one (1.12 eV) [8]. One can distinguish three regions if we compare the absorption of Si and Ge. From the visible up to the very near-infrared (600-950 nm) the absorption in Ge is about 50 times stronger than in Si. That means that even in the visible, Ge is a superior detector material as compared to Si. In the near-infrared (950-1500 nm) the absorption in Si fades out (band edge at 1100 nm) and therefore the absorption in Ge is many orders of magnitude larger. Beyond 1500-1800 nm the absorption of Ge fades out which requires geometries to nevertheless absorb the light (resonant cavity, waveguide detector).

#### 1.1.2 p-i-n photodiodes

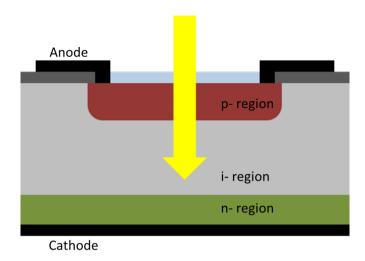

A p-i-n photodiode, also called pin photodiode, is a diode with a wide, lightly doped near intrinsic semiconductor region between a p-type semiconductor and an n-type semiconductor region. The p-type and n-type regions are typically heavily doped because they are used for ohmic contacts. Compared with an ordinary pn photodiode, a pin photodiode has a thicker depletion region, which allows a more efficient collection of the carriers and thus a larger quantum efficiency, and also leads to a lower capacitance and thus to higher detection bandwidth. In a pin photodiode most of the photons are absorbed in the intrinsic region, and generated carriers can efficiently contribute to the photocurrent. The pin photodiode does not have any gain, and for some applications this may be a disadvantage. Despite this, it is still the most widely used form of photodiode, finding applications in audio CD players, DVD players as well as computer CD drives. They are also used extensively in optical communication systems.

The pin photodiodes generally operate in reverse-bias in order to deplete the intrinsic region. A high reverse-bias can introduce a noise current which reduces signal to noise ratio, but pin diodes always have better performance for high-bandwidth and high-dynamic range applications than standard pn diodes [9]. Figure 1.5 shows a typical pin photodiode. The illumination window for a pin diode is usually on the p-region because the mobility of electrons is larger than holes and it provides better frequency response. The larger breakdown voltage of pin photodiodes in comparison to the pn diode allows it to be used with a voltage bias of up to 100 V which results in a faster response time in the nanosecond range, depending on the design [10].

For all applications ranging from optical communications to infrared sensing, high sensitivity and low noise are two important properties of pin photodiodes which are enabled by a low dark current of the device. There has been many studies of the dark current for different types of pin photodiodes [11–15]. Basically, the dark current is the combination of three components: (1) diffusion current, (2) generation-recombination current and (3) tunneling current.

**Diffusion current**, is produced by the thermal generation of electron-hole pairs in the intrinsic region and their diffusion toward the depletion region [6]:

$$I_{diff} \propto e^{-E_g/KT} \tag{1.2}$$

where K is Boltzmann's constant and T is the ambient temperature. From Equation 1.2 it is clear that semiconductors with lower bandgap have higher diffusion. One effective way to reduce the diffusion current is cooling of the device.

Figure 1.5: Schematic drawing of a pin photodiode. The blue layer is an antireflection coating.

**Generation-recombination current**, is the current produced due to presence of impurity trap levels inside the bandgap of semiconductor. Impurities and defects, form forbidden levels of energy inside the bandgap which induce the generation and recombination of carriers with energy smaller than  $E_g$ . This "trap-assisted" current is given by [6]:

$$I_{q-r} \propto W e^{-E_g/2KT} \tag{1.3}$$

where W is the width of the depletion region. Equation 1.3, shows that the generation-recombination current is proportional to the depletion width and so it increases with reverse-biasing [16], whereas the diffusion current in Equation 1.2 is bias independent. From this, one can conclude that for semiconductors with bandgaps lower than 1.0 eV the current is dominated by the diffusion current at room temperature.

**Tunneling current**, is generated when the electric field is so high (e.g. exceeds 10<sup>5</sup> V/cm) that carriers can tunnel through the valence band to the conduction band [16]. Tunneling usually occurs over narrow energy barriers and is given by [6]:

$$I_{tun} \propto EVexp\left(\frac{-\Theta\sqrt{m}}{E}E_g^{3/2}\right)$$

(1.4)

where E is the applied electric field, m is the effective mass of electrons and  $\Theta$  is a constant dependent on the tunneling barrier height. Semiconductors with

lower bandgaps have higher tunneling current. Tunneling is also dependent on the doping of the n- and p-regions while it has a weak dependency on the temperature with only a minor decrease in the breakdown voltage due to increase in  $E_g$ . Higher dopings of n- and p-regions results in narrower depletion widths and higher tunneling. In conclusion, the standard pin photodiodes that are fabricated based on semiconductors with low  $E_g$  (e.g. Ge and InGaAs) have higher dark current which is basically dominated by diffusion and tunneling currents while in pin photodiodes in high  $E_g$  semiconductors (e.g. Si and GaAs) the effect of generation-recombination current is higher and tunneling plays a less important role.

#### 1.1.3 PureB Si photodiodes

As explained in Section 1.1.1, despite the indirect bandgap of Si, it can still be considered as a good photonic material. It is the most common semiconductor in the electronics technology and its compatibility with different industrial needs is always of high significance. Pure dopant deposition of B on Si, also known as "PureB" technology that was developed in "Silicon Device Integration" group of Delft University of Technology offers an advance technique to fabricate nanometer-shallow junctions on Si with a damage-free junction [17]. The basic advantage of such diodes is that the photosensitive region of the junction is very ideal and very close to the Si surface and as a result, they are highly applicable in detection of low-energy and low-penetration beams. PureB has been demonstrated in several cutting-edge applications where the integration of high-quality ultrashallow junctions offer a solution to the performance challenges of Si photodetectors. This technology is attractive for a variety of applications: large-area high quality Si diodes, high-linearity varactor diode technology [18], EUV/VUV/DUV photodiodes [19] and low-energy electron photodiodes [20].

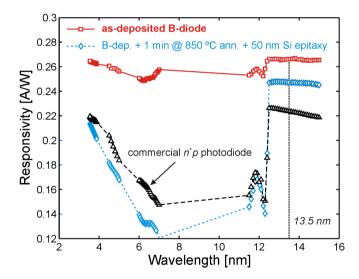

At the moment PureB photodiode detectors are being used in EUV wafer-steppers for monitoring the 13.5 nm light entering the alignment system from the source and for effectuating the actual wafer alignment to the mask. These detectors are also a demonstration of flexible integration schemes that have allowed low parasitic resistance and capacitance as well as on-chip combination with other electronic elements. With 2 nm-thick as-deposited PureB-layers as only front-entrance window the photodiode has a responsivity of 0.266 A/W, which is practically that of an ideal lossless system, 0.273 A/W [21]. Moreover, the responsivity degradation is negligible under high-power exposure. Extensive characterization of the PureB photodiodes has also been performed in the whole VUV range, including the deep-ultra-violet (DUV) wavelength of 193 nm that is

in demand for state-of-the-art optical lithography systems. For this wavelength there is a less than 6 nm penetration depth in Si. For VUV photodiodes fabricated with 700°C PureB layers, it has been demonstrated that the very high hole gradient right up to the surface, without roll-off, is very important for securing low leakage currents and high responsivity. This gradient repels electrons from the surface where they would otherwise recombine. Even when the PureB layer is driven-in by thermal annealing at temperatures up to 900°C, a high gradient is maintained up to the surface and, together with the damage-free nature of this doping technique, a high responsivity is maintained [22]. In future, the lithographic wavelength of choice may become 6.8 nm [23]. As shown in Figure 1.6, The PureB photodiodes also display high responsivity at this wavelength as compared to commercial Si detectors [24].

Figure 1.6: Measured EUV spectral responsivity of PureB diodes without and with a 1 min in-situ thermal anneal at 850°C and 30 nm epitaxial B-doped Si growth, compared to a commercial state-of-the-art n<sup>+</sup>p photodiode [24].

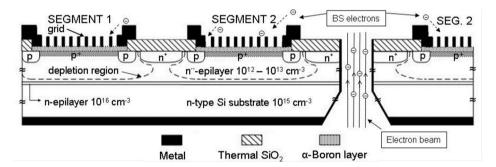

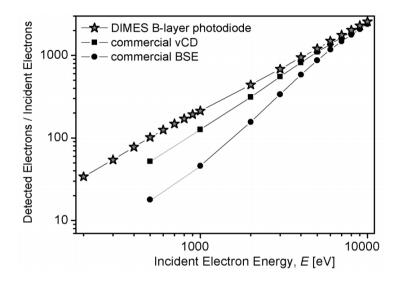

Another example of the versatility with which the PureB diodes can be integrated in detectors is the low-energy electron detectors developed for SEM imaging. A schematic cross-section of such a detector is shown in Figure 1.7 [20]. The front-entrance window is formed with the photosensitive depletion layer only being covered by a nm-thin p<sup>+</sup>-anode under an equally thin PureB layer. This has resulted in a record-high electron-signal-gain for electron energies below 1 keV down to 200 eV [25]. Figure 1.8 compares the performance of a PureB electron

detector with a commercially available back-scattered electron detector (BSE) and a low voltage high contrast detectors (vCDs) [20]. Going to lower deposition temperatures than the 700°C used in the applications up until now, is particularly interesting for increasing the integration flexibility. Below about 450°C it even becomes feasible to add the PureB to a fully processed CMOS wafer. Although equally good diode I-V characteristics have been obtained at temperatures down to 400°C there are more issues to be dealt with than for the 700°C deposition such as higher surface roughness, more pronounced loading effects, higher sheet resistance and probably also higher series resistance because effectively thicker layers must be used. Moreover, the optical responsivity and robustness as well as electrical degradation still need to be characterized.

Figure 1.7: Schematic cross-section of two neighboring photodiode segments of a PureB back-scatter detector designed for use in SEM imaging with high scanning speed. A through-wafer hole has been etched to form an aperture for the electron beam. Low capacitance is achieved by depletion of a 40  $\mu$ m deep n<sup>-</sup>-type epitaxial layer. To lower the series resistance a fine grid has been etched in Al metallization placed directly on the PureB layer covering the p<sup>+</sup> anode regions. This gives less than 2% loss of responsivity [20].

#### 1.1.4 Avalanche photodiodes

High-speed avalanche photodiodes (APDs) are widely used for many applications such as photon counting, laser pulse detection [26] and fiber-optic communication. In spite of the high operating bias, APDs can be designed for low noise operation [27] and with gain-bandwidth (GB) products in excess of 100 GHz [28–32].

In principle, an APD is a highly sensitive photodiode that exploits the photoelectric effect to convert light to electricity by providing a built-in first stage of

Figure 1.8: Measured electron signal gain for a PureB photodiode, a commercially available BSE detector and a low voltage high contrast detector (vCD) [20].

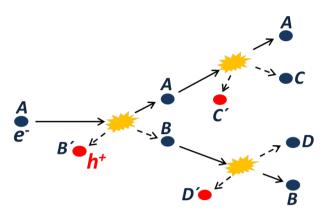

gain greater than unity through avalanche multiplication. This is obtained through the process of "impact ionization" by operating the photodiode at a sufficiently high reverse-bias voltage. The impact ionization process is illustrated in Figure 1.9. Under a localized electric field larger than about  $10^5$  V/cm [33], electron A gains sufficient kinetic energy to hit an atom in the crystal lattice and knock out an electron-hole pair B - B'. Electron A can move out and hit another atom and knock out electron-hole pair C - C', while electron B also gains sufficient energy to hit an atom and produce electron-hole pair D - D' and this process continues as an avalanche action.

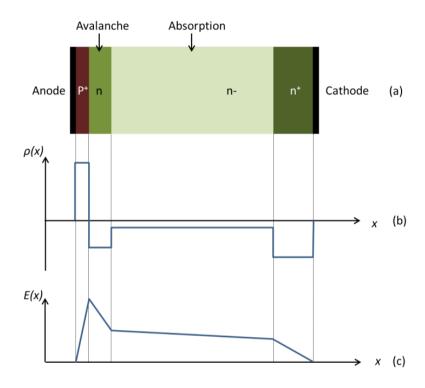

In Figure 1.10 the schematic structure is given for operation of a high speed and low noise APD. The electric field in the near intrinsic absorption layer is high enough for carriers to travel at saturated velocities, yet it is below the field where significant avalanching occurs and the tunneling current is negligible. The photo-generated electron-hole pairs then reach the multiplication layer which is thinner and with higher doping. In the multiplication layer, the electric field is high enough to cause impact ionization and hence achieve an avalanche gain that exceeds unity. In heterostructure APDs, the multiplication layer is fabricated with a higher bandgap semiconductor to further increase the electric field.

In ideal APDs, the total dark current  $I_d$  is a function of the multiplication

Figure 1.9: Impact ionization process

factor as follows [34]:

$$I_d = I_{dM} \times M + I_{d0} \tag{1.5}$$

where  $I_{dM}$  and  $I_{d0}$  are, respectively, the multiplied and the unmultiplied dark currents and M is the gain or avalanche multiplication factor. The multiplied dark current comes from the generation of carriers that takes place under the pn junction in the multiplication and transition regions where the electric field is high enough to generate impact ionization. While the unmultiplied dark current comes from the carrier-generations that are taking place at the absorption region, where the electric field is lower.

The gain or avalanche multiplication factor of an APD can be defined as the photocurrent of the diode generated by avalanche action divided by the unity gain photocurrent. At voltage breakdown of the APD, the multiplication factor M tends to infinity. An empirical relation between the multiplication factor M and reverse-bias V is given by [35]:

$$M = \frac{1}{1 - \left(\frac{V}{V_{br}}\right)^n} \tag{1.6}$$

where V is the applied reverse-bias and  $V_{br}$  is the breakdown voltage. The factor n is a constant depending on the semiconductor material and the temperature. Typical values for multiplication factors are in the order of at least 100 for Si APDs and 10-40 for Ge or InGaAs APDs [36].

Figure 1.10: a) A schematic illustration of an APD, b) the net space charge density across the photodiode and c) the field across the photodiode and the identification of absorption and multiplication regions

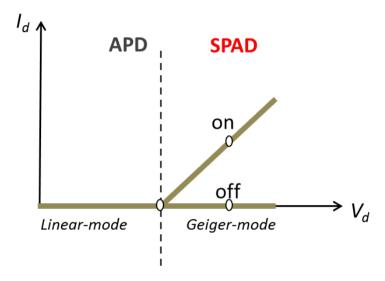

#### 1.1.5 Single photon avalanche photodiodes

Single photon avalanche photodiodes (SPADs) are identified as a class of APDs operating at a reverse-bias in which every single photon hitting the absorption region can generate an electron-hole pair that triggers an avalanche. In this operational mode, also known as *photon counting* mode, the APD is biased just above breakdown voltage where the avalanche multiplication factor is infinite, as a result the APD is able to detect very low intensity signals, in the scale of a single photon. Because the trigger nature of a photon counting APD, is similar to a Geiger-Muller counter of nuclear radiation, this mode of operation is also referred to as Geiger-mode operation [37]. It is important to note that in the photon counting mode when a photon is detected there is a dead-time before the next photon can be detected. For example, if  $10^6$  photons hit the detector at the same

time, only one pulse will be generated indicating that only 1 photon has been detected. However, if  $10^6$  photons were available for detection, photon counting would not be necessary, and a linear mode of detection would suffice. In other words, if there are a lot less photons (e.g. 25 photons per second), then photon counting would be required. Figure 1.11 shows the I-V characteristic of a SPAD in reverse-bias.

Figure 1.11: I-V characteristic of a photodetector in reverse-bias for APD and SPAD modes

The excess bias voltage  $V_e$  is defined as the voltage above breakdown that the detector is operating in Geiger mode:

$$V_e = V_{op} - V_{br} \tag{1.7}$$

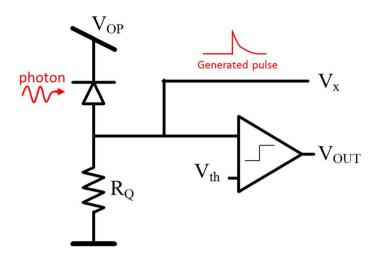

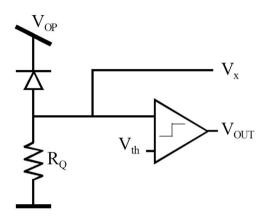

At a given temperature, as the excess bias increases the probability of break-down goes higher. This excess bias voltage causes high electric fields across the depleted region of the photodiode that may cause an avalanche current when the interaction of a photon or a thermal event creates electron-hole pairs. This current is then used to initiate an output pulse to indicate that a photon has been detected. In order to detect the next photon, the avalanche current must be quenched by pulling the SPAD bias voltage below breakdown again, and then resetting it at the excess bias voltage. The time it takes to reset the SPAD to its over-voltage is the "dead-time" [38]. Figure 1.12 shows a simple passive quenching circuit.

Figure 1.12: SPAD passive quenching circuit

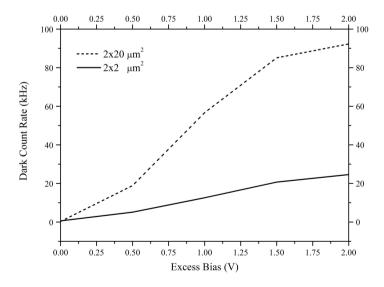

In addition to photon-induced avalanche, thermally-generated carriers (through generation-recombination processes within the semiconductor) can also trigger the avalanche process. Therefore, it is possible to observe output pulses when the SPAD is in complete darkness. The number of these pulses generated in darkness per unit time is known as the dark count rate (DCR). The most fundamental trade-off in the operation of SPADs is between DCR and photon detection efficiency (PDE). Increasing the avalanche probability by operating at larger excess bias increases the probability that both photo-excited and dark carriers generate avalanche; therefore, both PDE and DCR increase. Moreover, if electric field-mediated dark carrier generation is significant at the operating conditions of interest, the DCR will exhibit a faster increase with excess bias than PDE [39,40].

#### 1.2 Properties of germanium

Germanium is a key material for many applications and it has always been of interest for semiconductor technology. Needless to say that world's first point contact transistor that was demonstrated by Shockley, Bardeen and Brattain in December 23rd, 1947 at Bell laboratories [41], was a Ge slab, into which a plastic wedge pressed two strips of gold foil (Figure 1.13). Recently Ge regained a lot of attention in the semiconductor industry because of its attractive properties

which can lead to solutions for some of the major roadblocks that Si technology is facing in the development of advanced nano-scale electronic devices. Today, Ge is a well-known material for its high mobility, low energy bandgap and for the match of its lattice constant with some of the III-V semiconductors such as GaAs. Ge is widely applied in infrared optoelectronics, as a substrate for epitaxy of III-V multi-junction solar cells, for SiGe alloying in state-of-the-art CMOS technology, in radiation-hard materials for the fabrication of nuclear-radiation detectors, and it is playing a major role in high performance fiber-optic systems. Also the transport properties of Ge are very favorable compared with other semiconductors because of its high hole mobility (Table 1.2). Just like any other semiconductor, most of the interesting properties of Ge stem from point defects and impurities which provide for the local resistivity, the doping type and density. In the following Sections some properties and applications of Ge that were major motivations for the works of this thesis will be described in more detail.

Figure 1.13: The first point contact transistor that was based on Ge (Bell Labs 1947) [41].

|                     | Ge   | Si    | GaAs |

|---------------------|------|-------|------|

| Electrons $(\mu_n)$ | 0.39 | 0.15  | 0.85 |

| Holes $(\mu_p)$     | 0.19 | 0.045 | 0.04 |

Table 1.2: Mobility of Ge, Si and GaAs in  $m^2/V - s$

#### 1.2.1 Infrared detection

One of the unique properties of Ge is its small bandgap as compared to most other semiconductors. The bandgap of 0.66 eV which corresponds to a cut-off wavelenghts of around 1800 nm makes Ge a very interesting photonic material for infrared applications. High absorption of light with wavelenghts from visible to near-infrared can be achieved if the detector is made of Ge.

For growing Ge on Si there are technological problems such as the lattice mismatch of Ge to Si and the lack of good Ge oxide. Nevertheless, there are plenty research areas on Ge-on-Si detectors, even as photon counters. Highly sensitive Ge detectors in near-infrared can be very interesting for applications such as clear night vision in absolute darkness. Ge photodetectors have also been shown to be operational in the far-infrared light spectrum [42]. The far-infrared part of the spectrum is crucial for the study of many astrophysically important objects.

#### 1.2.2 Dopants in Ge

Doping in Ge- just like in Si- is normally achieved by Group III (p-type) or Group V (n-type) impurities, which are characterized by a high maximum solubility  $(S_{max})$  up to a few times  $10^{20}$  atoms/cm<sup>3</sup> [43]. Such dopants are especially useful as shallow-level dopants. Other impurities like the transition metals have a much lower  $S_{max}$  and generally act as generation-recombination centers in the semiconductor, forming deep levels in the bandgap. In other words, metal impurities can be centers of leakage current generation. For these and other reasons, both shallow and deep level impurities in semiconductors have been investigated in the fifties [44,45]. The maximum equilibrium solubility of the common dopants in Ge and the expected sheet resistance for a diffusion (junction) depth  $x_j$  of around 100 nm are summarized in Table 1.3 [3]. This sheet resistance is an important technological parameter, which can be used to determine the suitability of dopants for shallow junction formation in Ge devices. Based on these data, Ga and P are the most promising dopants for Ge. Nevertheless, to better un-

derstand the doping behavior in Ge one has to study the diffusion of Group III (p-type dopants) and Group V (n-type dopants). Self-diffusion in Si and Ge is the slowest process. With respect to impurities, a distinction is made between slow diffusers, which are up to 100 times faster than self-diffusion and fast diffusers, which follow generally an interstitial mechanism. From Figure 1.14 it can be seen that Group III dopants are among the slow diffusers [46], while Group V impurities are typically 100 times faster. In the following, solubility and diffusivity of few famous dopants of Group III and V will be summarized.

Table 1.3: Maximum equilibrium solubility of common dopants in Ge and corresponding calculated sheet resistance for a junction depth indicated in the last column

| Dopant element | Max. solubility (at./cm <sup>3</sup> ) | R <sub>s</sub> (Ohm/sq.) | $\mathbf{x}_{j}$ (nm) |

|----------------|----------------------------------------|--------------------------|-----------------------|

| В              | 5.51018                                | 315                      | 140                   |

| Ga             | 4.91020                                | 34                       | 115                   |

| P              | 2.01020                                | 42                       | 92                    |

| As             | 8.11019                                | 79                       | 120                   |

| Sb             | 1.21019                                | 163                      | 100                   |

#### Boron

B has an equilibrium solubility of around  $5\times10^{18}$  atoms/cm<sup>3</sup> at  $850^{\circ}$ C. Higher activated concentration of impurities up to around  $5\times10^{20}$  atoms/cm<sup>3</sup> -as the peak of electrically active concentration- is reported using rapid thermal anneal (RTA) steps [47]. However, recent studies confirm the low diffusivity of B in Ge, both under furnace anneal or RTA. B diffusion usually leaves a long diffusion tail in the profile inside Ge. The observed tail looks very similar to implanted B in Si where it is known that the predominant contribution to the tails is channeling rather than diffusion. However, radiation enhanced diffusion, can not be ruled out [48]. Such diffusion occurs when an ion-implantation is performed at elevated temperatures with an enhancement factor of several orders of magnitude, as compared with a room temperature implantation followed by an anneal at the same temperature. The enhancement is a result of higher than equilibrium concentration of vacancies under the higher temperature conditions.

Figure 1.14: Diffusivities of impurities in Ge and Ge self-diffusion [46].

#### Aluminum

With a high solid solubility of around  $4\times10^{20}$  atoms/cm<sup>3</sup>, Al is known to be a suitable p-type dopant for Ge. Al profiles also suffer from tailing, although no radiation-enhanced diffusion has been noted in this case [49]. Another problem with Al is its strong out-diffusion behavior which makes it critical to avoid reactions with oxygen and formation of Al<sub>2</sub>O<sub>3</sub>.

#### Gallium

The maximum solubility of Ga in Ge is around  $5\times10^{20}$  atoms/cm<sup>3</sup>, which is higher than for both Al and B. The diffusion of Ga is slightly smaller than Al [50], however, it still suffers from tailing effect in the doping profile, when the annealing temperature is above 650°C [51]. In general, due to low diffusion coefficient and high solid solubility, Ga seems to be the most promising p-type dopant for formation of pn shallow junctions in Ge.

#### Arsenic

As has a high solubility of around  $10^{20}$  atoms/cm<sup>3</sup> and therefore seems a suitable candidate for n-type doping. It has been shown that optimal n-type doping electronic performance can be obtained by As. Among P, As and Sb, only As shows up 100% activation at  $500^{\circ}$ C furnace anneal [52]. Also the tailing problem is less effective when forming the doping profile of As, as compared to other n-type dopants.

#### **Phosphorus**

The doping profile of P in Ge shows a tailing problem at annealing temperatures above  $550^{\circ}$ C, which is a drawback if shallow  $n^{+}p$  junctions are to be fabricated. The other problem with P as an n-type dopant is the out-diffusion during subsequent annealing [52]. A SiO<sub>2</sub> cap layer is usually utilized to prevent this from happening [52]. Diffusion of P in Ge increases significantly at large concentrations above  $10^{19}$  atoms/cm<sup>3</sup>.

#### **Antimony**

Compared to As, antimony (Sb) has serious disadvantages. It has smaller solubility than As (around 10<sup>19</sup> atoms/cm<sup>3</sup>) and a higher diffusivity than P or As [52] and also a high tendency to out-diffuse. All these make Sb less favorable as an n-type dopant in contrast with As and P.

#### 1.2.3 Ge as III-V epitaxy template

Direct growth of GaAs on Ge can be used for many III-V applications. The lattice mismatch of only 0.07% between Ge and GaAs (see Figure 1.2), allows the epitaxial growth of high quality GaAs on Ge utilizing metal organic chemical vapor deposition (MOCVD) techniques. Ge substrates are highly preferable over GaAs substrates, because of high crystallographic perfection, high mechanical strength and better recyclability. These advantages have led to the major use of Ge as a substrate for GaAs/Ge solar cells for telecommunication satellites [53], as well as other GaAs related devices different from solar cells. Also the integration of Ge PMOS with GaAs NMOS is a very attractive replacement for fast Si CMOS structures [54]. Combining GaAs as a very high electron mobility n-channel with a Ge p-channel on the same Ge substrate would yield very high mobility

structures. Especially Ge-on-Insulator (GOI) wafers<sup>1</sup> in advanced semiconductor technology are of interest, not only to allow III-V integration to mature Si devices but also to provide novelties such as III-V and Ge on Si substrates.

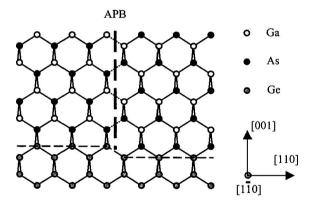

In general, lattice mismatch does not significantly degrade the quality of GaAs/Ge epitaxy; however compound semiconductor growth on an elemental substrate presents a somewhat increased complexity compared to homogeneous growth. Here this is because of the polar nature of GaAs as compared to the non-polar nature of the Ge substrate [56]. Due to the inequivalence of two facecentered-cubic (fcc) sublattices, the zinc-blende crystal structure of GaAs and other III-V compounds possesses lower symmetry than the diamond cubic structure. As a result, when GaAs is nucleated on a Ge substrate, two sublattice orientations are possible, each rotated 90°C. When both GaAs orientations are nucleated on a Ge surface, distinct domains of each sublattice, separated by antiphase boundaries (APBs) may propagate into the GaAs epilayer as illustrated in Figure 1.15 [57]. These boundaries between two different antiphase domains consist of electrically very active Ga-Ga and As-As bonds, which act as strong scattering centers and inhibit the free charge carrier flow with high mobility. As a result, any effort to grow device quality GaAs/Ge, must overcome the challenge of antiphase disorder.

Figure 1.15: A GaAs APB nucleated by the sublattice displacement induced by a single atomic-layer step lying on the (001) Ge surface. The bold dashed line marks the wrong nearest-neighbor bonds lying on the plane of the APB [56].

<sup>&</sup>lt;sup>1</sup>Germanium-on-insulator wafers are gaining attention as a high mobility material with the on-insulator advantages, potentially an ideal material platform to further boost the transistor performance. Its mechanical stability over fragile and heavy Ge bulk substrates is another practical advantage for processing in the current Si device lines [55].

#### 1.3 Outline of this thesis

The work presented in this thesis is focused on technological development of a CVD system (ASMI Epsilon 2000) from depositions in groups III, IV and V of the periodic table. The main motivation for this research is to merge alternative semiconductors with standard Si technology. Such techniques are advantageous when special properties of a specific semiconductor is needed together with routine IC technologies such as CMOS. The goal here is to introduce methods that are applicable in electronics/photonics industry for fabrication of different high-quality photodetectors on Si substrates.

In the Introduction Chapter, firstly, the important properties and applications of different photonic materials are reviewed and important types of photodetectors as well as some basic theoretical explanations are delivered. In the second part, the focus is put on Ge, which is playing the most important role in this work. The properties and applications of Ge are discussed in details. The knowledge delivered in this part is highly useful throughout this thesis.

In Chapter 2, epitaxial growth of GaAs by CVD system is characterized. The ASMI Epsilon 2000 CVD reactor which was firstly a standard system for epitaxial growth of Si and SiGe is introduced in this Chapter. The reactor is further modified with extension of a TMGa bubbler system for deposition of GaAs. It is shown in this Chapter that this CVD reactor is applicable both for Si/SiGe and GaAs processing. The characterizations over epitaxial growth of intrinsic, Si-doped and Ge-doped GaAs is delivered in this Chapter.

Chapter 3, introduces a strong and applicable method to selectively grow crystalline Ge on Si substrates. Different characterizations are given over the quality, selectivity and uniformity of this method. It is shown that the quality of the grown Ge on Si is good enough for fabrication of high-quality electronic devices.

In Chapter 4, pure dopant deposition of pure boron (PureB) and pure gallium (PureGa) on Si substrates is studied. It is shown that both methods are highly useful in fabrication of advance pure dopant p<sup>+</sup>n diodes on Si. Such diodes, with ultrashallow junctions and good-quality interface are proven highly useful in detection of low power and low penetration photonic signals. Both PureB and PureGa types of diodes are characterized in this Chapter and their exceptionally good electrical characteristics are presented.

In Chapter 5, the crystalline germanium growth technique of Chapter 3 and PureB/PureGa technologies of Chapter 4 were merged together to introduce a novel technique for fabrication of Si based ultrashallow Ge diodes. The idea is to first grow crystalline Ge selectively on Si substrates and then implement the pure

dopant junction by depositing both PureB and PureGa technologies. The term PureGaB is introduced in this Chapter for this method to create Ge ultrashallow junctions. It is shown that such Ge diodes can be used as high-quality photodetectors that works in infrared range of light spectrum. Ge single photon detectors are fabricated and a summary of their characterization is given in this Chapter.

Chapter 6 summerizes the main conclusions of this thesis and provides a number of recommendations for future work.

## Chapter 2

## Gallium arsenide epitaxial growth

For the experimental research in this thesis, a commercial Chemical Vapor Deposition (CVD) system, the ASMI Epsilon 2000 designed for Si and SiGe epitaxy, has, for the first time, been equipped for chemical vapor deposition of Ga compounds in a manner that does not exclude the use of the system also for Si-based depositions. With the new system, GaAs epitaxy has been achieved on GaAs substrate wafers by the decomposition of trimethylgallium (TMGa) and arsine (AsH<sub>3</sub>) in the reactor at reduced pressure and at a temperature of 600°C. A low AsH<sub>3</sub> concentration, 0.7% in H<sub>2</sub>, is used as one of the precursors, which permits the system to be operational with the same standard safety precautions.

In this Chapter, an overview is firstly given of the functions of the conventional Si/SiGe CVD reactor with modifications. Then details and conditions for the growth of high-quality intrinsic, Si-doped and Ge-doped GaAs epitaxy are provided. Finally, some brief experiments with GaAs epitaxy on Si substrates are described.

#### 2.1 Introduction

GaAs is potentially of great importance for many high-speed electronics and optoelectronics devices [58]. It is recognized as a material with a large electron mobility that is suitable for high-speed electronics and with a direct bandgap that is perfectly applicable for fabrication of light emitting diodes (LEDs), laser diodes (LDs), photodetectors and waveguides. Now, GaAs is the basis of several billion dollar worldwide industry for high-frequency, high-speed electronics and

optoelectronics and GaAs epitaxial growth techniques are playing an important role in this industry. The use of such techniques allows more flexibility in the growth and placement of semiconducting layers and dopants than is achieved by other approaches such as bulk crystal growth, ion implantation and diffusion [59].

Metal-organic CVD (MOCVD) and molecular beam epitaxy (MBE) are the two major processes of GaAs epitaxial growth which can meet the extremely stringent material requirements of advanced designs. Both MOCVD and MBE produce high-quality materials with similar purity, mobility, and photoluminescence properties, but MOCVD is more suitable for large-scale production since MBE requires extremely low pressure and has low deposition rates. In addition, MOCVD appears to produce better heterojunction bipolar transistor structures. Nevertheless, MBE still has two advantages: better film-growth control and more abrupt interfaces [60].

In the last few years, different MOCVD methods for epitaxial growth have been developed to such high level that excellent thin GaAs layers can be grown with good quality and growth rate control [61–65]. However, all these methods use reactors that are specially designed for GaAs and other III-V families, and they are not compatible with Si processing. So, the ability of merging standard MOCVD techniques for III-V semiconductors and Si epitaxy in one single reactor is new and could be of great interest for integration of III-V materials and Si devices. For this purpose, a standard commercial Si/SiGe CVD system has been modified to allow the deposition of III-V semiconductors such as GaAs and GaN in addition to the standard Si and SiGe depositions.

#### 2.2 Metal-organic CVD system

MOCVD is a specialized area of CVD techniques. The first reported use of MOCVD was in the 1960s for the deposition of indium phosphide (InP) and indium antimonide (InSb). The early experiments demonstrated that deposition of critical semiconductor materials could be obtained at lower temperature than conventional thermal CVD and that epitaxial growth could be successfully achieved. Metal-organics are compounds in which the atom of an element is bound to one or more carbon atoms of an organic hydrocarbon group. The term metal-organic is used somewhat loosely in CVD terminology, since it includes compounds of elements, such as Si, Ge, As and P that are not considered metallic. To conform to what appears to be a well-established tradition, such non-metal compounds will be included also as metal-organics [60].

The growth chamber of a conventional MOCVD system consists of four

zones: (1) precursor injection, (2) mixing, (3) boundary layer and (4) substrate surface. In the precursor injection zone, the precursor gases - including metalorganics - with the carrier gas are set with the proper flow and injected into the growth chamber or in the main manifold. In the mixing zone, the precursor gases are then mixed in the gas phase. It is important to have a uniform mixture of the gases without creating turbulent flow. If the mixing occurs in the chamber, the precursor gas stream experiences an abrupt change from the small cross-sectional area tubing in the lines to the large cross-sectional area and volume growth chamber during the mixing process. Therefore, mixing the gases in the manifold before injection to the reactor chamber can be advantageous. When the precursor gas stream enters the boundary layer zone, precursors are transferred mainly via diffusion onto the surface. In this zone, homogeneous reactions, such as vapor-phase pyrolysis, can also occur, possibly with a higher efficiency than in the mixing zone due to the higher temperature in this zone. Besides the diffusion of precursors onto the substrate surface, thermal convection can also occur, which can cause premature reactions and result in depleted precursor concentrations near the substrate surface. Such thermal convection-driven effects need to be minimized by careful reactor chamber design. On the substrate surface (the last zone) where surface reaction kinetics are important, the adsorption of pyrolyzed precursors, surface diffusion of atoms, chemical reactions and desorption of products occur to complete the crystal growth process [66].

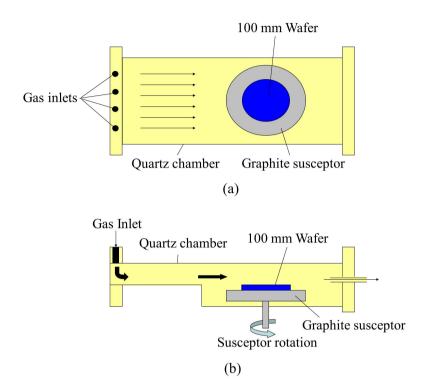

The epitaxial growth procedure that is described here is carried out in the ASMI Epsilon 2000 CVD system, mainly used for the epitaxial growth of Si and SiGe alloys. It is a single-wafer (100 mm) system with a quartz chamber and a rotating graphite susceptor and is equipped with integrated heating lamps to grow layers at temperatures up to 1200°C at atmospheric and reduced pressures. The gas flow in the chamber is laminar, parallel to the surface of the rotating wafer. The schematic diagram of the CVD reactor is shown in Figure 2.1.

The standard precursor gases of the system for different epitaxial growth and doping are listed in Table 2.1. The important extension of the system is a trimethylgallium  $[(CH_3)_3Ga, TMGa]$  bubbler and an extra gas line to allow the MOCVD of Ga as well as III-V semiconductor compounds such as GaAs and GaN in addition to the standard Si and SiGe CVD.  $H_2$  carrier gas is bubbled through the TMGa and the ratio of process and carrier gas is sensed and controlled by a state-of-the-art Lorex Piezocon binary gas concentration sensor. The system is also equipped with dilution setups which consist of additional mass flow controllers to further dilute the gas concentrations of the dopant precursor gases up to 20,000 times with  $H_2$  gas.

Figure 2.1: A schematic diagram of the (a) top view and (b) side view of the CVD reactor.

## 2.3 GaAs epitaxy

The precursor gases used for MOCVD of GaAs epitaxy in this research are TMGa and AsH<sub>3</sub>. These two gases are known as the most popular precursor gases for GaAs epitaxial growth with MOCVD [60]. The chemical reaction during the growth of intrinsic GaAs is:

$$(CH_3)_3Ga + AsH_3 \rightarrow GaAs + 3CH_4 \tag{2.1}$$

The crystal quality of the GaAs layers was analyzed by differential interference contrast microscopy (DIC). From this analysis, it appears that defect-free epitaxial GaAs on GaAs substrates is achieved. Also Si and Ge doping profiles of the GaAs during epitaxy are attainable by using the methylsilane (CH<sub>3</sub>SiH<sub>3</sub>) and germane (GeH<sub>4</sub>) gas lines that are already standard accessories of the MOCVD equipment. In this Section, the general description is given of the conditions for

| Precursor      | Molecular formula                | Concentration | Deposition |

|----------------|----------------------------------|---------------|------------|

| dichlorosilane | SiH <sub>2</sub> Cl <sub>2</sub> | 100%          | Si         |

| germane        | $GeH_4$                          | 2%            | Ge         |

| diborane       | $\mathrm{B_2H_6}$                | 0.02%         | В          |

| phosphine      | $\mathrm{PH}_3$                  | 0.5%          | P          |

| arsine         | $AsH_3$                          | 0.7%          | As         |

| methylsilane   | $SiH_3CH_3$                      | 0.2%          | C/Si       |

| TMGa bubbler   | $(CH_3)_3Ga/H_2$                 | -             | Ga         |

Table 2.1: Precursor gases of the ASMI Epsilon 2000 CVD system with their molecular formulas, concentrations and deposition material.

growing intrinsic, Si-doped and Ge-doped GaAs and the characterization of these layers.

#### 2.3.1 Characterization

For the GaAs epitaxial growth here, a low  $AsH_3$  concentration is applied: 0.7% as compared to the at least ten times higher values normally used in MOCVD equipment. This has the advantage that the severe safety precautions usually associated with MOCVD systems need not be implemented. The obvious effect of using a very low  $AsH_3$  concentration is the correspondingly low growth rate. Nevertheless, GaAs growth rates of 0.5 to 5 nm/min have been achieved, with the growth rate increasing as the TMGa and  $AsH_3$  concentrations are increased. Such values are acceptable for many of today's device applications for which layers in the 100 nm range are required.

GaAs epitaxial growth on GaAs substrates is performed at a pressure of 107 mbar (80 Torr) and at a temperature of 650°C. First, a baking step at 650°C is carried out in  $\rm H_2$  ambient for 4 minutes in order to remove the native oxide. Then the mixture of the TMGa and AsH<sub>3</sub> from the main manifold is injected into the chamber with AsH<sub>3</sub>/TMGa ratios from 20 to 40 in the gas phase.

In order to make the ASMI Epsilon 2000 CVD reactor applicable for both GaAs- and Si-related processes, after several GaAs growth cycles, the system can be cleaned by performing a few HCl cleaning steps<sup>1</sup>. Si epitaxy with dopant

$<sup>^{1}</sup>$ Each HCl cleaning step is performed by first depositing a thin Si layer on the susceptor using SiH $_{2}$ Cl $_{2}$  as precursor gas and then introducing HCl gas to the reactor chamber at  $1050^{\circ}$ C for 20 seconds to etch the coatings on the sidewalls as well as the deposited Si layer.

concentrations as low as  $10^{15}$  atoms/cm<sup>3</sup>, is then possible to be grown. An example of a situation where the ability to grow Si and GaAs layers in the same system can be of advantage, is the growth of GaAs on Si substrates by using an intermediate Ge or SiGe buffer layers. Since the wafers can remain in the same reactor during the SiGe/GaAs growth sequence, there is no need for cleaning steps in between the two layers to remove the native oxide.

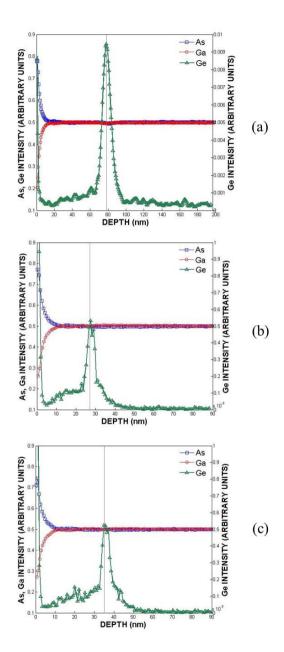

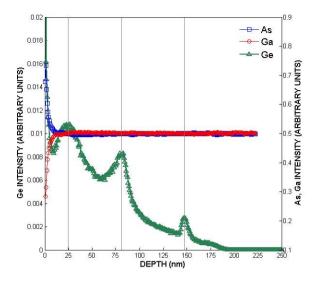

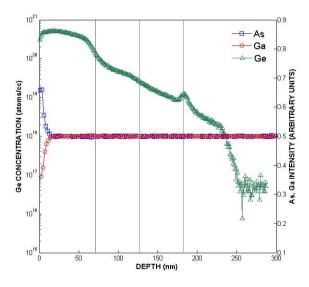

The AsH<sub>3</sub>/TMGa ratio was found not to be very critical. Figure 2.2 shows the plots from typical SIMS analysis carried out on GaAs epitaxial layers on GaAs substrates. The layers have been deposited with different AsH<sub>3</sub>/TMGa ratios. Ratios of 20, 30 and 40 have been investigated which proves that values from 20 - 40 in the gas phase all gives stoichiometric GaAs growth. However, different ratios still result in different growth rates. In all samples, a Ge marker has been used before commencing the GaAs growth so that the interface between the substrate and the epitaxial layer is accurately monitored by the SIMS. For this reason, In the beginning of each layer growth process, a 2-second pulse of low flow GeH<sub>4</sub> is introduced together with GaAs precursor gases which forms a delta doping in the GaAs epitaxy at the interfaces.

An experiment in which the AsH<sub>3</sub> and TMGa concentrations were varied while the AsH<sub>3</sub>/TMGa ratio was kept constant is shown in Figure 2.3. Three layers were grown consecutively. A Ge marker indicates where a decrease in concentration is implemented as going towards the surface. The first layer with the highest gas flows has a growth rate of 5 nm/min; the second and third layers have rates of 3 nm/min and 0.5 nm/min respectively. The AsH<sub>3</sub>/TMGa ratio was set to be 30 and the stoichiometry of Ga and As, as shown in Figure 2.3, is still perfect for all three cases with different gas flows and growth rates.

### 2.3.2 Doping profiles

For doping in GaAs, two possibilities are available in the ASMI Epsilon 2000 reactor: Si and Ge. They both are well-known n-type impurities for GaAs. Their incorporation in GaAs when epitaxial growth is mainly based on replacing Ga atoms in the lattice, which leads to n-type doping in GaAs [67, 68]. Both Si and Ge-doped GaAs epitaxial layers have been achieved in this research, using 0.1% CH<sub>3</sub>SiH<sub>3</sub> and 2% GeH<sub>4</sub> gases respectively, in addition to the main GaAs precursors. The lines for these two gases are part of the standard equipment of the reactor.

2.3 GaAs epitaxy 33

Figure 2.2: SIMS plots for GaAs epitaxial growth with AsH $_3$ /TMGa ratios of (a) 20, (b) 30 and (c) 40 in the gas phase with perfect stoichiometry at a temperature of 650°C.

Figure 2.3: SIMS profile of three intrinsic GaAs epitaxial layers at a temperature of 650°C with growth rates of 5, 3 and 0.5 nm/min, respectively. The Ge markers have been introduced for the determination of interfaces between layers. The same concentration of As and Ga indicating good stoichiometry in the deposited layers.

#### Si-doped GaAs

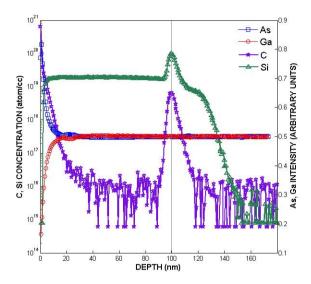

Figure 2.4 shows a SIMS profile of a 100 nm Si-doped GaAs epitaxy with a dopant concentration of  $2 \times 10^{19}$  atoms/cm<sup>3</sup>. It is interesting to note that the carbon (C) concentration in the GaAs epitaxy is lower than that of the substrate, in spite of the fact that methylsilane decomposition results in an introduction of the same amount of Si and C. Consequently methylsilane can be considered to be a good alternative for silane (SiH<sub>4</sub>), the standard dopant precursor for Si-doped GaAs epitaxy.

The Si spike at the interface in this and other SIMS plots is most probably caused by the coating of the susceptor: before loading the GaAs wafer, a thin Si coating is applied on the susceptor<sup>1</sup>. It is possible that this coating causes a Si spike at the interface. The C spike, visible in some of the SIMS plots, is most probably due to insufficient cleaning of the surface before the deposition starts.

<sup>&</sup>lt;sup>1</sup>Si coating on the susceptor is part of the standard HCl cleaning step before each deposition.

Figure 2.4: SIMS profile of a  $2 \times 10^{19}$  atoms/cm<sup>3</sup> Si-doping in a stoichiometric GaAs epitaxy at a temperature of 650°C.

Using the reactor's dilution system, the concentration of the impurity precursors can be reduced, giving rise to dopant concentration control over several orders of magnitude. This is illustrated in Figure 2.5, which shows a staircase doping profile of three Si-doped GaAs epitaxial layers with average levels of  $8\times10^{19}$  atoms/cm<sup>3</sup>,  $1\times10^{19}$  atoms/cm<sup>3</sup> and  $5\times10^{17}$ , respectively. However, the doping profile at the layer interfaces is not abrupt. This is because of the rather high diffusion coefficients of Si in GaAs above 600°C. As is clearly visible, considerable diffusion has taken place. Not only are the changes in concentration far from abrupt, but also the Si has diffused past the original interface into the substrate.

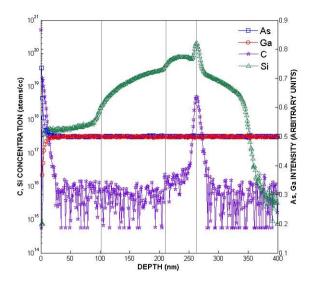

#### Ge-doped GaAs

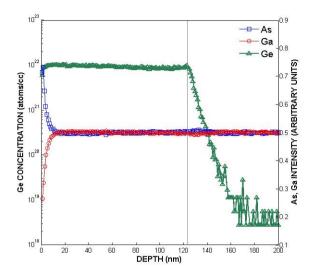

Very high Ge-doped GaAs epitaxial layers with a uniform dopant concentration of  $10^{22}$  atoms/cm<sup>3</sup> have been obtained, as shown in Figure 2.6, while the stoichiometry of GaAs epitaxy is still ideal. At this high concentration, well over 20%, the Ga and As concentrations still seem to be equal, within the SIMS accuracy. Hence, Ga and As are approximately equally replaced by Ge in this high concentration regime. On the other hand, using the reactor's dilution system,

Figure 2.5: SIMS plots for Si-doped staircase GaAs epitaxial layers at a temperature of 650°C with average levels of  $8\times10^{19}$  atoms/cm<sup>3</sup>,  $1\times10^{19}$  atoms/cm<sup>3</sup> and  $5\times10^{17}$ , respectively.

achieving lower Ge concentrations are also possible. Figure 2.7 shows the profile for three Ge doping levels with averages of approximately  $1\times10^{19}$ ,  $5\times10^{19}$  and  $5\times10^{20}$  atoms/cm<sup>3</sup>, respectively. It is also clear from Figure 2.7 that Ge - just like Si- suffer from high diffusion in GaAs at temperatures above 600°C. It is also clear that the deeper layers have suffered more from diffusion as they have been exposed to a higher temperature budget.

#### 2.4 GaAs on Si substrates

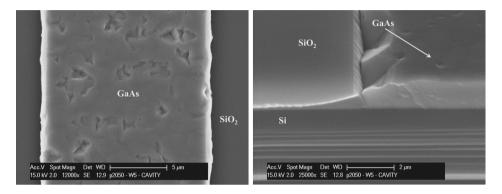

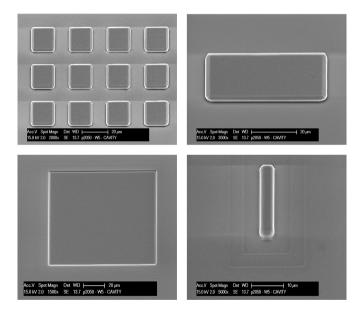

Due to the lattice mismatch of around 4.2% between GaAs and Si crystals, GaAs growth on Si is a big challenge and the compound nature of GaAs makes it further critical for crystalline growth on the Si substrate. In order to study the selective MOCVD of GaAs on Si, first 700 nm LPCVD SiO<sub>2</sub> was deposited at a temperature of 700°C on 100 mm n- or p-type Si wafers. The SiO<sub>2</sub> is patterned to open windows to Si with different sizes afterwards. The patterned wafers are then loaded in the MOCVD reactor for GaAs deposition after they are dip-etched in HF for 4 minutes and dried with Marangoni. The conditions used for GaAs

Figure 2.6: SIMS profile of a Ge doped GaAs epitaxial layer. At this high concentration Ge tends to replace Ga and As equally, at least within the accuracy of the measurement.

Figure 2.7: SIMS plots for Ge-doped staircase GaAs epitaxial layers with averages of  $1\times10^{19}$ ,  $5\times10^{19}$  and  $5\times10^{20}$  atoms/cm<sup>3</sup>, respectively.

growth on Si here is the same as described in Section 2.3.1 except for the baking step which is 4 minutes at 850°C to ensure a native-oxide-free Si surface. Figure 2.8 shows secondary electron microscopy (SEM) pictures of GaAs growth on Si. Early results show rather rough surfaces of GaAs that is more like a poly crystal, even though good selectivity over SiO<sub>2</sub> is observed.

Figure 2.8: top-view (left) and cross-sectional view (right) SEM images of selective GaAs growth on Si.

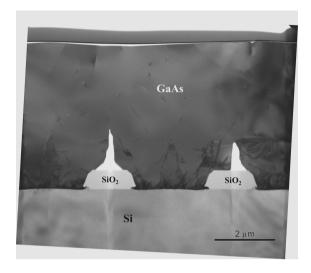

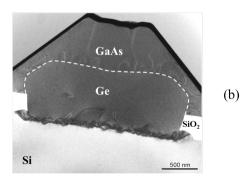

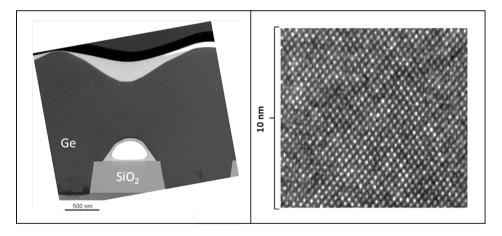

To better understand the quality of GaAs growth on Si, cross-sectional transmission electron-microscopy (TEM) is performed on a selective MOCVD of GaAs-on-Si with lateral overgrowth on SiO<sub>2</sub> as shown in Figure 2.9.

The GaAs layer thickness in Figure 2.9 is more than 5 µm and as can be seen the further the GaAs growth is from the Si interface, less defects are observed. On the other hand, the lateral overgrowth of GaAs on SiO<sub>2</sub> is reasonably good and as the TEM image shows. No additional defects are produced in the area where GaAs overgrowth from either sides of SiO<sub>2</sub> joins to each other. However, the amount of defects in the body of GaAs, especially at thicknesses of less than 1 µm, is still considerably high for any electronics and optoelectronics application. In Section 1.2.3, it was mentioned that Ge is a good candidate for a sacrificial layer between the Si substrate and GaAs to achieve better crystallinity. This is the motivation of an approach to crystalline Ge growth on Si which is the topic of the next Chapter.

#### 2.5 Conclusions

In this Chapter the MOCVD of GaAs epitaxy in a commercial Si/SiGe CVD reactor (ASMI Epsilon 2000) has been reported. The demonstration of this process

2.5 Conclusions 39

Figure 2.9: A cross-sectional TEM image of GaAs growth on Si substrate with lateral overgrowth on SiO<sub>2</sub>.

is in a manner that is compatible with the standard Si/SiGe epitaxy. Based on DIC microscopy and SIMS analysises it appears that good quality and stoichiometric GaAs is obtained for a wide range of deposition parameters and at useful growth rates. The background doping level of the reactor can quickly be returned to the range that is compatible with Si processing with standard cleaning methods. Moreover, doping with Si or Ge is readily obtained from standard gas sources.

Selective GaAs growth on Si substrate is also studied. The early results show good selectivity for GaAs growth and rather smooth layers of GaAs on Si is achieved.

# Chapter 3

# **Crystalline germanium growth on silicon**

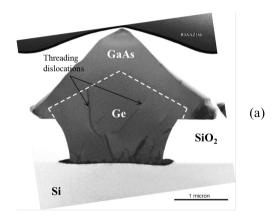

In the previous Chapters, a description was given over the standard Si/SiGe ASMI Epsilon 2000 reactor that was modified for CVD of both GaAs and Si epitaxy in one system. The conditions and mechanisms to achieve intrinsic and doped GaAs epitaxy was explained in detail and the challenges of GaAs epitaxial growth on Si substrates were described: the challenge related to the lattice-mismatch can be overcome by replacing the Si substrate with Ge according to the lattice-mismatch of only 0.07% between Ge and GaAs.

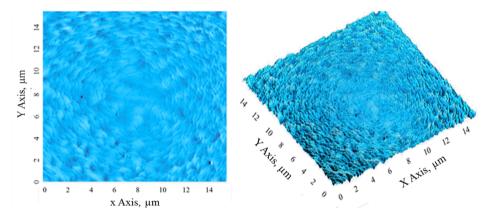

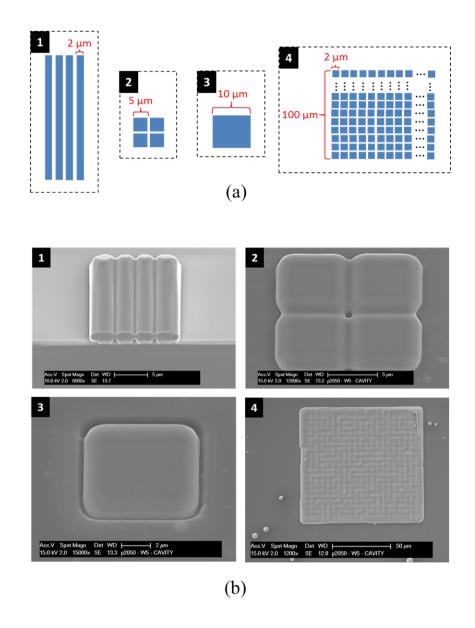

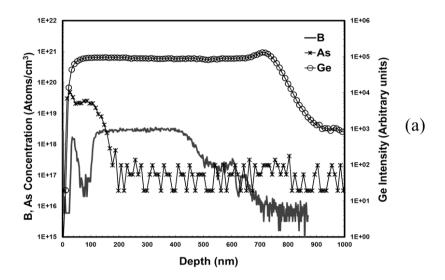

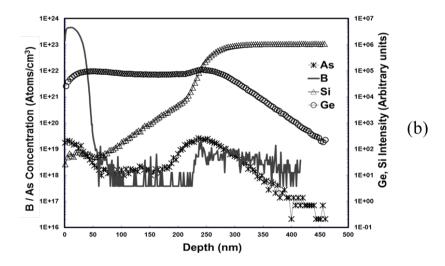

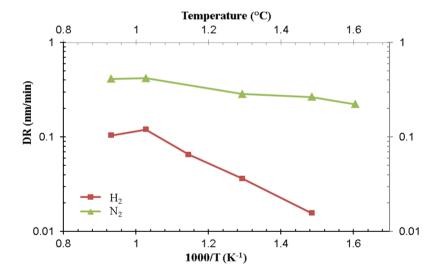

In this Chapter, the focus is on the utilization of the ASMI Epsilon 2000 system to develop crystalline Ge growth on Si substrates (Ge-on-Si) with low threading dislocation and defect densities. For this purpose, a novel method to grow good quality crystalline Ge within a layer thickness of approximately 1  $\mu m$  on different window sizes up to hundreds of  $\mu m^2$  is introduced. A 2% diluted GeH $_4$  gas is used as the main precursor gas for Ge growth; and  $AsH_3$  and  $B_2H_6$  precursor gases for As and B doping, respectively. Plan-view and cross-sectional transmission electron-microscopy (TEM) and atomic-force microscopy (AFM) analyses were performed on Ge-on-Si to confirm the quality and selectivity of the process as well as the crystallinity of the Ge-on-Si.

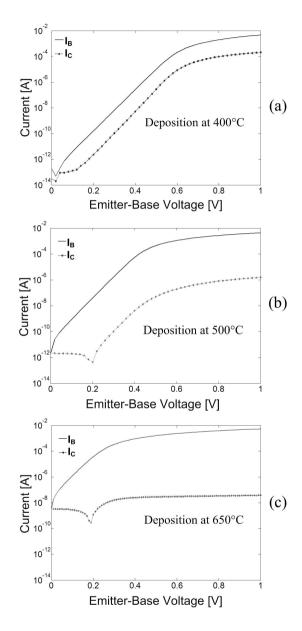

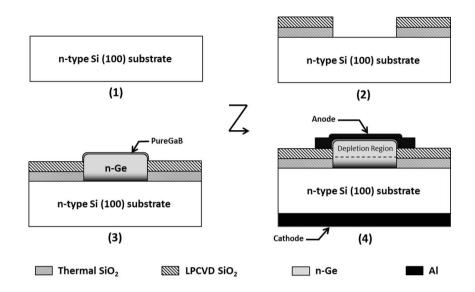

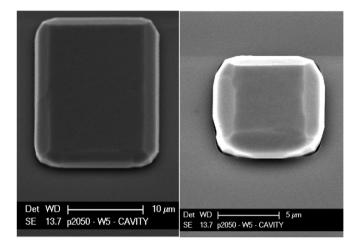

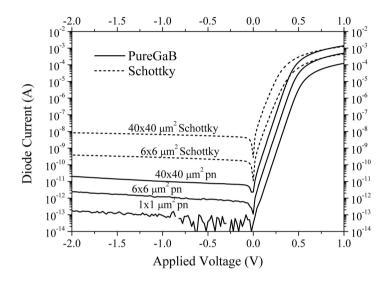

#### 3.1 Introduction