# Christos Strydis

# Universal Processor Architecture for Biomedical Implants

The SiMS Project

# Universal Processor Architecture for Biomedical Implants

The SiMS Project

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K.Ch.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen

op dinsdag 15 maart 2011 om 10:00 uur

door

Christos STRYDIS

Master in Computer Engineering Technische Universiteit Delft geboren te Athene, Griekenland Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. P.J. French

Copromotor:

Dr. G.N. Gaydajiev

#### Samenstelling promotiecommissie:

| Rector Magnificus, voorzitter   | Technische Universiteit Delft, NL     |

|---------------------------------|---------------------------------------|

| Prof. dr. P.J. French, promotor | Technische Universiteit Delft, NL     |

| Dr. G.N. Gaydadjiev, copromotor | Technische Universiteit Delft, NL     |

| Prof. dr. Y.N. Patt             | University of Texas at Austin, USA    |

| Prof. dr. A.V. Veidenbaum       | University of California, Irvine, USA |

| Prof. dr. D.F.A.M.E. De Ridder  | Universiteit Antwerpen, BE            |

| Prof. dr. ir. H.J. Sips         | Technische Universiteit Delft, NL     |

| Dr. H.R. Lopuhaä                | Technische Universiteit Delft, NL     |

#### CIP-DATA KONINKLIJKE BIBLIOTHEEK, DEN HAAG

#### Christos Strydis

Universal Processor Architecture for Biomedical Implants — The SiMS Project Delft: TU Delft, Faculty of Elektrotechniek, Wiskunde en Informatica - III Thesis Technische Universiteit Delft. – With ref. –

Met samenvatting in het Nederlands.

ISBN 978-90-72298-14-0

Subject headings: implant, survey, taxonomy, benchmark, processor, cache, branch prediction, microarchitecture, instruction set, design-space exploration.

#### Copyright © 2011 Christos Strydis

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without permission of the author.

Printed in The Netherlands

Dedicated to Stamatis who made sure this thesis would be started; to Georgi who made sure this thesis would be concluded.

# Universal Processor Architecture for Biomedical Implants

The SiMS Project

Christos Strydis

# **Abstract**

**EALTHCARE** in the 21st century is changing rapidly. In advanced countries, in particular, healthcare is moving from a public to a more personalized nature. However, the costs of healthcare worldwide are increasing every year. Better use of technology can and should be used to get control of these costs. At the same time, implants have clearly benefitted from the astounding technology-miniaturization trends of late, boasting smaller sizes, lower power consumption and increased performance of the transistor devices. However, such advances do not come for free. Adverse effects in current implant designs are being witnessed, such as increasing power consumption, absence of design for reliability and highly application-specific nature. Operating under the assumption that implants will constitute an important means towards improved, personal healthcare and, in view of the aforementioned design phenomena, we believe that a new paradigm in implant design is required. This dissertation establishes the concept of Smart implantable Medical Systems (SiMS). SiMS is a systematic approach – a framework – for providing biomedical researchers and, hopefully, industry with a toolbox of ready-to-use, highly reliable implant sub-systems and models in order to construct optimal implants for various medical applications. The SiMS framework has to guarantee essential attributes, such as high dependability, modular design, ultra-low power consumption and miniature size. Having defined the SiMS framework, this dissertation is, then, concerned with exploring the optimal microarchitectural details of a crucial SiMS component: the SiMS processor. Contrary to the current state of the art, this processor aspires to be a new universal, low-power and low-cost processor and capable of efficiently serving a wide range of diverse implant applications.

# Acknowledgements

There is a very good reason why acknowledgements are always found in the beginning of a book. They tell the private story of how the book you are holding in your hands came to be. A number of people have contributed in a number of ways to its contents and looks. Had they not helped when they did, I am certain this work would have never reached its present state of completion.

So, I would like to start off by thanking my co-promotor Georgi Gaydadjiev for the sustained insight and support he provided throughout the hardships of this thesis work. His being the yin, I would also like to thank my yang – my late promotor Stamatis Vassiliadis for his initial encouragement and *ab initio* backing of my research. God rest his soul. I will always consider both men as my mentors and my friends. I am also deeply grateful to my thesis-committee member Rik Lopuhaä for offering unstinting support on statistics, and on a very short notice at that. This thesis would have been far from complete without his contribution.

As far as the tool flow that was necessary for this thesis is concerned, the work would have come to an early standstill, had it not been for the valuable contributions of Stefanos Kaxiras, Margaret Martonosi and Gilberto Contreras who have been instrumental in providing me with an excellent powersimulation tool (XTREM) and all support I could ask. I am also indebted to Demid Borodin for his assistance in setting up and understanding the chaos that is called cross-compilation, as well as to Pepijn de Langen, Filipa Duarte and Vlad-Mihai Sima for their helpful insights on the matter. I would also like to thank Kyriakos Stavrou for his prompt, catalytic help with the CACTI cache-simulation tool and Carlo Galuzzi specifically for his formulating of the XTREM power analysis and, overall, for his valuable comments and help throughout. Special thanks are due to Bert Meijs, Erik de Vries and Eef Hartman – the past and present CE-Laboratory system administrators – for their inexplicable sympathy for my outrageous technical requests and for their excellent support in setting up and operating the custom computer cluster needed for our DSE experiments. Without them, this work would not have taken shape.

Furthermore, I remain truly grateful to all those people who responded to my persistent requests or unequivocal threats by offering precious resources, insights or even strong criticism. To name a few: Christopher Sadler for providing the sources of his intriguing SLZW compression algorithm, Peter Cross for providing the original sources for the excellent DMU application and limitless support, Johnny Ray Sears for providing resources on his biotelemetric heartvalve monitor, Pietro Valdastri for providing the assembly sources of running in his implantable telemetry platform system and Niki Frantzeskaki for her valuable help on statistics and otherwise. Also, Christoforos Kachris, Dhara Dave and Zhu Di for the fruitful collaboration we have achieved. Furthermore, I greatly appreciate and wish to thank Dimitris Theodoropoulos for his helpful insights on data encryption and computer architecture, Sebastian Isaza, Yiannis Sourdis, Daniele Ludovici and Lotfi Mhamdi for being the boxsack for me to hone my work on; and Nicolae & Nicole Stefu for giving me a nudge in the right direction when I needed it the most. My thanks are also due to both the CE-group secretaries Lidwina Tromp and Monique Tromp for their exceptional administrative assistance throughout my PhD years. My deep thanks are also due to Ana Laura Santos for – among other things – putting together the elegant design that is the book cover of this dissertation document. What is more, I wish to acknowledge the authorities responsible for (partially) funding this thesis work: the ICT Delft Research Centre (DRC-ICT) of the Delft University of Technology and Google Inc.. It was their timely aid that ensured the completion of this thesis.

Last but certainly not least, I feel the need to deeply thank my wife Olga and my parents Stefanos and Aristea for their immeasurable emotional as well as downright material support, for their patience and faith throughout the course of this research effort. I am – and always will be – in their debt.

Christos

Delft, The Netherlands, March 2011

# Table of Contents

| Ak  | stract   | t                                    | i  |

|-----|----------|--------------------------------------|----|

| Αc  | know     | ledgments                            | ii |

| Та  | ble of   | Contents                             | V  |

| Lis | st of Ta | ables                                | κi |

| Lis | st of F  | igures                               | ii |

| Lis | st of A  | acronyms                             | κi |

| 1   | Intro    | oduction                             | 1  |

|     | 1.1      | Background                           | 1  |

|     | 1.2      |                                      | 2  |

|     |          |                                      | 2  |

|     |          |                                      | 4  |

|     | 1.3      |                                      | 5  |

|     | 1.4      |                                      | 6  |

|     | 1.5      |                                      | 7  |

| 2   | A su     | rvey on microelectronic implants     | 9  |

|     | 2.1      | Survey goals                         | 9  |

|     | 2.2      | Survey scope                         | 0  |

|     | 2.3      | Survey structure                     | 2  |

|     | 2.4      | An implant primer                    | 2  |

|     | 2.5      | Survey setup                         | 4  |

|     |          | 2.5.1 Major categories               | 6  |

|     |          | 2.5.2 Minor categories               | 7  |

|     |          | 2.5.2.1 ELECTROMECHANICAL FEATURES 1 | 7  |

|   |     |         | 2.5.2.2    | POWER FEATURES                                                   | 17 |

|---|-----|---------|------------|------------------------------------------------------------------|----|

|   |     |         | 2.5.2.3    | GENERAL IMPLANT FEATURES                                         | 18 |

|   |     |         | 2.5.2.4    | PROCESSING/CONTROLLING-CORE                                      |    |

|   |     |         |            | FEATURES                                                         | 18 |

|   |     |         | 2.5.2.5    | ${\it MISCELLANEOUS~IMPLANT~FEATURES}~.$                         | 19 |

|   |     | 2.5.3   |            | on                                                               | 20 |

|   |     | 2.5.4   | Statistica | l tests                                                          | 21 |

|   |     |         | 2.5.4.1    | Testing independence of two categorical variables                | 21 |

|   |     |         | 2.5.4.2    | Testing whether categorical variables change over time           | 22 |

|   |     |         | 2.5.4.3    | Exploring the relation of a scale variable over time             | 23 |

|   |     |         | 2.5.4.4    | Exploring the relation of a scale variable over time over groups | 23 |

|   |     |         | 2.5.4.5    | Comparing a scale variable over groups                           | 24 |

|   | 2.6 | Survey  | results .  |                                                                  | 26 |

|   |     | 2.6.1   | Implant a  | applications & functionality                                     | 26 |

|   |     | 2.6.2   | Electrom   | echanical features                                               | 32 |

|   |     | 2.6.3   | Power fe   | atures                                                           | 41 |

|   |     | 2.6.4   | General i  | mplant features                                                  | 49 |

|   |     | 2.6.5   | PCC feat   | ures                                                             | 60 |

|   |     | 2.6.6   | Miscellar  | neous implant features                                           | 69 |

|   | 2.7 | Summ    | ary        |                                                                  | 85 |

| 3 | The | SiMS co | ncept & ba | ckground                                                         | 87 |

|   | 3.1 |         | =          | generation of implants                                           | 88 |

|   |     | 3.1.1   | -          | nomic trends                                                     | 88 |

|   |     | 3.1.2   | Technolo   | gical trends                                                     | 89 |

|   |     | 3.1.3   | Survey-b   | ased implant trends                                              | 90 |

|   | 3.2 | Smart   |            | e Medical Systems (SiMS)                                         | 91 |

|   |     | 3.2.1   | The SiM    | S concept                                                        | 91 |

|   |     | 3.2.2   |            | gital processor                                                  | 93 |

|   |     | 3.2.3   |            | SiMS workloads                                                   | 94 |

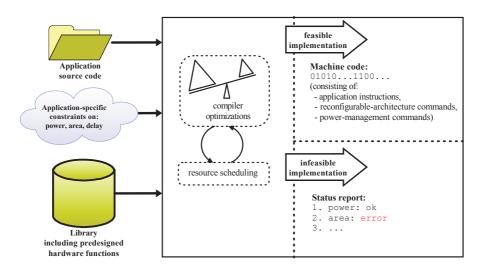

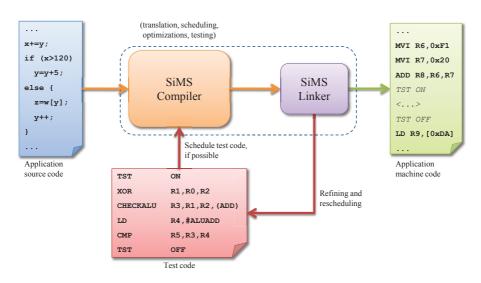

|   |     | 3.2.4   |            | LL Compiler                                                      | 95 |

|   |     | 3.2.5   | SiMS per   | ripherals                                                        | 97 |

|   |     | 3.2.6   | SiMS wi    | reless transceiver                                               | 98 |

|   |     |         |            |                                                                  |    |

|   |      | 3.2.7    | SiMS chip interfaces                                 | 99  |

|---|------|----------|------------------------------------------------------|-----|

|   |      | 3.2.8    | Miscellaneous SiMS components                        | 100 |

|   |      | 3.2.9    | SiMS relevance                                       | 100 |

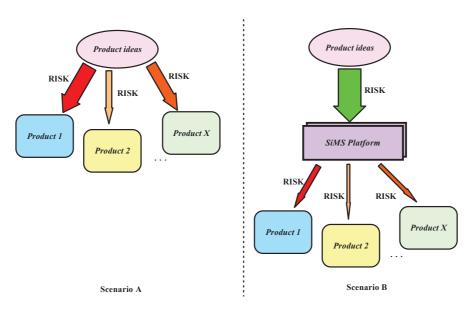

|   |      | 3.2.10   | Minimizing risks and costs                           | 101 |

|   |      | 3.2.11   | Prior art on generic implant designs                 | 102 |

|   | 3.3  | Techni   | cal background                                       | 103 |

|   |      | 3.3.1    | Work organization                                    | 104 |

|   |      | 3.3.2    | Processor simulators                                 | 105 |

|   |      | 3.3.3    | Evaluation of suitable implant benchmarks            | 107 |

|   |      |          | 3.3.3.1 Compression algorithms                       | 108 |

|   |      |          | 3.3.3.2 Encryption algorithms                        | 108 |

|   |      | 3.3.4    | Investigating benchmark suites for implants          | 109 |

|   |      | 3.3.5    | Processor microarchitecture exploration              | 110 |

|   |      |          | 3.3.5.1 Evaluation of L1 I-/D-cache organizations .  | 111 |

|   |      |          | 3.3.5.2 Evaluation of branch-prediction schemes      | 112 |

|   |      | 3.3.6    | Automated, multiobjective DSE for implant processors | 112 |

|   | 3.4  | Summa    | ary                                                  | 114 |

| 4 | SiMS | S-proces | sor simulation environment                           | 117 |

|   | 4.1  | XTRE     | M processor simulator                                | 118 |

|   |      | 4.1.1    | Hardware-modeling details                            | 118 |

|   |      | 4.1.2    | Program-execution details                            | 119 |

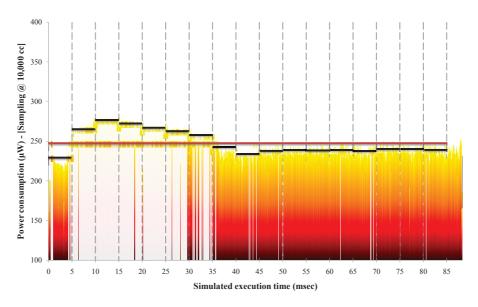

|   |      | 4.1.3    | Sampling details                                     | 120 |

|   | 4.2  | •        | t workloads                                          | 122 |

|   |      | 4.2.1    | Workload characteristics                             | 123 |

|   |      | 4.2.2    | Identifying generic workloads                        | 123 |

|   |      |          | 4.2.2.1 Real implant applications                    | 124 |

|   |      |          | 4.2.2.2 Data reduction & compression                 | 125 |

|   |      |          | 4.2.2.3 Data & command encryption                    | 125 |

|   |      |          | 4.2.2.4 Data & command integrity                     | 126 |

|   |      | 4.2.3    | Workload acquisition                                 | 126 |

|   | 4.3  | Input d  | latasets                                             | 127 |

|   | 4.4  | Profilir | ng of encryption algorithms                          | 129 |

|   |      | 4.4.1    | Selection criteria of ciphers                        | 131 |

|   |      | 4.4.2    | Experimental setup                                   | 132 |

|   |      |          | 4.4.2.1 Simulator configuration                      | 132 |

|     |                | 4.4.2.2              | Encryption datasets                | 132        |

|-----|----------------|----------------------|------------------------------------|------------|

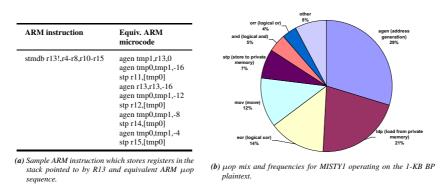

|     | 4.4.3          | 4.4.2.3 Profiling    | Encryption algorithms              |            |

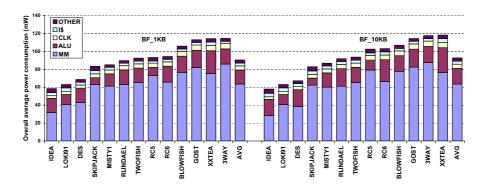

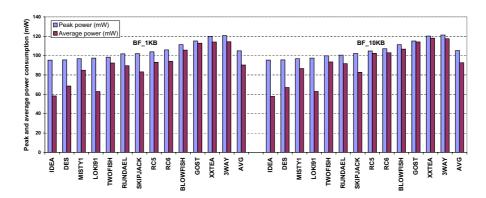

|     |                | 4.4.3.1              | Power consumption                  | 134        |

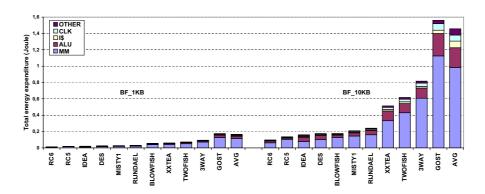

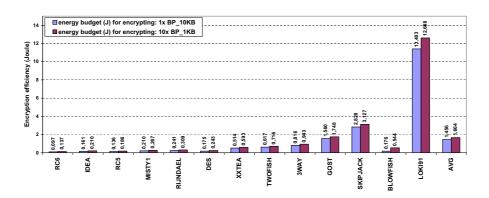

|     |                | 4.4.3.2              | Energy expenditure                 | 137        |

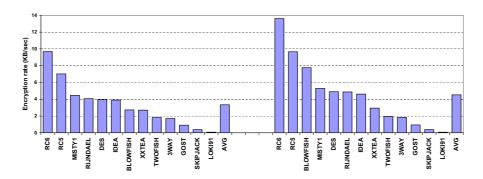

|     |                | 4.4.3.3              | Encryption rate                    | 138        |

|     |                | 4.4.3.4              | Executable-binary size             | 139        |

|     | 4.4.4          | 4.4.3.5<br>Results & | Security margin                    | 141<br>142 |

| 4.5 |                |                      |                                    |            |

|     | 4.5.1          |                      | E                                  | 144        |

|     | 4.5.2          |                      | ental setup                        | 145        |

|     |                | 4.5.2.1              | Simulator configuration            | 145        |

|     |                | 4.5.2.2              | Compression datasets               | 146        |

|     | 4.5.3          | 4.5.2.3<br>Profiling | ı E                                |            |

|     |                | 4.5.3.1              | ·                                  |            |

|     |                | 4.5.3.2              | 1                                  |            |

|     |                | 4.5.3.3              | •                                  | 149        |

|     |                | 4.5.3.4              | Overall energy budget              | 150        |

|     |                | 4.5.3.5              | Executable-binary size             | 151        |

|     | 4.5.4          |                      |                                    | 152        |

| 4.6 |                |                      | vel benchmark suite for implants   | 155        |

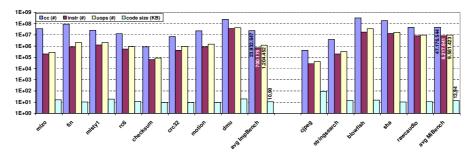

|     | 4.6.1<br>4.6.2 |                      | I for a new benchmark suite        | 156        |

|     | 4.6.3          | _                    | -                                  |            |

|     | 4.6.4          |                      | 1                                  |            |

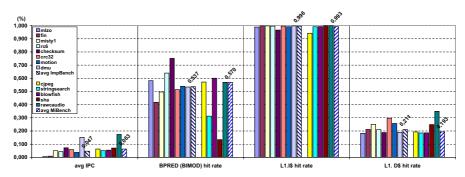

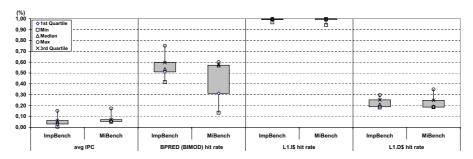

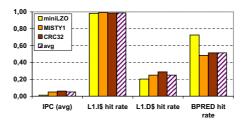

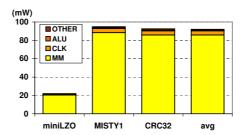

|     | 4.6.5          |                      | ance, caches and branch prediction |            |

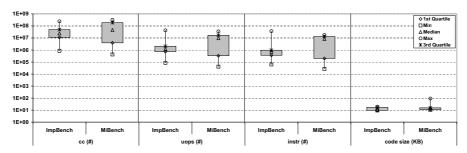

|     |                | 4.6.5.1              | Dynamic & static benchmark size    | 163        |

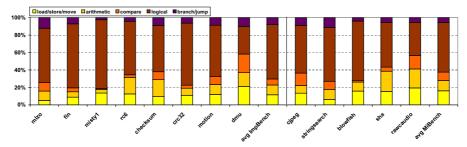

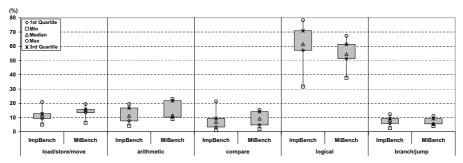

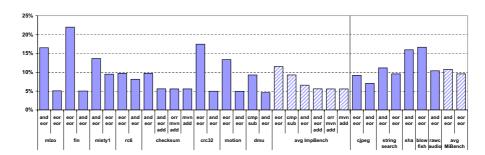

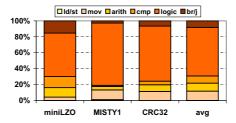

|     |                | 4.6.5.2              | Instruction distribution           | 164        |

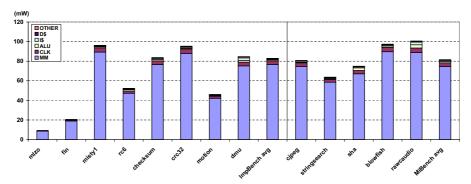

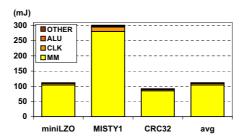

|     |                | 4.6.5.3              | Power consumption                  | 166        |

|     | 4.6.6          |                      | ,                                  |            |

| 4.7 |                |                      | •                                  |            |

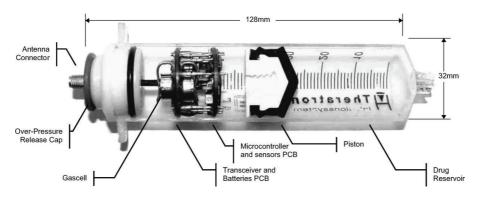

|     | <i>4</i> 7 1   | Implant a            | characteristics                    | 168        |

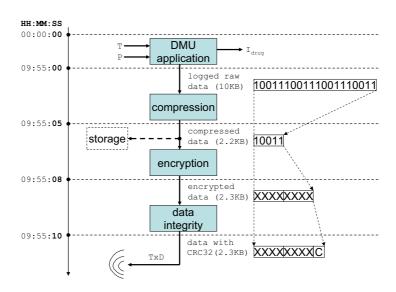

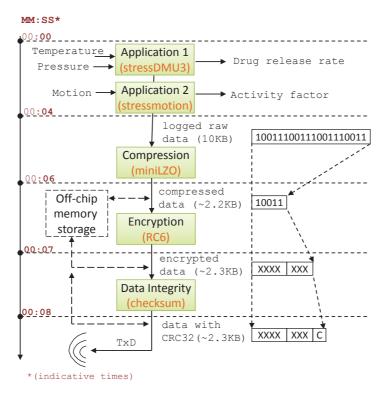

|   |      | 4.7.2    | Crafting    | a realistic application                | 169 |

|---|------|----------|-------------|----------------------------------------|-----|

|   |      | 4.7.3    | Experim     | ental setup                            | 172 |

|   |      | 4.7.4    |             | analysis                               | 172 |

|   |      | 4.7.5    | Discussion  | on                                     | 176 |

|   | 4.8  | Summ     | ary         |                                        | 176 |

| 5 | SiMS | S-proces | sor microa  | architecture evaluation                | 179 |

|   | 5.1  | Evalua   | tion of ca  | che organizations                      | 179 |

|   |      | 5.1.1    | Experim     | ental setup                            | 180 |

|   |      |          | 5.1.1.1     | Input datasets                         | 181 |

|   |      |          | 5.1.1.2     | Benchmarks                             | 181 |

|   |      |          | 5.1.1.3     | Simulation testbed                     | 181 |

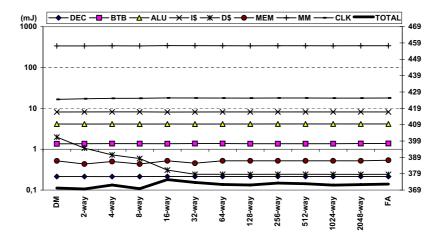

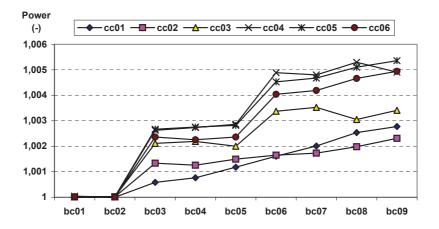

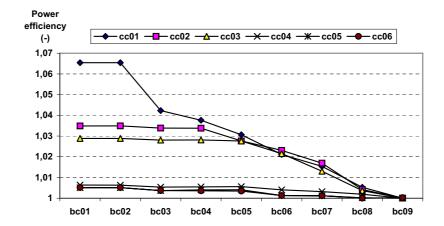

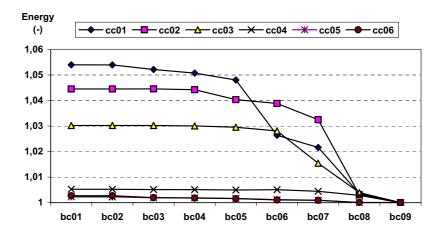

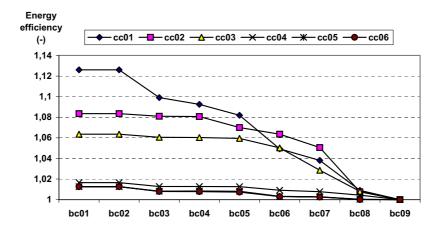

|   |      | 5.1.2    | Profiling   | analysis                               | 183 |

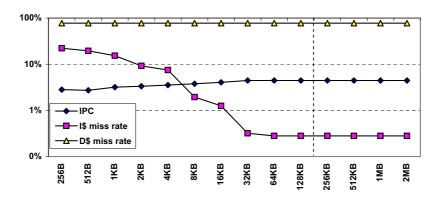

|   |      |          | 5.1.2.1     | Cache sizes                            | 184 |

|   |      |          | 5.1.2.2     | Cache associativity                    | 190 |

|   |      | 5.1.3    | Conclusi    | ons                                    | 196 |

|   | 5.2  | Evalua   | tion of bra | anch-prediction schemes                | 197 |

|   |      | 5.2.1    | _           | ental setup                            | 197 |

|   |      | 5.2.2    |             | red branch-prediction schemes          | 198 |

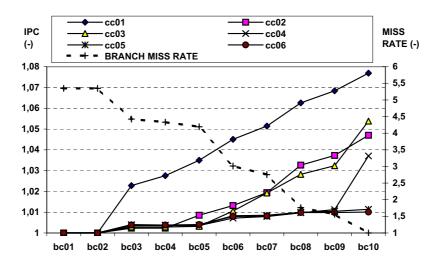

|   |      | 5.2.3    |             | on study                               | 200 |

|   |      | 5.2.4    | Conclusi    | ons                                    | 209 |

|   | 5.3  | Summ     | ary         |                                        | 209 |

| 6 | Auto | mated e  | xploration  | of SiMS-processor microarchitectures   | 211 |

|   | 6.1  | ImpEI    | DE: A DSE   | E tool for implant processors          | 212 |

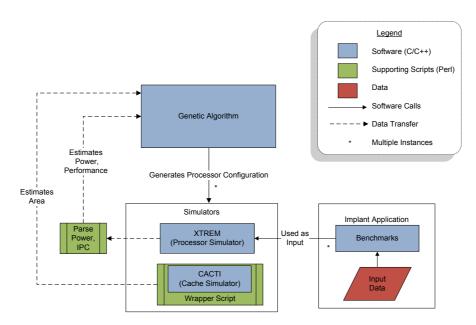

|   |      | 6.1.1    | Framewo     | ork organization                       | 213 |

|   |      |          | 6.1.1.1     | Genetic algorithm: NSGA-II             | 214 |

|   |      |          | 6.1.1.2     | Processor & cache simulators           | 216 |

|   |      |          | 6.1.1.3     | Biomedical benchmarks & input datasets | 217 |

|   |      |          | 6.1.1.4     | Parallelization & optimization         | 218 |

|   |      | 6.1.2    | Framewo     | ork fine-tuning                        | 219 |

|   |      |          | 6.1.2.1     | Chromosome encoding & XTREM errata     | 219 |

|   |      |          | 6.1.2.2     | Population size                        | 220 |

|   |      |          | 6.1.2.3     | Number of Generations                  | 220 |

|   |      |          | 6124        | Mutation                               | 223 |

|     |         | 6.1.3     | 6.1.2.5<br>Selected 1 | Crossover probability                  |     |

|-----|---------|-----------|-----------------------|----------------------------------------|-----|

|     |         |           | 6.1.3.1               | Implant-processor results              |     |

|     |         |           | 6.1.3.2               | Framework expansion                    | 226 |

|     |         | 6.1.4     |                       | ons                                    |     |

|     | 6.2     | ImpBer    |                       | Revisiting the implant benchmark suite |     |

|     |         | 6.2.1     |                       | h v1.1 overview                        |     |

|     |         | 6.2.2     | _                     | ental setup                            |     |

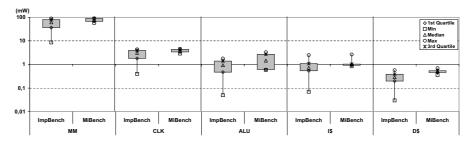

|     |         | 6.2.3     | Benchma               | rk characterization                    | 234 |

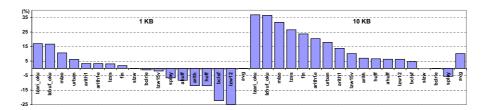

|     |         |           | 6.2.3.1               | Lossless compression                   | 235 |

|     |         |           | 6.2.3.2               | Symmetric encryption                   | 240 |

|     |         |           | 6.2.3.3               | Data integrity                         | 241 |

|     |         |           | 6.2.3.4               | Real applications & stressmarks        | 243 |

|     |         | 6.2.4     | Conclusio             | ons                                    | 246 |

|     | 6.3     | Explora   | ation of op           | timal SiMS Processors                  | 247 |

|     |         | 6.3.1     | Experime              | ental setup                            | 247 |

|     |         |           | 6.3.1.1               | Exploration framework                  | 247 |

|     |         |           | 6.3.1.2               | Worst-case workload mix                | 248 |

|     |         | 6.3.2     | •                     | ocessor DSE execution                  |     |

|     |         | 6.3.3     | _                     | tudy cases                             |     |

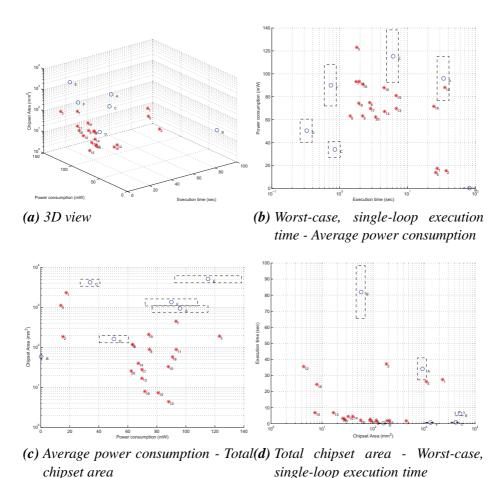

|     |         | 6.3.4     | •                     | on results                             |     |

|     |         | 6.3.5     |                       | n                                      | 257 |

|     |         | 6.3.6     |                       | ons                                    |     |

|     | 6.4     | Summa     | ıry                   |                                        | 258 |

| 7   | Conc    | lusions   |                       |                                        | 261 |

|     | 7.1     | Outlool   | k                     |                                        | 262 |

|     | 7.2     | Contrib   | outions .             |                                        | 263 |

|     | 7.3     | Open Is   | ssues and l           | Future Directions                      | 265 |

| Bib | liogra  | phy .     |                       |                                        | 269 |

| Lis | t of Pu | ıblicatio | ns                    |                                        | 281 |

| Sar | nenva   | tting .   |                       |                                        | 283 |

| Cu  | rriculu | m Vitae   |                       |                                        | 285 |

# List of Tables

| 4.1  | XScale architecture details                                                            | 119 |

|------|----------------------------------------------------------------------------------------|-----|

| 4.2  | 1-KB and 10-KB physiological datasets. Double-precision (8-Byte) data samples are used | 127 |

| 4.3  | Experimental setup and acquisition parameters of input datasets.                       | 129 |

| 4.4  | XTREM configuration for the encryption profiling study                                 | 132 |

| 4.5  | Collection of profiled symmetric ciphers                                               | 133 |

| 4.6  | Program sizes (in KB) of the encryption algorithms                                     | 140 |

| 4.7  | Security margins of the encryption algorithms                                          | 141 |

| 4.8  | Five best-performing encryption algorithms                                             | 142 |

| 4.9  | $\mu$ op mix and frequencies for IDEA and RC6 operating on the 1-KB BP plaintext       | 143 |

| 4.10 | XTREM configuration for compression profiling study                                    | 145 |

| 4.11 | Collection of profiled lossless-compression algorithms                                 | 146 |

| 4.12 | Compression algorithms' program sizes                                                  | 151 |

| 4.13 | Five best-performing compression algorithms                                            | 152 |

| 4.14 | Popular $mlzo~\mu$ op frequencies                                                      | 153 |

| 4.15 | Instruction-dependency algorithm                                                       | 153 |

| 4.16 | Popular $mlzo~\mu$ op pairs and triplets                                               | 153 |

| 4.17 | ImpBench components                                                                    | 157 |

| 4.18 | XTREM configuration for ImpBench evaluation                                            | 159 |

| 4.19 | XTREM configuration for exploring a SiMS-processor case study                          | 171 |

| 5.1 | ImpBench components and (static) binary size                                                                                          | 181 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.2 | XTREM configuration for study on cache geometries                                                                                     | 182 |

| 5.3 | Precision levels for IPC, power and energy in I/D-cache-size objective functions                                                      | 189 |

| 5.4 | Precision levels for IPC, power, energy and area in I/D-cacheway objective functions.                                                 | 195 |

| 5.5 | ImpBench components and useful general statistics                                                                                     | 197 |

| 5.6 | XTREM configuration for study on BPRED schemes                                                                                        | 198 |

| 5.7 | Branch-prediction and I/D-cache configurations used                                                                                   | 200 |

| 5.8 | Precision levels for IPC, power, energy and area in objective function (5.1) for all cache configurations when area is considered     | 206 |

| 5.9 | Precision levels for IPC, power, energy and area in objective function (5.1) for all cache configurations when area is not considered | 208 |

| 6.1 | XTREM configuration for ImpEDE integration                                                                                            | 216 |

| 6.2 | ImpBench components for ImpEDE integration                                                                                            | 217 |

| 6.3 | Physiological input datasets with double-precision (8-Byte) data samples of sizes 1-KB and 10-KB                                      | 217 |

| 6.4 | Processor design parameters considered in this work, encoded as 36 chromosomal bits                                                   | 221 |

| 6.5 | ImpBench v1.1 components and useful general statistics                                                                                | 231 |

| 6.6 | Pareto-front distance and normalized-spread metrics, and average simulation time per benchmark                                        | 239 |

| 6.7 | ImpEDE-evolved, optimal processor configurations                                                                                      | 251 |

| 6.8 | Study cases of real implantable applications                                                                                          | 253 |

|     |                                                                                                                                       |     |

# List of Figures

| 1.1  | The Da Vinci glider design                                                               | 2  |

|------|------------------------------------------------------------------------------------------|----|

| 1.2  | Block diagram of the SiMS concept                                                        | 5  |

| 2.1  | Concept of a typical implantable system                                                  | 13 |

| 2.2  | Overview of imposed survey taxonomy                                                      | 15 |

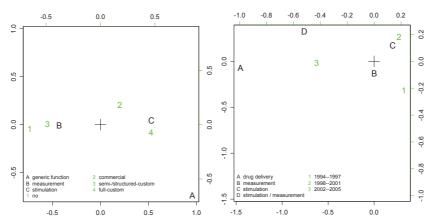

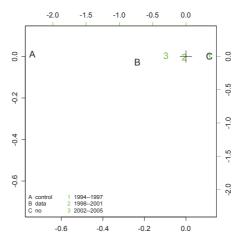

| 2.3  | CA plots between two categorical variables                                               | 22 |

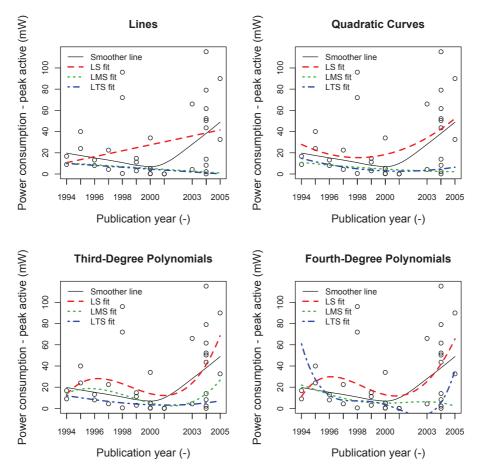

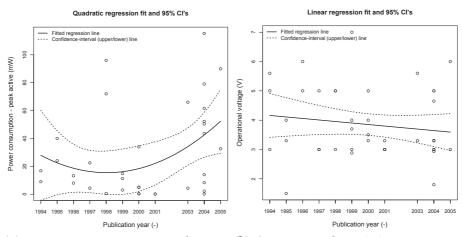

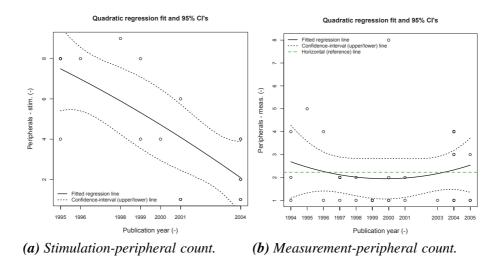

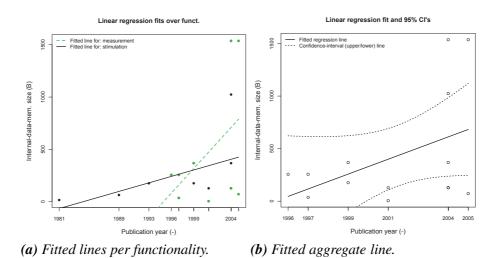

| 2.4  | Various regression lines fitting the power-consumption (peak active) data over the years | 24 |

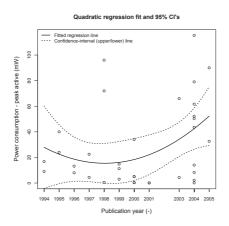

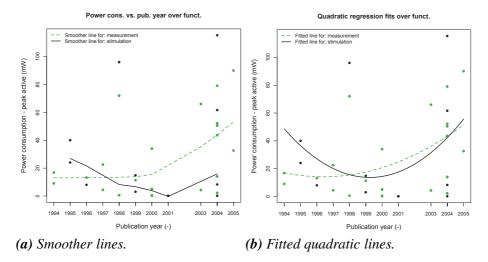

| 2.5  | Implant power-consumption (peak active) trends over the years.                           | 25 |

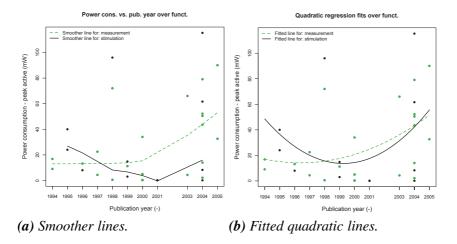

| 2.6  | Power-consumption trends over the years for different implant functionalities            | 25 |

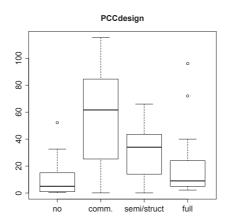

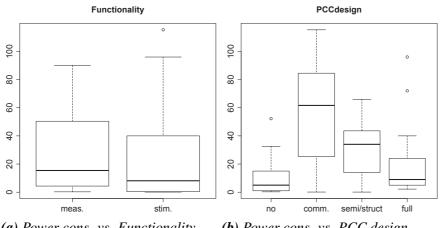

| 2.7  | Boxplot of implant power consumption (peak active) with respect to PCC design            | 26 |

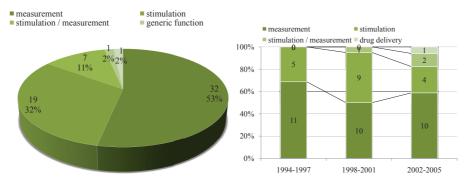

| 2.8  | Implant functionality                                                                    | 30 |

| 2.9  | CA plot of functionality vs. publication year                                            | 32 |

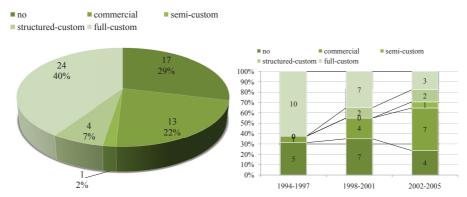

| 2.10 | Implant PCC design                                                                       | 33 |

| 2.11 | CA plot of PCC design vs. publication year                                               | 35 |

| 2.12 | CA plot of PCC design vs. functionality                                                  | 36 |

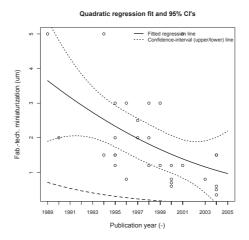

| 2.13 | Implant and mainstream microelectronics fabrication-technology trends over the years     | 37 |

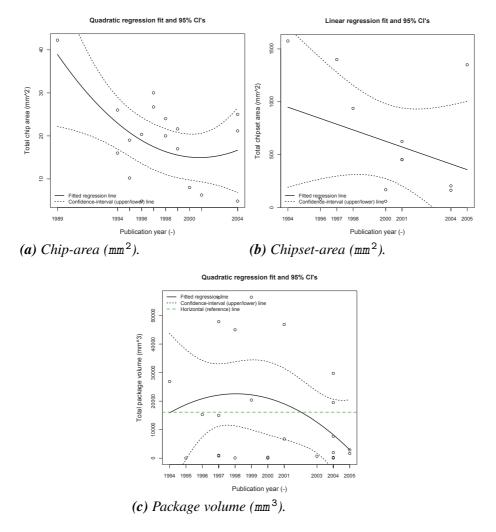

| 2.14 | Implant physical-dimensions trends over the years                                        | 40 |

| 2.15 | Schematic representation of RF-induction principle                                       | 41 |

| 2.16 | Implant low-power provisions                                                             | 43 |

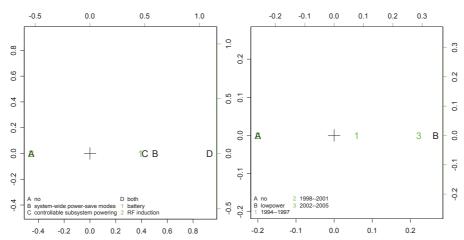

| 2.17 | CA plots of low-power provisions vs. power source and publication year                               | 44 |

|------|------------------------------------------------------------------------------------------------------|----|

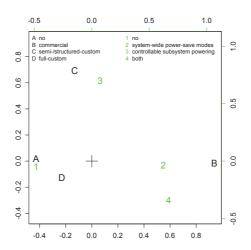

| 2.18 | CA plot of implant low-power provisions vs. PCC design                                               | 45 |

| 2.19 | Implant power-consumption and operating-voltage trends over the years                                | 46 |

| 2.20 | Power-consumption trends over the years for different implant functionalities                        | 48 |

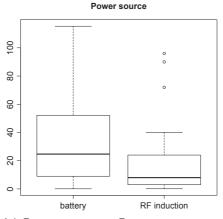

| 2.21 | Boxplots of implant power consumption (peak active) with respect to different device characteristics | 50 |

| 2.22 | Number of peripherals per implant over the years                                                     | 51 |

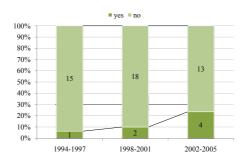

| 2.23 | Implants including both actuating and sensory elements over the years                                | 52 |

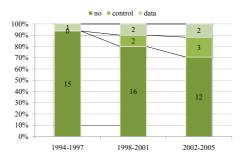

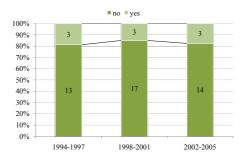

| 2.24 | Internal-processing-enabled implants over the years                                                  | 55 |

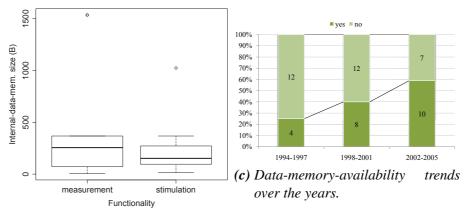

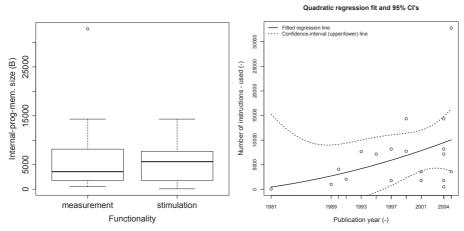

| 2.25 | Implant internal-data-memory availability and size                                                   | 56 |

| 2.26 | Internal-data-memory trends over the years                                                           | 57 |

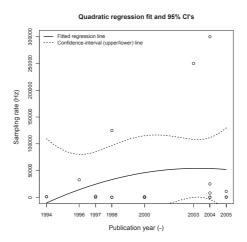

| 2.27 | Implant sampling-frequency trends over the years                                                     | 59 |

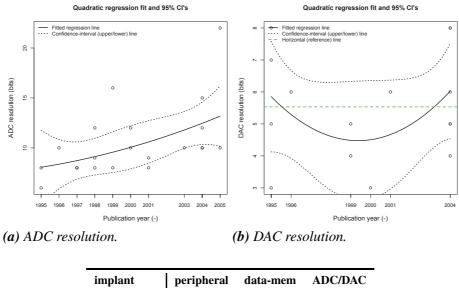

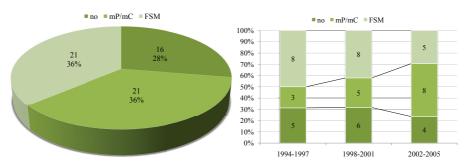

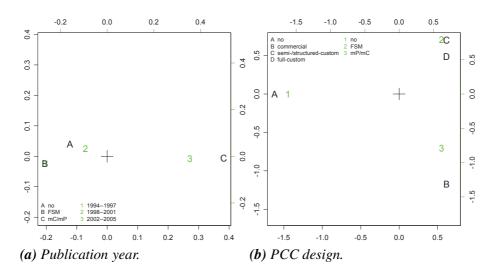

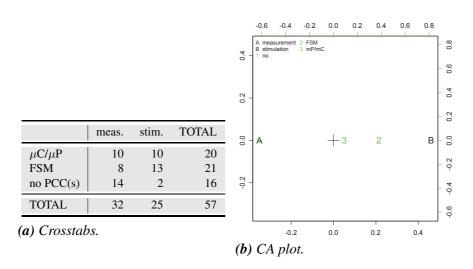

| 2.28 | ADC and DAC resolution trends over the years                                                         | 60 |

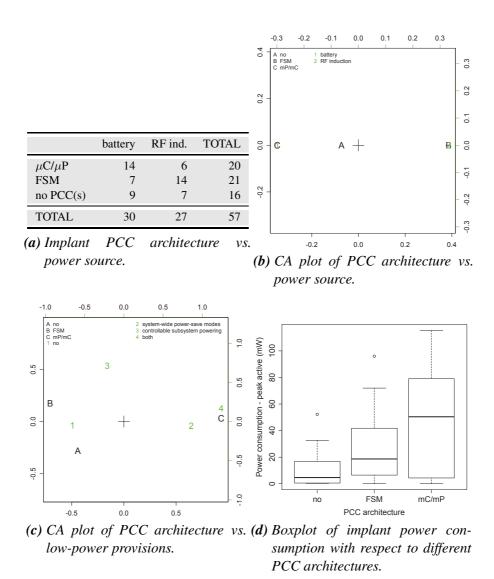

| 2.29 | Implant PCC architecture                                                                             | 61 |

| 2.30 | CA plots of PCC architecture vs. PCC design and publication year                                     | 62 |

| 2.31 | Implant PCC architecture vs. functionality                                                           | 64 |

| 2.32 | Implant PCC architecture vs. power features                                                          | 66 |

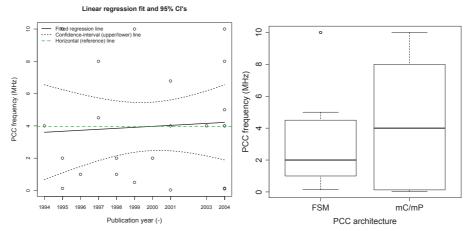

| 2.33 | PCC-operating-frequency characteristics with respect to PCC architecture and trends over the years   | 68 |

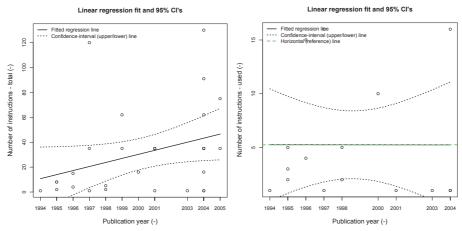

| 2.34 | Number of used and total instructions per implant PCC over the years                                 | 69 |

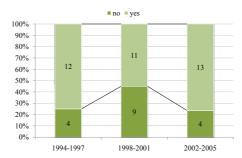

| 2.35 | Relative distribution of implants featuring adjustable peripherals over the years                    | 71 |

| 2.36 | CA plot of implant adjustability vs. publication year                                                | 72 |

| 2.37 | Relative distribution of implants featuring versatile (interchangeable) peripherals over the years   | 73 |

| 2.38 | CA plot of implant versatility vs. publication year                                                  | 7: |

| 2.39 | CA plot of implant programmability vs. publication year                                              | 76 |

| 2.40 | Implant programmability capabilities and trends over the years.                                                            | 77    |

|------|----------------------------------------------------------------------------------------------------------------------------|-------|

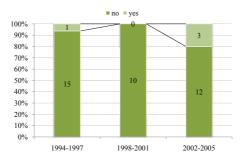

| 2.41 | Relative distribution of implants based on a modular design over the years                                                 | 79    |

| 2.42 | CA plot of implant modularity vs. publication year                                                                         | 80    |

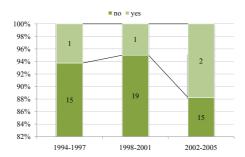

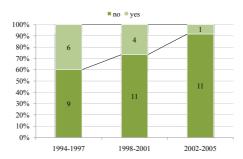

| 2.43 | Relative distribution of implants with reliability provisions over the years                                               | 81    |

| 2.44 | CA plot of implant reliability vs. publication year                                                                        | 82    |

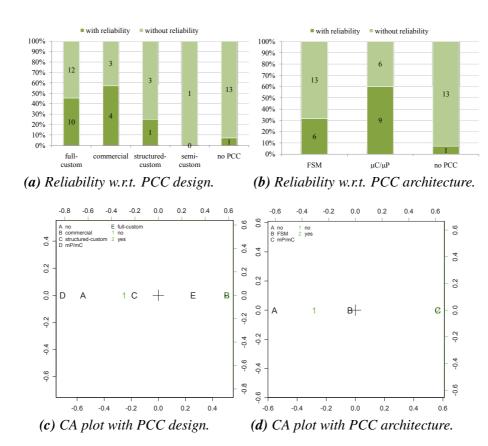

| 2.45 | Distribution of reliability per PCC design and per PCC architecture.                                                       | 83    |

| 3.1  | Block diagram of the SiMS concept                                                                                          | 92    |

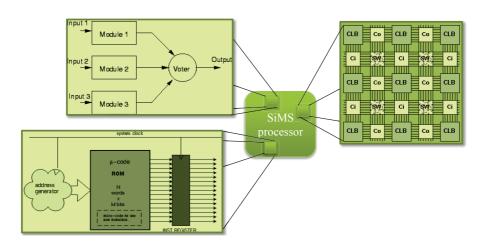

| 3.2  | Reconfigurable hardware, replicated hardware and microcoded units in the SiMS processor.                                   | 93    |

| 3.3  | Overview of dependability guarantee through SiMS-compiler provisions                                                       | 96    |

| 3.4  | Compiler scheduling of test instructions                                                                                   | 97    |

| 3.5  | Involved risk factors with (A) and without (B) a design platform.                                                          | 101   |

| 4.1  | XTREM-generated power profile for single program execution.                                                                | 120   |

| 4.2  | Envisioned standard tasks of implant processors                                                                            | 124   |

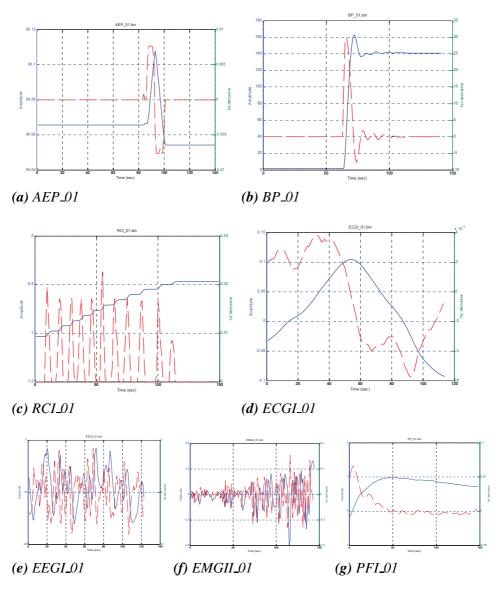

| 4.3  | Dataset amplitude vs. time and first-order derivative of amplitude vs. time                                                | 130   |

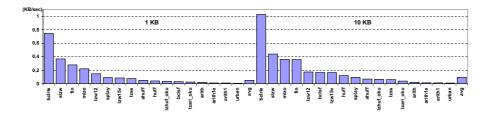

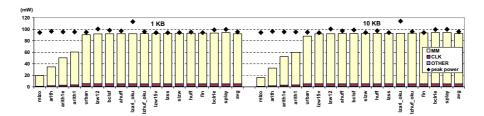

| 4.4  | Per-component, average power consumption (in mW) for two plaintext sizes                                                   | 134   |

| 4.5  | Average and peak power consumption (in mW) for two plaintext sizes                                                         | 136   |

| 4.6  | Per-component and total encryption energy costs (in Joules)                                                                | 137   |

| 4.7  | Computation overhead of ciphers manifested as energy penalty (in Joules) when encrypting one 10-KB and ten 1-KB plaintexts | 138   |

| 4.8  | Encryption rate (in KB/sec).                                                                                               | 139   |

| 4.9  | ARM microcode representation and MISTY1 $\mu$ op frequencies                                                               | 142   |

| 4.10 | Averaged compression ratios for 1-KB and 10-KB datasets                                                                    | 147   |

| 1.10 | 11. orașea compression ranos for 1-1xD and 10-1xD datasets                                                                 | 1 T / |

| 4.11 | Averaged, average compression rates for 1-KB and 10-KB datasets                                              | 148 |

|------|--------------------------------------------------------------------------------------------------------------|-----|

| 4.12 | Averaged, average and peak power consumption for 1-KB and 10-KB datasets                                     | 149 |

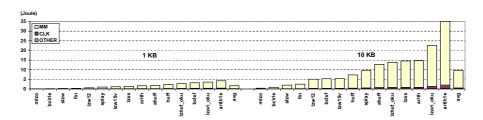

| 4.13 | Averaged, total energy expenditure for 1-KB and 10-KB datasets                                               | 150 |

| 4.14 | IPCs, I-/D-cache hit rates and branch-prediction rates                                                       | 161 |

| 4.15 | Static code size (in KB) and dynamic code size (instruction and clock-cycle count)                           | 163 |

| 4.16 | Relative frequencies for load/store/move, arithmetic (int/fp), compare, logic and branch/jump instructions   | 165 |

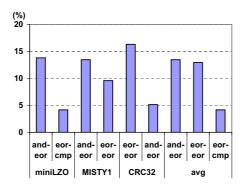

| 4.17 | Relative frequencies of data-dependent, dynamic-instruction combinations                                     | 166 |

| 4.18 | Per-component and overall average power consumption                                                          | 167 |

| 4.19 | DMU device lateral photograph                                                                                | 169 |

| 4.20 | Block diagram of simulated implant application and data-<br>payload sizes                                    | 171 |

| 4.21 | Average IPCs, I-/D-cache hit rates and branch-prediction rates.                                              | 172 |

| 4.22 | Per-component and overall average power consumption                                                          | 173 |

| 4.23 | Per-component and overall total energy expenditure                                                           | 174 |

| 4.24 | Relative frequencies for load/store, move, arithmetic, compare, logical and branch/jump $\mu$ op             | 174 |

| 4.25 | Relative frequencies of data-dependent, dynamic- $\mu$ op combinations                                       | 175 |

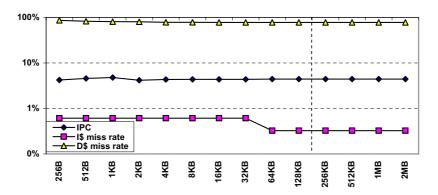

| 5.1  | Averaged, average IPC and I/D-cache miss rates for various direct-mapped, I-cache sizes                      | 183 |

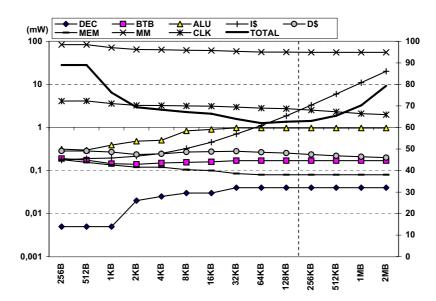

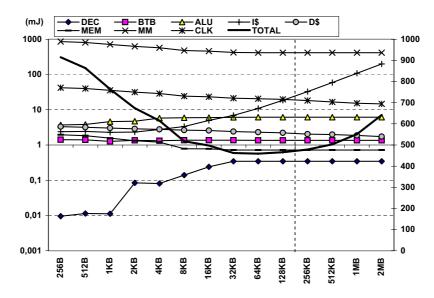

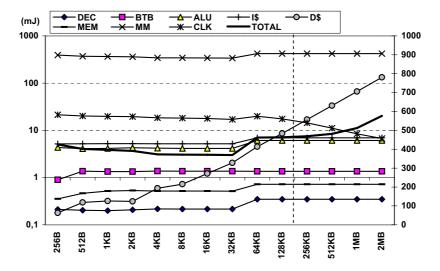

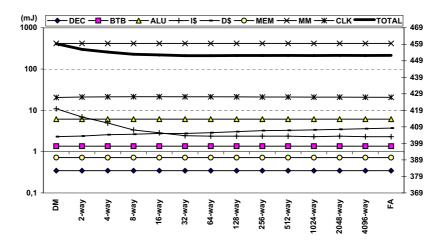

| 5.2  | Averaged, total and per-component average power consumption (in mW) for various direct-mapped, I-cache sizes | 185 |

| 5.3  | Averaged, total and per-component energy budget (in mJ) for various direct-mapped, I-cache sizes             | 186 |

| 5.4  | Averaged, average IPC and I/D-cache miss rates for various direct-mapped, D-cache sizes                      | 186 |

| 5.5  | Averaged, total and per-component average power consump-                                                               |     |

|------|------------------------------------------------------------------------------------------------------------------------|-----|

|      | tion (in mW) for various direct-mapped, D-cache sizes                                                                  | 187 |

| 5.6  | Averaged, total and per-component energy budget (in mJ) for various direct-mapped, D-cache sizes                       | 187 |

| 5.7  | Results for various I- and D-cache sizes of objective function (5.1)                                                   | 189 |

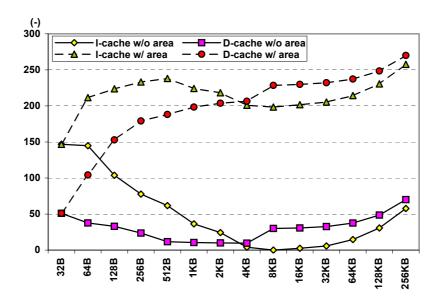

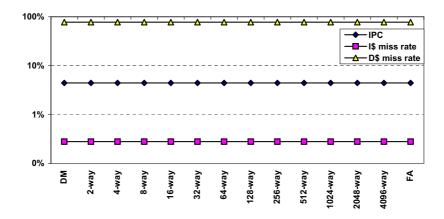

| 5.8  | Averaged, average IPC and I/D-cache miss rates for various I-cache associativity degrees                               | 190 |

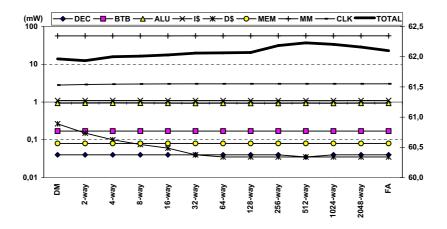

| 5.9  | Averaged, total and per-component average power consumption (in mW) for various I-cache associativity degrees. $\dots$ | 191 |

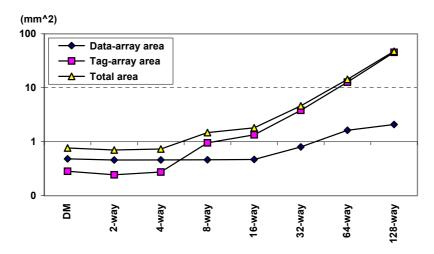

| 5.10 | Averaged, total and per-component energy budget (in mJ) for various direct-mapped, I-cache associativity degrees       | 192 |

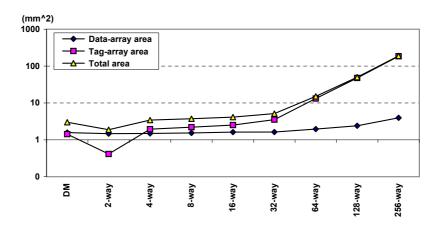

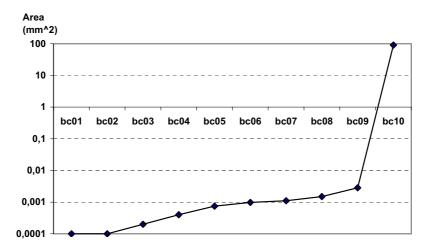

| 5.11 | Data-array, tag-array and total area (in $mm^2$ ) for various I-cache associativity degrees                            | 192 |

| 5.12 | Averaged, average IPC and I/D-cache miss rates for various D-cache associativity degrees                               | 193 |

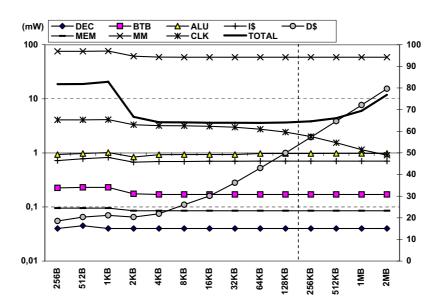

| 5.13 | Averaged, total and per-component average power consumption (in mW) for various D-cache associativity degrees          | 194 |

| 5.14 | Averaged, total and per-component energy budget (in mJ) for various D-cache associativity degrees.                     | 194 |

| 5.15 | Data-array, tag-array and total area (in mm <sup>2</sup> ) for various D-cache associativity degrees                   | 195 |

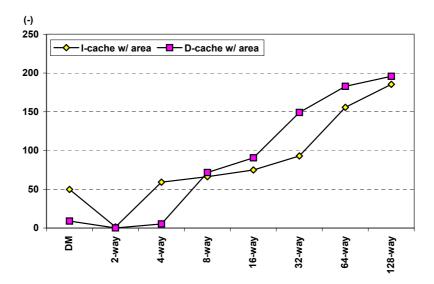

| 5.16 | Results for various I- and D-cache associativity degrees of objective function (5.3)                                   | 196 |

| 5.17 | Illustration of a BTB entry in the case of a bimodal predictor                                                         | 199 |

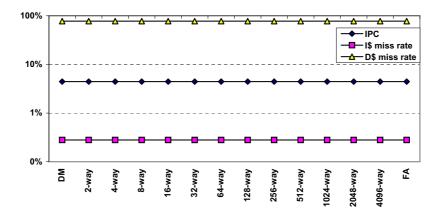

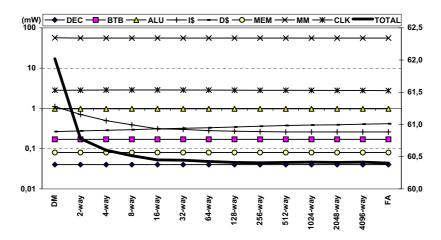

| 5.18 | Normalized, average IPCs and normalized overall branch miss rate for various BPRED/cache configurations                | 201 |

| 5.19 | Normalized, average power consumption for various BPRED/cache configurations.                                          | 202 |

| 5.20 | Normalized, average power consumption per instruction per cycle for various BPRED/cache configurations                 | 203 |

| 5.21 | Normalized, total energy expenditure for various BPRED/-cache configurations                                           | 204 |

| 5.22 | Normalized, total energy expenditure per instruction per cycle for various BPRED/cache configurations                          | 205 |

|------|--------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.23 | Total BPRED-scheme area (in $mm^2$ ) for all BPRED configurations                                                              | 205 |

| 5.24 | Normalized results to the minimum value for various cache configurations of objective function (5.1) when area is included.    | 207 |

| 5.25 | Normalized results to the minimum value for various cache configurations of objective function (5.1) when area is not included | 208 |

| 6.1  | Framework organization                                                                                                         | 214 |

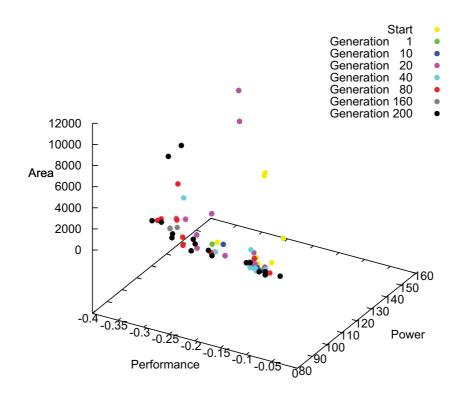

| 6.2  | ImpEDE-generated Pareto solutions                                                                                              | 215 |

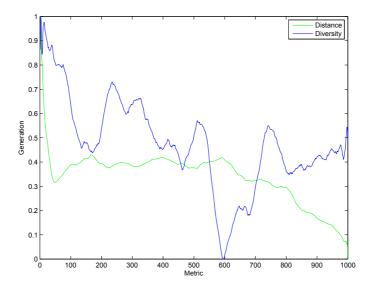

| 6.3  | Smoothed distance and diversity metrics over 1000 generations (Benchmark: checksum)                                            | 223 |

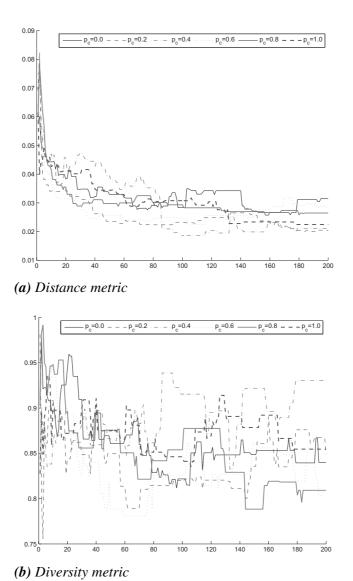

| 6.4  | Distance and Diversity metrics for various crossover probabilities $(P_c)$ over 200 generations (Benchmark: checksum)          | 225 |

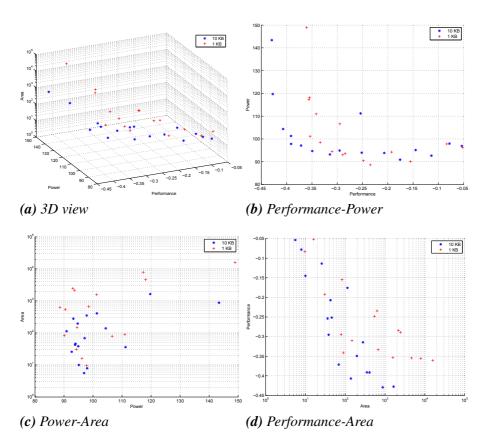

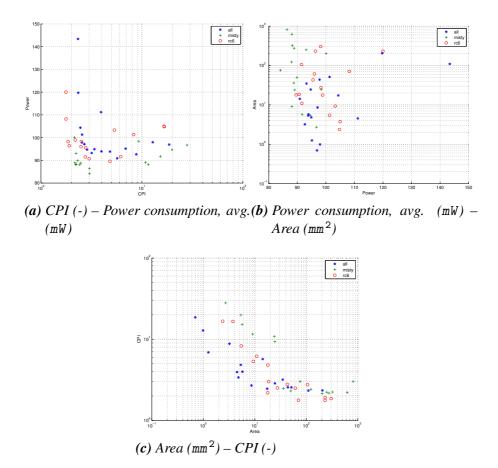

| 6.5  | Baseline DSE results for 1 KB and 10 KB datasets running on all benchmarks                                                     | 227 |

| 6.6  | Block diagram of simulated implant application with realtime deadlines                                                         | 228 |

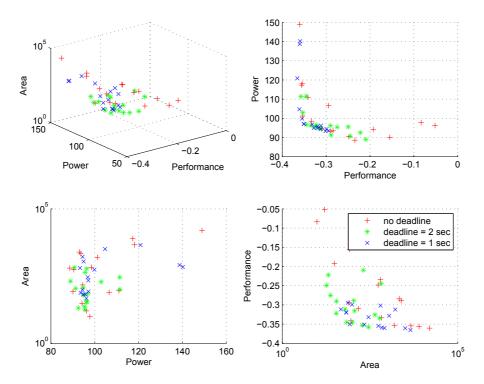

| 6.7  | DSE results expanded with hard realtime deadlines of 2 seconds and 1 second for 10 KB datasets running on all benchmarks       | 229 |

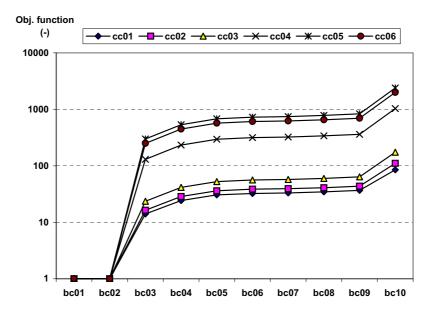

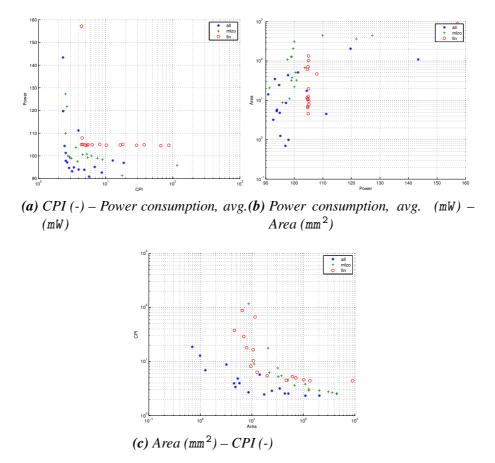

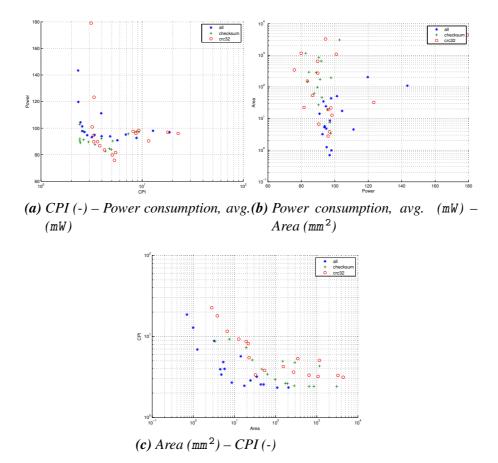

| 6.8  | Final Pareto-fronts (after 200 generations) for lossless-compression benchmarks on $10 - KB$ datasets                          | 236 |

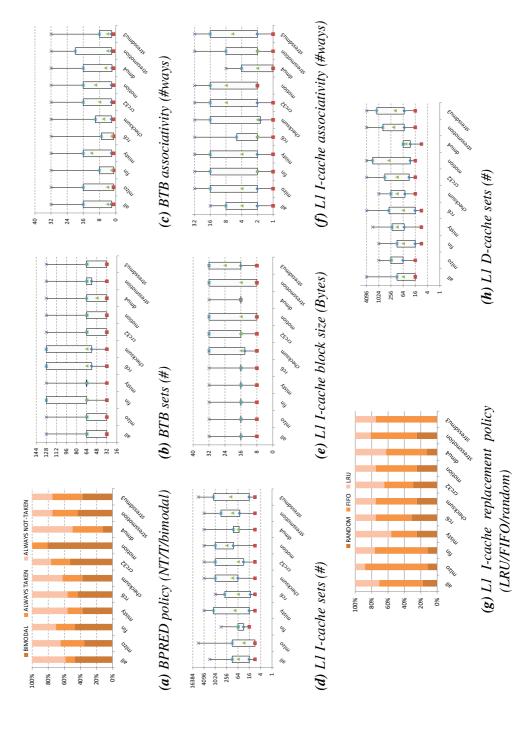

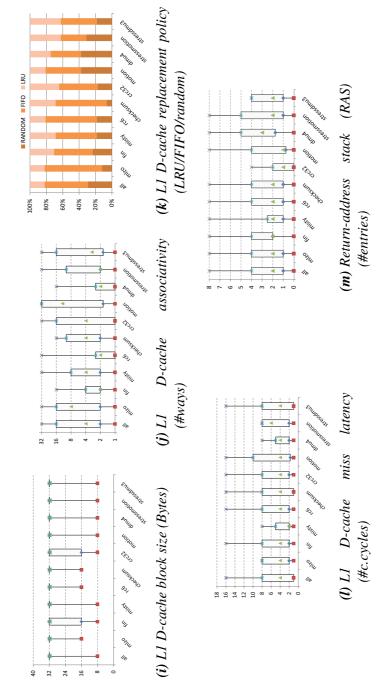

| 6.9  | Hardware requirements of optimal processors, as evolved over 200-generation runs                                               | 238 |

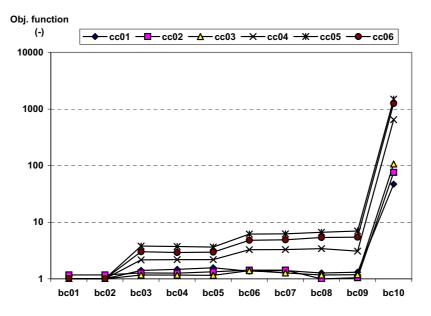

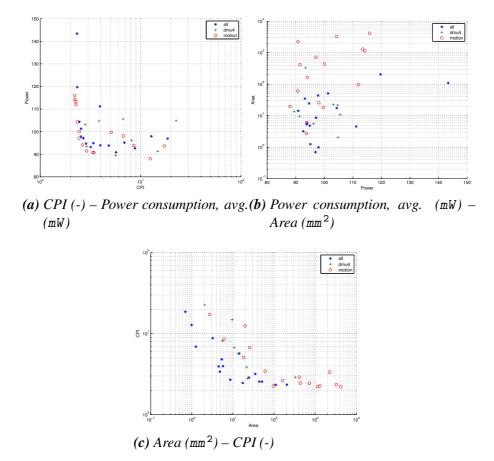

| 6.10 | Final (after 200 generations) Pareto-fronts for symmetric-encryption benchmarks on $10 - KB$ datasets                          | 240 |

| 6.11 | Final (after 200 generations) Pareto-fronts for data-integrity benchmarks on $10 - KB$ datasets                                | 242 |

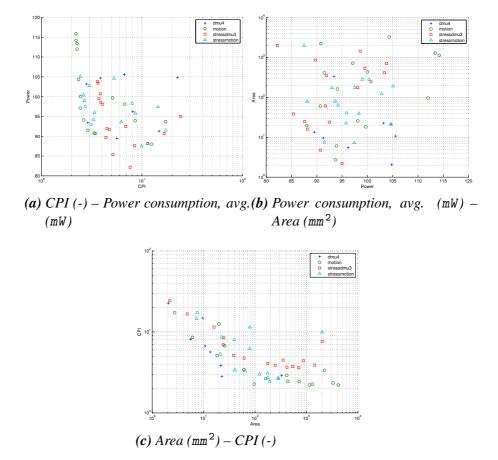

| 6.12 | Final (after 200 generations) Pareto-fronts for real applications on $10 - KB$ datasets                                        | 244 |

| 6.13 | Final (after 200 generations) Pareto-fronts for real applications and stressmarks on their respective datasets                 | 245 |

| 6.14 | Block diagram of simulated implant application with realtime |     |  |  |  |

|------|--------------------------------------------------------------|-----|--|--|--|

|      | deadlines                                                    | 249 |  |  |  |

| 6.15 | Comparison of study cases and DSE results for 10 KB datasets |     |  |  |  |

|      | running on the selected benchmarks.                          | 256 |  |  |  |

# List of Acronyms

ADC Analog-to-Digital Converter

ASIC Application-Specific Integrated Circuit

BAN Body-area Network

**BiCMOS** Bipolar CMOS

BioMEMS Special MEMS class wherein biological matter is manipulated

**BP** Blood Pressure

**BPRED** Branch PREDiction

CMOS Complementary Metal-Oxide Semiconductor

CNS Central Nervous System

**COTS** Commercial-Of-The-Shelf

**CRC** Cyclic-Redundancy Check

**DAC** Digital-to-Analog Converter

**DBS** Deep-Brain Stimulation

**DDM** Denervated, Degenerated Muscle

**DFR** Design For Reliability

**DSE** Design-Space Exploration

**ECG** Electro-Cardio-Graphy

EDA [in Computer Eng.] Electronic Design Automation

EDA [in Statistics] Exploratory Data Analysis

EMC Electro-Magnetic Compliance

EMG Electro-Myo-Graphy

EMI Electro-Magnetic Interference

**ENG** Electro-Neuro-Graphy

**EOG** Electro-Oculo-Graphy

**EPIC** Explicitly-Parallel-Instruction Computing

FES Functional Electrical Stimulation

FNS Functional, Neuromuscular Stimulation

FP Floating Point

FSM Finite-State Machine

**GA** Genetic Algorithm

**HDL** Hardware Description Language

**HLL** High-Level Language

**HPC** Hardware Performance Counter

IC Integrated Circuit

ICD Intra-Cardiac Defibrillator

**ICP** Intra-Cranial Pressure

ILP Instruction-Level Parallelism

IP Intellectual Property

IPC Instructions per Cycle

ISA Instruction-Set Architecture

LSK Load-Shift Keying

MEMS Micro-Electro-Mechanical System

**NPA** Non-Programmable Accelerator

**NPM** New Public Management

PCB Printed-Circuit Board

PCC Processing and/or Controlling Core

PD Parkinson's Disease

PDA Personal Digital Assistant

PNS Peripheral Nervous System

QoS Quality of Service

QRS The most visually obvious deflections seen on a typical ECG

RAS Return-Address Stack

RF Radio Frequency

RSNA Renal-Sympathetic-Nerve Activity

SC Switched-Capacitor

**SCS** Spinal-Cord Stimulation

**SE** Standard Error  $(\sigma)$

SNR Signal-to-Noise Ratio

SoC System-on-Chip

**ULP** Ultra-Low Power

UWB Ultra-Wide-Band

VLIW Very-Long-Instruction Word

WSN Wireless Sensor Network

# Introduction

OME to think of it, human inventions have always aspired to imitate nature. And shameless imitation it has been to the accuracy allowed by each era's conquered scientific knowledge and available technical means. This mimicry has at times been conscious and at others not. The Da Vinci Glider [ca. 1500] (Figure 1.1) is an infamous instance of such an attempt to imitate bird flight. Da Vinci went all the way from the theory of flight to – actually – designing flying machines and attempting to fly them. The fact that the original design proved to be too heavy for flight is besides the point.

# 1.1 Background

It may sound far-fetched at first but (bio)medical implants are just another instance of mimicking nature throughout human history. Prosthetic body parts such as wooden limbs and reeds for looking and listening inside the human body are proved to have been used by ancient Egyptians as early as 3,000 years B.C.. In recent years, scientific knowledge underpinned by astounding technological achievements - the "technical means" previously mentioned in fields such as microelectronics technology as well as material science and more have led to the fully implantable pacemaker. The implant was developed in 1958 and 1959 (of course, not microelectronic at the time) by Wilson Greatbatch and William M. Chardack and has been the first device to be implanted successfully into the human body and to operate seamlessly for long periods of time – modern pacemakers feature an in-body lifetime of a decade or longer. Perhaps more importantly, it has also acted as a catalyst on the general public closed-mindedness against biomedical implants. Ever since the pacemaker, a plethora of other biomedical implants has also been proposed for solving various medical problems, however, only a few of them have made it to the market

Figure 1.1: The Da Vinci glider design.

such as the widespread cochlear implants and the deep-brain stimulators for treating Parkinson's Disease.

#### 1.2 Problem overview

#### 1.2.1 Socioeconomic trends

Signified by the advent of the first, implantable pacemaker in the late fifties, biomedical microelectronic implants have evolved rapidly over the last 50 years, as much in application scope as in sophistication. However, a close look at the current implant market reveals relatively few successfully commercialized ideas. The phenomenon can be attributed to a number of reasons:

- the until recent times limited knowledge of many aspects of the human body combined with the large inter-patient genetic variability when coming to human pathoses, which makes it difficult and risky to define clear-cut implantable solutions to address all of them; and

- the practical limitations posed so far by technology; for instance, transistor sizes have not been small enough to allow for complex implant designs to fit inside the tight constraints of the human body. Besides, substituting sophisticated, physiological structures with artificial ones is a highly complex and largely interdisciplinary task.

While problems such as the above have been allowing for slow yet steady implant progress, current *socioeconomic trends* manifesting in modern societies may not permit us even this pace any longer. To illustrate, in advanced countries the following cascading trends are currently being observed:

- Population is aging through a net reduction in birth rates combined with an increase in life expectancy;

- Healthcare costs are growing out of proportion; and

- Higher demands for betterment of quality of life are placed (health, fitness, convenience etc.).

Healthcare in the 21st century is changing rapidly. In advanced countries, in particular, healthcare is moving from a public to a more personalized nature [3, 26]. The costs of healthcare worldwide are increasing every year. In the Netherlands, in particular, the government is trying to keep the health insurances affordable for all citizens by periodically reorganizing the system. Since healthcare spending always increases at a much faster rate than the average income, such practices work only for a limited period of time. The rising healthcare costs, in combination with population aging (i.e. more potential customers for the healthcare system), form a tough challenge for modern societies.

Such socioeconomic trends have given birth to the notion of *personalized healthcare*. The term introduces a new approach to effective healthcare – as far as economics go, at least – whereby default hospitalization and generic treatment of patients will be discouraged and supplanted by *patient-targeted* prognosis, diagnosis and, mainly, treatment. It is highly conceivable that *technology* will be the vehicle for enabling personalized healthcare. Similar trends have already been witnessed in the cell-phone and portable-computing technological revolutions.

Better use of technology – and, in our case, implants – can and should be used to get control of healthcare costs. For example, continuous monitoring of physiological parameters can be used instead of occasional meetings with the doctor. Having an up-to-date and complete picture of the changes in a patients condition will enable disease prognosis, which by definition is more effective and less costly than disease treatment. It should be stressed that such technology will be used not only for high-risk or chronic patients, but also for general lower-risk patients over periods of normal activity in their home or work environment.

Implants have clearly benefitted from the astounding recent *technology-miniaturization* trends [66], boasting smaller sizes, lower power consumption and increased performance of the transistor devices. Simply put, while the human-body dimensions have not changed, microelectronics dimensions have – by proportion – shrank to such an extent that modern implants are becoming sufficiently sophisticated and small so as to treat various human pathoses, even at the most constrained parts of the human body. It is this practical property along with their wider acceptance in modern societies that is making them a primary technological driver towards personalized healthcare.

#### 1.2.2 Implant-device trends

Although biomedical implants may be (advertised to be) a primary vehicle for the brave, new era in personalized healthcare, it has come to our attention – and we have verified it through an extensive survey – implant design is undergoing a shift itself. Namely, implants are gradually moving from application-specific, rigid (e.g. FSM-based) systems to more flexible (e.g.  $\mu$ Processor-based) ones. This implies that, in the near future, implant functionality will be based on executed software (written in some high-level, established language like C) rather than on hardwired circuits. However, this turn of events does not come for free; adverse effects are being witnessed:

- Implant *power budgets are increasing* over time, even though transistor dimensions are shrinking and implemented device functionality is not overtly complex;

- Implants exhibit serious absence of design for reliability. Softwarebased, ad-hoc reliability techniques have been replacing inherently reliable implant designs over the years. For a field of highly-mission critical embedded systems where human lives and high costs are involved, this poses a significant problem;

- Product development is still *highly application-specific*, even though implant designs are becoming more structured. Already established product cases such as the family of pacemakers introduced by Medtronic, Inc. [91], where previous design expertise is (re)used to enhance the next device version, are currently the exception.

1.3. MOTIVATION 5

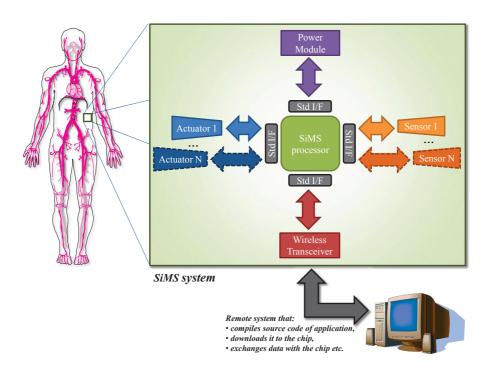

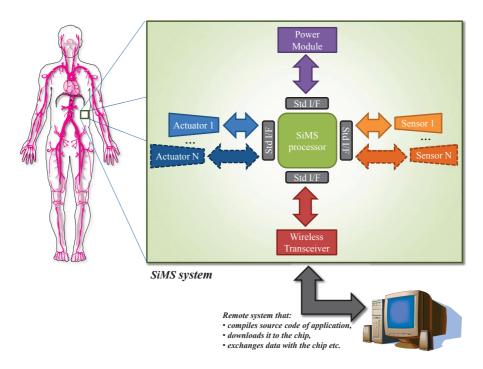

Figure 1.2: Block diagram of the SiMS concept.

### 1.3 Motivation

Operating under the assumption that implants will be the vehicle towards improved, personal healthcare and, in view of the aforementioned transitions, we believe that a *new paradigm in implant design* is required.

In this dissertation we introduce **Smart implantable Medical Systems** (**SiMS**). SiMS is a *systematic* approach – a framework – for providing biomedical researchers (and, hopefully, industry) with a toolbox of ready-to-use, highly reliable implant sub-systems and models in order to construct (optimal) implants for various medical applications. The SiMS framework is conceptually illustrated in Figure 1.2; it has to guarantee the following attributes:

- high dependability (reliability, availability, maintainability and safety);

- modular, versatile design for design reuse;

- ultra-low power consumption; and

- miniature size.

Devices built on the SiMS framework will be small, *fine-tuned* implantable devices to the application at hand, yet built of *generic* components. Without requiring redesign, they will be able to *measure* and/or *regulate* one or multiple biomedical parameters simultaneously and communicate with external (out-of-body) computing equipment wirelessly. Given that such devices are directly related to human life, they will be characterized by very high **reliability** and some degree of **autonomy** and **self-awareness** (within extremely demanding **low power** and **size** constraints).

A cornerstone of the SiMS framework is the **SiMS processor** which will be characterized by and will support the aforementioned attributes. After describing the overall SiMS framework, our foremost goal in this dissertation is the specification of the SiMS processor. In effect, we explore optimal processor configurations which are best-suited for serving diverse implant applications (i.e. have universal applicability) while exhibiting low power consumption, low energy expenditure and low area cost.

## 1.4 Dissertation challenges & contributions

Throughout this dissertation work, we have encountered various challenges of which we were utterly oblivious at the outset. Such challenges are as follows:

- Since the SiMS approach is original, no useful literature or resource base exists: Design specifications, reference designs, established benchmarking platform as well as suitable design tools are unavailable;

- The implant field is ruled by high risks and high profits. Implant companies generally assume a highly conservative (and often secretive) stance towards new product development. Their current state of the art has virtually been inaccessible to us to use for reference. A lot of careful guess-work is required;

- We are attempting to propose a different approach on implant design.

As with everything new, this has raised strong reactions from the current status-quo and, conversely, has made us question every new step we made in this unknown ground.

With this dissertation, the following diverse contributions have been delivered:

• Comprehensive survey and analysis of implantable systems revealed crucial trends in the field,

- Conceptualization and setup of a new, top-down design paradigm for implantable systems (SiMS),

- Development of new simulation/evaluation/DSE tools for implant processor design. Development of benchmarking base, and

- Automatic, multiobjective design-space exploration of optimal SiMS processor architectures.

We should make clear that, within the SiMS project, it has *not* been our express goal to propose novel implant applications but, rather, to specify a sound framework upon which many existent (but certainly not all) and, most importantly, new implant applications can be built. SiMS shall guarantee a reduction of development times by providing a solid substrate onto which prior art will be brought together, combined and integrated in the final product. Such prior art will be in the form of Intellectual-Property hardware and software components, all proven, pre-verified and pre-tested according to (inter)national medical-safety regulations. This shall, in turn, guarantee an increase in component-and device-level reliability.

By being fully aware that implantable devices are fruits of a multidisciplinary, combined effort, we also work within the SiMS framework towards a clear separation of partner expertices. That is, we aim at a framework where engineers from different fields provide the system architecture, the sensors and actuators, the power source, the wireless transceiver etc., while medical experts are actively involved in composing, adjusting the final system to the particular patient needs.

# 1.5 Dissertation organization

The dissertation at hand has been organized in chapters, each handling a different item of study.

In Chapter 2 we present the findings of an extensive *survey* performed on more than 60 different implantable systems, found in the *literature*. To make the analysis manageable, findings have been taxonomized in different categories covering all aspects of modern implantable systems. The chapter concludes by summarizing the most crucial trends observed in the implant domain, thus, providing the scientific background onto which the SiMS project has been based.

In Chapter 3 we discuss at length the socioeconomic drifts necessitating the

inception of SiMS. We, then, describe the *SiMS concept* in detail and present the *background information* required for its realization.

Chapter 4 is occupied with defining the *simulation environment* – simulator, benchmarks, input datasets – for our further experiments. The simulator employed is detailed and practical issues are discussed. Original *benchmark programs* are being investigated and the most suitable ones are grouped in a *novel benchmark suite* for implant processors, called **ImpBench**. Proper *input datasets* to these benchmarks are also discussed. With all pieces of the simulation environment finally in place, we conclude the chapter with the *case study* of an instance SiMS-processor application.

In Chapter 5, we offer an in-depth exploratory study on suitable cache organizations and branch-prediction policies for a novel processor for SiMS-based implants. Our standard first-order, optimization goals *performance*, *power consumption* and *energy expenditure* are in this chapter expanded by a third one, *area utilization*.

In Chapter 6, we first introduce **ImpEDE**, a new tool offering *automated*, *multiobjective* DSE (Design-Space Exploration) of optimal SiMS processor microarchitectural configurations. Through ImpEDE, we introduce one more optimization goal – *execution time* – next to performance, power consumption, energy expenditure and area. The need to introduce the notion of "hard deadlines" in program execution have coerced us in developing an updated version of ImpBench (v1.1), reported next. As a last and culminating point in this thesis, we utilize ImpEDE, ImpBench v1.1 and suitable implant applications extracted from the survey in Chapter 2 to offer a number of optimal SiMS-processor solutions.

Last, Chapter 7 provides concluding remarks on the work presented. The chapter summarizes the dissertation, outlines its contributions and proposes future research directions.

# 2

# A survey on microelectronic implants

HILE at first restricted to the field of pacemakers, biomedical microelectronic implants nowadays boast an expanding number of biomedical applications. These technological innovations have brought about a revolution in existing methods for disease diagnosis and therapy. However, the relatively short lifespan of the implant domain – traditionally subject to tight, demand-driven design policies and bound by economical constraints – has resulted in the absence of a holistic view of the field.

Structured, repeatable methods of implant design are currently sorely missed and previous, precious know-how is currently being wasted and rediscovered. Before any systematic implant-design approach such as the one we take in SiMS is feasible, a careful exploration of the field must take place.

In this chapter we present selected findings of an extensive *survey* performed on more than 60 different implantable systems, found in the literature. To make the analysis manageable, findings have been taxonomized in different categories covering all aspects of modern implantable systems. The chapter concludes by summarizing the most crucial trends observed in the implant domain, thus, providing the scientific background onto which the SiMS project has been based.

# 2.1 Survey goals

An extensive survey has been performed and serves a **twofold purpose**. Firstly, we create a detailed *implant taxonomy* of a large number of systems. An extensive list of device attributes has been extracted and a subset thereof (pertinent to the rest of this thesis) is presented in this chapter. Information has been collected, organized and is presented in a highly structured manner.

Secondly, we attempt to present a clear picture of the past and present state of things in the field: More than 60 implant cases over the period 1974–2005 have been studied and included in the survey. We also attempt to uncover potential problems along the way, and, through making suggestions for future design, to propose new directions for implant design. Survey results are, thus, extensively *commented* and *annotated*, and analysis is backed by *statistical tests* of the gathered data, where possible.

# 2.2 Survey scope

For this survey, reported literature dating back to 1974 has been collected but the scarcity of reported study cases in those earlier years has forced us to primarily focus on the more densely populated 12-year period 1994–2005. As we shall see through the course of this analysis, even for this later period, available data is very limited (i.e. *sample size* is small). To make matters worse, collected data is very "noisy" (i.e. *variance* is large), reflecting the aforementioned diverse nature and non-structured approach in implant design. Although both these effects weaken the strength of many of our performed statistical tests, we do include many such tests in the current study for completeness purposes and in the hopes of repeating them in an extended, future study on a larger sample size. Splitting the data into more focused subgroups might solve the variance problem but would result in prohibitively small sample-data sizes which would weaken our analysis.

While the, often, significant data variance is an inherent side-effect of the studied field, we have attempted to collect robust albeit more limited sample data. Robustness stems from the **scope** of this survey which has been restricted to study cases adhering to the following two requirements:

- 1. **Complete systems:** Stand-alone working devices providing complete functionality are considered; thus, simple implant components such as electronic front-ends, biosensors, readout electronics etc. are excluded.

- Microelectronic devices: Microelectronics- and MEMS-based devices for in-vivo operation are considered; thus, mechanical implants (e.g. artificial limbs), implant packaging, devices for medical studies (e.g. bioassay chips) etc. are excluded.

The rationale behind the above requirements lies in the fact that, first, we are interested in **complete implant solutions** available so far. We wish to investigate functional devices which have been designed with the whole system in mind, under system-wide design considerations. Second, we are especially focusing on the **architecture of the processing and/or controlling cores** (collectively termed PCC's) residing inside such systems since our expertise, interest and prior work chiefly lies in the field of computer architectures. It is, further, our strong belief that the implant architecture is a design aspect to benefit greatly from the recent advances in microtechnology and, due to this fact, also an aspect wherein lies much room for improvement.

Overall, with this study we are primarily interested in presenting how microelectronic implants have developed over the years from a system's perspective. This is not to say that other aspects of implant design such as e.g. device packaging should be overlooked. On the contrary, packing is one of the key elements for chronic implantation of implantable devices these days. However, it pertains to other fields of study like, for instance, materials science and, as such, lies outside the scope of this survey.

It should be stressed that all surveyed systems originate from published literature across various biomedical, microelectronics and other fields of science. That is, almost all devices are academic-level and not commercialized systems, with all that this implies. We are aware that this selection is *biased* in a number of ways: i) surveyed devices may have not reached the *level of optimization* demanded of industrial products, and ii) surveyed devices may not be accurately reflecting the at-the-time commercial state of the art, as devices used for research tend to be more *ambitious* and, in many ways, ahead of their time.

However, we do not expect these biasing effects to have a annulling effect on the findings of this survey for academia and industry alike: As it turns out, the implant domain still is a very limited embedded-systems subdomain whereby the path from a successfully researched new implant to a commercial product is short and straightforward.

What is more – and as will be made evident through the process of this study – most of the studied devices have actually been *implanted* in living animal or human specimens and *in-vivo* evaluated. As a result, functional specifications as well as physical dimensions had to have reached a high level of sophistication<sup>1</sup> before being tested, which is more than most experimental embedded devices can brag in other domains.

<sup>&</sup>lt;sup>1</sup>See, for instance, the discussion on implant chipset and packaging size in Section 2.6.2. Dimensions are very close to those of existing commercial systems.

In any case, this survey and analysis is a best-effort yet unique attempt at collecting, taxonomizing and characterizing data from a domain traditionally governed by high risks as well as profits; thus, by high secrecy, royalty-protected designs and largely non-disclosed information.

Last but not least, this survey has not been intended as a starting point for discussions on the impact biomedical implants have on societies or their ethical implications thereupon. Without dismissing the *ethical repercussions* arising from the improvement and widespread adoption of such devices, we restrict discussion on strictly technical matters throughout this document.

# 2.3 Survey structure

Overall survey structure is as follows: Section 2.4 gives a short description of the main components of microelectronic implants and their functionality. In Section 2.5, we discuss at length the imposed classification parameters we have used for organizing the survey information and we present the different types of statistical tests we are going to perform on them. Section 2.6 analyzes the survey findings through the use of illustrated observations and statistical analysis. Overall conclusions are drawn in Section 2.7.

# 2.4 An implant primer

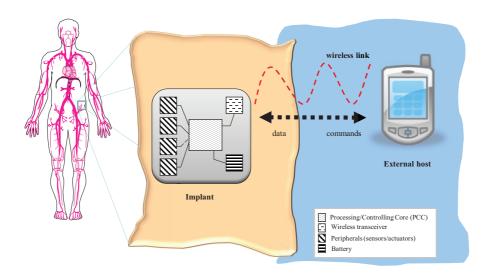

Since various parameters of microelectronic implants are investigated in this survey, a quick overview of the major implant subsystems is given here. A conceptual illustration of a typical microelectronic implant is depicted in Figure 2.1. As can be seen from the figure, a typical, modern implantable system comprises the following parts:

- **Internal part:** The actual *implant* with peripherals (sensors, actuators, wireless transceiver, power source etc.)

- External part: The (optional) external host unit (e.g. PDA) controlling or simply auditing the implant.

- Communication link: The (optional) wireless link between the internal and external part for exchange of physiological data and/or implantable-device commands.

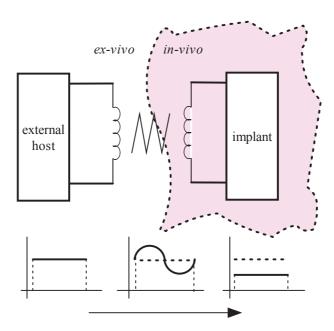

Figure 2.1: Concept of a typical implantable system.

The *internal part* consists of combinations of different components, most often, what we have termed a *Processing/Controlling Core* (PCC) lies in the heart of the device coordinating overall operation. Acquisition of physiological data on the part of the implants is usually achieved through appropriate *sensors* whereas intervention to the human body (such as insulin administration, nerve and muscle electrical stimulation, to name a few) is effectuated through *actuators*. One or more sensors and/or actuators collectively termed *peripherals* are included in the implant. Such peripherals realize the physical interface to the body, measuring and/or affecting physiological quantities, respectively.

A common characteristic in many modern implants is their ability to percutaneously accept commands from an external host system (e.g. computer, handheld device) and/or to transmit physiological data outwards, as measured from inside the body over a transcutaneous interface. *Communication* between the internal and external parts is optional yet is increasingly used these days, is commonly achieved wirelessly and can, per case, be unidirectional or bidirectional. For this reason implants also include some kind of wireless transceiver as a peripheral unit to the PCC.

*Power* inside the implant is provided by a separate peripheral, either an included battery cell or an induction coil receiving EM-power wirelessly from an external coil. Oftentimes, the same coil used for information broadcasting is also used for power transfer through living tissue.

The (also) optional *external part* typically is a (portable) computing unit such as a laptop or a palmtop or, even, a desktop computer. This is under the direct control of the patient, his/her treating physician and/or technician. From the external host, commands can be transmitted to the implant and physiological-data reception can be achieved. The external host often serves also as a data logger, storing large quantities of measured readouts acquired through the implant sensors since implant-native data memory is usually very limited.

# 2.5 Survey setup

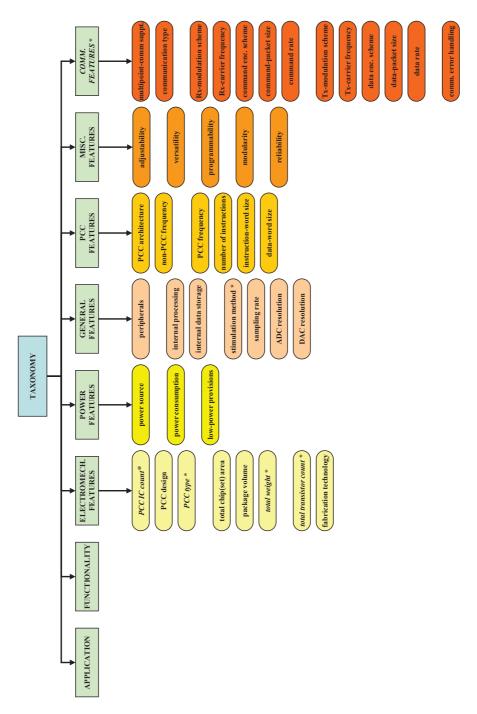

The existence of so many diverse attributes in the studied biomedical implants, makes their classification a non-trivial issue. We have attempted to take into consideration as many of these attributes as possible while, at the same time, keeping complexity manageable. To this end, a two-level hierarchical classification of data has been designed, as illustrated in Figure 2.2.

In the first level, eight major categories have been identified covering core aspects of an implantable system. In the second level, these categories have been further broken down, each into a set of related parameters considered to be pertinent to our study, as outlined in the previous section. For the purposes of this thesis document, we shall limit our analysis to only those categories related to the SiMS project. For an exhaustive analysis of all categories, the interested reader can refer to a complete technical report [133]. Below, we give a detailed description of the selected categories along with their measurement units and the policy followed in filling in the taxonomy tables. The omitted categories have been denoted with an asterisk ('\*') in Figure 2.2.

Figure 2.2: Overview of imposed survey taxonomy.

# 2.5.1 Major categories

In detail, seven major categories are described in this thesis, as follows:

- 1. *APPLICATION*: The medical problem the specific implantable system is designed to remedy. Intensive-care continuous monitoring, pain therapy, disease diagnosis, restoration of paralyzed limbs are all typical applications.