### Master's thesis report

by

### Rami Younis

to obtain the degree of Master of Science at the Delft University of Technology,

to be defended publicly on Wednesday December 7, 2022 at 13:00.

Thesis committee: Prof. G. Q. Zhang, TU Delft

Prof. P. J. French, TU Delft, Bioelectronics

Dr. R. Poelma, Nexperia Dr. H. W. van Zeijl, TU Delft

This thesis is confidential and cannot be made public until December 7, 2023.

An electronic version of this thesis is available at <a href="http://repository.tudelft.nl/">http://repository.tudelft.nl/</a>.

### **Abstract**

Power electronics are an important technology used to convert electricity from a source like a battery or high voltage DC bus to more usable forms of electricity. This has to be done efficiently, reliably and without failures which is critical in applications like electric cars or datacenters. Power MOSFETs with upcoming SiC and GaN devices are an important building block used in these converters. Hence these power MOSFET devices have to be improved continuously to get a lower on resistance ( $R_{DSon}$ ), a better thermal dissipation and lower parasitic losses. In this thesis we will take a look at the embedding of power MOSFETs inside a PCB to obtain these improvements. This new technology needs to be evaluated in terms of reliability, failure-modes and thermal/electrical performance. By designing, manufacturing and testing a PCB with embedded devices. During manufacturing silver sintering has been used for attaching the die to a copper coin. In the end the manufacturing has been done successfully. Testing showed an 18% lower  $R_{DSon}$  and a twice as low junction to ambient thermal impedance indicating a better performance compared to regular packaging.

### Acknowledgements

I would like to thank my supervisor René Poelma for the opportunity to do this graduation project with him at Nexperia. At Nexperia I was able to collaborate with many colleagues who I would also like to thank, Anton Terpstra who helped a lot with the setup of the electrical measurements and everyone else who assisted me either online or offline. During the manufacturing process of the copper coins at CITC I got to know Sander Dorrestein, Martien Kengen, Henry Martin and Dave Reijs who have all assisted me during this process. Thanks to them the manufacturing went smooth and resulted in a working sample. For reviewing and manufacturing the PCB I would like to thank Jue Chen from Schweizer. And last but not least I would like to thank my colleagues at TU Delft, Dong Hu for his assistance with thermal measurements, Nikhil Gupta who has supported me during the whole project and of course the rest of the ECTM department.

Rami Younis Delft, November 2022

## **Contents**

| Lis | st of I                         | Figures                                                                                                                                                                                                                                                        | ix                                           |

|-----|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Lis | st of                           | Tables                                                                                                                                                                                                                                                         | iii                                          |

| 1   | 1.1<br>1.2                      | Problem description                                                                                                                                                                                                                                            | 1<br>2                                       |

| 2   | 2.1<br>2.2<br>2.3               | Power electronic Packaging                                                                                                                                                                                                                                     | 6                                            |

| 3   | 3.1                             | ign & simulation  PCB schematics  PCB layout  3.2.1 Size and shape  3.2.2 Copper trace and vias sizing  3.2.3 HV clearance & creepage  3.2.4 Placement accuracy  3.2.5 Stackup and materials  Copper coin  Finite element analysis  3.4.1 Setup  3.4.2 Results | 11<br>12<br>13<br>13<br>14<br>15<br>15<br>16 |

| 5   | 4.1<br>4.2<br>4.3<br>4.4<br>4.5 | MOSFET die with copper top metalization  Copper coin frame with silver spot.  Sintering of the die to the copper coin.  4.3.1 Manufacturing steps.  4.3.2 Challenges & alternate methods.  PCB manufacturing and embedding.  Conclusion.                       | 24<br>26<br>26<br>29                         |

| -   | 5.1                             | Process measurements                                                                                                                                                                                                                                           | 33                                           |

viii Contents

|     | 5.2  | 5.1.3<br>5.1.4<br>Perfor<br>5.2.1<br>5.2.2<br>5.2.3 | Gate placement accuracy  X-ray Cu coins  Cascade probe station Cu coin resistance  mance characteristics  Parset Electrical parameters  Thermal impedance junction to heatsink  IR setup thermal profiles  Thermal impedance junction to ambient. | . 38<br>. 39<br>. 41<br>. 41<br>. 46<br>. 49 |

|-----|------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|     | 5.3  | Reliab                                              | oility evaluation                                                                                                                                                                                                                                 | . 56                                         |

|     | 5.4  | Concl                                               | usion                                                                                                                                                                                                                                             | . 57                                         |

| 6   | Con  | clusio                                              | n & summary                                                                                                                                                                                                                                       | 59                                           |

|     | 6.1  | Projec                                              | ot summary                                                                                                                                                                                                                                        | . 59                                         |

|     | 6.2  | Concl                                               | usions                                                                                                                                                                                                                                            | . 63                                         |

|     | 6.3  | Recor                                               | mmendations                                                                                                                                                                                                                                       | . 64                                         |

| Bib | liog | raphy                                               |                                                                                                                                                                                                                                                   | 65                                           |

# List of Figures

| 1.1        | bare die of the same device will be used for embedding                                                                                                                       | 2        |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2        | A preview of the packaged and embedded evaluation boards, the embedded evaluation                                                                                            |          |

|            | board has been designed and manufactured as part of this thesis and will be discussed                                                                                        |          |

|            | in depth                                                                                                                                                                     | 2        |

| 1.3        | Manufacturing and design approach. Starting with a wafer, the bare dies are attached to a copper coin, then embedded in the inner PCB layers, next the other layers and vias |          |

|            | are connected to get the final PCB. The design of this PCB has been done using finite                                                                                        |          |

|            | element analysis to optimize the design.                                                                                                                                     | 3        |

| 2.1        | Different ways of "packaging" a die, using a discrete package, using a module or em-                                                                                         |          |

|            | bedding the die in a PCB.[20][1][26]                                                                                                                                         | 5        |

| 2.2        | Example of manufactured die with wirebonds and cu clip for performance comparison[7].                                                                                        | 6        |

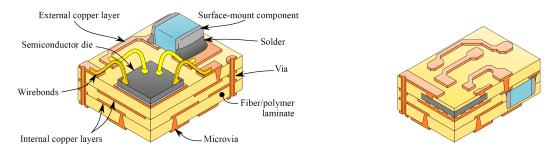

| 2.3        | An example of embedding a die and passive component inside a PCB[6].                                                                                                         | 7        |

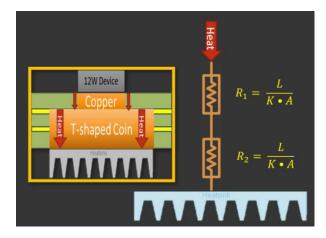

| 2.4        | A T shaped Cu coin is used to attach to a die and at the same time have an thermal                                                                                           | _        |

| 2.5        | connection to the backside[31].  Different stages of the silver sintering process[27].                                                                                       | 7<br>8   |

| 2.5        | Different stages of the silver sintering process[27].                                                                                                                        | O        |

| 3.1        | An overview of manufacturing from schematics to simulation, these will all be discussed                                                                                      |          |

|            | in the coming sections                                                                                                                                                       | 10       |

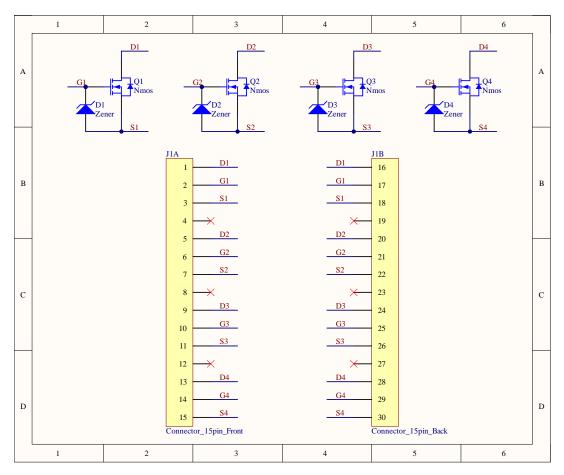

| 3.2        | Schematics showing 4 N-channel MOSFETs and the connections to the 15 pin edge                                                                                                |          |

| 0.0        | connector                                                                                                                                                                    | 11       |

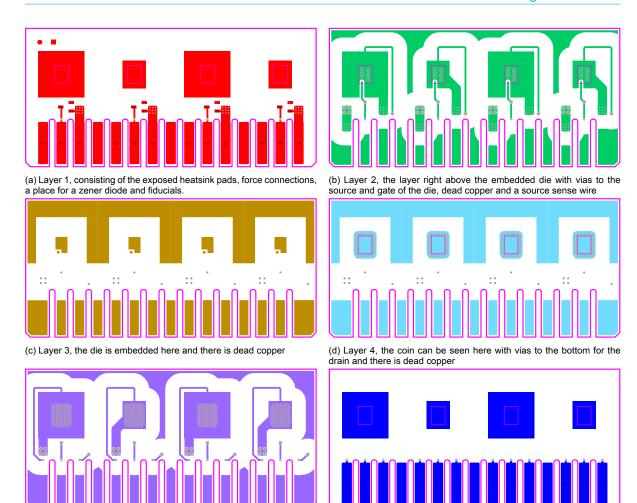

| 3.3        | All 6 PCB layers from top to bottom seen from above.                                                                                                                         | 12<br>14 |

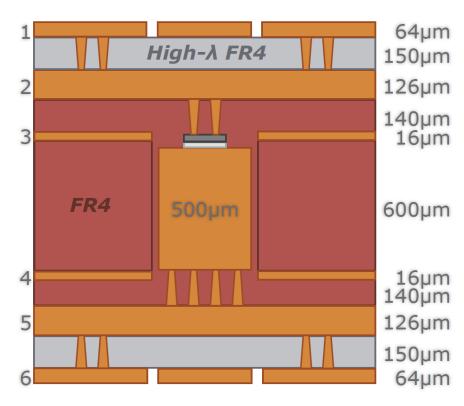

| 3.4<br>3.5 | Clearance and creepage definitions[17].  Stackup showing the 6 copper layers and dielectric FR4 like materials with thicknesses,                                             | 14       |

| 0.0        | with a total thickness of 1592µm                                                                                                                                             | 15       |

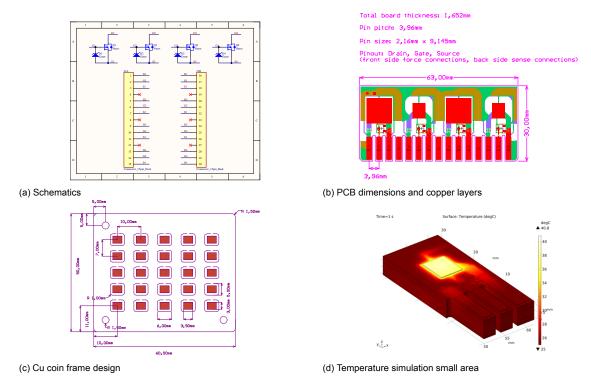

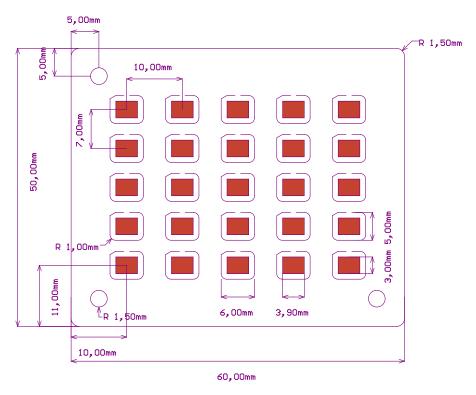

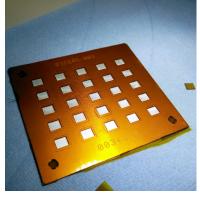

| 3.6        | The designed copper coin frame schematic to be used for manufacturing, showing 25                                                                                            |          |

|            | copper coins of 5x6mm with a silver spot of 3x3.9mm.                                                                                                                         | 16       |

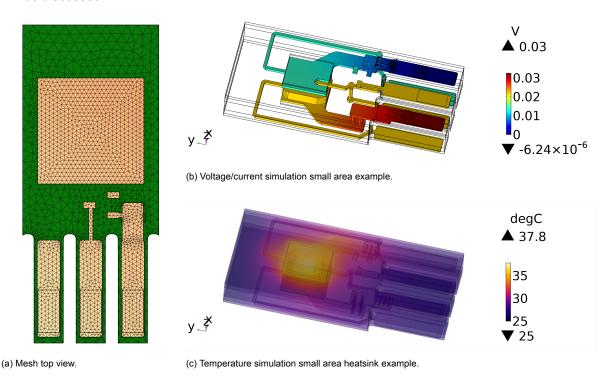

| 3.7        | A mesh view of the simulation with electrical and thermal results which will be explained                                                                                    |          |

|            | after the setup below.                                                                                                                                                       | 17       |

| 3.8        | The section of the PCB to be simulated is divided into small elements called a mesh as                                                                                       |          |

|            | seen here.                                                                                                                                                                   | 19       |

| 3.9        | Voltage and current distribution simulation results showing a uniform voltage for the                                                                                        | 20       |

| 3 10       | kelvin connection.  Thermal simulation results showing the temperature increase is greatest for the small                                                                    | 20       |

| 5.10       | area                                                                                                                                                                         | 20       |

| 3.11       | Simulated thermal impedance curves.                                                                                                                                          | 21       |

|            |                                                                                                                                                                              |          |

| 4 1        | Die picture and specifications                                                                                                                                               | 24       |

x List of Figures

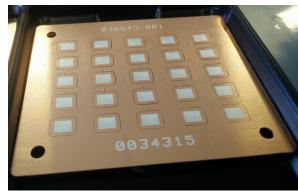

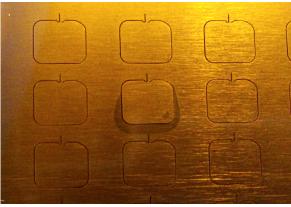

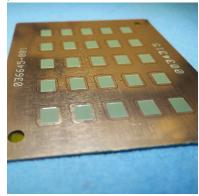

| 4.2  | Cu coin frame with 25 copper coins and sliver spots.                                               | 25 |

|------|----------------------------------------------------------------------------------------------------|----|

| 4.3  | Mousebite measurement showing a small trench between the copper and silver.                        | 25 |

| 4.4  | After applying kapton tape on the backside air bubbles will show how the coin is bend(this         |    |

|      | bending is also known as die paddle tilt)                                                          | 26 |

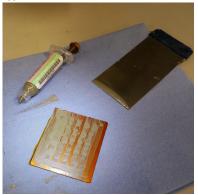

| 4.5  | Steps and tools needed to apply sinter paste.                                                      | 27 |

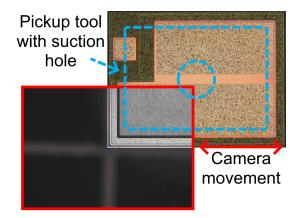

| 4.6  | Finetech sigma placer tool and camera view.                                                        | 28 |

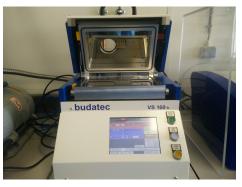

| 4.7  | Sinter oven with temperature curve.                                                                | 29 |

| 4.8  | Dispenser and setup.                                                                               | 30 |

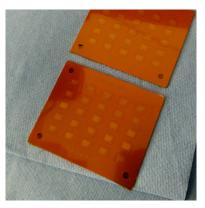

| 4.9  | First batch of manufactured PCBs.                                                                  | 31 |

| 4.10 | An overview of manufacturing steps from bare die to PCB                                            | 32 |

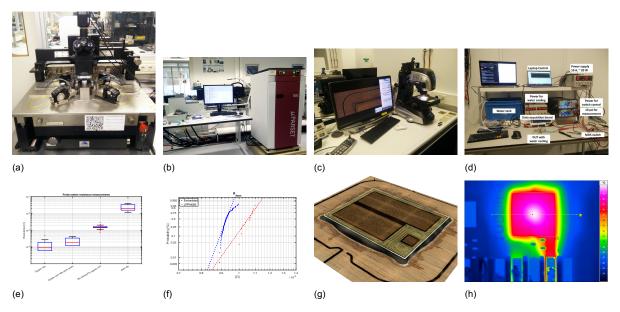

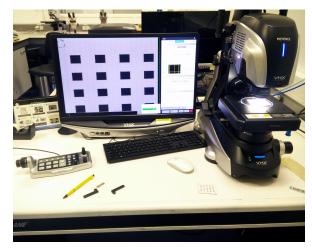

| 5.1  | A preview of measurement setups and results, to be discussed in the rest of this chapter.          | 33 |

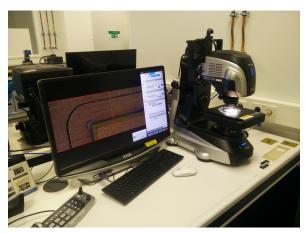

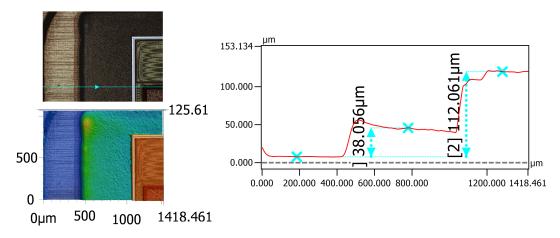

| 5.2  | Measurement setup for BLT using a confocal microscope.                                             | 34 |

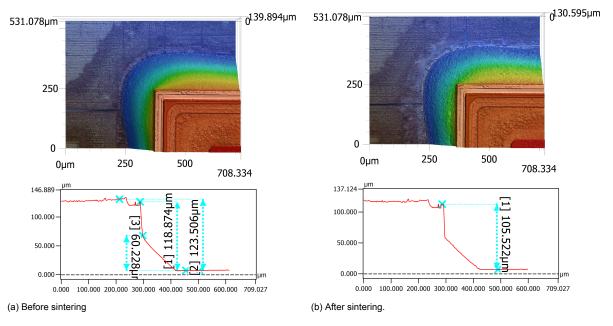

| 5.3  | Before and after sintering BLT measurements for dispensing.                                        | 35 |

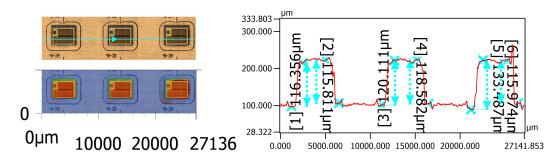

| 5.4  | Frame flatness measurement showing variation in height.                                            | 35 |

| 5.5  | Stencil printed before sintering with a 50 µm goal.                                                | 36 |

| 5.6  | Stencil printed before sintering with a 30 µm goal.                                                | 36 |

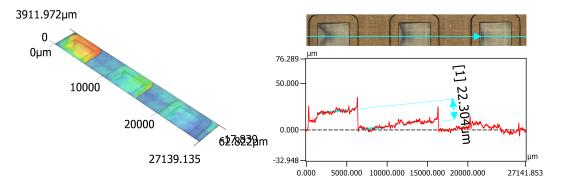

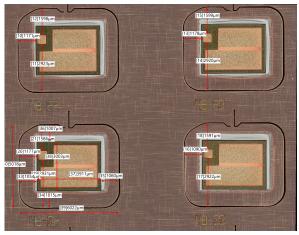

| 5.7  | Gate accuracy measurements using a confocal microscope.                                            | 38 |

| 5.8  | X-ray equipment and measurement images                                                             | 39 |

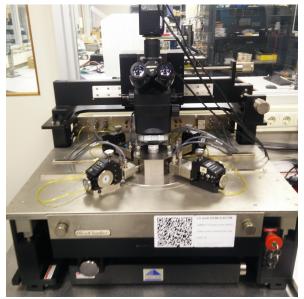

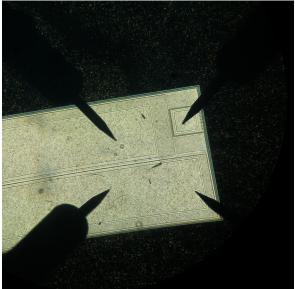

| 5.9  | Cascade needles probe station and microscope image.                                                | 40 |

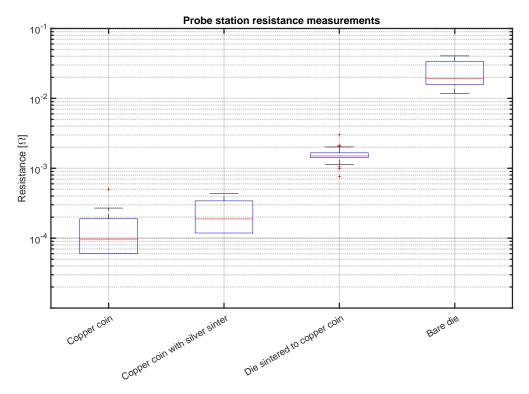

| 5.10 | Resistance for 4 measurement types, only a copper coin, a copper coins with silver sinter          |    |

|      | material on it, a copper coin with a die silver sintered to it and separate dies.                  | 41 |

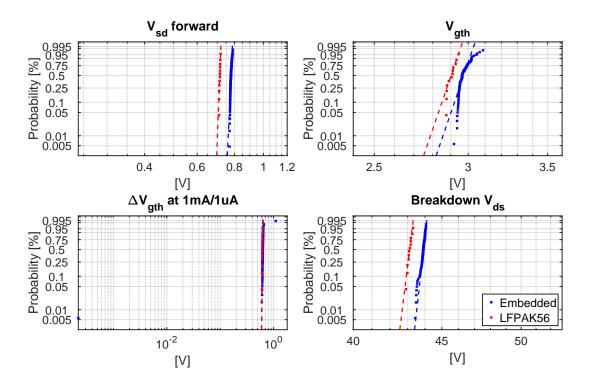

| 5.11 | Parset setup with custom socket.                                                                   | 42 |

| 5.12 | Parset voltage measurements showing only a small difference between packaged and                   |    |

|      | embedded devices.                                                                                  | 43 |

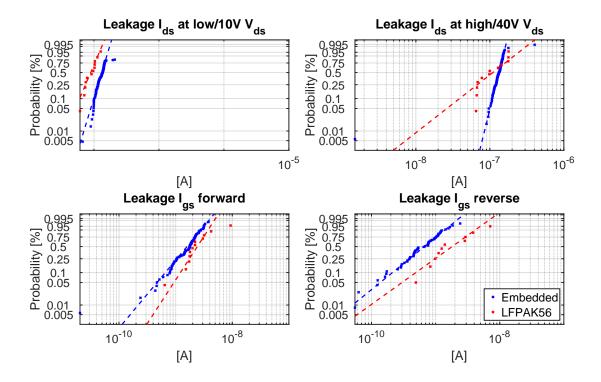

| 5.13 | Parset leakage current measurements showing only a small difference between pack-                  |    |

|      | aged and embedded devices                                                                          | 44 |

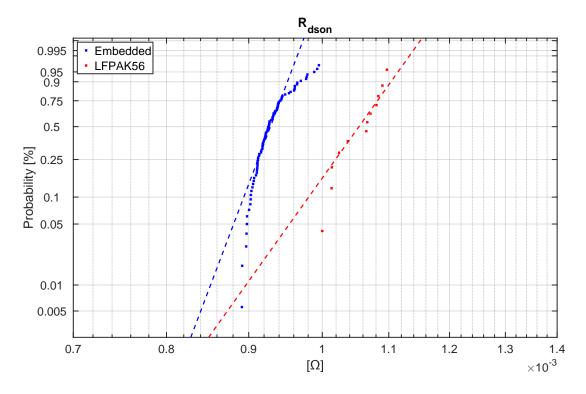

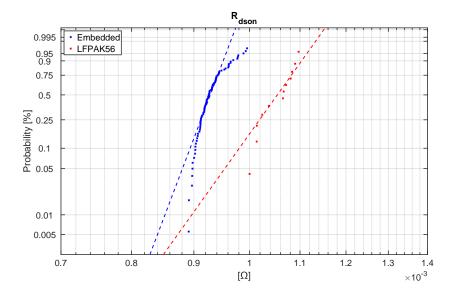

| 5.14 | Parset Rdson measurements showing a significantly lower resistance for the embedded                |    |

|      | devices compared to the packaged devices.                                                          | 45 |

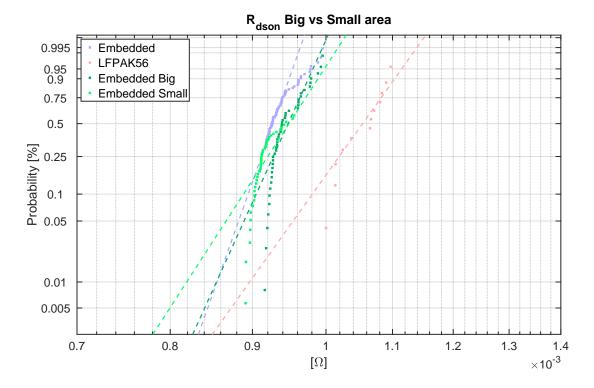

| 5.15 | Parset Rdson measurements showing the difference in resistance for a big vs small area             |    |

|      | above/below the device                                                                             | 46 |

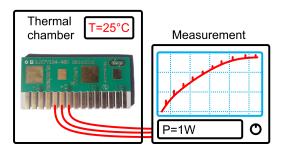

| 5.16 | Calibration measurement setup, a Keithly 2450 SourceMeter is used to measure the Vf                |    |

|      | with the device in the TPS thermal chamber at a know stable temperature.                           | 47 |

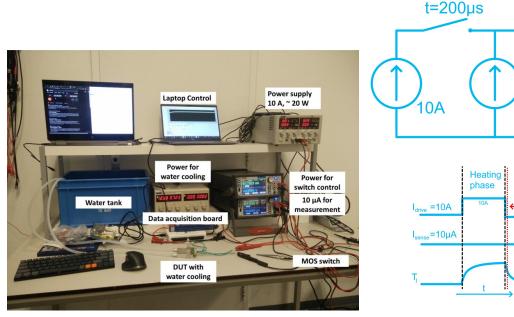

| 5.17 | Thermal impedance measurement setup and schematic.                                                 | 48 |

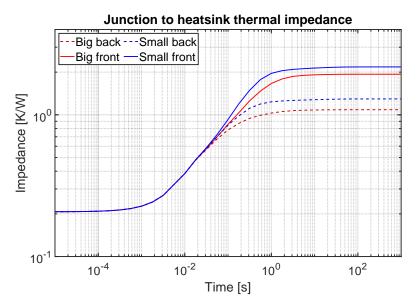

| 5.18 | Thermal impedance curves, measured during cooldown.                                                | 49 |

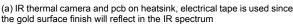

| 5.19 | The used setup for doing thermal measurements using an IR camera.                                  | 49 |

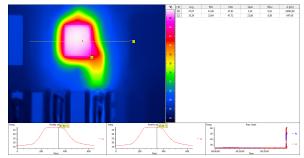

| 5.20 | Measuring points for temperature profile graphs at the first 10% of heating up, at halfway         |    |

|      | to steady state and at steady state                                                                | 50 |

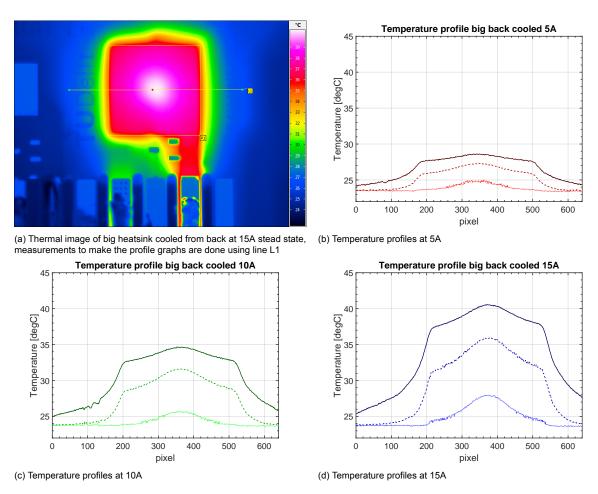

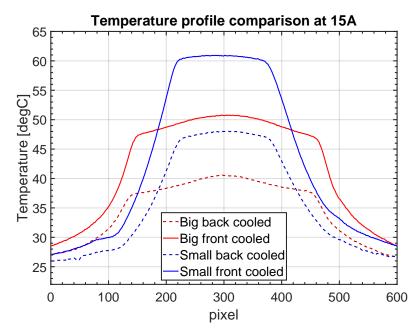

| 5.21 | Temperature profiles trough the center for the <b>big</b> heatsink cooled from the <b>back</b> at  |    |

|      | different currents, the dotted bright line is at the first 10% of heating up, the dashed line      |    |

|      | at halfway and the solid dark line at stead state                                                  | 51 |

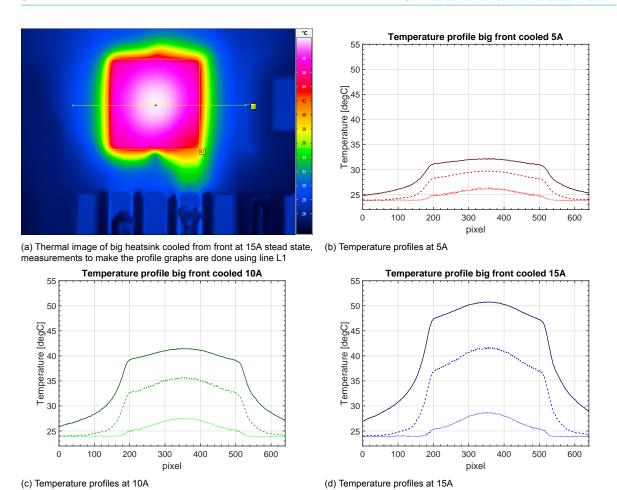

| 5.22 | Temperature profiles trough the center for the <b>big</b> heatsink cooled from the <b>front</b> at |    |

|      | different currents, the dotted bright line is at the first 10% of heating up, the dashed line      |    |

|      | at halfway and the solid dark line at stead state                                                  | 52 |

List of Figures xi

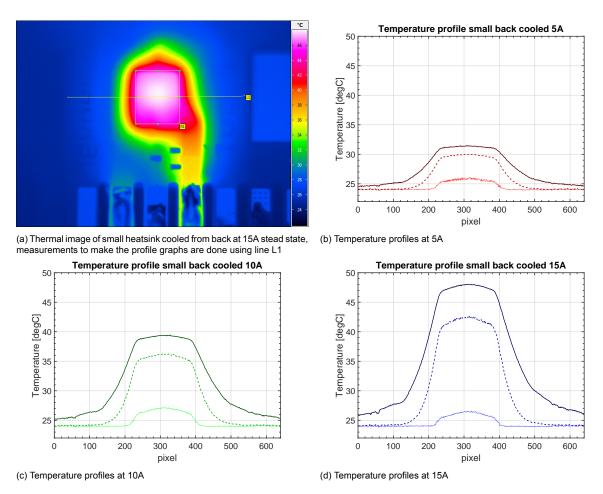

| 5.23 | Temperature profiles trough the center for the <b>small</b> heatsink cooled from the <b>back</b> at                                                                                                |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | different currents, the dotted bright line is at the first 10% of heating up, the dashed line                                                                                                      |    |

|      | at halfway and the solid dark line at stead state                                                                                                                                                  | 53 |

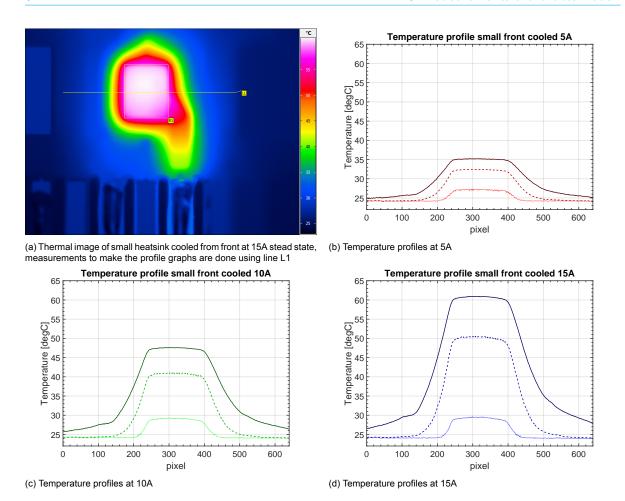

| 5.24 | Temperature profiles trough the center for the <b>small</b> heatsink cooled from the <b>front</b> at different currents, the dotted bright line is at the first 10% of heating up, the dashed line |    |

|      | at halfway and the solid dark line at stead state.                                                                                                                                                 | 54 |

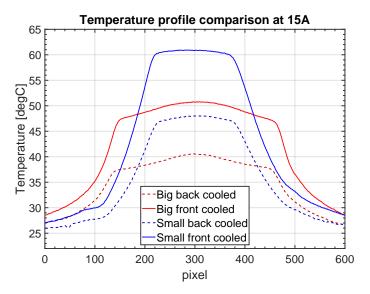

| 5.25 | Comparison of profiles at 15A for all configurations, note that the distance to the IR camera wasn't exactly the same for each measurement, resulting in slightly wider or                         |    |

|      | smaller profiles measured in pixels                                                                                                                                                                | 55 |

| 5.26 | Thermal to ambient impedance measurement results and setup                                                                                                                                         | 56 |

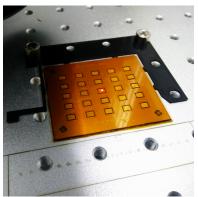

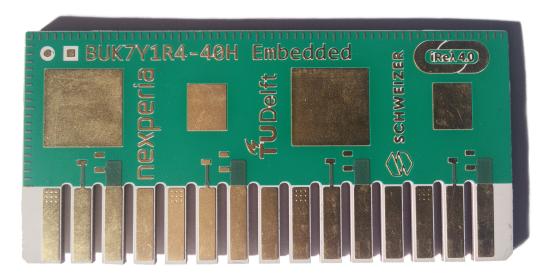

| 6.1  | The embedded evaluation board which is the result of the design and manufacturing                                                                                                                  |    |

|      | steps in this thesis                                                                                                                                                                               | 59 |

| 6.2  | PCB design and stackup.                                                                                                                                                                            | 60 |

| 6.3  | Parset Rdson measurements showing a significantly lower resistance for the embedded devices compared to the packaged devices.                                                                      | 62 |

| 6.4  | Simulation and measurement of junction to heatsink thermal impedance with the Y-axis at the same scale.                                                                                            | 62 |

| 6.5  | Comparison of profiles at 15A for all configurations, note that the distance to the IR camera wasn't exactly the same for each measurement, resulting in slightly wider or                         |    |

|      | smaller profiles measured in pixels                                                                                                                                                                | 63 |

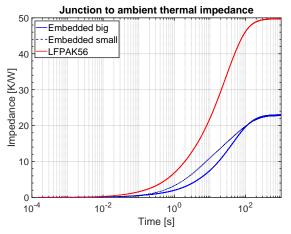

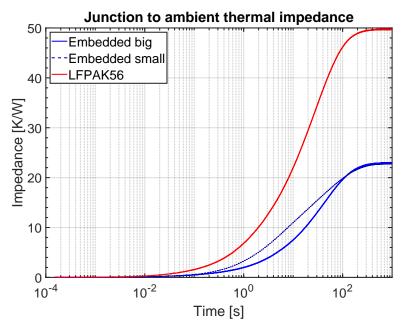

| 6.6  | Thermal impedance for big and small embedded device compared to LFPAK56 pack-                                                                                                                      |    |

|      | aged device                                                                                                                                                                                        | 63 |

## **List of Tables**

| 3.1 | Via types and sizes                                                                                                         | 13 |

|-----|-----------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Material parameters of inner and outer PCB layers                                                                           | 15 |

| 3.3 | Material properties used during the simulations.                                                                            | 18 |

| 4.1 | Die specifications.                                                                                                         | 24 |

| 5.1 | Dispense BLT before, after and shrinkage. Using a 60µm stencil before sintering. And using a 30µm stencil before sintering. | 37 |

| 5.2 | Gate location measurement results, all in µm                                                                                | 38 |

| 5.3 | Calibration of forward voltage for different temperatures.                                                                  | 46 |

| 5.4 | Reliability test list.                                                                                                      | 56 |

1

### **Project introduction**

Currently a lot of industries are seeing increased use of electrification and power usage. From electric cars to the big data centers hosting cloud applications. To keep up with this a lot of power electronics devices are needed for efficient operation. With power MOSFETs, especially upcoming SiC and GaN devices, playing an important role. These devices have to be improved continuously to get lower on resistance ( $R_{DSon}$ ), better thermal dissipation and lower parasitic losses.

Next to improving the bare devices themselves it is also needed to look at how they are packaged. With Moore's law on the decline there is the so called "more than Moore", meaning that instead of just improving transistors anything around it and smart architecture choices still improve performance. Here there are options to move away from using wirebonds, replace leaded solder with other alternatives, change the leadframes to attach the dies to and many more ways to increase integration.

So in this thesis we will take a look at improvements in the back end instead of the front end where just the device gets made. The focus will be on the embedding of power MOSFETs inside a PCB.

#### 1.1. Problem description

Embedding technology offers new packaging opportunities for a bare-die portfolio of devices. The new technology needs to be evaluated in terms of reliability, failure-modes and thermal/electrical performance. Managing of reliable performance of bare-die semiconductors in customer embedding applications is needed. Embedding offers improved performance advantages in terms of low parasitics and thermal resistance due to a direct electrical and thermal path. Moreover, it frees up board space and allows for higher integration and power density.

#### 1.2. Objectives

To investigate how embedding works and how it compares to a packaged device, in this case the BUK7Y1R4-40H see figure 1.1, a test vehicle with the same die embedded in it will be designed and manufactured. This will be a PCB with multiple embedded dies. Electrical and thermal measurements have to be done on this PCB to compare the performance. Besides that reliability tests have to be

done to investigate the life time of the devices when embedded. During the design, manufacturing and testing knowledge will be build up on design rules, failure modes, new manufacturing techniques and advantages or disadvantages of the technology.

#### 1. General description

Automotive qualified N-channel MOSFET using the latest Trench 9 low ohmic superjunction technology, housed in a robust LFPAK56 package. This product has been fully designed and qualified to meet AEC-Q101 requirements delivering high performance and endurance.

Figure 1.1: The BUK7Y1R4-40H, a N-channel MOSFET, which will be used as comparison and the bare die of the same device will be used for embedding.

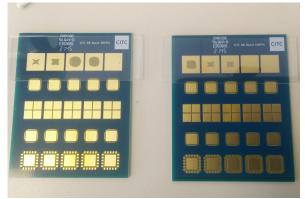

As a preview figure 1.2 shows a PCB with the mentioned packaged components and the PCB which is designed for this thesis with the embedded components. Its design and testing will be discussed in depth in this thesis.

(a) 5 LFPAK56 packaged devices on a PCB.

(b) 4 embedded devices inside a PCB.

Figure 1.2: A preview of the packaged and embedded evaluation boards, the embedded evaluation board has been designed and manufactured as part of this thesis and will be discussed in depth.

#### 1.3. Approach

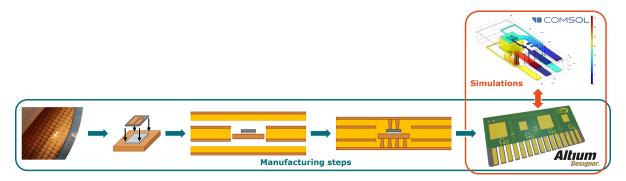

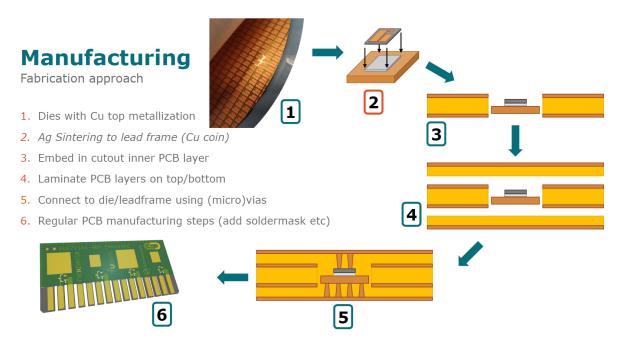

To be able to investigate embedded dies the design of a PCB/physical demonstrator based on a reliability evaluation board which is compatible to have dies embedded in them needs to be made. The test vehicle will be compared to a similar evaluation board which uses regular packaged LFPAK56 devices as shown in figure 1.2. Figure 1.3 shows an overview of the manufacturing and design steps needed to make the PCB.

To achieve the objectives the following steps need to be taken:

- 1. Obtain a wafer with dies that are suitable for embedding

- 2. Design a leadframe (Cu coin) to attach this die to

- 3. Design a PCB to embed the bare die with leadframe into by using finite element simulations

- 4. Attach the die to the leadframe using sintering

1.4. Thesis outline 3

- 5. Manufacture the PCB and embed the die in it.

- 6. Do electrical measurements like on resistance and analyze/compare the data

- 7. Do thermal measurements and analyze/compare the data

- 8. Do reliability measurements and analyze/compare the data

The expectation is that the embedded devices show a better electrical, thermal and reliability performance due to the shorter electrical path, shorter thermal path and different material choice compared to packaged devices. If this is actually the case will be investigated in the rest of this thesis.

Figure 1.3: Manufacturing and design approach. Starting with a wafer, the bare dies are attached to a copper coin, then embedded in the inner PCB layers, next the other layers and vias are connected to get the final PCB. The design of this PCB has been done using finite element analysis to optimize the design.

#### 1.4. Thesis outline

The thesis outline is as follows:

- **Ch 2, Literature** To start chapter 2 will give an overview of power electronics packaging, PCB embedding and silver sintering.

- Ch 3, Design & simulation Next chapter 3 will describe the design process and choices made. Going from the schematics of the PCB to the complete layout. This includes finite element analysis to verify the design and to predict the performance including the junction to heatsink thermal impedance.

- Ch 4, Manufacturing Here the steps to manufacture the used die, the copper coin and the PCB are discussed. A focus on the die attachment by pressureless silver sintering is made since this is a critical step to get right.

- Ch 5, Measurements & characterization Measurements have been done during the manufacturing phase, after manufacturing to characterize the electrical performance and to characterize the thermal performance. This includes among others: on resistance measurements, junction to heatsink thermal impedance measurements and junction to ambient thermal impedance measurements. Future reliability tests are planned as well.

- **Ch 6, Conclusion & summary** To conclude a summary is given and the most important results and conclusions are discussed. With some recommendations at the end.

### Literature

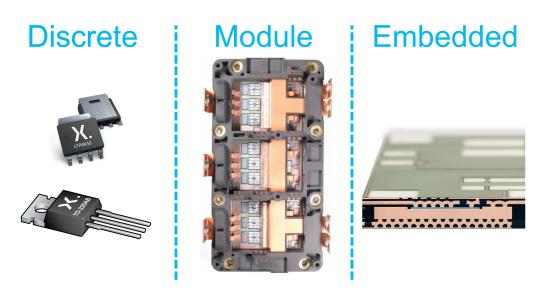

To get a better understanding of embedding it is important to first know how we got to this point. Figure 2.1 shows 3 ways of packaging a power MOSFET, discrete, in a module or embedded in a PCB. What is the current state of the art of packaging? This question will be answered in the next section 2.1 which will discuss current power electronic packaging. Section 2.2 will give an introduction on PCB design and how it relates to packaging. Finally section 2.3 will explain a die attachment technique called sintering.

Figure 2.1: Different ways of "packaging" a die, using a discrete package, using a module or embedding the die in a PCB.[20][1][26]

#### 2.1. Power electronic Packaging

A lot is done to improve the MOSFETs at the front end with innovations in trench design[21], making dies thinner [2], by moving to wide bandgap materials like Silicon Carbide (SiC) or Gallium Nitride

6 2. Literature

(GaN)[16][18] which can work at higher temperatures and voltages. Another approach which can be taken to improve power electronics is to look at the packaging. Traditionally a die will be placed on a leadframe and wirebonds connect the die to the leads of the device, then it is all encapsulated in an epoxy or silicone gel. Because of the coefficient of expansion (CTE) mismatch between silicone gel and aluminium wirebonds the risk of heel crack exists[32]. For a great introduction and overview of power electronic packaging you can refer to [17].

With advanced packaging techniques there are multiple challenges for both Si and SiC power devices. Challenges include extra manufacturing steps, fast switching speeds and high heat dissipation, especially for SiC[12]. Some examples of packaging that is currently used or being researched are: Clipbonds which are similar to wirebonds but instead of a wire a flat piece of copper, a so called copper clip, is soldered to the top of the device, this increases both the electrical and thermal performance compared to wirebonds due to the big copper area. A Transfer-molded Power Module which uses a copper clip instead of wirebonds was developed and has a more than 10 times longer lifetime in power cycling test of  $\Delta T_j$ =100°C [30]. A thin IGBT with copper clip with larger heat exchange area leads to 200% improvement in the IGBT power handling capability as compared with the conventional wirebonded IGBTs[7]. There are even ways to use double sided cooling enabling a reduction of up to 23% in junction to case thermal resistance[33].

(a) A bare die attach to a PCB using wirebonds.

(b) A bare die attach to a PCB using a Cu clip.

Figure 2.2: Example of manufactured die with wirebonds and cu clip for performance comparison[7].

A next step in the future of packaging techniques is the embedding of dies in a PCB or other substrate[1]. This will be explored further in the next section.

#### 2.2. PCB embedding

Usually a PCB is used as interface to connected components to each other by soldering them on the top or bottom of the PCB. A new idea is to also use the inside of the PCB to embed the components in it[1][6][10]. Figure 2.3 shows an example of what embedding is.

2.2. PCB embedding 7

(a) A PCB with regular components.

(b) A PCB with embedded components.

Figure 2.3: An example of embedding a die and passive component inside a PCB[6].

When using PCB embedding for SiC an alternative is needed to FR4 which is a fiberglass material PCBs are usually made of. This is because temperatures over 175°C can easily be reached [11]. Either different existing materials or completely new materials can be used[9]. The way of connecting the die inside the PCB to the outside also needs consideration. Finite element analysis has been done on using vias[8][28]. A power module with embedded dies using vias to connect has been fabricated and tested[22]. A proposed way to increase copper density compared to vias is using blind blocks, which are complete areas above the die made of copper[13]. For a completely different approach a die was embedded and connected using a compressed metal foam[23].

Figure 2.4: A T shaped Cu coin is used to attach to a die and at the same time have an thermal connection to the backside[31].

The embedded dies are usually connected to a piece of copper, referred to as direct bond copper, leadframe or copper coin. This can be done by attaching the die to a flat piece of copper[19]. This is also used for a Si and GaN die that are soldered on top[25]. A copper leadframe with a small cavity that fits the die was used in a three-phase inverter module, it was evaluated to have a thermal resistance of  $0.50~{^\circ}\text{C/W} \le R_{\text{th jmax-cooler}} \le 0.61~{^\circ}\text{C/W}$ . This equates to a 30%–44% reduction in  $R_{\text{th}}$  compared to a traditional LV module of comparable rating[16]. And a T shaped copper coin was used to both attach the die to and to replace vias on the bottom to connect to the outside since the bottom of the T shape is exposed on the bottom of the PCB, showing improved thermal performance[31].

8 2. Literature

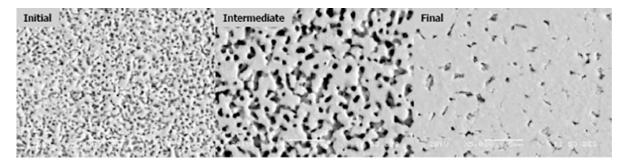

#### 2.3. Silver sintering

A lot of industries are moving towards a more sustainable future. This means one of the main die attach materials that is usually used, leaded solder, should be replaced. Besides the environmental reason, leaded solder has a low melting point, this means it is not suitable for high temperature applications. This can be replaced by using silver based materials. These cannot be soldered since silver doesn't have the same properties as leaded solder but instead sintering can be used[27]. A better electrical and thermal performance are also expected from silver. Figure 2.5 shows the sintering process from starting with small particles to a dense silver mass.

Figure 2.5: Different stages of the silver sintering process[27].

Silver sintering is already being used in research projects. A 10kW inverter module was made using IGBTs silver sintered to a copper leadframe[22]. A so called SKiN technology consist of sintering a chip to a substrate, on top of that a flexible PCB is sintered as well to make connections to the gate of the device. On the bottom of the substrate a heatsink is sintered. In all cases a layer of 30-100um silver is used as sinter material. This technique resulted in higher reliability and a 35% lower thermal resistance[29]. The mentioned copper leadframe with a cavity is filled with a thin layer of silver sinter material as die attach material as well[16].

3

## Design & simulation

A Nexperia testboard with embedded copper coins has been designed for testing. For this first both the copper coin and the testboard PCB have to be designed. The design is based on thermal and electrical simulation results. During the design it was kept in mind that a comparison to the LFPAK56 packaged device has to be made. The MOSFET design handbooks [3] and [4] have been referred to during the design for aspects like thermal area and via choice.

The tools used to make the designs are Altium Designed for the PCB and copper coin frame. And COMSOL for the finite element simulations. How these 2 CAD tools interface will be further explained in section 3.4.

The PCB has 2 sets of requirements, on the one hand it has functional requirements and on the other hand it has manufacturing requirements. The following sections will discuss these requirements, specifications, simulations and materials and the resulting design choices that are relevant for each of these parts. Starting with the schematics in section 3.1, then the PCB layout 3.2, the copper coin 3.3 and finally how the simulation was used in section 3.4.

Figure 3.1: An overview of manufacturing from schematics to simulation, these will all be discussed in the coming sections.

#### 3.1. PCB schematics

There will only be one component in the PCB, the embedded MOSFET. As you can see in figure 3.2 there is are a front and back connector, 4 N type MOSFETs and 4 zener diodes. While there are enough pins to connect 5 devices the choice to use only 4 was made to have a distance of at least 3 mm between the device tracks to comply to the HV requirements.

The zener diode is connected to the gate, it protects the gate in the event a high voltage pulse appears on it. Since this is not expected to happen during the controlled tests it wasn't placed on the PCB in the end.

3.2. PCB layout

Figure 3.2: Schematics showing 4 N-channel MOSFETs and the connections to the 15 pin edge connector.

The MOSFET needs to be connected so a 4 wire/kelvin connection is possible, for this reason the force connections are made to the front side connector and the sense connections to the backside. Multiple ways to do the pinout were possible, this will be further explained in the layout part see section 3.2.1.

#### 3.2. PCB layout

2 different layouts for the embedded MOSFET have been put on the PCB. The difference is the size of the copper area above and below the device. In once case a 10x10mm square is used, in the other case the minimum size of 5x6mm is used. In the simulation section 3.4 the effect of this area difference is discussed and the measurements in section 5.2.2 of the results show something similar.

Below all 6 layers are shown in figure 3.3a to 3.3f, for all of them the outline of the PCB and the embedded die are shown in pink. The next sections will explain all the design choices that went into making these.

Figure 3.3: All 6 PCB layers from top to bottom seen from above.

(e) Layer 5, the layer below the die with vias to the cu coins for the drain,

#### 3.2.1. Size and shape

a drain sense wire and dead copper

Since this is an embedded component no footprint to use for the layout exists yet. So a custom footprint that had to be made to fit it on the PCB.

nections

(f) Layer 6, consisting of the exposed heatsink pads and the sense con-

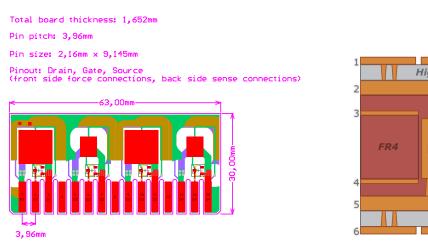

The PCB should fit in the used measurement equipment which uses an edge connector. This determines the connector type on the PCB side, which is a 2 sides 15pin connector with a pitch of 3.96mm, a total width of 63mm and each pad has a width x height of 2.16mm x 9.145mm. The thickness of the PCB should be between 1.55 and 1.59 mm to fit, as seen in section 3.2.5 the thickness is 1.59 mm which does fit.

To electrically connect to the embedded devices the pinout is decided. In total 6 connections have to be made, a force connection and a sense connection for the drain, gate and source. To be compatible with the measurement equipment and as a logical choice the front connections are all force connections and the back sense connections with the same connection on the front and back, so drain force and drain sense on top of each other. This is to reduce any crosstalk between pins. Only the order of the pins still has to be decided. To keep the routing simple the gate is connected to the middle pin, source on the right and drain on the left. In figure 3.3b it is most clear why the source is on the right because of the gate location on the die.

3.2. PCB layout

#### 3.2.2. Copper trace and vias sizing

The trace width and weight(term used for thickness in PCB manufacturing) is generally determined by the maximum constant current trough the trace and the maximum temperature it is allowed to reach taking into account the environments temperature. The thickness of the layers can be found in the stackup see figure 3.5. The toplayer at 64 µm is the thinnest layer that has current carrying traces on it. The force wire that carries the drain/source current is designed to be 2mm wide, so it has a cross-sectional area of 0.128·10<sup>-3</sup> mm<sup>2</sup>. Using the IPC-2152 Standard for Determining Current Carrying Capacity in Printed Board Design [14] the maximum allowed current can be calculated to be over 8A. A trace can support a higher current for short pulses, like when tests at very high currents need to be done[5].

To keep the PCB manufactureable there should be some "dead copper" on layer 2-4 since otherwise there is a risk of delamination because of air bubbles. In figure 3.3 the dead copper can be seen on the 4 middle layers. This copper has no electrical purpose so it isn't connected to anything.

Like the traces the vias should also be able to handle the used currents and have a size that is manufacturable. Vias can be classified as through, blind and buried.

- Through vias go from to top layer to the bottom layer

- Blind vias start at the top/bottom and end on a middle layer

- Burried vias start at a middle layer and end on another middle layer

They can be manufactured using regular drilling with a drill bit or using a laser for small vias. Small laser drilled vias are also called microVia or  $\mu$ Via. 6 copper layers have been used where layer 1 and 6 are the top and bottom layer respectively. The types of used vias can be seen in table 3.1. The radius of the laser drilled  $\mu$ Vias cannot be larger than the plated copper thickness of the layer above it to be completely filled. Since in this case the layers are around 0.1mm a diameter of max 0.2mm can be used.

Table 3.1: Via types and sizes

|                      | Diameter hole [mm] | Via type | Manfacturing type | Layer pair  |

|----------------------|--------------------|----------|-------------------|-------------|

| Vias to outer layers | 0.2                | Blind    | Laser drill       | 1-2 and 5-6 |

| Vias to die/coin     | 0.2                | Buried   | Laser drill       | 2-3 and 4-5 |

| Vias trough PCB      | 0.45               | Buried   | Regular drill     | 2-5         |

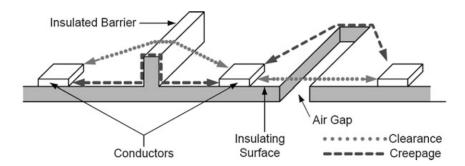

#### 3.2.3. HV clearance & creepage

Since compatibility with HV SiC devices of up to 1.5kV is needed the spacing requirements of the traces needs to be taken into account. First it is important to understand how the spacing is defined, there is clearance and creepage. Clearance is the shortest direct distance going trough air. Creepage on the other hand is the distance over the surface that 2 conductors share. This is made clear in figure 3.4.

Figure 3.4: Clearance and creepage definitions[17].

There are a multitude of reasons for needing a larger distance between traces at high voltages. The most obvious problem is electrical breakdown and arcing. Other less directly noticable issues are electrochemical migration and Conductive Anodic Filament (CAF) growth, in both cases traces of copper, silver or other conductive materials form thin wires in between the traces which reduces the distance and will eventually result in breakdown.

The first parameter to look at is the breakdown voltage of air at 3000V/mm. For 1.5kV this would mean having a spacing under 0.5mm results in arcing. But because of other breakdown mechanisms more space is needed. One way to measure this is by using the Comparative Tracking Index (CTI). The CTI is measured by observing when breakdown occurs at a distance of 4mm after 50 drops of 0.1% ammonium chloride solution on the material. The inner layers of the used PCB material has a CTI of 340V and the outer layer 600V.

There are many standards all with different design rules and requirements:

- IEC-61950-1

- IEC-60664

- IPC-2221

- IPC-9592B

- UL-60950

They all have different tables or formulas to calculate the minimum required spacing depending on CTI value, pollution factor, medical use, material or even height above sea level. Most commonly when there is no regulatory reason (like medical or military use) the IPC-2221 standard is used for PCB design. In this case at 1.5kV that would give a distance of 2.75mm. With this information in mind a distance of 3mm has been chosen which is on the safe side since enough space was available.

#### 3.2.4. Placement accuracy

Fiducials are features on a PCB that are used for camera based inspection and manufacturing. They are easy to detect shapes of a known size on a known location. In this case a small square and circle have been added to the top left corner for this. During manufacturing of multiple PCBs in a panel these can be used as reference for milling the PCB out of the panel.

Placement of the embedded device was done manually in this case, using the edge of the copper coin as reference. But for automatic placement fiducials on the inner layers could be needed as well.

3.3. Copper coin 15

#### 3.2.5. Stackup and materials

The stackup consists of 6 copper layers, of which 2 are not used electrically, with a total thickness of 1.592mm. See figure 3.5. The outer layers are used to connect to the pins and to radiate heat away using the copper area above the embedded dies. One layer lower from both sides is used for traces to connect the outer layer to the die in the middle, some extra dead copper is added all sufficient distance away from the traces just to keep it manufacture-able. And finally the 2 inner layers only consist of dead copper and a cutout for the embedded device.

The materials used are copper, and 2 different kind of FR4 like dielectric materials as replacement of regular FR4. The top and bottom dielectric layer are of a high thermal conductivity type which helps with the thermal path to the heatsink. In table 3.2 the CTI, glas transitiong temperature Tg and thermal conductivity  $\lambda$  are given. Because of the high voltage and high temperature there is compatibility with SiC devices.

Table 3.2: Material parameters of inner and outer PCB layers.

|              | CTI  | Tg    | λ          |

|--------------|------|-------|------------|

| Inner layers | 340V | 300°C | 0.5W/(m·K) |

| Outer layers | 600V | 300°C | 10W/(m·K)  |

Figure 3.5: Stackup showing the 6 copper layers and dielectric FR4 like materials with thicknesses, with a total thickness of 1592µm.

#### 3.3. Copper coin

To embed the MOSFET it is attached to a piece of copper, here called a copper coin. A frame with multiple coins is designed. The copper coin is used as a leadframe to attach the die to using silver

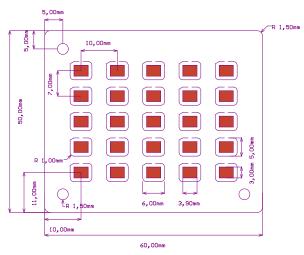

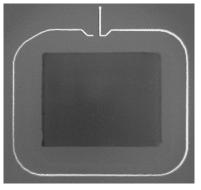

sintering. It's size and shape needed to be determined to make it suitable for embedding. A size of 5x6mm and thickness of 500um have been used. 5x6mm is the same size as the LFPAK56, this way a reasonably fair comparison in performance can be made. Since the die is 3x3.9mm and centered this gives at least 1mm around it on each side. The thickness is chosen so that the total thickness with the die on top fits in the inner PCB layer. The coin has rounded corners to make it easier to manufacture with one corner in a different shape to indicate the gate location of the die. This makes sure the coin can only be placed in the PCB in one way.

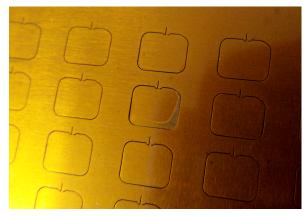

In figure 3.6 you can see how the copper coins are designed to be manufactured. A frame of 5x5 coins is made where the coin is connected at one point. Since this is a research project it has to be easy to manually handle which is the reason for the relatively large space between and around the coins.

Figure 3.6: The designed copper coin frame schematic to be used for manufacturing, showing 25 copper coins of 5x6mm with a silver spot of 3x3.9mm.

The die will be sintered to the coin, but it cannot be directly sintered to copper. So a silver spot is made on each coin. The silver spot is applied to the coin using photolitography and immersion silver coating. The steps to do this are as follows:

- 1. Photoresist is added with openings where the silver spot goes.

- 2. The Cu surface is micro etched to clean it and prepare it to for Ag coating.

- 3. Immersion silver coating, this exchanges Cu and Ag atoms.

- 4. The photoresist is removed.

#### 3.4. Finite element analysis

As mentioned at the start of the chapter simulations have been used to verify and optimize the design. This is done to get an indication in advance if and how embedding has an effect on performance without

going through the whole manufacturing process. Design parameters like PCB stackup, materials, trace widths and copper area size can all be changed easily.

The finite element analysis(FEA) is done using COMSOL. This means a model is split into a finite amount of small elements and numerical physics calculations can be done on those. In this case a 3D model of the PCB including the embedded Cu coin and die is used. Electrical and thermal calculations have been done.

To get a working simulations first the model has to be prepared. First the model has to be made or imported, materials have to be defined, next boundary conditions have to be defined and finally the model has to be split into small elements called a mesh. This will be discussed in the setup section bellow. Next the resulting data will be shown in plots and 3D heatmaps in the results section that follows. The current density, voltage distribution, heat distribution and calculated thermal impedance will be discussed.

Figure 3.7: A mesh view of the simulation with electrical and thermal results which will be explained after the setup below.

#### 3.4.1. **Setup**

The very first step is defining the geometry, the "ECAD file import" function was used. This imports all 3D geometry information into the working environment from in this case an ODB++ file. This file was exported using Altium, which is the PCB CAD software used to design the PCB. This way all layer and trace information is available in the simulation after minimal cleanup of the imported file. Since the PCB contains 4 embedded devices it was cut to only 1/4 of the PCB to only simulate a single device. Since the middle 2 copper layers are very thin and to optimize the model they have not been included.

Materials are defined using either build in material from COMSOL or using datasheet parameters. Below the used materials are described and in table 3.3 the used parameters are shown.

**Copper** All traces and vias are made of copper, since the model was imported it was easy to select them all without further modifications.

**Inner PCB layers** An FR4 alternative with high Tg was used, the datasheet parameters have been filled in.

**Outer PCB layers** An FR4 alternative with high Tg and high thermal conductivity was used, the datasheet parameters have been filled in.

**Silicon** The complete chip is defined to be pure silicon, no doping or trenches have been used to keep the simulation simple, instead the conductance was experimentally calculated to get an  $1m\Omega$  resistance.

**Sinter material** The hybrid silver sinter material was defined by changing the build in silver material using datasheet parameters.

Below the parameters that have been used for that materials in the simulation are listed:

- Electical conductivity,  $\sigma$ , (S/m), the electical conductivity is used for the electrical simulations, it will influence the voltage distribution and current density.

- Heat capacity, C<sub>p</sub>, (J/(kg·K)), the heat capacity is used during the thermal simulations

- Relative permittivity,  $\varepsilon$ , the relative permittivity is used during the electical simulations.

- Density,  $\rho$ , (kg/m<sup>3</sup>), the density is used for thermal simulations

- Thermal conductivity, k, (W/(m·K)), the thermal conductivity is used for thermal simulations

Table 3.3: Material properties used during the simulations.

| Material               | σ(S/m)  | $C_p (J/(kg \cdot K))$ | ε(-) | ρ(kg/m³) | k (W/(m·K)) |

|------------------------|---------|------------------------|------|----------|-------------|

| Copper                 | 5.998e7 | 385                    | 1    | 8960     | 400         |

| Inner layers           | -       | 860                    | 4.4  | 2000     | 0.5         |

| Outer layers           | -       | 800                    | 4.4  | 3000     | 6           |

| Silicon                | 1e4     | 700                    | 11.7 | 2330     | 85          |

| Silver sinter material | 1e6     | 235                    | 1    | 9336     | 130         |

After defining the materials the physics simulations have to be setup. Starting with the electrical simulation. First the materials that are involved have to be selected, then the boundary conditions have to be defined. Starting with current conservation which applies to everything. Then electric insulation which applies to the outside surfaces of the model, this means no current can enter or leave through those surfaces. The initial voltage of everything is set to 0V. Finally the source is permanently set to 0V and the drain has a current of 10A entering it. This fully defines the electrical part of the simulation.

For the thermal simulation again first all materials have to be selected. The initial value for everything is set to 25°C. All outside boundaries are automatically defined as insulation, this will be overwritten by the next definitions. Starting with heat flux, here all outside boundaries are defined to be in air so there is heat transfer due to convection. Since only a 1/4 slice of the PCB is simulated a symmetry option is added to the sides of this slice so it is as if the rest of the PCB is actually there while using less computational resources. To simulate having a cooling plate attached to one side of the PCB the temperature of the top or bottom is set to 25°C. And finally a heat source of 10W is defined, a volume of 2.6625mm x 3.5625 x 5µm at the top of the die is used for this. This is were the active area of the MOSFET is. It was already experimentally confirmed to give accurate simulation results by the die manufacturer so this volume was used.

The last step needed before the simulation can be run is to define a mesh, which means separating the model into small elements. The minimum element size shouldn't be smaller than the smallest feature size, which in this case will be the via sizes. The size of the elements will determine the resolution of the results so a big element size is also not desired. But smaller elements also increase the computation time, so an optimization between resolution and computation time has to be made. After changing the minimum element size, maximum element size and related parameters the mesh is generated as shown in figure 3.8

Figure 3.8: The section of the PCB to be simulated is divided into small elements called a mesh as seen here.

#### 3.4.2. **Results**

Now that the simulations have run, the results can be analyzed. A time independent study was done for the electrical simulations and a time dependent study for the thermal simulations. Time dependence was used for the thermal simulations to be able to generate a thermal impedance graph of the device heating up over time.

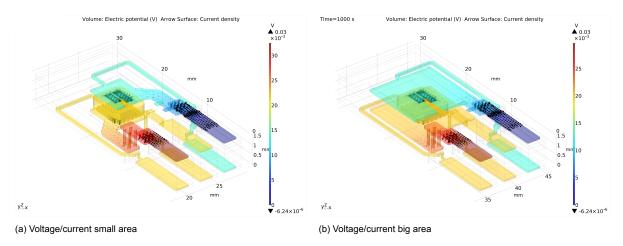

Figure 3.9 show a colored voltage distribution and arrows for the current distribution. First focusing on the voltage distribution it is clear that there is a small voltage drop from the drain and source force pins to the area in the center as expected. But the main voltage drop is over the die itself, this shows that the sense wires that run around the top and bottom areas to the drain and source sense pins on the bottom do actually measure the die. This is required for a kelvin connection and a desired result.

The current distribution shows that no current runs through the sense wires. The biggest current density is at the vias on top of the die and the vias connecting the pins to the rest of the trace on the PCB. Clearly the amount of vias on the back of the copper coin is more than needed to support the current density, but they are also used to transfer heat from the Cu coin to the next layer.

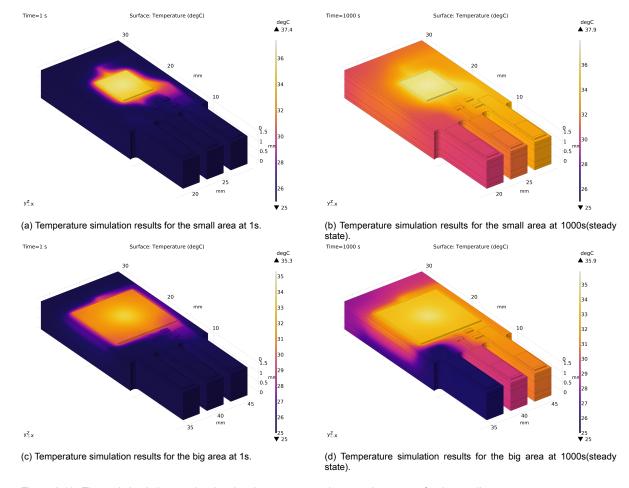

Figure 3.9: Voltage and current distribution simulation results showing a uniform voltage for the kelvin connection.

The thermal simulations ran from 10<sup>-5</sup>s till 10<sup>3</sup>s with 4 data points per decade. The simulations have been done for both the big and small area heatsinks with either the front or back heatsink connected to a cooling plate by setting it to 25°C. Figure 3.10 shows a top view of the big and small areas with backside cooling at different time steps. Here it already becomes clear that the heat mainly spreads to the copper on top and via the traces. The overall temperature for the bigger area is lower than the small area indicating better heat transfer to both the cooling plate and outside environment.

Figure 3.10: Thermal simulation results showing the temperature increase is greatest for the small area.

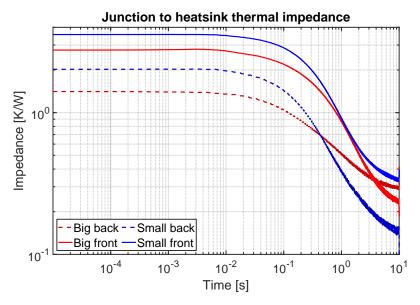

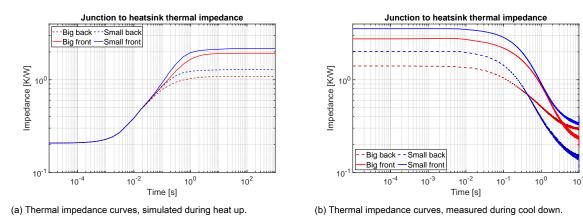

To quantise how well the heat is removed from the device junction to heatsink/solderpoint thermal impedance curves have been plotted. The thermal impedance here is defined as the temperature difference between the die and the area that is attached to the cooling block of 25°C divided by the input power. Resulting in the 4 curves in figure 3.11.

Figure 3.11: Simulated thermal impedance curves.

A lower thermal impedance indicates better heat transfer, so here we can conclude that from best to worst performance we have the big area cooled from the back, the small area cooled from the back the nig area cooled from the front and the small area cooled from the front. It also becomes clear that only for longer duration of over  $3 \cdot 10^{-2}$  different in cooling area or side makes a difference. Measurements similar to the simulations have been done by attaching a cooling block, resulting in a similar conclusion, see section 5.2.2

# Manufacturing

A working sample with embedded MOSFETs has been manufactured. To get to this working sample all parts have to be made, from the die and copper coin to the PCB. Extra focus is put on the sintering step since this was the most challenging and a manually done step.

Below is a list with an overview of manufacturing steps and thus what will be discussed in this chapter:

- A wafer with MOSFET dies with Cu top metalization

- Manufacturing of Cu coins

- · Sintering of the dies to the Cu coins

- Applying sinter paste using kapton tape mask

- Placing the dies using a pick and place tool

- Sintering in an oven using the correct temperature profile

- PCB manufacturing and embedding

- Placing/embedding the Cu coin with die in a hole in the middle PCB layer

- Laminating the top and bottom layers

- Finalizing by adding vias, traces, soldermask, etc

## 4.1. MOSFET die with copper top metalization

The embedded MOSFET is prepared by taking a wafer with regular Si MOSFETs and adding a top metalization layer. Figure 4.1a shows the manufactured die and figure 4.1b shows the size schematically.

24 4. Manufacturing

(a) Wafer with MOSFET dies with a copper top metalization.

(b) Die size specifications.

Figure 4.1: Die picture and specifications.

Table 4.1: Die specifications.

| BUK7Y1R4-40H           |                            |  |  |  |

|------------------------|----------------------------|--|--|--|

| Туре                   | Si N-channel Trench MOSFET |  |  |  |

| Die size               | 3.9 mm x 3.0 mm x 70 µm    |  |  |  |

| Metal top-side         | Pure Cu, tCu = 10 µm       |  |  |  |

| Passivation protection | Polyimide, tPI = 5 μm      |  |  |  |

| Metal back-side        | TiNiAg, tTiNiAg = 0.6 μm   |  |  |  |

As specified in table 4.1 a Si N-channel MOSFET is used. To manufacture this regular MOSFETs standard processing steps are done. Starting from a Si wafer and then layer by layer patterning and doping the features like trenches, gate, source, etc. For embedding an extra step is needed to get a copper top metal layer. As explained in previous chapter this is done so vias can attach to this layer. The top metalization is a 1P1M (1 poly layer and 1 metal layer) of copper and polyimide. The backside is TiNiAg which didn't need any modification since this can easily be silver sintered. Below the steps to add the top copper layer are listed:

- 1. A seed layer of 300nm is sputtered on the whole wafer.

- 2. A photoresist layer is added to pattern the copper above the gate and source area.

- 3. copper gets galvanicly plated on top of the exposed parts of the seed layer by running a current trough the seed layer and suspending the wafer in a solution with copper ions.

- 4. Once a 10 µm thick copper layer is plated on top of the seed layer the resist will be removed.

- 5. As a last step the seed layer will be etched away.

# 4.2. Copper coin frame with silver spot

The copper coin frame manufacturing steps will be explained in this section. The die will be bonded to the copper coin and then placed into the PCB.

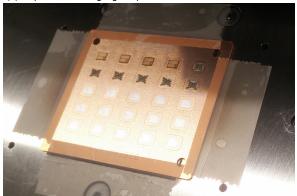

The copper coins are 5x6mm and .5mm thickness with a silver coated spot the size of the die in the middle. The silver spot is used for better adhesion to the silver sinter paste. These coins are delivered in a frame with 25 per frame, at a distance of 10x7mm away from each other as discussed in the design chapter, and see in figure 4.2.

- (a) Design drawing to manufacture the cu coin frame.

- (b) Manufactured cu coin frame.

Figure 4.2: Cu coin frame with 25 copper coins and silver spots.

The manufacturing ideally starts with a copper sheet of the correct thickness. Optionally a first step is etching or plating copper on a sheet that is too thick or thin respectively. Next the silver spot is made, this is done in 4 steps:

- 1. Photoresist is added with openings where the silver spot goes.

- 2. The Cu surface is micro etched to clean it and prepare it to for Ag coating.

- 3. Immersion silver coating, this exchanges Cu and Ag atoms.

- 4. The photoresist is removed.

Once this is done the Cu coins are lasercut in the correct shape. After the manufacturing the frame consists of only copper and silver.

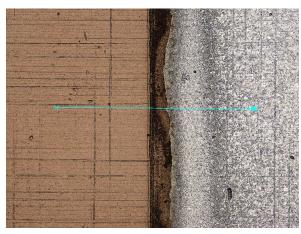

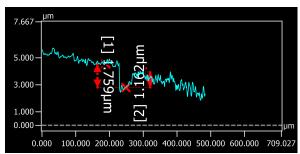

(a) Mousebite microscope picture.

(b) Height measurement of the mousebite.

Figure 4.3: Mousebite measurement showing a small trench between the copper and silver.

During the making of the silver spot a small undesirable trench is etched around it as a side effect. This phenomena is called mouse bite and becomes issue when applying sinter paste. This impact be discussed in the next section.

26 4. Manufacturing

## 4.3. Sintering of the die to the copper coin

The die with copper top metalization and the copper coins with silver spot have to be attached to each other in a leadfree way. During the sintering trials multiple ways of applying the sinter paste and placing the dies have been tried. First the final list of manufacturing steps will be elaborated on. Next the challenges that have been found using other methods will be explained to make clear why they haven't been used.

## 4.3.1. Manufacturing steps

The process all the way from applying kapton tape until sintering the die in an oven will be discussed here.

#### **Preparation before placement**

Since the copper coins all only have 1 connected point to the rest of the frame they can tilt in multiple directions. This issue is also known as die paddle tilt. So kapton tape was used at the back of the frame to keep the coins flat and so it can stick to the vacuum suction of the table on the Finetech. From the air bubbles that form when applying the tape you can see in which direction the coin is bend. They need to be gently pushed in the correct direction to remove all bubbles so all coins are as flat as possible relative to the frame. This is shown in figure 4.4 below.

(a) Air bubble under the coin indicates it is bend up.

(b) Air bubble around the coin indicates it is bend down.

Figure 4.4: After applying kapton tape on the backside air bubbles will show how the coin is bend(this bending is also known as die paddle tilt).

The next step is applying sinterpaste, to do this first a mask of kapton tape is made on the front side. An overview of the steps needed is shown in figure 4.5.

(a) High temperature kapton tape and tools

(b) Both sides of the frame have a layer of tape applied to them

(c) Openings are cut using a laser and 3D printed mall

(d) Tape rectangles are removed to expose the (e) Sinter paste is applied using a squeegee

(f) Tape is removed to end up with paste over all silver spots only

Figure 4.5: Steps and tools needed to apply sinter paste.

To make a mask for stencil printing kapton tape is put on the front side. 2 layers of tape with a thickness of 30µm each are used for a total of 60µm. One layer of tape and a metal stencil was tried as well with worse results, this will be discussed later in this chapter in the challenges section 4.3.2.

Openings are cut in the tape using a Huaray fiber laser. To align the frame with the laser a 3D printed mall has been designed, shown in subfigure 4.5c. The openings were cut larger than the silver spots, 3.4x4.4 mm instead of 3x3.9mm, since the aligning was done manually and not accurate enough to exactly line up.

To make the opening the tape rectangles that have been cut need to be removed using tweezers. This is done under a microscope, it is important to not accidentally scratch the copper coin with the tweezers.

Next sinter paste is applied using a squeegee. The squeegee has to be held as horizontal as possible and apply a only small a mount of pressure to make sure paste goes in all openings.

Finally the tape is removed to reveal the frame with paste only in the middle of each copper coin. The frame is now ready to have dies placed on it.

28 4. Manufacturing

#### Placement of dies

(a) Finetech sigma placer, this was used to accurately place the dies on (b) Pickup tool camera FOV and movement.

Figure 4.6: Finetech sigma placer tool and camera view.

The next step is using the Finetech sigma placer, see figure 4.6a, which is a pick and place tool with 0.5µm placement accuracy by using cameras and optics to align the die to the copper coin. It has a movable table to position the Cu coin frames and an arm to pick up the dies. Placement can be done with a set force or distance from the surface by doing a touchdown first to calibrate the 0 height.

First the setup of the machine had to be done. The arm to place the die had to be aligned with the camera manually. In this case the camera is looking at the bottom left of the pickup tool(instead of exactly the center), this is done so it is easier to see the rotation of the die once picked up since the camera can only move sideways, see figure 4.6b. The next setup step is to show masks on the screen, this is so there is a colored overlay to see how to align the die. Once aligned the dies are placed on a gelpack which is located next to the arm so they can be picked up. The prepared Cu coin frame with sinter paste is placed on the table, this table can be moved manually by pressing a foot pedal for big movements, or using 2 rotating knobs for fine movements. On the screen both the pickup tool with picked up die and the frame can be seen at the same time, using the overlay you align them by moving the table.

The challenge here now is to place the dies at the correct height. To do this the touchdown option is used. Since the frame and Cu coin are now flat because of the tape a touchdown next to the paste is possible, this is the 0 height. Then the die gets placed on the paste at a set height of 55µm, this way the die is pushed into the paste for 5µm. Getting this height correct so the die sticks to the paste and no paste overflows was done by testing multiple heights from 50-65µm.

#### Sintering using oven with N<sub>2</sub> flush

Now that the dies are placed a Budatec oven, figure 4.7a, is used for sintering, it follows a heating profile and can be flushed with nitrogen gas to keep oxygen out. A modified sinter profile with a peak temperature of 250°C was used. The modification was adding a 1h preheat at 70°C, see figure 4.7b for the profile.

- (a) Budatec vs 160, sinter oven, can setup thermal profile. (b) Budatek sinter profile used during manufacturing.

Figure 4.7: Sinter oven with temperature curve.

A hybrid pressure-less sinter paste was used as sinter material, which means it is a combination of silver particles and a glue with solvent.

### 4.3.2. Challenges & alternate methods

The main challenge is getting repeatability in placing dies correctly. There are 2 main parameters to get right, the thickness of the sinter paste and the flatness of the Cu coin or frame. With a too thick paste layer there is a big chance of overflow, which will short circuit the die. But with a too thin layer the paste dries out fast and risks having under fill/voids under the die or the die not sticking at all. If the Cu coin or frame are not flat the touchdown will not be at the same height as the paste, this again causes voiding, overflow or the die not sticking at all. This also includes the mousebite issue. How all these undesired phenomena are removed or reduced will be explained below.

#### Paste layer spreading and BLT

To get a reliable sinter paste layer thickness there are multiple techniques that can be applied. The first method that comes to mind is dispensing the paste on the copper coins and pressing the dies down on them to spread the paste.

30 4. Manufacturing

(a) Musashi image master 350pc smart, paste dispenser

(b) Dispense test using a glass plate

(c) Frame with paste before die placement.

(d) Frame with 4 dies placed, frame taped to keep it flat

Figure 4.8: Dispenser and setup.

A Musashi paste dispenser was used. It uses a laser and camera to scan the surface height for 3D alignment and air pressure for the paste dispensing. The parameters to be determined are the pressure, needle size, dispense gap and dispense pattern. These parameters were experimentally determined. In the end the following parameters were used:

pressure: 32kPa

· needle size: purple needle of 21 ga

dispense gap: 0.15mm

The used pattern with these parameters was cross shaped and can be seen in figure 4.8c. The goal was to get the pattern get as close to a rectangle as possible when a die is placed on top. Figure 4.8b shows a glass plate on top of different patterns to determine the best one.

In the end dispensing cannot give an accurate enough small amount of paste, even at low dispense pressure, it either gave overfill or under fill, rarely a good reproducible thickness.

The next option is using a stencil to apply the paste. Since here no 3D scan is made before applying the paste the flatness of the Cu coins and frame becomes important. So stencil printing using a metal stencil didn't work because the frames aren't flat enough. The silver spot mousebite makes a shape in the paste around the edge of the silver spot which aligned with the stencil opening further decreasing the reliability of stencil printing.

As solution a kapton tape mask was used as described in the sections above. This gives an accurate amount of paste and gets rid of the flatness issue since the tape sticks to the frame.

#### Frame flatness

The issue of the frame not being flat and the individual Cu coins not being flat in the frame was solved by applying tape to the backside as explained in the manufacturing steps. This solved the touchdown height not being the same as the 0 height when placing the die. Removing any overflow or voiding from this issue.

The problem of the mousebite around the silver spot could be removed by making the silver spot bigger than the placed die. Or the silver spot can be removed completely if the used sinter material can attach to copper, which is the case for the silver sinter material used here but wasn't verified. Another improvement to the frame would be to attach the Cu coins with 2 or more attachment points to reduce the degrees of freedom it has.

## 4.4. PCB manufacturing and embedding

The finished Cu coin frames with sintered dies on them are send to a PCB manufacturer to be embedded. There the Cu coins are singulated from the frame and embedded in the PCB.

Figure 4.9: First batch of manufactured PCBs.

As described in the design chapter the PCB consists of 6 copper layers. Which can easily be manufactured using standard procedures. The only addition to the process is the embedding. To do this a cutout is made in the middle FR4 layer after patterning the traces on the copper to place the Cu coin. Then the layers above and below are laminated and regular PCB manufacturing steps remain. Here it is important to make sure no air remains around the embedded Cu coin by adding enough resin. Figure 4.10 shows an schematic illustration of the embedding process.

32 4. Manufacturing

Figure 4.10: An overview of manufacturing steps from bare die to PCB.

In this case laser drilling of micro vias has to be done to attach the Cu coin and the gate and source on top of the die to the traces above it. After laminating the final layers regular vias are drilled, copper is plated on the top and bottom layer, soldermask is applied and the Electroless nickel immersion gold(ENIG) surface finish is applied to protect the copper from oxidation.

Some PCBs without embedded die have been manufactured as well for testing purposes.

## 4.5. Conclusion

To summarize the manufacturing steps, we start with a wafer of bare dies and they end up embedded inside a PCB. So first the wafer gets a top layer of copper. Then a Cu coin frame is prepared to attach the die to. The die is attached to it using sintering by stencil printing with a kapton tape mask of  $60\mu$ m thick, placing the dies with an accurate pick and place machine and putting them in a sinter oven. These Cu coins with dies are then embedded in the middle layer of the PCB and the rest of the PCB is build around it. From a manufacturing point of view some challenges have been solved to make all these steps possible. With these out of the way the process can be suitable for automatic stencil printing and pick & place machines for high volume manufacturing.

# Measurements & characterization