# Sampling Time Error Calibration for Time-Interleaved ADCs

Nandish Mehta

EEMCS

# Sampling Time Error Calibration for Time-Interleaved ADCs

MASTER OF SCIENCE THESIS

For the degree of Master of Science in Microelectronics at Delft University of Technology

Nandish Mehta

August 29,2013

Faculty of Electrical Engineering, Mathematics and Computer Science · Delft University of Technology

Copyright © Electrical Engineering

#### DELFT UNIVERSITY OF TECHNOLOGY DEPARTMENT OF ELECTRICAL ENGINEERING

The undersigned hereby certify that they have read and recommend to the Faculty of Electrical Engineering, Mathematics and Computer Science for acceptance a thesis entitled

SAMPLING TIME ERROR CALIBRATION FOR TIME-INTERLEAVED ADCs

by

NANDISH MEHTA

in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE MICROELECTRONICS

Dated: August 29,2013

Supervisor(s):

dr. Frank van der Goes

dr. Klaas Bult

prof. dr. Kofi A. A. Makinwa

Reader(s):

dr.ir.Michiel Pertijs

dr. ing. Leo de Vreede

### Abstract

In this thesis the design of the timing error calibration loop for a time-interleaved ADC is described.

The realization of fully-digital radio transceiver requires a wideband capture ADC that can simultaneously capture all the commercial wireless bands present in a mobile handset. These ADCs are expected to operate at GHz sampling speed with good energy efficiency. Both of these contradicting requirements can be fulfilled by employing time-interleaved architecture. Unfortunately, time-interleaved ADCs suffer from interleaving issues like mismatch in sampling time error. These issues can be addressed by designing a dedicated calibration loop.

In this thesis an attempt is made to design a calibration loop that detects and corrects the sampling time errors with high precision. The timing error detection technique relies on introducing two additional reference ADCs. The correction of timing errors is done using the least mean square iterative algorithm (LMS). Convergence and stability of such calibration loops are extremely critical. Hence, they are exhaustively investigated in this thesis. Factors that hamper the loop convergence were identified and relevant solutions are applied to overcome them. Furthermore, it was found that the loading effect of the reference ADCs greatly affects the accuracy of the timing error detection. A simple solution using delay lines is shown to remove this effect. Finally, techniques like inserting dummy sampling circuits, scaling sampling capacitance, and matching the clock-paths, are employed to achieve timing error correction accuracy in the order of 5fs level.

Some of these techniques are implemented at the architecture level, whereas some are implemented at circuit level. The effectiveness of the architecture level techniques is verified through MATLAB modeling while the circuit level techniques are verified through circuit simulations. The sub-blocks for the calibration loop are designed in industrial 28nm CMOS process and relevant simulation results are presented. Circuits like 11-bit  $10\mu$ W DAC with 0.6LSB DNL, a track-and-hold with  $HD_3$  of 72dB at 1GHz input frequency, and clock-path with a mean delay of 11ps, are designed for the timing error calibration loop.

**Keywords:** LMS calibration loop, Timing error detection, Time-interleaving, Observer Effect, Reference lanes, Wideband capture ADC, Digital-to-Analog converter, Track-and-hold, Low-power.

# **Table of Contents**

| 1 | Intro | oductio  | n                                                          | 1  |

|---|-------|----------|------------------------------------------------------------|----|

|   | 1-1   | Motiva   | tion                                                       | 1  |

|   | 1-2   | Basics   | of Time-Interleaved ADC                                    | 4  |

|   | 1-3   | Applica  | ation: Wideband Capture ADC                                | 5  |

|   | 1-4   | Target ' | Timing Error Correction Accuracy                           | 7  |

|   | 1-5   | Researc  | ch Goal and Contributions                                  | 8  |

|   | 1-6   | Thesis   | Organization                                               | 9  |

| 2 | San   | npling 1 | ime Errors in Time-Interleaved A/D Converters              | 11 |

|   | 2-1   | Basics   | of Time-Interleaving                                       | 11 |

|   | 2-2   | Types of | of Interleaving Issues                                     | 12 |

|   |       | 2-2-1    | Offset Mismatch                                            | 12 |

|   |       | 2-2-2    | Gain Mismatch                                              | 13 |

|   |       | 2-2-3    | Timing Mismatch                                            | 16 |

|   |       |          | 2-2-3-1 Impact of Timing Error                             | 17 |

|   |       |          | 2-2-3-2 Sources of Timing Mismatch                         | 18 |

|   |       | 2-2-4    | Bandwidth Mismatch                                         | 20 |

|   | 2-3   | Timing   | Error Detection and Calibration                            | 20 |

|   |       | 2-3-1    | Use of common sample-and-hold.                             | 21 |

|   |       | 2-3-2    | Foreground vs background calibration.                      | 21 |

|   |       | 2-3-3    | Digital detection and digital correction of timing errors. | 22 |

|   |       | 2-3-4    | Digital detection and analog correction of timing errors.  | 23 |

|   | 2-4   | Summa    | ury                                                        | 24 |

| 3                                                   | Tim  | ing Error Calibration Loop                                 | 25 |

|-----------------------------------------------------|------|------------------------------------------------------------|----|

|                                                     | 3-1  | Principle of Operation                                     | 25 |

|                                                     | 3-2  | Description of Calibration Loop                            | 28 |

|                                                     | 3-3  | Convergence of the Calibration Loop                        | 29 |

|                                                     |      | 3-3-1 Input Signal Statistics                              | 29 |

|                                                     |      | 3-3-2 Gain mismatch and offset of the two reference lanes  | 30 |

|                                                     |      | 3-3-3 Limit on Speed of Convergence                        | 32 |

|                                                     | 3-4  | Stability of Calibration Loop                              | 33 |

|                                                     | 3-5  | Impact of Finite Quantization of the two Reference Lanes   | 34 |

|                                                     | 3-6  | Summary                                                    | 36 |

| 4                                                   | San  | pling-Time Error Due to Observer Effect of Reference lanes | 37 |

|                                                     | 4-1  | Observer Effect: Simple RC Model Analysis                  | 38 |

|                                                     | 4-2  | Observer Effect: Sampling Instance Interactions            | 40 |

|                                                     | 4-3  | Isolating the Sampling Interactions using a Wire Delay     | 42 |

|                                                     | 4-4  | Mismatch between Dummy lane and REF lane                   | 44 |

|                                                     | 4-5  | Summary                                                    | 50 |

| 5                                                   | Circ | uit Implementation                                         | 51 |

|                                                     | 5-1  | System-Level Design                                        | 51 |

|                                                     | 5-2  | Clock Path                                                 | 53 |

|                                                     |      | 5-2-1 Clock-Phase generator                                | 53 |

|                                                     |      | 5-2-2 Sampling Edge Tuning Circuit                         | 53 |

|                                                     | 5-3  | Track-and-hold Design                                      | 56 |

|                                                     | 5-4  | HOLD Buffer Design                                         | 59 |

|                                                     | 5-5  | Digital-to-Analog Converter (DAC)                          | 61 |

|                                                     |      | 5-5-1 Estimating Dynamic Range                             | 64 |

|                                                     |      | 5-5-2 Circuit Implementation                               | 64 |

|                                                     |      | 5-5-3 Simulation of DNL                                    | 67 |

|                                                     |      | 5-5-4 Design Summary                                       | 67 |

|                                                     | 5-6  | Summary                                                    | 70 |

| 6                                                   | Con  | Inclusion                                                  | 71 |

|                                                     | 6-1  | Problem Definition: A Recap                                | 71 |

|                                                     | 6-2  | Thesis contribution                                        | 71 |

|                                                     | 6-3  | Future Work                                                | 73 |

| Α                                                   | Targ | get Specifications                                         | 75 |

| B MATLAB Code to Simulate Basic Interleaving Issues |      | TLAB Code to Simulate Basic Interleaving Issues            | 77 |

| С                                                   | Sim  | ulation Setup for Timing Errors                            | 81 |

| 0                                                   |      |                                                            | 81 |

|                                                     |      | Setting Up Variables                                       | 81 |

|                                                     |      |                                                            |    |

# **List of Figures**

| 1-1  | Mitola's wideband radio [1]                                                                                                                                   | 2  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1-2  | FoM versus ENOB and sampling frequency for ADCs published at ISSCC and VLSI from 1997-2013 [2]                                                                | 3  |

| 1-3  | FoM versus sampling frequency for single lane and M-lane interleaved ADC                                                                                      | 4  |

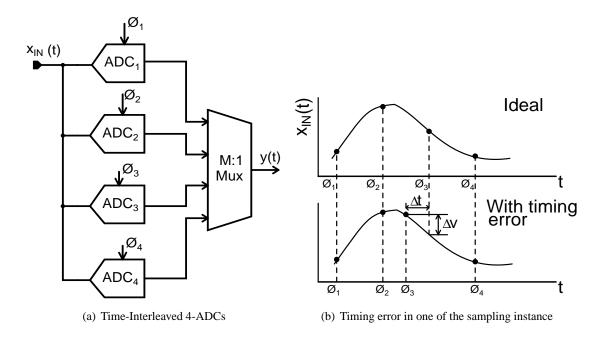

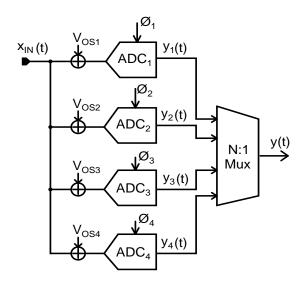

| 1-4  | Block diagram of basic 4-ADC interleaved with timing error                                                                                                    | 5  |

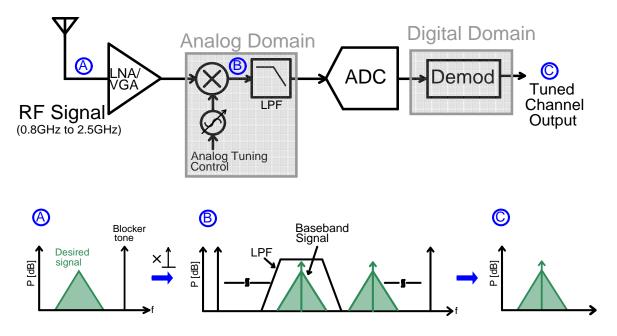

| 1-5  | Typical Rx link for zero-IF receiver.                                                                                                                         | 6  |

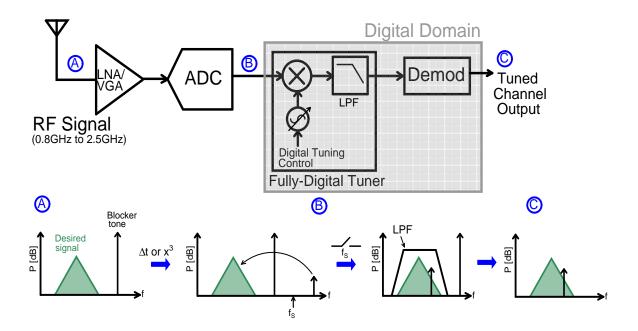

| 1-6  | Wideband capture receiver architecture for future mobile applications                                                                                         | 6  |

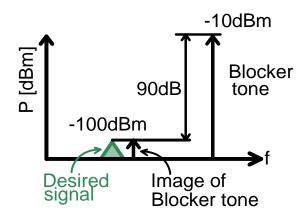

| 1-7  | Spurious free dynamic range requirement for wideband capture ADC for GSM signals.                                                                             | 8  |

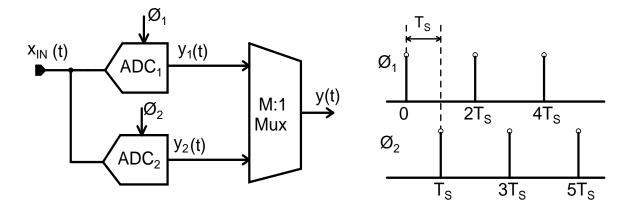

| 2-1  | Block Diagram of an ideal 2x interleaved ADC with timing waveforms                                                                                            | 12 |

| 2-2  | Input and output signal spectrum of ideal 2-interleaved ADCs                                                                                                  | 13 |

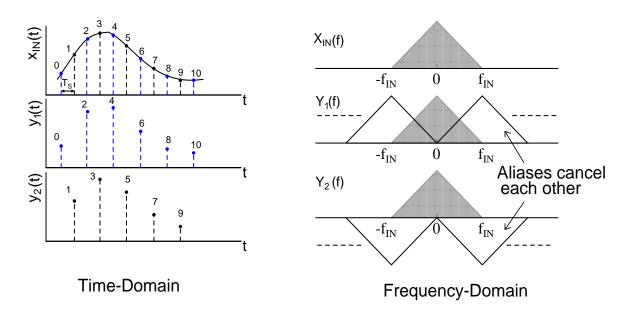

| 2-3  | Effect of input offset and its mismatch on the output spectrum of 4-interleaved ADCs for sinusoidal input tone of $f_{IN} = 498MHz$ sampled at $f_S = 5GHz$ . | 14 |

| 2-4  | Spurs due to gain error in the output of a 4x interleaved ADCs                                                                                                | 15 |

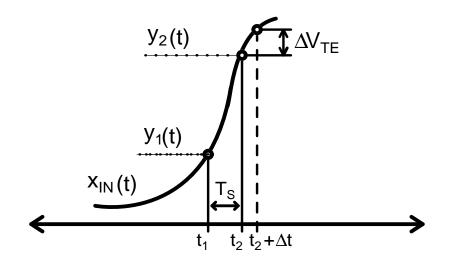

| 2-5  | Error in sampling input signal due to timing error                                                                                                            | 17 |

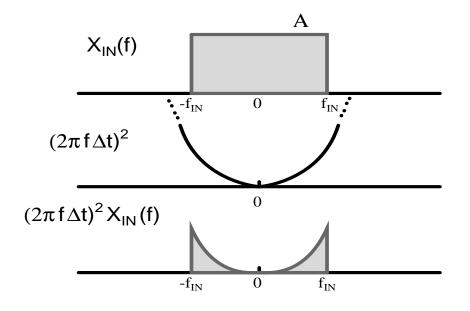

| 2-6  | Spectra of input signal and timing error component.                                                                                                           | 18 |

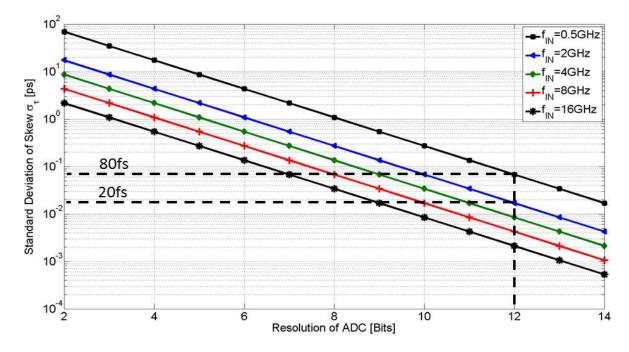

| 2-7  | Bound on timing error for varying SNR and input frequencies                                                                                                   | 19 |

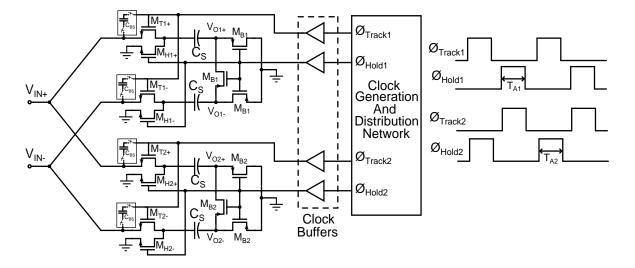

| 2-8  | Typical track-and-hold circuit for 2x interleaved ADC                                                                                                         | 20 |

| 2-9  | Impact of bandwidth mismatch on SNR for a 2x-interleaved ADC [3]                                                                                              | 21 |

| 2-10 | ADC under (a) foreground calibration (b) background calibration                                                                                               | 22 |

| 2-11 | Two different schemes for detection and correction of timing errors                                                                                           | 23 |

| 2-12 | Background timing error detection using reference lane ADC                                                                                                    | 24 |

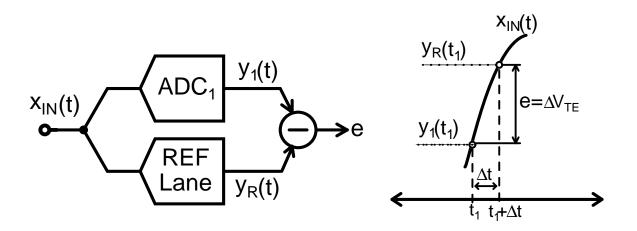

| 3-1  | Error signal computation using a reference lane for timing error estimation.                                                                                  | 26 |

| 3-2  | Estimation of input signal derivative by using additional reference lane with delayed input.                            | 27 |

|------|-------------------------------------------------------------------------------------------------------------------------|----|

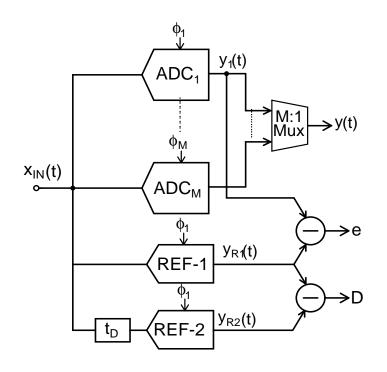

| 3-3  | Block diagram of timing calibration loop using two reference lane-ADCs                                                  | 28 |

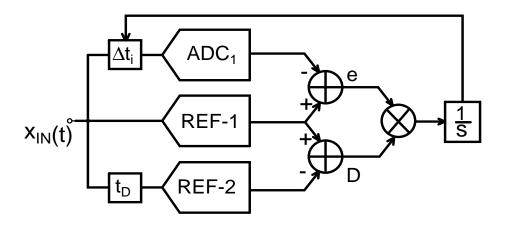

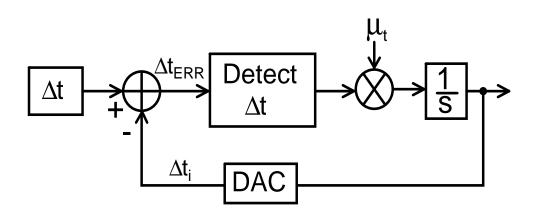

| 3-4  | Linearized model for timing error calibration loop                                                                      | 29 |

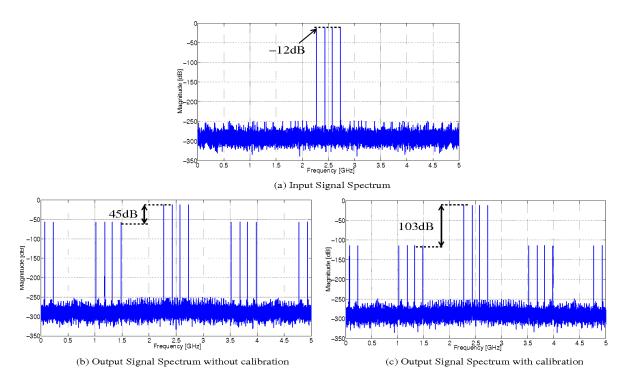

| 3-5  | Full (0 to $f_S$ ) signal spectra for input, output without calibration and output with calibration                     | 30 |

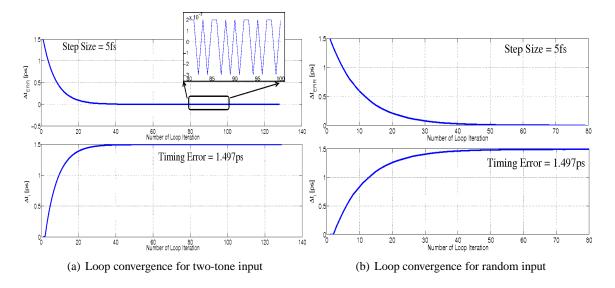

| 3-6  | Convergence of timing error calibration loop for different input signal statistics. $(\mu_t = 1/(2e7))$                 | 31 |

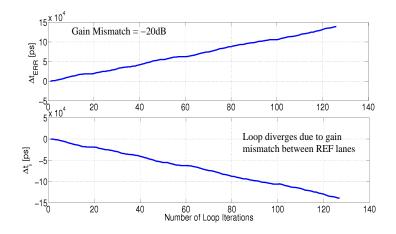

| 3-7  | Gain mismatch between two reference lanes.                                                                              | 31 |

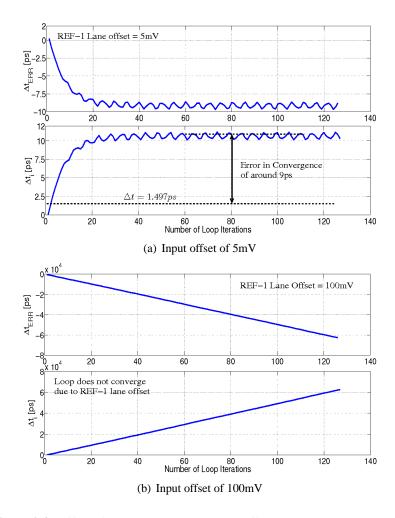

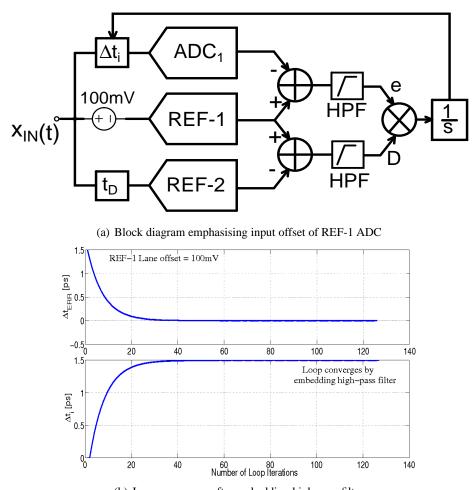

| 3-8  | Effect of REF-1 lane ADC's input offset on the loop convergence                                                         | 32 |

| 3-9  | Effect of adding high-pass filter on the convergence of the calibration loop                                            | 33 |

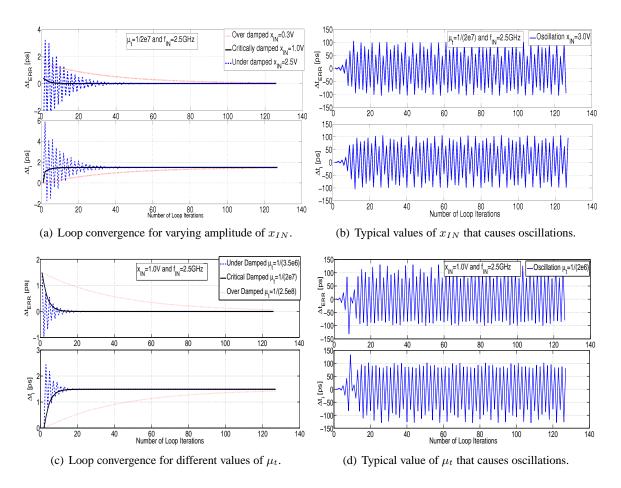

| 3-10 | Convergence of calibration loop for different values of $x_{IN}$ , $f_{IN}$ and $\mu_t$                                 | 34 |

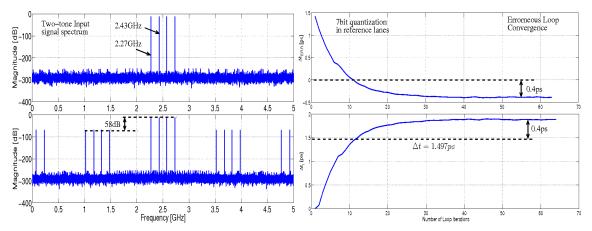

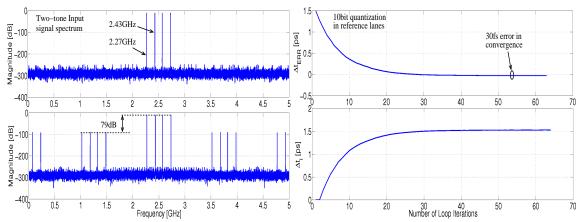

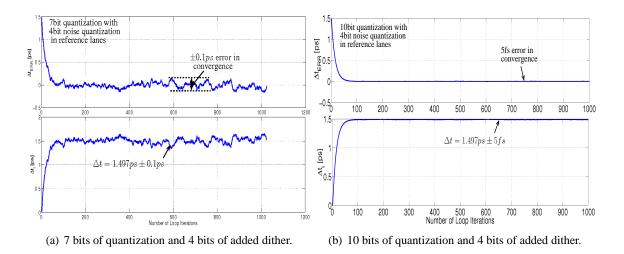

| 3-11 | Effect of finite quantization of the two reference lanes on the loop convergence.                                       | 35 |

| 3-12 | Reducing static error by adding uncorrelated dither to the input of the two reference lanes.                            | 36 |

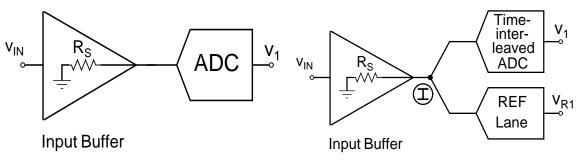

| 4-1  | Loading of input buffer by single ADC and a time-interleaved ADC alongwith its reference lane.                          | 38 |

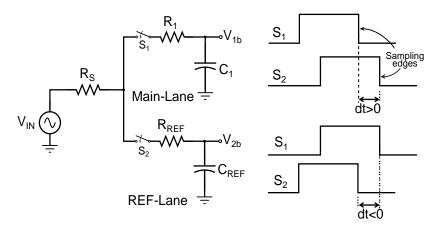

| 4-2  | RC models for sampling front end of one out M-interleaved ADCs in the ab-<br>sence and presence of reference lane       | 38 |

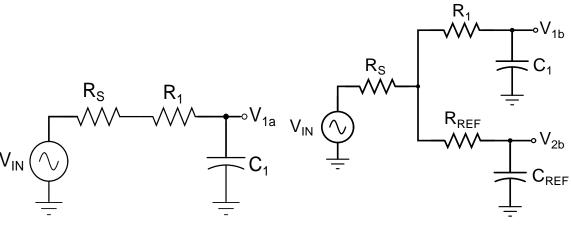

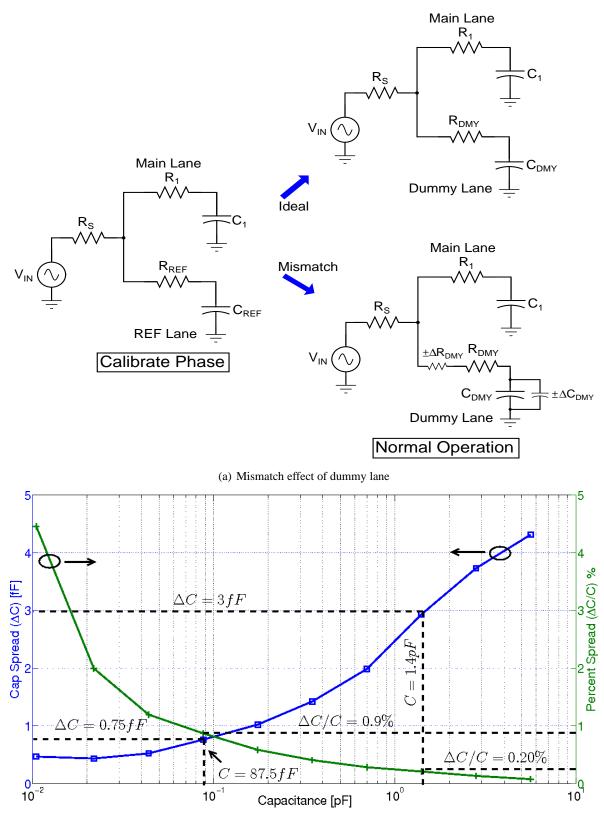

| 4-3  | Two phases of operation for time-interleaved ADC:a) Calibration phase and b)<br>Normal phase of operation.              | 40 |

| 4-4  | Estimation of input signal derivative by using additional reference lane with delayed input.                            | 40 |

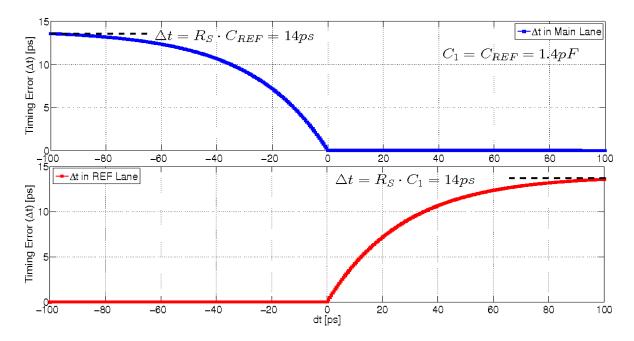

| 4-5  | Simulation of interaction between main-lane and reference lane sampling                                                 | 41 |

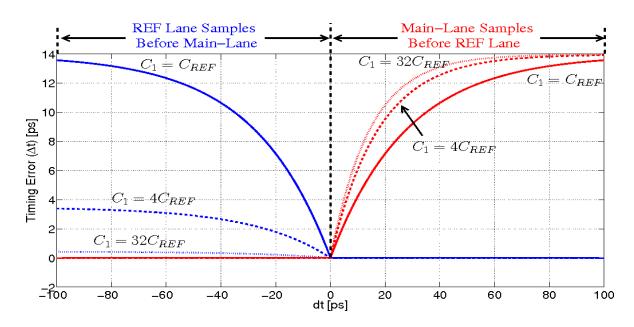

| 4-6  | Effect of $C_{REF}$ on the interaction between main-lane and reference lane sampling.                                   | 42 |

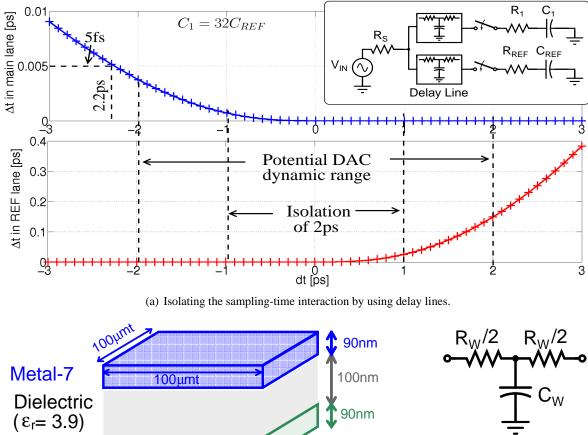

| 4-7  | Using wire based delay lines to isolate interaction between main-lane and reference lane sampling instances.            | 43 |

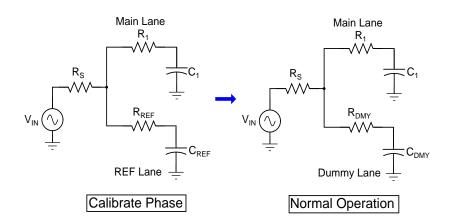

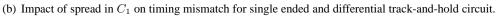

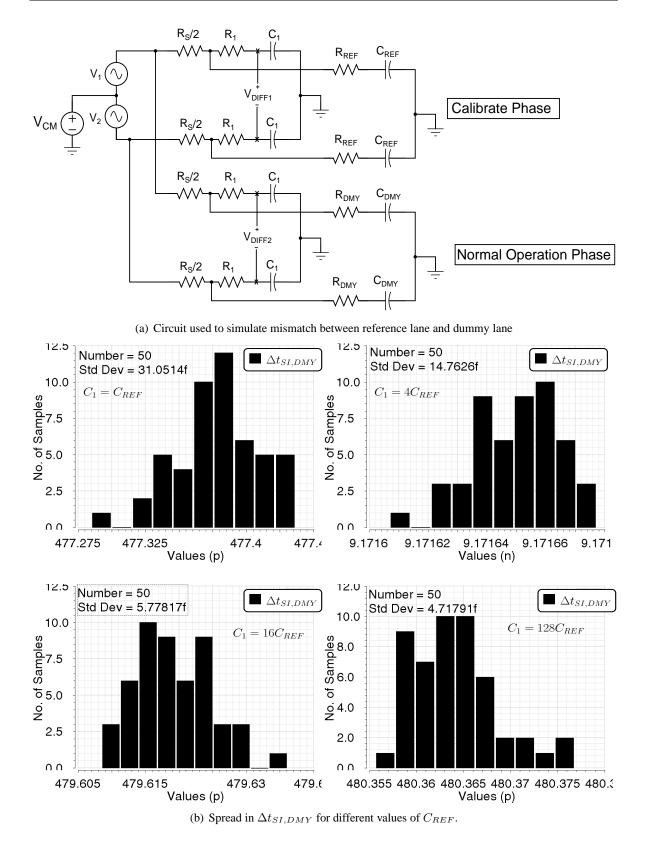

| 4-8  | Impact of mismatch between dummy lane and reference lane, and its depen-<br>dence on the size of the sampling capacitor | 45 |

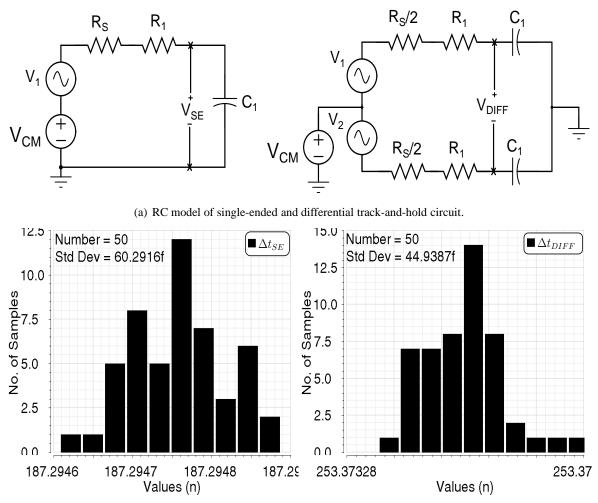

| 4-9  | Validating eqn.(4-13) and eqn.(4-20) for spread in $C_1$ .                                                              | 47 |

| 4-10 | Minimizing timing error due to mismatch between reference lane and dummy lane by scaling the sampling capacitor.        | 48 |

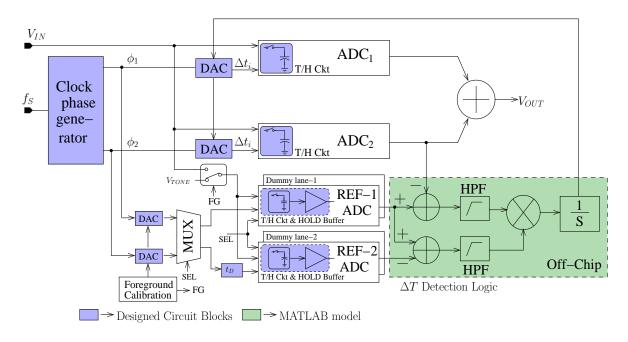

| 5-1  | System-level block diagram of timing error calibration loop.                                                            | 52 |

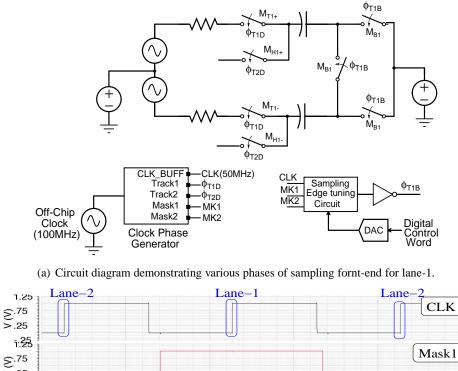

| 5-2  | Block diagram of clock path                                                                                             | 54 |

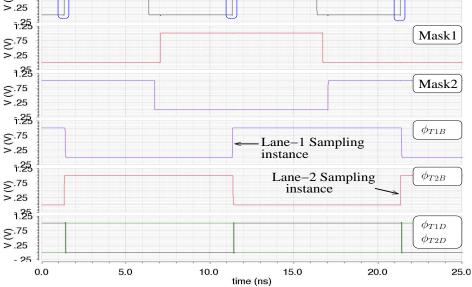

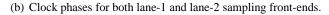

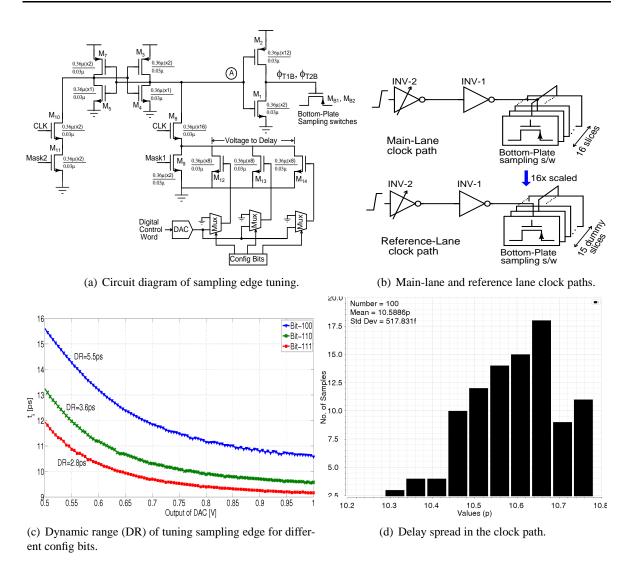

| 5-3  | Sampling edge tuning circuit and its simulation results.                                                                | 55 |

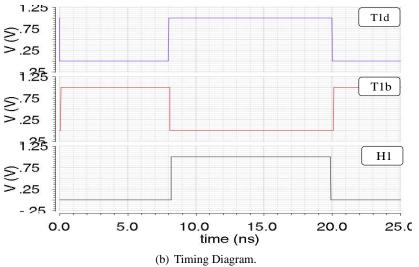

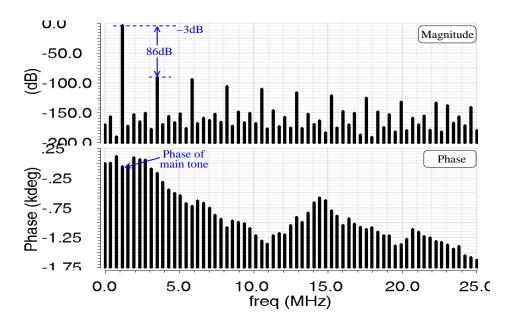

| 5-4  | Simulation results of the track-and-hold circuit for main-lane and 16x scaled reference lane.                           | 57 |

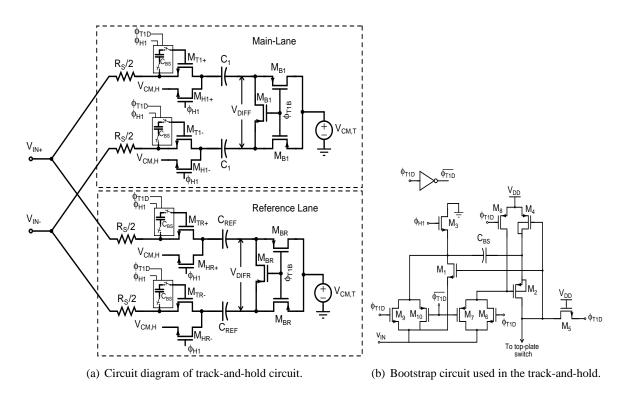

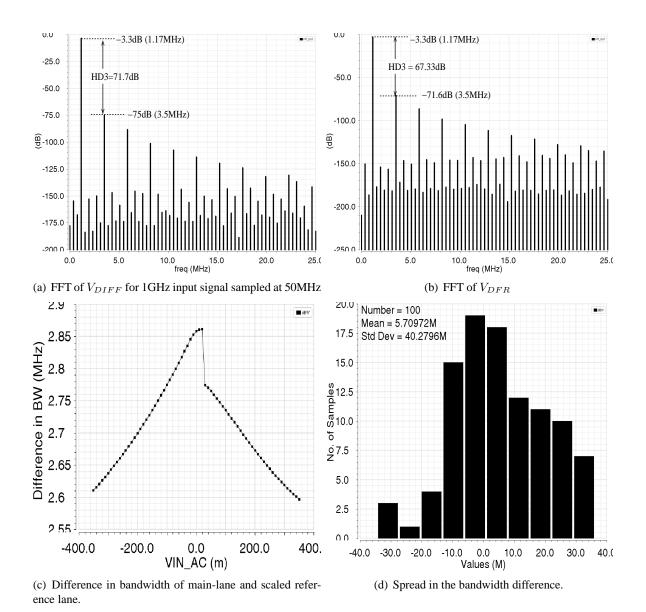

| 5-5  | Simulation results of the track-and-hold circuit for main-lane and 16x scaled reference lane.                           | 58 |

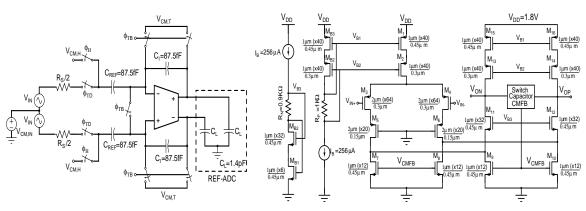

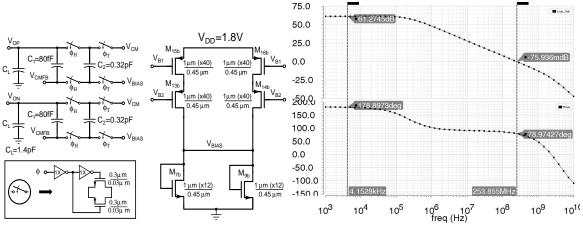

| 5-6  | Design of HOLD buffer for REF lane ADCs                                                                                 | 60 |

| 5-7  | Simulation Results of HOLD buffer                                                                                       | 62 |

Master of Science Thesis

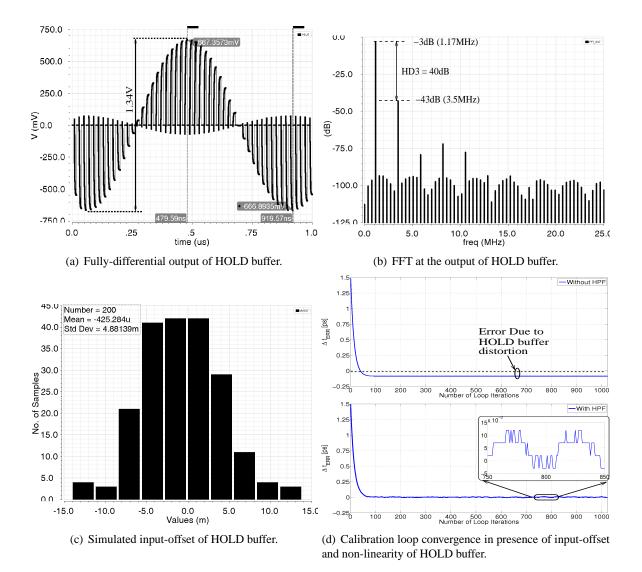

| 5-8  | Window of sampling instance due to various sources of timing errors   | 63 |

|------|-----------------------------------------------------------------------|----|

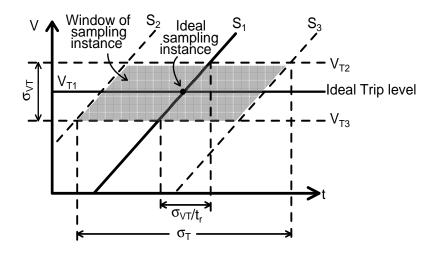

| 5-9  | Fine-coarse arrangement and unit cell of the DAC.                     | 63 |

| 5-10 | Circuit-level implementation of 11-bit DAC                            | 65 |

| 5-11 | DNL simulations of DNL of 11-bit DAC                                  | 68 |

| 5-12 | Area estimation of 11-bit DAC.                                        | 69 |

| A-1  | Signal power level expected at the output of the wideband capture ADC | 76 |

| C-1  | Track-and-hold circuit used in this thesis.                           | 82 |

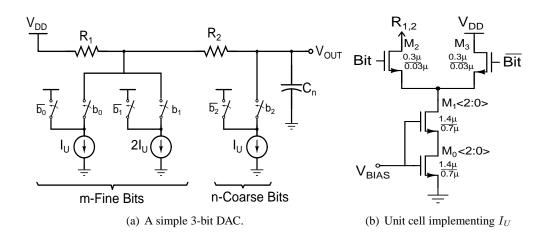

| C-2  | Magnitude and phase plot for output of the track-and-hold circuit     | 83 |

# **List of Tables**

| 5-1 | Device sizes for the track-and-hold circuit.                               | 59 |

|-----|----------------------------------------------------------------------------|----|

| 5-2 | Device sizes for the boot-strap circuit                                    | 59 |

| 5-3 | Specifications achieved by the HOLD buffer design.                         | 61 |

| 5-4 | Specifications achieved by the 11-bit DAC design.                          | 69 |

|     |                                                                            |    |

| A-1 | Summary of specifications for wideband capture ADC for mobile applications | 76 |

### Acknowledgment

Last two years that I have spent in Netherlands were a collection of bittersweet memories, both at TU Delft and Broadcom. I take this opportunity to thank all those who cheered with me during my "ups" and stood besides me during my "down" turns.

First and foremost, I would like to express my sincere gratitude to my mentor at Broadcom, Dr. Frank van der Goes, for his continuous support and encouragement. I am indebted to him for his faith in me, being tolerant to my weaknesses and sharing his immense knowledge of circuit design. There were innumerable instances when he allowed me to explore different fields while pulling my focus back on actual problem. I profusely thank Dr. Klaas Bult for giving me an opportunity to work at Broadcom, Netherlands, among an outstanding group of engineers. His intuitive and "equation-free" insight, creativity, and practical bent of mind have greatly enriched my learning and also benefited this work. I had received excellent guidance and had enlightening discussions with both Frank and Klaas. It was indeed an honor to work with both of them. They have sparked many research ideas which I will continue to pursue in future.

I would also like to extend my thanks to Prof. Michiel Pertijs and Prof. Leo de Vreede for reviewing this thesis and agreeing to serve on my thesis defense committee.

My heartiest thanks and appreciation go out to Prof. Kofi Makinwa for financial support, mentorship, test-chip support, and for reviewing my paper and this thesis. Through his actions he has set an example as a mentor and a researcher, which I can only aspire to come close. On the whole, I had a quite exciting experience working under him and I hope to continue interacting with him in the future. I also wish to thank Prof. J. Huijsing for his great enthusiastic support that I received during a hobby project. Prof. Huijsing has a remarkable ability to decompose a complex circuit into its most fundamental form. I am infinitely grateful to him for teaching me finer nuances of analog circuits and allowing me to attend the famous opamp design course.

Last one year at Broadcom has been a remarkable and fulfilling experience that has shaped my thoughts and will steer my future actions. During my initial days, our wonderful HR Els van Zijl, ensured that the cumbersome official formalities are kept smooth and simple. I am truly indebted to her for earnest efforts and help while I moved to a new house. Special thanks are due to Dr. Jan

Westra for keeping our work environment stress-free with his witty sense of humor. I also thank him for proof reading this thesis. I would also like to single out our receptionist, Cora Gunsing for being a "One Stop Solution" for all practical matters. I thank Dr. Davide Vecchi and Rob de Haas for helping in a hundred different ways. Thanks are also due a plenty to all my colleagues, the Chinese group, the Italian gang, and all others, for being such a good company.

I was very fortunate to be a part of coveted Electronics Instrumentation (EI) lab. I would like to thank all my friends and colleagues there for making it an incredible place to work. In particular, I thank Saleh and Ugur for proof reading my thesis, and Zu-Yao for his technical support. Thanks are due to rest all with whom I had hours of fun and fascinating discussions and who have shared many precious moments with me. I owe special thanks to Ugur for his help and support to meet pressing tape-out deadline. Special gratitude goes to the EI Lab office staff, Joyce and Karen, for all the help from managing finance and supporting conference travel to organizing day-out and new-year dinners.

I would like to thank Mirita for her loving support and encouragement. Her positive attitude and never give-up spirit has been an important driving force to see me through the tough times.

Finally, and most importantly, I would like to express gratitude to my parents, my brother and my grandfather. This work is a product of their endless love and support.

### **Chapter 1**

### Introduction

**I**NTEGRATED circuits technology has undergone rapid scaling since its invention. In 1960, Gordon Moore made an empirical observation that the number of devices on a chip approximately doubles every 18 months. With scaling to new technology nodes, feature size shrinks by 70%, transistor density doubles, wafer cost increases by 20% and chip cost comes down by 40%. These new technology nodes result in faster, smaller and cheaper transistors. In fact, due to scaling the price of one transistor has dropped 100 million times and the trend still continues. This rapid drop in price of a transistor has stimulated new applications and enabled advanced communication/computing appliances. By making the transistors and the interconnects smaller, more circuits can be fabricated on each silicon wafer thereby reducing the price of each circuit. Additionally, circuits of various nature like digital, analog, and RF circuits can be integrated together to reduce the price of the total system.

#### **1-1** Motivation

Wireless systems like mobile phones are one of the many systems that have benefited greatly from the integrated circuit technology. For instance, integrated radio subsystems for GSM [4], WLAN [5], and Bluetooth [6] have already been demonstrated in the literature. Present mobile-handsets contain many such transceivers of different standards, packed densely together. On the other hand, new wireless standards are being rapidly introduced in the market. The consumer demand of accessing these new wireless services from a single handset is thus, ever increasing. In the rush of providing more wireless services, future mobile handsets will only grow in size and cost which would eventually defeat the benefits derived from technology scaling [7]. This proliferation in size and cost of mobile-handsets can be subdued by integrating various wireless services using a universal and tunable hardware platform. Such a platform should be able to tune to a carrier frequency over a wide range, and should support a variety of modulation and data rates.

One such possible architecture, as proposed in [1], is shown in fig.(1-1). The receive link (Rx) which comprises of an amplifier and an ADC would receive RF signals from all wireless standards. Based on the service required by the user, the digital signal processor (DSP) will tune respective carrier frequency and demodulate the received data. Similarly, depending on desired wireless service, the data

Figure 1-1: Mitola's wideband radio [1]

is accordingly modulated by the DSP which is transmitted directly by a DAC. Thus, all functionality of a radio are implemented on a highly tunable platform of DSP. Finally, in addition of being tunable, a fully-digital radio implementation (like on a DSP) is also favored by steady performance improvement of digital circuits with technology scaling.

The focus of this research is to improve performance of the Rx ADC for wideband radios targeted for mobile applications. As the ADC is close to the antenna, it should support finer input signal amplitude and wider input frequency range. This translates into a stringent requirement on linearity, speed and resolution of the ADC. For instance, a wideband receiver for cable applications is designed to simultaneously capture 16 channels located between 48-1002MHz TV band, with 50dB SNDR (signal-to-noise and distortion ratio) 2.6GS/s sampling speed, and 10b quantization while consuming 0.5W power [8]. Note that a higher resolution may also be required in order to support complex modulation schemes across various wireless standards.

The accuracy of an ADC can be expressed by effective number of bits (ENOB) which is defined as,

$$ENOB = \frac{SNDR - 1.76}{6.02}$$

(1-1)

where, SNDR is defined as ratio of input signal power to total noise and distortion power. Depending on the design an ADC can consume varying amount of energy to achieve same ENOB. In order to compare energy efficiency of two different ADC design, a popular figure-of-merit (FoM) used in the literature [2] is given as,

$$FoM = \frac{P_{Total}}{2 \cdot min(f_S/2, ERBW) \cdot 2^{ENOB}}$$

(1-2)

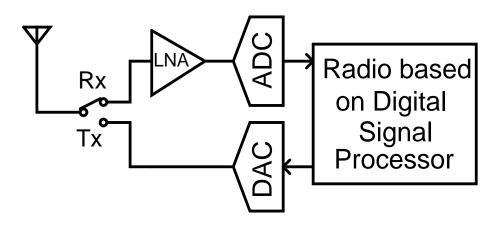

where,  $P_{Total}$  is the total power consumed by the ADC,  $f_S$  is the sampling frequency, and ERBW is the effective resolution bandwidth. Fig.(1-2)(a) is the plot of figure of merit (FoM) versus ENOB, for all ADCs published at ISSCC and VLSI symposium between 1997 and 2013. A larger value of FoM means that the ADC consumes more energy to while it makes one step to convert analog input to digital value. It is evident that FoM for ENOB of 12 bits is in the order of 20fJ/conv-step which is far from target FoM of 1fJ/conv-step (derived in Appendix-A). The FoM increases rapidly for a higher value of ENOB. FoM is also high for lower ENOB because, these designs primarily have high sampling speed designs. It is evident from the plot that best state-of-the art FoM lies between

(b) FoM versus sampling frequency for ADCs designed in 65nm CMOS process only. Number on each data point is the ENOB of that design.

**Figure 1-2:** FoM versus ENOB and sampling frequency for ADCs published at ISSCC and VLSI from 1997-2013 [2]

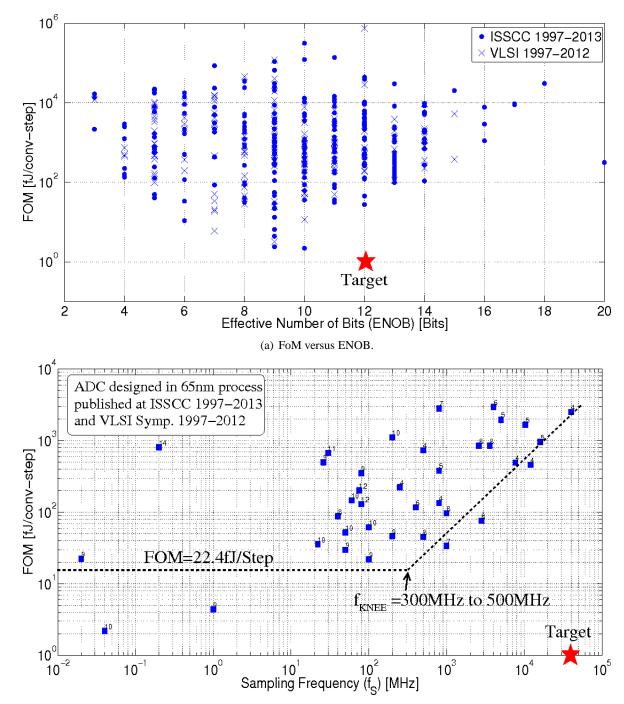

Figure 1-3: FoM versus sampling frequency for single lane and M-lane interleaved ADC

an ENOB of 8 to 9. A similar observation can also be made for FoM versus sampling frequency. The plot in fig.(1-2(b)) shows FoM versus sampling frequency for ADCs designed in 65nm CMOS process. The number on each data point represents ENOB of the design calculated using eqn.(1-1). For sampling frequencies below the knee frequency  $f_{KNEE}$ , the FoM curve is flat as the power consumption ( $P_{Total}$ ) increases linearly with  $f_S$ . But for  $f_S$  greater than  $f_{KNEE}$ , the speed-power relation turns non-linear and hence, mediocre improvement in  $f_S$  is achieved at considerable power penalty. The value of  $f_{KNEE}$  is determined by technology. For instance,  $f_{KNEE}$  is between 300-500MHz for CMOS 65nm process. Note that the FoM plot in fig.(1-2(b)) is on log-log scale and hence, for  $f_S$  greater than  $f_{KNEE}$ , the FoM increases linearly.

As shown in fig.(1-3), interleaving can break this speed-power trade-off and can improve the FoM of ADC. The technology limit,  $f_{KNEE}$ , for a single channel can be extended to  $M \cdot f_{KNEE}$  by interleaving M-lanes operating at  $f_{KNEE}$ . Due to overhead associated with interleaving, the benefits in FoM are not immediately visible. There exist a break even frequency  $f_B$  above FoM improves by interleaving. In other words, an interleaved ADC is more efficient than a single ADC for  $f_S$  above  $f_B$ . For  $f_S$  below  $f_B$  a single ADC is more efficient than an M-interleaved ADC because the hardware required to implement interleaving contributes only to  $P_{Total}$  in eqn.(1-2). On the other hand, for  $f_S$  greater than  $M \cdot f_{KNEE}$  the power consumption increases more rapidly for M-interleaved ADC than that for a single ADC. Hence, M-lane interleaved ADC would improve FoM only for sampling frequencies greater than  $f_B$  and smaller than  $M \cdot f_{KNEE}$ .

#### **1-2 Basics of Time-Interleaved ADC**

In a time-interleaved ADC many slow ADCs operate in parallel to achieve higher net throughput. The concept of time-interleaved ADCs is not new and was proposed first in [9]. However, the critical advantage of time-interleaved ADC is that it can break speed-power trade-off in a given technology. This benefit was not recognized till a decade ago. The research of [10] is mostly one of the first work to show that for a given speed and resolution overall power consumption of an ADC can be reduced by operating multiple slow single ADCs in time-interleaved fashion. Since then research on time-interleaved ADCs has been quite active.

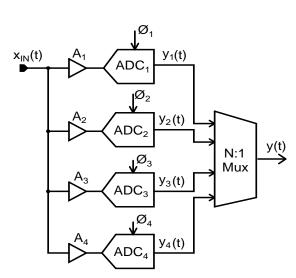

Figure 1-4: Block diagram of basic 4-ADC interleaved with timing error.

Fig.(1-4)(a) shows a simple time-interleaved ADC where 4 individual ADCs are operating in parallel. During  $\phi_i$  the input is sampled by the respective  $ADC_i$ . Under ideal conditions the overall output y(t) is obtained by adding the output of all 4 ADCs together. However, in real time-interleaved ADCs there are interleaving issues like input offset, gain mismatch, timing error and bandwidth mismatch. These issues are dealt in greater detail in Chapter-2. For sake of argument let's assume that only timing error,  $\Delta t$ , is present (sources of timing error are covered in Chapter-2). As shown fig.(1-4)(b), due to the timing error the sampling instance of  $ADC_3$  is shifted by  $\Delta t$ . This makes  $ADC_3$  sample input signal at a wrong time instance making an error of  $\Delta v$ . Now, when the outputs are added together, along with the input signal information an additional spurious tone is also created due to the error voltage  $\Delta v$ .

The focus of this thesis is to minimize  $\Delta t$  by employing a calibration loop around the timeinterleaved ADCs. As will be shown in the subsequent chapters, by suppressing  $\Delta t$  as much as possible, the magnitude of the spurious tone can be reduced. Spurious tones are also generated by other interleaving issues. However, the problem of input offset and gain mismatch can be solved like in any other ADC but the problem of a timing error is very specific to time-interleaved ADCs. Even though significant amount of work on timing errors has already been done, it is still an active area of research in current literature as it is not yet completely solved. Finally, out of all the interleaving issues timing error is the most difficult to calibrate because it does not easily lend itself to detection or correction which makes the design of calibration loop all the more interesting. Hence, the focus of this thesis is to solve timing errors out of all the other interleaving issues.

#### **1-3 Application: Wideband Capture ADC**

Time-interleaving is a well-suited architecture to realize wideband capture ADCs for mobile applications as it can achieve high sampling-speed and low power consumption simultaneously. To better

Figure 1-5: Typical Rx link for zero-IF receiver.

Figure 1-6: Wideband capture receiver architecture for future mobile applications.

7

understand the functioning of a wideband capture ADC, it is worthwhile to understand the role of an ADC in conventional Rx link. Fig.(1-5) shows one such Rx link for zero-IF receivers. An antenna would receive an input signal from 0.8GHz to 2.5GHz, which covers all the major bands used by today's mobile handsets [7]. Typical signal spectrum at the input of the LNA is shown by (A) in fig.(1-5) where the desired signal is received along with a blocker tone. If the LNA is assumed ideal then this spectrum will appear at the input of mixer unscathed. The mixer down-converts the received signal by multiplying it with local oscillator frequency. Thus, as apparent from (B), the desired signal is moved to baseband and can be retrieved by simple low-pass filtering. The receiver can tune to a new channel by analog tuning of the local oscillation frequency (shown in fig.(1-5)). Thus, as depicted from the spectrum at (C), the presence of a blocker tone does not hamper the receiver functionality.

Fully digital radio of fig.(1-1) can be realized by swapping the position of mixer and low-pass filter with that of the ADC. Thus, as shown in fig.(1-6), mixer and low-pass filter are moved completely into digital domain which relaxes their design. For instance, channels can be easily tuned by changing the digital tuning control word. As argued in the first section, this flexibility enables the implementation of a radio on a DSP platform. However, as the ADC moves closer to the antenna, its design specifications get more stringent and thus, the ADC design becomes more involved. For further apprehension, assume again that the spectrum of the received signal is represented as shown by  $(\widehat{A})$  in fig.(1-6). Due to the timing error,  $\Delta t$  of the time-interleaved ADC an image is created for the blocker tone. The image is only created for the blocker tone and not for the desired signal as the desired signal has much smaller amplitude level. Further, due to the sampling process of the ADC which samples at the rate of  $f_S$ , this image of the blocker tone can fold-back into the desired signal band as shown in  $(\widehat{B})$  in fig.(1-6). Once the image of blocker tone lands in the desired signal band even digital filtering will not help. Hence, as shown by the spectrum at  $(\widehat{C})$ , the image of the tone will persist at the output as it is indistinguishable from the desired signal.

Hence, designing a wideband capture receiver relaxes design specifications on the mixer, filter and channel selection, but it greatly increases the design challenge for the ADC. As the ADC will be invariably a time-interleaved ADC, its timing error should be low enough to avoid creating strong image of blocker tones.

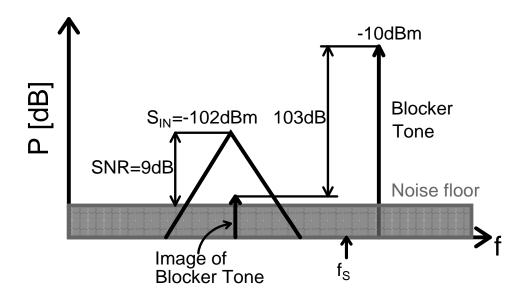

#### 1-4 Target Timing Error Correction Accuracy

While designing the calibration loop to compensate for the timing errors, it is important to know the level of accuracy expected from such a calibration loop. The wideband capture ADC would capture all wireless standards present in a mobile handset, including GSM cellular. As per GSM specification the sensitivity of the receiver should be at least -100dBm. The range of received signal is from -10dBm to -100dBm. Consider a case as shown in fig.(1-7), where a blocker tone has power of -10dBm whereas, the desired signal is at the lowest supported power level, i.e. -100dBm. Due to timing error and sampling process of an interleaved-ADC, an image of blocker tone might be created in the desired channel bandwidth. Clearly, in order to distinguish the desired signal the image of the blocker tone should be lower by at least 90dB or more. Thus, the timing error should be low enough such that the image of blocker if created, stays below 90dB.

The relation between the timing error and the SNR is given as (derived in Chapter-2),

$$SNR = \frac{3}{2\pi^2 \Delta t^2 f_{IN}^2} \tag{1-3}$$

Master of Science Thesis

Figure 1-7: Spurious free dynamic range requirement for wideband capture ADC for GSM signals.

For SNR=90dB,  $f_{IN} = 2.5$ GHz, the resulting timing error is 5fs. Thus, the timing correction accuracy of the calibration loop should be at least 5fs or better (Refer Appendix-A for additional specifications). To achieve this accuracy is the target of this thesis.

#### **1-5** Research Goal and Contributions

As argued in the previous section, the sampling time errors create unwanted spurious tones which cannot be distinguished from the desired signal. These spurious tones can be suppressed by calibrating the sampling time error. In order to receive a GSM signal the sampling time errors of the wideband capture ADC should be below 5fs level. To achieve this level of accuracy a calibration loop is needed. Hence, the initial goal of this research is to investigate various calibration architectures and choose the one which can achieve timing error correction accuracy of better than 5fs.

For achieving high timing error correction accuracy, it is vital to detect timing errors precisely. In this regards, it will be shown in Chapter-2 that the use of additional reference ADCs, is the most suitable topology [11]. From the results presented in [11] it is not evident that this topology can truly achieve 5fs accuracy. However, they do reveal that this topology is quite promising. Thus, the second goal of this research is to study this calibration architecture, identify any existing issues, and provide relevant solutions to overcome them.

As it will be shown in chapters-3 and 4, the topology of [11] has several shortcomings. For instance, the input offset of the reference lanes hampers the calibration loop convergence. Also, the use of reference lanes to detect timing error changes the load of the input buffer whenever it is used by the calibration loop. This change in the loading of the input buffer limits the accuracy with which the timing errors can be detected. Lastly, the sampling instance of reference lanes and the main-lane ADCs interact with each other to further degrade the timing error detection.

Finally, even if the above mentioned problems are solved, the calibration loop proposed in [11] can achieve 5fs accuracy only when a high resolution D/A converter is available to correct the timing errors. This D/A converter needs to have low-area and low-power as multiple copies of it would be employed.

The key research contributions which addresses all these goals are highlighted below:

- The calibration loop is made resilient to the input offset of the reference lane by incorporating a high-pass filter in the loop.

- The change in input buffer loading due to reference lanes, is solved by adding dummy lanes. Thus, making the loading of input buffer constant.

- The interaction between the sampling instance of the reference lanes and the main-lane ADCs is identified through analytical derivation. It is also cross verified through simulations. This problem is solved by inserting delay lines in the sampling front-end of reference lanes and main-lane ADCs.

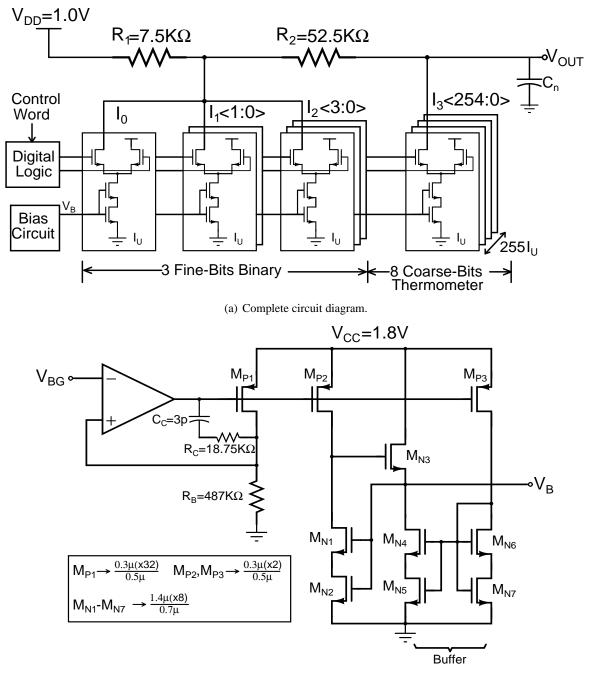

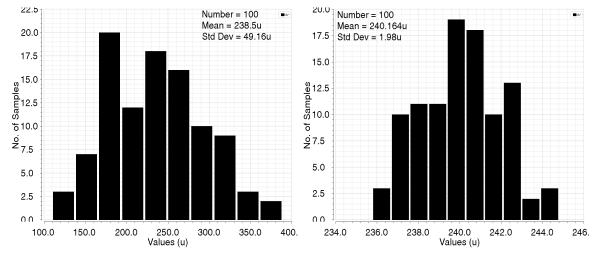

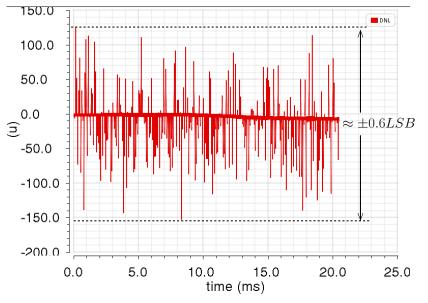

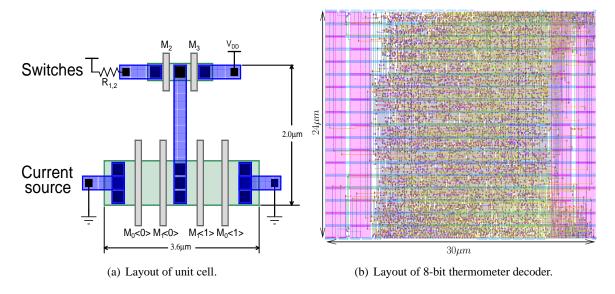

- For correcting the timing errors a low-power 11-bit D/A converter is designed which achieves DNL of < 1*LSB*. The D/A converter has sufficient dynamic range to correct errors within ±2.5ps.

#### **1-6** Thesis Organization

This thesis is divided into six chapters. Chapter-2 begins with an overview of time-interleaved ADCs and provides a brief explanation of various time-interleaving issues on the performance of an ADC. As the focus of this thesis is to calibrate timing errors, more emphasis is laid on it. Sources of timing errors and its impact on signal-to-noise ratio (SNR) are explained. Lastly, calibration topologies and techniques to detect timing errors are discussed.

In chapter-3, a background timing error calibration loop is discussed which uses two reference lanes for error detection and adjusts sampling clock edges for timing error correction. The stability and convergence of the calibration loop are studied using a MATLAB model. Stability of the loop is examined in the presence of input offset, gain mismatch, and varying input signal amplitude and frequency. Further, it was observed that finite quantization of reference lanes can cause an error in the steady-state convergence of the loop. This problem is solved by adding dithering at the input of the reference lanes. The effectiveness of adding dither is studied and relevant simulation results are discussed in this chapter.

Chapter-4 investigates the timing errors caused due to loading of the reference lane. Reference lanes only load the input buffer during calibration phase and not during the normal ADC operation. This modulation of input buffer load also contributes to a timing error. To avoid this problem, the reference lanes are replaced by a dummy sampling front-end during normal operation mode. Further, during calibrate phase the sampling instances of reference lane and main-lane can interact with each other adding to the timing errors. To mitigate this interaction, a solution of using delay lines in the sampling circuit is proposed. Lastly, mismatch between a dummy lane and a reference lane also contributes to timing error. A simple technique is proposed where scaled-down version of the main-lane sampling circuit is used for reference and dummy lanes to reduce the timing errors.

Chapter-5 shows circuit level implementation details of various blocks used in the timing error calibration loop. Design of blocks such as sampling front-end circuit of main-lane ADC and reference lanes, D/A converter for tuning sampling clock edges, and the reference lane buffer, are described along with circuit simulation results.

Finally, chapter-6 draws a conclusion from this work and potential topics for future improvements and research are suggested.

### Chapter 2

# Sampling Time Errors in Time-Interleaved A/D Converters

The time-interleaved ADC cycles through M-parallel lanes of ADCs generating a net throughput Mtimes higher than a single individual lane ADC. As a result, a time-interleaved ADC can achieve high sampling speeds which would not be possible with a single ADC without excessive power penalty. Thus, for a given resolution, time-interleaved ADCs can break the speed-power trade-off by reducing total power consumption and increasing the sampling speed. However, mismatch between the lane-ADCs degrade the performance of the total interleaved-ADC by introducing unwanted spurious tones in its output spectrum. Thus, it counteracts the speed benefit gained from time-interleaving.

In this chapter, the basic principles of time-interleaved ADCs is described. It is followed by a brief discussion on various sources of mismatch like offset, gain, timing and bandwidth. The focus of this thesis is mainly on calibration of timing errors. Hence, the topics pertaining to timing errors like their effect on ADCs performance, methods to detection and calibrate them, and calibration topolgy are elaborated.

#### 2-1 Basics of Time-Interleaving

In a typical time-interleaved ADC, M-number of ADCs operate in parallel with a conversion rate of  $f_S/M$ , where M is the number of interleaved ADCs and  $f_S$  is the sampling rate. These M-interleaved ADCs operate from individual sampling phases,  $\phi_i$  (where, i = 1, 2, ..., M), which are phase shifted from each other by one sampling period  $T_S$ . During these sampling phases, each individual ADCs sample the input signal. At the output, data from all M-interleaved ADCs is muxed together to achieve an overall sampling rate of  $f_S$ .

To further understand the operation of the time-interleaved ADCs, consider an ideal 2x interleaved ADC as shown in fig.(2-1). The input signal,  $x_{IN}(t)$  is sampled by two ideal ADCs,  $ADC_1$ and  $ADC_2$ . These two ADCs operate with phases  $\phi_1$  and  $\phi_2$ , and generate output data represented by  $y_1(t)$  and  $y_2(t)$  respectively. For a hypothetical input  $x_{IN}(t)$ , the output of two ADCs,  $y_1(t)$  and  $y_2(t)$

Figure 2-1: Block Diagram of an ideal 2x interleaved ADC with timing waveforms.

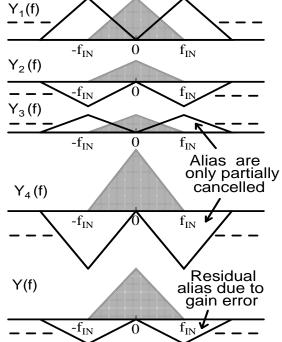

can be pictorially presented as shown in fig.(2-2). It would be apparent that both ADCs operate with their individual lane sampling rate of  $f_S/2$ . Thus, if  $f_{IN} > f_S/4$  then both  $y_1(t)$  and  $y_2(t)$  contain aliases of the input signal. However, when  $y_1(t)$  and  $y_2(t)$  are added together the final output contains no aliases. This phenomenon is depicted in frequency-domain picture of the interleaved ADC as shown in fig.(2-2).

The reason behind the absence of aliases is that, as shown in fig.(2-1) the sampling instance of each individual ADCs are exactly one  $T_S$  apart. Thus,  $\phi_2$  is time-shifted by one sampling period with respect to  $\phi_1$ . In frequency domain this time-shift corresponds to the rotation of phase. As the shift in time is exactly one clock period, the phase of the aliases in the output of  $ADC_2$  are exactly 180° out of phase with respect to the aliases in the output of  $ADC_1$ . Fig.(2-2) shows the spectra of the input signal and the outputs of the two ADCs. As the aliases in  $Y_2(f)$  are 180° out of phase with that in  $Y_1(f)$ , when added together they cancel each other exactly. An interesting mathematical account of this alias cancellation is exhaustively derived in [12].

Thus, M-interleaved ADCs operating at  $f_S/M$ , under ideal conditions, generates output identical to an individual ADC operating at  $f_S$ . Unfortunately, due to device mismatch, each lane-ADCs have slightly different offset, gain, bandwidth and sampling time instances. Due to these non-idealities, alias images in the output of each lane-ADC do not exactly cancel and thus, leave behind some residual alias images. Depending on the source of non-ideality, these residual alias images create spurs in the overall output spectrum.

#### **2-2** Types of Interleaving Issues

In this section various interleaving issues are discussed with more emphasis being laid on timing errors. A basic MATLAB script used to simulate these errors is provided in Appendix-B.

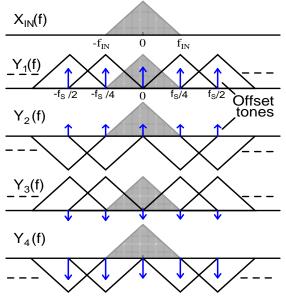

#### 2-2-1 Offset Mismatch

Figure.(2-3(a)) shows a typical 4-interleaved ADC with corresponding input offset. This offset arises from the input pair of a comparator used in an ADC and it is a random but additive error. In absence

Figure 2-2: Input and output signal spectrum of ideal 2-interleaved ADCs

of input signal, each lane-ADCs will sample their own offset which when combined with the output of another lane-ADCs would generate a periodic error signal. This periodic error signal creates spurious tones which are located at [3],

$$f_{SPUR,OS} = k \cdot \frac{f_S}{M}$$

where, k=1,2,...,M (2-1)

A typical spectrum of the input signal and the lane-ADC output is as shown in fig.(2-3(b)). The arrows (blue) are the tones due to sampling of input offset. These offset tones manifest themselves as spurs in the overall output spectrum of ADC as shown in fig.(2-3(c)). The time domain error signal due to different input offset of the lane-ADCs can be seen in fig.(2-3(d)). The magnitude of the offset spurs depends upon the amplitude and shape of this periodic error signal. However, these spurs are independent of input signal frequency and amplitude. Thus, they can be removed by employing techniques like digital filtering [13], chopping [14], or even calibration [11].

#### 2-2-2 Gain Mismatch

As shown in fig.(2-4(a)), assume that all 4-lane ADCs have different gains ( $A_1$  to  $A_4$ ). All the other characteristics are perfectly identical and ideal (e.g. zero input offset). Gain error is defined as the maximum difference between the gain of any two lane ADCs. The primary sources of gain error is the difference in reference voltages or the differences in the sampling circuit (e.g. charge injection or clock feedthrough) between various lane ADCs. Figure.(2-4(b)) shows that the gain error manifests itself by modulating the amplitude of the output spectrum. Thus, when the output of all the lane ADCs is combined, the alias in the output spectrum do not necessarily cancel each other. The magnitude of these spurs due to residual alias, depends on the magnitude of gain error and input amplitude.

Similar to offset mismatch, gain error also creates a periodic signal with frequency  $f_S/M$ . For a sinusoidal input, this periodic signal creates spurs by mixing with the input signal. These spurs,

Master of Science Thesis

(a) Block Diagram of 4-Interleaved ADC with input offset (b) Input spectrum and spectrum of individual lane ADCs

(b) Input spectrum and spectrum of individual lane ADCs with input offset

sampling frequency

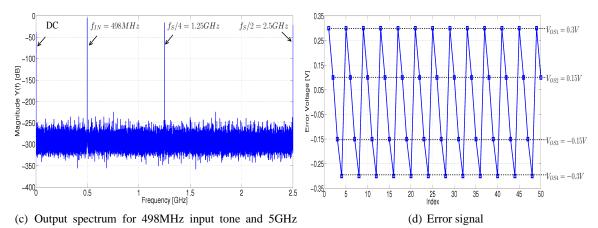

Figure 2-3: Effect of input offset and its mismatch on the output spectrum of 4-interleaved ADCs for sinusoidal input tone of  $f_{IN} = 498MHz$  sampled at  $f_S = 5GHz$

(a) Block Diagram of 4-Interleaved ADC with gain error

(b) Spectrum of individual lane-ADCs and total output with gain error

of -40dB

(c) Output spectrum showing spurs due to gain mismatch (d) Error signal for input sinusoid of  $f_{IN} = 498 MHz$ sampled at  $f_S = 5GHz$

Figure 2-4: Spurs due to gain error in the output of a 4x interleaved ADCs

#### Master of Science Thesis

$f_{SPUR,GE}$ , are located at [3],

$$f_{SPUR,GE} = \pm f_{IN} + k \cdot \frac{f_S}{M} \quad \text{where, } k=1,2,\dots,M$$

(2-2)

The location of these spurs can be verified from fig.(2-4(c)). Note that with a change in the input frequency, only the location of  $f_{SPUR,GE}$  changes and not its magnitude.

The magnitude of the gain error spurs is modulated by the input signal amplitude. Thus, the largest error in the output would occur when the input amplitude is the largest. As shown in fig.(2-4(d)), for a sinusoidal input, the maximum error in the output occurs at the peak of input amplitude and it is minimum when input crosses zero. Thus, like amplitude modulation, the spurs due to gain error are also multiplicative in time domain.

Unlike, the offset mismatch correction, the correction of gain mismatch is slightly involved. The gain mismatch can be easily calibrated by employing a foreground calibration which is not always possible. Hence, at present background calibration of gain mismatch is also a quite active research area. Research of [15], [16] and [17] are some of the popular works that can be used to combat the gain mismatch related errors.

#### 2-2-3 Timing Mismatch

Ideally the phase difference between the adjacent lane clocks, which are separated by one sampling period  $T_S$ , should be equal to  $2\pi/M$ . In practical implementation, the phase or timing errors are unavoidable due to the finite propagation of the clock signal, and variations in the clock buffers and sampling switches. For high input signal frequencies even a small timing mismatch can create significant error. The input signal effectively is phase modulated by a periodic timing error signal which has a frequency of  $f_S/M$ .

To highlight the impact of sampling time error, consider an ideal 2x interleaved ADC as shown in fig.(2-1). As shown in fig.(2-5),  $t_1$  and  $t_2$  are ideal sampling instances of  $ADC_1$  and  $ADC_2$  which are separated exactly by one sampling period  $(T_S)$  under ideal conditions. However, in the presence of a sampling time error,  $\Delta t$ , the sampling instances will shift from their ideal positions. As shown in fig.(2-5) the sampling instance of  $ADC_2$  has shifted from  $t_2$  to  $t_2 + \Delta t$ . This shift in the sampling instance will create an error voltage  $\Delta v_{TE}$  which can be expressed as,

$$\Delta v_{TE} = \frac{dx_{IN}}{dt} \cdot \Delta t \tag{2-3}$$

Thus, taking this error voltage into account the output of two ADCs at the sampling instances  $t_1$  and  $t_2 + \Delta t$  can be written as,

$$y_1(t_1) = x_{IN}(t_1)$$

(2-4)

$$y_2(t_2 + \Delta t) = x_{IN}(t_2) + \Delta v_{TE} = x_{IN}(t_2) + \frac{dx_{IN}(t_2)}{dt} \cdot \Delta t$$

(2-5)

It can be observed that  $y_2(t_2)$  contains the input signal  $x_{IN}(t_2)$  which is corrupted by its derivative. The operation of derivative in time-domain corresponds to a phase-shift of 90° in the frequency domain. Thus, the timing error tone will be 90° out of phase with the input signal. Thus, when the

Figure 2-5: Error in sampling input signal due to timing error

outputs of all the lanes are added together, the aliases again do not cancel each other. This creates spurs due to timing mismatch which are located at [3],

$$f_{SPUR,TE} = \pm f_{IN} + k \cdot \frac{f_S}{M} \text{ where, k=1,2,...,M}$$

(2-6)

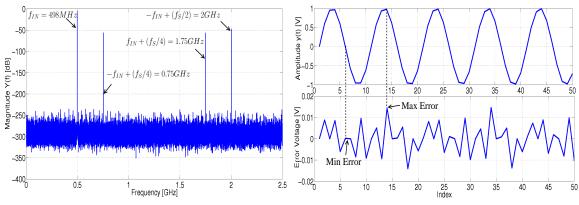

The location of  $f_{SPUR,TE}$  is same as the location of the spurs that stem from the gain mismatches. Unlike the spurs due to gain mismatch, the magnitude of  $f_{SPUR,TE}$  will not only depend upon input amplitude but also on the input frequency. This additional information might be exploited to separate gain error and timing error from each other. For DC input signals, timing error is zero and spurs in the output spectrum are only due to gain error. Once the gain error is calibrated or removed then, for high input frequencies, the spurs left in the output spectrum are due to timing mismatch or bandwidth mismatch.

#### 2-2-3-1 Impact of Timing Error

Assume a noise-free time-interleaved ADC. The output spectrum of such an ideal ADC will still have spurs due to interleaving issues (e.g. offset, gain, timing and bandwidth). Further, assume that these spurs are only due to timing error and not due to offset, gain or bandwidth mismatch. In such a scenario, the magnitude of these spurs will limit the maximum achievable SNR of a time-interleaved ADC. In order to get an estimate of this limit, assume a uniformly distributed input signal with the spectrum as shown in fig.(2-6). A uniformly distributed signal closely resembles a broadband signal which is the expected input signal for a wideband ADC in mobile applications.

On the other hand, the spectrum of the timing error signal,  $(2\pi f \Delta t)$ , is parabolic and increases infinitely with frequency. This spectrum when multiplied with input signal spectrum creates the total timing error spectrum, as shown in fig.(2-6), that corrupts the output spectrum of a time-interleaved ADC. Hence, it degrades the maximum SNR that can be achieved. To estimate the impact of timing error on the SNR, the input signal power and noise power needs to be computed. The signal power,

Figure 2-6: Spectra of input signal and timing error component.

$P_S$ , can be calculated by integrating the input spectrum shown in (fig.(2-6)), from  $-f_{IN}$  to  $f_{IN}$  as,

$$P_S = 2 \int_{-f_{IN}}^{+f_{IN}} A \, \mathrm{d}f \qquad (2-7)$$

$$= 4 \cdot f_{IN} \cdot A$$

Similarly, noise power can be calculated as,

$$P_{n} = \int_{-f_{IN}}^{+f_{IN}} (2\pi f \Delta t)^{2} X_{IN}(f) df \qquad (2-8)$$

$$= 8\pi^{2} \cdot \Delta t^{2} \cdot A[\frac{f_{IN}^{3}}{3}]$$

Solving the eqn.(2-7) and eqn.(2-8) yields signal-to-noise ratio (SNR) as,

$$SNR = \frac{P_S}{P_n} = \frac{3}{2\pi^2 \Delta t^2 f_{IN}^2}$$

(2-9)

This expression is an upper bound on the achievable SNR for a given timing error and given input signal frequency. A more elaborated discussion on plausibility of eqn.(2-9) can be found in [12]. Fig.(2-7) shows that for 12-bit required resolution, the timing error for a uniformly distributed input signal, has to be less than 80fs for an input frequency of 500MHz and less than 20fs for an input frequency of 2GHz. Recall that, as argued in Chapter-1 the target specification on the timing error is 5fs RMS.

#### 2-2-3-2 Sources of Timing Mismatch

The timing mismatch arises due to factors like finite skew of clock distribution network, systematic layout mismatches, delay variation of clock buffers, mismatch in the sampling switches, etc. However,

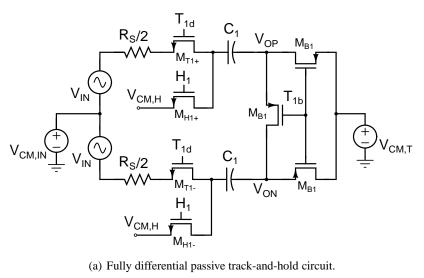

Figure 2-7: Bound on timing error for varying SNR and input frequencies

exact sources of timing mismatch, to certain extent, depend on the specific implementation of the sampling circuit. In this sub-section, the sources of timing error for a fully differential passive track-hold circuit, shown in fig.(2-8), are discussed. The design details of this circuit will be discussed in Chapter-5.

Fig.(2-8) shows two track-and-hold interleaved together. It also shows the clock distribution network and clock buffers. During the track phase ( $\phi_{Track1}$  is high) the top-plate switches ( $M_{T1+}$  and  $M_{T1-}$ ) are closed and the voltage on the sampling capacitor ( $C_S$ ) follows the input signal. During the hold phase the bottom-plate switches ( $M_{B1}$ ) opens and the top-plate of sampling capacitor is grounded. The differential output ( $V_{O+} - V_{O-}$ ) of the track-and-hold is thus, defined during the hold phase.

One of the timing error sources is a mismatch in the input distribution network which introduces systematic timing skew. Further, the mismatch in clock generation and distribution network also creates timing errors. These mismatches stem from different drive strength of clock buffers due to process variations, layout mismatches in clock buffers, HOLD period ( $T_{A1}$  and  $T_{A2}$  in fig.(2-8)) mismatch, and timing skew due to mismatches in the clock distribution network (routing of  $\phi_{Track1}$ ,  $\phi_{Track2}$ ,  $\phi_{Hold1}$  and  $\phi_{Hold2}$ ). For a larger interleaving factor, both clock distribution and input distribution become more complex and hence prone to larger mismatches.

In addition, mismatch in the passive sampling circuit also causes a timing error. These includes, mismatch in threshold voltage of bottom-plate sampling switches ( $M_{B1}$  and  $M_{B2}$ ), variation in ON-resistance of top-plate switches ( $M_{1+}$ ,  $M_{1-}$ ,  $M_{2+}$ , and  $M_{2-}$ ), and mismatch in sampling capacitor  $C_S$  due to process variation. Also, mismatch in bootstrap circuit (represented by  $C_{BS}$  and two switches in fig.(2-8)) will also introduce significant timing error.

Figure 2-8: Typical track-and-hold circuit for 2x interleaved ADC

#### 2-2-4 Bandwidth Mismatch

The last nonideality that hampers performance of time-interleaved ADCs is the mismatch in bandwidth of the sampling front end. The magnitude and phase response of sampling circuit changes with input frequency due to its finite bandwidth. The mismatch in bandwidth of different lane ADCs, thus, creates gain and timing error which changes with input frequency. To assess the effect of spread in bandwidth ( $\sigma(\Delta BW/BW)$ ) on the magnitude of gain and timing error, the sampling front-end can be modeled as a simple first order RC filter. Detailed derivation and analysis of timing and gain errors using this model can be found in [3].

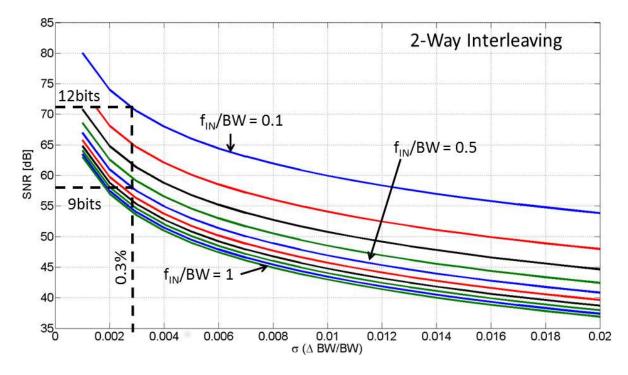

Fig.(2-9) shows degradation in SNR with increasing bandwidth mismatch  $\sigma(\Delta BW/BW)$ , for different ratios of input frequency to bandwidth. To achieve SNR corresponding to 12 bits with the sampling front-end bandwidth at least 10x greater than the maximum input frequency, the maximum allowable  $\sigma(\Delta BW/BW)$  is about 0.3%. However, if  $\sigma(\Delta BW/BW)$  is 0.3% but the bandwidth is just 2x larger than the maximum input frequency then, the SNR degrades down to 9 bits. Thus, to avoid considerable gain and timing errors the bandwidth of sampling front-end should be chosen large enough (about 10x). Alternately, bandwidth mismatch can also be calibrated [18].

## 2-3 Timing Error Detection and Calibration

As discussed in the previous section, to avoid spurs due to timing mismatch, in high speed timeinterleaved ADCs, the sampling edges of the individual lane sampling clocks should be set precisely (e.g. with maximum error of 20fs for 12 bits). Due to various timing error sources like finite propagation delay of clock signal distribution, systematic layout mismatches, delay variation of clock buffers, and threshold voltage variation of the sampling switches, it is impossible to achieve this level of accuracy only with careful layout. Hence, some form of calibration or correction is required to solve the errors due to sampling time.

Figure 2-9: Impact of bandwidth mismatch on SNR for a 2x-interleaved ADC [3].

#### 2-3-1 Use of common sample-and-hold.

One straightforward way to mitigate timing errors is to use a sample-hold front end common to all the interleaved lanes [8] and [19]. However, the common sampling front-end should work at the sampling rate  $f_S$  instead of  $f_S/M$  in case of per-lane sampler. The elevated sampling speed either creates harmonic distortion due to limited settling of the input sampler or incurs enormous power penalty as input sampler should operate M-times faster. Further, the noise of input sampler limits the overall resolution achievable by the ADC. Hence, using a common input sampler would be suitable only for moderate sampling speeds and moderate resolution ADCs. In addition, a common input sampler cannot solve bandwidth mismatch unless it is explicitly calibrated or each lane-ADC is ensured to have much wider bandwidth than input signal. Alternately, it would be desirable to part away with a common input sampler and instead have a way to calibrate timing error with lower area and power overhead.

### 2-3-2 Foreground vs background calibration.

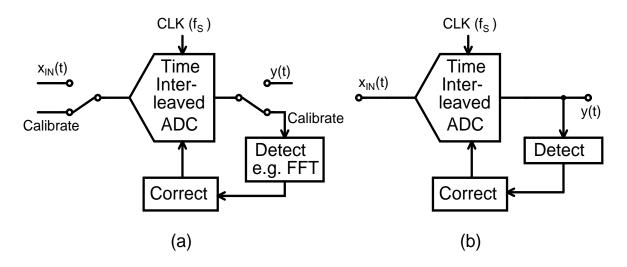

Invariably, all timing-error calibration techniques have two critical components: 1) timing error detection and 2) timing error correction. The detection and correction of timing errors can occur in the foreground or in the background as shown in fig.(2-10). Typically, during foreground calibration a test signal like a ramp or sinusoid is applied and timing error is detected in the digital domain (e.g. by using FFT) [20], [21] and [22]. Timing error correction can be done either in digital domain (e.g. fractional delay filter) or in analog domain (e.g adjusting sampling clock edges). Such foreground calibration is preferred when the circuit parameters like voltage and temperature or ambient operating conditions do not change dramatically. Foreground calibration is also attractive in applications

Figure 2-10: ADC under (a) foreground calibration (b) background calibration

like oscilloscopes, where occasionally ADC can be taken offline for calibration. However, for target application (wideband capture ADC for mobile applications discussed in Chapter-1), the ADC cannot be taken offline. Also, the circuit parameters and ambient operating conditions change significantly. In such scenarios, foreground calibration is not feasible and background calibration is the de facto choice. As shown in fig.(2-10)(b) during background calibration, timing error is detected and corrected while the ADC is still continuously operating.

#### 2-3-3 Digital detection and digital correction of timing errors.

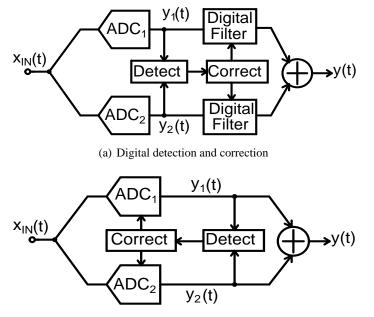

Irrespective of the type of calibration, timing error detection and correction techniques can be broadly classified to be either based on digital logic or analog circuitry. Figure.(2-11(a)) shows detection and correction of timing error in the digital domain. The lane ADC outputs,  $y_1(t)$  and  $y_2(t)$ , are passed through an adaptive fractional delay filter whose coefficients are tuned to correct for the timing error. Thus, when the two outputs are added together there is no timing error component in the final output. Based on the detected timing error, the filter coefficient can be tuned using various algorithms. For instance, researchers in [23] and [24] detect timing errors by chopping the output signal and using a 10-bit 21-tap FIR approximation to Hilbert transform filter. To correct the timing error in a 10-bit ADC, they employ a 29-tap FIR filter with 10-bit coefficients that realize an adaptive fractional delay filter. This particular approach has a drawback that if Nyquist-operation is desired then the input signal should be strictly band-limited to  $f_S/2$ . This condition may not be true for wideband capture ADCs where the spectral content beyond  $f_S/2$  may very well have finite energy. Further, the implementation of fig.(2-11(a)) would require the digital logic to observe and correct timing error on per sample basis. Thus, for M-interleaved ADCs, M digital blocks would operate at  $f_S/M$  rate. Although this approach might still be tractable for low sampling rates, it would incur very large power penalty for multi-GHz sampling rates. Finally, due to the complex adaptive fractional delay filters, this approach also has increased area and latency penalty.

(b) Digital detection and analog correction

Figure 2-11: Two different schemes for detection and correction of timing errors.

#### 2-3-4 Digital detection and analog correction of timing errors.

Alternately, as shown in fig.(2-11(b)), a second approach would be to detect the timing error in the digital domain and adjust analog circuit to correct for the timing error [20], [21]. As the timing error is compensated and thus physically removed, this technique can be very power efficient. The feedback loop does not operate on every sample, rather it gradually converges to remove timing error. Thus, once the feedback loop converges, it can enter into a low power mode. Analog tuning can be performed by adding a controlled phase shift (all-pass filter) in the input signal path or by controlling the sampling clock edges in the clock path. The latter technique is widely used as adding any analog circuit in the input path would hamper linearity and noise performance of the ADC. The sampling clock edges can be tuned by inserting a variable capacitive load in the clock path or by tuning the drive strength of the clock buffers.

Thus, background calibration of timing error with digital detection and analog correction is best suited for wideband capture ADC for mobile applications. Detection of timing error is challenging especially when the ADC is continuously operating. One solution is to add some form of pilot tone, like a known pseudo random signal or a ramp signal, along with the input. The timing error can than be detected by separating the pilot tone from the input signal by post-processing in background (e.g. low pass filtering [25], [26], and [27]). Unfortunately, invariably all post-processing techniques that can separate input signal and pilot tone rely heavily on the statistics of either input signal or pilot tone or both. For instance, in order to separate the pilot tone (e.g. a ramp signal) from the input signal, the input signal is required to have zero mean. Such constraints on input signal are not always feasible, however it might be possible to impose such constraints on the pilot tone. Still, in order to accommodate the amplitude of pilot tone the dynamic range of input signal has to restricted. Even if these limitations were to be overcome, the accuracy of detecting timing errors is limited by the poor efficacy of post-processing block to separate pilot tone from input signal.

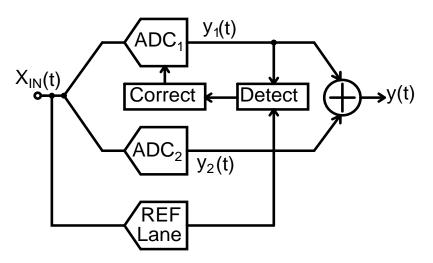

Alternately, timing error can be detected by using an additional reference lane as shown in fig.(2-12). In [28] a similar approach is used where the background calibration algorithm tries to maximize the correlation between the lane ADC and a 1-bit reference lane ADC. Thus, the timing error is removed by aligning the sampling time instance of all the lane ADCs to that of the same reference lane ADC. In addition, compared with using pilot tone, the timing error detection accuracy depends on how accurately input signal and pilot tone can be separated, which further depends on the amount of averaging being employed. Whereas, while using a reference lane, timing error is detected from same input sample directly. Hence, in order to meet the specification outlined in Chapter-1, the optimum choice of the timing error calibration loop would be to use background calibration with digital timing detection using reference lanes and analog correction.

Figure 2-12: Background timing error detection using reference lane ADC

## 2-4 Summary

In this chapter, the basic operation of time-interleaved ADCs is described. Several non-ideal effects that degrade the performance of such ADC are discussed. However, as the focus of this thesis is to calibrate timing errors in time-interleaved ADCs, they are discussed in greater detail. Formulation of the timing errors, its effect on SNR and its various sources are covered in this chapter. For a 12 bit SNR, the timing error has to be less than 20fs which cannot be achieved merely by careful layout. Hence, various calibration techniques are studied. Looking at the feasibility of calibration and desired precision, it can be concluded that background calibration with timing error detection based on reference lane and correction based on tuning sampling clock edge, is best suited for wideband capture ADCs for mobile applications.

# Chapter 3

## **Timing Error Calibration Loop**

**S** AMPLING time errors should be accurately detected to enable precise correction. As argued in Chapter-2, the timing error information can be separated from the input signal by using reference lanes. As a result, the timing errors can be detected with high accuracy. Based on the detected timing error, the sampling instances of all time-interleaved ADC lanes can be aligned to that of a common reference lane ADC. To fulfill this condition a background calibration algorithm in digital domain can be implemented. Similar attempt is reported in [11]. However, as shown in Chapter-2, for the target application of wideband capture ADC, the timing errors should be corrected with accuracy of 5fs RMS which is not possible if the calibration reported in [11] is used as it is. In this chapter, various limitations of the background timing error calibration loop of [11] is studied. Appropriate solutions are employed to overcome some of these limitations and realize the timing correction accuracy of 5fs. The core of the calibration loop is the use of two additional reference lanes for computing the timing errors. One reference lane quantizes the input signal whereas, the other quantizes the derivative of the input signal. The timing errors are compensated by analog fine-tuning of the sampling clock edges. The factors that govern the stability and convergence of the calibration loop are explored using a MATLAB model. Also, the input offset of the reference lanes or any of the main lanes can hamper the loop convergence. A high-pass filter (HPF) is embedded in the loop to circumvent this problem. Finally, the finite quantization of reference lane can potentially limit the correction accuracy of the loop. This problem is solved by adding dither to the input of the reference lanes. The effectiveness of this solution is studied in this chapter and pertinent simulation results are presented in the sections below.

## **3-1** Principle of Operation

Assume a simple timing error detection system as shown in fig.(3-1), where an ideal main lane-ADC and an ideal reference lane-ADC sample the input,  $x_{IN}(t)$ , at the same moment. However, due to various sources of timing error (discussed in Chapter-2) the sampling instance of main lane-ADC is shifted by  $\Delta t$ . The goal of the timing calibration loop is to precisely detect this shift and compensate for it. The output of main lane ADC, y(t), and the output of reference lane ADC,  $y_R(t)$ , can be written

Figure 3-1: Error signal computation using a reference lane for timing error estimation.

as,

$$y_{1}(t) = x_{IN}(t_{1} + \Delta t) = x_{IN}(t_{1}) + \Delta v_{TE}$$

$$y_{R}(t) = x_{IN}(t_{1})$$

(3-1)

where,  $\Delta v_{TE}$  is given by eqn.(2-3) in Chapter-2. The error signal, defined as the difference between the main lane and the reference ADC outputs, can be obtained from eqn.(3-2) as,

$$e = y_1 - y_R = \Delta v_{TE} = \left(\frac{dx_{IN}(t)}{dt}\right) \cdot \Delta t \tag{3-2}$$

$$= D \cdot \Delta t \quad \text{where, } D = \frac{dx_{IN}(t)}{dt}$$

(3-3)

Calibration loop can correct  $\Delta t$  if its value is known. However, as shown by eqn.(3-3), the error signal, e, not only depends on  $\Delta t$  but also on the derivative of the input signal. Hence, along with the error signal, it is critical to estimate the derivative of the input signal. One brute force approach would be to compute derivative in the digital domain and use it along with eqn.(3-3) to estimate and correct  $\Delta t$  in one shot. Unfortunately, such digital computation should be very precise which requires considerable amount of hardware at operates at full sampling speed. This will incur heavy area and power penalty. For example, as argued in [29], to keep the error in derivative estimation below half LSB, a 10-bit ADC operating at 3GHz would at least need 20-tap FIR filter with floating-precision coefficients. Alternatively, the precision requirement on the computation of the input signal derivative can be relaxed if a feedback loop is employed which tunes some analog knob (e.g. the sampling clock edges) to minimize  $\Delta t$ . In this case the precision of the input signal derivative should be just good enough to ensure that the loop converges. As shown in fig.(3-2), a derivative of the input signal can be easily estimated by using an additional reference lane whose input is delayed by a fixed fraction  $t_D$ . The value of the delay element  $t_D$  is not required to be known accurately as long as it stays constant with input amplitude and frequency. However, to keep the timing error detection accuracy intact for the input frequencies close to Nyquist frequency, the maximum input frequency should be much smaller than  $1/t_D$ . The delay element,  $t_D$ , can be implemented either in the input signal path or in the clock path. In the input signal path, it can be implemented by inserting a small series resistor. As the track bandwidth is the product of sampling capacitor and ON resistance of sampling switch,

**Figure 3-2:** Estimation of input signal derivative by using additional reference lane with delayed input.

adding a series resistor will effectively change the track-bandwidth thereby implementing the required delay  $t_D$ . Unfortunately, as this series resistor is in the input signal path, it would inevitably contribute to the noise and distortion performance of the ADC. On the other hand, inserting  $t_D$  in the clock path would simply mean delaying the sampling clock edges which can be done by adding a capacitive-D/A converter at the output of the clock buffer.

However, sometimes having an additional reference lane for estimating a derivative can pose considerable overhead (e.g. when small interleaving factors are used). Hence, it would be convenient if the derivative can be obtained by using succeeding interleaved lanes whose clock edge is one sampling period delayed. For example, as shown in fig.(3-2), the derivative of the input signal can be obtained by using the output of  $ADC_M$  instead of using a dedicated REF-2 lane. Both of these approach would yield exactly the same result if the delay element  $t_D$  is chosen to be one sampling sampling period  $T_S$ . The difference is that the method of using one of the interleaved lanes would have low estimation error when the input frequencies are much below the Nyquist frequency. For higher input frequency the estimate of the derivative gets much worse. In fact, if the calibration loop uses this method for derivative estimation then it can work only for input frequencies smaller than the Nyquist frequency [29]. Whereas, when the derivative is estimated using an additional REF-2 lane, the criteria to be ensured is that the maximum input frequency is much smaller than  $1/t_D$ . Thus, the method of using additional REF-2 lane is more robust and accurate. Hence, it is preferred for detecting timing errors in this thesis.

Figure 3-3: Block diagram of timing calibration loop using two reference lane-ADCs.

### **3-2 Description of Calibration Loop**