# Performance modeling of PageRank in large-scale systems

A case study

N.A. Doekemeijer

# Performance modeling of PageRank in large-scale systems

# A case study

by

N.A. Doekemeijer

submitted in partial fulfillment of the requirements for the degree of

#### **MASTER OF SCIENCE**

in

#### COMPUTER SCIENCE.

#### **Abstract**

Graphs are a ubiquitous concept used for modeling entities and their relationships. Large graphs, present in a variety of domains, are often fundamentally difficult to process because of sheer size and irregular computation structure. In recent years, both academia and industry have committed to designing scalable solutions to efficiently process these graphs.

Next to processing large datasets in a distributed environment, a relatively new trend is to accelerate single node computation performance using heterogeneous platforms (for example, by leveraging the GPU as well as the CPU). However, the structure of the input graph can markedly influence the processing speed on a certain platform and it is unclear what would be the most efficient platform for execution given an input dataset.

In this thesis, we will analyze the performance of multiple PageRank implementations for diverse platforms. Using implementations for CPU (using OMP), GPU (using OpenCL and CUDA), and heterogeneous environments (using StarPU and MPI), we will characterize platform performance in relation to the structure of the input dataset. Finally, we will propose and evaluate a performance model for PageRank that takes into account traits of the input graph.

Student number: 4103890

Public Defence: August 26, 2020

Thesis committee: prof. dr. ir. H. J. Sips (chair)

dr. ir. A. L. Varbanescu (supervisor)

dr. ir. P. Pawełczak dr. ir. J. Hidders Delft University of Technology University of Amsterdam

Delft University of Technology Birkbeck University of London

An electronic version of this thesis is available at

https://repository.tudelft.nl/.

## **Preface**

With this thesis, my time at TU Delft comes to an end. Over the years, I've had the privilege to meet, learn from, and work with a lot of talented people. I want to thank a few people in particular.

First, I want to thank Ana Lucia Varbanescu, my supervisor, for her guidance and support throughout the years. You are a great inspiration and I'm glad that we were able complete this thesis at long last.

Second, I want to thank Ernst van der Hoeven and Hans van den Bogert for their enjoyable company and thoughtful insights. You have made my time working in the Distributed Systems department a memorable experience. Similarly, I want to thank Elric, Laurens, Laurent, Maria, Martijn, Nir, Otto, Paul, Rob, Steffan, Wing, and everyone else from *MSc Lab 7.240*.

Finally, I want to thank my family for their endless love, support, and patience.

Niels Doekemeijer Delft, August 14, 2020

# Contents

| 1 | 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Problem Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1<br>2<br>2<br>3<br>4                                                                  |

|---|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 2 | Bac<br>2.1<br>2.2<br>2.3<br>2.4 | kground and Related Work Graph Theory                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>5</b> 6 8 9                                                                         |

| 3 | Desi<br>3.1<br>3.2<br>3.3       | Methodology Graph-Processing Considerations 3.2.1 Timing Model 3.2.2 Execution Model 3.2.3 Communication Model 3.2.4 Data Partitioning Platform Considerations 3.3.1 CPU Traits 3.3.2 GPU Traits 3.3.3 Heterogeneous Environments Design and Implementation of Parallel PageRank 3.4.1 Data Representation for Graph Topology 3.4.2 Data Representation for Computational State 3.4.3 Data Partitioning 3.4.4 Computation Kernels 3.4.5 CPU Implementations 3.4.6 GPU Implementations | 11<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>17<br>18<br>19<br>20<br>21<br>22<br>23 |

|   | 3.5                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 24                                                                                     |

| 4 | 4.1<br>4.2<br>4.3               | Methodology Datasets 4.2.1 Synthetic Graphs 4.2.2 Real-world Graphs Kernel Performance 4.3.1 Graph Difficulty 4.3.2 Workload 4.3.3 Hardware Cache                                                                                                                                                                                                                                                                                                                                     | 28<br>30<br>31<br>32<br>33<br>35                                                       |

|   | 4.4                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 36<br>37                                                                               |

|   | 4.5                             | Performance Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 38                                                                                     |

|   | 46                              | Main Findings                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 39                                                                                     |

vi Contents

| 5   | 5.1<br>5.2 | Methodology            | 42<br>42<br>43<br>44<br>45 |

|-----|------------|------------------------|----------------------------|

|     |            | 5.3.1 Execution Stages | 47<br>48                   |

| 6   | 6.1        |                        | <b>51</b><br>51<br>52      |

| Ril | olioai     | ranhy                  | 55                         |

1

## Introduction

Graph theory provides an abstract model for entities and their relationships in the form of graphs. Formally, a graph (or network) consists of a set of vertices (entities) and a set of edges (links that connect vertices). In many fields of science, this system is used to model information. For example, the Internet is a collection of web pages connected by hyperlinks. A social network is a graph of people connected by friendship. The brain is a network of neurons. Transport networks, food webs, metabolic pathways can all be intuitively mapped to a graph representation.

Recent examples of hot research topics related to graph theory and graph processing are data mining, machine learning, and pattern recognition [43]. In these domains, one of the main challenges is the sheer size and velocity of input data. Early in 2011, the number of active Facebook users was 721 million with 68.7 billion friendship edges between them [57]. In 2020, the number of active users has grown to 2.6 billion [18]. The largest publicly available hyperlink graph of the World Wide Web, extracted from a crawl in 2012, contains over 3.5 billion pages and 128.7 billion links [46].

In computer science, time and space are two dimensions of a fundamental tradeoff; efficiently processing large quantities of data is an inherently difficult challenge (if data is stored compressed, it takes less space, but access time increases). One way to efficiently process the increasingly large datasets, is by distributing work over multiple processing units. However, this makes the design and implementation of graph-processing systems much more difficult.

In general, graph computations are data-driven [30, 41, 42]. This, in combination with the irregular structure of graphs, leads to a poor data locality and a varying degree of parallelism. While low-level implementations of graph algorithms allow for specific architectural and algorithmic optimization, they are subject to substantial (repeated) implementation effort. For example, loading a large graph dataset into memory, selecting optimal data structures, and implementing basic (but efficient) graph iteration are non-trivial tasks shared by most graph processing implementations. To speed up processing, it can be interesting to use accelerators in a system or distribute workload over a cluster. This brings extra challenges regarding synchronization, data consistency, and reliability. Again, non-trivial effort that would have to be repeated for each low-level implementation.

General-purpose large-scale batch processing frameworks such as MapReduce [13] and Spark [64] provide a certain level of abstraction (for fault tolerance, coordination, par-

2 1. Introduction

allelism, etc.), but are not optimized for working with graph data and graph algorithms. Representing graphs and graph algorithms still requires a substantial implementation effort [48], which resulted in specialized graph-processing frameworks built on top of general-purpose frameworks ([31, 32, 49, 63]). Google, the organization that introduced MapReduce in 2004, recognized that existing general-purpose systems were ill-suited for graph processing and introduced Pregel [44] in 2010, a framework for graph processing that increases performance and usability compared to general systems.

Next to processing large datasets in a distributed environment, accelerating single node computation performance using heterogeneous platforms is a promising trend. However, because processing large-scale graphs involves data-driven computations, performance characteristics differ per system architecture and graph topology. So far, there has been little effort to model these performance characteristics for graph algorithms on heterogeneous architectures. A lot of (future) graph-processing frameworks would benefit from relying on such models to improve workload distribution that matches nodes' capabilities.

In this work, we present a case study of multiple implementations of one graph algorithm for a variety of architectures, in order to model performance and guide workload distribution between processors in heterogeneous environments. For this case study, we have decided to use PageRank [50] as main subject. By its nature, PageRank is a memory-intensive algorithm, which makes it interesting for investigating the influence of graph topology on performance.

#### 1.1. Problem Statement

Due to the abundance of present-day graph computing problems and the ever-growing volume and velocity of data acquisition, academia and industry have committed a significant amount of effort into simplifying large-scale graph processing. For an extensive overview and comparison of over 80 large-scale graph frameworks released in recent years, we refer the reader to a survey by the authors [14].

The compelling next step, one that few frameworks have made so far, is to efficiently exploit an environment with heterogeneous processing capabilities. Hardware and memory topology does not have to be uniform in a cluster; some machines may have a newer generation of hardware, hardware with different processing capabilities, or some machines may be better connected than others. For example, Surfer[9] tries to partition the input graph based on available bandwidth between machines, while TOTEM[23] processes high-degree vertices on the CPU and offloads the low-degree vertices to the GPU.

In order to better guide the distribution of tasks and data between workers in a heterogeneous environment, more research is needed. Ideally, we would like to be able to predict the performance of a given workload and select the best computing infrastructure. However, the data-driven nature of graph computations, and varying topologies of graph datasets make this a non-trivial problem.

#### 1.2. Research Questions

The main goal of this work is to provide models to support the distribution of a graph-processing workload in a large-scale heterogeneous system. This thesis proposes a three-stage research process driven by the following research questions:

**RQ1** How to evaluate the graph-processing performance characteristics of a processing unit?

In a heterogeneous environment, it is unclear what would be the best allocation of resources to optimally process a given graph-processing workload. To this

1.3. Approach 3

end, we need to evaluate the performance characteristics of a processing unit in order to characterize and compare computing devices. Moreover, we must understand and characterize the performance impact of dataset properties, in the context of vertex-centric graph processing, on device performance.

**RQ2** How to model the graph-processing performance of a processing unit with respect to dataset topology?

The data-driven aspect of graph computations adds a layer of complexity when modeling performance in graph-processing systems. Therefore, we must identify the graph metrics that indicate complexity, and assess to what degree they correlate to processing performance. Finally, the goal is to model the *graph-processing performance* of a processing unit with respect to a dataset topology, in order to more accurately predict its performance for a given workload.

**RQ3** How to take into account the graph-processing performance characteristics of each processing unit in a heterogeneous system when distributing a workload?

The optimal composition of heterogeneous devices might differ depending on the graph-processing workload. In some cases, it might even be beneficial to use a single device over a composition of devices. To maximize performance, we must understand how to use the graph-processing performance characteristics of each processing unit in a heterogeneous system to effectively distribute a graph-processing workload.

#### 1.3. Approach

Addressing RQ1, we outline the general design decisions for graph-processing frameworks and propose a structural benchmarking method that determines the relative performance impact of each decision. Following this approach, we use PageRank as example algorithm for an in-depth case study of graph-processing performance on the CPU and the GPU.

Using a mix of real-world and synthetic datasets, we benchmark 20 custom PageR-ank kernels with gradually varying design decisions to evaluate the impact of each design decision. Addressing RQ2, we work towards modeling the kernel performance by determining the main performance indicators and correlating these to topological graph metrics of the input dataset.

Finally, addressing RQ3, we benchmark our kernels in a controlled heterogeneous setting and determine the speedup after expanding system resources. We relate this to our earlier findings and work towards systematically optimizing a workload distribution guided by the graph-processing performance characteristics of each processing unit in a heterogeneous system.

#### 1.4. Main Contributions

The main contributions of this thesis are:

- C1. (Conceptual) A structural benchmarking strategy aimed at measuring the impact of each design decision in a graph-processing framework.

- C2. (Experimental) An in-depth evaluation of graph-processing performance characteristics of CPUs and GPUs using a PageRank case-study.

- C3. (Experimental) A definition and evaluation of a graph-processing performance model that takes into account the topological structure of an input dataset.

4 1. Introduction

C4. (Experimental) An in-depth evaluation of graph processing scalability in a heterogeneous environment using a PageRank case-study.

- C5. (Software Artifact) 20 PageRank kernels with varying graph processing design decisions for CPU and GPU devices. 10 additional PageRank kernels specifically targeting heterogeneous environments.

- C6. (Software Artifact) A benchmarking suite that facilitates structurally measuring the graph-processing performance characteristics of devices in a heterogeneous environment.

#### 1.5. Document Structure

The remainder of this document is organized as follows. Chapter 2 briefly discusses the main concepts and related work. We provide a succinct introduction to graph theory and graph computing and define relevant terminology before discussing how this work relates to previous work. Chapter 3 addresses RQ1 and proposes a structural benchmarking method. Using this method, we design multiple PageRank kernels targeting various platforms. Chapters 4 and 5 study the performance of these kernels and address RQ2 and RQ3 respectively; chapter 4 proposes and evaluates a device performance model, chapter 5 evaluates performance and scalability in a heterogeneous setting. Finally, chapter 6 concludes this thesis and proposes directions for future work.

To readers who are interested in our main performance findings, we recommend reading sections 4.6 and 5.5. An overview of PageRank kernels is available in section 3.5. To readers who are interested in performance modeling, we recommend reading sections 4.5 and 5.4. To readers who want to learn more about our benchmarking suite, we recommend reading chapter 3 and sections 4.1 and 4.2.

# Background and Related Work

In this chapter we introduce the main concepts needed to understand the remainder of this work. Moreover, we provide a brief overview of related work, specifically focusing on workload distribution in heterogeneous systems.

#### 2.1. Graph Theory

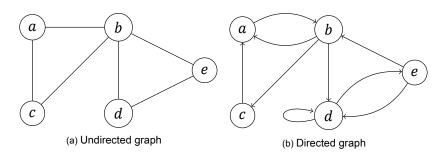

Graph theory provides an abstract model for entities and their relationships in the form graphs. Formally, a graph (or network) consists of a set of *vertices* (entities) and a set of *edges* (links that pair vertices). Simply said, graph theory is the study of points and lines. Figure 2.1 illustrates the common way of visualizing graph data, with letters denoting vertices.

Figure 2.1: Common way of representing undirected (2.1a) and directed (2.1b) graphs.

Edges may be directed or undirected. Undirected edges indicate a two-way relationship, which means that the edge can be traversed in both directions (e.g., a collaboration graph). Directed edges represent a one-way relationship and can only be traversed in one direction (e.g., a citation graph). As undirected graphs can be simply mapped to a directed equivalent (by replacing each undirected edge with two directed edges), working with directed graphs for algorithms, proofs, and computation frameworks is more common.

We refer to the number of edges directly connected to a vertex as the vertex degree. For directed graphs, we can further distinguish between incoming and outgoing degree. The degree distribution models the probability that a selected vertex has exactly a given number of edges.

Graph topology refers to the arrangement of nodes and edges. Some examples of regular arrangements are: a mesh (every vertex is connected to every other vertex), a star (every vertex has a single edge towards the center vertex), or a ring (every vertex has a single edge towards the next vertex). However, most real-world networks do not follow a regular pattern and have a non-trivial topology, these networks are often referred to as Complex Networks.

#### 2.2. Complex Networks

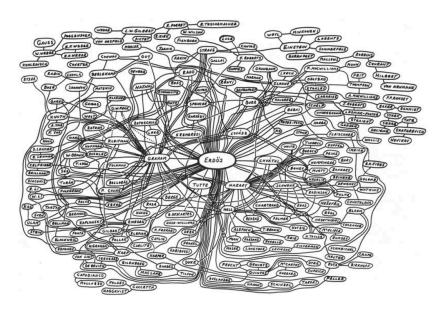

This section will briefly introduce complex networks, for a more extensive introduction the reader is referred to Wang and Chen [59]. In graph theory, a complex network is a graph with non-trivial topology, often observed in networks and models based on real-world phenomena. Among mathematicians, a well-known example of such a network is the Erdős collaboration graph (figure 2.2). It indicates the relation between authors of mathematical publications and their "collaboration distance" to Paul Erdős [28] (an influential mathematician who, among a broad number of other fields, contributed to graph theory).

Figure 2.2: Illustration of a small part of the Erdős collaboration graph. The original dataset tracks over 400,000 authors. Courtesy of Easley and Kleinberg [15].

The Erdős collaboration graph has some properties that are typical of real-world networks. For example, while the average number of collaborators is 3, there is a small amount of authors that greatly exceed this number (e.g., Erdős himself has directly collaborated with over 500 people). The distribution of edges indicates a preferential attachment towards a small amount of authors. Next to that, the median path length between any two authors is very short. Even though the dataset consists of over 400,000 authors, the longest path is only 26 hops. These are phenomenons not seen in random graphs, where each possible edge between any two vertices has the same probability of existing.

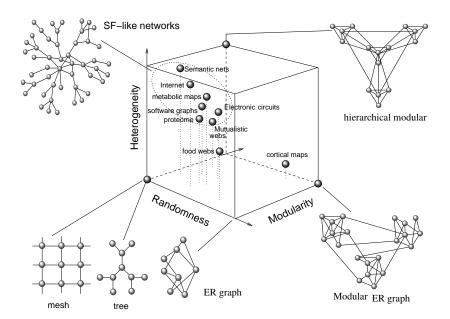

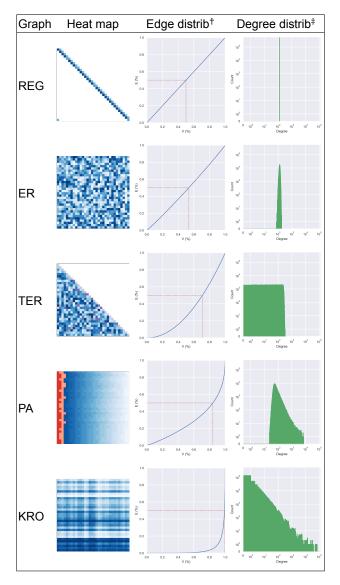

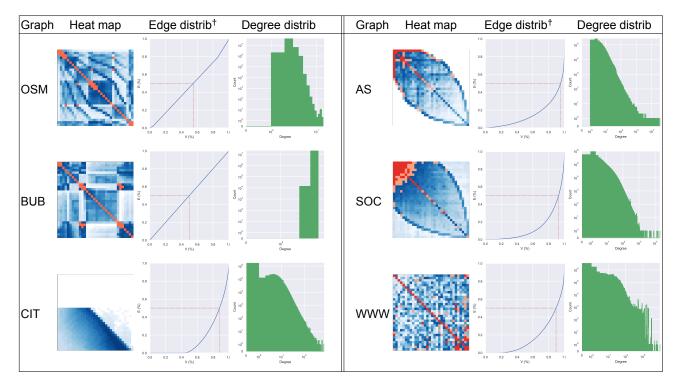

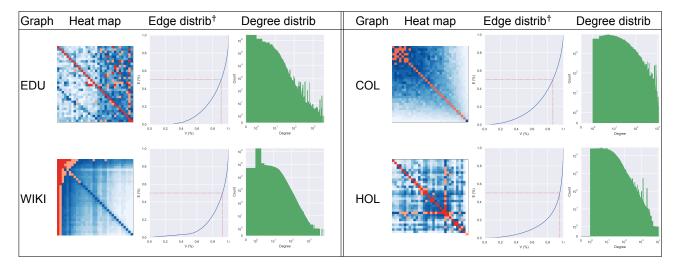

Solé and Valverde [55] present a way of classifying graph topologies based on randomness, heterogeneity and modularity (figure 2.3). The authors note that most real-world complex networks can be characterized as highly heterogeneous, irregular, hierarchical graphs.

Figure 2.3: Zoo of complex networks. A classification of several graph types based on randomness, heterogeneity and modularity. Courtesy of Solé and Valverde [55].

The randomness dimension illustrates how much randomness is involved in modeling the network. This is done by comparing how similar the graph and its characteristics are to a uniformly random edge distribution of the same size. The Erdős–Rényi (ER) model [17], on the end of this axis, is used to model fully random graphs. The model dictates that for a set of vertices, there exists an edge between any two vertices with a given probability.

Graph heterogeneity distinguishes between degree distributions; a homogeneous distribution evenly scatters all edges among the vertices (such as with the Erdős–Rényi model), while in a heterogeneous distribution some vertices have a degree that significantly differs from the average. For heterogeneous graphs, preferential attachment causes a few hubs to be connected to most of the edges, which causes a power-law degree distribution. These networks are called scale-free (SF) networks and can be recognized by fitting a power-law function (or fitting a linear function on logarithmic axes).

From degree distribution alone, it is difficult to observe graph modularity. Graph modularity refers to the extent to which vertices can be divided into separate clusters (modules), where connectivity with vertices within the cluster is considerably stronger than to those in other clusters. The average local clustering coefficient can be used to quantify graph modularity. For each vertex, this coefficient is given by the proportion of links between the vertices within its neighborhood divided by the number of links that could possibly exist between them.

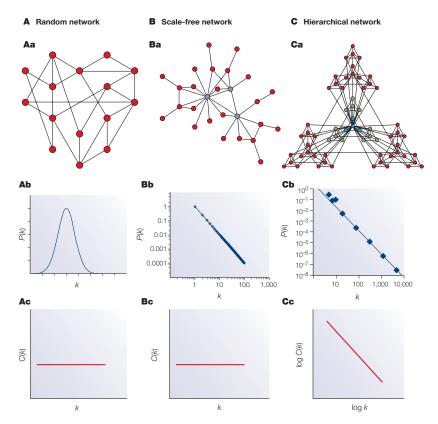

Figure 2.4 compares the degree distribution and clustering coefficient of three graphs of different heterogeneity and modularity and shows that degree distribution and average clustering coefficient vary accordingly. The clustering coefficient chart Cc implies that the low-degree nodes belong to very dense sub-graphs and, combined with chart Cb, we can observe that those sub-graphs are connected to each other through hubs.

The Erdős collaboration graph is an example of a scale-free real-world complex network. In this graph, most authors are connected via a short path even though no direct edge exists between the two. It also has a high clustering coefficient (significantly higher

Figure 2.4: Comparison of (a) topology, (b) degree distribution, and (c) average clustering coefficient for (A) a random network, (B) a scale-free network, and (C) a hierarchical scale-free network. Note the logarithmic scales in Bb, Cb, Cc. Courtesy of Barabasi and Oltvai [5].

than its corresponding random graph), which means there is a tendency to form communities (for example, authors from the same department). Combined, these two characteristics are referred to as the small-world effect.

Watts and Strogatz [60] show that many real-world graphs exhibit the small-world effect and that this class of graphs should be classified somewhere between regular and random. Regular meshes are clustered, but have a high average path length. Random graphs have a short average path length, but do not show clustering.

The highly heterogeneous, irregular structure of complex networks make them inherently difficult to process efficiently in parallel. As graph algorithms are often data-driven, a scale-free degree distribution makes load-balancing difficult. On top of that, realizing a minimum graph cut with equal-sized subsets is an NP-complete problem [21], so partitioning to minimize communication is non-trivial as well.

## 2.3. PageRank

PageRank [50], named after its author, is a well known graph algorithm and is often used for demonstrating and testing graph-processing frameworks [14]. Although several accuracy and performance improvements have been proposed for the algorithm, we focus on the original algorithm as we are more concerned with the fundamental graph-processing challenges it exhibits than the actual output.

Traditionally meant for estimating the relative importance of a web page based on the number and quality of incoming hyperlinks, PageRank has proven its worth in more 2.4. Related Work 9

general settings as well (e.g., researcher impact, spam detection and trust networks [25]). As computation considers an entire dataset at once, it is a primary example of offline graph analytics. Contrary to online graph analytics (or graph querying), which desires fast response times, emphasis lays on high throughput.

Equation (2.1) shows the function for calculating the rank of a single vertex. V refers to the set of vertices,  $E_{in}(x)$  refers to the set of vertices that have an edge pointed towards vertex x, and  $D_{out}(x)$  refers to the degree of outgoing edges for vertex x.

$$PR(v_i, s) = \frac{1 - d}{|V|} + d \times \sum_{w_i \in E_{in}(v_i)} \frac{PR(w_i, s - 1)}{D_{out}(w_i)}$$

(2.1)

This equation models a *random surfer*; a visitor randomly following links on every visited page. For every page, the resulting rank represents the likelihood that any random surfer ends up on that particular page. In that sense, PageRank outputs a probability distribution where a higher value represents a more dominant (important) page. Each rank will have a value between 0 and 1 and the sum of all ranks equals 1. The damping factor *d* represents the chance that the random surfer will keep on following links. When no link is followed, surfing is assumed to continue on any other page.

Although the algorithm is simple in terms of theoretical description, PageRank exhibits one of the intrinsic challenges of graph processing well: computation is data-driven and parallelization is non-trivial. A second intrinsic challenge is the recursive nature of the equation. To practically approximate the result, evaluation ensues in iterations until the result converges.

We implement and study multiple PageRank implementations in order to gain insight into the graph-processing performance characteristics of different architectures. By its nature, PageRank is a more memory-intensive than computation-intensive algorithm, which makes it interesting for investigation of the influence of graph topology on performance. In essence, it can be regarded as the composition of two graph-processing building blocks: per vertex iteration over neighboring edges (information propagation) and a global reduction over all vertices (rank update and stop condition).

#### 2.4. Related Work

With the Bulk Synchronous Parallel (BSP) paradigm, Valiant [58] introduced a simple model for designing and analyzing parallel systems. Key of the paradigm is that computation and communication proceed in synchronized iterations, referred to as supersteps. Cost of a superstep can then be determined using the sum of computation cost, communication cost, and the cost of a global barrier.

Williams and Parsons [61] recognize that BSP is not sufficient for heterogeneous parallel systems since it assumes all components have equal computation and communication abilities. The authors extend the model and introduce the Heterogeneous Bulk Synchronous Parallel (HBSP) framework.

HBSP takes into account the relative speed, bandwidth, and latency between all available components in a system. The concept of supersteps remains similar, but the cost calculation becomes a little more complex. In essence, it is the cost of the slowest worker (straggler) that determines the final cost, and the goal is to find a workload distribution that minimizes the final cost. BSP and HBSP abstractions can be used to reason about parallel graph-processing systems, but actual performance models will depend on (and vary between) algorithms and their implementations.

Using a simple BSP-based performance model for heterogeneous graph processing, Gharaibeh et al. [22] demonstrate that, theoretically, GPUs can be used to accelerate parallel graph applications. The relative computing power between processors is expressed through edges per second and communication is expressed through the number of partition-crossing edges (assumed to be an upper-bounded percentage of the number of total edges). In their demonstration, the authors use theoretical bounds of today's platforms for processing rates, memory space, and communication cost to show offloading 30% of a graph to the GPU can result in a theoretical speedup of up to  $\sim\!1.35\times$  for a reasonably sized dataset.

The authors also introduce a heterogeneous graph-processing framework called TOTEM that offloads part of the dataset to the GPU. The framework is used to verify the theoretical performance model (for PageRank and Breadth-First-Search) and demonstrate the real-world potential of GPUs as accelerators for graph processing. Dataset partitioning is done based on vertex degree; the (few) high-degree vertices are processed on the CPU, while the many low-degree nodes are offloaded to the GPU under the assumption that the GPU can process these more efficiently.

The performance model introduced by Gharaibeh et al. [22] shows potential, but ignores some graph-processing complexities in exchange for model simplicity. For example, the model assumes that the processing rate for a processor is constant and can be determined by a benchmark independent of the graph characteristics of the actual workload. In this work (inspired by the HBSP abstraction) we generalize and extend TOTEM's heterogeneous performance model to take into account the usage of multiple accelerators, as well as the graph characteristics of the dataset.

With StarPU, Augonnet et al. [1] take a more top-down approach to try and solve the problem of optimally scheduling tasks inside a heterogeneous system. Instead of working with performance models designed beforehand for the algorithm and datasets at hand, the StarPU framework provides a "black-box" task scheduler that uses execution heuristics from previous runs. In some cases, the authors note a speedup in a hybrid system that exceeds the sum of speed of the individual elements (because of the distribution of tasks with respect to the strengths of each processing unit). Currently, these scheduling heuristics are only based on the kernel, execution unit, and task size, which has proven not to be sufficient for graph processing. Our work focuses on finding better heuristics, such that future heterogeneous schedulers can also benefit graph algorithms.

# **Design and Implementation**

In this chapter, we address RQ1: how to evaluate the graph-processing performance characteristics of a processing unit? To this end, section 3.1 proposes a novel benchmarking methodology on the basis of a PageRank case-study. Sections 3.2 and 3.3 discuss the design principles for such a benchmark.

Section 3.4 elaborates on implementation and describes each of our benchmark kernels in detail. Finally, section 3.5 provides an overview and succinctly lists all kernels.

#### 3.1. Methodology

PageRank is a graph algorithm that is composed of two graph-processing building blocks: per-vertex iteration over neighboring edges (information propagation), and a global reduction over all vertices (rank update and stop condition). The actual computation is relatively simple, which makes PageRank well-suited to analyze the influence of graph topology on performance.

A lot of general-purpose graph-processing frameworks offer users a higher-level programming interface to implement graph applications. The "think like a vertex" (*TLAV*) paradigm (also referred to as *vertex-centric*), as introduced with the Pregel framework by Malewicz et al. [44], limits the scope of computation to a single vertex, thereby allowing fine-grained parallelization. As shown in the original paper, PageRank is one of the algorithms that maps elegantly to this model (algorithm 1 displays a simplified representation; note that Pregel does not allow for global gather/scatter operations, so a prefixed number of iterations coordinates the stop condition).

#### Algorithm 1 Pseudocode for Pregel's Vertex-Centric PageRank

```

function ComputeVertexPageRank(M:Messages)

Vertex.Value \leftarrow \frac{1-d}{|V|} + d \times Sum(M)

if SuperStep < 30 then

for all \ w_i \in Vertex.OutEdges \ do

SendMessage(w_i, \frac{Vertex.Value}{Vertex.OutDegree})

end for

else

VoteHalt()

end if

end function

```

Each iteration and for every vertex, the ComputeVertexPageRank program is scheduled for execution. Communication between vertices is message-based and synchronized (i.e., all messages sent at iteration i are processed in iteration i+1). This methodology of a conceptually parallel bulk execution of vertex-programs, followed by a global synchronization step between iterations (*supersteps*), derives from the Bulk Synchronous Parallel (BSP) parallelization pattern [58].

Nguyen et al. [49] show that, even though the higher-level programming interfaces are similar (i.e., vertex-centric), performance varies greatly between graph-processing frameworks, and the framework achieving the lowest runtime changes depending on the input dataset. Moreover, frameworks also diverge in their APIs and optimization strategies: a more restricted API allows for more lower-level framework optimizations that target data structures, data transfer, and task scheduling [14]. In order to compare hardware platforms on equal footing and in a structured manner, we propose the use of straightforward in-house PageRank kernel implementations with gradually varying design decisions. To allow for a certain extent of generalization, implementations should follow patterns generic to graph processing. Section 3.2 elaborates on the requirements and design decisions made regarding this aspect.

Next to "traditional" (multi-core) CPUs, we take GPUs into account. In big-data processing applications, GPUs are very often used as platform for offloading computation. In graph processing, too, the platform has proven its potential ([20, 23, 34, 67]). However, due to the intrinsic graph-processing challenges, implementing graph algorithms for the GPU is significantly more challenging. Section 3.3 discusses how the benchmark kernels should address the traits and implementation objectives per platform, as well as the challenges of heterogeneous environments, where a set of independent processors is exploited (e.g., exploiting distributed CPUs in a cluster or exploiting both the CPU and GPU on a single node).

#### 3.2. Graph-Processing Considerations

McCune et al. [45] define TLAV-frameworks as software that supports iterative execution of user-defined vertex-programs over vertices of a graph. The authors identify four principle design decisions (interdependent *pillars*) that dictate how programs execute and utilize the underlying hardware: Timing, Communication, Execution Model, and Partitioning. However, the performance implications of different decisions for these components are unclear.

This section discusses, per graph-processing pillar, the requirements and design decisions (and subsequent implications) for our benchmark kernels. First, section 3.2.1 (Timing Model) elaborates on how vertex calculations are scheduled for execution. Section 3.2.2 (Execution Model) explains the decisions made regarding abstraction level and data flow. Section 3.2.3 (Communication Model) considers how program data is shared between entities. Finally, section 3.2.4 (Data Partitioning) focuses on the distribution of input data among workers.

#### 3.2.1. Timing Model

The timing model portrays how vertices are ordered by the scheduler for computation. In the traditional BSP model, all entities are executed (conceptually, in parallel) in supersteps with a global synchronization barrier between supersteps. Computation follows a deterministic pattern, where calculation is performed on data from the previous iteration, and updates are exchanged between iterations. Per iteration, vertices can be scheduled in any (random) order, as the execution order does not affect the state of the program. This is the synchronous timing model.

Alternatively, the asynchronous timing model discards a global iteration barrier, allow-

ing calculations to be performed on most recent data. In synchronous execution, each superstep takes as long as the computation time for the slowest vertex (also known as the *straggler* problem). For asynchronous execution, vertex execution order can be dynamically reorganized by the scheduler, which helps counter the problem of imbalanced workloads.

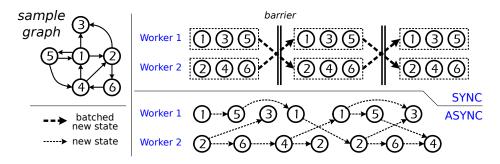

Figure 3.1 depicts the difference in execution flow for synchronous (upper part of the figure) and asynchronous timing models (lower part). Asynchronous execution shows more fine-grained synchronization without a global barrier. States update immediately and execution order is not fixed.

Figure 3.1: Visualization of the different execution flows for synchronous (upper part of the figure) and asynchronous timing models (lower part). Courtesy of Xie et al. [62].

PageRank is an algorithm with a high communication-to-computation ratio, which means it can benefit from optimizations to communication [62]. For synchronous implementations, communication patterns are predictable, so throughput can be improved through batch operations. Next to that, the nondeterministic nature of asynchronous execution makes performance modeling more difficult, so we restrict to implementing a **synchronous timing model**. We also assume all vertices to stay active during execution, as opposed to more intricate techniques that feature early termination for vertices that remain inactive ([40, 65]).

#### 3.2.2. Execution Model

McCune et al. [45] define a framework's execution model as the style of algorithm implementation and flow of data. The authors differentiate between models using the number of distinct computation phases; instead of the single computation function used by Pregel (algorithm 1), a more general description of PageRank — using the Scatter-Gather model [52, 53, 56] (two phases) — would be: (1) summation of partial rank based on iteration over edges; (2) vertex rank update based on iteration over vertices.

The flow of data between vertex-programs can be characterized as either *push* or *pull*. In a push style flow, information flows from a vertex to its neighbors (for example, Pregel's message-based abstraction naturally maps to a push-based information flow). In a pull style flow, information flows in the reverse direction: a vertex reads data directly from its neighbors. Algorithm 2 illustrates a pull-based variant of algorithm 1.

Implementations are markedly different depending on the chosen execution model (e.g., several typical data structures for topology map to different execution models — see section 3.4.1). As it is unclear how these decisions impact performance [14, 49], we have decided to develop multiple benchmark kernels with different model parameters: both the **push** and the **pull** data flows are taken into account.

#### Algorithm 2 Pseudocode for pull-based Vertex-Centric PageRank

```

function ComputeVertexPageRank if SuperStep < 30 then sum \leftarrow 0 for all Neighbor \in Vertex.InEdges do sum \leftarrow sum + \frac{Neighbor.Value}{Neighbor.OutDegree} end for Vertex.Value \leftarrow \frac{1-d}{|V|} + d \times sum else VoteHalt() end if end function

```

#### 3.2.3. Communication Model

Parallel systems generally distinguish between two models of communication: shared-memory and message-passing. Although both models can emulate each other, the implemented communication model usually depends on the target platform, which natively implies a model — i.e., global address space systems rely on shared-memory communication, while distributed-memory systems rely on message-passing communication. In our case, we target distributed-memory systems and thus rely on message-passing.

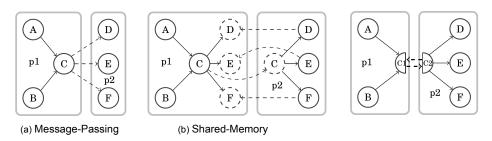

However, in terms of vertex-centric graph processing, the communication model defines the *abstraction* method for sharing information between vertex-programs. Figure 3.2 depicts the communication pattern between two workers for the message-passing and shared-memory abstractions. The vertices with dashed outline in figure 3.2b represent so-called *ghost-vertices*; one worker is assigned ownership of the vertex, while other workers use replicas that are synchronized after each iteration.

Figure 3.2: Comparison of TLAV communication models in distributed-memory systems for vertices (A–F) partitioned over two workers (p1–p2). Courtesy of McCune et al. [45].

Figure 3.3: Communication pattern with vertex-cut [45].

For PageRank, we use a **shared-memory** abstraction for two reasons. First, because pull-based information flow is only possible with this model. Second, because it allows for an optimized push-based information flow: message-passing with sender-side message aggregation (locally aggregate messages in a ghost-vertex, then globally aggregate the values of ghost-vertices in their respective origin — resulting in the communication pattern depicted in figure 3.3).

#### 3.2.4. Data Partitioning

Partitioning refers to the way in which data is divided between workers. Data volume is an intrinsic challenge of large-scale graph processing: the data exceeds the capacity of a single node, so a straightforward solution is to split the input over distributed memory. Traditionally, a good data distribution optimizes for equal processing time, while minimizing communication between workers. However, realizing a minimum graph cut with equal-sized subsets is an NP-complete problem [21]. In practice, with METIS[33] algorithms being the industrial standard [45], it is common to use pragmatic heuristics for graph partitioning. We use **METIS** as one of the methods for data partitioning.

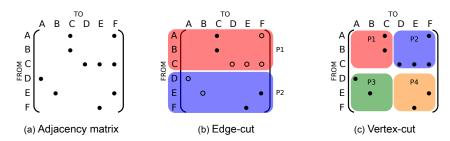

METIS provides *edge-cut* partitioning, i.e., nearly equal size clusters of disjoint vertices, while minimizing the number of edges that span clusters (see figure 3.2a). For graphs with a power-law degree distribution, this partitioning might result in unbalanced workloads due to the imbalance in number of edges between clusters [26]. To counter this, *vertex-cut* partitioning balances edges between clusters, while minimizing the number of vertices that span clusters (figure 3.3). Blocks are balanced based on vertex size.

Partitioning data with METIS is a time-intensive and memory-intensive preprocessing operation. For that reason, we also implement a streaming **block-based** partitioning method. Figure 3.4 illustrates the methodology: 3.4a depicts an example graph as adjacency matrix where non-empty entries represent edges, 3.4b displays a sample edge-cut partitioning (vertices A-C are placed on worker p1, D-F on p2), and 3.4c shows a sample vertex-cut partitioning (non-diagonal blocks work with replicas of vertices).

Figure 3.4: Visualization of block-based edge-cut and vertex-cut partitioning of an adjacency matrix. A dot in the adjacency matrix represents the existence of edge  $(row \rightarrow col)$ . In (b), a hollow dot represents an edge to another partition. In (c), non-diagonal blocks work with vertex replicas.

Note that this block-based partitioning method is naive, and does not approximate an optimal vertex-cut; blocks are simply balanced using the number of vertices. However, it does allow for more structured communication patterns, as the set of ghost-vertices is defined by the row and column of a block, thereby allowing utilization of (possibly optimized) data-broadcasting operations.

#### 3.3. Platform Considerations

This section elaborates on the design objectives, and the decisions we made, regarding our parallel PageRank implementations for different platforms. As discussed in section 3.1, we target (compositions of) CPU and GPU platforms. To take maximum advantage of a platform, it is important to take its hardware architecture and performance traits into account. Section 3.3.1 and section 3.3.2 discuss these traits for CPU and GPU, respectively, and section 3.3.3 considers the heterogeneous aggregation of platforms where computation or memory access capabilities are unbalanced between processors.

#### 3.3.1. CPU Traits

The parallelization technique used by multi-core CPU architectures can be classified as Multiple Instruction, Multiple Data (MIMD) under Flynn's taxonomy [19]. That is, different CPUs (cores) are working independently, and thus typically are executing different instructions and are accessing different memory locations at any given instant.

At the time of writing, modern commodity multi-core processors have up to 32 cores. Intel, in their guide to developing multi-threaded applications, recommend not using more software threads than the number of processing cores in the system [10]. For our application, this means that each software thread will execute a batch of vertex programs. To avoid false sharing, a cache consistency issue where two processors write to the same cache line, each thread should ideally write to consecutive block(s) of memory.

Nowadays, it is commonplace for multi-core CPUs to support SIMD instructions (Single Instruction, Multiple Data) in order to improve throughput for vector operations. Intel's Advanced Vector Extensions (AVX) instructions are able to process 256 bit registers. To benefit from these instructions, operations on consecutive memory are a prerequisite.

To summarize, the primary design objectives for graph processing on CPUs are: **limit the amount of threads** and operate on **consecutive blocks of memory** if possible.

#### 3.3.2. GPU Traits

Contrary to CPUs, which are designed to execute a limited amount of threads at once, GPUs focus on highly parallel applications by processing thousands of threads concurrently. GPUs possess many more execution units than CPUs, but generally operate on a lower frequency. Execution follows a Single Instruction, Multiple Data (SIMD) pattern: a group of threads (warp) is physically executed in parallel on cores of a streaming multiprocessor (SMP), one instruction per cycle per warp.

This SIMD model differs from the model offered by the CPU SIMD intrinsics described in section 3.3.1. NVIDIA labels their parallel programming model for GPUs as Single Instruction, Multiple Threads (SIMT) [38]. With SIMT, each core is assigned its own thread with a corresponding context, which means that, although the executed instruction is similar for all threads in a warp, context may vary (i.e., registers, memory access, or flow path). This enables parallel processing of constructs that cannot be expressed with CPU SIMD intrinsics, such as indirect memory access and execution of conditional branches.

Another architectural difference between GPUs and CPUs is the limited implementation of memory caches on GPUs. CPUs are optimized for minimal latency by utilizing large caches for, e.g., instruction pre-fetching, out-of-order execution, and operations on memory. GPUs are optimized for maximal throughput, and try to hide latency through heavy multi-threading. Whenever a warp is waiting for memory access, the hardware-based scheduler can switch execution to another warp (time-slicing principle). This encourages the use of a large number of light-weight threads, preferably a multiple of the number of cores in an SMP.

Grouping of threads into warps is not only relevant to computation, but also to memory loads and stores. The SMP is able to coalesce memory requests issued by threads of a warp into as few transactions as possible. A single memory transaction can address up to 128 bytes, so threads in a warp should ideally work with neighboring memory in order to maximize bandwidth efficiency [11].

Exploiting the full capacity of the GPU for parallel PageRank is non-trivial. For vertex-centric programs, one of the most important performance challenges is keeping all cores busy as much as possible (i.e., we aim for high core occupancy). Whenever threads in a warp diverge, for example through conditional branches or loops of unequal number of iterations, only a subset of the cores is able to execute their instruction. A straightforward vertex-centric application would map the computation of a single vertex to a single

**thread**, but data-driven computation (i.e., edge iteration) in combination with imbalanced input graphs (many real-world graphs exhibit power-law degree distributions) results in thread divergence and therefore low occupancy.

To increase (theoretical) occupancy, another way of parallelizing PageRank is to divide the work of **a single vertex program over a full warp**, so each core iterates over part of the vertex edges. As added benefit, this iteration pattern allows for memory coalescing over edge data as well as vertex data. However, this does add synchronization overhead and results in low occupancy when the input graph has a lower average degree than the number of threads in a warp.

Liu and Schmidt [39] propose a lightweight work distribution algorithm in order to further combat workload imbalance. By atomically increasing a counter, **each warp dynamically determines the vertices to be processed**. We implement all three methods of work distribution.

To summarize, a primary design objective is to operate on **consecutive memory blocks** as much as possible. Secondly, work should be split into a large number of light-weight threads that spread load equally among threads in a warp, in order to **keep core occupancy high** and maximize data throughput. Finally, a CPU manages the coordination and invocation of GPU programs (kernels) in a system, but it is idle during kernel execution. This opens opportunities for sharing the workload between the two devices, thereby using a heterogeneous computing paradigm.

#### 3.3.3. Heterogeneous Environments

Heterogeneous computing refers to the use of more than one kind of processor in a system, with the purpose of increasing performance or energy efficiency. We will refer to heterogeneous environments as environments with dissimilar processors (i.e., different clock speed or performance characteristics) or environments that exhibit Non-Uniform Memory Access (NUMA) characteristics (i.e., distributed CPUs or usage of external memory, where communication latency and bandwidth depends on location). For the sake of simplicity, we assume each independent processor to have an independent pool of local memory, and communication between separate processors to occur through message-passing.

Balancing workloads in heterogeneous environments is challenging, especially with data-driven computations such as PageRank and other graph-processing algorithms. In this regard, it is interesting to know the graph-processing performance characteristics of different platforms. With the ambition of defining these characteristics, we implement PageRank targeting only a CPU or a GPU, but also heterogeneous mixes, such as a **cluster** of multi-core CPUs and **CPU+GPU** on a single node.

As inter-worker communication is markedly more expensive than local memory operations (higher latency / lower bandwidth), a design objective for these implementations is to **optimize communication** between workers, for example, by combining messages and performing batch operations.

## 3.4. Design and Implementation of Parallel PageRank

Taking into account the design considerations from sections 3.2 and 3.3, this section will now discuss the design and implementation of our PageRank benchmark kernels. First, sections 3.4.1 to 3.4.3 explain the design and usage of data structures. Next, sections 3.4.5 to 3.4.7 explain implementation details for CPU, GPU, and heterogeneous platforms, respectively.

#### 3.4.1. Data Representation for Graph Topology

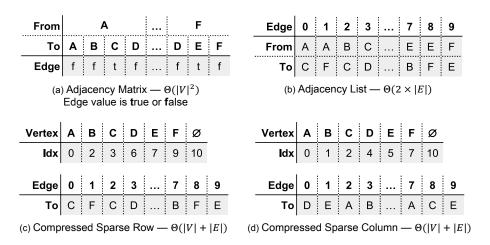

Effectively storing graph topology is one of the most important aspects of high-performance graph processing. Mapping unique vertex identifiers to ascending indices allows efficient storage of vertex data in vectors. Edge data, however, is less straightforward. Adjacency matrices (figure 3.4a) allow for efficient querying of vertex adjacency, but are memory-inefficient for sparse graphs (i.e., graphs with low average degree). The number of edges between two vertices is also limited to one per direction.

As real-world graphs are generally sparse, and PageRank performs edge iteration (rather than edge querying), data storage using adjacency matrices is not a viable option. Depending on the type of edge iteration, we prefer different data representations for topology. Following is the list of storage formats we use, with descriptions and use cases.

Figure 3.5: Partial memory layout for different graph topology representations of figure 3.4a with corresponding storage requirements.

#### **Adjacency List**

Storing edges in a list (dubbed *adjacency list*, figure 3.5b) prevents waste of memory and enables trivial edge iteration. Contrary to adjacency matrices, where vertex addition/removal is expensive as it requires a matrix resize, topology modification is relatively cheap.

However, performing vertex calculations through (the more fine-grained) concurrent iteration of edges requires synchronization before modifying vertex data (e.g., memory locks or atomic operations). Secondly, there is no easy way of finding and iterating over edges belonging to a single vertex without sorting the list first.

For GPUs, which are optimized for fine-grained parallelism, this is a viable representation of data. Edge vectors will be accessed consecutively, but the potential for coalescing (atomic) requests to vertex data depends on the ordering of the adjacency list.

#### **Compressed Sparse Row**

Sorting and creating an index for one of the two vectors of an adjacency list facilitates per-vertex edge iteration, and reduces storage requirements further (assuming |V| < |E|). Creating an index for the to-vertex list corresponds to compressing the adjacency matrix by storing non-empty cells consecutively in row-major order; hence, this format is referred to as "Compressed Sparse Row" (CSR, figure 3.5c).

Edge addition/removal is more expensive than with previous data structures. For *push-based* PageRank, however, an algorithm that works with outgoing edges and does not

alter graph topology, this is a straightforward approach to storage. Note that push-based modification of vertex data does require atomic operations.

#### **Compressed Sparse Column**

Using Compressed Sparse Column storage (CSC, figure 3.5d) implies creating an index for the from-vertex vector in an adjacency list. CSC has the same storage requirements as CSR, but facilitates iteration of reversed edges. For *pull-based* PageRank, this is the storage format of choice. Atomic operations are not required, as each vertex-program propagates read-operations over edges and only modifies values associated to itself.

#### 3.4.2. Data Representation for Computational State

For PageRank, the main computational state is expressed as one floating point value per vertex. Information flows through the system over graph edges. Because vertex identifiers are mapped to numerical indices, vertex state can be stored as a vector of floating point numbers. Messages can be trivially combined through mathematical addition, so we also store message state in a vector with one floating point value per (destination) vertex. When exclusive data access cannot be guaranteed and messages from multiple threads target the same vertex, atomic addition is required.

For pull-based PageRank, no (explicit) messages are sent between vertices. However, to guarantee synchronous execution of the algorithm without executing all vertex programs concurrently (which is physically impossible), an immutable copy of vertex values is used as read-only source of data. In practice, this means that the destination vector of the current iteration becomes the source vector of the next iteration.

#### 3.4.3. Data Partitioning

As described in section 3.2.4, partitioning data over distributed memory is a necessity for processing large input data. A low-overhead, autonomous, and naive way of partitioning data is by using a hash function to determine the location of a vertex (edge-cut) or edge (vertex-cut). This allows graphs to be loaded independently by workers in a single-pass (streaming) fashion.

Illustrated by figure 3.4, our hash function simply takes a vertex identifier into account and partitions data in a round-robin fashion. Besides low overhead, this partitioning enables relatively straightforward ghost-vertices management, because ghost-data is also placed consistently throughout memory. Within a partition, data is stored with one of the previously mentioned data structures for graph topology.

Alternatively, we distribute data using a METIS partitioning. METIS aims to provide equally sized partitions with a minimal number of partition-crossing edges. This partitioning is (pre)processed once per graph, and can be reused for multiple applications. Workers then autonomously load their part of the graph based on a provided vertex mapping file (note: METIS only provides edge-cuts).

Again, workers use one of the previously mentioned data structures for local topology storage. Additionally, each worker maintains a dedicated list of inter-worker edges to synchronize ghost-vertices efficiently. Compared to block-based partitioning, communication volume is reduced. However, as memory access requires one step of indirection, management overhead is increased.

#### 3.4.4. Computation Kernels

23: end function

Following the Scatter-Gather model, PageRank is a composition of two building blocks: (1) computation of a partial rank based on iteration over edges; (2) vertex rank update based on aggregated information from the scattering phase (section 3.2.2). These building blocks will be referred to as the *computation kernels* of PageRank, and are implemented according to graph-processing considerations discussed in section 3.2.

```

Algorithm 3 Generalized PageRank Computation

s Inter-worker synchronization task

© PageRank computation task

1: function ComputePageRank(W: Workers; (V, E): Graph)

for all w \in W in parallel do

2:

(V', E', deg) \leftarrow load\_local\_graph(V, E, w)

3:

4:

\begin{aligned} src_v &\leftarrow \frac{1}{|V|} \text{ for } v \in V' \\ dst_v &\leftarrow \frac{1}{|V|} \text{ for } v \in V' \end{aligned}

5:

6:

7:

repeat

8:

\S synchronize_ghost_vertices(origin \rightarrow ghost, update)

⊳ Scatter

9:

© dst \leftarrow pagerank edge traversal(src, deg, V', E')

10:

11:

\bigcirc synchronize ghost vertices(origin \leftarrow ghost, sum)

12:

© err_w \leftarrow \text{pagerank\_vertex\_apply}(src, dst, DAMPING, V')

§ err \leftarrow \sum_{w \in W} err_w

13:

\triangleright

\triangleright

14:

15:

SWAP(src, dst)

16:

until err < EPSILON

17.

18:

(s) result \leftarrow collect result(src)

19.

end for

20:

21:

return result

22.

```

Algorithm 3 presents a generalized Parallel PageRank computation. Note that the manner of kernel execution and data synchronization is dependent on the target platform and execution model. Every inter-worker synchronization task (depicted with §) implies a computation barrier. For edge-cut data, all edges for a vertex are placed on the same worker, so only *one* ghost-data synchronization step is required; pull-based computation style requires the first synchronization (replication) step, while push-based requires the second (aggregation).

Note that we implement the actual PageRank algorithm using convergence detection, rather than Pregel's simplified algorithm which uses a preset number of iterations (resulting in another synchronization step). We also make sure vertices without outgoing edges ("endpoints") distribute their value over the full set of vertices, as per the original algorithm (not depicted in pseudocode). This guarantees an output vector with sum 1.0.

#### Algorithm 4 Push-Based Traversal Kernel

```

1: for all v \in V' do

for all e \in v.OutEdges(E') do

2:

dst_e \leftarrow dst_e \cup \frac{s\overline{r}c_v}{deg_v}

3:

end for

4:

5: end for

6: return dst

```

#### Algorithm 5 Pull-Based Traversal Kernel

```

1: for all v \in V' do

for all e \in v.InEdges(E') do

2:

dst_v \leftarrow dst_v \cup \frac{src_e}{deg_e}

3:

end for

4:

5: end for

6: return dst

```

Algorithms 4 and 5 show reference PageRank edge traversal kernels for push and pull-based flows, respectively. Although the computation structure is similar between the two, memory access patterns are markedly different. Implementation details differ per platform and will be discussed in following sections.

#### Algorithm 6 Vertex Apply Kernel

```

1: for all v \in V' do

2: dst_v \leftarrow \frac{1-DAMPING}{|V|} + DAMPING \times dst_v

4: end for

5: return err

```

Algorithm 6 shows the reference kernel for PageRank's vertex-value update. This kernel's implementation is relatively straightforward on all platforms, as its memory access patterns and computation structure are familiar.

#### 3.4.5. CPU Implementations

Ideally, each kernel is programmed once, independent of its target platform. However, different platforms demand different optimization strategies. High-level cross-platform parallelization Application Programming Interfaces (APIs) exist, but they inherently provide a lesser ability of fine-tuning. Not knowing the effect of these tradeoffs in the context of graph processing, we implement all PageRank kernels for CPUs using three conceptually different interfaces: OpenMP, OpenCL, and MKL. The programming language of choice is C11, as it is the common denominator between all target APIs. This section will briefly discuss the concepts behind each implementation.

#### OpenMP

OpenMP is an open standard that defines a collection of compiler directives and library routines for straightforward parallelization of shared-memory C/C++/Fortran programs. The standard is well-established and adopted by most popular open source and commercial C/C++ compilers.

The PageRank kernels using OpenMP are similar to their sequential counterpart, only adding explicit threading directives for guided data management and parallel execution, but a grasp of basic concurrency concepts is required to optimally place directives and guarantee proper execution without race conditions.

A single "omp parallel for" directive before algorithm 3 line 2 ensures threaded execution. The number of threads (workers) is statically set to the number of local graph partitions and the compiler is guided to vectorize inner loops using the "omp simd" directive (e.g., algorithm 6 line 1). Inter-worker synchronization is achieved through explicit barriers, atomic operations, and reduction directives.

#### **OpenCL**

OpenCL is an open standard for the development of parallel programs across a wide range of processors and hardware accelerators. It defines a set of library routines and a kernel programming language (subset of the C programming language) that enable the execution of arbitrary user programs (kernels) on varying processors (such as CPUs, GPUs, and FPGAs). Rather than relying on compiler adoption, this standard relies on vendor adoption. Every supporting vendor provides an OpenCL implementation that is optimized for the target platform. Compilation of user kernels is done at runtime and fully tailored for the executing hardware.

The PageRank kernels using OpenCL are implemented as vertex-centric OpenCL functions and enqueued for execution using vendor heuristics for work distribution (with <code>clGetKernelWorkGroupInfo</code>). OpenCL event wait lists are used for kernel synchronization.

#### MKL

The Intel Math Kernel Library (MKL) is a collection of vendor-optimized math routines. It can be used for implementing graph-processing algorithms in their algebraic formulation. MKL trades the ability of fine-tuning performance for a programming interface with a higher level of abstraction. Instead of allowing parallelization of arbitrary user constructs, the library offers a set of basic composable high-performance computation kernels. These kernels are specifically optimized for Intel processors, and support the CSR/CSC data structures discussed in section 3.4.1.

It should be noted that the MKL cannot be used to implement arbitrary custom kernels and, due to its limited set of available kernels, only a few graph algorithms can benefit from using this library. However, this PageRank implementation can be used as a performance reference point for the platform.

#### 3.4.6. GPU Implementations

For the GPU, we use three different programming interfaces with concepts corresponding to their CPU counterparts: CUDA, OpenCL, and cuSPARSE. This section will briefly discuss the concepts behind each implementation.

#### **CUDA**

The CUDA (Compute Unified Device Architecture) framework is a parallel programming framework by NVIDIA that enables the use of CUDA-enabled (NVIDIA) GPUs as accelerators for general purpose processing. It is the most commonly used interface for writing arbitrary user programs for GPUs. User kernels are annotated with specific syntax and can be intertwined with "traditional" code. Contrary to OpenCL, user kernels are compiled beforehand and target a specific CUDA (hardware) version.

Compared to OpenCL, the PageRank kernels are implemented quite similarly. However, CUDA exposes more low-level GPU capabilities useful for graph processing, most notably more atomic operations, which allows for more straightforward/optimized implementations. Again, we use vendor heuristics for work distribution (with cudaOccupan-cyMaxPotentialBlockSize).

#### **OpenCL**

Although OpenCL targets both CPUs and GPUs and implementations can be reused, we implement additional kernels to exploit the GPU execution characteristics as described in section 3.3.2. More specifically, instead of having each execution unit process one vertex, we process one vertex per warp.

#### **cuSPARSE**

The CUDA Sparse Matrix (cuSPARSE) library is part of the CUDA framework and provides composable GPU-accelerated computation kernels for sparse data structures. The API is similar to MKL, but targets NVIDIA hardware rather than Intel's. Just as the MKL, cuSPARSE cannot be used to implement arbitrary custom kernels, so this PageRank implementation will be used as a performance reference point for the platform.

#### 3.4.7. Heterogeneous Implementations

When targeting heterogeneous platforms, writing software becomes notably more difficult. Taking into account the performance characteristics of each platform and non-uniform inter-worker communication times make data partitioning and task scheduling non-trivial problems, especially in the area of graph processing.

We can observe the performance characteristics of each platform by benchmarking the respective specialized implementations, but we need to take into consideration the overhead of orchestrating different devices as well. We use two markedly different programming interfaces to be able to model these overheads: the low-level MPI and the high-level StarPU.

#### MPI

OpenMPI is a low-level Message Passing Interface (MPI) library that enables a cluster of processors to communicate through messages. The best way of transport is selected transparently (i.e., in order of preference, shared-memory, InfiniBand, or Ethernet). The library also offers intrinsics for coordination, such as global barriers and topology management.

For each node in the cluster, already-made kernels for the platform can be reused, while OpenMPI takes care of the data synchronization. Partitioning and task scheduling (selecting the best device for a task) is done manually.

#### **StarPU**

StarPU is a framework that allows programmers to exploit all processors in a heterogeneous system (i.e., all CPUs and GPUs), while abstracting away the task scheduling and data synchronization parts. For each "task", users attach one or multiple kernels (CPU, OpenCL, and CUDA are supported), and StarPU automatically schedules the task on the best suited device, and migrates data accordingly. It does this based on task size and heuristics from on earlier runs. In this regard, StarPU should automatically learn to execute a set of tasks optimally over time.

For the StarPU implementations, we reuse the CPU and GPU kernels. We let StarPU model performance based on task size, and execute tasks accordingly (this is known as StarPU's dequeue model data aware ready or dmdar scheduler). However, StarPU does not partition data to execute simultaneously on all processors, so we partition the input data manually, and create a StarPU task for each partition in order to create the possibility of parallel execution on multiple devices.

#### 3.5. Overview

In order to evaluate the graph-processing performance characteristics of a processing unit, we propose a structural benchmarking method based on the four pillar design principles of graph-processing frameworks defined by McCune et al. [45]. To examine different platforms, we follow a bottom-up approach and prefer in-house PageRank implementations over preexisting graph-processing frameworks and libraries. This allows for a more structured comparison and a better understanding of the performance characteristics of each platform. The design requirements for each benchmark kernel, based on both graph-processing considerations (section 3.2) and platform considerations (section 3.3), are summarized in listing 3.1.

- 1. Must return correct result (not an optimized approximation).

- 2. Must work with directed graphs.

- 3. Must follow TLAV model (section 3.2):

- (a) synchronous timing model for deterministic execution.

- (b) shared-memory communication abstraction.

- (c) push or pull execution model depending on topology data structure.

- (d) edge-cut or vertex-cut data partitioning depending on topology data structure.

- 4. Should optimize for target architecture (section 3.3):

- (a) CPU kernels should limit the amount of threads and operate on consecutive memory blocks.

- (b) GPU kernels should exploit a large number of light-weight threads and operate on consecutive memory blocks.

- (c) heterogeneous implementations should reuse CPU/GPU kernels while taking care of data synchronization and scheduling.

- 5. Should use fitting programming interface for each platform (section 3.4).

Listing 3.1: Requirements for benchmark kernels.

Table 3.1 provides an overview of all kernel implementations. For each platform, we use multiple programming interfaces. First, we use the most commonly used interface for each platform: OpenMP for CPU, CUDA for GPU. Second, we use OpenCL to target both CPU and GPU with the same implementation. Finally, we use a vendor-optimized library for a performance reference point: MKL for CPU, cuSPARSE for GPU.

Kernels mostly differ on granularity, i.e., the the amount of work performed by a single execution unit. For each kernel, we implement both the push and pull execution modes (with CSR and CSC memory layouts respectively); this makes for a total of 30 kernels. For source code, the reader is referred to github.com/nielsAD/hgb.

3.5. Overview 25

| Platform | Interface | Kernel | Granularity      | Implementation notes                                                                         |

|----------|-----------|--------|------------------|----------------------------------------------------------------------------------------------|

| CPU      | OpenMP    | OMP1   | edge-cut block   | Parallel pragma for (outer) vertex loop,<br>SIMD pragma for (inner) edge loop.               |

|          |           | OMP2   | vertex-cut block | Use parallel reduction to merge vertex progress.                                             |

|          |           | OMP3   | vertex-cut range | Thread cuts 2 vertices at most (range start/end), processes all edges of vertices inbetween. |

| CPU/GPU  | OpenCL    | OCL1   | vertex           | Use clGetKernelWorkGroupInfo to determine work-group size.                                   |

|          |           | OCL2   | warp             | Constant warp size of 32.                                                                    |

| GPU      | CUDA      | CUD1   | vertex           | Use cudaOccupancyMaxPotentialBlockSize to determine block size.                              |

|          |           | CUD2   | warp             | Vary warp size between 2 and 32 based on average degree.                                     |

|          |           | CUD3   | warp             | Use atomically increasing global counter to distribute vertices among warps.                 |

|          | StarPU    | SPU1   | edge-cut block   | Provide all OMP, OCL, CUD kernels as codelets. Use regression perfmodel, DMDA scheduler.     |

| HET      |           | SPU2   | vertex-cut block | Use STARPU_REDUX to merge vertex progress.                                                   |

|          | MPI       | MPI1   | edge-cut block   | Use OMP or CUD kernels on each worker. Use MPI_Allgather to synchronize ghost-data.          |

|          |           | MPI2   | vertex-cut block | Use MPI_Reduce to merge vertex progress.                                                     |

|          |           | MPI3   | METIS partition  | Use MPI_Alltoallv to synchronize ghost-data.                                                 |

| CPU      | MKL       | MKL    | graph            | Vendor-optimized reference implementation. Internals unknown.                                |

| GPU      | cuSPARSE  | CSP    | graph            | Vendor-optimized reference implementation. Interals unknown.                                 |

Table 3.1: Overview of our in-house PageRank kernels for each platform.

4

## **Device Performance Evaluation**

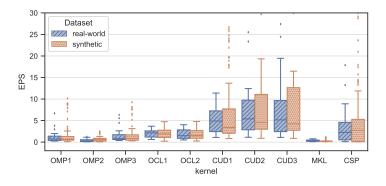

In this chapter, we address RQ2: how to model the graph-processing performance of a processing unit with respect to dataset topology? For this, we conduct an in-depth case study of the graph-processing performance characteristics of CPUs and GPUs. Sections 4.1 and 4.2 introduce our evaluation methodology, metrics, and datasets.

Sections 4.3 and 4.4 discuss our results. Consequently, we propose a graph-processing performance model that takes into account dataset topology in section 4.5. Finally, we conclude this chapter with our main findings in section 4.6.

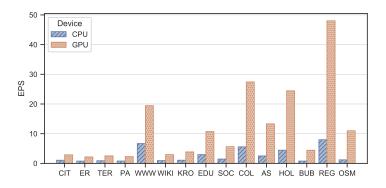

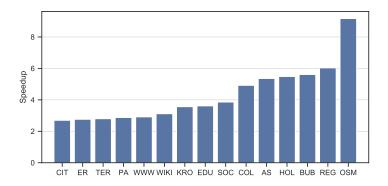

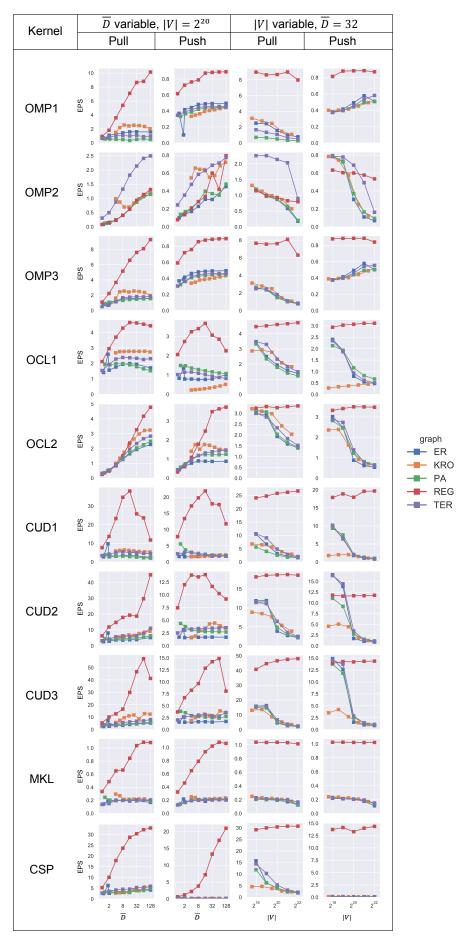

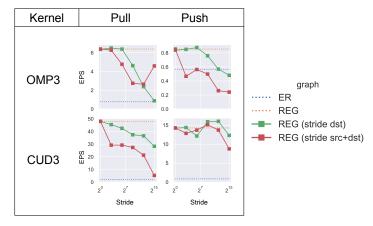

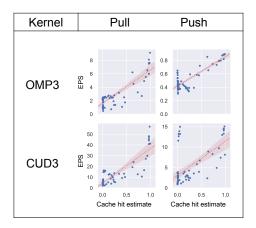

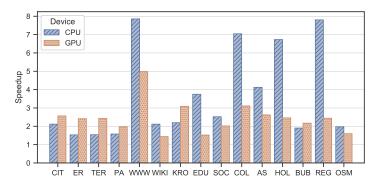

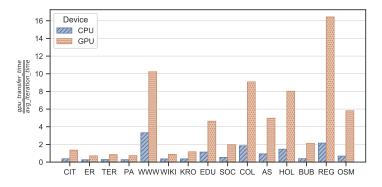

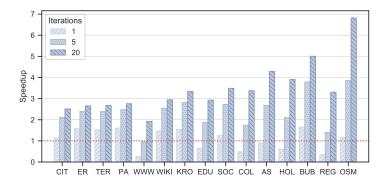

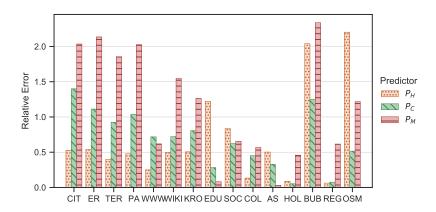

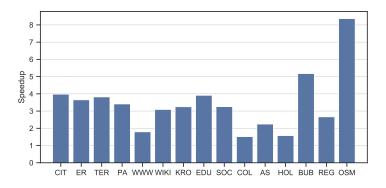

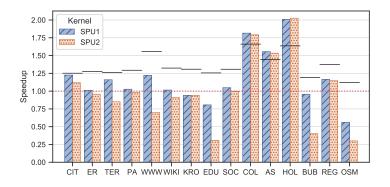

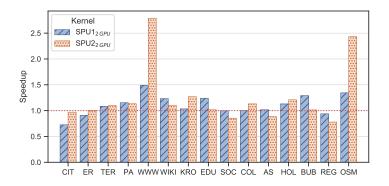

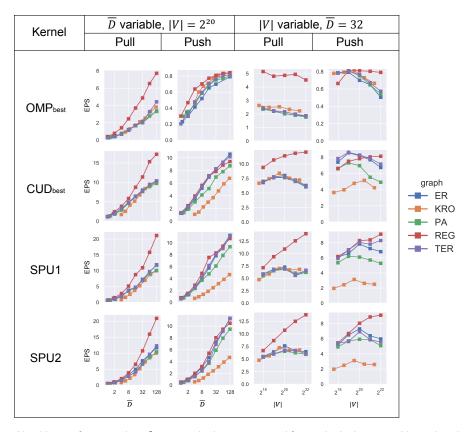

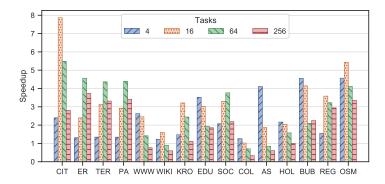

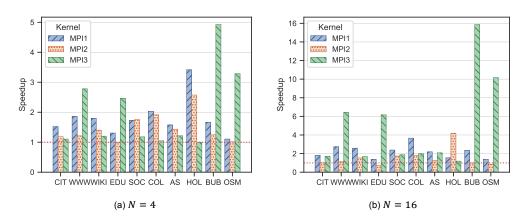

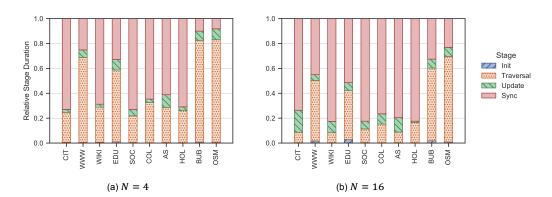

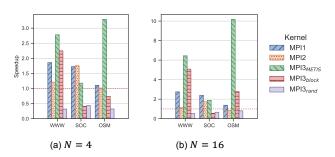

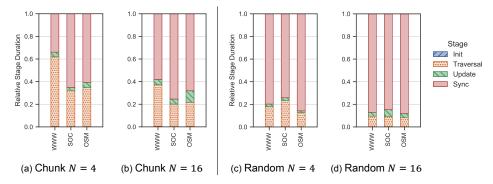

#### 4.1. Methodology