TRdin 1066 5

#### Stellingen behorende bij het proefschrift

# PROGRAMMABLE SURFACE ACOUSTIC WAVE DETECTION IN SILICON

Design of Programmable Filters

van

Jacobus Cornelis Haartsen

- Voor een goed begrip van de detectoren beschreven in dit proefschrift is het voldoende om alleen de elektrische velden, die aan de (akoestoelektrische) oppervlaktegolven gebonden zijn, te beschouwen. In dit verband is het voor een elektrotechnisch ingenieur aantrekkelijker te spreken van elektrische oppervlaktegolven (Surface Electric Waves) dan van akoestische oppervlaktegolven.

- 2. Het vergroten van het rendement van transducenten op piëzoelektrische substraten door de toevoeging van een dunne, niet-piëzoelektrische laag kan uitsluitend toegeschreven worden aan de verandering in de akoestische eigenschappen van het nieuwe, gelaagde medium. De verandering in de diëlektrische eigenschappen als gevolg van de toegevoegde laag zal altijd een verlaging van het rendement tot gevolg hebben.

Dit proefschrift, hoofdstuk 2.

3. Indien in een programmeerbare oppervlaktegolf detector hoge eisen gesteld worden aan signaal-ruisverhouding, regelbereik en onderdrukking van storende invloeden zoals regeneratie en elektromagnetische overspraak, moet men van een actief detectiemechanisme gebruik maken.

Dit proefschrift, hoofdstuk 3.

4. Zonder compensatiemethoden wordt de ondergrens van het regelbereik in een actieve detector bepaald door het passieve detectiemechanisme.

Dit proesschrift, hoofdstuk 4 en 5.

5. Om reflecties aan oppervlaktegolf detectoren in ZnO-SiO<sub>2</sub>-Si structuren te vermijden kunnen gediffundeerde of ionen-geïmplanteerde junctie-elektroden toegepast worden, mits van een actief detectiemechanisme gebruik gemaakt wordt.

Dit proefschrift, hoofdstuk 3.

- 6. Voor het voortbestaan van het menselijk ras is een mondiale geboorteregeling een eerste vereiste.

- 7. Koken is één van de weinige hobby's waarbij het aangename met het nuttige gecombineerd wordt. Bovendien profiteren van deze hobby in het algemeen meer personen dan de hobbyist alleen.

- 8. De welvaart van een land is af te leiden uit de grootte van het per hoofd van de bevolking geproduceerde hoeveelheid afval van (nog) hoge kwaliteit.

- 9. Onze werkelijkheid reikt zover onze sensoren reiken.

- 10. Veel van het hedendaagse wetenschappelijk onderzoek is eerder grensbepalend dan grensverleggend.

- 11. Coïncidentieproblemen in digitale fasevergelijkers kunnen opgelost worden door een scheiding te maken tussen de toestandsvariabelen van het sequentiële circuit en de daadwerkelijke uitgangsvariabelen.

J.C. Haartsen and R.C. den Dulk: "Novel circuit design and implementation of adaptive phase comparators," Electr. Lett. 23, pp. 551-552, 1987.

12. Modelvorming speelt een belangrijke rol in de hedendaagse wetenschap; dit is een direct gevolg van het gelimiteerde perceptie- en bevattingsvermogen van de mens.

## TR diss 1866

# PROGRAMMABLE SURFACE ACOUSTIC WAVE DETECTION IN SILICON

Design of Programmable Filters

# PROGRAMMABLE SURFACE ACOUSTIC WAVE DETECTION IN SILICON

Design of Programmable Filters

Programmeerbare akoestische oppervlaktegolf detectie in silicium. Ontwerp van programmeerbare filters.

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus, prof. drs. P. A. Schenck, in het openbaar te verdedigen ten overstaan van een commissie aangewezen door het College van Dekanen op dinsdag 20 november 1990 te 16.00 uur

door

### Jacobus Cornelis Haartsen

elektrotechnisch ingenieur geboren te 's-Gravenhage, Nederland Dit proefschrift is goedgekeurd door de promotor prof. dr. ir. S. Middelhoek.

Dr. ir. A. Venema heeft als toegevoegd promotor in hoge mate bijgedragen aan het totstandkomen van het proefschrift.

## Leden van de promotiecommissie:

Rector Magnificus prof. drs. P. A. Schenck Promotor prof. dr. ir. S. Middelhoek Toegevoegd promotor dr. ir. A. Venema Prof. dipl.-ing. dr. techn. F. J. Seifert Prof. dr. H. Wallinga Prof. dr. ir. J. H. Huijsing Dr. L. K. Nanver Dr. A. G. Tijhuis Technische Universiteit Delft Technische Universiteit Delft Technische Universiteit Delft Technische Universität Wien Universiteit Twente Technische Universiteit Delft DIMES, Delft Technische Universiteit Delft

Action induces Reaction

## CONTENTS

| 1 | INT           | rodi  | UCTION                                     | 1  |

|---|---------------|-------|--------------------------------------------|----|

|   | 1.1           | PROC  | GRAMMABLE TRANSVERSAL FILTERS              | 2  |

|   |               | 1.1.1 | Matched and Adaptive Filtering             | 2  |

|   |               | 1.1.2 | -                                          | 4  |

|   | 1.2           | SURF  | ACE ACOUSTIC WAVE FILTERS                  | 6  |

|   |               | 1.2.1 | Acoustic Signal Processing                 | 6  |

|   |               | 1.2.2 | Programmable Tapped Delay Lines            | 8  |

|   |               | 1.2.3 | •                                          | 11 |

|   | 1.3           | OBJE  | CTIVES OF THIS WORK                        | 13 |

|   | 1.4           | ORGA  | ANIZATION OF THIS THESIS                   | 15 |

| 2 | $\mathbf{TH}$ | E ACC | OUSTOELECTRIC SYSTEM                       | 17 |

|   | 2.1           | INTR  | ODUCTION                                   | 17 |

|   | 2.2           | THE.  | ACOUSTOELECTRIC FIELD PROBLEM              | 19 |

|   |               | 2.2.1 | Layered Configuration                      | 19 |

|   |               | 2.2.2 | Basic Equations                            | 20 |

|   |               | 2.2.3 | Equivalent-Surface-Charge Method           | 24 |

|   |               | 2.2.4 | Piezoelectric Coupling                     | 27 |

|   | 2.3           | HOM   | OGENEOUS INSULATING SUBSTRATE              | 30 |

|   |               | 2.3.1 | Equivalent Surface Charge                  | 30 |

|   |               | 2.3.2 | Potential Solution                         | 31 |

|   | 2.4           | HOM   | OGENEOUS SEMICONDUCTING SUBSTRATE          | 33 |

|   |               | 2.4.1 | Small-Signal Theory                        | 35 |

|   |               | 2.4.2 | Acoustoelectric Phenomena                  | 38 |

|   | 2.5           | INHO  | MOGENEOUS SEMICONDUCTING SUBSTRATE         | 42 |

|   |               | 2.5.1 | Band Bending                               | 42 |

|   |               | 2.5.2 | Active Semiconductor Devices               | 46 |

|   | 2.6           | CHAF  | RGES AND TRAPS                             | 47 |

|   |               | 2.6.1 | Classification                             | 47 |

|   |               | 2.6.2 | Influence on the Acoustoelectric Phenomena | 50 |

|   |               | 2.6.3 | Acoustoconductivity                        | 51 |

| viii | PROGRAMMABLE SAW DETECTION IN SILICON J. C. HAART | rsen |

|------|---------------------------------------------------|------|

| 2.7  | DEFORMATION POTENTIAL COUPLING                    | 51   |

|      | 2.7.1 Physical Mechanism                          | 51   |

|      | 2.7.2 Acoustoelectric Phenomena                   | 52   |

|      | 2.7.3 Velocity Perturbation                       | 53   |

|      | 2.7.4 Piezoresistive Effect                       | 55   |

| 2.8  | CONCLUSIONS                                       | 55   |

| 3 CC | ONTROLLABLE SAW DETECTION                         | 57   |

| 3.1  | INTRODUCTION                                      | 57   |

| 3.2  | SAW DETECTION MECHANISMS                          | 58   |

|      | 3.2.1 Passive Detection                           | 60   |

|      | 3.2.2 Active Detection                            | 62   |

|      | 3.2.3 Parametric Detection                        | 65   |

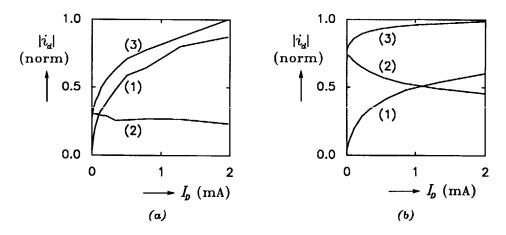

|      | 3.2.4 Detector Efficiency                         | 66   |

| 3.3  | TAP WEIGHTING                                     | 68   |

|      | 3.3.1 Amplitude Control                           | 69   |

|      | 3.3.2 Phase Control                               | 72   |

| 3.4  | JUNCTION STRUCTURES                               | 73   |

|      | 3.4.1 Junction Electrode Reflections              | 74   |

|      | 3.4.2 SAW Detectors using Junction Electrodes     | 78   |

| 3.5  | CONCLUSIONS                                       | 80   |

| 4 T  | HE BARRIER-MODULATED TAP                          | 81   |

| 4.1  |                                                   | 81   |

| 4.2  | REACH-THROUGH OPERATION                           | 82   |

|      | 4.2.1 One-Dimensional Case                        | 82   |

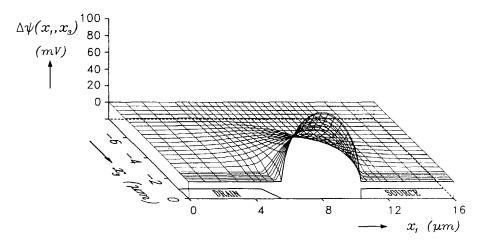

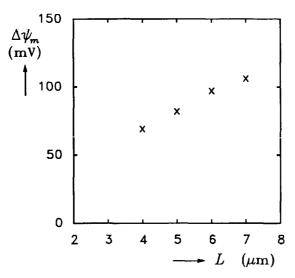

|      | 4.2.2 Two-Dimensional Case                        | 89   |

| 4.3  | SAW DETECTION                                     | 96   |

|      | 4.3.1 Active Detection                            | 96   |

|      | 4.3.2 Passive Detection                           | 102  |

|      | 4.3.3 Secondary Effects                           | 102  |

| 4.   |                                                   | 103  |

| 4.   | •                                                 | 106  |

| 4.   |                                                   | 111  |

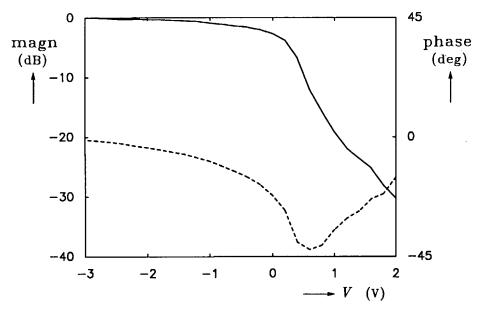

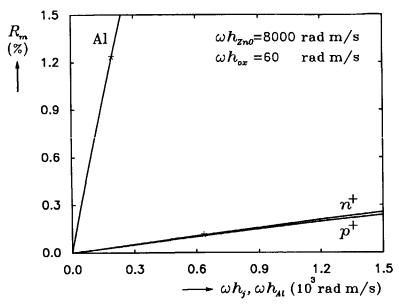

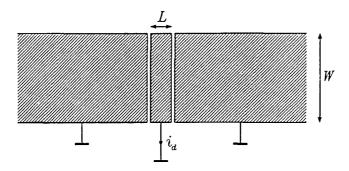

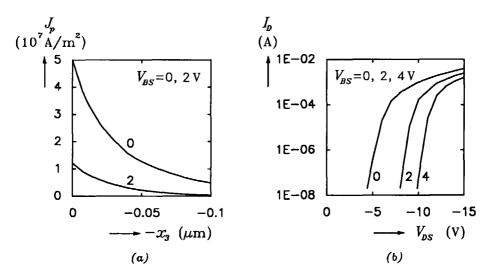

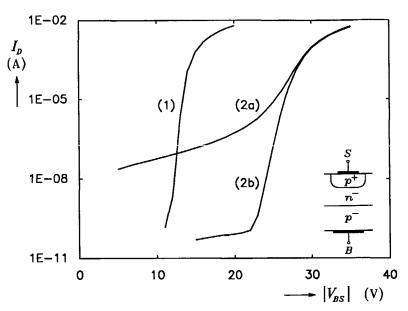

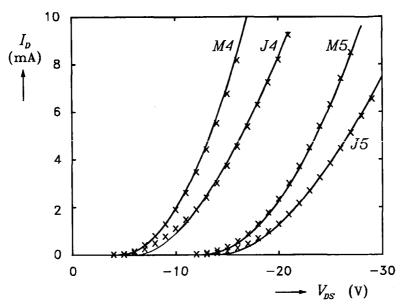

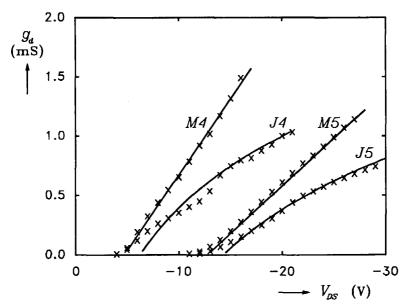

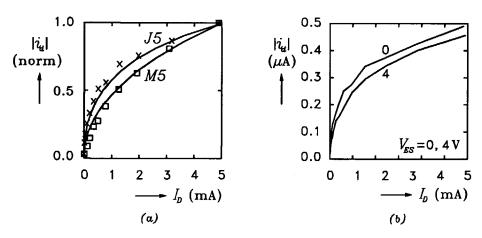

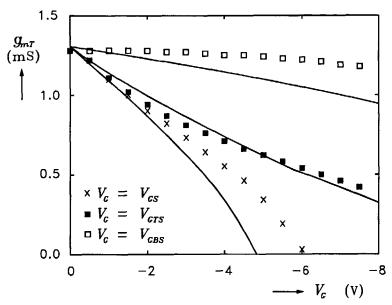

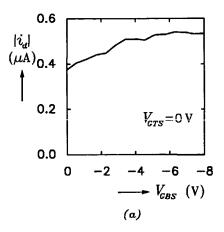

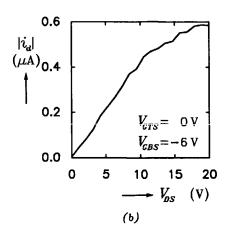

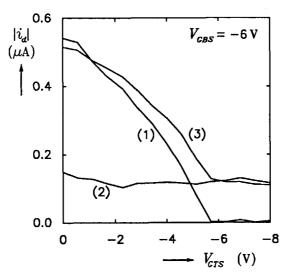

|      | 4.6.1 DC Measurements                             | 111  |

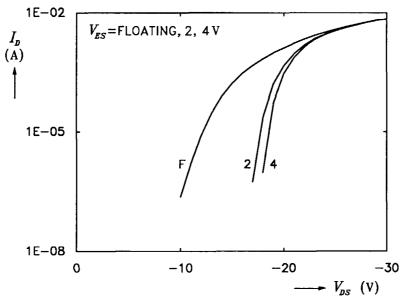

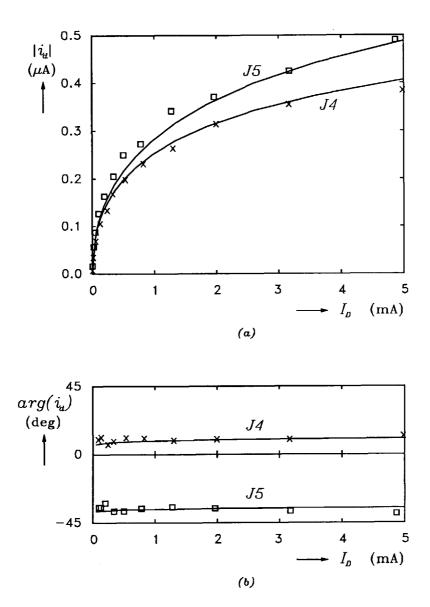

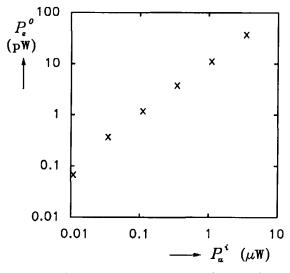

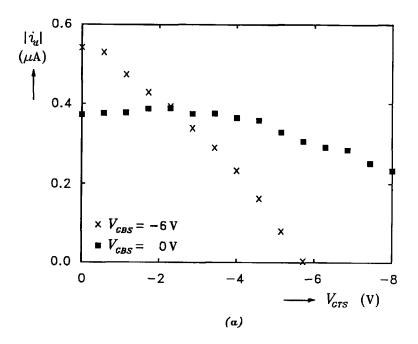

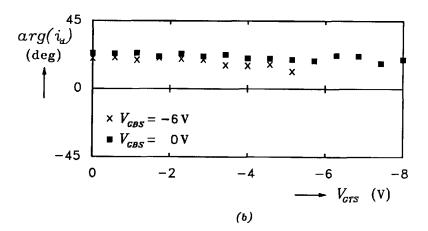

|      | 4.6.2 RF Measurements                             | 117  |

|      | 4.6.3 Noise Measurements                          | 122  |

| 4.   | 7 CONCLUSIONS                                     | 123  |

CONTENTS ix

| 5 | TH  | E PIEZOELECTRIC JUNCTION FET              | 125 |

|---|-----|-------------------------------------------|-----|

|   | 5.1 |                                           | 125 |

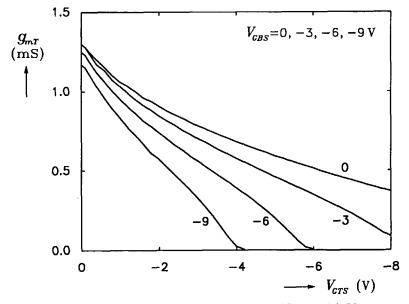

|   | 5.2 | THEORETICAL JEET OPERATION                | 126 |

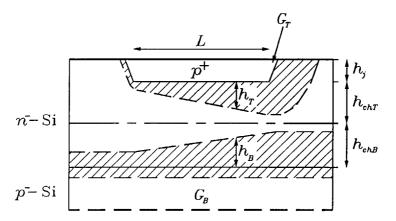

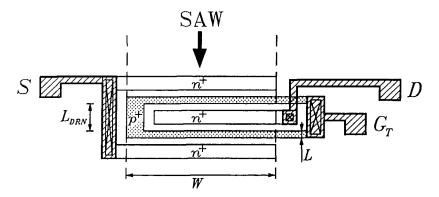

|   |     | 5.2.1 Basic Structure                     | 126 |

|   |     | 5.2.2 JFET Parameters                     | 127 |

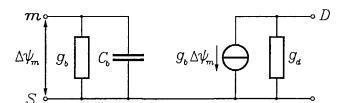

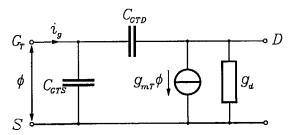

|   |     | 5.2.3 Small-Signal Model                  | 133 |

|   | 5.3 | SAW DETECTION WITH PI-JFET                | 135 |

|   |     | 5.3.1 Active SAW Detection                | 135 |

|   |     | 5.3.2 Passive SAW Detection               | 137 |

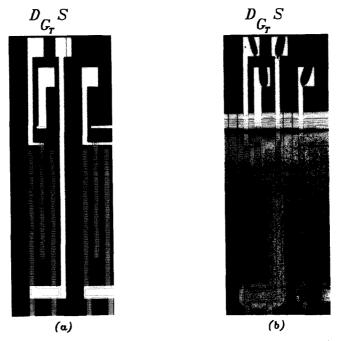

|   | 5.4 | FABRICATION TECHNOLOGY                    | 137 |

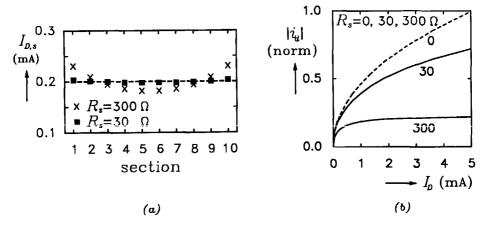

|   | 5.5 | EXPERIMENTAL RESULTS                      | 138 |

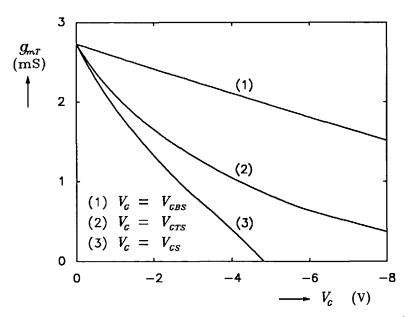

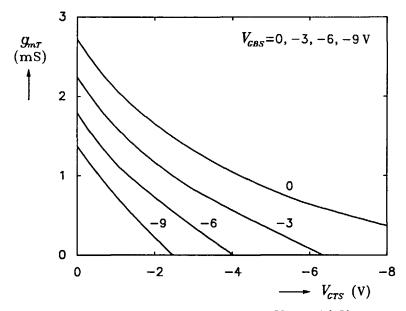

|   |     | 5.5.1 Parameter Analysis                  | 139 |

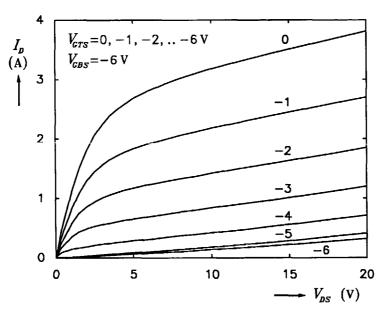

|   |     | 5.5.2 DC Measurements                     | 141 |

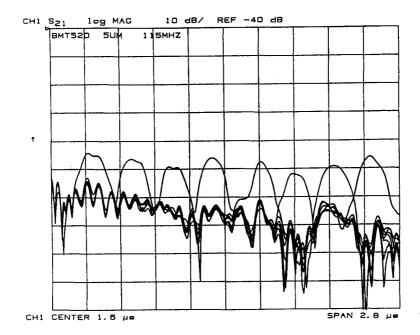

|   |     | 5.5.3 RF Measurements                     | 144 |

|   |     | 5.5.4 Noise Measurements                  | 147 |

|   | 5.6 | CONCLUSIONS                               | 148 |

| 6 | FIL | TER ARCHITECTURE                          | 149 |

|   | 6.1 | INTRODUCTION                              | 149 |

|   | 6.2 | SAW PROPAGATION PATH                      | 149 |

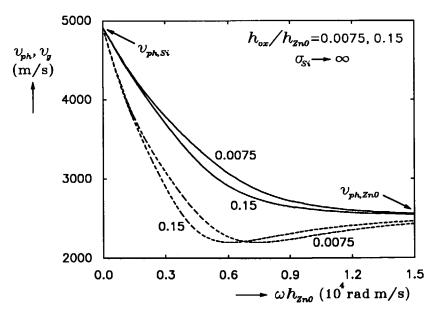

|   |     | 6.2.1 Dispersion                          | 150 |

|   |     | 6.2.2 Higher-order Modes                  | 151 |

|   |     | 6.2.3 Propagation Loss                    | 153 |

|   |     | 6.2.4 Diffraction and Beam Steering       | 154 |

|   |     | 6.2.5 Secondary Effects                   | 155 |

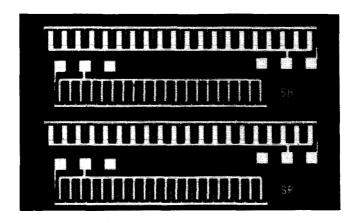

|   | 6.3 | GENERATION PART                           | 158 |

|   |     | 6.3.1 Conventional IDT                    | 159 |

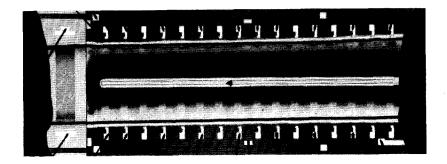

|   |     | 6.3.2 Combined Junction-Metal IDT         | 162 |

|   | 6.4 | DETECTION PART                            | 164 |

|   |     | 6.4.1 The Array Factor                    | 164 |

|   |     | 6.4.2 Dual-Track Configuration            | 166 |

|   |     | 6.4.3 Detection Array of Active Detectors | 168 |

|   | 6.5 | PERIPHERAL ELECTRONICS                    | 173 |

|   |     | 6.5.1 General Applications                | 174 |

|   |     | 6.5.2 BPSK Matched Filters                | 174 |

|   |     | 6.5.3 Adaptive Filters                    | 174 |

|   | 6.6 | CONCLUSIONS                               | 175 |

| REFERENCES                             | 177         |

|----------------------------------------|-------------|

| LIST OF SYMBOLS                        | 191         |

| SUMMARY                                | 195         |

| SAMENVATTING                           | 199         |

| ACKNOWLEDGEMENTS                       | 203         |

| ABOUT THE AUTHOR                       | <b>20</b> 5 |

| LIST OF PUBLICATIONS AND PRESENTATIONS | 207         |

## Chapter 1

### INTRODUCTION

Filtering is one of the most important functions of modern signal transmission systems. Optimal signal detection requires a careful selection of the desired signal and rejection of all unwanted signals. Continuous progress in modulation and coding techniques not only improves the transfer of information, but at the same time requires sophisticated signal-processing techniques. The flexibility of the system can greatly be enhanced by making the filters real-time programmable in order to be able to alter the filter characteristics at will, which enables it to switch arbitrarily between different transmission channels. In addition, it allows adaptive filtering, which enables the adjustment of the system to unknown and time-varying conditions in the transmission channel.

The gradual shift to higher operating frequencies and broader bandwidths is a continuous trend in radar and communication systems; they increase the speed of information transfer in communication systems and improve the resolution in radar systems. Surface Acoustic Wave devices operating in the VHF and UHF range can, to a large extent, perform the required wideband signal-processing functions. This thesis contributes to the development of wideband, programmable filters in which surface acoustic wave technology is employed.

#### 1.1 PROGRAMMABLE TRANSVERSAL FILTERS

#### 1.1.1 Matched and Adaptive Filtering

In general, the flexibility and application range of a filter are enhanced when some kind of programmability is included in the design. However, adding programmability always results in an increase in complexity, and usually performance degradation, of the filter. Before considering the realization and implementation of programmable filters, two types of filters will be discussed in which programmability is highly desirable and even indispensible. These filters, which are extensively used in communication and radar systems are the *matched* filter and the *adaptive* filter.

A matched filter provides the maximal signal-to-interference ratio when the detection of pulse-shaped signals embedded in noise of a known spectral density is involved [1]. If the interfering noise is white, the required impulse response is the time-reversed replica of the signal pulse to be detected. Under matched conditions, the filter produces the autocorrelation of the incoming signal and is, therefore, also called a correlation filter. The matched filter is extensively used in pulsed radar and digital communication systems in which Spread-Spectrum techniques are employed. In these systems the transmitted signals are encoded making use of wideband, phase-modulated codes. Usually, FM chirp or binary Phase-Shift-Keyed (PSK) codes are used. Matched filters are the obvious elements to employ to demodulate such signals.

In the design of radar systems, two basic concepts must be taken into account: resolution and signal-to-interference ratio (SIR). For a high resolution, a short pulse is required, whereas a large SIR requires a large energy content in the pulse. The ultimate performance of the radar is limited by the maximal allowable, instantaneous output power of the transmitter. Pulse-compression techniques can improve the radar performance considerably [2]. Before transmission, the pulse is modulated with an FM or PSK waveform, which produces a very wide bandwidth that is not related to the pulse duration. Therefore, the bandwidth and the duration of the transmitted pulse can be fixed independently. In the radar receiver, the reflected pulse is fed into a pulse-compression filter, which is basically a filter that is matched to the waveform of the coded pulse. The received pulse is compressed into a very short correlation pulse, the duration of which is only determined by the bandwidth of the code. By using transmitters with different codes and receiver units with corresponding matched filters, several radar systems can operate without mutual interference [3].

The expansion of the signal bandwidth before transmission is also

INTRODUCTION — 1

widely used in digital communication systems. In Direct-Sequence Spread-Spectrum systems, each data symbol is transmitted as a binary PSK code sequence [4]. Usually, a pseudonoise (PN) code is used. Because the bandwidth of a PN code sequence is much larger than the symbol rate. the signal power is spread over a wide range in the frequency spectrum. The power density per Hz becomes very low and signal-to-noise ratios much lower than 0 dB are present in the transmission channel. Therefore, the signal is difficult to detect and quite insensitive to narrowband interference. Since the signal is uniquely determined by its code, several communication channels can be accommodated in the same frequency band, provided they use different codes. Demodulation of the spread signal is achieved by the correlation of the received signal with a reference signal, which contains the same binary code as is used in the transmitter. Correlation is a synchronous process, and a strict timing relation between the incoming and reference signals is mandatory. Synchronizing the reference signal to the incoming signal is a time-consuming task. However, in the matched filter, the correlation process is performed instantaneously. The matched filter provides an asynchronous detection of the coded information, and long search times are avoided. Although the matched filters cannot adequately be used when very long code sequences are involved, they do have an important task in reducing the acquisition time in Spread-Spectrum receivers. Since the Spread-Spectrum systems produce a secure means to transfer information, which is protected against interference, interception and multipath echoes, there is an increasing interest in using these systems, e.g. in (mobile) digital radio [5], indoor wireless digital communication [6], packet radio [7].

Programmability in matched filters, both for radar and communication applications, is highly desirable. Since different channels are distinguished by different codes (code-division multiplexing), the receiver can switch between different channels by changing the code of its matched filter. In addition, security is increased by using different codes sequentially in the same transmission channel. Only the receiver which is continuously adjusted to the rapidly changing code sequences can demodulate the signal.

In practice, the transmission channels are not optimal. Distortions and all kinds of interfering signals disturb the transfer of information. In many cases, these distortions and interferences are time variant and are not known in advance; then adaptive filtering is required: the filter function is periodically updated, until a maximal SIR is obtained. In the following, some specific adaptive filters are considered.

Adaptive bandpass filters are applied in transmission systems in which the center frequency of the signal changes. This can be an unintended shift which is caused by drift or Doppler phenomena, or an intended shift, for example in frequency-multiplexed and in Spread-Spectrum frequency-hopping systems. When the shift is intended and thus known in advance, real-time adjustment of the pass band can be achieved.

Adaptive whitening filters are used to reject time-varying interfering signals. These kinds of filters are extensively used in transmission channels, where continuous-wave (CW) interferences are present. The adaptive filter algorithm will eventually produce a bandstop filter function with the notch exactly situated on the CW tone.

Equalizers are adaptive filters which restore the signal when distortions have been incurred in the transmission channel. An equalizer can be considered as an inverse filter with a filter function, which is reciprocal to the transfer function of the channel. Used as an echo canceller, the equalizer can enormously improve the signal detection in a multipath environment [5].

The need for programmability in adaptive filters is quite obvious. Usually a lot of post processing has to be performed to find the optimal filter characteristic. For this purpose, computer-based algorithms are employed [8]. As a consequence, only slowly varying interferences can be suppressed.

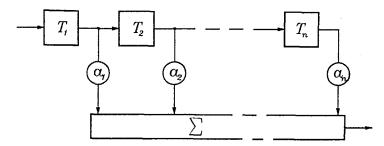

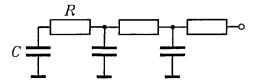

#### 1.1.2 Basic Transversal Filter Structure

Sophisticated filters of the types discussed above cannot be constructed with lumped network elements such as, for example, those encountered in LC filters. The realization of filter functions like these can conveniently be carried out using the transversal filter concept. This concept was first described by H.E. Kallmann [9]. In Fig. 1.1 the basic realization of a transversal filter is shown. It consists of three elements: a tapped delay line, a weight circuit in which each tap output is multiplied by a certain tap weight factor, and finally a summation circuit in which all weighted tap signals are superposed. The transversal filter is a linear filter with a finite impulse response (FIR). The filter operation is completely asynchronous and produces a fixed timing relation between the input and output signals.

The impulse response h(t) of the filter is given by

$$h(t) = \sum_{n=1}^{N} a_n \delta(t - \sum_{m=1}^{n} T_m)$$

(1.1)

in which  $a_n$  is the tap weight factor and  $\sum_{m=1}^n T_m$  the time delay which corresponds to the  $n^{th}$  tap. Because of the discrete nature of the tapping,

Introduction -1 5

Figure 1.1: Functional diagram of a transversal filter.

the signal in the delay line is sampled at a rate which is determined by the inter-tap delay. For programmable filters, a uniform sampling is used, which results in a constant inter-tap delay  $\Delta T$  and simplifies the impulse response to

$$h(t) = \sum_{n=1}^{N} a_n \delta(t - n \Delta T)$$

(1.2)

With Fourier Transform techniques the frequency response H(f) of the filter can be derived

$$H(f) = \sum_{n=1}^{N} a_n e^{-j\omega n\Delta T}$$

(1.3)

Because the transversal filter is a nonminimum phase filter, a wide variation in both the amplitude and phase characteristics can be obtained simply by choosing the tap weight factors appropriately. For filtering at baseband, the tap values are real and the weight factor  $a_n$  is a real number; for IF signals on the other hand, complex weight factors can be applied, since both the magnitude and the phase of the tap output can be varied.

Several technologies have been adopted for the implementation of transversal filters [10, 11]. The largest extent of flexibility is obtained with digital filters. The rapid progresses in IC technology during the past decades allows Very Large Scale Integration. However, digital signal processing is not very attractive for broadband systems which require a large dynamic range. In these applications, a high clock frequency combined with a long word length (> 10 bits for a 60 dB dynamic range) are required, which results in high power dissipations. In particular, the analog-to-digital conversion process imposes difficulties. In practice, this limits the bandwidth of digital transversal filters to a few hundred kHz. A method which consumes much less power is achieved with analog Charge-Transfer devices (CTD). The signal is represented by an amount of charge, which is shifted and nondestructively detected along a delay line [12]. Typ-

ically, CTD transversal filters operate with filter bandwidths up to a few MHz.

Digital and Charge-Transfer filters operate at baseband. Because the input signal is sampled, a clock frequency of twice the bandwidth is required to prevent aliasing. For the implementation in silicon, typically filter bandwidths up to 10 MHz are feasible. Continuous progress in the GaAs technology will move these bandwidths into the 100 MHz-1 GHz range. However, an attractive alternative for wideband filters in this frequency range is the Surface Acoustic Wave (SAW) technology. Analog filters employing SAW techniques operate at IF frequencies in the range of 10 MHz-10 GHz. Bandwidths up to 30 or 40 % of the operating frequencies are feasible. Because SAW filters are passive devices, low-power operation results. In the next section the realization of programmable SAW filters is discussed.

#### 1.2 SURFACE ACOUSTIC WAVE FILTERS

#### 1.2.1 Acoustic Signal Processing

Acoustic or elastic waves in a solid result from mechanical vibrations around an equilibrium position. This vibration can be in the direction of the wave propagation which corresponds to a longitudinal mode, or normal to the propagation direction which corresponds to a transverse or shear mode. Acoustic waves have a propagation velocity which typically lies between 10<sup>3</sup> and 10<sup>4</sup> m/s. This is about five orders of magnitude slower than electromagnetic waves. Therefore, acoustic waves are very attractive for delay line applications: one microsecond of delay only requires a few mm of propagation path.

An important subject of research has always been the link between the electrical and the acoustical domain. How are the electric signals converted into acoustic signals and vice versa? The key to this problem is piezoelectricity. This phenomena couples the elastic strains to electric fields and occurs in anisotropic materials that lack a center of symmetry in their atomic structure. By using resonating structures, which are constructed with metal electrodes and piezoelectric materials mechanically connected with the propagation medium, an efficient in and out coupling of acoustic waves can be achieved.

The simplest types of waves are Bulk Acoustic Waves (BAW). These waves propagate in an infinite homogeneous medium and have either a longitudinal or transverse motion. An efficient bulk-wave excitation is achieved in a sandwich structure consisting of a piezoelectric plate placed

1 Introduction -1

between two metal electrodes of opposite RF polarity. By placing this structure at the beginning and the end of an oblong object, a BAW delay line can be constructed.

At the stress-free boundary of a semi-infinite solid another type of wave can exist: the Surface Acoustic Wave (SAW). This wave sticks to the surface and the penetration depth into the medium is in the order of one wavelength. One type of SAW, the Rayleigh wave, had already been described mathematically by Lord Rayleigh in 1885 [13]. The Rayleigh wave has both a longitudinal and a transverse component, and has a propagation velocity which is smaller than the corresponding longitudinal and shear wave velocities [14]. Although many other types of SAWs can exist at the surface, in this thesis only the Rayleigh type is considered and the term "SAW" is restricted to this type of wave.

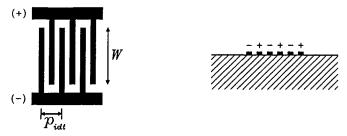

The use of SAWs for signal-processing functions was postponed because of the lack of an efficient method to couple the electric signals to the SAW. A breakthrough was accomplished by the introduction of the Interdigital Transducer (IDT), the application of which was first published in open literature by White and Voltmer [15]. The IDT can be considered to be the basic element of all SAW devices applied today. It consists of an array of metal electrodes of alternate RF polarities placed at the surface of the propagation medium, see Fig. 1.2. The piezoelectricity is added by using piezoelectric crystals like quartz or lithium niobate as the propagation medium, or by covering the nonpiezoelectric propagation medium with a piezoelectric film. When a time-varying electric voltage is applied across the transducer terminals, a standing wave pattern is built up in the interdigital pattern. This standing wave pattern can be considered as the superposition of two contra-directed traveling waves which leave the IDT at the edges. Since piezoelectricity is a reciprocal phenomenon, the conversion process is reversible and the IDT can also convert traveling

Figure 1.2: Top view (left) and cross section (right) of an Interdigital Transducer.

mechanical waves into electric signals. An optimal conversion occurs when the wavelength of standing acoustic wave pattern corresponds to the period of the electrode pattern. The resonance frequency  $f_0$  is determined by the SAW phase velocity  $v_{ph}$  and the transducer period  $p_{idt}$

$$f_0 = \frac{v_{ph}}{p_{idt}} \tag{1.4}$$

Electrode spacings in the order of  $10 \,\mu\mathrm{m}$  amount to operation frequencies of several decades of MHz.

The acoustic signal is concentrated at the surface of the delay medium and can therefore be reached anywhere in the delay path. Therefore, so-phisticated filter functions can be realized by designing appropriate metal ID structures. Since the dimensions and the planar fabrication techniques of the metal ID patterns are compatible with modern IC technology, the SAW technology is well established and allows mass fabrication of SAW filters.

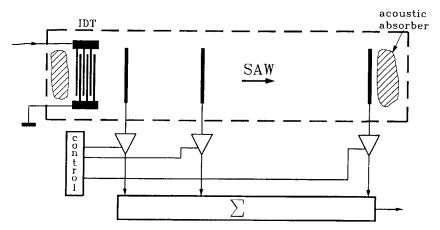

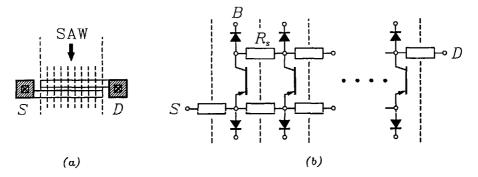

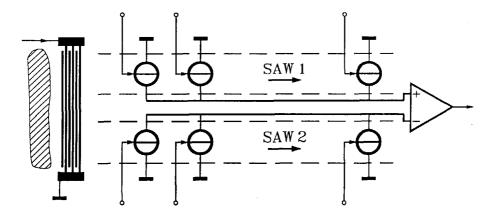

#### 1.2.2 Programmable Tapped Delay Lines

Since low-power and small-sized delay functions can readily be obtained with SAW technology, this technology is very suitable for the implementation of tapped delay lines. In Fig. 1.3 the generalized implementation of a programmable SAW filter is depicted, which corresponds to the basic transversal filter structure shown in Fig. 1.1. The electric input signal is converted into an acoustic wave by using a conventional IDT structure. In the propagation path of the traveling wave, SAW detectors are placed to sample the wave. The wave which is transmitted in the opposite direction is absorbed by an acoustic absorber at the edge of the delay line. The detector outputs are electronically weighted, and then accumulated in a collective summation circuit. Basically, this structure is a tapped delay line with programmable tap outputs, and is, therefore, denoted as *Programmable Tapped Delay Line*.

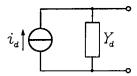

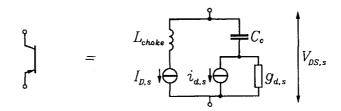

The key elements of the programmable tapped delay line (PTDL) are the programmable taps. In these taps two functions are performed: signal conversion from the acoustical into the electrical domain at the sampling positions, and controlling the electric output signal to obtain the desired tap weight factor. For the acoustoelectric conversion process, two detection mechanisms are available: a passive and an active mechanism. In the passive detector, the electric output signal results directly from the mechanically induced electric fields. The weight function must be applied afterwards in an electronic circuit, which is located outside the SAW

INTRODUCTION — 1 9

Figure 1.3: General structure of a programmable SAW Tapped Delay Line.

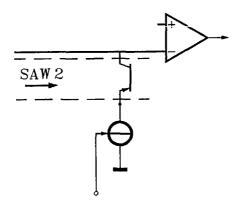

propagation path. Because the detection and the control functions are separated, this type of tap is denoted as Separated-Control Tap. In the active detector, the mechanically induced electric fields modulate a much larger electric signal within the detector, which is supplied by an auxiliary electric source. By varying the signal supplied by this auxiliary source, the output signal is controlled directly at the origin. In fact, the detection and control functions are merged into a single, active element which is located in the propagation path. Therefore, this tap is denoted as Integrated-Control Tap.

In the previous discussion, linear detection processes were assumed. A detection mechanism, which uses a nonlinear process, is the parametric detection. The parametric detector can be considered as an active detector in which the auxiliary source is not electric but acoustic. This auxiliary or pump signal is present as an acoustic CW signal in the propagation path. Because of nonlinear effects in the detector or in the control circuitry, the output signal is the product of the main and the pump signal. By controlling the nonlinear coefficients, a programmable tap can be obtained. An elaborated discussion of passive, active and parametric detectors is presented in Chapter 3.

Various technologies have been adopted for the PTDL fabrication. The very first PTDLs were merely extensions of the fixed TDLs: passive taps, located in a conventional delay line on a piezoelectric substrate, were individually connected to a control circuit by use of bonding wires [16]. Initially, the control circuitry of these hybrid, separated-control taps was

very simple, consisting of only a few discrete diodes [17]. However, continuous progress in IC technology yielded more complex circuitry, making use of MOS [18] and bipolar LSI [19] in a Silicon-on-Sapphire (SOS) and full silicon technology, respectively. SOS technology seems to be an attractive approach because of the low capacitances of the electronic devices, which yield high on-off ratios, high RF tap-to-tap isolation, and low-loss RF switching in the control circuitry. At the beginning of the eighties, GaAs was introduced in high-speed control electronics in hybrid PTDL configurations [20]. The piezoelectric media generally applied in hybrid PTDLs are ST-X Quartz or YZ-LiNbO<sub>3</sub>, which provide temperature-stable and low-loss delay media, respectively.

The hybrid PTDL is an attractive configuration, because both the acoustical and electrical properties of the system can be optimized simultaneously. However, the hybrid technology prevents the implementation of active detectors, and the use of wire connections between delay line and electronics becomes very unattractive when the frequency and the number of taps increases. Bonding wires can be circumvented by using an air-gap structure. In this structure, a piezoelectric medium is placed upside down and very close to a semiconducting medium. Usually, a spring assembly and SiO<sub>2</sub> spacer rails on the semiconductor are applied in order to maintain a uniform air gap of a few hundred nm [21]. SAWs travel along the surface boundary facing the semiconductor. Because the air gap is very small, the fringing electric fields induced in the piezoelectric medium couple directly to detectors located at the semiconductor surface.

Several laboratories demonstrated the feasibility of wideband PTDLs with reasonable performance by using a hybrid technology. However, hybrid configurations do have disadvantages with respect to compactness, reliability, and price-to-performance ratio when large volumes are involved. Monolithic integration of the SAW delay line and the control electronics is preferable, and should ultimately give the best performance. However, the fabrication complexity of this monolithic integration has always hindered its progress. For the integration of SAW devices and electronic circuitry, both piezoelectric and semiconducting properties must be combined in a single chip. Two methods are available: a piezoelectric semiconductor, or a nonpiezoelectric semiconductor covered with a piezoelectric film.

Piezoelectric semiconductors like ZnO and CdS have extensively been investigated because of the acoustoelectric phenomena which occur in these materials. However, if electronic circuitry must be added, only GaAs provides the required properties [22]. A full monolithic integration of a PTDL in GaAs with passive taps is reported in Reference [23]. Much

INTRODUCTION — 1

attention has been paid to parametric detectors which employ MESFETs [24]. GaAs is only weakly piezoelectric, and IC fabrication on GaAs is expensive and not a trivial task. Although the use and knowledge of GaAs IC fabrication is steadily growing in all areas of the industry, the wide use of silicon and the experience in handling this material makes it highly attractive for monolithic PTDL implementations.

Since silicon is not piezoelectric, silicon implementations always require a piezoelectric overlay in order to enable the acoustoelectric conversion processes to occur. Several films like AlN, ZnO and CdS have been applied. Programmable matched filters, that use AlN in combination with an SOS technology, are reported in Reference [25]. However, AlN does not have attractive delay properties because of the high wave velocities and strong dispersive behavior [26]; CdS films, on the other hand, are difficult to manufacture. Therefore, ZnO is the most attractive material to use as piezoelectric overlay in integrated SAW devices. Because the ZnO-Si combination provides a much stronger piezoelectric coupling than GaAs, much higher conversion efficiencies can be achieved. A full silicon implementation of a PTDL which uses a ZnO film, was first reported by Hickernell in 1973 [27]. In this filter the piezoresistive effect in MOSFETs is applied. ZnO is only required in the IDT region, where the SAWs are to be excited. A ZnO-Si implementation, in which piezoelectricity is used in both the SAW generation and detection, is described in Reference [28], where passive detectors in the SAW propagation path are connected to external dual-gate FETs for tap control.

### 1.2.3 Alternative Programmable Filter Techniques

Although the Programmable Tapped Delay Line is the most direct realization of a filter with a programmable filter function, several other techniques which perform the same function were investigated. Two important ones will be discussed briefly: the Convolver and the Fourier Transform Processor. Basically, these two realizations produce the convolution of two input signals. Since filtering is merely the convolution of the input signal with the filter impulse response, the Convolver and the Fourier Transform Processor (FTP) can be used as filters if one of the input signals is a reference signal which contains the required filter function. Since this reference signal is applied externally, its format can readily be changed and the filter becomes programmable.

In a convolver, two contra-directed SAWs travel in a common delay medium. Because of nonlinear effects in the overlap region, product terms appear. These nonlinearities can be caused by the elastic medium itself [29], or by the nonlinear interaction with charge carriers, which are located in a nearby semiconductor [30]. The latter effects are strongly related to the afore-mentioned parametric detection mechanism. By using a conventional IDT (the nondegenerate case) or an electrode plate (the degenerate case) in the interaction region, the output signal can be coupled out at the sum or difference frequency of the input and reference signals.

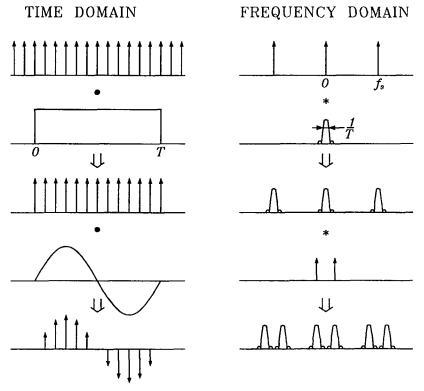

The Fourier Transform technique is a general method to perform signal-processing functions in the frequency domain instead of in the time domain. Because convolution in the time domain corresponds to multiplication in the frequency domain, filter functions can be realized by first transforming the input signals into the frequency domain, performing the multiplication in the frequency domain, and then transforming the result back into the time domain. For the transformation from the time to the frequency domain and vice versa, the chirp Z-transform can be employed [31]. SAW chirp filters are extremely suitable to perform this transformation in the high frequency range. A complete FTP contains several of these chirp filters [32].

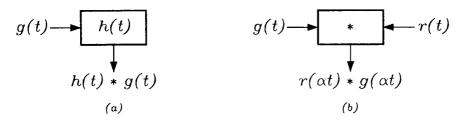

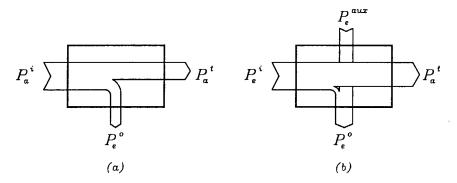

The fundamental difference between the direct realization of the PTDL and the indirect techniques, is shown in Fig. 1.4. The PTDL is a two-port device which operates completely asynchronously. There is a fixed timing relation between the input and the output signals. The filter response h(t) is embedded in the device itself. The Convolver and FTP are three-port devices. The filter response is provided externally as a reference signal r(t). An exact timing relation between the input signal g(t) and the reference signal r(t) is required, which yields a synchronous filter operation. The timing relation between the input and the output signals depends on the timing of the reference signal. In the convolver a time contraction takes place ( $\alpha = 2$ ).

A great deal of effort was put into realizing the asynchronous and continuous operation of the Convolver and FTP by the use of repetitive

**Figure 1.4:** Functional diagrams of (a) a PTDL, and (b) indirect techniques such as the Convolver ( $\alpha = 2$ ) or the Fourier Transform Processor ( $\alpha = 1$ ).

INTRODUCTION — 1

reference signals combined with time gating [33] or a special signal transfer protocol [34], and by the use of parallel channels for signal interlacing [35]. In a number of applications, an acceptable asynchronous operation can be achieved, however, at the expense of additional hardware complexity, power consumption and volume of the required timing circuits and waveform-generation circuits that provide the RF reference signals. For comparison, the PTDL, although its programmability is limited, only requires control circuitry to set the tap weight factors.

A new and promising development, which should be mentioned here, is the Acoustic-Charge-Transfer (ACT) technique. This technique, which was first introduced by Gaalema [36], is comparable to the operation of conventional Charge-Coupled techniques. However, the traveling potential wells, which contain the charge, do not arise from clocked electrodes, but from the traveling electric potential of the SAW itself. The device operates at baseband, but bandwidths up to 150 MHz were realized. At the moment, the research focusses on buried-channel devices in GaAs, in which very high transfer efficiencies can be achieved [37]. Recently, a monolithic programmable PTDL, based on ACT techniques in GaAs, was presented and it has some very promising features [38].

Silicon was also investigated for the implementation of ACT techniques. ZnO-SiO<sub>2</sub>-Si structures were applied to realize surface-channel ACT devices [39], but charge trapping at the SiO<sub>2</sub>-Si interface severely deteriorated the transfer operation [40]. Buried-channel devices are not likely to be developed in silicon, because the depletion layer, which must be applied from the surface, is difficult to realize in ZnO-SiO<sub>2</sub>-Si structures.

#### 1.3 OBJECTIVES OF THIS WORK

If, in the future, the SAW technology must compete with other analog and digital technologies, the merging with electronic circuitry is indispensable. It is believed that monolithic integration will in the end provide the most compact, reliable and cost-effective solution. Silicon has been chosen as the starting material, because of the advanced IC fabrication experience and the excellent electronic circuitry that can be obtained. In addition, acceptance by industry is likely to be more rapid, if merging SAW and electronics only involves a few extra steps in a standard fabrication process.

A full, monolithic integration in a ZnO-SiO<sub>2</sub>-Si structure of a conventional SAW filter and electronic circuitry for mixing and amplification was

presented by Visser [26]. However, the combination of SAW and semiconductor technology not only provides a means to combine acoustical and electronic devices on a single chip but, in addition, new acoustoelectric devices can be designed, in which both acoustic and electronic signal-processing functions are merged into a single element. This functional integration, which can be denoted by the name piezotronics, offers a wide range of new devices and potential applications. One application is the tapped delay line with a programmable filter function. Piezotronic elements in the SAW propagation path, electronic control and impedance-matching circuitry to link to the external world, and other electronic signal-processing circuitry, are all contributing to the development of a truly monolithic, smart filter.

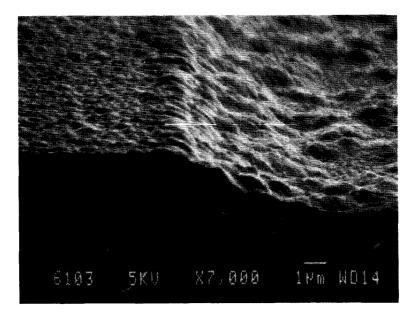

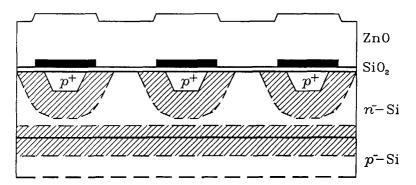

The main object of research in this thesis is the synthesis, realization and implementation of programmable SAW detectors in ZnO-SiO<sub>2</sub>-Si layered structures. New semiconductor elements in silicon are investigated, in which the charge carriers are directly influenced by the electric fields which are mechanically induced by the SAW. The ZnO-SiO<sub>2</sub>-Si configuration offers the possibility to fabricate these elements with highly conductive, diffused or implanted regions in the silicon substrate, thus avoiding metal parts in the propagation path of the SAW. In this method of fabrication, a smooth surface above the detector results, which improves the growth of ZnO, and reduces reflections which are caused by mechanical and topological discontinuities. Sensitive taps with a wide control range require active detection mechanisms.

From scientific point of view, the combination of SAW and semiconductor technology is very attractive, because it provides almost limitless possibilities. Challenging research projects result from the inherent multidisciplinary field where SAW physics, semiconductor physics, and IC technology meet. However, monolithic integration of SAW and semiconductors has continuously been hindered by technological problems, and the choice for a monolithic solution instead of for an alternative technology always seems to exchange hardware complexity for technological complexity. For the ZnO-SiO<sub>2</sub>-Si structure in particular, this relates to the growth of high-quality ZnO layers, which is not yet as state-of-the-art as the silicon technology. However, encouraging results have been achieved, and the history of IC technology shows that if effort is put into the improvement of the technology, these problems will eventually be surmounted. The author hopes that this thesis will motivate and encourage many co-workers in the field to achieve this aim, which will eventually lead to high-performance, integrated acoustics.

INTRODUCTION - 1 15

#### 1.4 ORGANIZATION OF THIS THESIS

The contents of this thesis can roughly be divided into three parts and follows a bottom-to-top approach. The first part is a theoretical discussion concerning acoustoelectric effects, and the detection mechanisms that are based on these effects. In Chapter 2, all the phenomena are considered that occur when a SAW travels through a ZnO-SiO<sub>2</sub>-Si layered structure and its penetrating electric fields interact with the mobile charge carriers in the silicon. In addition, the influences of depletion layers, accumulation layers, and interface states are examined. In Chapter 3, the realization of controllable SAW detectors which use the phenomena discussed in Chapter 2 is investigated. Both passive and active detectors are considered. The active detectors which can be implemented merely by using junction structures in the silicon are of particular interest.

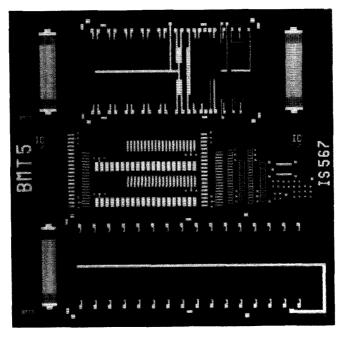

In the second part, two implementations of programmable taps are presented. Chapters 4 and 5, respectively, discuss the Barrier-Modulated Tap and the piezoelectric Junction FET, which are both active junction devices with an electronically controllable output. These chapters include the discussion on physical operation, modeling, implementation, and verification by experimental results. In addition, technological aspects are considered.

The final part discusses the architecture of the complete programmable filter in the  $\rm ZnO\text{-}SiO_2\text{-}Si$  layered structure. In Chapter 6, a general discussion about the structure of a programmable filter, which uses the detectors presented in Chapters 4 and 5, is given. Attention is paid to the generation of SAWs and a new IDT configuration is introduced, which is compatible with the new detector structures.

## Chapter 2

## THE ACOUSTOELECTRIC SYSTEM

#### 2.1 INTRODUCTION

In this chapter, the combined acoustic and electric phenomena which originate when a Rayleigh wave travels along the surface of a ZnO-SiO<sub>2</sub>-Si layered structure are considered. The investigation of SAWs in a layered system involving piezoelectric and semiconducting layers is not a trivial one. The mechanical displacements induce electric fields in the piezoelectric ZnO layer, which penetrate into the semiconducting silicon substrate. As a consequence, an interaction takes place between the acoustic wave and the mobile charge carriers in the semiconductor, which not only results in a perturbation of the charge carrier distribution, but also in a perturbation of the wave propagation itself.

Initially, the interactions between (bulk) acoustic waves and charge carriers were investigated in piezoelectric semiconductors [41, 42]. In this case, a one-dimensional approach can be applied. Two-dimensional wave-carrier interactions involving SAWs were first investigated in piezoelectric insulators covered with a thin, semiconducting film [43], and in air-gap structures [44]. Although many interesting acoustoelectric phenomena can be observed, three effects have been given most attention because of their practical applicability. These are the acoustic amplification caused by linear, wave-carrier interactions; the transverse acoustoelectric voltage (TAV) caused by nonlinear effects, which induce DC terms in the wave-

carrier interaction; and the parametric effects caused by nonlinear effects, which induce AC terms at the sum and the difference frequencies of two SAWs. Especially in the latter field, the ZnO-SiO<sub>2</sub>-Si structure has successfully been applied to obtain the required acoustoelectric interactions [45].

In the theory described in this chapter, the weak-coupling approximation is used. Under weak-coupling conditions, it is assumed that the mechanical field variables, stress and strain, are not disturbed by the presence of free charge carriers or other electrical conditions. This assumption, which is valid when the piezoelectric coupling is small, simplifies the theory considerably. In addition, it is assumed that  $kl_{free} \ll 1$ , where k is the SAW wavenumber ( $k = \omega/v_{ph}$ , with  $v_{ph}$  the SAW phase velocity), and where  $l_{free}$  is the mean free path of the charge carriers. This implies that the carriers undergo many collisions when moving one wavelength, and a macroscopic theory can be applied. The charge carriers are then approached collectively, and mobility and effective carrier mass are meaningful concepts. This assumption is valid in silicon for frequencies below 5 GHz. If  $kl_{free} > 1$  a microscopic theory must be used, where the individual phonon–electron interaction requires a quantum-mechanical treatment [46].

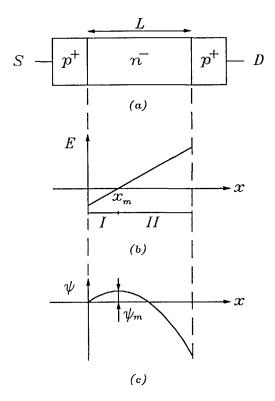

In the next section, a general discussion of the acoustoelectric field problem in the layered structure is given. Firstly, the basic equations of the individual layers are considered. Then a method to solve the equations is discussed, in which the polarization charge in the ZnO layer is replaced by a surface charge at the ZnO-SiO<sub>2</sub> interface. This method reduces the acoustoelectrical problem to a mere electrical one. In sections 2.3 and 2.4, the solution is considered for homogeneous silicon substrates of zero and arbitrary conductivity, respectively. In the latter section, the interaction phenomena between the SAW and the mobile charge carriers are examined; both linear and nonlinear phenomena are considered. In section 2.5 the theory is extended to inhomogeneous substrates, which involves the presence of active devices in the semiconductor. This theory is later used in the discussion of the active SAW detectors, which are described in Chapters 4 and 5. The influence of charges and traps in the layered structure is discussed in section 2.6. Besides the piezoelectric coupling mechanism in the ZnO layer, there is an additional coupling mechanism in the silicon substrate: the deformation potential coupling. This coupling mechanism is described in section 2.7.

#### 2.2 THE ACOUSTOELECTRIC FIELD PROBLEM

#### 2.2.1 Layered Configuration

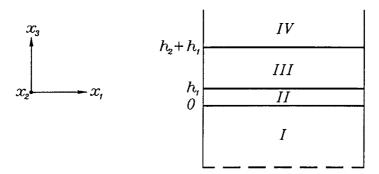

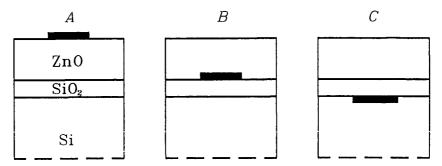

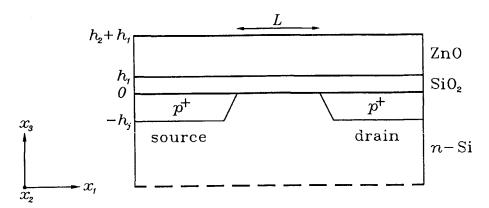

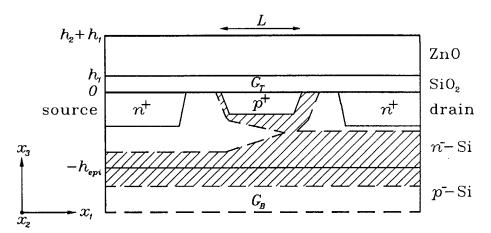

The general layered configuration which is considered in this chapter is shown in Fig. 2.1. A Cartesian coordinate system  $x_1, x_2, x_3$  is introduced such that the SiO<sub>2</sub>-Si interface is located at the plane  $x_3 = 0$ .

Figure 2.1: The considered layered configuration.

The semi-infinite substrate (region I) is a nonpiezoelectric, semiconducting silicon layer. Silicon has a cubic crystal lattice, which is anisotropic and of class  $m\Im m$ . On top of the silicon substrate an amorphous  $SiO_2$  layer (region II) with thickness  $h_1$  is present. This layer can be considered as an isotropic medium. The surface of the structure is covered with a piezoelectric ZnO layer (region III) of thickness  $h_2$ . The sputtered ZnO layer has a hexagonal crystal lattice of class 6mm with a preferred c-axis orientation perpendicular to the surface. Above the ZnO layer a semi-infinite vacuum is assumed (region IV).

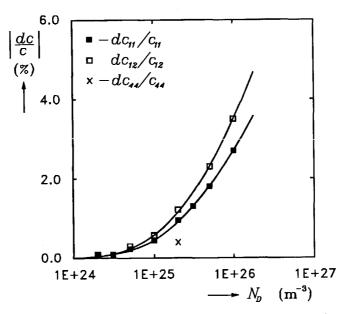

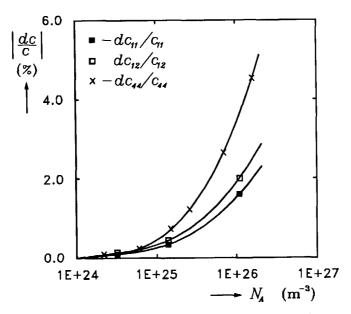

The elastic and electrical properties of this layered structure are determined by the material constants and the thicknesses of the individual layers. The dominant parameters are the stiffness tensor  $c_{ijkl}^E$  (determined at constant electric field), the dielectric permittivity tensor  $\epsilon_{ik}^S$  (determined at constant strain), and the mass density  $\rho_m$ . The acoustoelectric coupling is determined by the piezoelectric tensor  $e_{kij}$ . The values of the constants for the various layers at room temperature are given in Table 2.1, in which the Voigt notation for the tensor parameters is used. The values for the Si and SiO<sub>2</sub> layers are from Ono et al. [47]. The ZnO constants are from Carlotti et al. [48], who derived the data from sputtered ZnO films. The ZnO film constants are 10% to 25% lower than the corresponding

bulk constants. All theoretical results presented in this thesis have been obtained using the material constants of Table 2.1.

| <b>Table 2.1:</b> | Material    | constants | at $T =$ | = 300 K | of silicon, | silicon | dioxide ( | fused |

|-------------------|-------------|-----------|----------|---------|-------------|---------|-----------|-------|

| quartz), and      | l thin-film | ZnO.      |          |         |             |         |           |       |

|                                        |                        | Si      | $SiO_2$ | ZnO   |

|----------------------------------------|------------------------|---------|---------|-------|

| $\rho_m$                               | $10^3 \text{ kg/m}^3$  | 2.33    | 2.20    | 5.72  |

| $c_{11}^E$                             | 10 <sup>11</sup> Pa    | 1.66    | 0.785   | 1.57  |

| $c_{13}^E$                             |                        | 0.639   | 0.161   | 0.83  |

| $c_{33}^E$                             |                        | 1.66    | 0.785   | 2.08  |

| $c_{13}^{E} \ c_{33}^{E} \ c_{44}^{E}$ |                        | 0.796   | 0.312   | 0.38  |

| $e_{31}$                               | $\mathrm{C/m^2}$       |         |         | -0.51 |

| $e_{33}$                               | ļ                      |         |         | 1.22  |

| $e_{15}$                               |                        |         |         | -0.45 |

| $\epsilon_{11}$                        | $10^{-10} \text{ F/m}$ | 1.03594 | 0.33468 | 0.737 |

| $\epsilon_{33}$                        |                        | 1.03594 | 0.33468 | 0.782 |

#### 2.2.2 Basic Equations

The SAW propagation and the acoustoelectric interactions in this layered structure can be determined by solving a set of differential equations which describe the relationships between the mechanical field variables, stress and strain, and the electrical variables, electric field and electric displacement. The structure is assumed linear, time invariant and locally reacting. A coupling between the mechanical and electrical variables takes place through the piezoelectric behavior of the ZnO layer. In the following, the basic equations of each individual region are given. The tensor notation is used, and the summation convention on repeated subscripts is employed. A list of notations can be found at the end of this thesis.

For the solution of the wave propagation problem, the equation of motion, which is valid for the regions I to III, is essential

$$\rho_m \frac{\partial^2 u_i}{\partial t^2} = \frac{\partial T_{ij}}{\partial x_j} \qquad i, j = 1, 2, 3$$

(2.1)

where

| $ ho_m$  | mass density                      | $(kg/m^3)$ |

|----------|-----------------------------------|------------|

| $u_i$    | particle displacement             | (m)        |

| t        | time                              | (s)        |

| $T_{ij}$ | stress tensor                     | (Pa)       |

| $x_i$    | position in Cartesian coordinates | (m)        |

For the solution of the electric field, Poisson's equation must be applied

$$\frac{\partial D_i}{\partial x_i} = \rho_e \tag{2.2}$$

in which

$$D_i$$

electric displacement vector (C/m<sup>2</sup>)

$\rho_e$  electric charge density (C/m<sup>3</sup>)

The electric charge density  $\rho_e$  includes both the mobile charge carriers and the ionized atoms. Equation 2.2 is valid in all regions, but only in the conductive silicon substrate can the charge density be nonzero. Since the acoustic wave velocities are five orders of magnitude lower than the velocity of light, the magnetic fields can be ignored and electrostatic conditions can be assumed. In this case, the electric field components  $E_k$  (V/m) can be derived from a scalar potential  $\phi$  (V)

$$E_k = -\frac{\partial \phi}{\partial x_k} \tag{2.3}$$

Equations 2.1 and 2.2 are the fundamental relations of the acoustoelectric field problem. The following equations specify the electrical and elastic characteristics of the layers. The piezoelectric and elastic properties of regions I to III are described by the constitutive relations

$$T_{ij} = c_{ijkl}^E S_{kl} - e_{kij} E_k (2.4)$$

$$D_i = e_{ikl}S_{kl} + \epsilon_{ik}^S E_k \tag{2.5}$$

with i, j, k, l = 1, 2, 3, and the strain S defined as

$$S_{kl} = \frac{1}{2} \left( \frac{\partial u_k}{\partial x_l} + \frac{\partial u_l}{\partial x_k} \right) \tag{2.6}$$

and the material constants

| $c^E_{ijkl}$      | stiffness tensor at constant electric field       | (Pa)      |

|-------------------|---------------------------------------------------|-----------|

| $e_{kij}$         | piezoelectric tensor                              | $(C/m^2)$ |

| $\epsilon^S_{ik}$ | dielectric permittivity tensor at constant strain | (F/m)     |

The symmetry in  $T_{ij}$  and  $S_{kl}$  leads to  $c_{ijkl} = c_{jikl} = c_{ijlk} = c_{jilk}$  and  $e_{kij} = e_{kji}$ . For the nonpiezoelectric regions I and II,  $e_{kij}$  is zero, and the Eqs. 2.4, 2.5 reduce to Hooke's law and the definition of electric displacement, respectively.

In the conductive substrate (region I), mobile charge carriers are present, and the current equations must be added. Applying the Boltzmann approximation [49, p.84] the free hole and electron densities at thermal equilibrium are given by

$$p = n_i \exp\left[\frac{q(\psi_F - \psi_i)}{k_B T}\right] \tag{2.7}$$

$$n = n_i \exp\left[\frac{q(\psi_i - \psi_F)}{k_B T}\right] \tag{2.8}$$

with

| p              | free hole density                               | $(m^{-3})$ |

|----------------|-------------------------------------------------|------------|

| n              | free electron density                           | $(m^{-3})$ |

| $n_i$          | intrinsic electron density                      | $(m^{-3})$ |

| q              | electron charge; $q = 1.602 \cdot 10^{-19}$     | (C)        |

| $\dot{\psi}_F$ | potential associated with semiconductor         | (V)        |

|                | Fermi level                                     |            |

| $\psi_i$       | potential associated with intrinsic             | (V)        |

|                | Fermi level                                     |            |

| $k_B$          | Boltzmann constant; $k_B = 1.38 \cdot 10^{-23}$ | (J/K)      |

| $\overline{T}$ | temperature                                     | (K)        |

As a result of the mobile charge carriers and electric fields in the silicon region, currents flow which are described by

$$J_{p,i} = pq\mu_p E_i + qD_p \frac{\partial p}{\partial x_i}$$

(2.9)

$$J_{n,i} = nq\mu_n E_i - qD_n \frac{\partial n}{\partial x_i}$$

(2.10)

with i = 1, 2, 3, and

| $J_{p,i}$ | hole current-density vector     | $(A/m^2)$  |

|-----------|---------------------------------|------------|

| $J_{n,i}$ | electron current-density vector | $(A/m^2)$  |

| $\mu_p$   | hole mobility                   | $(m^2/Vs)$ |

| $\mu_n$   | electron mobility               | $(m^2/Vs)$ |

| $D_p$     | hole diffusion coefficient      | $(m^2/s)$  |

| $D_n$     | electron diffusion coefficient  | $(m^2/s)$  |

and by the continuity equations for holes and electrons (generation and recombination effects are ignored)

$$\frac{\partial J_{p,i}}{\partial x_i} = -q \frac{\partial p}{\partial t} \tag{2.11}$$

$$\frac{\partial J_{n,i}}{\partial x_i} = q \frac{\partial n}{\partial t} \tag{2.12}$$

In addition to the equations given above, the boundary conditions at the interface planes between the different regions must be taken into account. At the interface between ZnO and the vacuum  $(x_3 = h_1 + h_2)$ , a traction-free surface is assumed. Therefore, the normal component of the stress  $T_3$  vanishes here. At all other interfaces, the normal stress component must be continuous. This also applies to the particle displacement  $u_i$  and the potential  $\phi$ . Since no surface charges are assumed, the normal component of the electric displacement field  $D_3$  must be continuous at each interface plane. Finally, since the SiO<sub>2</sub> and ZnO layers are insulating, no current is assumed for  $x_3 > 0$  and the normal component of the current density must vanish at the silicon surface.

An analytical solution to the problem is severely hindered by the non-linear relations, which describe the semiconductor properties, see Eqs. 2.7 to 2.12. A strong reduction of complexity is obtained when an insulating substrate is assumed. In this case, the semiconductor and current equations vanish, and a lossless propagation medium results. A solution to the propagation problem can then be obtained by determining the zeros of the determinant, which is constituted by the equations. Venema [50] has shown that pure Rayleigh-wave propagation is possible in this system, provided a proper wave direction with respect to the anisotropic silicon crystal is adopted. The general solutions are time-harmonic plane waves of the form

$$A\exp(jkbx_3)\exp\left[j(kx_1-\omega t)\right] \tag{2.13}$$

in which k is wavenumber and  $\omega$  the angular frequency. Since the considered layered system is dispersive, the wavenumber is not constant, but depends on  $\omega$ . The wave motions described in Eq. 2.13 are confined to the sagittal  $(x_1, x_3)$  plane and have no components in the  $x_2$ -direction. With these straight-crested waves, the problem is reduced to a two-dimensional one. The constant factors A and b are fixed by the boundary conditions, the piezoelectric coupling, and the power of the wave. For (100) silicon, pure Rayleigh-wave propagation is possible in the [001] direction, whereas the (111) cut requires a [11 $\bar{2}$ ] propagation direction. The theoretical and experimental results given in this thesis are all based on the (100)[001] silicon system. The layered structure gives rise to higher-order wave modes with subsequent higher phase velocities. In this chapter, the term SAW is restricted to Rayleigh waves of which only the first mode is considered.

A more rigorous solution method is described by Ghijsen and Van den Berg [51, 52], who reduce the problem to a dual-boundary-value problem in  $\phi$  and J at one of the interfaces. All numerical results in this thesis of the SAW velocity in a lossless configuration have been obtained using computer programs based on this method. With the inclusion of mobile charge carriers which interact with the SAW, a lossy medium results, and the complexity of the problem is highly increased.

Other methods, such as the perturbation [53] and the normal mode theory [54] can be applied, but these methods are limited to homogeneous substrates. When diffused and implanted regions are added, which represent active SAW detectors or other piezotronic elements, the problems become formidable and untractable when using the above-mentioned solution methods. For the investigation of such devices, only the potential distribution in the silicon region is of importance. Therefore, another method has been developed, in which the influence of the acoustic wave is reduced to a surface charge, which is located at the ZnO-SiO<sub>2</sub> interface. The problem is then reduced to a mere electrical one, in which only Poisson's equation has to be solved. This method is described in the next section.

### 2.2.3 Equivalent-Surface-Charge Method

The acoustoelectrical problem can be reduced to an electrical one, provided the weak-coupling approximation can be applied. This approximation assumes that the mechanical field variables are virtually unperturbed by the presence of free charge carriers in the silicon [55]. It can be applied as long as the piezoelectric coupling is small, which is the case in the considered ZnO layered structures.

Because of the piezoelectricity in the ZnO layer, the stress component  $S_{kl}$ , which is of the form of Eq. 2.13, creates a periodic piezoelectric polarization charge distribution  $\rho_{pe}$  in this layer. This charge distribution can be obtained with Eqs. 2.2 and 2.5. Since the ZnO layer is assumed insulating ( $\rho_e = 0$ )

$$\frac{\partial}{\partial x_i} (\epsilon_{ik}^S E_k) = -\frac{\partial}{\partial x_i} (e_{ikl} S_{kl}) \tag{2.14}$$

in which  $\partial(\epsilon_{ik}^S E_k)/\partial x_i$  represents the dielectric polarization charge  $\rho_{\epsilon}$ , and  $\partial(\epsilon_{ikl}S_{kl})/\partial x_i$  the piezoelectric polarization charge  $\rho_{pe}$ . The piezoelectric polarization charge can be obtained by determining  $S_{kl}$  using one of the afore-mentioned analytical methods, assuming an insulating silicon substrate. In the weak-coupling approximation the mechanical variable  $S_{kl}$  is not perturbed by the presence of mobile charge carriers in the silicon, nor is the piezoelectric polarization charge  $\rho_{pe}$ . Therefore, the acoustoelectric interaction can be determined by inserting this piezoelectric charge in region III of the layered structure, which may now contain active junction devices and mobile charge carriers in the substrate. The electrical problem can be solved with the two-dimensional Poisson equation

$$\frac{\partial}{\partial x_{i}} (\epsilon_{ij}^{S} \frac{\partial \phi}{\partial x_{j}}) = -q(p - n + N_{D^{+}} - N_{A^{-}}) \text{ in region I}$$

$$0 \text{ in region II}$$

$$\frac{\partial}{\partial x_{i}} (e_{ikl} S_{kl}) \text{ in region III}$$

$$0 \text{ in region IV}$$

in which  $N_{D^+}$  and  $N_{A^-}$  represent the ionized donor and acceptor densities, respectively.

This two-step method requires the solution of the mechanical field variable  $S_{kl}$  in the ZnO layer, in order to determine  $\rho_{pe}$  in the electrical solution method. However, for the interaction under consideration, we are only interested in the potential distribution in the SiO<sub>2</sub> and Si regions, or  $x_3 < h_1$ . For this situation a much simpler method can be applied, in which the piezoelectric polarization charge  $\rho_{pe}$  is replaced by an equivalent surface charge  $\rho_s$ , which is located at the ZnO-SiO<sub>2</sub> interface. This fictitious surface charge  $\rho_s$  is chosen such that it causes the same potential distribution for  $x_3 < h_1$  as the volume charge  $\rho_{pe}$ .

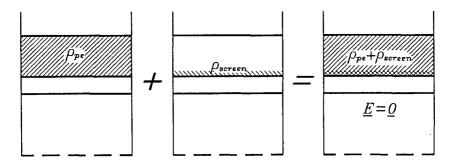

The equivalent surface charge can be determined by placing an infinitesimally thin, perfectly conducting metal sheet at the plane  $x_3 = h_1$ .

This metal sheet completely screens the electric fields induced in the ZnO layer. As a result, the electric field  $E_k$  vanishes for  $x_3 < h_1$ . The screening is accomplished by an induced (surface) charge distribution  $\rho_{screen}$  at the metal shield, which exactly cancels the electric fields for  $x_3 < h_1$ . Because all relations are assumed linear, the resulting system can be considered as a superposition of a system only containing  $\rho_{pe}$  and a system only containing  $\rho_{screen}$ . Since  $E_k = 0$  for  $x_3 < h_1$  in the superposed system,  $\rho_{pe}$  and  $\rho_{screen}$  create an equal but opposite potential distribution in the SiO<sub>2</sub> and Si regions, as is illustrated in Fig. 2.2. As a result, the volume charge

Figure 2.2: Superposition of volume charge  $\rho_{pe}$  and screening charge  $\rho_{screen}$ .

$\rho_{pe}$  and the surface charge  $-\rho_{screen}$  give the same potential distribution for  $x_3 < h_1$ , and the desired equivalent surface charge  $\rho_s$  is given by

$$\rho_s = -\rho_{screen} \tag{2.16}$$

The magnitude of  $\rho_s$  can be obtained analytically, provided the power of the wave and the piezoelectric coupling strength are known. This is discussed in the next section. The method described here is denoted as the *Equivalent-Surface-Charge* method.

It is here emphasized that the Equivalent-Surface-Charge (ESC) method assumes electrostatic conditions. When mobile charge carriers are involved, their dynamic properties should be taken into account. The static approach can be applied as long as the response or transit time of the carriers is much shorter than the wave period  $1/\omega$ . The ESC method can be applied at any interface below the ZnO layer. However, it must be taken into account that only the electrical solution beneath this interface is significant.

Summarizing, the Equivalent-Surface-Charge method reduces the acoustoelectric field problem in the semiconducting substrate of the ZnO-SiO<sub>2</sub>-Si structure to a mere electric field problem. The polarization phenomena induced by the SAW in the ZnO layer are represented by an equivalent surface charge, which is located at the ZnO-SiO<sub>2</sub> interface. Since the weak-coupling approximation is assumed, this surface charge is not influenced by the electrical conditions in the silicon substrate. Therefore, it can most easily be determined in a layered structure with a homogeneous, insulating substrate. This is performed in section 2.3.1. With this equivalent surface charge, the acoustoelectrical problem in a layered structure with a complex substrate structure can be solved. The problem is reduced to solving the Poisson equation. This method can be implemented in numerical solution methods using finite-element or finite-difference techniques, which are commonly used for the two-dimensional calculations on active semiconductor devices. In the next subsection, the strength of the equivalent surface charge  $\rho_s$  is derived.

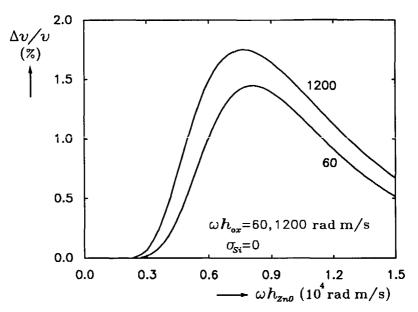

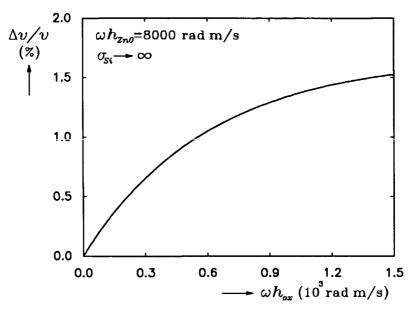

### 2.2.4 Piezoelectric Coupling

The coupling between the mechanical and electric field variables is determined by the strength of the piezoelectric phenomenon. The coupling strength determines the transduction efficiency of SAW generation and detection, and determines the strength of the interaction between the acoustic wave and the mobile charge carriers. The coupling strength can be represented by the piezoelectric or electromechanical coupling factor  $\kappa^2$ , which is proportional to the piezoelectric tensor  $e_{kij}$ , and is inversely proportional to the stiffness and dielectric tensors  $c_{ijkl}$  and  $\epsilon_{ik}$  [56]. In the one-dimensional case of longitudinal bulk waves, it can be shown that this coupling factor is the ratio between the electric potential (or stored) energy and the total potential energy [57]. The coupling factor can be determined by observing the change in the phase velocity  $v_{ph}$  when the insulating piezoelectric medium is replaced by a perfectly conducting piezoelectric medium. In the latter case, the electric fields are short-circuited, which results in an unstiffening of the elastic material and in a decrease of the wave velocity. Therefore, the velocity change is a measure of the electric field strength in the unperturbed case. For weak-piezoelectric materials,  $\Delta v/v \ll 1$ , and the coupling factor can be approximated with  $\kappa^2 \approx 2\Delta v/v$ .

Essentially, the piezoelectric coupling factor is a bulk parameter. Therefore, it is not very convenient to use it in the SAW case. However, the piezoelectric coupling strength can still be determined by measuring the

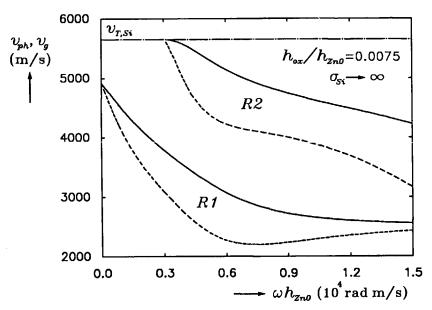

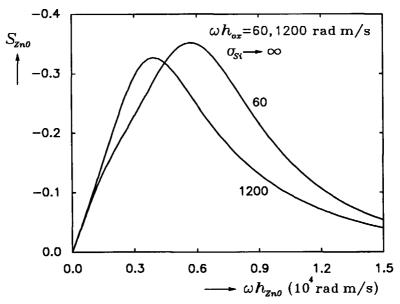

relative velocity change  $\Delta v/v$  when an infinitesimally thin, perfectly conducting plate is placed at the surface of the propagation medium [58]. Therefore, only the factor  $\Delta v/v$  is used throughout this work. In the layered configuration, the coupling strength  $\Delta v/v$  can be determined at any interface by inserting a conductive plate at the interface plane under consideration. The value of  $\Delta v/v$  depends on the material parameters and the layer thicknesses. Computer programs, based on Ghijsen's method [52], have been developed to predict the  $\Delta v/v$  value.

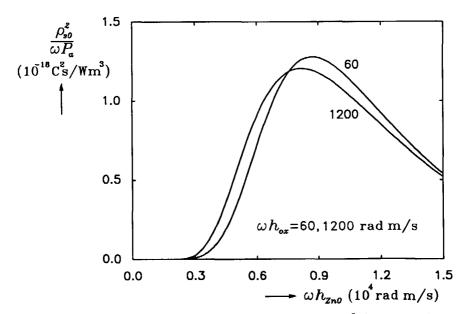

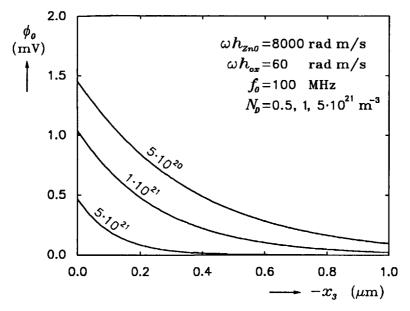

Two parameters, which are strongly related to  $\Delta v/v$ , and are of importance for the description of the coupling mechanism in the layered structure, are the potential  $\phi$  and the equivalent surface charge  $\rho_s$ , both normalized to the SAW power flow  $P_a$  (W/m). It is assumed that they are plane wave solutions of the form

$$\phi = \phi_0(x_3) \exp[j(kx_1 - \omega t)] \tag{2.17}$$

$$\rho_s = \rho_{s0}(x_3) \exp[j(kx_1 - \omega t)]$$

(2.18)

These strongly related parameters can be derived from the normal mode theory [59]. This was performed by Kino and Wagers in order to determine the admittance of a transducer in a layered structure [60]. By using their theory, the values of  $\phi_0^2/P_a$  and  $\rho_{s0}^2/P_a$  can be determined at any interface. The following discussion is restricted to the plane at  $x_3 = h_1$ . From [60] it can be derived that

$$\frac{\phi_0^2}{P_a}\Big|_{h_1} = \frac{4}{v_{ph}} \frac{\phi_0}{\rho_{screen,0}} \left. \frac{\Delta v}{v} \right|_{h_1}$$

(2.19)

where  $v_{ph}$  is the SAW phase velocity, and  $\rho_{screen,0}$  the magnitude of the screening charge. A similar expression was found by Lakin [53], who applied the perturbation theory. The ratio  $\phi_0/\rho_{screen,0}$  is a constant, which only depends on the material constants and the layer thicknesses. Because  $\rho_{s0} = -\rho_{screen,0}$ , Eq. 2.19 suffices to obtain both  $\phi_0^2/P_a$  and  $\rho_{s0}^2/P_a$ .

In order to evaluate  $\phi_0/\rho_{s0}$ , it is convenient to introduce an effective dielectric permittivity [61] in each layer, which is defined by

$$\epsilon_{eff}(x_3) = \frac{D_3(x_3)}{k\phi(x_3)} \tag{2.20}$$

These effective constants are purely electrical, and can be derived by solving the Poisson equation. The effective permittivity is continuous across each interface plane, except for the one which contains the equivalent surface charge. The equivalent surface charge causes a discontinuity in the

normal displacement field, and is thus related to the effective permittivities

$$\rho_{s}|_{h_{1}} = \lim_{x_{3} \downarrow h_{1}} D_{3} - \lim_{x_{3} \uparrow h_{1}} D_{3}$$

$$= (\epsilon_{eff,U} - \epsilon_{eff,L}) \cdot k\phi(h_{1})$$

(2.21)

in which  $\epsilon_{eff,U}$  and  $\epsilon_{eff,L}$  are the upper and lower effective dielectric permittivities above and below the plane of interest (here  $x_3 = h_1$ ) defined by

$$\epsilon_{eff,U}(h_1) = \lim_{x_3 \downarrow h_1} \frac{D_3(x_3)}{k\phi(x_3)}$$

(2.22)

$$\epsilon_{eff,L}(h_1) = \lim_{x_3 \uparrow h_1} \frac{D_3(x_3)}{k\phi(x_3)}$$

(2.23)

Equation 2.21 fixes the relation between the equivalent surface charge and the potential at  $x_3 = h_1$ , and is the central equation of the Equivalent-Surface-Charge method. By using Eqs. 2.19 and 2.21, the parameters  $\phi_0^2/P_a$  and  $\rho_{s0}^2/P_a$  at  $x_3 = h_1$  can now be expressed in the upper and lower effective permittivities at  $x_3 = h_1$

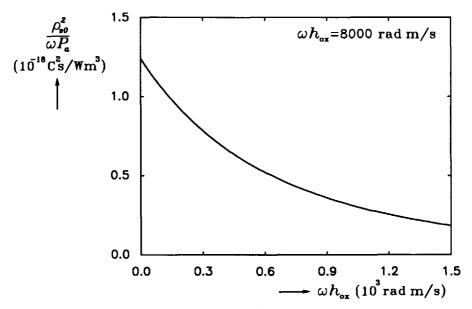

$$\frac{\phi_0^2}{P_a}\Big|_{h_1} = \frac{4}{v_{ph}} \frac{1}{k(\epsilon_{eff,U} - \epsilon_{eff,L})_{h_1}} \frac{\Delta v}{v}\Big|_{h_1}$$

(2.24)

$$\frac{\rho_{s0}^2}{P_a}\bigg|_{h_1} = \frac{4}{v_{ph}} k(\epsilon_{eff,U} - \epsilon_{eff,L})_{h_1} \frac{\Delta v}{v}\bigg|_{h_1}$$

(2.25)

The ratio  $\rho_{s0}^2/P_a$  can be considered as a new coupling factor. It should be noted, that in the weak-coupling case,  $\phi_0$  is affected by the presence of free charge carriers, but  $\rho_{s0}$  is not. By using Eq. 2.25 in the unperturbed case to obtain  $\rho_{s0}$ , and inserting this in Eq. 2.21 with the effective permittivities of the perturbed case, the potential distribution in the perturbed case can be calculated. In the next section, the unperturbed case (homogeneous substrate, free of charge) is considered in order to evaluate  $\rho_{s0}$  in the layered structure. This  $\rho_{s0}$  can then be used in the subsequent sections 2.4 and 2.5, where the acoustoelectric field problem for conductive and inhomogeneous substrates is examined.

#### 2.3 HOMOGENEOUS INSULATING SUBSTRATE

### 2.3.1 Equivalent Surface Charge