Delft University of Technology

## Strained silicon quantum wells for spin qubits

Degli Esposti, D.

**DOI**

[10.4233/uuid:a925b226-ca58-491e-8c6d-e0d4ff3d98fb](https://doi.org/10.4233/uuid:a925b226-ca58-491e-8c6d-e0d4ff3d98fb)

**Publication date**

2025

**Document Version**

Final published version

**Citation (APA)**

Degli Esposti, D. (2025). *Strained silicon quantum wells for spin qubits*. [Dissertation (TU Delft), Delft University of Technology]. <https://doi.org/10.4233/uuid:a925b226-ca58-491e-8c6d-e0d4ff3d98fb>

**Important note**

To cite this publication, please use the final published version (if applicable).

Please check the document version above.

**Copyright**

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

**Takedown policy**

Please contact us and provide details if you believe this document breaches copyrights.

We will remove access to the work immediately and investigate your claim.

# Strained silicon quantum wells for spin qubits

Davide Degli Esposti

# **STRAINED SILICON QUANTUM WELLS FOR SPIN QUBITS**

# **STRAINED SILICON QUANTUM WELLS FOR SPIN QUBITS**

## **Dissertation**

Dissertation for the purpose of obtaining the degree of doctor

at Delft University of Technology

by the authority of the Rector Magnificus, prof. dr. ir. T.H.J.J. van der Hagen,

chair of the Board for Doctorates

to be defended publicly on

Monday 14 April 2025 at 17:30

by

**Davide DEGLI ESPOSTI**

Master of Science in Physics,

Università di Pisa, Pisa, Italy,

born in Teramo, Italy.

This dissertation has been approved by the promotors

promotor: prof. dr. ir. L.M.K. Vandersypen

copromotor: dr. G. Scappucci

Composition of the doctoral committee:

Rector Magnificus,

prof. dr. ir. L.M.K. Vandersypen

dr. G. Scappucci

chairperson

Delft University of Technology, promotor

Delft University of Technology, copromotor

*Independent members:*

prof. dr L. DiCarlo

dr. A. Chatterjee

prof. dr. M. Friesen

prof. dr. K. De Greve

Delft University of Technology

Delft University of Technology

University of Wisconsin-Madison, USA

IMEC and KU Leuven, Belgium

*Reserve member:*

prof. dr G.A. Steele

Delft University of Technology

*Keywords:* Si/SiGe heterostructure, Valley splitting, Charge Noise, Spin qubits

*Printed by:* Gildeprint - [www.gildeprint.nl](http://www.gildeprint.nl)

*Front & Back:* Artistic impression of a STEM image of a strained Si quantum well & tilted SEM image of four quantum dots device on a Si/SiGe heterostructure.

Copyright © 2025 by D. Degli Esposti

ISBN 978-94-6384-734-6

An electronic version of this dissertation is available at

<https://resolver.tudelft.nl/uuid:955fab3d-fc33-4ccb-8c58-c6eaf7b56c9c>.

*Felix qui potuit rerum cognoscere causas*

Lucrezio, Geordiche, (2), 490

# CONTENTS

|                                                                                               |           |

|-----------------------------------------------------------------------------------------------|-----------|

| <b>Summary</b>                                                                                | <b>ix</b> |

| <b>Samenvatting</b>                                                                           | <b>xi</b> |

| <b>1 Introduction</b>                                                                         | <b>1</b>  |

| 1.1 The first quantum revolution . . . . .                                                    | 2         |

| 1.2 The second quantum revolution . . . . .                                                   | 2         |

| 1.2.1 The DiVincenzo criteria . . . . .                                                       | 4         |

| 1.3 Development cycle of silicon-based materials for spin qubits. . . . .                     | 5         |

| 1.4 Thesis outline . . . . .                                                                  | 7         |

| <b>2 Semiconductor stacks: theoretical considerations</b>                                     | <b>13</b> |

| 2.1 Material stacks for semiconductor quantum dots . . . . .                                  | 14        |

| 2.2 Si/SiGe heterostructure . . . . .                                                         | 18        |

| 2.2.1 Band structure . . . . .                                                                | 18        |

| 2.2.2 Strained heterostructures . . . . .                                                     | 20        |

| 2.3 Material challenges and metrics . . . . .                                                 | 22        |

| 2.3.1 Disorder . . . . .                                                                      | 22        |

| 2.3.2 Valley splitting . . . . .                                                              | 24        |

| 2.3.3 Strain noise . . . . .                                                                  | 26        |

| 2.3.4 Charge noise . . . . .                                                                  | 27        |

| 2.3.5 Magnetic noise. . . . .                                                                 | 28        |

| <b>3 Methods</b>                                                                              | <b>39</b> |

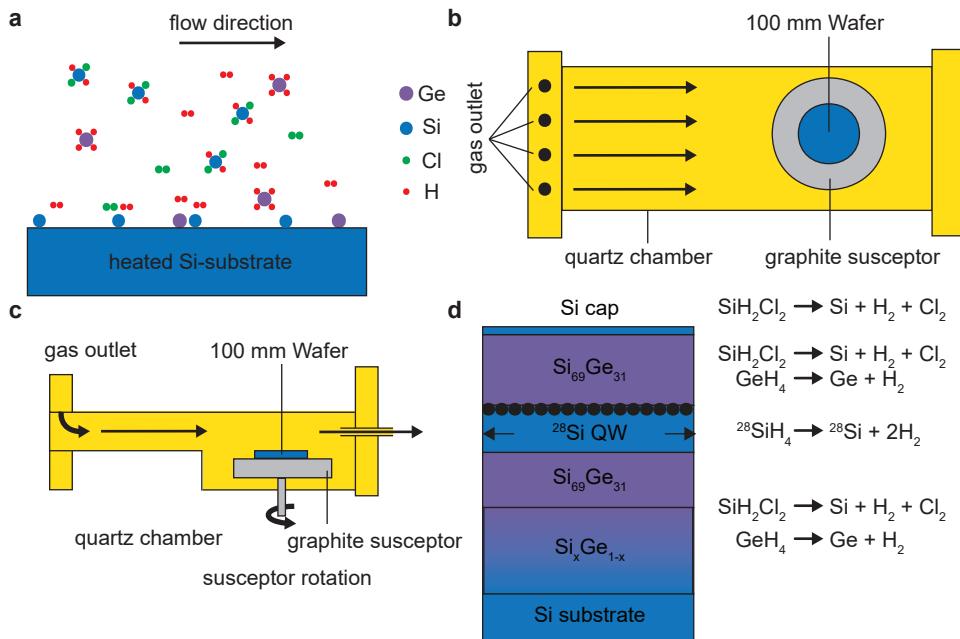

| 3.1 Epitaxy of Si/SiGe heterostructures . . . . .                                             | 40        |

| 3.2 Structural characterization . . . . .                                                     | 42        |

| 3.3 Device fabrication . . . . .                                                              | 44        |

| 3.3.1 Pre-nanofabrication . . . . .                                                           | 44        |

| 3.3.2 Nanofabrication . . . . .                                                               | 45        |

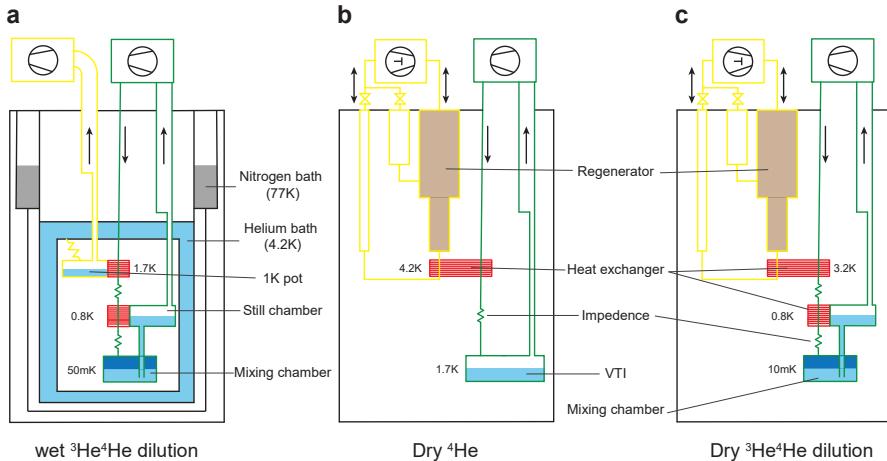

| 3.4 Experimental setup for cryogenic measurements. . . . .                                    | 46        |

| 3.4.1 Hallbar measurement . . . . .                                                           | 47        |

| 3.4.2 Quantum dot measurements . . . . .                                                      | 48        |

| <b>4 <math>^{28}\text{Si}/\text{SiGe}</math> heterostructures without an epitaxial Si cap</b> | <b>53</b> |

| 4.1 Introduction . . . . .                                                                    | 54        |

| 4.2 $^{28}\text{Si}/\text{SiGe}$ heterostructures . . . . .                                   | 54        |

| 4.3 Electrical characterization at 1.7 K . . . . .                                            | 57        |

| 4.4 Discussion . . . . .                                                                      | 61        |

| 4.5 Supplementary . . . . .                                                                   | 62        |

---

|                                                                                 |            |

|---------------------------------------------------------------------------------|------------|

| <b>5 Reducing charge noise in quantum dots by using a thin Si quantum well</b>  | <b>69</b>  |

| 5.1 Introduction . . . . .                                                      | 70         |

| 5.2 Results . . . . .                                                           | 70         |

| 5.2.1 Description of Si/SiGe heterostructures . . . . .                         | 70         |

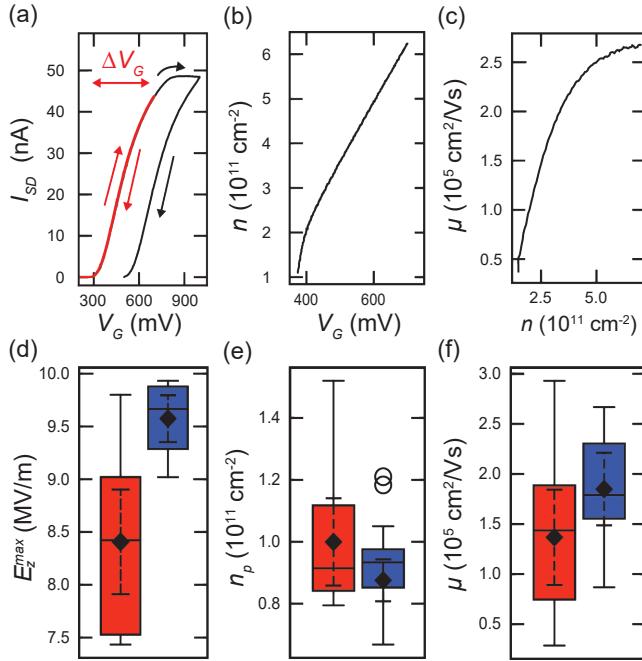

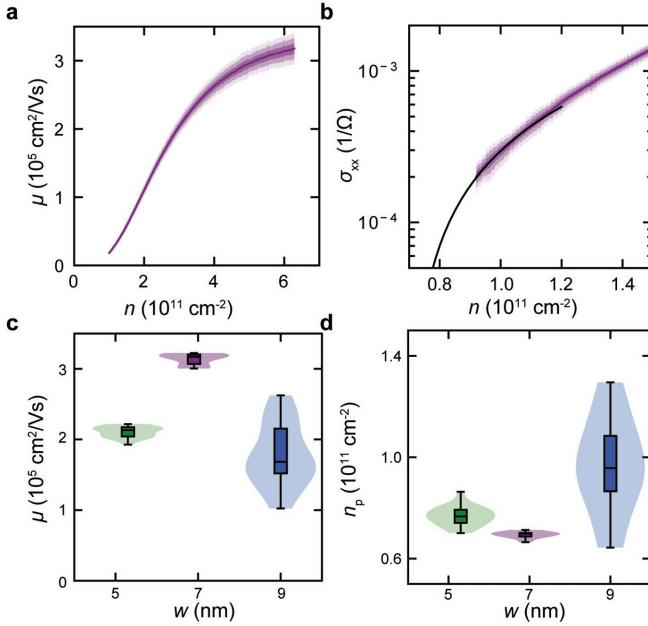

| 5.2.2 Electrical characterization of H-FETs . . . . .                           | 72         |

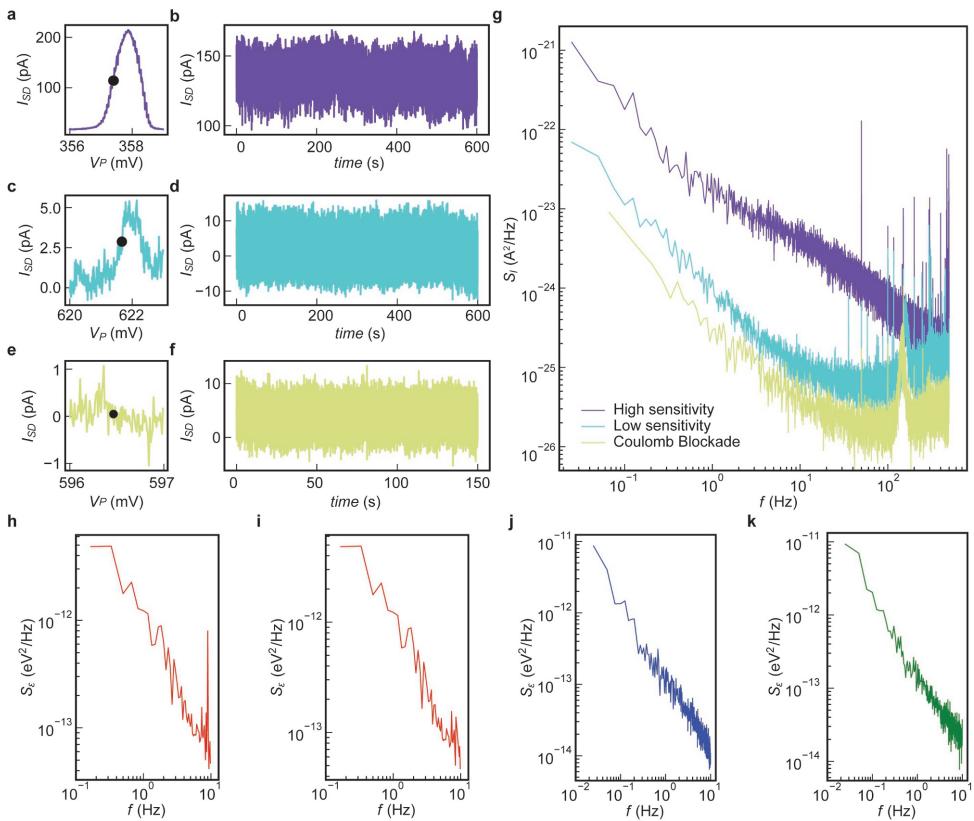

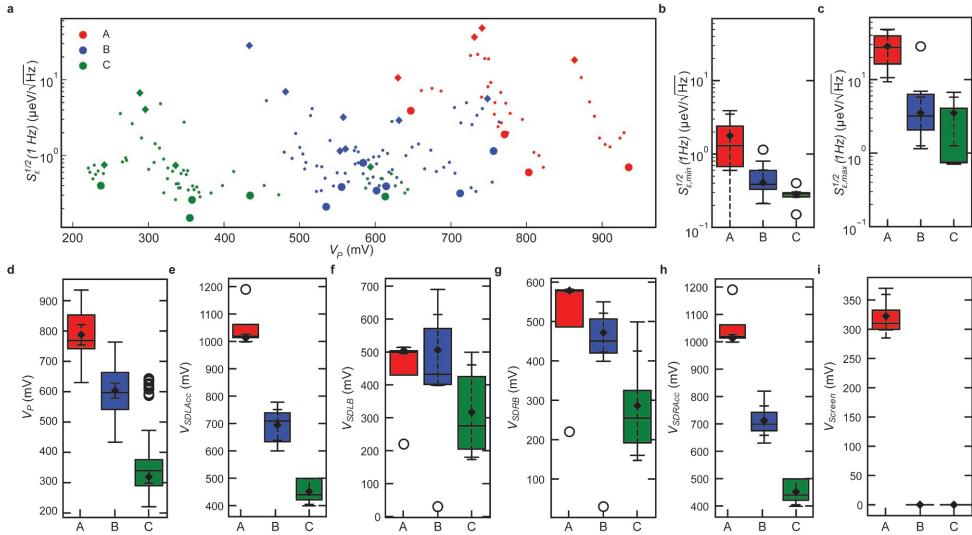

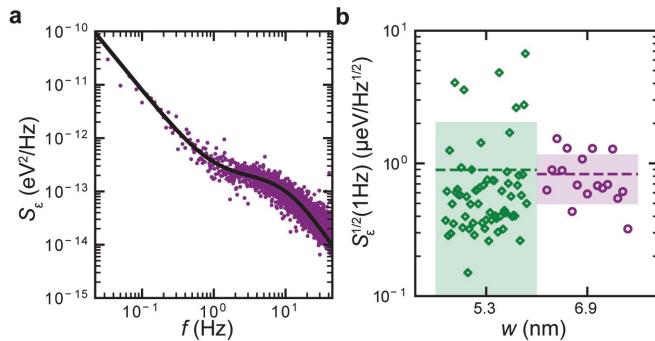

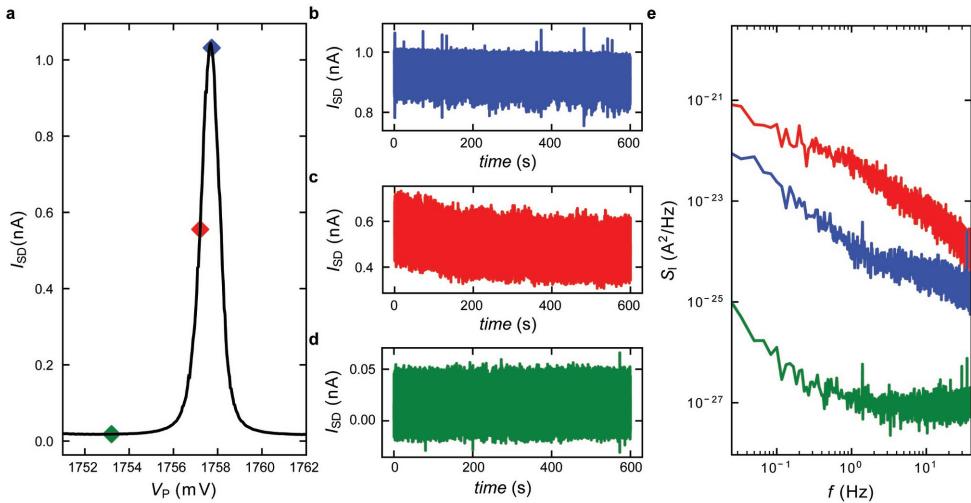

| 5.2.3 Charge noise measurements in quantum dots . . . . .                       | 72         |

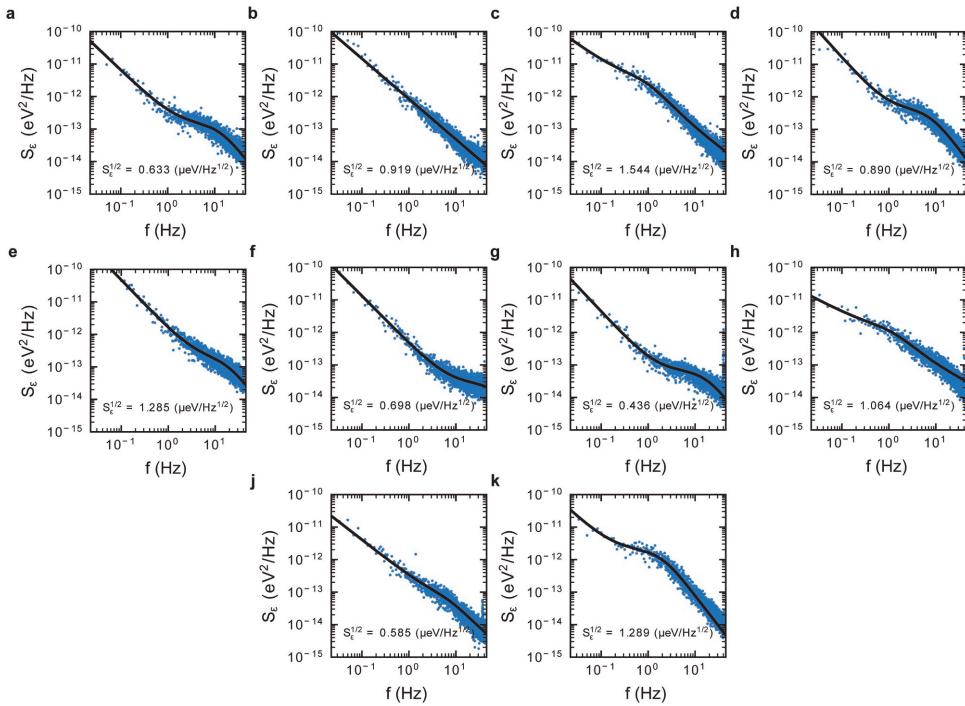

| 5.2.4 Distribution of transport properties and charge noise . . . . .           | 74         |

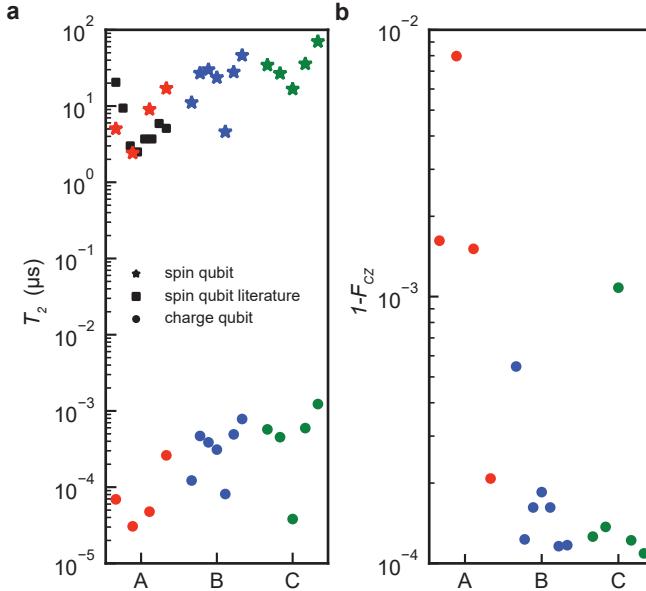

| 5.2.5 Calculated dephasing time and infidelity . . . . .                        | 76         |

| 5.2.6 Discussion . . . . .                                                      | 78         |

| 5.3 Methods . . . . .                                                           | 78         |

| 5.4 Supplementary . . . . .                                                     | 80         |

| <b>6 Low disorder and high valley splitting in silicon</b>                      | <b>93</b>  |

| 6.1 Introduction . . . . .                                                      | 94         |

| 6.2 Results . . . . .                                                           | 95         |

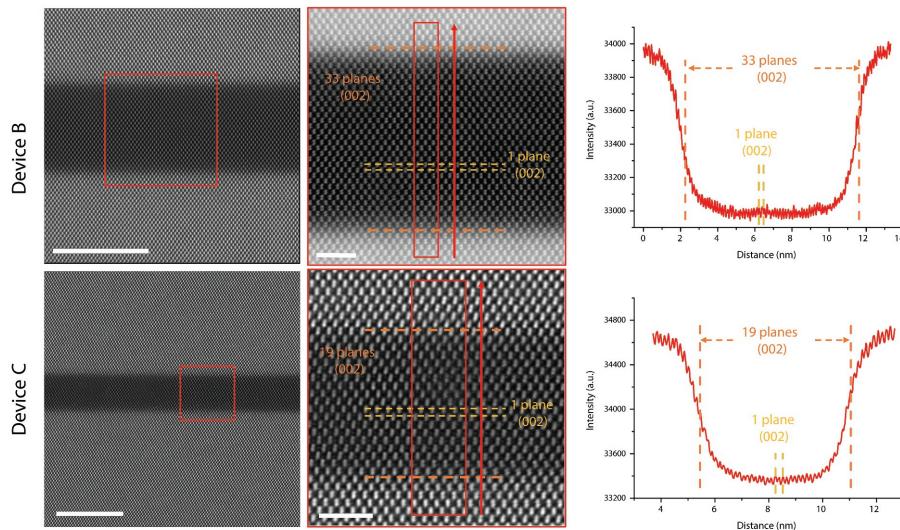

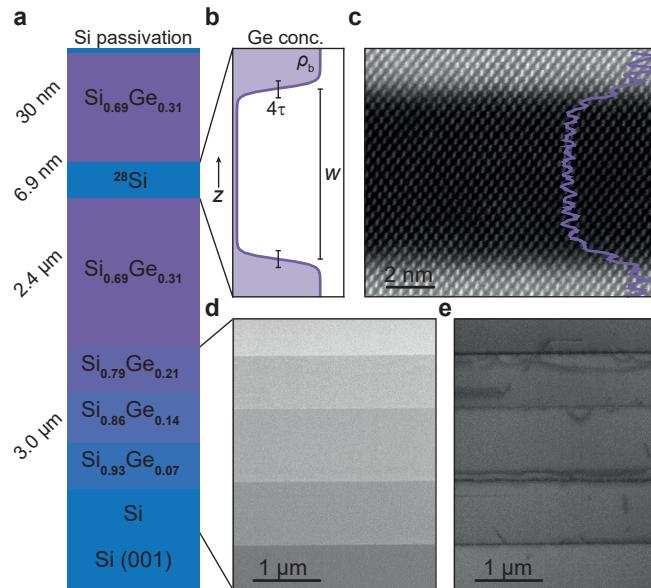

| 6.2.1 Description of $^{28}\text{Si}/\text{SiGe}$ heterostructures . . . . .    | 95         |

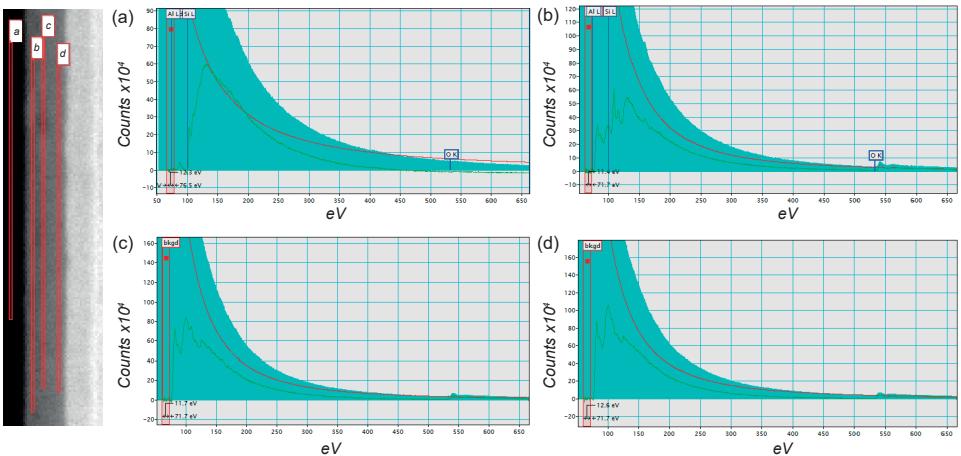

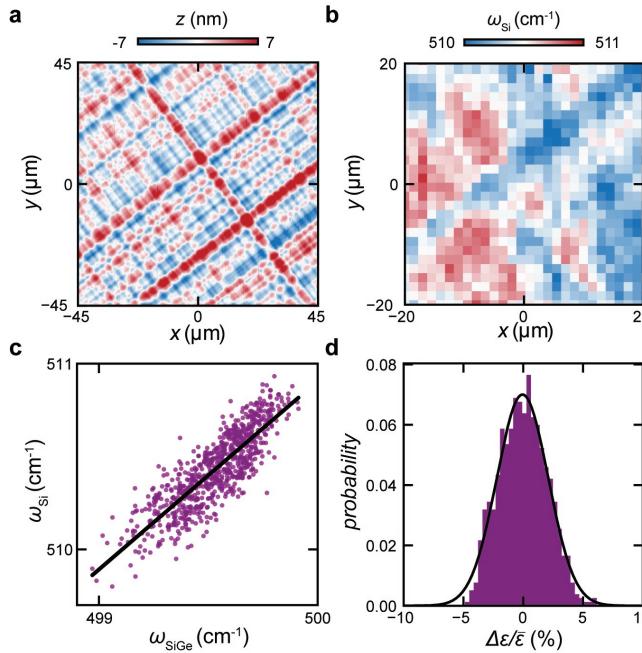

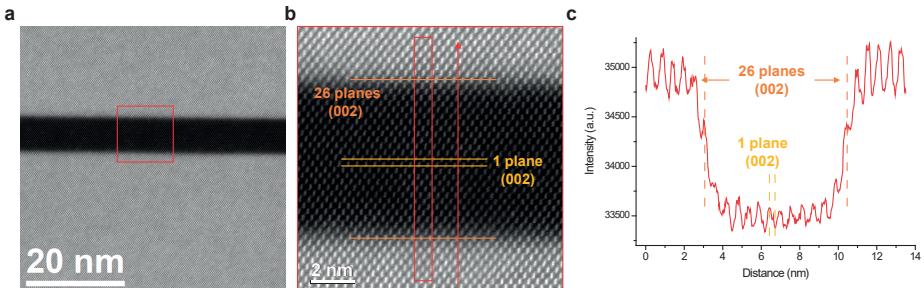

| 6.2.2 Characterisation of strain distribution . . . . .                         | 97         |

| 6.2.3 Electrical characterisation of heterostructure field effect transistors . | 98         |

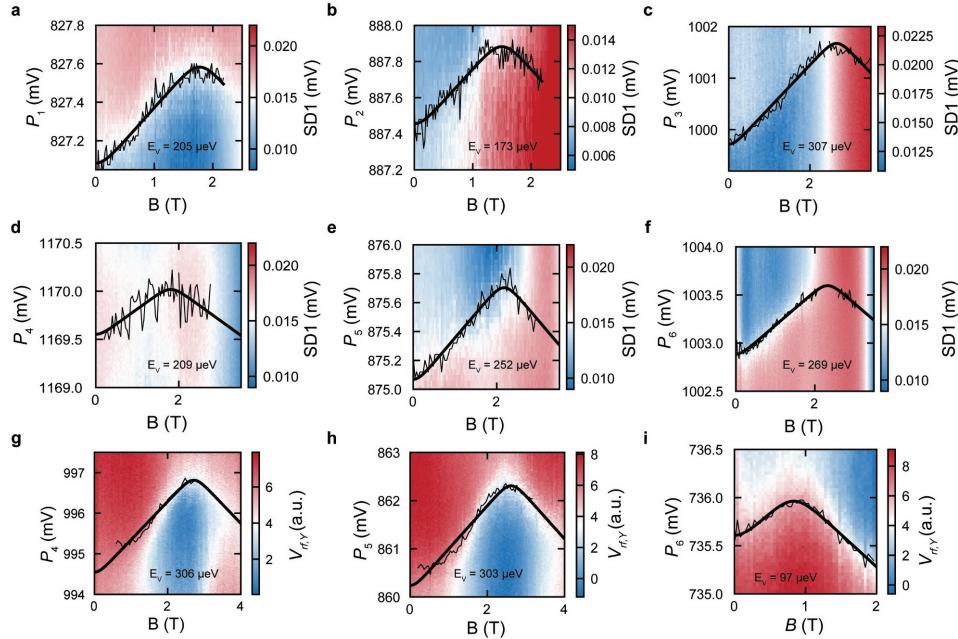

| 6.2.4 Charge noise measurements in quantum dots . . . . .                       | 100        |

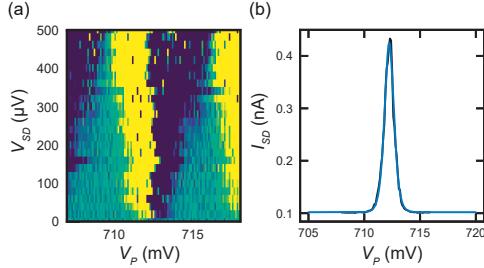

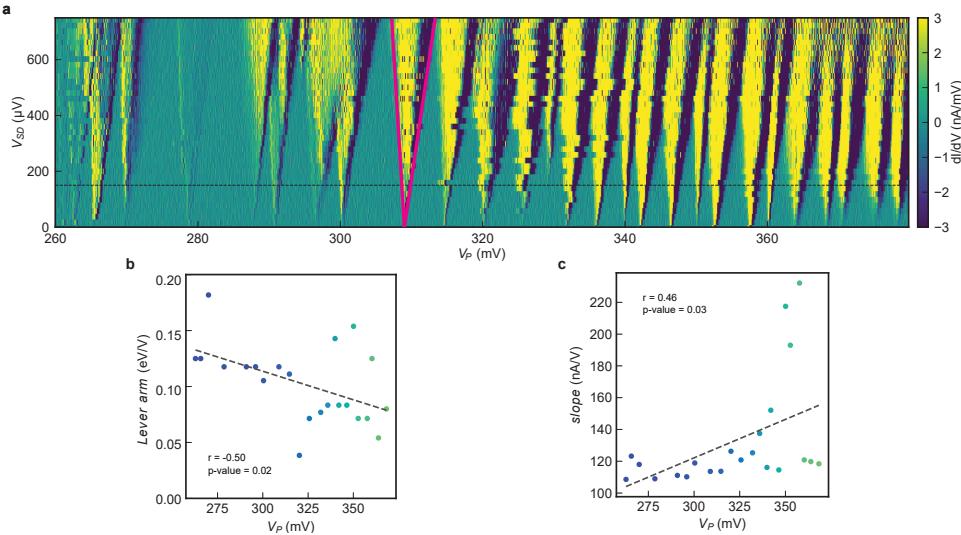

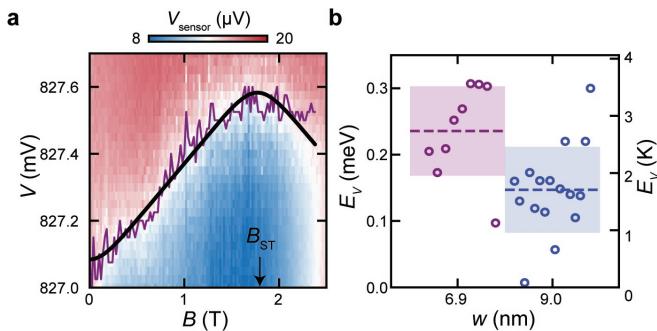

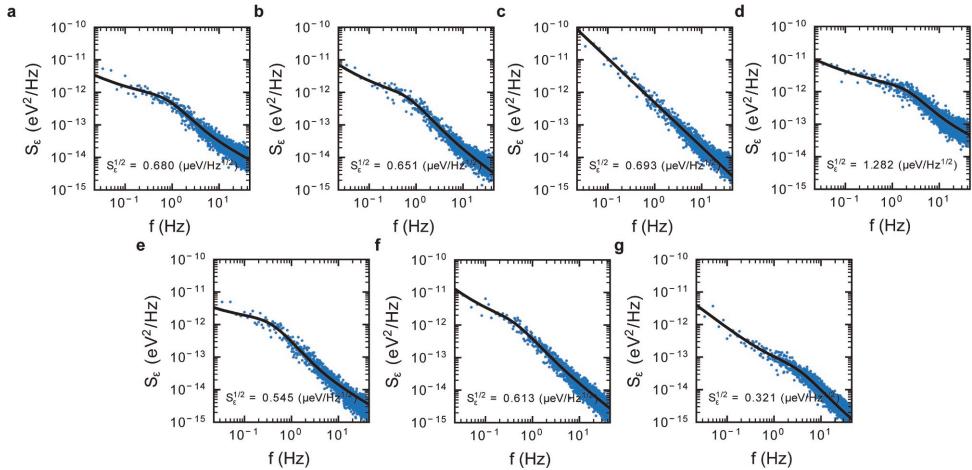

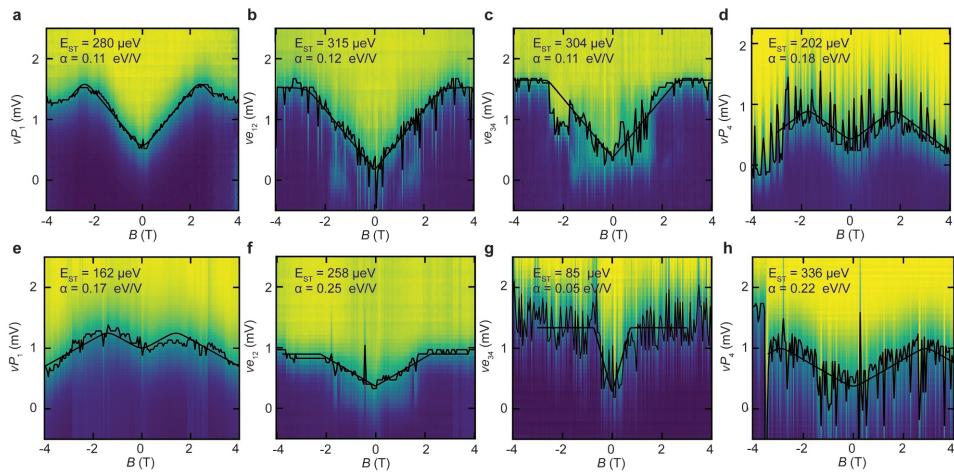

| 6.2.5 Valley splitting measurements in quantum dots . . . . .                   | 101        |

| 6.2.6 Discussion . . . . .                                                      | 103        |

| 6.3 Methods . . . . .                                                           | 104        |

| 6.4 Supplementary . . . . .                                                     | 106        |

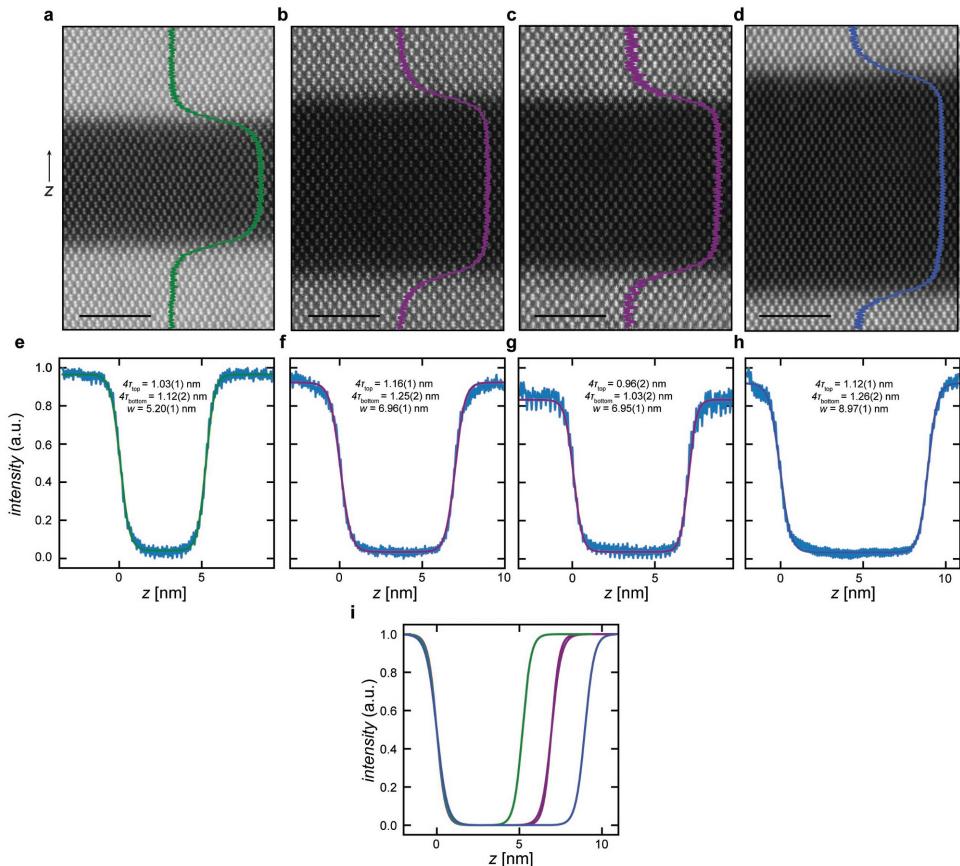

| 6.4.1 Measurement of the thickness and sharpness of the quantum wells .         | 106        |

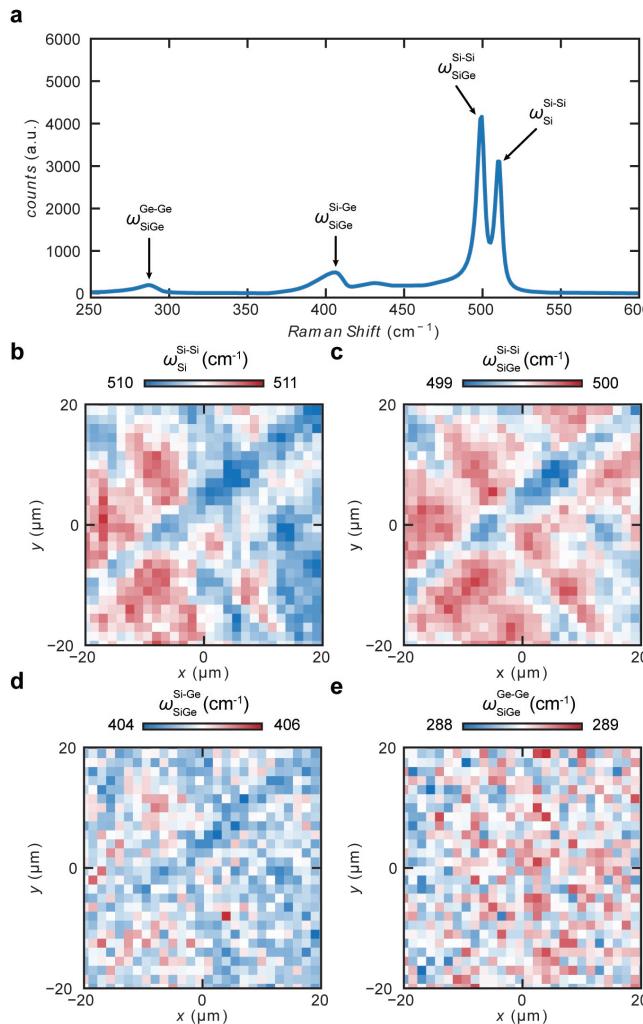

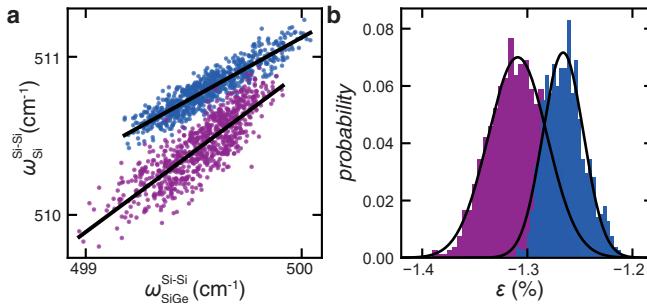

| 6.4.2 Strain analysis with Raman spectroscopy . . . . .                         | 109        |

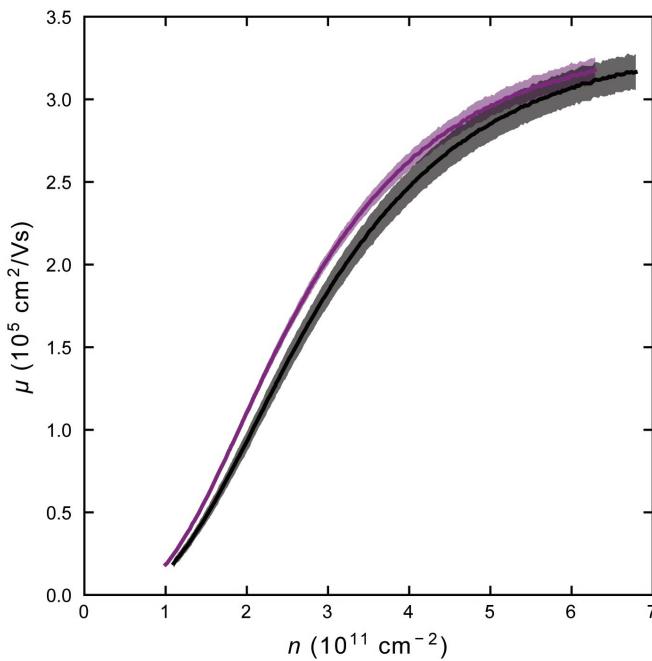

| 6.4.3 Supplementary mobility density curves . . . . .                           | 111        |

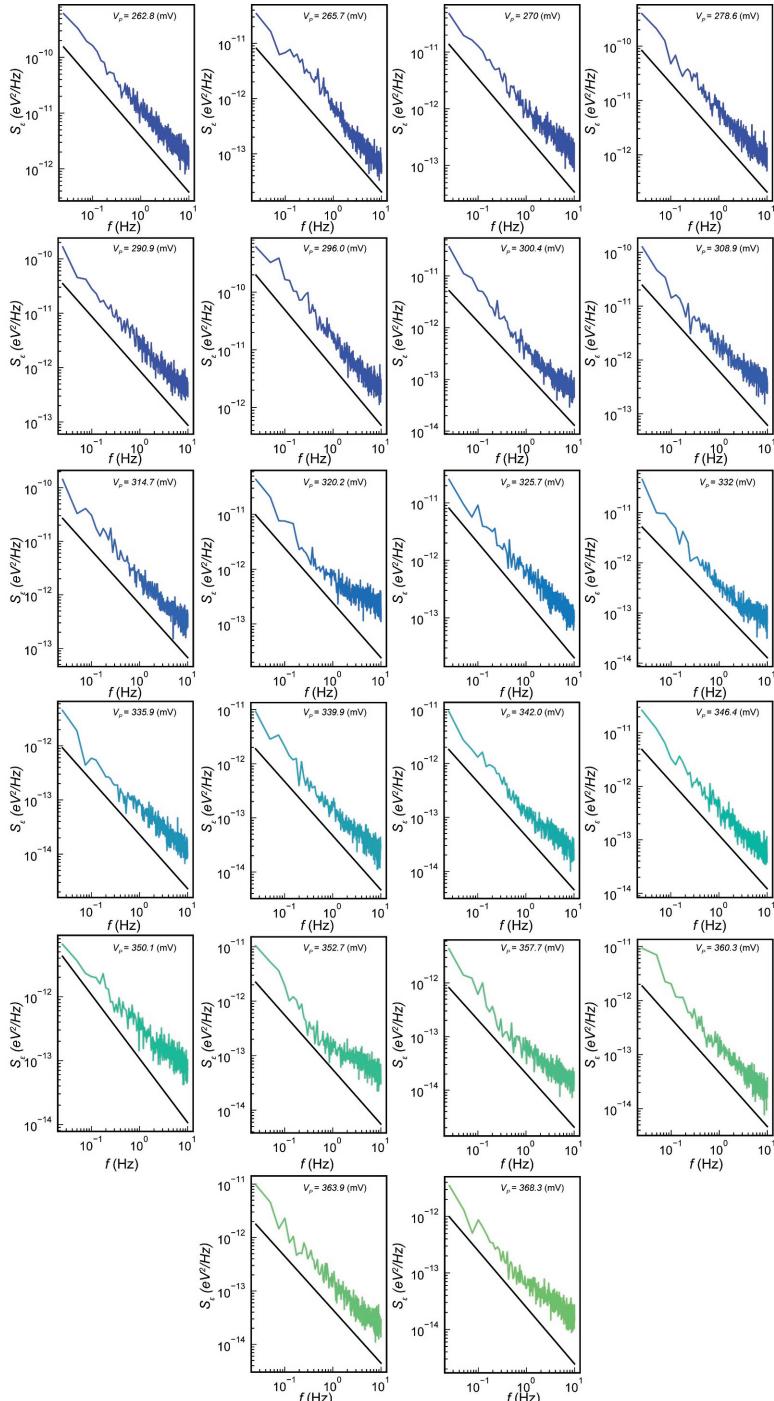

| 6.4.4 Charge noise measurements . . . . .                                       | 112        |

| 6.4.5 Valley splitting measurements . . . . .                                   | 115        |

| <b>7 Discussion and outlook</b>                                                 | <b>125</b> |

| 7.1 Noise and addressability . . . . .                                          | 127        |

| 7.2 Valleys and Single-Triplet splitting . . . . .                              | 128        |

| 7.3 Future Si/SiGe heterostructures . . . . .                                   | 129        |

| <b>Acknowledgements</b>                                                         | <b>133</b> |

| <b>Curriculum Vitæ</b>                                                          | <b>137</b> |

| <b>List of Publications</b>                                                     | <b>139</b> |

# SUMMARY

Spin qubits in semiconductor quantum dots hold great promises for quantum information processing thanks to their small footprint, long coherence time, and similarities with classical transistors. However, such a new technology comes with new challenges and requires considering new metrics to develop proof-of-principle devices into a technological platform at scale.

Here, we study Si/SiGe heterostructures developed to host single electron spin qubits. We characterize the heterostructure and material stack using different structural techniques and measure the performances of multiple quantum devices with statistical significance. We use classical and quantum metrics to identify the performance-limiting mechanisms and improve them upon modification of selected parameters of the material stack to enable the next generation of spin qubit devices.

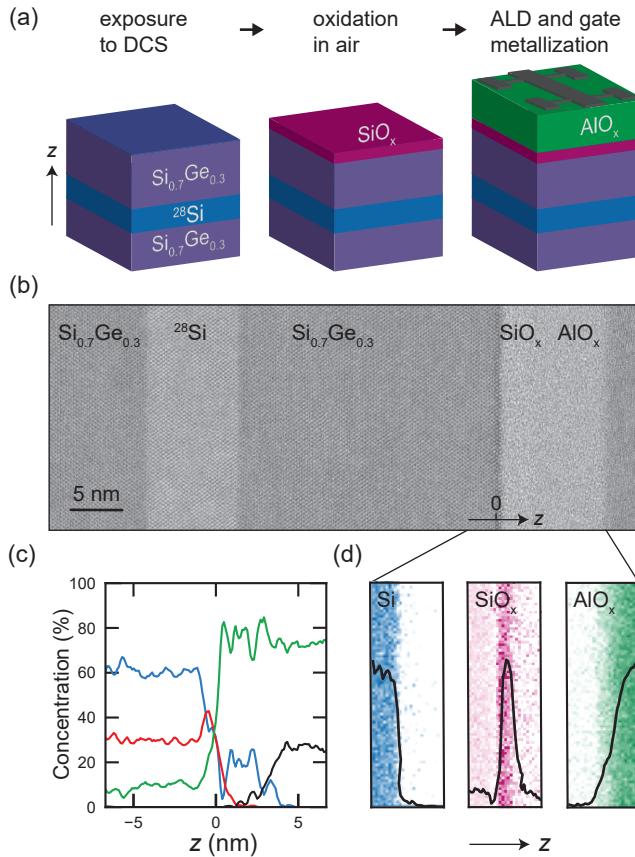

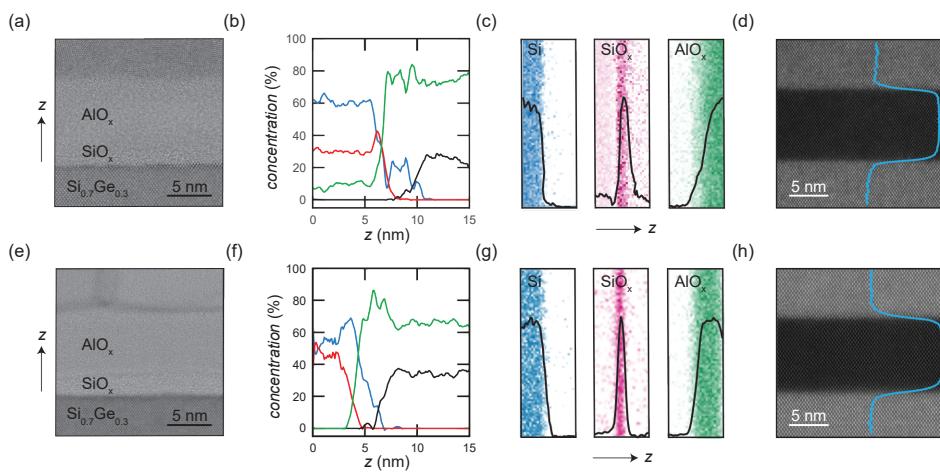

The first experiment is about the electrostatics of undoped Si/SiGe heterostructures. We study the semiconductor/dielectric interface between the epitaxial SiGe spacer and the SiO<sub>x</sub> and AlO<sub>x</sub> dielectrics. Against the mainstream approach, we grow heterostructures without an epitaxial Si cap. We find an improved interface from a structural characterization and in the two-dimensional electron transport at low temperatures.

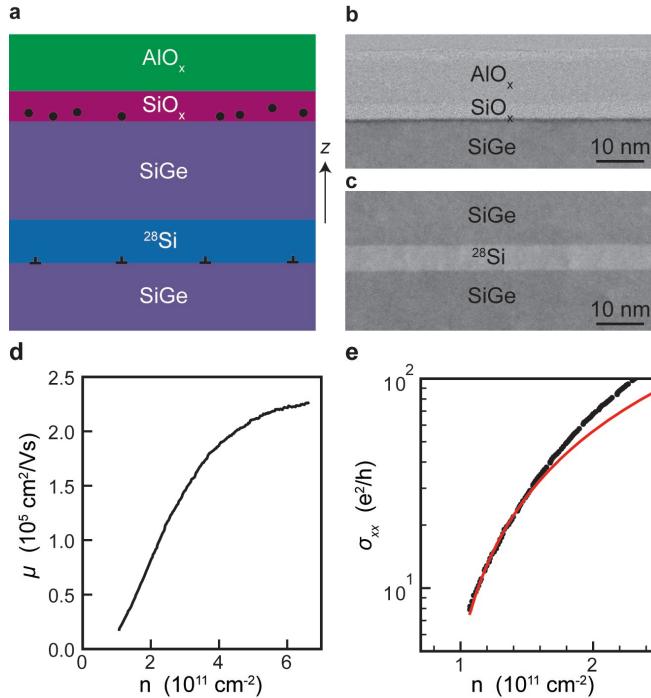

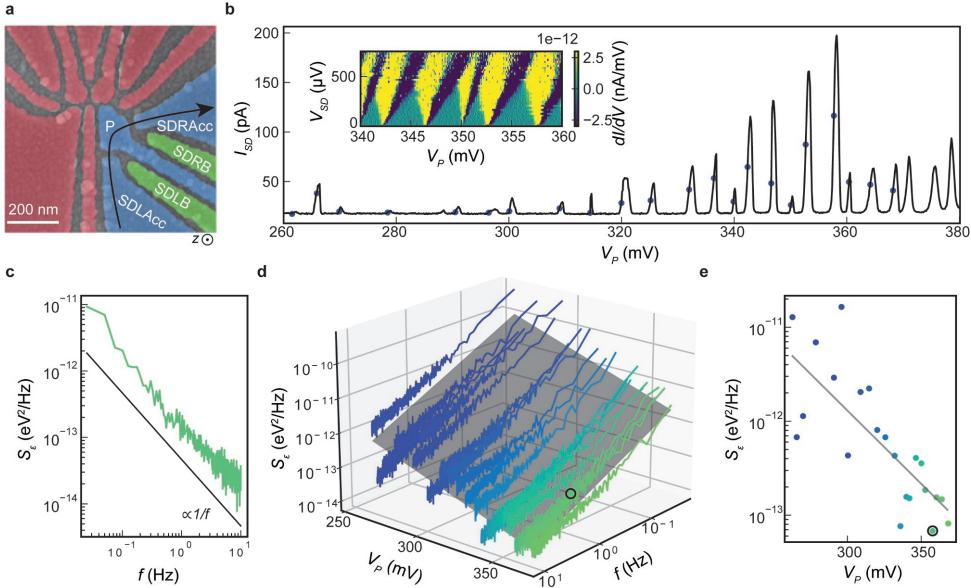

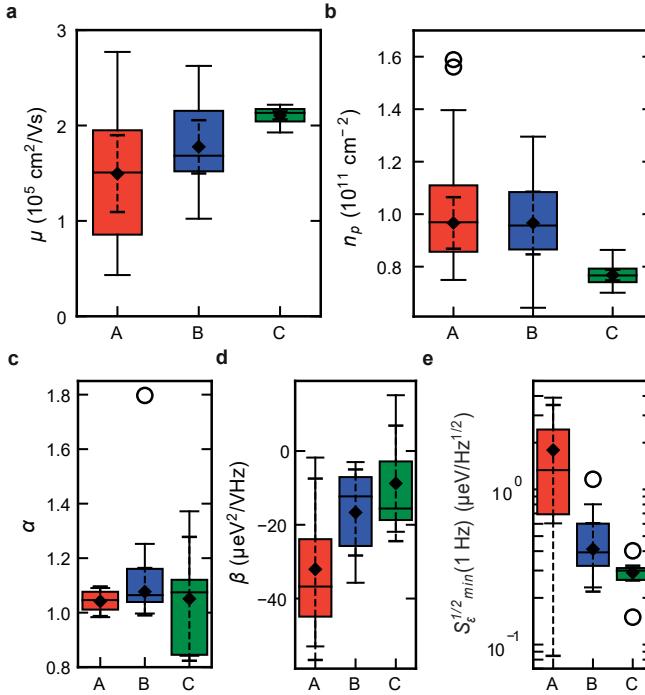

The second experiment concerns the charge noise in few-electron quantum dots. We build on the previous results and focus our attention on the thickness of the <sup>28</sup>Si quantum well. In thin quantum wells without a sacrificial Si cap, we find lower charge noise that we attribute to decreased density of remote impurities and misfit dislocations at the SiGe/Si and Si/SiGe interfaces arising from the local quantum well strain relaxation.

The third experiment finds the balance between disorder and the energy splitting of the nearly degenerate conduction band valleys (valley splitting) by fine-tuning the thickness of the <sup>28</sup>Si quantum well. We challenge the apparent dichotomy between these two parameters and demonstrate heterostructures with simultaneously low disorder and high valley splitting. Besides, we give a quantitative estimation of the amplitude of the strain fluctuations in the quantum well arising from the virtual substrate.

The advancements reported in this thesis confirm the steady progress of the Si/SiGe platform towards realizing a full-scale quantum computer. We summarize the results in the conclusion chapter, where we also highlight the general trends in the spin qubit community and suggest a few knobs to tweak to further improve the material platform.

# SAMENVATTING

Spin qubits in halfgeleider quantum dots houden grote beloften in voor quantuminformatieverwerking dankzij hun kleine voetafdruk, lange coherentietijd en overeenkomsten met klassieke transistors. Zo'n nieuwe technologie brengt echter nieuwe uitdagingen met zich mee en vereist het overwegen van nieuwe metrieken om proof-of-principle apparaten te ontwikkelen tot een technologisch platform op schaal.

Hier bestuderen we Si/SiGe heterostructuren die zijn ontwikkeld om spin qubits met één elektron te bevatten. We karakteriseren de heterostructuur en de materiaalstapel met verschillende structurele technieken en meten de prestaties van meerdere kwantumapparaten met statistische significantie. We gebruiken klassieke en kwantummetrieken om de prestatiebeperkende mechanismen te identificeren en deze te verbeteren door geselecteerde parameters van de materiaalstapel aan te passen om de volgende generatie spin-qubitapparaten mogelijk te maken.

Het eerste experiment gaat over de elektrostatica van ongedoteerde Si/SiGe heterostructuren. We bestuderen de halfgeleider/diëlektrische interface tussen de epitaxiale SiGe spacer en de SiO<sub>x</sub> en AlO<sub>x</sub> diëlektrica. Tegen de gangbare aanpak in, kweken we heterostructuren zonder een epitaxiale Si kap. We vinden een verbeterde interface vanuit een structurele karakterisatie en in het tweedimensionale elektronentransport bij lage temperaturen.

Het tweede experiment betreft de ladingsruis in kwantumstippen met weinig elektronen. We bouwen voort op de vorige resultaten en richten onze aandacht op de dikte van de <sup>28</sup>Si kwantumput. In dunne kwantumputten zonder een Si opofferingskapje vinden we een lagere ladingsruis die we toeschrijven aan een verminderde dichtheid van onzuiverheden op afstand en misfit dislocaties bij de SiGe/Si en Si/SiGe interfaces als gevolg van de lokale rekrelaxatie van de kwantumput.

Het derde experiment vindt het evenwicht tussen wanorde en de energiesplitsing van de bijna ontaarde geleidingsbanddalen (dalsplitsing) door de dikte van de quantumput <sup>28</sup>Si nauwkeurig af te stellen. We bestrijden de schijnbare dichotomie tussen deze twee parameters en tonen heterostructuren met tegelijkertijd een lage wanorde en een hoge dalsplitsing. Bovendien geven we een kwantitatieve schatting van de amplitude van de vervormingsfluctuaties in de kwantumput die het gevolg zijn van het virtuele substraat.

De in dit proefschrift gerapporteerde vooruitgang bevestigt de gestage vooruitgang van het Si/SiGe platform in de richting van het realiseren van een full-scale quantumcomputer. We vatten de resultaten samen in het concluderende hoofdstuk, waar we ook de algemene trends in de spin qubit gemeenschap belichten en een paar knoppen suggereren om aan te draaien om het materiaalplatform verder te verbeteren.

# 1

## INTRODUCTION

*A digital computer is generally believed to be an efficient universal computing device...

...This may not be true when quantum mechanics is taken into consideration.*

P. W. Shor, arXiv:quant-ph/9508027, 1995

---

Parts of this introduction follow a lecture from Steven Girvin [1].

1

## 1.1. THE FIRST QUANTUM REVOLUTION

Quantum mechanics describes nature's behaviour at atomic scales and low energies. The theory arose in the early decades of the 20th century to explain experiments on black-body radiation [2], light-matter interaction [3], and interference [4]. The experiments forced into play the idea of wave-particle duality – that matter particles can behave like waves and light waves can act like particles. This simple idea has proven to be an extremely precise description of physical reality. It underlines nearly all the scientific and technological breakthroughs associated with the *so-called first quantum revolution*.

This first quantum revolution took place in the first half of the 20<sup>th</sup> century, with scientists busy with apparently useless and curiosity-driven experiments that ultimately led to technological inventions with a huge impact on society. The atomic clock was invented in 1955 [5] to test some specific hypotheses of special and general relativity [6]. However, it turned out that the possibility of measuring time within a few nanoseconds could be translated into the ability to measure position within a few meters, known today as the Global Positioning System (GPS). The inventors of the laser in 1960 [7] were trying to perform precise spectroscopic measurements of the hyperfine structure of atoms [8]. They did not expect their invention to be used to play music or to transport information across large distances through fiber optic communication. The transistor was created in 1947 to take over the vacuum tube [9, 10]. It led to the integrated circuit [11], and its exponential scale-down in price and size made it the most produced component in human history [12]. Today, we produce 20 trillion transistors per second ( $20\,000\,000\,000\,000\,000\text{ s}^{-1}$ ).

All these inventions radically changed society and share some common characteristics. The founders of quantum mechanics did not foresee these quantum devices. The inventors of these quantum devices did not foresee their applications. Most importantly, these quantum devices do not take full advantage of the power of quantum mechanics.

## 1.2. THE SECOND QUANTUM REVOLUTION

Some years after the realization that nature is not classical, it was understood that simulations at the quantum level are resource-expensive and, especially, become exponentially demanding with the system size [13, 14]. From this, the idea of using quantum mechanics to simulate quantum mechanics [13] and to build a *quantum computing* machine. Basically, to fight fire with fire.

The possible applications of such a machine are extensive, ranging from pharmaceuticals (drug design) and agriculture (nitrogen fixation) to the sustainability of our planet (energy storage and transportation, and carbon capture) [15]. A quantum computer will be an extremely efficient machine also for the factorization in prime numbers[16], a problem at the basis of encryption, the calculus of logarithms, and the unstructured search [17]. Still, a quantum computer will probably be able to do much more than this, and as it happened with classical computers, the only way to find this out is to build it.

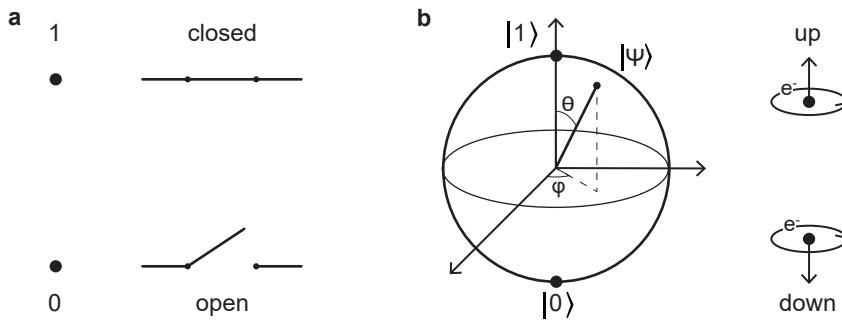

At the basis of quantum information processing, there is the quantum bit (qubit). Like classical bits, this is the smallest unit of information. It is implemented as a well-defined two-level quantum system in which the ground ( $|0\rangle$ ) and excited ( $|1\rangle$ ) states work as the substitutes for the "1" and "0" or "*True*" and "*False*" of classical bits. On the other side, qubits can leverage two quantum properties that make them much more powerful

Figure 1.1: **Graphical representations of a classical and quantum bit.** **a** A classical bit can be either in a 1 (*True*) or 0 (*False*) state. This can be physically implemented using, for example, an electrical switch that can be either "open" or "closed." **b** A quantum bit (qubit) can be in any state  $|\Psi\rangle$  superposition of the two states  $|0\rangle$  and  $|1\rangle$ . This can be represented as a point on the surface of a sphere, so-called *Bloch sphere*, and parameterized by the angles  $\theta$  and  $\phi$ . It can be physically implemented by using the spin's state of an electron, which can be in any superposition of the "up" and "down" states.

than classical bits: *superposition* and *entanglement*.

Superposition is the property of a quantum system to be in multiple quantum states at the same time—for a qubit to be simultaneously in both the  $|0\rangle$  and  $|1\rangle$  states. Mathematically, any qubit state ( $|\Psi\rangle$ ) can be expressed as:

$$|\Psi\rangle = \alpha|0\rangle + \beta|1\rangle \quad (1.1)$$

where  $|0\rangle$  and  $|1\rangle$  are called basis states, and  $\alpha$  and  $\beta$  are complex coefficients ( $\alpha^2 + \beta^2 = 1$ ). Therefore, every quantum state can be visualized as a point on the surface of a sphere (fig. 1.1), commonly called *Bloch sphere*.

Superposition is a game-changer for computational power. While classical bits can be initialized in either one of the two states and have to perform the computation for each one, quantum systems can be initialized in both states at the same time and complete the computation only once. As the number of states scales exponentially with the number of qubits, a quantum computer could be exponentially more efficient. Already, 20 qubits can assume more than 1 million configurations in parallel ( $2^{20}$ ).

Entanglement manifests as non-classical correlations affecting distant qubits. Let us imagine that a specific quantum state describing two qubits is:

$$|\Psi\rangle = \alpha|0\rangle|0\rangle + \beta|1\rangle|1\rangle \quad (1.2)$$

where  $\alpha$  and  $\beta$  are complex coefficients, and the first number between brackets refers to the state of the first qubits and the second number to the second qubit. If we measure the first qubit in the  $|0\rangle$  state, then we immediately know the second qubit to be in the  $|0\rangle$  state. If we measure the first qubit in the  $|1\rangle$  state, then we immediately know the second qubit to be in the  $|1\rangle$  state. Entanglement acts as a magic wire connecting multiple qubits, allowing us to operate and measure them simultaneously without the need to "actually" act on all of them.

The combination of these two principles, superposition and entanglement, leads to a massive parallelism of the computation. Not because of computation speed but rather

because the computation power and the complexity of tasks scale differently with problem size.

However, the power of a quantum computer is also its Achilles' heel. While the only possible error in a classical bit is the bit flip — either a "0" misinterpreted as a "1" or vice versa — qubits are susceptible to an infinitely larger number of errors. Any unwanted rotation or movement on the Bloch sphere is a possible quantum error. As a consequence, it is very easy to leak the quantum information through a process known as *decoherence*. Decoherence sets how long the quantum information can be stored and, as a consequence, how many quantum operations can be performed in series. One of today's most researched problems in quantum information processing is to limit decoherence and preserve information losses. The challenge is to build a nearly perfect system out of very imperfect components.

### 1.2.1. THE DIVINCENZO CRITERIA

While the theory and motivation to pursue a quantum computer are clear, multiple physical platforms still compete to host a quantum processor. To be able to compare and evaluate different systems, David DiVincenzo formulated a series of requirements that a scalable quantum computing platform must satisfy [18]:

- A scalable physical system with well-characterized qubit.

- The ability to initialize the state of the qubits to a simple fiducial state, such as  $|00000\dots\rangle$ .

- Long relevant decoherence times, much longer than the gate operation time.

- A "universal" set of quantum gates.

- A qubit-specific measurement capability.

The first requirement asks that the two quantum states  $|0\rangle$  and  $|1\rangle$  are well separated from each other and that we can create multiple copies to scale the computer size. This sets a first constraint on all the energy scales involved. For example, thermal processes are activated at an energy scale of  $E_T = k_B T$ , where  $k_B$  is the Boltzmann constant. This corresponds to  $E_{300K} = 25$  meV at room temperature. In principle, a "well-defined" two-level system will have an energy separation  $\Delta E$  between the two quantum states  $|0\rangle$  and  $|1\rangle$  such that  $\Delta E \gg E_T$ .

Then, we are required to be able to choose the initial state of all the qubits so that the starting state of the computation is deterministic. In the case of spins, this could mean initializing all the qubits in the spin-down state, for example.

The third criterion is the necessary condition to be able to perform multiple quantum operations in series. Since quantum information cannot be stored for a long time, we require the single quantum operations to be much faster than the coherence time so that these are performed while the state of the qubits is still quantum mechanical. The ratio between coherence and operations' time, together with the number of qubits, ultimately sets the complexity of the algorithm that can be run on a specific quantum computer.

As it happens for classical logic operations, it turns out that all the possible quantum gates can be performed once we know how to perform a few particular single and two-qubit operations, forming together a *universal* set. We also have some freedom in choosing this set of quantum gates, so we can choose the most convenient for the specific physical implementation.

Finally, we demand to be able to measure each qubit independently to collect the results of the computation. In quantum mechanics, measuring is an active action. The measurement collapses the quantum state in one of the two states we choose as a basis for the computation,  $|0\rangle$  or  $|1\rangle$ . Therefore, at the end of the computation, we can verify the final state of each qubit.

So far, many different physical platforms have been shown to fulfil some or most of these requirements, motivating scientists to implement qubits in different physical systems. The platforms pursued to date include superconducting circuits[19–21], cold ions[22–24], nuclear magnetic resonance[25, 26], topologically protected states[27, 28], color centers[29, 30], photons[31, 32], and spins[33–35].

### 1.3. DEVELOPMENT CYCLE OF SILICON-BASED MATERIALS FOR SPIN QUBITS

Classical modern electronics is made out of Silicon (Si). The possibility of reusing the expertise already developed to fabricate classical electronics motivated the development of quantum technologies in semiconductor materials, *e.g.* Si and Ge. Si/SiGe heterostructures confine electrons inside a strained Si quantum well sandwiched between two SiGe layers. Additional gate electrodes on top of the heterostructure stack further confine the electrons in an effective zero-dimensional system called *quantum dot*. Quantum dot spin qubits on Si/SiGe heterostructures are especially appealing thanks to their small footprint, resemblance with classical transistors, and long coherence times [34, 35]. However, despite the many similarities, the more stringent requirements of the quantum computing platform require considering new metrics to fully evaluate performance.

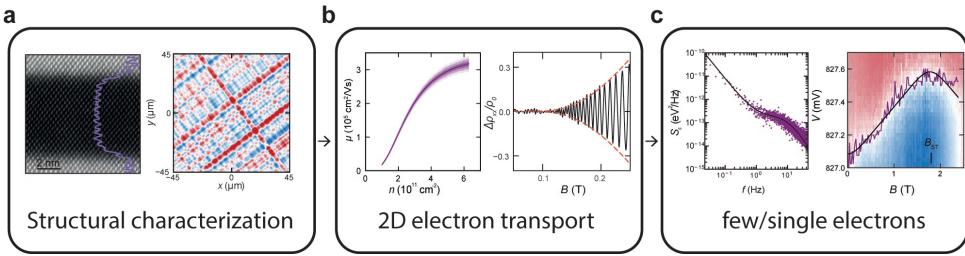

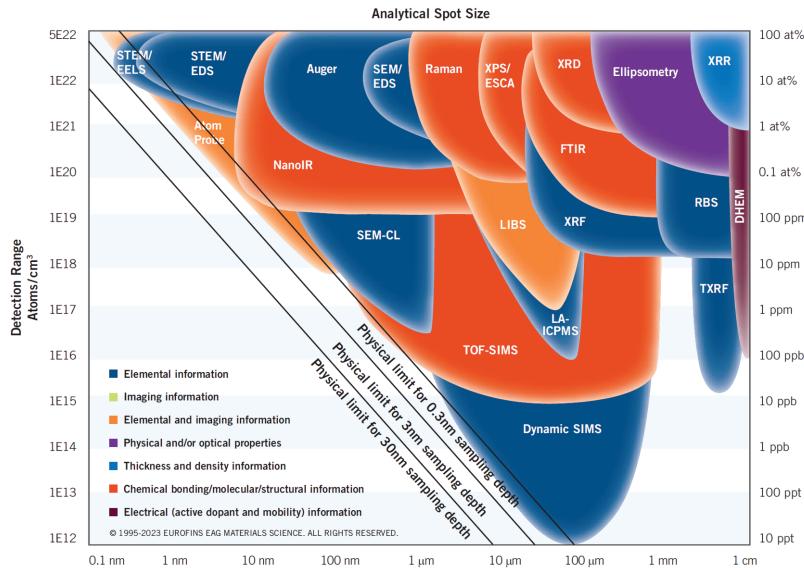

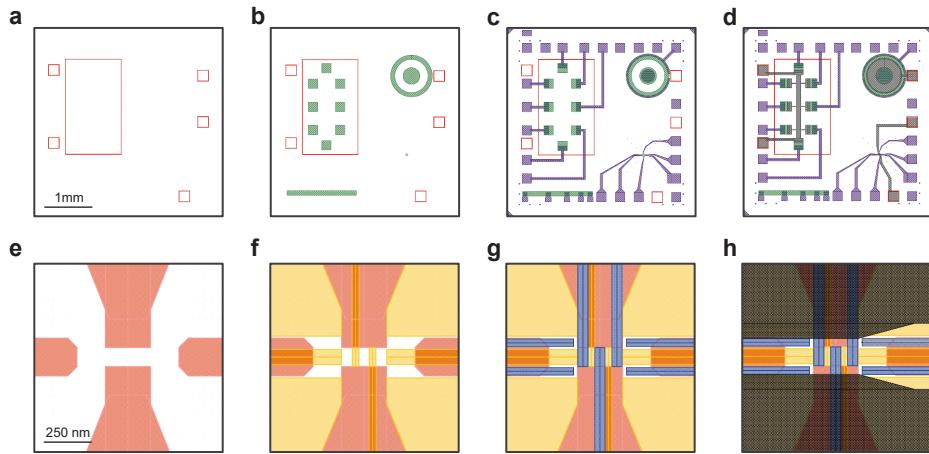

As with classical transistors, a careful engineering of the device architecture and material stack is necessary to obtain the best performance. This is achieved through the iteration of *feedback loops* in which multiple metrics are compared upon variation of others. Figure 1.2 depicts the three macro categories forming a development loop for the Si/SiGe platform. Ideally, a typical single loop gathers information about the crystalline structure and chemical composition of the material stack, the two-dimensional electron gas (2DEG) transport properties, and the measurement of few and single-electron metrics. For each stage, we show an example of a metric already used for classical electronics (left) and a metric that is relevant for spin qubits (right). The typical feedback cycle moves from left to right and starts with the growth of the heterostructure and the structural characterization, passes through the statistical validation of the classical and quantum transport properties, and ultimately seeks to enable a new generation of quantum devices and processors.

The structural and chemical characterization lays at the basis of every development loop. Scanning transmission electron microscopy is a powerful technique to characterize crystalline structures and is used routinely as an in-line diagnostic tool in modern

Figure 1.2: **Illustration of the three steps forming a complete material development loop.** Each loop gathers information about the crystalline and chemical composition (a), the two-dimensional electron gas (2DEG) transport properties (b), and proper metrics of few/single electrons and qubits (c). Although the development cycles take great advantage of techniques already developed for the classical electronic, such as STEM, mobility-density, and electrostatic noise (on the left of each box), the peculiarities of the spin qubits demand a more in-depth characterization and consider metrics such as strain fluctuations, quantum mobility, and Valley splitting (on the right of each box).

semiconductor foundries. Figure 1.2(a) shows on the left a high-resolution STEM image of a Si quantum well (dark) sandwiched between SiGe layers (light), with the brightness contrast due to the different chemical compositions. The single atoms forming the crystalline lattice can be recognized. On the right is an atomic force microscopy image of the surface of a Si/SiGe heterostructure. Strain fluctuations in the SiGe substrate arise as a morphological pattern at the surface aligned with the crystallographic directions.

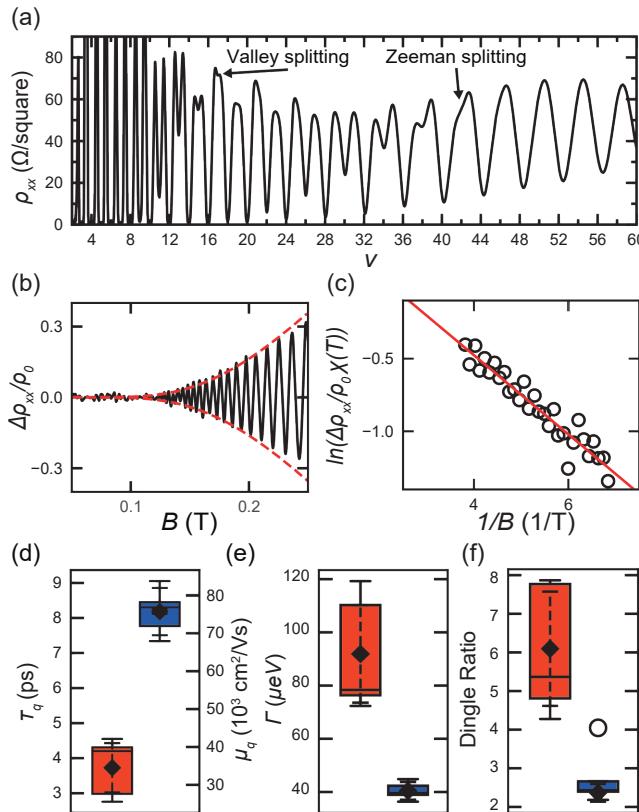

Next, electron transport within the two-dimensional channel is used to characterize the disorder properties at the micrometer scale and validate the first fabrication steps, such as the ohmic contacts and the 2DEG accumulation. Probably the most common metric in classical electronics is electron mobility. Figure 1.2(b) shows a mobility-density curve of the 2DEG accumulated in a Si/SiGe heterostructure, albeit at cryogenic temperatures. At the same time, other properties of the 2DEG are required to fully characterize the material stack. The right panel displays a magnetoresistance curve, which is used to extract the single particle quantum lifetime and quantum mobility. Quantum mobility is influenced by scattering events at all angles; therefore, it is more sensitive than classical mobility to different scattering mechanisms.

Ultimately, the few/single electron properties and qubits metrics are used to benchmark the material. Electrostatic noise is a common problem in classical electronics. On the left is a low-frequency noise spectral density trace measuring the electrical noise power spectral density sensed by a quantum dot in the many-electrons regime. The few-electrons regime makes quantum dot qubits extremely sensitive to electric noise than classical transistors, where many electrons screen such a noise. The necessity to identify well-defined quantum states requires considering metrics such as the single electron valley splitting that are not necessary for classical transistors. On the right is a magnetospectroscopy trace used to evaluate the valley splitting in a quantum dot in the single electron regime.

The complete cycle of the material stack considers all of these parameters with the ultimate ambition of improving spin qubit performances by finding correlations between metrics at different stages of the characterisation loops.

## 1.4. THESIS OUTLINE

This thesis discusses recent advancements in the Si/SiGe platform tailored for spin qubit applications. The aim is to advance the Si/SiGe heterostructure and optimize disorder, charge noise, and valley splitting while using a comprehensive approach to the material stack to highlight the connection between material characteristics and device performances. This approach adopts metrics familiar to classical transistors as well as new ones that are relevant to single-electron spin qubits.

Chapter 2 reviews the relevant theoretical framework and introduces most of the common language used throughout the manuscript. Starting from the electronic band structure of bulk Si, we describe the effects of strain and confinement on the electronic wave function. We show how these knobs can be tuned to enhance spin qubits performances and focus the attention on a few specific arguments of interest, such as disorder, strain fluctuations, valley splitting, and electric and magnetic noise. At the end of the chapter, we describe the various devices used to quantify performances, the different metrics, and how they relate to each other and the material stack.

Chapter 3 describes the experimental techniques. We describe the growth of the Si/SiGe heterostructure, the device fabrication, and measurement setups. This constitutes a detailed description of the characterization methods adopted in the experiments.

The journey in the material development starts in chapter 4, where we focus on improving the semiconductor-dielectric interface and, thereby, the electrostatic control over charge carriers in the Si quantum well. We challenge the mainstream approach of depositing a sacrificial Si cap and instead terminate the growth with a self-terminating low-temperature exposure to dichlorosilane. As a result, we demonstrate a statistical improvement in uniformity and performance of the 2DEG transport on a 100 mm wafer-scale.

We build upon these results and study in chapter 5 the influence of the semiconductor/dielectric interface and quantum well thickness on the low-frequency charge noise measured statistically on a plethora of quantum dot devices. We find that both parameters affect the charge noise, indicating that both impurities in the dielectrics and amorphous layers and dislocations at the heterogeneous interfaces play a role in shaping the electrostatic landscape.

We complete the feedback loop in chapter 6 with the fine-tuning of the thickness of the  $^{28}\text{Si}$  quantum well, where we also provide a quantitative estimation of the average strain and amplitude of the strain fluctuations in the quantum well. Here, we show that such a parameter strongly influences the disorder landscape and suggest a correlation with valley splitting, demonstrating heterostructures able to support low disorder and high valley splitting.

Finally, in chapter 7, we summarize the main results and suggest a few future possible directions of focus to develop the material properties further.

# BIBLIOGRAPHY

- [1] Steven Girvin - *The Race to Build Quantum Computers* (February 12, 2020). it-IT. URL: [https://www.youtube.com/watch?v=nhUKHf-GN\\_Y](https://www.youtube.com/watch?v=nhUKHf-GN_Y) (visited on 12/01/2023).

- [2] Max Planck. "Ueber das Gesetz der Energieverteilung im Normalspectrum". en. In: *Annalen der Physik* 309.3 (Jan. 1901), pp. 553–563. ISSN: 0003-3804, 1521-3889. DOI: 10.1002/andp.19013090310. URL: <https://onlinelibrary.wiley.com/doi/10.1002/andp.19013090310> (visited on 12/01/2023).

- [3] A. Einstein. "Über einen die Erzeugung und Verwandlung des Lichtes betreffenden heuristischen Gesichtspunkt". en. In: *Annalen der Physik* 322.6 (Jan. 1905), pp. 132–148. ISSN: 0003-3804, 1521-3889. DOI: 10.1002/andp.19053220607. URL: <https://onlinelibrary.wiley.com/doi/10.1002/andp.19053220607> (visited on 12/01/2023).

- [4] G. I. Taylor. "Interference Fringes with Feeble Light". In: *Concepts of Quantum Optics*. Ed. by P. L. Knight and L. Allen. Pergamon, Jan. 1983, pp. 91–92. ISBN: 9780080291604. DOI: 10.1016/B978-0-08-029160-4.50015-4. URL: <https://www.sciencedirect.com/science/article/pii/B9780080291604500154> (visited on 12/01/2023).

- [5] L. Essen and J. V. L. Parry. "An Atomic Standard of Frequency and Time Interval: A Cæsium Resonator". en. In: *Nature* 176.4476 (Aug. 1955), pp. 280–282. ISSN: 1476-4687. DOI: 10.1038/176280a0. URL: <https://www.nature.com/articles/176280a0> (visited on 11/25/2023).

- [6] J. C. Hafele and Richard E. Keating. "Around-the-World Atomic Clocks: Predicted Relativistic Time Gains". In: *Science* 177.4044 (1972), pp. 166–168. ISSN: 0036-8075. URL: <https://www.jstor.org/stable/1734833> (visited on 11/25/2023).

- [7] T. H. Maiman. "Stimulated Optical Radiation in Ruby". en. In: *Nature* 187.4736 (Aug. 1960), pp. 493–494. ISSN: 1476-4687. DOI: 10.1038/187493a0. URL: <https://www.nature.com/articles/187493a0> (visited on 11/25/2023).

- [8] Arthur L. Schawlow. "Spectroscopy in a New Light". en. In: *Science* 217.4554 (July 1982), pp. 9–16. ISSN: 0036-8075, 1095-9203. DOI: 10.1126/science.217.4554.9. URL: <https://www.science.org/doi/10.1126/science.217.4554.9> (visited on 11/25/2023).

- [9] John Bardeen. "Surface States and Rectification at a Metal Semi-Conductor Contact". en. In: *Physical Review* 71.10 (May 1947), pp. 717–727. ISSN: 0031-899X. DOI: 10.1103/PhysRev.71.717. URL: <https://link.aps.org/doi/10.1103/PhysRev.71.717> (visited on 11/25/2023).

[10] J. Bardeen and W. H. Brattain. "The Transistor, A Semi-Conductor Triode". In: *Physical Review* 74.2 (July 1948), pp. 230–231. DOI: 10.1103/PhysRev.74.230. URL: <https://link.aps.org/doi/10.1103/PhysRev.74.230> (visited on 11/25/2023).

[11] Martin M. Atalla. "Semiconductor devices having dielectric coatings". US3206670A. Sept. 1965. URL: <https://patents.google.com/patent/US3206670A/en> (visited on 11/25/2023).

[12] Gordon E. Moore. "Cramming more components onto integrated circuits, Reprinted from Electronics, volume 38, number 8, April 19, 1965, pp.114 ff." In: *IEEE Solid-State Circuits Society Newsletter* 11.3 (Sept. 2006), pp. 33–35. ISSN: 1098-4232. DOI: 10.1109/N-SSC.2006.4785860. URL: <https://ieeexplore.ieee.org/document/4785860> (visited on 11/25/2023).

[13] Richard P. Feynman. "Simulating physics with computers". en. In: *International Journal of Theoretical Physics* 21.6 (June 1982), pp. 467–488. ISSN: 1572-9575. DOI: 10.1007/BF02650179. URL: <https://doi.org/10.1007/BF02650179> (visited on 11/26/2023).

[14] Paul Benioff. "The computer as a physical system: A microscopic quantum mechanical Hamiltonian model of computers as represented by Turing machines". en. In: *Journal of Statistical Physics* 22.5 (May 1980), pp. 563–591. ISSN: 1572-9613. DOI: 10.1007/BF01011339. URL: <https://doi.org/10.1007/BF01011339> (visited on 11/26/2023).

[15] Sam McArdle et al. "Quantum computational chemistry". In: *Reviews of Modern Physics* 92.1 (Mar. 2020), p. 015003. DOI: 10.1103/RevModPhys.92.015003. URL: <https://link.aps.org/doi/10.1103/RevModPhys.92.015003> (visited on 11/26/2023).

[16] P.W. Shor. "Algorithms for quantum computation: discrete logarithms and factoring". In: *Proceedings 35th Annual Symposium on Foundations of Computer Science*. Nov. 1994, pp. 124–134. DOI: 10.1109/SFCS.1994.365700. URL: <https://ieeexplore.ieee.org/document/365700> (visited on 11/27/2023).

[17] Lov K. Grover. "A fast quantum mechanical algorithm for database search". en. In: *Proceedings of the twenty-eighth annual ACM symposium on Theory of computing - STOC '96*. Philadelphia, Pennsylvania, United States: ACM Press, 1996, pp. 212–219. ISBN: 9780897917858. DOI: 10.1145/237814.237866. URL: <http://portal.acm.org/citation.cfm?doid=237814.237866> (visited on 11/27/2023).

[18] David P. DiVincenzo. "The Physical Implementation of Quantum Computation". In: *Fortschritte der Physik* 48.9-11 (Sept. 2000), pp. 771–783. ISSN: 00158208. DOI: 10.1002/1521-3978(200009)48:9/11<771::AID-PROP771>3.0.CO;2-E.

[19] Frank Arute et al. "Quantum supremacy using a programmable superconducting processor". en. In: *Nature* 574.7779 (Oct. 2019), pp. 505–510. ISSN: 1476-4687. DOI: 10.1038/s41586-019-1666-5. URL: <https://www.nature.com/articles/s41586-019-1666-5> (visited on 12/01/2023).

- [20] He-Liang Huang et al. "Superconducting quantum computing: a review". en. In: *Science China Information Sciences* 63.8 (July 2020), p. 180501. ISSN: 1869-1919. DOI: 10.1007/s11432-020-2881-9. URL: <https://doi.org/10.1007/s11432-020-2881-9> (visited on 12/01/2023).

- [21] Jens Koch et al. "Charge-insensitive qubit design derived from the Cooper pair box". In: *Physical Review A* 76.4 (Oct. 2007), p. 042319. DOI: 10.1103/PhysRevA.76.042319. URL: <https://link.aps.org/doi/10.1103/PhysRevA.76.042319> (visited on 12/01/2023).

- [22] Immanuel Bloch, Jean Dalibard, and Wilhelm Zwerger. "Many-body physics with ultracold gases". In: *Reviews of Modern Physics* 80.3 (July 2008), pp. 885–964. DOI: 10.1103/RevModPhys.80.885. URL: <https://link.aps.org/doi/10.1103/RevModPhys.80.885> (visited on 12/01/2023).

- [23] J. I. Cirac and P. Zoller. "Quantum Computations with Cold Trapped Ions". In: *Physical Review Letters* 74.20 (May 1995), pp. 4091–4094. DOI: 10.1103/PhysRevLett.74.4091. URL: <https://link.aps.org/doi/10.1103/PhysRevLett.74.4091> (visited on 12/01/2023).

- [24] Giacomo Roati et al. "Anderson localization of a non-interacting Bose–Einstein condensate". en. In: *Nature* 453.7197 (June 2008), pp. 895–898. ISSN: 1476-4687. DOI: 10.1038/nature07071. URL: <https://www.nature.com/articles/nature07071> (visited on 12/01/2023).

- [25] Neil A. Gershenfeld and Isaac L. Chuang. "Bulk Spin-Resonance Quantum Computation". en. In: *Science* 275.5298 (Jan. 1997), pp. 350–356. ISSN: 0036-8075, 1095-9203. DOI: 10.1126/science.275.5298.350. URL: <https://www.science.org/doi/10.1126/science.275.5298.350> (visited on 12/01/2023).

- [26] Lieven M. K. Vandersypen et al. "Experimental realization of Shor's quantum factoring algorithm using nuclear magnetic resonance". en. In: *Nature* 414.6866 (Dec. 2001), pp. 883–887. ISSN: 1476-4687. DOI: 10.1038/414883a. URL: <https://www.nature.com/articles/414883a> (visited on 12/01/2023).

- [27] A Yu Kitaev. "Unpaired Majorana fermions in quantum wires". In: *Physics-Uspekhi* 44.10S (Oct. 2001), pp. 131–136. ISSN: 1468-4780. DOI: 10.1070/1063-7869/44/10S/S29. URL: <https://iopscience.iop.org/article/10.1070/1063-7869/44/10S/S29> (visited on 12/01/2023).

- [28] Chetan Nayak et al. "Non-Abelian anyons and topological quantum computation". In: *Reviews of Modern Physics* 80.3 (Sept. 2008), pp. 1083–1159. DOI: 10.1103/RevModPhys.80.1083. URL: <https://link.aps.org/doi/10.1103/RevModPhys.80.1083> (visited on 12/01/2023).

- [29] M. Pompili et al. "Realization of a multinode quantum network of remote solid-state qubits". en. In: *Science* 372.6539 (Apr. 2021), pp. 259–264. ISSN: 0036-8075, 1095-9203. DOI: 10.1126/science.abg1919. URL: <https://www.science.org/doi/10.1126/science.abg1919> (visited on 12/01/2023).

1

- [30] Peter C. Humphreys et al. “Deterministic delivery of remote entanglement on a quantum network”. en. In: *Nature* 558.7709 (June 2018), pp. 268–273. ISSN: 1476-4687. DOI: 10.1038/s41586-018-0200-5. URL: <https://www.nature.com/articles/s41586-018-0200-5> (visited on 12/01/2023).

- [31] Han-Sen Zhong et al. “Quantum computational advantage using photons”. en. In: *Science* 370.6523 (Dec. 2020), pp. 1460–1463. ISSN: 0036-8075, 1095-9203. DOI: 10.1126/science.abe8770. URL: <https://www.science.org/doi/10.1126/science.abe8770> (visited on 12/01/2023).

- [32] Jeremy L. O’Brien, Akira Furusawa, and Jelena Vučković. “Photonic quantum technologies”. In: *Nature Photonics* 3.12 (Dec. 2009), pp. 687–695. ISSN: 1749-4885. DOI: 10.1038/nphoton.2009.229.

- [33] Daniel Loss and David P Divincenzo. *Quantum computation with quantum dots*. Tech. rep. 1998.

- [34] R. Hanson et al. “Spins in few-electron quantum dots”. In: *Reviews of Modern Physics* 79.4 (Oct. 2007), pp. 1217–1265. ISSN: 0034-6861. DOI: 10.1103/RevModPhys.79.1217.

- [35] Floris A. Zwanenburg et al. “Silicon quantum electronics”. In: *Reviews of Modern Physics* 85.3 (July 2013), pp. 961–1019. DOI: 10.1103/RevModPhys.85.961. URL: <https://link.aps.org/doi/10.1103/RevModPhys.85.961> (visited on 05/27/2020).

# 2

## SEMICONDUCTOR STACKS: THEORETICAL CONSIDERATIONS

*If quantum mechanics hasn't profoundly shocked you,

you haven't understood it yet*

Niels Bohr, Copenhagen, June 1952

## 2.1. MATERIAL STACKS FOR SEMICONDUCTOR QUANTUM DOTS

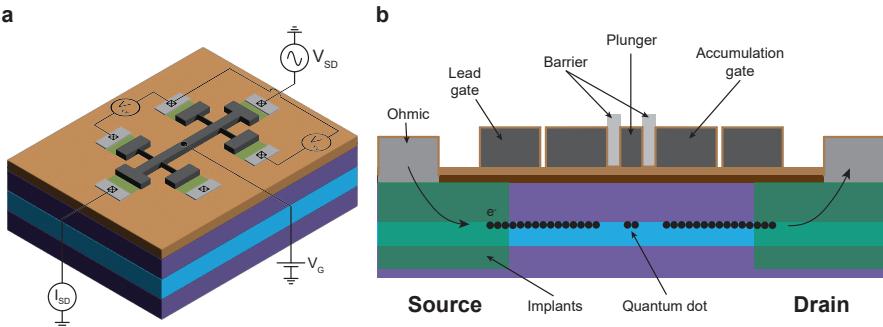

The joint effect of the band structure and device engineering produces the three-dimensional electrostatic potential to confine a single charge in a planar heterostructure. The energy band offset between different materials composing the heterostructure traps the charges in a two-dimensional electron (2DEG) or hole (2DHG) gas at the heterojunction. Next, a series of metallic gate electrodes electrically isolated from each other and from the charges at the heterojunction are fabricated on top of the heterostructure. Here, a series of voltages applied to each gate shape the in-plane electrostatic potential and trap the charge carrier in an effectively zero-dimensional system, defining a *quantum dot*.

To date, the most advanced heterostructure stacks hosting quantum dots spin qubits comprise: gallium-arsenide/aluminium-gallium-arsenide (GaAs/AlGaAs) [1], silicon metal-oxide-semiconductor (Si-MOS) [2, 3], silicon/silicon-germanium (Si/SiGe)[4, 5], and germanium/silicon-germanium (Ge/SiGe) [6, 7]. Figure 2.1 provides a schematic representation of these heterostructures and respective material stacks used to fabricate quantum dot spin qubit devices. The material stacks are compared considering the epitaxial and bandstructure properties of the host heterostructure, the quantum dot architectures, the electrical transport properties and the quantum dots and qubit performances. From top to bottom, the table follows the steps already described for the material development loops in fig. 1.2. The specific values compare LossDiVincenzo[8] qubits in the respective platforms that use the spin up ( $\uparrow\downarrow$ ) and down ( $\downarrow\uparrow$ ) states, separated by the Zeeman energy ( $E_Z = 2\mu_B B$ ), that a charge in an external magnetic field ( $B$ ) can occupy.

The epitaxy of the heterostructures differentiates in terms of the growth technique (Chemical Vapour Deposition (CVD)/Molecular Beam Epitaxy (MBE)), the nature of the heterointerface (epitaxial/amorphous), the presence of strain in the active channel, the compatibility with the CMOS manufacturing process, the thermal budget, and the possibility of isotopic purification. The properties of each heterostructure are reflected in the band structure and charge carrier properties, such as the effective mass, which influences the energy level spacing and hence the lateral dimensions of the confining potential; the presence of spin-orbit coupling, useful for local coherent manipulation; and the energy separation of the orbital states necessary to guarantee a well-defined two-level system for computation.

The thermal budget and the effective mass are two of the main factors constraining the integration, from a fabrication perspective, of quantum dot devices. Carriers with a large effective mass require tighter electric confinement to isolate the single electron or hole and, therefore, smaller gate electrodes to shape the electrostatic potential. A narrow gate pitch suffers more from dimension non-uniformities among gates and misalignment between different layers, complicating fabrication. The thermal budget constrains all the thermal processes taking place during the fabrication and, for example, forces the adoption of low-temperature techniques for the deposition of dielectrics, which are usually characterized by a high density of interface traps ( $D_{it}$ ). Moreover, the possibility of contacting the charge carriers with metals diffusing throughout the heterostructure dramatically simplifies the fabrication process. It avoids the use of implantation, which is hard to integrate into small structures.

The two-dimensional (2D) transport properties of the channel offer a first overview

of the disorder present in the different structures. Maximum mobility is a widely used metric to quantify the disorder landscape already employed in classical electronics. However, mobility peaks at high carrier density due to electrostatic screening, a regime typically far away from the single charge occupancy of quantum dot qubits. Percolation density, on the opposite side of the density range, measures the minimum density required to establish a metallic conduction channel and is, therefore, considered a better metric to characterize disorder in the regime relevant for quantum dot spin qubits. In addition, the quantum mobility can be extracted from the envelope of the Shubnikov-de Haas oscillations in the quantum Hall regime and, differently from classical mobility, is affected by scattering from all angles. In particular, comparing classical and quantum mobility allows us to understand the location of the dominant scattering sources.

Ultimately, we benchmark the semiconducting platform using quantum dots and qubit metrics. In the few charges regime, we compare them in terms of a maximum number of dots, *i.e.*, the largest array able to operate single charges with controllable exchange interaction, and low-frequency charge noise at 1 Hz. We also report on the number of qubits, intended as the largest array of simultaneous coherent operations, and compare the relaxation time ( $T_1$ ), the coherence time extracted from the Gaussian decay typically appearing in a Ramsey experiment and measuring the inhomogeneous dephasing ( $T_2^*$ ), the coherence time measured under Dynamical Decoupling sequences filtering out low-frequency noise ( $T_2^{DynD}$ ), the decay of coherent Rabi oscillations ( $T_2^{Rabi}$ ), and single ( $F_{1Q}$ ) and two ( $F_{2Q}$ ) qubit gate fidelities.

The first quantum dots were demonstrated in modulation-doped GaAs/AlGaAs [1] heterostructures thanks to the maturity of the molecular beam epitaxy of III-V compounds [9] and availability of dislocation-free single crystal commercial substrate. High mobility [10, 11] ( $10^6 - 10^7 \text{ cm}^2/\text{Vs}$ ) and low percolation [12] ( $< 10^{10} \text{ cm}^{-2}$ ) 2DEGs are easily produced thanks to the small lattice mismatch ( $\approx 0.01\%$ ) between GaAs and AlGaAs. The extremely clean disorder landscape is confirmed in the quantum Hall regime. Quantum mobility is also very high  $\mu_q \approx 10^6 \text{ cm}^2/\text{Vs}$  correspondent to a single particle quantum relaxation time of  $\tau_q \approx 24 \text{ ps}$  [13]. The single electrons are defined by selectively depleting the 2DEG with Schottky contacts on top of the heterostructure without the need for dielectric layers. The non-degenerate conduction band and light, effective mass ( $m^* = 0.067$ ) allow the definition of the quantum dots using large gate electrodes ( $\approx 80 \text{ nm}$ ), easing the fabrication process. Moreover, the large spin-orbit coupling allows addressing single spins with full electrical control [14].

The development of spin qubits in GaAs/AlGaAs heterostructures has been challenging due to the absence of zero-spin isotopes and the incompatibility with the CMOS semiconductor manufacturing process. The former strongly limits coherence time ( $T_2^*$ ) due to the hyperfine interaction of the electron's spin with the nuclear spin bath of the host material. The latter makes it difficult to leverage advanced semiconductor manufacturing and integrate such devices with on-chip classical electronics, which will probably be necessary to control practical large-scale quantum processors.

These two constraints motivated extensive effort in using Silicon as spin qubit host material. The isotopic purification of the naturally abundant  $^{28}\text{Si}$  ( $\approx 93\%$ ) drastically reduces the hyperfine interactions, boosting the coherence time of more than one order of magnitude [16]. Isotopic purification of a few hundred parts per million (ppm) is nowa-

2

|                 | GaAs                                                                    | Si-MOS                           | Si/SiGe          | Ge/SiGe           |

|-----------------|-------------------------------------------------------------------------|----------------------------------|------------------|-------------------|

| Material stack  | <p>Electrons<br/>Holes<br/>← → Tensile strain<br/>→ ← Compr. strain</p> |                                  |                  |                   |

| Heterostructure | Growth technique                                                        | MBE                              | CVD              | CVD               |

|                 | Heterointerface                                                         | Epitaxial                        | Amorphous        | Epitaxial         |

|                 | Strain                                                                  | No                               | No               | Yes               |

|                 | CMOS compatible                                                         | No                               | Complete         | Yes               |

|                 | Thermal budget (°C)                                                     | 600-800                          | >1000            | 750               |

|                 | Isotopic purification                                                   | No                               | Yes              | Yes               |

|                 | Effective mass ( $m_e$ )                                                | 0.067                            | 0.19             | 0.19              |

|                 | Spin-orbit coupling                                                     | Yes                              | No               | No                |

| Device          | Excited state energy (meV)                                              | >1                               | 0.3 - 0.8        | >1                |

|                 | Gates size (nm)                                                         | >100                             | 30-40            | 30-40             |

|                 | Dielectric/Dit (cm <sup>-2</sup> )                                      | No                               | 10 <sup>10</sup> | 10 <sup>12</sup>  |

| 2D transp.      | Ohmic contacts                                                          | Metals                           | Implant          | Implant           |

|                 | Mobility (cm <sup>2</sup> /Vs)                                          | 10 <sup>6</sup> -10 <sup>7</sup> | 10 <sup>4</sup>  | 10 <sup>5</sup>   |

|                 | Percolation density (10 <sup>10</sup> cm <sup>-2</sup> )                | >1                               | 10-20            | 5                 |

| Dots & qubits   | Quantum mobility (cm <sup>2</sup> /Vs)                                  | 10 <sup>6</sup>                  | 10 <sup>4</sup>  | 7·10 <sup>4</sup> |

|                 | Number of dots                                                          | 3 x 3                            | 2 x 2            | 9 x 1             |

|                 | Charge noise (μeV/Hz <sup>1/2</sup> )                                   | 8.5                              | 0.61             | 0.9               |

|                 | Number of Qubits                                                        | 3 x 3                            | 2 x 1            | 6 x 1             |

|                 | T <sub>1</sub> (s)                                                      | 57                               | 9                | 5                 |

|                 | T <sub>2</sub> * (μs)                                                   | 0.77                             | 120              | 21                |

|                 | T <sub>2</sub> (ms)                                                     | 0.87                             | 28               | 0.87              |

|                 | T <sub>2n</sub> (ns)                                                    | 1.3                              | 110              | 7                 |

|                 | F <sub>1Q</sub> (%)                                                     | 99.5                             | 99.91            | 99.92             |

|                 | F <sub>2Q</sub> (%)                                                     | 90                               | 98.2             | 99.81             |

Figure 2.1: **Material stacks for quantum dot spin qubits.** We compare GaAs/AlGaAs, Si-MOS, Si/SiGe, and Ge/SiGe heterostructures for spin qubits on multiple metrics related to the heterostructure, device fabrication, two-dimensional (2D) electron or hole transport, quantum dots, and spin qubits. Adapted from [15].

days commercially available [17], and a purity of 60 ppm has been demonstrated [18]. Single electron confinement can be implemented at the silicon/silicon-oxide interface in Si-MOS structures or in buried quantum wells in Si/SiGe heterostructures. The larger effective mass ( $m^* = 0.19$ ) requires the quantum dots to have a much smaller dimension than in GaAs [19], making the device fabrication process more challenging. Moreover, the multiple metallic layers necessary to shape the electrostatic potential must be insulated with high-k dielectrics, often deposited at low temperatures via atomic layer deposition, further increasing device process complexity. Still, the compatibility of the Si-MOS platform with the semiconductor manufacturing process already enabled the demonstration of industry-fabricated spin qubits [2].

The presence of two quasi-degenerate conduction band valleys is the major limitation of Si, complicating the qubit initialization, manipulation, and readout[20]. The two-valley energy separation, called *valley splitting*, is a less stringent constraint in Si-MOS where the large electric field at the Si/Silicon-oxide interface permits to obtain reasonable values ( $E_{VS} \approx 1$  meV) [21]. These were the necessary requirements to demonstrate the operation of spin qubits at "hot" temperatures above 1 K [22], encouraging for the integration of the quantum processor with on-chip classical electronics. Unfortunately, the presence of the  $\text{SiO}_x$  amorphous layer forces the electrons to be close to impurities and charged defects responsible for a strong disorder landscape. For this reason, mobility ( $\approx 10^4$  cm<sup>2</sup>/Vs) and percolation density ( $\approx 10^{11}$  cm<sup>-2</sup>) are very limited in Si-MOS [17], and the control of large devices has proven difficult. The quantum mobility is also rather limited ( $\mu_q \approx 13 \times 10^3$  cm<sup>2</sup>/Vs equivalent to a quantum lifetime of  $\tau_q \approx 1.4$  ps [23]).

Si/SiGe heterostructures overcome this main drawback by confining the electrons at the Si/SiGe epitaxial heterointerface buried 30-50 nm under the surface in an environment characterized by less disorder than Si-MOS. The tensely strained Si quantum well is sandwiched between two Si-rich  $\text{Si}_{(1-x)}\text{Ge}_x$  ( $x \approx 0.3$ ) layers of specific stoichiometric concentration. Here, the absence of pristine SiGe crystalline substrates of specific chemical concentration poses a major challenge to the growth of high-quality Si/SiGe heterostructures. This has been overcome by growing virtual substrates that, starting from Si wafers, increase the Ge concentration in subsequent steps to create the desired  $\text{Si}_{(1-x)}\text{Ge}_x$  substrate under the active layer. The development of virtual substrate with a low density of threading dislocations enabled heterostructures with high mobility ( $> 10^5$  cm<sup>2</sup>/Vs) and low percolation density ( $\approx 10^{10}$  cm<sup>-2</sup>) [24, 25] testifying the low level of disorder. Quantum mobility and lifetimes are also higher compared to SiMOS ( $\mu_q \approx 75 \times 10^3$  cm<sup>2</sup>/Vs,  $\tau_q \approx 9$  ps) [25]. The low level of disorder made it possible to control multi-quantum dot devices [26] and linear arrays of qubits [4].

The two current challenges of the Si/SiGe platform are the low average valley splitting compared to Si-MOS and the large dot-to-dot variability of this parameter, which can prevent the isolation of the two-level qubit system. Moreover, the charge noise has also proved to limit the coherence time [27] by coupling to the spin degree of freedom through the magnetic field gradient created by the micromagnets [28].

Conversely, Ge/SiGe heterostructures comprise a compressively strained Ge quantum well between two Ge-rich  $\text{Si}_{(1-x)}\text{Ge}_x$  ( $x \approx 0.8$ ) layers. These are grown in similar conditions as the Si/SiGe platform and have seen fast progress in the last years[6]. The smaller effective mass of holes in these heterostructures [29] ( $m^* = 0.055$ ) allows to de-

fine quantum dots using larger gate electrodes ( $\approx 80$  nm), facilitating the fabrication process. At the same time, the sizeable spin-orbit coupling permits the full-electrical and fast drive of the spin state [30]. In recent years, the utilization of Ge substrates further improved the level of disorder, boosting mobility  $> 10^6$  cm $^2$ /Vs and reducing percolation density ( $< 10^{10}$  cm $^{-2}$ ) [31]. Quantum mobility and single particle lifetime are comparable with Si/SiGe heterostructures ( $\mu_q \approx 25 \times 10^3$  cm $^2$ /Vs and  $\tau_q \approx 1$  ps [29]). For these reasons, Ge/SiGe heterostructures have seen an extremely fast development, moving from proof of principle demonstrations [32] to single-qubit [30] and multi-qubit operations [33] in just a few years. Arrays with as many as 16 quantum dots have been demonstrated [34], and ten qubit chips are currently being measured in the laboratory.

In Ge/SiGe, the large g-factor anisotropy [35, 36] and dot-to-dot variability pose a challenge in scaling to large arrays while ensuring single qubit addressability. Moreover, the strong spin-orbit coupling represents a double-edged sword, opening the qubits to decoherence from electrostatic fluctuations and charge noise.

## 2.2. Si/SiGe HETEROSTRUCTURE

In this thesis, we focus on the Si/SiGe platform tailored to host electron spin qubits. Here, we provide a brief introduction to the band structure of bulk Si, which is used to understand the single electron energy levels achieved in Si/SiGe heterostructures. We then move to analyze the multiple disorder and noise sources that currently limit the operation of electron spin qubits in Si/SiGe heterostructures.

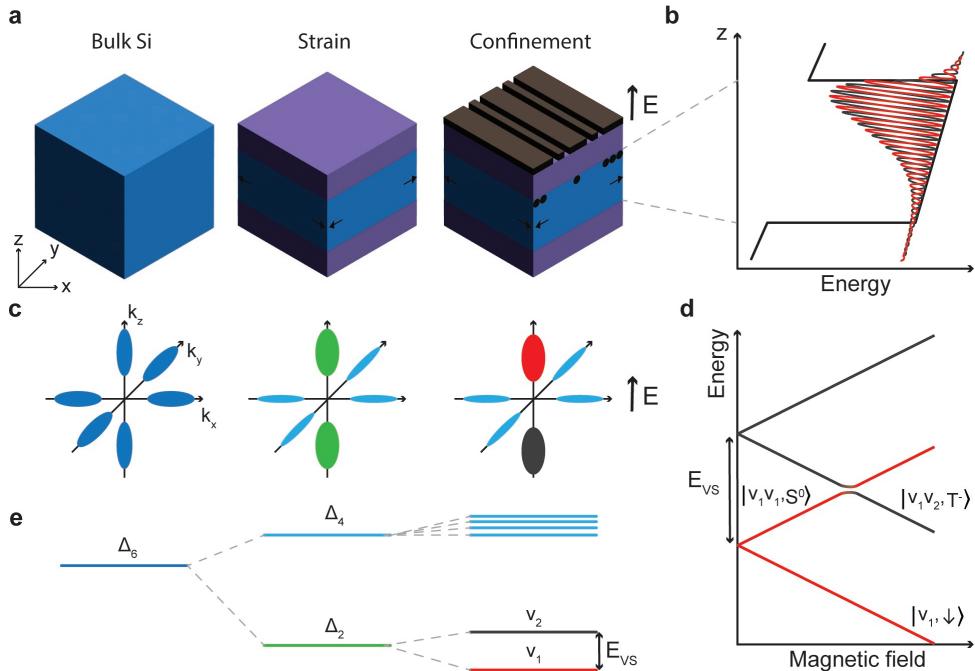

### 2.2.1. BAND STRUCTURE

Solids are collections of tightly bound atoms. For most solids, these atoms arrange themselves in regular patterns on an underlying crystalline lattice. When the atoms are brought together to form the crystal, their orbitals overlap, and the interaction between orbitals spreads the energy levels to form bands of almost continuous energy levels, *i.e.*, the electronic energy bands. The electronic band structure in solids is a direct consequence of the periodicity of their crystalline lattice and the interaction of the atoms forming the lattice. The smallest unit of this periodicity is called the lattice unit cell.

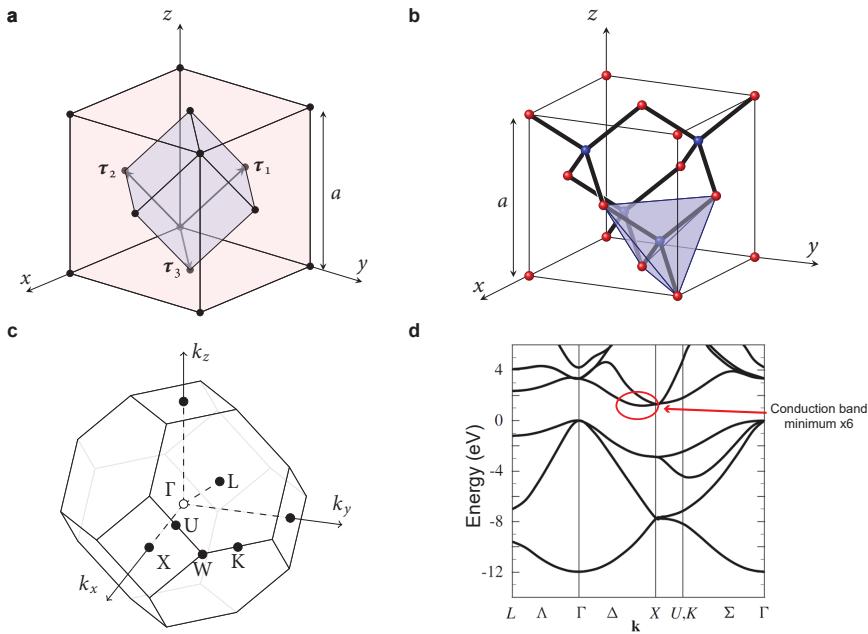

Silicon (Si) and Germanium (Ge) are group IV semiconductors that crystallize in the diamond cubic structure with a lattice constant of  $a_{Si} = 5.43070\text{\AA}$  and  $a_{Ge} = 5.65735\text{\AA}$ , respectively [38]. This is a special case of zincblende structure, most typical of III-V semiconductors like Gallium Arsenide (GaAs) and Indium Arsenide (InAs). The zincblende structure can be seen as formed by two interpenetrating face-centered cubic (FFC) structures with the two atoms forming the primitive cell in the origin  $d_1 = (0, 0, 0)$  and at one-fourth of the diagonal of the cube  $d_2 = a/4(1, 1, 1)$ . Such lattice has three translation vectors:

$$\tau_1 = \frac{a}{2} (0, 1, 1) \quad \tau_2 = \frac{a}{2} (1, 0, 1) \quad \tau_3 = \frac{a}{2} (1, 1, 0) \quad (2.1)$$

These are the directions in which the crystal is symmetric under translations, *i.e.*, the so-called crystallographic axes. Figure 2.2(a) shows the primitive cell formed by these vectors. The entire diamond crystal can be built using translations of such a primitive cell. To fully emphasize the cubic symmetry of the lattice, it is also common to use a larger conventional unit cell (displayed in fig. 2.2(b)).

Figure 2.2: **Primitive cell and band structure of Silicon.** **a** FCC lattice. The primitive vectors  $\tau_1$   $\tau_2$  and  $\tau_3$  are shown.  $a$  is the dimension of the conventional unit cell. The primitive cell is shown in a different colour at the centre. The conventional unit cell emphasizes the full cubic symmetry of the lattice. **b** Conventional unit cell of the zincblende structure. First-neighbor bonds are also shown. Blue and red atoms belong to the two compenetrating FFC cells forming the conventional unit cell. In the case of group IV semiconductors, all the atoms are identical, and the zincblende reduces to the diamond structure. In the zincblende structure, each atom has four first neighbours of the opposite kind, which form a regular tetrahedron centred on the atom. One tetrahedron is shown in blue. **c** Brillouin zone of a crystal with an FCC Bravais lattice. The reciprocal lattice is a body-centred cubic (BCC), and the Brillouin zone is a truncated octahedron centred on  $\Gamma = (0, 0, 0)$ . The points of high symmetry are shown. **d** Band structure of crystalline silicon between the symmetry point of the Brillouin zone. The energy zero is set to the Fermi energy. The conduction band minimum instead is located between the  $\Gamma$  and  $X$  points. This makes Si an indirect band gap semiconductor with an energy band gap of  $E_G = 1.14$  eV. Adapted from [37].

The periodicity in the physical space ( $x, y, z$ ) translates into a periodicity in momentum space ( $k_x, k_y, k_z$ ) where another primitive cell can be defined. This is called the Brillouin zone. The Brillouin zone of a diamond lattice assumes the form of a truncated octaedron (BBC) characterized by the three translation vectors:

$$g_1 = \frac{2\pi}{a} (-1, 1, 1) \quad g_2 = \frac{2\pi}{a} (1, -1, 1) \quad g_3 = \frac{2\pi}{a} (1, 1, -1) \quad (2.2)$$

The BCC Brillouin zone is shown in fig. 2.2(c) together with some high symmetry points. The use of momentum space is particularly useful because the wavefunctions in momentum space are eigenvectors of the Schrödinger equation for an electron in a crystal [37, 39]. Therefore, for each momentum vector, we can calculate an energy. The dispersion relation between momentum vectors and energy is the electronic band structure of the solid.

Figure 2.2(d) shows a portion of the electronic band structure of Si around the  $\Gamma$  symmetry point. The zero of the energy axis is set at the Fermi energy, *i.e.*, the energy of the last electron filling the top of the valence band at the  $\Gamma$  point. The bottom of the conduction band is highlighted with a red circle. This is in between the  $\Gamma$  and  $X$  points, making Si a semiconductor with an indirect bandgap semiconductor. Due to the cubic symmetry of Si, the  $X$  point is six-fold degenerate, and therefore, the conduction band minimum has the same degeneracy.

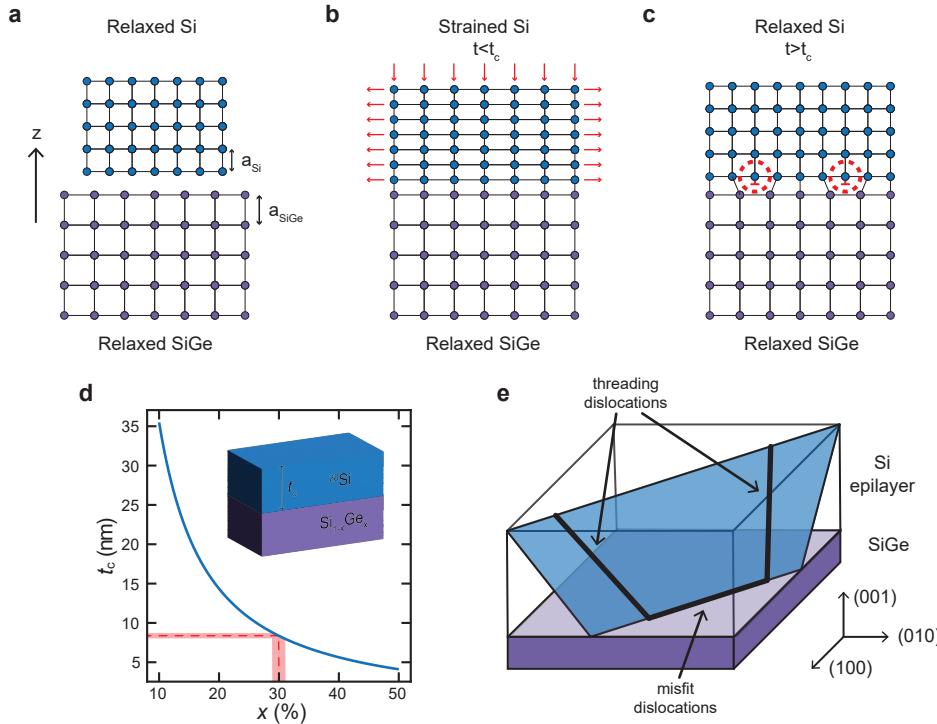

### 2.2.2. STRAINED HETEROSTRUCTURES

The key element of a Si/SiGe heterostructure is a thin Si layer sandwiched between two layers of SiGe. The bandgap in the SiGe alloys is larger than in Si and depends on the Ge concentration. Therefore, the electrons populating the conduction band in the Si layer are confined by two energy walls in a structure called *quantum well*. Moreover, Ge has a 4.2 % larger lattice constant than Si. Therefore, the thin Si layer has to adapt its lattice constant, *i.e.* is *strained*, to the cladding SiGe. The lattice constant of a relaxed  $\text{Si}_{1-x}\text{Ge}_x$  layer with Ge concentration  $x$  ( $0 < x < 1$ ) varies between the lattice constant of Si and Ge. It is described by an empirical relation called Vegard's law [41, 42]:

$$a_{\text{Si}_{1-x}\text{Ge}_x} = 0.5431 + 0.01992x + 0.002733x^2 \text{ (nm)} \quad (2.3)$$

which is accurate to about  $10^{-4}$  nm.

If a sufficiently thin layer of  $\text{Si}_{1-x}\text{Ge}_x$  is grown on top of a  $\text{Si}_{1-y}\text{Ge}_y$  substrate, the top layer will be compressively strained for  $x > y$  and tensely strained for  $x < y$  due to the lattice mismatch. In both cases, the strain is in-plane ( $\epsilon_x = \epsilon_y = \epsilon_{\parallel}$ ), *i.e.*, perpendicular to the growth direction ( $z$ ). This also results in a perpendicular strain ( $\epsilon_{\perp}$ ) caused by an opposite distortion of the lattice cell in the  $z$  direction due to the fact that the crystalline cell readjusts to minimize the total energy, and resulting in a tetragonal distortion of the unit cell as shown in fig. 2.3(b). The parallel ( $\epsilon_{\parallel}$ ) and perpendicular ( $\epsilon_{\perp}$ ) components of the strain tensor can be related by the Poisson ratio ( $\nu$ ) through the relation:

$$\epsilon_{\perp} = \frac{-2\nu}{1-\nu} \epsilon_{\parallel} \quad (2.4)$$

which is accurate as long as the strain is fully elastic and uniform in the entire layer.

A strained layer can be grown on a strain-relaxed or bulk  $\text{Si}_{1-x}\text{Ge}_x$  substrate, which is substantially thicker than the epitaxial layer. The first atomic layers grown on such a substrate will be strained and lattice matched to the substrate. In this case, the heterointerface is coherent and pseudomorphic, and the epitaxial layer is forced to have the same in-plane lattice constant of the substrate, consequently reducing its out-of-plane lattice constant following Eq.2.4.

As the thickness of the strained layer increases, there is a critical thickness ( $t_c$ ) above which it costs too much energy to strain additional heterolayers in coherence with the substrate. As soon as the strained layer thickness exceeds  $t_c$ , misfits dislocation at the heterointerface starts to appear and relieve the strain in the epitaxial film (fig. 2.3(c)). The misfit dislocations create subsequent defects called threading dislocations (fig. 2.3(e)), which propagate following a specific  $60^{\circ}$  through the (110) crystallographic direction. At

Figure 2.3: **Strain and dislocations in Si/SiGe heterostructure.** **a** Schematic representation of fully relaxed Si and SiGe layers. The arrow indicates the growth direction  $z$ . **b** The  $^{28}\text{Si}$  epilayer making the quantum well is grown on top of the SiGe strain relaxed buffer. If the thickness of the  $^{28}\text{Si}$  quantum well ( $t$ ) is smaller than the critical thickness ( $t_c$ ), the epilayer is conformal and pseudomorphic with the virtual substrate. Hence, the quantum well is tensile-strained in the in-plane direction, and there are no strain-induced defects or dangling bonds at the hetero-interface. **c** Growing a Si quantum well beyond the critical thickness triggers relaxation of the epilayer. As a consequence, dangling bonds (in red) and defects start to form at the heterointerface. **d** Critical thickness of a strained silicon epilayer, grown on top of a fully relaxed  $\text{Si}_{1-x}\text{Ge}_x$  substrate, as a function of Ge composition ( $x$ ) of the underlying relaxed substrate. A Si layer grown on top of a  $\text{Si}_{70}\text{Ge}_{30}$  substrate has a critical thickness of 8.5 nm[40] (red dashed line). Fluctuations in the chemical composition of the substrate will result in a lower local critical thickness, facilitating an early relaxation (red shade). **d** Schematic representation of the crystallographic defects forming after relaxation at the interface between the SiGe and Si layers. As soon as the Si epilayer exceeds the critical thickness and starts to relax, a series of dislocations arises at the SiGe/Si interface. These propagate along the crystallographic directions in-plane called *misfit* dislocations, and out-of-plane called *threading* dislocations.

this point, the epitaxial layer relaxes, and the defects may interact with the electrical, optical, and thermal properties of the material, typically degrading the performances [40].

An analytic expression for the critical thickness can be obtained by balancing the force of the threading dislocation arm in an uncapped epilayer with the restoring force from the extra interfacial dislocation created during relaxation. In the case of a strained Si layer grown on top of a SiGe relaxed virtual substrate, the People and Bean criterion

based on the Matthews-Blakeslee calculations[43] yield:

$$t_c \approx \frac{b}{4\pi f(1+\nu)} \left( \ln \frac{t_c}{b} + 1 \right) \quad (2.5)$$

## 2

where  $b = 0.384$  is the Burgers vector,  $\nu = 0.28$  is the Poisson ratio, and  $f$  is the lattice mismatch between Si and the relaxed SiGe virtual substrate calculated from eq. (2.3). This critical thickness is plotted in fig. 2.3(d) and predicts a critical thickness of 8.5 nm for a Si layer grown on a  $\text{Si}_{1-x}\text{Ge}_x$  relaxed virtual substrate with 30% Ge concentration. Since the critical thickness is a direct function of the chemical composition, via the lattice mismatch  $f$  in eq. (2.5), fluctuations in the chemical composition of the substrate can result in a smaller local critical thickness, favouring an early relaxation of the Si quantum well. Therefore, the choice of the quantum well thickness becomes very critical, as it might be easily overlooked in the design phase of the material stack.

## 2.3. MATERIAL CHALLENGES AND METRICS

Some of the major improvements in spin qubit performances can be traced down to the advancements of the material science of the host heterostructure [45]. The first Si/SiGe heterostructures used a phosphorous-doped  $\delta$ -layer to accumulate electrons in the quantum well and depletion gates to confine single electrons. The subsequent adoption of undoped heterostructures, where the  $\delta$ -layer is removed, and the gate electrodes are used to directly accumulate the electrons, decreased disorder, reduced hysteresis, and gate leakage [46, 47]. Again, the purification of the naturally abundant  $^{28}\text{Si}$  isotope boosted the coherence times of more than an order of magnitude by placing the electrons in a nuclear-spin-free magnetic vacuum [48]. Major advances in the materials science of quantum information devices will still be needed to realize large-scale systems. In particular, material issues will be crucial to address in the coming years as the field transitions from few qubits noisy systems to large-scale fault-tolerant quantum processors.

In the following, we identify the critical material challenges that currently limit the progress of electron spin qubits in Si/SiGe heterostructures. We review the theoretical framework leading to the interaction between the single electron spin and the source of decoherence and pinpoint the weaknesses and strengths of such a platform.

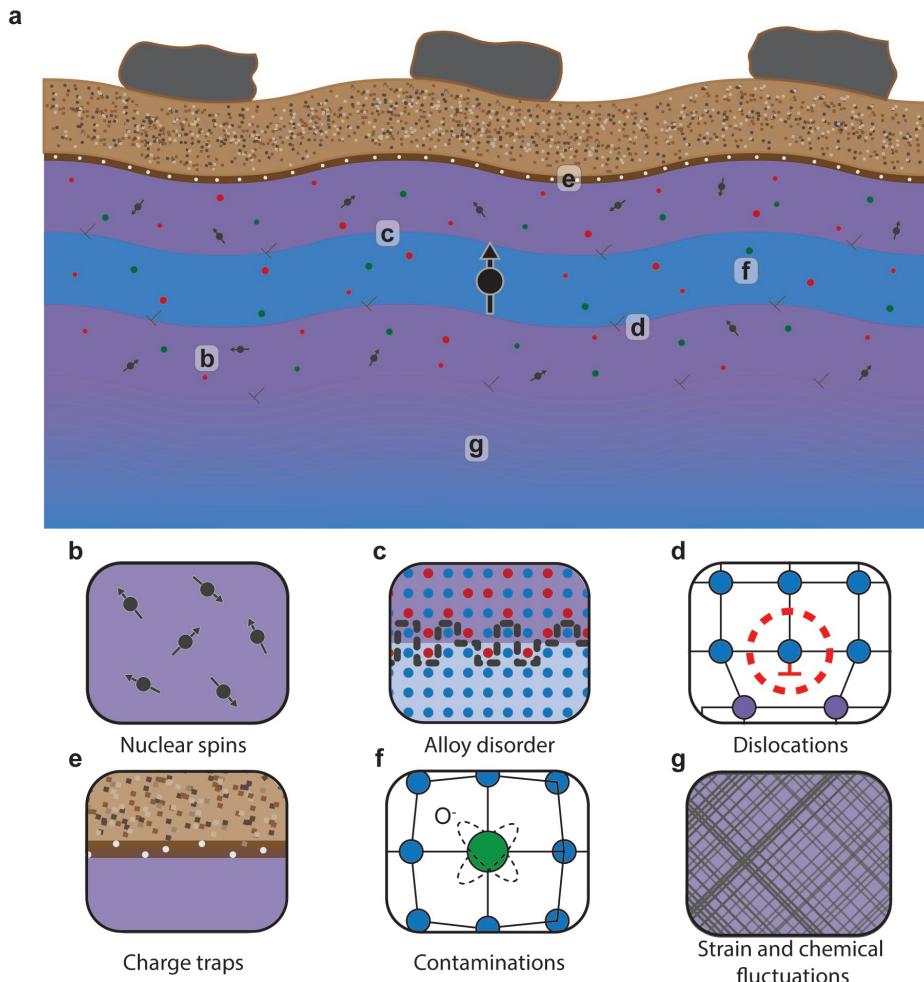

### 2.3.1. DISORDER

We refer to *disorder* as any scattering mechanisms that can interact with the electrons accumulated in the Si/SiGe heterostructure. Scattering centers may also interact with the single electrons and constitute a source of decoherence for the qubit state. Moreover, a low disorder landscape is desirable to ensure uniform control of the single qubits and their interaction. Controlling disorder at different length scales will be, therefore, paramount in scaling to larger quantum devices. Electron mobility ( $\mu$ ) is the standard metric used in classical integrated circuits to quantify disorder. The mobility is related to the average time between two scattering events ( $\tau_t$ ) through the relations:

$$\mu = e\tau_t/m^* \quad (2.6)$$