# Radio-Frequency High-Voltage CMOS Drivers for High-Efficiency Base-Station Power Amplifiers

### A thesis submitted to the

Department of Microelectronics and Computer Engineering Faculty of Electrical Engineering, Mathematics and Computer Sciences

> in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

> > at

### **DELFT UNIVERSITY OF TECHNOLOGY**

by

### David Angel Calvillo Cortés

### Thesis supervisors:

Ir. Mustafa Acar Dr.-Ing. Mark P. van der Heijden P.D.Eng. Melina Apostolidou

Dr.-Ing. Leo C.N. de Vreede

NXP Semiconductors Research Eindhoven, The Netherlands

August 2009

### Abstract

In base-station applications, there is a need of high-voltage CMOS drivers for cost and integration reasons. This is because RF power amplifiers (PA) for base stations are realized in dedicated transistor technologies, while Silicon CMOS is the technology of choice for digital/baseband blocks. Some of those PA technologies, like GaN HEMT, are wide bandgap semiconductors that require high-voltage swings (e.g. 5V) for their optimum input drive. Hence, this thesis investigates two approaches for implementing high-voltage (HV) CMOS drivers for such transistors in low-breakdown voltage baseline CMOS technology. In this work, TSMC 65-nm CMOS technology is employed in this work.

As a first approach, cascoding topologies are investigated. Class E has been used to preserve efficiency. The main efficiency loss mechanisms have been identified and two topologies are proposed: 3 and 4 stacked devices. Only standard devices has been used in this approach in order to be able to use the outcomes to other deep sub-micron CMOS technologies. More than 5.5 and 7.0V output swing has been reached with the 3 and 4 stacked devices topologies, respectively. The complexity increases and the efficiency reduces with the number of stacked devices. Deep N-Well and a dedicated biasing network were needed for the 4-device cascode. However, in spite of these efforts, other HV solutions employing special extended-drain (ED) devices outperformed the best results achieved by the cascode approach, showing than the use of those ED devices is advantageous for high-voltage/power applications.

The second approach consisted in exploring an inverter-base topology, employing the special ED devices available in the baseline 65-nm CMOS technology. Three CMOS drivers were designed, implemented and fabricated. CMOS drivers I and II employed novel thin-oxide ED devices, while CMOS driver III used thick-oxide ED devices. Additionally, pre-driver stages with standard thin-oxide devices were implemented in the CMOS driver I. The three CMOS drivers demonstrated the feasibility of a complete broadband and high-efficiency amplifier lineup bridging the gap between GaN and CMOS technologies. CMOS driver I reached the best performance due to its pre-drivers. The use of thick-gate oxide, in CMOS driver III, was found not to be optimum for the application due to its required high input power. Additionally, in view of the application, the drivers had duty-cycle control capabilities to enhance the efficiency. The CMOS driver I reached a duty-cycle range of 32 to 70% with a 5pF load, within a 2.1 to 2.7GHz bandwidth.

### Acknowledgements

This 1-year thesis has been the concluding work of a tough but marvelous 2-year knowledge and life journey. It has been possible thanks to many people to whom I would like to express my deepest gratitude.

My most sincere gratitude goes to Ir. Mustafa Acar, my main supervisor at NXP Semiconductors Research (NXP). He kindly led me through this entire 1-year thesis project and patiently shared with me a lot of valuable knowledge. Undoubtedly, more people from NXP were of great help too. Thanks to my other two supervisors at the company: P.D.Eng. Melina Apostolidou for her constant support on personal and technical matters; and, Dr.-Ing. Mark P. van der Heijden for fruitful discussions about the general system. Also thanks go to: Dr.-Ing. Domine M. W. Leenaerts and Ir. Edwin van der Heijden for their useful comments during the design review phase of the project; and, Ing. Juan F. Osorio for helpful discussions in Cadence Skill coding.

A great gratitude and appreciation goes to Dr.-Ing. Leo C.N. de Vreede, my tutor at Delft University of Technology (TU-Delft), for his kind and constant support and encouragement on many matters, from even before starting my studies at TU-Delft up to the end of my thesis project. I also thank all the M.Sc. Thesis Committee members for reading this thesis report.

I would also like to gratefully acknowledge the financial support during the entire Master of Science programme provided by: the Programme Alβan, the European Union Programme of High Level Scholarships for Latin America, scholarship No. E07M401622MX; and, the Mexican National Council for Science and Technology (CONACYT), scholarship No. 230803.

This journey could not have been special without my friends, the ones that have been there even before and the ones I met along it. To all of them: 'gracias'.

Last but certainly not least, I am grateful to my Family in Mexico for their continuous support, faith and love. It is because of them that I am finally here. A special mention is for Veronica, for sharing many wonderful times and for her patience and understanding during the toughest times of this journey.

Ing. David A. Calvillo Eindhoven, The Netherlands August 10th, 2009

### **Contents**

| Acknowledgements                                                            | iv     |

|-----------------------------------------------------------------------------|--------|

|                                                                             |        |

| List of Figures                                                             | ix     |

| List of Tables                                                              | xi     |

| 1 Introduction                                                              | 1      |

| 1.1 Motivation                                                              | <br>1  |

| 1.2 Thesis Research Goal                                                    | <br>2  |

| 1.3 State of the art review                                                 | <br>3  |

| 1.4 Thesis organization                                                     | <br>3  |

| 2 Background                                                                | 7      |

| 2.1 Introduction                                                            | <br>7  |

| 2.2 RF power amplifier basics                                               | <br>7  |

| 2.2.1 Main performance metrics                                              | <br>8  |

| 2.2.1.1 Power Gain                                                          | <br>8  |

| 2.2.1.2 Efficiency                                                          | <br>8  |

| 2.2.1.3 Linearity                                                           | <br>9  |

| 2.2.2 Output power                                                          | <br>9  |

| 2.2.3 PA classification                                                     | <br>11 |

| 2.2.3.1 gm-based PAs                                                        | <br>11 |

| 2.2.3.2 Switchmode-based PAs                                                | <br>15 |

| 2.2.4 Conclusions about the output power of the different PA classes        | <br>20 |

| 2.3 CMOS technology and reliability                                         | <br>21 |

| 2.3.0.1 Hot-carrier degradation                                             | <br>21 |

| 2.3.0.2 Junction breakdown                                                  |        |

| 2.3.0.3 Oxide breakdown                                                     |        |

| 2.3.0.4 AC oxide breakdown limit                                            | <br>24 |

| 2.4 Addressing the high-voltage needs of power amplifiers and their drivers | <br>25 |

| 3 Class E cascoding approach for HV swings                                  | 27     |

*Contents* vi

|   | 3.2  | Sources of efficiency loss on a cascode topology |                                                                 |  |  |  |

|---|------|--------------------------------------------------|-----------------------------------------------------------------|--|--|--|

|   | 3.3  | Study                                            | of two proposed cascode topologies                              |  |  |  |

|   |      | 3.3.1                                            | 3-device class E cascode topology                               |  |  |  |

|   |      | 3.3.2                                            | 4-device class E cascode topology                               |  |  |  |

|   |      | 3.3.3                                            | Other topologies employing extended-drain devices               |  |  |  |

|   | 3.4  | Conclu                                           | sions                                                           |  |  |  |

|   |      |                                                  |                                                                 |  |  |  |

| 4 |      |                                                  | sed driver approach for HV swings, design and implementation 43 |  |  |  |

|   | 4.1  |                                                  | action                                                          |  |  |  |

|   | 4.2  |                                                  | r-based driver topologies                                       |  |  |  |

|   |      | 4.2.1                                            | General inverter-based driver topologies                        |  |  |  |

|   |      | 4.2.2                                            | The proposed driver topology                                    |  |  |  |

|   | 4.3  |                                                  | and layout design description for the CMOS driver I             |  |  |  |

|   |      | 4.3.1                                            | Initial considerations                                          |  |  |  |

|   |      |                                                  | 4.3.1.1 Target specifications                                   |  |  |  |

|   |      |                                                  | 4.3.1.2 Duty-cycle control requirement                          |  |  |  |

|   |      |                                                  | 4.3.1.3 NMOS/PMOS transistors size ratio                        |  |  |  |

|   |      |                                                  | 4.3.1.4 Out-phasing system oriented layout requirement          |  |  |  |

|   |      | 4.3.2                                            | General schematic for the CMOS driver I                         |  |  |  |

|   |      | 4.3.3                                            | Output stage design                                             |  |  |  |

|   |      |                                                  | 4.3.3.1 Unit transistor (P)cell design                          |  |  |  |

|   |      | 404                                              | 4.3.3.2 Final layout implementation                             |  |  |  |

|   |      | 4.3.4                                            | Pre-driver design                                               |  |  |  |

|   |      |                                                  | 4.3.4.1 Use of Deep N-Well                                      |  |  |  |

|   |      |                                                  | 4.3.4.2 Optimum unit transistor (P)cell design                  |  |  |  |

|   |      | 4.0.5                                            | 4.3.4.3 Final layout implementation 61                          |  |  |  |

|   |      | 4.3.5                                            | Capacitors design concepts                                      |  |  |  |

|   |      |                                                  | 4.3.5.1 Fringe Capacitor P–cell design                          |  |  |  |

|   |      |                                                  | 4.3.5.2 Power routes with embedded capacitor concept            |  |  |  |

|   |      |                                                  | 4.3.5.3 Bondpad with embedded capacitor concept                 |  |  |  |

|   |      |                                                  | 4.3.5.4 AC-coupling capacitors                                  |  |  |  |

|   |      | 4.0.6                                            | 4.3.5.5 Implemented capacitors summary                          |  |  |  |

|   |      | 4.3.6                                            | ESD protection design                                           |  |  |  |

|   |      |                                                  | 4.3.6.1 ESD protection strategy                                 |  |  |  |

|   |      | 4 2 7                                            | 4.3.6.2 Use of Deep N-Well                                      |  |  |  |

|   | 4.4  | 4.3.7                                            | Complete layout of the CMOS driver I                            |  |  |  |

|   | 4.4  | CMOS                                             | drivers II and III                                              |  |  |  |

| 5 | Inve | rter-ba                                          | sed CMOS drivers simulation results 77                          |  |  |  |

|   | 5.1  | Introdu                                          | uction                                                          |  |  |  |

|   | 5.2  | Perfor                                           | mance of CMOS driver I                                          |  |  |  |

|   |      | 5.2.1                                            | Performance with ideal capacitive load                          |  |  |  |

|   |      |                                                  | 5.2.1.1 Simulation setup                                        |  |  |  |

|   |      |                                                  | 5.2.1.2 High-voltage operation and PSS voltage waveforms 79     |  |  |  |

|   |      |                                                  | 5.2.1.3 Duty-cycle sensitivity                                  |  |  |  |

|   |      |                                                  | 5.2.1.4 Duty-cycle results                                      |  |  |  |

|   |      |                                                  | 5.2.1.5 Sources of power dissipation                            |  |  |  |

*Contents* vii

|   |             | 5.2.2                                                           | Performa                                                                                                 | nce driving a Class-E GaN power amplifier                                                                                                                                                                                                                                                                                                    |       |                                       |              | 86                                                                               |

|---|-------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------|--------------|----------------------------------------------------------------------------------|

|   |             |                                                                 | 5.2.2.1                                                                                                  | Simulation setup                                                                                                                                                                                                                                                                                                                             |       |                                       |              | 86                                                                               |

|   |             |                                                                 | 5.2.2.2                                                                                                  | Influence of interstage network                                                                                                                                                                                                                                                                                                              |       |                                       |              | 87                                                                               |

|   |             |                                                                 | 5.2.2.3                                                                                                  | Simulations results without bondwires                                                                                                                                                                                                                                                                                                        |       |                                       |              | 88                                                                               |

|   |             |                                                                 | 5.2.2.4                                                                                                  | Simulations results with bondwires                                                                                                                                                                                                                                                                                                           |       |                                       |              | 88                                                                               |

|   | 5.3         | Perform                                                         | nance of C                                                                                               | CMOS drivers II and III                                                                                                                                                                                                                                                                                                                      |       |                                       |              | 90                                                                               |

|   |             | 5.3.1                                                           | Performa                                                                                                 | nce with ideal capacitive load                                                                                                                                                                                                                                                                                                               |       |                                       |              | 90                                                                               |

|   |             |                                                                 | 5.3.1.1                                                                                                  | Simulation setup                                                                                                                                                                                                                                                                                                                             |       |                                       |              | 90                                                                               |

|   |             |                                                                 | 5.3.1.2                                                                                                  | PSS voltage waveforms                                                                                                                                                                                                                                                                                                                        |       |                                       |              | 90                                                                               |

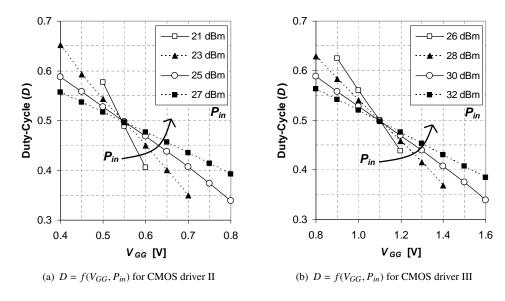

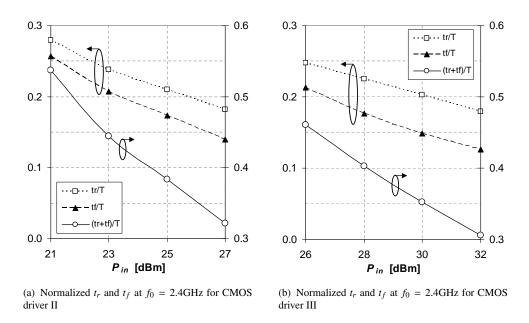

|   |             |                                                                 | 5.3.1.3                                                                                                  | Duty-cycle performance                                                                                                                                                                                                                                                                                                                       |       |                                       |              | 92                                                                               |

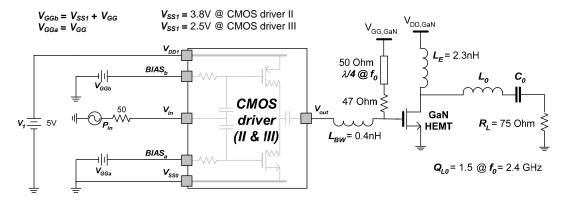

|   |             | 5.3.2                                                           | Performa                                                                                                 | ance driving a Class E GaN power amplifier                                                                                                                                                                                                                                                                                                   |       |                                       |              | 95                                                                               |

|   |             |                                                                 | 5.3.2.1                                                                                                  | Simulation setup                                                                                                                                                                                                                                                                                                                             |       |                                       |              | 95                                                                               |

|   |             |                                                                 | 5.3.2.2                                                                                                  | Influence of input power on the Class-E GaN PA                                                                                                                                                                                                                                                                                               |       |                                       |              | 95                                                                               |

|   |             |                                                                 | 5.3.2.3                                                                                                  | Simulations results without bondwires                                                                                                                                                                                                                                                                                                        |       |                                       |              | 96                                                                               |

|   | 5.4         | Perform                                                         | nance con                                                                                                | nparison of the CMOS drivers I, II and III                                                                                                                                                                                                                                                                                                   |       |                                       |              | 97                                                                               |

|   |             | 5.4.1                                                           | Duty-cyc                                                                                                 | le capabilities                                                                                                                                                                                                                                                                                                                              |       |                                       |              | 97                                                                               |

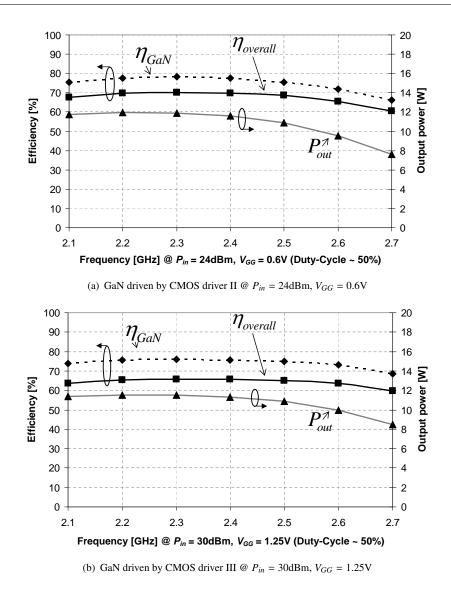

|   |             | 5.4.2                                                           | Driving a                                                                                                | a broadband Class-E GaN power amplifier                                                                                                                                                                                                                                                                                                      |       |                                       |              | 98                                                                               |

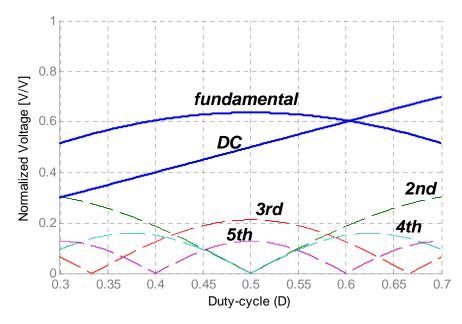

|   | 5.5         | Intersta                                                        | age netwoi                                                                                               | k requirements to preserve duty-cycle                                                                                                                                                                                                                                                                                                        |       |                                       |              | 99                                                                               |

| _ | ~           |                                                                 |                                                                                                          |                                                                                                                                                                                                                                                                                                                                              |       |                                       |              | 400                                                                              |

| 6 |             |                                                                 |                                                                                                          | mmendations                                                                                                                                                                                                                                                                                                                                  |       |                                       |              | 103                                                                              |

|   | 6.1         |                                                                 | •                                                                                                        | n contributions                                                                                                                                                                                                                                                                                                                              |       |                                       |              | 103                                                                              |

|   | 6.2         |                                                                 |                                                                                                          |                                                                                                                                                                                                                                                                                                                                              |       |                                       |              | 104                                                                              |

|   | 6.3         | Future                                                          | work reco                                                                                                | mmendations                                                                                                                                                                                                                                                                                                                                  | <br>٠ | •                                     | <br>٠        | 106                                                                              |

|   |             |                                                                 |                                                                                                          |                                                                                                                                                                                                                                                                                                                                              |       |                                       |              |                                                                                  |

|   |             |                                                                 |                                                                                                          |                                                                                                                                                                                                                                                                                                                                              |       |                                       |              |                                                                                  |

| A |             |                                                                 |                                                                                                          | echnology characterization for switchmode circ                                                                                                                                                                                                                                                                                               |       |                                       |              | 107                                                                              |

|   | <b>A</b> .1 |                                                                 |                                                                                                          | chnology overview                                                                                                                                                                                                                                                                                                                            |       |                                       |              | 107                                                                              |

|   | A.2         |                                                                 |                                                                                                          | evices                                                                                                                                                                                                                                                                                                                                       |       |                                       |              | 108                                                                              |

|   | A.3         | Extend                                                          | led-drain N                                                                                              | MOS devices                                                                                                                                                                                                                                                                                                                                  | <br>• | •                                     | <br>•        | 111                                                                              |

| В | Doto        | ilad An                                                         | alvtical D                                                                                               | onivation for the Canaral Class E Madel                                                                                                                                                                                                                                                                                                      |       |                                       |              | 117                                                                              |

| D | B.1         |                                                                 | •                                                                                                        | erivation for the General Class E Model                                                                                                                                                                                                                                                                                                      |       |                                       |              | 117                                                                              |

|   | B.1<br>B.2  |                                                                 | . descriptic                                                                                             | on and assumptions                                                                                                                                                                                                                                                                                                                           |       |                                       |              | 11/                                                                              |

|   | B.3         | Denva                                                           | tion of the                                                                                              | on and assumptions                                                                                                                                                                                                                                                                                                                           |       |                                       |              |                                                                                  |

|   |             |                                                                 |                                                                                                          | switch voltage equations                                                                                                                                                                                                                                                                                                                     |       |                                       |              | 118                                                                              |

|   | В.3         | Solving                                                         | g the switc                                                                                              | switch voltage equations                                                                                                                                                                                                                                                                                                                     |       |                                       |              | 118<br>122                                                                       |

|   | Б.3         | Solving<br>B.3.1                                                | g the switch<br>Finding a                                                                                | switch voltage equations                                                                                                                                                                                                                                                                                                                     |       |                                       |              | 118<br>122<br>123                                                                |

|   | Б.3         | Solving<br>B.3.1<br>B.3.2                                       | g the switch<br>Finding a<br>Finding I                                                                   | switch voltage equations                                                                                                                                                                                                                                                                                                                     | <br>  |                                       | <br><br><br> | 118<br>122<br>123<br>124                                                         |

|   | Б.3         | Solving<br>B.3.1<br>B.3.2<br>B.3.3                              | Finding a Finding a Finding a                                                                            | switch voltage equations                                                                                                                                                                                                                                                                                                                     | <br>  | •                                     | <br><br><br> | 118<br>122<br>123<br>124<br>125                                                  |

|   |             | Solving<br>B.3.1<br>B.3.2<br>B.3.3<br>B.3.4                     | g the switch<br>Finding a<br>Finding a<br>Finding t                                                      | switch voltage equations                                                                                                                                                                                                                                                                                                                     | <br>  |                                       | <br><br><br> | 118<br>122<br>123<br>124<br>125<br>129                                           |

|   | B.4         | Solving<br>B.3.1<br>B.3.2<br>B.3.3<br>B.3.4                     | g the switch<br>Finding a<br>Finding a<br>Finding t                                                      | switch voltage equations                                                                                                                                                                                                                                                                                                                     | <br>  |                                       | <br><br><br> | 118<br>122<br>123<br>124<br>125<br>129                                           |

| C | B.4         | Solving<br>B.3.1<br>B.3.2<br>B.3.3<br>B.3.4<br>Finding          | Finding a<br>Finding a<br>Finding a<br>Finding a<br>Finding t<br>g the Class                             | switch voltage equations                                                                                                                                                                                                                                                                                                                     | <br>  |                                       | <br><br><br> | 118<br>122<br>123<br>124<br>125<br>129<br>130                                    |

| C | B.4         | Solving<br>B.3.1<br>B.3.2<br>B.3.3<br>B.3.4<br>Finding          | Finding a Finding a Finding a Finding a Finding t g the Class d discussion                               | switch voltage equations                                                                                                                                                                                                                                                                                                                     | <br>  |                                       | <br>         | 118<br>122<br>123<br>124<br>125<br>129                                           |

| C | B.4 Ana     | Solving B.3.1 B.3.2 B.3.3 B.3.4 Finding                         | Finding a<br>Finding a<br>Finding a<br>Finding t<br>Finding t<br>g the Class<br>d discussion             | switch voltage equations                                                                                                                                                                                                                                                                                                                     | <br>  |                                       | <br>         | 118<br>122<br>123<br>124<br>125<br>129<br>130                                    |

| C | B.4 Ana C.1 | Solving B.3.1 B.3.2 B.3.3 B.3.4 Finding                         | g the switch Finding a Finding a Finding a Finding t g the Class d discussion v-Band Ge                  | switch voltage equations                                                                                                                                                                                                                                                                                                                     | <br>  |                                       | <br>         | 118<br>122<br>123<br>124<br>125<br>129<br>130<br><b>135</b><br>135               |

| C | B.4 Ana C.1 | Solving<br>B.3.1<br>B.3.2<br>B.3.3<br>B.3.4<br>Finding          | Finding a Finding a Finding a Finding a Finding t g the Class d discussion v-Band Ge Design o            | switch voltage equations                                                                                                                                                                                                                                                                                                                     | <br>  | · · · · · · · · · · · · · · · · · · · | <br>         | 118<br>122<br>123<br>124<br>125<br>129<br>130<br><b>135</b>                      |

| C | B.4 Ana C.1 | Solving B.3.1 B.3.2 B.3.3 B.3.4 Finding  Introdu  Narrow  C.2.1 | Finding a Finding a Finding a Finding a Finding t g the Class d discussion v-Band Ge Design o Discussion | switch voltage equations  th voltage equations $a_{1,1}, a_{1,2}$ and $a_{2,1}, a_{2,2}$ $K_{1,3}-K_{1,5}$ and $K_{2,3}-K_{2,5}$ $K_{1,1}, K_{1,2}$ and $K_{2,1}, K_{2,2}$ the unknown parameters  SE Circuit Elements  on of the general Class E model  thereal Class E model  of Class E power amplifiers  on of the Class E model results | <br>  |                                       |              | 118<br>122<br>123<br>124<br>125<br>129<br>130<br><b>135</b><br>136<br>137<br>139 |

| C | B.4 Ana C.1 | Solving B.3.1 B.3.2 B.3.3 B.3.4 Finding  Introdu  Narrow  C.2.1 | Finding a Finding a Finding a Finding a Finding t g the Class d discussion v-Band Ge Design o            | switch voltage equations                                                                                                                                                                                                                                                                                                                     |       |                                       |              | 118<br>122<br>123<br>124<br>125<br>129<br>130<br><b>135</b><br>135<br>136        |

| Contents    | ;                                                | viii |

|-------------|--------------------------------------------------|------|

|             | C.2.3 Conclusions                                | 150  |

| <b>C</b> .3 | Broadband Class E design with duty-cycle control | 153  |

| C.3         | Broadband Class E design with duty-cycle control | ]    |

|             |                                                  |      |

| ibliogr     | raphy                                            | 161  |

## **List of Figures**

| 2.1  | Generic schematic and waveforms for gm-based power amplifiers                    |

|------|----------------------------------------------------------------------------------|

| 2.2  | $\eta$ , $P_{out}$ , and harmonics for Class A to C                              |

| 2.3  | Output power capability factor for Class A to C                                  |

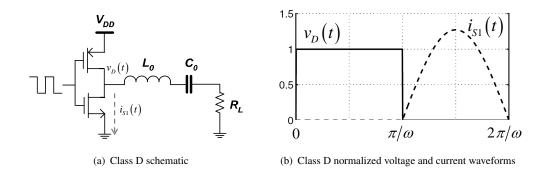

| 2.4  | Class D schematic and waveforms                                                  |

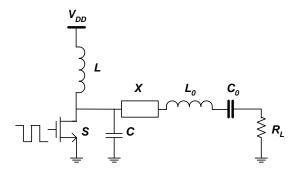

| 2.5  | Class E schematic                                                                |

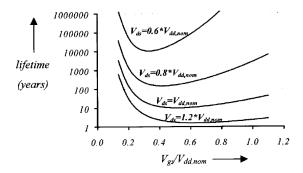

| 2.6  | Typical hot-carrier-based lifetime behavior versus biasing                       |

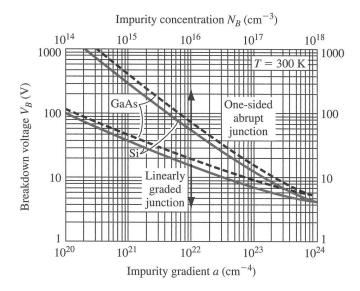

| 2.7  | Breakdown voltage versus impurity concentration                                  |

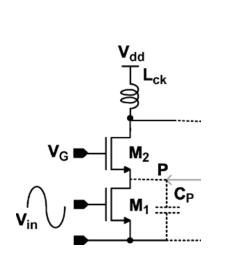

| 3.1  | Class E cascode schematic                                                        |

| 3.2  | Cascode internal losses description                                              |

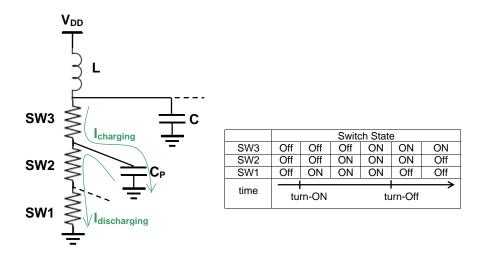

| 3.3  | Charging and discharging process in a cascode                                    |

| 3.4  | 3-MOS cascode topology schematic                                                 |

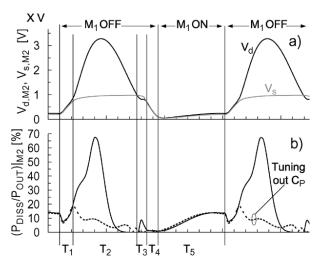

| 3.5  | 3-MOS cascode topology simulation results                                        |

| 3.6  | 4-MOS cascode topology schematic                                                 |

| 3.7  | 4-MOS cascode topology simulation results                                        |

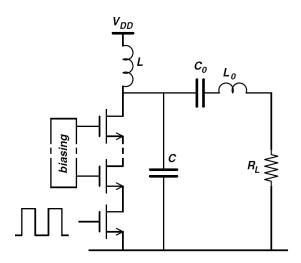

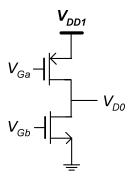

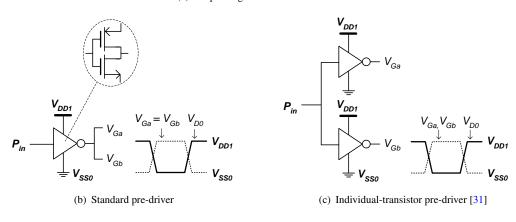

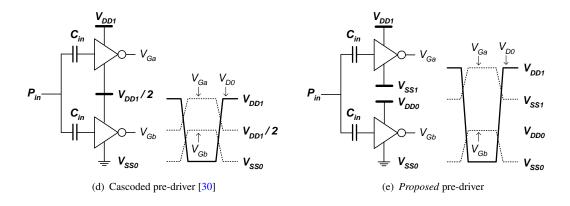

| 4.1  | Inverter-based driver topologies                                                 |

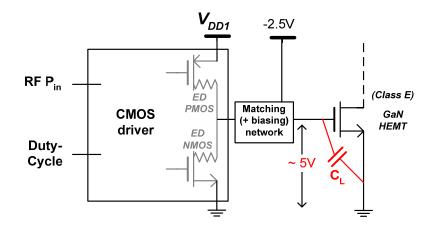

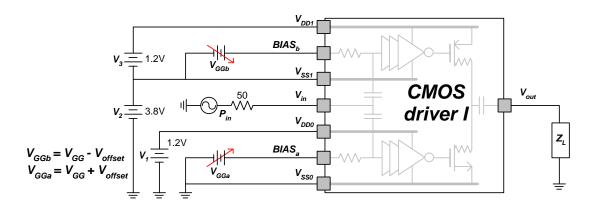

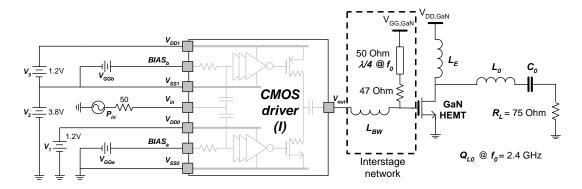

| 4.2  | Schematic for the intended application of the CMOS driver circuit 49             |

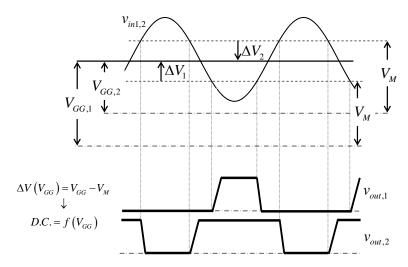

| 4.3  | Operating principle of PWMVGB                                                    |

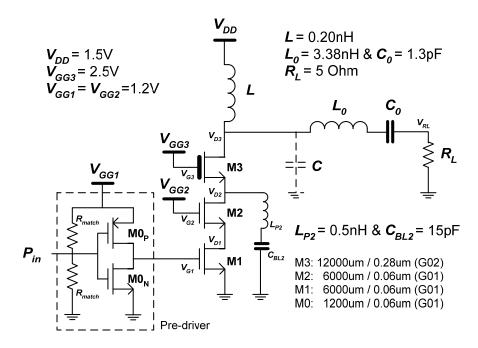

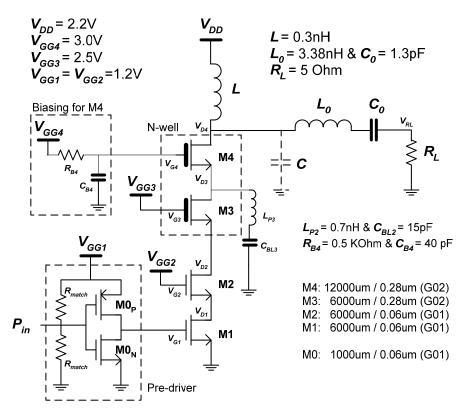

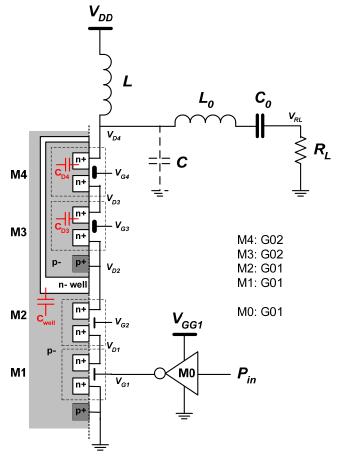

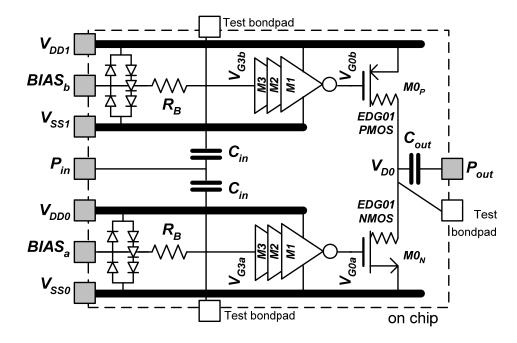

| 4.4  | Schematic of the CMOS driver I                                                   |

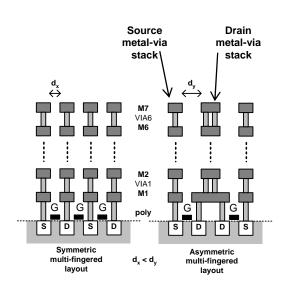

| 4.5  | Symmetric and asymmetric transistor layout                                       |

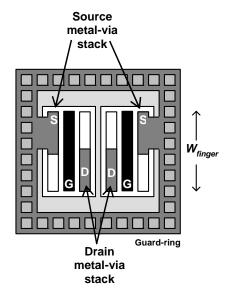

| 4.6  | Top view of unit transistor P-cell                                               |

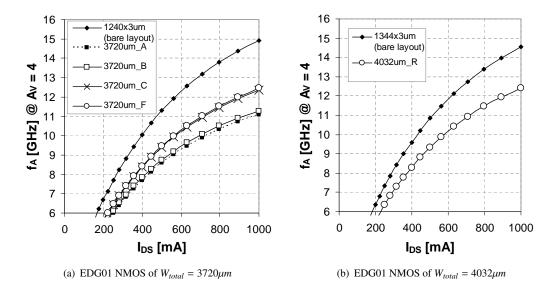

| 4.7  | $f_A$ for the output EDG01 NMOS transistor                                       |

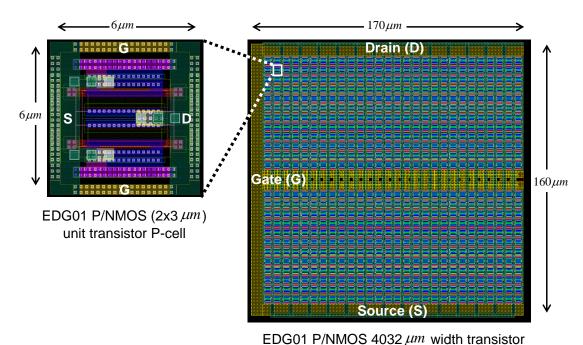

| 4.8  | Layout for the output EDG01 NMOS transistor                                      |

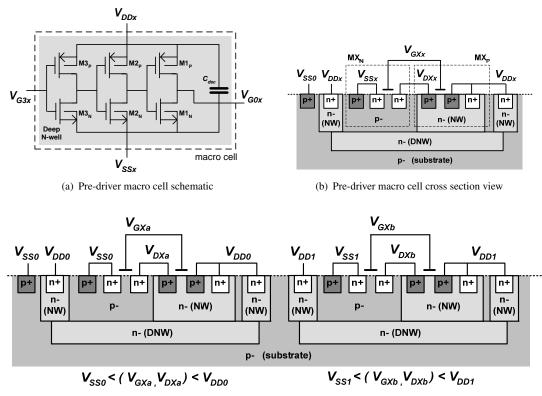

| 4.9  | Details for the design of the pre-driver circuit block                           |

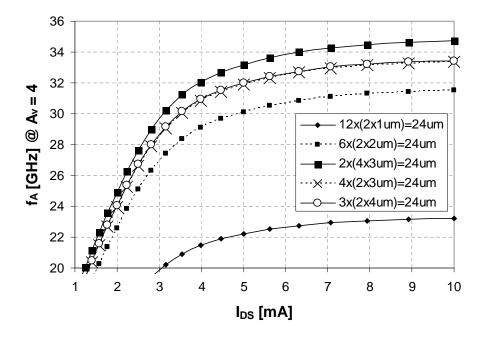

| 4.10 | f <sub>A</sub> results for several G01 NMOS unit cells                           |

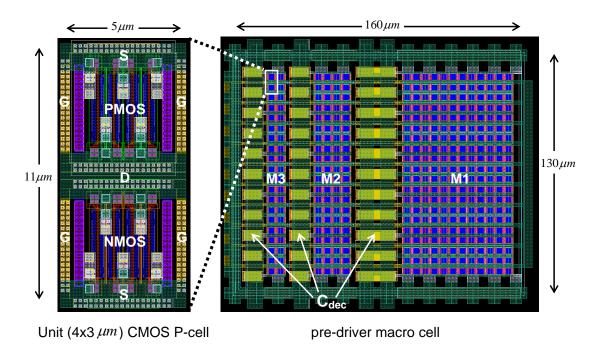

| 4.11 | Layout view of the G01 pre-driver macro cell 61                                  |

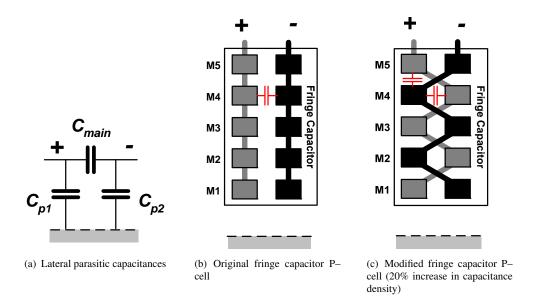

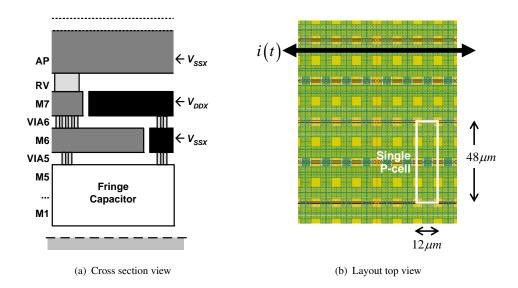

| 4.12 | Fringe capacitor (M1 to M5) P-cells                                              |

| 4.13 | Power traces with embedded capacitor concept                                     |

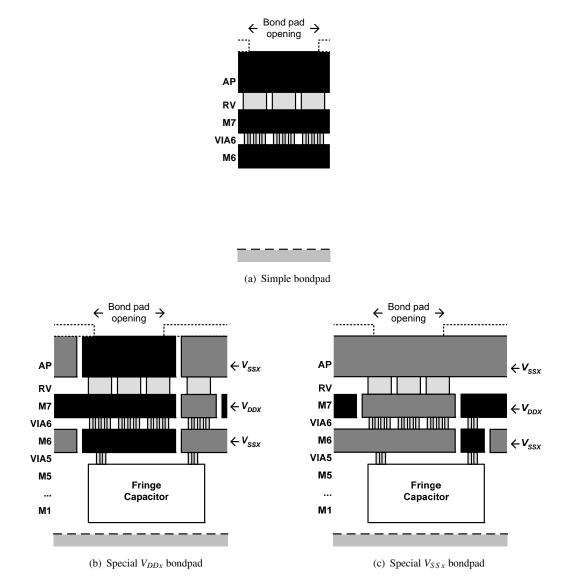

| 4.14 | Bondpads with embedded capacitor concept 66                                      |

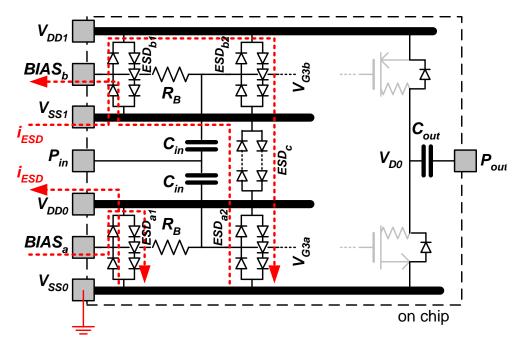

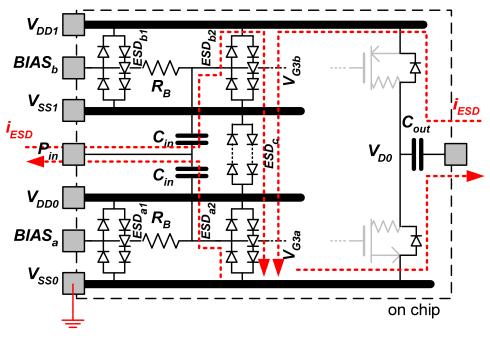

| 4.15 | Schematic of the ESD circuitry with ESD currents                                 |

| 4.16 | Cross section view for the ESD protection circuits involving the signal paths 71 |

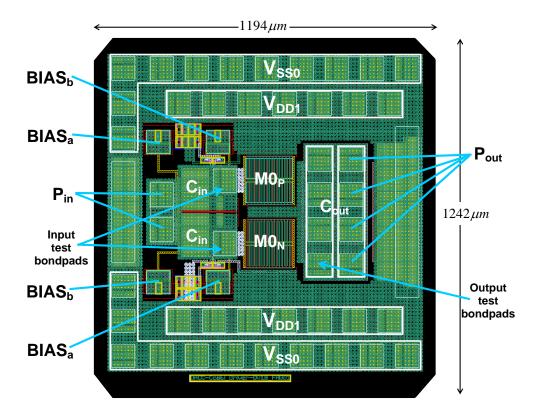

| 4.17 | Layout for the CMOS driver I                                                     |

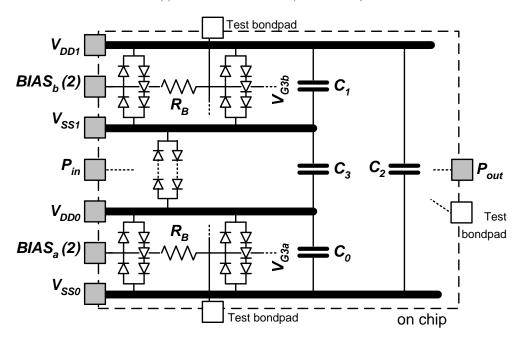

| 4.18 | Schematic of the CMOS driver II and III                                          |

|      | Layout for the CMOS driver II and III                                            |

| 5.1  | Simulation setup for the CMOS driver I chip                                      |

List of Figures x

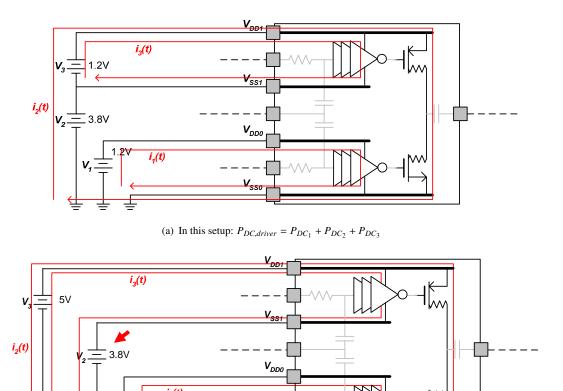

| 5.2          | Two possible arrangements for the voltage supplies in the simulation setup for              |     |

|--------------|---------------------------------------------------------------------------------------------|-----|

|              | the CMOS driver                                                                             | 79  |

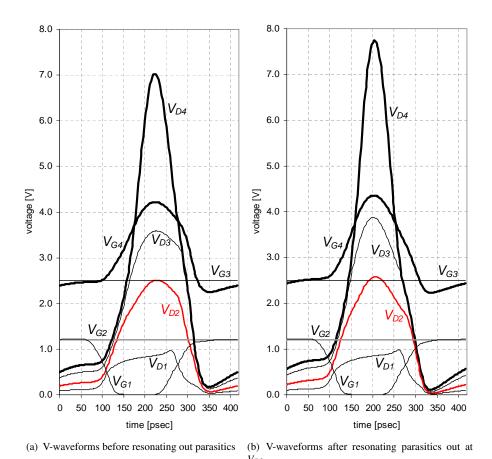

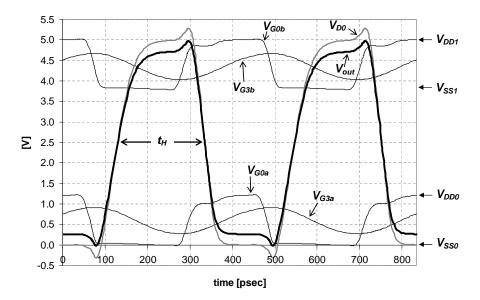

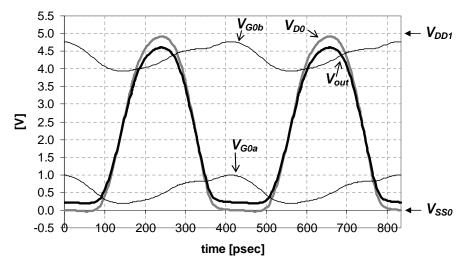

| 5.3          | PSS voltage waveforms for the CMOS driver I                                                 | 80  |

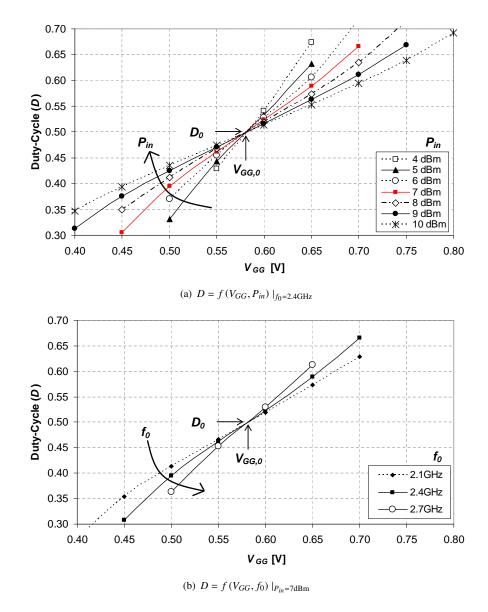

| 5.4          | Duty-cycle as a function of biasing level $V_{GG}$ , $P_{in}$ , and $f_0$ for CMOS driver I | 81  |

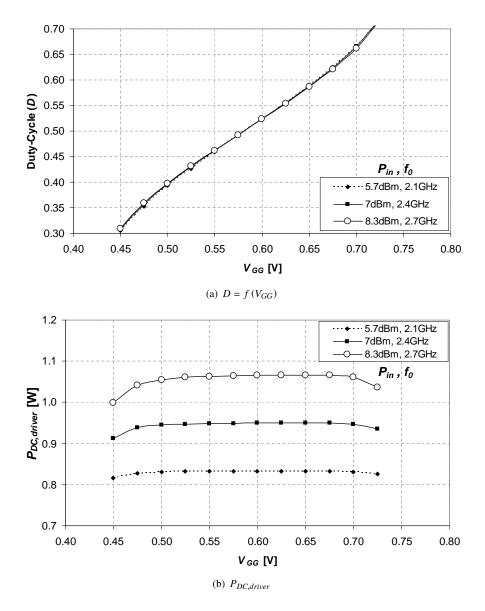

| 5.5          | Duty-cycle results for CMOS driver I                                                        | 83  |

| 5.6          | Load seen by the EDG01 output transistors                                                   | 85  |

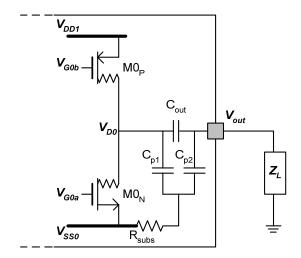

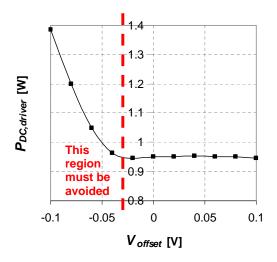

| 5.7          | $P_{DC,driver}$ as a function of $V_{offset}$                                               | 85  |

| 5.8          | Simulation setup for the lineup of the GaN PA with the CMOS driver I                        | 86  |

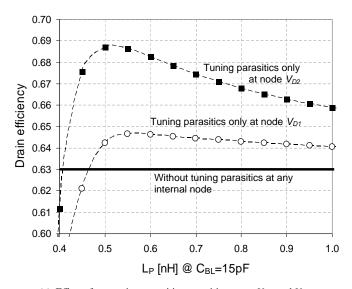

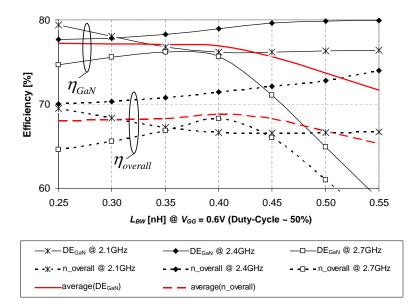

| 5.9          | Selection of interstage bondwire                                                            | 87  |

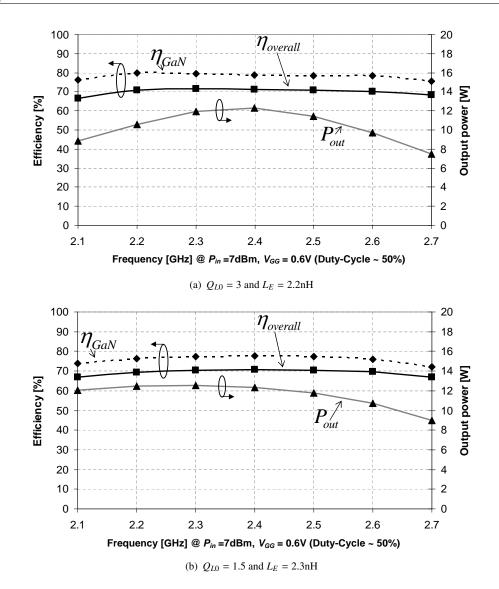

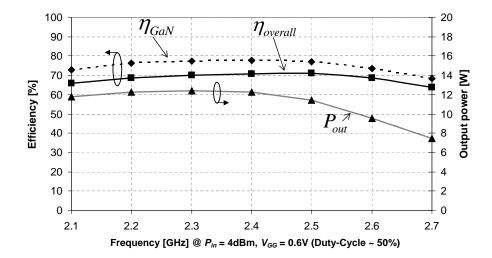

| 5.10         | Simulation results for the GaN PA with CMOS driver I without bondwires                      | 89  |

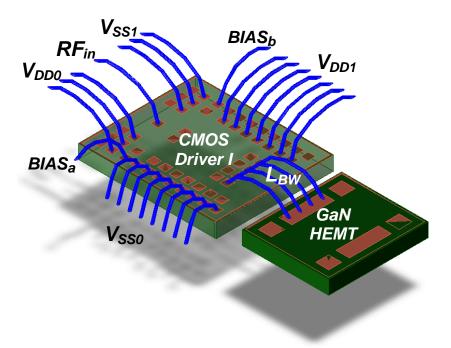

| 5.11         | 3D view of the bondwire models                                                              | 90  |

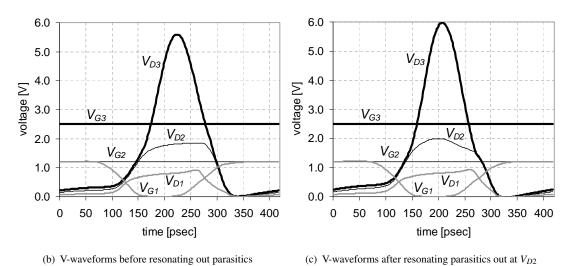

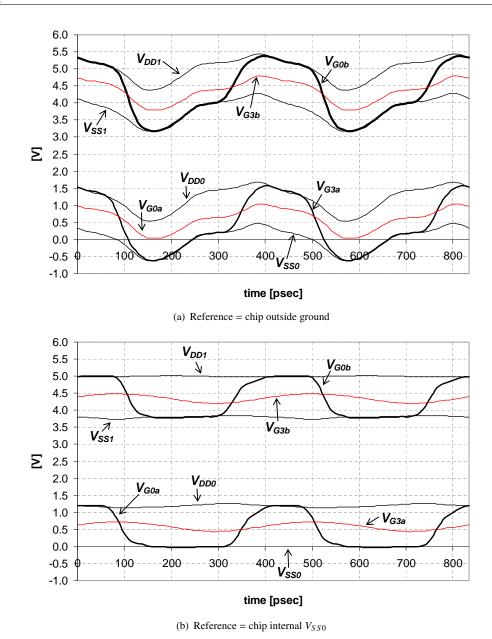

| 5.12         | PSS internal voltage waveforms of the CMOS driver I with bondwires                          | 91  |

|              | Simulation results for the GaN PA with CMOS driver I with bondwires                         | 92  |

|              | Simulation setup for the CMOS drivers II and III                                            | 92  |

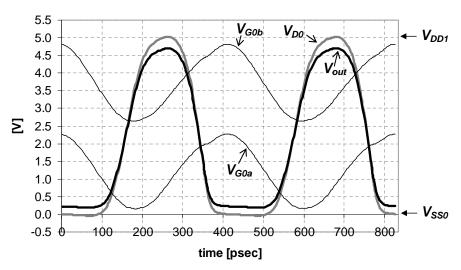

|              | PSS voltage waveforms for the CMOS drivers II and III                                       | 93  |

|              | Duty-cycle in the CMOS driver II and III                                                    | 94  |

|              | Rising and falling times dependency on $P_{in}$ for the CMOS drivers II and III             | 94  |

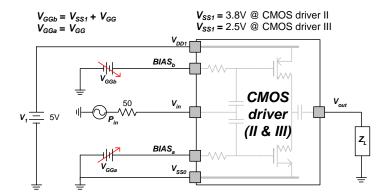

|              | Simulation setup for the line-up of the GaN PA with the CMOS drivers II and III             | 95  |

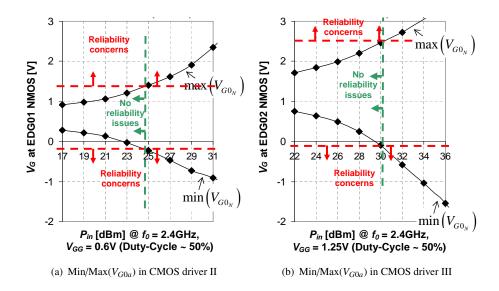

| 5.19         | Minimum and maximum gate voltage at the EDG0x transistors for the CMOS                      |     |

|              | driver II and III                                                                           | 96  |

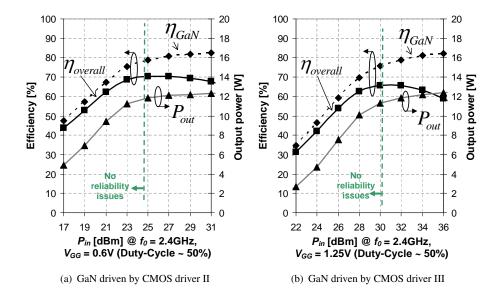

|              | GaN performance as a function of the $P_{in}$ when using CMOS driver II and III.            | 97  |

|              | Simulation results for the GaN PA with CMOS drivers II and III without bondwires            |     |

|              | Harmonic content of a square wave as a function of its duty-cycle                           | 100 |

| 5.23         | Square wave with and without DC coupling                                                    | 102 |

| <b>A.</b> 1  | Common simulation setup for the extraction of $R_{ON}$ , $C_g$ and $C_d$                    | 109 |

| A.2          | $R_{ON}$ for Standard transistors                                                           | 109 |

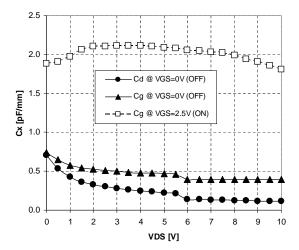

| A.3          | $C_g$ and $C_d$ for Standard transistors                                                    | 110 |

| A.4          | EDG02 NMOS cross-section                                                                    | 111 |

| A.5          | EDG01 NMOS model schematic                                                                  | 112 |

| A.6          | EDG01 model simulation vs. DC measurements                                                  | 113 |

| <b>A.7</b>   | $R_{ON}$ for ED transistors                                                                 | 114 |

| A.8          | $C_g$ and $C_d$ for EDG02 transistors                                                       | 114 |

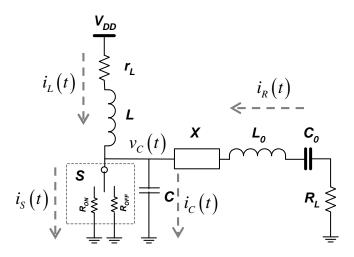

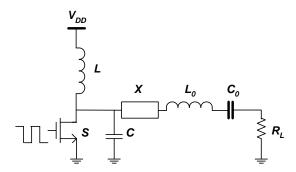

| B.1          | General Class E circuit schematic                                                           | 118 |

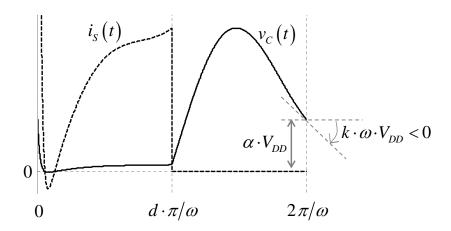

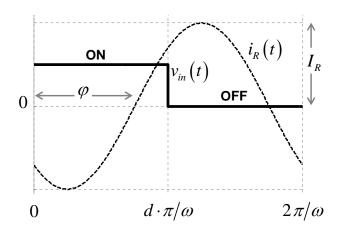

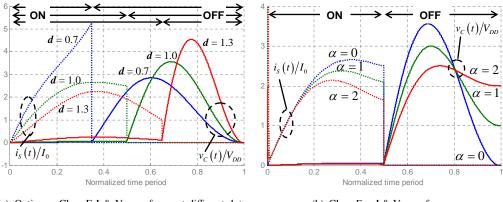

| B.2          | General Class E voltage and current waveforms                                               | 119 |

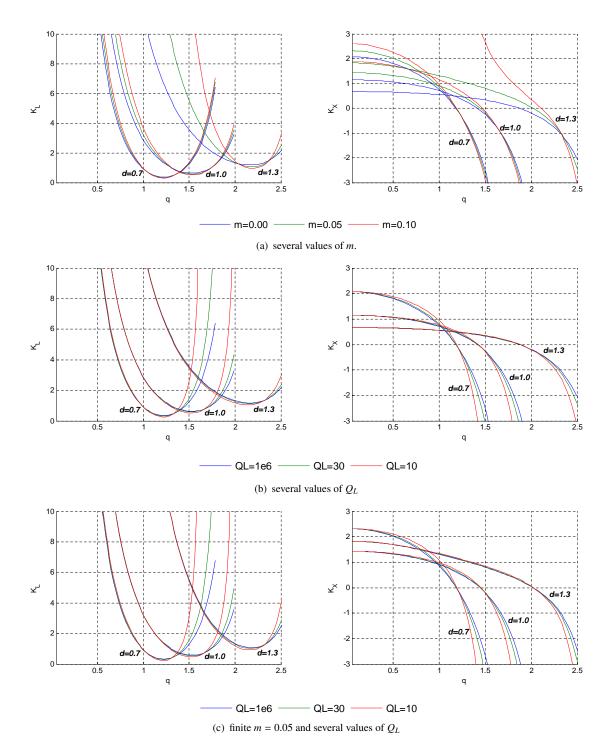

| C.1          | Single-ended Class E circuit schematic                                                      | 136 |

| <b>C</b> .2  | Design Set $K_E$ and drain efficiency for Class E Optimum Mode                              | 139 |

| <b>C</b> .3  | Class E typical I & V waveforms                                                             | 140 |

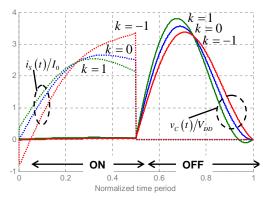

| <b>C</b> .4  | $K_L$ and $K_X$ for Class E in Optimum Mode as a function of $q$                            | 142 |

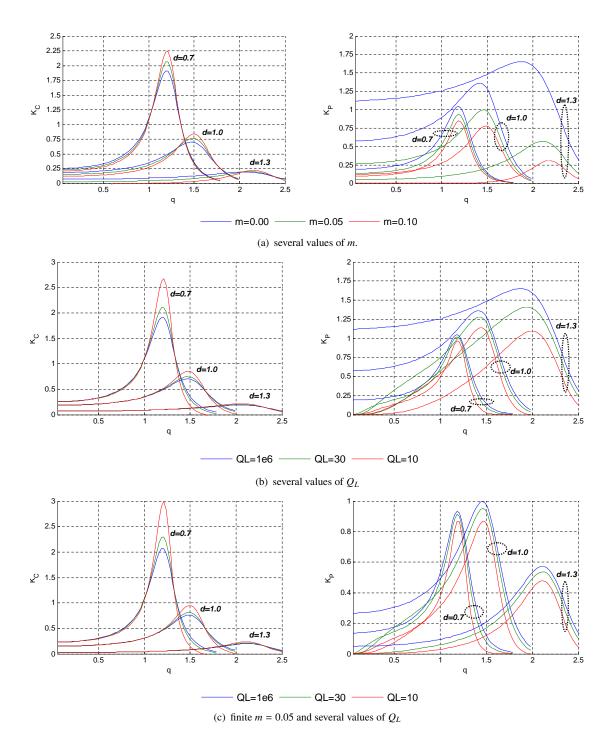

| C.5          | $K_C$ and $K_P$ for Class E in Optimum Mode as a function of $q$                            | 143 |

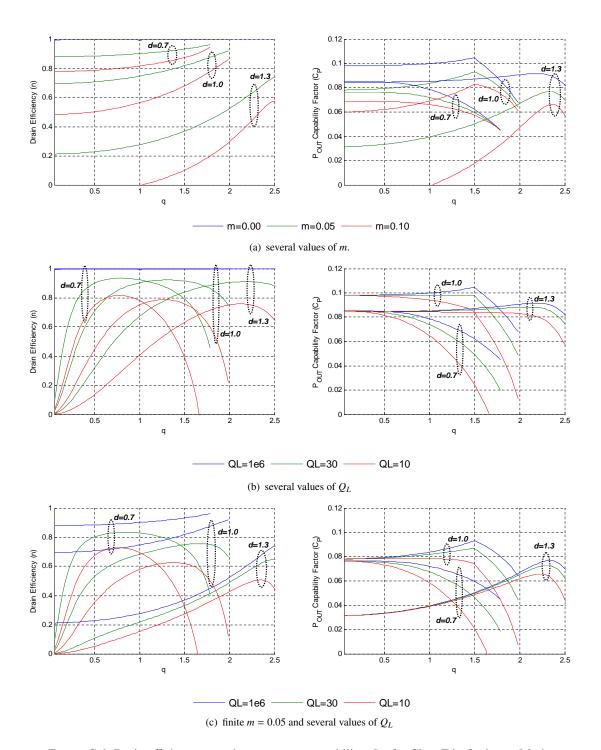

| <b>C</b> .6  | Drain efficiency and output power capability for Class E in Optimum Mode                    | 145 |

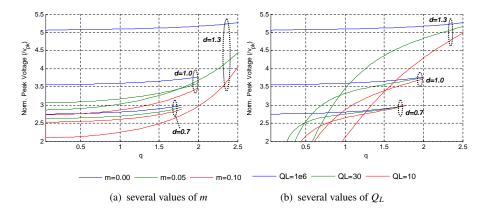

| <b>C</b> .7  | Normalized peak switch voltage for Class E in Optimum Mode                                  | 146 |

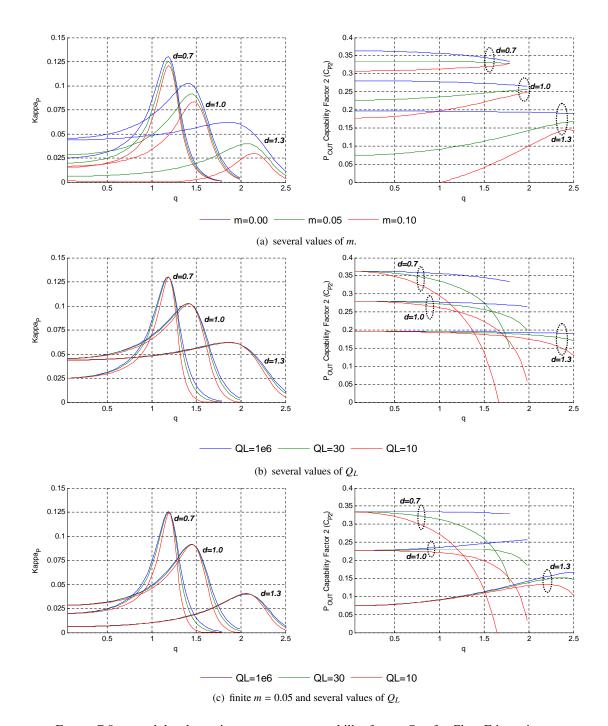

| <b>C</b> .8  | $\kappa_P$ and alternative output power capability factor for Class E in optimum mode .     | 149 |

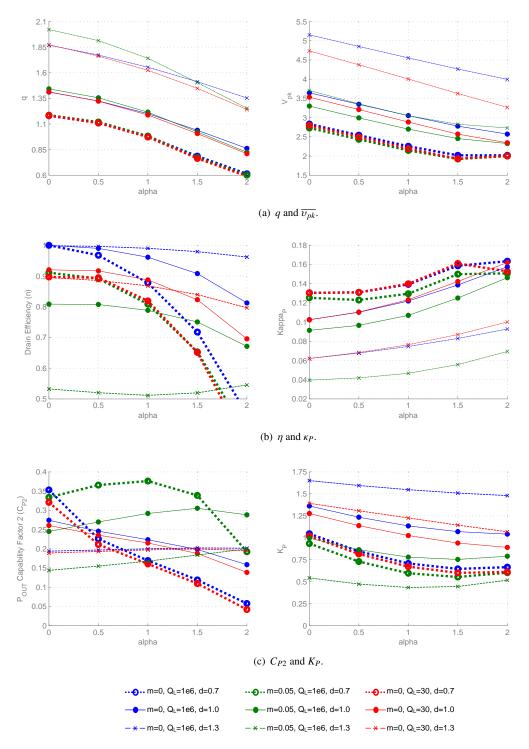

| <b>C</b> .9  | Properties for Variable-Voltage Class E as a function of $\alpha$                           | 151 |

| <b>C</b> .10 | Properties for Variable-Slope Class E as a function of <i>k</i>                             | 152 |

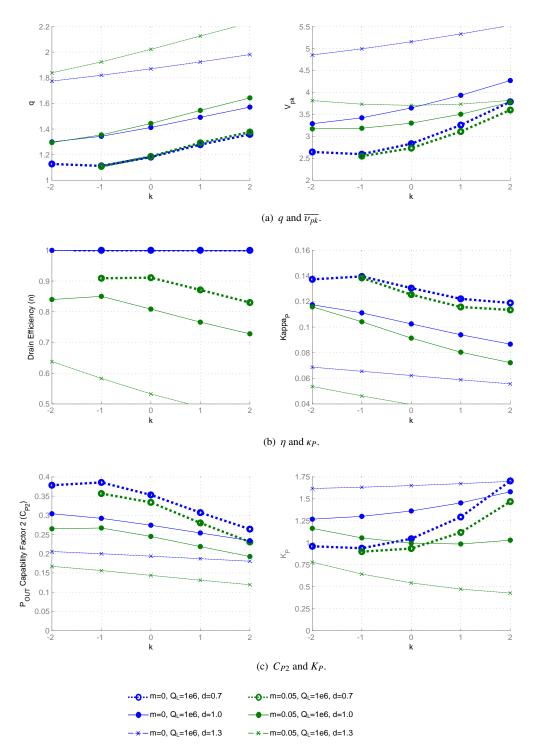

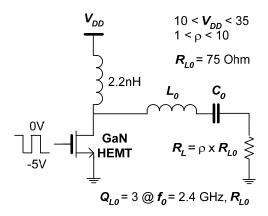

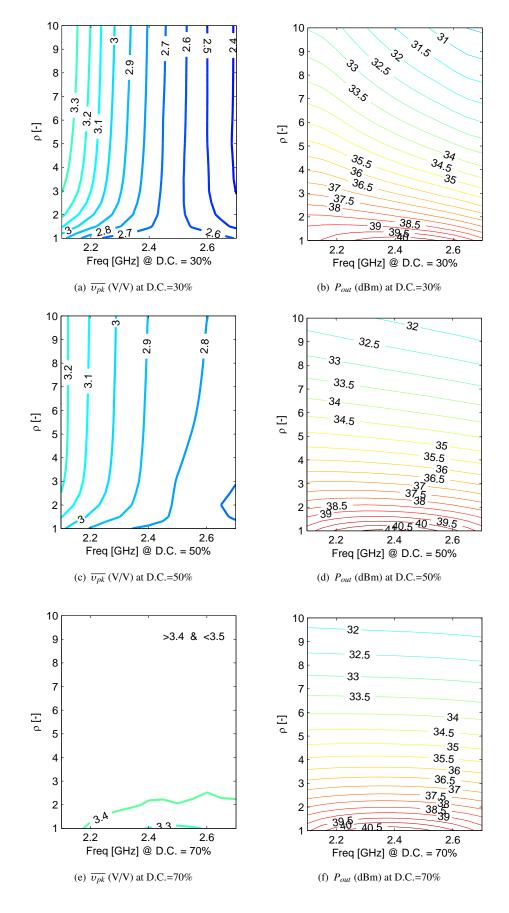

| C 11         | Schematic for the broadband Class E amplifier designed with a GaN HEMT                      | 153 |

| List of Tables | xi |

|----------------|----|

|                |    |

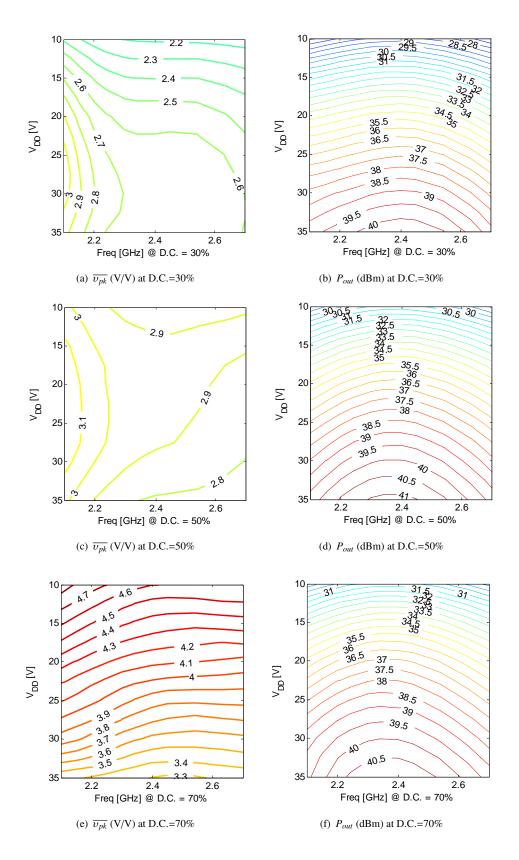

| C.12 $\overline{v_{pk}}$ and $P_{out}$ planes for load modulation   | 155 |

|---------------------------------------------------------------------|-----|

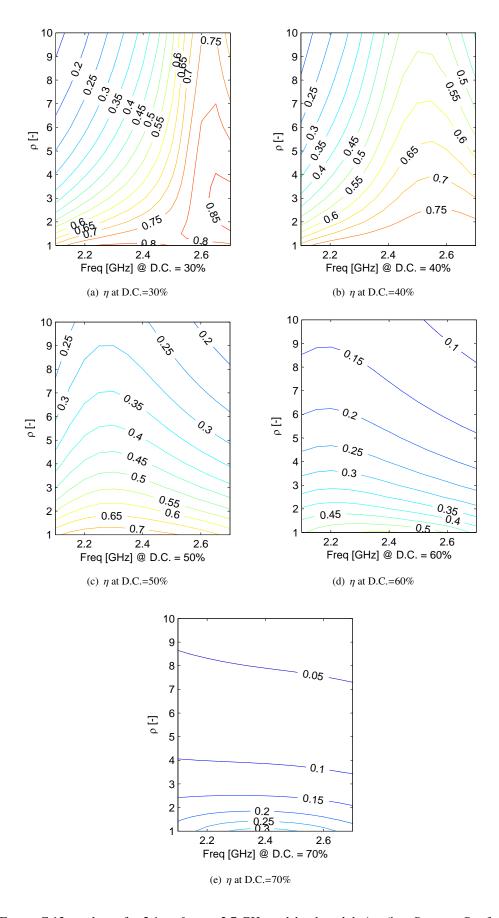

| C.13 $\eta$ planes for load modulation                              | 156 |

| C.14 $\overline{v_{pk}}$ and $P_{out}$ planes for supply modulation | 157 |

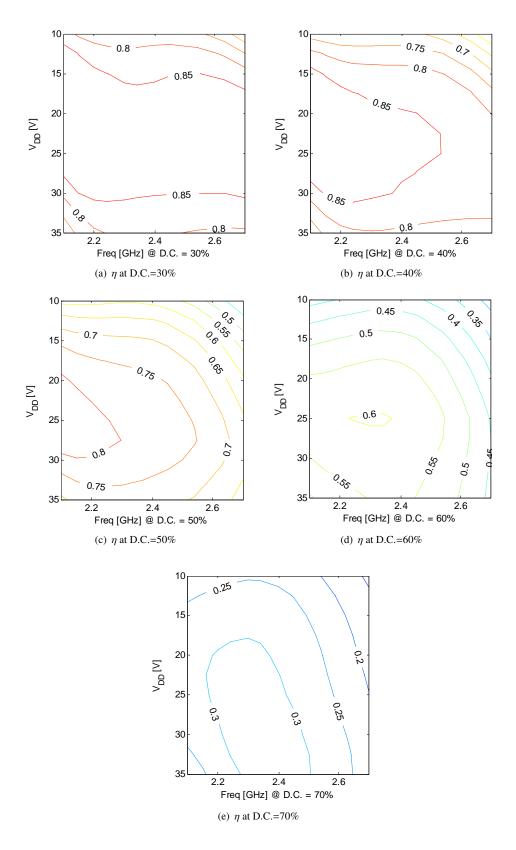

| C.15 $\eta$ planes for supply modulation                            | 158 |

### **List of Tables**

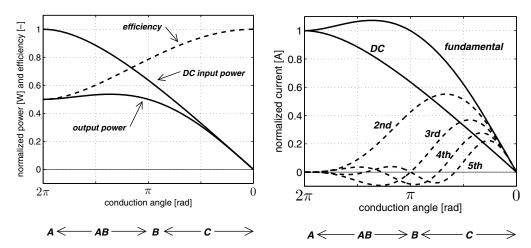

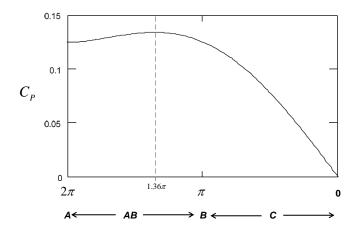

| 2.1         | Summary of $\eta$ , $K_P$ , and $\kappa_P$ for the main gm-based power amplifiers         | 17  |

|-------------|-------------------------------------------------------------------------------------------|-----|

| 2.2         | Summary of $\eta$ , $K_P$ , and $\kappa_P$ for the main switchmode-based power amplifiers | 17  |

| 3.1         | Summary of simulated performance for the 3-MOS Class E topology                           | 35  |

| 3.2         | Summary of simulated performance for the 4-MOS Class E topology                           | 39  |

| 3.3         | Summary of <i>measured</i> performance for the Class E implementations in [1] and         | 39  |

|             | [2]                                                                                       | 39  |

| 4.1         | Summary of target specifications for the CMOS HV driver                                   | 49  |

| 4.2         | Summary of additional features in the CMOS HV driver                                      | 49  |

| 4.3         | Summary of all the transistors sizes in the CMOS driver                                   | 58  |

| 4.4         | Summary of all the AC-coupling capacitors in the CMOS driver I                            | 68  |

| 4.5         | Summary of all the AC-decoupling capacitors in the CMOS driver I                          | 68  |

| 4.6         | Summary of all the AC-decoupling and -coupling capacitors in the CMOS drivers             |     |

|             | II and III                                                                                | 75  |

| 5.1         | Summary of CMOS driver I simulation performance with $C_L = 5 \text{pF}$                  | 84  |

| 5.2         | Summary of CMOS driver I simulation performance with $C_L = 4pF$                          | 84  |

| 5.3         | Summary of CMOS driver II simulation performance with $C_L = 5 \text{pF} \dots \dots$     | 94  |

| 5.4         | Summary of CMOS driver III simulation performance with $C_L = 5 \text{pF}$                | 95  |

| 5.5         | Summary of performance of the CMOS drivers when driving a Class-E GaN                     |     |

|             | HEMT power amplifier                                                                      | 99  |

| <b>A</b> .1 | Summary of the characterization for Standard MOS devices in 65-nm CMOS .                  | 110 |

| A.2         | Summary of the characterization for extended-drain MOS devices in 65-nm CMOS              | 115 |

| <b>B</b> .1 | Description of the parameters used in the Class E Model                                   | 119 |

| B.2         | Classification of the parameters used in the general Class E model                        | 130 |

| B.3         | Design Set $K_E$                                                                          | 131 |

### **Chapter 1**

### Introduction

### 1.1 Motivation

In modern cellular systems, power level, efficiency and linearity are key requirements for the design of power amplifiers (PAs). The PAs for handset applications must provide output powers up to 1-4 Watts, while the output power level for base-stations applications is substantially higher (50 to 600 W) [3].

In base-station applications, the RF power amplifiers are realized in dedicated transistor technologies (e.g. Si LDMOS, GaAs, GaN, InP) because of their superior break-down voltages, that translates in the higher output power levels required. Although at the moment LDMOS technology owns a significant part of the market (95%) for base-station applications, Gallium Nitride (GaN) is gaining interest [3]. The attraction of GaN technology is its substantially higher RF power density, due to its increased breakdown voltage, and higher current density. These factors in GaN devices enable power densities that are two to four times that of LDMOS and GaAs devices. However, GaN is a wide bandgap semiconductor optimized for high voltage (HV) applications, therefore this imposes special requirements on its driving circuitry.

Implementing the driver stages for GaN transistors in CMOS technology has cost and integration advantages; for example, it facilitates the use of digital techniques to improve system performance, or other digital blocks. However, driving GaN transistors using CMOS technology requires drivers able to withstand voltage swings in the order of 5V. Consequently, the implementation of these drivers is a big challenge in CMOS technology due to its limited breakdown

voltages and RF capabilities, which also limit the efficiency of the (pre-)driving stages. However, when implemented successfully, not only cost but also system functionality and system efficiency can be improved. By combining efficient amplifier designs with increased functionality offered by a CMOS driver chip, more complicated amplifier architectures such as Outphasing/LINC (Linear amplification using Non linear Components), Doherty, as well as others, can be further explored to overcome efficiency and linearity limitations.

### 1.2 Thesis Research Goal

The main objective in this thesis is to understand the feasibility and limitations in the design and implementation of high-voltage (HV) CMOS drivers for high-efficiency PAs in base-station applications. The target load of the CMOS driver is a broadband Class E GaN HEMT power amplifier.

The main challenge towards this objective is the low breakdown voltage of advanced sub-micron CMOS technologies, that in 65- and 45-nm CMOS is 1.2 and 1V, respectively. Designing power driver circuits that can sustain 5V swings reliably and efficiently is a big challenge. For our design study we have used the baseline 65-nm CMOS technology, from TSMC.

Two design approaches were explored as potential solutions to reach reliable high-voltage operation. First, a cascoding approach employing the Class E circuit topology, which provides high efficiency, was investigated. Second, an inverter-based driver approach was studied, which has a better wideband performance. This later approach can be considered as a Class D or Class DE like topology.

In the design of these driver circuits, use has been made of standard 65-nm CMOS devices, as well as novel high voltage devices. These later devices make use of a lightly doped drain extension to handle larger voltage swings than the standard devices. These extended-drain (ED) devices have been compared for their RF performance and design trade-offs when utilizing them in practical driver implementations.

### 1.3 State of the art review

To the best of the author's knowledge, there is very little published work on high-voltage CMOS drivers for compound semiconductors power amplifiers. In general, the published work is focused in demonstrating the capabilities of the power amplifiers themselves without considering the implementation of the driving stages.

The work in [4] demonstrates a Class S system that linearizes a switchmode power amplifier realized in GaAs pHEMT technology, for multi-carrier CDMA 2000 and WCDMA patterns, both at 874 MHz and 2.14 GHz. The system includes an integrated multi-stage broadband CMOS amplifier that drives the GaAs transistor. The CMOS amplifier is an inverter-based driver, fabricated in 0.18- $\mu m$  technology. However, its swing is only 2V. Two volt swing is enough for GaAs, but it is insufficient for driving LDMOS and GaN [4].

The work in [5] shows a high-efficient and broadband (2.1 - 2.7GHz) Class-E GaN HEMT PA for base stations. It is concluded in that work, that square-wave input drive is required for a correct switching behavior of the GaN device in a class-E PA. Since that work did not implement a driver circuit, they made use of the nonlinear gate capacitance of the GaN HEMT and tuned the 2nd-harmonic at the input to shape the gate voltage drive waveform. The input power required to drive the PA in that work was 600mW (27.8dBm).

This thesis investigates the CMOS circuits that can drive PAs such as the one in [5], ensuring a reliable operation of the CMOS driver and maintaining the high-performance of the PA.

### 1.4 Thesis organization

Once the overall objective of this thesis has been established and the two main design approaches has been outlined, the rest of this document is organized as follows:

#### Chapter 2 - Background

An overview of basic concepts with respect to the content of this thesis is done in this chapter. We start with a brief description of the main performance parameters of PAs and drivers followed by a short review of all the amplifier classes. Then, the general Class E is introduced. Further details in this amplifier class can be found in two appendices: Appendix B (it presents

the complete analytical derivation of the General Class E model), and Appendix C (it extends the discussion about the general Class E model, including all its operating modes, and it presents a novel way to improve efficiency in back-off for broadband Class E power amplifiers by duty-cycle control). With the need of high voltage device operation in Class E exposed, an overview of the CMOS technology in the context of reliable HV operation is discussed. A description of the available standard and extended-drain devices in 65-nm CMOS technology is presented in Appendix A. Finally, ways to increase the voltage swing in drivers are given.

### Chapter 3 - Class E cascoding approach for HV swings

The device cascoding approach towards HV CMOS driver circuits is presented in this chapter. It is based on Class E cascode topologies. In view of this, the efficiency loss mechanisms associated to the cascode topologies are discussed first. Then, two Class E cascode topologies based on standard devices in 65-nm CMOS are proposed. The Cadence Spectre simulation results of these circuits are presented. Then, a discussion is given between these simulated results and very recently published results of novel extended-drain HV CMOS devices, which have become recently available.

### Chapter 4 - Inverter-based driver approach for HV swings, design and implementation

In this chapter, as alternative to the cascode Class E approach, an inverter-based CMOS HV driver topology is proposed and its target specifications are provided. Three inverter-based drivers have been implemented. The first two employed novel HV thin-oxide extended-drain devices, and the third CMOS driver employed thick-oxide extended-drain devices. At the moment of this thesis report, these devices are still under research.

All drivers were implemented in TSMC 65-nm CMOS technology and were sent to fabrication. These drivers have added functionality such as duty-cycle control to enhance the efficiency of the final PA stage, AC-coupling and -decoupling integrated capacitors to enhance their use in their final application.

#### Chapter 5 - Inverter-based CMOS drivers simulation results

The post layout simulation results for the CMOS driver I, II and III introduced in Chapter 4 are presented and discussed here. Those simulation results include the high-voltage operation

performance and the duty-cycle capabilities of the drivers. Also, simulations including the complete amplifier lineup, i.e. including the broadband Class E GaN power amplifier and the CMOS drivers, are presented. Finally, a comparison between the three CMOS drivers is performed.

### Chapter 6 - Conclusions and recommendations

The main conclusions reached in this work are presented in this chapter. Additionally, suggestions for future work are provided along with some guidelines for their implementation.

### Chapter 2

### **Background**

### 2.1 Introduction

In this chapter, we mainly present background information about the area of this work. First, the main performance metrics and classification of power amplifiers are presented, with a focus on Class E. Then an overview of the most important reliability concerns when designing CMOS power amplifiers/drivers is provided. Finally, a discussion in the options to generate high-voltage swings is given.

### 2.2 RF power amplifier basics

A Power Amplifier (PA) is a key building block in the physical layer of any communication system. A PA is the last block in any transmitter chain and its goal is to provide the required output power to its load, an antenna. It can be composed of several cascaded stages (some of which could be cascoded, as it will be seen later) to boost the output power to the level required. In general, the stages before the output are called *drivers*. Drivers and power amplifiers share many features, and probably the only main difference is the load of each one. A driver will generally have a capacitive load (i.e. the input of another transistor) while the amplifier will have a real load (i.e. an antenna). Next, we discuss the main amplifier performance parameters which we will utilize in this work.

### 2.2.1 Main performance metrics

#### **2.2.1.1 Power Gain**

The (operating) power gain,  $G_P$ , of a PA is the ratio between the output power (i.e. the power delivered to the load<sup>1</sup>),  $P_{out}$ , and the driving input power,  $P_{in}$ . This is,

$$G_{P,dB} = 10\log_{10}\left(\frac{P_{out}}{P_{in}}\right) \tag{2.1}$$

#### 2.2.1.2 Efficiency

The efficiency tells about how good or bad a PA is in converting DC power into RF output power, controlled by an RF input signal. There are several metrics to measure and report the efficiency of a PA [6].

The *Drain* (or *Collector*) *Efficiency*,  $\eta$ , is the ratio between the RF output power to the DC supply power,  $P_{DC}$ :

$$\eta = \frac{P_{out}}{P_{DC}} \tag{2.2}$$

If the gain of the amplifier is not high (as it is usually the case at RF) the driving input power will be significant and  $\eta$  will not properly describe the efficiency of the PA for not considering the driving input power level,  $P_{in}$ . The *Power Added Efficiency*, PAE, includes the driving input power by subtract it from the output power, this is:

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}} \tag{2.3}$$

Notice that PAE approaches  $\eta$  for high values of  $G_P^2$  and it could become negative if  $G_P < 0dB$  since:

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}} = \frac{1 - \frac{P_{in}}{P_{out}}}{\frac{P_{DC}}{P_{out}}} = \eta \left(1 - \frac{1}{G_P}\right)$$

(2.4)

<sup>&</sup>lt;sup>1</sup>In this document, the output power will refer to the power delivered to the load at the fundamental frequency.

<sup>&</sup>lt;sup>2</sup>For  $G_P = 10dB \rightarrow PAE = 0.9\eta$ ;  $G_P = 15dB \rightarrow PAE \approx 0.97\eta$ ;  $G_P \ge 20dB \rightarrow PAE \ge 0.99\eta$

A more general metric is the *Overall Efficiency*,  $\eta_{overall}$ . This metric is always applicable and accounts for the DC power of the driving stages [6],  $\sum P_{DC,drivers}$ :

$$\eta_{overall} = \frac{P_{out}}{P_{DC} + P_{in} + \sum P_{DC,drivers}}$$

(2.5)

### 2.2.1.3 Linearity

Linearity of a power amplifier can be defined by its phase linearity and amplitude linearity. Phase nonlinearity or phase distortion is denoted as PM-PM distortion. Likewise, AM-AM denotes amplitude distortion. The varying envelope of the RF signal may also induce phase errors, indicated as AM-PM. Similarly, PM-AM are amplitude or envelope errors caused by the phase or frequency modulation of the carrier [7].

Linearity is characterized, measured, and specified by various techniques, depending upon the specific signal and application. Single and dual tone tests provide quick and rough information about the linearity of an amplifier, although the real performance is obtained when the amplifier is measured with the real modulated complex signal. The most widely used measure of linearity is the adjacent channel power ratio (ACPR), which compares the power in an adjacent channel to that of the signal [6]. Error vector magnitude (EVM) is a measure of the accuracy of the modulation of the transmitted waveform; it is a measure of the distance between the ideal and measured signal vectors.

### 2.2.2 Output power

A reliable operation of the transistors in any PA is a very important consideration. The *output* power capability factor (also called *transistor utilization factor*) [6] is a metric that measures the amount of output power deliverable from a PA when the transistor is operating under the technology's maximum reliable limits<sup>3</sup>. It is given as

$$C_P = \frac{P_{out,max}}{v_{DS.max} \cdot i_{DS.max}} \tag{2.6}$$

<sup>&</sup>lt;sup>3</sup>Since the transistors used in PAs are in general among the most expensive components in the system, an optimum use of those devices close to their maximum capabilities has become mandatory in practical designs.

where  $P_{out,max}$  is the maximum output power,  $v_{DS,max}$  is the maximum (peak) voltage at the transistor's terminals, and  $i_{DS,max}$  is the maximum current flowing through the transistor.

The output power delivered to a real load  $R_L$  by a PA is proportional to the square of the output voltage swing (drain-source voltage in the case of MOS transistors) and inversely proportional to the load itself. The output voltage swing is in turn directly proportional to the supply voltage  $V_{DD}$ ; this is  $v_{DS} = \overline{v_{pk}} \cdot V_{DD}$ , where  $\overline{v_{pk}}$  is the (unitless) proportionality factor.  $\overline{v_{pk}}$  depends on the amplifier class of operation. Hence, the proportionality factor between  $P_{out}$  and  $V_{DD}/R_L$  will also be determined by the amplifier class of operation. This factor will be called  $K_P$ . Then, the output power of any 'PA class' can be written as:

$$P_{out_{\text{PA class}}} = K_P \cdot \frac{V_{DD}^2}{R_L} \tag{2.7a}$$

$$K_P = f$$

(PA class) (2.7b)

Note that the  $K_P$  factor can be seen as the output power level normalized with respect to the (square of the) voltage supply for a given load. This rather general quantitative definition of output power will help to make direct comparisons between all the amplifier classes that will be discussed in the next section.

However, observe that  $K_P$  does not state anything about the reliability of the PAs, as  $C_P$  does.  $K_P$  only states how much  $P_{out}$  will be generated from a given supply voltage, regardless of whether or not the voltage swing due to that supply voltage can be supported by the transistor in the PA. For this reason, the maximum output power level can also be normalized with respect to the *maximum reliable supply voltage*, that will be called  $V_{DD,max}$ , for a given load. This normalization will be done through a parameter that will be called  $K_P$ . This last parameter can be very useful for switchmode-based power amplifiers<sup>4</sup>, and it is introduced here as a tool to compare those amplifiers with the gm-based PAs. These two PAs types will be discussed in the next section.

<sup>&</sup>lt;sup>4</sup>In CMOS, the reliability of switchmode PAs is more concerned with the limited breakdown voltage capabilities than with the maximum currents, as they scale directly with the number of parallel instances used to constitute the switching devices [8], while the limited voltage does not.

The  $\kappa_P$  factor will be defined from

$$P_{out,max} = \kappa_P \cdot \frac{V_{DD,max}^2}{R_L} \tag{2.8a}$$

(2.8b)

Then,  $\kappa_P$  states the maximum output power  $P_{out,max}$  obtainable with a supply voltage  $V_{DD,max} = v_{DS,max}/\overline{v_{pk}}$  that always ensure a reliable voltage operation of the transistor in the PA. Observe that both  $K_P$  and  $\kappa_P$  are directly related, through  $\kappa_P = K_P/\overline{v_{pk}}^2$ .

#### 2.2.3 PA classification

Power amplifiers can be mainly classified in two big groups [9]: transconductance-based (or gm-based) and switchmode-based. The familiar lettered classification (Class A, B, C, D, E, F, etc.) of PAs makes reference to amplifiers belonging to one of the two groups. Briefly, the first type of PA (gm-based) works as a high impedance *current source* while the second group (switchmode-based) works as a *switch* toggling between two opposite states: ON (or low-impedance) and OFF (or high-impedance). These very different behaviors have important implications in the design methodology and capabilities of such amplifiers.

The closed-form analysis of some of those amplifiers (specially of the switchmode ones) can be very complex, however a basic understanding of those two groups of amplifiers can provide valuable insight for PA and drivers design. A brief description of both types of PA will be given next for that purpose. For a complete and detailed description the reader is referred to more comprehensible works (e.g. [10–12]). This thesis deals with the drivers of switchmode-based PAs for base station applications, specifically Class E.

### 2.2.3.1 gm-based PAs

The transconductance-based PAs are designed with the assumption that they behave as high-impedance *current sources*. An input signal directly controls the output current waveform, and hence these groups of amplifiers are considered to be linear. This is, *there is a linear relation-ship*<sup>5</sup> between the amplitude and phase of the output and input signals.

<sup>&</sup>lt;sup>5</sup>Class B and C could be considered nonlinear, but still there is some relationship between input and output.

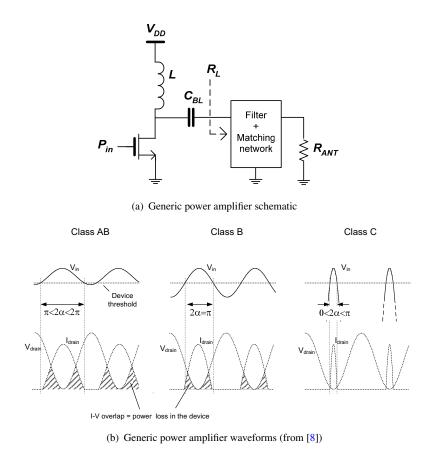

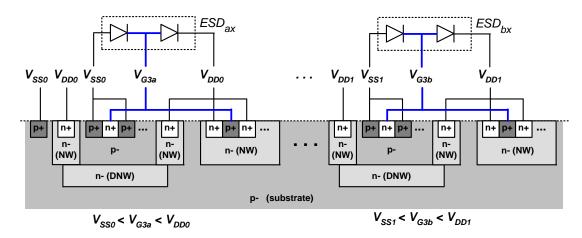

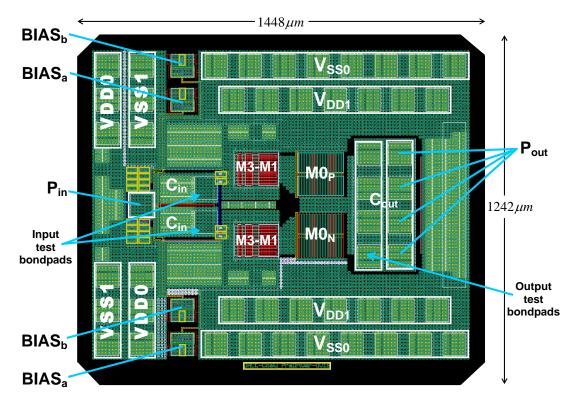

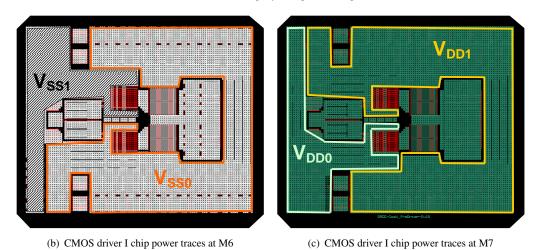

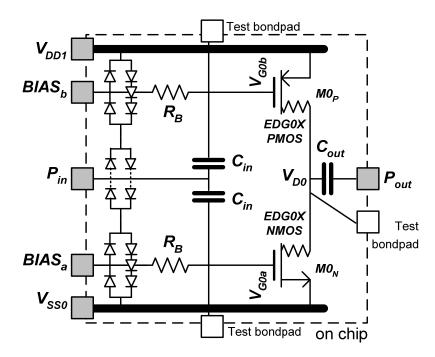

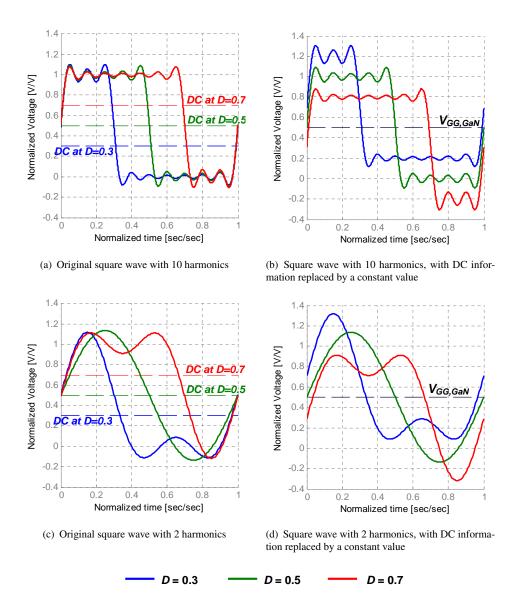

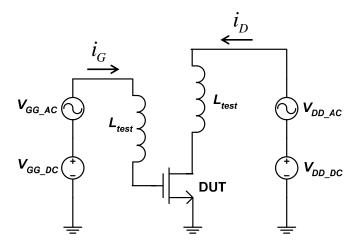

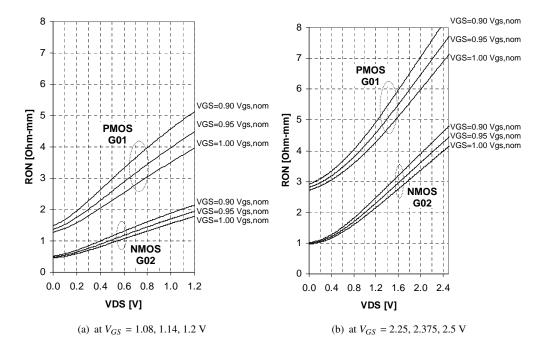

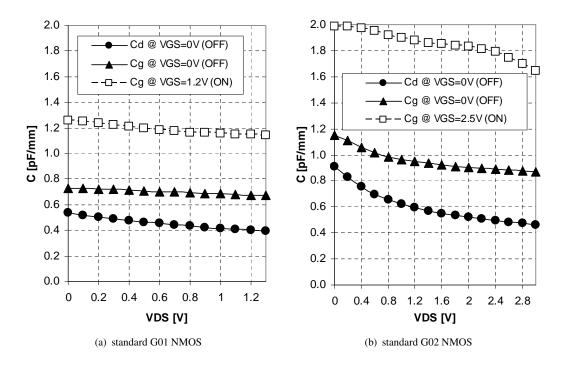

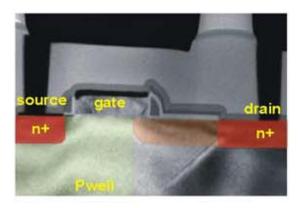

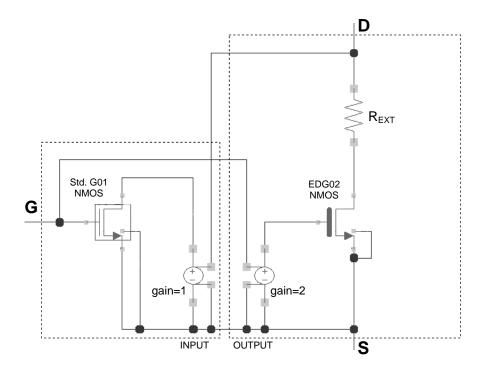

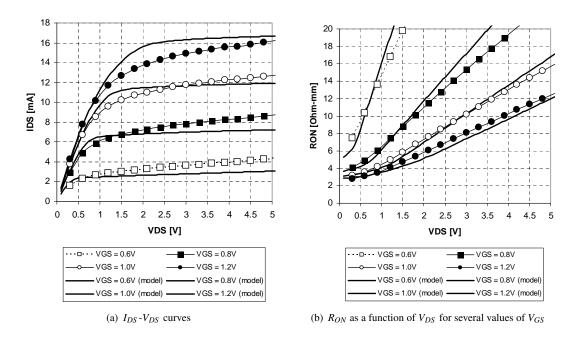

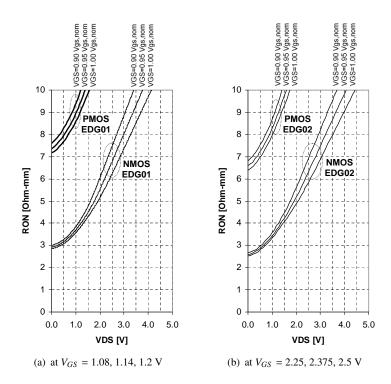

FIGURE 2.1: Generic gm-based power amplifier a) schematic, and b)waveforms.