# Field Programmable Gate Arrays with Hardwired Networks on Chip

# **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen op

dinsdag 6 november 2012 om 15:00 uur

door

MUHAMMAD AQEEL WAHLAH

Master of Science in Information Technology Pakistan Institute of Engineering and Applied Sciences (PIEAS) geboren te Lahore, Pakistan. Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. K.G.W. Goossens

Copromotor:

Dr. ir. J.S.S.M. Wong

### Samenstelling promotiecommissie:

Rector Magnificus voorzitter

Prof. dr. K.G.W. Goossens

Dr. ir. J.S.S.M. Wong

Prof. dr. S. Pillement

Prof. dr.-Ing. M. Hubner

Technische Universiteit Eindhoven, promotor

Technische Universiteit Delft, copromotor

Technical University of Nantes, France

Ruhr-Universitat-Bochum, Germany

Prof. dr. D. Stroobandt University of Gent, Belgium Prof. dr. K.L.M. Bertels Technische Universiteit Delft

Prof. dr.ir. A.J. van der Veen Technische Universiteit Delft, reservelid

ISBN: 978-94-6186-066-8

Keywords: Field Programmable Gate Arrays, Hardwired, Networks on Chip

### Copyright © 2012 Muhammad Aqeel Wahlah

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without permission of the author.

Printed in The Netherlands

# Acknowledgments

oday when I look back, I find it a very interesting journey filled with different emotions, i.e., joy and frustration, hope and despair, and laughter and sadness. At the same time, I feel that I am lucky enough to have some great people around, without whom the journey could not have been possible. I would like to express my gratitude to all of them as following.

First of all I would like to convey my gratitude to Kees Goossens, my promoter and supervisor, for his erudite and invaluable supervision with sustained inspirations and incessant motivation. He guided me to explore the challenging research problems while giving me the complete flexibility, which provided the rationale to unleash my ingenuity and creativity along with an in-depth exploration of various research issues. Despite being a busy person, he still managed to extract time to provide me with his sufficient feedback. His encouragement and meticulous feedback wrapped in constructive criticism helped me to keep the impetus and to remain streamlined on the road of research that resulted in the triumphant completion of this work.

I would also like to thank the PhD committee, i.e., Kees Goossens, Sebastien Pillment, Dirk Stroobandt, Michael Hubner, Koen Bertels, and Stephan Wong for investing their precious time to read the thesis and providing me with their valuable feedback.

I am grateful to Higher Education Commission (HEC) Pakistan for financially supporting my research work during the initial four years of my PhD that enabled me to work and do research in the Computer engineering department of Technical University of Delft, one of the leading universities in the world.

I would like to pay my thanks to all of the colleagues from the Computer engineering department for their discussions and feedback. In particular, I want to thank Dr. Jae Young Hur for the many discussions, motivational talks and valuable guidance during my first two years of PhD. I also want to extend my thanks to Dr. Chunyang Guo for being such a nice friend and office mate in all those PhD years. Furthermore, I want to acknowledge the support of our chair secretary Lidwina Tromp, and administrators Erik de Vries and Eef Hartman to provide a good working environment.

I would like to pay my deepest gratitude to my parents (Muhammad Siddique Wahlah and Razia Sultana) and my siblings (Anwar-us-Saeed, Riffat Shahid, Tasneem Khalid, Muhammad Shafique, Naseem Atif), and my in-laws (Razia

Naveed, Afzal Naveed, and Saba Naveed) for their never-ending support, sincere prayers, and encouragement throughout my Ph.D studies. In particular, I am thankful and pay salute to my parents (Muhammad Siddique Wahlah and Razia Sultana) for their unconditional love and exceptional sacrifice. I always found them standing beside me whenever I needed them. I must say that I can not thank enough to Almighty Allah, Who gave me such great parents.

Finally, I get to the persons who I owe the most for the completion of this journey. My wife Tahira Aqeel, who always stood beside me through this long journey. I must say that she endures all the efforts that were put in to produce the thesis. I would not have reached this point without her loving and caring support, and I want to take this opportunity to thank her from the core of my heart. I also want to present bundle of thanks and love to my little three years old princess Ayesha Aqeel, whose smile and little acts always freshens up my mind and brightens up my days. More so often she makes me feel how beautiful life could have been, and how much blessed a person I am.

I dedicate this thesis to all of my family members, and my advisor Prof. Kees Goossens.

# Field Programmable Gate Arrays with Hardwired Networks on Chip

Muhammad Ageel Wahlah

# **Abstract**

**echnology** down-scaling and platform-based designs have enforced a number of application and architecture trends for system-on-chip (SoC) designs. A modern SoC is now a multi-functional machine that can execute a large number of complex applications by using tens or even hundreds of intellectual properties (IPs). Meanwhile, due to a number of constraints, e.g., short time to market, fickle market demands, and high non-recurring engineering (NRE) costs to name a few, Field Programmable Gate Arrays (FPGAs) have gained popularity to implement SoC designs. The applications in an SoC can be dynamically started and stopped thus forming multiple use-cases. The applications can also have diverse Quality-of-Service (QoS) constraints ranging from non real-time to soft, firm, and hard real-time constraints. At the same time the IP cores in an SoC are heterogenous in nature and run at diverse clock frequencies. The IPs can be microprocessors, DSP slices, memories, and ALU units, etc. The increasing number and diversity of applications and IPs require a powerful onchip communication architecture for quick integration and appropriate QoS. In contemporary FPGAs the onchip interconnect would be soft, i.e., programmed in the configurable fabric.

The above-mentioned application and architecture trends have triggered a series of problems. (1) An increasing number of applications on an FPGA often requires dynamic reconfiguration of an application, which in turn can produce interference with other running applications. (2) The increasing complexity of an application may mean that it can not be mapped entirely on the FPGA, which in turn can encounter loss of state of data during intra-application dynamic partial reconfiguration. (3) The diverse natures of applications make it difficult to fulfill the Quality-of-Service constraints of an application. (4) Similarly, it is hard to achieve (physical) timing closure in an SoC, because of the

increasing number and diversity of the IP cores. (5) The technology down-scaling leads to FPGA architectures that are more prone to faults, e.g., configuration memories and logic elements in an FPGA can be stuck at a particular value. (6) Because communication architecture and IPs are both mapped as soft IPs in the same logic plane of the FPGA, their placement has many restrictions to allow for dynamic partial reconfiguration.

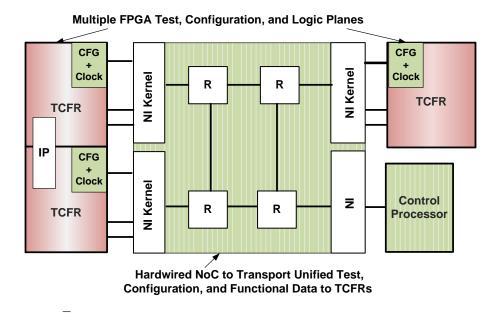

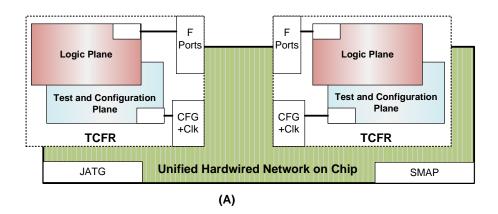

In this thesis, we aim to address the above-mentioned problems by proposing the architecture and design flow of a new FPGA. As the main contribution of the thesis, we propose the FPGA architecture with a hardwired network on chip (HWNoC), and multiple test, configuration, and functional regions (TCFRs). We call it hardwired, because the NoC in an FPGA is built in silicon and not by using the reconfigurable elements. By having a HWNoC we can have a globally asynchronous locally synchronous (GALS) environment, which in turn ensures that data is not lost during inter-IP communication. The HWNoC separates the communication and computation in two disjoint planes, which alleviates restrictions on the placement of IPs. As the second contribution of the thesis, we show how we can use the HWNoC to transport unified test, configuration, and functional data to TCFRs, for testing, faster configuration, and interference-free communication during execution of applications. As the third contribution of the thesis, we demonstrate that how the proposed design flow ensures predictable application behavior by fulfilling the QoS constraints. We also present a 3-tier reconfiguration model that uses the HWNoC, which ensures contention-free communication at architecture level, to overcome the problems of interference and state-loss during inter-application and intra-application reconfiguration respectively. Another contribution of the thesis is that it proposes a non-intrusive test methodology that uses the HWNoC as a test access mechanism to test the presence of faults reliability of FPGA architecture. In other words, the proposed methodology makes sure that applications are always reconfigured and executed on a reliable region of an FPGA, and without effecting the other running applications.

# Table of contents

| Acknov    | vledgme  | ents                                              | 3    |

|-----------|----------|---------------------------------------------------|------|

| Abstrac   | et       |                                                   | i    |

| List of   | Tables . |                                                   | ix   |

| List of l | Figures  |                                                   | xi   |

| List of A | Algorith | nms                                               | xvii |

| 1 Intr    | oductio  | n                                                 | 1    |

| 1.1       | Trends   | 3                                                 | 2    |

|           | 1.1.1    | Application Point of View                         | 2    |

|           | 1.1.2    | Architecture Point of View                        | 6    |

|           | 1.1.3    | Summary                                           | 11   |

| 1.2       | Proble   | ems                                               | 12   |

|           | 1.2.1    | Application Point of View                         | 12   |

|           | 1.2.2    | Architecture Point of View                        | 13   |

|           | 1.2.3    | Summary                                           | 15   |

| 1.3       | Requir   | rements                                           | 16   |

| 1.4       | Techni   | iques                                             | 17   |

|           | 1.4.1    | Hardwired Network on Chip                         | 19   |

|           | 1.4.2    | Design Flow to Bind Applications on FPGA          | 21   |

|           | 1.4.3    | Composable and Persistent-State Dynamic Reconfig- |      |

|           |          | uration using 3-Tier Model                        | 21   |

|           | 1.4.4    | Online FPGA Testing                               | 22   |

|           | 1.4.5    | Summary                                           | 23   |

| 1.5       | Proble   | em Statement                                      | 24   |

| 1.6       |          | Organisation                                      | 24   |

| 1.7       |          | Contributions                                     | 25   |

| 2 | Bac  | kgroun  | d on FPGA & Networks on Chip                        | 27  |

|---|------|---------|-----------------------------------------------------|-----|

|   | 2.1  | Backg   | round: Field Programmable Gate Array                | 27  |

|   |      | 2.1.1   | FPGA Architecture                                   | 27  |

|   |      | 2.1.2   | FPGA Design Flow                                    | 32  |

|   | 2.2  | Backg   | round: Networks on Chip                             | 35  |

|   |      | 2.2.1   | NoC Architecture                                    | 35  |

|   |      | 2.2.2   | NoC Design Flow                                     | 44  |

|   | 2.3  | Conclu  | usions                                              | 46  |

| 3 | Proj | posed S | olution and Related Work                            | 47  |

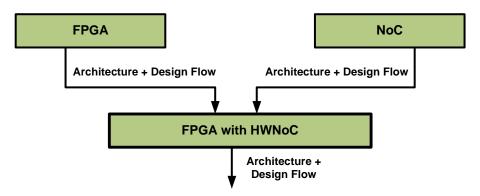

|   | 3.1  | Propos  | sed Solution: FPGA with Hardwired NoC               | 47  |

|   |      | 3.1.1   | Proposed Architecture                               | 47  |

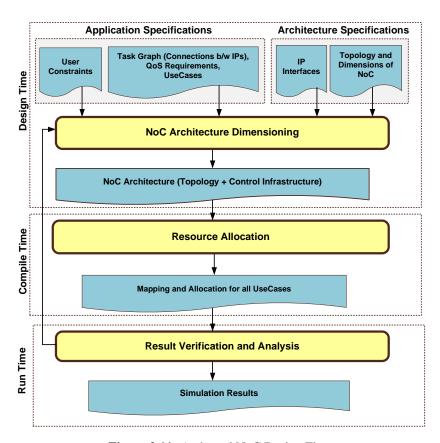

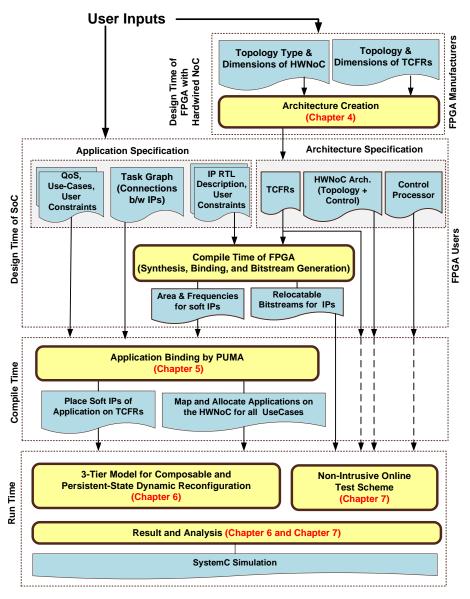

|   |      | 3.1.2   | Proposed Design Flow                                | 50  |

|   | 3.2  | Techni  | ique: Hardwired Network on Chip                     | 53  |

|   |      | 3.2.1   | Overview                                            | 54  |

|   |      | 3.2.2   | Motivation                                          | 54  |

|   |      | 3.2.3   | Related Work on Conventional FPGA with Soft &       |     |

|   |      |         | Hard Interconnect                                   | 55  |

|   |      | 3.2.4   | Positioning with the State of the Art               | 57  |

|   |      | 3.2.5   | Related Work on Custom Reconfigurable Architectures | 59  |

|   |      | 3.2.6   | Positioning with the State of the Art               | 61  |

|   | 3.3  | Techni  | ique: Binding of Applications to FPGA               | 62  |

|   |      | 3.3.1   | Overview                                            | 62  |

|   |      | 3.3.2   | Motivation                                          | 64  |

|   |      | 3.3.3   | Related Work                                        | 65  |

|   |      | 3.3.4   | Positioning with the State of the Art               | 67  |

|   | 3.4  | Techn   | ique: Composable and Persistent-State Dynamic Re-   |     |

|   |      | config  | uration                                             | 69  |

|   |      | 3.4.1   | Overview                                            | 69  |

|   |      | 3.4.2   | Motivation                                          | 70  |

|   |      | 3.4.3   | Related Work                                        | 72  |

|   |      | 3.4.4   | Positioning with the State of the Art               | 74  |

|   | 3.5  | Techni  | ique: Online Testing                                | 76  |

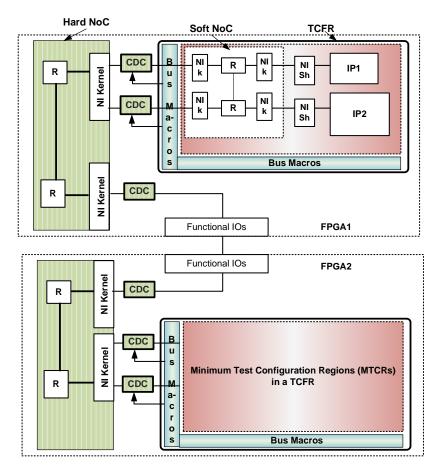

|   |      | 3.5.1   | Overview                                            | 77  |

|   |      | 3.5.2   | Motivation                                          | 78  |

|   |      | 3.5.3   | Related Work                                        | 81  |

|   |      | 3.5.4   | Positioning with the State of the Art               | 82  |

|   | 3.6  | Concl   |                                                     | 8/1 |

| 4 | FPG  | A Archi  | itecture with a Hardwired Network on Chip              | 85  |

|---|------|----------|--------------------------------------------------------|-----|

| - | 4.1  | Overvie  | <del>-</del>                                           | 85  |

|   | 4.2  |          | red NoC Architecture                                   | 88  |

|   | 4.3  |          | onfiguration Functional Region Architecture            | 89  |

|   |      | 4.3.1    | Minimum Test Configuration Regions                     | 89  |

|   |      | 4.3.2    | Bus Macros                                             | 90  |

|   |      | 4.3.3    | Clock Domain Crossing FIFOs                            | 91  |

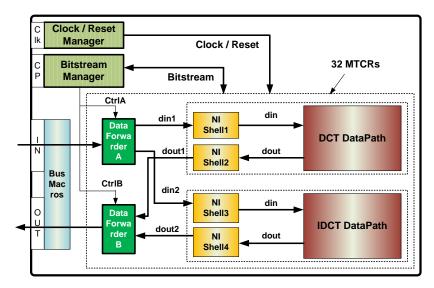

|   |      | 4.3.4    | Bitstream Manager                                      | 91  |

|   |      | 4.3.5    | Clock / Reset Manager                                  | 92  |

|   | 4.4  | Control  | Processor Architecture                                 | 94  |

|   | 4.5  |          | oft Partitioning                                       | 97  |

|   |      | 4.5.1    | Hardwired NoC Partitioning                             | 97  |

|   |      | 4.5.2    | TCFR Partitioning                                      | 99  |

|   |      | 4.5.3    | Control Processor Partitioning                         | 101 |

|   | 4.6  | Implem   | nentation versus Modeling                              | 101 |

|   |      | 4.6.1    | Hardwired NoC Implementation versus Modeling           | 101 |

|   |      | 4.6.2    | TCFR Implementation versus Modeling                    | 102 |

|   |      | 4.6.3    | Control Processor Implementation versus Modeling       | 104 |

|   | 4.7  | Hardwi   | red NoC Extensions                                     | 104 |

|   |      | 4.7.1    | Soft & Multi FPGA NoC                                  | 104 |

|   |      | 4.7.2    | Applicability Extensions                               | 105 |

|   | 4.8  | Archite  | ectural Limitations                                    | 106 |

|   | 4.9  | Results  | and Analysis                                           | 107 |

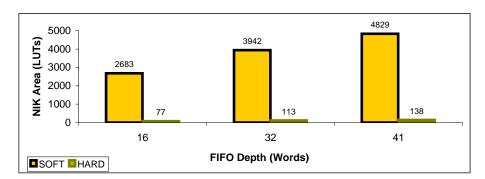

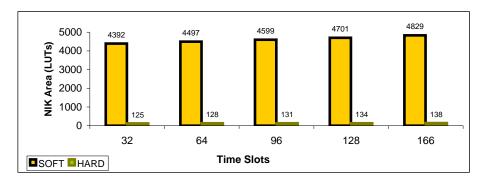

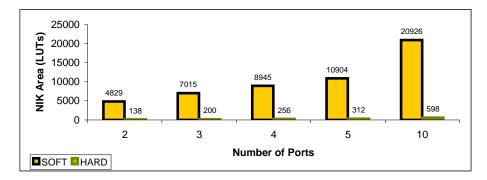

|   |      | 4.9.1    | Network Interface Variations                           | 108 |

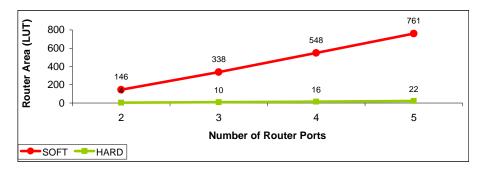

|   |      | 4.9.2    | Router Variations                                      | 110 |

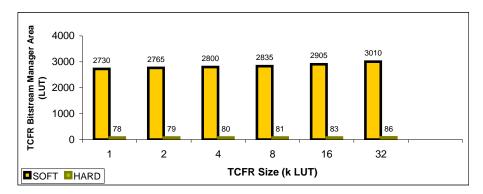

|   |      | 4.9.3    | Test Configuration Functional Region Variations        | 110 |

|   |      | 4.9.4    | Design Space Exploration with Constant TCFR Size .     | 111 |

|   |      | 4.9.5    | Design Space Exploration with Variable TCFR Size .     | 114 |

|   |      | 4.9.6    | Area & Functional Performance Comparison of Soft       |     |

|   |      |          | & Hard NoC                                             | 116 |

|   | 4.10 | Conclu   | sions                                                  | 119 |

| 5 | Prep | aring th | ne FPGA System at Compile Time                         | 121 |

|   | 5.1  | Archite  | ecture and Application Specifications                  | 121 |

|   |      | 5.1.1    | Architecture Specifications                            | 121 |

|   |      | 5.1.2    | Application Specifications                             | 122 |

|   |      | 5.1.3    | Required Objectives                                    | 123 |

|   | 5.2  | PUMA     | : (Road to) Unified Placement, Mapping, and Allocation | 124 |

|   |      |          |                                                        |     |

|   |     | 5.2.1                 | Preprocessing: Database Creation                      | 126  |

|---|-----|-----------------------|-------------------------------------------------------|------|

|   |     | 5.2.2                 | Traversing the Application and Creating Clusters      |      |

|   |     | 5.2.3                 | Solution Space Extraction                             | 130  |

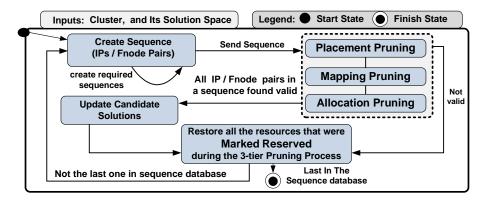

|   |     | 5.2.4                 | Candidate Solution Finding                            | 133  |

|   |     | 5.2.5                 | Solution Construction                                 | 139  |

|   |     | 5.2.6                 | Cluster Resource Reservation                          | 143  |

|   | 5.3 | Limita                | tions                                                 | 143  |

|   | 5.4 | Results               | s And Analysis                                        | 144  |

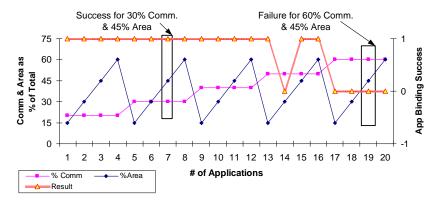

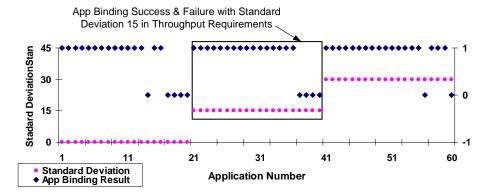

|   |     | 5.4.1                 | Performance: Success Rate                             | 145  |

|   |     | 5.4.2                 | PUMA Scalability                                      | 147  |

|   | 5.5 | Conclu                | isions                                                | 148  |

| 6 | Run |                       | FPGA System Adaptation                                |      |

|   | 6.1 | System                | n Configuration & Programming: Overview               |      |

|   |     | 6.1.1                 | FPGA With Soft Interconnect                           |      |

|   |     | 6.1.2                 | FPGA With Hard Interconnect                           |      |

|   |     | 6.1.3                 | Summary                                               | 153  |

|   | 6.2 |                       | Model for Composable & Persistent-State Run-Time      |      |

|   |     |                       | figuration                                            |      |

|   |     | 6.2.1                 | Responsibilities Across the 3 Tiers                   |      |

|   |     | 6.2.2                 | Enforcing the Inter-Application Composability         |      |

|   |     | 6.2.3                 | Run Time Application Reconfiguration                  | 156  |

|   |     | 6.2.4                 | Assuring the Intra-Application Persistent-State Tran- | 1.50 |

|   |     | <i>.</i> 2 <i>.</i> 7 | sition                                                |      |

|   | 6.0 | 6.2.5                 | Summary                                               |      |

|   | 6.3 |                       | tions                                                 |      |

|   | 6.4 |                       | tion and Results                                      | 168  |

|   |     | 6.4.1                 | Configuration, Programming, & Functional: Compar-     | 160  |

|   |     | 6.4.2                 | ison                                                  | 109  |

|   |     | 0.4.2                 | for Larger Systems                                    | 172  |

|   | 6.5 | Conclu                | isions                                                |      |

| 7 |     |                       | ing of FPGA Architecture                              |      |

| • | 7.1 |                       | est Methodology                                       |      |

|   |     | 7.1.1                 | TCFR Testing                                          |      |

|   |     | 7.1.2                 | Perform HWNoC Test                                    |      |

|   | 7.2 | Limita                |                                                       | 101  |

|     | 7.3     | Results And Analysis                              | 81         |

|-----|---------|---------------------------------------------------|------------|

|     |         | 7.3.1 A Non-Intrusive Test Methodology            | 82         |

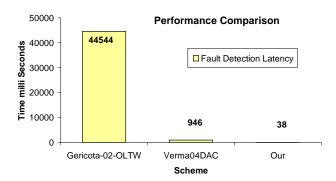

|     |         | 7.3.2 Performance: Fault Detection Latency        | 84         |

|     |         | 7.3.3 Spatiotemporal Cost                         | 85         |

|     |         | 7.3.4 TCFR Area Impact on Performance & Cost 18   | 86         |

|     |         | 7.3.5 Comparison with the State of the Art        | 87         |

|     | 7.4     | Conclusion                                        | 90         |

| 8   | H.26    | 64 Encoder Case Study                             | 93         |

|     | 8.1     | Design Time Specifications                        | 93         |

|     |         |                                                   | 93         |

|     |         | 8.1.2 FPGA Specifications                         | 94         |

|     | 8.2     |                                                   | 95         |

|     |         | 8.2.1 Cluster Creation                            | 95         |

|     |         | 8.2.2 QoS Ensured Cluster Binding                 | 96         |

|     |         | 8.2.3 Cost of QoS Guarantees                      | 97         |

|     | 8.3     | Run Time H.264 Dynamic Reconfiguration            | 98         |

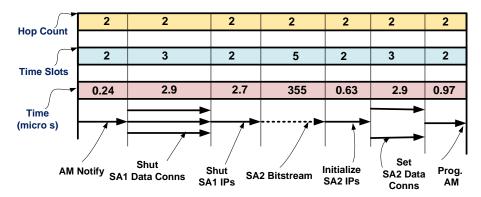

|     |         | 8.3.1 Temporal Analysis of Application Binding 19 | 99         |

|     |         | 8.3.2 Persistent State Intra-Application          | 00         |

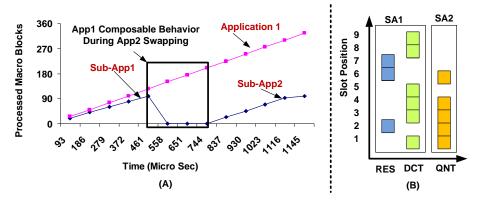

|     |         | 8.3.3 Composable Inter-Application                | 03         |

|     | 8.4     | Conclusions                                       | 03         |

| 9   | Cone    | clusions                                          | 05         |

|     | 9.1     | Thesis Summary                                    | 05         |

|     | 9.2     | Thesis Contributions                              | 07         |

|     | 9.3     | Open Issues and Future Directions                 | 80         |

| Bil | oliogr  | caphy                                             | 09         |

| A   | Glos    | ssary                                             | 25         |

| 1.  | A.1     | ······································            | <b>2</b> 5 |

|     | A.2     |                                                   | 27         |

|     | A.3     |                                                   | 29         |

| В   | Syste   | em XML specification                              | 30         |

|     | B.1     | <del>-</del>                                      | 30         |

|     | B.2     | •                                                 | 32         |

| Lis | st of P | Publications                                      | 34         |

| Samenvatting     | • | • | • |  | • | • | • | • |  |  | • | • | • | • | • | • | • | • | • | • | • | 237 |

|------------------|---|---|---|--|---|---|---|---|--|--|---|---|---|---|---|---|---|---|---|---|---|-----|

| Curriculum Vitae |   |   |   |  |   |   |   |   |  |  |   |   |   |   |   |   |   |   |   |   |   | 239 |

# List of Tables

| 1.1 | Overview Of Trends, Problems, Requirements, and Techniques                                | 18  |

|-----|-------------------------------------------------------------------------------------------|-----|

| 3.1 | Our Work Positioning with respect to the State of the Art on Traditional FPGAs            | 57  |

| 3.2 | Our Work Positioning with respect to the State of the Art on Traditional FPGAs            | 63  |

| 3.3 | Our Work Positioning with respect to the State of the Art on Traditional FPGAs            | 68  |

| 3.4 | Our Work Positioning with respect to Composable Dynamic Reconfiguration Approaches        | 75  |

| 3.5 | Our Work Positioning with respect to Persistent-State Dynamic Reconfiguration Approaches. | 76  |

| 3.6 | Our Work Positioning with respect to the State of the Art on Traditional FPGAs            | 83  |

| 4.1 | Hard Soft Partitioning of FPGA with Hardwired NoC                                         | 98  |

| 4.2 | Modeling Vs Implementation of the Proposed Architecture                                   | 102 |

| 4.3 | Specifications of the Target FPGA Architecture                                            | 111 |

| 4.4 | Soft and Hard Values of Different Components in FPGA                                      | 112 |

| 4.5 | Results of Design Space Exploration with Variable TCFR Size.                              | 115 |

| 4.6 | Area of Network on Chip Components                                                        | 117 |

| 5.1 | Success Rate over Multiple Applications and FPGA Dimensions.                              | 148 |

| 6.1 | Configuration, Programming, and Functional Comparison of Conventional and Proposed Architectures | 172 |

|-----|--------------------------------------------------------------------------------------------------|-----|

| 7.1 | IP Synthesized Area, Frequency, and Bitstream Frames                                             | 182 |

| 7.2 | Cost Evaluated for <b>the Complete</b> FPGA after Varying TCFR Area                              | 186 |

| 8.1 | Application IP Synthesized Area, Frequency and Reconfiguration Time                              | 194 |

| 8.2 | Application IP Frequency and Reconfiguration Time                                                | 199 |

# List of Figures

| 1.1  | A Simple Application                                                                | 3  |

|------|-------------------------------------------------------------------------------------|----|

| 1.2  | Video Application Standards Become More Complex                                     | 4  |

| 1.3  | SoC Architecture Example                                                            | 5  |

| 1.4  | Design Productivity Gap [68]                                                        | 6  |

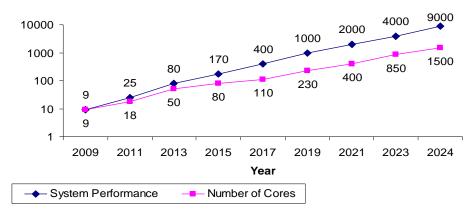

| 1.5  | System on Chip Predicted Future Performance [69]                                    | 7  |

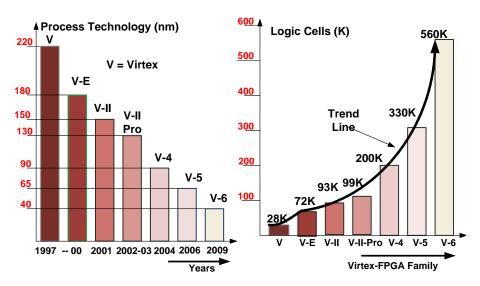

| 1.6  | FPGA Virtex Family Logic Densities over the Years [155,156, 158, 161, 162]          | 8  |

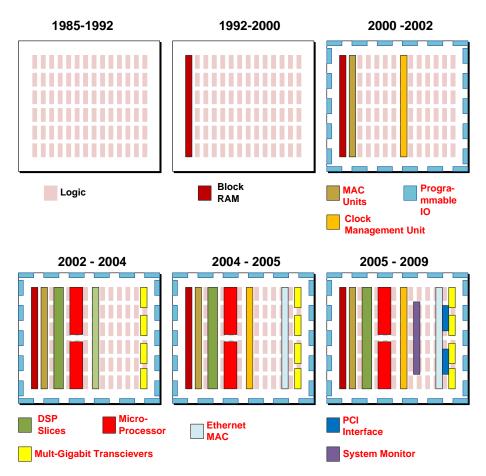

| 1.7  | FPGA Virtex Family Architectural Evolution over the Years [155, 156, 158, 161, 162] | 9  |

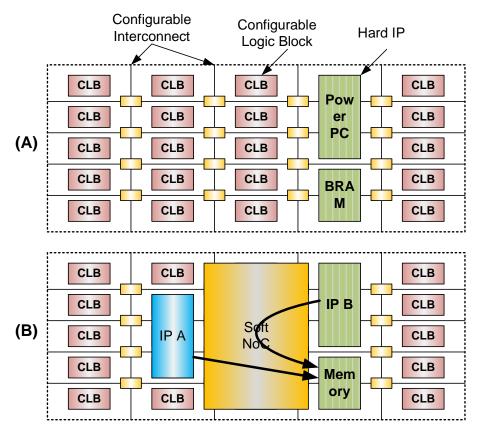

| 1.8  | FPGA Architecture and Application on FPGA                                           | 10 |

| 1.9  | Interconnect Delay over Different Process Technologies [67]                         | 11 |

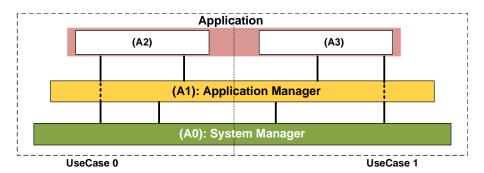

| 1.10 | 3-Tier Behavior and Interaction in Multiple Use-cases                               | 22 |

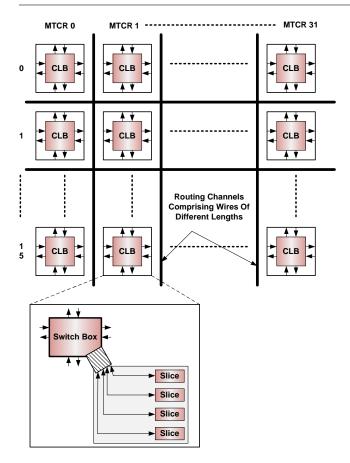

| 2.1  | Architecture of Conventional FPGA                                                   | 28 |

| 2.2  | Configurable Logic Block Architecture                                               | 29 |

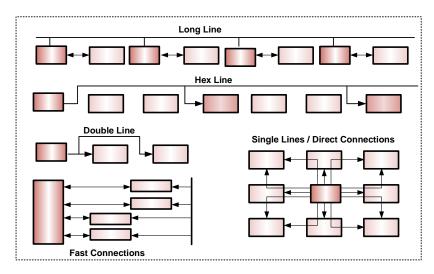

| 2.3  | Different Types of Wires to Connect Logic Blocks                                    | 30 |

| 2.4  | High Level View of FPGA Architecture with Application on it.                        | 31 |

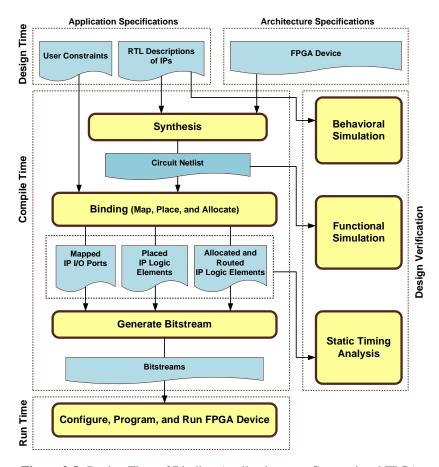

| 2.5  | Design Flow of Binding Application on a Conventional FPGA.                          | 33 |

| 2.6  | Network on Chip Architecture                                                        | 36 |

| 2.7  | Architecture of Master and Slave Buses in NoC                                       | 38 |

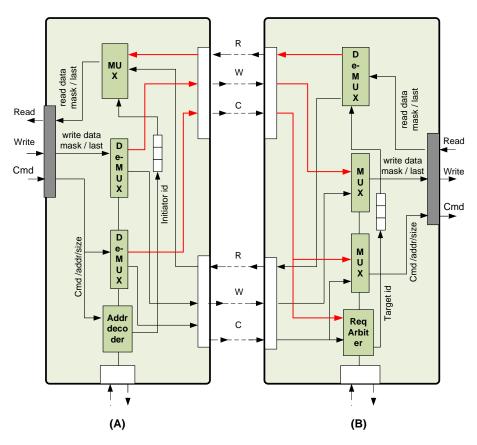

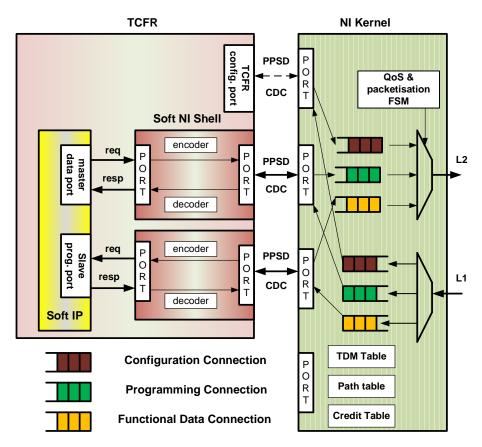

| 2.8  | Architecture of Master and Slave Network Interface Shells                           | 40 |

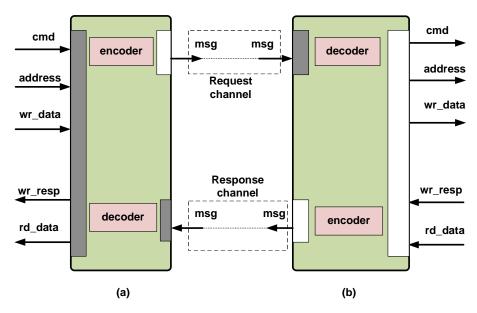

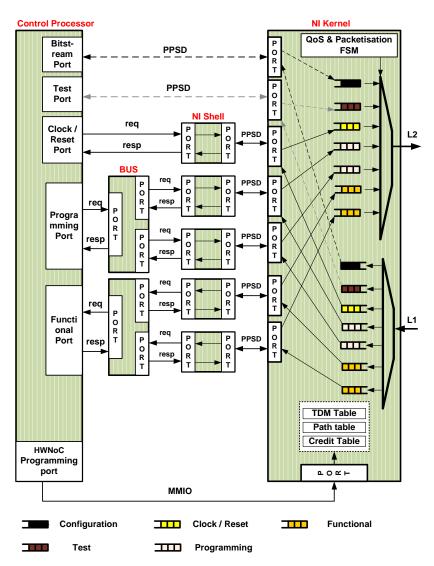

| 2.9  | Network Interface Kernel Architecture                                               | 41 |

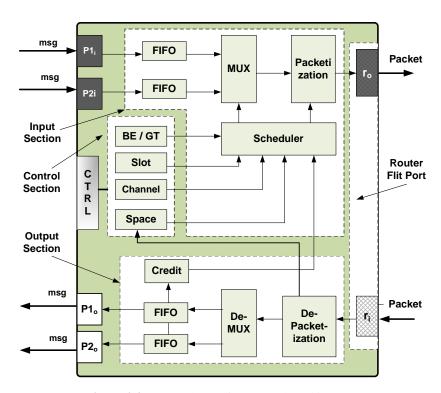

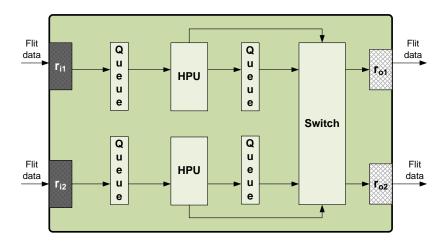

| 2.10 | Router Architecture                                                                 | 43 |

| 2.11 | Aethereal NoC Design Flow                                                                                                 | 45  |

|------|---------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1  | Abstract View of the Proposed Solution (FPGA with Hardwired NoC)                                                          | 48  |

| 3.2  | Architecture of the Proposed FPGA                                                                                         | 49  |

| 3.3  | Architecture of the Proposed FPGA Architecture and Application on it.                                                     | 50  |

| 3.4  | Our Design Flow for the Proposed FPGA Architecture                                                                        | 51  |

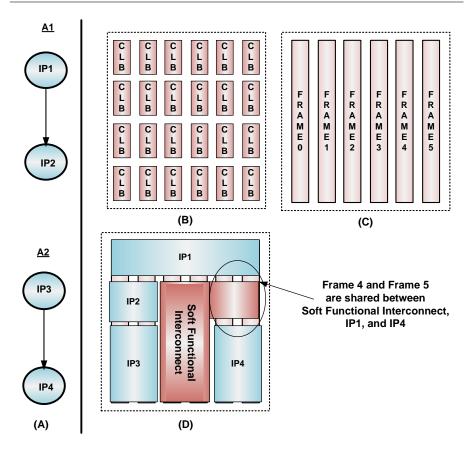

| 3.5  | Restricted IP Placement due to the Presence of Soft Functional Interconnect.                                              | 55  |

| 3.6  | Motivational Case Study for Unified Placement, Mapping, and Allocation                                                    | 64  |

| 3.7  | Motivation for 3-Tier Reconfiguration Model with HWNoC                                                                    | 71  |

| 3.8  | Motivation for our Online Test Scheme                                                                                     | 79  |

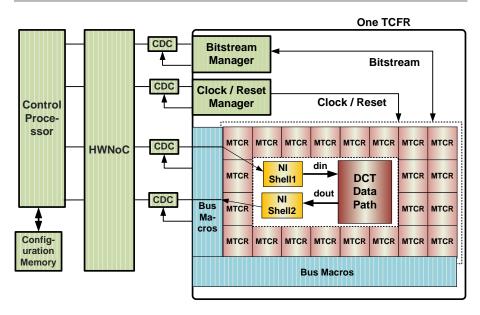

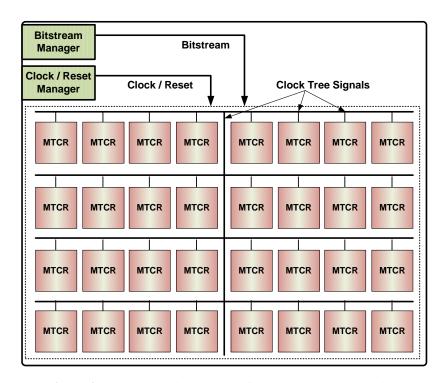

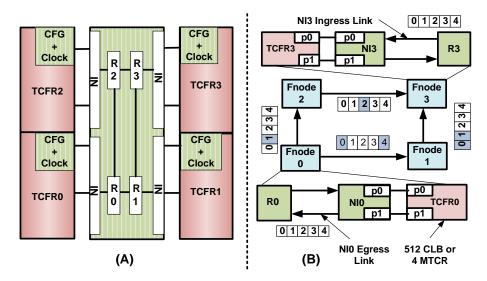

| 4.1  | Overview Diagram of the Proposed FPGA Architecture                                                                        | 86  |

| 4.2  | IP with one Master and one Slave Port, without Reprogramming and Reconfiguration Privileges, and its NI Shell and Kernel. | 87  |

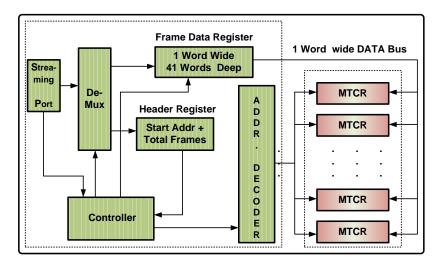

| 4.3  | Detailed Functional Architecture of a Minimum Test Configuration Region                                                   | 90  |

| 4.4  | Bitstream Manager to Write Bitstreams in a TCFR                                                                           | 92  |

| 4.5  | Clock Tree in a Test Configuration Functional Region                                                                      | 93  |

| 4.6  | Control Processor Communication with TCFRs                                                                                | 94  |

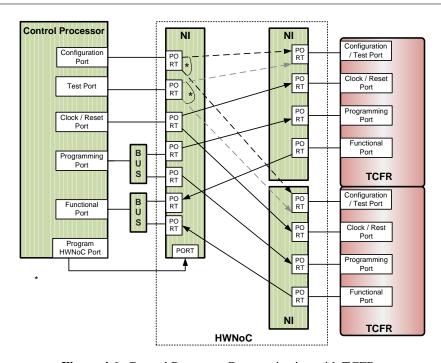

| 4.7  | Details Architecture of the Control Processor                                                                             | 95  |

| 4.8  | Data Forwarders in the SystemC Model of a Test Configuration Functional Region                                            | 103 |

| 4.9  | Architectural Extensions of the Hardwired NoC                                                                             | 105 |

| 4.10 | NI Kernel with Variable FIFO Depths                                                                                       | 108 |

| 4.11 | NI Kernel with Variable Time-Slots                                                                                        | 108 |

| 4.12 | NI Kernel with Variable Ports                                                                                             | 109 |

| 4 13 | Router Area Overhead with Variable Number of Ports                                                                        | 110 |

| 4.14 | Bitstream Manager Area Overhead with Variable Sizes of a TCFR                                                                                        | 111 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

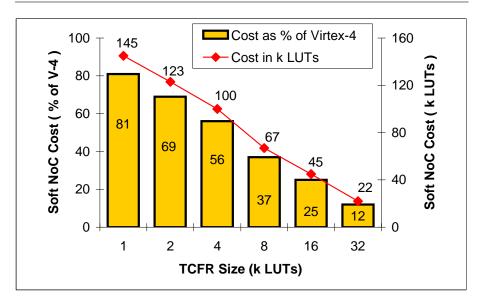

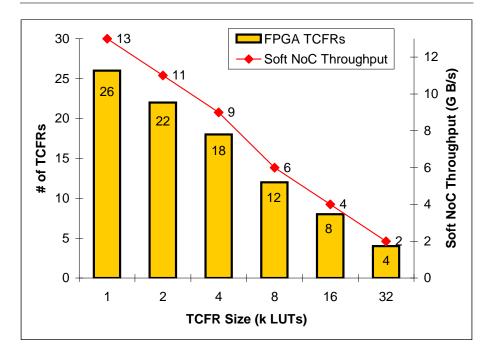

| 4.15 | Soft NoC Cost for a Virtex-4 FPGA with Variable TCFR Sizes.                                                                                          | 114 |

| 4.16 | Soft NoC Benefit for a Virtex-4 FPGA with Variable TCFR                                                                                              |     |

|      | Sizes                                                                                                                                                | 116 |

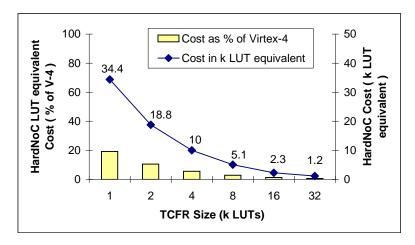

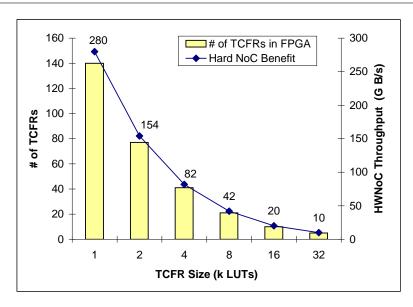

| 4.17 | HWNoC Cost for a Virtex-4 FPGA with Variable TCFR Sizes.                                                                                             | 117 |

| 4.18 | HWNoC Benefit for a Virtex-4 FPGA with Variable TCFR Sizes                                                                                           | 118 |

| 5.1  | FPGA with Hardwired NoC: (A) High level Architecture, (B) Architecture Resource Details                                                              | 122 |

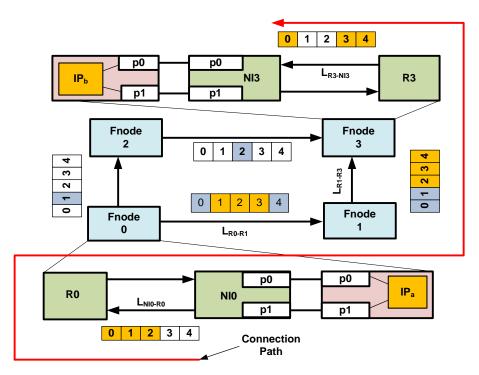

| 5.2  | An Example Instance of Two IPs on FPGA Nodes and Connection Path in Between Them                                                                     | 123 |

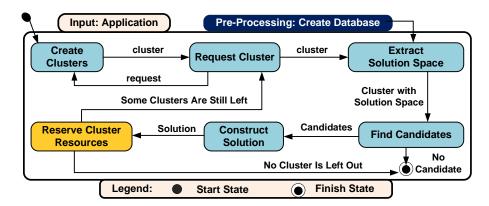

| 5.3  | High Level Flow of our PUMA Scheme                                                                                                                   | 125 |

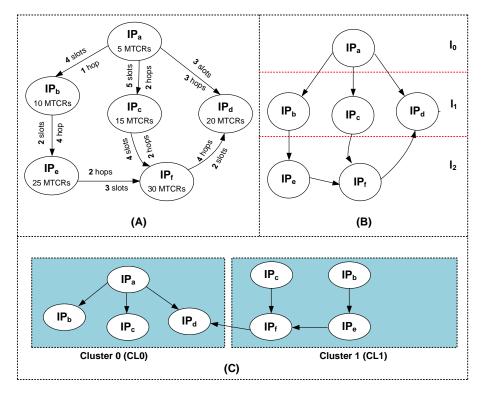

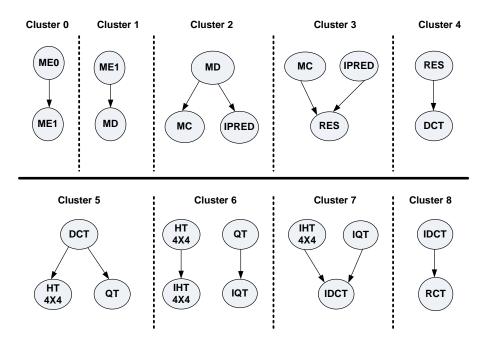

| 5.4  | An Example Application Task Graph and its Clusters                                                                                                   | 128 |

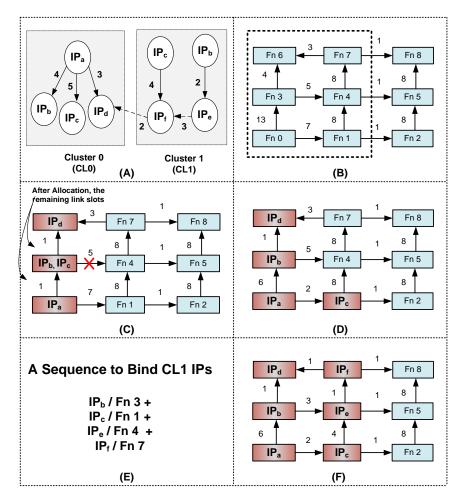

| 5.5  | Example that Shows the Binding of Clusters on our FPGA                                                                                               | 134 |

| 5.6  | Finding the Candidates Solutions                                                                                                                     | 135 |

| 5.7  | PUMA Success Rate with Variable Communication and Area Demands                                                                                       | 144 |

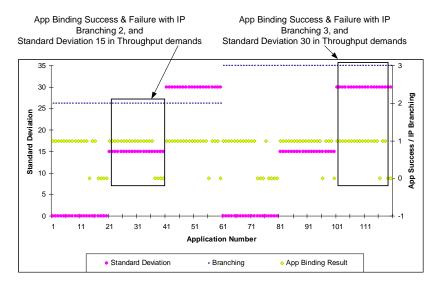

| 5.8  | Binding Results of Applications with Variable Standard Deviations w.r.t. the Communication Throughput Demands                                        | 145 |

| 5.9  | Impact on the Binding Success of Applications by Increasing Inter-IP Dependencies                                                                    | 146 |

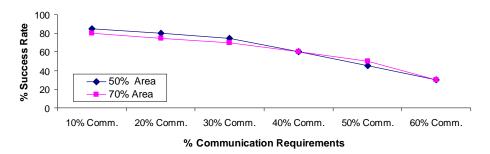

| 5.10 | PUMA Success Rate with High Area (i.e., 50% and 70% Area of FPGA) and Variable Communication Requirements                                            | 147 |

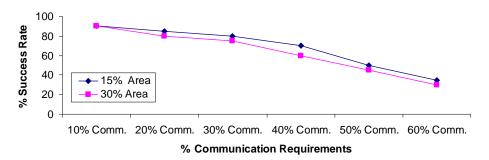

| 5.11 | PUMA Success Rate with Low Area (i.e., 15% and 30% Area of FPGA) and Variable Communication Requirements                                             | 148 |

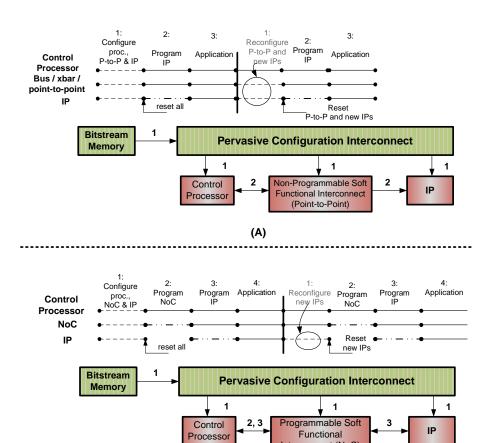

| 6.1  | Conventional Configuration and Programming with (A) Non-Programmable Soft Functional Interconnect, and (B) Programmable Soft Functional Interconnect | 150 |

| 6.2  | New Configuration and Programming with Programmable Hardwired Network on Chip.                                                                       | 152 |

| 6.3  | 3-Tier Reconfiguration Model with an Overview of Responsibilities of each Tier                                | 154 |

|------|---------------------------------------------------------------------------------------------------------------|-----|

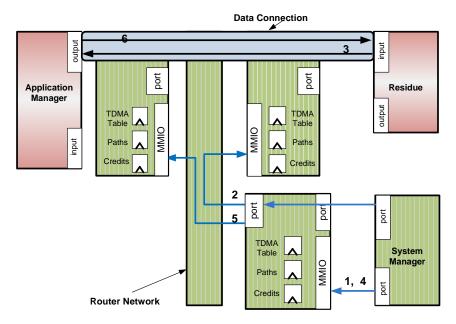

| 6.4  | Application Configuration by Using the System Manager                                                         | 157 |

| 6.5  | Starting a Soft IP                                                                                            | 158 |

| 6.6  | Interaction between an Application Manager and its Application.                                               | 159 |

| 6.7  | Application with Sub Applications and its Interaction with an Application Manager                             | 160 |

| 6.8  | Procedural Description to Assure Persistent State by Using Application Manager                                | 162 |

| 6.9  | Programming Protocol Structure                                                                                | 164 |

| 6.10 | An Example Case Study of Application Manager Operating on Input Data                                          | 166 |

| 6.11 | Procedure to Program NoC Connection                                                                           | 170 |

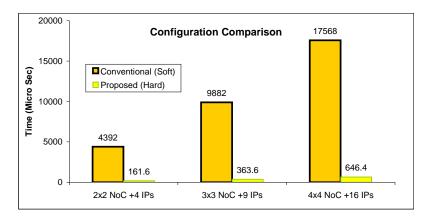

| 6.12 | Configuration Time Comparison Between the Soft and Hard Architectures                                         | 173 |

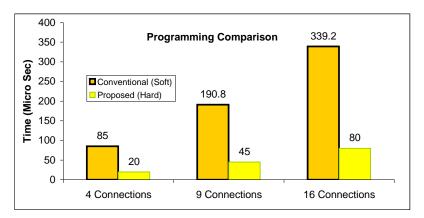

| 6.13 | Programming Time Comparison Between the Soft and Hard Architectures                                           | 173 |

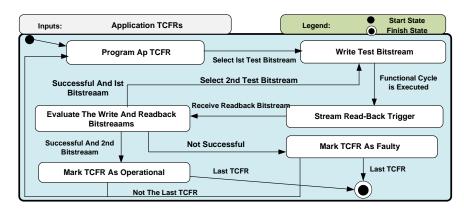

| 7.1  | Run Time Flow for the Test Process                                                                            | 176 |

| 7.2  | Test IP placed in our FPGA with Different Abstract Level Details                                              | 179 |

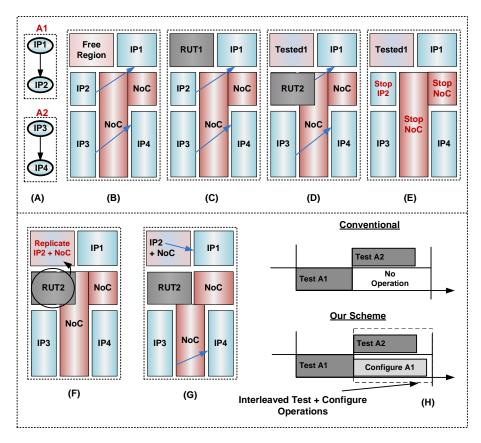

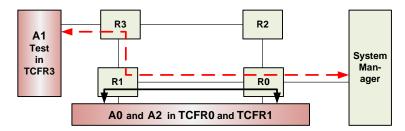

| 7.3  | Applications in Different TCFRs                                                                               | 183 |

| 7.4  | Details of Interleaved Test, Load, and Execute for Multiple Applications                                      | 184 |

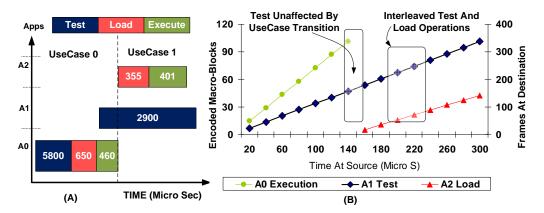

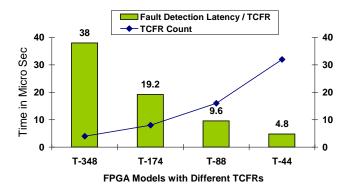

| 7.5  | Different FPGA Architectures with Variable TCFR Area and Count. Also Showing Fault Detection Latency Per TCFR | 187 |

| 7.6  | Per TCFR: Fault Detection Latency ( mili sec)                                                                 | 188 |

| 7.7  | Per TCFR: Spatiotemporal Overheads                                                                            | 189 |

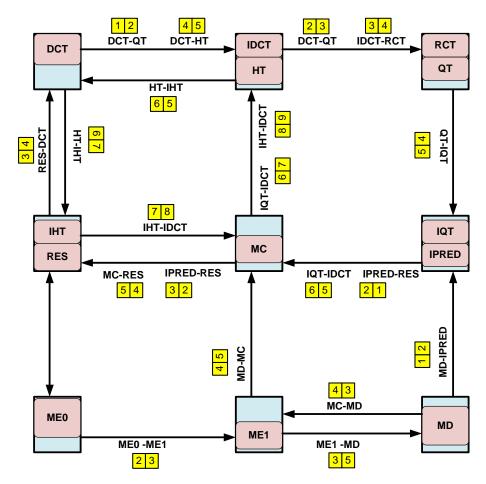

| 8.1  | H.264 Task Graph with Communication Demands                                                                   | 194 |

| 8.2  | Specification of the Target FPGA Architecture                                                                 | 195 |

| 8.3  | Showing H264 Clusters Created by using PUMA                                                                   | 196 |

| 8.4  | Compile Time Binding of H.264 to the Target FPGA Architecture.                                                            | 197 |

|------|---------------------------------------------------------------------------------------------------------------------------|-----|

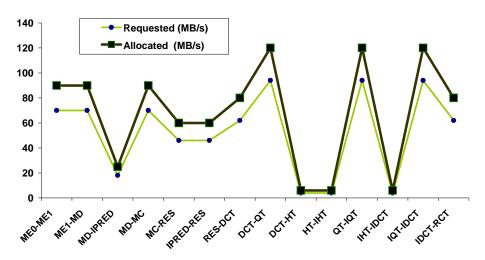

| 8.5  | Showing Communication Cost that is Paid for the H.264 Binding                                                             |     |

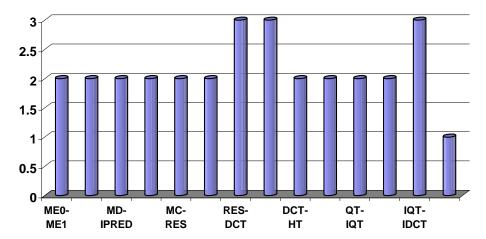

| 8.6  | Showing Hop Count between the IP that Communicate with Each Other                                                         | 199 |

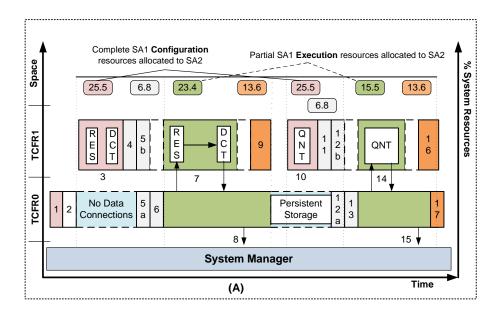

| 8.7  | Showing: Temporal Analysis for SA1 and SA2                                                                                | 201 |

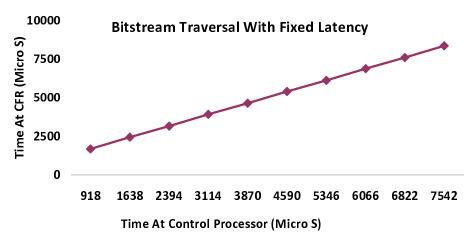

| 8.8  | Bitstream Loading with Fixed Latency with Departure Time at Control Processor (X-axis) and Arrival Time at TCFR (Y-axis). | 202 |

| 8.9  | Persistent State Intra-Application Analysis                                                                               | 202 |

| 8.10 | Showing: (A) Composable Inter-Application Reconfiguration, (B) Allocated Time Slots                                       | 203 |

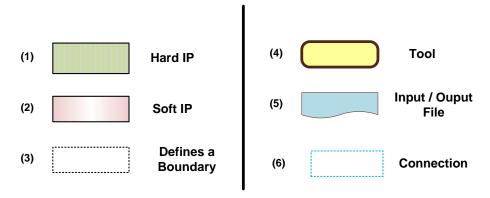

| A.1  | Showing Different Figures that are Used in the Thesis                                                                     | 229 |

# List of Algorithms

| 5.1  | Calculation of Effective Throughput between two FPGA Nodes. | 126 |

|------|-------------------------------------------------------------|-----|

| 5.2  | Cluster Creation Process                                    | 129 |

| 5.3  | Finding the Solution Space for a Cluster                    | 131 |

| 5.4  | Determining the Placement of Source IP of a Cluster         | 132 |

| 5.5  | Determining the Solution Space for an IP of a Cluster       | 133 |

| 5.6  | The Process to Find Candidate Solutions                     | 136 |

| 5.7  | Allocation Pruning Process                                  | 138 |

| 5.8  | Construction of the Best Solution.                          | 140 |

| 5.9  | Calculating Area Cost Matrix to Determine the Best Solution | 141 |

| 5.10 | Resource Reservation Process for the Best Solution          | 142 |

# Introduction

Over the years, the down-scaling of silicon process technologies has followed Moore's law [96, 97], due to which millions of transistors can be placed on a single chip of few millimeter dimensions [34, 65]. System designers have exploited the increased transistor densities by building systems on a single chip (SoC), with enhanced features and increased complexities [10, 33]. The SoCs have proliferated into almost every walk of our life in the form of embedded systems [54, 55], such as cell phones, PDA, GPS, MP3 players, video / still cameras, and many more. A modern day SoC can comprise numerous heterogenous intellectual properties (IPs) to execute multiple applications [69, 138]. The on-chip interconnect that enables different IPs to communicate with each other plays a pivotal role in achieving the desired performance for an SoC [48, 55].

From a target platform viewpoint, Field Programmable Gate Arrays (FPGAs) are increasingly popular to implement SoC designs [85]. The FPGA-based SoCs promise a solution to short time to market, fickle market demands, tight fiscal constraints, and high non-recurring engineering (NRE) costs [73]. A modern day FPGA architecture can offer application-specific integrated circuit (ASIC) like features [8,162], by embedding *hardwired*<sup>1</sup> IP blocks [8,162], e.g. DSP units, MAC units, memory blocks, etc. These computational blocks achieve performance gains for FPGA systems compared to their *soft*<sup>2</sup> implementation. However, as we shall discuss, the current FPGA architectures still face critical challenges in meeting the requirements of scalability, composability, predictability, and reliability required for SoC designs.

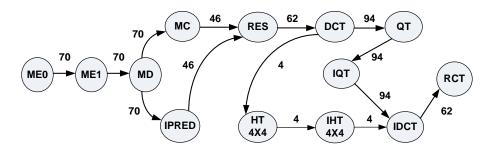

To fulfill the requirements, we propose a new FPGA architecture with a hard-wired network on chip (HWNoC), and multiple test, configuration, and func-

<sup>&</sup>lt;sup>1</sup>We define an IP as *hardwired* or *hard* when it is directly implemented in silicon.

<sup>&</sup>lt;sup>2</sup>A soft IP is mapped on the reconfigurable resources (e.g. CLBs) of FPGA.

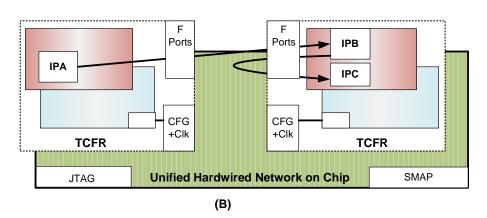

tional regions (TCFRs). The HWNoC serves as the system-level communication architecture and transports test, configuration, and functional data to TCFRs, so as to test, configure, and execute the applications on TCFRs. The proposed architecture has been simulated in SystemC (and is not implemented in the real FPGA hardware). This differs from current FPGA chips that, as we shall explain in Section 2.1, have only a single test and configuration architecture. Additionally, the conventional FPGAs do not have hardwired communication architecture. Instead, the FPGA-based SoCs make use of *soft* communication architecture (e.g., bus, cross bar, and NoC) to transport inter-IP data.

The rest of this chapter is organised as follows. We start with describing the trends of SoCs, Section 1.1. We then point out the problems that have emerged due to these trends, Section1.2. We continue by discussing the key requirements to overcome the problems to implement the FPGA-based SoC in Section 1.3. We then present the techniques to fulfill the requirements in Section 1.4. Afterwards, we state the problem that is the focus of the thesis in Section 1.5. At the end, we list the organisation and contributions of our thesis in Section 1.6 and Section 1.7, respectively.

# 1.1 Trends

In this section we explain the SoC trends from the application point of view, and from the architecture point of view.

### 1.1.1 Application Point of View

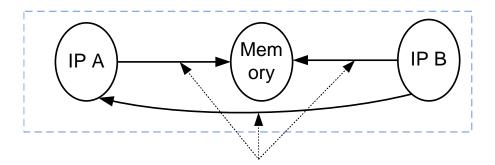

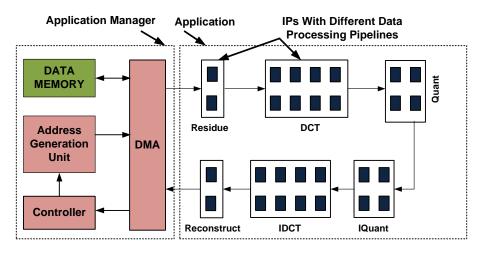

SoC functionality is defined by the set of its *applications*<sup>3</sup>. An application is comprised of multiple (hardwired) IPs, which can have data and control ports to process the *functional data*<sup>4</sup> and *control data*<sup>5</sup>. The IPs use logical connections to communicate with each other, as shown in Figure 1.1.

The recent trends indicate a large number of applications in SoC designs [10, 138]. For instance, OMAP SoC from Texas Instruments can be used for video and speech processing, location-based services, security, gaming, and

<sup>&</sup>lt;sup>3</sup>An application can be defined as a program that is designed to perform a specific function.

<sup>&</sup>lt;sup>4</sup>Functional data (or simply data) stands for the data that is computed or stored by the IPs.

<sup>&</sup>lt;sup>5</sup>Control data is used to program the IPs by writing to their memory-mapped input output (MMIO) registers.

# **Communication Connections**

Figure 1.1: A Simple Application.

multimedia [138]. Similarly, the present day cell phones, which were traditionally used to receive and place phones calls, are now capable of conducting video conferencing, messaging, web browsing, storing pictures, and many more functions [55]. Today's FPGAs [158, 161] are used to implement SoCs that can run complex use-cases<sup>6</sup> [45, 100]. The applications can be started and stopped independently (e.g., on user command). As applications are often developed by different companies, it is desirable that they can be designed and tested independently. Therefore, the absence of interference is required for this, so that applications can be safely loaded at run time<sup>7</sup> and without affecting the already running applications [5, 49, 81]. In short, SoCs have *many applications* that are *dynamically started / stopped* as per user demand.

Typically, applications that execute on FPGA or ASIC architecture, can have diverse performance constraints on the basis of which SoC applications can be classified as *control-oriented* or *streaming* [105,152] applications. Control-oriented applications often have non real-time constraints<sup>8</sup>, whereas the streaming applications often have real-time Quality-of-Service (QoS) requirements and are widely used in embedded systems in the form of video, audio, and gaming. The real-time QoS constraints of streaming applications should be met in a timely manner to ensure a *predictable application behavior* [12]. The QoS constraints of an application are related to its *throughput*<sup>9</sup>

<sup>&</sup>lt;sup>6</sup>A use-case is defined as the set of applications that execute in parallel at a given time.

<sup>&</sup>lt;sup>7</sup>Run time is defined as the time during which an application executes.

<sup>&</sup>lt;sup>8</sup>Control-oriented applications at times can have hard real-time guarantees, e.g., in automotive industry [108] and aerospace

<sup>&</sup>lt;sup>9</sup>Throughput is the average data transfer rate that is required over a communication connection.

**Figure 1.2:** Video Application Standards Become More Complex.

and latency<sup>10</sup> requirements [12], and can fall into soft, firm, and hard categories. In applications with soft real-time quality constraints, the temporal behavior is not critical to preserve the functional correctness of SoC. For instance, during the video conferencing involving H.264 application, an occasional frame's processing deadline miss can be tolerated. On the other hand, the applications with firm and hard real-time quality constraints can not afford such a deadline miss. In these applications, the temporal behavior is critical to preserve the functional correctness of the SoC. Notably, the applications with firm and hard QoS requirements differ with each other in a safety or security aspect. The applications with firm requirements are not safety critical and can be found in consumer electronics, e.g., a Software-Defined Radio (SDR) [98]. On the contrary, in applications with hard real-time requirements, along with satisfaction over the quality constraints, an additional aspect of customer safety is also introduced. The applications with hard constraints occur in the automotive industry [108] and aerospace. Hence we can say that SoCs can have applications with diverse natures, i.e., with different performance constraints. For the thesis, we consider streaming applications that execute on FPGA architectures, and have soft and firm QoS constraints [95].

The end-user influence has also become a driving force in implementing SoC designs. The end users are pushing the vendors for better service quality [12],

<sup>&</sup>lt;sup>10</sup> Latency stands for the amount of time data takes to traverse the communication connection.

Figure 1.3: SoC Architecture Example.

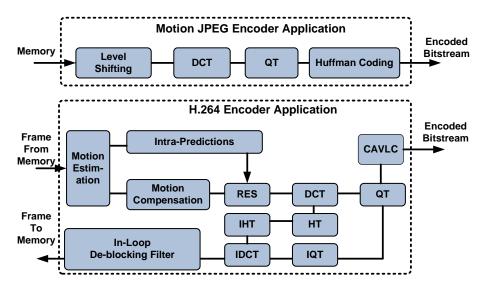

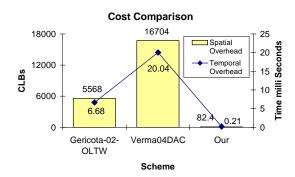

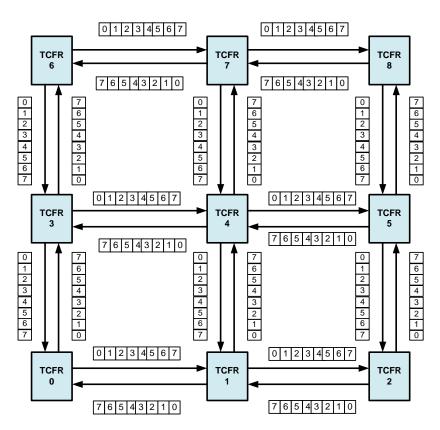

such as higher video resolutions. For instance, the authors in [91] show that H.264 [75] Intra Prediction modes outperform the previously used motion JPEG 2000 [74], in terms of both subjective (visual appearance) and objective (Peak Signal to Noise Ratio) video quality. However, the high quality of H.264 Intra Prediction modes induce high computation as well as communication requirements [59]. Figure 1.2 shows an abstract comparison (in terms of IP blocks) between H.264 and motion JPEG. It shows that the H.264 encoder task graph contains more computational IPs than that of an earlier video coding standard of motion JPEG. Hence we can conclude that SoC applications are becoming more complex.

In recent years the SoC *product life cycle* has shortened due to the rapid technology changes [69]. The product life cycle is defined as the period in which the product is: (i) introduced through marketing, (ii) grows in sales, (iii) attains the maturity during which sales revenue stabilizes, and at some point reaches (iv) a saturation or decline stage [23]. *Time to market has become a critical factor*, because shorter time to market enables a company to launch its products ahead of its competitors.

These application trends have enforced a number of architecture trends for the SoC implementation of these applications. We explain these in the next Section 1.1.2.

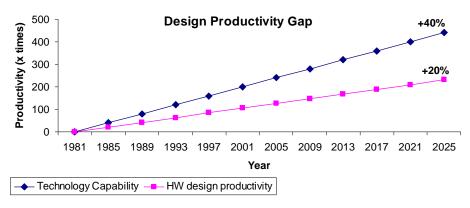

Figure 1.4: Design Productivity Gap [68].

### 1.1.2 Architecture Point of View

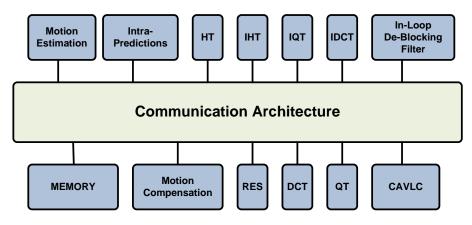

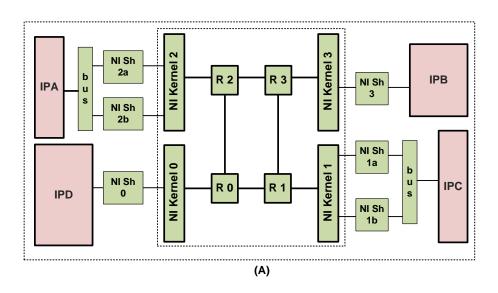

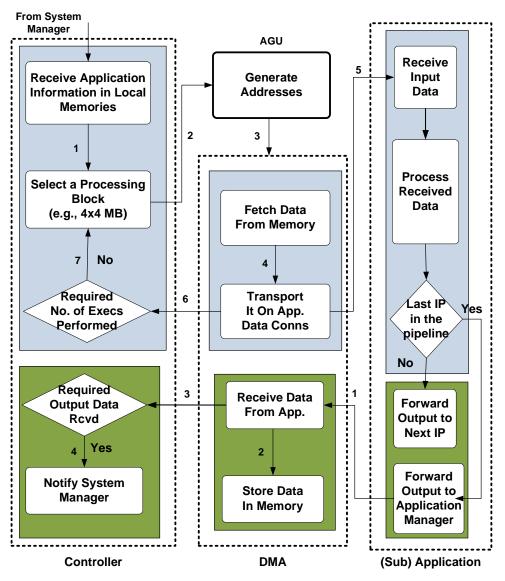

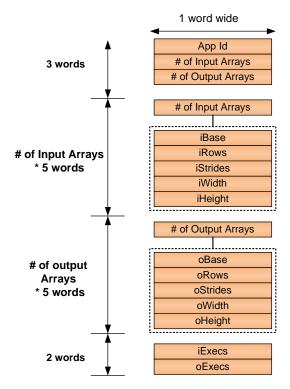

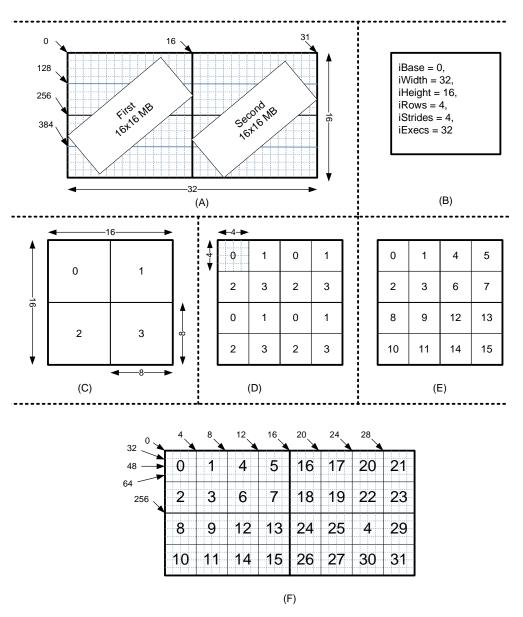

From the architecture point of view, a SoC comprises multiple IPs and a communication architecture [10, 33, 152]. The IPs implement computation or storage to execute the set of applications<sup>11</sup>. The IPs in SoC can be programmable processors, on-chip memories, digital signal processing units, dedicated hardware, peripherals, and internal / external interfaces such as SelectMap, ICAP, etc. [10, 162]. The IPs are made by multiple vendors and, therefore, can have different clocks and interfaces, e.g., AXI [9], DTL [110] for IPs from Philips and NXP, and PLB [157] for the  $\mu$ Blaze family from Xilinx. The IPs communicate (send control and functional data) with each other by making use of standard communication protocols (e.g. Advanced eXtensible Interface (AXI) and Device Transaction Level (DTL)) implemented by a communication architecture such as bus [10, 33], cross-bar switch [62, 151], or a Network-on-Chip (NoC) [13, 43, 48]. Figure 1.3 is an example of a SoC architecture, where the IPs of H.264 video encoder connect to the communication architecture. In short, a single SoC chip can have many IPs with diverse natures in terms of clock frequencies and interfaces, and a communication architecture is used to implement inter-IP communication, i.e., transporting functional and control data.

As a result of the technology down-scaling, the architecture of SoC chip has taken a giant leap during the past twenty years or so. Modern SoCs can comprise tens of IP cores [55], and the designers have enforced platform-based design to implement such complex systems [69]. The platform-based design relies on high reuse of IPs and performs scalable IP integration in a plug-and-

<sup>&</sup>lt;sup>11</sup> In our discussions Memory is considered as an IP.

**Figure 1.5:** System on Chip Predicted Future Performance [69].

play fashion [123]. Through platform-based design, system designers try to reduce the design productivity gap, which indicates the difference in between the available and used number of transistors on a chip [55]. Figure 1.4 shows that the number of transistors on a chip double every 24 months (annual increase of 40%) [68], but the hardware design productivity (of VLSI designers) increases annually with 20%. Importantly, the predicted trends [18, 69] show that future systems will be far complex than the existing ones. Figure 1.5 illustrates one such trend that is mentioned in [69]. It shows that in comparison with an existing SoC in year 2009, a future SoC in year 2024 would posses approximately 150 times more processing elements to obtain a performance of 9000 times better. Hence we can say that the current and predicted trends indicate SoCs with *many IP cores*.

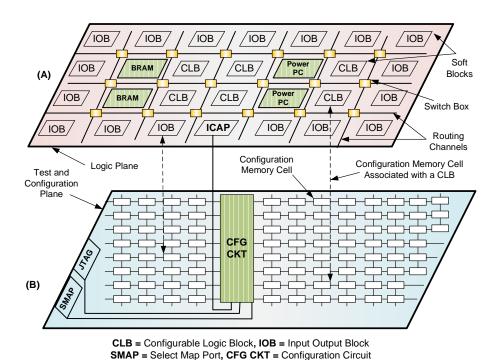

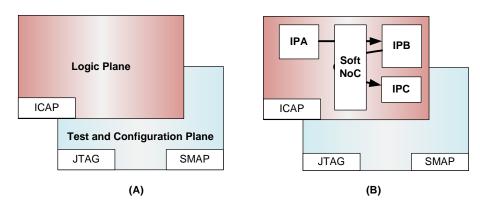

In recent years, FPGAs have emerged as target architectures to implement SoC designs [76,85]. For instance, the modern FPGAs can now be found in the fields of communications [114], medicine [3,27], radio astronomy [24], particle physics [35], and high performance computing [7,27,28], etc. The architecture of FPGA can be divided into two physical planes: the logic and configuration planes<sup>12</sup>. The *logic plane* executes the desired application(s), whereas the *configuration plane* (re)configures<sup>13</sup> the desired application on the logic plane.

The increasing FPGA popularity is due to the FPGA architectures, which are at the forefront of technology down-scaling. This trend can be observed from

<sup>&</sup>lt;sup>12</sup>The detailed discussion on FPGA architecture can be found in Section 2.1.1.

<sup>&</sup>lt;sup>13</sup>We define *(re)configuration* as the installation of new functionality in the FPGA by sending a bitstream to a reconfiguration region.

**Figure 1.6:** FPGA Virtex Family Logic Densities over the Years [155, 156, 158, 161, 162].

Figure 1.6A, which shows that modern FPGA features have scaled down from 220 nm to 40 nm during the last 15 years<sup>14</sup>. Consequently, the logic density of FPGA chip has increased by approximately 2000% over the same period, Figure 1.6B. The decreasing number of successful ASIC design starts also motivate the use of FPGAs for SoC implementations. As stated in [113], the number of successful ASIC design starts have significantly reduced from 4000 in 1997 to approximately 1000 in year 2008. The decline of ASIC designs is mainly because of: (i) longer time to market that has become one of the key element in deciding the success of SoC designs [69], (ii) high non-recurring-engineering (NRE) cost [22], (iii) and increased mask plus wafer costs [22]. In short, the modern FPGAs use the most advanced semiconductor processes and have become popular for SoC designs.

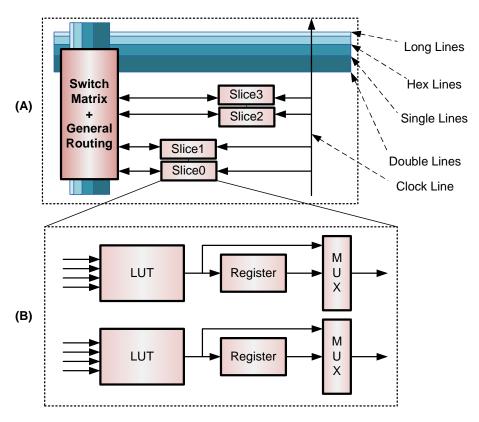

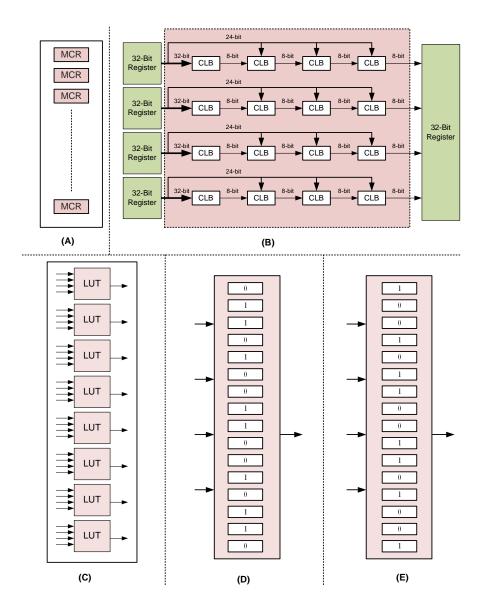

It is also important to note that the architectures of modern FPGAs are no longer a mere combination of configurable interconnection network and reconfigurable logic blocks (CLBs). The modern FPGA architectures also contain a number of hardwired blocks [162]. Figure 1.7 illustrates the architectural evolution for one of the Xilinx Virtex families. Over the years, in addition to increasing the reconfigurable logic density, the Virtex families [158, 161, 162] have been embellished with an increasing number and size of ASIC-like hard

<sup>&</sup>lt;sup>14</sup>The new Virtex-7, which is not part of Figure 1.6, is even of smaller dimension of 28 nm [163].

**Figure 1.7:** FPGA Virtex Family Architectural Evolution over the Years [155, 156, 158, 161, 162].

IP blocks. These include on-chip block RAMs, DSP slices, digital clock managers, programmable IO, programmable processors, Ethernet MAC, system monitor, transceivers, and PCI Interfaces. In existing FPGA architectures, application IPs can be *hard* or *soft*. However, the inter-IP communication architecture (e.g., NoC), which transports control and functional data among the IPs, is *soft only*. This means, in existing FPGA architectures, the bus, switch, or NoC is configurable and mapped on the reconfigurable resources of FPGA, i.e., CLBs, switch-matrices, and interconnection wires.

For the convenience of the reader, an abstract view of FPGA architecture is shown in Figure 1.8A. An FPGA is comprised of reconfigurable interconnect and logic blocks (CLBs), and programmable hard IP blocks. The Figure 1.8B

Figure 1.8: (A) Abstract View of FPGA Architecture, and (B) Application on FPGA.

shows an application (of Figure 1.1) that is mapped on FPGA architecture. In Figure 1.8B, application IPs are mapped on soft and hard blocks of the FPGA, and a soft network on chip (consisting of network interfaces and routers)<sup>15</sup> is used for inter-IP communication.

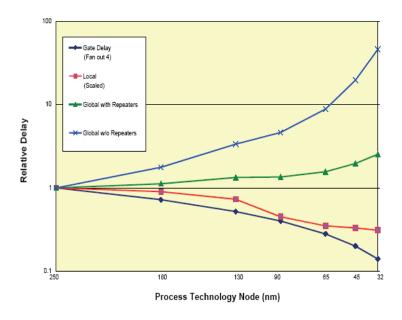

Existing ASIC and FPGA architectures belong to the deep sub-micron (DSM) regime, where the delays due to long wires have become prominent. With each developing process technology, the gap between the interconnection delay and the gate delay is increasing [67]. Figure 1.9 shows this trend, according to which the gap between the interconnection delay and the gate delay is expected to increase from 2:1 for 180 nm to 9:1 for 65 nm technology. This indicates that the *communication is becoming the key performance bottleneck* in the deep-sub-micron regime.

<sup>&</sup>lt;sup>15</sup>The detailed discussion on NoC architecture can be found in Section 2.2.1.

Figure 1.9: Interconnect Delay over Different Process Technologies [67].

# 1.1.3 Summary

Recapitulating the preceding discussions, we see that the technology down-scaling has enabled system designers to converge multiple applications in a single chip. Therefore, a number of application and architecture trends have emerged to implement SoCs.

From the application point of view, SoC can have an *increasing number of complex applications*. A user can *dynamically start / stop applications*, thus forming multiple use-cases. A single SoC can be used for multiple purposes, which means *applications can impose diverse Quality-of-Service constraints*. Meanwhile, time to market has become important due to shorter product life cycles.

From the architecture point of view, SoC applications require computation and storage resources in the form of IPs. The IPs in turn require communication resources for inter-IP communication to transport control and functional data. Importantly, the technology down-scaling and platform based designs have enabled the integration of *many IPs*. These IPs, which reach tens or even hundreds in number, can have *diverse clock frequencies*. Meanwhile, FPGAs are now popular (as target architecture) to implement SoC designs. The delays

in the interconnection wires of ASIC and FPGA architectures have become prominent, due to the deep sub-micron regime. This increases the *importance* of communication in comparison with the computation.

# 1.2 Problems

The above-mentioned trends give rise to a number of problems that need to be addressed. The problems are explained below, and can be classified from application and (FPGA) architecture points of view.

# 1.2.1 Application Point of View

The first problem is due to many applications in SoC. Due to the increasing number of applications, all the applications might not fit in a single FPGA simultaneously. This means at a particular time instance, not all applications are executing on FPGA architecture. To execute the applications that do not reside on FPGA, dynamic partial reconfiguration 16 is performed. However, the dynamically configured applications might interfere with the execution of applications that already execute on the FPGA [60, 125]. The interference can arise due to the rerouting of signal paths (i.e., the wires that connect different CLBs at inter-IP level) of existing applications, when a new application is dynamically reconfigured [125]. Moreover, the interference can be in the form of resource conflicts between the newly reconfigured application and already executing applications. For instance, the new application can induce resource conflicts in the communication architecture, or by sharing the same set of CLBs that are in use by the executing applications. In short, we can say that the presence of many applications can lead to dynamic reconfiguration of applications, which can introduce the problem of inter-application interference.

Due to the increasing complexity of applications, a single application might not even fit on a FPGA, which means the resources required by the application exceed the available FPGA resources. In this situation, a complex application is divided into multiple sub-applications [144]. For a single execution of the application, one by one, all of its sub-applications are swapped in FPGA. A sub-application is swapped out when it completes a (partial) computation. Afterwards, the next sub-application is swapped in. This implements

<sup>&</sup>lt;sup>16</sup>Dynamic partial reconfiguration allows the reconfiguration of selected area of FPGA without shutting down the applications that run on rest of FPGA.

1.2. PROBLEMS 13

dynamic partial reconfiguration at the intra-application level. However, without an adequate partial dynamic reconfiguration process the state information of a sub-application, which is swapped out of FPGA, might be lost [107]. Hence the presence of a complex application that does not fit on FPGA can trigger dynamic reconfiguration at sub-application level, which can introduce the problem of *intra-application state loss*. Dynamic inter / intra application reconfiguration lead to interference, which is a problem because QoS may not be met, verification is harder since you need all applications and all interleaving / usecases to test. Hence we wish no interference between applications.

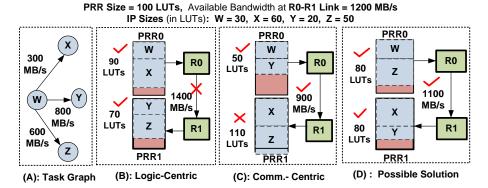

Applications can have different area and Quality-of-Service constraints. Some applications might occupy large area, whereas some applications might occupy small area in an FPGA. Moreover, due to the diverse Quality-of-Service constraints, the *functional interconnect* resources (e.g., communication links, buffers, etc.) that are shared between multiple applications are utilized differently by the SoC applications. In other words, the applications with high throughput have high resource requirements as compared to applications with low throughput. The diverse natures of applications, therefore, can produce high fragmentation of resources, which makes it difficult to meet area and Quality-of-Service constraints. The problem is aggravated with each additional application. A new application introduces additional requirements in terms of area and throughput, which in turn can increase the probability of resource conflict at an application level. This again makes it *hard to ensure area and Quality-of-Service* requirements for SoCs that have diverse as well as many applications.

As the number and complexity of applications increase in SoC, more time and efforts are required to solve the issues that can come while reconfiguring and / or executing applications on FPGA. This means the complexity and number of applications translate into *long design time*, which directly impacts the time to market trend of SoC implementation.

### 1.2.2 Architecture Point of View

Each IP that is integrated in a SoC operates synchronously, i.e., an IP has its own independent clock. However, an IP can have a different clock frequency than the functional interconnect. This introduces multiple clock domains, due to which the timing closure problem can arise during inter-IP communication. Importantly, the growing diversity of IPs introduces an increasing number of clock domains, making it *improbable to achieve a single clock domain* in a SoC.

The problem of IP integration can get aggravated due to the growing number of IPs, because the number of inter-IP communication connections increases. The communication architecture is therefore required to serve more number of communication connections. This in turn can raise a number of issues, e.g., (a) redesign of the communication architecture to accommodate an increasing number of connections, (b) contention of data that belong to different connections, and (c) congestion of data that flows through the communication architecture. In short, we can conclude that more number of IPs can introduce the problem of *more communication connections*.

Generally, the timing closure of an IP in isolation is not problematic, because its size is limited by the size of a single clock domain, and its lay-out is confined in space. However, the communication architecture (e.g., NoC) can introduce unpredictable delays during inter-IP communication [41]. This is due to the *soft* nature of the communication architecture, which means the reconfigurable elements (i.e., CLBs, switch-matrices, and interconnection wires) are used to construct the communication architecture. Since the global communication wires are long and span the chip, and should operate at high speed, it is difficult to achieve timing closure, i.e., to synthesise, and place and route them without timing violations.

The functional interconnect serves as the backbone for the SoC, because it provides transportation of data for all applications. The dynamic reconfiguration of an application involves the reconfiguration of its IPs and updating i.e., reconfiguration<sup>17</sup> and / or reprogramming<sup>18</sup> the functional interconnect [125, 144]. Ideally, updating the functional interconnect should not affect the executing applications. However, if it becomes inevitable to stop / pause the execution of already running application during the reconfiguration of new application, then the functional interconnect must be updated as fast as possible [144]. It is important to note that reconfiguration is a slow process as compared to reprogramming. When the reconfigured part of functional interconnect occupies significant resources of FPGA. It will induce high reconfiguration overhead in terms of bitstream size and latency. A high reconfiguration overhead might, therefore, lead to highly delayed response to execute the user application. In short, the soft nature of functional interconnect leads to the problem of *high reconfiguration overhead*.

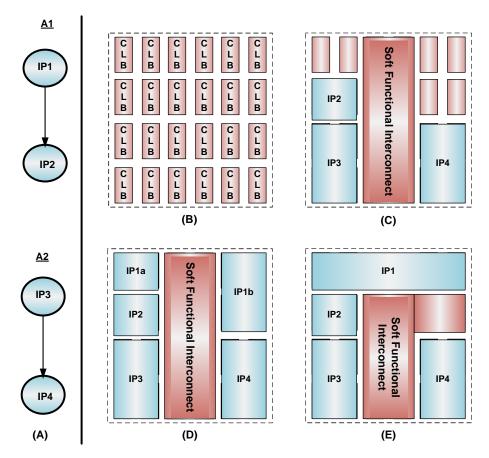

Additionally, a soft communication architecture, which is placed in different areas of FPGA, can also pose restrictions on the placement of application IPs.

<sup>&</sup>lt;sup>17</sup>Configuring an IP means loading its bitstream in the configuration plane.

<sup>&</sup>lt;sup>18</sup>Programming an IP means changing the state of its registers.

1.2. PROBLEMS 15

The reason is that due to the presence of a soft communication architecture (in the same logic plane), an IP of a particular dimension might not be placeable. In this situation the IP has to be partitioned into multiple smaller IPs, so that they can be placed in the FPGA, as illustrated in Section 3.2. To solve the problem of restricted IP placement, which is worse with the soft functional interconnect, communication and computation should be separated from each other. In short, the soft nature of functional interconnect causes the problem of restricted IP placement.

The existing FPGA architectures have small feature size, and are therefore, prone to faults [1,2,37,142]. The chances of FPGA to become faulty increases, if it is used for mission-critical systems or exposed to harsh external conditions (e.g., cosmic radiations). The radiations can flip the bits in the memory cells of the configuration plane, thus resulting in wrong values for the memory cells. A value in the memory cells of configuration plane can be propagated to the logic plane [86], i.e., in CLBs, IPs, and interconnection network, resulting in an unreliable logic plane. In other words, due to small feature sizes and harsh external conditions, *faults can arise* in FPGAs.

#### **1.2.3 Summary**

Recapitulating the above discussion, we see that the application and architecture trends have raised a number of problems.

From the application point of view, an increasing number of applications might trigger dynamic reconfiguration at inter-application level. The dynamic reconfiguration process might interfere with already executing applications. Meanwhile, due to the increasing complexity of applications, an application can be dynamically reconfigured at sub-application level. In this case, the problem of state loss at intra-application level can arise during dynamic reconfiguration. At the same time, due to the diversity of applications, it becomes hard to fulfill area and Quality-of-Service constraints. Finally, an increasing number and diversity of applications is translated into long design times.

From the architecture point of view, an *increasing number and diversity of IPs* introduce difficulties in the integration of IPs in a SoC. Particularly, due to the diversity of IPs multiple clock domains exist in a SoC, which create the problem in achieving the global synchronisation. The *technology down-scaling* has resulted in small feature sizes for FPGA architectures, which are more prone to faults. Moreover, *the soft nature of the functional interconnect* can give rise to multiple problems that include: a) hard to achieve timing closure for inter-

IP communication, b) high reconfiguration overhead, and c) restrictions on the placement of IPs in FPGA.

#### 1.3 Requirements

Base on problems in the previous Section 1.2, we impose nine requirements that should be fulfilled for a successful SoC design.

- Globally Asynchronous Locally Synchronous (GALS) techniques are required to solve the problem of single clock domain. In a GALS environment, the synchronous IPs communicate with each other in an asynchronous fashion. This can be exercised by using asynchronous wrappers or bisynchronous FIFOs to connect two distinct clock domains [82].

- 2. *Scalable IP integration* is required to solve the problem *hard to achieve IP integration*. This can be achieved by using a communication architecture, supported by a design flow, with an inherent modular and scalable <sup>19</sup> nature.

- 3. Communication and computation should be separate from each other to alleviate restrictions on IP placement. This can be achieved at the physical level, i.e., communication architecture and computational IPs both do not coexist in the same logic plane.

- 4. Fast updates for the communication architecture should be performed to reduce the reconfiguration time of a dynamically started new application.

- 5. Composable dynamic reconfiguration is required to overcome the problem of interference during inter-application dynamic reconfiguration. Composable dynamic reconfiguration ensures that no interference is experienced during the steady state or dynamic run time reconfiguration. This can be achieved when the principles [80] of error containment, non-interfering interactions, and stability of prior services are fulfilled, while applications are executed or dynamically started and stopped in FPGA. Here, avoiding error containment means that errors in one application are not propagated to other application(s). Stability of prior services

<sup>&</sup>lt;sup>19</sup>Scalability is the ability of something (hardware of software) to adapt to increased demands [116].

means that a dynamically inserted application has no impact and conflict with the logic and communication plane resources of the existing application(s). *Non-interfering interactions* mean that application during its execution time does not affect the other applications as long as their allocation remains unchanged.

- 6. *Persistent-state dynamic reconfiguration* is required to overcome the problem of state loss during intra-application dynamic reconfiguration. *Persistent-state dynamic reconfiguration* makes sure that data is not lost during intra-application dynamic reconfiguration [94, 107]. This means the state information (spread at multiple places in the system) of the subapplication must be saved, when it is swapped out. It is essential to avoid unpredictable behavior of the system.

- 7. *Predictability* is required to offer good application QoS, and avoid unpredictable application behavior and architecture. At the application level, predictability is required to fulfil QoS, i.e., throughput and latency constraints [48]. At the architectural level, predictability is required to resolve the timing closure issues of the soft communication architecture.

- 8. *Reliable architecture* for the target FPGA to ensure that the applications always execute on a fault-free FPGA.

- 9. *Automation*, which refers to having parts of the design process done by tools, is required to overcome the problem of high design times. Automating the process of binding<sup>20</sup> of application to FPGA can directly impact the time to market by reducing the design and verification efforts.

### 1.4 Techniques

To fulfill the above requirements, we propose a number of techniques that are shown in Table 1.1. We position the trends, problems, requirements, and techniques, where the order in which techniques are explained defines the order of Table 1.1 rows.

<sup>&</sup>lt;sup>20</sup>An application is said to be: (i) *placed* when its IPs are placed on FPGA logic plane, (ii) *mapped* when its IP ports are connected to the functional interconnect, and (iii) *allocated* when its IPs can communicate (after programming the NoC) with each other as per QoS constraints. We term the whole process of placing, mapping, and allocation as *binding*.

Table 1.1: Overview Of Trends, Problems, Requirements, and Techniques

| Trends         | Problems      | Requirements      | Techniques        |

|----------------|---------------|-------------------|-------------------|

| Diverse        | Many          | GALS              | Hardwired         |

| IPs            | Clock         | Environment       | Network on Chip   |

|                | Domains       | (1)               |                   |

| Many           | Many          | Scalable IP       | Hardwired         |

| IPs            | Connections   | Integration (2)   | Network on Chip   |

| Soft Inter-IP  | Restricted    | Separate          | Hardwired         |

| Interconnect   | IP Placement  | Communication     | Network on Chip   |

| (Layout Trend) |               | & Computation (3) |                   |

| Soft Inter-IP  | High (Re)Con- | Fast Updates for  | Hardwired         |

| Interconnect   | figuration    | Communication     | Network on Chip   |

| (Update Trend) | Overhead      | Architecture (4)  |                   |

| Soft Inter-IP  | Hard to Meet  | Predictability    | Hardwired         |

| Interconnect   | Timing        | (7)               | Network on Chip   |

| (DSM Trend)    | Closure       |                   |                   |

| Short          | High          | Automation        | Design Flow to    |

| Time to        | Design        | (9)               | Bind Applications |

| Market         | Times         |                   | on FPGA           |

| Diverse        | Hard to Meet  | Predictability    | Design Flow to    |

| Applications   | Area &        | (7)               | Bind Applications |

|                | QoS           |                   | on FPGA           |

|                | Constraints   |                   |                   |

| Multiple       | Inter-        | Composable        | 3-Tier Model      |

| Applications   | Application   | Dynamic           | for Composable    |

|                | Interference  | Reconfiguration   | Dynamic           |

|                |               | (5)               | Reconfiguration   |

| (Too) Large    | Intra-        | Persistent-       | 3-Tier Model      |

| Applications   | Application   | state             | for Persistent-   |

|                | State         | Dynamic           | State Dynamic     |

|                | Loss          | Reconfiguration   | Reconfiguration   |

|                |               | (6)               |                   |

| Small FPGA     | Increasing    | Reliable          | Online            |

| Feature size   | Faults        | Architecture (8)  | Testing           |

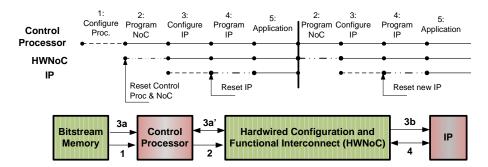

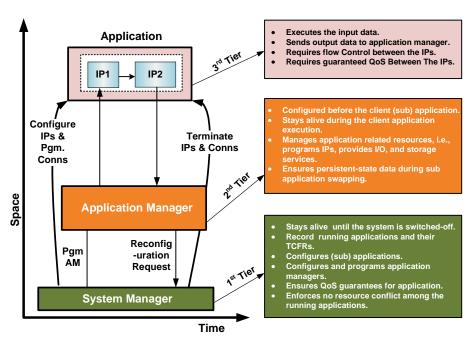

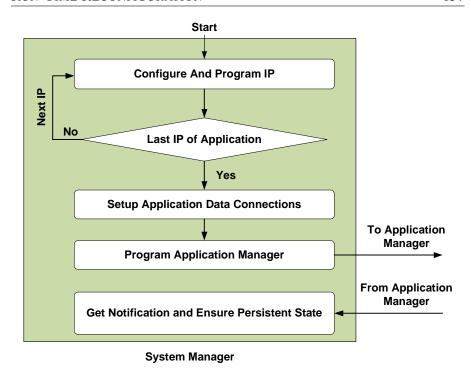

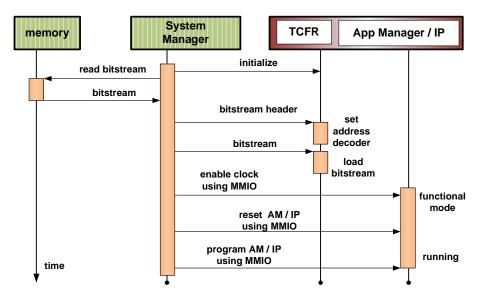

#### 1.4.1 Hardwired Network on Chip