#### PHILIP MATHEW

## PULSED AGEING OF OIL-PAPER: TEST MODULATORS AND AGEING TRENDS

#### THESIS REPORT

# PULSED AGEING OF OIL-PAPER: TEST MODULATORS AND AGEING TRENDS

by

## Philip Mathew

in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering

at the Delft University of Technology Delft, The Netherlands

to be defended publicly on Friday August 27 2021 at 9:00 AM Student number: 4988035

Project duration: November 2020 to August 2021

### Thesis supervisors:

Dr. ir. Mohamad Ghaffarian Niasar Assistant Professor, DCE&S Research Group Delft University of Technology, The Netherlands

Prof. ir. Peter Vaessen

Professor, DCE&S Research Group

Delft University of Technology, The Netherlands

#### Thesis committee:

Dr. ir. Mohamad Ghaffarian Niasar Assistant Professor, DCE&S Research Group Delft University of Technology, The Netherlands

Prof. ir. Peter Vaessen

Professor, DCE&S Research Group

Delft University of Technology, The Netherlands

Dr. ir. Marjan Popov Associate Professor, IEPG Research Group Delft University of Technology, The Netherlands

Pulsed Ageing of Oil-Paper: Test Modulators and Ageing Trends

Philip Mathew © 2021

Thesis is confidential and cannot be made public until December 31 2023.

An electronic version of this dissertation is available at http://repository.tudelft.nl/.

The ambitious transition towards a renewable future is being made possible by power electronic systems that facilitate effective control and efficient conversion of energy. One such system is the solid-state transformer (SST) which aims to replace conventional transformers by offering larger energy densities and flexible power flow. However these benefits come at the cost of severe mixed-frequency stresses experienced by the medium frequency transformer (MFT) of the SST. These stresses are characterised by fast-rising pulsed waveforms of several tens of kilovolts repeating at frequencies of up to hundred kilohertz. In contrast to pure sinusoids, the behaviour of dielectrics under mixed-frequency stresses is to a large extent unknown. This research gap forms the core motivation behind this thesis project.

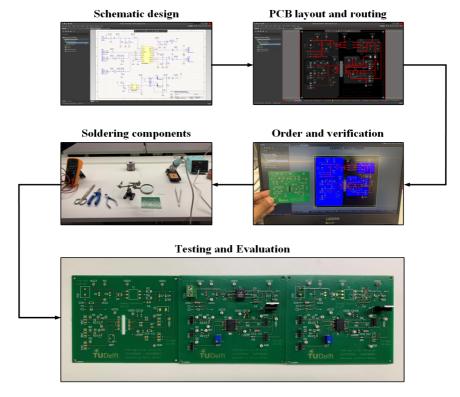

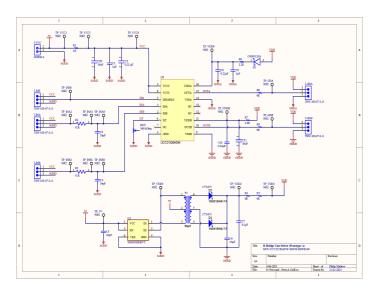

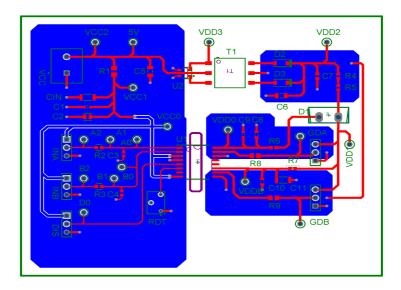

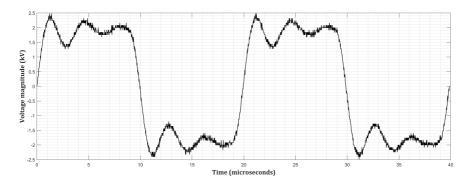

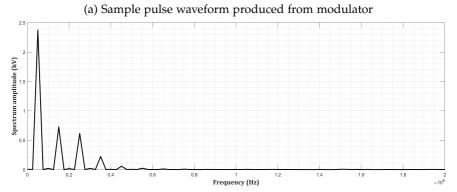

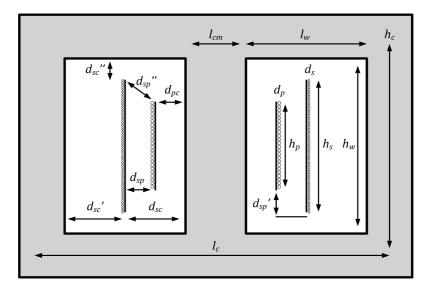

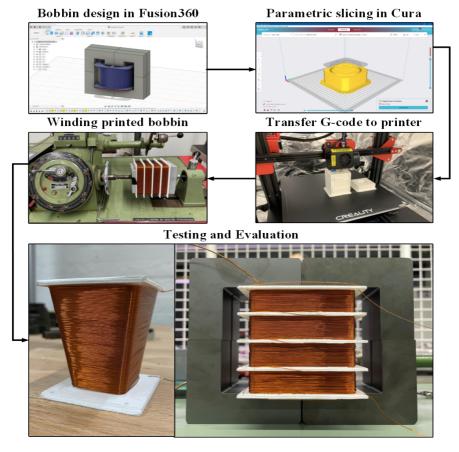

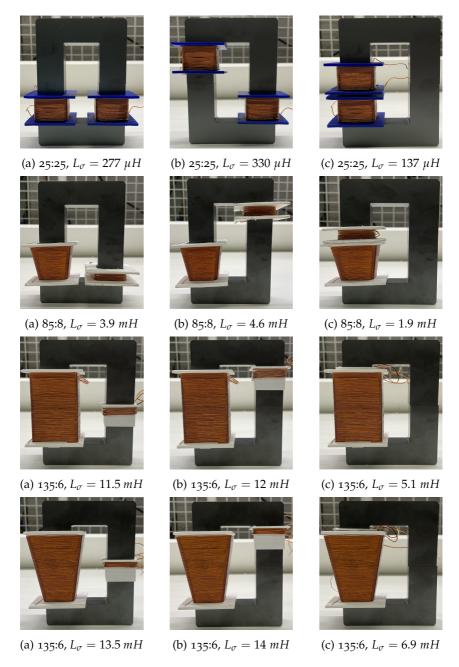

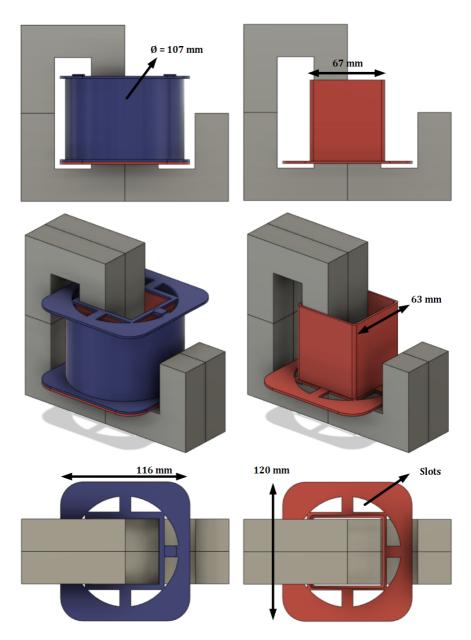

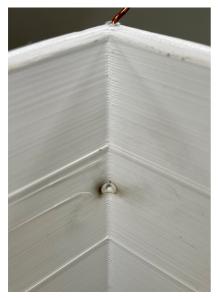

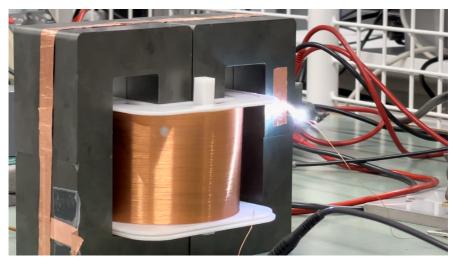

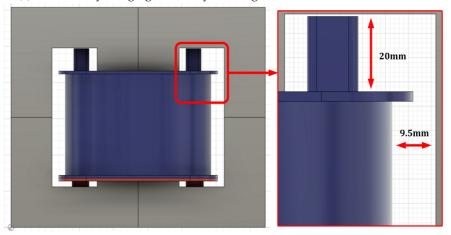

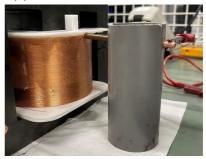

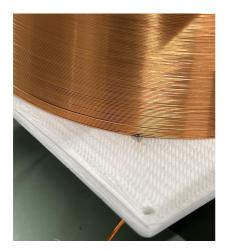

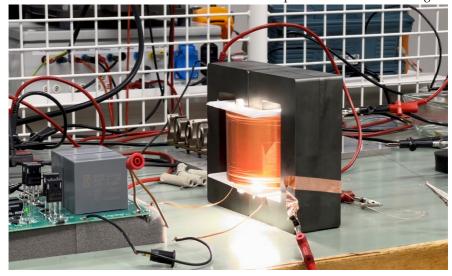

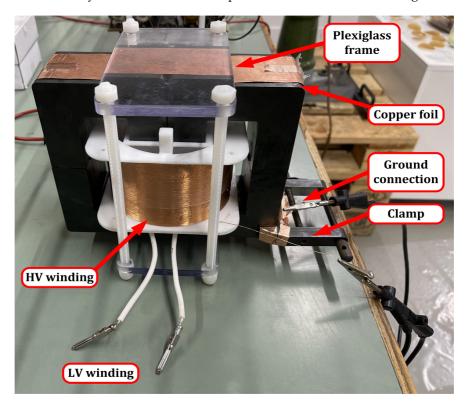

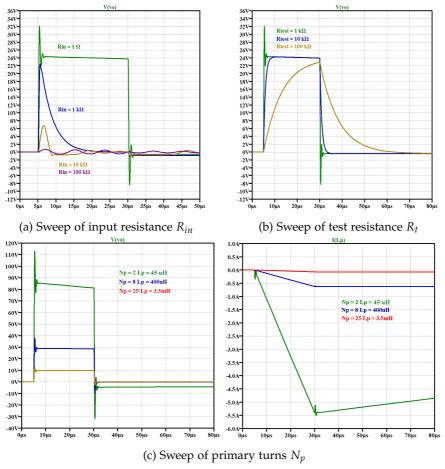

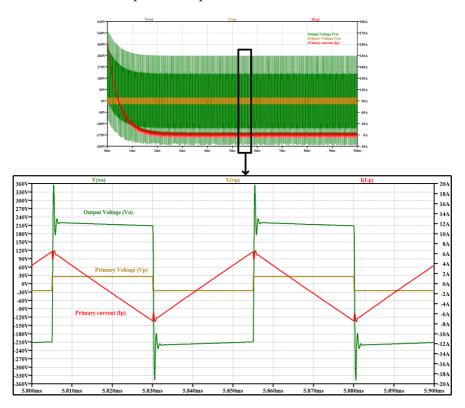

To analyse these exciting yet extreme phenomenon, the first objective was to build a pulse modulator for testing cellulosic dielectrics under voltages up to 10 kV with rise-times  $\approx$  2 µs at frequencies between 10 to 50 kHz. The topology consists of a rectified DC supply feeding a SiC H-bridge pulse generator connected to a 4:200 pulse transformer and other variable test elements. The work began with selecting the switch and gate driver, simulations in LTspice and TINA-TI, and the fabrication of the PCB pulse generator prototype using Altium Designer. Next, a novel third-order PQR equation was derived for a PT with capacitive load involving the parasitic leakage flux  $L_{\sigma}$  and distributed capacitance  $C_d$ . The influence of bobbin geometry on parasitics was studied with 20 different 3D printed iterations designed in Fusion 360. A failure mode analysis was conducted to identify weak points in a transformer, and the solutions detailed in this report.

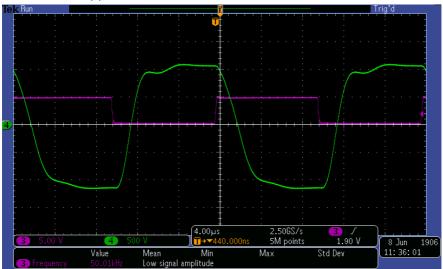

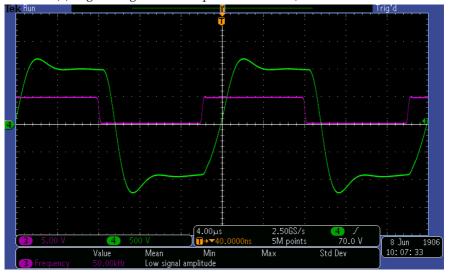

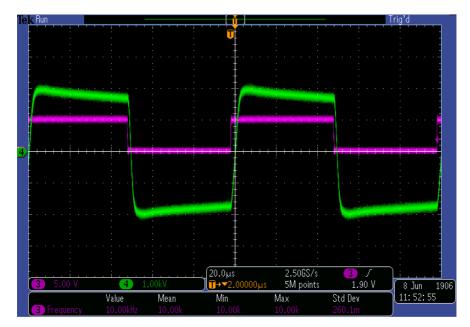

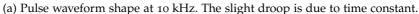

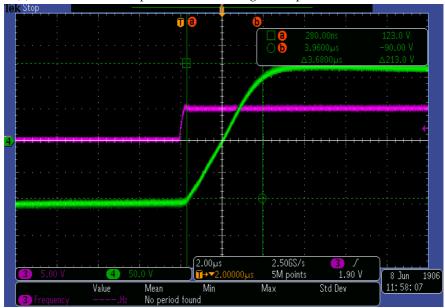

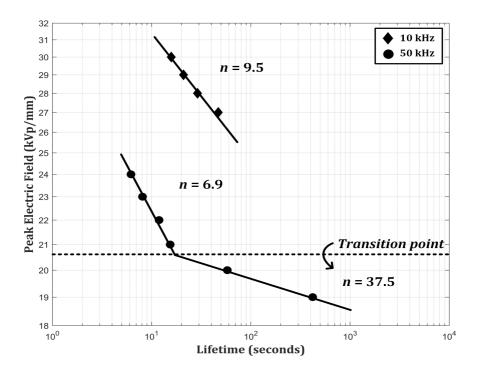

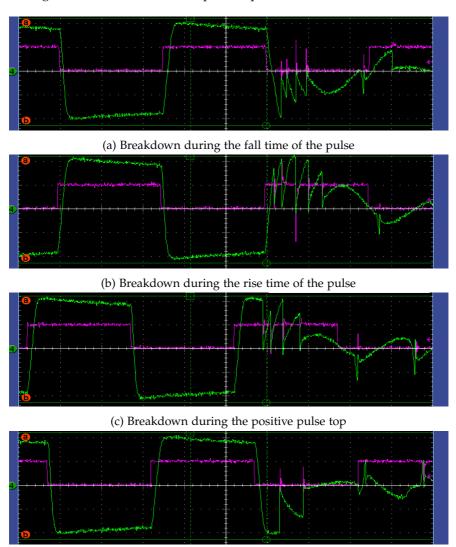

The final objective was to apply the produced waveforms of  $T_r \approx 1.8 \mu s$  across single-layer OIP samples at 10 kHz and 50 kHz. The sample strength was determined through ramp tests with 1 kV/s slope. The lifetime curves were obtained by performing ageing tests at 10 field strengths each for 21-41 samples, and fitting the median failure time into a inverse power law model. The results show a clear reduction in lifetime at higher frequencies proving the unsuitability of OIP in its current form as an insulation for MFTs. A transition point was observed indicating a shift in ageing mechanism at lower fields. The report ends with a discussion on future scopes of research.

#### ACKNOWLEDGEMENTS

In a countless number of ways, the past two years have changed me more than I could have ever prepared for. Studying at the TU Delft has been wholesome in every sense, academic and otherwise, and I am grateful for the opportunity to have carried out my masters in this beautiful country.

I owe the culmination of this thesis to several individuals and elements.

Firstly, to *the scientific truth*, for humbling me to the core (pun intended) with its brutal honesty. I have felt it crush my hopes with every fried MOSFET, failed experiment, and seemingly unsolvable problem. But every dead-end has brought another chance to build in me the patience to repair, the will to rethink, the wisdom to reason, and the warmth of rationale. Research has proven to be like incomplete alliteration, a perfect imperfection.

To *Mohamad Niasar*, for educating me on the importance of failures and the lessons to be learnt from them. Your passion for the subject has been the greatest inspiration for me to turn every stone and push every limit. The late evenings we spent working at the lab were genuinely fun, two nerds delving into physics and mathematics to understand our observations. I am grateful to have had you as a mentor, teacher, and friend. I aspire to become for students what you were for me, supporting them just enough to promote original and independent ideas. I look forward to joining forces on more scientific adventures, or at least start a repair shop for PCBs.

To *Peter Vaessen*, for introducing to me the field of high-voltage engineering, and enthusiastically teaching it to me as a beautiful amalgamation of physics, chemistry, mechanics, and a good amount of common-sense.

To *Wim*, for his energy to strive for perfection in the tiniest of details. And to *Luis*, *Geert Jan*, *and Radek*, for helping me make the most out of our HV lab.

To *Dhanashree, Tianming, Weichuan, and Christian,* for being approachable to have intellectual discussions about our projects, which have played a significant role in exciting me about pursuing a PhD in the future.

To *Mama and Dada*, for teaching my sister and I the value of education, culture, and genuine hardwork. I am so proud to be your son, that every sleepless night spent has partly been to make you proud to be my parent.

To *Nonie*, for being my sister. Although you spent your first four (tragic) years without me, I pray that I never have to spend a single day without you.

To *Keeka*, for being my raccoon through chonk and thin, for the paws of appwoval that supported me the past two years, and for being merciful towards apple peels. To *CoeurdeLion and Zangetsu*, for being my fellow guardians, siegers, and racers. To *Sai*, for being a constant friend in need, and the best SSD board-mate indeed. To *Meenu*, for the food truck lunches and positive encouragement. To my *classmates*, for providing me the fondest of memories.

To *my teachers*, from high-school to bachelors to masters and more, for their sincerity in fostering the courage to follow my curiosities and ambitions.

To *strawberry yoghurt and muesli*, for keeping me healthy and happy, two aspects of life I tend to ignore. To my *iPhone*, for providing photos worth oggling at and to my *laptop*, for not giving up on me. Lastly to *cellophane tape* and *copper tape*, for fixing too many problems that I have lost count of.

The stochasticity of this universe has instilled in me time after time a fire to answer its endless questions, to teach others the answers to these questions, and to eagerly work together on searching for new puzzles to solve.

With joy in my soul, and a cat on my lap.

Philip Mathew Delft, 2021

## CONTENTS

| 1 | Intro | oductio | on                                                | 1  |  |  |  |  |

|---|-------|---------|---------------------------------------------------|----|--|--|--|--|

|   | 1.1   | Thesis  | Thesis context                                    |    |  |  |  |  |

|   | 1.2   | Resea   | rch questions                                     | 2  |  |  |  |  |

|   | 1.3   | Modu    | ılator topology                                   | 3  |  |  |  |  |

|   | 1.4   | Projec  | et overview                                       | 3  |  |  |  |  |

| 2 | Lite  | rature  | Survey                                            | 5  |  |  |  |  |

|   | 2.1   | Prope   | erties and applications of oil-impregnated paper  | 5  |  |  |  |  |

|   | 2.2   | Origin  | n and characterization of pulse waveforms         | 9  |  |  |  |  |

|   | 2.3   | Effect  | s of pulsed stresses on insulation materials      | 13 |  |  |  |  |

|   | 2.4   | Techn   | iques for replicating quasi-rectangular voltages  | 18 |  |  |  |  |

| 3 | Puls  | se Gene | erator                                            | 21 |  |  |  |  |

|   | 3.1   | SiC M   | IOSFET                                            | 21 |  |  |  |  |

|   |       | 3.1.1   | Theory and mechanisms                             | 21 |  |  |  |  |

|   |       | 3.1.2   | Switch selection: IMW120R140                      | 23 |  |  |  |  |

|   |       | 3.1.3   | Operational characteristics in LTspice            | 24 |  |  |  |  |

|   | 3.2   | Gate o  | driver                                            | 25 |  |  |  |  |

|   |       | 3.2.1   | Theory and mechanisms                             | 25 |  |  |  |  |

|   |       | 3.2.2   | Driver selection: UCC21521                        | 26 |  |  |  |  |

|   |       | 3.2.3   | Operational characteristics in TINA-TI            | 27 |  |  |  |  |

|   | 3.3   | Hardy   | ware prototypes                                   | 28 |  |  |  |  |

|   |       | 3.3.1   | Proto-H <sub>1</sub> : UCC-Driver PCB             | 29 |  |  |  |  |

|   |       | 3.3.2   | Power and parameter calculations                  | 32 |  |  |  |  |

|   |       | 3.3.3   | Proto-Hx: Complete H-bridge PCB                   | 35 |  |  |  |  |

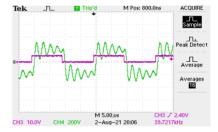

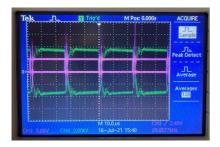

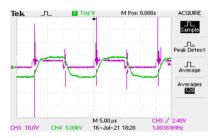

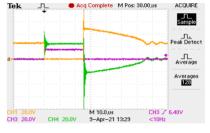

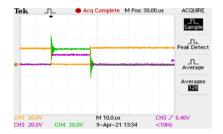

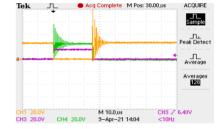

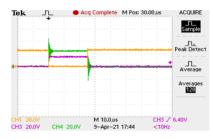

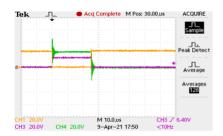

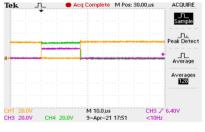

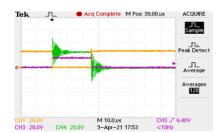

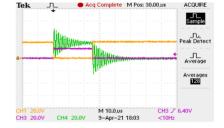

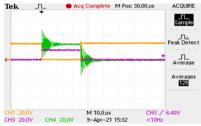

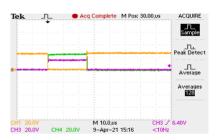

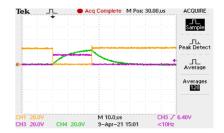

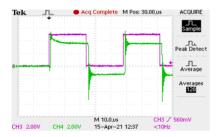

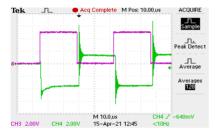

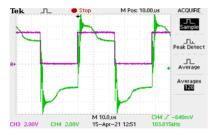

|   | 3.4   | Evalu   | ation tests                                       | 38 |  |  |  |  |

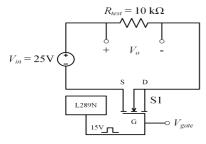

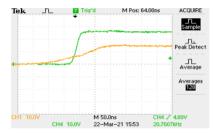

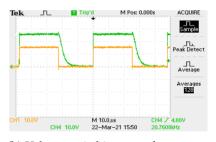

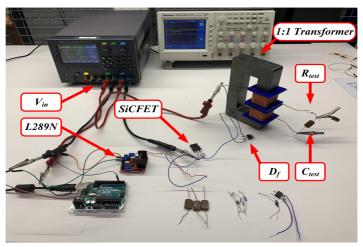

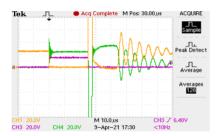

|   |       | 3.4.1   | T1: SiCFET with L289N driver                      | 38 |  |  |  |  |

|   |       | 3.4.2   | T2: SiCFET with Proto-H1                          | 39 |  |  |  |  |

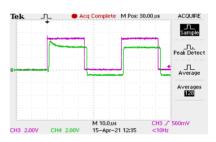

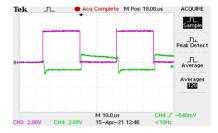

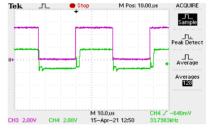

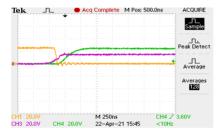

|   |       | 3.4.3   | T <sub>3</sub> : Low-voltage response of Proto-Hx | 40 |  |  |  |  |

| 4 | Puls | e Tran | sformer                                    | 41 |

|---|------|--------|--------------------------------------------|----|

|   | 4.1  | Theor  | retical background                         | 41 |

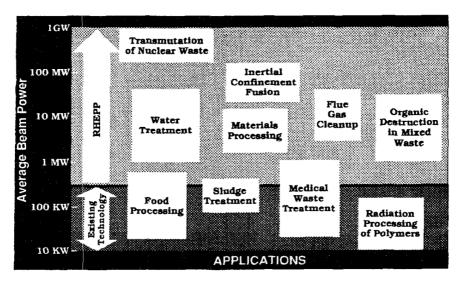

|   |      | 4.1.1  | Brief history of pulsed power applications | 41 |

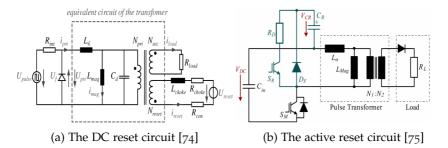

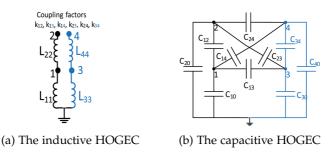

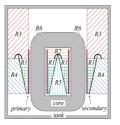

|   |      | 4.1.2  | Literature on pulse transformer design     | 44 |

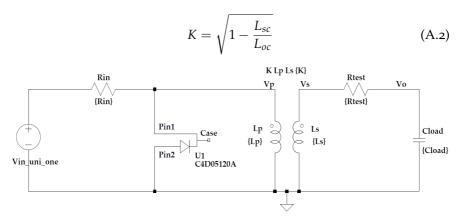

|   | 4.2  | Deriv  | ing an equivalent modulator model          | 47 |

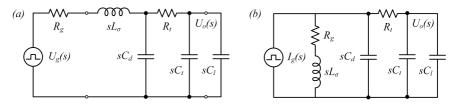

|   |      | 4.2.1  | For resistive (klystron) loads             | 49 |

|   |      | 4.2.2  | For capacitive (dielectric) loads          | 52 |

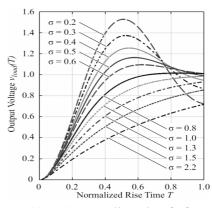

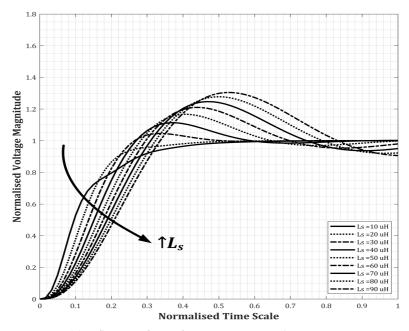

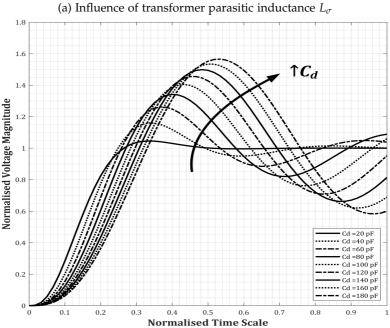

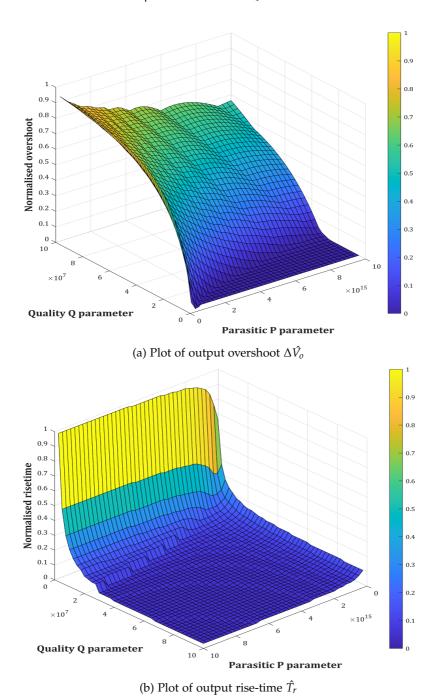

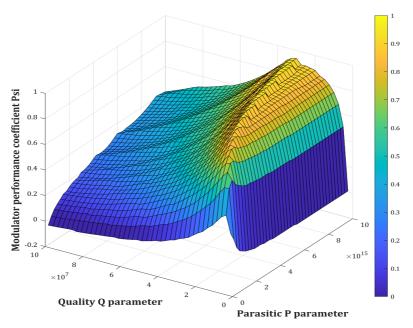

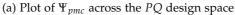

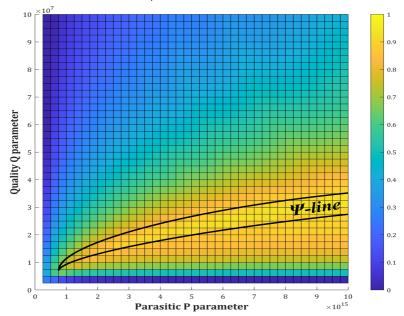

|   |      | 4.2.3  | Understanding the PQR equation             | 56 |

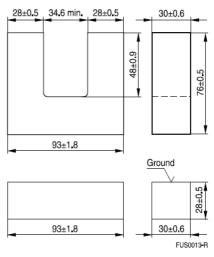

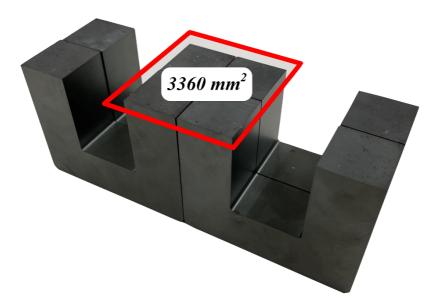

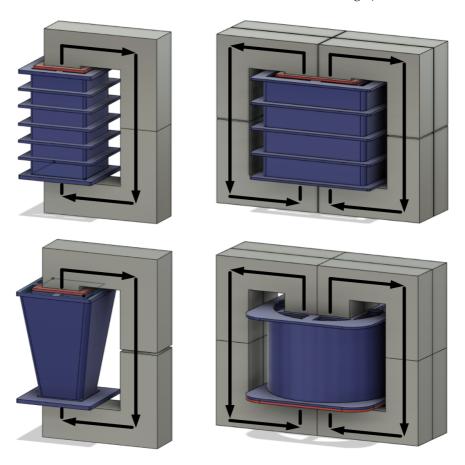

|   | 4.3  | Trans  | former design                              | 59 |

|   |      | 4.3.1  | Desired output specifications              | 60 |

|   |      | 4.3.2  | Parameters and tradeoffs                   | 61 |

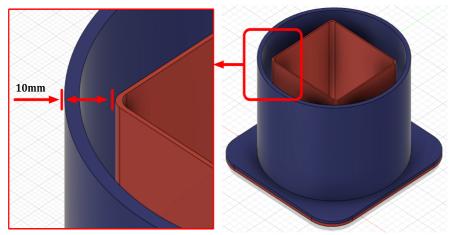

|   | 4.4  | Parasi | itic evaluation                            | 63 |

|   |      | 4.4.1  | Measuring leakage inductance               | 63 |

|   |      | 4.4.2  | Measuring distributed capacitance          | 63 |

|   |      | 4.4.3  | Bobbin iterations and comparisons          | 64 |

|   |      | 4.4.4  | Winding design summary                     | 68 |

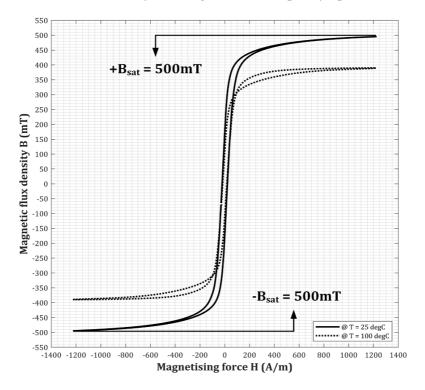

|   | 4.5  | Magn   | etic core                                  | 7º |

|   |      | 4.5.1  | Material hysteresis characteristics        | 7º |

|   |      | 4.5.2  | Saturation prevention criteria             | 72 |

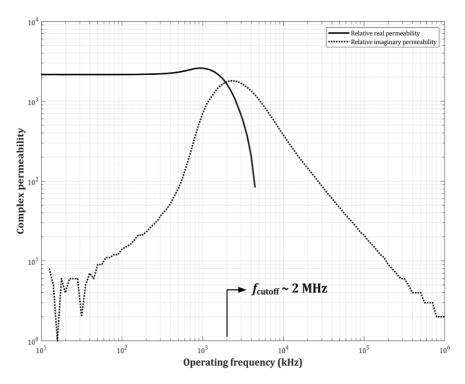

|   |      | 4.5.3  | Complex permeability curves                | 75 |

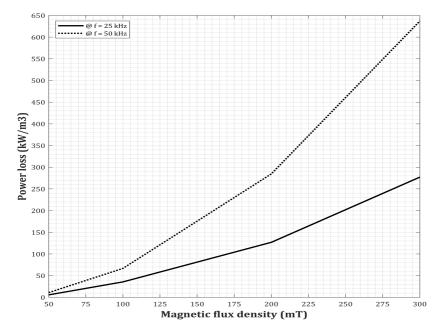

|   |      | 4.5.4  | Evaluation of core losses                  | 76 |

|   | 4.6  | Failur | re modes and solutions                     | 77 |

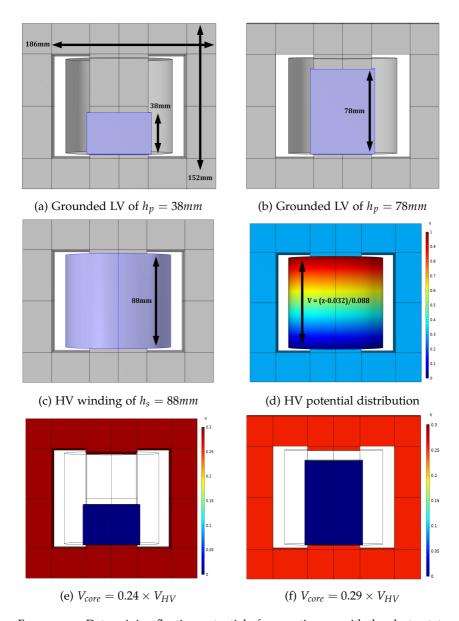

|   |      | 4.6.1  | Mode I: Core to LV discharges              | 77 |

|   |      | 4.6.2  | Mode II: HV to core discharges             | 8c |

|   |      | 4.6.3  | Mode III: HV to LV discharges              | 82 |

|   |      | 4.6.4  | Mode IV: Core to core discharges           | 85 |

|   |      | 4.6.5  | Mode V: Breakdown of FET/Driver            | 87 |

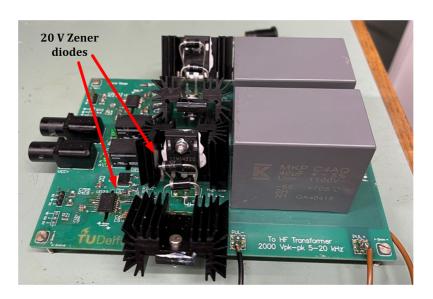

|   | 4.7  | Modu   | alator subcircuits                         | 92 |

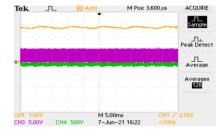

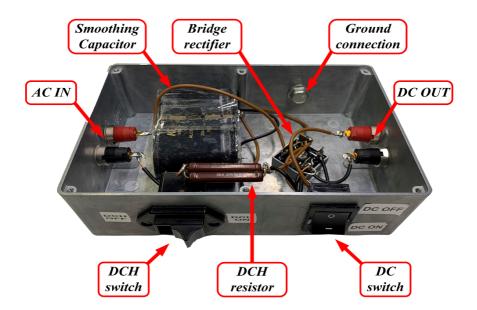

|   |      | 4.7.1  | Rectified DC power supply                  | 92 |

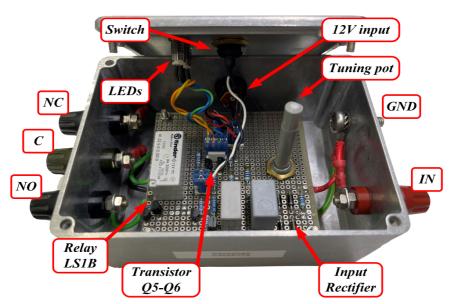

|   |      | 4.7.2  | Dielectric breakdown protection            | 95 |

|   |      | 4.7.3  | Variable test elements                     | 98 |

|   | 4.8  | Modu   | ılator summary                             | 02 |

| 5 | Age          | ing Ex   | periments                                       | 105   |

|---|--------------|----------|-------------------------------------------------|-------|

|   | 5.1          | Theor    | retical background                              | . 105 |

|   |              | 5.1.1    | Dielectric loss under sinusoidal stresses       | . 105 |

|   |              | 5.1.2    | Dielectric loss under pulsed stresses           | . 106 |

|   |              | 5.1.3    | Weibull distribution for breakdown strengths    | . 107 |

|   |              | 5.1.4    | Inverse power law model for lifetime estimation | . 107 |

|   | 5.2          | Test p   | protocol                                        | . 108 |

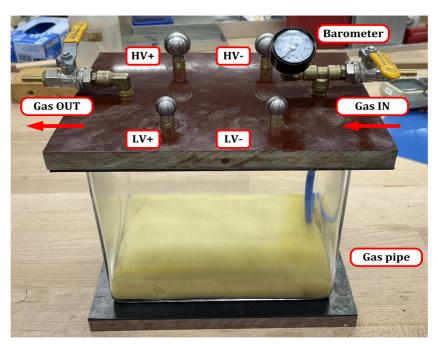

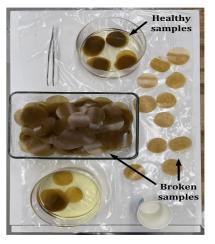

|   |              | 5.2.1    | Preparing oil-paper samples                     | . 108 |

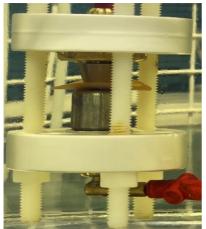

|   |              | 5.2.2    | Arranging test electrodes                       | . 109 |

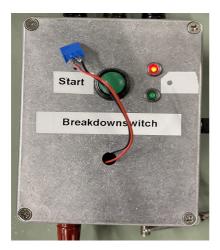

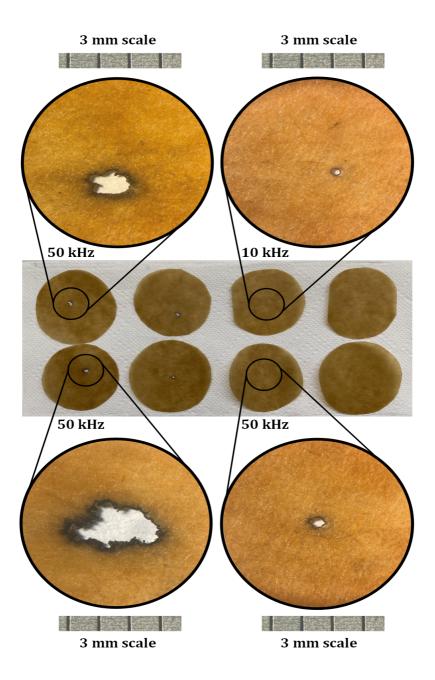

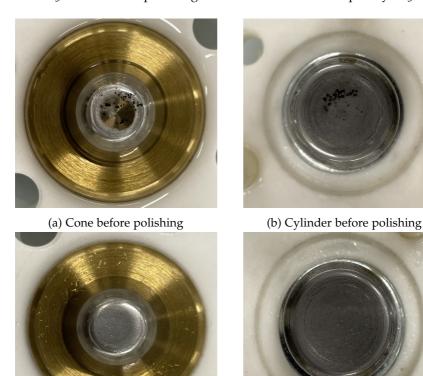

|   |              | 5.2.3    | Tuning breaker sensitivity                      | . 110 |

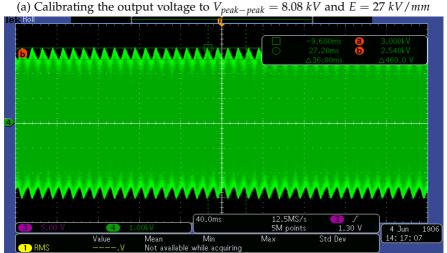

|   |              | 5.2.4    | Calibrating applied voltage                     | . 113 |

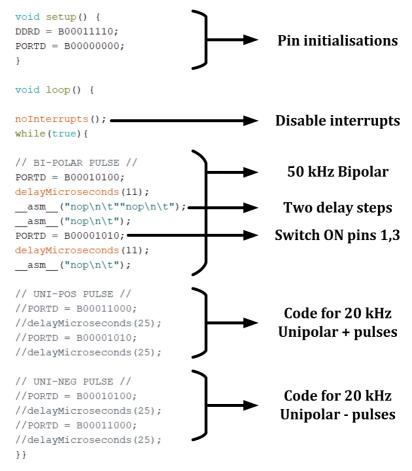

|   |              | 5.2.5    | Setting frequency in Arduino                    | . 114 |

|   | 5.3          | Diele    | ctric experiments                               | . 115 |

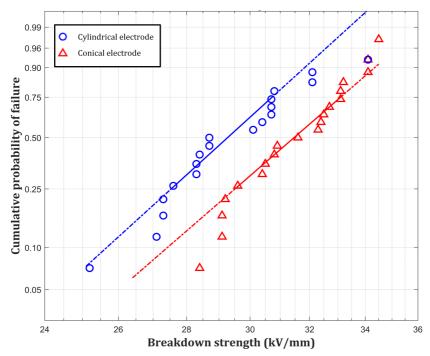

|   |              | 5.3.1    | Determining breakdown strength                  | . 115 |

|   |              | 5.3.2    | Estimating remaining lifetime                   | . 116 |

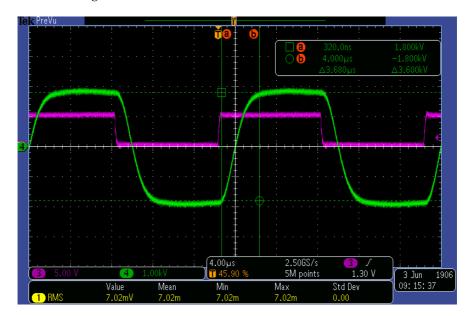

|   |              | 5.3.3    | Analysing breakdown instant                     | . 121 |

|   | 5.4          | Resul    | ts summary                                      | . 122 |

| 6 | Con          | clusion  | ıs                                              | 123   |

|   | 6.1          | Scient   | tific challenges and limitations                | . 123 |

|   | 6.2          | Resea    | rch answers and accomplishments                 | . 124 |

|   | 6.3          | Futur    | e research directions                           | . 125 |

|   | Bibl         | iograpl  | hy                                              | 127   |

| Α | Арр          | endix    |                                                 | 135   |

|   | α: P         | lanning  | g and practices for successful PCB design       | . 135 |

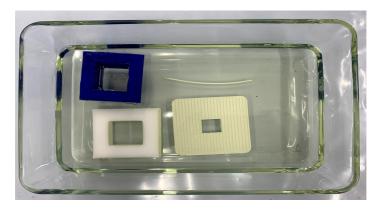

|   | β: T         | esting 1 | resilience of PLA against transformer oil       | . 137 |

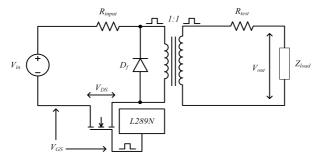

|   | γ: P         | rototyp  | oing an initial low-voltage modulator           | . 138 |

|   | δ: D         | eriving  | the $PQR$ modulator equation in Laplace domain  | . 149 |

|   | <i>ϵ</i> : C | omputi   | ing third-order time-domain solutions in MATLAB | . 150 |

## NOTATION

#### PHYSICAL CONSTANTS

| SYMBOL       | VALUE                          | UNIT | DESCRIPTION                  |

|--------------|--------------------------------|------|------------------------------|

| С            | $2.99792458\times 10^{8}$      | m/s  | Speed of light in Vacuum     |

| $\epsilon_0$ | $8.854 \times 10^{-12}$        | F/m  | Permittivity of Free Space   |

| $\mu_0$      | $4 \text{G} 10 \times 10^{-7}$ | H/m  | Permeability of Free Space   |

| $q_e$        | $1.602\times10^{19}$           | C    | Elementary electrical charge |

#### FREQUENTLY USED SYMBOLS

| $V_{peak}$   | Pulse peak amplitude in kilovolts         |

|--------------|-------------------------------------------|

| $V_{pk-pk}$  | Pulse peak-to-peak amplitude in kilovolts |

| $\Delta V_o$ | Pulse overshoot in $\% V_p$               |

| $T_r$        | Pulse rise time in nanoseconds            |

| $T_f$        | Pulse fall time in nanoseconds            |

| $T_p$        | Pulse top width in nanoseconds            |

| $L_{\sigma}$ | Leakage inductance in milli/micro-henries |

| $C_d$        | Distributed capacitance                   |

#### FREQUENTLY USED ABBREVIATIONS

| SST    | Solid-state transformer                 |  |  |  |

|--------|-----------------------------------------|--|--|--|

| MFT    | Medium frequency transformer            |  |  |  |

| PDs    | Partial discharges                      |  |  |  |

| PDIV   | Partial discharge inception voltage     |  |  |  |

| OIP    | Oil-impregnated paper                   |  |  |  |

| PT     | Pulse transformer                       |  |  |  |

| SiCFET | Silicon-carbide Field-effect transistor |  |  |  |

1

#### INTRODUCTION

The consequences of a failure in an electric power system are tremendous and high reliability and a long voltage life of its components are absolute musts.

> F. H. Kreuger Industrial High DC Voltage (1995)

The first chapter of this thesis begins by setting the context of the project, describing its research objectives and scientific challenges, illustrating the topology of the designed pulse modulator system, and providing the project timeline.

#### 1.1 THESIS CONTEXT

While it is only human to take our own inventions for granted, there is perhaps no technology as underappreciated than the blessing of a stable electric power supply. From lighting up homes and schools across the globe to providing life in the busiest of hospitals, we have all come to expect our access to energy as a fundamental human right. Although it is hard to imagine life without electricity, its conception occurred not so long ago. Compared to the discovery of fire around two million years ago and the wheel sometime between 2800-4000 BC, the invention of the battery in 1800 can be considered relatively recent. Since then electricity rapidly reached every corner of the world within the span of a hundred years, making it one of the greatest engineering achievements of the 20th century [1]. During this period the techniques for generation, transmission, and distribution of electric power have remained fairly constant. In recent decades, however, two transformative research directions have emerged viz. towards distributed generation [2] and towards renewable integration [3]. This massive energy transition has been made possible through wide-spread application of power electronics at numerous points in the grid, albeit limited in operational voltage due to inherently low bandgaps of silicon-based power switches. With the introduction of silicon carbide, these limitations are gradually being pushed towards the medium-voltage level with technologies such as the solid-state transformer. SSTs are expected to be a vital part of future power systems, wherein renewable energies are integrated seamlessly without any significant disturbance [4]. The medium-voltage transformers used in these SSTs will experience a diverse variety of quasi-rectangular stresses across their insulations, characterised by fast rise and fall times repeating at frequencies of up to a hundred kilohertz. This "mix" of stresses are known to catalyze gradual deterioration on account of enhanced partial discharge activity [5], which are further exacerbated by thermal runaways caused by capacitive currents flowing through the dielectric. All of this leads to increased probabilities of breakdown thereby lowering the expected life-times of the insulation. Hence, it is of crucial importance to quantify this accelerated ageing in meaningful ways, understand what causes it, and draft guidelines for designing insulations in solid-state transformers for the future. Considering this, it is therefore the responsibility of us Electrical Power engineers to explore these questions to ensure resilient infrastructure that can last generations. This forms the core motivation behind this thesis.

#### 1.2 RESEARCH QUESTIONS

The aim of this work is to investigate the performance of oil-paper insulations under pulsed waveforms, by linking the dielectric breakdown to specific pulse parameters such as repetition rate and peak voltage magnitude. To do this, the research objectives (RO) were set as follows,

- RO1: To develop a solid-state pulse modulator for testing dielectrics

- RO2: To study the ageing trend of oil-paper under pulsed stresses

In the process of achieving these objectives, the answers to three research questions (RQs) were found. These are summarised as follows,

- RQ1: Are SiC MOSFETs a practical substitute to Si IGBTs in solid-state medium-voltage pulse-modulator applications?

- RQ2: What are the critical pulse transformer design considerations when generating quasi-rectangular pulses across capacitive samples?

- RQ3: How does the frequency of pulsed voltages accelerate the ageing processes in oil-impregnated paper?

Apart from these academic objectives, the personal goals of the thesis were to build hardware from the ground-up, use this hardware to produce suitable results, and finally analyse these results to gain important insights.

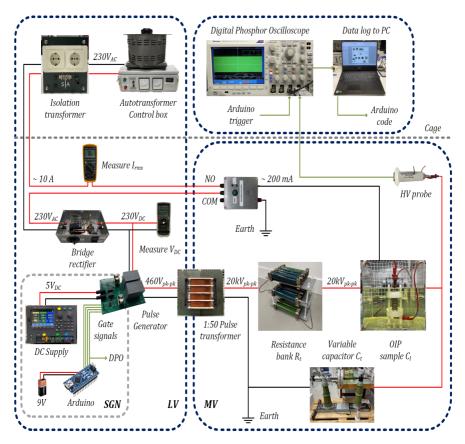

#### 1.3 MODULATOR TOPOLOGY

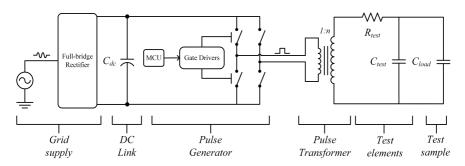

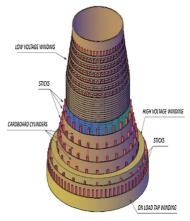

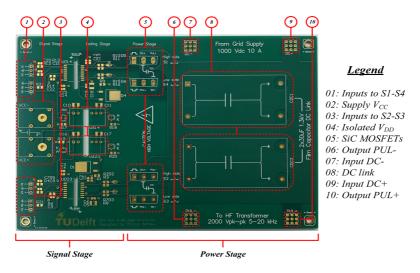

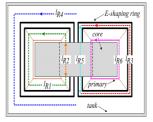

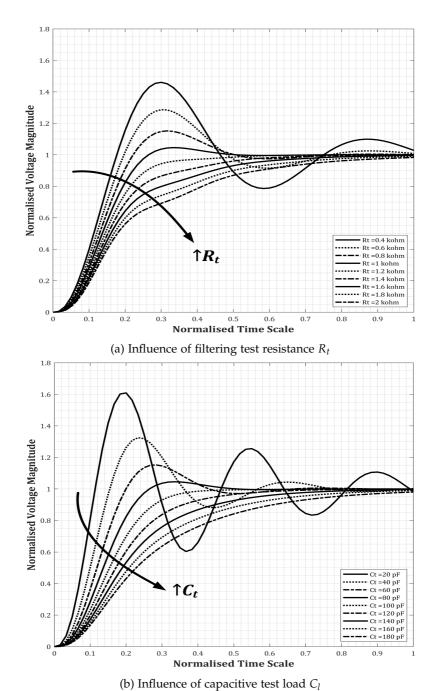

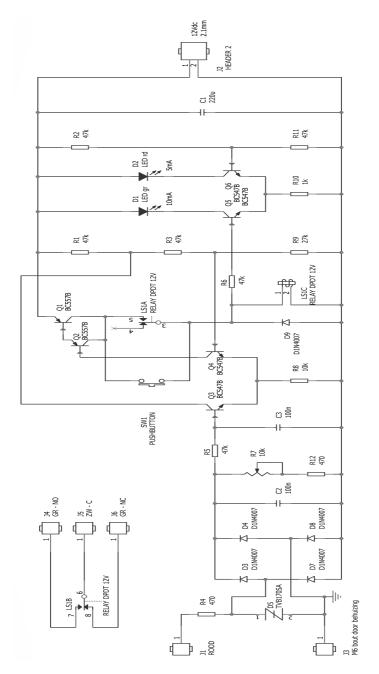

The designed pulse modulator is shown in Fig. 1.1. The full-bridge converter rectifies power from the AC mains to charge the DC link capacitor  $C_{dc}$  the voltage across which is then converted to sharp pulses through the H-bridge pulse generator. The switches are controlled with a microcontroller to produce unipolar/bipolar pulses of variable frequency. The output is then stepped up via the pulse transformer with turns ratio n and finally applied onto the oil-paper sample through elements  $R_t$  and  $C_t$ .

Figure 1.1: Circuit of the pulse modulator system

#### 1.4 PROJECT OVERVIEW

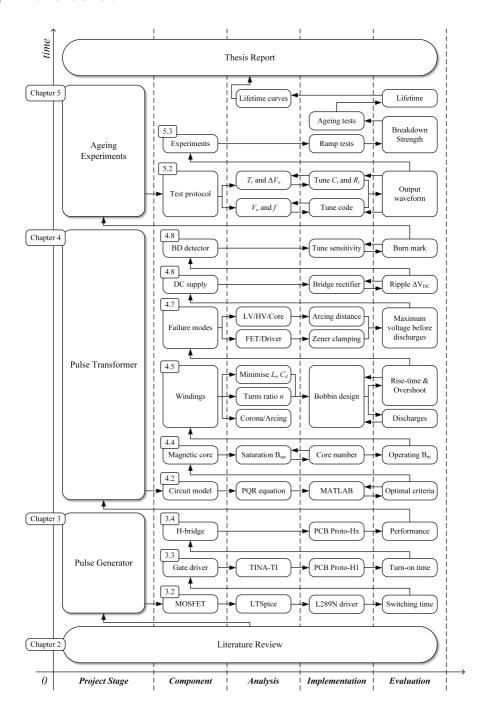

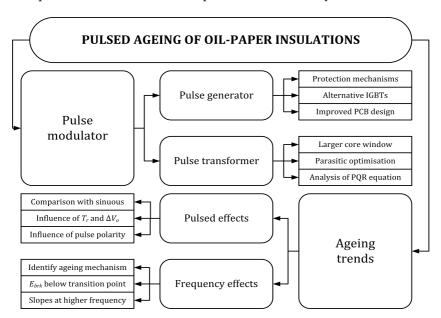

An overview of the project timeline is given in Fig 1.2. **Chapter 2** discusses the history of oil-paper insulation, the origin of pulses in the grid, their deteriorating effects on insulations, and techniques to replicate these pulses for experiments. **Chapter 3** develops the variable frequency SiC-based H-bridge pulse generator through component selection, simulation studies, PCB prototypes, and evaluation tests. **Chapter 4** derives a novel *PQR* equation to characterise the modulator, designs the pulse transformer through analysing the tradeoffs, comparing the bobbin iterations, the magnetic core characteristics, the failure modes with their solutions, and the required modulator sub-circuits. **Chapter 5** describes the theory of the ageing experiments, the followed test protocols, and demonstrates the influence of pulse parameters on oil-paper samples through statistical analysis. **Chapter 6** draws the main conclusions through a reflection of the obtained results, the learning experiences, the possible scopes of improvement, and new research questions that emerged during the course of the thesis.

#### 4 INTRODUCTION

FIGURE 1.2: Project timeline

#### LITERATURE SURVEY

My goal is simple. It is a complete understanding of the universe, why it is as it is and why it exists at all.

Stephen Hawking The Theory of Everything (2002)

Since the thesis project spans several different subtopics of high-voltage engineering and power electronics, the purpose of this chapter is to impart to the reader a thorough theoretical background related to the concepts utilised in subsequent chapters. This is done by walking through relevant works in the form of journal articles, books, standards, and so on. Considering the vast expanse of available literature, special care has been taken to condense it into a sizeable chapter by citing what the author believes to be the most influential works in the respective subtopics.

#### 2.1 PROPERTIES AND APPLICATIONS OF OIL-IMPREGNATED PAPER

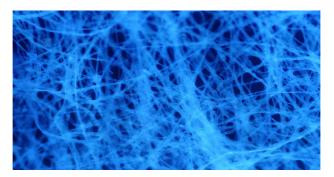

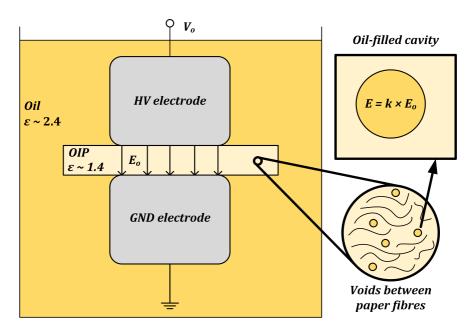

Cellulose-based materials such as paper have been used as electrical winding insulation ever since the invention of the first transformer. This can be attributed to two reasons viz. the natural abundance of its primary source i.e. wood, and the excellent dielectric properties of pure cellulose [6]. The primary ingredient for making paper is pulp, a fibrous material prepared by extracting cellulose fibres from tree wood through mechanical, chemical, or chemi-thermomechanical techniques. Paper pulp consists of around 80% cellulose (crystalline and hydrophilic), 10-15% hemicellulose (amorphous and semi-soluble), and 2-5% lignin (rigid and hydrophobic). The ratio of these three "incompatible" polymers determine the strength of the pulp and depends on the pulping process [7]. One such process is the Kraft process used to produce Kraft paper, the dominant insulation material in power transformers. Unlike other techniques, the kraft method uses sodium hydroxide (NaOH) and sodium sulphide ( $Na_2S$ ) to break the bonds between cellulose, hemicellulose, and lignin. In doing so, the resulting Kraft paper is made free from almost all lignin content, which is responsible for weakening the bonds between cellulose and hemicellulose due to its hydrophobic nature. The pulp is finally converted into paper through pressing and drying. The fibrous intricacy of paper can be better appreciated from the micrograph of common tissue paper shown in Fig 2.1. The picture was constructed by manually stitching 9 separate images into a single panorama. Each individual fibre is approximately 10 micrometres wide.

Figure 2.1: Micrograph of tissue paper fibres under ultraviolet light by R. Wheeler

Historically speaking, cellulose has been a major tool in shaping human culture and development, from the Egyptian papyri we studied ancient writings from to the cotton clothes we wear to the wooden furniture we use. This has made it the most common polymer on Earth and is also considered to be almost inexhaustible [8]. Cellulose ( $[C_6H_{10}O_5]_n$ ) is an organic polysaccharide made up of hundreds (poly) of glucose chains (saccharide) linked to each other via glycosidic bonds. The molecular structure of a cellulose fibre (Fig 2.2) contains a large number of anhydroglucose units, each made of 3 hydroxy groups, with every second ring rotated 180° in the plane. The number of these units define the polymer's Degree of Polymerisation (DP), a useful measure of its chemical and mechanical properties. The DP values for newly installed transformer insulation can range from 1000-1400, slowly degrading over time to values of 200-300 at the end of its lifetime.

Figure 2.2: Molecular structure of cellulose; n = Degree of Polymerisation [8]

Being hydrophilic, cellulose is highly susceptible to absorb moisture even in the presence of the slightest amount of humidity. For this reason, paper is always dried before it is used in combination with either oil or a resin, oil-paper being the most common form. Additionally, the oil is filtered to remove unwanted impurities and degassed to remove any gases dissolved in it. While paper provides mechanical support to the windings, oil provides cooling from the heat generated within the equipment. Hence the quality of the oil used is also another factor for healthy transformer operation. Mineral oil is obtained as a by-product during the distillation of crude petroleum. The refining processes are selected in such a way so as to produce oil which satisfies the operating limits of the transformer. These processes are similar to those used to produce common lubricating oils, making transformer oil a monetarily feasible choice as an electrical insulating liquid [9]. However their dependence on crude petroleum makes mineral oils a non-renewable resource with limited biodegradability. They also have low ignition temperatures which can lead to disastrous consequences in the event of an arc or lightning strike. As an alternative, synthetic silicone oils (polydimethylsiloxane or PDMS) have excellent thermal stability, selfextinguishing capabilities, and do not require major transformer design alterations [10]. Despite this, mineral oil still remains as the most widely used insulating liquid in transformers. A comparison of typical properties between mineral and silicone oils is given in Fig 2.4.

(b) Insulation layers [11]

Figure 2.3: Illustrations of Kraft paper implemented as insulation

The developments in high-voltage equipment such as power transformers and cables have been hand in hand with the developments in oil-paper insulations. Some early examples of transformer insulations include cotton or jute cloth boiled in oil. It was in 1922 that the *American Institute of Electrical Engineering* (AIEE) began their experiments on oil-paper materials to better analyse their breakdown strengths and mechanisms [12]. At the time, however, chemistry was not considered a significant contributor to the field of high-voltage, making it difficult for the then physicists to gain significant insights. Regardless of this knowledge gap, the major findings were the need to reduce air bubbles and moisture content, both of which are direct causative factors for dielectric loss and breakdown.

Through the next decade, scientists slowly recognised the importance of material science expertise in studying insulation materials. It was this realisation that led to several key improvements in high-voltage equipment constructions and designs during the 1930s, such as the introduction of plastic-based insulations for power cables [12]. By the 1950s, Kraft paper had gained massive traction as the prime dielectric used in power transformers and a prime topic of research for material scientists across the world. To meet the increase in insulation requirements due to increase in voltage levels, power transformers began to use Kraft paper with insulating oil. These international efforts led to a number of enhancements in paper strength, for example by adding synthetic fibres. Now again in the 21st century, oil-paper studies have regained interest due to the effect of pulsed waveforms on accelerate ageing of these insulation materials. But before studying the effects of sharply changing stresses on oil-paper insulations, it is first important to identify the source of these waveforms and parametrise them. This is discussed in the next section.

| Table II: Mineral Transformer Oil—Typical Molecular Characteristics |            |            | TABLE I<br>TYPICAL PROPERTIES OF SILICONE TRANSFORMER LIQUII     |              |

|---------------------------------------------------------------------|------------|------------|------------------------------------------------------------------|--------------|

| Transformer Oil Type                                                | Naphthenic | Paraffinic | TYPICAL PROPERTIES OF SILICONE TRANSPO                           | JKMEK LIQUID |

| Distillate Boiling Range (ASTM D2887)                               |            |            | Thermal                                                          |              |

| Initial Boiling Point, °C                                           | 238        | 239        | Flash point °C<br>Fire point °C                                  | >300<br>>350 |

| 5% Recovery Temperature, °C                                         | 271        | 306        | Pour point °C                                                    | -55          |

| 50% Recovery Temperature, °C                                        | 330        | 372        | Relative thermal conductivity (cal/cm/s/°C)10-4<br>Specific heat | 3.6          |

| 95% Recovery Temperature, °C                                        | 384        | 419        | (cal/gm/°C) 25°C<br>Coefficient of expansion                     | 0.360        |

| Final Boiling Point, °C                                             | 429        | 531        | (cm <sup>3</sup> /cm <sup>3</sup> /°C) 25°C                      | 0.00109      |

| Average Molecular Weight - g/mole                                   | 384        | 419        | Rate of heat release (kW/m <sup>2</sup> ) (48-in pan)            | 100-125      |

| Number of Carbon in Average Molecule                                | 18         | 21         | U.L. fire hazard rating                                          | 4-5          |

| (a) Miner                                                           | al oil [9] |            | (b) Silicone oil [                                               | 10]          |

FIGURE 2.4: Property tables for typical transformer oils

#### 2.2 ORIGIN AND CHARACTERIZATION OF PULSE WAVEFORMS

As mentioned in Chapter 1, the energy sector is currently undergoing a transition to a greener future wherein our dependence on fossil fuels is reduced through renewable integration. The use of power electronics have facilitated the interfacing of these renewables to function in tandem with the existing AC-dominated infrastructure. Advancements in semiconductor technologies in the second-half of the twentieth century made possible the accurate control and efficient conversion of power, such as in variable speed drives (VSDs) [13] and solid-state transformers (SSTs) [14]. The idea of an SST was first patented in 1970 by W. McMurray, stemming from the concept that a high frequency link in power circuits could significantly reduce the effective volume of the device while also being able to push through larger power densities. This can be implemented by using solid-state switches to produce medium-frequency voltages which would then be passed through a transformer (hence the term SST). This is illustrated in Fig. 2.5.

FIGURE 2.5: Figures from Patent US3517300 filed by W. McMurray [15]

Due to the limited capabilities of semiconductor devices, SST technology could not be fully realised in that era. However with massive breakthroughs in the field of power electronics during the last decade, SSTs are now a central topic of research in several leading groups across the world. Some examples of such transformative work are those carried out by J. W. Kolar of ETH Zürich, Switzerland [4] and W. van der Merwe of University of Stellenbosch, South Africa [16]. The simple yet powerful concept of an SST can provide several flexibility features such as bi-directional power flow between AC or DC grids, real-time active/reactive power control, as well as conversion or conditioning of energy within the grid. A comprehensive overview of SST applications is given in [17]. For high-voltage applications, multi-level converters (MMCs) are implemented to reduce the harmonic

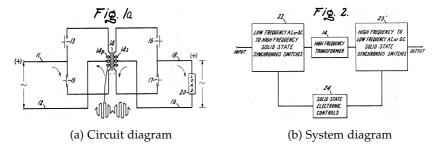

distortion, reduce the size of the output filter, increase the power efficiency, and to allow better fault tolerance [18]. In addition to these benefits, increasing the number of levels n in an MMC reduces the withstand potential of each switch in the converter. As an example, an 11 kV SST requires at least seven voltage levels which brings the per-switch rating to around 2.7 kV [14]. On the other hand, a higher n results in higher costs and complex switching control. There is hence a tradeoff between choosing higher values of *n* and using switches with greater voltage ratings. This tradeoff is what made the introduction of wide band gap silicon-carbide (SiC) monumental for the future of high-power electronics [19]. While Si MOSFETs have superior switching speeds of a few nanoseconds, their inherently low band gap makes them unsuitable for high-voltage switching applications. Conversely, Si IGBTs can withstand larger voltages up to 6.5 kV, but have significantly slower switching characteristics. The SiC MOSFET, introduced by CREE Wolfspeed in 2011, overcomes both these drawbacks by combining the strength of IGBTs and the speed of MOSFETs (Fig. 2.6). Consequently, they are expected to play an integral role in SST applications for the power systems of the future. Due to their unique properties, the implementation of SiC-devices requires extra considerations that will be explained in Chapter 3. It is another one of the research objectives (RQ1) of this thesis to explore the design of SiC-devices in high-voltage high-speed switching applications.

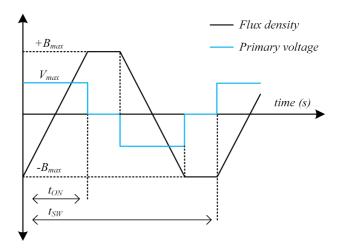

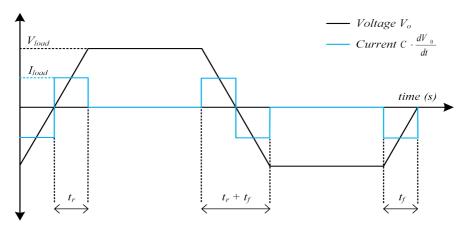

FIGURE 2.6: Comparison of Power and Switching capabilities of Si and SiC devices

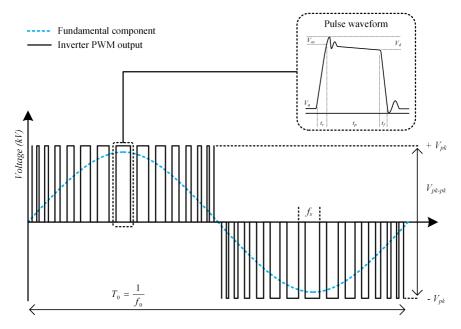

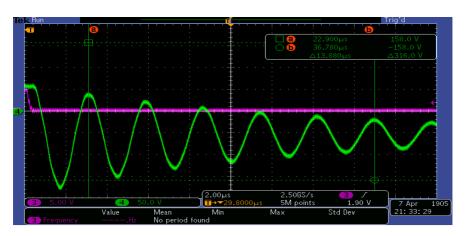

The most critical component of the SST is the medium frequency transformer. In the modern power system, SSTs consist of pulse-width-modulation (PWM) controlled inverters that operate at frequencies of up to several tens of kilohertz. As a result, the waveforms observed in these SSTs contain fast-rising frequency components as shown in Fig. 2.7, and can be characterised using certain parameters. The peak amplitude  $V_{pk}$  is measured as the maximum numerical voltage value for a unipolar pulse, while the peak-to-peak swing  $V_{vk-vk}$  depends on the polarity of the pulses i.e. unipolar  $(V_{vk} = V_{vk-vk})$  or bipolar  $(V_{vk} = 2V_{vk-vk})$ . The fundamental fourier component of the waveform is a sine wave corresponding to the operating frequency of the SST. The terms switching frequency  $f_s$  and repetition rate RR are used interchangeably, since they are both related to the time between two successive pulses. Apart from the parameters that define the waveform as a whole, specific parameters define each individual pulse. The rise time  $t_r$  is the time taken for the pulse to rise from 10% to 90% of its final value, converse to the fall time  $t_f$ . The  $V_{vk}$  and  $t_r$  determine the slew rate of the pulse, an important characteristic that measures the rate of change of voltage (and thereby field stress) across the insulation in kV/ $\mu$ s. When designing pulse transformers, the  $t_r$  and overshoot  $V_{os}$ possess an inverse relationship as will be shown later in Chapter 4. The pulse width  $t_p$  and droop  $V_d$  have a direct proportionality, which is intuitive since a larger pulse width would provide more time for the pulse top to decay. The  $t_n$  is related to the duty cycle D which varies per pulse due to pulse width modulation [20]. After the pulse completes its fall transition, it usually settles at a non-zero value known as quiescent voltage  $V_a$ . Finally, it is important to note that since only 2-level inverters are considered here, parameters such as number of levels n are not discussed. The standard IEC 60034 Part 18-41 provides some common characteristic ranges of the terminal voltages of converter-fed rotating machines [21]. Similar, if not faster and larger, values can be expected in present day SSTs. Table 2.1 summarises the values given in the IEC standard as well as those used by R. Färber in his PhD thesis [22]. In this thesis he explored the effect of mixed-frequency medium-voltage stresses on polymeric insulations to determined the best potting material for MFTs. To that end, he designed and developed an online dielectric spectrometer for evaluating the dielectric health. Now that we have learnt the origin of pulsed waveforms in the power system, characterised them with familiar parameters, and observed their usual values we can now study the impact of these sharp voltages on insulation materials, specifically oil-paper.

Figure 2.7: Typical pulse-width modulated voltage output of an inverter

| PARAMETER                  | SYMBOL      | RANGE                 |

|----------------------------|-------------|-----------------------|

| Peak voltage amplitude     | $V_{pk}$    | 0.5 to 10 kV          |

| Peak-to-peak voltage swing | $V_{pk-pk}$ | 0.5 to 20 kV          |

| Switching frequency        | $f_s$       | 5 Hz to 20 kHz        |

| Fundamental frequency      | $f_0$       | 5 Hz to 1 kHz         |

| Pulse Rise time            | $t_r$       | 0.05 to 2 μs          |

| Pulse Fall time            | $t_f$       | 0.05 to 4 μs          |

| Slew rate                  | -           | 0.5 to 50 kV/ $\mu$ s |

| Pulse Polarity             | -           | Unipolar or Bipolar   |

| Pulse width                | $t_p$       | 2 µs to 100 µs        |

| Peak overshoot             | $\Delta V$  | 2 % to 5%             |

| Voltage droop              | $V_d$       | variable              |

| Quiescent voltage          | $V_q$       | variable              |

Table 2.1: Common parameter ranges of 2-level SST inverter waveforms

#### 2.3 EFFECTS OF PULSED STRESSES ON INSULATION MATERIALS

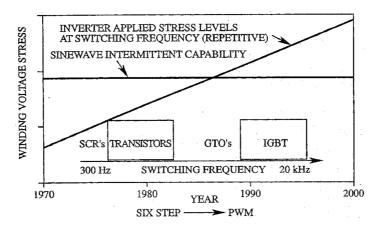

The influence of quasi-rectangular voltages on insulation ageing was first observed in the stator windings of inverter-fed motors which were "magnet" wires embedded in epoxy. The 1980s saw an increased application of variable speed drives for the control of motors used in industrial sectors. The engineers at the time also observed proportionately higher occurrences of failures in the insulations of these motor stator windings. It was then hypothesised that there must be some link between medium frequency components and insulation ageing, thereby leading to several studies in the 1990s in this topic [23] [24] [25]. In 1992, G.C. Stone et al. examined the effect of unipolar repetitive voltage surges on the ageing of pure epoxy [26]. His results showed that accelerated ageing could occur even in the absence of partial discharges (PDs), which was then believed to be the phenomenon that causes ageing. He studied how the repetition rate, polarity and magnitude of voltage surges could instead better explain ageing in the non-PD regime. In 1995, J.A. Oliver et al. elucidated in detail the effect of steepfronted surges on motor windings [27]. The brief moment at which such a wave strikes the stator, the frequency content causes a capacitive division of surge voltage across the windings which is concentrated in the first few turns. Sharper waves contain faster frequencies causing larger voltages across these turns leading to sooner failures in the insulation. The magnitude of this voltage is expected to increase with developments in semiconductor switches, shown in Fig. 2.8 by A.H. Bonnett.

Figure 2.8: Winding stresses versus transistor developments [28]

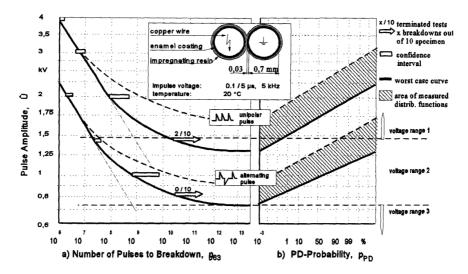

An important insight from these studies was that the mechanism of failure in the PD and non-PD regimes diffed greatly. This was illustrated by M. Kaufhold in 1995 [29] when investigating the failure mechanism of interturn winding insulations with 0.1/5  $\mu$ s 5 kHz 0.7 to 4 kV pulses. He introduced the idea that dielectric failure in the PD regime is determined by a  $p_{PD}$ probability of partial discharge occurrence and a  $n_h$  number of PD pulses required to induce breakdown. The values of  $p_{PD}$  were computed as the ratio of measured pulses which caused PD to the number of pulses applied. These two parameters were then plotted against the amplitude of the pulse in three distinct ranges, as shown in Fig. 2.9. In voltage range 1 almost all applied pulses cause a PD ( $p_{PD} = 1$ ), indicating that failure would occur exactly after  $n_h$  pulses. In voltage range 2 the probability reduces but to some non-zero value (0 <  $p_{PD}$  < 1), indicating that  $n > n_h$  pulses would cause breakdown. Voltage range 3 refers to the non-PD regime ( $p_{PD} = 0$ ) where partial discharges are hardly observed. He also noted that it was the peak-to-peak voltage  $V_{vk-vk}$  that caused breakdown, indicating that alternating (bipolar) pulses can cause quicker failures than unipolar ones. With these results, he concluded that failures were a consequence of partial discharges alone. It would then be expected that failures under partial discharge inception voltage (PDIV) should be non-existent, but this is not the case and hence requires more research (which was later explored for epoxy by R. Färber from ETH Zürich in 2019 [22]).

Figure 2.9: Plot of  $p_{PD}$  and  $n_h$  in three pulse voltage regions [29]

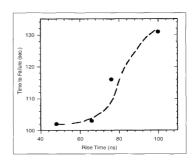

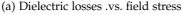

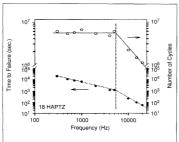

The most influential work that answered these pending questions was by W. Yin in 1997. She explained that the failure of these insulation materials cannot be attributed to a single factor, but rather a combination of multiple factors such as partial discharge, dielectric heating, and space charge formation [30]. She first showed that under the PDIV, the flow of high-frequency component currents through the insulation caused dielectric heating which result in failures. This is further increased in the PD regime as illustrated in Fig. 2.10a. Next, she showed that fast pulse rise-times lead to rapid changes in temperature and an inability to dissipate this heat quickly enough is what causes failures, as illustrated in Fig. 4.8. She then showed the effect of frequency, illustrated in Fig. 2.10c, which indicated a transition point at around 5 kHz above which failure times decreased significantly. Finally, she showed that insulations under bipolar fail the quickest due to the local space-charge field, similar to that in modern HVDC cables. For this reason, bipolar pulses at 10 kHz and above were selected for this thesis to reduce experimental time. W. Yin's comprehensive analysis ended the debate at the time, paving the way for standardised rules for motor windings [31].

(b) Effect of pulse rise time

(c) Effect of pulse frequency

(d) Effect of pulse polarity

FIGURE 2.10: Important dependencies found by W. Yin [30]

Following W. Yin's work and subsequent standards, the need for dielectric ageing studies under mixed frequencies died down in the 2000s. This decade saw an increased research in SST technologies and by the 2010s the SST was seen as a vital part of future smart grids. This renewed the interest in studying insulation materials used in medium-frequency transformers, since they would experience stresses quite similar to those in motor windings. Above PDIV, the factors affecting the lifetime include,

• **Pulse magnitude**: The most influential parameter causing dielectric failure is the peak-to-peak voltage magnitude, regardless of the waveform shape. This follows the inverse power model of the form,

$$L = L_0 V^{-n} \tag{2.1}$$

Cavallini *et al.* elucidates this with the fact that the lifetimes for different waveforms of the same frequency when plotted on a double logarithmic plot fall on the same line [32].

• **Pulse frequency**: There is a common consensus that the lifetime decreases with an increase in frequency. This is expressed as an inverse exponential,

$$T_{failure} \propto f_s^{-k}$$

(2.2)

There is still debate on the value of k > 0 itself. M. Moonesan *et al.* proposed an inverse relationship (k = 1) wherein the damage due to PDs is independent of  $f_s$  [33]. But P. Wang *et al.* obtained  $k \approx 0.6 - 0.8$  with the per-PD degradation being proportional to  $f_s$  [34].

- Pulse rise time: As shown by W. Yin [30] and M. Kaufhold [29], faster rise times can reduce the lifetime. This is consistent with the observation that these shorter rise times lead to larger PD magnitudes [34] [35].

- Pulse polarity: It was also shown by W. Yin [30] and M. Kaufhold [29] that the peak to peak voltage magnitude is what reduces insulation lifetime, as opposed to just peak magnitude. M. Kaufhold explains that PD occurrences lead to an accumulation of heteropolar space charges on the enamel surface. The electric field due to this charge negates the applied electric field for unipolar excitations, but instead increases the field intensity for bipolar excitation. Hence the time to failure under bipolar pulses is almost half as much as it is under unipolar pulses.

• **Pulse duty cycle**: Cavallini *et al.* illustrated that the shorter impulse widths require larger voltages to incept repetitive PDs, but the PDIV itself does not depend on the impulse width [36]. However the authors showed that longer pulse widths can result in lower repetitive partial discharge inception voltage (RPDIV) since there is more time for a starting electron to become available and begin the discharge. This was further validated by P. Wang *et al.* by observing that reducing the duty cycle from 50% to 5% can bring about almost 30% increase in failure time [37].

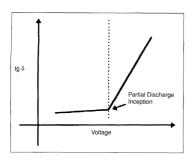

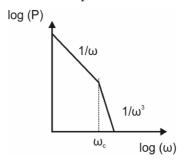

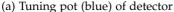

When compared to the ageing above PDIV, the trend of insulation failures under PDIV is significantly less severe. An excellent example of this is provided in [38] wherein the drops in lifetime of twisted enamelled wires were compared between 50 Hz and 10 kHz. It was observed that in the PD regime the drop was around 4 orders of magnitude while in the non-PD regime the drop was only 2 orders of magnitude. This then leads to the question: "What causes insulation failure under PDIV?" The closest answer was provided by D. König et al. in 1998 when comparing lifetimes of "healthy" well-impregnated samples and "unhealthy" partially-impregnated samples under 50 Hz and 50 kHz [39]. Although the PDIV of healthy samples was measured to be 20 kV, they began to fail at only 10 kV under 50 kHz. The authors attribute this to higher dielectric losses (by 1000 times) at 50 kHz. The temperature increases when the rate of cooling is insufficiently fast to compensate for the rate of heating. Further, the losses increase at higher temperatures leading to a thermal runaway [40]. The losses themselves are due to conduction and polarisation currents, both of which are temperaturedependent [41]. B. Sonerud et al. importantly described the dielectric heating involving harmonics as a function of RMS voltage  $U_n$ , harmonic phase n, fundamental frequency  $\omega_0$ , real part of capacitance C', and the loss factor  $\tan \delta$  [42]. This is then summed for each harmonic and written as,

$$P = \sum_{n=1}^{\infty} |U_n|^2 n\omega_0 C'(n\omega_0) \tan \delta(n\omega_0)$$

(2.3)

This equation will be revisited in Chapter 5. Considering that PDs in oil-impregnated paper is relatively less probable than in polymeric insulations such as epoxy, the failure mechanism due to dielectric heating is important to consider when designing insulations for medium frequency applications. Despite its need, substantive work for oil-paper in this area has been limited in frequency (up to 10 kHz). **This thesis project aims to fill this research gap** by comparing lifetimes at 10 kHz and 50 kHz. Next, we study techniques for replicating pulsed waveforms for experiments.

#### 2.4 TECHNIQUES FOR REPLICATING QUASI-RECTANGULAR VOLTAGES

The generation of high voltage (and usually high power) pulses has been widely explored in literature, owing to their diverse set of applications such as in linear accelerators, klystrons, and high-power RF tubes. The system which generate these pulses are termed pulse modulators and can be realised using different approaches, which are described below.

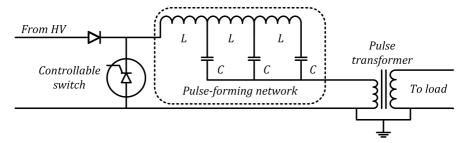

### • Line-type modulators

These modulators employ a pulse-forming network (PFN) feeding a pulse transformer which is then connected to the load, as shown in Fig. 2.11 (a). PFNs comprise of energy storage components such as capacitors and inductors charged by a high-voltage source. This energy is then released in the form of fast pulses (up to a few kHz) into the load, the impedance of which is matched with that of the PFN [43]. Such modulators have been used for several decades, and are relatively compact. However they suffer from limited pulse precision, since the pulse shape is mainly determined by the PFN discharge characteristics. Additionally, load impedance matching is imperative for its functioning.

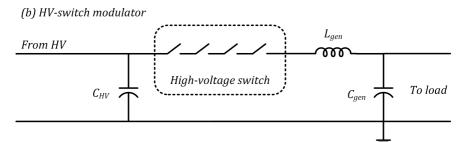

## High-voltage switch

The simplest topology is to directly discharge a capacitor charged to high-voltage through a semiconductor switch as shown in Fig. 2.11 (b). To allow for higher ratings, multiple switches (IGBTs or MOSFETs) can be used in series. Several such modulators are commercially available with ratings up to 200 kV and 5 kA. The main advantages of this topology include precise control of pulse parameters, the ability to attain very fast rise-times, and no limitation on voltage-time product since there is no transformer present. However the switches and capacitors required for this topology are expensive resulting in high development costs and procurement times. Higher voltage ratings require multiple switches which calls for accurate synchronisation in their gate pulses without which the output pulse is deformed and can lead to failure. Further, more switches results in a decrease in overall reliability [44].

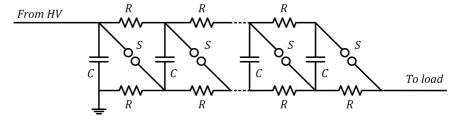

## • Marx generators

As an alternative to the HV-switch modulator, Marx generators produce a high-voltage pulse from a low-voltage supply by discharging a series of identical capacitances with spark gaps as in Fig. 2.11 (c). These are limited in repetition rate, since the required charging time  $\approx 2N^2RC$

and is further increased due to the resistors [45]. The resistors can be replaced with inductors to achieve better repetition rates, but the pulses are restricted by the operation of spark gaps. Replacing these with semiconductor switches such as IGBTs result in the more modern solid-state Marx generators which have been built to generate several kilovolts at repetition rates up to tens of kilohertz [46]. However reaching higher voltages requires higher number of stages in the Marx generator, which also reduces flexibility in varying the voltage magnitude (and hence field stress) across the test sample during ramp tests.

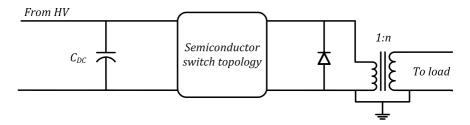

## • Solid-state fed pulse transformer

With the advent of silicon-carbide, the fast switching speeds of Si-MOSFETs and voltage/current ruggedness of Si-IGBTs have found an attractive overlap, resulting in power converters with high  $\frac{dV}{dt}$  capabilities. These converters can be connected to pulse transformers to produce sharp pulses with nanosecond rise-times as in [47]. The advantages are flexible control over pulse parameters with a simple microcontroller and galvanic isolation [48]. Also, very high voltages of hundreds of kilovolts can be achieved with high turns ratios. However this also requires careful design minimisation of leakage flux and parasitic capacitance which reduce the bandwidth and slow the waveform.

An overview of the four discussed pulse modulator topologies is given in Table 2.2. Since pulse shape control is a priority in dielectric testing the line-type is not considered. Breakdown tests can cause failures in system parts which would need replacement, hence an expensive option like HV-switch is not suitable. The Marx generator requires too many stages to produce higher voltages which is unreliable for dielectric testing. Therefore, a solid-state fed pulse transformer configuration was chosen, with an H-bridge pulse generator (for uni/bipolar pulses) feeding a 1:50 pulse transformer.

| TOPOLOGY           | MAIN-PRO               | MAIN-CON                                              |  |

|--------------------|------------------------|-------------------------------------------------------|--|

| Line-type          | Relatively compact     | Limited shape control                                 |  |

| HV-switch          | Simple design          | ↑ Cost (source, switches)                             |  |

| Marx generator     | Sourced at LV          | $\uparrow N_{stages} = \downarrow \text{Reliability}$ |  |

| Solid-state fed PT | Voltage, shape control | Sensitive transformer design                          |  |

TABLE 2.2: Main advantages and disadvantages of modulator topologies

#### (a) Line-type modulator

## (c) Marx generator

#### (d) Solid-state modulator with PT

FIGURE 2.11: Schematics of pulse modulator topologies from literature

#### PULSE GENERATOR

*In broad terms, the task of power electronics* is to process and control the flow of electric energy by supplying voltages and currents in a form that is optimally suited for user loads. Ned Mohan

Power Electronics (1989)

The pulse generator can be seen as the most reliable component of the pulse modulator, thanks to the control that power electronics provides. Since the pulse transformer suffers from its parasitics which affects its output waveform shape, the goal while building the pulse generator is to produce the fastest possible pulses so as to give more design flexibility in later stages. The subsequent sections of this chapter describe the theory and selection of semiconductor switches with their drivers, the PCB hardware prototypes and their learning outcomes, the power and parameter calculations, and finally the performed evaluation tests and an analysis of results.

#### 3.1 SIC MOSFET

## 3.1.1 Theory and mechanisms

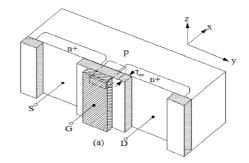

The typical structure of an *n*-channel MOSFET, as shown in Fig 3.1, consists of a p-type doped silicon substrate connected to two heavily n-type doped regions called the source (S) and the drain (D). Under biased conditions i.e. when a potential  $V_{DS}$  is applied across the structure, the device does not allow charge to be conducted through it. However when a positive potential  $V_{GS}$  is applied to the gate terminal (*G*), an inversion layer begins to develop that allows charges to "leak" in the *D* to *S* direction. This is the underlying principle of field-effect transistors (FETs). As an improvement over siliconbased FETs, materials such as SiC and GaN have wider energy bandgaps (lower leakage currents), higher critical electric field (lower on-resistances), higher electron saturation velocity (higher switching frequencies), and higher thermal conductivity (higher operating power densities) [49]. Several studies have been carried out to compare the characteristics of SiC MOSFETs with Si IGBTs [50] and Si MOSFETs [51].

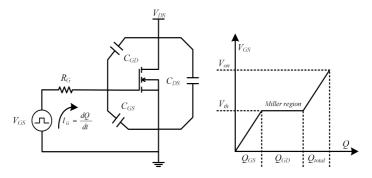

A capacitive model of the MOSFET, shown in Fig 3.2, is used to better understand the mechanism of turning on the MOSFET. The three junctions within the transistor can be represented with three equivalent capacitors  $C_{GD}$ - $C_{GS}$ - $C_{DS}$ . The first step in switching on is to linearly charge the capacitance  $C_{GS}$  to a potential  $V_{th}$  at which the switch begins to conduct *i.e.* in the D to S direction. Due to this new flow of current the capacitance  $C_{GS}$  injects charge into the D terminal of the transistor while at the same time  $C_{GD}$  is being charged from the G terminal. This period where further increase in charge causes no increase in potential is called the Miller region and is quantified with an equivalent Miller capacitance. This phenomenon ends when the charge reaches a certain value  $Q_B$ , after which  $C_{GD}$  and  $C_{GS}$  resuming charging linearly until the transistor is completed turned on at a potential  $V_{on}$ . Since the gate is inherently an insulator its resistance is modelled with an internal gate resistance  $R_G$ , an important factor to consider during switch selection as will be discussed later.

FIGURE 3.1: Idealised MOSFET structure [52]

FIGURE 3.2: Capacitive MOSFET model and Turn-on mechanism

#### 3.1.2 Switch selection: IMW120R140

The right selection of power switch can make a monumental difference in the simplicity of the converter circuitry and must hence be carried out with care. Although a SiC MOSFET can accommodate the high-voltage and high-frequency requirements of the pulse modulator, they are made by only a handful of manufacturers such as CREE Wolfspeed, Infineon Technologies, Rohm Semiconductor, and ON Semiconductor. The required criteria for the MOSFET include,

- A withstand voltage  $V_{DS} \ge$  1200 V

- A sufficient pulse current rating  $I_{D(pulse)}$  in the order of 10 A

- A low on resistance  $R_{DS(on)}$  in the order of 100 m $\Omega$

- A low switching delay  $t_{d(on)}$  and  $t_{d(off)}$  in the order of 10 ns

- A fast switching characteristic  $t_r$  and  $t_f$  in the order of a few ns

- A low internal gate resistance  $R_{G(int)}$  in the order of 10  $\Omega$

- A suitable through-hole package to allow a heat sink to be used

- A cost price below 10 euros, since multiple switches are required

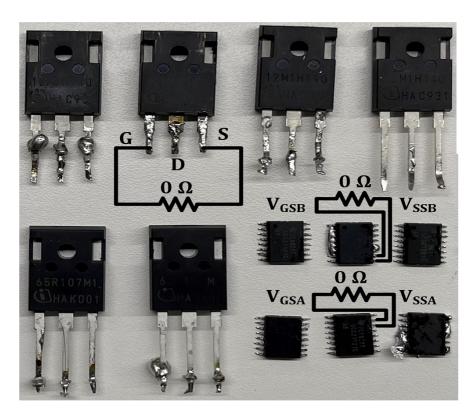

There is of course no switch that excels in all these criteria, and hence a trade-off analysis must be performed to make an educated decision. Such an analysis was conducted for 20 SiC MOSFETs from 4 manufacturers to produce a switch selection chart as shown in Fig 3.3.

| MOSFET            |           |         |           |                    |                  |        |                      |                       |                     |                      |                     |                 |                    |      |                     |                |       |         |      |      |                 |                |       |

|-------------------|-----------|---------|-----------|--------------------|------------------|--------|----------------------|-----------------------|---------------------|----------------------|---------------------|-----------------|--------------------|------|---------------------|----------------|-------|---------|------|------|-----------------|----------------|-------|

| SWITCH PARAMETERS |           |         |           |                    |                  | STATIC |                      |                       |                     |                      |                     |                 | SWITCHING          |      |                     |                |       | DYNAMIC |      |      |                 | LOSSES         |       |

| Supplier          | Price (€) |         | Datasheet | Name               | Package          | Vos    | l <sub>O[cont]</sub> | I <sub>O(pulse)</sub> | R <sub>OS(on)</sub> | V <sub>GS[max]</sub> | V <sub>GS[op)</sub> | V <sub>so</sub> | t <sub>d(on)</sub> | t,   | t <sub>d(eff)</sub> | t <sub>i</sub> | Rojes | Q       | Cm   | Con  | C <sub>ma</sub> | T <sub>i</sub> | Po    |

|                   | RS        | Farnell | Name      | V                  |                  | A      | A                    | mΩ                    | V                   | V                    | V                   | ns              | ns                 | ns   | ns                  | Ω              | nC    | pF      | pF   | pF   | °C              | W              |       |

| Wolfspeed         | 99,18     | 78,49   | link      | C2M0045170D        | TO-247-3         | 1700   | 72                   | 160                   | 45                  | -10/+25              | -5/+20              | 4.1             | 65                 | 20   | 48                  | 18             | 1.3   | 188     | 3672 | 171  | 6.7             | -40/+150       | 520   |

|                   | -         | 69,37   | link      | C2M0045170P        | TO-247-4         | 1700   | 72                   | 160                   | 45                  | -10/+25              | -5/+20              | 4.1             | 35                 | 13   | 46                  | 10             | 1.3   | 188     | 3672 | 171  | 6.7             | -40/+150       | 520   |

|                   | 6,79      |         | link      | C2M1000170D        | TO-247-3         | 1700   | 5                    | 6                     | 1000                | -10/+25              | -5/+20              | 3.8             | 6                  | 10.5 | 11                  | 60             | 24.8  | 13      | 200  | 12   | 1.3             | -55/+150       | 69    |

|                   | 13,42     | 11,80   | link      | C3M0075120D        | TO-247-3         | 1200   | 30                   | 80                    | 75                  | -8/+19               | -4/+15              | 4.1             | 56                 | 17   | 32                  | 13             | 10.5  | 54      | 1350 | 58   | 3               | -55/+150       | 113.6 |

|                   | 11,5      | 12,12   | link      | C3M0075120K        | TO-247-3         | 1200   | 30                   | 80                    | 75                  | -8/+19               | -4/+15              | 4.5             | 30                 | 14   | 38                  | 10             | 9     | 53      | 1390 | 58   | 2               | -55/+150       | 113.6 |

| Infineon          | -         | 3,95    | link      | IMBF170R1K0M1      | TO-263-7 (D2PAK) | 1700   | 5.2                  | 13.3                  | 1000                | -10/+20              | -0/+15              | -               | 19                 | 14   | 20                  | 22             | 35    | 5       | 275  | 7.2  | 0.7             | -55/+175       | 68    |

|                   | -         | 8,37    | link      | IMBF170R450M1      | TO-263-7 (D2PAK) | 1700   | 9.8                  | 24.8                  | 450                 | -10/+20              | -0/+15              | -               | 27                 | 20   | 32                  | 24             | 20    | 11      | 610  | 16   | 1.7             | -55/+175       | 107   |

|                   | -         | 6,20    | link      | IMBF170R650M1      | TO-263-7 (D2PAK) | 1700   | 7.4                  | 18.7                  | 650                 | -10/+20              | -0/+15              | -               | 22                 | 16   | 24                  | 22             | 25.4  | 8       | 422  | 12   | 1.1             | -55/+175       | 88    |

|                   | -         | 7,79    | link      | IMW120R220M1HXKSA1 | TO-247-3         | 1200   | 13                   | 21                    | 220                 | -7/+23               | -0/+15              | -               | 5                  | 1.4  | 10                  | 14             | 22    | 8.5     | 289  | 16   | 2               | -55/+175       | 75    |

|                   | -         | 9,13    | link      | IMZ120R220M1HXKSA1 | TO-247-4         | 1200   | 13                   | 21                    | 220                 | -7/+23               | -0/+15              | -               | 4.8                | 1    | 9.8                 | 12.7           | 22    | 8.5     | 289  | 16   | 2               | -55/+175       | 75    |

|                   | -         | 9,52    | link      | IMW120R140M1HXKSA1 | TO-247-3         | 1200   | 19                   | 32                    | 140                 | -7/+23               | -0/+15              | 4.1             | 5                  | 2.4  | 10.4                | 13             | 14    | 13      | 454  | 25   | 3               | -55/+175       | 94    |

|                   | -         | 9,33    | link      | IMZ120R140M1HXKSA1 | TO-247-4         | 1200   | 19                   | 32                    | 140                 | -7/+23               | -0/+15              | 4.1             | 5                  | 2    | 10.3                | 11.6           | 14    | 13      | 454  | 25   | 3               | -55/+175       | 94    |

|                   | -         | 7,22    | link      | IMW120R350M1HXKSA1 | TO-247-3         | 1200   | 4.7                  | 13                    | 350                 | -7/+23               | -0/+15              | 4.1             | 7                  | 0.7  | 11.4                | 21.5           | 35    | 5.3     | 182  | 10   | 1               | -55/+175       | 60    |

|                   | -         | 7,22    | link      | IMZ120R350M1HXKSA1 | TO-247-4         | 1200   | 4.7                  | 13                    | 350                 | -7/+23               | -0/+15              | 4.1             | 4.8                | 0.7  | 10.8                | 19.3           | 35    | 5.3     | 182  | 10   | 1               | -55/+175       | 60    |

| ON-SEMI           | 8,24      | 9,78    | link      | NVHL160N120SC1     | TO-247-3         | 1200   | 17                   | 69                    | 162                 | -15/+25              | -5/+20              | 4               | 11                 | 19   | 15                  | 8              | 1.4   | 34      | 665  | 50   | 5               | -55/+175       | 119   |

|                   | 8,24      | 9,78    | link      | NVH4L160N120SC1    | TO-247-4         | 1200   | 17.3                 | 69                    | 160                 | -15/+25              | -5/+20              | 4               | 11                 | 10   | 14                  | 7              | 1.4   | 34      | 665  | 49.5 | 4.3             | -55/+175       | 111   |

|                   |           | 9,92    | link      | NVHL080N120SC1A    | TO-247-3         | 1200   | 31                   | 132                   | 110                 | -15/+25              | -5/+20              | 4               | 13                 | 20   | 22                  | 10             | 1.7   | 56      | 1112 | 80   | 6.5             | -55/+175       | 178   |

|                   | 11,17     | 6,83    | link      | NTHL080N120SC1A    | TO-247-3         | 1200   | 31                   | 132                   | 110                 | -15/+25              | -5/+20              | 4               | 13                 | 20   | 22                  | 10             | 1.7   | 56      | 1112 | 80   | 6.5             | -55/+175       | 178   |

| ROHM              | 6,18      | 8,31    | link      | SCT2280KEC         | TO-247-3         | 1200   | 14                   | 35                    | 280                 | -10/+26              | -6/+22              | 4               | 19                 | 19   | 47                  | 29             | 17    | 36      | 667  | 27   | 5               | -55/+175       | 108   |

| 8                 | 4,90      | 7,72    | link      | SCT2450KEC         | TO-247-3         | 1200   | 10                   | 25                    | 450                 | -10/+26              | -6/+22              | 4.3             | 19                 | 17   | 38                  | 34             | 25    | 27      | 463  | 21   | 4               | -55/+175       | 85    |

FIGURE 3.3: Switch selection chart used to compare available SiC MOSFETS

The 1700V CREE Wolfspeed MOSFETs have the most attractive  $V_{DS}$ ,  $I_{D(pulse)}$  and  $R_{DS(on)}$  but are also the most expensive. The 1700V Infineon MOSFETs are only available in surface-mount-device (SMD) packages and are not suitable for this application. The switches from ON Semiconductor and Rohm Semiconductor are affordable but do not have impressive functional capabilities. The best overall switches are the 1200V CREE Wolfspeed C2M1000170D (lower  $R_{G(int)}$  lower  $I_{D(pulse)}$ ) and the 1200V Infineon IMW120R140M1H (higher  $R_{G(int)}$  higher  $I_{D(pulse)}$ ). What distinguishes the latter is its unique oV turn-off potential  $V_{GS}$  making it possible to drive the MOSFET with a unipolar positive supply instead of a +20/-5 supply. Also, its higher  $R_{G(int)}$  is nullified by its much lower gate charge  $Q_g$  meaning that the gate capacitance can be charged quickly. Hence, it was selected for the H-bridge.

# 3.1.3 Operational characteristics in LTspice

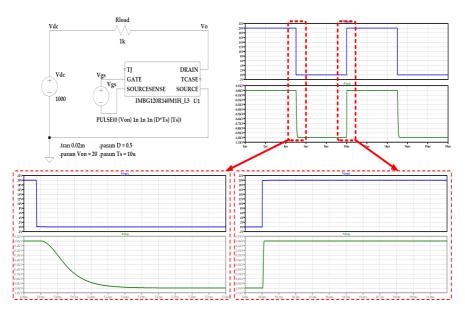

The switching characteristics of the Infineon SiCFET [53] were simulated in LTspice and the results shown in Fig. 3.4. The on/off time and the propagation delays of  $V_{GS}$  were set to 1 ns. It can be seen that the turn-on is significantly quicker than the turn-off. This can be tackled by either applying a negative  $V_{GS}$  or selecting a gate driver with higher sink current.

FIGURE 3.4: Simulation of IMW120R140M1H in LTspice

#### 3.2 GATE DRIVER

### 3.2.1 Theory and mechanisms

Behind every well-functioning MOSFET is a driver selected specifically for operating that semiconductor switch. The primary purposes of gate drivers are to galvanically isolate power signals from control signals and to condition the gate signals as per the input requirements of the switch. Reinforced isolation (between power-side and signal-side) comes in three forms viz. optical (high current and low noise immunity), magnetic (high current and medium noise immunity), and capacitive (low current and high noise immunity) [54]. Additional features such as functional isolation (between high-side and low-side outputs) and basic isolation (to prevent electrical shocks) are available for high-voltage applications [55]. The most critical criteria of the gate driver is its drive strength, parameter that determines how fast it can switch the MOSFET and how much current it requires to do so. The switching operation of the MOSFET is carried out by charging and discharging the input capacitance  $C_{ISS} = C_{GD} + C_{GS}$  with a gate charge  $Q_G$  through a gate current  $I_G$ . This is calculated as,

$$Q_G = \int I_G dt \Rightarrow I_G = \frac{Q_G}{T_r \text{ or } T_f} = \frac{13 \text{ nC}}{7.4 \text{ ns}} = 1.8 \text{ A}$$

(3.1)

The current  $I_G$  differs for switching on and switching off operations as source  $I_{o+}$  and sink  $I_{o-}$  currents, respectively. For SiC applications, drivers with +4/-6 A outputs are used to ensure effective charge transmission to the MOSFET gate terminal. The internal  $R_{G(int)}$  and external  $R_{G(ext)}$  gate resistances of the MOSFET limit the gate current depending on the drive voltage  $V_{DD}$  *i.e* the amplitude of the gating pulses sent to the MOSFET.

$$I_G = \frac{V_{DD}}{R_{G(int)} + R_{G(ext)}}$$

(3.2)

The  $R_{G(ext)}$  is kept smaller for the sink path than the source path to allow higher sink currents. The switching frequency  $f_s$  determines the power requirement of the driver as,

$$P_C = V_{DD} \times Q_G \times f_s = 20 \ V \times 13 \ nC \times 20 kHz = 5.2 \ mW \qquad (3.3)$$

Hence, Higher gate currents equate to faster switching times. Faster switching causes higher switching losses, requiring higher power rated drivers.

#### 3.2.2 Driver selection: UCC21521

The selection of gate driver limits the operation of the switch and must hence be done in tandem with the datasheet of the switch. Most high-quality driver ICs are manufactured by Texas Instruments making them a leader in the semiconductor control industry. The considerations for the SiC driver include,

- A reinforced isolation voltage rating  $\geq$  1200 V

- A high source/sink current rating preferably +4/-6 A

- A low propagation delay in the order of tens of ns

- A low rise and fall time in the order of ns

- A sufficient power rating  $\geq$  5.2 mW

- A high-side low-side driving functionality

- A suitable SMD package for easy PCB designing

- A interfacing range of  $V_{CC} = 5V$  and  $V_{DD} = 20V$

- A common-mode transient immunity (CMTI) greater than 100 V/s

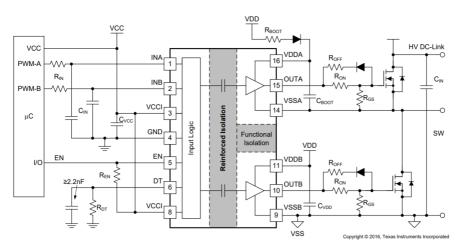

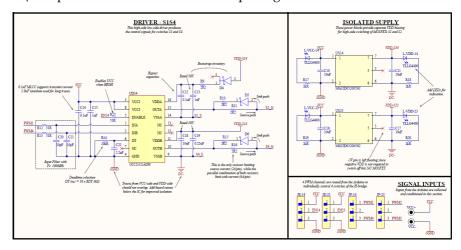

In half-bridge applications, a minimum dead-time is required to prevent a current shoot-through between the high and low side switches. A gate driver with a programmable dead-time is therefore a must. Since the pulse modulator is being used for test applications, which ends in an insulation failure, it is useful to have a separate Enable/Disable pin on the gate driver IC to implement short-circuit protection. The dual-channel +4/-6 A isolated driver UCC21521 from Texas Instruments was finally selected since it satisfies all necessary criteria requirements. It features a 5.7  $kV_{RMS}$ reinforced isolation barrier between power and signal sides, as well as a 1500 kV<sub>DC</sub> function isolation between high and low outputs. With a 19 ns propagation delay, 6 ns rise-time, and 7 ns fall-time, its switching characteristics match the selected SiC MOSFET. It also has programmable dead-time and Enable pin capabilities, both discussed in better detail in later subsections. The UCC21521 comes in two under-voltage lock-out (UVLO) variants, the UCC21521ADW with 5 V UVLO and the UCC21521DW with 8 V UVLO. Both variants are identical and were used interchangeably depending on their availability.

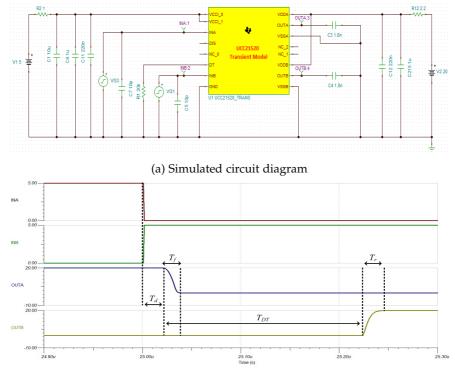

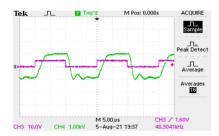

## 3.2.3 Operational characteristics in TINA-TI

To observe the driver characteristics in simulation the TINA-TI software was used, the Texas Instruments equivalent of LTspice. The simulated circuit is shown in Fig. 3.5a. It should be noted that the UCC21520 model is used for this purpose which has a DISABLE pin instead of an ENABLE pin in the UCC21521. The source V1 = 5V represents  $V_{CC}$  which powers the driver and is supported by C1-C6-C11 through R2. The source V2 = 20V represents  $V_{DD}$  which biases the output pulses, and is supported by the C12-C215 through R12. The pulse inputs VG3 and VG1 are filtered by 10pF capacitors C7-C5. The DT pin is connected to a  $20k\Omega$  resistor resulting in a dead-time of  $DT = 10 \times 20 = 200ns$  (explained again in 3.3.1). The dead-time is the period from before the fall ( $T_f$ ) of the first output (OUTA) to before the rise ( $T_r$ ) of the second output (OUTB), shown in Fig. 3.5b.

(b) Switching characteristic showing the  $T_r$ - $T_f$ - $T_d$ - $T_{DT}$  time periods

FIGURE 3.5: Simulation of UCC21520-UCC21521 in TINA-TI

#### 3.3 HARDWARE PROTOTYPES

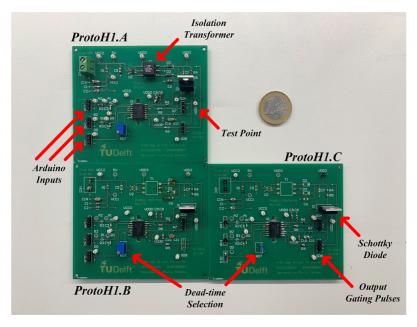

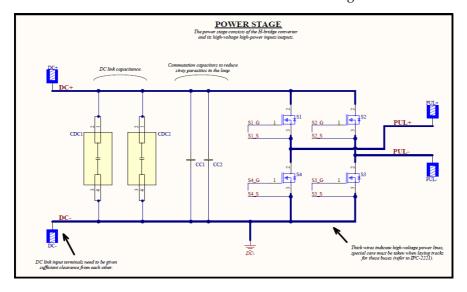

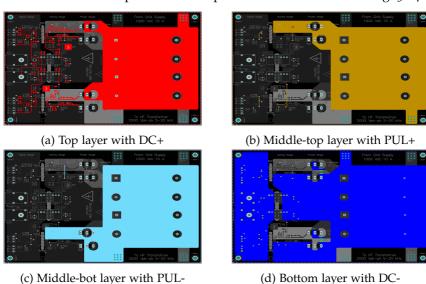

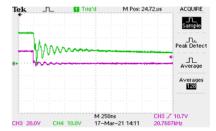

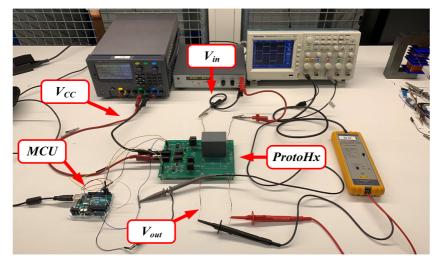

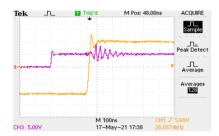

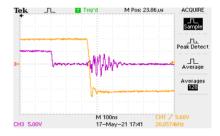

After simulating the characteristics of both switch and driver, two PCB prototypes were built. ProtoH1 is a unoptimised test PCB of the gate circuitry of a single UCC-driver. The traces are made longer and test-points were added to each part of the trace for evaluation. This allowed an in-depth analysis of the effect of each component on the signals flowing through the traces. Using the results from this analysis modifications were implemented when designing ProtoHx, the final PCB of the complete H-bridge converter including the DC link, the switches, and their gate drivers. Additional considerations had to be taken when designing the high-voltage power-stage of the PCB as per the IPCC2221 standard. The following sub-sections discuss the procedure and calculations used for producing ProtoH1 and ProtoHx. An overview of the employed PCB workflow is shown in Fig. 3.6.

FIGURE 3.6: PCB design workflow using Altium Designer

#### 3.3.1 Proto-H1: UCC-Driver PCB

The objectives when designing ProtoH1 were first to get acquainted with the Altium Designer software, and second to produce a single gate-driver so as to individually test the IMW-switch and UCC-driver. The datasheet of the UCC21521 provides a typical application schematic as shown in Fig. 3.7. A brief description of each component is given below.

- Signal-side components:

- $R_{IN}$  and  $C_{IN}$  filters the input pulse signals from the MCU

- $C_{VCC}$  supports the supply voltage  $V_{CC}$  for long PCB traces

- $R_{EN}$  provides limits the current to the EN pin

- R<sub>DT</sub> programs the dead-time selection of output pulses

- $C_{DT}$  supports the 1.8 V source held at the DT pin

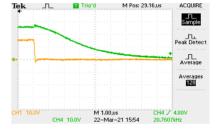

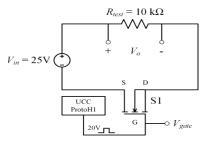

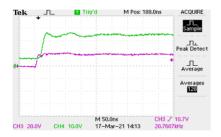

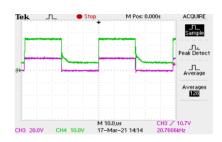

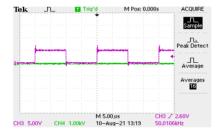

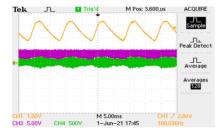

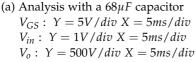

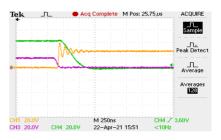

- Gate-side components: