Innovative, Unique and On Point

Martin Geertjes

# An Energy-Recycling Inductive Power Converter for Battery-Powered CMUT-Based Ultrasound Wearables

Innovative, Unique and On Point

by

Martin Geertjes

Student Number:

4324285

Project Year:

2024 - 2025

Thesis Committee: dr. ir. M.A.P. Pertijs TU Delft supervisor

ir. I. Bellouki TU Delft supervisor

dr. ir. Qinwen Fan TU Delft

Version: 1.0

# **Abstract**

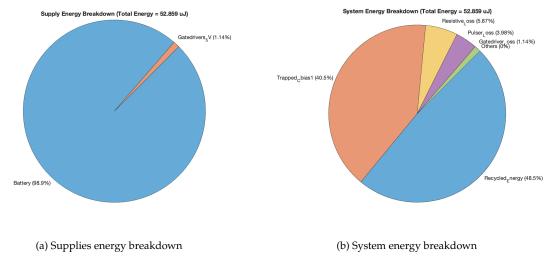

Wearable ultrasound systems hold significant potential for continuous health monitoring but face challenges in minimizing energy consumption and device size. This research investigates the design and simulation of an energy-recycling inductive power converter for CMUT-based wearable ultrasound applications. A comparison between conventional class-D and resonant pulsers highlights the trade-off between operational flexibility and energy efficiency, emphasizing the critical impact of high-voltage bias generation, which can consume hundreds of times more energy than a single transmit pulse.

A novel four-switch converter topology is proposed, enabling both high-voltage biasing and pulsing with energy recycling. Unlike traditional buck-boost converters, the proposed converter operates in a unique regime: it only functions during the initial charging of capacitive loads, after which the output can be fully decoupled, allowing the inductor to perform other tasks. This places the design in a fundamentally different and largely unexplored operating point within power-converter research. It also facilitates energy recycling, allowing the recovered energy to be reused after pulse-acquisitions in other systems where power is required.

System-level simulations explore the influence of inductor sizing, switch dimensioning, and current optimization on efficiency, while break-even analysis indicates that conventional pulsers may remain more practical for typical pulse counts due to lower complexity. Circuit-level implementation in Cadence confirms functional operation, high-voltage generation, pulsing and energy recycling.

This work identifies the primary sources of energy inefficiency and proposes control strategies, including optimized switch timing and parasitic energy recovery, to enhance performance. The study provides a validated foundation for future experimental research and practical implementation, demonstrating the feasibility of energy-efficient wearable ultrasound systems using 180nm technology.

# Acknowledgements

This project has meant more to me than just obtaining my degree. After a period of hard and challenging moments, I can finally transition from being a student to embracing a new phase: citizenship. Believe it or not, I am looking forward to it. Although my ambitions sometimes went further than what was realistic, such as the idea of achieving a tape-out, I now look back with pride at what has been accomplished and how the project was set up.

First of all, I would like to sincerely thank my supervisors, Michiel Pertijs and Imad Bellouki. Michiel, thank you for your sharp questions, creative solutions, and the way you truly involve students in the department. You always managed to provide direction and gave us a real sense of belonging. Imad, your daily guidance, enthusiasm, and genuine interest made working on this project not only very instructive but also truly enjoyable. I will not easily forget our weekly meetings with the three of us: your energy, problem-solving skills, and curiosity were a constant source of inspiration. Thanks to both of you, my learning curve this year has been remarkable, and for that I am deeply grateful.

I would also like to thank the entire department, including the other thesis students, for creating such an open and welcoming environment. In particular, I am grateful to Nuriel and Zu-Yao for their accessibility and support throughout the project. Your involvement has been of great value to me.

Furthermore, I am thankful to my friends and family for their support during this year. Without the nice lunches, the workouts, the evening distractions, including 'Pieletjes gooien' (throwing darts) at Café Bergpolder, and all the fun activities in between, I would not have made it through this project. In particular, I want to thank my parents, who have always supported me through everything; I sincerely hope they can soon enjoy a well-deserved retirement. And finally, to my dear girlfriend Kyra: thank you for your unconditional support, day in and day out. I could not have done this without you.

Martin Geertjes Delft, September 2025

# Contents

| A | Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                      |  |  |  |  |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|

| A | cknowledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ii                                                                   |  |  |  |  |

| 1 | Introduction  1.1 Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2<br>2<br>3<br>5<br>7<br>7<br>9                                      |  |  |  |  |

| 2 | 2.1 Prior Art 2.2 Problem Statement 2.3 Method 2.3.1 Fundamental Analysis 2.3.2 Simulation Models 2.3.3 Transient Models 2.4 Architecture Simulations 2.5 Resonant Pulser versus Conventional Pulser 2.5.1 Bias Circuit 65V Simulations 2.5.2 Resonant Pulser Simulations 2.5.3 Conventional Pulser Simulations 2.5.4 Final results: break-even analysis 2.5.5 Impact of other design variables on 4-switch power converter 2.6 Final Configuration and Detailed Simulation Results | 10<br>11<br>11<br>11<br>14<br>17<br>21<br>25<br>27<br>29<br>31<br>34 |  |  |  |  |

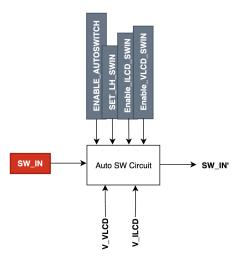

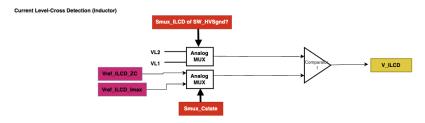

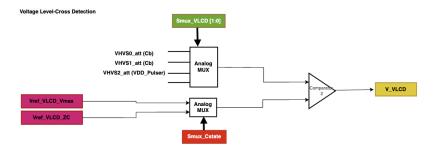

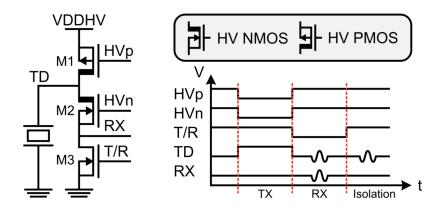

| 3 | 3.1 Overview of US Wearable System 3.2 Overview of Prototype 3.3 Power Converter 3.3.1 Finite State Machine 3.4 Floating Level-Shift Gate Driver 3.4.1 On-Chip Logic 3.5 Current Level Detection 3.6 Voltage Level Detection 3.7 Class-D Pulser 3.7.1 Pulser Core 3.7.2 Pulser Module                                                                                                                                                                                               | 38<br>38<br>39<br>40<br>42<br>43<br>45<br>47<br>48<br>48<br>49<br>50 |  |  |  |  |

| 4 | Circuit Level Simulation 4.1 Pulser                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51<br>52<br>53<br>54<br>55                                           |  |  |  |  |

| Contents | iv  |

|----------|-----|

| Contents | 1.4 |

|                    | 2 Resistive Loss Analysis                      |                 |

|--------------------|------------------------------------------------|-----------------|

|                    | ion and Future Work<br>ure Work                | <b>61</b><br>62 |

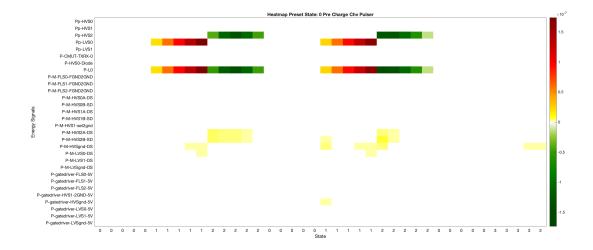

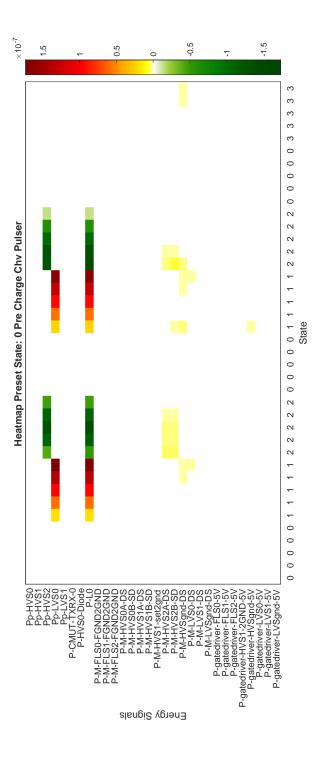

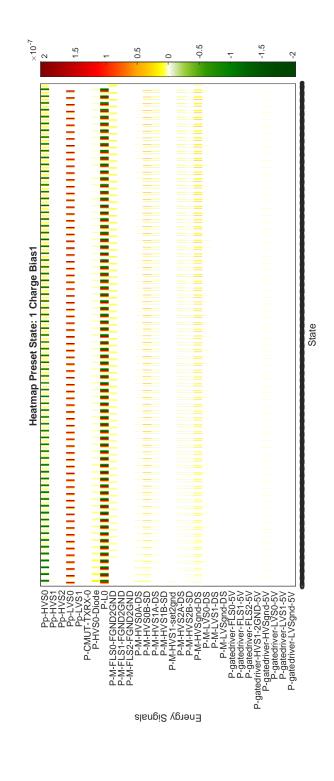

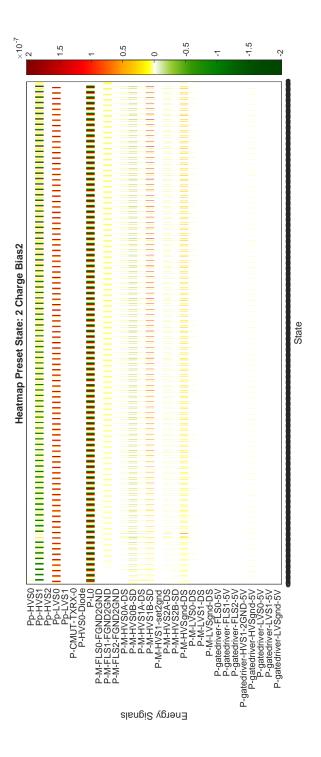

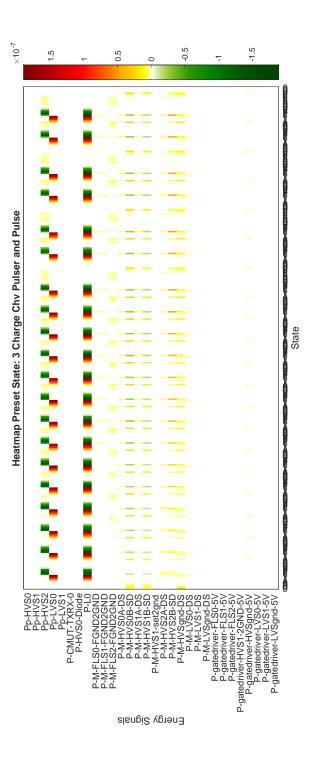

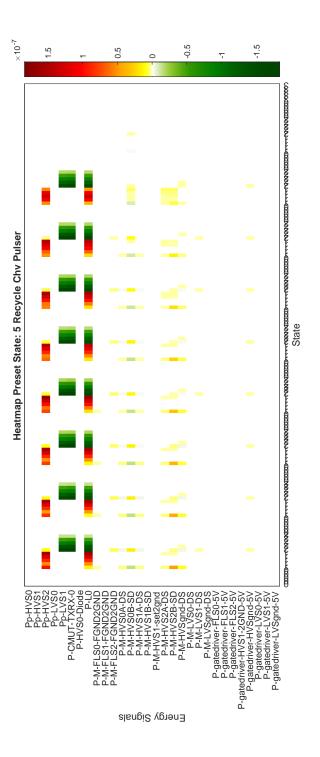

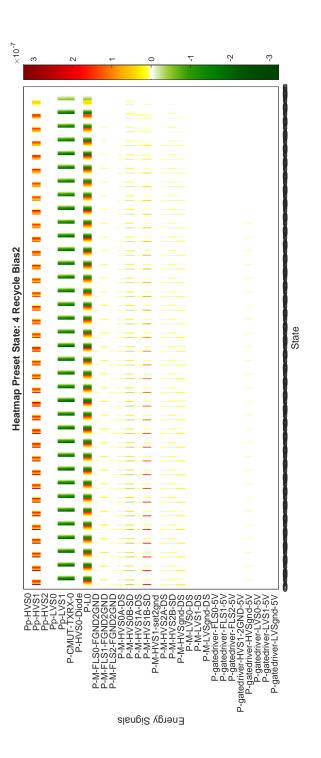

| Appendi<br>A.1 Cac | ix<br>dence Simulation: System Preset Heatmaps | <b>65</b><br>65 |

# Acronyms

- BB Back-to-Back (switch configuration)

- BCD Bipolar-CMOS-DMOS (in TSMC 180nm BCD Gen2 technology)

- BVD Butterworth-van Dyke Model (CMUT Model)

- Cadence EDA software

- CMUT Capacitive Micromachined Ultrasound Transducer

- CP Conventional Pulser / Class-D Pulser

- DAC Digital-to-Analog Converter

- DC Direct Current

- ESD Electrostatic Discharge

- FEM Finite Element Modeling

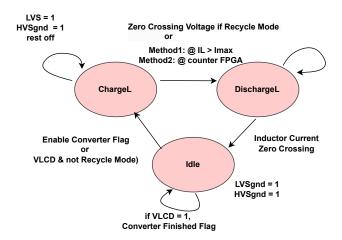

- FSM Finite State Machine

- HV High Voltage

- LNA Low-Noise Amplifier

- LV Low Voltage

- MATLAB MathWorks software

- MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

- NMOS N-channel Metal-Oxide-Semiconductor

- PDK Process Design Kit (in context of TSMC 180nm BCD-Gen2 PDK)

- PMOS P-channel Metal-Oxide-Semiconductor

- Q-factor Quality Factor

- RP Resonant Pulser / Resonant Pulsing

- RxTx Receive/Transmit

- SNR Signal-to-Noise Ratio

- SR-latch Set-Reset Latch

- T/R Transmit/Receive

- TSMC Taiwan Semiconductor Manufacturing Company

- TX Transmit

- US Ultrasound

$\int$

# Introduction

### 1.1. Motivation

Ultrasound (US) imaging is a widely used technique in both medical diagnostics and industrial applications. By transmitting short acoustic pulses and analyzing their echoes, ultrasound systems can generate real-time images of internal structures, quantify volumes, or track motion using Doppler-based methods. Despite these advantages, conventional ultrasound devices are still bulky, multifunctional, and require trained professionals for operation. [1] [2]

Imagine this technique tool while focussing on just one single application, to fit the device in a wearable patch that can continuously monitor your heart or which is able to detect early signs of specific diseases. This all while running on a single battery charge for weeks. This provides 24/7 health insights and enables remote patient monitoring, reducing the need for frequent hospital visits and potentially lowering healthcare costs. Moreover, the pressure on the healthcare system can be reduced.

There is a growing interest in developing compact, portable ultrasound systems for point-of-care diagnostics and wearable health monitoring. [2] [3] This thesis focuses on enabling ultrasound for wearable applications in an energy-efficient manner.

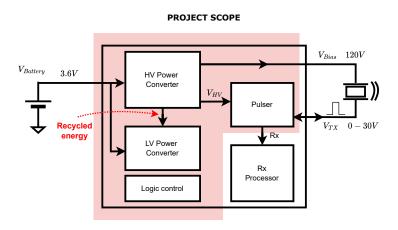

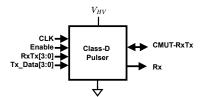

## 1.2. Background and Prior Art

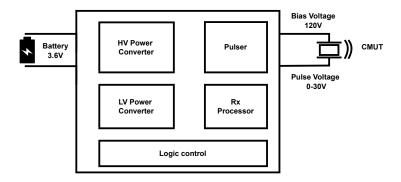

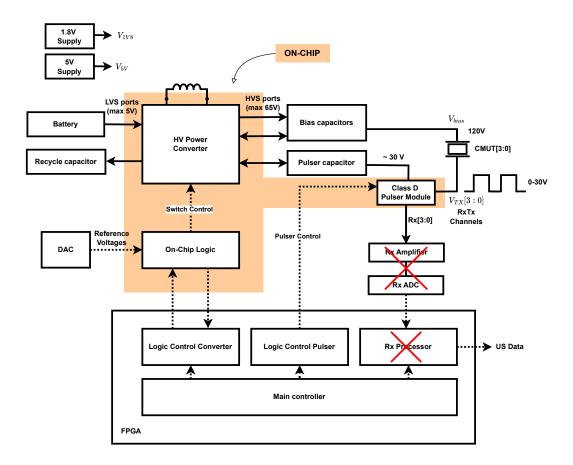

An Ultrasound Imaging System generates sound waves and listens for reflections from within a medium, such as the human body. By analyzing these reflections, it can construct data of internal structures and moving liquids or material. To illustrate the operation of such a system, a simplified overview of the system is shown in Figure 1.1. It can be divided in five sub-systems: first, an energy source is applied to supply to the entire system, typically a low-voltage battery in wearable applications. Power converters ensure that all subsystems operate under the correct electrical conditions. The core subsystems include the pulser system, receiver, ultrasound transducer (CMUT), and a logic unit that controls the system and optionally processes the received data.

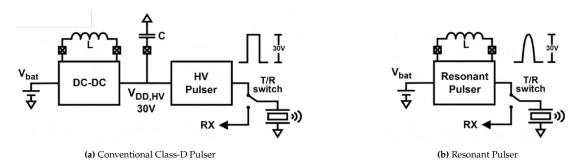

Recent work has shown a new technique for half-sine energy-efficient pulsing of capacitive micromachined ultrasound transducers (CMUT) called Resonant Pulsing (RP) [4]. This technique enables pulsing with energy recycling from the paracitic transducer capacitance during ultrasound pulsing using a single external inductor, potentially leading to significant pulse energy savings up to 76.8%. However, the RP architecture is still in its infancy and lacks many features compared to conventional pulsers. Consecutive work has demonstrated continuous-wave beamforming [5] and explored methods for generating pulse-trains [6], both of which are important for wearable applications: beamforming allows the ultrasound energy to be focused on a specific region of interest [1], while pulse-trains improve acoustic pressure and enable coded excitation techniques that can enhance the signal-to-noise ratio (SNR) up to 24.8dB [1, 7, 8]. Such performance gains cannot be achieved to the same extent on the receiving side, or would otherwise entail a significant energy cost, making them particularly attractive for wearable devices. Improvements in SNR are especially important since recent work in ultrasound

1.3. CMUT-Transducer 3

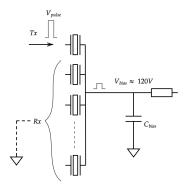

Figure 1.1: Simplified US Transceiver System

systems has shown that the low-noise amplifier (LNA) at the receiver front-end dominates the overall system power consumption, typically operating in the milliWatt range [9, 10]. Nonetheless, studies on resonant pulsers show that the technique requires complex trimming and calibration to function reliably, and its functionality remains restricted by the reliance on a single inductor—although minimizing external components is an advantage for wearables in terms of cost and area efficiency. Moreover, CMUT devices require high-voltage biasing, which incurs additional energy losses and is not addressed in these studies.

### 1.3. CMUT-Transducer

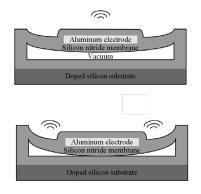

**Figure 1.2:** CMUT Device Illustration

Figure 1.2 illustrates a CMUT device. CMUTs consist of a membrane suspended over a cavity, forming a capacitor. By applying a high-voltage bias, the CMUT can be set in collapse mode, which enhances its sensitivity and bandwidth, and also results in a higher acoustic output [11, 12]. These are important advantages for achieving higher signal-to-noise ratios and improving energy efficiency in wearables. However, generating this high DC-bias voltage in a low-voltage environment remains both challenging and energy expensive. When combined with the limitations of resonant pulsing, this raises the question of whether the resonant pulser technique is currently the right path forward for ultrasound wearable devices.

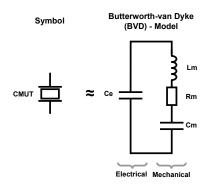

Figure 1.3 shows the Butterworth-van Dyke (BVD) model for the CMUT. This model consists of four elements arranged in two parallel branches and describes both the mechanical and electrical dynamics of the transducer [13]. Here,  $R_m$  captures the mechanical dissipation and is directly linked to the energy transfered into the ultrasound pressure waves. The static capacitance  $C_e$  accounts for the parasitic electrical capacitance of the CMUT electrodes. The static capacitance  $C_e$  accounts for the electrical parasitic capacitance of the CMUT device. This branch dominates the capacitive  $CV^2$  losses, and is therefore often used to characterize the electrical energy losses in the device.

1.3. CMUT-Transducer

Figure 1.3: CMUT Symbol and equivalent BVD Model

Figure 1.4: CMUT element Coupling

In Figure 1.4 a CMUT device is illustrated existing of an array of CMUT elements. Each element can be pulsed independently, but they all share a common biasing node connected to a single biasing capacitor  $C_{bias}$ . When considering the size of the biasing capacitor, it is important to note if all elements of the array are connected on the same biasing node as illustrated.

Depending on the ratio between the biasing capacitance and the transducer capacitance, multiple elements may be charged together.

As an example, consider an array with 64 elements. If one element is excited, the remaining 63 elements are still connected to the common bias node through their transducer capacitances. In this case, the bias capacitor  $C_{\text{bias}}$  is effectively in parallel with the sum of the other 63 transducer capacitances.

The electrical pulse amplitude that appears across the idle elements is determined by the capacitive divider ratio as given in equation 1.1:

$$V_{\text{pulse-coupling}} = V_{\text{tx}} \cdot \frac{C_{\text{tx}}}{C_{\text{bias}} + (N-1)C_{\text{tx}}} [V]$$

(1.1)

where  $V_{tx}$  is the applied transmit pulse on the active element,  $C_{tx}$  is the capacitance of a single transducer cell,  $C_{bias}$  is the bias capacitor, and N is the total number of elements (e.g., N = 64).

Figure 1.5 illustrates the power dissipated in the transducer elements due to this coupling effect. It shows unwanted transmission by the other elements which causes an extra parasitic plane wave during the pulse acquisition. This effect can lead to reduced signal integrity.

Figure 1.5: CMUT Coupling between elements

1.4. Power Converter 5

### 1.4. Power Converter

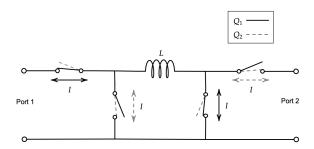

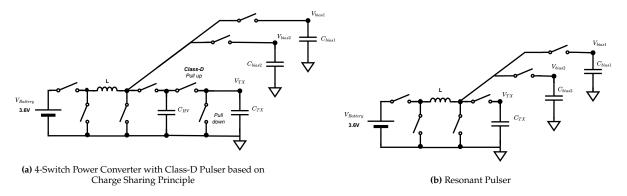

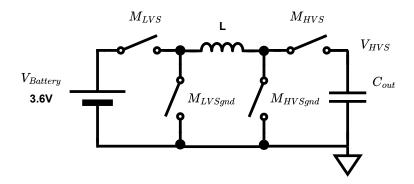

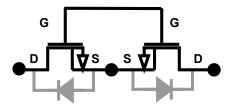

Given that we still aim to use a single inductor, it becomes relevant to investigate whether it is better to continue with the resonant pulser architecture, where the inductor is fixed by the resonance frequency, or to switch to a conventional class-D pulser combined with a buck-boost converter and an optimized inductor. Both architectures consist of a 4-switch topology as shown in Figure 1.6, which are comparable topologies used in buck-boost converters.

Figure 1.6: 4-Switch Topology

As illustrated with two operating modes, the topology enables power conversion between two ports charging and discharging the inductors magnetic field while redirecting the inductor current to either the input or output port. From this perspective, the resonant pulser can be seen as a special case of the 4-switch topology, where the switches are controlled to create a specific resonance frequency. Combining these two functions in a single topology is an interesting approach to explore, since it could potentially lead to energy recycling from capacitive output loads while also enabling the generation of a high-voltage bias. It is conceivable that this could be an opportunity for wearable applications, given the expectation that for specific applications the intensity of measurements will be lower, while the daily frequency will be higher. Otherwise, the energy required to build up the bias voltage would be lost multiple times a day, which would reduce the system's efficiency.

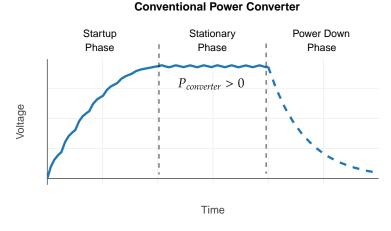

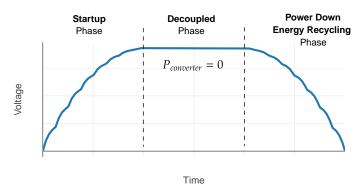

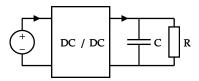

However, when comparing the operation of a conventional buck–boost converter, an important distinction becomes apparent. In theory, a buck–boost converter operates into a resistive load and continuously delivers an average power to maintain the output voltage. To reduce ripple, an output capacitor is typically added, as illustrated in converter start-up waveforms where the output capacitor is charged and the output voltage is regulated. This concept is illustrated in Figure 1.7.

Figure 1.7: Operational illustration of a conventional buck-boost converter.

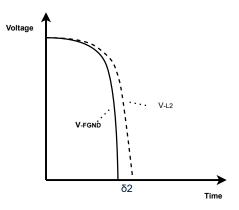

In contrast, as illustrated in Figure 1.8, the US power converter is only required for charging the capacitive loads. While charging this load, the converter only operates during the 'start-up phase' of the

1.4. Power Converter 6

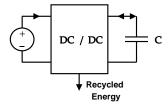

conventional buck-boost converter. After charging, the output can be fully decoupled and the inductor can be used for other tasks, such as pulsing or charging other capacitors. Decoupling the output has the added benefit of preventing the output from system noise or other disturbances induced by the converter. Afterwards, even full discharge of the bias capacitor back through the converter would be possible, enabling energy recycling.

### **Proposed US Power Converter**

Figure 1.8: Operational illustration of the proposed converter.

Comparing the operating phases, the proposed converter would never operate in an equivalent steady-state regime whereon buck-boost converters are optimized. This makes this ultrasound power-converter system unique in its operation and places it in an unexplored area of power-converter research. Unlike a buck-boost converter, its objective and operating point are fundamentally different. To summarize, the difference between a conventional buck-boost converter and the proposed converter is shown in figures 1.9 and 1.10. The arrows indicate the energy flow during operation.

**Figure 1.9:** Conventional buck-boost converter: simplified diagram.

Figure 1.10: Proposed converter: simplified diagram.

The proposed converter is able, when using multiple output switches, to charge multiple capacitive loads. This could be used to charge the bias capacitor and to pulse the transducer. When considering the energy efficiency of the proposed converter, it is important to note that the energy required to charge the bias capacitor is significantly higher than that needed for a single pulse on the transducer. Assuming that the biasing capacitor ( $C_{bias}$ ) is 50 times larger than the transducer capacitance ( $C_{tx}$ ), we can compare the required energy for a 30V pulse on  $C_{tx}$  with the energy needed to charge  $C_{bias}$  to 120V, as shown in the following equation:

$$E_{c,\text{bias}} = \frac{1}{2}C_{\text{bias}}V_{\text{bias}}^{2} [J] \qquad = \frac{1}{2} \cdot 50C_{\text{tx}} \cdot 120^{2} [J] = 360000 C_{\text{tx}} [J] E_{c,\text{tx}} = \frac{1}{2}C_{\text{tx}}V_{\text{tx}}^{2} [J] \qquad = \frac{1}{2}C_{\text{tx}} \cdot 30^{2} [J] \qquad = 450 C_{\text{tx}} [J]$$

$\Rightarrow E_{c,\text{bias}} = 800 E_{c,\text{tx}} [J]$  (1.2)

This means that the energy required to charge the bias capacitor is approximately 800 times larger than that needed for a single pulse on the transducer. Because the inductor is fixed in the resonant pulser, it is not possible to optimize it for buck-boost operation. This can make a significant difference in the efficiency of the converter. From this perspective, it is the question whether the resonant pulser technique is still the right path forward, or if a conventional power converter in combination with a class-D pulser supplied by a high-voltage capacitor would be more energy efficient.

1.5. Problem Statement 7

### 1.5. Problem Statement

The main question addressed in this thesis is the development of an energy-efficient ultrasound system suitable for wearable applications. For a wearable it is important that the system has minimal off-chip components and it must be energy-efficient. The resonant pulser technique is efficient in generating high-voltage pulses but requires complex calibration, or lacks features which improves imaging performance, such as beamforming and pulse-trains. Conventional class-D pulsers can provide these features, but have full  $CV^2$  losses. Additionally, the efficient generation and management of high-voltage biasing for CMUTs from low-voltage supplies remains a challenge. Because the energy required to build up the bias voltage is significantly higher than that needed for a single pulse on the transducer, the question arises if it is not more efficient to recycle the bias energy, instead of pulsing energy.

The operating region of the proposed converter is fundamentally different from conventional converters, which opens up a new field of research. Combined with the need for energy recycling, this makes it crucial to explore the proposed converter architecture and its potential for wearable ultrasound systems. More generally, the central question is whether a deeper understanding of the converter load and its behavior can be used to optimize the architecture towards higher energy efficiency, and ultimately energy recycling, particularly for wearable US applications.

### 1.6. Research Objectives and Approach

The objective of this thesis is to investigate and develop a power converter and pulser architecture that enables energy-efficient ultrasound operation in wearable devices. The approach includes:

- Studying and comparing different converter and pulser topologies for their suitability in wearables.

- Designing and implementing a prototype based on the most promising architecture.

- Evaluating the performance through circuit-level simulations and comparing the results to the requirements for wearable ultrasound systems.

### 1.7. Design Scope

This section outlines the scope and limitations of the design work presented in this thesis. The focus is on the conceptualization, prototyping, and simulation of the power converter and pulser architecture for wearable ultrasound applications.

### Design

- The design focuses on application-specific ultrasound (US) wearable devices.

- Example in healthcare: a US skin-patch device capable of measuring bladder volume.

- The design must demonstrate improvement or introduce a novel technique.

- Use of off-chip components must be minimized.

- The overall volume and area of the device must be acceptable for wearable applications.

- The focus should be on demonstrating new methods or functionalities in the new architecture; therefore, limitations depending on available technologies or devices will not be a show-stopper. However, it must be functionally demonstrated that the entire system can work.

### **Technology**

- The design must be implementable with the technologies available for this project:

- TSMC 180nm BCD Gen 2 Technology

- \* Given Design Limitations

- · Maximum gate width: 10.000μm

- \* Technology Limitations

- · Voltage limited to maximum of 65 V

- Xiver Collapse mode CMUT Transducer Types:

1.7. Design Scope 8

- \* CM5: f = 2.6 MHz,  $C_e = 120$  pF \* CM8: f = 5 MHz,  $C_e = 80$  pF \* CM12: f = 8 MHz,  $C_e = 20$  pF

- \* Xiver CM5 transducer has been selected based on the following considerations:

- · (+): Lowest operation frequency, best performing penetration depth.

- · (-/+): high capacitance, this will lead to higher energy losses which makes innovation in energy recycling methods more important.

- · (–): Lowest operation frequency, lower resolution. Assuming US wearables would be application specific so data efficient, this should not be a problem. In the meantime, lower frequency means lower data-rate, which is also an advantage for wearables.

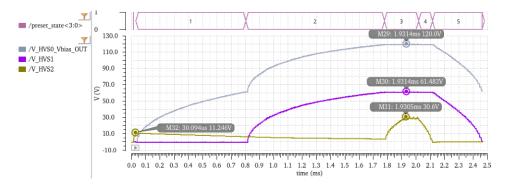

### **Power Converter**

- Must enable to operate the system on a low-power energy source, such as a single lithium cell with a voltage of 3.6 V.

- Must provide output voltages in ranges from 0 to 120 V for CMUT biasing .

- Must provide output voltages in ranges from 0 to 30 V for pulser operation.

- Must enable energy recycling between high- and low-voltage power stages.

- Must be able to supply recycled energy to other parts of the system. Either to improve efficiency

or to eliminate limitations of batteries such as non-rechargeability or complicated charging and

discharging specifications.

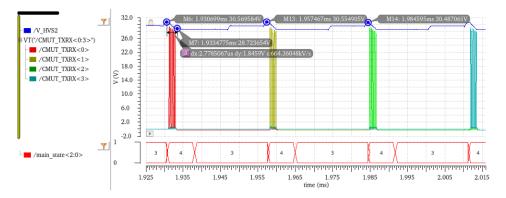

### **Ultrasound Pulse Acquisition**

- Transmission/Reception method: Synthetic Aperture (SA).

- Transmission: single-channel.

- Reception: multi-channel.

- Ability to switch between Tx and Rx modes.

- Transceiver capabilities:

- Transmission up to 64 channels (expected usage: 4 channels).

- Tx pulse-train functionality (expected length: 5 pulses).

### **Xiver Collapse mode CM5 Transducer**

The Xiver CM5 is a Collapse mode CMUT transducer that consists of a lin64 elements (channels), with 33 CMUT drums per element. For a bias voltage of 120 V, the corresponding transducer parameters per element are summarized in Table 1.1.

| Parameter                        | Value                        |

|----------------------------------|------------------------------|

| Bias Voltage ( $V_{\rm bias}$ )  | 120 V                        |

| Electrical Capacitance ( $C_e$ ) | 118.8 pF                     |

| Mechanical Capacitance ( $C_m$ ) | 56.1 pF                      |

| Mechanical Inductance $(L_m)$    | 68 μH                        |

| Mechanical Resistance ( $R_m$ )  | 1.6 kΩ                       |

| Resonance Frequency              | 2.58 MHz                     |

| Drums per Element                | 33                           |

| Number of Elements               | 64                           |

| Active Area                      | $12 \times 21 \mathrm{mm}^2$ |

| Pitch                            | $315 \mu\mathrm{m}$          |

Table 1.1: Xiver CM5 CMUT Parameters

### Other considerations

• Operating temperature range: 20–40 °C (body temperature range).

1.8. Thesis Outline

### 1.8. Thesis Outline

The report is structured as follows:

### • Chapter 2: Architecture Study

This chapter reviews the requirements and explores possible system architectures for energy-efficient ultrasound in wearable applications. It compares different converter and pulser topologies, and motivates the selection of the most promising approach for further development.

### • Chapter 3: Prototype Design

Here, the chosen architecture is translated into full system implementation with detailed circuit design. The chapter discusses the design choices, implementation challenges, and integration of the power converter and pulser within the constraints of the selected technology.

### • Chapter 4: Circuit-Level Simulations

This chapter presents simulation results of the designed circuits. It evaluates the performance, efficiency, and functionality of the prototype under various operating conditions, and compares the results to the initial requirements.

### • Chapter 5: Conclusion and Future Work

The final chapter summarizes the main findings, discusses the limitations of the current work, and suggests directions for future research and improvements.

# Architecture Study

### 2.1. Prior Art

Conventional class-D ultrasound (US) pulsers as described in [14] are highly developed and offer a wide range of functionalities, including advanced features such as beamforming and pulse-train generation. However, a recently developed technique called Resonant Pulsing (RP) [4] enables energy recycling during ultrasound pulsing in capacitive micromachined US transducers (CMUT). Despite its potential for energy savings, this technology is still in its infancy and lacks many features compared to conventional pulsers. Additionally, CMUT devices require high voltage biasing, which can entail significant energy losses and is not yet included in the RP design.

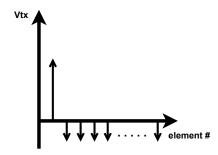

Figure 2.1: Introduction to Resonant and Conventional Class-D Pulsers

Theoretically, by adding a single switch to the output of the RP design, it should be possible to use the same architecture to charge and discharge the biasing capacitance while maintaining energy recycling capabilities. However, a significant drawback exists: since the inductor size is determined by the resonance frequency relative to the CMUT, charging and discharging this biasing capacitance may not be efficient. This is particularly problematic considering that the energy stored in the bias capacitance is estimated to be thousands times larger than the energy needed for a single pulse in the CMUT.

Given these limitations of the RP design, it raises the question whether resonant pulsing is the right path forward. Investigating from a wearable system perspective, it remains unclear whether the energy savings from pulse recycling outweigh the limitations of the RP architecture. Additionally, alternative energy recycling techniques applied elsewhere in the system may address larger energy losses.

For these reasons, a new architecture has been composed. Like the resonant pulser, it incorporates a 4-switch configuration with a single inductor. However, instead of directly driving CMUTs as the load, it features a multi-output design to charge and discharge DC capacitors for biasing and DC voltages. This allows a conventional pulser to be used, powered through charge-sharing principles from the DC capacitance. Under this configuration, it becomes possible to efficiently select the inductor, potentially yielding energy gains. Furthermore, well-developed techniques become available through the use of the

2.2. Problem Statement

class-D pulser, such as pulse trains that improve signal-to-noise ratio (SNR) and can therefore provide energy savings in pulse acquisition. A drawback of this architecture is that a conventional class-D pulser introduces full  $CV^2$  energy losses, which are largely recycled in the resonant pulser.

### 2.2. Problem Statement

This simulation study aims to determine which architecture, resonant pulsing or the new multi-output converter with conventional class-D pulser, is more energy-efficient for wearable ultrasound applications. The comparison will focus on several key aspects:

- Energy efficiency analysis: Quantifying the total energy consumption per ultrasound acquisition, including both pulse generation and biasing energy requirements.

- **Design optimization**: Identifying the optimal design variables for each architecture, such as inductor sizing or switch sizing.

- Architecture trade-offs: Evaluating when each architecture performs better under different operating conditions and system .specifications.

The primary metric for comparison will be the net energy consumption, taking into account both the charged, pulsed and recycled energy losses inherent to each architecture. However, comparing both architectures without selecting (reasonable) optimal design variables, will provide a unfair comparison. That is why this simulation study will also focus on identifying the optimal design variables for each architecture, such as inductor sizing or switch sizing. After determining the optimal architecture, a more detailed simulation is performed to identify design-keys and architecture performances usefull for prototyping.

### 2.3. Method

This chapter outlines the approach taken to compare the energy efficiency of the two architectures. First, an analytical approach is used to identify both systems in terms of energy efficiency, associated design parameters and their boundaries. Also identified design risks or conflicts will be discussed. Consequently, this section will conclude the main considerations and motivation for choosing a simulation-based approach. At the end, the simulation models are introduced whereafter the simulation setup for each architecture will be described.

### 2.3.1. Fundamental Analysis

### **Architectures**

As introduced, two scenarios are considered: (1) using the resonant pulser architecture for charging the biasing capacitor with fixed inductor size, which means efficient pulsing up to 76.8% energy loss reduction [4], but at cost of inefficient biasing. Or (2) using a conventional DC/DC converter with class-D pulser architecture, which has full capacitive pulse energy losses but offers higher efficiency for both charging and recycling energy to biasing capacitor and the DC capacitor used for pulsing.

Since pulsing energy losses have already been well described in literature, this chapter focuses primarily on the energy flow related to DC capacitors using the 4-switch configuration. In general, the energy stored in a capacitor is given by the equation 2.1, where C is the capacitance and V is the voltage across the capacitor. The energy stored in a inductor is given by the equation 2.2, where L is the inductance and I is the current through the inductor.

$$E_C = \frac{1}{2}CV^2 \quad [15] \tag{2.1}$$

$$E_L = \frac{1}{2}LI^2 \quad [15] \tag{2.2}$$

The assumption is made that to charge a capacitor to a certain energy level, for a chosen energy stored in L minus the associated energy losses, we need  $N_c$  charge-discharge cycles for L, as shown in equation 2.3. Combining these three equations results in equation 2.4, which states that, for a fixed output capacitance

$C_{out}$  and output voltage  $V_{out}$ , the stored energy at the load capacitor depends on the number of cycles  $N_c$ , the inductor size and peak current  $I_{pk}$  through the inductor.

$$N_c(E_L - E_{loss}) = E_C (2.3)$$

$$N_c \cdot (\frac{1}{2}LI_{pk}^2 - E_{loss}) = \frac{1}{2}C_{load}V_{load}^2$$

(2.4)

Charging the inductor from an initial state of zero energy, the peak current is given by formula 2.5. Where V is the voltage across the inductor, L is the inductance and T is the time needed to charge or discharge the inductor. In reality the discharging step can be described by a second order differential equation between the inductor and capacitor.

Assuming the energy losses are mainly induced by resistive and gate switching losses, the energy losses are approximated by equation 2.6. Other losses to mention are losses which occurs in surrounding systems or layout by resistive connections and parasitic capacitances, but are left for now assuming they are less dominant.

$$|\Delta I| = |I_{pk}| = \frac{V_{source}}{L} T_{charge} \approx \frac{V_{load}}{L} T_{discharge}$$

[16]

$$E_{loss} \approx E_R + E_{gsw} \tag{2.6}$$

The resistive losses are induced by the current through the on-resistances of the switches and inductor. While this resistances are in each operation of the system always in series, the equivalent series resistance  $R_s$  can be obtained. Obviously as illustrated in equation 2.5 and 2.7, the losses becomes higher at higher currents or resistances. Additionally,  $V_{load}$  will differ per cycle, which indicates varying losses over time when energy transfers between L and C.

$$E_{loss-R} = \int_{t_0}^{t_0 + T_{charge}} R_{s1} I(t)^2 dt + \int_{T_{charge}}^{T_{charge} + T_{discharge}} R_{s2} I(t)^2 dt \quad [15]$$

(2.7)

The next sub-section will briefly outline the individual components.

### **MOSFET Device**

Energy losses in MOSFET devices are typically caused by resistive and switching losses. The switching losses are mainly caused by gate driver stages and  $CV^2$  energy losses used for driving the gate capacitance per switching event of the MOSFET device. The optimal number of stages to drive the switch gate is related to the inter- and outer-stage fan-out f and F as shown in equation 2.8 and 2.9.

$$N = \log_f(F) \quad [17] \tag{2.8}$$

$$F = \frac{C_{gg}}{C_{in}} \quad [17] \tag{2.9}$$

The inter-stage fan-out f is an adjustable variable which is a trade-off between speed and power consumption. Typically values around 4 are close to optimal [17], which should be a good starting point. When the number of stages is defined and round to an integer, the total dynamic power dissipation in driver and gate capacitance can be approximated by equation 2.10. With  $C_{gg}$  being the total input capacitance at the gate of the MOSFET, and  $V_g$  the gate drive voltage and N the number of driver stages. This is the energy loss per switching event of the MOSFET.

$$E_{driver-gate} = \sum_{k=0}^{N} \frac{1}{4^{(N-k)}} \cdot C_{gg} V_g^2 \quad [17]$$

(2.10)

Resistive losses are caused by the on-resistance  $R_{on}$  of the MOSFET device. The resistive losses are given by equation 2.11, where  $R_{on}$  is the on-resistance and I the current through the MOSFET device over time.

$$E_{loss-Ron} = \int_{t_0}^{t_1} R_{on} I(t)^2 dt$$

(2.11)

To conclude, the MOSFET switch devices should have a minimized  $V_g$ ,  $R_{on}$  or  $C_{gg}$ . This conflicts with the physical characteristics of the MOSFET as explained in [17, 18]. Investigating the on-resistance and gate capacitance, they have conflicting interests in the physical dimensions of the device as shown in equation 2.12 and 2.13. In this formulas are  $C_u$  and  $R_u$  the capacity and resistance per unity area. Minimal device lengths are in favour of both minimal resistance and capacities. However, larger device widths results in less on-resitance but larger gate (and parasitic) capacitances and vice-versa. So sizing the device is an optimization problem between  $E_{gsw}$ ,  $E_{loss-Ron}$ . Then, for most MOSFET devices used as switch, the gate drive voltage is typically recommended or set dependent of process technology. This means that if the choice is possible, devices with lowest possible gate voltages should be considered.

$$C_{gg} \approx W \cdot L \cdot C_u \quad [17] \tag{2.12}$$

$$R_{on} \approx \frac{L}{W} \cdot R_u \quad [17] \tag{2.13}$$

### **Inductor**

The inductor is a critical component in both architectures, as it stores and transfers energy between the source and the load. Although in the first approximations the inductor is assumed to be ideal or with fixed resistances, it is important to consider the limitations, parasitics and design variables of a real inductor to understand or prevent problems in later stages of the design.

Assuming a solenoid inductor, the inductance is given by equation 2.14. Where N is the number of turns, A is the cross-sectional area, and l is the length of the inductor. The inductance can be maximized by increasing both the number of turns, the cross-sectional area or the length of the solenoid. Increasing the number of turns is at costs of the wire resistance as showed in equation 2.15, where  $\rho$  is the resistivity of the wire material, l is the length of the wire, and  $A_w$  is the cross-sectional area of the wire.

$$L = \frac{\mu_0 N^2 A}{l_s}$$

[19] (2.14)

$$R_L = \rho \frac{l_{wire}}{A_{wire}}$$

[19]

In favour of both higher inductance and lower wire resistance, larger areas are preferred. However, larger areas also increase the size of the inductor, which is a critical limitation in wearable applications. An engaging effect is increase of parasitic capacitances between between the wires, which can limit the operating frequency or the self-resonance frequency of the inductor it self. Additionally favour for inductance and resistance is the use of materials with low resistances or high (core) permeabilities. This could also benefit in lowering the total area or volume of the inductor, but this will depend on availability or budget.

A general approach to indicate the quality of an inductor is the Q-factor 2.16. This is a frequency dependent ratio between the inductance and the DC wire resistance of the inductor. A higher Q-factor indicates a better quality inductor with lower losses at a certain frequency. Note that higher Q-factors will conflict with the physical size of the inductor. When choosing a real inductor, the Q-factor could be maximized for the frequency of operation and maximum allowed physical size of the inductor.

$$Q = 2\pi f \cdot \frac{L}{R_I} \quad [15][19] \tag{2.16}$$

The total energy stored in the inductor is given, as mentioned before in equation 2.14, in the following equation:

$$E_L = \frac{1}{2}LI^2 \quad [15] \tag{2.17}$$

On-Chip wires are typically small, which results in low inductance values and high resistances. The expectation is, as indicated above, this leads to low Q-factors, making them inefficient for energy storage and transfer. This is why off-chip inductors are preferred.

### Capacitor

The capacitor is a critical component in both architectures, as it stores and releases energy between the source and the load. Although in first-order approximations the capacitor is assumed to be ideal, it is important to consider the limitations, parasitics and design variables of a real capacitor to understand or prevent problems in later stages of the design.

The amount of charge that can be stored on a capacitor is directly proportional to both its capacitance and the voltage applied across it. This relationship is expressed as

$$Q = C \cdot V \quad [15] \tag{2.18}$$

where Q is the charge in coulombs, C is the capacitance in farads, and V is the voltage in volts. A larger capacitance or higher voltage allows more charge to be stored. Assuming a parallel-plate capacitor, the capacitance is given by equation 2.19. Where  $\varepsilon$  is the permittivity of the dielectric material, A is the plate area, and d is the separation between the plates. The capacitance can be maximized by increasing the plate area or decreasing the distance between the plates. However, reducing the plate spacing is limited by breakdown voltage of the material.

$$C = \epsilon \frac{A}{d} \quad [15] \tag{2.19}$$

In favour of both higher capacitance and higher voltage ratings, larger plate areas are preferred. However, larger areas also increase the physical size of the capacitor, which is a critical limitation or very costly for on-chip applications.

From the extracted values of the TSMC 180 nm PDK, the capacitance density for a 'CFMOM' type capacitor is found to be approximately  $1.30\,\mathrm{fF}/\mu\mathrm{m}^2$ . This implies that to realize a capacitance in the nanofarad range, an area of about  $1000\times1000\,\mu\mathrm{m}^2$  (i.e.  $1\,\mathrm{mm}^2$ ) would be required for 1 nF. Such an area is technically feasible but very large for on-chip integration in 180 nm technology. Therefore, in practical circuit design, a trade-off must be made between placing capacitors on-chip, where integration and parasitic reduction are beneficial, or off-chip, where much higher capacitance values can be achieved without significant area penalties.

### 2.3.2. Simulation Models

This section describes the simplified models used for both architectures, highlighting their similarities and key differences in terms of circuit topology and operation. The models were specifically developed to allow implementation and simulation in MATLAB, enabling flexible analysis and efficient exploration of a large number of parameters. Since the architectures can be simulated in a step-by-step manner, they can be broken down into simple subsystems. By deriving the corresponding state-space models for each subsystem and sequentially combining them while sharing their state variables, the complete cycle of both architectures can be simulated in a structured and straightforward way. This approach allows for detailed investigation of various parameters and components, and enables analysis of their impact on the energy efficiency of both architectures.

The following section outlines practical consideration and explains the structure of the implemented models. After introducing the models, the simulation setup for both architectures will be described. Finally, it will be detailed how the different operating cycles of both systems are simulated using these models.

### **Practical Considerations and Implemented Architecture Models**

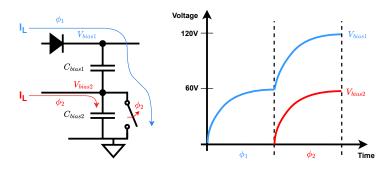

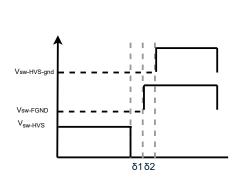

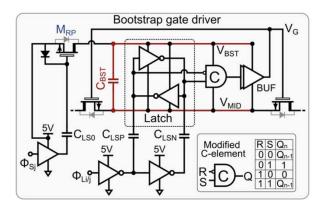

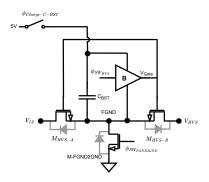

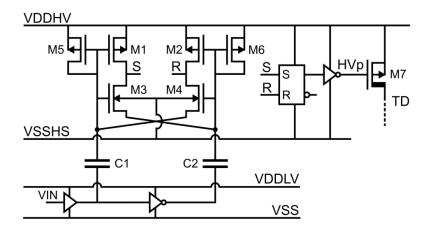

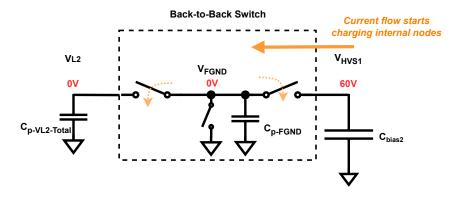

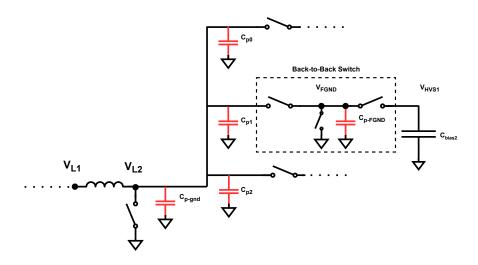

In TSMC 180nm BCD Gen2 technology, the maximum safe operating voltage is limited to 65 V. Exceeding this value risks permanent damage to the substrate. However, the CMUT requires a bias voltage of up to 120 V, which is well beyond the intrinsic voltage tolerance of the technology. A pragmatic solution is chosen that allows the desired bias voltage to be reached while remaining fully compatible with the available technology and project objectives. A floating capacitor configuration in combination with a diode can be employed for isolation, as shown in Figure 2.2. This configuration makes use of two capacitors connected in series. The charging process can be compared to a two-stage rocket. During the first stage, indicated by  $\phi_1$  in red, the upper capacitor is charged from the inductor current while the switch is closed. Subsequently, the switch opens, and the lower capacitor is charged, causing the voltage of the upper capacitor to float along. This process finally results in a combined voltage of 120 V across the series connection after both capacitors are charged to 60 V.

Figure 2.2: Floating capacitor configuration for generating a 120 V bias from a 65 V-limited technology

In order to protect the on-chip components from direct exposure to voltages higher than 65 V, the diode is placed between the high-voltage node of the floating capacitor stage and the system output. This provides isolation and ensures that the 120 V bias can be safely achieved with the available technology. However, this approach also comes with trade-offs. The diode prevents current from flowing back into the system, which is an advantage in terms of safety and reliability, but it also means that the stored energy in the upper capacitor is effectively trapped and cannot be recovered. Additional drawbacks are the voltage drop with resistive losses across the diode and the requirement for an extra output channel to bias the CMUT.

Furthermore, the use of two capacitors in series introduces an additional consideration regarding the effective capacitance. In general, the equivalent capacitance of capacitors connected in series is given by

$$\frac{1}{C_{\text{eq}}} = \sum_{i=1}^{n} \frac{1}{C_i}.$$

(2.20)

For the case of two identical capacitors with capacitance C, this reduces to

$$C_{\text{eq}} = \frac{C}{2}.\tag{2.21}$$

This reduction in capacitance is not a fundamental limitation, but must be taken into account during the design phase. Because this configuration addresses the practical limitations of the TSMC technology rather than a fundamental constraint of the proposed architecture, these drawbacks are not considered an obstacle for this work. With this approach, the primary objective can still be achieved, namely to demonstrate the feasibility of the architecture. In future implementations, when CMUT devices are innovated with lower biasing voltages or technology processes with higher voltage tolerances may be available, these practical workarounds will no longer be required.

That is why in this project this practical solution will be used, which means that a power converter capable of charging two bias capacitors is required. As illustrated in Figure 2.3, both architectures consist of a 4-switch power converter with a single inductor used to drive capacitive loads. The schematic to charge- and discharge the biasing capacitor are similar. The main difference lies in inductor optimization and the pulser design: the conventional class-D pulser uses a charge-sharing principle, whereas the resonant pulser drives the transducer at its resonant frequency using the same 4-switch configuration.

Figure 2.3: Simplified Schematics of Architectures

### **MOSFET Switch Characteristics**

This section describes the used switching models and key characteristics of the MOSFET devices. During switching and conduction, power losses occur in the switches, as previously explained in Section 2.3.1. These losses are determined by both type and size of the selected MOSFET. Based on these input variables, relevant characteristics of each MOSFET including driver losses are calculated at the start of the simulation.

During simulation are switching losses calculated by counting the number of switching events. In the meantime, the on-resistance of the switches is included in the equivalent series resistance. This combined resistance is incorporated into the transient state-space models described in the following sections.

All device parameters have been extracted from the TSMC 180nm BCD-Gen2 process design kit (PDK) using Cadence simulation tools. Table 2.1 summarizes the most relevant unity parameters for the selected devices, including on-resistance and various parasitic capacitances.

It is important to note that devices rated for higher voltages inherently exhibit higher on-resistances and larger gate capacitances. For example, the 65V devices show significantly higher  $R_{\rm on-u}$  and  $C_{\rm gg-u}$  values compared to the 5V low-Ron devices. These characteristics directly impact the conduction and switching losses in the converter and must be carefully considered during the design and optimization process.

The table also includes the total drain and source capacitances ( $C_{\rm dd-u}$  and  $C_{\rm ss-u}$ ), as well as the gate length ( $L_{\rm gate}$ ) for each device. While these parameters are not directly used for accurate modeling of the switching behavior, they are important for validating simulation results afterwards.

All values in Table 2.1 are obtained from the PDK device models and reflect the typical performance in simulation. These characteristics form the basis for the subsequent selection and sizing of switches in both the low-voltage and high-voltage sections of the converter, which will be discussed in detail in the following sections.

It is important to note that the HV switches inherently exhibit higher on-resistances and capacitances. This is crucial for later analyses and validation of the simulations.

| Device Name              | Voltage<br>Rating [V] | $R_{\text{on-u}}$ $[\Omega \cdot \mu \mathbf{m}]$ | C <sub>gg-u</sub><br>[ <b>F/μm</b> ] | C <sub>dd-u</sub><br>[ <b>F/μm</b> ] | $C_{\rm ss-u}$ [ <b>F</b> / $\mu$ <b>m</b> ] | $L_{\rm gate}$ [ $\mu$ <b>m</b> ] |

|--------------------------|-----------------------|---------------------------------------------------|--------------------------------------|--------------------------------------|----------------------------------------------|-----------------------------------|

| nch_5_switch_low_ron_mac | 5                     | 1798                                              | $1.72 \times 10^{-15}$               | $9.04 \times 10^{-16}$               | $1.14 \times 10^{-15}$                       | 0.550                             |

| pch_5_switch_low_ron_mac | 5                     | 5131.5                                            | $1.42 \times 10^{-15}$               | $8.48 \times 10^{-16}$               | $1.05 \times 10^{-15}$                       | 0.470                             |

| nld65_g5b_mac            | 65                    | 11726                                             | $4.61 \times 10^{-15}$               | $2.52 \times 10^{-15}$               | $3.92 \times 10^{-15}$                       | 0.700                             |

| nld65_g5b_mac_BB         | 65                    | 23451                                             | $9.21 \times 10^{-15}$               | _                                    | _                                            | _                                 |

**Table 2.1:** Overview of unity parameters for MOSFET devices in 180nm BCD-Gen2 technology, including voltage ratings, drain and source capacitances. Values extracted from Cadence PDK simulations for indicated gate lengths.

### 2.3.3. Transient Models

### **Store Energy to Load Capacitor**

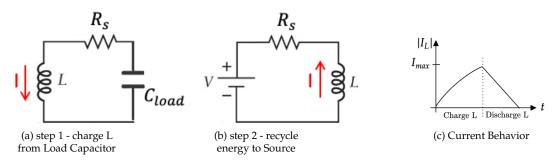

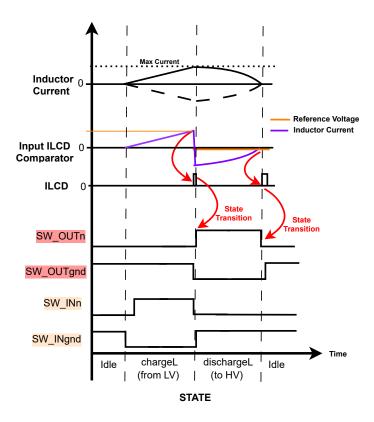

To charge a load capacitor, both architectures follow a similar process. Initially, the inductor is charged from the source until it reaches a maximum current, whereafter the inductor is switched to discharge its current or energy into the capacitive load. After all energy from the inductor is discharged, if current zero-crosses, the output switch is turned off and all energy is transferred to the load capacitor. The submodels used are illustrated with current behavior in Figure 2.4. These steps are repeated until the output voltage reaches the desired level. This model is used for charging the biasing capacitor in both architectures, as well as for charging the DC load capacitor in the class-D pulser architecture.

Figure 2.4: Sequential sub-models Charging Load Capacitor Cycle

### **Recycle Energy from Load Capacitor**

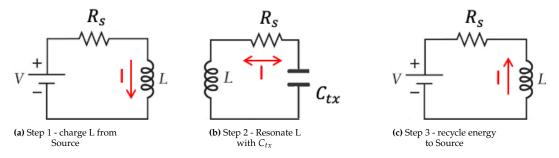

Discharging the load capacitor is similar, but the other way around. For this case, initially, the inductor gets charged with energy stored at the capacitive load, whereafter it is switched to the source to discharge its energy back. This process repeats itself until energy is transfered and nothing is left on the capacitor. It is measured when the output voltage crosses zero while charging the inductor from the load capacitor. This means that the end time of charging the inductor from the load capacitor is triggered by both maximum current and zero-crossing of the output voltage. This process is illustrated in Figure 2.5 and used for energy recycling.

Figure 2.5: Sequential sub-models Recycle Energy from Load Capacitor Cycle

### **Resonant Pulse Cycle**

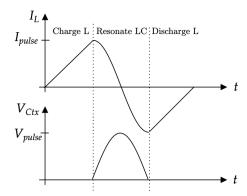

Merging previously mentioned models and leaving out switching off the load capacitor in between, it follows that charged energy on the load capacitor will flow back into the inductor. This mechanism is used for resonant pulsing the capacitive transducer. This can be modelled by a charging step for the inductor by pre-calibrated time or maximum current, whereafter the stored energy in the inductor wil resonate with the load capacitor. When the energy is fully bounced back to the inductor, the inductor is switched and the energy flows back to the source. The result is a half sine pulse at half time of the resonating frequency between L and C. The pre-calibrated time or maximum current is related to the pulse amplitude as explained in [4]. The sequential model with voltage and current graph are illustrated in Figure 2.6 and 2.7.

Figure 2.6: Sequential sub-models Resonant Pulse Cycle

Figure 2.7: Voltage and Current Behavior of Resonant Pulse Cycle

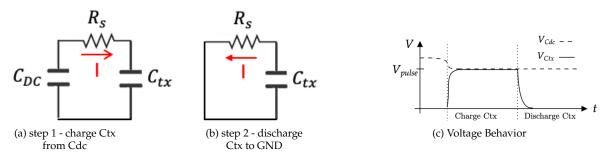

### **Class-D Pulse Cycle**

At the end, the model for class-D pulser based on charge sharing is presented. Before this model is used, the DC capacitor is charged as explained before. This model contains charge sharing principle between DC capacitor and transceiver, whereafter the pulse length the charge is resetted to ground. This sub-models and steps are illustrated in Figure 2.8.

Figure 2.8: Sequential sub-models Class-D Pulse Cycle

The voltage drop over the DC capacitor after each pulse can be calculated using the law of conservation of charge, as shown in equation 2.25. [15]

Assuming an initial voltage  $V_{dc-initial}$  on the DC capacitor, and zero voltage on the transducer capacitor, then the initial total charge over both capacitors is given by equation 2.22. After charge sharing, the total charge must be equal, and the new voltage can be calculated by equation 2.24. Combining these equations results in equation 2.25, which describes the voltage drop over the DC capacitor after each pulse.

The voltage drop over the DC capacitor after each pulse can be calculated using the law of conservation of charge, as shown in equation 2.25. [15]

Assuming an initial voltage  $V_{dc-initial}$  on the DC capacitor, and zero voltage on the transducer capacitor, the initial total charge over both capacitors is given by

$$Q_{\text{total}} = C_{\text{DC}} V_{dc-initial} + C_{\text{TX}} \cdot 0 = C_{\text{DC}} V_{dc-initial}$$

(2.22)

After charge sharing, the total charge must be equal, and the new voltage on both capacitors can be calculated by

$$Q_{\text{total}} = (C_{\text{DC}} + C_{\text{TX}})V_{\text{final}}$$

(2.23)

Solving for the final voltage gives:

$$V_{\text{final}} = \frac{C_{\text{DC}}}{C_{\text{DC}} + C_{\text{TX}}} V_{dc-initial}$$

(2.24)

Combining these equations results in the voltage drop over the DC capacitor after the first pulse is given by:

$$\Delta V_{\rm DC} = V_{dc-initial} - V_{\rm final} = \frac{C_{\rm TX}}{C_{\rm DC} + C_{\rm TX}} V_{dc-initial}$$

(2.25)

or stepwise for sequential pulses as used in pulse-trains:

$$\Delta V_{\rm DC}^{(n)} = \frac{C_{\rm TX}}{C_{\rm DC} + C_{\rm TX}} V_{\rm DC}^{(n-1)}$$

(2.26)

Assuming Cdc = 100xCtx and Vdc-initial = 30V, the voltage drops for the first pulses are approximately:

$$\Delta V_{\rm DC} \approx \frac{1}{1 + 100} \cdot 30 \approx 0.3 \,\mathrm{V} \tag{2.27}$$

Table 2.2 shows the voltage drop over the DC capacitor for different ratios between the DC capacitor and transducer capacitance when choosing an initial voltage of 30V. These values can be used to verify the simulation results.

**Table 2.2:** Voltage drop over the DC capacitor for 5 pulses ( $C_{DC} = 100 C_{TX}$ ,  $V_{dc\text{-initial}} = 30 \text{ V}$ )

| Pulse # | $V_{\rm DC,initial}$ [V] | $V_{\text{TX}} = V_{\text{DC, final}} [V]$ | $\Delta V$ [V] |

|---------|--------------------------|--------------------------------------------|----------------|

| 1       | 30.000                   | 29.703                                     | 0.297          |

| 2       | 29.703                   | 29.407                                     | 0.296          |

| 3       | 29.407                   | 29.113                                     | 0.294          |

| 4       | 29.113                   | 28.822                                     | 0.291          |

| 5       | 28.822                   | 28.532                                     | 0.290          |

### Setup Sub-Models per Architecture

By combining all described steps and sub-models, the complete operating cycle of both architectures can be simulated, as summarized in Table 2.3 and Table 2.4. Executing these steps in the correct sequence enables a transient simulation that accurately reproduces the behavior of both systems. This approach allows for easy simulation across a wide range of variables, and additional models can be incorporated or extended where needed. Since the models are implemented using simple state-space representations, they can be solved efficiently under predefined conditions or constrains. Moreover, the simulation provides detailed insight into each step of the operation, including when and where energy losses occur, allowing for a clear comparison of the energy efficiency of both systems.

| Step | Description                           | Finish Condition             |

|------|---------------------------------------|------------------------------|

| 1    | Store Energy to Biasing Capacitor1    | $V_{bias} > V_{target-bias}$ |

| 2    | Store Energy to Biasing Capacitor2    | $V_{bias} > V_{target-bias}$ |

| 3    | Store Energy to DC Capacitor          | $V_{dc} > V_{target-dc}$     |

| 4    | Class-D Pulser                        | Repeat N Pulses              |

| 5    | Recycle Energy from Biasing Capacitor | $V_{bias} \leq 0$            |

| 6    | Recycle Energy from DC Capacitor2     | $V_{hv} \leq 0$              |

Table 2.3: Steps for Class-D Pulser Architecture

| Step | Description                            | Finish Condition             |

|------|----------------------------------------|------------------------------|

| 1    | Store Energy to Biasing Capacitor1     | $V_{bias} > V_{target-bias}$ |

| 2    | Store Energy to Biasing Capacitor2     | $V_{bias} > V_{target-bias}$ |

| 2    | Resonant Pulse                         | Repeat N Pulses              |

| 3    | Recycle Energy from Biasing Capacitor2 | $V_{bias} \leq 0$            |

Table 2.4: Steps for Resonant Pulser Architecture

Note that in both configurations, the energy stored in the first bias capacitor cannot be recovered due to the presence of the diode as explained in section 2.3.2.

### 2.4. Architecture Simulations

This chapter presents a comprehensive simulation study of the power converter architectures and their key design variables. The following sections discuss the switch configuration and technology choices, the main simulation parameters, and the impact of inductor size, output capacitance, and output voltage on energy efficiency. Both the resonant and conventional pulser architectures are analyzed and compared, including detailed optimization of switch sizes and system currents. The results include break-even analyses, practical component selection, and a summary of the final configuration with detailed energy and timing breakdowns. Altogether, the results highlight the key trade-offs and design choices that determine power conversion efficiency in the next prototype of wearable ultrasound systems.

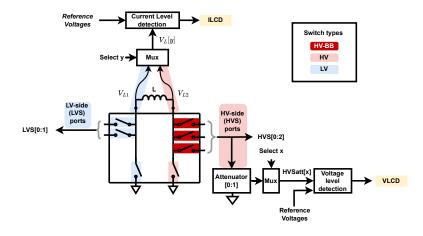

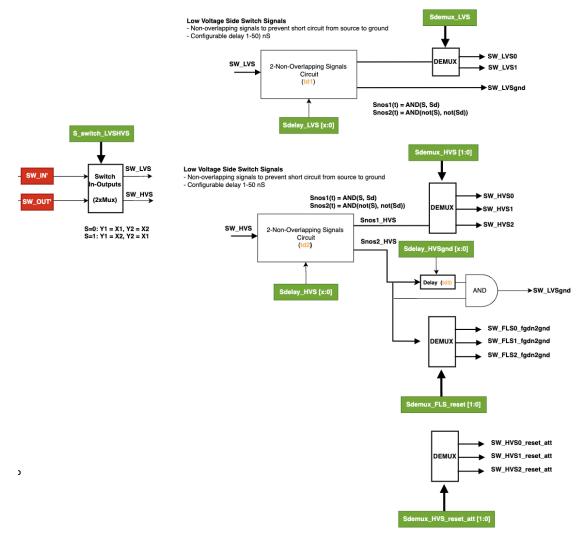

All simulations are performed using a basic four-switch topology as shown in the following figure. This schematic indicates the main voltages and component names. Naturally, the output names for the voltage and capacitor depends on the application, for example, when used for pulsing, the output voltage is called  $V_{tx}$  and the output capacitor  $C_{tx}$ , while for biasing, these are called  $V_{bias}$  and  $C_{bias}$  respectively.

Figure 2.9: Basic four-switch topology used for simulations of both architectures

### 2.5. Resonant Pulser versus Conventional Pulser

### 2.5.1. Bias Circuit 65V Simulations

This section describes the simulations performed to analyze the bias circuit. The focus is on how different parameters affect the performance of the power converter in charging and discharging the output capacitor. In this section are the following aspects investigated in advantage of energy efficiency:

- 1. The effect of inductor size

- 2. The influence of output capacitance

- 3. The impact of varying output voltage

The specific switch configuration used in the biasing power converter is summarized in Table 2.5. This table lists the device types selected for each switch position in the four-switch topology, based on the requirements for voltage rating and on-resistance as discussed above. The chosen configuration ensures reliable operation within the voltage limits of the technology, while minimizing conduction and switching losses. The use of a back-to-back device for the high-voltage output switch further improves isolation and prevents unwanted current paths during operation.

| Switch Name | Device Type              |

|-------------|--------------------------|

| LVSgnd      | nch_5_switch_low_ron_mac |

| LVS         | pch_5_switch_low_ron_mac |

| HVSgnd      | nld65_g5b_mac            |

| HVS         | nld65_g5b_mac_BB         |

Table 2.5: Switch configuration for biasing power converter

### **Inductor Optimization**

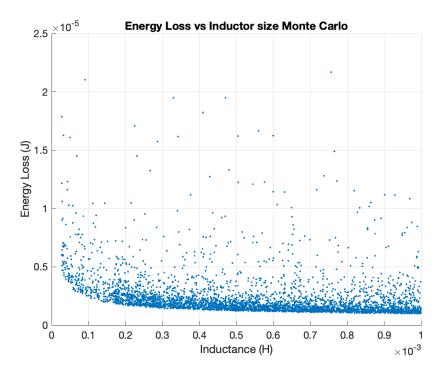

In this simulation, different inductor sizes are evaluated. Assuming equal series resistance, from section 2.1, it is expected that larger inductances will lead to lower energy consumption. The first question to be answered is while charging and discharging the (biasing) output capacitor, how much the energy consumption can be reduced by increasing the inductance. Then it must be determined how this competes with the profit in energy energy efficiency during pulse acquisitions using the resonant pulser.

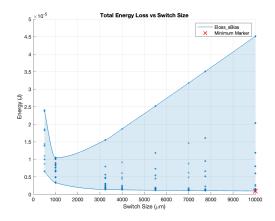

The inductance is swept between  $27\mu$  H and  $1000\mu$  H, then the energy consumption is minimized by optimizing switch size and appropriate maximum current through the circuit.

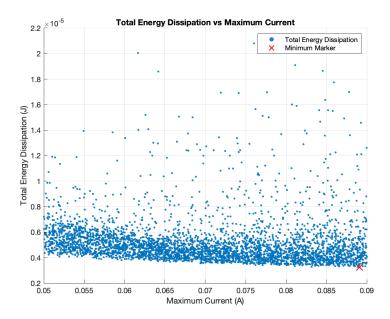

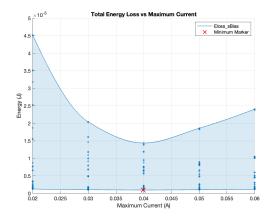

A Monte Carlo simulation is performed to find the global minimum energy consumption by randomly sampling switch sizes and maximum current values for each inductor size. The results are shown in figure 2.10, where the inductance is plotted against the corresponding converter losses using optimal switch size system currents.

Figure 2.10: Bias Configuration - Monte Carlo Inductor size and corresponding energy loss

This simulation shows that the energy consumption decreases with increasing inductance, and so the largest inductor of  $1000\mu$ H provides the lowest energy consumption.

To compare with the resonant pulser, which uses a  $27\mu H$  inductor, the energy consumption is much lower when a larger inductor is used. For a single charge and discharge cycle, the energy consumption decreases from  $4.42\mu J$  to  $0.97\mu J$ , representing a reduction of approximately 78%. The energy losses, optimal switch sizes, and maximum current for both inductance values are summarized in Table 2.6. This table includes the energy consumption for two full cycles, as a 2-step charging method is used to charge the bias.

| <b>Inductor</b> [μ <b>H</b> ] | Switch Size [μm] | I <sub>max</sub> [mA] | Energy Loss [μJ] | 2x Energy Loss [μJ] |

|-------------------------------|------------------|-----------------------|------------------|---------------------|

| 27                            | 4000             | 60                    | 4.422            | 8.844               |

| 1000                          | 10000            | 40                    | 0.973            | 1.946               |

Table 2.6: Overview of energy loss for different inductor values with corresponding optimal switch sizes and maximum current

The difference in energy consumption is

$$\Delta E = 8.84 - 1.94 = 6.90 \,\mu J$$

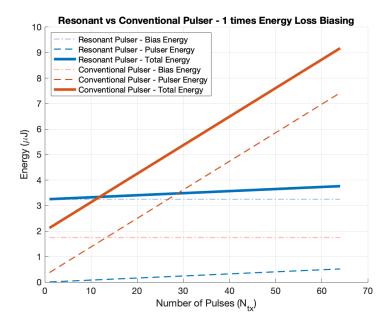

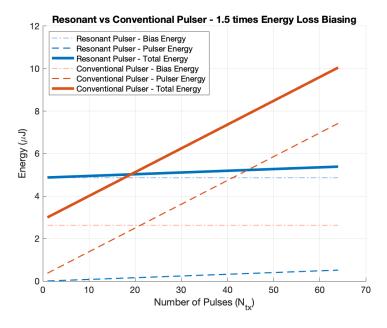

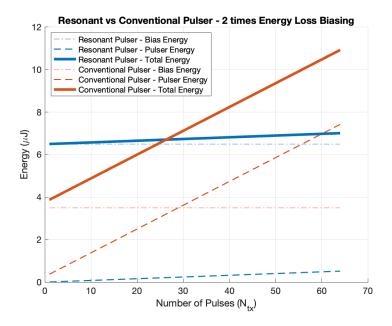

per charge and discharge cycle. By comparing this difference to the total transducer  $CV^2$  pulse losses, it can be estimated that a converter with an optimally sized inductor and a class-D pulser is more energy efficient, as long as fewer than 65 pulses are transmitted per acquisition. This number is within the typical range for wearable applications. The energy efficiencies of both pulser configurations are further investigated in the following sections.

$$N_{tx} = \frac{\Delta E}{E_{\text{pulse}}} = \frac{(E_{L=27\mu H} - E_{L=1000\mu H})}{C_{tx}V_{pulse}^2} = \frac{6.90 \,\mu\text{J}}{0.10692 \,\mu\text{J}} \approx 65 \,\text{pulses}$$

(2.28)

At this point, it became clear that the impact of inductor size on energy consumption is significant, and that the largest possible inductance should be selected. To determine the actual difference with the

resonant pulser, both the switch size and the maximum current through the inductor must be optimized for each configuration.

First, this optimization was performed for the resonant pulser circuit, using the inductor as in the resonant pulser project. The results are shown in Figure 2.11 and Figure 2.12.

Figure 2.11: Energy loss versus maximum current for the resonant pulser inductor size

Figure 2.12: Switch sizes versus energy loss for the resonant pulser inductor size

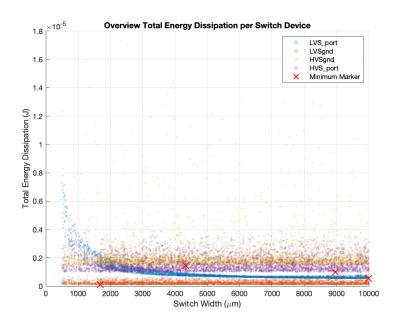

Next, the same optimization was performed for the conventional pulser with a  $1000\mu H$  inductor. For this, a commercially available inductor was selected: the B82472P6105M0000 from TDK [20], with a physical size of 7.3 mm  $\times$  7.3 mm  $\times$  4.5 mm, an inductance of  $1000\mu H$ , a series resistance of approximately 3.85  $\Omega$ , and a Q-factor of 22 at 14.6 kHz. The maximum Q-factor for this inductor is 78 at 200 kHz, which suggests it may not be fully optimal for this application. If future results show that the energy

savings for a larger inductor are less than expected, further investigation into alternative inductors may be warranted.

The results for the conventional pulser are shown in Figure 2.13 and Figure 2.14.

Figure 2.13: Energy loss versus maximum current for the conventional pulser inductor size

Figure 2.14: Switch sizes versus energy loss for the conventional pulser inductor size

For both optimizations, the best results based on minimal energy losses are summarized in Table 2.7. This table shows that, even with a higher inductor resistance, the power converter with a large inductor still consumes 54% less energy than the converter with a small inductor. Notably, by optimizing the switches, the converter with the small inductor now consumes 27% less energy than in the previous simulation in Section 2.5.1. The simulation also shows that the optimal current shifts to a higher value, mainly due to the larger gate switches that are selected. Apparently, these were far from optimal in the

previous simulation, resulting in significant resistive losses. By reducing the resistance, higher currents are allowed in the circuit, and the switches need to operate less frequently.

| Indu                   | ıctor         | Switch Size [μm] |        | I <sub>max</sub> [mA] | Engrav [u I] | 2x Energy [μ J] |               |                 |

|------------------------|---------------|------------------|--------|-----------------------|--------------|-----------------|---------------|-----------------|

| <b>L</b> [μ <b>H</b> ] | $R_L[\Omega]$ | LVS              | LVSgnd | HVSgnd                | HVS          | Imax [IIIA]     | Ellergy [µ ]] | 2x Energy [μ ]] |

| 27                     | 0.085         | 9639.9           | 3833.9 | 8710.1                | 3816         | 89              | 3.24          | 6.48            |

| 1000                   | 3.85          | 7865.3           | 1743.1 | 5543.8                | 1963.2       | 18              | 1.75          | 3.50            |

Table 2.7: Overview of simulation results for different inductor and switch configurations

### 2.5.2. Resonant Pulser Simulations

This section describes the simulations performed to analyze the resonant pulser. The focus is on finding the optimal parameters to ultimately compare the energy consumption with the conventional pulser configuration.

In this configuration, the inductor size depends on the transducer capacitance and operating frequency, as shown in Equation 2.29. An inductance of 27  $\mu$ H with a series resistance of 0.085  $\Omega$  is used in this simulation, matching the values used in the resonant pulser project [4]. In this circuit, there is no optimal current value, since the inductor must be charged in a single step to deliver the required pulse voltage.

$$f_{res} = \frac{1}{2\pi\sqrt{LC_{tx}}} \Rightarrow L = \frac{1}{(2\pi f_{res})^2 C_{tx}} = 31.8\mu \rightarrow \approx 27\mu H$$

(2.29)

The inductor for the RP was deliberately chosen larger to tolerate  $\pm 20\%$  variations in L and other capacitive parasitics while keeping  $f_0 = f_{res}$  accurate. With a larger L, even in the worst case (both L and C  $\pm 20\%$ ), there remains sufficient margin for frequency calibration to reliably generate the 2.6 MHz pulse. Although this slightly reduces efficiency, it ensures stable, power-efficient calibration that does not drift over time [4].

Unlike the conventional pulser, the resonant pulser does not require a back-to-back switch at the output port. This is because the energy is always resonated back to create a complete pulse, so there is no need to isolate a high voltage at the output from the internal circuit. However, the switch must still withstand up to 65 V, as it is connected to the same node as the switch used to charge the bias capacitor. Therefore, the switches in the resonant pulser are configured as shown in Table 2.8.

| Switch Name | Device Type              |

|-------------|--------------------------|

| LVSgnd      | nch_5_switch_low_ron_mac |

| LVS         | pch_5_switch_low_ron_mac |

| HVSgnd      | nld65_g5b_mac            |

| HVS         | nld65_g5b_mac            |

Table 2.8: Switch configuration for the resonant pulser power converter

The following aspects are investigated with a focus on energy efficiency:

- 1. The optimal switch values for the resonant pulser to minimize energy consumption.

- 2. The expected energy consumption with individually optimized switch sizes.

- 3. With these optimal switch sizes, the energy consumption for different pulse counts.

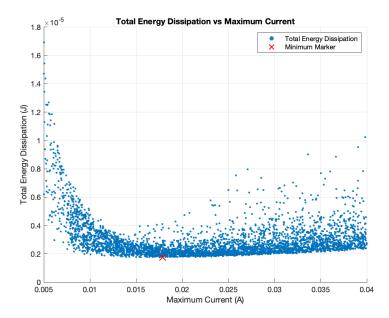

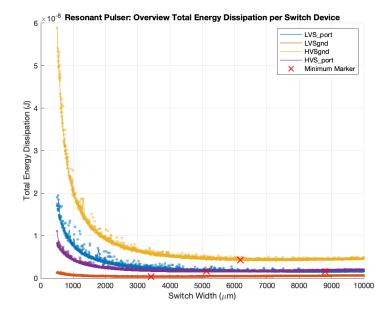

A Monte Carlo simulation was performed to find the optimal switch values. The individual switch sizes were randomly chosen within the range of 0.18 to  $10,000~\mu m$ . The results of this simulation are shown in Figure 2.15, where the individual switch sizes are plotted against the total energy consumption. The total energy loss in the switches is the sum of gate losses and conduction losses. If an optimum is found within the range, this indicates a global minimum, where resistive and switching losses are balanced.

Figure 2.15: Energy loss versus pulse count for the resonant pulser

From this simulation, the configuration with the minimum energy loss was selected, with values shown in Table 2.9. The resulting energy consumption is 8.10 nJ per pulse, or, when scaled to  $CV^2$ , a dissipation of  $0.08\,C_{tx}V_{pulse}^2$ .

| LVS [μm] | LVSgnd [µm] | HVSgnd [μm] | HVS [μm] | Energy [nJ] |

|----------|-------------|-------------|----------|-------------|

| 8606.8   | 3390.5      | 7577.2      | 5194.2   | 8.10        |

Table 2.9: Optimale switchwaardes en energieverbruik voor de resonante pulser

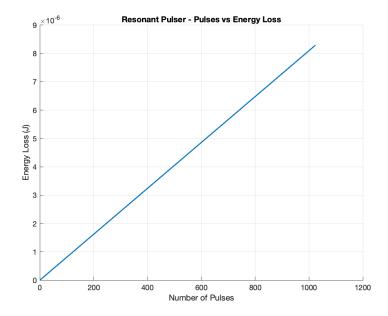

Next, with these optimal switch values, the energy consumption was investigated for different pulse counts. As expected, this results in a linear relationship. The results are shown in Figure 2.16, which confirms that the energy consumption increases linearly with the number of pulses, as each pulse consumes the same amount of energy.

Figure 2.16: Energy loss versus pulse count for the resonant pulser

### 2.5.3. Conventional Pulser Simulations

This section describes the simulations performed to analyze the power converter in combination with a conventional pulser. In these simulations, the high-voltage capacitor is first charged, after which the pulser is activated, and finally, the remaining energy on the high-voltage capacitor is recovered. The focus is on finding the optimal parameters to ultimately compare the energy consumption with the resonant pulser configuration.

In this configuration, the inductor size can be freely chosen. As shown in the previous section, a larger inductor leads to lower energy consumption. Therefore, a 1000  $\mu H$  inductor with a series resistance of 0.085  $\Omega$  is used in these simulations, matching the values used in the resonant pulser simulations. This ensures that the inductor resistance does not influence the comparison between both pulser configurations. It should be noted, however, that a 1000  $\mu H$  inductor with the same resistance will be physically larger than a 27  $\mu H$  inductor, which is an important consideration for the final inductor selection.

In this circuit, a back-to-back switch is required at the output port to isolate the high voltage from the internal circuit. Therefore, the switches in the conventional pulser are configured as shown in Table 2.10.

| Switch Name | Device Type              |  |

|-------------|--------------------------|--|

| LVSgnd      | nch_5_switch_low_ron_mac |  |

| LVS         | pch_5_switch_low_ron_mac |  |

| HVSgnd      | nld65_g5b_mac            |  |

| HVS         | nld65_g5b_mac_BB         |  |

Table 2.10: Switch configuration for the conventional pulser power converter

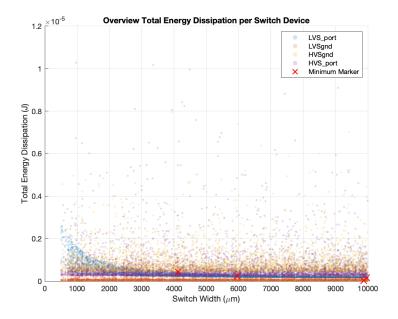

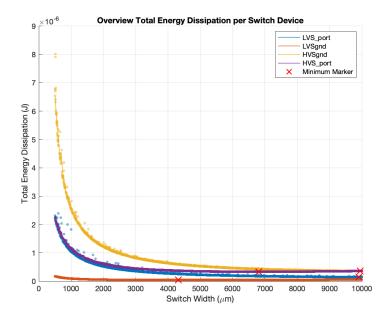

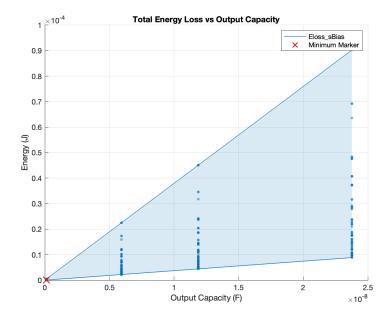

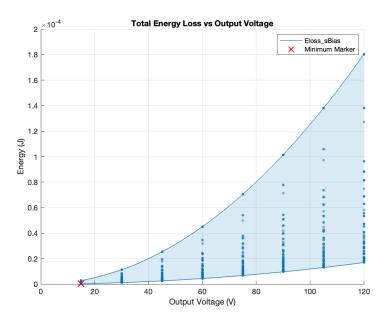

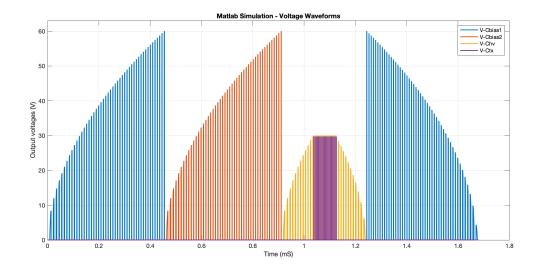

The following aspects were investigated with the focus on energy efficiency:

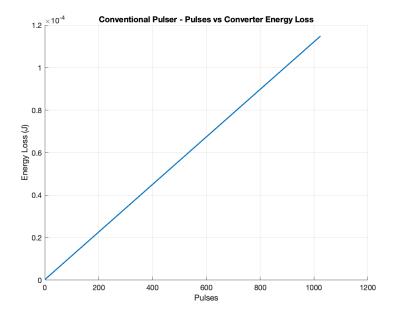

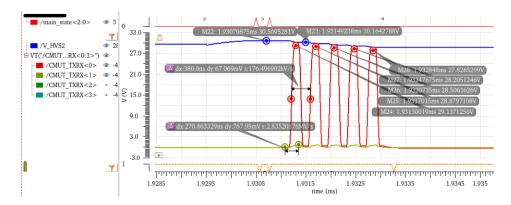

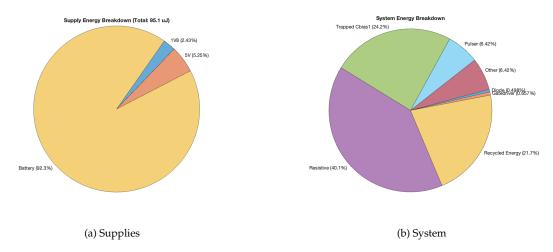

- 1. The optimal switch values for the conventional pulser to minimize energy consumption.