# Analysis and Test Development for Parasitic Fails in Deep Sub-Micron Memory Devices

Ijeoma Sandra Irobi

# Analysis and Test Development for Parasitic Fails in Deep Sub-Micron Memory Devices

Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus Prof.. K.C.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen

op donderdag 15 september 2011 om 15:00 uur

door

Ijeoma Sandra IROBI

Master of Science in Computer Science,

Uppsala University, Zweden

Master of Science in Computer Engineering,

Mälardalen University, Zweden

geboren te Aba, Nigeria

#### Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. ir. H.J. Sips

Copromotor: Dr. ir. Z. Al-Ars

#### Samenstelling promotiecommissie:

Rector Magnificus Prof. dr. ir. H.J. Sips

Dr. ir. Z. Al-Ars

Prof. dr. Engr. C. Nebo Prof. dr. P. Prinetto

Prof. dr. Z. Peng

Prof. dr. ir. C.I.M. Beenakker Prof. dr. ir. M.A. Gutiérrez

Prof. dr. ir. P. Jonker

voorzitter

Technische Universiteit Delft, promotor Technische Universiteit Delft, copromotor University of Nigeria, Nsukka, Nigeria

Politecnico di Torino, Italië Linköping University, Zweden Technische Universiteit Delft Technische Universiteit Delft

Technische Universiteit Delft, reservelid

ISBN: 978-90-72298-22-5

Cover page design: www.Hanike.nl

### Copyright © 2011 by Ijeoma Sandra Irobi

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without prior written permission from the author.

Typeset by the author with the LATEX Documentation system.

Author email: i.s.irobi@TUDelft.nl Alternative email: s.irobi@yefa.nl

Printed in The Netherlands

This dissertation is dedicated to: The third person in the Trinity, the custodian of my dreams. To my loving parents for setting my feet early on the solid ground.

# Analysis and Test Development for Parasitic Fails in Deep Sub-Micron Memory Devices

#### **Abstract**

merging technology trends are gravitating towards extremely high levels of , integration at the package and chip levels, and use of deeply scaled technology in nanometer, approaching 10nm CMOS. Challenges will arise due to the ability to design complex systems such as robots that encompass sensors, transducers, communications systems and processors, all of which require memory devices, and are required to be fault-free, and exhibit fault-tolerance, reliability and survivability characteristics. A key area of challenge is in memory testing, since deep scaling and smaller dimensions of semiconductor cell area will exacerbate the presence of complex defects and can induce effects, such as parasitic effects, which necessitate fails in memory devices. In this thesis, parasitic effects induced by spot defects in memory devices have been evaluated. The thesis presents the analysis, evaluation, validation and test remedies for parasitic fails in deep sub-micron memories. On the one hand, it presents analysis for parasitic bit line coupling effects, and the impact of bit line coupling effect on the static random access memory (SRAM) faulty behavior. Thereafter, it determines both the necessary and sufficient detection conditions for memory fault models, and demonstrates the limitations of existing industrial memory tests to adequately detect faults in the presence of bit line coupling. In addition, the thesis presents a systematic approach for test development and optimization, and new memory tests - March SSSc an optimal test that detects all single-cell static faults, and March m-MSS and March BLC that detect all two-cell static faults, in the presence and absence of bit line coupling. On the other hand, this thesis also presents the analysis, evaluation, validation and test remedies for parasitic memory effect in SRAMs. The work presents the impact of the parasitic memory effect on the detection of static faults, and clearly shows that fault detection is influenced by the presence of parasitic node components and not the resistive defect alone; something that must be considered in generating effective memory tests. In addition, the thesis presents the detection conditions and a new memory tests, March SME that targets and detects single-cell static faults, in the presence of the parasitic memory effect.

# Analysis and Test Development for Parasitic Fails in Deep Sub-Micron Memory Devices

Samenvatting (Abstract in Dutch)

uidige technologische trends leiden tot uiterst hoge niveaus van integratie in geïntegreerde schakelingen, waarbij gebruik wordt gemaakt van nanometer technologieën met afmetingen die tot 10nm CMOS kunnen gaan. De uitdagingen zijn het ontwerpen van complexe systemen zoals robots welke sensoren, omvormers, communicatie systemen en processors bevatten. Deze componenten vereisen allen een betrouwbaar geheugen met fout tolerantie en overlevingskenmerken. Een belangrijk aspect is het testen van geheugens. Door de compactere transistoren, en de daarbij behorende kleinere afmetingen, kunnen door parasitische effecten complexe defecten in het geheugen worden veroorzaakt. In dit proefschrift, zijn de parasitische effecten in geheugens die door spot defects worden veroorzaakt geëvalueerd. Dit proefschrift presenteert de analyse, evaluatie, validatie en test oplossingen voor parasitaire mankementen in deep sub-micron geheugens. Allereerst wordt de analyse voor parasitische bit-lijn koppeling en de impact van het koppelingseffect van de bit-lijn op het foutieve gedrag van static random access memory (SRAM) beschreven. Vervolgens worden zowel de noodzakelijke als de sufficiënte detectievoorwaarden voor fout modellen van het geheugen gepresenteerd en worden de beperkingen van bestaande industriële geheugentests besproken. Bovendien beveelt dit proefschrift een systematische benadering voor testontwikkeling en optimalisering aan. Nieuwe geheugentests -March SSSc een optimale test die alle eencellige statische fouten ontdekt, en March m-MSS en March BLC die alle tweecellige statische fouten detecteert, welke zowel in aanwezigheid als afwezigheid van bit-lijn koppeling kunnen werken. Anderzijds, presenteert dit proefschrift ook een analyse, evaluatie, validatie en test oplossingen voor parasitische effecten in SRAMs. De impact van parasitische effecten op de detectie van statische fouten wordt aangetoond. Hierbij wordt duidelijk dat foutopsporing wordt beïnvloed door aanwezigheid van parasitische componenten en niet slechts door aanwezigheid van weerstand defecten. Hiermee moet rekening worden gehouden bij het produceren van efficiënte geheugentests. Bovendien presenteert het proefschrift detectievoorwaarden voor nieuwe geheugentests zoals March SME, welke zich richt op statische fouten in enkele cellen en deze detecteert, in de aanwezigheid van parasitische effecten.

## Acknowledgments

his doctoral research has been the product of resilience, hard work, determination and conscientious effort over these years. In this journey, several people have played strategic roles at different points that have greatly encouraged me, improved the quality of my work, and made my stay in the Netherlands an enjoyable experience. To these people, words are not enough to represent the depth of gratitude that I wish to express to all of you. Neither the order in which this acknowledgement goes nor the length of the sentences are commensurate to the value I place on your help, kindness and support.

In the first place, I remain very grateful to Prof. Stamatis Vassiliadis, who gave me a 23 minutes convincing pitch that informed part of my decision to follow the PhD program at TU Delft, and encouraged me to make my experiences here count. Even though he is no longer here with us, he is always remembered and the legacy he has left behind speaks in so many ways. I am also ever so grateful to Dr. Koen Bertels, who was my first contact at the CE group, who has also provided much more support and encouragement through these years than I could imagine. Koen *dalu!*.

Importantly, I wish to immensely thank my PhD supervisor, Dr. Zaid Al-Ars who believed in me and my ability to complete this work successfully much more than I did. For his consistent committment and patience that has greatly improved my thought process and the quality of my work I remain so grateful. Zaid, I cannot thank you enough, *Imela!*. I am very thankful to Dr. Said Hamdioui whose comments, reviews and positive chat about Africa encouraged me to think of how much better things could be. I wish to thank Prof. Michel Renovell for his collaboration, insightful reviews and support in the later phase of my research work. I am also grateful to Prof. Claude Thibeault for giving me the opportunity of working with him on my internship at LACIME, École de Technologie Supérieure, Université du Québec, Montreal, Canada in the later part of my PhD.

To the fantastic staff team in CE group that have professionally handled important administrative and technical aspects of my stay, Lidwina, Bert, Eric and Eef *unu emela!* Also, to CICAT staff, especially Veronique van der Varst, who worked tirelessly to get all the paper work and my stay arrangements made, I was indeed lucky to have you, thank you very much. I also wish to thank my colleagues in CE group who have contributed to the lovely atmosphere that made my research enjoyable. I thank my officemate Tariq, who has provided interesting discussions - scientific and non-scientific that made the office lively; my colleagues Motta, Roel, Behnaz, Hamid, Mahmoud, Seyab, Zaidi, Mafalda, Innocent to mention only a few.

I remain grateful to Prof. Henk Sips, my promotor, who is well known for his efficiency and quality inputs. I also thank all my PhD promotion committee members for graciously accepting to serve on the committee. I wish to say thank you to Prof. Chinedu Nebo whose insight and vision as UNN Vice Chancellor inspired me to seek channels of mutual collaboration between TU Delft and UNN, and to Prof. Dan Lenstra and Prof. Kees Beenakker for providing immeasurably support from EEMCS and DIMES to facilitate the collaboration. Many thanks to my teachers who pointed me in the right direction - Dr. Ivan Christoff, Dr. Roland Bol and Prof. Gerhard Fohler.

My appreciation also goes to my Church, friends and acquantancies who have generally made my stay and social life so much fun. I thank Austine, Chinelo, Dubem, Peter, Ijeoma, Solomon, Sam, Obioma, philip, the Adeniyi's, the Nwosu's, the Abarshi's and many more that for the sake of space I cannot mention. I deeply appreciate you all *Ndewo nu!* I wish to also express my gratitude to my colleagues at Young Entrepreneurs for Africa (YEFA), whose constant committment to excellence and development sharpened my focus, *Unu emekalum!*.

Finally, I wish to thank my family, my parents, siblings, nieces and nephews for their unending love, support, committment and the sparkle they have added to my life and have shown beyond measure. To you all, it is impossible to fully express my appreciation, *Chineke gozie unu nile!* To everyone else who I have not mentioned but who have affected my life in special ways, I am grateful to you and wish you well.

# **Contents**

| Al | ostrac | et                                       | i   |

|----|--------|------------------------------------------|-----|

| Al | ostrac | et in Dutch                              | iii |

| 1  | Intr   | oduction                                 | 1   |

|    | 1.1    | Semiconductor memory technology          | 2   |

|    |        | 1.1.1 Memory devices hierarchy           | 4   |

|    |        | 1.1.2 DRAM architecture and types        | 5   |

|    |        | 1.1.3 SRAM architecture and types        | 7   |

|    |        | 1.1.4 Emerging memory technologies       | 9   |

|    | 1.2    | Testing semiconductor memories           | 9   |

|    |        | 1.2.1 Motivation for memory testing      | 10  |

|    |        | 1.2.2 Memory test levels and time        | 11  |

|    |        | 1.2.3 Challenges in testing memories     | 11  |

|    | 1.3    | Contributions and scope of thesis        | 13  |

|    |        | 1.3.1 Specific contributions             | 13  |

|    |        | 1.3.2 Scope of work                      | 14  |

|    | 1.4    | Thesis outline                           | 14  |

| 2  | Mod    | deling memory devices                    | 17  |

|    | 2.1    | Semiconductor memory models              | 18  |

|    | 2.2    | DRAM model and characteristics           | 21  |

|    |        | 2.2.1 Functional DRAM chip model         | 23  |

|    |        | 2.2.2 Reduced functional DRAM chip model | 26  |

|    |        | 2.2.3 Electrical DRAM chip model         | 26  |

|    | 2.3    | SRAM model and characteristics           | 30  |

|    |        | 2.3.1 SRAM memory cell                   | 30  |

|    |        | 2.3.2 SRAM operations                    | 33  |

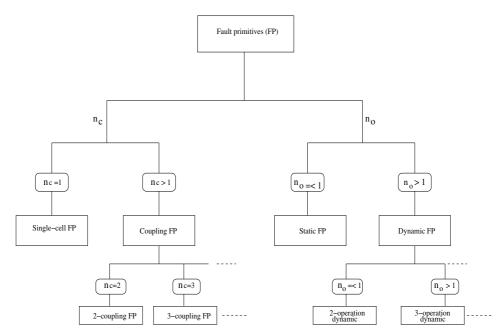

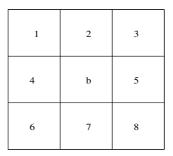

| 3 | Fun  | ctional fault modeling approaches 3                            |

|---|------|----------------------------------------------------------------|

|   | 3.1  | Memory operation sequence                                      |

|   | 3.2  | Fault primitives                                               |

|   |      | 3.2.1 Classification of FPs by number of cells                 |

|   |      | 3.2.2 Classification of FPs by number of operations            |

|   | 3.3  | Static fault models                                            |

|   |      | 3.3.1 Single-cell static faults                                |

|   |      | 3.3.2 Two-cell static faults                                   |

|   |      | 3.3.3 Multiple cell faults                                     |

|   | 3.4  | Fault modeling and memory testing                              |

| 4 | Para | asitic bit line coupling effect 4                              |

|   | 4.1  | Modeling BL coupling                                           |

|   |      | 4.1.1 Quantifying BL coupling effect                           |

|   |      | 4.1.2 Impact on faulty behavior                                |

|   | 4.2  | BL coupling impact on opens                                    |

|   | 7.2  | 4.2.1 Simulation of open defects                               |

|   |      | 4.2.2 Simulations of OD-R1 <sub>t</sub> and OD-R1 <sub>c</sub> |

|   |      | 4.2.3 Analysis of other ODs                                    |

|   | 4.3  | BL coupling impact on shorts                                   |

|   | 4.4  |                                                                |

|   | 4.4  |                                                                |

|   |      | · ·                                                            |

|   |      | 4.4.2 Simulation analysis of bridges 6                         |

| 5 |      | asitic memory effect 6                                         |

|   | 5.1  | Modeling the failure mechanism                                 |

|   |      | 5.1.1 Resistive open defects                                   |

|   |      | 5.1.2 Modeling parasitic node capacitance                      |

|   | 5.2  | Impact of parasitic node capacitance                           |

|   | 5.3  | Analysis of the faulty behavior                                |

|   |      | 5.3.1 Undetectable faulty behavior                             |

|   |      | 5.3.2 Detectable faulty behavior                               |

|   |      | 5.3.3 Detection using n-sequence                               |

|   | 5.4  | Impact on static faults                                        |

|   |      | 5.4.1 Simulation parameters                                    |

|   |      | 5.4.2 Analysis for defect R1c                                  |

|   |      | 5.4.3 Analysis for defect position R2c 8                       |

|   |      | 5.4.4 Analysis for the other defect positions                  |

| 6 | Men  | nory testing for parasitic fails 8                             |

| _ | 6.1  | Data backgrounds for BL coupling                               |

|   |      | Tests for RI counling                                          |

|    |         | 6.2.1   | Single-cell faults: limitations of existing tests | 91  |

|----|---------|---------|---------------------------------------------------|-----|

|    |         | 6.2.2   | March SSS and March SSSc                          | 93  |

|    |         | 6.2.3   | Two-cell faults: limitations of existing tests    | 94  |

|    |         | 6.2.4   | March m-MSS                                       | 96  |

|    | 6.3     | Test of | ptimization for BL coupling                       | 97  |

|    |         | 6.3.1   | Impact of BL coupling on static FFMs              | 98  |

|    |         | 6.3.2   | CBs identification for static FFMs                | 101 |

|    |         | 6.3.3   | Optimized test for BL coupling: March BLC         | 104 |

|    | 6.4     | Testin  | g for parasitic memory effect                     | 106 |

|    |         | 6.4.1   | Detection conditions for parasitic memory effect  | 107 |

|    |         | 6.4.2   | March SME                                         | 109 |

| 7  | Con     | clusion | s and recommendations                             | 113 |

|    | 7.1     | Summ    | nary of thesis chapters                           | 113 |

|    | 7.2     | Specif  | ic thesis contributions                           | 115 |

|    | 7.3     | Recon   | nmendations for future research                   | 117 |

| Li | st of l | Publica | tions                                             | 129 |

| Cı | ırricu  | ılum Vi | tae                                               | 131 |

| Chanter | - 1 |  |

|---------|-----|--|

|         |     |  |

| Onapion |     |  |

ith significant advances in deep sub-micron complementary metal oxide semiconductor (CMOS) technology, more feature-rich integrated silicon devices are being used in consumer electronics, advanced communication and networking systems, computers, servers and virtually all electronic systems. One of such devices is the memory chip.

Memories perform an essential function, which is to store data and provide for its retrieval.

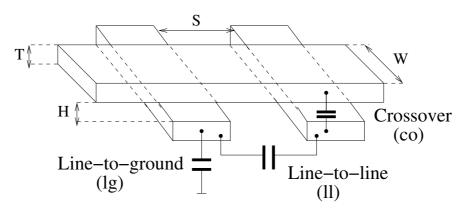

On the one hand, the quest for increase in functionality and smaller dimensions have been the driving force behind the continued scaling of cell area in semiconductor devices as encapsulated by Moore's law [69]. However, smaller dimensions of memory devices can elicit various types of defects such as spot defects - opens, shorts and bridges during the manufacturing process [16, 17, 20, 82, 87]. In addition, it can induce capacitive coupling among signal lines, power and ground lines, thereby resulting in high sensitivity level to defects in the memory.

On the other hand, this quest for smaller dimensions comes with the increased demand for reliability of the manufactured devices. However, for decades it has been obvious that the reliability, availability, and safety of electronics systems cannot be obtained solely by the careful design, quality assurance, or other fault avoidance techniques without proper testing mechanisms [19]. In fact, high defect density as well as new failure mechanisms in the nano-era are expected to be significantly larger in the future [21, 22, 92], and this will create major challenges in designing and testing memories in nanotechnology [38]. Conventional fault models and test approaches are inadequate to realize the required product quality [45, 46, 70, 77]. In the absence of new theories capable of modeling their failures mechanism and developing appropriate test solutions, the production of future electronics systems will become infeasible.

Combining the demand for higher densities, which can exacerbate the presence of

complex defects, and the assurance of reliability of the manufactured devices underscores the importance of investigating appropriate and superior methodologies in failure analysis and testing that target the consequences and complexities of the evolving technologies [49, 100].

This thesis presents the work done in one of such studies. The thesis presents the analysis, evaluation and validation of parasitic fails in deep sub-micron memory devices, and the development of suitable memory tests that detect such fails.

In this chapter, an introduction to semiconductor memories is presented. Section 1.1 describes the semiconductor memory technology. Section 1.2 discusses the motivation for memory testing, memory test levels and the concept of test time. The contributions and scope of this thesis are presented in Section 1.3 and finally, Section 1.4 provides the thesis outline and a brief conclusion of the chapter.

## 1.1 Semiconductor memory technology

The term memory in this thesis refers to data storage that comes in the form of packaged semiconductor memory chips.

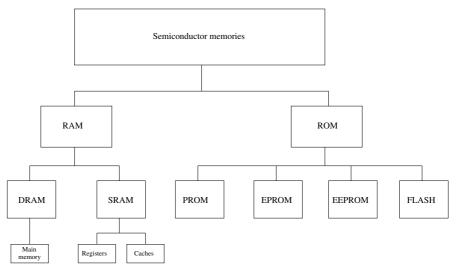

A diagrammatic representation of the classification of semiconductor memories is depicted in Figure 1.1. There are two broad categories of memories, which are the *read-only memory (ROM)* and the *random access memory (RAM)*. Both types of memory are often packaged as integrated circuits (ICs). ICs are small electronic circuits that consist mostly of semiconductors.

ROM is a special memory used to store programs for booting and performing diagnostics on computers. It contains data that normally can only be read, but not written to. ROMs are considered non-volatile since they do not loose their information when power is switched off. ROMs can be classified as follows.

- 1. *Programmable read-only memory (PROM)*. This is the type of ROM that can only be programmed once. Once the PROM has been used, you cannot erase and reuse it.

- 2. *Erasable programmable read-only memory (EPROM)*. An EPROM is a special type of PROM that can be erased as a result of exposure to ultraviolet rays.

- 3. *Electrically erasable programmable read-only memory (EEPROM)*. An EEP-ROM is the type of PROM that can be erased electrically.

- 4. *Flash memory*. This is a variant of the EEPROM. It has a high density, low cost, fast (to read but not to write) and is electrically reprogrammable. The flash memory can be distinguished from the EEPROM in the sense that flash devices can be erased in chunks, one sector at a time and not on a byte-by-byte basis.

Figure 1.1: Types of semiconductor memories

RAM is the most common memory type found in computers. In contrast to ROMs, it is volatile because it looses its data when power is switched off and therefore requires continuous power supply. More so, data can both be written to and read from RAMs. The word "random" in the name "random access memory" refers to the fact that any location in such memory can be addressed directly at any time. This is different from sequential access media, such as magnetic tape, which must be read in sequence irrespective of the desired content. Depending on the technology used in holding the stored data, RAM can be classified into two categories, namely, the static random access memory and the dynamic access random memory. A brief discussion on each of these categories is given below.

- 1. Static random access memory (SRAM). The SRAM stores its data inside latches and can store it for as long as needed. The term static is used because the memory does not need to be refreshed as long as power is supplied to the circuit. Refreshing refers to the process of periodically reading information from an area of the computer memory, and immediately rewriting the read information to the same cells with no alterations. The evolution of hardware systems over the years has led to the manufacture of different types of SRAMs made up of 4 to 6 transistors and is very fast. Examples of memories made with SRAM are registers and cache memories. A main disadvantage of an SRAM is that it consumes more silicon area per bit and relatively more power than DRAMs, which explains why they are equally more expensive.

- 2. Dynamic random access memory (DRAM). The DRAM stores information in capacitors, which loose their charge over time and therefore needs to be refreshed regularly in order to retain their contents. This refreshing action is the

Figure 1.2: Memory hierarchy

reason why the memory is called *dynamic*. The refresh time in DRAMs also explains why SRAMs are faster than DRAMs, since SRAMs do not need to be refreshed. An example application of a DRAM device is the main memory of a computer. In comparison to SRAMs, DRAMs can use one transistor and a capacitor per memory cell. Due to this internal capacitive element, some delay is incurred, with access time usually above 30ns.

#### 1.1.1 Memory devices hierarchy

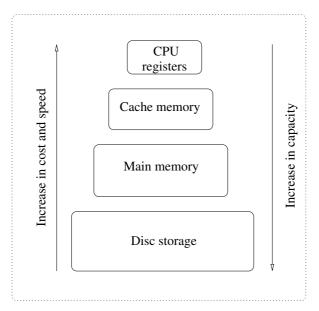

Memory devices in most systems can be implemented as a hierarchy. Figure 1.2 depicts the common memory hierarchy in most modern personal computers. Moving from bottom to top of the figure shows the order of increase in speed as well as cost but a decrease in storage capacity.

At the bottom of the hierarchy is the disc storage. It typically has an access time of hundreds of thousands of central processing unit (CPU) cycles. This relatively slow speed is the result of using mechanical parts, particularly electric motors and moving magnetic heads. However, disc storage can have a capacity ranging from tens of gigabytes on small computers to many thousands of gigabytes on large systems.

Above the disc storage is the main memory. Main memory usually has an access time equal to several hundred CPU cycles. The term *main memory* commonly refers to physical memory, which uses DRAM to store its data, and is considerably faster than the disc storage.

The cache memory serves basically to reduce the mismatch in speeds between the CPU and the main memory. There could be different levels of cache memories for example Level 1 (L1), Level 2 (L2) caches. L1 cache consists of high speed SRAM cells. To save space and reduce cost, there is usually only a small amount of L1 cache on a processor. The secondary cache memory, L2, could hold larger sizes of data than the L1. L2 caches are likewise composed of SRAM cells, but they are made up of more such cells than L1 caches. Due to the reduced size of the L1 cache, it is much faster than the L2 cache, thus access time to and from the cache is reduced due to fewer cells.

At the top of the memory hierarchy are processor registers. These comprise an extremely small amount of very fast memory cells that are built into the CPU. The aim is to speed up the execution of the CPU, and thus of programs, by providing quick access to commonly used values. Registers are usually implemented as an array of multi-port SRAM cells.

#### 1.1.2 DRAM architecture and types

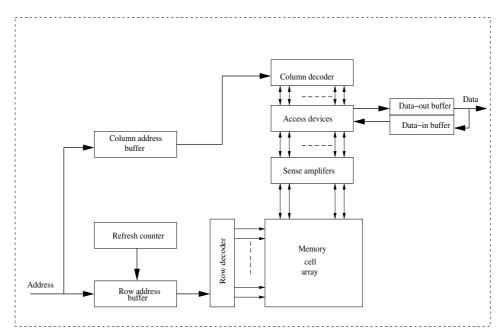

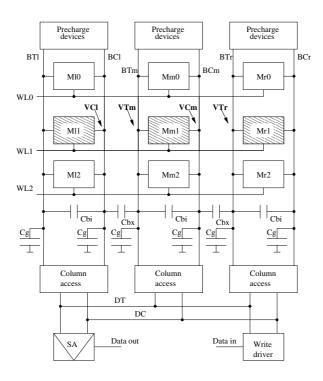

The DRAM array consists of cells organized in a number of rows and columns. For example, a 1M bit chip could be externally organized as 1M addresses. Internally, memory cells are arranged as a matrix or number of matrices and cells can be grouped together as words containing multiple bits of data. Figure 1.3 depicts the internal functional block diagram of the DRAM.

During a read operation, first, the row address is presented through the *row address* buffer, and decoded by the *row decoder*. Next, the column address is presented through the *column address buffer*, and decoded by the *column decoder* to determine the exact cell(s) to be accessed. The high-order bits of the address are connected to the row decoder, which selects a row in the memory cell array. The lower-order address bits go to the column decoder which selects the required columns. The contents of the selected row in the memory cell array are amplified by the *sense amplifier*, loaded into the data-out buffer and presented on the data line. For a write operation, the data on the data line is loaded into the data-in buffer and written into the memory cell array through the write driver.

The refresh counter of the memory counts through the memory addresses in order to refresh the data stored in the memory cells. During a refresh operation, the column decoder selects all columns and the row decoder selects the row that is indicated by the address latch. All the bits in the selected row are read and refreshed at the same time. Reading each row and writing it back compensates for the gradual leakage of charge from the capacitors, which store the data. If this is not done regularly, then the DRAM looses its contents, despite continued power supply.

A major drawback in the DRAM technology compared to SRAM is low speed. In or-

Figure 1.3: An internal functional block diagram of the DRAM

der to overcome this drawback, more efficient types of DRAM for instance, Fast Page Mode DRAM (FPM), Extended Data Out (EDO), Synchronous DRAM (SDRAM), Double Data Rate (DDR) have been developed. A brief explanation of each technology is provided below.

- FPM DRAM: This is the fast page mode dynamic random access memory (FPM DRAM). While the standard DRAM requires that a row and column be sent for each access, FPM DRAM works by sending the row address just once for many accesses to memory in locations near each other, thereby improving access time. The row of bits is selected only once for all columns within the row.

- EDO DRAM: Extended data-out dynamic random access memory is faster than

the FPM DRAM. The reason is because unlike conventional DRAM which can

only access one block of data at a time, EDO RAM can start fetching the next

block of memory at the same time that it sends the previous block to the CPU.

- SDRAM: Synchronous dynamic random access memory is a type of DRAM

that has a synchronous interface. This implies that it waits for a clock signal

prior to responding to control inputs, thus is synchronized with the computer's

system bus. SDRAM chips eliminate wait states by dividing the chip into two

cell blocks and interleaving data between them. While a bit in one block is

accessed, a bit in the other is prepared for access.

• DDR SDRAM: Double data rate synchronous dynamic RAM is a type of SDRAM that supports data transfers on both edges of each clock cycle (the rising and falling edges), thereby effectively doubling the memory chip's data throughput with less power consumption than the SDRAM.

#### 1.1.3 SRAM architecture and types

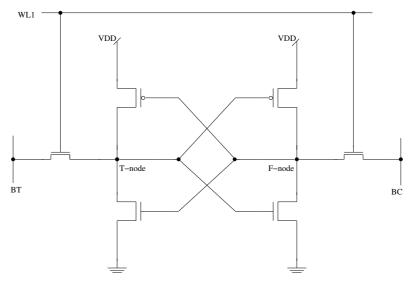

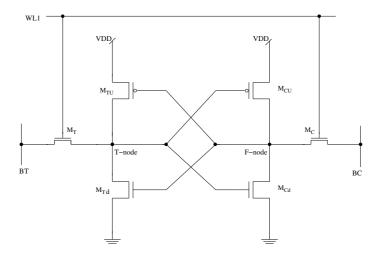

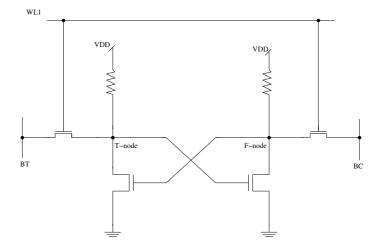

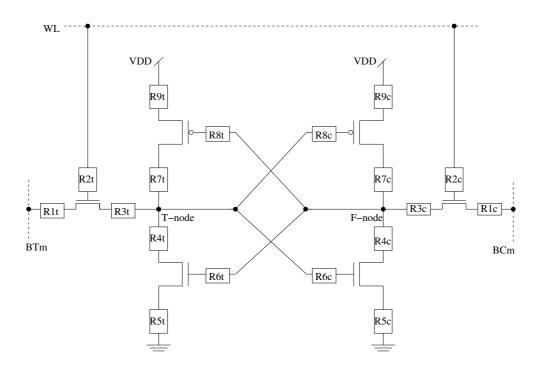

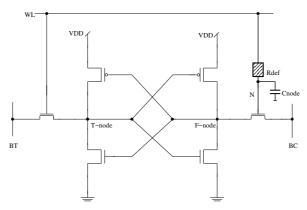

The SRAM cell consists of a bi-stable flip-flop connected to the internal circuitry by two access transistors as depicted in Figure 1.4. The access transistors are connected to the word line (WL) and to a bit line (BL) pair comprising the true (BT) and complementary (BC). Each flip-flop has four to six transistors that are cross-coupled to form inverters. When the cell is not addressed, the two access transistors are closed and the data is kept to a stable state, latched within the flip-flop. The flip-flop needs the power supply to keep the information. The data in an SRAM cell is volatile since the cell structures allow data to be stored for an indefinite amount of time in the device as long as powered and is lost when power is removed. Unlike DRAMs, data does not leak away in an SRAM, thus refresh cycles are not required. The flip-flop may be in either of two states interpreted by the support circuitry as a 1 or a 0.

There are several types of SRAM classifications. One type of classification of SRAM is based on the SRAM memory cells. They are classified as the 4T cell which have four NMOS transistors plus two poly load resistors; the 6T cell which have six transistors - four NMOS transistors plus two PMOS transistors; the thin film transistor (TFT) cell which has four NMOS transistors plus two loads called TFTs.

The four-transistor SRAMs are suitable for medium to high performance, but have relatively high leakage current, and consequently high standby current. Four-transistor designs may also be more susceptible to various types of radiation induced soft errors. On the other hand, the six-transistor (6T) memory cell are highly stable, relatively impervious to soft errors, and have low leakage and standby currents. Current SRAM chip architectures use six-transistor memory cells and is the type used throughout this thesis.

SRAMs can be differentiated based on their function or by the transistor type. By their function they can be classified into four main categories, namely, asynchronous SRAMs, synchronous SRAMs, special SRAMs, and non-volatile SRAMs.

1. Asynchronous SRAMs: Asynchronous SRAMs are devices that are not synchronized with an external signal clock, and begin their data operation (read or write) as soon as it receives the instruction to do so. In asynchronous SRAMs the memory is managed by three control signals. One signal is the chip select (CS) or chip enable (CE), the second is the output enable (OE) and the third is the write enable (WE).

Asynchronous devices can be categorized as low speed, medium speed and

Figure 1.4: 6T SRAM cell

high speed based on their access time. Access time refers to the total time it takes for a device to yield a data output after receiving a read instruction. These categories are:

- Fast asynchronous SRAMs: These devices are often used in buffer memory applications, consumer products, etc. The density range for these types of SRAMs is from the sub 64K to 4Mb and have data words that are mostly configured as x8, x16, which is the size in bits that each memory location can store.

- Low power SRAMs: These can also be referred to as low speed SRAMs. These SRAMs are typically designed to consume very low power and are used in applications where power is a major concern, which include digital signal processors (DSPs), PDAs, consumer electronic products, and so on. The density range for these SRAMs is usually from 64K to 8Mb and are mostly configured with word widths of 8 and 16 bits.

- 2. Synchronous SRAMs: As computer system clocks increased, the demand for very fast SRAMs necessitated variations on the standard asynchronous fast SRAM. This demand resulted in the development of synchronous SRAMs (SS-RAM). In synchronous SRAMs the read or write cycles are synchronized with the microprocessor clock and therefore can be used in very high-speed applications.

- 3. Special SRAMs: Multi-port SRAMs are specially designed chips using fast SRAM memory cells. Synchronous and asynchronous FIFOs are available.

- 4. Battery-Back SRAM (BRAM): is also called zero-power SRAMs. Battery-

backed SRAM combine an SRAM and a small lithium battery.

#### 1.1.4 Emerging memory technologies

This discussion will not be complete without examining the memory technologies that are currently being developed. The demand for faster, cheaper, better memory is enormous, and memory manufacturers are responding with several innovative solutions.

- Zero capacitor RAM (Z-RAM): This is a potential replacement for SRAM. It offers the performance of six transistor SRAM using only a single transistor, which therefore can provide much higher densities.

- Ferroelectric RAM (FeRAM): This is another non-volatile memory type, which is similar to flash RAM. However, it provides better power efficiency, write speeds, and write-erase duty cycles.

- Magnetoresistive RAM (MRAM): This memory stores data in magnetic storage elements, not as electrical charge or current flow. MRAM is physically similar to DRAM, however, it does not require refresh cycles.

- Phase-change memory (PRAM or PCM): This is another non-volatile memory type, which is based on the phase change properties of chalcogenide glass, which can be switched from crystalline to amorphous states by the application of heat. PRAM offers high densities and can be useful in harsh environments where radiation disrupts other types of RAM.

## 1.2 Testing semiconductor memories

The essence of any memory test could be to detect, diagnose or localize faults in a given memory device. A fault is said to have occurred when a wrong output is yielded by a defective system, or a distinguishable difference is observed between a correct version of the given device and the current device under test (DUT). A fault can arise during all phases of a computer system design process specification, design, development, manufacturing, assembly and installation throughout its entire operational life [19, 27]. The process of determining whether a given memory device contains faults or not is referred to as *memory testing*. The algorithms with which the presence or absence of faults are ascertained are called *memory tests*.

Since faults can occur, the need to perform quality tests to ensure that manufactured chips are capable of performing their intended functions at the point of use cannot be over emphasized.

#### 1.2.1 Motivation for memory testing

There are several motivations for memory testing. Memories practically dominate the chip area. Due to the desirability of smaller chip dimensions, there is increase in density on as much reduced chip area as possible [62, 61]. The implication of this increase in density is that the area occupied by each memory cell exponentially decreases and cells are located closer to one another. Because of the increased proximity between memory cells, memories become increasingly sensitive and prone to complex defects.

Failures in the memory device can significantly impact the defect-per-million (DPM) rate, since memories largely dominate the chip area. Therefore, prior to the end of the production chain from the manufacturer to an end user, highly efficient memory tests are required to appropriately test and detect faults in the memory device. Further motivations for memory testing include:

#### 1. To mitigate the impact of increased chip density

Due to high cell density, individual cells become closer to one another and become prone to influences from other cells in their neighborhood. This can adversely affect the cell and impact the expected behavior of the memory device.

#### 2. To detect disturbances due to use

Noise and crosstalk [30] effects, for example, noise on address and data lines, could occur in the cells due to repeated use and could induce disturbances transferable from one part of the memory device to the other.

### 3. To detect defects due to the manufacturing process

Defects could be introduced into the memory device during the manufacturing process. The continuos shrinking of semiconductor's nodes makes semiconductor memories increasingly prone to electrical defects tightly related to the internal structure of the memory [91]. For example, differences in capacitance or leakage current could occur during the manufacturing since charges are stored in capacitors and is prone to leakage. Such abnormalities could be detected by testing.

#### 4. To detect faults in the presence of complex defects

Due to shrinking memory dimensions relating to increased chip density, complex factors, such as bit line coupling, can affect the memory's behavior thereby causing faults that cannot be detected by already known memory tests. Understanding these behaviors and generating appropriate memory tests that specifically target the resulting faults can help to minimize fails recorded as a result of such complexities.

#### 5. Ensuring functionality under stressful conditions

Testing helps to ascertain the reliability of a device given specific stress conditions such as time, voltage and temperature. Several research work have addressed the effectiveness the effectiveness of stresses [39, 89, 96].

#### 1.2.2 Memory test levels and time

Testing can be carried out at three different levels, namely, the cell array, chip and the memory board levels.

- 1. Cell array level. At the array level, testing comprises the memory chips, control logic and chip select.

- 2. Chip level. At this level, testing is focused on the memory chip, which contains the actual data of the memory.

- 3. Board level. A memory board comprises board selection and memory board controller, data and address registers, support logic as well as the memory array. Tests at this level involve these components.

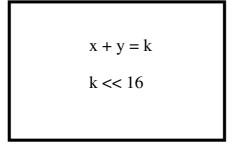

An objective of memory tests is to basically detect malfunctioning memory cells. With recent memory manufacturing technology, the density of cells per silicon area continues to increase. Since each cell must be tested to ascertain the presence or absence of faults, it follows that the total test time required to investigate a DUT is proportional to the amount of memory being tested. In brief:

$$t_{\text{test}} = n(\#_{\text{op}} \cdot t_{\text{op}}) \tag{1.1}$$

where n is the total number of cells,  $\#_{op}$  is the number of necessary and sufficient test operations performed per cell to detect fault, and  $t_{op}$  is the time taken per test operation.

Whereas linear tests have test time complexities of the order O(n), some non-linear tests can have complexity of the order  $O(n^y)$ , where y is greater than 1. Hence, reduction in both the time required to run a test as well as the number of tests necessary and sufficient for fault detection, while maintaining high *fault coverage* (i.e., the number of detected faults divided by the number of total faults) in a given device is an important challenge and priority for developing memory tests.

#### 1.2.3 Challenges in testing memories

Due to high cell density, the number of bits per chip (example in DRAMs) increases exponentially (estimated as 4 times in less than 3 years), but the price per bit decreases exponentially [60]. Older test algorithms are known to have test run time

complexities in the order of  $O(n^2)$ , but to cope with the exponential increase in density there is the need to use efficient tests with test times in the order of O(n) that can effectively test the DUT at no significant increase in test cost. As a result of recent complex innovations in semiconductor memory technology, testing memory devices face enormous challenges. The use of embedded memories has compounded this challenge due to lack of *controllability* of the inputs and observability of the outputs, and to ameliorate this problem, built-in-self-test (BIST) was introduced [63, 64, 67, 80, 88]. The challenges in memory testing can be broadly categorized into three main issues namely, test time, test cost and complex fault behaviors.

- Test time: The growing density and capacity of memory chips requires new test methodologies and equipment since the total test time required to investigate a DUT is proportional to the amount of memory being tested. Thus, for tests to be desirable, they must be generated to ensure optimal test times and still yield high fault coverages.

- Test cost: In the deep sub-micron era silicon, packaging and testing costs are substantial parts of the total manufacturing cost [65] depending on production volume. As the volume of production increases, so could the total cost for administering effective tests to ensure reliability. However, if the test cost increases as the increase in density, it could become increasingly difficult to effectively test all manufactured devices.

- Complex faults behavior: Decrease of cell area can result in coupling noise and sensitivity higher to defects in memory devices. In recent times, several companies are not able to explain all electronic failures using existing test approaches [28, 68, 77, 102]. An example is AUDI, which reported that from all its electronic failures, only 35% can be mapped using existing approaches, while about 41% are not yet understood [68]. For example factors such as bit line coupling [10, 11] can occur, which is the development of small coupling voltages on adjacent bit lines that can influence proper sense amplifier operation. In fact, bit coupling and the resulting crosstalk noise is strongly considered as a limiting factor in designing high speed, low power SRAM devices [71]. This has a huge impact on the faulty behavior of the memory, potentially causing readily detectable memory faults to become undetectable with several memory tests.

Thus, memory tests must continually evolve to investigate, model and develop appropriate detection conditions and test algorithm detecting, diagnosing or locating such resulting complex faulty behavior in memory devices [9, 52, 50]. In addition, such evolving test algorithms are required to run at minimal test times and incur no significant costs compared to existing memory tests.

## 1.3 Contributions and scope of thesis

In response to the challenges posed to memory testing due to increased memory density as a result of reduced chip size discussed in Section 1.2.3, this thesis presents an investigation of the complex faulty behavior induced by parasitic fails in deep sub-micron memory devices.

The thesis presents the analyzes, modeling, simulation, evaluation and validation of the impact of parasitic component on the faulty behavior of memory devices. It presents new test methodologies developed and memory tests generated to appropriately detect memory fails in the presence of such parasitic effects.

#### 1.3.1 Specific contributions

In a nutshell, the main contributions of this thesis are the following:

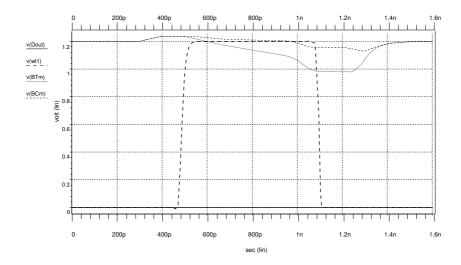

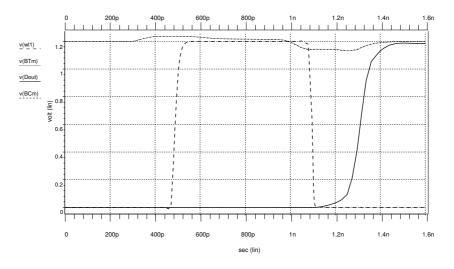

- This thesis presents a theoretical framework that models bit line (BL) parasitic

capacitance, and the effect of capacitive BL coupling on the faulty behavior

of the memory cell array. The thesis validates this behavior theoretically and

through electrical SPICE simulations.

- 2. Neighboring cells can influence the faulty behavior of defective cells through coupling. This thesis analyzes, simulates and evaluates the impact of parasitic bit line coupling and neighborhood coupling data backgrounds on the faulty behavior of SRAMs. It validates the analysis through defect injection and circuit simulation of all possible spot defects in the memory cell array.

- 3. The thesis investigates and establishes the worst case coupling backgrounds required to induce worst case coupling effects in deep sub-micron devices. It presents the conditions necessary to ensure proper detection of memory faults, while taking BL capacitive coupling into consideration.

- 4. The fault coverage of otherwise efficient memory tests can be dramatically reduced due to the influence of bit line coupling. The thesis clearly demonstrates the inadequacies and limitations of several well-known industrial tests in detecting memory faults in the presence of capacitive bit line coupling effect.

- 5. The thesis presents March SSS, March SSSc and March m-MSS, which target and detect all single and two-cell static faults in the presence and absence of BL coupling for any possible spot defect.

- 6. Memory test optimization can significantly reduce test complexity and cost, while retaining the quality of the test. This thesis introduces a systematic approach for developing optimized tests for memory faults in the presence of bit line coupling. It shows how to identify the required coupling backgrounds for all static memory faults, and presents March BLC, an optimized test that

detects all static memory faults in the presence of BL coupling.

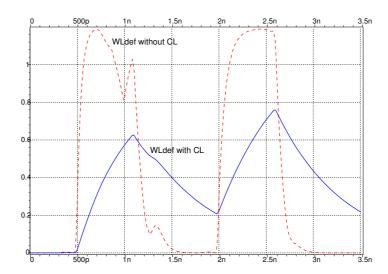

7. The thesis investigated and analyzed the impact of parasitic node capacitance on defective resistive nodes. The resultant effect referred to as parasitic memory effect can induce dynamic changes in the electrical behavior of the circuit thereby necessitating faults. The thesis presents the modeling of parasitic memory effect in memories. It demonstrates that the faulty behavior in the memory is exacerbated in the presence of parasitic node capacitance; something that reduces the fault coverage of current memory tests, and increases the DPM rate.

8. Parasitic node capacitance and faulty node voltage as components of a defective node can induce serious parasitic effects on the electrical behavior of the memory. This thesis analyzed, evaluated and characterized parasitic memory effect, and the variation of the floating node voltages on the faulty behavior of the memory. In fact, it demonstrates that the detection of memory faults is not determined by the value of the defect resistance alone, but is significantly influenced by the parasitic components of the defective node; something that is often not accounted for during memory testing. It presents the detection conditions for faults in the presence of parasitic memory effect, and finally presents March SME, which detects all targeted faults in the presence of parasitic memory effect.

#### 1.3.2 Scope of work

In this thesis, the main contributions are focused on SRAMs. All spot defects namely, opens, bridges and shorts have been analyzed and evaluated. The work also targeted functional fault models for all single-cell and two cell faults.

#### 1.4 Thesis outline

The work reported in this thesis is structured in seven chapters. This section provides a brief insight into each of the chapters and the general organization of the thesis.

Chapter 2 presents modeling of memory devices. It discusses the different levels of modeling namely, behavioral, functional and electrical modeling.

Chapter 3 introduces the concept of faults, describing the fault models, fault primitives and notations. It also explains the concept of memory testing, march tests and march test notations.

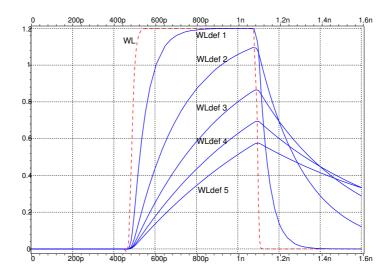

Chapter 4 presents parasitic bit line coupling effects. It extensively provides a theoretical framework for bit line coupling effect, a modeling of parasitic bit line capacitance and the impact of bit line coupling on the faulty behavior of SRAMs.

1.4 Thesis outline 15

Chapter 5 introduces the concept of parasitic memory effect. It presents a model for this effect and presents the analysis and evaluation of the impact of parasitic memory effect on the faulty behavior of SRAMs.

Chapter 6 presents memory testing for parasitic fails. It presents a systematic approach used to develop march tests to detect faults in the presence of bit line coupling effect, and an optimization technique that generates an optimized test to detect such faults. Finally, the chapter introduces a testing technique, and test that detects faults in the presence of parasitic memory effect.

Chapter 7 lists conclusions and recommendations of this thesis, and possible future work.

|         | _   |   |

|---------|-----|---|

|         | ٠ ) | ) |

| Chapter |     |   |

| Onaptor |     |   |

# Modeling memory devices

memory device is a group of interacting, interrelated, or interdependent parts forming a whole to achieve the storage and retrieval of stored data. Generally, testing a device can be done in different ways. One way is by physically inspecting the device with a view to identifying defects or anomalies between the inspected system and the correct version of the system. However, for semiconductor devices this method of testing will entail inspecting internal structures of the device, which is both cumbersome and error prone, and therefore unrealistic.

Another method of testing involves creating a model, which is an abstraction of the real system. This is done by adequately representing the essential characteristics or functional blocks of the device for which changes can significantly impact the device. Creating an abstraction is a mechanism and practice to reduce and factor out details so that one can focus on a few concepts at a time; or a generalized, condensed, and simplified concept derived from a more complex situation. It is a part representation of some whole. In this way, the behavior of the model can be compared with the actual behavior of the device with the intent of establishing the presence of anomalies or faults. Figure 2.1 shows a simplified general model, where input(s) are introduced and output(s) obtained. In brief,

A model is a representation of a system that allows for investigation of the properties of the system and, in some cases, prediction of future outcomes. It is an abstraction of the actual system under consideration.

Consequently, a memory model abstracts the memory sub-system of the semiconductor device, and contains representations in an appropriate approximation of the device. Using models in semiconductor testing has several advantages. One such advantage is that it provides clarity on the structure and functional behavior of the system. This clarity simplifies the test method, because it allows specific focus on functional blocks of the system, instead of an observation of the system as a whole. Another advantage is that due to its support for a targeted or pre-defined scope of

Figure 2.1: A block diagram of a general model

coverage, it saves test time and is invariably less expensive.

A device can be modeled at different levels of abstraction. A level of abstraction refers to the extent of details (for example, functional blocks or detailed components connections) that is revealed by a model. The models that exist categorized by their different levels of abstraction are geometrical, logical, electrical, functional and behavioral models. The lower the level of abstraction of a model, the more representative it is of the device.

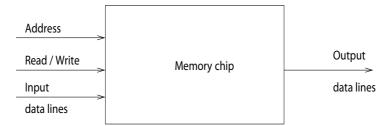

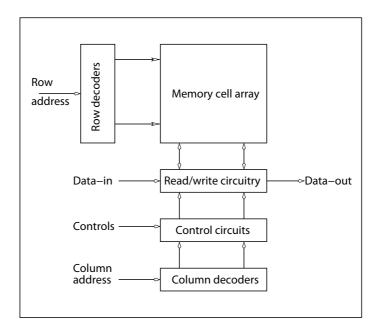

Figure 2.2 depicts a typical memory chip model. The inputs to the model include the address, which indicates the cell to be accessed, a read/write switch showing the kind of operation to be performed on the cell and input data lines that provide data in the case of a *write* operation. The outcome is observed through the output data lines. Brief descriptions are given below on the different kinds of models.

The rest of this chapter describes the various types of semiconductor memory models and their characteristics.

## 2.1 Semiconductor memory models

For semiconductor devices, models are often used to investigate faults. The extent to which a model is put to use can be determined based on the model's level of abstraction, for example whether it can be used for *fault detection* or for *fault localization*.

*Fault detection* refers to the ability to establish the presence of a fault in a given functional block of a DUT due to an observed anomaly in its behavior.

Fault localization is the ability both to establish the presence of a fault and to identify the exact location of the fault (example component). Having a knowledge of the internal structure of the device is essential for fault localization.

Brief descriptions of the different models are given as follows.

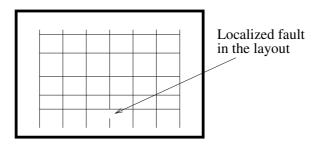

• **Geometrical models**. At this level of abstraction, details such as the layout implementation of the system is known, for example, line distances between the electrical components, as well as general system's layout are included. This

Figure 2.2: A block diagram of a memory chip model

Figure 2.3: Geometrical model

model makes for good identification of faults based on the manufacturing process and provides insight into the aging process of components. A diagrammatic representation of this model is depicted in Figure 2.3.

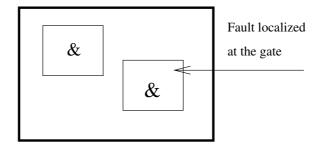

• Logical models. Modeling a system based on the logic gates in which Boolean expressions are used to mimic the targeted system's function yields logic models. The main aim of a logic model is to localize faults resident in logic gates of a device. Because instead of logic gates, transistors and capacitors are used in manufacturing semiconductor memories, modeling faults using the logic gate will not provide a good correspondence to reality. A diagrammatic representation of this model is depicted in Figure 2.4.

Figure 2.4: Logical model

Figure 2.5: Electrical model

Figure 2.6: Functional model

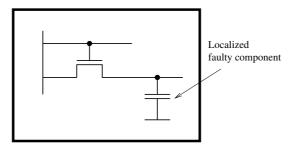

- **Electrical models**. In this model, a detailed description of the system specifications, based on their electrical components and internal structures' implementation are known and represented. The aim is to target and localize faults at the electrical components level of the system. A diagrammatic representation of this model is depicted in Figure 2.5.

- **Functional models**. This is also known as the gray-box model. Abstraction is based on the functional specifications of the device, with partial assumptions on its internal structure. This means that relevant system parts can be represented as *functional blocks* with definite functions, for instance, the memory cell array or address decoder in the memory. A diagrammatic representation of this model is depicted in Figure 2.6.

- **Behavioral models**. This is also known as a *black-box*, since little or nothing is known of its internal structure. Specifically, the internal structures of the system using this level of abstraction is unknown. The aim of this model is to represent the system only based on its specifications, therefore, only the system's behavior can be verified. For any given system, this model provides the highest level of abstraction of the system. This model can be cited as a special case of the functional model, with the condition that only one function is represented, which is the system's function as a whole. As a result of this, the behavioral and functional models can be referred to as special cases of the structural model, where the structural model describes a system as a number of interconnected functional blocks [2, 4]. A diagrammatic representation of this

Figure 2.7: Behavioral model

model is depicted in Figure 2.7.

In this thesis, focus will be on functional models. The reason is that at this abstraction level, both the system's functional specifications and partial assumptions on its internal structures (gray-box) can be made, which is sufficient for fault detection. However, some of the assumptions on the device would require some knowledge of the internal structures of the device, for example a cell's electrical structure. Therefore, some details of the electrical behavior have been included. In the rest of this chapter discussions on models of DRAMs and SRAMs are presented.

## 2.2 DRAM model and characteristics

This section introduces some DRAM characteristics namely, the size of the DRAM cell array, DRAM chip pin layout, the timing parameters and some specific DRAM instructions.

The logical organization of the memory array is made up of words (W), which comprises bits (B). Each bit represents a cell, thus, the total number of cells in the array is given by the number of bits B, multiplied by the number of words W. The internal structure comprises rows and columns.

Addresses are required to specify the right row and column locations. The number of address lines is the maximum number of bits necessary to specify either a row or a column address (a) is given by  $\lceil \log_2 max \{R, C\} \rceil$ . Addressing lines are represented as  $A_0, A_1 \dots A_{a-1}$ . For example, if a memory array has 1024 rows and 2048 columns, then  $a = \log_2 2048 = 11$  addressing lines. This means that address  $A_0 \dots A_{10}$  are required. Data lines are required for data input and output. These pins are usually merged in order to save pins. The number of pins required for data input-output is B, where B is the number of bits in a word (W). Control lines are required in order to control the input and output of the device, and to determine when the chip should read a row or column address. The most common of these control pins are the row access strobe  $(\overline{RAS})$ , column access strobe  $(\overline{CAS})$ , and the write enable control line

Figure 2.8: DRAM timing characteristics

$(\overline{WE}).$

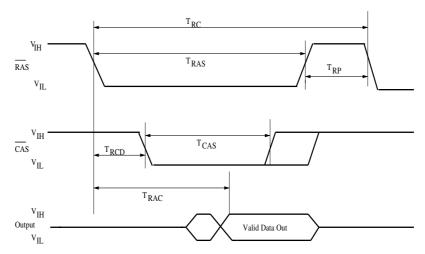

The timing characteristic of the DRAM chip provides the maximum and minimum delays for high and low edges of different signals and their duration to both read and write the needed signals to the output pin.

A typical illustration of the timing characteristics is provided in Figure 2.8. The  $\overline{RAS}$  to  $\overline{CAS}$  delay time represented as  $T_{RCD}$  is defined as the time between the low edges of the  $\overline{RAS}$  and  $\overline{CAS}$  signals. That is, the delay from the point  $\overline{RAS}$  is low to the time  $\overline{CAS}$  is low.

The least and highest values of the  $T_{\rm RCD}$  provide the least and highest delay, and are directed by the speed of the row and column decoders. The least value produces maximal stress<sup>1</sup> to the row access path, whereas the highest value stresses the column access maximally.

The precharge time is the time necessary before the device can accept a fall of the  $\overline{RAS}$  signal, in other words, how earliest the memory can be accessed again after having been accessed from the  $\overline{RAS}$  signal.

$T_{RC}$  is the time required to perform a random read/write cycle.  $T_{RC}$  is made up of  $\overline{RAS}$  precharge time,  $T_{RP}$  and the  $\overline{RAS}$  pulse width referred to as  $T_{RAS}$ .

Similarly,  $\overline{CAS}$  precharge,  $T_{\text{CAS}}$  is defined as how early the memory can be reaccessed after having been accessed from the  $\overline{CAS}$  signal. The least delay from the low edge of the  $\overline{RAS}$  signal to the time data becomes available on the output pins is known as the access time,  $T_{\text{RAC}}$ .

Finally, the refresh time, (not shown)  $T_{\text{REF}}$  refers to the maximum time which can pass before a fresh operation is required to keep the information in the memory cells.

<sup>&</sup>lt;sup>1</sup>Parameters, for example temperature, needed to test functionality within given specifications

The DRAM uses five main primitives for its commands. These primitives are:

- 1. *Read Rd*. This refers to the *read* command. Here, data in one of the sense amplifiers is moved to the data registers and finally to the data bus.

- 2. Write Wr. This is the write command. When given, the data in the data register is conveyed to the sense amplifiers as well as the memory cell array.

- 3. Activate Act. This is referred to as the activate command. In this case, a word line (WL) in the cell array is chosen. It then accesses a row of the memory cells. Coupled with this, an internal read command is done by moving the data from the row of memory cells to the sense amplifiers.

- 4. *Precharge Pre*. This is the *precharge* command. At this instance, any selected word line is deselected and the internal voltages are precharged to their already defined voltages.

- 5. *No Operation Nop*. This command indicates *no operation*. It does not alter the state of the memory but rather extends the time duration of any already issued command. Thus, its impact depends on the previously issued command and not in itself. The number of *Nop* issued is dependent on the specific timing characteristic of the given memory device.

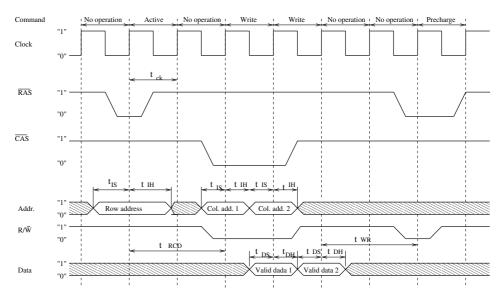

Nowadays, certain a variety of operational modes that enable DRAMs to provide more functional flexibility or higher performance are available. These include:

- Refresh operation In this case, all cells are rewritten using the same values they

contain in order to prevent loss of data as a result of naturally occurring leakage

currents. The refresh operation is issued to the memory by providing a special

sequence of values on the command bus that the DRAM interprets as a request

for refresh.

- 2. Fast page mode. This mode starts by issuing a row address to the memory, which opens a full row of memory cells (also called a memory cell). Any cell from this page can be read or written by providing only the column address of the specific cell to be accessed. Figure 2.9 depicts the timing diagram of the two operations performed in the fast page mode. The first is performed on a cell with col. add. 1 and thereafter, another write operation is performed on a different cell with col. add. 2. This mode of operation can increase the bandwidth of the memory by reducing the access time, since only column address part need to be provided at the inputs [79].

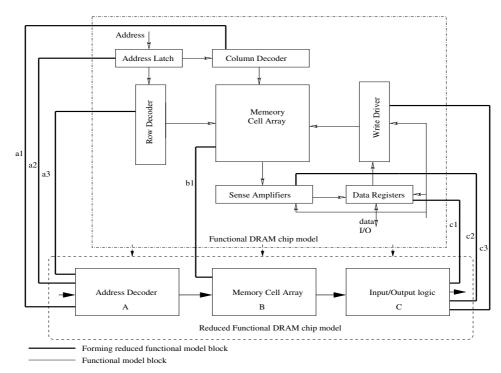

## 2.2.1 Functional DRAM chip model

The functional DRAM chip model shows the interacting functional blocks in the DRAM. A block diagram of this model is the same as shown in Figure 2.10. At this functional level, the internal structure of the memory that represents it as a collection

Figure 2.9: Timing diagram corresponding to DRAM fast page mode of operation

of interconnected functional blocks with separate functions are considered. Brief explanation of each block is given below:

- Memory cell array. This block occupies up to 60% [4] of the chip area and consists of the memory cells arranged close to one another in an array form in rows and columns. For instance, 1 Mega bits of memory with one million cells can be arranged as an array of 1024 rows and 1024 columns, 2048 rows and 512 columns and vice versa. The external DRAM behavior partly reflects this internal arrangement by requiring to split the address into columns and rows.

- *Control logic*. This is also known as the timing generator. The memory uses the control logic to regulate, activate and deactivate the required functional block when needed.

- Address decoders. This is used to decode the row and column addresses of a

cell in memory that needed to be referred to (addressed). The inputs are cell

addresses and the output is called word lines (WL) or the row decoder and

column select (CS) for the column decoder. Rows and columns are selected

by specific lines and a combination of selection of a row and a column results

in selecting a single word in the array.

- Sense amplifiers. This part of memory is used to identify the data stored within

the memory cells. Because the data in the cells are stored in capacitors, which

are prone to leakages, data in the cell need amplification so as to drive other

circuits in the memory. The interface between the sense amplifiers and the data

buffers is called the access device. A limited number of columns is connected

to the data buffers depending on the column address, while depending on the

Figure 2.10: Conversion from the functional to the reduced functional DRAM chip model

- operation that is performed, either the *read* or *write* buffer is connected to the sense amplifier.

- *Data-in/data-out buffers*. The data-in buffer is required to latch the input data and addresses while the data-out buffer stores the *read* output data and keeps it for the user on the data bus.

# 2.2.2 Reduced functional DRAM chip model

The reduced functional DRAM chip model is deduced from the functional model. In brief, the reduction is a result of merging functional blocks with similar functions together in order to reduce the overall blocks targeted. Figure 2.10 shows which functional blocks were combined to yield the three main blocks of the reduced functional DRAM chip model.

As shown in Figure 2.10, the row decoder, a3, and column a1 decoder are merged with the address latch denoted by a2 to form the address decoder, A, in the reduced functional model. This is because these three entities deal specifically with addressing. Likewise, the sense amplifier, c2, write logic, c3 as well as the data registers c1 are lumped together as the input/output logic, C, or read/write logic of the reduced functional model. The reason is that they similarly handle input and output data from the memory cell array. The memory cell array, b1, is retained as the only block in the memory cell array of the reduced functional model since no other block performs a similar function.

Thus concisely, a typical reduced functional model of a DRAM chip basically contains three main entities namely: The *input and output* or data read/write logic, the *address decoder* logic and the *memory cell array*. The reduced functional fault remains an authentic representation of the entire functional blocks covered by the functional model without any loss of information. Note that the fault coverage achieved by the functional model is the same as that of the reduced model since there is no information loss, i.e., no functional block is discarded.

Because localization of faults is not paramount but fault detection alone suffices; more an equivalent fault coverage obtained from the functional model is achievable using the reduced functional model henceforth, our focus and discussion including testing for the DRAM chip model will remain at the reduced functional chip level.

# 2.2.3 Electrical DRAM chip model

The DRAM chip is composed of individual memory cells. Each memory cell holds only one bit of information at a time, which could either be a "1" or "0", electrically represented by a different voltage level. Internally, the voltage level corresponding to any of the bits could be high or low. The representative voltage is dependent on

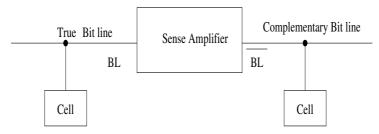

Figure 2.11: Cells connection to a sense amplifier

the location of the bit in the array and the architecture used. However, a high voltage represents the "0" bit whereas a low voltage represents a "1" bit. Basic cell structure is as follows:

Internally, the memory array consists of a number of rows and columns of words. These words can be accessed as a complete row only. Per row there is a WL, which determines if the row is connected to the sense amplifiers. The BL, are needed to connect to the sense amplifiers and get longer when the array increases in size. Raising or lowering the voltage on an entire line takes more time when the difference in voltage gets larger or when the line becomes longer.

Each cell in a row can be connected to one of the BL or  $\overline{BL}$  of a sense amplifier as illustrated in Figure 2.11. Which bit line a cell is connected to depends on the location of the cell in the memory array. Sometimes, odd rows are connected to BL (also known as true bit line) and even rows to  $\overline{BL}$  (also known as complementary bit line). In other designs, the sense amplifiers are located midway between the rows, so the left part of the row is connected to BL and the right part to  $\overline{BL}$ . A sense amplifier compares the voltage difference between its BL and  $\overline{BL}$ . When connecting a cell to a single bit line, the other bit line is usually connected to a dummy cell, in order to sense a valid voltage difference. Depending on the design, the internal structures of the DRAM cell could differ. These differences culminate in varied cell sizes and power requirements. Here we describe the different cell designs in order of their size and power requirement.

Four types of DRAM cell designs exist [94]. They can be distinguished following their internal structures, size and power requirement. These are:

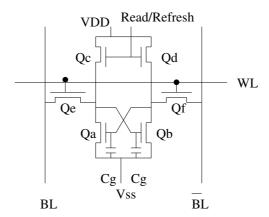

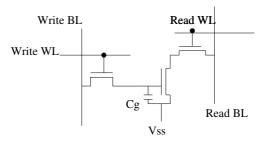

1. 6-device DRAM cell. This is as shown in Figure 2.12. In this cell structure, there are six clock enhancement mode transistors and two gate capacitors. Qc and Qd have their input gates connected to the read/refresh line. The stored charge in the gate capacitor, Cg, keeps the information dynamically. Note that two gate capacitors are used, that is, one for a logic "1" and the other when charged for a logic "0". During the read or refresh period, the transistive loads are enabled but thereafter disabled in order to avoid power dissipation. The 6-device structure is the most expensive in terms of area and power requirements.

Figure 2.12: Electrical structures of the 6-device DRAM cell

Figure 2.13: Electrical structures of the 4-device DRAM cell

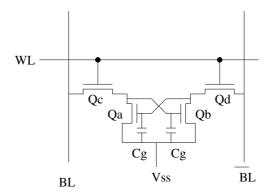

- 2. 4-device DRAM cell. This is as depicted in Figure 2.13. This cell structure consists of two capacitors and four enhancement mode cross-coupled transistors. As shown, transistors Qa and Qb form a latch, with the pass transistors Qc and Qd. This is an improvement over the 6-device cell since the two extra load devices (transistors),  $V_{\rm DD}$  and the read/refresh lines are removed in this structure, thus resulting in an area gain of over 50%.

- The charge kept in the gate capacitor Cg determines the device's ability to retain data. Two Cg are used: each for a charge of either logic "1" or "0". During its refresh period, the target row's word line, WL becomes high, while data is read through the already precharged BL. It is then sensed by the sense amplifier and BL is driven to cause the latch to be positioned in the required state. This refresh function is carried out by a dummy read cycle, since the read/refresh logic are eliminated.

- 3. 3-device DRAM cell. This cell structure is pictorially shown in Figure 2.14, being made up of three transistors and one capacitor. It stores its information or data as a charge in a single capacitor, Cg, thereby relegating the need for a

Figure 2.14: Electrical structures of the 3-device DRAM cell

second capacitor as in the case of the 4 and 6-device cell structures.

In the same way, need for one of the cross-coupled transistor pair is consequently eliminated because the logic stored in the in a cell is kept by the capacitor and a single transistor. However, although a single capacitor and transistor is enough to store its data, it still maintains two extra transistors because it has separate WL and BL. Its data is written by driving the write WL high and forcing the write BL to the desired value. Data can be read by precharging the read BL and then driving the read WL high. A refresh operation consists of a read, followed by a write through the write BL.

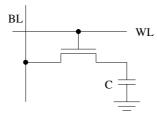

4. 1-device DRAM cell. This is the most widely known and deployed DRAM cell structure. It basically comprises of one capacitor, C and an enhancement mode transistor as depicted in Figure 2.15. The drain of the transistor is connected to the bit line, BL while the gate is connected to WL.

Before reading the cell, the bit lines are precharged with a voltage midway between the low and high voltage. Precharging bit lines decreases the settling time of the bit lines because the voltage difference between the connected bit line and the cell is smaller. After precharging, either BL or  $\overline{BL}$  is connected to the cell in order to read it. When reading, the contents of a cell are destroyed as the charge of the capacitor is leaked to the sense amplifier. This operation is called a destructive read. Because there is a single word line for the entire row, the contents of the entire row are destroyed. Therefore, all cells in the row are rewritten to retain the information. When data is written to cells in a row, all the cells in this row are rewritten. This happens because cells can only be accessed as a single row. The unmodified cells are read (which destroys their contents) and rewritten to keep their values.

A main advantage of the 1-device cell structure is that it has the lowest power requirement and size compared to the other cell structures. It also provides high density and low cost per bit memory cell.

Figure 2.15: Electrical structures of the 1-device DRAM cell

## 2.3 SRAM model and characteristics

An SRAM functional block diagram is depicted in Figure 2.16. As shown, the functional model consists of sub-functional blocks described in this section.

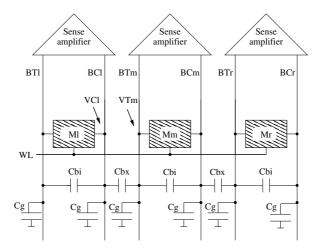

- The memory cell array: The memory cell array consists of several cells, which are addressed by an N-bit address. On the one hand, the row decoder is used for selecting the requested row also referred to as *word line (WL)* among several rows in the memory cell array.

- Address decoders: As shown in Figure 2.16, the row decoder receives its input, i.e., specified address from the *address latch* through the address lines, and then selects the required WL in the memory cell array. As the specified WL is selected, all the cells connected to the selected WL become active and thus, put their data on the BLs connected to each cell. On the other hand, the column decoder is used for selecting required BL or BL pair among several BLs or BL pairs that are on the selected WL.

- **Read/write circuitry:** The read/write circuitry consists of the the required devices to read or write a cell. The *data in* line conveys the data to be written to BT and BC, while the *data-out* lines conveys the data that has been read. The read circuitry is more complex than the write circuitry, importantly consisting of data registers and the sense amplifiers.

#### 2.3.1 SRAM memory cell

The SRAM memory array is made up of several individual cells, each connected to BLs and their corresponding WL. These memory cells form the most basic part of the memory. There are different types of SRAM cells based on the type of load used in the elementary inverter of the cell. We identify three types of SRAM memory cells namely, *four-transistor* (4T), *six-transistor* (6T), and *thin film transistor* (TFT) SRAM cells. Each of these SRAM cell types are described below as follows.

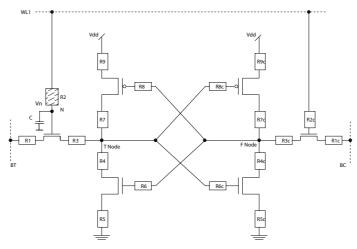

• **6T cell:** The 6T SRAM cell is depicted in Figure 2.17. The cell consists of six transistors, which are four NMOS transistors and two PMOS transistors The

Figure 2.16: SRAM functional block diagram

four transistors form two cross coupled inverters used in SRAM to hold the bits of memory. This cell offers better electrical performances in terms of speed, noise immunity and standby current than the 4T cell structure. 6T cell has better switching performance, a higher impedance, and is relatively insensitive to power supply variations [78, 42]. The work in this thesis has been done using the 6T cell structure.

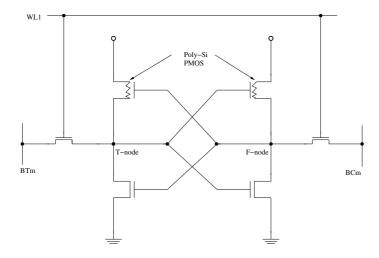

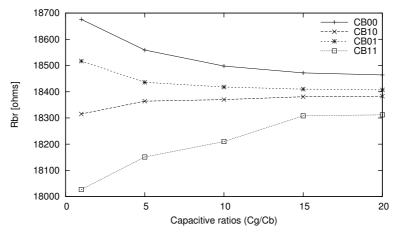

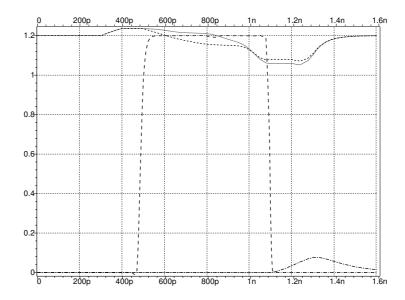

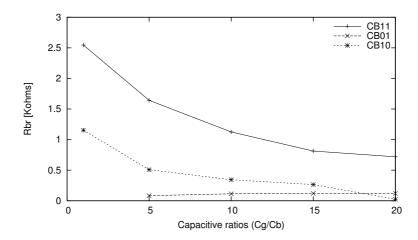

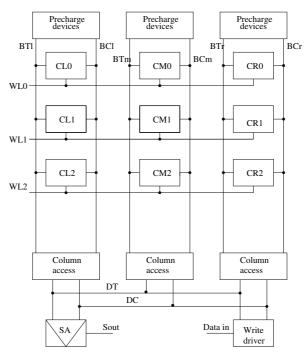

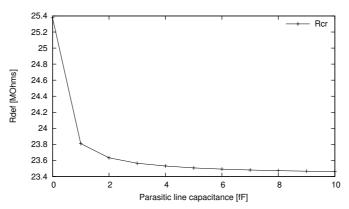

- 4T cell: The 4T SRAM cell is depicted in Figure 2.18. The 4T cell SRAM consists of four NMOS transistors and two poly-load resistors [40]. The most common SRAM cell consists of four NMOS transistors plus two poly-load resistors. Two NMOS transistors are pass-transistors. These transistors have their gates tied to the word line and connect the cell to the columns. The two other NMOS transistors are the pull-downs of the flip-flop inverters. The loads of the inverters consist of a very high poly-silicon resistor. This design used to be popular because of its size compared to a 6T cell, since the cell needs only four NMOS transistors. Despite its size advantage, the 4T cells have several limitations. These include the fact that each cell has current flowing in one resistor (i.e., the SRAM has a high standby current), the cell is sensitive to noise and soft errors because the resistance is so high, and the cell is not as fast as the 6T cell.